## B 0311/B 0418 **CARD PERIPHERAL** I/O CONTROLS

(For B700 Systems)

INTRODUCTION AND **OPERATION**

## Burroughs

FIELD ENGINEERING

# TECHNICAL MANUA

Copyright © 1973, 1975 **Burroughs Corporation** Detroit, Michigan 48232

AA472193

**FUNCTIONAL** DETAIL

> CIRCUIT DETAIL

MAINTENANCE PROCEDURES

**INSTALLATION** PROCEDURES

For Library Binder III Form 1068095

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions. л÷:

#### INDEX

#### Page No.

#### INTRODUCTION AND OPERATION - SECTION I

| A9418 General Description .   |   |  |   |   |   | 6 |

|-------------------------------|---|--|---|---|---|---|

| A9419 General Dexcription .   |   |  | ۰ | • | • | 6 |

| B700 Processor Interface      | • |  |   |   | • | 1 |

| Card-Reader-Punch Interface . |   |  | • |   | • | 1 |

| Glossary of Terms and Symbols |   |  | • |   |   | 8 |

| Introduction                  |   |  |   | • |   | 1 |

#### FUNCTIONAL DETAIL – SECTION II

| A/B9419 On-Line Interf     | ace |      |     |   | • |  |   |   | 1  |

|----------------------------|-----|------|-----|---|---|--|---|---|----|

| Clear Read Buffer .        | •   |      |     |   |   |  | • |   | 10 |

| Control Buffer             | •   |      |     |   |   |  | • |   | 5  |

| Data Interrupt             | •   | •    |     |   |   |  | • |   | 6  |

| Data or Status to Ext Li   | nes | ;    |     |   |   |  | • | • | 9  |

| Enable Flip-Flop .         |     |      |     |   |   |  |   |   | 5  |

| Motion Bits/Data Buffer    | ſ   |      |     |   |   |  |   |   | 2  |

| <b>OPREQ &amp; OPALERT</b> |     |      |     |   |   |  |   |   | 1  |

| SCCL Generation .          |     | •    | •   |   |   |  |   |   | 2  |

| Selected Hopper Empty      | Fli | ip-l | Flo | р |   |  |   |   | 7  |

| Status Interrupt Control   | l   |      |     |   |   |  |   |   | 8  |

| XFRCP Control .            | •   |      |     |   |   |  |   |   | 6  |

|                            |     |      |     |   |   |  |   |   |    |

#### CIRCUIT DETAIL - SECTION III

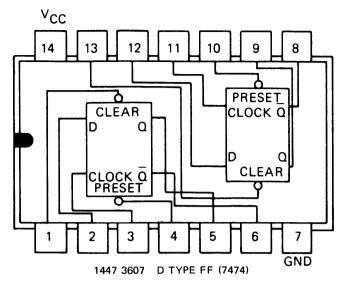

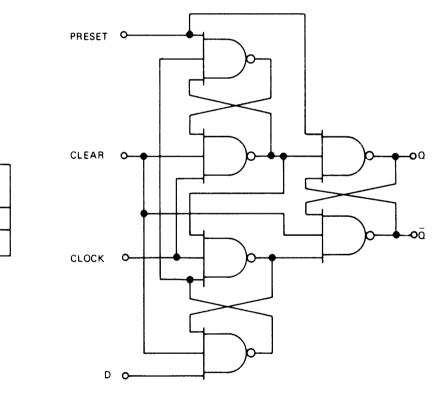

| DF Dual D-Type Flip-Flop      |    |   |    |      |      |   | 6 |

|-------------------------------|----|---|----|------|------|---|---|

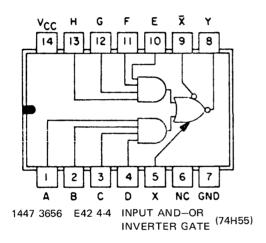

| E24 2x2x2x3 AND/OR Invert     |    |   |    |      |      |   | 3 |

| E42 4x4 AND/OR Invert         |    |   | •  |      |      | • | 3 |

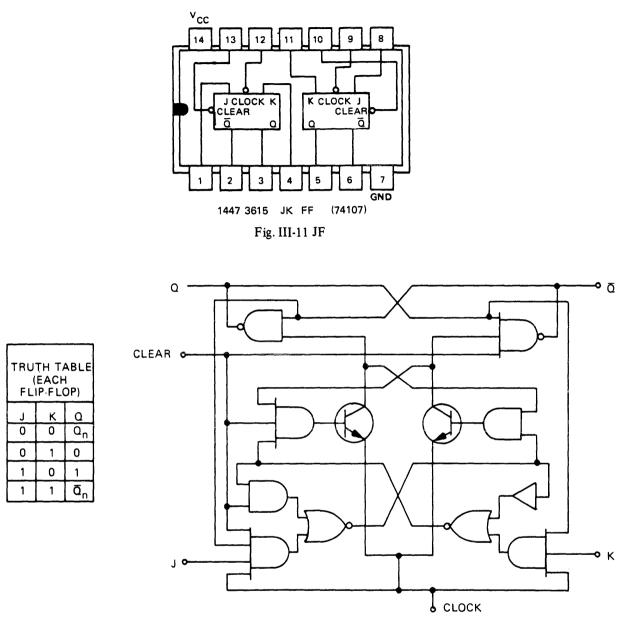

| JF Dual J-K Flip-Flop         | •  | • |    |      |      | • | 7 |

| Nand Gates                    |    |   |    |      |      |   | 1 |

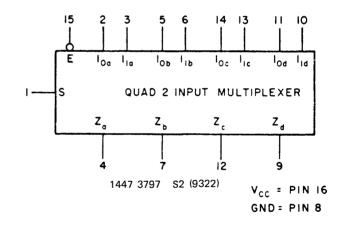

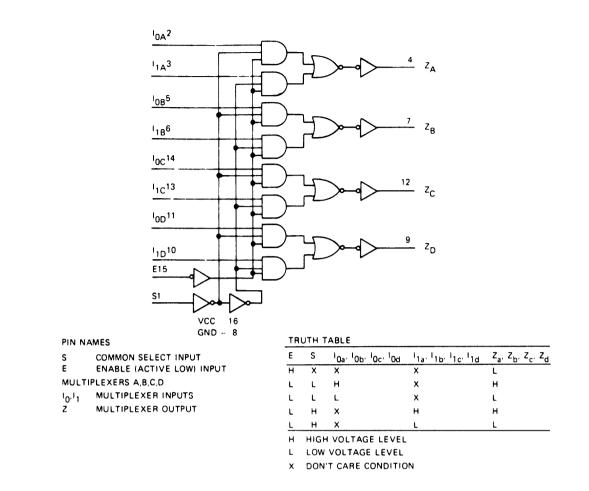

| S2 Quad-2-Input Data Selector | r. |   |    |      |      |   | 3 |

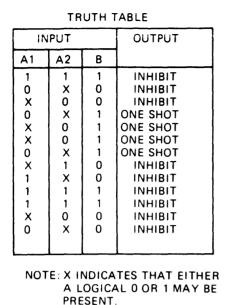

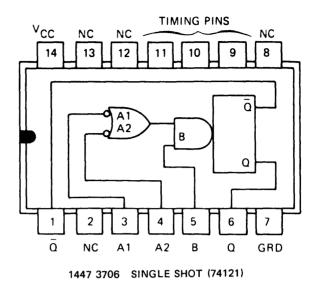

| SS Monostable M.V.            |    | • |    |      |      |   | 7 |

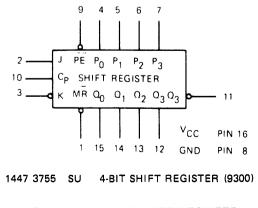

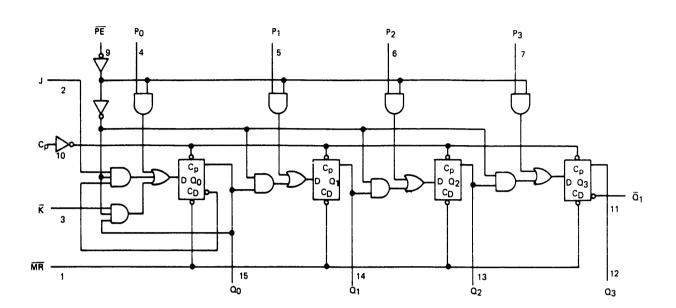

| SU 4-Bit Shift Register .     |    |   |    |      |      |   | 4 |

| T1 Hex Inverter               |    |   | •  |      |      |   | 2 |

| Transistor-Transistor Logic   |    | • |    |      |      |   | 1 |

|                               |    |   |    |      |      |   |   |

| MADENIANCE DROCEDID           | TO | 1 | OF | ATC. | NT X | 7 |   |

Page No.

#### MAINTENANCE PROCEDURES – SECTION V

| 96 Col Code S<br>RP96MTR |    |     |    |    |    |     |     |    | •   | •   | • | •  | • | 2<br>1 |

|--------------------------|----|-----|----|----|----|-----|-----|----|-----|-----|---|----|---|--------|

| INSTALLATI               | ON | I P | RO | CE | DU | JRI | Ξ — | SE | ECT | rio | N | VI |   |        |

| Adaptor Cable            | e  |     | •  |    |    |     | •   |    |     |     | • | •  |   | 1      |

| Installation             |    |     |    |    |    |     |     |    |     |     |   |    |   | 1      |

#### INTRODUCTION

This manual covers the B0311 and B0418 readerpunch I/O controls (IOC'S). The B0311 reader-punch I/O control is used to interface a B700-series processor with the 96-column A9119 and A9419 series card readers-punches. The B0418 reader punch I/O control is used to interface a B700 series processor with the 80-column A9418 card reader-punch. The B0311 and B0418 are identical in terms of hardware; they differ only in the software applications. In this manual, the B0311 and B0418 are referred to as the reader-punch IOC. The reader-punch IOC provides the necessary control functions for directing card read and card punch operations and also provides the buffering required for transferring information to and from the card reader-punch.

The reader-punch IOC consists of four plug-in chip boards (RC1, RC2, RC3, and RC4) which can be located in any of the interchangeable Device-Dependent Ports (DDP's) in the processor logic rack. (Refer to Section VI.) All operating voltages are derived from the internal power supplies of the processor cabinet.

#### CARD READER-PUNCH INTERFACE

The standard interface for the card reader-punch peripherals consists of two 25-pin connectors, serviced by two I/O signal cables. One connector and one cable are used for reader units; the other cable and connector are used for punch-print units. Any unit capable of reading, punching, and printing (such as the A9419-2) uses two cables and connectors.

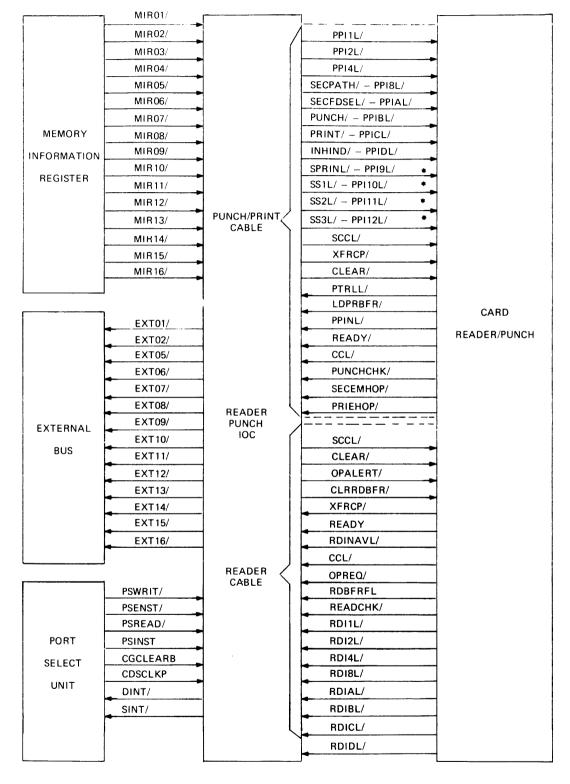

The pin assignments and signal names for the I/O connectors are shown in Figure I-1. It should be noted that the interface is capable of handling either 96- or 80-column card codes. Some of the signals are time-shared; that is, the line may transmit data or control signals at different points of time in the peripheral operation. Also note that, because either or both of the I/O connectors may be used with different styles of peripherals, some controls are transmitted through both I/O cables.

As shown in Figure I-1, control signals and data are interchanged between the reader-punch IOC and the card reader-punch peripheral. These signals are transferred as false levels and are defined in the signal glossary provided at the end of this section.

#### **IOC/READER-PUNCH OPERATIONS**

When the processor sends a control word, with the punch and/or print instruction bits set to the reader punch IOC, the IOC effects the feeding of the card in the visible station through the punch and print stations and to a selected stacker. When the card is approximately half-way through the punch station, the next card (if required) may be released from the selected hopper, read, and then left in the visible station.

The data required to be printed and/or punched is sent to the peripheral and loaded into a memory, called the punch buffer, prior to the card moving out of the visible station. If a separate print operation is required, the card pauses in the punch station while the processor transmits the required print data.

#### **B700 PROCESSOR INTERFACE**

As shown in Figure I-1, interface communications between the reader-punch IOC and the processor consists of input data lines MIR01/ through MIR16/, output data lines EXT01/, EXT02/, and EXT05/ through EXT16/, and various control signal lines. The reader-punch IOC/ processor interface control signals are as follows:

- a. Write Line (PSWRIT). When false, PSWRIT/ initiates a one-character data transfer from the processor to the reader-punch IOC.

- b. Read Line (PSREAD). When false, PSREAD/ initiates a one-character data transfer from the reader-punch IOC to the processor.

- c. Enable Status Line (PSENST). When false, PSENST/ initiates transfer of the status word from the readerpunch IOC to the processor.

- d. Instruction Line (PSINST). When false, PSINST/ indicates that the data on the MIR input data lines is a control word.

- e. Clear Line (CGCLEARB). When true, CGCLEARB clears all control flip-flops in reader-punch IOC.

- f. Data Interrupt (DINT). When false, DINT/ indicates to the processor that the reader-punch IOC is ready for another data-transfer operation.

- g. Status Interrupt (SINT). When false, SINT/ indicates that the reader-punch IOC has a status word for the processor.

- h. System Clock Pulse (CDSCLKP). When true, CDSCLKP indicates a 1-MHz clock pulse.

#### **IOC/PROCESSOR OPERATIONS**

The initiation of an information transfer between the processor and the IOC is controlled by the firmware and is the same for all devices. The distinction is made by the device address contained in the Base Register (BR1 or BR2) of the processor output select gates. The Port Select Unit decodes three-bit groups from the processor to completely define the operation that is to take place. The command field (nanobits 51 through 54) establishes whether the operation is to be a device read (DR) or a device write (DW). The four least-significant bits of BR1 or BR2 contain the specific device address. The most-significant bit of BR1

#### \* - SIGNALS PPI9L/ THROUGH PPI12L/ APPLY TO 80-COLUMN CARD PUNCH

### Fig. I-1 INTERFACE BLOCK DIAGRAM

|                     | MSB           |                   |       |                  |                  |                  |                  |                  |                      |                        |           |                           |                          |                          |                           | LSB                    |

|---------------------|---------------|-------------------|-------|------------------|------------------|------------------|------------------|------------------|----------------------|------------------------|-----------|---------------------------|--------------------------|--------------------------|---------------------------|------------------------|

|                     | 1             | 2                 | 3     | 4                | 5                | 6                | 7                | 8                | 9                    | 10                     | 11        | 12                        | 13                       | 14                       | 15                        | 16                     |

| CONTROL<br>WORD     | OPER<br>ALERT | DISABLE<br>STATUS | CLEAR | TERM             | STKR<br>SEL<br>4 | STKR<br>SEL<br>2 | STKR<br>SEL<br>1 | SEP<br>PRINT     | INH<br>INPUT<br>FEED | PRINT                  | PUNCH     | SECOND<br>FEED<br>SELECT  | SELECT<br>SECOND<br>PATH | LOAD<br>OUTPUT<br>BUFFER | UNLOAD<br>INPUT<br>BUFFER | START<br>CARD<br>CYCLE |

| 96 COL.,<br>6 BITS  |               |                   |       |                  |                  |                  | н н              |                  | · -                  |                        | DATA<br>5 | DATA<br>4                 | DATA<br>3                | DATA<br>2                | DATA<br>1                 | DATA<br>0              |

| 96 COL.,<br>8 BITS  |               |                   |       | -                |                  | -                |                  |                  | DATA<br>7            | DATA<br>6              | DATA<br>5 | DATA<br>4                 | DATA<br>3                | DATA<br>2                | DATA<br>I                 | DATA<br>0              |

| 80 COL.,<br>12 BITS |               |                   |       |                  | DATA<br>11       | DATA<br>10       | DATA<br>9        | DATA<br>8        | DATA<br>7            | DATA<br>6              | DATA<br>5 | DATA<br>4                 | DATA<br>3                | DATA                     | DATA<br>1                 | DATA<br>0              |

| STATUS<br>WORD      | DATA<br>REQ   | OPER<br>REQ       |       | DEV<br>ADDR<br>4 | DEV<br>ADDR<br>3 | DEV<br>ADDR<br>2 | DEV<br>ADDR<br>1 | DEV<br>ADDR<br>0 |                      | PRINT<br>LINE<br>LGTH. |           | SELECT<br>HOPPER<br>EMPTY | PUNCH<br>CHECK           | READ<br>CHECK            | CARD<br>CYCLE<br>COMPL    | NOT<br>READY           |

NOTE: DEVICE ADDRESS BITS OF STATUS WORD ARE INSERTED AT PSU.

#### FIGURE I-2. IOC INTERFACE WORD FORMATS

or BR2, in conjunction with the command type, determines whether the data transfer is a control word, data word, or status word.

The control and data words are sent over the same interface lines (MIR01 through MIR16). The instruction signal (PSINST) determines whether the word present on the MIR lines is a control word or data word. The presence of the instruction signal in conjunction with the write signal (PSWRIT) indicates the presence of a control word. The absence of the instruction signal in conjunction with signal PSWRIT indicates the presence of a data word. Likewise, the instruction signal determines whether a data word or status word is sent to the processor by the IOC. The presence of the instruction signal in conjunction with the read signal (PSREAD) enables a readout of the status word over the EXT data lines, whereas the receipt of signal PSREAD without the instruction signal enables the transfer of a data word to the processor over the EXT data lines.

When the IOC requires data from the processor, or when the IOC has data for the processor, it generates a data-interrupt (DINT) to indicate to the processor that I/O service is required. When some unexpected action occurs within the peripheral (for example: feed hopper empty or peripheral is not ready) the IOC generates a status-interrupt (SINT) to alert the processor. These two interrupts are under the control of the processor and may be enabled or disabled, as required.

The data exchanged between the processor and IOC is present on the EXT and MIR lines for one clock cycle. Because the card peripheral requires the data at different times in its operation, the IOC contains various buffers to hold the data until it is required by the peripheral.

The formats of the control, data, and status words for the reader-punch IOC are shown in Figure I-2.

#### Control Word

A control word is a 16-bit word which is sent to the reader-punch IOC by the processor to initiate a card operation. The control word contains various control bits which define the operation to be performed. The following is a description of the control bits:

Bit Function

- 1 Operator Alert. Unlocks the keyboard to allow keying into the input buffer and activates the READY indicator to alert the operator that the processor is ready to accept a keyboard input.

- 2 Disable Status. Disables status interrupts to the processor.

- 3 Clear. Activates the clear logic in the IOC.

- 4 Terminate. Terminates the buffer unload sequence.

- 5-7 Stacker Select. Used to specify the output stacker for the card sitting in the wait station as follows:

|                 | STKR   | STK    | STK  |

|-----------------|--------|--------|------|

| Stacker         | SEL4   | SEL2   | SEL1 |

| Error stacker   | 0      | 0      | 0    |

| 1               | 0      | 0      | 1    |

| 2               | 0      | 1      | 0    |

| 3               | 0      | 1      | 1    |

| 4               | 1      | 0      | 0    |

| 5               | 1      | 0      | 1    |

| 6               | 1      | 1      | 0    |

| Overflow        | 1      | 1      | 1    |

| Companyte Duint | T., 11 | . 1 1. | C .1 |

8 Separate Print. Indicates separate loading of the print buffer and the output buffer when both the print and punch control bits are present.

9 Inhibit Input Feed. Inhibits the input feed portion of the feed cycle. Permits the last card

of the job to be fed through the punch and print station.

- 10 Print. Enables printing of a card as it is advanced through the punch station.

- 11 Punch. Enables punching of a card as it is advanced through the punch station.

- 12 Secondary Feed Select. Enables feeding of cards from the secondary input hopper.

- 13 Select Secondary Path. When set in conjunction with the secondary feed select bit, causes the card fed from the secondary hopper to be stopped at the secondary wait stacker; otherwise, the card will go directly to the primary wait station without stopping at the secondary wait station.

- 14 Load Output Buffer. Enables IOC to load output buffer.

- 15 Unload Input Buffer. Enables IOC to unload input buffer.

- 16 Start Cycle Card. Initiates advancement of a card from the wait station through the primary or secondary path to the selected stacker.

#### Data Word

As shown in Figure I-2, the data words vary in length, depending on the particular model of card reader-punch being used. The data words are transferred on parallel lines; bit 16 is the least-significant bit.

#### Status Word

The status word is sent to the processor by the

reader-punch IOC to notify the processor that a failure or specific functional condition has occurred. The status word consists of a device status field (bits 10 through 16), an operator request bit (bit 2), and a data request bit (bit 1). Before the status word is sent to the processor, the Port Select Unit (PSU) inserts a device address field (bits 4 through 8). The following is a description of the status bits:

- Bit Function

- 1 Data Request. Indicates that the IOC is ready to receive or transmit the next character. This status condition follows the data interrupt signal to the processor.

- 2 Operator Request. Indicates that the operator has pressed a program select key and is ready to enter input data.

- 3 Not used.

- 4-8 Device Address. IOC address inserted by the PSU.

- 9 Not used.

- 10 Print Line Length. Card reader punch has 128-character printer capability.

- 11 Not used.

- 12 Selected Hopper Empty. Indicates no card is present in the selected hopper.

- 13 Punch Check. Punch error detected.

- 14 Read Check. Read error detected.

- 15 Card Cycle Complete. Card reader-punch has processed card and is ready to start another card cycle.

- 16 Not Ready. Card reader-punch is not in the ready state and is incapable of accepting and executing commands.

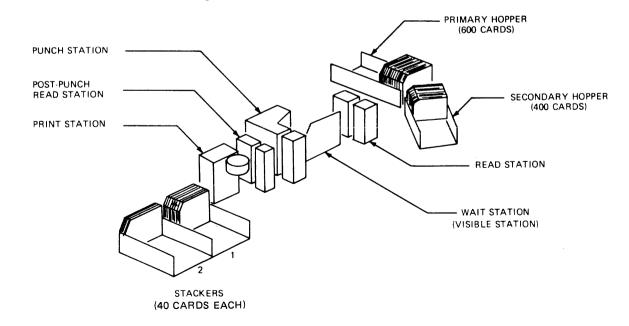

#### Fig. I-3 A9419-2 MECHANICAL LAYOUT

|       | Card Code                               |        | Card Code |

|-------|-----------------------------------------|--------|-----------|

| Char. | $\square [A   \infty   4   \infty   1]$ | Char.  |           |

| Space | 00 0000                                 | -      | 10 0000   |

| 1     | 00 0001                                 | J      | 10 0001   |

| 2     | 00 0010                                 | К      | 10 0010   |

| 3     | 00 0011                                 | L      | 10 0011   |

| 4     | 00 0100                                 | М      | 10 0100   |

| 5     | 00 0101                                 | N      | 10 0101   |

| 6     | 00 0110                                 | 0      | 10 0110   |

| 7     | 00 0111                                 | P      | 10 0111   |

| 8     | 00 1000                                 | Q      | 10 1000   |

| 9     | 00 1001                                 | R      | 10 1001   |

| :     | 00 1010                                 | I      | 10 1010   |

| #     | 00 1011                                 | \$     | 10 1011   |

| Q     | 00 1100                                 | *      | 10 1100   |

| 1     | 00 1101                                 | )      | 10 1101   |

| -     | 00 1110                                 | e<br>9 | 10 1110   |

|       | 00 1111                                 | ſ      | 10 1111   |

|       |                                         |        |           |

| 0     | 01 0000                                 | }      | 11 0000   |

| 1     | 01 0001                                 | А      | 11 0001   |

| S     | 01 0010                                 | В      | 11 0010   |

| Т     | 01 0011                                 | С      | 11 0011   |

| U     | 01 0100                                 | D      | 11 0100   |

| v     | 01 0101                                 | Е      | 11 0101   |

| W     | 01 0110                                 | F      | 11 0110   |

| x     | 01 0111                                 | G      | 11 0111   |

| Y     | 01 1000                                 | Н      | 11 1000   |

| Z     | 01 1001                                 | I      | 11 1001   |

| &     | 01 1010                                 | ¢      | 11 1010   |

| ,     | 01 1011                                 | •      | 11 1011   |

| %     | 01 1100                                 | <      | 11 1100   |

| _     | 01 1101                                 | (      | 11 1101   |

| >     | 01 1110                                 | +      | 11 1110   |

| ?     | 01 1111                                 | I      | 11 1111   |

|       |                                         |        |           |

| ,           | •          | :  | 3          | 4  | \$ | ٥           | ,          | 9        | •  | 3  | **         | 4   | 13          | 4  | *\$ | *    | 17   | *   | 73  | 20  | 21 | 32       | 11 | 24  | 15         | 26          | 27         | 25  | 29         | N   | 31 | 32 |

|-------------|------------|----|------------|----|----|-------------|------------|----------|----|----|------------|-----|-------------|----|-----|------|------|-----|-----|-----|----|----------|----|-----|------------|-------------|------------|-----|------------|-----|----|----|

|             | n          | μ  | 35         | ы  | v  | 34          | 13         | 40       | 41 | 42 | 43         | -   | 43          | 4  | 47  | 48   | 43   | S   | 31  | 52  | 1) | 5.0      | "  | 54  | <b>3</b> 7 | м           | 59         | ĸ   | •          | 62  | Ð  | u  |

|             | 65         | 64 | <b>8</b> 7 | 64 | "  | 73          | ħ          | n        | 73 | 74 | n          | 76  | n           | 78 | ",  | 80   | •    | 42  | ស   |     | 83 | 84       | 37 | 44  | •          | N           | <b>9</b> 1 | 1:  | "          | н   | •3 | 14 |

| B<br>A<br>8 | <b>1</b> 7 | ×  | 77         | rx | 9  | <b>4</b> 22 | <b>K</b> 1 | -54      | 47 | ×. | <b>N</b> 7 | -64 | '2 <b>9</b> | нa | 14  | 11 2 | £ 11 | 114 | "1  | 1:6 | ,  | •••      |    | 130 | ur.        | ш           | u)         | 2.  | 25         | 124 |    |    |

| 4 2 1 B A 8 | •          | :  | 3          | ٠  | 1  | •           | ,          | •        | •  | 4  | e          | ų   | u           | u  | 15  | *    | 17   | 48  | -1  | 23  | 2: | u        | 23 | 24  | 25         | N           | 27         | 11  | 29         | ю   | r  | »: |

| 4 2 1 B A 8 | u          | ч  | л          | ы  | 17 | 30          | 39         | <b>ب</b> | 41 | 42 | 43         | ••  | 45          | 4  | 47  | 48   | 4    | 50  | 31  | N   | 53 | 54       | 33 | 54  | 57         | 54          | 1,         | • > | <b>6</b> 1 | 62  | •) | •• |

| 4<br>2<br>1 | 41         |    | 67         | 4  |    | 70          | 7          | 72       | "  | 74 |            |     | 77          | 78 | 71  |      | 6.   |     | ••• | •   | •3 | <b>.</b> | ÷7 |     |            | <b>\$</b> 0 |            | 92  | •.         |     | •• | •• |

#### Fig. I-4 96 COLUMN CARD CODES

Page 6

#### Introduction and Operation

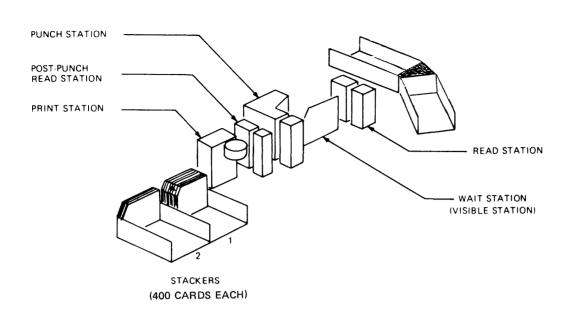

#### Fig. I-5 A9418-2 MECHANICAL LAYOUT

#### A9419 GENERAL DESCRIPTION

As stated previously, the B0311 IOC services the A9419 (96-olumn) card peripheral unit. In the on-line mode, the A9419 performs either independently, or in combination, any of the following functions:

- a. Read.

- b. Punch.

- c. Print (same data as punched).

- d. Separate print.

In addition to controlling the above functions, the processor can select the required hoppers and stackers for the card in process and may also permit data entry through the peripheral keyboard by the system operator. Figure I-3 shows the layout of the physical components of the A9419. Figure I-4 illustrates the 96-column card format. The physical components are as follows:

- a. Primary Hopper. The primary hopper has a capacity of 600 cards. The cards are placed in the hopper face forward, with column 1 to the left and the printing area across the top. The front card feeds into the machine first. The card follower holds the cards firmly against the feed rollers.

- b. Secondary Hopper. The secondary hopper has a capacity of 400 cards. The cards are also placed in the hopper face forward, with column 1 to the left and the printing area along the top of the first card visible. This visible card is the last card to feed into the machine.

- c. Read Station. The read station reads the data prepunched on input cards when in certain operating modes.

- d. Visible Station. Prior to entry into the punch station, the card is stopped in the visible station, where the

print and punch areas of the card can be seen. This is helpful when in the verify mode of operation because the card does not have to be removed to be read by the operator.

- e. Punch Station. Data is punched in the card three tiers  $\overline{\text{at a time. The card is then moved to the next column}$  pair that is to be punched.

- f. <u>Post-Punch Read Station</u>. This read station functions to detect punching errors that occur during an on-line operation. The data transferred to the punch memory is compared with the data read from the punched card. A non-comparison condition lights the PUNCH CHECK indicator.

- g. <u>Print Station</u>. The print station consists of a fourcolumn drum printer. A replaceable ink cartridge rides in contact with the drum to maintain a constant supply of ink on the drum characters.

- h. <u>Stackers</u>. Two stackers with a capacity of 400 cards each receive cards in the order they are fed. Stacker selection is determined by the various operating modes described later.

#### A9418 GENERAL DESCRIPTION

The A9418 (80-column) card peripheral unit is controlled by the B0418 IOC. In the on-line mode, the A9418 may be used to perform card punch and/or read operations. The processor can select the required hoppers and stackers for the card in process. Figure I-5 shows the layout of the physical components of the A9418-2. The function of these components is the same as described for the A9419-2. Figure I-6 illustrates the 80-column card format.

| NUMERIC<br>Graphic Card Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ALPHABETIC<br>Graphic Card Code                                                                                                                                                                                          | SPECI<br>Graphic C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AL<br>ard Code                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A $12-1$ B $12-2$ C $12-3$ D $12-4$ E $12-5$ F $12-6$ G $12-7$ H $12-9$ J $11-1$ K $11-2$ L $11-3$ M $11-4$ N $11-5$ O $11-6$ P $11-7$ Q $11-8$ R $11-9$ S $0-2$ T $0-3$ U $0-4$ V $0-5$ W $0-6$ X $0-7$ Y $0-8$ Z $0-9$ | ¢<br>•<br>(<br>+<br> <br>-<br>!<br>\$<br>*<br>)<br>;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>12<br>12-8-2<br>12-8-3<br>12-8-4<br>12-8-5<br>12-8-6<br>12-8-7<br>11<br>11-8-2<br>11-8-3<br>11-8-4<br>11-8-5<br>11-8-6<br>11-8-7<br>0-1<br>0-8-2<br>0-8-3<br>0-8-4<br>0-8-5<br>0-8-6<br>0-8-7<br>NONE |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | STUVWXYZ:#@;="#¢。<(+ -!\$*);¬/ ;%_>?<br>BBBBBBB<br>                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PRINT AREA<br>12 BIT                                                                                                                                                                                                                            |

| 1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1 <th></th> <th>1     1     1     1     1     1     1       2     2     2     2     2     2     2     2     2       3     3     3     3     3     3     3     3     3       3     3     3     3     3     3     3     3     3       4     4     4     4     4     4     4     4       5     5     5     5     5     5     5       5     5     5     5     5     5     5       5     5     5     5     5     5     5       6     6     6     6     6     6     6       7     7     7     7     7     7       7     7     7     7     7     7       7     7     7     7     7     7</th> <th>11 BIT<br/>0 BIT<br/>1 BIT<br/>2 BIT<br/>3 BIT<br/>4 BIT<br/>5 BIT<br/>6 BIT<br/>7 BIT<br/>8 BIT<br/>9 BIT</th> |                                                                                                                                                                                                                          | 1     1     1     1     1     1     1       2     2     2     2     2     2     2     2     2       3     3     3     3     3     3     3     3     3       3     3     3     3     3     3     3     3     3       4     4     4     4     4     4     4     4       5     5     5     5     5     5     5       5     5     5     5     5     5     5       5     5     5     5     5     5     5       6     6     6     6     6     6     6       7     7     7     7     7     7       7     7     7     7     7     7       7     7     7     7     7     7 | 11 BIT<br>0 BIT<br>1 BIT<br>2 BIT<br>3 BIT<br>4 BIT<br>5 BIT<br>6 BIT<br>7 BIT<br>8 BIT<br>9 BIT                                                                                                                                                |

Fig. I-6 80-COLUMN CARD BIT CODES

Introduction and Operation

#### GLOSSARY OF TERMS AND SYMBOLS

#### NOTE

In the schematics and backplane circuit list, many of the following signals are prefixed with RC. This indicates that they originate within the B0311 or B0418 logic.

| Signal or Term | Description                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------|

| ASR            | Address and Status Request. Nanoinstruction which causes the PSU to enable the status bits of the            |

|                | highest priority IOC generating an IRQ to the ERT lines, together with the address of that IOC, from the     |

|                | PSU.                                                                                                         |

| ACPONCL        | Power-on Clear. Signal from the AC control section of processor. Used to initially reset all logic at        |

|                | power-on time.                                                                                               |

| BRn            | Base Register n ( $n = 1$ or 2). One of two registers in processor (MCU) which controls the address lines to |

|                | select an IOC.                                                                                               |

| Bit14          | Decoded from MIR14 line.                                                                                     |

| Bit15          | Decoded from MIR15 line.                                                                                     |

| CCC/           | Card Cycle Complete Not. Indicates that a peripheral operation is in progress. Goes low when processor       |

|                | sends a control word to IOC, and remains low until end of peripheral operation.                              |

| CCL/           | Card Cycle Level Not. Interface signal from peripheral. Low while peripheral operation is in progress.       |

| CLEAR/         | Interface signal to peripheral (30 microseconds). Used to reset peripheral logic.                            |

| CLR/           | Clear Not. Used to reset most of the B0311 logic; developed from Processor CLEAR line.                       |

| CLRRDBFR/      | Clear Read Buffer Not. Interface signal to peripheral. When low, indicates that processor does not desire    |

|                | to read any more data from peripheral input memory.                                                          |

| CSF            | Cycle Start Flip-flop. Used to control CCC/.                                                                 |

| DATRD/         | Data Read/. Developed from READ*INST/.                                                                       |

| DINT           | Data Interrupt.                                                                                              |

| DISTAT         | Disable Status.                                                                                              |

| ENABLE         | Output of Interrupt enable flip-flop.                                                                        |

| ENST           | Enable Status. (Refer to PSENSTn.)                                                                           |

| EXTn           | Processor External (input) data bus line.                                                                    |

| INHCLK/        | Inhibit Clock Not. Single, low-going clock pulse used to initiate SCCL when processor sends a control        |

|                | word to IOC.                                                                                                 |

| INHINFD/       | Inhibit Input Feed Not. Interface signal to peripheral. When low, prevents peripheral from feeding a card    |

|                | from its input hoppers.                                                                                      |

| INST           | Instruction bit. (Refer to PSINST.)                                                                          |

| INST*WRITE     | Indicates that processor is sending a control word to IOC.                                                   |

| IOC            | I/O Control.                                                                                                 |

| IWNB4          | Instruction Write Not Bit 4. Indicates that processor is sending a control word that does not specify        |

|                | terminate operation.                                                                                         |

| LDPRBFR/       | Load Print Buffer Not. Interface signal from peripheral. When low, indicates that the processor may send     |

|                | separate print data.                                                                                         |

| LOB            | Load Output Buffer. Developed from MIR14; indicates that processor wishes to transmit either punch or        |

|                | print data (or both) to peripheral.                                                                          |

| MIR            | Memory Input Register. Data output bus from processor (to memory or peripheral devices).                     |

| OPALERT/       | Operator Alert Not. Interface signal to peripheral to enable entry of data at peripheral keyboard.           |

| OPALF          | Operator Alert Flip-flop.                                                                                    |

| OPREQ/         | Operator Request Not. Interface signal from peripheral. When low, indicates that operator wishes to          |

|                | input data.                                                                                                  |

| PONCL          | Power on Clear. (Refer to ACPONCL.)                                                                          |

| PPInL/         | Punch or Print Information n Level. (where $n = 1$ through D Hex, or 1 through 12 Dec.) Interface data       |

|                | lines to peripheral.                                                                                         |

| PPINL/         | Punch or Print Information Needed Level. Interface signal from peripheral. When low, indicates that          |

|                | peripheral is ready to load a character for punching or printing.                                            |

#### GLOSSARY OF TERMS AND SYMBOLS (CONTINUED)

| Signal or Term       | Description                                                                                                                                                                                                                                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRIEHOP/<br>PRINT/   | Primary Empty Hopper Not. Interface signal from peripheral; low when primary hopper is empty.<br>Interface signal to peripheral. When low, indicates that processor wishes to print data during the subsequent card cycle.                 |

| PSENT                | Port Select Enable Status. Control line from PSU to IOC. Used to put status data on the EXT lines when processor executes an ASR.                                                                                                          |

| PSINSTn/             | Instruction bit from PSU, true when MSB of selected Br equals 1. When true during a device write, indicates that data on the MIR lines is a control word. When true during a device-read, calls for status, rather than data from the IOC. |

| PSREADn/             | Port Select Read n ( $n = IOC$ address). Read line from PSU to IOC.                                                                                                                                                                        |

| PSWRITEn/            | Port Select Write n ( $n = IOC$ address). Write line from PSU to IOC.                                                                                                                                                                      |

| PSU                  | Port Select Unit.                                                                                                                                                                                                                          |

| PTRLL/               | Print Line Length Not. Interface signal from peripheral. When low, indicates device has 128 print positions, as opposed to 96.                                                                                                             |

| PUNCH/               | Interface signal to peripheral. When low, indicates that processor wishes to punch data during the subsequent card cycle.                                                                                                                  |

| RC1 through RC4      | B0311 IOC printed circuit board types 1 through 4.                                                                                                                                                                                         |

| RDBFRFL/             | Read Buffer Full Not. Interface signal from peripheral. When low, indicates presence of data in the input                                                                                                                                  |

| RDn/L                | memory.<br>Read Data n Level. (Where n = 1 through D Hex, or 1 through 12 Dec.) Interface data from peripheral.                                                                                                                            |

| RDINAVL/             | Read In Available Not. Interface signal from peripheral. When low, indicates that a character is present                                                                                                                                   |

|                      | on the data lines. (RDnL)                                                                                                                                                                                                                  |

| READ                 | Refer to PSREADn.                                                                                                                                                                                                                          |

| READCHK/             | Read Check Not. Interface signal from peripheral. When low, indicates that an error was detected during                                                                                                                                    |

|                      | a card-read operation.                                                                                                                                                                                                                     |

| READY/               | Interface signal from peripheral. When low, indicates that device is in the on-line mode.                                                                                                                                                  |

| RESET/               | Low-going signal used to reset the motion control data in the B0311 after the peripheral has received it.                                                                                                                                  |

| SCC1-2-3F<br>SCCL/   | Timing control flip-flops for generation of SCCL.                                                                                                                                                                                          |

| SUCL/                | Start card cycle level not. Interface signal to peripheral to strobe motion data to device and commence a card cycle.                                                                                                                      |

| SCCLF                | Control flip-flop for SCCL.                                                                                                                                                                                                                |

| SCLK                 | System clock.                                                                                                                                                                                                                              |

| SECEHOP/             | Secondary Empty Hopper Not. Interface signal from peripheral; low when hopper is empty.                                                                                                                                                    |

| SECPATH/             | Second Path Not. Interface signal to peripheral. When low, instructs peripheral to feed the next card over the secondary path (only devices with two feed paths).                                                                          |

| SELHOP               | Selected Hopper (empty). When true, indicates that hopper selected by the processor is empty.                                                                                                                                              |

| SINT                 | Status Interrupt.                                                                                                                                                                                                                          |

| SINTF                | Control flip-flop for SINT.                                                                                                                                                                                                                |

| SPRINL/              | Separate Print Level Not. Interface signals to peripheral. When low, indicates that processor requires                                                                                                                                     |

| SS1 2 /I /           | data, other than that which is punched, to be printed on the card.                                                                                                                                                                         |

| SS1-2-4L/<br>ST+INRD | Stacker Select n Level Not. Interface signals to peripheral. Used to select one of six receiving stackers.<br>Status or Instruction Read. Used to gate status data to EXT lines.                                                           |

| SECFDSEL/            | Secondary Feed Select No. Interface signal to peripheral. When low, instructs device to feed the next                                                                                                                                      |

| SLCI DBLE            | card from the secondary hopper.                                                                                                                                                                                                            |

| SU                   | Storage Unit. IC chip type.                                                                                                                                                                                                                |

| UIB                  | Unload Input Buffer Developed from MIR15. Indicates that processor wishes to read data from the next                                                                                                                                       |

|                      | card fed to the visible station.                                                                                                                                                                                                           |

| WRITE                | Refer to PSWRITEn/.                                                                                                                                                                                                                        |

| XFRC1-2F             | Timing control flip-flops for generation of XFRCP/.                                                                                                                                                                                        |

| XFRCP/               | Transfer Clock Pulse Not. Interface signal to peripheral. Used to strobe individual characters to the                                                                                                                                      |

| XFRCPF               | device.<br>Control flip-flop for XFRCP/.                                                                                                                                                                                                   |

|                      |                                                                                                                                                                                                                                            |

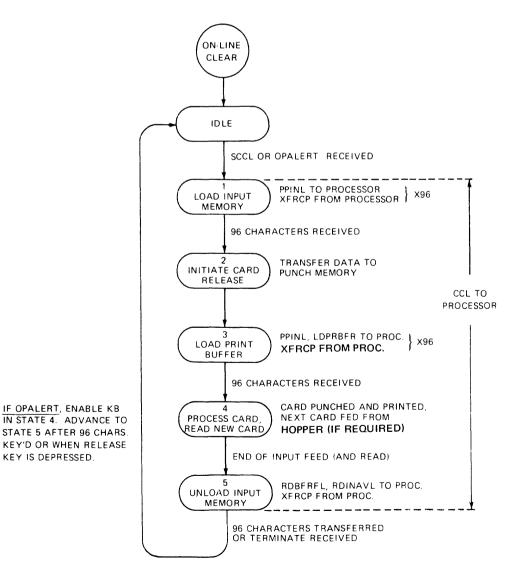

#### A/B9419 ON LINE INTERFACE

In order to understand the functions of the B311 IOC it is necessary to understand the basic operation of the A/B9419 on-line interface.

The interface logic within the A/B9419 contains a six-state Control Counter as represented in Fig. II-1, these states, for reference, are numbered 0 through 5.

State 0 represents the idle state of logic. While it is in state 0 the IOC may condition the control lines to the peripheral and then make the signal SCCL/ false. When the peripheral receives SCCL from the IOC, it accepts the data on the control lines, which correspond to Control word bits 1 and 5 through 12, into some buffer flip-flops, and advances to state 1. As it goes to state 1 the signal CCL/ is made false to indicate to the IOC that a Card cycle is in process.

Note that CCL/ remains false until the Control Counter returns to state 0. CCL is returned to the IOC approximately 12 microseconds after SCCL/ goes false.

In State 1 the peripheral is ready to receive data which is to be loaded into its input memory. It then makes the signal PPINL/ false to indicate that it is ready to receive one character.

Upon receipt of PPINL the IOC sends a data interrupt (DINT) to the processor which will respond by sending one character to the IOC. The IOC then buffers the data, conditions the data lines to the A/B9419, resets the DINT and sends XFRCP to the peripheral.

When the peripheral receives XFRCP it resets PPINL and loads the character into its input memory. After loading is completed the peripheral will again make PPINL/ false to indicate that it is ready to receive the next character.

The above procedure is then repeated, for a total of 96 operations, so as to load a complete card image into the input memory of the A/B9419. When 96 data transfers are completed the logic advances to state 2.

In State 2 the logic initiates the release of a Card, from the Visible Station, to the Punch registration stop and advances to State 3. At about this time the data in the input memory is transferred to the Punch memory.

In State 3, if Separate Print was called for in the original Control word (MIR08), the peripheral is ready to receive data to be loaded into its Print Buffer. It then makes the signal PPINL/ false to indicate to the IOC that it is ready to receive a character. However at this time it also makes LDPRBFR/ false to indicate that the data is required for printing.

When the IOC receives PPINL it then, as in the State 1 operation, sends DINT to the processor. The operation is then exactly the same as the State 1 operation where the input memory was loaded. Again 96 data transfers are required to fill the Print buffer. When the data transfer is completed the logic advances to state 4.

As the logic advances to state 4 the card, which was last left at the Punch registration stop, continues its movement through the Punch and Print Stations, where it is processed, and on to the stacker selected in the original control word (MIR 05, 06, 07). When this card is approximately halfway through the Punch station the A/B9419 initiates an Input feed cycle which feeds the next card in the input hopper (selected in the original control word, MIR 12) through the Read station and into the Visible station. Any data pre-punched in the Card is now in the input memory and available for the Processor. At the completion of the read operation the logic advances to state 5.

In State 5 the peripheral is ready, if required, to unload its input memory to the processor. It then places the first character onto the data lines and makes RDINAVL/ and RDBFRFL/ false to alert the IOC. If "Unload Input Buffer" was requested in the original Control word the IOC will send DINT to the Processor. The Processor will respond by executing a device read to call the data from the IOC.

The IOC will then reset the DINT put the character onto the EXT lines and send and XFRCP to the peripheral to call for the next character.

When the peripheral receives XFRCP it resets RDINAVL and shifts the next character to the data lines. When shifting is completed the peripheral again makes RDINAVL/ false and the above process is repeated. The data transfer operation will then consist of 96 operations as described above to unload a complete card image to the Processor.

If the Processor does not require a complete card image it may terminate this operation, after receiving the required number of characters, by sending a Control word to the IOC with MIR 04 set. The IOC will then make CLRRDBFR/ false which causes the peripheral to cease transmitting data. The A/B9419 interface control counter returns to state 0 and the signal CCL/ goes true to indicate that the Card cycle is completed.

#### **OPREQ & OPALERT**

Built into the logic of the A/B9419 and the B311 IOC is the ability to permit the system operator to key-in additional data at the peripheral keyboard while the peripheral is in the On-line mode.

If the operator depresses program key 1 the A/B9419 will make OPREQ/ false. The IOC will then generate a status interrupt (SINT) to alert the Processor.

When the Processor interpreter is ready it may send a Control word with MIR01 true. This causes the IOC to make OPALERT/ false to the peripheral.

When the peripheral receives OPALERT the Control counter states advance through to State 4. (See Fig. II-1.) At this time the peripheral KB is enabled and the Ready indicator lamp, on the peripheral, flashes to indicate to the operator, that the KB is available.

After 96 characters have been indexed, or when the operator depresses the Release key, the Control counter advances to state 6 where the data may be unloaded to the Processor, as in a normal read operation.

NOTE: This function is not presently used by the B705/711 system software.

#### MOTION BITS/DATA BUFFER

MIR05 through 16 (ref. Fig. I-2) can either contain information related to a card process (motion bits) or data to be sent to the peripheral for either Punching or Printing.

Whenever the Processor executes a device write to the IOC MIR05 through MIR16 are loaded into a buffer consisting of three S.U. IC chips located on RC2 and RC3.

As soon as the data is loaded into the buffer it is made available to the peripheral. Fig. II-2 shows the buffers. When the WRITE signal goes true, from the PSU, it permits one clock pulse to strobe the MIR data into the buffers. In the case of a Control word the data remains in the buffers until the CCL signal is received from the peripheral to indicate that it has received the motion bits, at this time the signal RESET/ will go false to clear the SU chips through the master reset. In the case of Data characters the data remains in the buffer until the Processor executes a device write to send the next character to the IOC.

NOTE: The signal RESET/ will also go false to clear the buffer whenever the Processor is cleared. XFRCP is the signal which alerts the peripheral to accept data on the interface lines (see Fig. II-8).

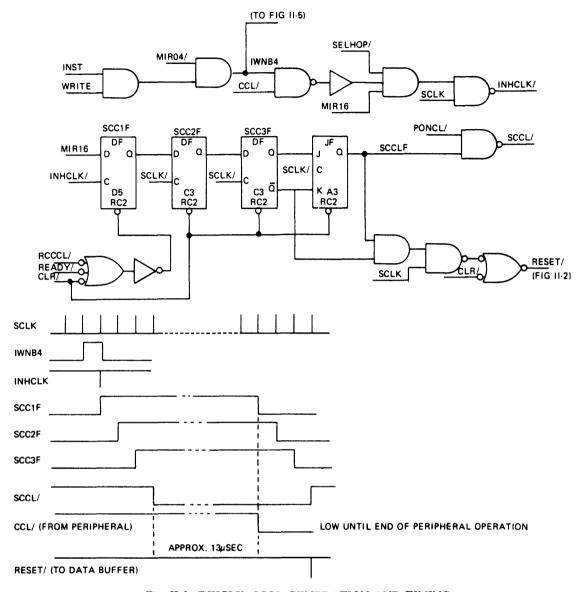

#### SCCL GENERATION

The interface logic in the A/B9419 requires that the motion control data be stable on the interface for 1 microsecond prior to SCCL/ going false. This is to ensure that the

Fig. II-1 A9419 ON-LINE CONTROL COUNTER STATES

Fig. II-2 MOTION BITS/DATA BUFFER

data is accurately read into the peripheral.

When the Processor executes a device write, to the B311, with MIR16 true and MIR04 false, a single low going INHCLK/ is enabled (see Fig. II-3) which sets the first flip-flop (SCC1F) in the SCCL delay circuit. Three clock periods later the signal SCCL goes true to make SCCL/ false to the peripheral. Within approximately 13 microseconds (10-16) the peripheral will make CCL/ false to indicate that it has received the data. RCCCL/ going false directly resets the SCC1F in the SCCL delay circuit. Thus three clock periods later SCCL goes false.

SCCL is gated with SCC3F so that the clock pulse which resets SCCL also makes RESET/ false to clear the databuffer. Thus, at 1 MHz clock rate, the motion control data is present on the interface lines for 3 usec before SCCL. The signal PONCL/ is false when the Processor is first powered up. It is used to inhibit SCCL until the Processor power supply and logic is stabilized, this is to prevent any spurious peripheral operation being initiated.

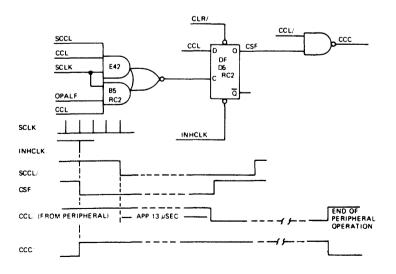

The signal CCC/ (card cycle complete not) is generated to make the status word bit 1 true, (ref. Fig. I-2) until the peripheral has completed any operation.

Referring to Fig. II-4 it is seen that the INHCLK/ signal, which generates SCCL/, is also used to reset CSF (cycle start flip-flop). CSF is set by CCL \* SCCL \* SCLK, or by OPALF \* CCL \* SCLK once the peripheral has started the required operation.

CSF is then gated with CCL/ to produce the signal CCC/, which will be true from the time that the Processor sends a control word to the IOC, until the device completes that required operation.

#### Burroughs - B311 Card Peripheral I.O. Control Technical Manual

#### Functional Detail

Fig. II-4 CSF, CCC/ AND TIMING

#### CONTROL BUFFER

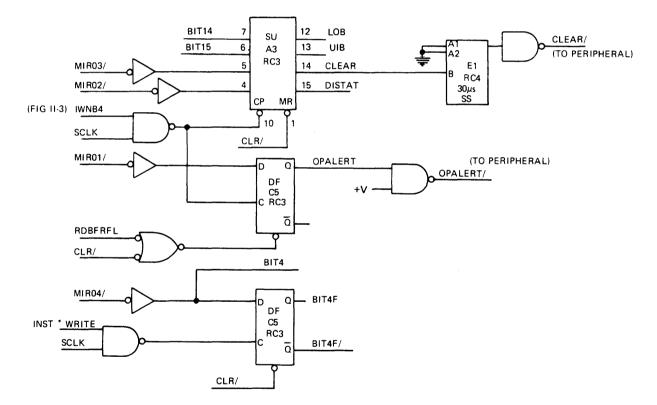

MIR Bits 1 through 4 contain only control data for the IOC, never data. These bits, together with MIR14 and MIR15 are stored in a separate Control Buffer whenever they are present in a Control word. They are stored in the buffer for use later in the peripheral operation.

Fig. II-5 shows the Control Buffer which consists of an SU chip and two D-type flip-flops. When the Processor executes a Device write to the IOC with the Instruction bit set, (MSB of Base Register) and MIR04 = 0, the signal IWNB4 is developed (see Fig. 11-3). This is gated with SCLK to strobe bit 14, Bit 15, MIR03, and MIR02 in the SU chip, Fig. II-5 and conditions one D type flip-flop according to the state of MIR01. The other flip-flop, for MIR04 is set or reset by INST\*WRITE gated with SCLK.

Thus it can be seen that when MIR04 is true in a Control word it will cause BIT4F to be set but will inhibit the loading of the SU and OPALERT flip-flop by making IWNB4 false.

Of these signals only one, OPALERT, is sent directly to the peripheral. The output of MIR03, CLEAR, triggers a 30 microsecond single shot which makes CLEAR/ false to the peripheral, and the remaining signals are used within the DDP.

Note that under normal operations MIR bits 1, 2, 3, 4, and 16 would not be present together in one control word since each is a separate control function.

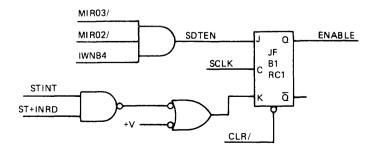

#### **ENABLE FLIP-FLOP**

The purpose of the Enable flip-flop is to prevent the IOC generating either Data or Status interrupts (DINT, SINT)

#### Fig. II-5 CONTROL BUFFER

Fig. II-6 INTERRUPT ENABLE FF

when it is not in use. For example turning the peripheral on or off while the Processor is working with other devices should not cause any interrupts to the Interpreter.

Referring to Fig. II-6 it is seen that when the Processor executes a device-write to the peripheral with the instruction bit set, and MIR2, 3, and 4 false (ref. Fig. I-2) the Enable flip-flop is set. This will permit the generation of DINT and SINT (reference Figs. II-7 and II-10).

In normal operation the first SINT generated will be when CCC/ goes false at the completion of the peripheral operation. When the Processor executes an ASR (or device-read with the instruction bit set) to interrogate the SINT, the signals STINT \* ST+INRD will reset the Enable flip-flop thus preventing further DINT's or SINT's until another operation is required.

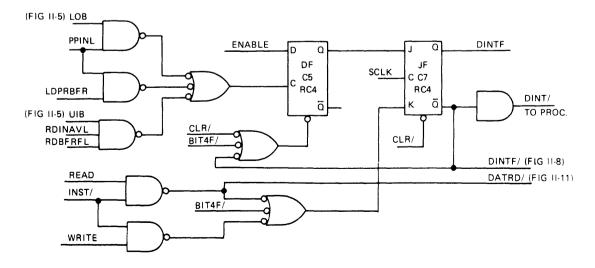

#### DATA INTERRUPT (DINT)

Referring to Fig. II-1, it can be seen that there are three states, of the peripheral card cycle operation, during which data is transferred between the Peripheral and the Processor. These occur when the Peripheral is ready to load its Input buffer (state 1), when the Peripheral is ready to load its Print buffer (state 3), and when the Peripheral is ready to unload its Input memory, following a card read operation (state 5).

In state 1, the signal received from the Peripheral is PPINL. Referring to Fig. II-7, it can be seen that PPINL is gated with LOB to set a D flip-flop, provided that Enable flip-flop is set. (LOB will be true if MIR14 = 1 in the Control word which initiates the card cycle.) The set output of the D flip-flop allows the next SCLK to set the DINT flip-flop thus making DINT/ false to the Processor. The reset output of the DINT flip-flop then resets the D flip-flop.

The DINT flip-flop is reset, when the Processor executes

a device write to transmit a data character to the IOC, by the signals INST/ and WRITE.

In state 3 the Peripheral sends PPINL and LDPRBFR when it is ready to receive a print character. These two signals are gated to set the DINT flip-flop and, as above, DINT flip-flop will reset when the Processor responds by executing a device write.

Note that LDPRBFR is true throughout the load Print buffer operation, while PPINL is the signal which goes true for each of the 96 characters.

In state 5, the Peripheral sends RDBFRFL for the duration of state 5, and RDINAVL as each character is made available to the IOC. In Fig. II-7 it may be seen that RDINAVL and RDBFRFL are gated with UIB (from MIR15 in the initiating control word) to set the D type flip-flop and generate DINT.

The DINT will be reset when the Processor executes a Device read, to take the character from the IOC, by the signals READ and INST/.

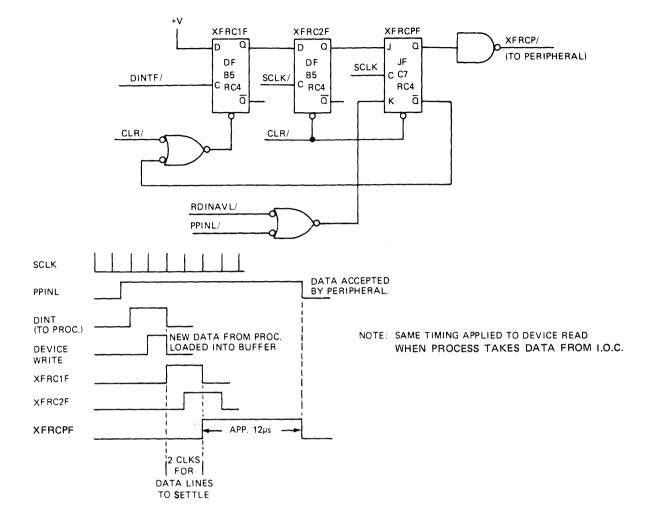

#### XFRCP CONTROL

When the IOC outputs data, the signal XFRCP (Transfer clock pulse) is sent to the peripheral to generate a data transfer within the peripheral interface. This will load the output character into the Input Memory of the peripheral. The "load cycle" takes approximately 12 us.

Referring to Fig. II-8, it is seen that when the Processor sends a character to the IOC and resets DINT, (Ref. Figs. II-2, II-7) DINTF/ going true sets XFRC1F. Two clock times later XFRCPF is set and XFRCP/ goes false to the peripheral to initiate a load to the Input Memory.

When XFRCPF sets it initiates the reset of XFRC1F and XFRC2F, however XFRCPF remains set until PPINL/ or RDINAVL/ goes true indicating that the data has been accepted by the peripheral. PPINL is used during interface states 2 and 3 (ref. Fig. II-1) and RDINAVL is used during interface state 5.

Fig. II-7 DATA INTERRUPT CONTROL

Sec. II Page 7

#### Fig. II-8 XFRCP CONTROL AND TIMING

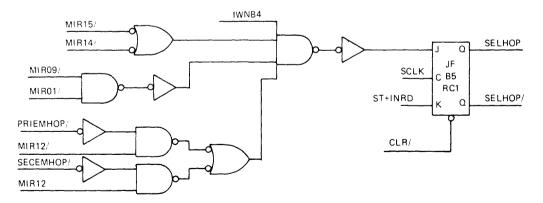

#### Fig. II-9 SELECTED HOPPER EMPTY FF

#### SELECTED HOPPER EMPTY FLIP-FLOP

Whenever the card hopper, selected in the control word, is empty the SELHOPF is set and a status interrupt is sent to the processor.

The peripheral has two interface signals which can indicate an empty hopper, these are PRIEMHOP/, primary

hopper empty not, and SECEMHOP/, secondary hopper empty not.

In a control word (ref. Fig. I-2) MIR12 is used to select the secondary hopper, if MIR12 is false then the primary hopper is selected.

Referring to Fig. II-9 it is seen that the signals IWNB4 \*

(MIR15 + MIR14) \* MIR09/ \* MIR01/ are used to enable the set input of SELHOPF. This gating is active when a control word is sent to the IOC which requires a card to be fed from either the primary or secondary hopper.

To complete the gating PRIEMHOP is gated with MIR12/, and SECEMHOP is gated with MIR12. Thus, if the selected hopper is empty, SELHOPF is set.

SELHOPF will generate a SINT to the processor (see Fig. II-10) and when the processor interrogates the SINT, by executing an ASR or a Device read with the instruction bit set, the signal ST + INRD will reset SELHOPF.

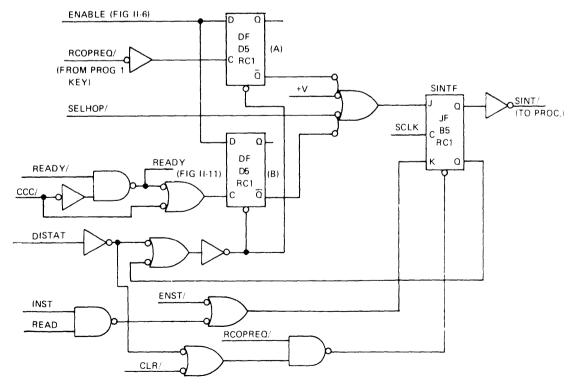

#### STATUS INTERRUPT CONTROL

A status interrupt (SINT) is sent to the processor whenever certain conditions occur within the peripheral and alerts the processor that some action may be required. It is then a function of the interpreter (firmware) to interrogate the status condition, determine what it is, and take the necessary action.

- A SINT is generated by the following conditions:

- 1. Operator request (from Prog. 1 key on the peripheral).

- 2. Empty selected card hopper.

- 3. End of peripheral card cycle (when the peripheral interface states go from 5 to 0 and CCC/ goes false).

- 4. Peripheral going to the not-ready condition between card cycles (from Punch data check, Read check –

optional, both hoppers empty, Full stacker or Card-jam).

Referring to Figure II-10 it is seen that when the operator depresses Prog. 1 key on the peripheral keyboard the signal RCOPREQ/ going false will set a D flip-flop (A). This in turn will set the SINT FF at the next SCLK.

If a selected hopper is empty the signal SELHOP/ (ref. Fig. II-9) going low sets SINTF.

At the end of a peripheral operation the signal CCC/ going low will set a D flip-flop (B) which will set SINTF.

The signal READY/ from the peripheral, if it goes true, can also set the D flip-flop (B) but only while CCC/ is false (i.e., between peripheral operations).

Note that when SINTF sets its reset output going low will directly reset the D flip-flops.

Under certain conditions the processor firmware may choose to ignore a SINT from the IOC. If a control word is sent to the IOC with MIR02 true the signal DISTAT (ref. Fig. II-5) will reset both the D flip-flops (A & B) and SINTF. The only exception being if SINTF has been set from OPREQ/. In this case the processor must execute an ASR or Instruction-read to take the status condition and clear the SINT.

When the processor executes an ASR, or Device-read with the instruction bit set, the signals ENST/, or INST \* READ, will rest SINTF through its K input.

Fig. II-10 STATUS INTERRUPT CONTROL

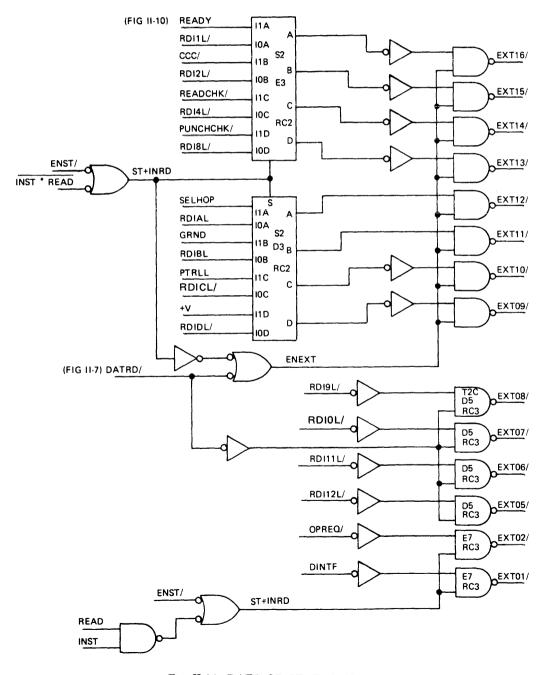

#### DATA OR STATUS TO EXT LINES

When the processor executes a device-read to the IOC it is the instruction bit (MSB of BRn) which indicates whether data from the peripheral or status information from the IOC is required. The selection of data or status is accomplished through the use of two quad-one-of-two data selector IC's on the RC2 board.

Referring to Fig. II-11 it can be seen that when the processor executes an ASR or an Instruction-read to the IOC the signals ENST or INST \* READ will generate the

signal ST+INRD. This signal controls the data-selectors (S2) so that the inputs I1A, B, C, & D are gated to the A B C & D outputs. At the same time ENEXT enables the output of the selectors to the EXT lines. Thus the processor receives the status information.

When the processor executes a device-read with the instruction bit reset the signal ST+INRD is false so the inputs IOA, B, C, & D are gated to the A B C & D outputs of the selectors. In this case the signal DATRD/ (ref. Fig. II-7) generates ENEXT and gates the data out to the EXT lines.

Fig. II-11 DATA OR STATUS TO EXT

Note that because of logic partitioning and circuit board layout the signal ST+INRD is generated twice, once on RC2 and again on RC3.

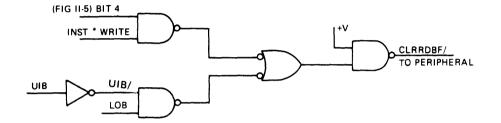

#### **CLEAR READ BUFFER**

During interface state 5 (ref. Fig. II-1) the processor may terminate the unload input memory operation after it has received sufficient data. (i.e., it is not obliged to read all ninety-six columns.) Referring to Fig. II-12 it can be seen that if the processor sends a control word with MIR04 (terminate) true, to the IOC, the signals BIT4 and INST \* WRITE make CLRRDBF/ false to the peripheral. This will cause the peripheral to cease its operation and the interface states return to 0.

If the processor sends a control word to the IOC with MIR14 and MIR15/, indicating a card operation with no data to be read, the signals UIB/ and LOB will make CLRRDBF/ false. In this case the interface states will effectively skip state 5 and return to state 0 from state 4.

Fig. II-12 CLEAR READ BUFFER

#### INTRODUCTION

Section III contains the detailed description of the circuits used in the B311 IOC. The following subsections explains the electronic functions of all the Transistor-Transistor Logic (TTL) circuits used in the B311 IOC.

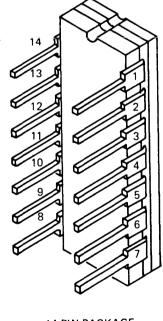

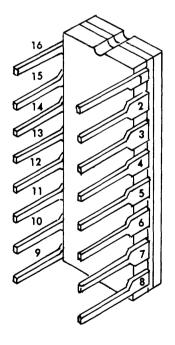

#### TRANSISTOR-TRANSISTOR LOGIC (TTL)

The Monolithic Elements, known as chips, are Dual-In-Line packages with either 14 or 16 pins. See Fig. III-1. The supply voltage for the TTL chips is +5.0 volts. A logical true level (HIGH LEVEL) is between +2.4 volts and +5.25 volts, and a logical false level (LOW LEVEL) is between 0 volts and 0.4 volts.

#### NAND GATES

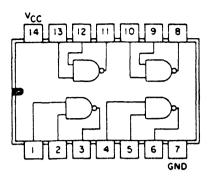

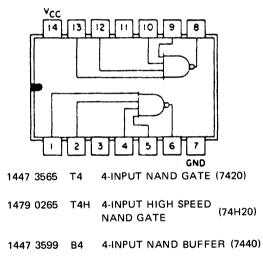

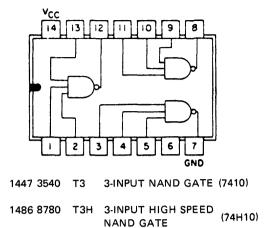

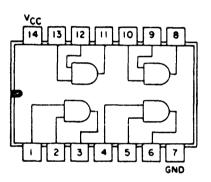

The various Nand Gates used in the B311 IOC are

shown in Fig. III-2. The Nand Gates are 2, 3, 4 or 8 input gates. The 2, 3 and 4 input Nand Gates have a high speed gate series. The Nand Gates are identified by: T2 for the 2 input Nand Gate, T3 for the 3 input Nand Gate, T4 for the 4 input Nand Gate and T8 for the 8 input Gate.

The High Speed Gates are identified by T2H for the 2 input gate, T3H for the 3 input gate and T4H for the 4 input gate. The T2C series Nand Gate chips are opencollector output gates and are used for wire or functions. Whenever a Nand Gate is used from this chip, the output of the gate will be connected for a wire or function.

Operation for all Nand Gates used in the B311 IOC is as follows: a high level output is produced by any low level input and a low level output is provided when all inputs are high.

14-PIN PACKAGE

**16-PIN PACKAGE**

#### Fig. III-1 14 AND 16 PIN CHIPS

- 1447 3516 T2 2-INPUT NAND GATE (7400)

- 1479 0240 T2H 2-INPUT HIGH SPEED NAND GATE (74H00)

- 1447 3581 T2C 2-INPUT NAND GATE OPEN COLLECTOR (7438)

1447 3524 T2A 2-INPUT AND GATE (7408)

#### Fig. III-2 NAND & AND GATES

#### **T1 HEX INVERTER**

The Hex Inverter contains 6 inverter gates as shown in Fig. III-3. T1 is a standard inverter whereby a high level

output is produced by a low level input and a low level output is produced by a high level input.

1447 3532 1447 3532 T1 HEX INVERTER (7404)

Page 2

Fig. III-3

1447 3649 E24 2-2-2-3 INPUT AND-OR INVERTER GATE <sup>(74H53)</sup>