**Ab** 911484

# AEROSPACE MULTIPROCESSOR FINAL REPORT

Robert L. Davis Sandra Zucker, et al

Burroughs Corporation Defense, Space and Special Systems Group Advanced Development Organization Paoli, Pennsylvania 19301

# **TECHNICAL REPORT AFAL-TR-73-114**

June 1973

Distribution limited to U. S. Government agencies only; test and evaluation results reported March 1973. Other requests for this document must be referred to Air Force Avionics Laboratory (AAM), Wright-Patterson Air Force Base, Ohio 45433.

Air Force Avionics Laboratory Air Force Systems Command Wright-Patterson Air Force Ease, Ohio 45433

NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

# AEROSPACE MULTIPROCESSOR FINAL REPORT

Robert L. Davis Sandra Zucker, et al

Distribution limited to P. S. Government agencies only: rest and evaluation results reported March 1973. Other requests for this document must be referred to Air Force Avionics Laboratory (AAM), Wright-Patterson Air Force Base, Ohio 45433.

#### FOREWORD

This Final Engineering Report was prepared by the Burroughs Corporation, Defense, Space and Special Systems Group, Advanced Development Organization, Paoli, Pennsylvania. The work was accomplished under USAF Project 6090 entitled "Avionics Data Handling Technology", Task 01 entitled "Avionics Information Processing" and Contract No. F33615-70-C-1773 entitled "Aerospace Multiprocessor." The work was administored under the direction of Mr. D. Brewer, Air Force Avionics Laboratory, AFAL/AAM, Wright-Patterson AFB, Ohio.

This report covers work conducted from June 1970 to March 1973 and was submitted by the authors March 1973.

The authors, Mr. Robert Davis and Mrs. Sandra Zucker, are grateful for the help and contributions of many of their associates in the Advanced Development Organization for the documentation, wiring, machining, board layout and fabrication, and artwork generation necessary to build the multiprocessor and for the help of their associates in Advanced Development and Technical Publications in the writing, drafting, typing, and proofreading necessary to produce this report. The authors are especially grateful to Messrs. Peter Molloy and Gilbert Reid for their help in the fabrication and debugging of the multiprocessor; Messrs. Melvin Brooks and Carl Campbell for their help in writing and debugging the control and demonstration programs; Messrs. Ulbe Faber and Richard Bradley for the design of the Switch Interlock; and Mr. John T. Lyrch, Director of Advanced Development and Messrs. Dewey Brewer and Kalph Barrera of the Avionics Laboratory (AFAL/AAM) for their patience and support throughout this program.

This technical report has been reviewed and is approved for publication.

EUX. ?

COZIER S. KLINE Colonel, USAF Chief System Avionics Division

#### ABSTRACT

The aerospace multiprocessor described is based upon a modular, building block approach. An exchange concept that is expandable with the number of processors, memory modules, and device ports, was developed whose path width is a function of the amount of serialization desired in the transmission of data and address through the exchange. The processors (called Interpreters) are microprogrammable utilizing a 2-level microprogram memory structure and were designed for implementation with large scale integrated circuits. The modularity exhibited in the Interpreters is in the size of the microprogram memories and in the word length of the Interpreters from 8 bits through 64 bits in 8-bit increments.

The specific implementation of the exchange for the aerospace multiprocessor is for five processors, eight memory modules, and eight device ports with eight wires each carrying four serial bits of data through the exchange. The processors each have word lengths of 32 bits with a 512 word  $\times$  15 bit firs -level microprogram memory and a 256 word  $\times$  54 bit second-level microprogram memory.

A simplified control program based upon concepts for a modular executive structure, and some user type programs were written for demonstration of the aerospace multiprocessor.

# TABLE OF CONTENTS

.

,

PERCEDING PACE BLANK-NOT FILMED

| Section |                                      | Page       |

|---------|--------------------------------------|------------|

| I       | INTRODUCTION                         | 1          |

| II      | INTERPRETER HARDWARE BUILDING BLOCKS | 7          |

|         | Logic Unit (LU).                     | 9          |

|         | Control Unit (CU)                    | 11         |

|         | Memory Control Unit (MCU)            | 13         |

|         | Nanomemory (N Memory)                | 13         |

|         | Microprogram Memory (MPM)            | 15         |

|         | Microprogram Memory Considerations   | 17         |

|         | Loader $(LDR)$                       | 21         |

| IΠ      | MULTIPROCESSING HARDWARE DESCRIPTION | 23         |

|         | Multiprocessor Interconnection       | 23         |

|         | The Switch Interlock                 | 27         |

|         | Power Distribution.                  | 35         |

|         | Clock and Power Control              | <b>3</b> 6 |

|         | Global and Interrupt Condition Bits  | 43         |

|         | Real Time Clock and the Horns        | 45         |

|         | Interpreter Number                   | 45         |

| IV      | AEROSPACE MULTIPROCESSOR             |            |

|         | PACKAGING DESCRIPTION                | 47         |

|         | Mechanical Design                    | 47         |

|         | Circuit Configurations               | 51         |

| v       | INTERPRETER OPERATION                | 61         |

# TABLE OF CONTENTS (Cont'd)

| Section |                                              | Page         |

|---------|----------------------------------------------|--------------|

| VI      | SWITCH INTERLOCK (SWI) OPERATION             | 69           |

|         | Overall Switch Interlock Control and Timing  | 69           |

|         | Device Operations                            | 72           |

|         | Memory Operations                            | 78           |

|         | Interface to SWI.                            | 83           |

|         | Device Interface Operation Examples          | 85           |

| VII     | INTERPRETER MICROPROGRAMMING.                | 89           |

|         | TRANSLANG for Microprogramming.              | 92           |

|         | Literal Assignment Instruction               | 94           |

|         | N Instruction                                | 95           |

|         | Condition                                    | 96           |

|         | External Operations                          | 100          |

|         | Logical Operations                           | 103          |

|         | Input Selects                                | 106          |

|         | Destination Operations                       | 107          |

|         | Successor                                    | 110          |

|         | Program Structure                            | 111          |

|         | Microprogramming Examples                    | 1 <b>1</b> 5 |

|         |                                              |              |

| VIII    | MULTIPROCESSING CONTROL PROGRAM AND          | 101          |

|         | DEMONSTRATION PROGRAMS                       | 121          |

|         | Control Program                              | 121          |

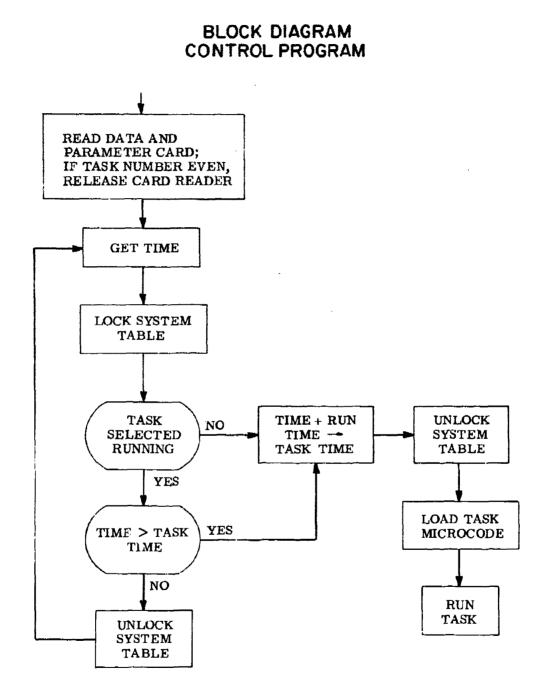

|         | System Loading                               | 122          |

|         | Task Execution and Monitoring                | 125          |

|         | S to M Loader                                | 127          |

|         |                                              |              |

|         | Demonstration Programs.                      | 131          |

|         | Memory Dump                                  | 134          |

|         | Program to "S" Loader                        | 134          |

|         | Plot                                         | 134          |

|         | Mortgage                                     | 135          |

|         | Sort                                         | 135          |

|         | Matrix Multiply and Print                    | 138          |

|         | , matthe matching and a time a sea sea sea s | 100          |

|         | Confidence Routines                          | 1 <b>3</b> 9 |

:

,

# TABLE OF CONTENTS (Cont'd)

| Appendices   |                                       | Page |

|--------------|---------------------------------------|------|

| I ·          | Historical Review of Microprogramming | 145  |

| Ш            | Final Summary Report - Bipolar LSI    | 151  |

| 111          | Adder Operations                      | 183  |

| IV           | TRANSLANG Syntax                      | 187  |

| v            | TRANSLANG Reserved Words and Terminal |      |

|              | Characters                            | 191  |

| VI           | TRANSLANG Error Messages              | 199  |

| VII          | Glossary                              | 203  |

| References   |                                       |      |

| Form DD 1473 |                                       |      |

# LIST OF ILLUSTRATIONS

| Figure |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

| 1      | Basic Aerospace Multiprocessor                                              | 2    |

| 2      | LSI Multi-Interpreter System Block Diagram                                  | 3    |

| 3      | Interpreter Block Diagram                                                   | 8    |

| 4      | Logic Unit Block Diagram                                                    | 8    |

| 5      | Interpreter Functional Units                                                | 12   |

| 6      | Instruction Memory Hierarchy                                                | 14   |

| 7      | One Memory vs. Two Memory Implementation                                    | 16   |

| 8      | Sample Program Statistics                                                   | 17   |

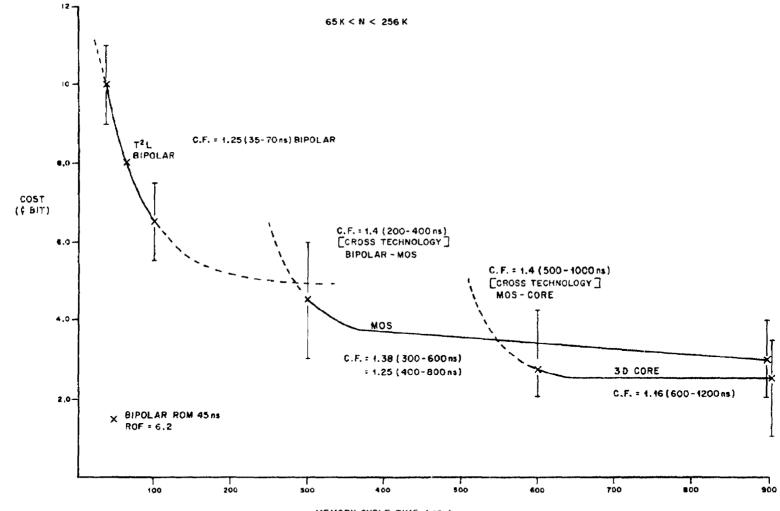

| 9      | Memory Cost vs. Memory Speed                                                | 19   |

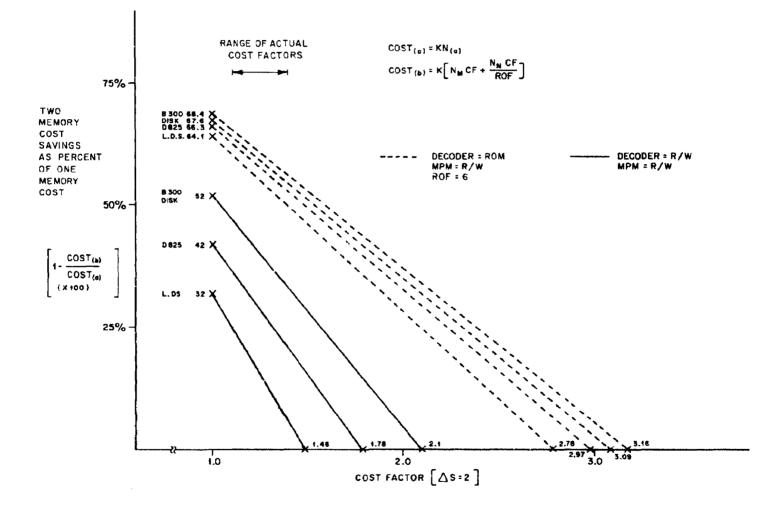

| 10     | Two Memory Cost Savings vs. Cost Factor                                     | 20   |

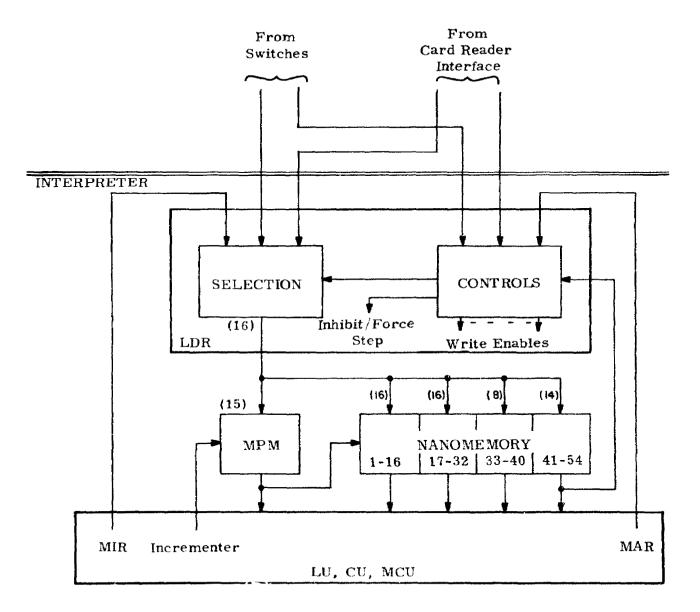

| 11     | Implementation of Loading Functions Block Diagram                           | 22   |

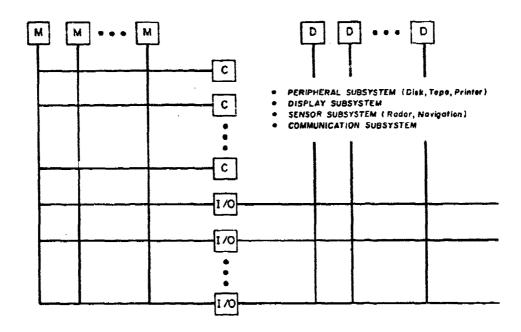

| 12     | Functional Multiprocessor Interconnection Scheme                            | 24   |

| 13     | Physical Multiprocessor Interconnection Scheme                              | 26   |

| 14     | Centralized Multiprocessor System                                           | 28   |

| 15     | Distributed Multiprocessing Interpreter System                              | 28   |

| 16     | Implementation of the Switch Interlock                                      | 29   |

| 17     | Memory/Device Controls (MDC) Block Diagram                                  | 30   |

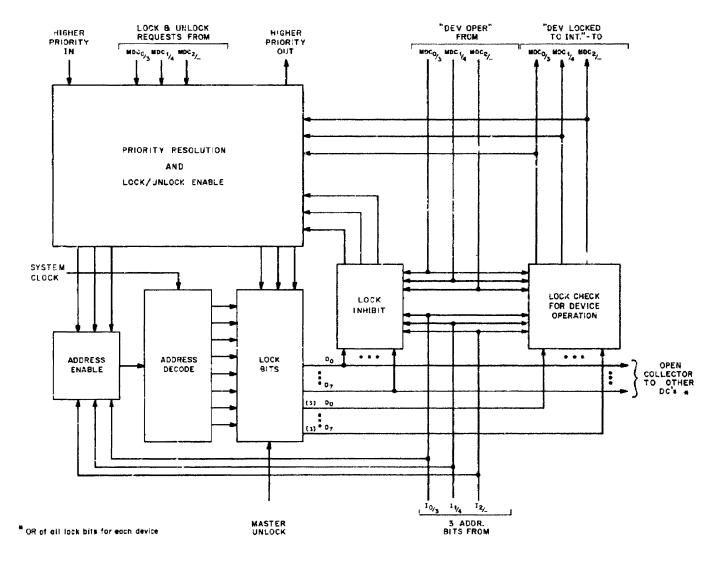

| 18     | Device Controls (DC) Block Diagram                                          | 32   |

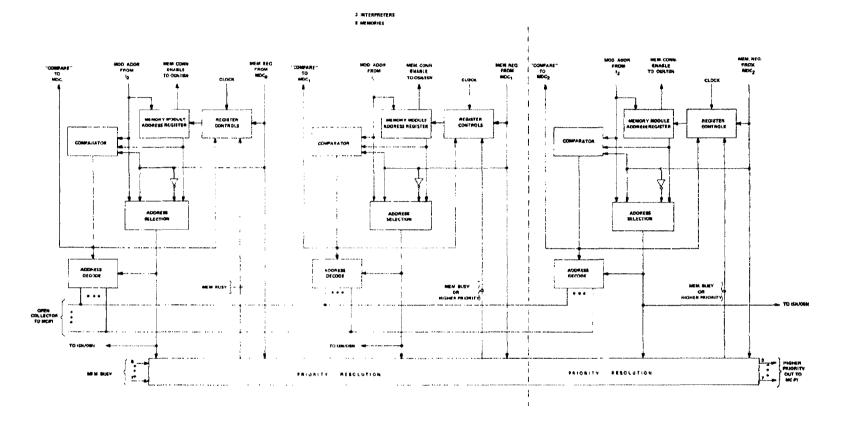

| 19     | Memory Control No. 0, Block Diagram                                         | 33   |

| 20     | Memory Control No. 1, Block Diagram                                         | 34   |

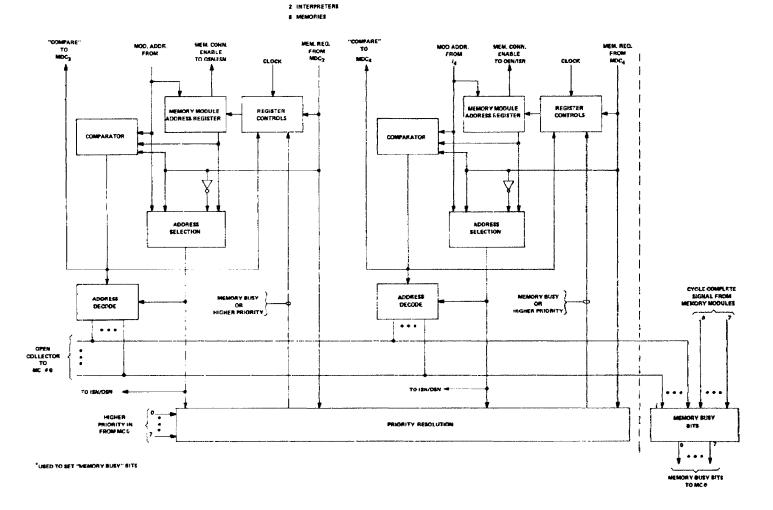

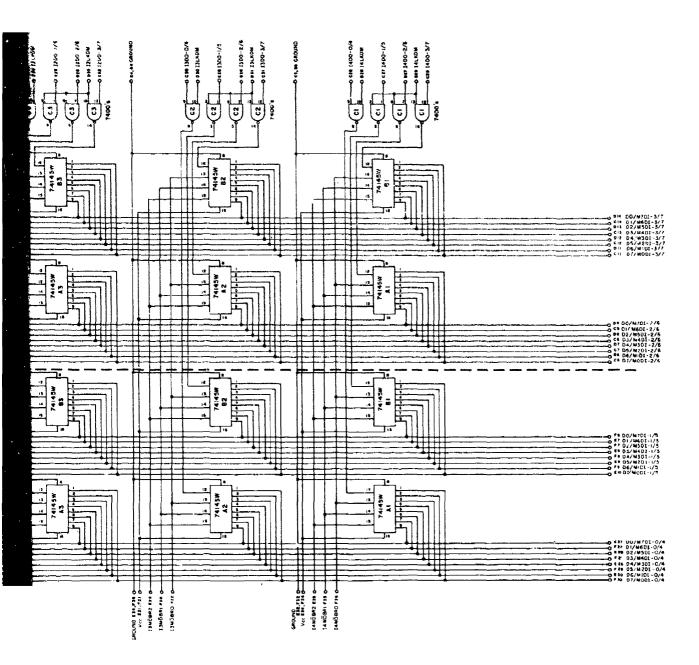

| 21     | Output Switch Network No. 0, Logic Diagram                                  | 37   |

| 22     | Output Switch Network No. 1, Logic Diagram                                  | 38   |

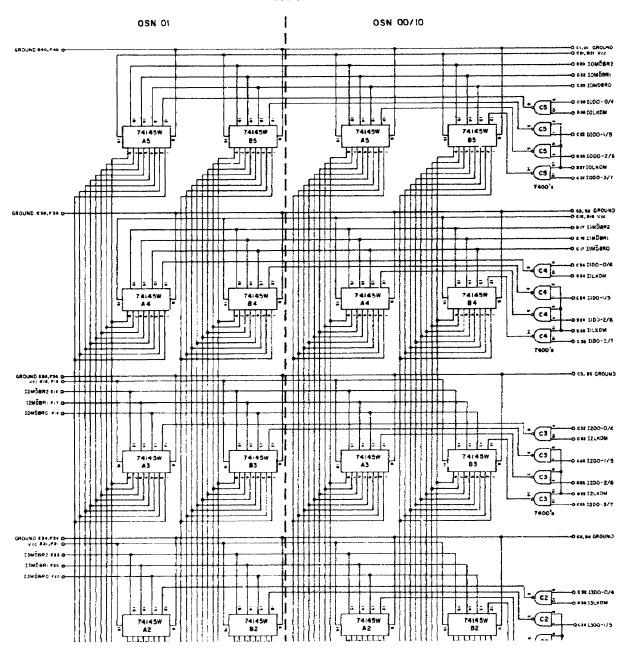

| 23     | Input Switch Network, Logic Diagram                                         | 39   |

| 24     | Power Distribution System                                                   | 40   |

| 25     | Implementation of Multiprocessor Clocks                                     | 41   |

| 26     | Conflict Resolution Logic for Global Condition Bit GC1                      | 42   |

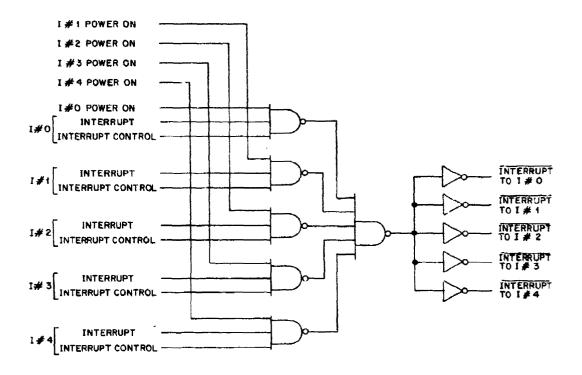

| 27     | Implementation of Interrupt Controls                                        | 44   |

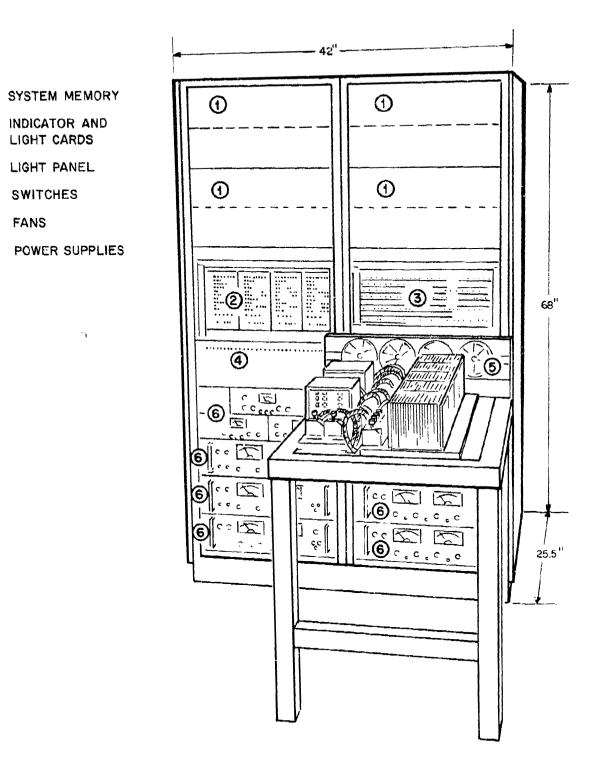

| 28     | Aerospace Multiprocessor Configuration                                      | 48   |

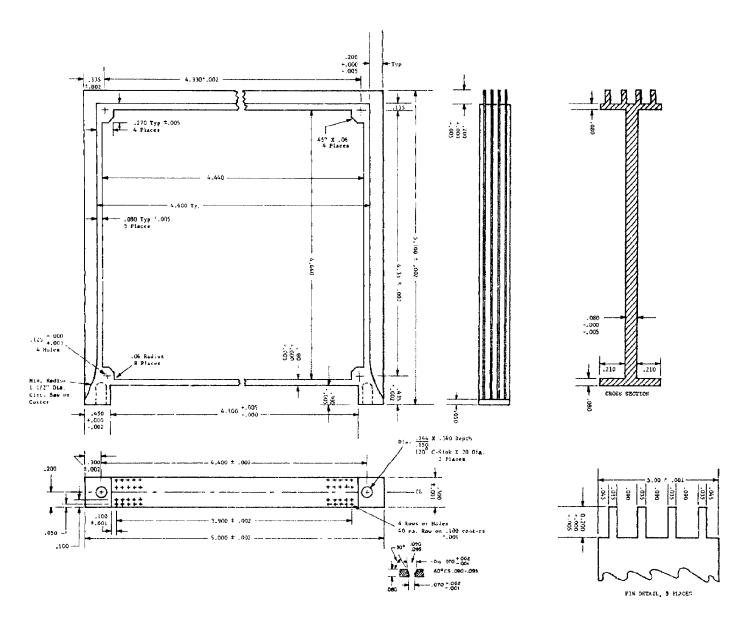

| 29     | Submodule Housing                                                           | 49   |

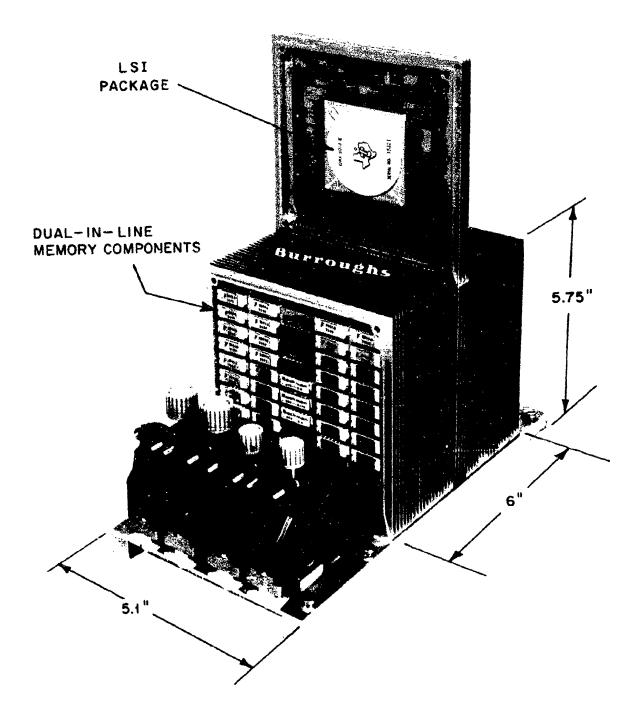

| 30     | Interpreter Module Packaging                                                | 50   |

| 31     | Aerospace Multiprocessor Installation at Wright-Patterson<br>Air Force Base | 52   |

| 32     | Multiprocessor Interconnection Scheme                                       | 53   |

| 33     | Microprogram Memory, Nanomemory Submodule Packaging                         | 54   |

| 34     | Loader, Switch Interlock Submodule Packaging                                | 55   |

| 35     | Alternative Packaging Approach Utilizing 16-pin Flat Packs                  | 58   |

# LIST OF ILLUSTRATIONS (Cont'd)

| Figure     |                                                     | Page       |

|------------|-----------------------------------------------------|------------|

| 36         | Alternative Packaging Approach Utilizing 60-pin     |            |

|            | Flat Packs                                          | <b>5</b> 9 |

| 37         | Timing Analysis, Type I Instructions                | 62         |

| 38         | Instruction Timing                                  | 64         |

| 39         | Timing Example                                      | 66         |

| 40         | Microprogram Instruction Sequencing                 | 68         |

| 41         | Switch Interlock, Block Diagram                     | 70         |

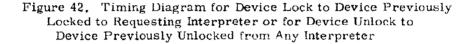

| 42         | Timing Diagram for Device Lock to Device Previously |            |

|            | Locked to Requesting Interpreter or for Device      |            |

|            | Unlock to Device Previously Unlocked from Any       |            |

|            | Interpreter                                         | 74         |

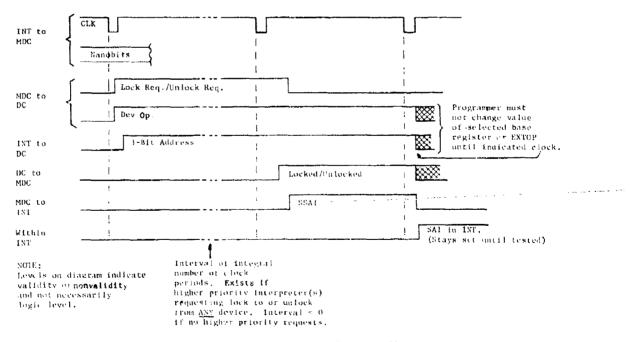

| 43         | Timing Diagram for Device Lock to Colocked Device   |            |

|            | Unlock to Device Locked to Pequesting Interpreter   | 74         |

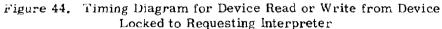

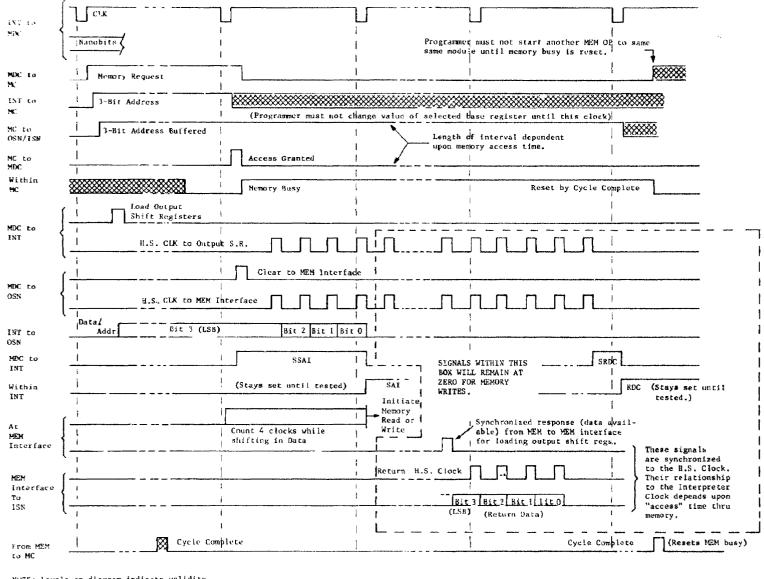

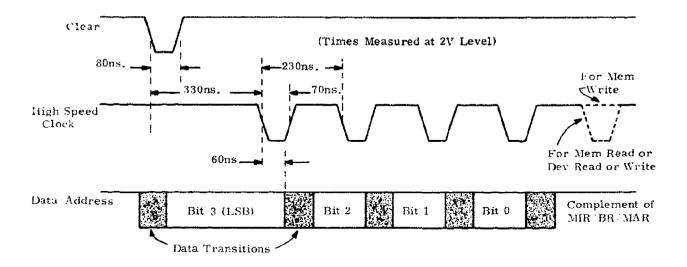

| 44         | Timing Diagram for Device Road or Write from Device |            |

|            | Locked to Requesting Interpreter                    | 75         |

| 45         | fiming Diagram for Memory Read or Write             | 80         |

| 46         | SWI/Interface Timing Signals                        | 82         |

| 47         | Memory/Device Interface with SWI, Block Diagram     | 84         |

| 48         | Microinstruction Types                              | 9 <b>0</b> |

| 49         | Detailed Nanobit Assignments                        | 114        |

| 50         | Binary Multiply                                     | 116        |

| 51         | Generation of Fibonacci Series                      | 117        |

| 52         | Microtranslator Output                              | 118        |

| 53         | S to M Loader                                       | 119        |

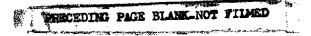

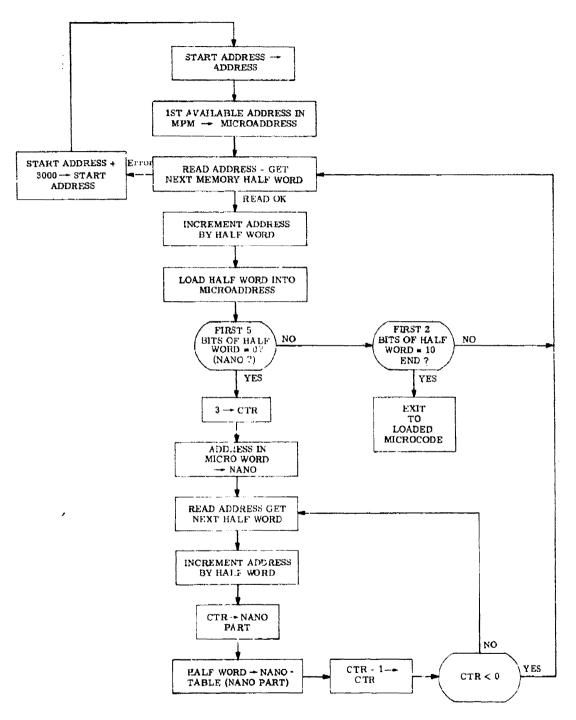

| 54         | Control Program Flow Diagram                        | 124        |

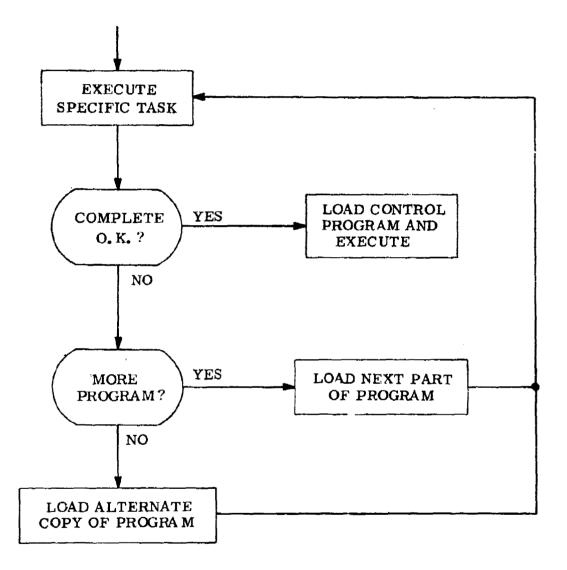

| 55         | Multiprocessor System Flow Diagram                  | 126        |

| 56         | Memory Map                                          | 128        |

| 57         | Load Microprogram Memory from Main Memory           |            |

|            | Flow Diagram                                        | 129        |

| 58         | Task Control Flow Diagram                           | 130        |

| 59         | Example of Memory Damp Ourput                       | 133        |

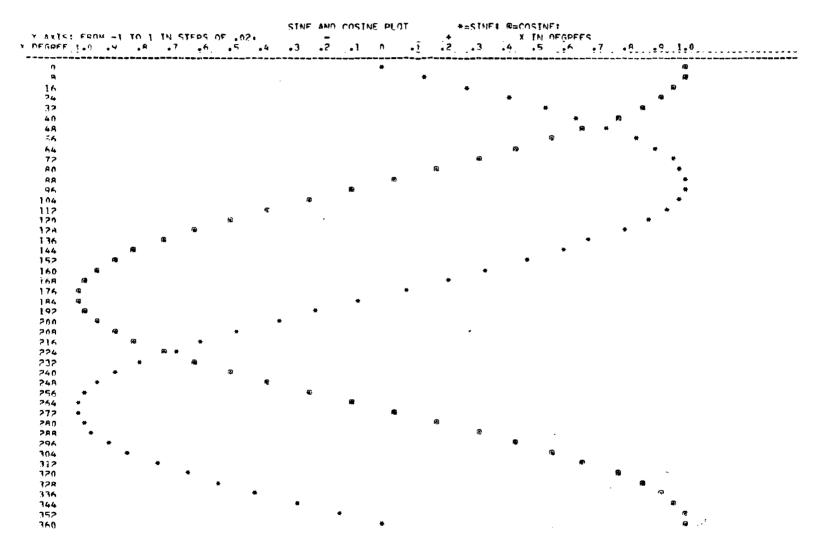

| 6 <b>0</b> | Example of Plot Routine Output                      | 136        |

| 6 <b>1</b> | Example of Mortgage Table Output                    | 137        |

| 62         | Example of Sort Routine Output                      | 141        |

| 6 <b>3</b> | Examples of Matrix Print Routine Output             | 143        |

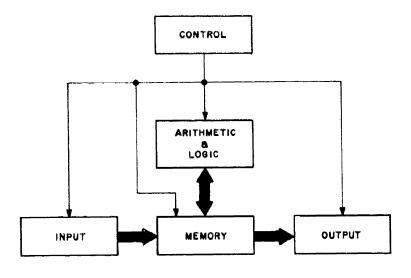

| 64         | Traditional Digital Computing System Block Diagram  | 146        |

# Page

#### SECTION I

# INTRODUCTION

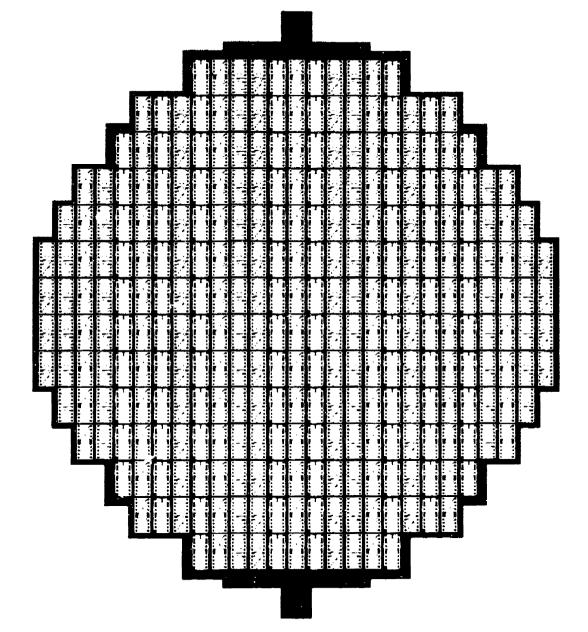

This final report describes the results of work performed by the Advanced Development Organization of Burroughs Defense, Space and Special Systems Group for the Air Force Avionics Laboratory, Wright-Patterson Air Force Base under contract F33615-70-C-1773. The purpose of this program was to fabricate an aerospace multiprocessor utilizing large scale integrated circuits with techniques developed under contract F33615-69-C-1200 by Burroughs for the Avionics Laboratory.

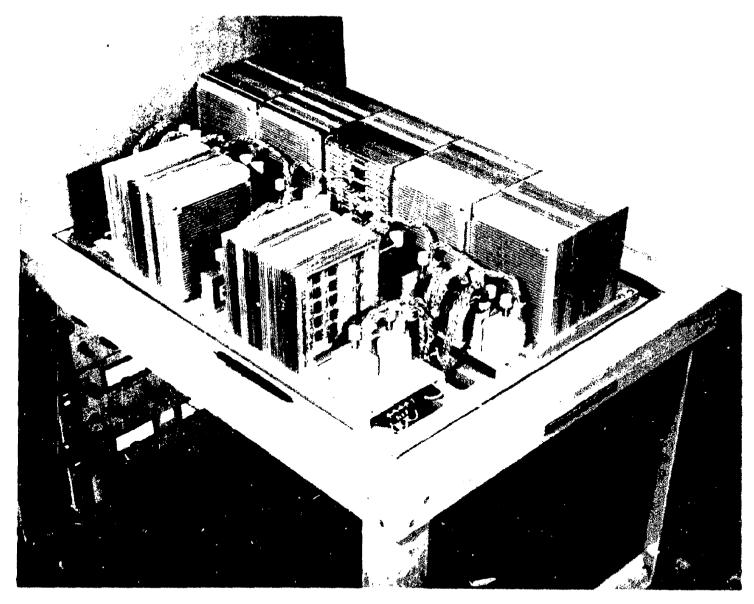

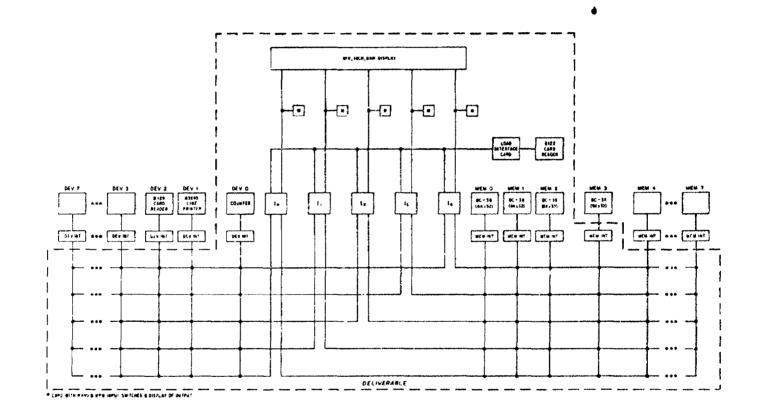

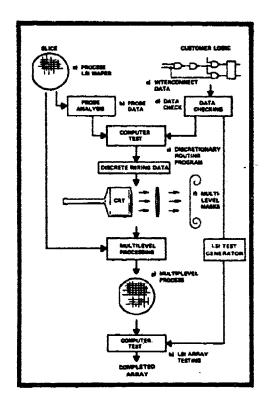

The aerospace multiprocessor is made up of five identical microprogrammable. LSI processors called interpreters connected to devices and memory modules by an exchange called a Switch Interlock. Since the intent of the contract was to produce only those parts of a multiprocessing system (processors and exchange as shown in Figure 1) not readily available in "miniaturized" form, the system is completed with commercially available memory modules, power supplies, and devices as shown in Figure 2. In this figure, the items delivered are shown within the dotted line. The Switch Interlock module comprises the "network" shown by the connected lines on the bottom half of Figure 2. The system characteristics for the aerospace multiprocessor are listed in Table I.

The remainder of this report consists of seven sections and seven appendices. Section II describes the LSI, microprogrammable processor (called an Interpreter), consisting of three types of logic parts utilizing discretionary-wired LSI arrays, two types of microprogram memories and a loader for loading these two memories. Also included is a discussion of the rationale for splitting the microprogram memory into two parts, based on work done by Mr. Ernest Trimbur.

Figure 1, Basic Aerospace Multiprocessor

$\sim$

:

Figure 2, LSI Multi-Interpreter System Block Diagram

ω

## Table I. Aerospace Multiprocessor, System Characteristics Summary

#### 5 Interpreters

| 32-bit word len | ngth                                                                                                               |             |

|-----------------|--------------------------------------------------------------------------------------------------------------------|-------------|

| 2.5 mHz clock   | rate                                                                                                               |             |

| Discretionary f | Routed TTL, LSI                                                                                                    |             |

| 512 words (exp  | andable to 1024 words) by 15 bits, read/w                                                                          | rite MPM    |

| 256 words by 5  | 4 bits, read/write Nanomemory                                                                                      |             |

| Volume:         | 5.75 in. $\times$ 5.1 in. $\times$ 6 in. without connec<br>5.75 in. $\times$ 5.1 in. $\times$ 10 in. with connecto |             |

| Typ. Power:     | 42 watts for LSI arrays<br>4 watts for loader<br>44 watts for MPM and Nanomemory                                   | +5 volts dc |

## 3 Memory Modules

Datacraft DC-38 3-wire, 3D, coincident current core Read/write, random access 8K words (expandable to 16K words) by 32 bits per module 350 ns access/900 ns cycle Volume: 19 in. × 19 in. × 5 1/4 in. Typ. Power: 6A at 117 Vac

#### 1 Switch Interlock

5 Interpreter ports

Serial data interface of 8 wires of 4 serial bits each

8 serial interfaces for memory modules (32 bits wide)

8 serial interfaces for device ports (32 bits wide)

Volume: 5,75 in.  $\times 5.1$  in.  $\times 22$  in. with connectors

Typ. Power: 72 watts at +5 volts de

Section III includes a general discussion of multiprocessor interconnection and a description of the hardware specifically needed for multiprocessing. This hardware includes the exchange for interconnecting processors to memories and devices, clock and power control, a "real-time" clock, a time-out counter, and the hardware necessary for one Interpreter to lock other Interpreters out of selected tables in memory. Also included in this section is a description of the system power distribution.

Section IV describes the packaging of the multiprocessor for its laboratory environment and briefly discusses the LSI partitioning and possible future implementations.

Section V is a detailed discussion of the Interpreter operation as a single processor, centering primarily on the fetching, execution, and sequencing of microprogram instructions and the condition testing involved in the microprogram instruction's successor determination.

Section VI is a detailed discussion of the Switch Interlock operation. The conflict resolution problem in accessing memories and "locking" to devices is discussed along with the handshaking between the Interpreters and the Switch Interlock in performing memory and device operations. Detailed timing diagrams are given for all Switch Interlock operations.

Section VII describes the microprogramming of the Interpreter and gives the syntax and semantics and examples for all Interpreter operations.

Section VIII is divided into two parts. The first part describes the simplified control program used to control the multiprocessor with its associated task tables in memory and also describes the method for loading either tasks or the control program into the Interpreter's microprogram memories from "S" memory. The second part of this section describes the six programs written to be executed as user tasks in the demonstration of the multiprocessor. This section is concluded with a short discussion of the confidence routines that were used during debugging of the Interpreters and which could be modified to run under the operating system for on-line confidence checks of the Interpreters.

Appendix I is a historical review of microprogramming written by Dr. Earl Reigel. Appendix II is a copy of the final report from Texas Instruments, Inc. on the discretionary-wired LSI used in the Interpreters. Appendices III-VI are details for the use of TRANSLANG, an assembler for Interpreter microprograms. Appendix VII is a glossary.

PRECEDING PAGE BLANK-NOT FILMED

#### SECTION II

#### INTERPRETER HARDWARE BUILDING BLOCKS

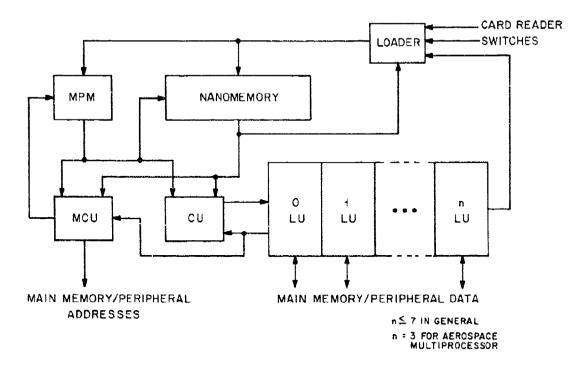

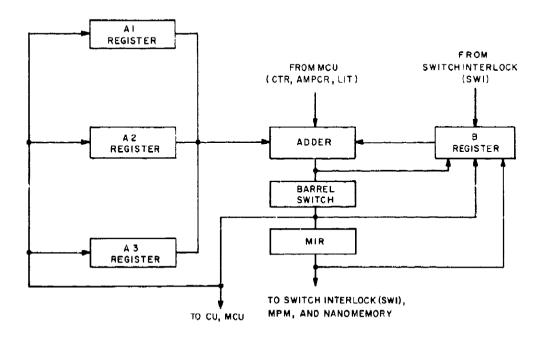

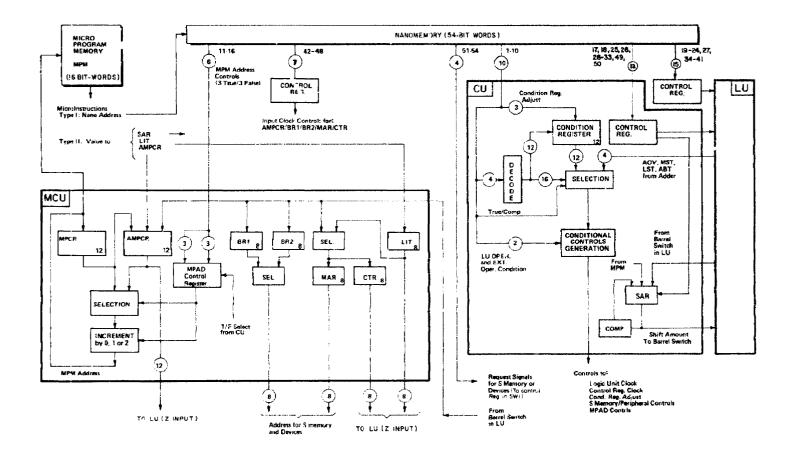

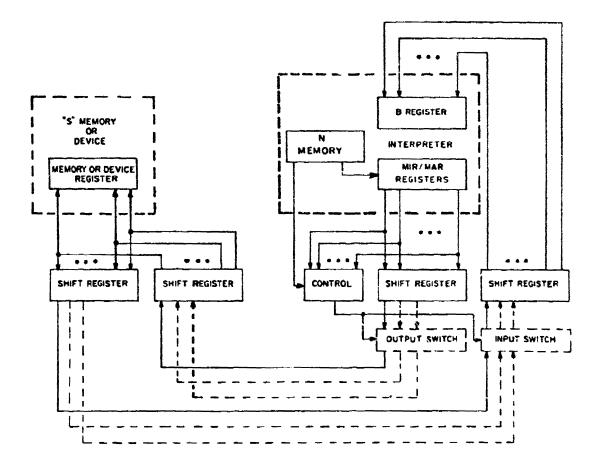

The Interpreter is composed of four logic package types: the Logic Unit (UU), the Control Unit (CU), the Memory Control Unit (MCU), and the Loader (LDR). The microprograms which provide the control functions are contained in two memories: the Microprogram Memory (MPM) and the Nano program Memory (Nano or NM). These units and their interconnections are shown in Figure 3.

The unique split memory scheme for microprogram memories allows a significant reduction in the number of bits for the microinstruction storage. It should be noted, however, that a single microprogram memory scheme (MPM and Nano combined) could also have been used, potentially increasing the clock rate of the system. In addition, the cycle rates of the memories could be altered, to gain speed or reduce cost, without any redesign of the logic packages. In fact, a variety of memory organizations (single memory and different split memory configurations) and memory speeds have been implemented in other Interpreter based systems, thus providing a range of cost/speed trade-offs.

The LU performs the required shifting, arithmetic, and logic functions as well as providing a set of scratch pad registers and data interfaces to and from the Switch Interlock (SWI). Of primary importance is the modularity of the LU, providing expansion of the word length in 8-bits increments from 8 bits through 64 bits using the same functional unit. The word length of the Interpreters used in the aerospace multiprocessor is 32-bits.

The CU contains a condition register, logic for testing the conditions, a shift amount register for controlling shift operations in the LU, and part of the control register used for storage of some of the control signals to be sent to the LU.

Figure 3. Interpreter Block Diagram

Figure 4. Logic Unit Block Diagram

The MCU provides addressing logic to the Switch Interlock for data accesses, controls for the selection of microinstructions, literal storage, and counter operation. This unit is also expandable when larger addressing capability is required. The Loader (LDR) enables the MPM and Nanomemory to be loaded from either switches, a card reader, or programmatically from the LU.

#### LOGIC UNIT (LU)

A functional block diagram of the LU is shown in Figure 4. The design of the LU is predicated upon implementation with one LSI silicon slice per eight bits. The present 8-bit LU is implemented with two LSI slices.

Registers A1, A2, and A3 are functionally identical. Each temporarily stores data and serves as a primary input to the adder. Selection gates permit the contents of any A register to be used as one of the inputs to the adder. Any of the A registers can be loaded with the output of the barrel switch.

The B register is the input buffer (from the Switch Interlock). It serves as the second input to the adder and can also collect certain side effects or arithmetic operations. The B register may be loaded with any of the following (one per instruction):

- 1. The barrel switch output

- 2. The adder output

- 3. The data from the Switch Interlock

- 4. The MIR output

- 5. The carry complements (from the adder) of 4- or 8-bit groups with selected zeros (for use in decimal arithmetic or character processing)

- 6. The barrel switch output ORed with the adder output

- 7. The barrel switch output ORed with the data from the Switch Interlock

- 8. The MIR output ORed with 1, 2, 5, or 6 above.

The output of the B register has true/complement selection gates which are controlled in three separate sections: the most significant bit, the least significant bit, and all the remaining central bits. Each of these parts is controlled independently and may be either all zeros, all ones, the true contents or the complement (ones complement) of the contents of the respective bits of the B register. The operation of these selection gates affects only the output of the B register. The contents remain unchanged. The MIR primarily buffers information being written to main system memory or to a peripheral device. It is loaded from the barrel switch output and its output may be sent to the Switch Interlock, to the B register, or to the data input of the MPM or Nanomemory for programmatic loading.

The adder in the LU is a modified version of a straightforward carry look-ahead adder such as that discussed by  $MacSorley^1$  and others. Therefore, the details of its operation will not be included.

Inputs to the adder are from selection gates which allow various combinations of the A, B, and Z inputs. The A input is from the  $\Lambda$  register output selection gates and the B input from the B register true/complement selection gates. The Z input is an external input to the LU and can be:

- 1. The 8-bit output of the counter of the MCU into the most significant 8 bits with all other bits being zeros.

- 2. The 8-bit output of the literal register of the MCU into the least significant 8 bits with all other bits being zeros.

- 3. The 12-bit output of the alternate microprogram count register (AMPCR) right justified into the middle 16 bits and the (wired) Interpreter number right justified in the remaining four bits of the middle 16 bits. All other bits are zeros.

- 4. All zeros.

Using various combinations of inputs to the selection gates, any two of the three inputs can be added together, or can be added together with an additional "one" added to the least significant bit. Also, all binary Boolean operations between the A and B and between the B and Z adder inputs and most of the binary Boolean operations between the A and Z adder inputs can be done.

The barrel switch is a matrix of gates that shifts a parallel input data word any number of places to the left or right, either end-off or end-around, in one clock time.

The output of the barrel switch is sent to:

- 1. The A registers (A1, A2, A3)

- 2. The B register

- 3. Memory Information Register (MIR)

- 4. Least significant 16 bits to MCU (registers BR1, BR2, MAR, AMPCR, LIT, CTR)

- 5. Least significant 5 bits to shift amount register (SAR) in the CU.

#### CONTROL UNIT (CU)

One CU is required for each Interpreter. The design of the CU is predicated upon implementation with one LSI silicon slice, but is presently constructed with two LSI slices. Major sections of this unit (Figure 5) are: the shift amount register (SAR), the condition register, part of the control register (CR), the MPM content decoding, and part of the clock control.

The functions of the SAR and its associated logic are:

- To load shift amounts into the SAR to be used in the shifting operations. Left end-off shifts require a shift amount equal to the "word length complement" of the number of positions to be shifted. ("Word length complement" is defined as the amount that will restore the bits of a word to their original position after an end-around shift of N followed by an end-around of the "complement" of N. For the 32-bit word length in the aerospace multiprocessor, this is the 2's complement.)

- 2. To generate the required controls for the barrel switch shift operation indicated by the controls from the Nanomemory.

- 3. To generate the "word length complement" of the SAR contents and load this value back into the SAR.

The condition register section of the CU performs four major functions:

- 1. Stores 12 resettable condition bits in the condition registers. The 12 bils of the condition register are used as error indicators, interrupts, status indicators, and lockout indicators.

- Selects 1 of 16 condition bits (12 from the register and 4 generated during the present clock time in the Logic Unit) for use in performing conditional operations.

- 3. Decodes bits from the Nanomemory for resetting, setting, or requesting the setting of certain bits in the condition register.

- 4. Resolves priority between Interpreters in the setting of global condition (GC) bits.

Figure 5. Interpreter Functional Units

12

The control register is a register that stores 38 of the 54 control signals from the Nanomemory that are used in the LU, CU, and MCU for controlling the execution phase of a microinstruction. Twelve of the 38 outputs from the Nanomemory are stored in the CU. Four of the other 38 Nanomemory outputs are controls to the Switch Interlock and are stored there. The other 22 of the 38 Nanomemory outputs are stored in a part of the control register physically located in the Nanomemory.

The MPM content decoding determines (based upon the first four bits of the MPM) whether the MPM output is to be used as a Type I instruction (Nanomemory address) or as a Type II instruction (literal). Several decoding options are available. The particular option chosen is described in the Interpreter Micro-programming section of this report.

#### MEMORY CONTROL UNIT (MCU)

- One MCU is required for an Interpreter in the aerospace multiprocessor, but a second MCU could have been added to provide additional memory addressing capability. The design of the MCU is predicated upon implementation with one LSI silicon slice, but is presently constructed with two LSI slices. This unit has three major sections (Figure 5):

- 1. The microprogram address section contains the microprogram count register (MPCR), the alternate microprogram count register (AMPCR), the incrementer, the microprogram address control register, and associated control logic. The output of the incrementer addresses the MPM for the sequencing of the microinstructions. The AMPCR contents are also used as one of the Z inputs to the adder in the LU.

- 2. The memory/device address section contains the memory address register (MAR), base registers one and two (BR1, BR2), the base register output selection gates, and the associated control logic.

- 3. The Z register section contains registers which are two of the Z inputs to the LU adder: a loadable counter (CTR), the literal register (LIT), selection gates for the input to the memory address register and the loadable counter and their associated control logic.

## NANOMEMORY (N MEMORY)

The Interpreter is controlled by the output of the 54-bit wide Nanomemory which may be implemented with a read/write memory, a read-only memory, wired logic, or a combination of the three. The present implementation is a 256-word by 54-bit read/write semiconductor random access memory using the Fairchild 93410, a 256-word by 1-bit package.

Figure 6. Instruction Memory Hierarchy

Each of the 54 bits represents a unique enable line for the gates and flip-flops within the LU, the CU, and the MCU. Each Nanomemory word represents a microinstruction that is executed by the simultaneous presentation of a specific enable pattern for the 54 outputs, represented by corresponding ones and zeros in its word. The definition of these bits is presented in the microprogramming section.

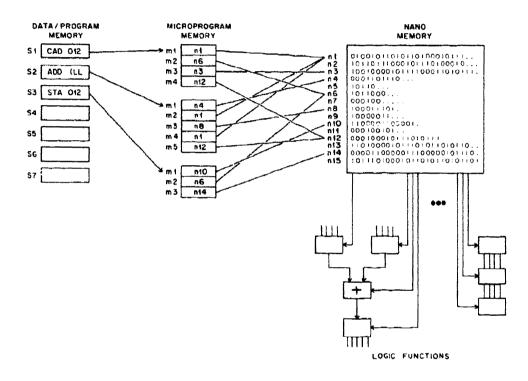

A unique feature of the Interpreter-Based System with its separate Nanomemory and Microprogram Memory (Figure 5) is that the explicit enable lines for each microinstruction need be stored in the Nanomemory only once (regardless of the number of times that a specific microinstruction is needed in a program). To accomplish this saving in memory, the Microprogram Memory (MPM) contains the address in the Nanomemory where the explicit ones and zeros are stored that are needed to execute that instruction' type rather than the full microinstruction. Thus, several microprogram sequences which use the same microinstruction (e.g., transfer A to B) need only store in the Microprogram Memory the address of the Nanomemory word containing that microinstruction. Figure 6 illustrates this feature.

#### MICROPROGRAM MEMORY (MPM)

Each Interpreter requires a source of microprogram instructions to define the operation of the Interpreter.

Two possible solutions for providing this source of microprogram instructions are listed below:

- 1. A semiconductor MPM. This memory can be a read-only memory (EOM) if the Interpreter is to be dedicated to the function defined by the ROM. A read-write memory can be used for experimental purposes or when the function of the Interpreter might be changed, such as reconfiguration in a multiple Interpreter system. In this instance, the system could afford to wait while the MPM was reloaded from a remote microprogram store accessed via the Switch Interlock.

- 2. A buffer into a slower-speed, wider-word memory.

In presently deliverable large scale integration form of the Interpreter, the MPM is also implemented with Fairchild 256-work by 1-bit bipolar, nondestructive readout semiconductor memory packages. Both the MPM and the Nanomemory can be loaded from an external loader, switches or programmatically from its own MIR. The basic MPM is expandable in places of 256 words, and can be expanded up to 1024 words in the present Interpre Srs.

١

Figure 7. One Memory vs. Two Memory Implementation

#### **Microprogram Memory Considerations**

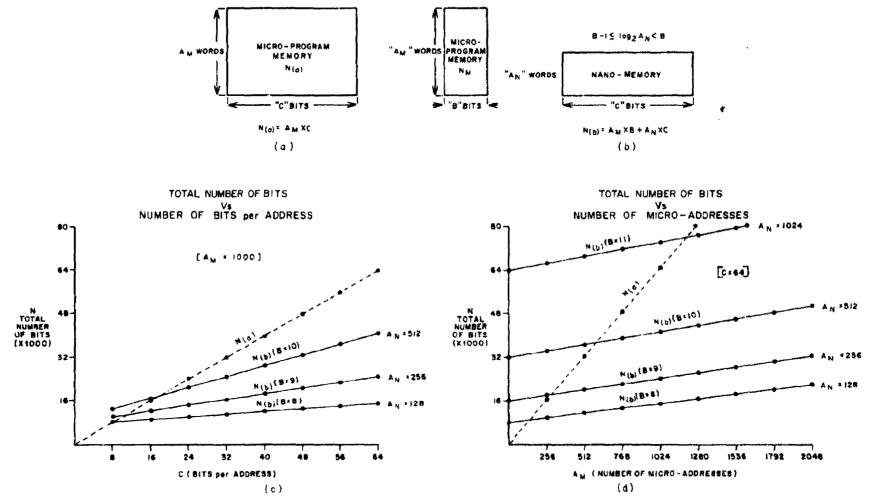

The potential advantage of dividing what is considered to be the Microprogram memory into two parts is more graphically illustrated by comparing the total memory requirements of the two approaches shown in Figure 7.

The total number of bits  $(N_{(a)})$  in Figure 7 (a) is given by  $N_1 = A_M \times C$ . The total number of bits  $(N_{(b)})$  in Figure 7 (b) is given by  $(A_M \times B) + A_N \times C$ . A plot of the total number of bits vs. B and C and a plot of the total number of bits vs. A and B for both approaches are shown in Figures 7 (c) and (d).

From these figures, it is obvious that as  $A_N$  approaches  $A_M$ , one memory is the proper approach. Two factors affect the relationship between  $A_M$  and  $A_N$ . One is that literal values (type II instructions) used for shift amounts, jump addresses and 8-bit literals, that appear in the Microprogram memory, make no reference to the Nanomemory. Second, repetitive use of the same nanoinstruction causes an increase in  $A_M$  without adding words to the Nanomemory. Some cample program statistics are shown in Figure 8. This tigure shows, for four sample programs, the total number of microprogram and nanomemory words, the total number of bits for both the one and two memory approaches and the percentage and actual value of the number of bits saved using the two instead of the one memory approach. In addition, this table shows the comparison among the number of literals (type II instructions), the number of Nanomemory locations in the four sample programs.

It should be remembered that the two memory approach would require memories with approximately twice as fast an access time (and hence are more expensive per bit) because both memories must be accessed sequentially within one clock time.

Memory cost per bit vs. memory cycle time is shown in Figure 9, where the vertical bars indicate the range on these prices which were gathered during January, 1972. Although the absolute prices have decreased, the relative pricing should still be valid. Several cost factors (C. F.'s) are shown for memory speeds having a 2:1 ratio. The cost factors are simply the ratio of the price of the faster memory to that for the slower memory. The higher cost factor encountered when crossing technology boundaries should be noted.

The solid lines in Figure 10 show the actual cost savings of the two memory approach for the four sample programs taking into account the difference in memory prices for the two approaches.

Also it is important to realize that many applications require a writable Microprogram memory. This means that the entire memory in the one memory approach must be read-write, while with the two memory approach, the Nanomemory could be read-only with the Microprogram memory being read-write. (In fact the Nanomemory could even be partly read-only and partly read-write.) This is shown by the dashed lines

|                       | PROGRAM STATISTICS |            |            |     | TOTAL | BITS |      | 2 MEMORY TECHNIQUE<br>BIT BREAK DOWN |                |           |      |      |

|-----------------------|--------------------|------------|------------|-----|-------|------|------|--------------------------------------|----------------|-----------|------|------|

| TASK                  | A <sub>M</sub>     |            |            |     | Í T   |      |      | •1                                   | BIT SAVINGS    |           |      |      |

|                       | TOTAL              | TYPE I (%) | TYPEI (%)  | AN  | Rav.  | N(a) | N(b) | NM                                   | N <sub>N</sub> | N(a)-N(b) | ∆n₁  |      |

| D-825 EMULATION       | 3337               | 2224 (67%) | 1113 (33%) | 964 | 2.31  | 187K | 108K | 54K                                  | 54K            | 79K (42%) | 35 K | 44 K |

| B-300 EMULATION       | 3265               | 1996 (61%) | 1269 (39%) | 624 | 3.20  | 183K | 87K  | 52K                                  | 35K            | 96K (52%) | 45 K | SIK  |

| DISK CONTROLLER       | 1288               | 910 (71%)  | 37% (29%)  | 244 | 3.73  | 72K  | 34 K | 21K                                  | 14K            | 38K (52%) | 23 K | 15K  |

| ANGLAGE DESIGN SYSTEM | 659                | 394 (60%)  | 265 (40%)  | 244 | 1.61  | 37K  | 25K  | 418                                  | 14K            | 12K (32%) | 2 K  | 10 K |

4

-

.

Figure 8. Sample Program Statistics

MEMORY COST vs MEMORY SPEED

MEMORY CYCLE TIME ( ns )

Figure 9. Memory Cost vs. Memory Speed

19

Figure 10. Two Memory Cost Savings vs. Cost Factor

20

in Figure 10 for the four sample programs using a "read only factor (ROF)" of 6. This ROF is an estimate of the ratio of the price of read-write memory to that for read-only memory.

In both cases, the values for a cost factor of 1.0 are the cost savings if memory cost were constant with respect to memory speed. The abscissa gives the cost factors required for the two approaches to be equal in cost.

#### LOADER (LDR)

One LDR is required for each Interpreter. 'The LDR provides clock controls for the Interpreter and the means for loading the Interpreter's MPM and Nanomemory from one of three sources:

- 1. Switches on the MPM/Nanomemory light panels.

- 2. A card reader assigned to loading.

- 3. The least significant 16 bits of the MIR of the same Interpreter.

It is possible to load several Interpreters concurrently from their panel switches or from their MIR's. Concurrent loading into more than one Interpreter from the card reader assigned to loading is not permitted.

Figure 11 is a diagram of the loading functions in the LSI multiprocessor.

Loading from the MIR is under microprogram control and provides the capability for programmatic overlay of the MPM and Nanomemory from any S memory module or any device attached to the Switch Interlock. A more detailed description of programmatic overlay from S memory is given in Sections VII and VIII.

Figure 11. Implementation of Loading Functions Block Diagram

#### SECTION III

### MULTIPROCESSING HARDWARE DESCRIPTION

## MULTIPROCESSOR INTERCONNECTION

A major goal in multiprocessor system design is to increase efficiency by the sharing of available resources in some optimal manner. The primary resource, main memory, may be more effectively shared when split into several memory "modules". A technique for reducing delays in accessing data in main memory is allowing concurrent access to different memory modules. With this concurrent access capability present, an attempt is made to assign tasks and data to memory modules so as to reduce conflicts between processors attempting to access the same memory module. Nevertheless, since some conflicts are unavoidable, a second technique (reduction of conflict resolution time) is required. These two techniques are largely a function of the multiprocessor interconnection scheme which has been discussed by Curtin<sup>2</sup> and others.<sup>3,4</sup>

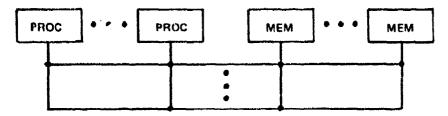

Figure 12 shows three basic functional interconnection schemes. These are described in more detailby Curtin.<sup>2</sup>

The disadvantages of the single bus approach (Figure 12) for many processors are:

- 1. the obvious bottleneck in information transfer between processors and memory modules due to both bus contention and memory contention

- 2. the catastrophic failure mode due to a single component failure in the bus.

A solution to the first problem has been to increase the frequency of operation of the bus.<sup>2,5</sup>

.

•

(a) Single Bus Interconnection

(b) Multiple Bus Interconnection

(c) Dedicated Bus Interconnection

.

Figure 12. Functional Multiprocessor Interconnection Scheme

,

The multiple bus approach is merely an extension of the single bus approach where all processors contend for use of any available (non-busy) bus. The advantages are redundancy and allowing an appropriate number of buses (less than the number of processors) to handle the traffic between processors and memory modules.

The third approach utilizes a dedicated bus structure (one per processor). Although this approach required more buses, it requires neither the logic nor, more importantly, the time for resolving priority between processors requesting the use of a bus. Proponents of this approach contend that the time penalty for resolving conflicts for access to a memory module is enough of a price to pay without having to wait for the availability of a bus.

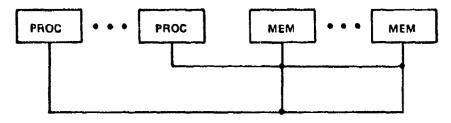

In a Hughes report,<sup>4</sup> the authors distinguish the physical differences between two multiprocessor interconnection schemes. The two approaches (one called multiport and the other called matrix switch) are shown in Figure 13.

The Hughes report characterizes the two connection approaches as follows:

"In the multiport approach, the access control logic for each module is contained within that module, and intercabling is required between each processor and memory pair. Thus, the total number of interconnecting cables is the product of the number of processors and the number of memories. Each module must be designed to accommodate the maximum computer configuration.

"In the matrix switch approach, the same interconnection capability is achieved by placing the access control logic for each module in a separate module. The addition of this module to the system is compensated (for) by reducing the intercables required to the sum of the processors and memories rather than the product and by not penalizing the other modules with maximum switching logic.

"There generally is no speed differential between multiport and matrix arrangements. The major difference lies in the ability to grow in wiring complexity. Multiprocessors with multiport arrangements are generally wired, at production time, to the maximum purchased configuration. Future subsystem expansion generally requires depot level rewiring. This problem generally does not exist with the matrix arrangement. The maximum capacity is wired in but the switching logic complement reflects the purchased system. Subsystem expansion entails purchase of added processor/memory modules (and necessary cabinetry if required) plus the required switch matrix logic cards."

Apparent from the arguments in this report is the desire to reduce the number of wires interconnecting the processors and memory modules. A way to reduce the wiring (in addition to the use of the matrix switch) is by using serial transmission of partial words at a frequency several times that of the processors. This technique has been used by Meng<sup>5</sup> and Curtin.<sup>2</sup> The tradeoff here is between the cost

.

,

(a) Multiport

.

(b) Matrix Switch

Figure 13. Physical Multiprocessor Interconnection Scheme

of the transmitting and receiving shift registers and the extra logic necessary for timing and control of the serial transmission versus the cost of wiring and logic for the extra interconnection nodes for a fully parallel transmission path.

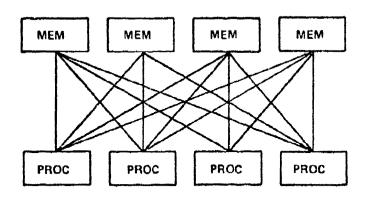

Another factor adversely affecting efficiency in a multiprocessing system is a variation in the amount of computation versus I/O processing that must be done. In previous multiprocessing systems I/O functions and data processing functions have been performed in physically different hardware modules with devices being attached only to the I/O controllers (Figure 14). (This technique is typical of Burroughs D825, B 5500, or B 6700). In a multi-interpreter system, however, processing and I/O control functions are all performed by identical Interpreters whose writable microprogram memory can be reloaded to change their function. This technique allows a configuration (Figure 15) in which the devices are attached to the same exchange as the memories and processors.

#### THE SWITCH INTERLOCK

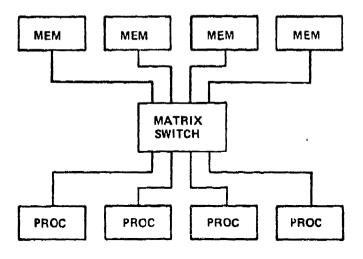

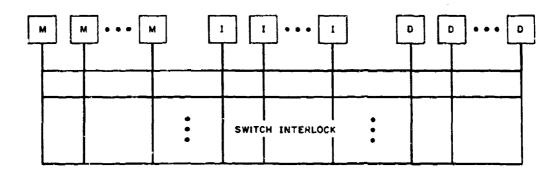

The Multi-Interpreter interconnection scheme for forming a multiprocessor is called a "Switch Interlock": a dedicated bus, matrix switch with an optional amount of serial transmission.

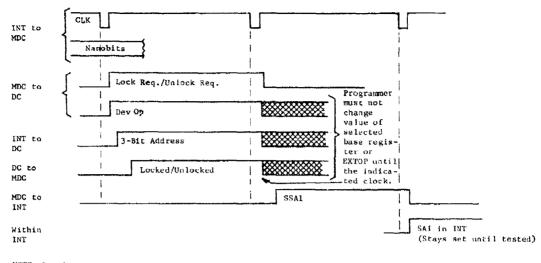

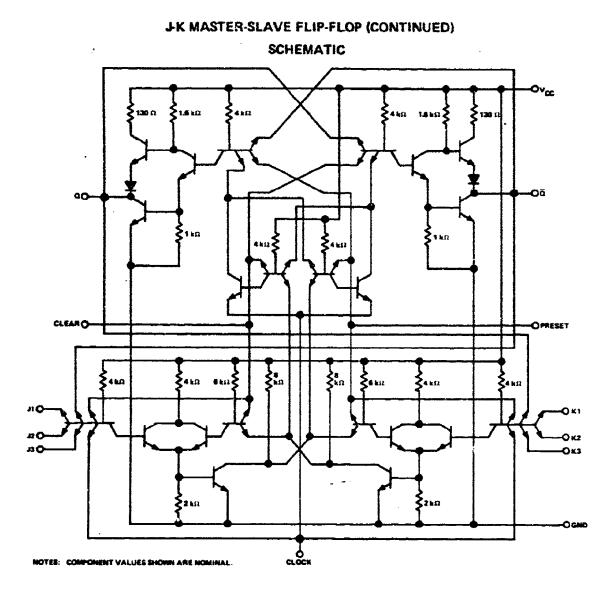

The Switch Interlock is a set of hardware building blocks that connects Interpreters to devices and memory modules. Connection between Interpreters and devices is by reservation with the Interpreter having exclusive use of the (locked) device until specifically released. Connection with a memory module is for the duration of a single data word exchange, but is maintained until some other module is requested or some other Interpreter requests that module.

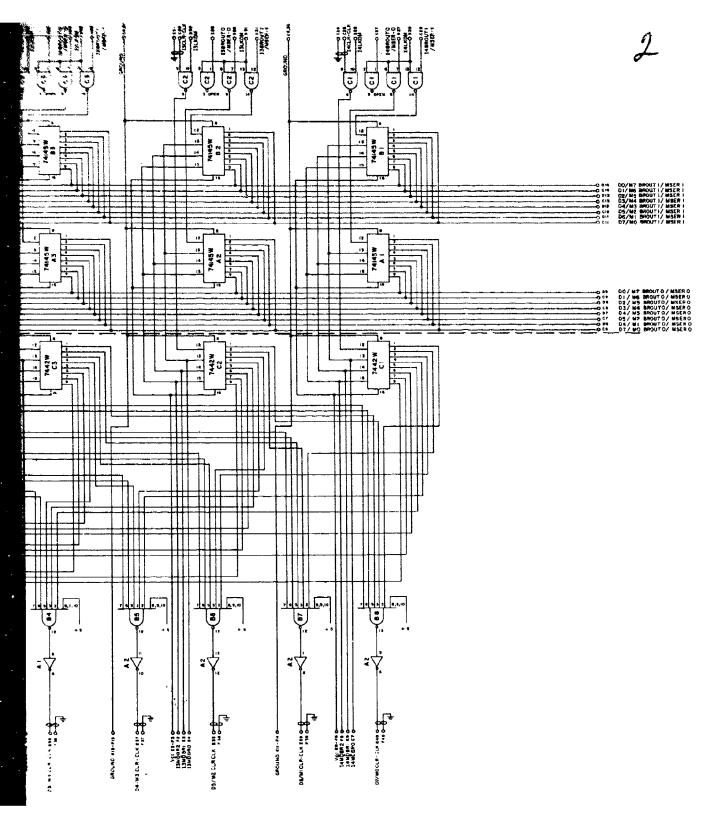

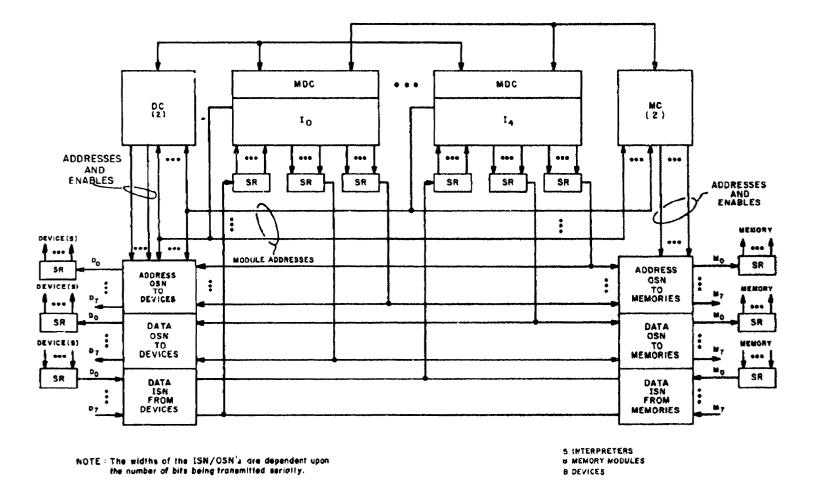

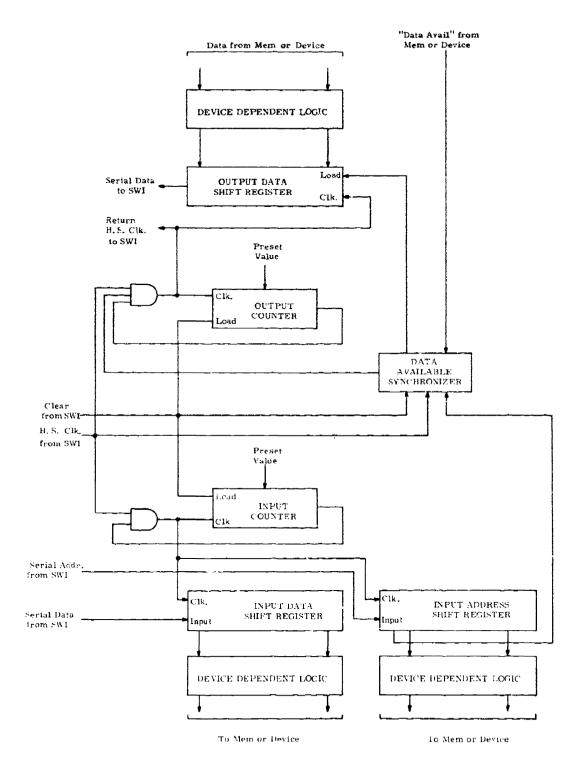

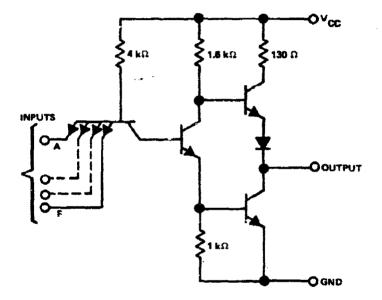

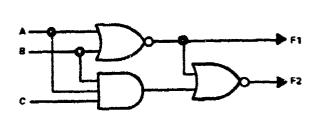

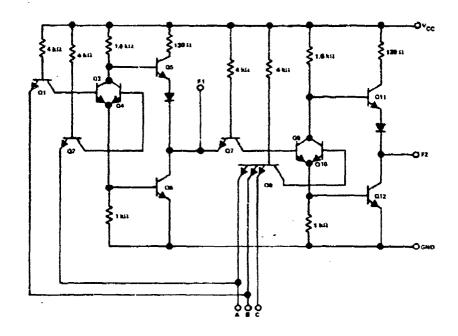

Consistent with the building block philosophy of Interpreter-based systems, the Switch Interlock is partitioned to permit modular expansion for incremental numbers of Interpreters, memory modules or device ports and modular selection of the amount of parallelism in the transfer of address and data through the Switch Interlock from fully parallel to fully serial. Functionally, the Switch Interlock consists of: parallel-serial conversion registers for each Interpreter, input and output selection gates, parallel-serial conversion registers for each memory module and each device, and associated control logic. Figure 16 outlines the implementation of the Switch Interlock and shows the functional logic units that are repeated for each Interpreter, memory module, and device. The bit expandability of the Switch Interlock is shown by dashed lines between the input/output switches and the shift registers associated with the memory module, devices, and Interpreters.

The Switch Interlock in the LSI Multiprocessor handles five Interpreters, eight memories and eight device ports (more than one device could be attached to each port). The transmission paths through the Switch Interlock break the 32-bit data word into 8 wires carrying 4 serial bits each, transmitted with a "high speed" clock having a frequency five times that of an Interpreter clock.

Figure 14. Centralized Multiprocessor System

Figure 15. Distributed Multiprocessing Interpreter System

Figure 16. Implementation of the Switch Interlock

Figure 17. Memory/Device Controls (MDC) Block Diagram

.

The six basic modules for the Switch Interlock of the LSI Multiprocessor are described below.

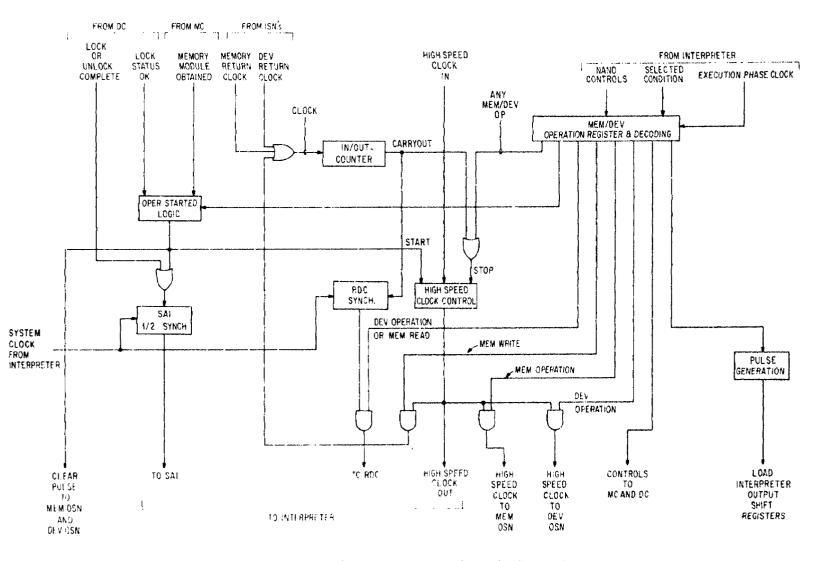

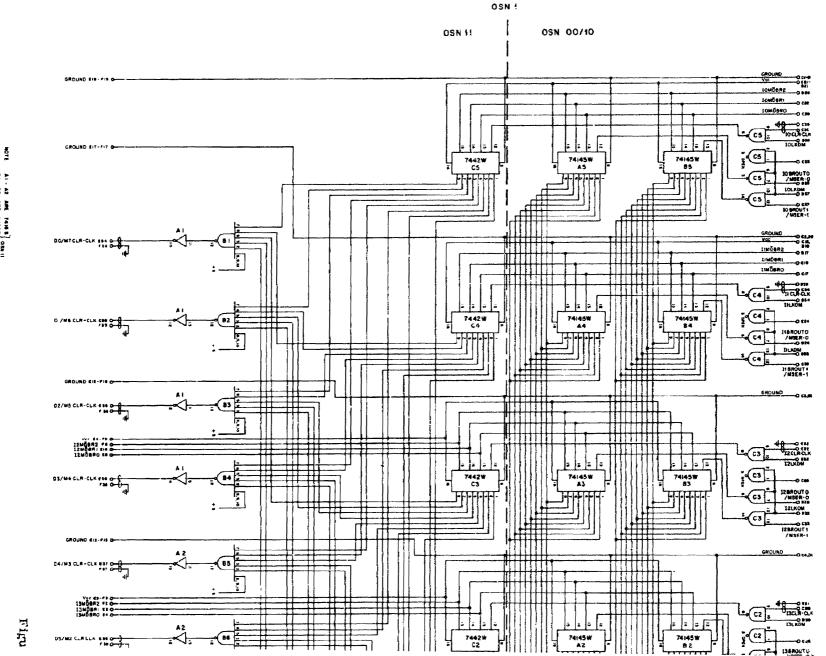

### Memory/Device Controls (MDC)

The MDC controls the high-speed clock used for the serial transmission of data (Figure 17) and is an interface between the Interpreter and the controls described below (MC and DC). There is one MDC per Interpreter. Physically, the MDC's for two Interpreters are contained in one finned 5-inch by 5-inch by 1/2-inch plate.

### Device Controls (DC)

The DC resolves conflicts between Interpreters trying to lock to a device and checks the lock status of any Interpreter attempting a device operation (Figure 18). Physically, the DC is contained on two identical finned plates, each plate capable of handling up to three Interpreters and up to eight devices. System expansion using this module could be in number of Interpreters or in number of devices.

### Memory Controls (MC)

The MC resolves conflicts between Interpreters requesting the use of the same memory module (Figures 19 and 20). Physically, the MC is contained on two finned plates. One plate contains the MC for three Interpreters and eight memory modules and the other plate contains the MC for the other two Interpreters and eight memory modules, plus the "memory-busy" flip-flops. The global condition bit priority resolution and the interrupt Interpreter logic is also physically located on this second plate although it is functionally independent. System expansion using the MC could be in number of Interpreters or in number of memory modules.

#### Output Switch Network (OSN)

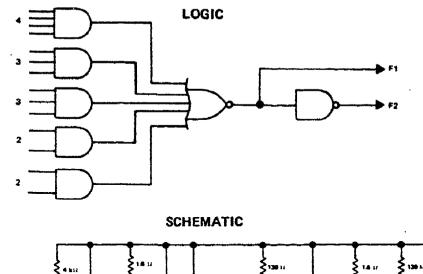

The OSN sends data, address, clock, and control from Interpreters to addressed devices or memory modules (i. e., the OSN is a "demultiplexer"). Physically, the OSN is made of two different types of finned plates handling either three or four wires for up to five Interpreters and eight devices or memory modules. One type of plate handles four data-type paths for five Interpreters and eight devices or memories. The other type of plate handles two data-type paths and one clock-type path for five Interpreters and eight devices or memories. Logic diagrams of these types of OSN's are shown in Figures 21 and 22. Each column of logic is for one Interpreter with the inputs from the Interpreter coming in the top. Each row represents one serial transmission path and the outputs to eight devices or memories coming from the side and bottom of the drawing. System expansion using these modules could be in number of

Figure 18. Device Controls (DC) Block Diagram

Figure 19. Memory Control No. 0, Block Diagram

Figure 20. Memory Control No. 1, Block Diagram

Interpreters or in number of devices or memories. The number of replications of this plate would also change if the amount of serialization of the data path were changed.

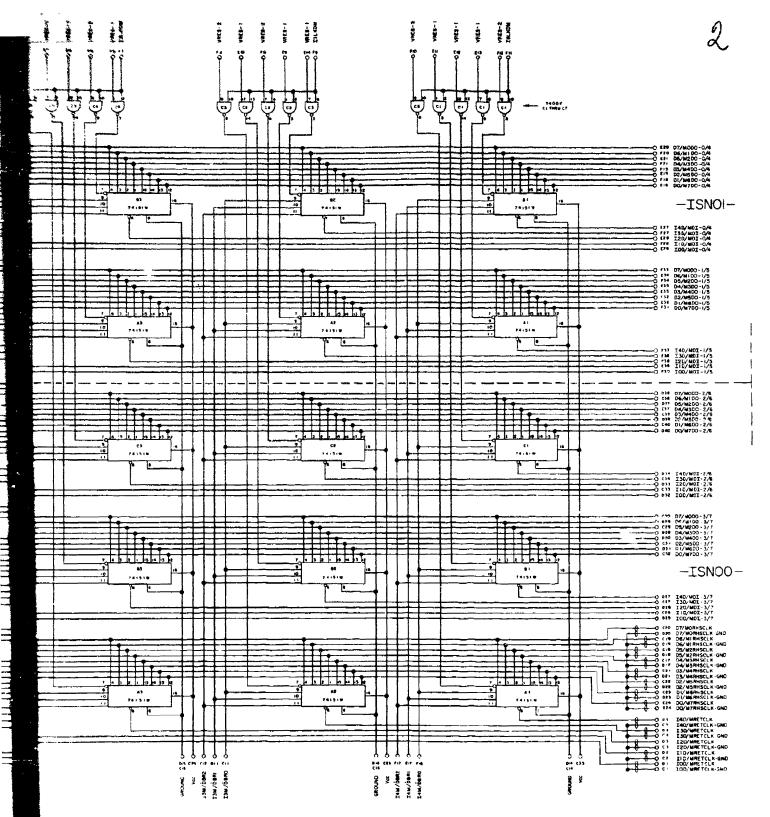

#### Input Switch Network (ISN)

The ISN returns data from addressed devices or memory modules to the Interpreters (i. e., the ISN is a "multiplexer"). One finned plate handles five wires for five Interpreters and up to eight devices or memory modules. A logic diagram for the ISN is shown in Figure 23. As with the OSN, each column of logic is for one Interpreter with the outputs to the Interpreter coming from the top. Each row also represents one serial transmission path with the inputs from eight devices or memories coming in the side of the drawing. System expansion using this module could be in number of Interpreters or in number of devices or memories. The number of replications of this plate would also change if the amount of serialization of the data path were changed.

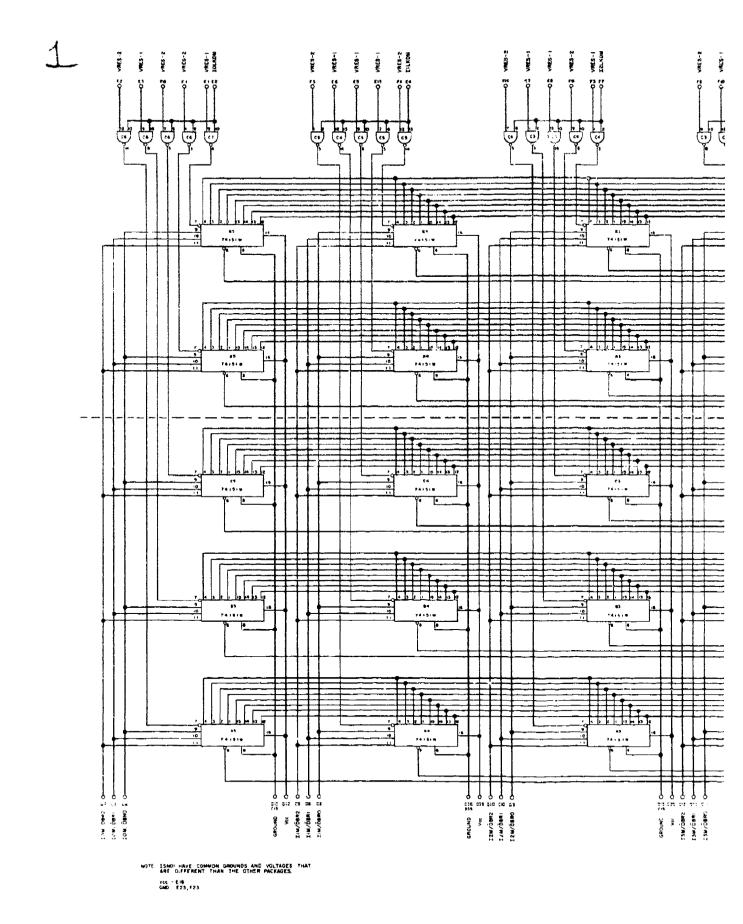

## Shift Register (SR)

These units are parallel-to-serial shift registers or serial-to-parallel shift registers that use a high frequency clock for serial transmission of groups of four data and address bits through the ISN's and OSN's. They are physically located with the Interpreters, device interfaces, and memory module interfaces.

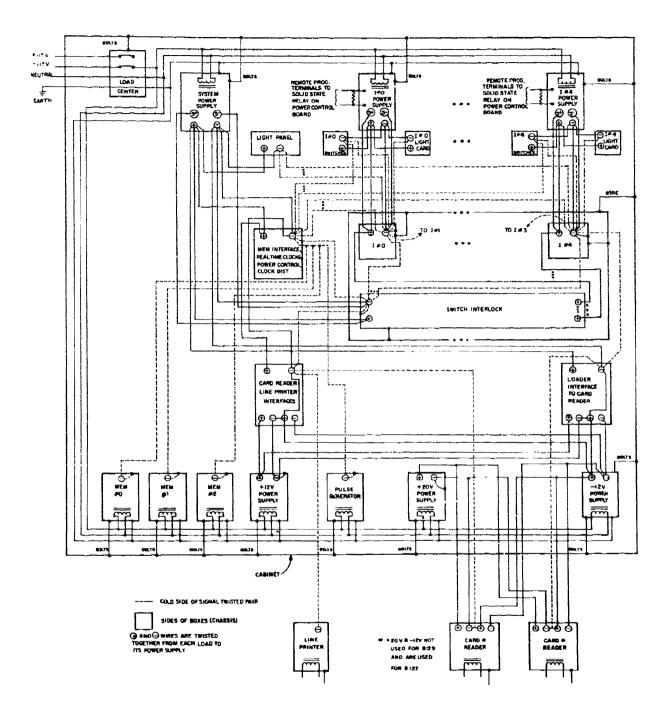

#### POWER DISTRIBUTION

Figure 24 shows the details of the power distribution system in the aerospace multiprocessor. Even though all a-c connections are shown schematically attached to one line, a load center is mounted inside the cabinet and two phases of a three phase four wire 120/208 volt 60 Hz input are each connected through the load center to four strips of electrical outlets mounted inside the cabinet.

As shown, each Interpreter has its own power supply with a connection to the Switch Interlock for supplying +5 volts to the MDC for that Interpreter. All +5 volt distribution is by heavy gauge wire twisted with its return. All sensing and connections of return to chassis are done at the point of load. The system power supply provides power to the device and memory interfaces, the real time clock, power control and clock distribution, the light panel, and the Switch Interlock. The sensing for the system power supply is on the Switch Interlock.

As can be seen, the multiplicity of reference-to-reference connections via the cold side of the twisted pairs made proper "treeing<sup>6</sup>" of the references before connection to earth impractical. Therefore freely tying reference to chassis was allowed.

In retrospect, the only changes suggested would be providing a better referenceto-reference connection between each Interpreter and the Switch Interlock, and removing the reference to chassis connections on the  $\pm 12$  volt,  $\pm 12$  volt, and  $\pm 20$  volt supplies after insuring a suitable reference to chassis connection at the loads.

The only grounding problem encountered was on the loader board in the Interpreters. This problem was eliminated by installing a wire ground grid on the board and by providing extra ground pins from the board to the backplane. Of interest is that no decoupling capacitors exist in the system. Space for decoupling capacitors has been provided and should be added if noise problems are encountered; however no such problems have arisen during the fairly extensive testing before and after delivery.

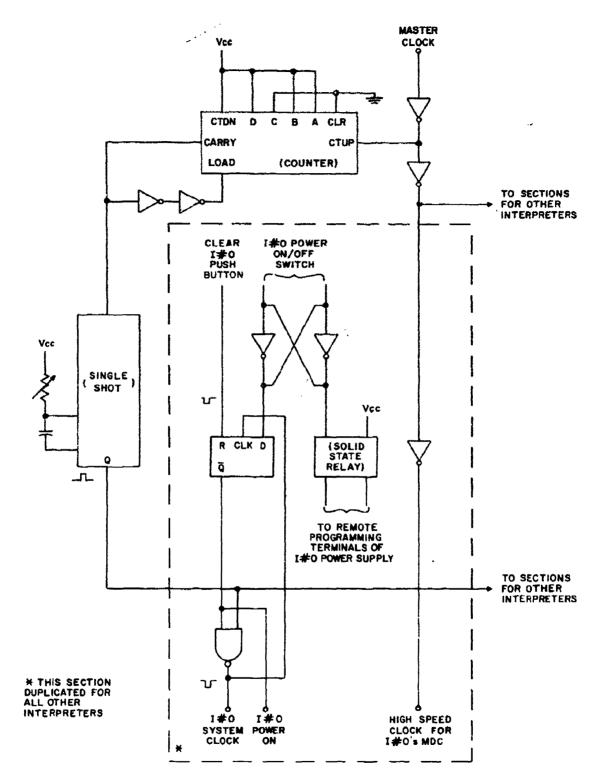

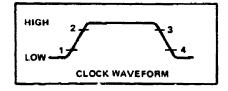

#### CLOCK AND POWER CONTROL

From the description of the Switch Interlock, it is clear that two clocks having different frequencies are needed in the aerospace multiprocessor. During the design of the aerospace multiprocessor the relationship between the maximum shift rate through the Switch Interlock and the maximum speed of the Interpreters was determined to be at least 4:1. Since four bits are transmitted serially on each path through the Switch Interlock and shifting is to be finished within one Interpreter clock time, a ratio of 5:1 was selected. However, from the implementation as shown in Figure 25, this ratio could be easily changed by changing the value preset into the counter. The logic appearing in this figure is all controlled by a central system power supply, which in a failsafe system must be made redundant.

As shown in the figure, the width of the high-speed clock to the MDC's in the Switch Interlock is controlled by the width of the master clock coming in from the pulse generator, and the width of the Interpreters' clock is controllable by varying the resistor value on the single shot. The flip-flop control has been added to the clock for each Interpreter to insure against performing any spurious memory or device operations while power is either being applied or being shut off

OSN O

Figure 21. Output Switch Network No. 0, Logic Diagram

A1- A2 AME 74305 05H D0/10 C1- C5 AME 74305 05H D0/10

Figure 22. Output Switch Network No. 1, Logic Diagram

Figure 23. Input Switch Network No. 1, Logic Diagram

Figure 24. Power Distribution System

Figure 25. Implementation of Multiprocessor Clocks

•

Figure 26. Conflict Resolution Logic for Global Condition Bit GC1

to an Interpreter. This is done by a front panel switch setting the flip-flop (which will shut clocks off) and turning the solid state relay on, which will then short across the resistor on the remote programming terminals of the Interpreter's power supply, turning the power supply off. When the front panel switch is set to turn power back on, the solid state relay will turn off, opening up the output of the relay and turning power back on to the Interpreter. However, if clocks were applied at this time, they would start during the powering up of the Interpreter and would continue even though no valid information existed in the Interpreter's Microprogram and Nano memories.

To avoid this problem, clocks are not restarted until the Clear pushbutton is pressed on the front panel, which is done in conjunction with pressing the Load pushbutton for loading the Microprogram and Nano memories from the loader card reader. Since during loading, a pseudo Type II instruction is forced by the loader,  $r_{2}$  clocks will be present to initiate any memory or device operations until loading is completed and the microprogram just loaded begins execution.

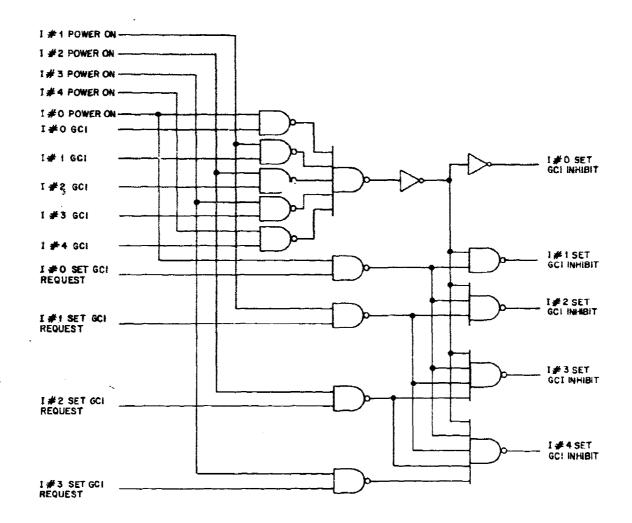

#### GLOBAL AND INTERRUPT CONDITION BITS

The two global condition bits in each Interpreter are used by programmatic convention for locking out other Interpreters during a read-modify-write to system tables resident in S memory. This is done independently for each of the two condition bits by not allowing an Interpreter to set its condition bit if any Interpreter's condition bit is already set or if a higher wired priority Interpreter is requesting to set its condition bit at the same time. This was initially to be done by chaining the priority through the Interpreters so that no external logic would be required. However, if an Interpreter's power were turned off, the chain would be broken and the same global condition bit in two Interpreters could have been set. To avoid this problem the global condition bit and the requests to set the global condition bits are brought from each Interpreter to a centralized location. (The Switch Interlock was chosen, although this logic is totally independent of the Switch Interlock operation.) In this centralized location, the power-on signals show a previously in this section are used to allow only signals from powered on Intermeters to participate in the conflict resolution. This conflict resolution logic is , wered by the system power supply and in turn sends enables back to the Interpreters for setting the global condition bits. This conflict resolution logic is shown for one of the global condition bits (GCI) in Figure 26. The same logic is repeated for the other global condition bit (GC2).

The Interrupt Interpreters condition bit, although having no priority logic associated with it, has the similar problem of having a signal from an Interpreter that is either powered down or whose power is undergoing a transition, setting the Interrupt condition bit in other Interpreters in an uncontrolled manner. To avoid this, the Interrupt signal and its control coming from each Interpreter are gated against the power-on signal for that Interpreter. These signals are then all ORed together and sent back to all Interpreters. This logic (shown in Figure 27) is also located in the Switch Interlock and is powered by the system power supply.

Figure 27. Implementation of Interrupt Controls

### REAL TIME CLOCK AND THE HORNS

One device (device number zero) has been permanently assigned to a device called a "real time" clock, which is used programmatically to determine the failure of a task running on an Interpreter. This use is explained more fully in the Multiprocessing Control Program and Demonstration Programs section of this report. This device is merely a 32-bit counter that is counted up at a rate of once each 256 Interpreter clocks. It is powered by the system power supply and runs continuously. This device is read just as any other device attached to the Switch Interlock and must be locked to in order to be read. Since programmatically this counter is used as an interval timer, a potential problem exists if the interval to be timed were started just prior to this device overflowing (once every  $2^{40}$ Interpreter clocks). This can be avoided by forcing the programs to test the value of the counter to insure it will not be reset during the interval of interest.

Also physically located with the real time clock are five, 4-bit counters, one associated with each Interpreter. These counters, called horns, if not reset, will overflow after every 2<sup>20</sup> Interpreter clocks (approximately every 1 second for a 1 MHz Interpreter clock rate). These counters detect an Interpreter waiting for a response from a memory or device that has failed. An overflow from one of these counters will force a one clock time STEP and will set a condition bit in its associated Interpreter which then can be tested by the Interpreter. To avoid continual setting of this bit, each counter is reset every time its associated Interpreter does any memory or device operation. These operations should occur often in any program except perhaps during internal Interpreter diagnostics. These diagnostics should not require 2<sup>20</sup> Interpreter clocks to run but if they did the horn for the Interpreter may be manually turned off.

#### INTERPRETER NUMBER

Each Interpreter is logically identical to all other Interpreters. A multiprocessing control program, however, must have a means of distinguishing between Interpreters. This is accomplished by wiring the most significant four bits of the next to the most significant 8-bit byte of the Z-input to the adder, to the connector to which the loader cable is attached. Ground and +5 volts are also wired to this connector. Within the other side of the connector, which is part of the loader cable, ground and +5 volts are jumpered to the 4 bits of Z input to appropriately indicate the Interpreter number, right justified within the 4-bit field.

| SECEDING PAGE BLANK NOT FILMED |

|--------------------------------|

|--------------------------------|

# SECTION IV

# AEROSPACE MULTIPROCESSOR PACKAGING DESCRIPTION

## MECHANICAL DESIGN

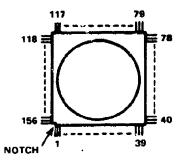

The aerospace multiprocessor is housed in a cabinet consisting of two bays 21 inches wide by 25 1/2 inches deep by 68 inches high (Figure 28). The Interpreters, and Switch Interlock modules are built up of mechanically similar submodular sections. The S memory module and power supplies are commerically available rack mounted units.

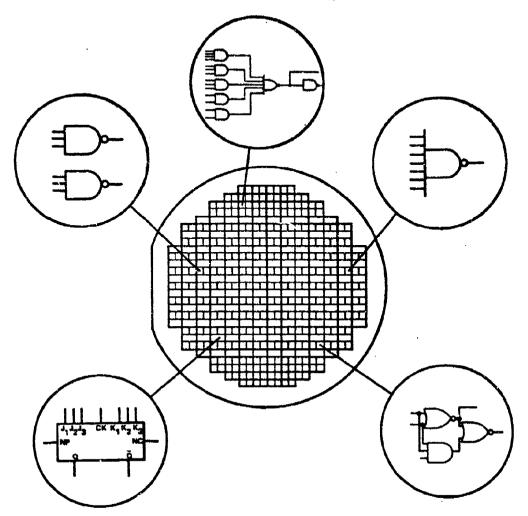

Each of the modules is made up of several finned aluminum castings (Figure 29) with massive heat sinks for mounting of the printed wiring boards and direct heat sinking of the LSI packages. Modification of the finned aluminum casting allows direct heat sinking of conventional dual in-line packages for the MPM and Nanomemories. The 5-inch by 5-inch by 1/2-inch thick submodule houses two LSI chips, as many as 98, 16-lead flat packs or as many as 45, 16-pin dual-in-line packages, depending on its function in the system.

Each of the Interpreter modules (Figure 3) and the Switch Interlock module is packaged complete with its own backplane and I/O connectors to simulate remote physical distribution of the modules.

To maintain a close physical arrangement with simulated module distribution, all of the Interpreters are mounted on a common mechanical structure which allows the multiprocessor to be mounted as a single unit on a shelf extending at right angles to the front of the two electronics cabinets as shown in Figure 1. The multiprocessor is mounted on a swivel to allow direct access to the wire wrapped backplane during debugging and testing procedures.

(f)

(5)

Figure 28. Aerospace Multiprocessor Configuration

Figure 29. Submodule Housing

Figure 30. Interpreter Module Packaging

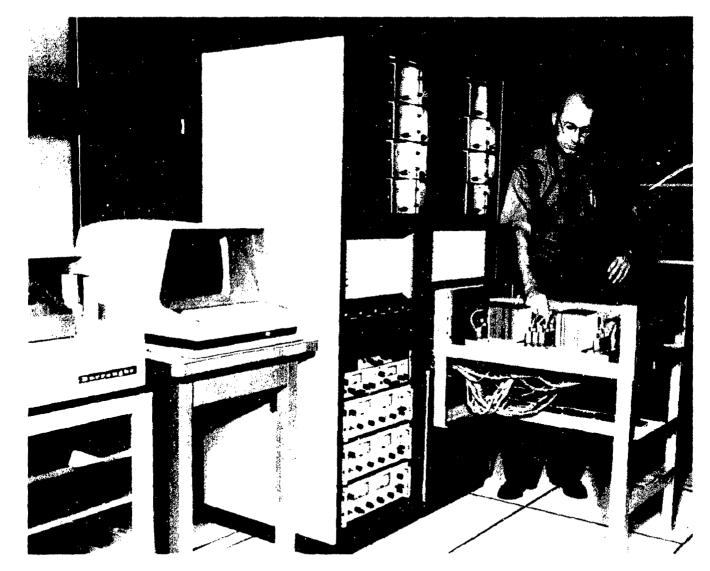

Figure 31 is a photograph of the system as installed at Wright-Patterson Air Force Base.

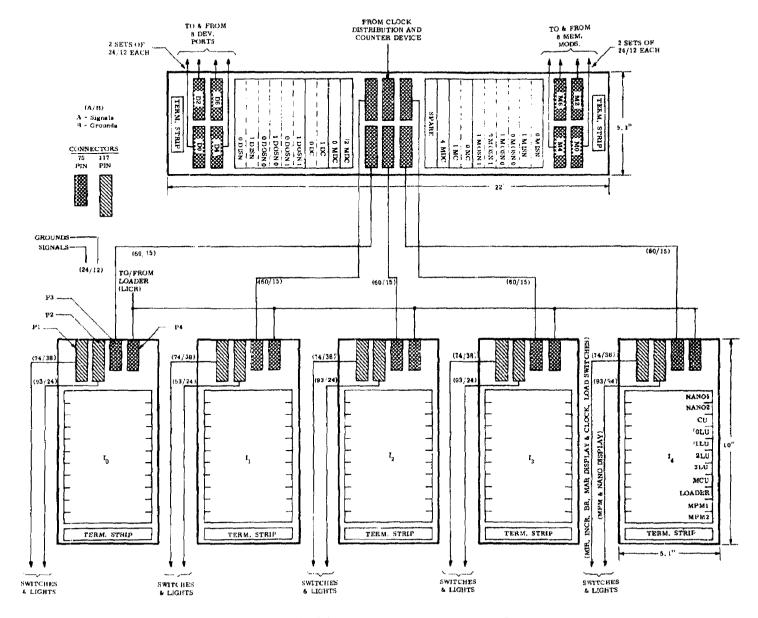

Figure 32 is a plan view of the Interpreters, Switch Interlock and connectors for interconnection among the modules.

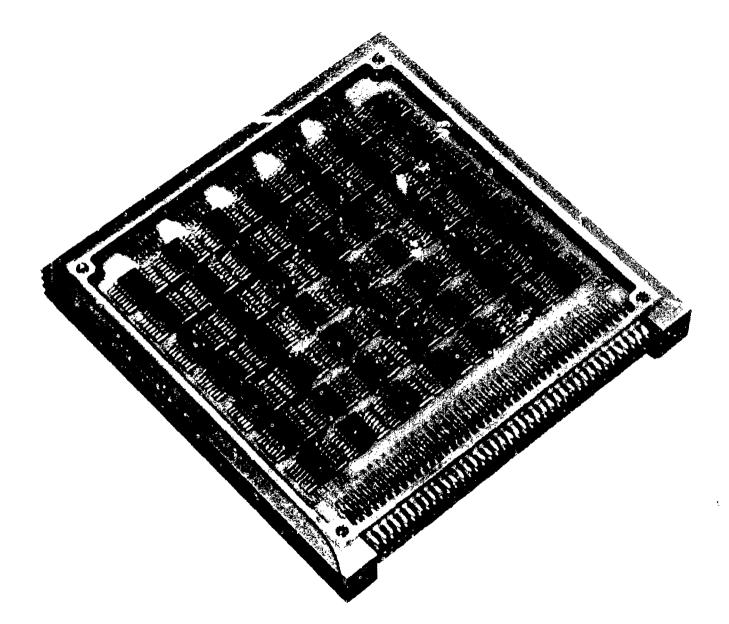

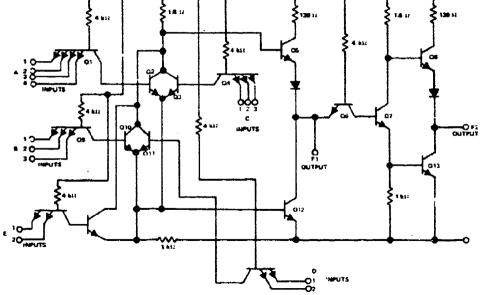

## CIRCUIT CONFIGURATIONS

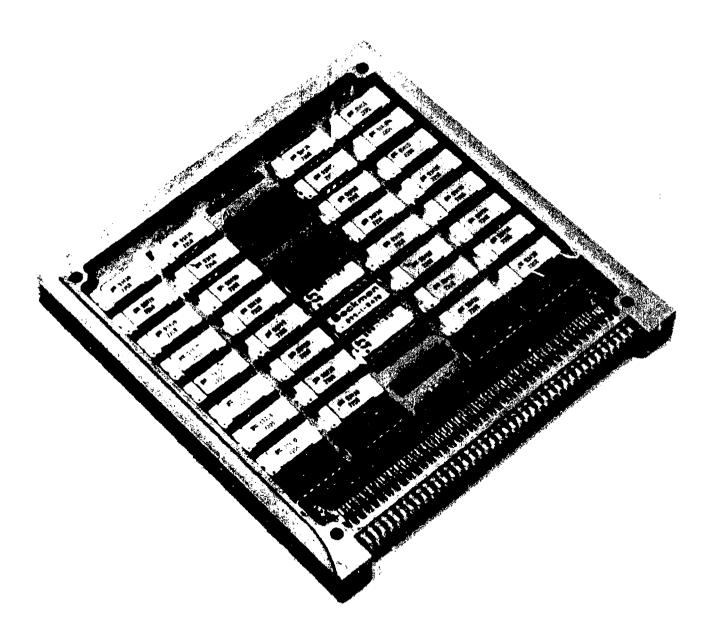

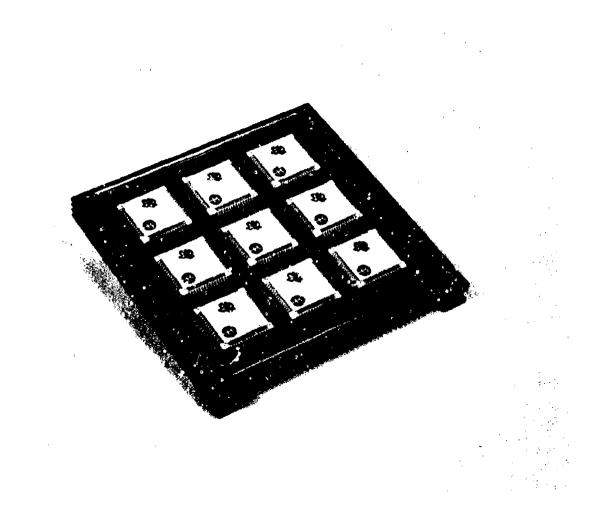

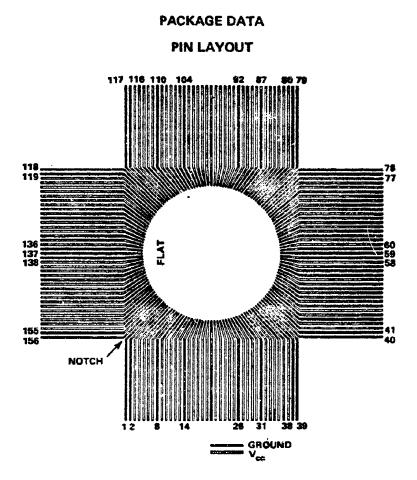

The LSI multiprocessor system is implemented with the three types of submodules. The Microprogram and Nano memories in the Interpreter both use Fairchild 93410 ceramic dual-in-line packages, each containing 256 words  $\times 1$  bit of memory, interconnected with a four-layer printed circuit board mounted on the opposite side from the packages as shown in Figure 33. Since the selection of this package, Fairchild has introduced the 93415, a 1024 word  $\times 1$  bit memory package with approximately the same power dissipation as the 93410. This more dense memory package is recommended for future Interpreter systems.

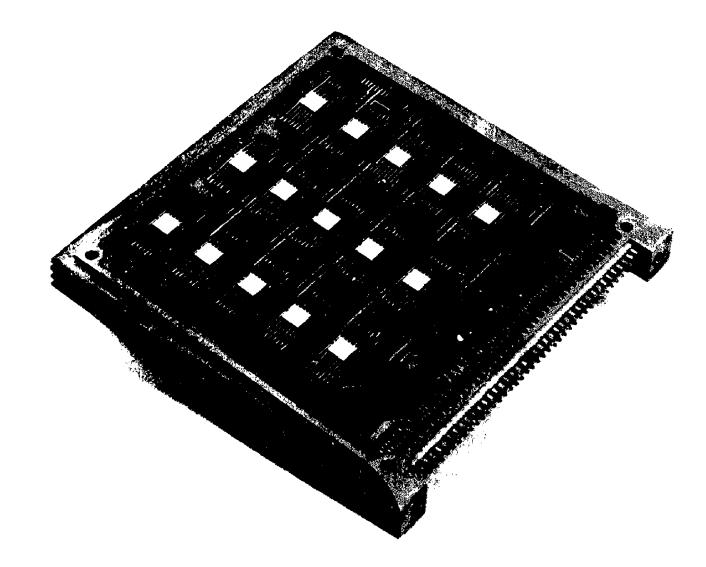

The Loader submodule in the Interpreters and all submodules in the Switch Interlock use standard 54/7400 series flat packs which are mounted on either two or four layer printed circuit boards which are then mounted on the two sides of the aluminum plate submodule as shown in Figure 34. The packing density of the flat packs is typically between 25-30 per board, since most of these submodules are pin limited and would have required six to eight layer boards to achieve the maximum packing density of 49 flat packs per board.

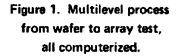

The remainder of the Interpreter logic is implemented with Texas Instruments discretionary wired, transistor-transistor logic (TTL) using their "N" and "S" arrays as follows:

8-bit Logic Unit (two Type "N" slices)

Memory Control Unit (two Type "N" slices)

Control Unit (two Type "S" slices)

This type of submodule is shown extended above the Interpreter in Figure 30.

A summary of the general characteristics of the individual arrays is given in Table II. Appendix II is the final report from Texas Instruments Incorporated on the LSI arrays.

Texas Instruments informed Burroughs in December 1971 that they were discontinuing fabrication of LSI Discretionary Routed Arrays (DRA) after the conclusion of their present commitments. However, several alternative packaging approaches exist which could package the Interpreter logic as densely as in the LSI/DRA approach of Texas Instruments.

Figure 31. Aerospace Multiprocessor Installation at Wright-Patterson Air Force Base

Figure 32. Multiprocessor Interconnection Scheme

Figure 33. Microprogram Memory, Nanomemory Submodule Packaging

Figure 34. Loader, Switch Interlock Submodule Packaging

| Name    | TI<br>LSI/DRA<br>Number | Function                           | Typical<br>Power | Input<br>Pins | Output<br>Pins | Number of Cells |                |                |      |      |                      | Number                          |

|---------|-------------------------|------------------------------------|------------------|---------------|----------------|-----------------|----------------|----------------|------|------|----------------------|---------------------------------|

|         |                         |                                    |                  |               |                | Exclusive<br>OR | 3-inp.<br>NAND | 7-inp.<br>NAND | ANI  | FF   | Equivalent<br>Gates* | of Test<br>Pattern:<br>Required |

| LU #1   | 3013                    | B Reg., Adder, BSW1 Controls       | 3.14             | 67            | 26             | 18              | 93             | 15             | 30   | 8    | 420                  | 338                             |

| LU #2   | 3014                    | BSW1, BSW2, A-Reg., MIR            | 4.10             | 47            | 34             | 16              | 113            | 17             | 26   | 32   | <b>552</b>           | 207                             |

| CU #1   | 3015                    | SAR, Clock Controls, Adder Decode  | 2.82             | 36            | 35             | 9               | 83             | 0              | 21   | 22   | 389                  | 452                             |

| CU #2   | 3016                    | Condition Reg., MPM Content Decode | 2.71             | 40            | 15             | 10              | 68             | 17             | 25   | 14   | 374                  | 786                             |

| MCU #1  | 3017                    | BR's, MAR, CTR, MPAD Controls      | 3.52             | 42            | 35             | 11              | 71             | 4              | 23   | 38   | 497                  | 348                             |

| MCU #2  | 3018                    | MPCR, AMPCR, LIT, INCR.            | 3.97             | 55            | 34             | 9               | 86             | 16             | 31   | 36   | 562                  | 531                             |

| N-slice |                         | Total Availabie                    |                  |               | ł              | 60              | 232            | 56             | 82   | 100  |                      |                                 |

|         |                         | (Recommended Ussage)**             | 1                |               |                | (18)            | (70)           | (17)           | (25) | (30) |                      |                                 |

| S-slige |                         | Total Available                    | }                |               |                | 18              | 96             | 30             | 46   | 58   |                      |                                 |

|         |                         | (Recommended Useage)               |                  | ļ             | 1              | (10)            | (60)           | (19)           | (21) | (26) |                      |                                 |

|         |                         |                                    | ļ                | [<br>]        |                |                 |                |                |      |      |                      |                                 |

Table II. Multiprocessor LSI Array Details

\*Exclusive OR = 3 gates; 3-inp NAND = 1 gate; 7-inp. NAND = 1 gate; And-Nor-Invert = 7 gates; Flip-Flop = 6 gates

\*\* Recommended Design with up to 30% of each single circuit type. This due to limitation on routing capability, not to circuit yield. Three of the approaches are as follows:

1. A flat pack version of the multiprocessor can be produced with the same volume, weight and power requirements as the LSI version.

The logic provided by two LSI chips can be duplicated with a maximum of 98,16-pin flat packs as shown in Figure 35. With the use of multilayer boards, the 98 flat packs can be interconnected on the same 5-inch by 5-inch 1/2-inch thick heat sink as used for two LSI chips.

- 2. By utilizing 60-pin hybrid flat packs as produced by TI, it is possible to package two 8-bit Logic Units on a single heat sink as shown in Figure 36. The Control Unit and Memory Control Unit can be packaged together on a single heat sink to provide a reduction of 1/2 the original volume. This technique would use Shottky low-power TTL.

- 3. A third approach which would give the same volumetric density as the present LSI model would be to utilize Hughes LSI which is produced by a proprietary pad-relocation process. The Hughes chips could be produced as one for one replacement of the LSI arrays used in the present processor or as a replacement for the logic on two LSI arrays that are presently mounted on one of the submodular housings.

Figure 35. Alternative Packaging Approach Utilizing 16-pin Flat Packs

Figure 36. Alternative Packaging Approach Utilizing 60-pin Flat Packs

## SECTION V

## INTERPRETER OPERATION

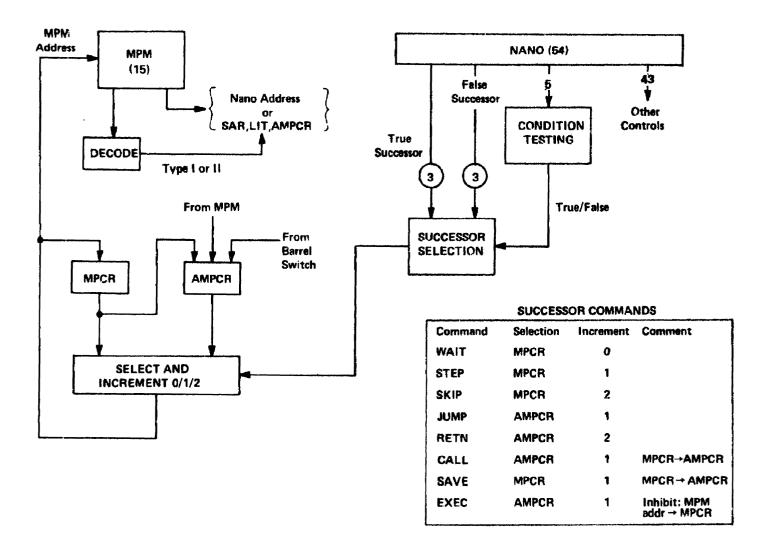

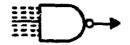

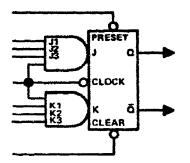

During each clock period, a microinstruction is read from the MPM. The first four bits of this microinstruction indicate which of two types of instruction it is. If it is a Type I instruction, the remaining bits of the MPM word specify a Nanomemory address to be accessed. The Nanomemory is then initiated and its output, a set of 54 bits, provides the control functions as indicated in the listing below.

## Nano-Bits

| 1-4     | Select a condition.                                                                     |

|---------|-----------------------------------------------------------------------------------------|

| 5       | Selects true or complement of condition.                                                |

| 6       | Specifies conditional or unconditional LU operation.                                    |

| 7       | Specifies conditional or unconditional external operation (memory or device)            |

| 8-10    | Specifies set/reset of condition.                                                       |

| 11-16   | Successor controls (wait, skip, step, etc.).                                            |

| 17-26   | Selects A, B, and Z adder inputs                                                        |

| 27      | Byte carry control.                                                                     |

| 28 - 31 | Selects Boolean and basic arithmetic operations.                                        |

| 32-33   | Selects shift operation.                                                                |

| 34-36   | Enables input to A registers.                                                           |

| 37-40   | Selects input(s) to B register.                                                         |

| 41      | Enables input to MIR.                                                                   |

| · 42    | Enables input to AMPCR.                                                                 |

| 43-48   | Enables and selects input to address registers and counter (MAR, BR1, BR2, CTR).        |

| 49-50   | Selects input to SAR.                                                                   |

| 51-54   | Selects external operations (read, write, lock, etc.),<br>MPM load, or Nanomemory load. |

BSW - BARREL SWITCH

DEST - BARREL SWITCH OUTPUT DESTINATIONS;I.E., REGISTERS (B, CTR, ETC.) AND THEIR INPUT LOGIC

- C.R. CONTROL REGISTER AND ASSOCIATED LOGIC

- AIS = ADDER INPUT SELECTION FROM COMMAND REGISTER

Figure 37. Timing Analysis, Type I Instructions

If the microinstruction is Type II, the remaining bits of the MPM word are stored into one or two registers: namely, the SAR, LIT, SAR and LIT, or the AMPCR. The determination of which registers are to be loaded is specified by the first bits of the MPM word. The Nanomemory is not accessed during a Type II operation.

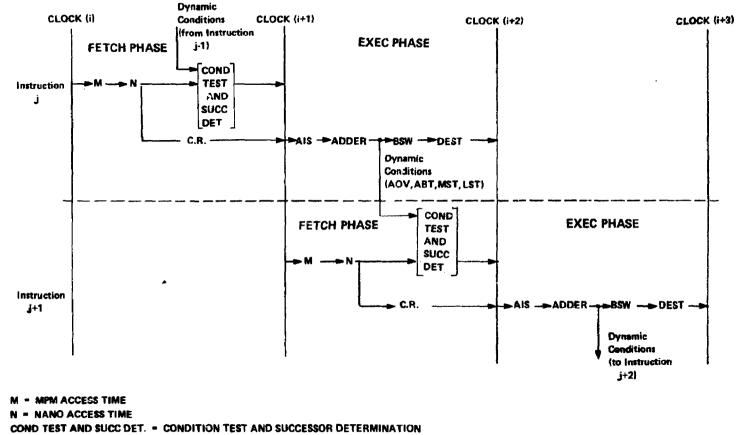

Each Type I microinstruction has two parts (or phases). The first feiches the instruction from the MPM and Nanomemory and the second executes the fetched instruction. Figure 37 illustrates these two basic phases of each Type I microinstruction.

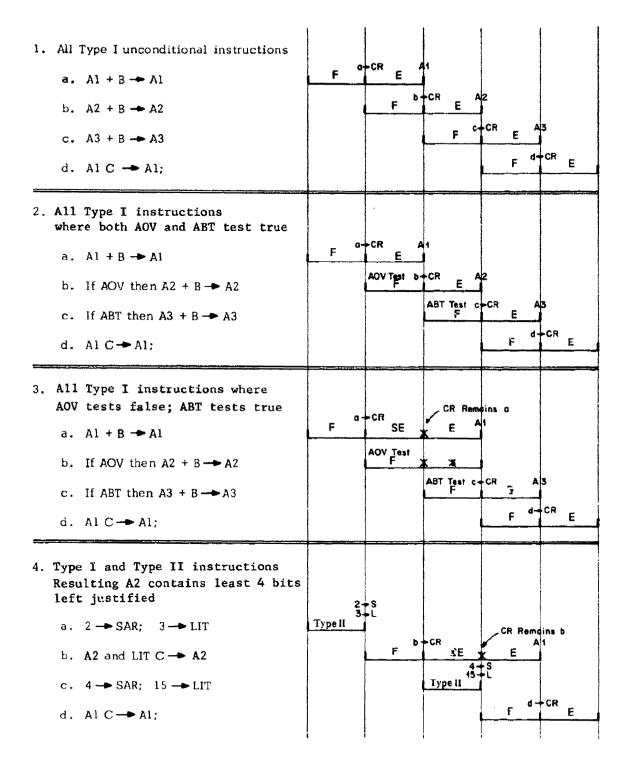

The fetch phase involves: MPM accessing, Nanomemory accessing, condition testing, selection of controls for the next instruction (successor) address computation, and, in parallel, loading the control register for the execution of the microinstruction. A fetch phase occurs for every Type I microinstruction and requires one clock time. Since it always overlaps the execution phase of a prior Type I microinstruction (Figure 37), the performance of each micro-instruction requires effectively one clock interval.