# B 9499-6 DISK DRIVE ELECTRONIC CONTROLLER

## TECHNICAL MANUAL VOLUME 1

OPERATION AND MAINTENANCE

### FIELD ENGINEERING

#### FIELD ENGINEERING PROPRIETARY DATA

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown, or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished for Burroughs Field Engineering Personnel, and is not furnished to customers except under special License Agreement.

THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished For Burroughs Field Engineering Personnel, and is not furnished to customers except under special Licence Agreement.

THIS DOCUMENT IS PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DE-TROIT, MICHIGAN 48232.

Burroughs believes that information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

## TABLE OF CONTENTS

| Section | Title                                       | Page       | Section | Title                               | <b>Page</b><br>3-3 |

|---------|---------------------------------------------|------------|---------|-------------------------------------|--------------------|

|         | INTRODUCTION                                | v          |         | IC Locations                        | 3-3                |

| 1       | FUNCTION AND OPERATION                      | 1-1        |         | Edge Connector Contact Numbering    | 3-5                |

| -       | GENERAL DESCRIPTION                         | 1-1        |         | Component Reference Charts          | 3-5                |

|         | Disk Drive Electronic Controller            | 1-1        |         | General Description                 | 3-5                |

|         | Subsystem                                   | 1-2        |         | REFERENCE CHARTS                    |                    |

|         | Error Detection                             | 1-2        | 4       | MAINTENANCE TECHNIQUES              | 4-1                |

|         | Local Operation                             | 1-2        | •       | LOCAL OPERATION                     | 4-1                |

|         | Operator Controls                           | 1-2        |         | GENERAL DESCRIPTION                 | 4-1                |

| 2       | INSTALLATION                                | 2-1        |         | Switch Function                     | 4-1                |

| 2       | SITE REQUIREMENTS                           | 2-1        |         | Entering an Address in the Initiate | 4-4                |

|         | Floor Space                                 | 2-1        |         | Words                               |                    |

|         | Power                                       | 2-1        |         | Initialize Operation                | 4-4                |

|         | Cable Length                                | 2-1        |         | Full Pack Initialize with Header    | 4-4                |

|         | Environment                                 | 2-1        |         | Single Track Initialize             | 4-4                |

|         | Unpacking Instructions                      | 2-1        |         | Read Operation                      | 4-6                |

|         | DDEC Installation                           | 2-1        |         | Write Operation                     | 4-6                |

|         | Preinstallation Checkout                    | 2-1        |         | Read Maintenance Operation          | 4-6                |

|         | AC Power Input                              | 2-1        |         | Relocate Operation                  | 4-6                |

|         | DDEC to D.P.C. Cabling                      | 2-2        |         | Spare Sector Verify Operation       | 4-7                |

|         | Subsystem Installation                      | 2-3        |         | Alternate Operations                | 4-7                |

|         | Cabinet Bolting Procedure                   | 2-3        |         | Read Extended Status Operation      | 4-7                |

|         | Cabling                                     | 2-3        |         | General Troubleshooting             | 4-8                |

|         | Power Distribution                          | 2-4        |         | Drive/DDEC Fault Isolation          | 4-8                |

|         | Grounding                                   | 2-4        |         | DDEC/DPC Fault Isolation            | 4-8                |

| * .     | AC-DC Ground Jumper                         | 2-4        |         | Voltage Margins                     | 4-8                |

|         | DDEC/DPD Cables                             | 2-4        |         | Clock Stopper Feature               | 4-10               |

|         | Configuration Switches                      | 2-4        |         | Trigger Gate Feature                | 4-10               |

|         | Drive Type Switch                           | 2-4        |         | Clear Diagnostic Feature            | 4-8                |

|         | Power Conversions                           | 2-4        |         | Displaying the Firecode             | 4-9                |

|         | 50 to 60 Hz Conversion                      | 2-5        |         | EXTENDED RESULT DESCRIPTOR          | 4-11               |

|         | 60 to 50 Hz Conversion                      | 2-3        |         | USAGE                               |                    |

|         | Single Phase Conversion                     | 2-8        |         | CM Error                            | 4-11               |

|         | Line to Neutral Conversion                  | 2-9        |         | Fan Fail                            | 4-11               |

|         | Voltage Tap Conversion                      | 2-9        |         | Drive Clock OK/                     | 4-11               |

|         | Checkout Procedure                          | 2-9        |         | Address Mark Missing                | 4-11               |

|         | Power on Checks                             | 2-9        |         | No Read Data Transitions            | 4-11               |

|         | DC Voltage Check                            | 2-9        |         | Index Mark Missing                  | 4-11               |

|         | Clock Frequency Check                       | 2-11       |         | Bad DM Response                     | 4-11               |

|         | Local Operations                            | 2-11       |         | Address Overflow                    | 4-11               |

|         | Online Operations                           | 2-11       |         | Maintenance Log (ELOG)              | 4-11               |

|         | •                                           |            |         | Result Descriptor                   | 4-11               |

| 3       | DOCUMENTATION AND                           | 3-1        |         | Extended Result                     | 4-11               |

|         | COMPONENTS                                  | 2.1        | _       |                                     | 5-1                |

|         | REFERENCE DOCUMENTS                         | 3-1        | -5      | ADJUSTMENTS                         | 5-1                |

|         | Test and Field Documents                    | 3-1<br>3-1 |         | Power Supply Adjustments            | 5-1                |

|         | General Description                         | 3-1        |         | +5 Volt Adjustment                  | 5-1                |

|         | Index<br>Black Discreme                     | 3-1        |         | 5 Volt Adjustment                   | 5-1                |

|         | Block Diagrams                              | 3-1        |         | Local Clock Check                   |                    |

|         | Flow Charts<br>Control Equations            | 3-1        |         | APPENDIX A                          | A-1                |

|         | Control Equations                           | 3-1        |         | SIGNAL GLOSSARY                     | A-1                |

|         | Schematics<br>Backplane Wirelist            | 3-1        |         |                                     | A-8                |

|         |                                             | 3-3        |         | USEFUL TEST AND TRIGGER             | A-0                |

|         | Component Location System<br>Backplane Pins | 3-3        |         | POINTS                              |                    |

|         | Printed Circuit Boards                      | 3-3        |         |                                     |                    |

|         | Timea Circuit Doalus                        | 5-5        |         |                                     |                    |

## LIST OF ILLUSTRATIONS

| Figure | Title                                   | Page | Figure | Title                                    | Page |

|--------|-----------------------------------------|------|--------|------------------------------------------|------|

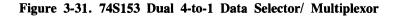

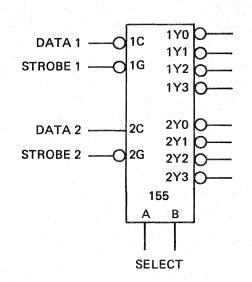

| 1-1    | Disk Drive Electronic Controller        | 1-1  | 3-32   | 74155 Dual 2-to-4 Line Decoder/          | 3-32 |

| 2-1    | Cabling Continuation Example            | 2-4  |        | Demultiplexor                            |      |

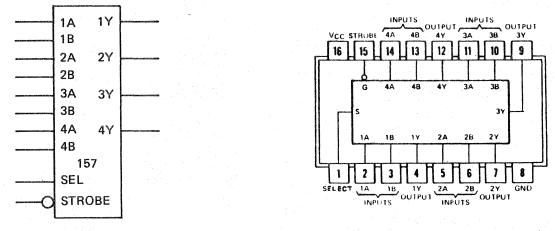

| 2-2    | Configuration Switch                    | 2-5  | 74157  | Quad 2-1 Line Data Selector              | 3-16 |

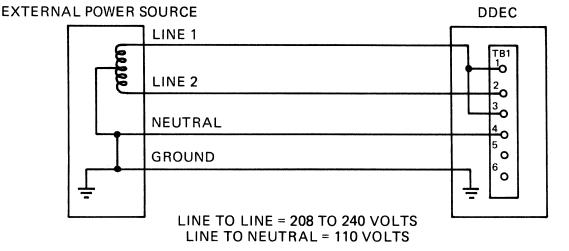

| 2-3    | Single Phase Input Power Connection     | 2-3  |        | Multiplexor                              |      |

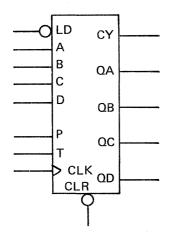

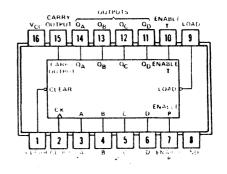

| 2-4    | Schematic Showing Line-Neutral          | 2-4  | 3-34   | 74161 Synchronous 4-Bit Binary Counter   | 3-17 |

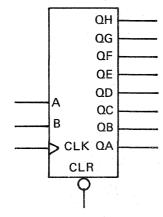

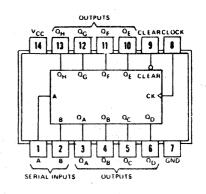

|        | Conversion                              |      | 3-35   | 74164 8-Bit Parallel-Out Shift Registers | 3-17 |

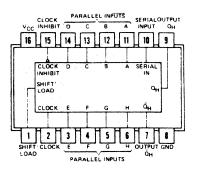

| 2-5    | TB3 Connections                         | 2-11 | 3-36   | 74165 Parallel-Load 8-Bit Shift Register | 3-18 |

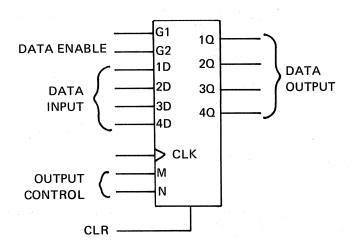

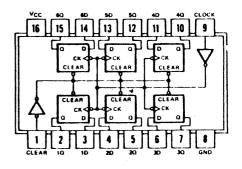

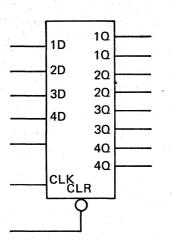

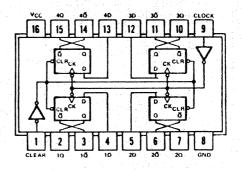

| 3-1    | Flow Chart Example                      | 3-1  | 3-37   | 74173 4-Bit D-Type Register with 3-      | 3-18 |

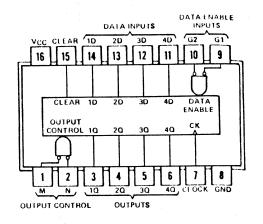

| 3-2    | Schematic Details                       | 3-2  |        | State Output                             |      |

| 3-3    | Negative or Function                    | 3-3  | 3-38   | 74174 Hex D-Type Flip-flops with Clear   | 3-19 |

| 3-4    | Positive NAND Function                  | 3-3  | 3-39   | 74175 Quad D-Type Flip-flops with        | 3-20 |

| 3-5    | Front View Backplane                    | 3-3  |        | Clear                                    |      |

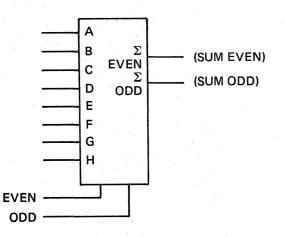

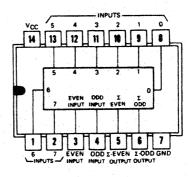

| 3-6    | Typical PCB                             | 3-6  | 3-40   | 74180 9-Bit Odd/Even Parity Generator/   | 3-20 |

| 3-7    | 7400 74S00 Quad 2-Input Positive        | 3-5  |        | Checker                                  |      |

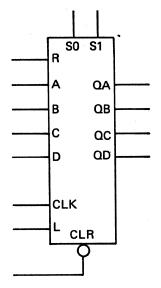

|        | NAAND Gate                              |      | 3-41   | 4-Bit Bidirectional Universal Shift      | 3-21 |

| 3-8    | 7402 74S02 Quad 2-Input Positive NOR    | 3-6  |        | Registers                                |      |

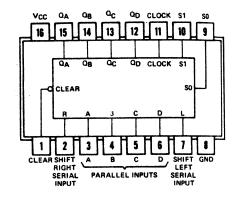

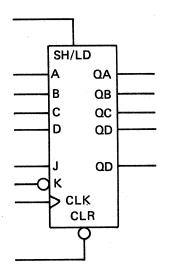

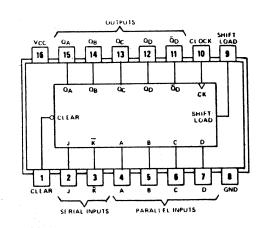

|        | Gate                                    |      | 3-43   | 74195 74S195 4-Bit Parallel-Access Shift | 3-21 |

| 3-9    | 7404 74S04 74H04 Hex Inverter           | 3-6  |        | Registers                                |      |

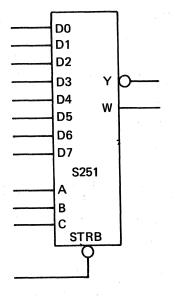

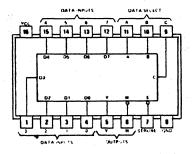

| 3-10   | 7408 74S08 Quad 2-Input and Gate        | 3-6  | 3-43   | 74S251 8-1 Data Selector Multiplexor     | 3-22 |

| 3-11   | 7410 74S10 Triple 3-Input Positive      | 3-7  |        | with 3-State Output                      |      |

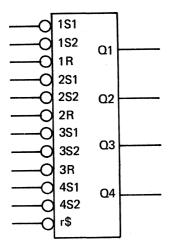

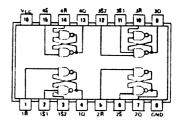

|        | NAND Gate                               |      | 3-44   | 74279 Quad RS Latches                    | 3-23 |

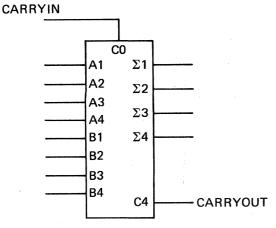

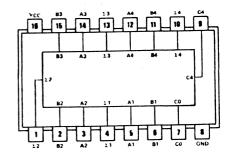

| 3-12   | 74S11 Triple 3-Input Positive and Gates |      | 3-45   | 74283 4-Bit Binary Adder with Fast       | 3-23 |

|        | 3-7                                     |      |        | Carry                                    |      |

| 3-13   | 7420, 74S20 Dual 4-Input Positive       | 3-7  | 3-46   | 75101 Dual Line Receivers                | 3-24 |

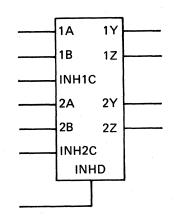

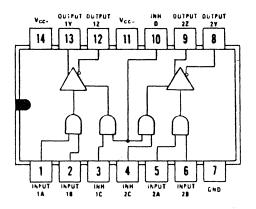

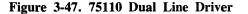

|        | NAND Gates                              |      | 3-47   | 75110 Dual Line Driver                   | 3-25 |

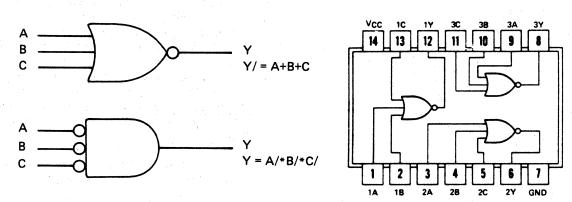

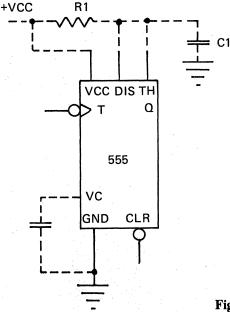

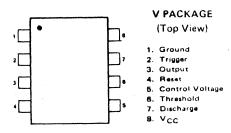

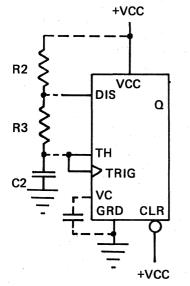

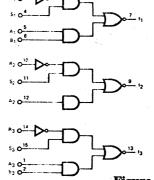

| 3-14   | 7427 Triple 3-input Positive NOR gates  | 3-8  | 3-48   | 555 Timer                                | 3-25 |

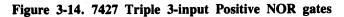

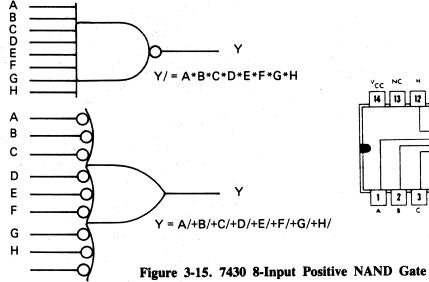

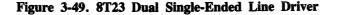

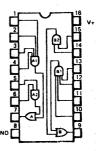

| 3-15   | 7430 8-Input Positive NAND Gate         | 3-8  | 3-49   | 8T23 Dual Single-Ended Line Driver       | 3-26 |

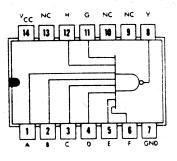

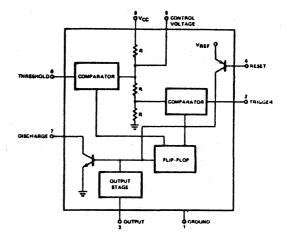

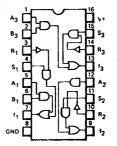

| 3-16   | 7432 Quad 2-Input Positive or Gates     | 3-8  | 3-50   | 8T24 Triple Line Recever                 | 3-26 |

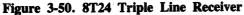

| 3-17   | 7437 Quad 2-Input NAND Buffers          | 3-9  | 3-51   | 8T37 DM8837 Hex Receiver with            | 3-27 |

| 3-18   | 7440 74S40 Dual 4-Input NAND Buffers    | 3-9  |        | Hysteresis                               |      |

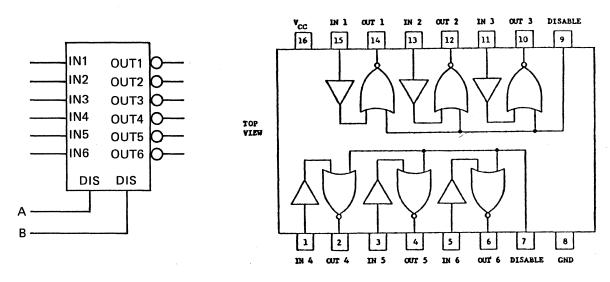

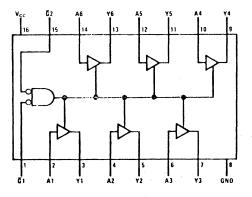

| 3-19   | 7442 4-10 Line Decoder                  | 3-10 | 3-52   | DM8095 Tri-state Hex Buffers             | 3-27 |

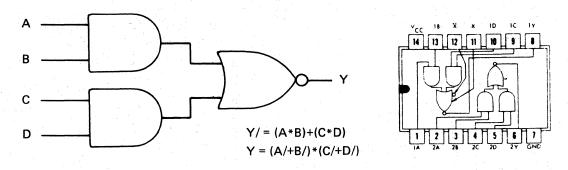

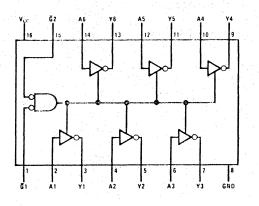

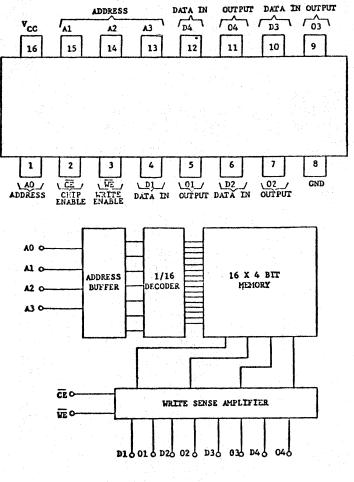

| 3-20   | 74H51 Dual 2-Wide 2-Input and OR        | 3-10 | 3-53   | DM 8096 Tri-state Hex Inverter           | 3-28 |

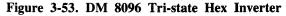

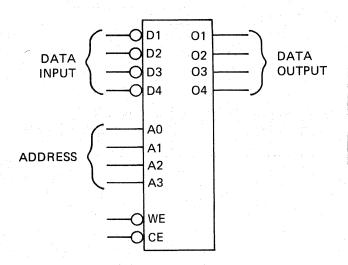

|        | Invert Gates                            |      | 3-54   | MM6561 Random Access Memory 16 x         | 3-28 |

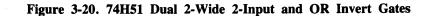

| 3-21   | 74S64 4-2-3-2 Input and-OR-Invert Gates | 3-10 |        | 4 Tri-state Output                       |      |

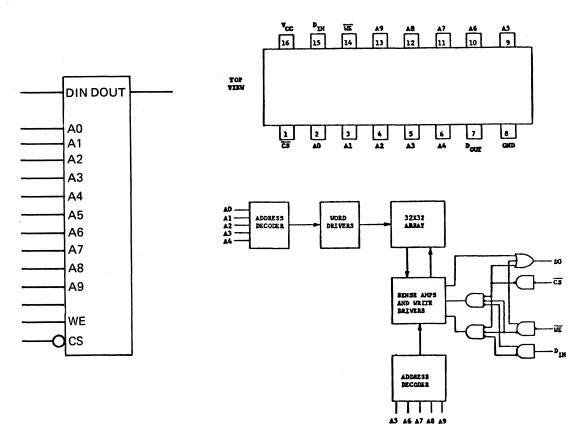

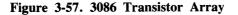

| 3-22   | 7474 74S74 Dual D-Type Flipflop         | 3-11 | 3-56   | 93415 1024 x 1 Random Access Memory      | 3-29 |

| 3-23   | 7486 74S86 Quad 2-Input Exclusive OR    | 3-11 | 3-57   | 723 Voltage Regulator                    | 3-29 |

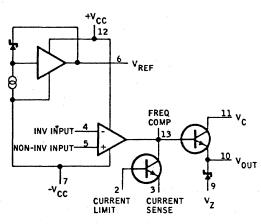

|        | Gates                                   |      | 3-57   | 3086 Transistor Array                    | 3-30 |

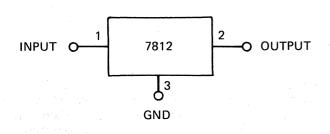

| 3-24   | 74S109 Dual J K flipflop                | 3-11 | 3-58   | 7812 Voltage Regulator                   | 3-30 |

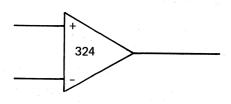

| 3-25   | 74123 Dual Retriggerable Monostable     | 3-12 | 3-59   | 324 Operational Amplifier                | 3-30 |

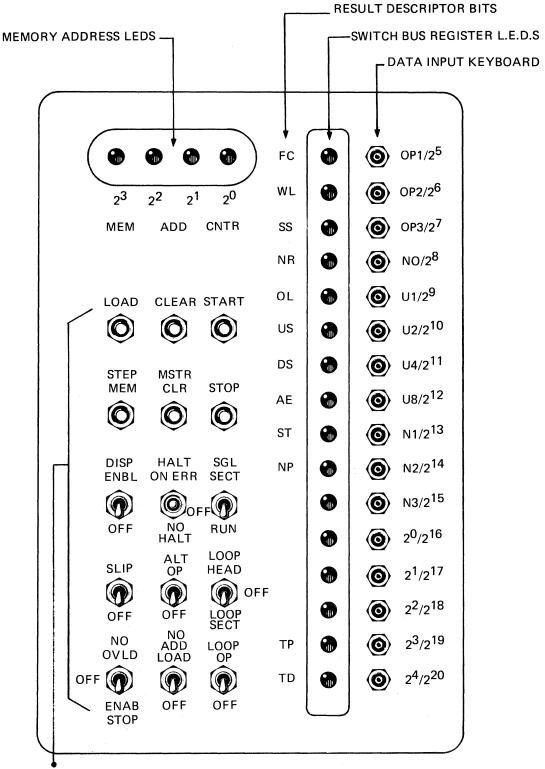

|        | Multivibrator                           |      | 4-1    | Maintenance Panel                        | 4-3  |

| 3-26   | 74S124 Dual Voltage-Controlled          | 3-12 | 4-2    | Voltage Adjustments                      | 4-9  |

|        | Oscillator                              |      | 4-3    | Trigger Gate                             | 4-9  |

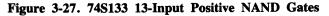

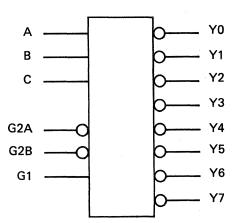

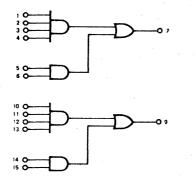

| 3-27   | 74S133 13-Input Positive NAND Gates     | 3-13 | 4-4    | Display of Firecode                      | 4-10 |

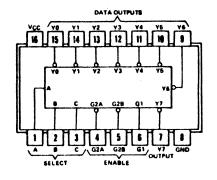

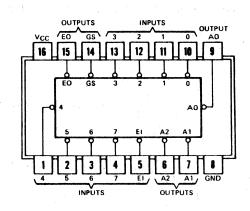

| 3-28   | 74S138 Decoder Demultiplexor            | 3-13 | 4-5    | Disk Errors in the E-log (two formats    | 4-10 |

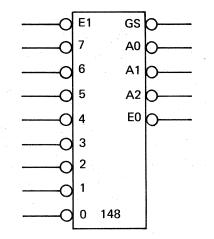

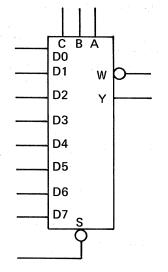

| 3-29   | 74148 8 to 3 Line Priority Encoder      | 3-14 |        | are shown)                               | 7-12 |

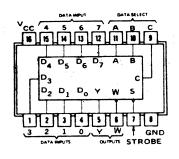

| 3-30   | 74151 Data Selector/Multiplexor         | 3-14 | 5-1    | Power Supply Adjustments                 | 5-1  |

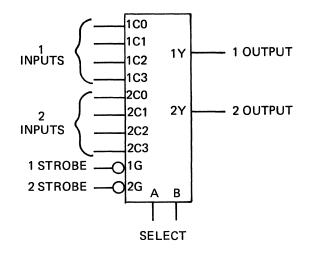

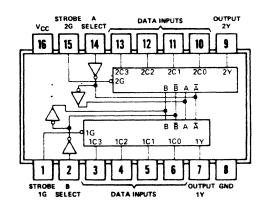

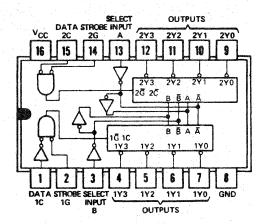

| 3-31   | 74S153 Dual 4-to-1 Data Selector        | 3-15 | 5-1    | rower suppry Aujustitients               | 5-1  |

|        | Multiplexor                             |      |        |                                          |      |

|        | · · ·                                   |      |        |                                          |      |

## LIST OF TABLES

Title

#### Table

| 2-1 | Subsystem Power Requirements         | 2-2  |

|-----|--------------------------------------|------|

| 3-1 | T & F Sections                       | 3-1  |

| 3-2 | TTL Family Types                     | 3-5  |

| 4-1 | Maintenance Memory Word Usage        | 4-1  |

| 4-2 | Initiate Words                       | 4-1  |

| 4-3 | OPCODE Decode                        | 4-2  |

| 4-4 | R.D. and E.R.D. Decodes              | 4-2  |

| 4-5 | Decimal-to-Hexadecimal Conversion    | 4-5  |

| 4-6 | Normal Position of Maintenance Panel |      |

|     | Toggle Switches                      | 4-5  |

| 4-7 | Firecode Examples                    | 4-11 |

| 4-9 | Extended Result Descriptor           | 4-13 |

| 5-1 | Summary of Adjustments               |      |

Page

### INTRODUCTION

This Field Engineering Technical Manual is prepared in a revised format as follows:

1) Volume 1, Operation and Maintenance

2) Volume 2, Illustrated Parts

3) Volume 3, Theory of Operation

The division of the manual into volumes provides a more complete concentration of the subject matter with respect to machine maintenance and theory.

Correspondence regarding this manual should be directed to:

Manager, Hardware Support - TIO Winnipeg

Burroughs Business Machines Limited

> 51 Burmac Road PO Box 861 Winnipeg, Manitoba Canada, R3C - 2P7

V

## SECTION 1 FUNCTION AND OPERATION

#### **GENERAL DESCRIPTION**

#### **Disk Drive Electronic Controller**

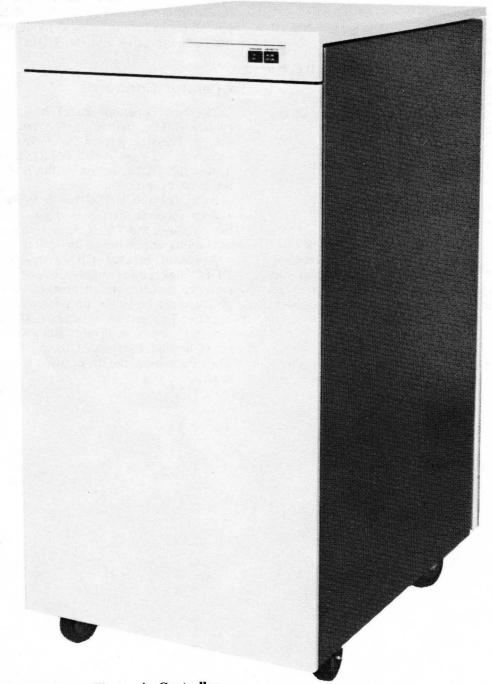

The B 9499-6 Disk Drive Electronic Controller

(DDEC) interfaces one B 1700 or B 1800 Series computer to a maximum of 8 disk drives. The disk drives may be any mix of B 9484-2, -5 or B 9494-4 drives (205, 206, or 207).

Figure 1-1. Disk Drive Electronic Controller

#### Subsystem

The DDEC receives commands from the Disk Pack Control (D.P.C.) in the central system, and interfaces with the required drive in order to complete the command. A typical command from the D.P.C. might be:

Read on unit 5 starting at sector 472824. The following is the function of DDEC:

1) Select the required unit.

- 2) Decode the sector address into cylinder, Head and sector address for the type of drive.

- 3) Issue a seek command if necessary.

- 4) Read the addresses on the track until the required address is read.

- 5) Read the data into the DDEC, convert it from serial to parallel and transfer to the D.P.C. 16 bits at a time.

- 6) At the conclusion of the operation, report a result descriptor to the D.P.C. informing it of any errors detected during the operation.

#### NOTE

This is an over-simplified explanation intended to illustrate the operation in general terms. Actual operating details may be obtained in Volume 3, Theory of Operation.

In addition to reading, the DDEC performs other operations such as write, initialize, verify, relocate, read maintenance, and read Extended Result Descriptor. The intention of this volume is not to explain each of these operations. Volume 3 explains each in detail.

#### **Error** Detection

Error protection code (firecode) for every sector on disk enables the DDEC to detect read errors and to inform the system. The system retries a read operation if a read error occurs. Software attempts correction of a read error.

The DDEC can do error correction on a B 9494-4 (207) disk drive. It does error correction on a single sector basis when asked by the processor.

#### Local Operation

On line operations are simulated by a field engineer using the DDEC maintenance panel. Maintenance logic throughout the DDEC allows all operations to be run in local mode for troubleshooting both the drive and the DDEC.

#### **Operator Controls**

The front operator panel has two push button switches. The switch on the left is the POWER switch. Pressing it puts the DDEC on or off. The switch on the right is the REMOTE switch. Pressing it puts the DDEC online to the processor or offline for local operation.

Note that the DDEC has a Power Reset Timer. For 25 seconds after pressing the power switch to the on state, the DDEC is not able to perform any operations either online or offline.

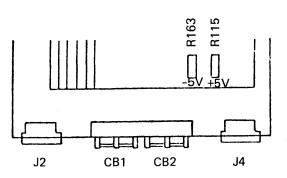

A circuit breaker CB3 provides power to the DDEC logic power supply. Remove the DDEC front panel to find the circuit breaker on the Power Supply. It must be in the up position for the DDEC to operate. Two circuit breakers CB1 and CB2 provide power to the disk drives. Remove the DDEC rear panel to find CB1 and CB2 on the power supply. They must be in the up position for the drives to operate.

## SECTION 2 INSTALLATION

### SITE REQUIREMENTS

#### Floor Space

|                                         | Inches | СМ  |

|-----------------------------------------|--------|-----|

| Width                                   | 22     | 54  |

| Depth (including maintenance clearance) | 102    | 257 |

| Height                                  | 44     | 112 |

Normally the DDEC is bolted to one disk drive or between two drives.

#### Power

Input power is wired directly by an electrician. The wiring must enter the DDEC through the hole in the frame base at the right side. The DDEC can be powered by 60 Hz or 50 Hz power, either phase to phase or phase to neutral. Input voltage must be 208 to 240 volts AC. Many alternatives are given in this section under the title Power Conversions. Note that if the DDEC is wired to a single phase either line to line or line to neutral, a 1 x 4 Configuration is the maximum.

The DDEC provides power to the disk drives. Since the drives can be a mixture of B 9484-5 (206) and B 9494 - 4 (207), total power requirements for the subsystem can vary. Table 2-1 gives combinations of frequency and voltage and the drive and DDEC power requirements for each. Use Table 2-1 to calculate the total subsystem power requirement.

#### Cable Length

Four cable kits are available for the disk subsystem using the 206/DDEC

| Cable Kits<br>Part Number | 1 x 2<br>2781 0050 | 1 x 4<br>2781 0068 | 1 x 6<br>2783 3680 | 1 x 8<br>2783 3698 |

|---------------------------|--------------------|--------------------|--------------------|--------------------|

| I/O Cable 12 Ft.          | 1                  |                    |                    |                    |

| I/O Cable 14 Ft.          |                    | 1                  | 2                  | 2                  |

| A/C GND 2 Ft.             |                    | 1                  | . 1                | 2                  |

| A/C GND 3 Ft.             | 1 .                | 1                  | 2                  | 2                  |

| DC Logic                  |                    |                    |                    |                    |

| GND 3 Ft.                 | 2                  | 2                  | 4                  | 4                  |

| DC Logic                  |                    |                    |                    |                    |

| GND 4.5 Ft                |                    | 2                  | 2                  | 4                  |

#### Environment

Operating Temperature - 60 to 100 degrees F. - 16 to 38 degrees C.

Relative humidity 10 to 90 percent.

Shipping and storage

Temperature - 50 to 160 degrees F.

- 45 to 71 degrees C.

Relative humidity up to 95 percent

#### **Unpacking Instructions**

The DDEC is shipped from the factory in a crate. The crate is a pallet, cushion supports for the DDEC, tri-wall card board top and four sided box. The DDEC is in a polyethylene bag. Styrofoam edge guards are put between the DDEC and the crate. The pallet, sides and top are held together with two straps.

- To remove the DDEC from the packing crate:

- 1) Remove the two straps holding all together.

- 2) Remove the cardboard top.

- 3) Remove the edge guards from inside the crate.

- 4) Lift the cardboard box from the DDEC

- 5) Remove the polyethylene bag from the D DEC.

- 6) Lift the DDEC from the pallet. At least two people are required to lift the DDEC safely.

#### **DDEC** Installation

After uncrating the DDEC, place it in approximately the position where it is finally to be installed. Before any drives are placed beside it, some check-out and cabling must be done.

#### **Preinstallation Checkout**

The following checks must be made with no power applied to the DDEC

- 1) Remove the front, rear, and side panels from the DDEC

- 2) At the rear of the DDEC remove the tape which holds the circuit cards in the card cage.

- 3) Press each circuit card to be sure it is fully inserted into the backplane.

- 4) On the power supply on the base of the cabinet, remove the six bolts which hold the power supply cover to the sides.

- 5) Inspect the power supply for shipping damage including loose wires, scraped wires or loose components.

- 6) On the outside of the power supply, at the right rear side locate the AC/DC ground shorting jumper wire. Remove the nut securing one end of this wire and pull that end from it s stud.

- 7) Using a VOM or DVM measure the resistance between the frame and the DC ground stud on the backplane. The DC ground stud is on the right side of the backplane when facing the

wired side. The resistance should be greater than one megohm.

- 8) Replace the shorting jumper wire removed in step 6.

- 9) Remove the AC cover on the right side of the power supply.

- 10) Switch CB3 to the down (off) position. CB3 is located on the front cover of the power supply.

- 11) Using a VOM or DVM measure the resistance between TB1 terminals 1, 2, 3 and 4. All combinations must measure greater than one megohm.

- 12) Switch CB3 to the up (on) position. The resistance between TB1-1 and TB1-2 must be low but is greater than 0.6 ohm. Switch CB3 to the down (off) position.

- 13) Replace the power supply top cover.

| r                                     | r          | ·                                       | · · · · · · · · · · · · · · · · · · ·             | r                                      | r                                            |                                              |                                              |

|---------------------------------------|------------|-----------------------------------------|---------------------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| UNIT                                  | FREQ.      | VOLTAGE                                 | START<br>CURRENT A                                | WORST<br>CASE A                        | VA                                           | BTU/HR                                       | KCAL/HR                                      |

| B9284-2/5<br>205/206<br>DUAL<br>DRIVE | 60HZ<br>50 | 208v<br>240<br>200<br>220<br>230<br>240 | 21.0<br>24.2<br>22.6<br>25.0<br>23.2<br>27.2      | 7.0<br>8.0<br>7.5<br>8.2<br>7.7<br>9.0 | 1455<br>1920<br>1500<br>1804<br>1770<br>2160 | 3975<br>5240<br>4090<br>4930<br>4840<br>5900 | 1000<br>1340<br>1030<br>1242<br>1218<br>1488 |

| B9494-2<br>(SINGLE<br>SPINDLE         | 60         | 208<br>240                              |                                                   |                                        |                                              |                                              |                                              |

| 207<br>DRIVE)                         | 50         | 200<br>220<br>230                       |                                                   |                                        |                                              |                                              |                                              |

| B9494-4                               | 60         | 240<br>208                              |                                                   | 8.5                                    | 1768                                         | 4820                                         | 1214                                         |

| (DUAL<br>SPINDLE<br>207               |            | 240                                     |                                                   | 7.0                                    | 1680                                         | 4590                                         | 1158                                         |

| DRIVE)                                | 50         | 200<br>220<br>230<br>240                | a<br>Si ta sa sa sa sa sa sa sa sa sa sa<br>Si ga | 8.0<br>7.8<br>7.5<br>6.6               | 1600<br>1730<br>1725<br>1585                 | 4360<br>4720<br>4710<br>4320                 | 1100<br>1190<br>1188<br>1090                 |

| B9499-6<br>206/7                      | 60         | 208                                     | N/A                                               | 2.1                                    | 436                                          | 1190                                         | 300                                          |

| DDEC                                  | 50         | 240<br>200<br>220<br>230                | N/A<br>N/A<br>N/A<br>N/A                          | 1.9<br>2.4<br>2.2<br>2.2               | 456<br>480<br>484<br>506                     | 1245<br>1310<br>1321<br>1380                 | 314<br>330<br>333<br>348                     |

|                                       |            | 230<br>240                              | N/A<br>N/A                                        | 2.2<br>2.1                             | 506<br>504                                   | 1380                                         | 348<br>350                                   |

| Table | 2-1. | Subsystem | Power | Requirements |

|-------|------|-----------|-------|--------------|

|-------|------|-----------|-------|--------------|

#### AC Power Input

Power input cables must be installed by an electrician. The field engineer must determine the specifications of the available power. If the available power is not the same as the required power as stamped on the machine label, some change must be made to the DDEC. See the changes below the heading *Power Conversions* in this section. The following procedure is to be used to connect the AC input lines to the DDEC

- 1) Remove the AC cover from the right side of the power supply.

- 2) The hole-piece through which the input cable passes to TB1 is designed for conduit pipe to be clamped. The conduit must pass up through the hole in the DDEC base, then turn 90 degrees to be clamped at the hole-piece beside TB1

- 3) If the normal 3 phase, neutral, and ground input wires are provided, connect.

| Phase A | to | TB1 - 1                                |

|---------|----|----------------------------------------|

| Phase B | to | TB1 - 2                                |

| Phase C | to | TB1 - 3                                |

| Neutral | to | TB1 - 4                                |

| Ground  | to | E7 (stud under and to the left of TB1) |

4) Replace the AC cover.

Verify that the transformer tap chosen on the DDEC power supply at TB3 is rated the same as the input voltage. The method for making changes is under the heading *Voltage Tap Conversion* in this section.

#### DDEC to D.P.C. Cabling

The interface between the DDEC and the D.P.C. in the processor is a 25-wire coaxial cable. Before positioning drives beside the DDEC install the processor interface cable. Pass the cable up through the hole in the base of the DDEC cabinet and bring it to the rear of the card cage. Attach it to circuit card 16 (third card from left in the lower row of cards). The processor end must connect to the D.P.C. at the I/O connector panel.

#### Subsystem Installation

Before proceeding with these installation steps be sure that all AC input wiring to the DDEC has been done, that the necessary conversions have been made to the DDEC power wiring, and that the processor interface cable has been installed in the DDEC

#### Cabinet Bolting Procedure

The disk drives are shipped each with a set of brackets to bolt it to the drive or DDEC next to it. Install the bolting hardware using the procedure which follows, position the drives beside the DDEC and level all cabinets, and then complete the wiring for the subsystem.

- 1) Remove all panels from all cabinets.

- 2) Sort front and rear bolting brackets. In a set there are two long brackets painted black for the cabinet front members. There are two small brackets which are cadmium plated. They are for the cabinet rear members.

- 3) Move the cabinets near to their final positions but leave one or two feet between them.

- 4) Mount left-hand and right hand front brackets to adjacent vertical frame members at the front of the cabinets. Each is secured with four 8-32 screws with lock washers and flat washers. Do not tighten the mounting hardware until alignment has been done.

- 5) Mount left-hand and right-hand rear brackets to adjacent vertical frame members at the rear of the cabinets. Each is secured with two 8-32 screws with lock washers and flat washers. Do not tighten the mounting hardware until alignment has been done.

- 6) Move the first drive into it's final position beside the DDEC

- 7) On the cabinets just aligned, move the front bracket which has slotted mating holes so that it is flush with the front of the frame and tighten it's mounting screws. Move the adjacent bracket with tapped holes so that it is behind the bracket on the other cabinet. Tighten the mounting hardware.

#### NOTE

Step 7 requires sliding the cabinets apart and back together several times to place the brackets correctly. Remember that the bracket with slotted holes must finally overlap the bracket with tapped holes when the cabinets are brought together. This permits the screws which hold the brackets together to be installed and tightened from the outside of the cabinet.

- 8) Repeat step 7 for the rear brackets.

- 9) Follow the above procedure for all cabinets. Finally move all cabinets to their positions with front and rear brackets overlapping correctly.

- 10) Level the cabinets and align their top panels by lowering and adjusting the four levelling jacks in each cabinet.

- 11) Install two 8-32 screws, lock-washers and flat washers in each set of front brackets and one screw and washer in each set of rear brackets.

#### Cabling

For B 9495-5 (206) disk drives a cable trough is formed along the rear of the cabinets. All interconnecting cables are laid in the J member brackets behind the rear frame uprights on each drive. This permits the rear covers to be installed on the drives and DDEC with no cable interference.

For B 9494-4 (207) disk drives a cable trough is formed along the top of the cabinets. Remove the top covers of the drives and lay interconnecting cables in the trough. To reach the DDEC the cables pass down the cable trough on the side of the drive closest to the DDEC More cabling information is found in the installation section of the drive technical manual.

#### Power Distribution

The disk drives in the subsystem are powered from the four receptacles at the rear of the DDEC power supply. Before proceeding, place all circuit breakers in the off position.

Lay the drive power cables in the cable trough and insert the plug for each in one receptacle at the rear of the DDEC Store excess cable at the drive.

#### Grounding

Ground cables come as part of the cable kits. They are green. The heavy gauge cables are AC ground cables. The lighter gauge cables are DC ground cables.

The installation section of the drive technical manuals has information about ground interconnection which is useful.

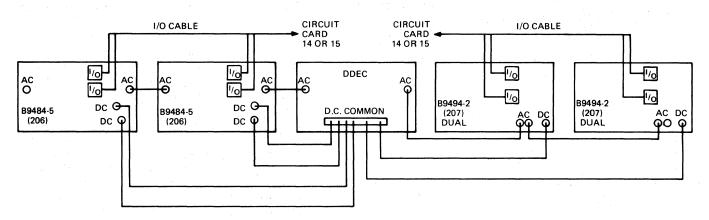

Figure 2-1. Cabling Configuration Example

Figure 2-1 gives an example of a 1 x 8 mixed subsystem with four B 9494-4 (207) drives and four B 9484-5 (206) drives. The AC and DC ground cables are shown in figure 2-1.

The following rules apply to ground cables in the subsystem:

- 1) Link all the machines in a *daisy chain* between AC ground connections.

- 2) Each DC ground in the drives must be joined with a separate wire to the DC common terminal block at the rear of the DDEC power supply. The common ground point where AC ground and DC ground are joined is the DDEC The B 9494-4 (207) drive has only one DC ground for both drives since the DC power supply is common. The B 9484-5 (206) has a separate DC ground for each spindle.

- 3) Route all ground wires in the cable trough.

#### AC - DC Ground Jumper

The DDEC provides a common connection for AC and DC ground. The DDEC is shipped with AC ground and DC ground joined by a jumper wire.

If isolation is required between AC ground and DC ground remove the jumper wire. It is located on the right side of the power supply, at the rear of the DDEC. It joins the two terminals labelled E2 (DC ground) and E6 (AC ground).

#### **DDEC/DPD** Cables

The drive interface coaxial cable is provided in the cable kit. One cable is required for four spindles

(two drives). For units 0, 1, 2 and 3 connect one interface cable to circuit card 14. For units 4, 5, 6 and 7 connect one interface cable to circuit card 15.

Lay the drive interface cables along the bases at the rear of the 206 drives and along the cable troughs on top of the 207 drives (top cover removed). Connect the interface plugs to the drive receptacles. The plugs are marked 1 to 4 corresponding to spindle address 0 to 3 and 4 to 7.

See figure 2-1 for an example of cabling. Also see the installation section of the drive technical manuals for more cabling information.

#### **Configuration Switches**

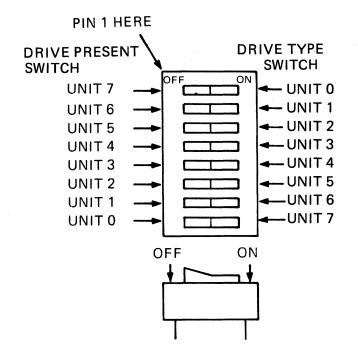

Document 07.03.01 in the T and F Document package shows two sets of switches which designate to the DDEC the subsystem configuration.

#### **Drive Present Switch**

This is located on circuit card 04. It is a set of eight switches in a dual-in-line package at location B4 on the card. Figure 2-2 shows which switch corresponds to each drive unit. The on position designates that unit present. Set these switches to indicate the same drive units present as the jumper chip in the DPC indicates.

#### Drive Type Switch

This is located on circuit card 03 at location D1. In the on position, the switch designates the unit a B 9494-4 (207) type drive. In the off position, the switch designates the unit a B 9484-2/5 (205/206) type

**Figure 2-2 Configuration Switch**

drive. These switches must be correct for the DDEC to communicate with the drive. The unit type jumpers in the DPC must correspond also. See the jumper chip instructions for the disk pack control in the processor.

#### **Power Conversions**

The DDEC is shipped from the factory wired for one of the following configurations:

- 1) 60 Hz, 3 phase, line to line voltage of 208 to 240 volts.

- 2) 50 Hz 3 phase, line to line voltage of 208 to 240 volts.

The field engineer must check which transformer primary tap is used at TB3 on the power supply. If the tap used is different from the input voltage available, change the connection at TB3. See Voltage Tap Conversion in this section.

The DDEC label is attached to the base of the machine, behind the front panel. It gives the configuration for which the DDEC is wired. If there is any difference between that configuation and the power available, one or more of the following deviations must be made.

- 1) 50 to 60 Hz Conversion

- 2) 60 to 50 Hz Conversion

- 3) Single Phase Conversion

- 4) Phase to Neutral Conversion

- 5) Voltage Tap Conversion

#### 50 to 60 Hz Conversion

1) In 50 to 60 Hz conversion kit check that the transformer supplied bears part number 2783 6683.

- 2) Ensure that all AC power is removed from DDEC by first disconnecting any known power source.

- 3) Remove all side panels by loosening the two clamps at the bottom of the frame below each panel with a 7/16 inch open end wrench, then raising each panel and pulling it away from the frame at the top end.

- 4) Remove the AC cover on the right side of the power supply with a flat screwdriver applied to its four screws. With an AC voltmeter measure between all terminals of TB1. There should be no voltage indicated.

- 5) Remove the six screws securing the top cover of the power supply using a flat screwdriver. Slide the top cover forward and out of the machine.

- 6) Remove the four screws securing the front cover of the power supply. Allow the front cover to rest loosely away from the power supply.

- 7) Unplug J7 and P7 and remove P7 from the front panel with a flat screwdriver used to compress the springs holding it to the sheet metal.

- 8) On the printed circuit board on the top of the power supply module, remove the screw holding the white wire to the board in the front, left corner, marked TB4, 5V out (left terminal).

- 9) In the same location as step 8, remove the screw holding two black wires to the board, marked +5VRTN (right terminal).

- 11) At TB3 remove all wires from the terminal screws.

- 12) Remove the two screws securing the front of the power supply module to the base of the DDEC using a long flat screwdriver.

- 13) Loosen but do not remove the corresponding two screws securing the rear of the power supply module.

- 14) Grasping the power supply module by its built in handles on the front, pull it slightly forward then tip it up and lift it from the power supply and place it on a table.

- 15) Unplug the three secondary output wires of the transformer from the top of the printed circuit board. These wires are brown, brown and purple and are plugged onto terminals marked F, B, and A. (it does not matter which brown wire goes to F or which goes to B).

- 16) Using a flat screwdriver remove the three screws holding the two red wires and one blue wire to terminals marked C, E, and D on the top of the circuit board. (it does not matter which red wire goes to C, or which goes to E).

- 17) Remove the two large screws and four washers holding C103 and the two screws and four washers holding C102 (both are marked) to the printed circuit board on top of the power supply.

- 18) Using a Phillips screwdriver remove the seven screws around the edge of the circuit board then raise the board from the metal frame and set it on one side. At this time note the part number stamped on the 50 Hz transformer. It should be 2783 7244.

- 19) At the inside of TB3 described in step 10, unplug the blue wire from the terminal marked com (far right). Unplug the black wire from the terminal marked 200V (second from right). Unplug the orange wrie from the terminal marked 220V (third from right). Unplug the yellow wire from the terminal marked 230V (fourth from right). Unplug the red wire from the terminal marked 240V (fifth from right).

- 20) At the rear base of the power supply module, remove the rubber cap covering the end of C101) Unplug the two white wires from the terminals of C101, (it does not matter which white wire goes to which terminal).

- 21) Unbolt the transformwer from the base by removing the four nuts using a 7/16 inch nut driver. Lift the transformer from the power supply.

- 22) From the 50Hz 60Hz conversion kit take the transformer and ensure the part number stamped on it is 2783 6683. If correct, bolt it to the base of the power supply module using the four nuts removed in step 21) Place the transformer so that the side with wires is on the inside of the power supply.

- 23) Remove the label above TB3 indicating a 50Hz power supply and replace with the 60Hz from the kit with new voltage assignments for the terminals.

- 24) Remove the label showing the part number of the power supply module as 2782 3789 and replace it with the new lable from the conversion kit with part number 2783 7872.

- 25) Plug the blue wire from the transformer which has a plug end into the rear of TB3 at the terminal marked common (far right). Plug the black wire onto TB3 terminal marked 208V (second from right). Plug the orange wire onto TB3 terminal marked 240V (third from right).

- 26) Plug the two white wires on to each terminal of C101 at the left rear base of the power supply. Replace the rubber cap on C101) (It does not matter which white wire goes to which terminal.

- 27) Replace the circuit board on the metal frame, taking care to hold the remaining transformer wires so that they curl around the front of the board to its top without pinching them be-

tween any components. Secure the board to the metal with the seven Phillips screws removed in step 18.

- 28) Plug one brown wire from the transformer onto the circuit board terminal marked F at the center front of the board. Plug the other brown wire onto the board terminal marked B. It does not matter which brown wire goes to terminal F and which goes to terminal B or which red wire goes to terminal C and which goes to terminal E. Plug the purple wire onto the board terminal marked A. Using the screws removed in step 16, fasten one red wire from the transformer to the board terminal marked C, the other red wire to the board terminal marked E, and the blue wire to the board terminal marked D.

- 29) Secure the two capacitors C102 and C103 to the circuit board using the two screws for each removed in step 17.

- 30) Reinstall the power supply module in the base of the DDEC by setting it forward of its final position, and then sliding it to the rear to engage the two screws securing it to the base at the rear. Refit two screws at front and tighten all four screws.

- 31) Connect the white wire to the TB4 terminal marked 5 Volt (left terminal) in the left front corner of the circuit board using the screw removed in step 8.

- 32) Connect the two black wires to TB4 terminal marked 5VRTN (right terminal) using the screws removed in step 9.

- 34) At TB3 in the lower front right corner of the power supply module, connect one white AC input wire, along with the white wire from each of the two sheathed fan harness cables all to TB3 terminal marked com (far right terminal). The other white AC input wire along with the black wire from each of the sheathed fan harness cables should be connected to the appropriate terminal of TB3 depending on the voltage source. Determine from the electrician what voltage the source is before connecting these wires. The second from right terminal is for 208V input. The third from right terminal is for 240V input. It does not matter which white AC input wire goes to com, and which goes to the voltage input terminal.

- 35) Mark in ink the power conversion label 2783 7608 with the correct voltage, frequency and phase information, and attach this adjacent to the machine nameplate label at the rear.

- 36) With circuit breaker CB3 on front cover power supply turned off, apply AC power source

to the machine. With an AC voltmeter measure the voltage between TB3-1 and the other terminal of TB3 connected in step 34. Be sure that the terminals used on TB3 in step 34 correspond to the voltage measured here. Change the terminal used in step 34 if necessary, being sure AC source is disconnected before making changes.

- 37) Using the four screws removed in step 6, fasten the front cover power supply to the rear cover power supply.

- 38) Using the six screws removed in step 5, fasten the top cover power supply to the rear cover power supply.

- 39) Refit the AC cover over TB1 and secure with the four screws removed in step 4.

- 40) Turn CB3 and check that all fans operate.

- 41) Refit all side panels to the DDEC by engaging them in the two holes at the top, then tightening the two clamps in the frame below each panel.

60 to 50 Hz Conversion

- 1) In 60 to 50 Hz conversion kit check that the transformer supplied bears part number 2783 7244.

- 2) Ensure that all AC power is removed from DDEC by first disconnecting any known power source.

- 3) Remove all side panels by loosening the two clamps at the bottom of the frame below each panel with a 7/16 inch open end wrench, then raising each panel and pulling it away from the frame at the top end.

- 4) Remove the AC cover on the right side of the power supply with a flat screwdriver applied to its four screws. With an AC voltmeter measure between all terminals of TB1) There should be no voltage indicated.

- 5) Remove the six screws securing the top cover of the power supply using a flat screwdriver. Slide the top cover forward and out the machine.

- 6) Remove the four screws securing the front cover of the power supply. Allow the front cover to rest loosely away from the power supply.

- 7) Unplug J7 from P7 and remove P7 from the front panel with a flat screwdriver used to compress the springs holding it to the sheet metal.

- 8) On the printed circuit board on the top of the power supply module, remove the screw holding the white wire to the board in the front, left corner, marked TB4, 5V out (left terminal).

- 9) In the same location as step 8, remove the screw holding two black wires to the board, marked +5VRTN (right terminal).

- 10) At TB3 in the lower, front right corner of the power supply module, remove the screw holding the green/yellow wire to the separate

terminal screw with a ground sign \_\_\_\_\_ (above TB3).

- 11) At TB3 remove all wires from the terminal screws.

- 12) Remove the two screws securing the front of the power supply module to the base of the DDEC using a long flat screwdriver.

- 13) Loosen but do not remove the corresponding two screws securing the rear of the power supply module.

- 14) Grasping the power supply module by its built in handles on the front, pull it slightly forward then tip it up and lift it from the power supply and place it on a table.

- 15) Unplug the three secondary output wires of the transformer from the top of the printed circuit board. These wires are brown, brown and purple and are plugged onto terminals marked F, B, and A. It does not matter which brown wire goes to F, or which goes to B.

- 16) Using a flat screwdriver remove the three screws holding the two red wires and one blue wire to terminals marked C, E, and D on the top of the circuit board. (it does not matter which red wire goes to C or which goes to E).

- 17) Remove the two large screws and four washers board on top of the power supply.

- 18) Using a Phillips screwdriver remove the seven screws around the edge of the circuit board then raise the board from the metal frame and set it to one side. At this time note the part number stamped on the 60Hz transformer. It should be 2783 6683.

- 19) At the inside of TB3 described in step 10, unplug the blue wire from the terminal marked *com* (far right). Unplug the black wire from the terminal wire from the terminal marked 240V (third from right).

- 20) At the rear base of the power supply module, remove the rubber cap covering the end of C101) Unplug the two white wires from the terminals of C101, (it does not matter which white wire goes to which terminal).

- 21) Unbolt the transformer from the base by removing the four nuts using a 7/16 inch nut driver. Lift the transformer from the power supply.

- 22) From the 60Hz 50Hz conversion kit take the transformer and ensure the part number stamped on it is 2783 7244. If correct bolt it to the base of the power supply module using the four nuts removed in step 21) Place the transformer so that the side with wires is on the inside of the power supply.

- 23) Remove the label above TB3 indicating a 60Hz power supply and replace with the 50Hz label from the kit with new voltage assignments for the terminals.

- 24) Remove the label showing the part number of

the power supply module as 2783 7872 and replace it with the new label from the conversion kit with part number 2783 3789.

- 25) Plug the blue wire from the transformer which has a plug end into the rear of TB3 at the terminal marked common (far right). Plug the black wire onto TB3 terminal marked 200V (second from right). Plug the orange wire onto TB3 terminal marked 220V (third from right). Plug the yellow wire onto TB3 terminal marked 230V (fourth from right). Plug the red wire onto TB3 terminal marked 240V (fifth from right).

- 26) Plug the two white wires on to each terminal of C101 at the left rear base of the power supply. Replace the rubber cap on C101) (It does not matter which white wire goes to which terminal).

- 27) Replace the circuit board on the metal frame, taking care to hold the remaining transformer wires so that they curl around the front of the board to its top without pinching them between any components. Secure the board to the metal with the seven Phillips screws removed in step 18.

- 28) Plug one brown wire from the transformer onto the circuit board terminal marked F at the center front of the board. Plug the other brown wire onto the board terminal marked B. It does not matter which brown wire goes to terminal C and which goes to terminal E. Plug the purple wire onto the board terminal marked A. Using the screws removed in step 16, fasten one red wire from the transformer to the board terminal marked C, the other red wire to the board terminal marked E, and the blue wire to the board terminal marked D.

- 29) Secure the two capacitors C102 and C103 to the circuit board using the two screws for each removed in step 17.

- 30) Reinstall the power supply module in the base of the DDEC by setting it forward of its final position then sliding it to the rear to engage the two screws securing it to the base at the rear. Refit 2 screws at front and tighten all four screws.

- 31) Connect the white wire to the TB4 terminal marked 5V out (left terminal) in the left front corner of the circuit board using the screw removed in step 8.

- 32) Connect the two black wires to TB4 terminal marked 5VRTN (right terminal) using the screw removed in step 9.

- 33) Connect the green/yellow ground wire to the terminal marked with the ground sign <u>—</u> above TB3 using the screw removed in step 10.

- 34) At TB3 in the lower front right corner of the power supply module, connect one white AC

input wire, along with the white wire from each of the two sheathed fan harness cables all to TB3 terminal marked com (far right terminal). The other white AC input wire along with the black wire from each of the sheathed fan harness cables should be connected to the appropriate terminal of TB3 depending on the voltage source. Determine from the electrician what voltage the source is before connecting these wires. The second from right terminal is for 200V input. The third from right terminal is for 222V input. The fourth from right terminal is for 230V input. The fifth from right terminal is for 240V input. It does not matter which white AC input wire goes to com and which goes to the voltage input terminal.

- 35) Mark in ink the power conversion label 2783 7608 with the correct voltage, frequency and phase information and attach this adjacent to the machine nameplate label at the rear.

- 36) With circuit breaker CB3 on front cover power supply turned off, and CB1 and CB2 on rear cover power supply turned off, apply AC power source to the machine. With an AC voltmeter measure the voltage between TB3-1 and the other terminal of TB3 connected in step 34. Be sure that the terminals used on TB3 in step 34 correspond to the voltage measured here. Change the terminal used in step 34 if necessary, being sure AC source is disconnected before making changes.

- 37) Using the four screws removed in step 6, fasten the front cover power supply to the rear cover power supply.

- 38) Using the six screws removed in step 5, fasten the top cover power supply to the rear cover power supply.

- 39) Refit the AC cover over TB1 and secure with the four screws removed in step 4.

- 40) Turn CB3 on and check that all fans operate.

- 41) Refit all side panels to the DDEC by engaging them in the two holes at the top, then tightening the two clamps in the frame below each panel.

#### Single Phase Conversion

Use this method when only 2 phase power is available. Line to line voltage is 208 to 240 volts. Figure 2-3 shows the method of connecting the input power.

- 1) Connect line 1 to TB1 terminal 1 and terminal 3.

- 2) Connect line 2 to TB1 terminal 2.

- 3) Connect neutral to TB1 terminal 4.

- 4) Connect ground to E7 below TB1.

If the single phase method of installation is used, only J3 and J4 may be used to power drives. J3 is the lower left receptacle on the front panel power supply. J4 is the upper right receptacle. The drives are wired in the normal line to line manner.

Figure 2-3. Single Phase Input Power Connection

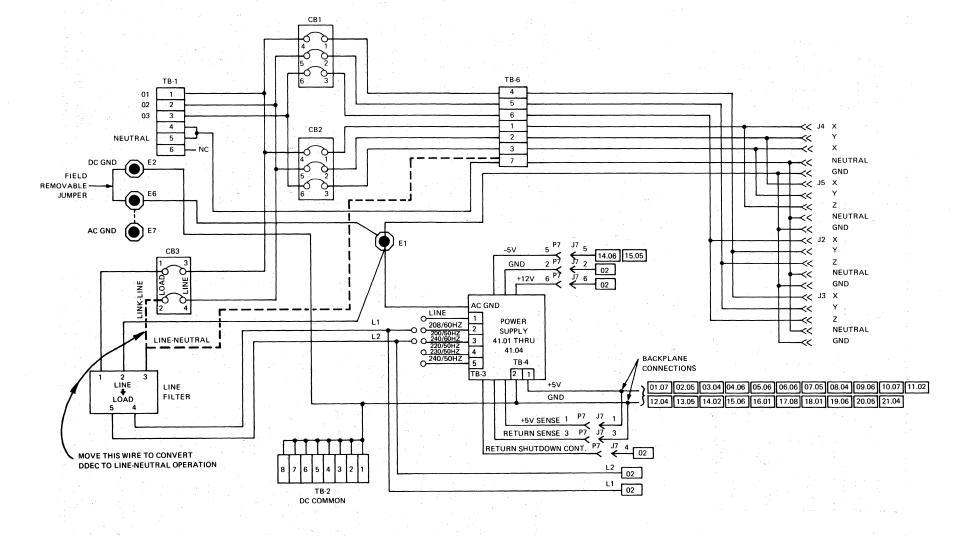

#### Line to Neutral Conversion

When the 206/7 DDEC is powered from an AC source which provides 200 VAC to 240 VAC measured from line to neutral, two conversions must be done.

- 1) Rewire the power distribution in the DDEC according to the following procedure.

- 2) Select the correct transformer tap according to the procedure below the heading *Voltage Tap Conversion*.

The following rewiring procedure must be performed to install the DDEC with line to neutral AC input power. Figure 2-4 shows the conversion.

- 1) Remove the power supply top cover.

- 2) Find TB6. It is bolted to the inside of the power supply on the right-hand side.

- 3) Find CB3. It is bolted to the inside of the front cover of the power supply.

- 4) Unplug the quick-connect and wire from CB3 terminal 1. This wire can be identified by its extra length.

- 5) Uncoil the wire removed in step 4 and pass it down the right side of the power supply. Plug the quick-connect to TB6 terminal 7.

- 6) Be sure the wire does not interfere with the fan for the power supply.

7) Replace the power supply top cover.

Any disk drives powered from the DDEC must be converted to line-neutral operation.

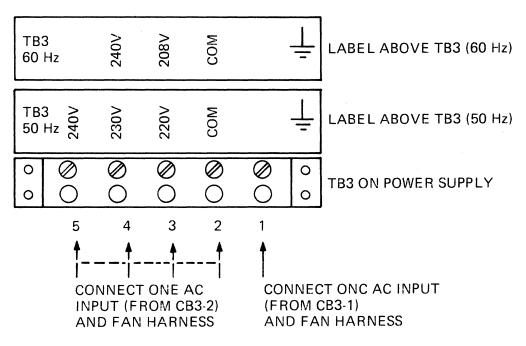

#### Voltage Tap Conversion

Use this procedure when the input voltage is greater than the transformer tap rating for which the DDEC power supply is wired. The primary tap of the power supply transformer must be chosen to correspond to the input voltage. Figure 2-5 is TB3, located on the power supply module, front right corner. TB3 terminals are marked for the appropriate tap. Terminal 1 must have one input line connected as well as one wire from each of the fan harness cables. The other input line must go to the correct terminal of TB3 according to the line voltage. Remaining fan harness wires connect to the same terminal.

#### **Checkout Procedure**

The following steps must be used when doing a check out of the DDEC and the subsystem after installation.

#### Power on Checks

- 1) Be sure that all the requirements have been met in this section for powering the DDEC and cabling it to the drives and the processor.

- 2) Be sure that all installation steps for the drives have been followed.

- 3) Move the switch on CB3 at the front of the power supply to the up position. Off and offline should be indicated on the front operator panel switches. If on or online is indicated, press the switch to change it to off or offline.

- 4) Check that the three fans are operating. One is on the front of the power supply. Two are on the sides of the card cage.

- 5) Look through the two fans on the card cage to see that the airflow switches are activated. The vanes on these switches may be caught due to shipping vibration.

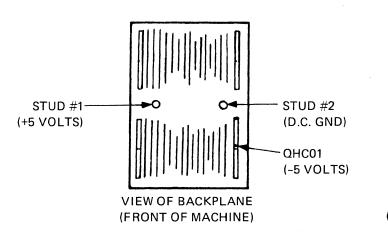

- DC Voltage Check

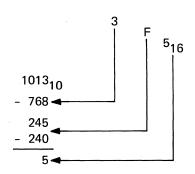

- 1) Press the power switch on the operator panel to light the on indicator.

- 2) Using a DVM, measure the voltage between the two studs on the backplane. The stud on

Figure 2-4. Schematic Showing Line-Neutral Conversion

Figure 2-5. TB3 Connections

the left must be +5 volts referenced to the stud on the right (DC ground).

- 3) Measure the voltage at the backplane pin QHC01. It must be -5 volts referenced to the DC ground stud.

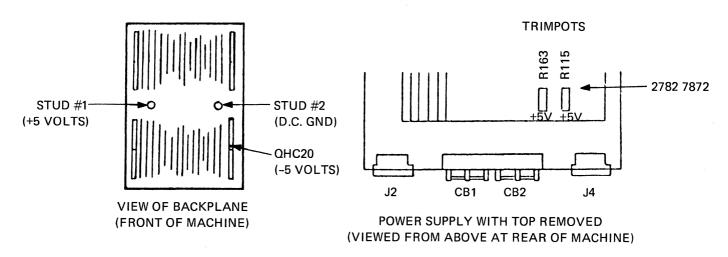

- 4) Adjust the +5 volts and -5 volts using potentiometer adjusting tool. The adjusting potentiometers are located on the rear edge of the printed circuit card of the power supply unit. The top cover of the power supply must be removed in order to adjust the voltages. Sheet 07.03.02 of the Test and Field Documents package illustrates the voltage adjustment.

#### **Clock Frequency Check**

- 1) Using a frequency counter or oscilloscope, measure the internal DDEC clock at the backplane test point DDE17. Be sure that the drive clock is not selected at this time. To ensure the clock at the test point is *local clock*, put DDEC offline and press MSTR CLEAR on the maintenance panel.

- There is no adjustment of the local clock frequency. The frequency must be between 9.25 MHz and 10.75 MHz.

#### Local Operations

- 1) At the rear of the DDEC observe the address counter display. Some LED's should be illuminated.

- 2) Press MSTR CLEAR on the maintenance panel. All LED's on the maintenance panel are illuminated while MSTR CLEAR is pressed.

- 3) Do a test operation from the maintenance panel. Section 4 of this technical manual gives details for doing operations in local mode. The result descriptor must be NR and OL since the drive is not powered on.

- 4) Power on a drive. Ensure that the write enable switch on the drive is not illuminated.

- 5) Repeat a test operation with a drive powered on the heads loaded. The result descriptor must have no error bits set.

- 6) Test all operations on one drive. Use caution. Write, initialize, and relocate operations destroy customer data and system software. For all such operations, install a scratch pack or use only the maintenance cylinder.

- 7) Power On all drives in the subsystem and verify that operations can be performed with each in local mode.

#### **Online Operations**

- 1) Press the REMOTE switch on the operator panel of the DDEC to light the online but ton.

- 2) At the processor, use the latest revision of the Disk Pack Diagnostic and its listing to exercise the disk subsystem.

- 3) If no problems exist in local mode and under test from the processor, installation is complete. Replace all panels on the DDEC and drives.

- 4) Cold start and clear start as instructed in the System Software Operational guide in order to prepare the system for customer use.

## **SECTION 3**

## **DOCUMENTATION AND COMPONENTS**

#### **REFERENCE DOCUMENTS**

The following is a list of publications which apply to the B 9499-6 DDEC.

| Field Engineering Technical Manual: | Form<br>Numb <b>e</b> r: |

|-------------------------------------|--------------------------|

| Volume 1, Operation and Maintenance | 2011342                  |

| Volume 2. Parts Catalogue           | 2011359                  |

| Volume 3. Theory of Operation       | 2011367                  |

| Reference Card                      | 3026929                  |

#### **Test and Field Documents**

#### General

The T & F documents are divided into Sections as shown in table 3-1.

#### Table 3-1. T & F Sections

| Section | Contents                    |  |  |

|---------|-----------------------------|--|--|

| 01      | Index                       |  |  |

| 02      | Block Diagrams              |  |  |

| 03      | Flow Charts                 |  |  |

| 04      | Timing Diagrams             |  |  |

| 05      | Control Equations           |  |  |

| 06      | I.C. Locations              |  |  |

| 07      | Assembly and Set-up Details |  |  |

| 08      | Backplane Circuit Lists     |  |  |

| 09      | Schematics                  |  |  |

| 10      | MTR                         |  |  |

Each section is divided into subjects and each subject has a number of physical pages associated with it. Each page is numbered according to section, subject no., and physical page number.

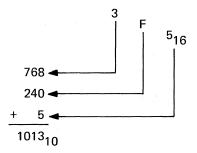

Example:

03.08.01Page 1 of the flow chart for data transfer03.08.02Page 2 of the flow chart for data transfer09.04.06Page 6 of the schematic, DM-ERD con-trol OP code Decode.

#### Description

#### Index

The index lists each subject in each section, giving the section no., subject no., title of subject, and the Engineering Document Number.

#### **Block Diagrams**

The block diagrams are intended to assist in understanding the structure of the unit. The overall block diagram contains the main blocks. Each of the blocks in the overall block diagram contains a reference. This reference is a page where a block diagram of each of the main blocks can be found.

In the individual block diagrams, a reference number in each block points to the schematic page where the logic can be seen.

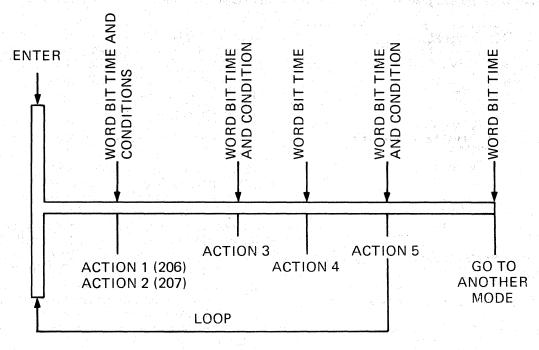

#### Flow Charts

The flow charts consist of an overall mode flow diagram, showing how the modes link together and an individual flow for each mode.

An individual mode flow chart is depicted in figure 3-1. The flow generally starts at the top left hand and flows from left to right. If the conditions above the double horizontal line are met, the action below the double horizontal line is performed. The action performed is sometimes different depending on whether the unit selected is a 206 or 207. In some cases 206 or 207 is shown as a condition. In some cases, two actions are given, however, one action has (206) next to it and the other has (207). In some cases the flow splits into two, one for 206 and the other for 207.

#### **Control Equations**

The control equations are contained in section 5. They are the equations for the control logic only not the complete unti. The control logic consists of the logic that controls the flows. The unit was designed from these equations.

#### Schematics

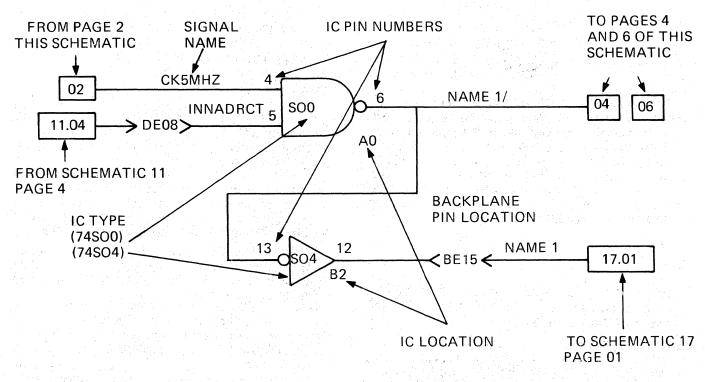

The schematics are cross-referenced for easy signal tracing. Refer to figure 3-2 for details about cross-referencing, IC types, IC locations, backplane pin locations, IC pin numbering, etc.

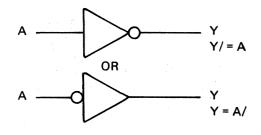

In most cases the signal is named according to the function if performs. The Glossary of Terms in appendix A of this technical manual explains each signal and gives the schemtatic page where the signal is sourced. A mixture of positive and negative logic is used in TTL. When negative logic is used, signal name is terminated with a slash (/). Also the signal starts from a negation symbol (bubble) and goes into a bubble.

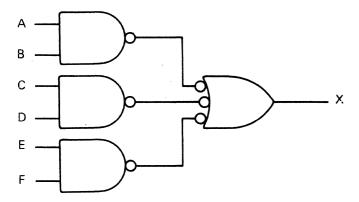

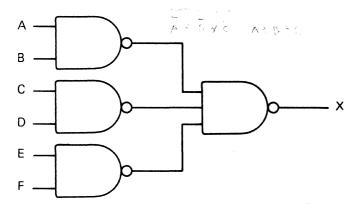

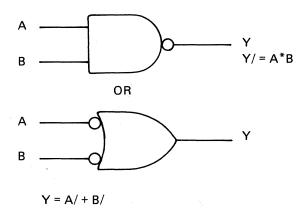

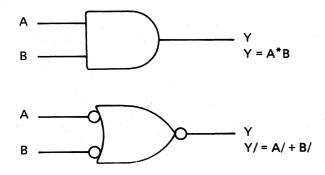

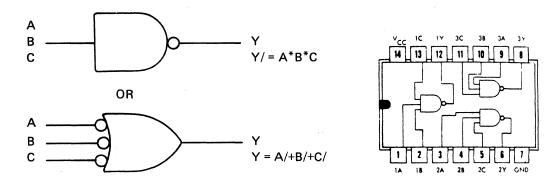

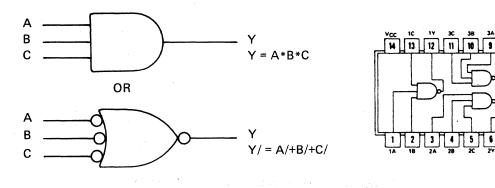

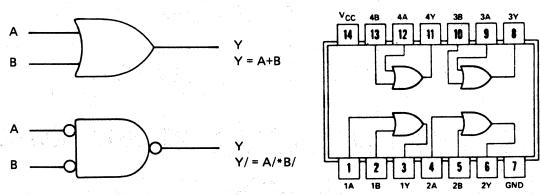

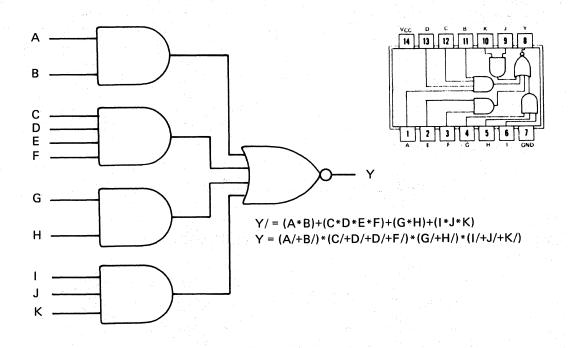

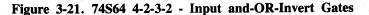

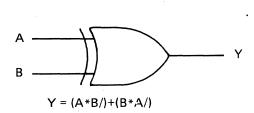

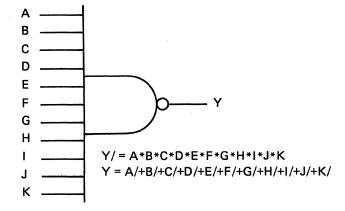

NAND, NOR, AND, OR gates are drawn in the way in which they are used. Figures 3-3 and 3-4 show the same logical function. The schematic shown in figure 3-3 is used because it is visually easier to understand.

The backplane locations of each printed circuit board is marked on sheet 1 of the schematic for each board. For example, on page 09.10.01 of the T & F

Document package, the words E UPPER are printed above the page number. Sheet one of the schematics for circuit board ten is 09.10.01. 10. Circuit board 10 corresponds on the backplane to the upper set of pins in column E.

Figure 3-1. Flow Chart Example

Figure 3-2. Schematic Details

Figure 3-3. Negative or Function

Figure 3-4. Positive NAND Function

#### **Backplane Wirelist**

Section 08 of the T & F Documents contains the Backplane Wirelist. Signal names are listed in alphabetical order. The first column after the name is the source pin for that signal.

The From and To columns name every pin which is wired into each network. The last column gives the level of the backplane wire on the pins. Level 1 is closest to the base of the pins. Level 2 is further out on the pins. There are only 2 levels of backplane wiring.

#### **Component Location System**

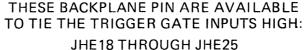

#### **Backplane** Pins

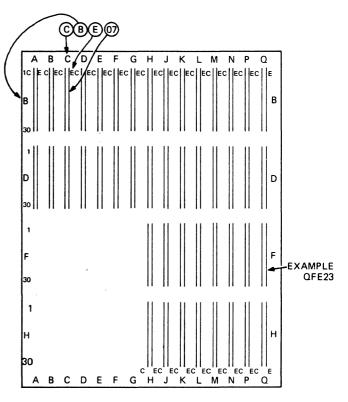

Backplane pins are called up on the schematics and the backplane wire list according to the following example:

#### QFE23

Refer to figure 3-5 to locate this pin.

Q - is marked along the top of the backplane. This marks a card slot which may be upper or lower.

F - is marked along the sides of the backplane. This gives a horizontal reference to identify 60 pins for each card slot. E - is marked at the top of a column of pins. This marks a vertical row of pins on the etch side of the card slot.

23 - is marked at the sides of the backplane. This identifies the pin.

Figure 3-5. Front View Backplane

#### **Printed Circuit Boards**

#### **IC** Locations

Figure 3-6 shows the component side of a typical printed circuit board. The columns of ICs are lettered from A to H. The rows are numbered from 0 to 5. Schematics refer to IC locations by a letter and a number. For example C3. This is column C, row 3.

#### Edge Connector Contact Numbering

Figure 3-6 shows the component side of a typical printed circuit board. Backplane contacts are at the right side of figure 3-6. Each contact has a four character designation. For example HE19.

1st Character

This can be B, D, F, or H. B is for the top half and D is for the bottom half of a board located in the upper row of cards in the DDEC. F and H are for the top half and bottom half of a board located in the lower row of cards in the DDEC. 2nd Character

This can be C for the component side of the card or E for the etched side of the card.

3rd and 4th Character Are the pin number from 1 to 30.

Frontplane contacts are shown on the left edge of the card in figure 3-6. On a circuit board with one set of frontplane contacts, they are numbered from 1 to 20. The prefix is FC for component side and FE for etch side. Circuit board 13 has two sets of frontplane contacts. The prefix GC is the top of the card, component side. Prefix GE is the top of the card, etch side. Prefix HC is the bottom of the card, component side. Prefix HE is the bottom of the card, etch side.

| BOARD LOCATION                   |                                                       |

|----------------------------------|-------------------------------------------------------|

| FRONTPLANE<br>CONTACTS           |                                                       |

| FC01 TO FC20<br>(COMPONENT SIDE) | CKPLANE CONTACTS                                      |

| FE01 TO FE20                     | COMPONENT SIDE BC01 TO BC30<br>ETCH SIDE BE01 TO BE30 |

| (ETCH SIDE) LOWER LEVEL CARD     | COMPONENT SIDE FC01 TO FC30<br>ETCH SIDE FE01 TO FE30 |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

|                                  |                                                       |

| UPPER LEVEL CARD                 | COMPONENT SIDE DC01 TO DC30<br>ETCH SIDE DE01 TO DE30 |

| LOWER LEVEL CARE                 | COMPONENT SIDE HC01 TO HC30<br>ETCH SIDE HE01 TO HE30 |

Figure 3-6. Typical PCB

#### **Component Reference Charts**

#### **GENERAL DESCRIPTION**

In the unit schematics ICs are identified by an abbreviated manufacturers number. example:

S251 means 74S251 A list of abbreviations is contained at the front of the Schematics. T.T.L. is used with the exception of a few specialized ICs. A description of the T.T.L. family types is given in table 3-2.

| Table | 3-2. | TTL | Family | Types |

|-------|------|-----|--------|-------|

|-------|------|-----|--------|-------|

| SERIES                      | GAT         | FLIP-FLOPS  |           |

|-----------------------------|-------------|-------------|-----------|

|                             | Propogation | Power       | Max Clock |

|                             | Delay       | Dissipation | Frequency |

| 74LSnn (Low Power Schottky) | 9.5 ns      | 2 mw        | 45 MHz    |

| 74L nn (Low Power)          | 33 ns       | 1 mw        | 3 MHz     |

| 74Snn (Schottky)            | 3 ns        | 19 mw       | 125 M Hz  |

| 74 nn (Standard)            | 10 ns       | 10 mw       | 35 MHz    |

| 74Hnn (High Power)          | 6 ns        | 22 mw       | 50 MHz    |

Schottky T.T.L. contains Schottky barrier diode clamped inputs in order to prevent saturation of the inputs and lower output resistances. These two factors provide low propogation times. Schottky T.T.L. is used for high speed applications. Schottky T.T.L. should never be tied to ground due to excessive heat dissipation when the output is in the high state. No T.T. L. should be tied to +5V since this destroys the output transistor when the output tries to go low.

Three State logic is used on the data buses in the unit. The three states are: High, Low and High Impedence. This enables many outputs to be connected to a bus, however, all except one is in high impedence mode. The output not in high impedence mode determines whether the bus is high or low.

#### **REFERENCE CHARTS**

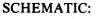

SCHEMATIC:

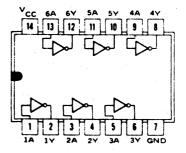

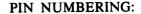

PIN NUMBERING:

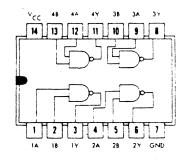

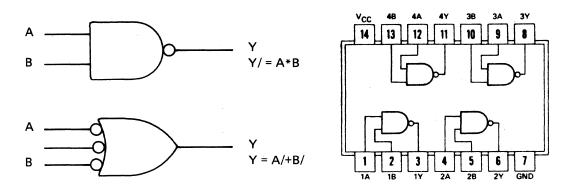

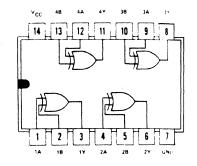

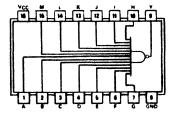

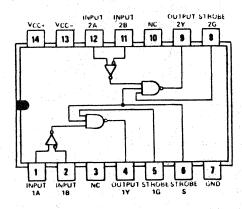

Figure 3-7. 7400 74S00 Quad 2-Input Positive NAND Gate

PIN NUMBERING:

Figure 3-8. 7402 74S02 Quad 2-Input Positive NOR Gate

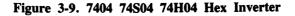

SCHEMATIC:

PIN NUMBERING:

SCHEMATIC:

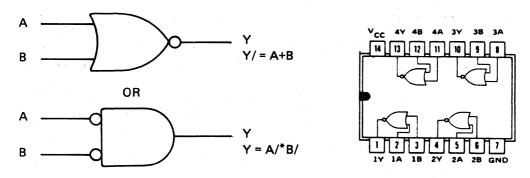

Figure 3-10. 7408 74S08 Quad 2-Input and Gate

PIN NUMBERING:

Figure 3-11. 7410 74S10 Triple 3-Input Positive NAND Gate

SCHEMATIC:

PIN NUMBERING:

Figure 3-12. 74S11 Triple 3-Input Positive and Gates

SCHEMATIC:

PIN NUMBERING:

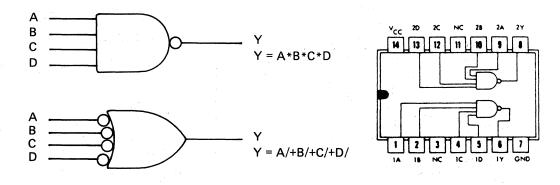

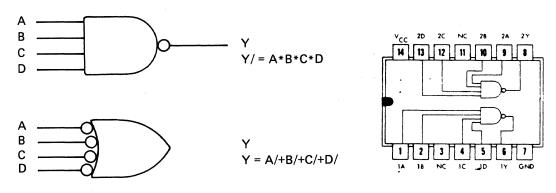

Figure 3-13. 7420, 74S20 Dual 4-Input Positive NAND Gates

**PIN NUMBERING:**

**SCHEMATIC:**

PIN NUMBERING:

**PIN NUMBERING:**

**SCHEMATIC:**

Figure 3-16. 7432 Quad 2-Input Positive or Gates

3-8

PIN NUMBERING:

Figure 3-17. 7437 Quad 2-Input NAND Buffers

**SCHEMATIC:**

#### **PIN NUMBERING:**

Figure 3-18. 7440 74S40 Dual 4-Input NAND Buffers

#### SCHEMATIC:

**PIN NUMBERING:**

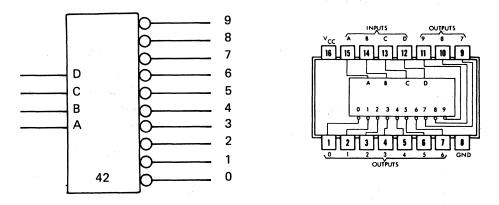

Figure 3-19. 7442 4-10 Line Decoder

Description:

The 7442 is a BCD to decimal decoder. A Binary input zero through nine is decoded to make one output low. (The rest are high). Input values from 10-

15 are invalid and all outputs are held high. Inputs A, B, C and D are weighted 1, 2, 4 and 8 respectively.

#### PIN NUMBERING:

SCHEMATIC:

PIN NUMBERING:

**PIN NUMBERING:**

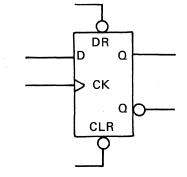

Figure 3-22. 7474 74S74 Dual D-Type Flipflop

#### Description:

The flipflop can be set by a low on PR and reset by a low on CLR. The positive edge of the clock triggers the flipflop. If D is high the flipflop sets on

SCHEMATIC:

the clock, if D is low the flipflop resets on the clock.

**PIN NUMBERING:**

Figure 3-23. 7486 74S86 Quad 2-Input Exclusive OR Gates

#### **SCHEMATIC:**

**PIN NUMBERING:**

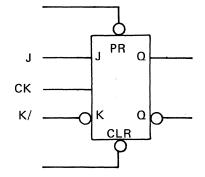

Figure 3-24. 74S109 Dual J K/ flipflop

Description:

A low on PR sets the flipflop. A low on CLR resets the flipflop.

If J is low and K/ low, the flipflop resets on the positive edge of the clock.

If J is high and K/ is high the flipflop sets on the

positive edge of the clock.

If J is high and K/ is low, the flipflop toggles (changes state) on the leading edge of the clock.

If J is low and K/ is high there is no change in the state of the flipflop when the clock occurs.

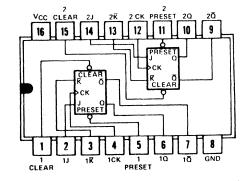

**PIN NUMBERING:**

| INPL         | JTS | OUTPUTS        |     |   |

|--------------|-----|----------------|-----|---|

| CLEAR        |     | B              | Q   | Õ |

| L            | x   | X              | L   | н |

| <b>X</b> -   | н   | · x. ·         | L   | н |

| ×            | x   | · L.           | L   | н |

| H            | L.  | :: <b>t</b> 1; | L U | ប |

| н            | 4   | H              | Л   | ប |

| 1 <b>†</b> 1 | ΓL. | Ĥ              | J.  | ີ |

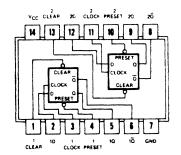

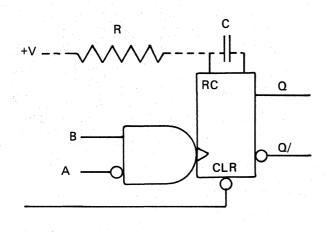

Figure 3-25. 74123 Dual Retriggerable Monostable Multivibrator

Description:

A low CLR resets the timer. (Q Low and Q/high). When the input conditions are met (B high and A low) a pulse is generated at the output with the length dependent on R and C. The output pulse can

be extended by retriggering the IC before it has timed out. The output pulse extends a length depending on RC.

#### SCHEMATIC:

ABLE OUTPUT GND OVCC R VCC 15 11 18 12

**PIN NUMBERING:**

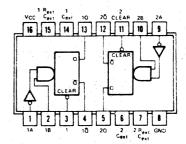

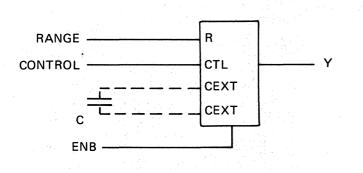

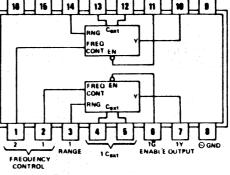

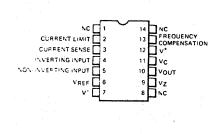

Figure 3-26 74S124 Dual Voltage-Controlled Oscillator

#### Description:

ent on CEXT, Range Voltage and control voltage. When enable goes low, the output is enabled, giving a square wave out-put. The frequency is depend-

**PIN NUMBERING:**

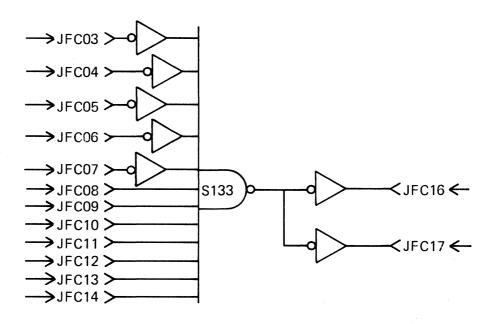

SCHEMATIC:

PIN NUMBERING:

|     | IN  | IPUT | s    |   | OUTPUTS |    |    |     |     |    |    |    |

|-----|-----|------|------|---|---------|----|----|-----|-----|----|----|----|

| ENA | BLE | S    | ELEC | T |         |    | Ľ  | 101 | rui | 3  |    |    |

| G1  | G2* | С    | 8    |   | YO      | ¥1 | ¥2 | ¥3  | ¥4  | ¥5 | ¥6 | ¥7 |

| X   | н   | X    | x    | X | н       | н  | Ή  | Н   | Н   | Н  | н  | н  |