MBB Microprogrammer's Handbook

R. Weissler, M. Kraley, P. Herman

First Published January 1980 Revised August 1980

Copyright (c) 1980 by Bolt Beranek and Newman Inc.

# Table of Contents

| 1 II<br>1.1<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4                               | NTRODUCTION AND OVERVIEW.<br>MPMs and Emulation.<br>Physical Description.<br>Processor Design.<br>Basic Data Loop.<br>MIR and Dispatch.<br>MAR and Main Memory.<br>Other Features.<br>18                                                                                              | L 5 ) ) 1 5 |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2 P1<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | ROCESSOR20Basic Data Flow20Register Selection22ALU Status24Program Control25Conditional Execution27Constants28Certain Coding Awkwardnesses30MIR Daughterboard and Dispatch Memory31Shifting37Loading and Reading Microcode39Miscellaneous Features41Handling Exceptional Conditions42 |             |

| 3 M/<br>3.1<br>3.2<br>3.3<br>3.4                                                            | AIN MEMORY                                                                                                                                                                                                                                                                            | 57          |

|                                                                                             | AIN MEMORY ERROR DETECTION AND CORRECTION<br>EDAC)                                                                                                                                                                                                                                    | )<br>2      |

| 5.1                                                                                         | <pre>/0 and INTERRUPTS</pre>                                                                                                                                                                                                                                                          | 11570121555 |

-

| 5.5.2Servicing Interrupt Requests                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

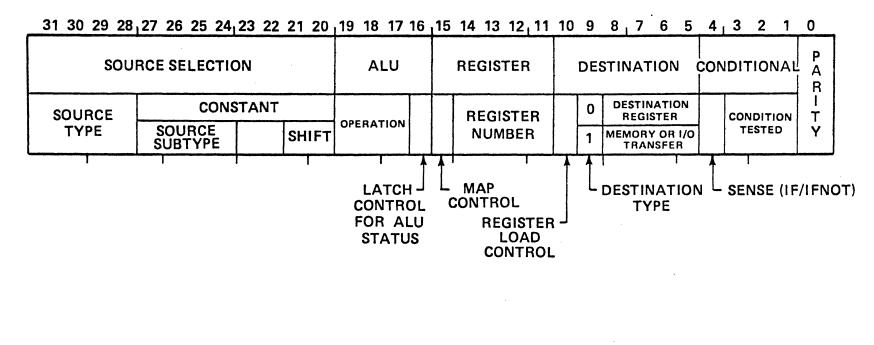

| 6       MICROINSTRUCTION FORMAT.       82         6.1       Source Field (UIR 31 - 20)       82         6.2       ALU Field (UIR 19 - 16)       87         6.3       Register Field (UIR 15 - 11)       88         6.4       Destination Field (UIR 10 - 5)       88         6.5       Condition Field (UIR 4-1)       90         6.6       Parity (UIR 0)       90         6.7       Special Considerations for Using Dispatch as a Source.       91 |

| 7       BIT ASSIGNMENTS IN CERTAIN REGISTERS.       92         7.1       ALUST.       92         7.2       MISC.       93         7.3       MISC2.       94         7.4       The EDAC Register.       97                                                                                                                                                                                                                                             |

| 8THE MBB'S SYSTEM SOFTWARE.998.1The Terminal Handlers.998.2'Running' and 'Not Running' States.1008.3Exceptional Conditions and Initialization.1028.4Source File.103                                                                                                                                                                                                                                                                                   |

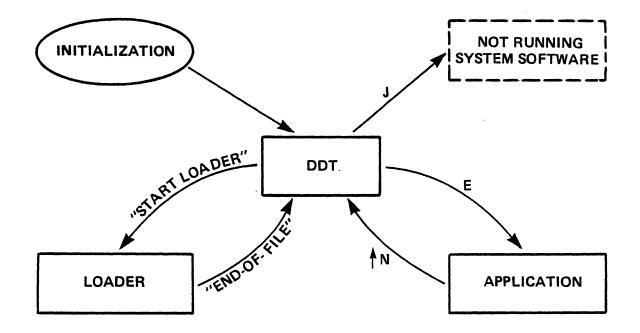

| 9 THE MBB'S UDDT COMMANDS 104                                                                                                                                                                                                                                                                                                                                                                                                                         |

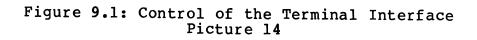

| 10THE CONTROL AND DEBUGGING PACKAGE.10910.1The CDP's Modes.11010.2The CDP's Command Mode.11410.2.1Examining and Changing Locations.11510.2.2Symbols.11510.2.3Controlling MBB Program Execution.11810.3The Simulated MBB.11910.4Summary of Commands.12510.5Current CDP Bugs and Confusion.12810.6Invoking the CDP.129                                                                                                                                  |

| 11THE MBB ASSEMBLER.13111.1Format Considerations.13111.2Numbers and Expressions.13211.3Microcode Instructions.13311.3.1Sources and Destinations.13411.3.2Constants.13511.3.3ALU Registers and Operations.13511.3.4Conditional Execution.13611.3.5Other Special Cases.13711.4Pseudo-Ops and Address Spaces.13811.5The Parser.14011.6Invoking the Assembler; Files Generated;<br>Loading.142                                                            |

# PICTURES

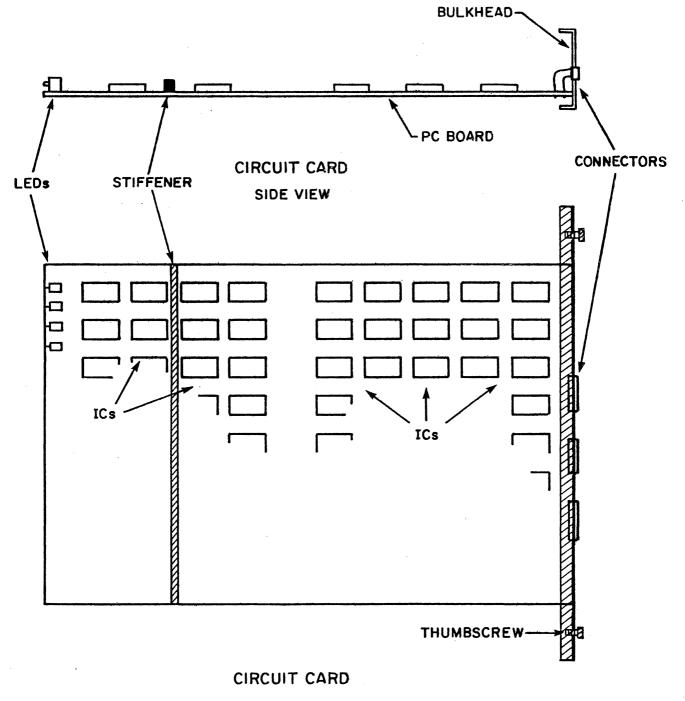

| Figure | 1.1a: MBB Physical Structure             | 6  |

|--------|------------------------------------------|----|

| Figure | 1.1b: MBB Physical Structure (continued) | 7  |

|        | 1.1c: MBB Physical Structure (continued) |    |

| Figure | 1.2: MBB Logical Structure               | 12 |

|        | 2.1: Processor                           |    |

| Figure | 2.2: The MIRDB and Dispatch Memory       | 32 |

|        | 2.3: Shifting                            |    |

| Figure | 3.1 Main Memory Address and Data Paths   | 45 |

| Figure | 4.1: EDAC Data Paths                     | 51 |

| Figure | 5.1 I/O Data Transfer                    | 68 |

| Figure | 5.2 I/O Device Addressing                | 73 |

| Figure | 5.3 I/O Interrupt Vector Addresses       | 78 |

|        | 6.1: Microinstruction Format             |    |

|        | 9.1: Control of the Terminal Interface 1 |    |

|        | 10.1: The CDP's States 1                 |    |

Bolt Beranek and Newman Inc.

#### 1 INTRODUCTION AND OVERVIEW

The Microprogrammable Building Block (MBB) is a general purpose, easily microprogrammable, powerful computer which can be used for a variety of applications. This manual attempts to completely describe the MBB's hardware elements and their function from the microprogrammer's point of view.

Although the MBB can be programmed directly in its microlanguage for a specific application we envision that in most application, the MBB will be emulating some other machine, either existing or invented. Accordingly, we begin with a discussion of emulation, which also introduces some terms which will be used throughout this document. We then describe some of the physical characteristics of the machine and give an overview of its logical structure.

### 1.1 MPMs and Emulation

Because they allow close program control over hardware action, microprogrammable computers are often suited for emulating other computers. When used for such emulation, the microprogrammable machine (MPM) is called the "micromachine" or "microcomputer"; its code is "microcode", its instructions are "microinstructions", the execution of a microinstruction is a "microcycle", and so on. (We are not using "microcomputer" to

mean a very small computer, as is sometimes done.) The emulated machine is called the "macromachine", its code is "macrocode", and so on.

To emulate the macrocomputer's execution of a given macroprogram, the microcomputer needs that program loaded as data. The microcomputer's microprogram reads macroinstructions one at a time, decoding each one and emulating its execution. For example, a macroprogram branch corresponds to the microprogram's breaking out of sequence in its examination of macroinstructions.

Emulating a macroinstruction is often straightforward. Macroinstructions generally deal with macroregisters, macromemory, and macro-I/O (including interrupts); and the macromachine's data operations generally consist of unary and binary operations such as NOT and ADD. The microcomputer generally contains registers which the microprogram uses as images of macroregisters. For example, one of the microregisters is maintained to have its contents reflect the macromachine's program counter, and is used to determine the next macroinstruction to be emulated. Normally, emulating the execution of a macroinstruction would involve increasing that register by one; emulating the execution of a macro-JUMP command would involve setting that register to reflect the new macromachine's execution address. Other microregisters would

mirror the macromachine's accumulators and index registers. A macroinstruction to clear an accumulator, for example, would be emulated by clearing the corresponding microregister.

The microcomputer also generally has a memory area which the microprogram uses as a direct image for macromemory. This area holds the macromachine's program and data. To fetch the next macroinstruction to be executed, the microprogram simply reads from this area at an address indicated by its image of the macromachine's program counter. To emulate a macroinstruction to clear a memory cell, the microprogram simply clears the corresponding location in its image of macromemory.

Further, the microcomputer has, in general, an Arithmetic and Logic Unit (ALU) which can perform the macrocomputer's data operations such as NOT and ADD. To simulate a macroinstruction to add memory contents to an accumulator, the microprogram uses its ALU to add the contents of its image of the memory cell to the contents of its image of the accumulator and stores the result in its image of the accumulator.

Because the macromachine's registers, memory, and data operations have direct representations, emulating their functions is easy. In contrast, the macromachine's I/O system often is not replicated. For example, the macrocomputer may have many priority-ordered interrupt levels, while the microcomputer may make available only one; the macrocomputer's I/O instructions may

send signals down an I/O bus which has no equivalent in the microcomputer: or the macrocomputer may have sophisticated hardware which lets it initiate a block transfer with one instruction, while the microcomputer lacks such hardware and must transfer each word separately under microcode control. When I/O hardware is not mirrored precisely, emulating I/O functions can be difficult. Generally, the micromachine's system I/O handlers interact with microcode which emulates I/O-related macroinstructions such as instructions to request an interrupt or to initiate a block transfer.

In addition to I/O hardware, certain other specialized hardware may not be mirrored. For example, the micromachine may lack the macromachine's hardware logic for decoding macroinstructions or performing memory mapping. In all of these cases, the microcode assumes the burden of emulating the macromachine's specialized hardware. The microcode's close control over the microcomputer's hardware is usually important for efficient emulation.

An MPM used for emulation may offer two advantages over the macrocomputer it emulates. First, the MPM may be cheaper, since it can use simple, inexpensive. regularly structured hardware, using microcode to mimic the macromachine's expensive specialized hardware features. Second, it may be easy to change the microcode to enhance the macrocomputer's configuration, primitive

operation, or efficiency. For example, it might be easy to expand macromemory, to add new macroinstructions, or to optimize the emulation of frequently executed macrocode.

# 1.2 Physical Description

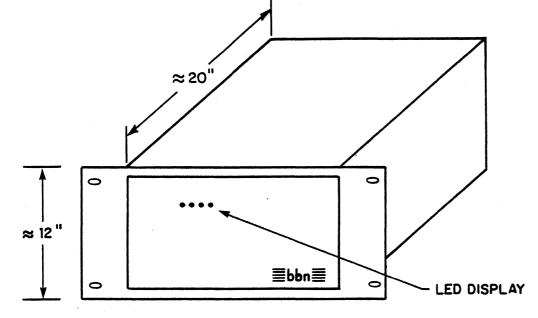

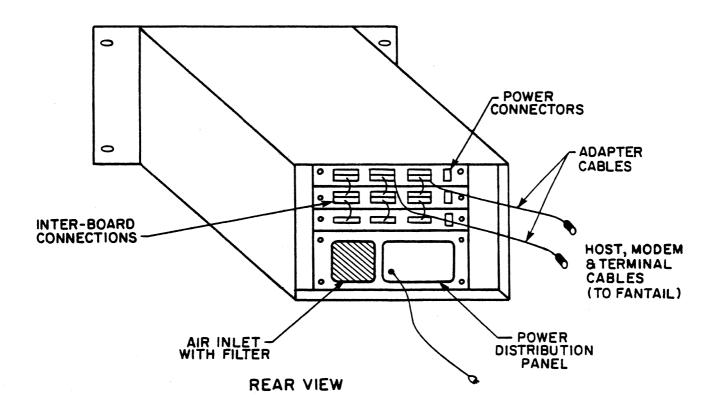

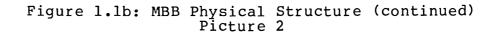

Before discussing the detailed logical design of the MBB we will describe the MBB's physical structure. Figures 1.1a through 1.1c show various views of a minimum MBB configuration. The exact configuration is dependent on the intended application.

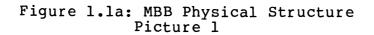

The housing is a box approximately 12" high and 20" deep, mountable in a standard 19" rack. A smoked plexiglass front lets display lights shine through. Inside, four printed circuit (PC) cards rest between guide rails; one is for the power supply, two are for the basic MBB processor/memory system, and one is available for I/O circuitry. (The power supply card has some logic circuitry in addition to fans, power supply, and other bulky units. For convenience it too is called simply a "card".) Because the cards are fairly wide (about 14"), each has a transverse stiffener to prevent bowing.

Each card has a metal bulkhead mounted at the rear. The cards use L-shaped electrical connectors, one end soldered to the card and the other mounted in the bulkhead. All electrical

Bolt Beranek and Newman Inc.

FRONT VIEW

Bolt Beranek and Newman Inc.

TOP VIEW

Figure 1.1c: MBB Physical Structure (continued) Picture 3

connections from one card to another are made with cables which attach to the connectors mounted on the bulkhead. The bulkhead is wider than the card, and it transfers the force of connector mating to the side rails of the box. The bulkhead screws into the box to keep the card still. The bulkhead, like the transverse stiffener mentioned above, helps to prevent bowing.

The MBB's side walls extend past the rear; the overhang protects the connectors mounted on the bulkheads.

Since the box has no internal wiring or edge connectors, tight tolerances are not needed for placement of cards in the box.

PC cards are spaced rather widely to ease cooling, relax mechanical tolerances, and provide sufficient area for connectors. Spacing is not uniform; the power card, containing two fans, needs considerable space while an I/O card may need a wide bulkhead to accommodate many connectors.

Power consumption is only about 350 watts at the AC plug, so two fans easily provide adequate cooling. Figure 1.1c shows air flow viewed from the rear. Air flows in at the bottom left rear. across the left half of the power board, up and across the other boards from left to right, down and across the right half of the power board, and out the bottom right rear. A baffle, reaching from the power board up to the next higher board, prevents "short-circuit" air flow between the inlet and outlet sides. The

power board has its logic elements on the left side to be cooled by incoming air, and its heavy heat dissipaters on the right side to be at the end of the airflow.

A battery on the power board provides one minute of backup power. Our experience suggests that such a battery will enable the MBB to withstand a large majority of external power outages. The battery will recharge automatically and will require no regular maintenance; under normal conditions it should last 3-5 years.

The MBB's hardware is divided into a "standard" or "system" part, which is present in every MBB system, and an "application" part, which is peculiar to the particular application. The standard part consists of the housing, the power card, and two PC cards for processor/memory. The processor/memory logic is designed to permit two inserts: small PC cards called the MIR and MAR daughterboards. These daughterboards are custom designed for each MBB application.

### 1.3 Processor Design

### 1.3.1 Basic Data Loop

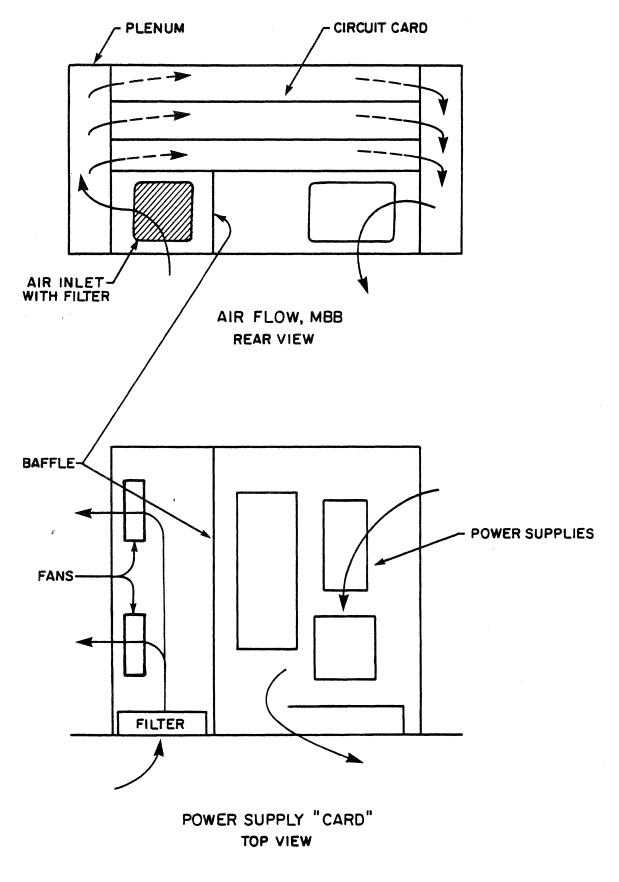

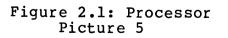

Figure 1.2 shows the logical structure of the MBB's data paths. The ALU is the heart of the machine. Forming a loop with the ALU are the source and destination busses and various

registers. This loop is referred to as the "processor", and is shown in more detail in Figure 2.1. The source and destination busses are driven by "tri-state" logic; that is, the hardware selects one source of data at a time to drive them, holding the other possible sources in а neutral state. A typical microinstruction determines the ALU's two inputs, an ALU operation, and destinations for the ALU's output. The ALU's "A" input comes from one of the ALU's scratch pad registers. The ALU's "B" input comes from one of the possible inputs to the source bus. The ALU operation may be ADD, SUBtract (scratch register minus source bus), EXOR, OR, AND, PASS source bus, and NOT source bus. The ALU's output may be written to any one register driven by the destination bus; it may also be written back to the same scratch pad register which supplied the "A" input.

The data paths of the MBB are 20 bits wide. While only 16bit paths are needed for a straightforward emulation of a 16-bit machine, the only significant price paid for the extra bits is PC board space consumed by the extra data paths; the the processor's internal ICs to populate them cost very little. (In contrast, the extra bits for the ALU scratch registers and main memory are reasonably expensive, and are also easier to optionally omit.) The potential use of the extra 4 bits seems well worth the price. These bits could be used to expand the instruction set and address space of a 16-bit machine. Such an

DESTINATION BUS

Figure 1.2: MBB Logical Structure Picture 4

expansion would involve changing the emulation microcode (maintaining compatibility with existing macrocode), and probably could be performed in easy steps.

A software-controlled system status bit specifies whether the machine performs arithmetic operations (such as adding and shifting) and records ALU status based on either 16-bit or 20-bit data words.

The basic microcycle time of a 16-bit MBB is 125 nsec. If an MBB uses the full 20-bit data width, the microcycle time must be increased from 125 nsec to 135 nsec to accommodate a longer ALU carrying propagation time. To effect this change, a different crystal is used to control the system clock signal.

A microprogram counter, the UPC, controls the fetching of microinstructions from microcode memory. The UPC can be loaded from the destination bus to effect a program branch; therefore, the machine's full data computation power may be used to direct the flow of program execution. The microinstruction being executed is held in the microinstruction register (UIR) for decoding.

Microcode is contained in both PROM and RAM. PROM is readonly and non-volatile. RAM is writable, and its contents are lost on power failure. PROM code is intended for such tasks as a system bootstrap or a mini-DDT; code size is kept small, but code

speed is not an issue. For RAM code, in contrast, size is less important and speed is more important.

The ALU with its scratch registers, and the microcode memory coupled with instruction fetching and decoding, provide a basic computing capability. Further power is supplied by other major components, which we now describe.

### 1.3.2 MIR and Dispatch

A macroinstruction to be emulated may be loaded into the macroinstruction register (MIR). The MIR daughterboard (MIRDB), custom designed for each macromachine to be emulated, assists in macroinstruction decoding. Some simple, application-dependent in the MIRDB can free the microcode from hardware some cumbersome, frequently required calculations which would seriously slow the machine. The MIRDB has three principal functions:

- 1. to ease macroregister selection

- 2. to facilitate dispatching to microroutines based on the macroinstruction

- 3. to provide a specific transformation of the macroinstruction

For register selection, bits from the MIR may be used (under microinstruction control) to select the scratch pad register that feeds the ALU's "A" input. This feature is intended for

macromachines whose macroinstructions have a field specifying which of several macroregisters to use. These different macroregisters would be mirrored by a block of ALU scratch pad registers, and a macroinstruction's register specification field would automatically cause the MBB to access the corresponding microregister.

The second function of the MIRDB is to assist the microprogram in dispatching to the proper routines for emulating the various macroinstructions. Bits from the microinstruction (UIR), the macroinstruction (MIR), and the system status register (MISC) are combined in an application-dependent manner to produce a 10-bit "dispatch address". This dispatch address is not itself an address of a microcode routine; such a situation would have required a complicated MIRDB, as well as fixed routine addresses. Instead, these 10 bits address a cell in a 1K x 12-bit "dispatch memory"; this cell holds the microcode address to which to branch. A microinstruction may load this microcode address into the UPC to effect the branch. (Because of memory timing constraints, this address is loaded directly onto the destination rather than being loaded onto the source bus and passed bus through the ALU.) Dispatch memory is easily rewritten, so that locations of emulation routines need not be fixed.

Bolt Beranek and Newman Inc.

1.3.3 MAR and Main Memory

Another major MBB component is the main memory and associated logic. Main memory is intended to include the macroaddress space (containing the macroprogram's code and variables), plus an area reserved for microcode use. In general, main memory is used, as are the ALU scratch registers, for read/write data. Compared with the scratch register memory, main memory is much larger, but slower (as discussed shortly).

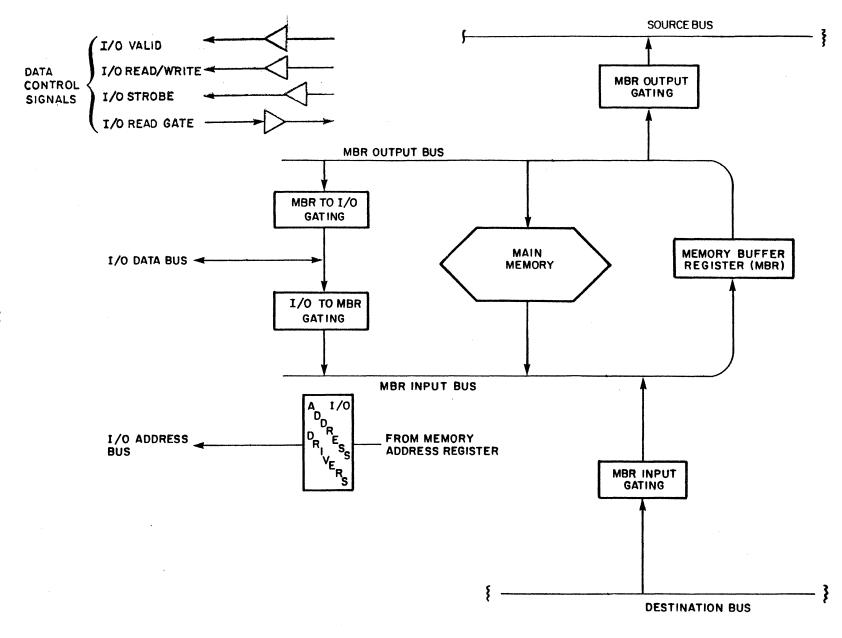

The memory address register (MAR) controls main memory access. When a microinstruction loads the MAR, certain microinstruction bits specify whether to initiate a main memory transfer, an I/O transfer, or neither; whether the transfer is a read or a write; and for main memory transfers, whether the reference is "macro" (using an address supplied by an MAR daughterboard, as explained below) or "physical" (using the address in the MAR directly).

Compared with the MBB's internal processing, the main memory access is rather slow; reading from a main memory cell takes three microcycles. The first microcycle is used to load the MAR with the address desired. The next two cycles may be used freely, except that they may not write to the MAR or to the memory buffer register (MBR). At the start of the following cycle, the contents fetched from main memory are available in the MBR. Writing to main memory proceeds similarly. The MBR must be

set up beforehand with the data to be written, the MAR is loaded to specify the memory address, and the two cycles following the MAR load may not alter the MAR or the MBR.

The main memory address selected may be passed directly from the MAR to main memory; or it may instead, under microinstruction daughterboard control, pass through an MAR (MARDB) for translation and validity checking. Main memory references which emulate macromemory references will pass through the MARDB to validity undergo address translation and checking any characteristic of the macromachine. An illegal address detected MARDB prevents any memory access and sets a status bit. by the Since valid addresses are properly translated and illegal addresses prevent access, an emulation of a macromachine memory operation cannot access the area reserved for private microcode use. This private area can only be accessed by a "physical" read or write, in which the address is passed directly from the MAR to the memory.

Like the MIRDB, the MARDB is tailored for each application; here again, a simple piece of hardware may greatly speed up emulation by freeing the microcode from some tedious, frequently required calculations.

On some machines, I/O transfer instructions look like memory reference instructions; the hardware traps references to certain addresses as really referring to certain I/O devices. To

emulate such a machine, the MARDB would treat such addresses as illegal, preventing access and setting an easily testable status bit. The microcode could then test this bit and branch to an appropriate routine.

I/O devices are read and written much like main memory. The MAR specifies an I/O address, and the MBR serves as a data buffer. I/O transfers differ from main memory transfers in two ways. First, while main memory transfers take three cycles (including the MAR load), I/O transfers take either two or four, depending on the device. Second, while for main memory the intervening cycles after the MAR load may be used rather freely, for I/O these cycles (one or three, depending on the device) must be devoted to supporting the transfer.

# 1.3.4 Other Features

Figure 2.1 shows certain other MBB features worth mentioning. To facilitate byte operations, two byte-swapped forms of the MBR are available as sources, one for 8-bit bytes, and one for 10-bit bytes. The MBR was chosen because many of the byte operations desired will probably deal with data bytes read from main memory or I/O devices. To support shift operations, the MAR and MBR form a double-length shift register; one microinstruction may shift their contents right or left one bit (end off, 0 shifted in). We decided not to add more shifting

hardware to handle multiple-position shifts and different shift types (rotate, arithmetic). Such hardware, while it would have speeded emulation of shifts for some machines, seemed too specialized and thus not worth the cost. The microcode, aided by our simple shift hardware, assumes the burden of emulating the various types of shift instructions.

Bolt Beranek and Newman Inc.

#### 2 PROCESSOR

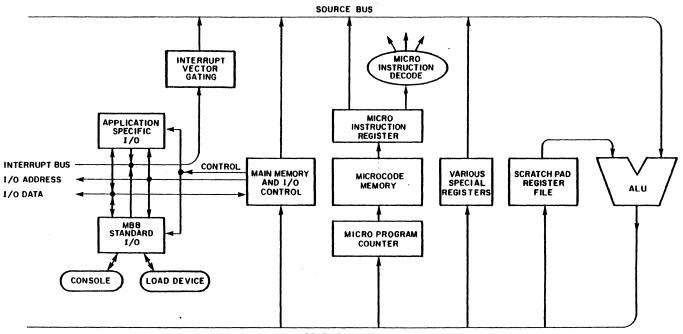

Now that we have had an overview of the processor structure, (we can examine the pieces of the MBB in more detail (see Figure 2.1).

Bits in registers and on busses are numbered starting from 0, the low order bit. All numbers are decimal, unless otherwise specified.

### 2.1 Basic Data Flow

Data flow centers around the Arithmetic Logic Unit (ALU). The ALU has two inputs. Its "A" input is from a scratch pad register file (1024 words \* 20 bits). Its B input is from a 20bit "source bus". All drivers of the source bus, plus Dispatch memory, are called "sources". A 20-bit "destination bus" is driven by the ALU's output (or Dispatch memory, see below). All registers which can be driven from the destination bus, except the ALU's scratch pad registers, are called "destinations".

Selecting the ALU's two inputs, performing an arithmetic or logic operation, and storing the result are the main events in a microcycle. A microinstruction specifies a source to drive the B input, a scratch pad register to drive the A input, an ALU operation, and a single destination to receive the output. (If Dispatch memory is the source, it drives the destination bus

21

Bolt

directly, and the ALU is not used.) The ALU's output may optionally be written back to the same scratch pad register which fed the A input.

Some sources are less than 20 bits wide. When they are read onto the source bus, the bus is padded with high order 0's. When registers less than 20 bits wide are written from the destination bus, the high order bits on the bus are ignored.

The seven available ALU operations are:

ADD SUBTRACT (scratch register minus source bus) AND Inclusive OR Exclusive OR PASS source bus NOT source bus (bitwise complement)

The eighth possible ALU operation is undefined. The ALU is combinatorial only; it has no storage. To pass a scratch pad register, the assembler uses the ADD operation with a constant of 0 driving the source bus; we may think of passing a scratch register as an available "operation".

2.2 Register Selection

There are 1024 registers; only 32 are accessible at any given time. Sixteen global registers are always accessible; a "window" of 16 registers is movable within the 1K address space

depending on the contents of a register called BASE. Registers may also be selected on the basis of the contents of MIR. In detail:

A five-bit microinstruction field selects the scratch pad register for the ALU's input. Let R be the field's value. For R = 0 through 15, the contents of the 10-bit BASE register determines the window of addresses available; BASE is inclusive ORed with R to select the desired register. (This inclusive OR function allows several uses of BASE. If BASE is a multiple of 16, then the local register block is a full sized 16 register With the appropriate choice for BASE, the local register block. block can be half, quarter or eighth sized. If local register 0 is selected, then BASE serves as a direct 10 bit address into the register file.) The set of registers addressable at any moment with R = 0 through 15 is called the current "local register" block". Registers 0-13, the "global" registers, are always accessible, using R = 16 through 29. For R = 30 or 31, BASE again sets the window; the particular register in the local block is determined by the Macroinstruction Register daughterboard in an application-dependent manner. Two (MIRDB) different registers may be selected using R = 30 and R = 31. Register addresses supplied by the MIR are also ORed with the contents of BASE, so the registers are always within the current "local" block. The MIR may not be used for register selection on any cycle immediately following a load of the MIR.

In summary, the register address is determined as follows:

| <u>value of R</u> | regi        | ster      |

|-------------------|-------------|-----------|

| 0-15              | R! {BASE}   | (locals)  |

| 16-29             | R-16        | (globals) |

| 30,31             | MIR functio | n}!{BASE} |

If BASE is loaded from the destination bus in cycle N, its new value takes effect for register selection in cycle N+1. The value of BASE when referenced as a source, however, does not change until cycle N+2. This special one cycle delay permits the old value of BASE to be saved in the new local register block.

# 2.3 ALU Status

Each microinstruction may optionally latch the ALU status. If the microinstruction specifies latching, the following ALU bits and conditions are latched into the ALU Status Register (ALUST):

> high bit of A input high bit of B input high bit of output low bit of output ALU result zero carry

The "high" bits are bit 19 or 15, depending on whether the machine's data width mode specifies 20 or 16 bits respectively. The "ALU result zero" status bit is set when the ALU result is zero; in 16-bit mode, only the low 16 bits matter. The carry,

also dependent on the data width mode, reflects the traditional "carry-out" on addition, and the complement of "borrow-in" on subtraction; the "carry" status bit is set as follows on addition and subtraction:

| high bit of A input                       | 1 | 1      | 1 | 1      | 0 | 0      | 0      | 0      |

|-------------------------------------------|---|--------|---|--------|---|--------|--------|--------|

| high bit of B input                       | 1 | 1      | 0 | 0      | 1 | 1      | 0      | 0      |

| high bit of output                        | 1 | 0      | 1 | 0      | 1 | 0      | 1      | 0      |

| carry on addition<br>carry on subtraction |   | 1<br>1 | - | 1<br>1 | - | 1<br>0 | 0<br>0 | 0<br>1 |

The "carry" bit for other operations is meaningless.

These ALU status bits provide primitives for computing various status bits set by arithmetic and logical operations in a macromachine. In emulating macromachine operations which set status bits, the microcode would latch the ALU status on the appropriate microcode operation and then save the value of ALUST in a register or in main memory. If later the macromachines's status bits must then be tested, the saved value of ALUST can be decoded.

### 2.4 Program Control

Program execution is controlled by the Microcode Program Counter (UPC) and the Microinstruction Register (UIR). The UIR holds the instruction being executed, while the UPC holds the address of the instruction being fetched into the UIR for

execution during the next cycle. In detail, suppose the UPC has value X at the start of microcycle M. During cycle M, the microcode instruction at address X is fetched into the UIR. Then during cycle M + 1, this instruction is decoded and executed.

The hardware normally increments the UPC at the start of each cycle, so that sequential instructions are fetched and executed. To effect a program branch, however, the microcode can load the UPC as a destination. (When the microcode specifies loading the UPC, actually both the UPC and another register, RAMADDR, are loaded. Section 2.10 explains RAMADDR.) Because microinstruction fetching is pipelined as described above, the transfer of control takes two cycles: on the second cycle following the UPC load, the instruction at the new address will be executed. To clarify, suppose that in cycle M the machine executes a microinstruction at address X which loads Y into the UPC. The following table then gives the contents of the UPC and UIR at the beginning of cycles M, M+1, and M+2:

| M+1 Y instruction at X+1 | Cycle | <u>UPC</u> | UIR                                                                   |

|--------------------------|-------|------------|-----------------------------------------------------------------------|

|                          | M+1   | Ŷ          | instruction at X (Y -> UPC)<br>instruction at X+1<br>instruction at Y |

----

The intervening instruction at X+1, executed before control transfers to address Y, may be any otherwise legal microinstruction, including another transfer of control. In the above example, if the instruction at X+1 transfers control to

address Z, the machine behaves as follows:

| Cycle      | UPC      | UIR                                                          |

|------------|----------|--------------------------------------------------------------|

| M<br>M+1   | X+1<br>V | instruction at X (Y -> UPC)<br>instruction at X+1 (Z -> UPC) |

| M+1<br>M+2 | Z        | instruction at Y                                             |

| M+3        | Z+1      | instruction at Z                                             |

If further Z = X+2, then the code has spliced an execution of the statement at Y into an otherwise sequential execution sequence.

Because the UPC may be loaded as a destination, the full data computation power of the machine is available for computing transfers of control.

Execution must never "fall through" from the lower 8K addresses to the upper 8K; Section 2.10 explains why.

### 2.5 Conditional Execution

Every microinstruction has a field for conditional execution. The following conditions are available:

always true} ALU status: result zero ALU status: result odd (low bit on) ALU status: result negative (high bit on) interrupt pending mode flag 0 on MAR condition

The ALU status conditions refer to the appropriate bits in the ALU Status Register. The "interrupt pending" condition is true

if a microinterrupt request (Section 5) other than the programmable request is pending, and may change at any time. Mode flag 0, controlled by the application software, is a bit in the MISC register. The MAR condition is determined by the application-dependent MAR daughterboard.

The microinstruction may specify execution either when the selected condition is true or when it is false. By selecting the "always true" condition the instruction may specify either unconditional execution or unconditional non-execution.

When non-execution is specified, ALU performs the indicated operation on the indicated inputs, but the result goes nowhere: the hardware prevents writing to any destination or ALU scratch register, and also prevents latching the ALU status in ALUST.

Conditional execution is useful not only for program jumps but also for in-line execution.

# 2.6 Constants

The microinstruction may specify an explicit constant value to drive the source bus. Because the microinstruction field which specifies the constant is kept to a reasonable size, not all 20-bit constants may be specified. The instruction may specify any one of three 8-bit fields and can then choose only all 0's or all 1's for the other bits. The three fields are:

#### Bolt Beranek and Newman Inc.

bits 0-7 (right), bits 8-15 (middle), and bits 12-19 (left). In addition to these six possibilities, the instruction may specify an "extended constant". In this case, bits 0-13 may be set as desired and the other bits are 0. Since the microcode address space only has 14 bits (16K words), loading an extended constant into the UPC can effect a program branch to any microcode address. When an extended constant is used, the ALU always does a PASS operation.

The assembler automatically encodes permitted constants into one of these seven forms, flagging illegal constants.

Any 20-bit constant C can be built in at most three cycles. Let

> C1 = C AND 377 C2 = C AND 177400C3 = C AND 3600000

and let R be an ALU scratch pad register. Then the instruction sequence

load C1 into R load (C2 OR R) into R load (C3 OR R) into ...

provides constant C.

Bolt Beranek and Newman Inc.

2.7 Certain Coding Awkwardnesses

It is not possible to copy one scratch pad register to another, or to perform an ALU operation involving two scratch pad registers in a single microinstruction. Such operations take two cycles, requiring a register for temporary storage which is both a source and a destination. TEMP is often used for this purpose. Let R and S be registers. To copy the contents of R into S:

> load R into TEMP load TEMP into S

To add the contents of R and S:

load R into TEMP

load (S PLUS TEMP) into...

It is also not possible to combine two sources in a single microcycle. Such a combination takes two cycles, requiring a scratch pad register for temporary storage. For example, to add MIR to TEMP, a scratch pad register R is used as follows:

> load MIR into R load (TEMP PLUS R) into...

It is possible to subtract a source from a scratch pad register in one cycle, but not vice versa. To subtract a register R from a source S various techniques are possible, depending on where the result must go, whether R and S may be overwritten, and what constants are available in registers. For example, if the constant 0 is in some scratch pad register 2, and

the result is to go to some register D (possibly S itself) which is both a source and a destination, the following two-cycle sequence works:

> load (R MINUS S) into D load (Z MINUS D) into D

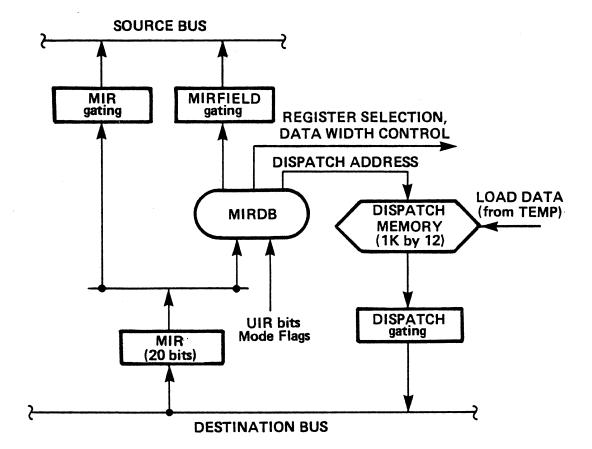

# 2.8 MIR Daughterboard and Dispatch Memory

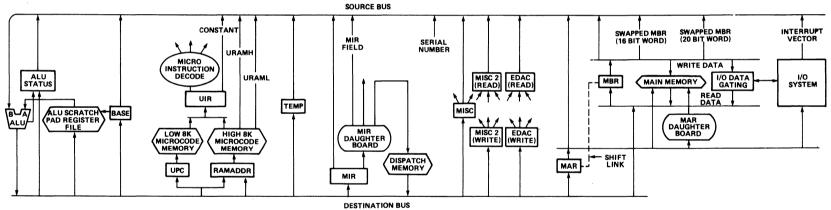

The Macroinstruction Register (MIR) is designed to hold macroinstructions. An application-dependent MIR daughterboard (MIRDB) helps to interpret the macroinstruction held in the MIR (see Figure 2.2).

The MIRDB can free the software from some cumbersome, frequently required calculations. As inputs to its computations, the MIRDB has: the 20 MIR bits, the four Mode Flags in MISC, and the microinstruction's eight-bit constant field.

The MIRDB has four functions. First, it provides a source, MIRFIELD, which is usually a modified form of the MIR. In emulating the SUE or PDP-11, for example, a good use for MIRFIELD might be to provide displacements on branch instructions. These machines compute the displacements by sign extending the low order byte and then shifting left one bit. In emulating these machines, performing such a calculation in software on every branch instruction would be tedious; some simple logic in the

# Figure 2.2: The MIRDB and Dispatch Memory Picture 6

MIRDB, however, could provide the displacement in MIRFIELD.

Second, the MIRDB, under microcode control, can select ALU Values scratch pad registers. of 30 and 31 in the microinstruction's Register field indicate register selection by the MIRDB; the daughterboard generates two four-bit fields, corresponding to register values 30 and 31. When one of these two registers is selected, the register address supplied by the MIRDB is inclusive ORed with the contents of BASE to determine a scratch pad register address. This feature is useful for emulating macromachines whose instructions have fields specifying several macroregisters to use (such as index registers which of The macroregisters would be mirrored in a or accumulators). block of ALU scratch pad registers, and the macroinstruction's macroregister selection field would be used by the MIRDB to determine the corresponding ALU scratch pad register address. The application specific MIRDB helps solve the problem that these register fields are in different bit positions in different processors' instruction sets. The register selection function is and should be relatively efficient. performed frequently, Because of timing constraints, the MIR must not be used to select a register in the cycle immediately following an MIR load.

Third, the MIRDB can control the machine's data width mode (16 or 20 bits). This control is enabled when the DWIDTHCTRL bit in the MISC register is on. This feature might be useful for

simultaneously emulating the instruction sets of a 16-bit machine and a 20-bit machine, or for providing an extension to the instruction set and memory of a 16-bit machine.

Fourth, the MIRDB, together with Dispatch memory, permits easy dispatching to the proper microcode routine to emulate different macroinstructions. When a microinstruction selects Dispatch as a source, the daughterboard calculates a 10-bit address. Dispatch memory is then interrogated at this address; the contents read are passed directly to the destination bus, and may be loaded into the UPC to effect a program branch.

The address computed depends on the contents of the MIR, the microinstruction's Constant field, and the Mode Flags in MISC. The MIRDB can let the microcode dispatch to an emulation routine which depends on the macroinstruction (MIR contents). Further, the microinstruction's Constant field lets the microcode specify different kinds of dispatches. For example, a macroinstruction's first dispatch might take all memory reference instructions to a routine to calculate the effective address; memory common reference instructions may then dispatch again, this time to separate routines to perform the indicated operation. The Mode Flags in MISC could reflect macromachine state bits which affect microcode could then macroinstruction interpretation; the dispatch to different macroinstruction emulation routines as In the H316 emulation, for example, Mode Flag 0 appropriate.

gives the addressing mode ("normal" or "extended"), and the instructions JST, STA, IMA, and IRS have different emulation routines depending on the flag.

Dispatch memory is 1024 words by 12 bits. Its contents drive the destination bus directly because there is not enough time to send them through the ALU. The 12-bit value fetched from Dispatch memory is right justified in the destination bus. The MIRDB can specify the next two bits, allowing the memory values, when interpreted as microcode addresses, to reach all locations in the microcode address space.

Dispatch memory is itself loadable, permitting easy 👘 relocation of instruction emulation routines. Dispatch loading is enabled only when the LOADDISP bit in MISC is on. As long as the LOADDISP bit is on, any microinstruction which references an "odd" ALU scratch pad register (see next paragraph) risks loading a Dispatch location (even if it specifies conditional execution with a condition not satisfied); otherwise, the LOADDISP bit does not affect machine behavior. The low 12 bits of TEMP specify the data contents to be loaded. The MIR, the Mode Flags, and the microinstruction's Constants field specify the address to be loaded, in the same way that they specify the address to be read when Dispatch is selected as a source. To load a location, execute three microinstructions in a row. The first and third must reference an "even" register and the second must reference

#### Bolt Beranek and Newman Inc.

an "odd" register (see next paragraph). All three instructions must have the appropriate Constants field. Otherwise, these three instructions may be freely specified. (They may even specify conditional execution with a condition not satisfied.)

Every microinstruction specifies an ALU scratch pad register address in its Register field. We say that the instruction references an "even" or "odd" register according to whether the register address specified, <u>before any mapping by BASE</u>, is even or odd. Usually, bit 11 in the microinstruction (the low order bit of the Register Number subfield) determines this evenness or oddness: 0 for even, 1 for odd. However, if the Register field has value 30 or 31, specifying register selection by the MIR daughterboard, then the crucial bit is the low order bit of the four-bit field generated by the MIR daughterboard: again, 0 for even and 1 for odd.

To simplify loading, the MIR daughterboard should permit one value of the microinstruction's Constant field to specify a "transparent" mapping, in which the MIR's low 10 bits give the Dispatch address. By convention, a Constant field value of 0 will specify this transparent mapping. The current system software assumes this convention in the DDT code to examine and change Dispatch memory.

Bolt Beranek and Newman Inc.

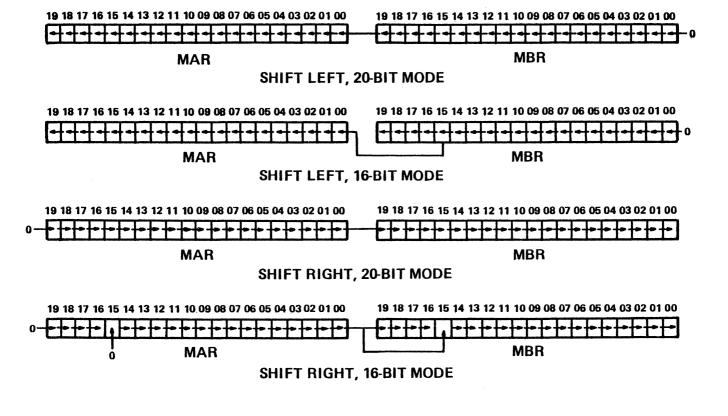

# 2.9 Shifting

The MAR and MBR form a double precision shift register, with the MAR on the left (high order). When the MAR is referenced as a source, the low two bits of the microinstruction's Constant field specify a shift operation:

00 no shift

01 shift right one bit

10 shift left one bit

11 undefined

Independent of the operation specified, the value of the MAR before shifting is loaded onto the source bus. The MAR and MBR shift only one bit per microinstruction, and 0 is shifted into the vacated bit; the burden of more complicated shift operations is on the microcode.

As shown in Figure 2.3, shifting respects the data width mode. In 20-bit mode, the MAR and MBR act as two 20-bit registers; in 16-bit mode, the MAR and MBR act as two 16-bit registers. Actually, the only difference is in driving MAR00 (bit 0 of the MAR) on left shifts, and in driving MAR15 and MBR15 on right shifts. In 16-bit mode, the top 4 bits of the MAR and MBR themselves shift, though they do not drive any other bits.

Figure 2.3: Shifting Picture 7 2.10 Loading and Reading Microcode

The upper 8K of the 16K microcode address space may be loaded by the microcode, provided that the physical memory itself is loadable (RAM rather than PROM). To load the upper 8K, the program must be executing in the lower 8K. The low 16 bits of TEMP contains the contents to be loaded, and the 14-bit register RAMADDR (located on the microcode daughterboard) must contain the address to be loaded. Writing a l into the M2.LOADUH bit of MISC2 loads the high 16 bits of the microcode word; writing a 1 into the M2.LOADUL bit loads the low 16 bits. (Writing both of these bits at once loads both halves of the microcode word, each with the same contents.) If the bit is written in cycle m, then in cycle m+1 the memory's contents are indeterminate; by cycle m+2 the new contents are present. Further, cycle m+1 must not change the value of TEMP or RAMADDR.

Between writing the load address to RAMADDR and loading the microcode, the program must not load the UPC. (This restriction extends through the cycle after writing M2.LOADUH or M2.LOADUL.)

RAMADDR must not be loaded while executing in the upper 8K of the microcode address space. Further, the program must never "fall through" to the upper 8K of memory; any entry to the upper 8K must be by an explicit load of the UPC.

The hardware structure that imposes these restrictions is as follows. There are two 14-bit registers, UPC and RAMADDR. Specifying UPC as a destination loads both; specifying RAMADDR as a destination loads only RAMADDR. The high bit of UPC determines whether to fetch an instruction from the lower or upper 8K. If the lower half is used, the low 13 bits of the UPC give the rest of the address; if the upper half is used, the low 13 bits of RAMADDR give the rest of the address. Execution in the upper 8K increments both UPC and RAMADDR; execution in the lower 8K increments only UPC. When executing in the lower half, RAMADDR, not being incremented, is free to be used for specifying a address. The M2.LOADUH and M2.LOADUL bits enable loading loading, which takes two cycles. Since loading the UPC would overwrite any load address in RAMADDR, loading the UPC must be avoided during microcode loading. Execution must never "fall through" to the upper 8K since RAMADDR would not be in step with the UPC.

The microcode parity bit must be explicitly loaded as desired (to give the word odd parity), as part of the low 16 bits. The hardware does not generate parity.

Reading microcode memory also uses RAMADDR. Only the upper 8K may be read, and the reading must be executed in the lower 8K. If RAMADDR contains address x at the start of cycles m and m+1, then in cycle m+1 the sources URAMH and URAML yield the contents

of the high and low 16 bits, respectively, of the location at address x. Thus, the standard reading sequence is: load RAMADDR, wait one cycle, and read URAMH or URAML (or one after the other).

# 2.11 Miscellaneous Features

To ease byte operations, two byte-swapped forms of the MBR (called S16MBR and S20MBR) are available as sources. When S16MBR is specified, the low 8 bits are exchanged with the middle 8 bits (the order within each byte staying the same); the top 4 bits stay in place. When S20MBR is specified, the low 10 bits are exchanged with the high 10 bits. The MBR was chosen because it is a read/write register which serves as a data buffer for main memory and I/O operations, and desired byte operations will likely deal with data transferred to or from main memory or I/O devices.

A "serial number" source yields a fixed 16-bit constant. The low order 12 bits, determined by cuts in PC board etchings, hold the machine's unique serial number. The high order 4 bits, determined by solder wire jumpers on the PC boards, represent the assembly revision level of the machine.

Bolt Beranek and Newman Inc.

# 2.12 Handling Exceptional Conditions

On detecting various exceptional conditions, the hardware traps microcode execution to address 0. The PROM memory starting at address 0 should have an appropriate handler. The conditions detected include new power, microcode parity error, uncorrectable main memory error, and button pushed.

When power is restored, the hardware forces execution to address 0 and holds it there for roughly a half second to let the hardware settle.

Microinstructions should have odd parity. When an instruction with even parity is fetched, the hardware detects an error and signals for a trap to address 0. Subject to the caveat below on trap multiplexing, the trap is timed so that execution branches to 0 after the instruction following the instruction with the bad parity.

If the main memory Error Detection and Correction (EDAC) option is present, the hardware senses certain uncorrectable errors in main memory (Section 4). If EDAC trapping is enabled, the EDAC logic will then signal for a trap to address 0. Subject to the caveat below on trap multiplexing, the trap is timed so that execution branches to 0 after the second cycle in which the fetched value is available. (Section 3 discusses memory access timing, including when fetched values becomes available.)

A manual push-button is located on the processor card. When the button is pushed, the hardware signals for a trap to address 0. This is used to unilaterally enter the microcode DDT.

The conditions of microcode parity error, uncorrectable main memory error, and button being pushed are actually multiplexed to one trap generator. The trap is generated by the rising edge of inclusive OR of the microcode parity error condition, the the main memory error condition, and the button being pushed. The microcode parity error and main memory error conditions are asserted for only one microcycle on each error, but the button condition is asserted as long as the button is pushed; as long as the button remains pushed, microcode parity errors and main memory errors cannot cause traps. The trap's mechanism is to force the microprogram counter to 0 for several cycles. (The power-up trap uses the same mechanism, but it forces the microprogram counter to 0 for much longer.)

Various status bits let the handler at address 0 determine what conditions have occurred. A bit in register MISC2 reflects whether the button is being pushed; other bits in MISC2 are latched upon new power, a microcode parity error, and an uncorrectable main memory error.

### 3 MAIN MEMORY

Main memory, like the ALU scratch pad register file, holds read/write data. Compared with the ALU register file, main memory is much larger but somewhat slower. Main memory is intended to contain the macromachine's address space, holding the macromachine's program and data. Main memory may also store information for the microcode's private use.

Main memory is implemented with dynamic RAMs. These are much larger than the static RAMs used elsewhere in the MBB, and have a much longer access time. Dynamic RAMs have special constraints which must be accommodated by the microcode, such as refreshing and power up "priming". These are discussed later.

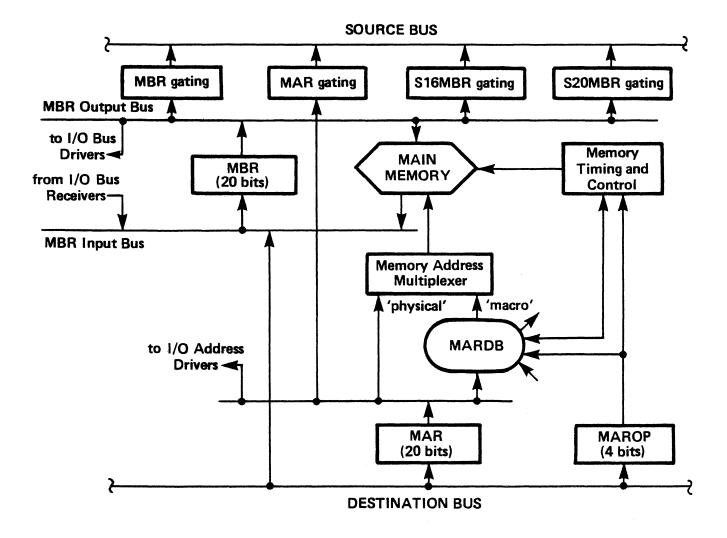

The Memory Buffer Register (MBR) buffers data, and the Memory Address Register (MAR) specifies the memory address (see Figure 3.1). Whenever the MAR is loaded, a four-bit transfer field is latched into an auxiliary "memory operation" register (called MAROP). The value latched specifies whether or not to initiate a memory or I/O transfer and, if so, whether to read or write and whether to use "physical" or "macro" access (discussed below).

Figure 3.1 Main Memory Address and Data Paths Picture 8

Report No. 4268

Bolt Beranek and Newman Inc.

3.1 Read and Write Paradigms

By convention, cycles are numbered starting with the cycle after the MAR load. The read paradigm for a "physical" memory access is as follows:

|     | load address  | in MAR (Transfer  | code  | says "read" | ) |

|-----|---------------|-------------------|-------|-------------|---|

| [1] | don't change  | MAR, MBR unchang  | ed    | -           |   |

| [2] | don't change  | MAR, MBR unchang  | ed    |             |   |

| [3] | memory conter | nts in MBR, MAR m | ay be | changed     |   |

Cycles [1] and [2] may be used freely, provided the MAR is unchanged. In cycles [1] and [2], the MBR retains its old contents. In cycle [3], the MBR contains the fetched memory contents, and the MAR may be loaded to initiate another memory operation.

The write paradigm for a "physical" memory access is as follows:

load contents into MBR

...

load address into MAR (transfer code says "write")

[1] don't change MAR or MBR

[2] don't change MAR or MBR

[3] main memory has been changed

Again, cycles [1] and [2] may be used freely except to write the MAR or MBR, and cycle [3] may start a new transfer. Any number of cycles may intervene between the MBR load and the MAR load.

Bolt Beranek and Newman Inc.

# 3.2 Memory Timing

Main memory transfers take more than a single microcycle. When nested as closely as possible, transfers in general take N cycles each; with the current hardware, N is 3. To change the paradigm to fit a memory where N is greater than 3,\* simply expand cycles [1] and [2] into N-1 cycles, with the same constraints The fetched contents on reads are then available in on each one. general case, an uncorrectable main memory cycle [N]. In the error detected by the optional Error Detection and Correction (EDAC) logic will trap to execute at microcode address 0 during cycle [N+2]. Section 2.12 discusses traps to address 0, and Section 4 discusses EDAC.

#### 3.3 Memory Access Modes

On each read and write, the transfer code latched into MAROP specifies an access mode. Access may be "physical" or "macro". For a "physical" access, the address is passed directly to the memory from the MAR. For a "macro" access, the address is obtained from the application-dependent MAR daughterboard (MARDB), as shown in Figure 3.1. The daughterboard may perform memory address translation, either simple schemes (like byte-

<sup>\*</sup>For example, the overhead of the UNIX memory management MARDB adds one microcyle to every "macro" main memory access; here N is 4.

word) or full scale memory mapping. Further, the MARDB may treat some values in the MAR as specifying illegal addresses, and prevent any memory operation from occurring. In addition, the MARDB can control a condition MARCOND, which the microcode can test with conditional execution (Section 2.5).

The "physical" access is intended for handling the microcode's private data area, while the "macro" access is intended for emulating a macromachine's memory operations. The MAR daughterboard can emulate the macromachine's memory mapping, and can ensure that macromachine operations never reference the microcode's reserved area of main memory. As input for its decisions, the MARDB has the 20 MAR bits, the four MAROP bits, and the four Mode Flags in MISC. (In the H316 emulation, one Mode Flag bit indicates "normal" or "extended" addressing mode, and a second bit indicates "upper" or "lower" bank if in "normal" mode; the MAR daughterboard uses both flags.)

In some machines (such as the SUE), the same instruction codes reference memory and I/O devices; some addresses simply point to I/O devices rather than to actual memory. To emulate such a machine, memory reference macroinstructions must be handled differently depending on the address. The MAR daughterboard could help by setting the MARCOND condition according to whether the address loaded in the MAR indicates memory or I/O. (Presumably the MARDB would also prevent main

memory access if the address indicated I/O.)

By providing some basic application-dependent hardware capabilities, the MAR daughterboard can free the microcode from common, tedious calculations.

# 3.4 Special Considerations

Main memory uses dynamic RAMs, which must be periodically "refreshed" to maintain their contents. For the MBB, this refreshing consists of reading the memory. The scope of reading needed depends on the chip size. If a chip contains 2N bits of addressing, the low N bits are called the "row" bits and the high N bits are called the "column" bits. For every combination of row bits, that combination must occur in a main memory read at least every 2 milliseconds. Currently 16K (14-bit address) RAMs are used, so there are 2\*\*7 (128) reads to perform. (The total number of chips used does not matter, since all chips are refreshed in parallel.)

After power-up, the dynamic RAMs must be accessed (either read or written) a minimum of eight times before they will function properly. This "priming" of main memory is done automatically by the system PROM microcode.

4 MAIN MEMORY ERROR DETECTION AND CORRECTION (EDAC)

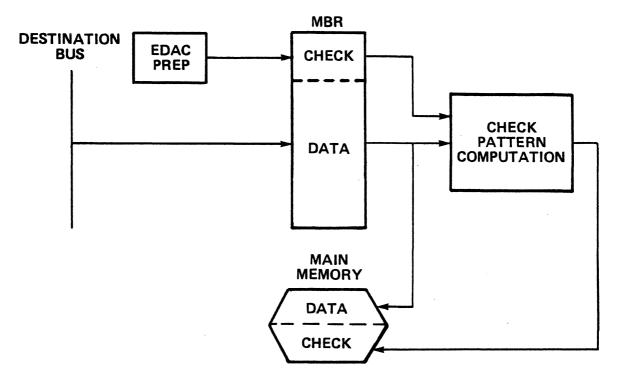

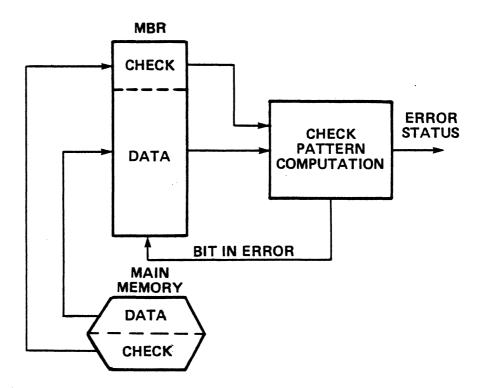

The MBB uses dynamic semiconductor memory devices for its Because these devices may give occasional bit main memory. errors, the MBB provides special error detection and correction logic (EDAC) as an option. If the EDAC option is present, main memory and the MBR are 26 instead of 20 bits wide. The extra 6 bits, called "check" or "syndrome" bits, provide redundant information used to detect and correct bit errors. A11 single bit errors can be corrected; all double bit errors can be detected; errors in more than two bits are generally either not improperly corrected. We first describe detected the or algorithm used to detect and correct errors, and prove the algorithm's correctness; we then explain how EDAC is integrated into the MBB. Figure 4.1 summarizes EDAC data paths and operation.

4.1 The EDAC Data Paths

Both main memory and the MBR are 26 bits wide: 20 data bits, plus 6 check bits. When a word is written from the MBR to memory or read from memory to the MBR, the data bits are passed without change.

When a word is written from the MBR into memory, a 6-bit "write check pattern" is computed and stored in the memory

# WRITE ACCESS

Figure 4.1: EDAC Data Paths Picture 9

#### Report No. 4268

#### Bolt Beranek and Newman Inc.

location's check bits. When a word is read from memory into the MBR, the memory's check bits are copied into the MBR; a 6-bit "read check pattern" is then computed to detect and correct bit errors. Both the write check pattern and the read check pattern are functions (described below) of the 26 bits in the MBR; essentially the same logic is used to compute the two patterns.

# 4.2 The EDAC Algorithm

Two "boundary conditions" are assumed for memory use: no memory word is read without having first been written, and before a write the MBR's check bits all have value 1. In this section these conditions will enter our proof at peripheral points; in the next section their "physical meaning" will be discussed.

The check bits' values in the MBR and memory, as well as the read and write check patterns, can be represented 6-bit strings such as "OllIII". From left to right, these bits will be called the "parity" bit P and the "syndrome" bits S4, S3, S2, S1, and S0. The data bits in the MBR and memory are labeled D19 through D00 (D00 is the low order bit). Lower case p and s denote bit values while upper case P and S denote the bits themselves.

The check pattern computation functions can be determined from Table 4.1. Each column is associated with a certain check

Bolt Beranek and Newman Inc.

Report No. 4268

bit, and each row is associated with a certain check or data bit in the MBR (or is "unused"). For any check bit R, define c(R) (the set of bits "covered" by R) as the set of check and data bits B such that the entry in R's column and B's row is an "\*". Define c'(R) to be just the data bits in c(R). Thus, for example, c(P) is the set of all 26 bits, since P's column contains all \*'s; and c'(P) is the set of all data bits.

| Ρ | S4  | S3 | S2     | Sl     | S0     |            |

|---|-----|----|--------|--------|--------|------------|

| * | _   | _  | _      | _      | _      | Р          |

| * | _   |    | _      |        | *      | S0         |

| * |     | _  | _      | *      | _      | 50<br>S1   |

| * |     |    | _      | *      | *      | unused     |

| * | _   | _  | *      | _      | _      | S2         |

| * | _   | _  | *      | _      | *      | unused     |

| * | _   | _  | *      | *      | _      | unused     |

| * | _   | _  | *      | *      | *      | unused     |

| * | _   | *  | _      | _      | -      | S3         |

| * | _   | *  | _      | _      | *      | unused     |

| * |     | *  |        | *      | _      | unused     |

| * | _   | *  | _      | *      | *      | D19        |

| * | _   | *  | *      | · ·    | _      | D19<br>D18 |

| * | _   | *  | *      | _      | *      | D17        |

| * | _   | *  | *      | *      | _      | D16        |

| * | _   | *  | *      | *      | *      | D10<br>D15 |

| * | *   | _  | _      | _      |        | S4         |

| * | *   | _  | _      | _      | *      | D14        |

| * | *   |    | _      | *      |        | D14<br>D13 |

| * | *   | _  | _      | *      | *      | D13<br>D12 |

| * | · * |    | *      |        |        | D12<br>D11 |

| * | *   |    | *      |        | *      | D11<br>D10 |

| * | *   | -  | *      | *      |        | D10<br>D09 |

| * | *   | -  | *      | *      | *      | D09<br>D08 |

| * | *   | *  | ~      | ~      |        | D08<br>D07 |

| * | *   | *  |        | -      | *      | D07<br>D06 |

| * | *   | *  |        | *      |        | D06<br>D05 |

| * | *   | *  |        | *      | -<br>* |            |

| * | *   | *  | -<br>* | n      | ~      | D04        |

| * | *   | *  | *      | -      | -<br>* | D03        |

| * | *   | *  | *      | -<br>* | ^      | D02        |

|   |     |    |        |        | -      | D01        |

| * | *   | *  | *      | *      | *      | D00        |

Table 4.1: EDAC Check Bit Computation

The check bits are computed in the same way for the read and write check patterns. The value for a check bit Sn (n=0,1,2,3,4) in the check pattern is the complement of the EXOR of the values in the MBR of all bits in c(Sn).

Similarly, the value for P in a read check pattern is the complement of the EXOR of the values in the MBR of all bits in c(P). The value for P in the write check pattern, however, is the EXOR of the value of P in the MBR, the values of the bits in c'(P) in the MBR, and the values of the check bits in the write check pattern itself.

Since c(P) includes all 26 bits and P has value 1 in the MBR before a write, we can restate the computation of P in the check patterns as follows. In the write check pattern, P gives the word written (data plus check bits) an odd parity. In the read check pattern, P reflects the parity of the word read: 1 for even parity, 0 for odd parity.

We will study first the check patterns generated according to these rules. Later we will analyze the effect of hardware errors.

We will show that, if a word is written into memory and then read back without error, the read check pattern is always Olllll. Let p, s4, s3, s2, s1, and s0 be the values of the bits in the read check pattern; let p', s4', s3', s2', s1' and s0' be the values of the bits in the write check pattern (which are stored in memory during the write); and let p", s4", s3", s2", s1", and s0" be the values of the check bits in the MBR before the write. (p", s4", s3", s2", s1", and s0" are normally 1's, but we defer using this assumption in order to make our result

more general for later use. Since all data bits have the same value throughout the transfer, we need not define separate symbols for their values before the write, after the write, and after the read.) If a and b are bit values, let a \* b denote a EXOR b and let a denote the complement of a; if A is a set of bits, let \*A denote the EXOR of the values of all bits in A.

We can express succinctly with equations the rules given above in prose for calculating the read and write check patterns. The read check pattern is computed from values in memory as follows:

(1) p = ((\*c'(P)) \* p' \* s0' \* S1' \* s2' \* s3' \* s4')(2) sn = (\*c'(Sn) \* sn').

(We use n to stand for 0, 1, 2, 3 or 4. Thus, the second equation is really five equations, one for each check bit. Equation (2) holds because Sn covers itself but no other check bit; equation (1) holds because P covers every check bit.) The write check pattern is computed from the values in the MBR as follows:

(3) p' = (\*c'(P)) \* p" \* s0' \* s1' \* s2' \* s3' \* s4'

(4) sn' = ((\*c'(Sn)) \* sn").

We can substitute (3) and (4) into (1) and (2) to yield the read check pattern values as functions of the original values in the MBR. Substituting (3) into (1) yields

Report No. 4268

Bolt Beranek and Newman Inc.

(5) p = (p")

and substituting (4) into (2) yields

(6) sn = sn''.

Thus, the read check pattern depends only on the initial check bit values in the MBR, not on the data bits. We are assuming an initial pattern of 111111; (5) and (6) thus yield a read check pattern of 011111.

So far, we have shown that an error-free "round trip transfer" from MBR to memory and back to MBR yields the read check pattern Olllll. We will now examine the read check patterns caused by various hardware errors.

Our model of a hardware error is that in memory, between the write and the read, one or more bits change value. P's behavior on errors is easy to analyze. P in the read check pattern reflects the parity of the word read. In the absence of errors, P in the read check pattern is 0, reflecting the memory word's correct odd parity. In general, P in the read check pattern reflects the number of bits in error in memory: P is 0 if the number of errors is even (including none), and 1 if the number of errors is odd.

Having completely analyzed P's behavior with errors, we now consider that of the check bits. If only one bit in memory is in

error, just those check bits which cover the erroneous bit will appear as 0 in the read check pattern instead of the normal 1. For example, if D19 is in error, since just S3, S1, and S0 of the check bits cover D19, the check bits will appear as 10100 in the read check pattern. From this example, we see that the bit in error can be read from Table 4.2 by matching the parity and check bits in the read check pattern. (The EDAC.BANK field of the EDAC register must be examined to uniquely determine the failing memory chip.)

If exactly two bits are in error, then, since the two bits cannot be covered by exactly the same syndrome bits, the syndrome bits in the error pattern will not be lllll.

We can summarize the read check patterns for zero, one, and two errors:

| Read Check                                                                                                | Bit in                                                                                                                                                                                                               | Physical                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pattern                                                                                                   | Error                                                                                                                                                                                                                | Location                                                                                                                                                                                                                                                                               |

| 100000<br>100001<br>100010<br>100011<br>100100<br>100101<br>100110<br>10000<br>101001<br>101001<br>101101 | MBR00<br>MBR01<br>MBR02<br>MBR03<br>MBR04<br>MBR05<br>MBR06<br>MBR07<br>MBR08<br>MBR09<br>MBR10<br>MBR10<br>MBR11<br>MBR12<br>MBR13<br>MBR14<br>S4<br>MBR15<br>MBR15<br>MBR16<br>MBR17<br>MBR18<br>MBR19<br>S3<br>S2 | Location<br>M1, M27<br>M13, M39<br>M14, M40<br>M26, M52<br>M2, M28<br>M12, M38<br>M15, M41<br>M25, M51<br>M3, M29<br>M11, M37<br>M16, M42<br>M24, M50<br>M4, M30<br>M10, M36<br>M17, M43<br>M20, M46<br>M23, M49<br>M5, M31<br>M9, M35<br>M18, M44<br>M22, M48<br>M21, M47<br>M19, M45 |

| 111101                                                                                                    | Sl                                                                                                                                                                                                                   | M8, M34                                                                                                                                                                                                                                                                                |

| 111110                                                                                                    | SO                                                                                                                                                                                                                   | M6, M32                                                                                                                                                                                                                                                                                |

| 111111                                                                                                    | P                                                                                                                                                                                                                    | M7, M33                                                                                                                                                                                                                                                                                |

Table 4.2: Read check pattern following a single-bit error

| Number of Errors |        | <u>Read Check Pattern</u>  |

|------------------|--------|----------------------------|

| 0                | 011111 |                            |

| 1                | lxxxxx | (xxxxx gives bit in error) |

| 2                | 0xxxxx | (xxxxx is not 11111)       |

Single errors can be detected by P being 1, and corrected using the check bits' value. Double errors can be detected by both P and at least one check bit being zero. The EDAC logic interprets any read check pattern as no error, a single error, or a double error. If more than two bits are in error, an odd number of errors will be interpreted as a single error, and an even number of errors will be interpreted as no error or a double error.

Since no memory location is read without first having been written, every read from memory is the second half of a "round trip transfer". Therefore, the EDAC logic can safely perform this error analysis on every read.

# 4.3 Integrating EDAC into the MBB

The discussion of the EDAC algorithm assumed that the MBR's check bits were all 1's before a write to memory. When the MBR is loaded from the destination bus, the check bits are loaded from the 6-bit EDAC.PREP field of the EDAC register (Section 7.4). For normal operation, this field should be set to 111111. For hardware debugging, it may be given another value. When the MBR is loaded by a memory or I/O fetch, the check bits generally

are loaded with different values. (A memory fetch, of course, copies the check bits from memory. An I/O fetch loads the check bits randomly.) Therefore, before any main memory write, the last load of the MBR must be from the destination bus. In the following memory-to-memory transfer sequence, the statement "MBR->MBR" copying the MBR to itself through the ALU, is needed for this reason.

> LOC1->MAR(R) ; read main memory at address LOC1 ... MBR->MBR ; fix MBR's check bits LOC2->MAR(W) ; write value to main memory at address LOC2 ...

Equations (5) and (6) of the last section show that in the error-free case, toggling any EDAC.PREP bit in the EDAC register simply toggles the corresponding bit in the read check pattern. For example, having 010111 instead of 111111 in the EDAC register produces a read check pattern in the absence of hardware errors of 110111 instead of 011111. This would be detected as an error by the EDAC hardware. (Errors will work much as before, changing bits in the read check pattern away from their values in the error-free case.)

The discussion of the algorithm also considered only those reads which follow writes. In fact, the EDAC logic would be confused on reading a location which had never been written,

since the check bits in memory would be random. Therefore, as part of the initialization after power-up, all main memory locations should be written. (Such writing must be preceded by the eight memory cycles required to prime main memory.)

On detecting errors after reads, the EDAC logic affects MBB operation in three ways. First, various status conditions and error data are latched. On detecting any error, the "M2.MEMERR" bit in MISC2 is set. On detecting any double (uncorrectable) error, the "M2.UCERR" bit in MISC2 is set. On detecting any single (correctable) error, the read check pattern and the memory bank from which the erroneous data came are saved in the EDAC register. Thus, faulty bits in individual chips may be identified.

Second, if enabled, EDAC corrects single data errors. On detecting a single data error, EDAC steals two microcycles to fix the indicated bit in the MBR. EDAC does not eliminate the error in memory, so every subsequent fetch would require the same fixing. (The program should eventually eliminate the error by rewriting the corrected data to memory.) Setting the "EDAC.FIX" bit in the EDAC register enables the cycle stealing and MBR fixing; clearing the bit disables them.\*

<sup>\*</sup>Note that if fixing is not enabled, the read check pattern is <u>not</u> latched in the EDAC register on an error.

Third, if enabled, EDAC traps to microcode address 0 on detecting a double error. Setting the "EDAC.TRAP" bit in the EDAC register enables this feature; clearing the bit disables the feature.