# TC2000<sup>™</sup> Hardware Architecture

VERSION OF FEBRUARY 14, 1990

# THIS DOCUMENT IS BBN ACI PROPRIETARY

Revision: 2/14/90 February 14, 1990

BBN Advanced Computers Inc.

Part No. Document Rev:

# TC2000<sup>™</sup> Hardware Architecture

VERSION OF FEBRUARY 14, 1990

# THIS DOCUMENT IS BBN ACI PROPRIETARY

Revision: 2/14/90 February 14, 1990

Part No. Document Rev:

BBN Advanced Computers Inc.

#### Copyright © 1989 by BBN Advanced Computers Inc. ALL RIGHTS RESERVED

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise without the prior written permission of BBN Advanced Computers Inc. (BBN ACI).

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013.

BBN Advanced Computers Inc 10 Fawcett St. Cambridge MA 02138

#### **RELEASE LEVEL**

This document conforms to the February 1990 TC2000<sup>™</sup> multiprocessor hardware..

#### NOTICE

BBN ACI has prepared this manual for the exclusive use of BBN customers, personnel, and licensees. The information in this manual is subject to change without notice, and should not be construed as a commitment by BBN ACI. BBN ACI assumes no responsibility for any errors that appear in this document.

#### TRADEMARKS

Butterfly is a registered trademark of Bolt Beranek and Newman Inc.

Chrysalis, TC2000, nX, Uniform System, Xtra, Gist, and TotalView are trademarks of Bolt Beranek and Newman Inc.

UNIX is a registered trademark of AT&T Bell Laboratories.

DEC, VAX, and VT are registered trademarks of Digital Equipment Corporation.

VMS, VAX/VMS, MicroVAX, Ultrix, and DECnet are trademarks of Digital Equipment Corporation.

IBM and IBM PC are trademarks of International Business Machines.

Multibus and Intel are registered trademarks of Intel Corporation.

X Window System is a trademark of the Massachusetts Institute of Technology.

MC68000, MC68020, MC68881, MC68882, MC68851, MC88000, MC88100, MC88200, and VMEbus are trademarks of Motorola Semiconductor Products, Inc.

QTC and Math Advantage are registered trademarks of Quantitative Technology Corporation.

pSOS, pSOS<sup>+</sup>, pSOS<sup>+</sup><sup>m</sup>, pRISM, pUCP, pREP/C, pROBE, and pHILE are trademarks of Software Components Group, Inc.

MS-DOS is a registered trademark of Microsoft Corporation.

TeleSoft and TeleGen2 are trademarks of Telesoft.

Sun Microsystems and Sun Workstation are registered trademarks of Sun Microsystems, Inc.

OSN, ONC, NeWS, and NFS are trademarks of Sun Microsystems, Inc.

4.2BSD and 4.3BSD are trademarks of the Trustees of the University of California.

Ethernet is a registered trademark of Xerox Corporation.

I am grateful to the engineers on this project for their support and encouragement, their writing of documents used as source material for this book, and their helpfulness and patience. John Goodhue has been instrumental in managing the Butterfly II hardware development, and in guiding the development of this book as well.

- Micahel Beeler, author, April 1989

Justin Aborn Arthur Babitz Tom Blackadar Kent Cauble Guy Fedorkow Tom Feist John Goodhue Lise Graham Ward Harriman Phil Herman Jack Hill Kent Hoult Brian Kalita Allen King Cinsy Krehbiel Stan Lackey Andy Latto Phil Levin Kevin McGrattan Paul Moruzzi Gary Muntz Lou Piazza Randy Rettberg Mike Sollins Julie Tiao Jeff Wise

Also instrumental were the early developers of bootstrap, TCS, diagnostic and operating system software:

> Tom Calderwood Ken Chin Bob Clements Jim Gibson Carl Howe Mark Hutcheson

Nancy Keene Jeff Kenton Bill Mathews Jim Mcleish Roger Preston Wolfgang Rupprecht

The development of the Butterfly II machine builds on earlier multiprocessor work at BBN, particularly the Pluribus and more recently the original Butterfly computer. The architects and developers of these machines have indirectly, and often directly, aided the development of the Butterfly II machine.

BBN ACI thanks the above contributors for their efforts in developing this manual.

iii

# Contents

|      | Foreword  |                                                  | <b>1</b>      |

|------|-----------|--------------------------------------------------|---------------|

|      |           |                                                  | •             |

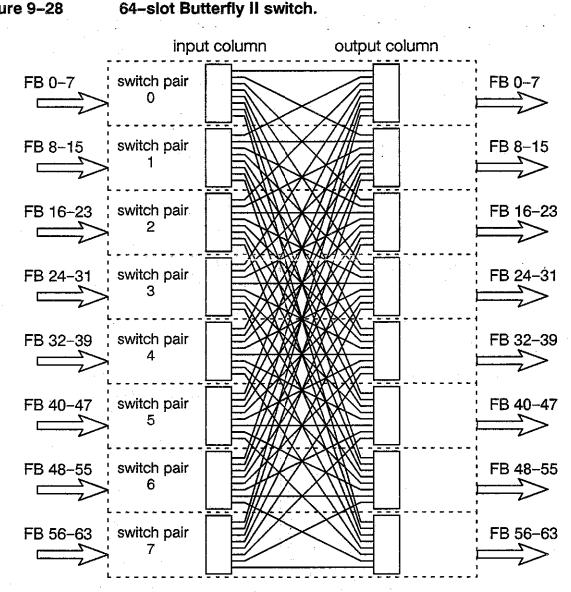

| 3    | The Butte | rfly II Switch                                   | 5             |

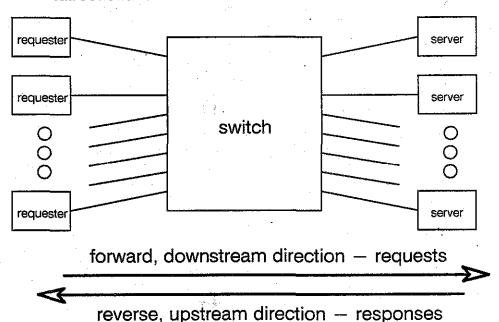

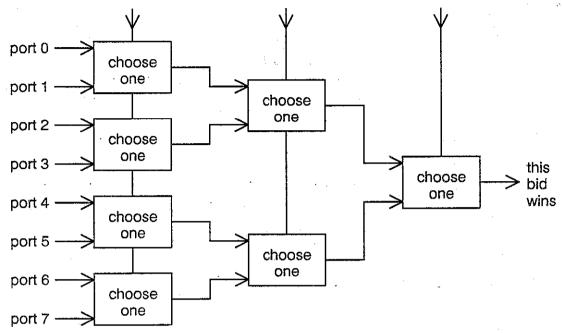

| 3.1  |           | Design Concept                                   | 5             |

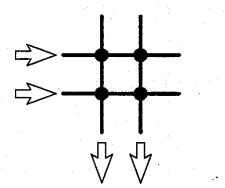

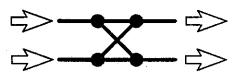

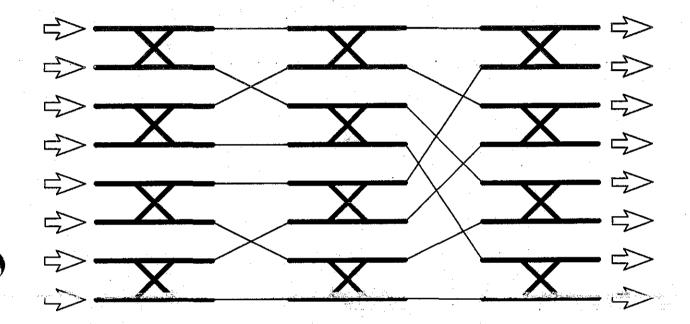

|      | 3.1.1     | Butterfly Switch Basics                          | 5             |

|      | 3.1.2     | Routing in the Butterfly Switch                  | 7             |

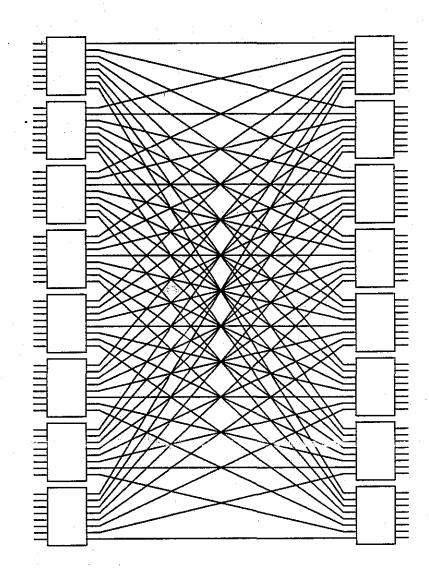

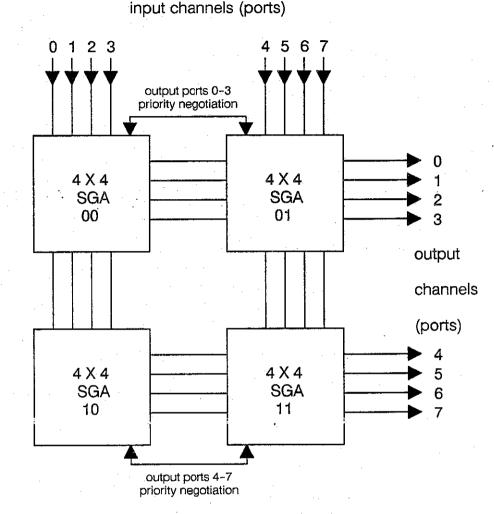

|      | 3.1.3     | Organization of the Butterfly II Switch          | 8             |

|      | 3.1.4     | How Data Flows                                   | 11            |

|      | 3.1.5     | Resources Employed                               | 12            |

| 3.2  |           | tionality                                        | 14            |

| 3.3  |           | g                                                | 15            |

| 3.4  |           | Б                                                | 17            |

| 3.5  |           | e Priority Promotion                             | 19            |

| 3.6  |           | Injection Pacing                                 | 23            |

| 3.7  |           | tion and Retry Strategies                        | 23            |

| 2.,  | 3.7.1     | Port Is Already In Use                           | 23            |

|      | 3.7.2     | Head-on Collision at the Port                    | 24            |

|      | 3.7.3     | Retransmission Pacing                            | 25            |

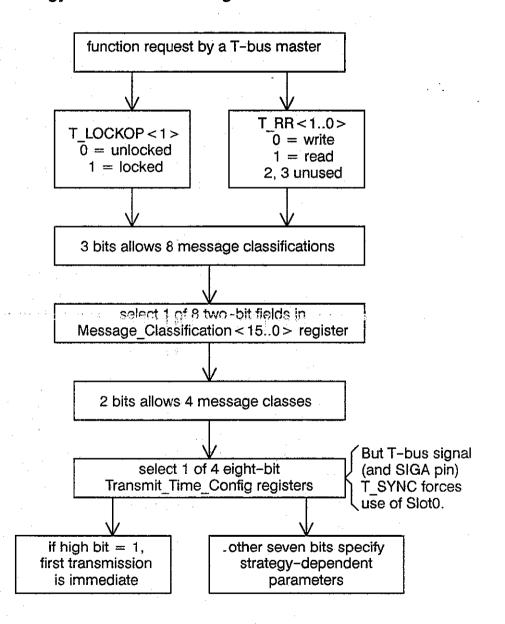

|      | 3.7.4     | Strategy Selection                               | 25            |

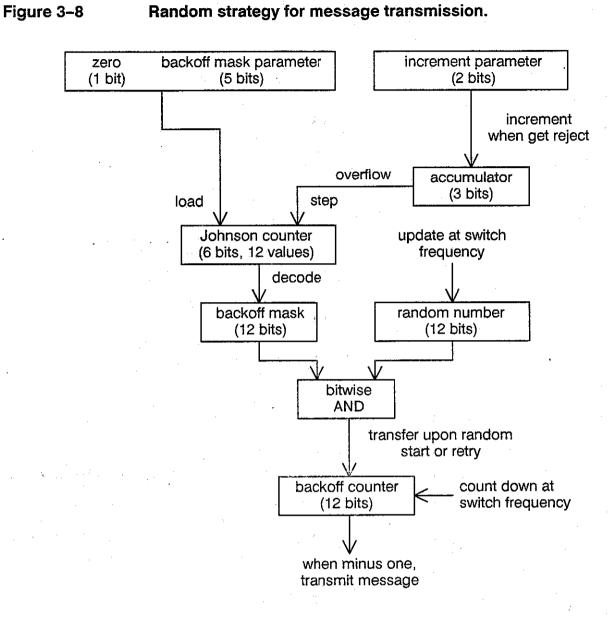

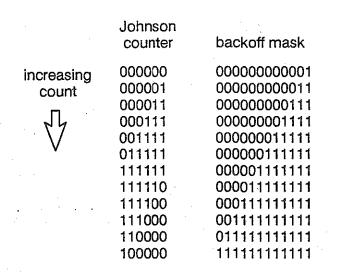

|      | 3.7.5     | Random Strategy                                  | 26            |

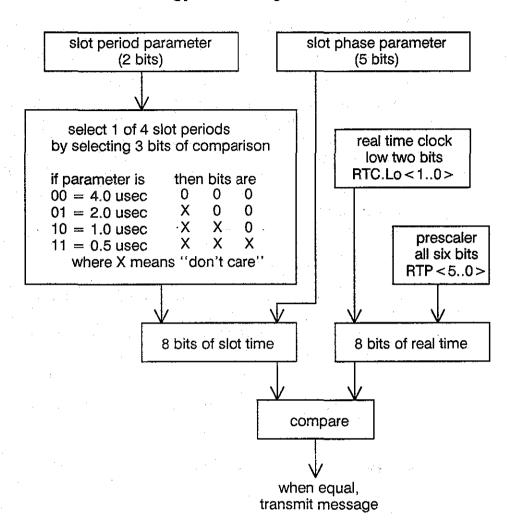

|      | 3.7.6     | Slotted Strategy                                 | 30            |

| 3.8  |           | Jancy                                            | 33            |

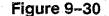

| 3.9  |           | Distribution                                     | 33            |

| 0.5  | 3.9.1     | Clock Master Card                                | 34            |

|      | 3.9.2     | Switch Card                                      | 34            |

|      | 3.9.3     | Function Boards                                  | 35            |

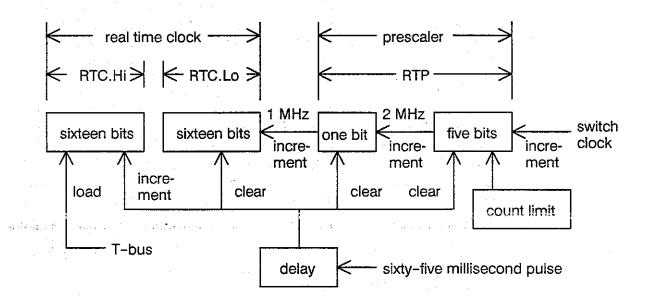

|      | 3.9.4     | Real Time Clock                                  | 36            |

|      | 3.9.5     | Other Functions of the Clock Distribution System | <del>39</del> |

| 3.10 |           | ndent Clocks                                     | 40            |

|      | 3.10.1    | Test and Control System Clocks                   | 40            |

|      | 3.10.2    | T-bus (Function Board) Clocks                    | 40            |

|      | 3.10.3    | Net Time Support                                 | 41            |

|      | 3.10.4    | VMEbus System Clock Support                      | 41            |

| 3.1  |           | Protocol and Message Formats                     | 42            |

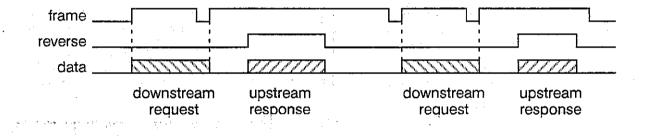

|      | 3.11.1    | Frame and Reverse                                | 42            |

| · ·  | 3.11.2    | Message and Connection Boundaries                | 43            |

|      | 3.11.3    | Basics of Message Functions                      | 44            |

v

vi

|                                                              |                | • • • • • • • • • • • • • • • • • • •        |      |

|--------------------------------------------------------------|----------------|----------------------------------------------|------|

|                                                              | 3.11.4         | Message Components                           | 45   |

|                                                              | 3.11.5         | Message Header                               | 46   |

|                                                              | 3.11.6         | Message Command                              | 49   |

|                                                              | 3.11.7         | Message Data                                 | 50   |

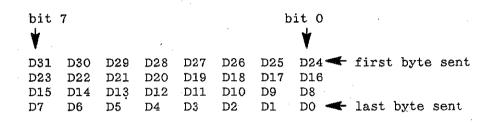

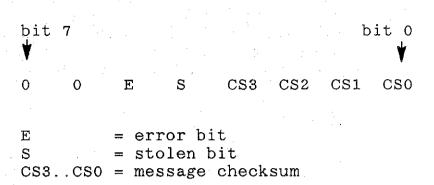

|                                                              | 3.11.8         | Message Checksum Byte                        | 51   |

|                                                              | 3.11.9         | Message Sizes                                | 54   |

| •                                                            | 3.11.10        | Switch Protocol Timers                       | 55   |

|                                                              | 3.11.11        | The Switch as a T-bus Device                 | 56   |

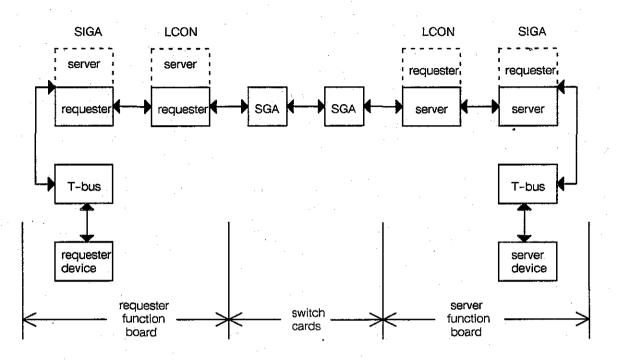

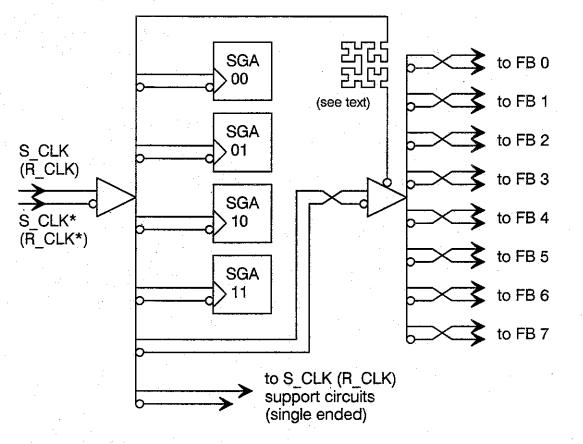

| 3.12                                                         | Switch         | Chip Set: SGA, LCON, SIGA                    | 56   |

|                                                              | 3.12.1         | LĈON                                         | 56   |

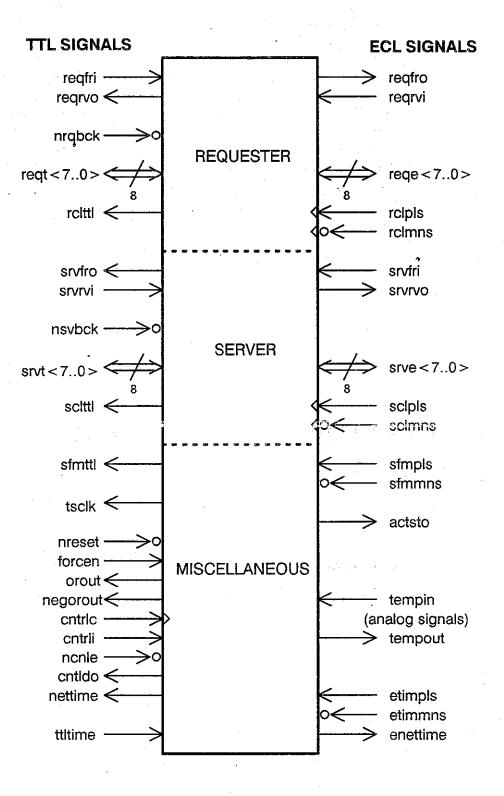

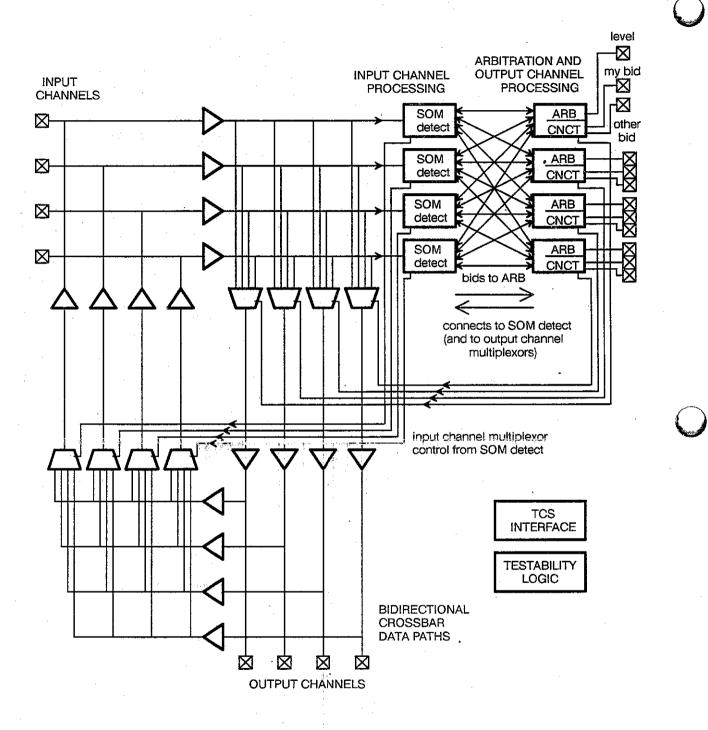

|                                                              | 3.12.2         | SGA                                          | 63   |

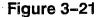

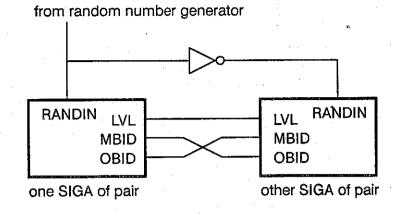

|                                                              | 3.12.3         | SIGA                                         | 73   |

| 3.13                                                         | Analysi        | is of Selected Cases                         | 73   |

|                                                              | 3.13.1         | High Priority Bid and Hold De-asserted       | 73   |

|                                                              | 3.13.2         | Bid Arbitration Unfairness                   | 74   |

|                                                              |                |                                              |      |

| 4 Th                                                         | o Butto        | erfly II Memory System                       | 77   |

|                                                              |                |                                              |      |

| 4.1                                                          |                | al Characteristics                           | . 77 |

| 4.2                                                          |                | versus Remote Access                         | 79   |

| 4.3                                                          |                | versus Globally Accessible                   | 80   |

| 4.4                                                          |                | s Formats*                                   | 80   |

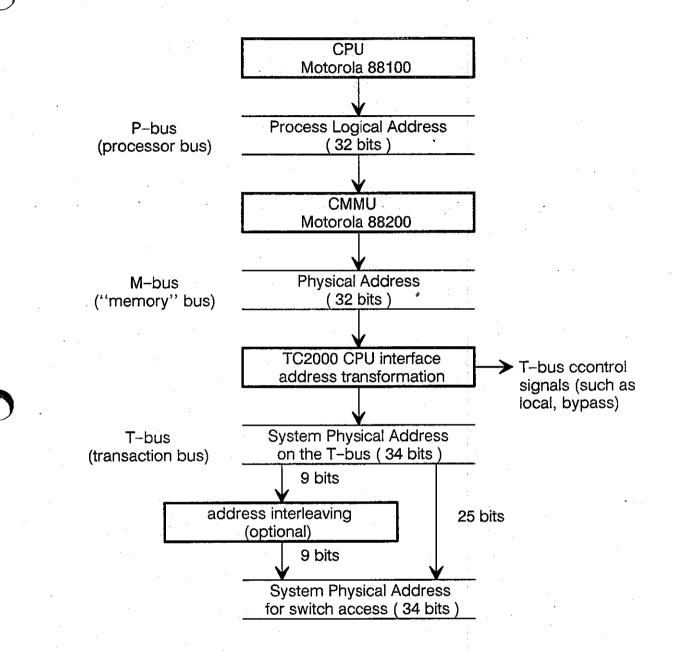

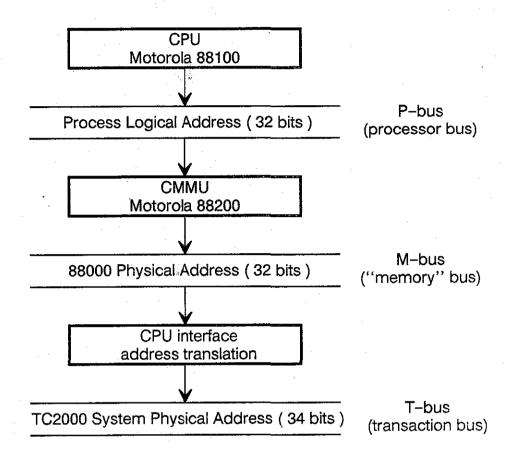

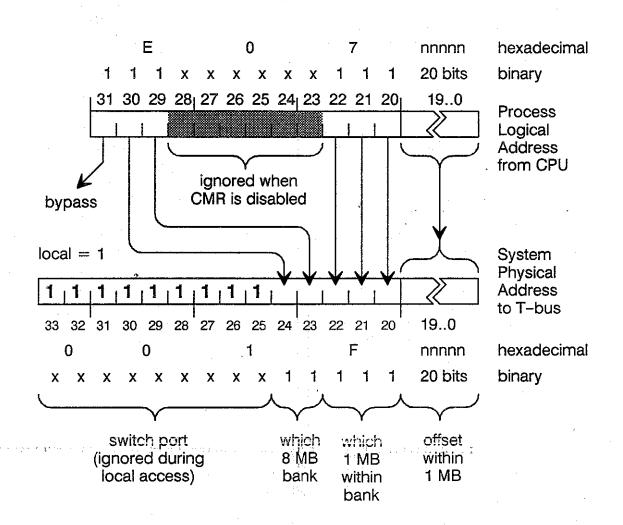

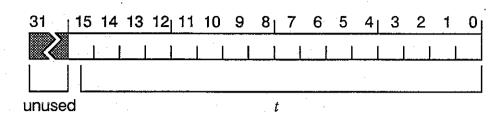

|                                                              | 4.4.1          | Process Logical Address                      | 81   |

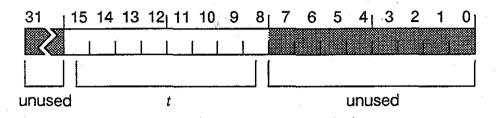

|                                                              | 4.4.2          | Physical Address                             | 82   |

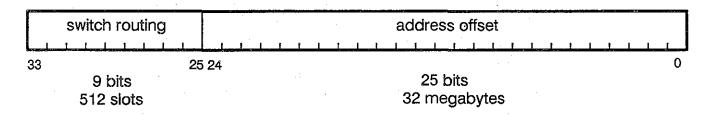

|                                                              | 4.4.3          | System Physical Address                      | 83   |

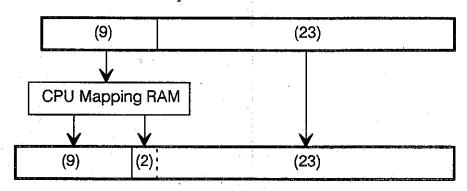

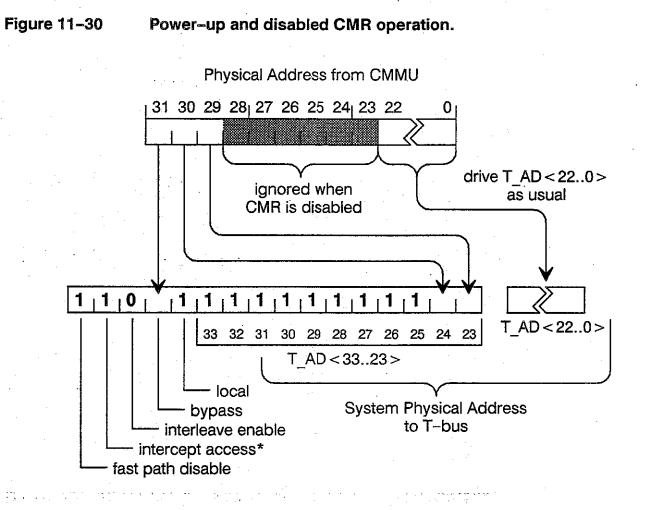

|                                                              | 4.4.4          | Address Transformation in the CPU Interface  | 84   |

| 4.5                                                          |                | aving                                        | 86   |

|                                                              | 4.5.1          | Overview of Interleaving                     | 86   |

|                                                              | 4.5.2          | Motivation for Interleaving                  | 86   |

|                                                              | 4.5.3          | Uniform Use of Butterfly II Interleaving     | 87   |

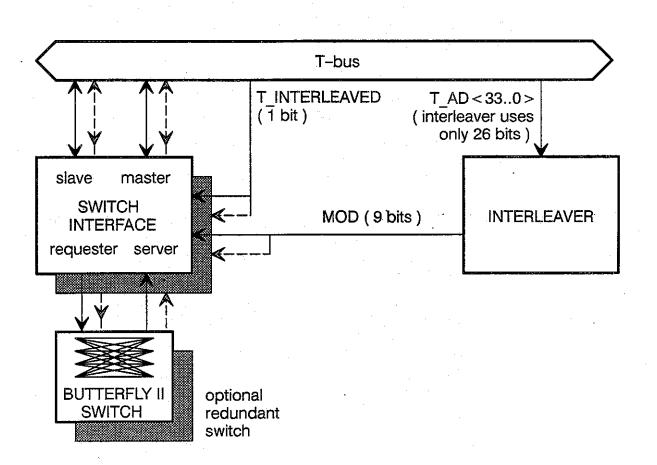

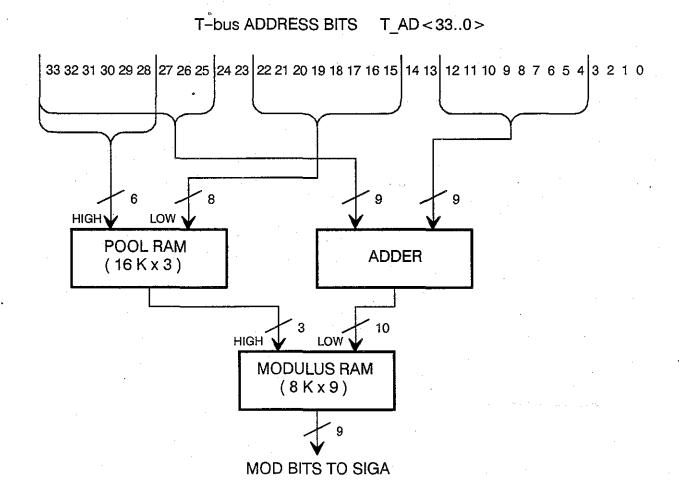

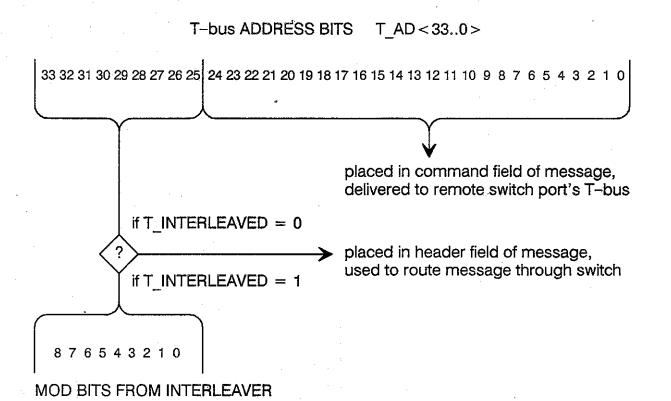

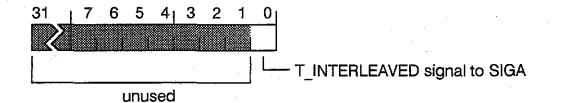

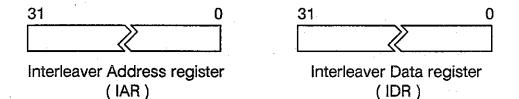

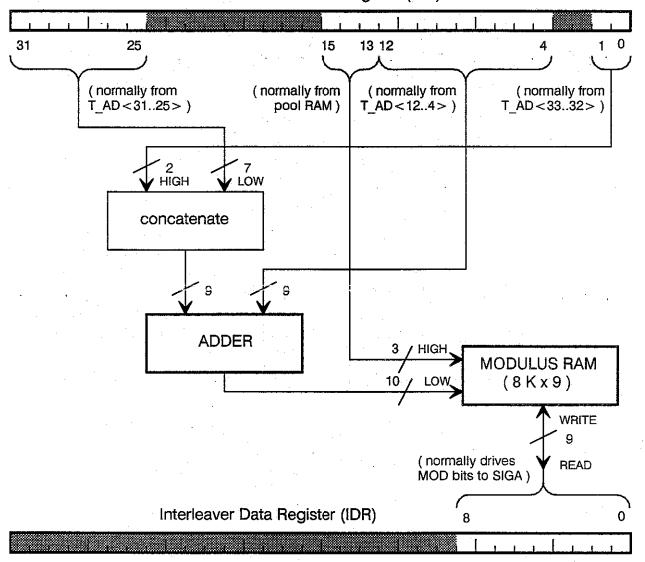

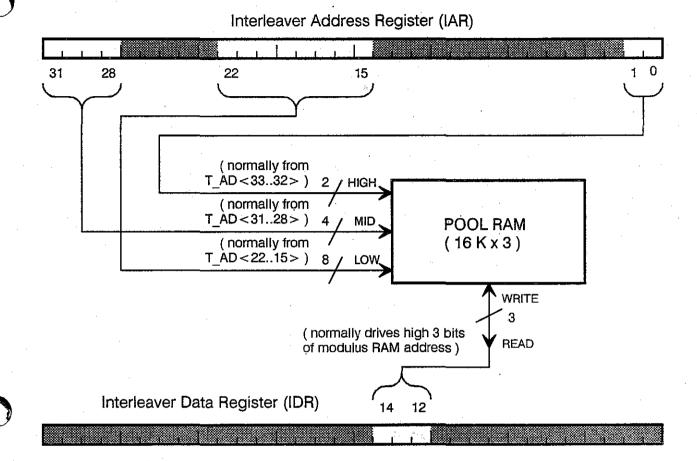

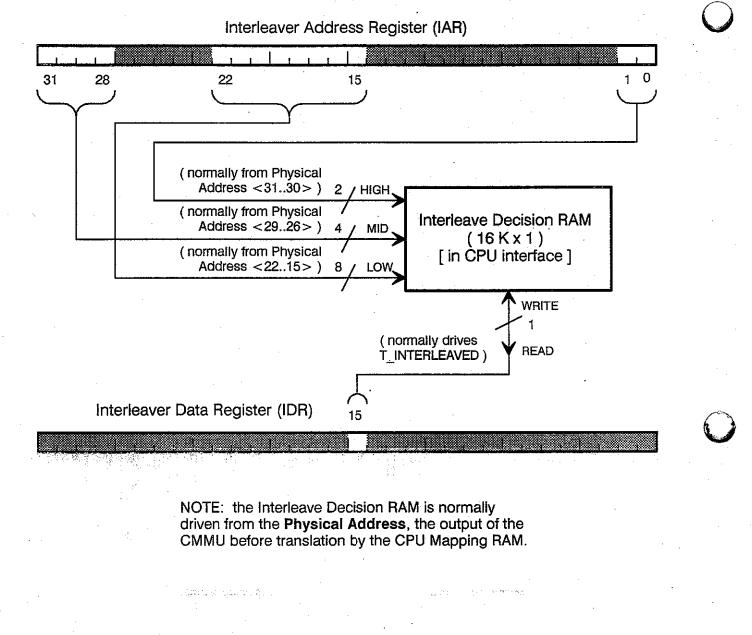

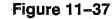

| $   _{\mathcal{L}^{\infty}} \geq    _{\mathcal{L}^{\infty}}$ | 4.5.4          | Implementation of Butterfly II Interleaving  | .88  |

| 1                                                            | 4.5.5          | Conceptual Operation of the Interleaver      | 92   |

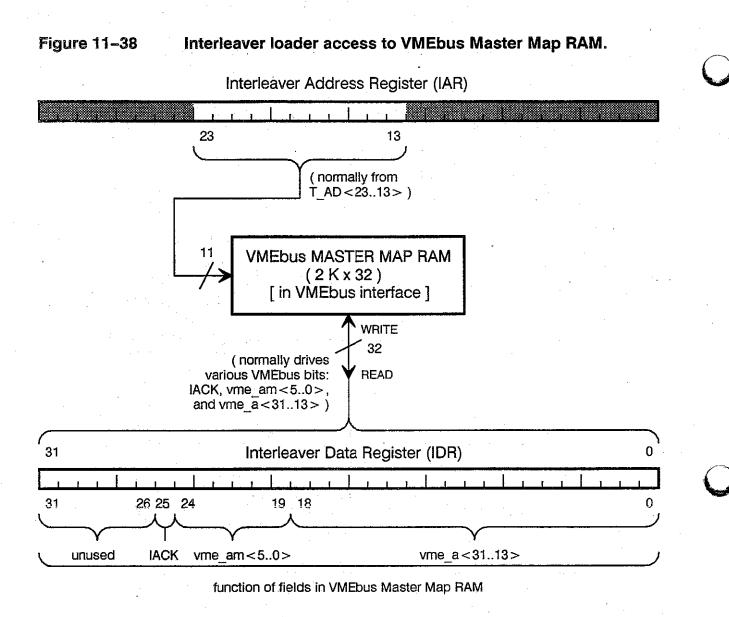

|                                                              | 4.5.6          | The Interleaver Loader                       | 101  |

| 4.6                                                          | Error I        | Detection and Error Rate                     | 101  |

|                                                              | 4.6.1          | Detected Soft Error Rate                     | 102  |

|                                                              | 4.6.2          | Undetected Soft Error Rate                   | 103  |

|                                                              | 4.6.3          | Hard Error Rate                              | 105  |

|                                                              | 4.6.4          | Write Wrong Parity                           | 106  |

| 4.7                                                          | Histori        | cal Note: Steal Bit                          | 106  |

| -                                                            | ·              |                                              |      |

| 6 Th                                                         | e Butte        | rfly II Test and Control System (TCS)        | 109  |

| 6.1                                                          | Introdu        | iction                                       | 109  |

| 6.2                                                          |                | ew of TCS Use                                | 110  |

| 6.3                                                          |                | are Components                               | 111  |

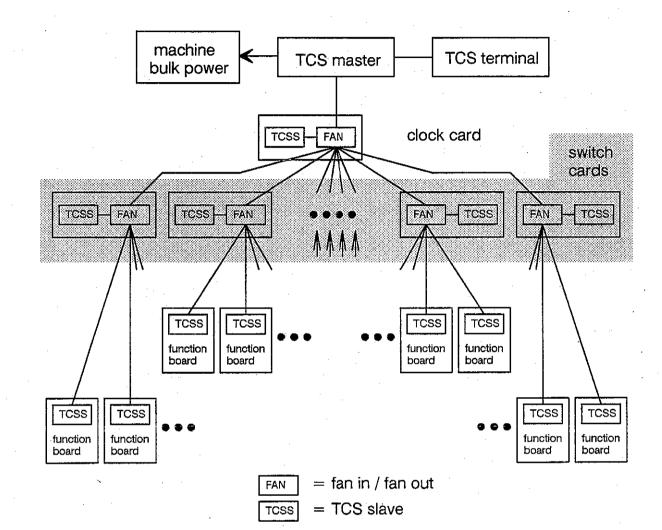

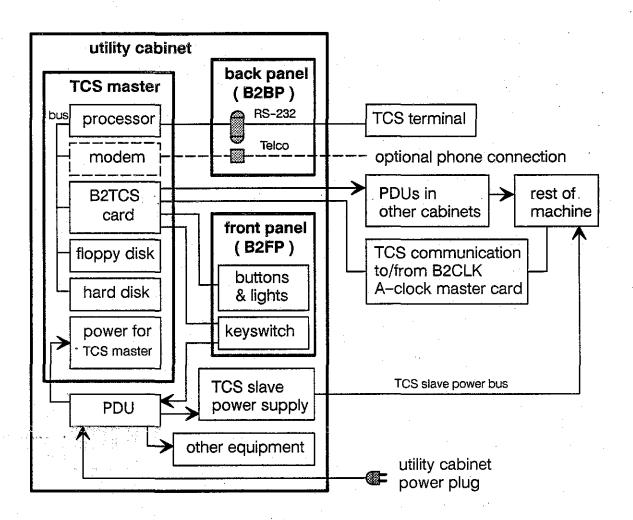

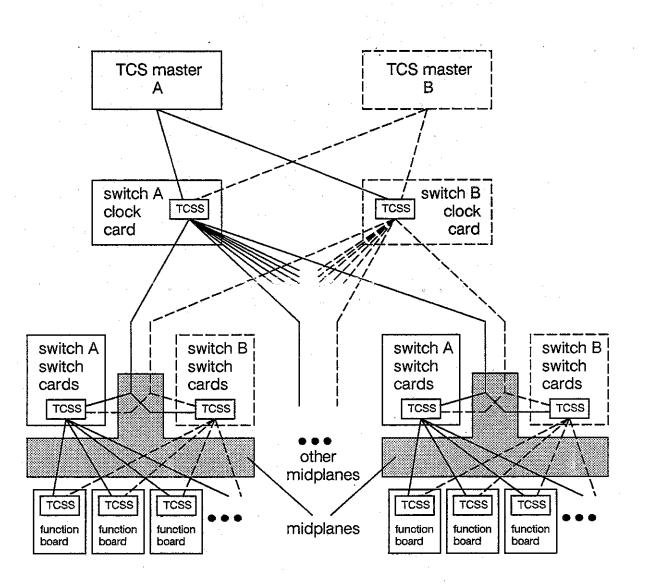

| 0.5                                                          | 6.3.1          | TCS Master                                   | 113  |

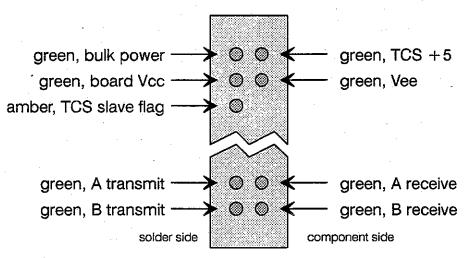

|                                                              | 6.3.2          | TCS Bus                                      | 115  |

|                                                              | 6.3.2<br>6.3.3 | TCS Bus                                      | 120  |

|                                                              |                |                                              |      |

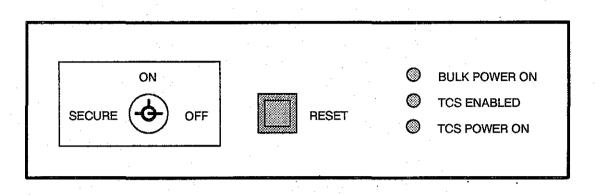

|                                                              | 6.3.4          | TCS Front Panel                              | 127  |

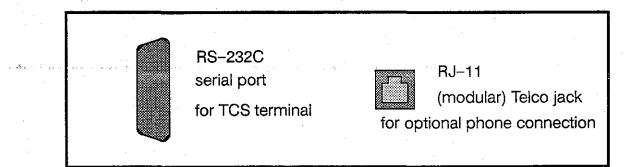

|                                                              | 6.3.5          | TCS Back Panel                               | 129  |

|                                                              | 6.3.6          | TCS Power Supplies                           | 129  |

| C A                                                          | 6.3.7          | Bulk Power Control                           | 130  |

| 6.4                                                          |                | perational Capabilities                      | 130  |

|                                                              | 6.4.1          | Power-On and Bootstrapping                   | 130  |

|                                                              | 6.4.2          | Monitoring                                   | 133  |

|                                                              | 6.4.3          | Field Service and System Management Commands | 135  |

TC2000 Hardware Archirecture

|          |               |                                                 | •    |

|----------|---------------|-------------------------------------------------|------|

| 6.5      | B2TCS         | Functional Specification                        | 138  |

|          | 6.5.1         | Introduction                                    | 138  |

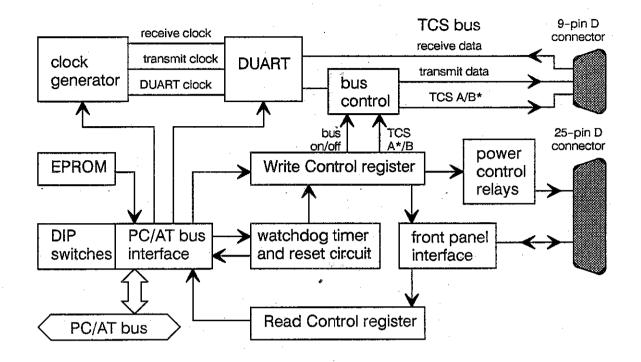

|          | 6.5.2         | Major Card Functions                            | 138  |

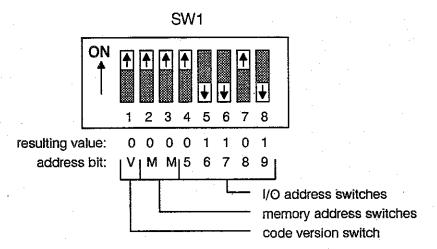

|          | 6.5.3         | B2TCS Address Space                             | 142  |

|          | 6.5.4         | B2TCS Register Summary                          | 144  |

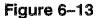

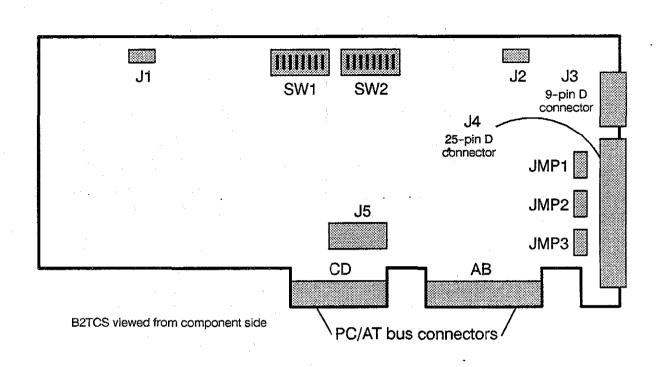

| . •      | 6.5.5         | B2TCS Controls and Indicators                   | 148  |

| 6.6      | Redund        | Jancy Support                                   | 151  |

|          | 6.6.1         | Redundant Modules                               | 151  |

|          | 6.6.2         | List of Backup Features                         | 151  |

|          | 6.6.3         | Redundant Switch and/or TCS Master              | 152  |

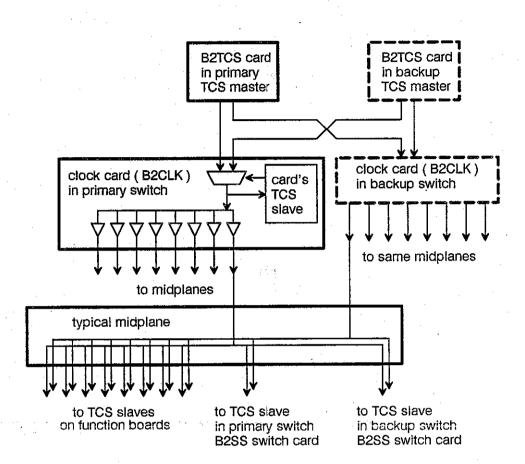

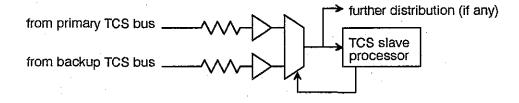

|          | 6.6.4         | Redundant TCS Bus                               | 153  |

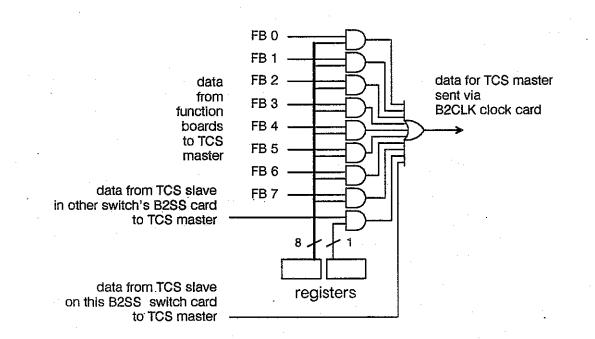

|          | 6.6.5         | TCS Bus Fan-in Details                          | 153  |

|          | 6.6.6         | TCS Bus Fan-out Details                         | 154  |

|          | 6.6.7         | Redundant Power for the TCS Master              | 156  |

|          | 6.6.8         | Redundant Control of Bulk Power                 | 156  |

|          | 6.6.9         | Backup TCS Testing                              | 156  |

|          | 6.6.10        | Mastership Negotiation                          | 157  |

|          | 6.6.11        | Power-On with a Redundant Switch                | 158  |

|          | 6.6.12        | Configuration with a Redundant Switch           | 158  |

|          |               | Backup Switch Testing                           | 159  |

| 6.7      | B2TCS         | Backup Switch Testing                           | 159  |

| 0.7      | 12100         |                                                 | 157  |

| ~        | De the effect |                                                 | 4.04 |

| 9        | Butterny      | Il Switch Components                            |      |

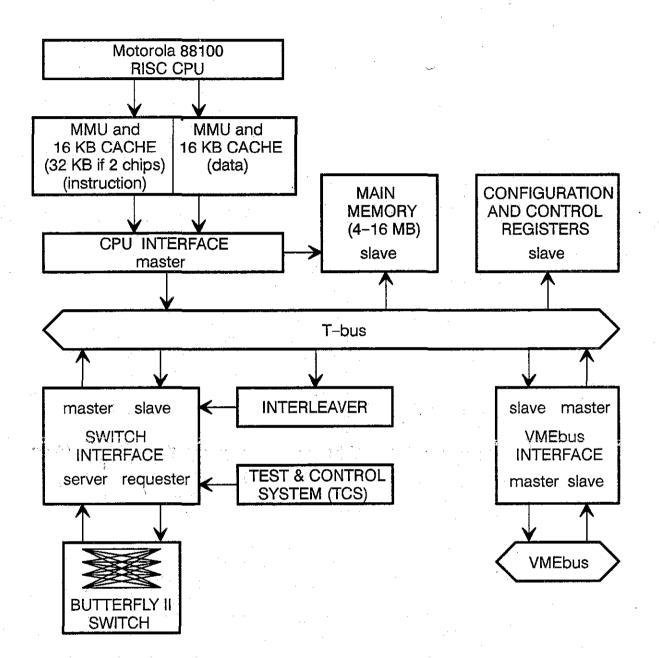

| 9.1      |               | ore of the Butterfly II Computer                | 161  |

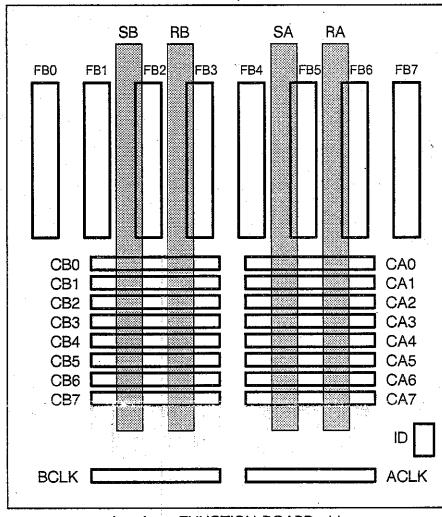

| 9.2      |               | utterfly II Midplane (B2MP)                     | 161  |

|          | 9.2.1         | Function and Motivation                         | 161  |

|          | 9.2.2         | Physical Characteristics                        | 163  |

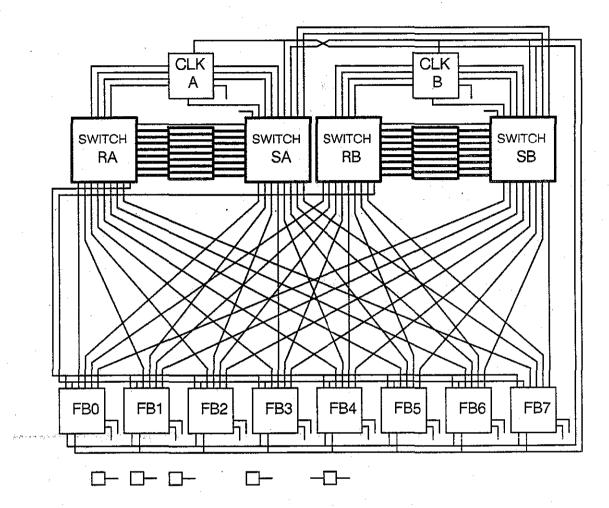

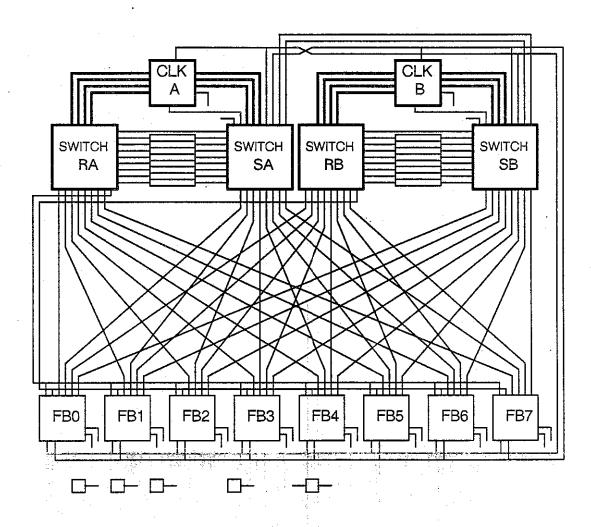

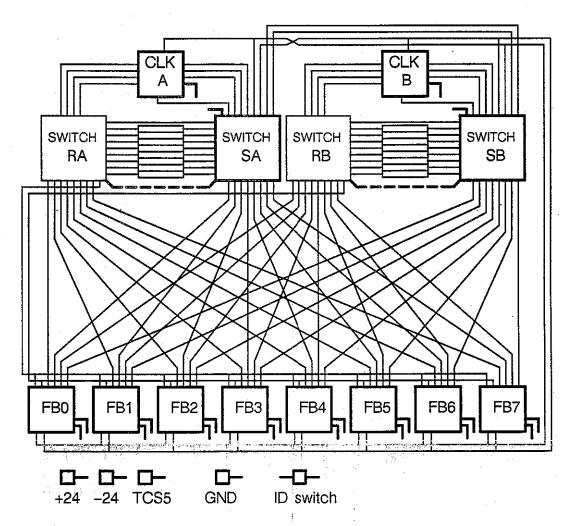

|          | 9.2.3         | Block Diagram                                   | 167  |

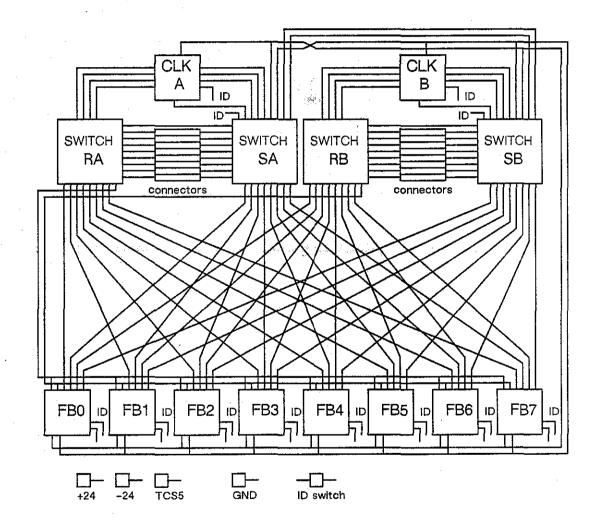

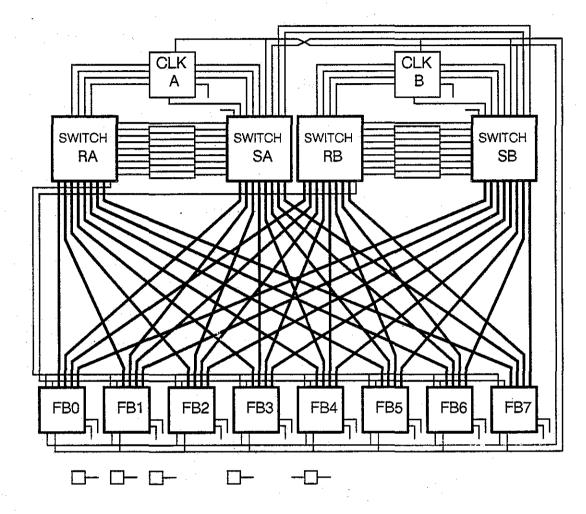

| t st     | 9.2.4         | Wiring between switch cards and function boards | 168  |

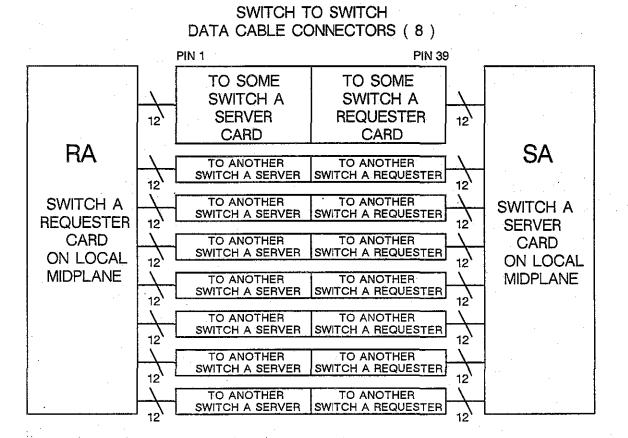

| <br>1000 | 9.2.5         | Withing between switch cards and data cables    | 170  |

|          | 9.2.6         | Wiring between switch cards and clock cables    | 173  |

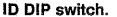

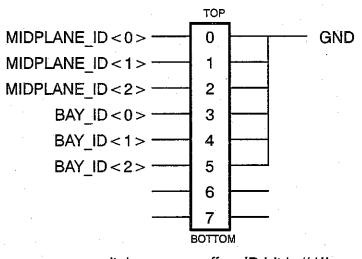

|          | 9.2.7         | Power and ID wiring                             | 175  |

|          | 9.2.8         | TCS wiring                                      | 179  |

| :        | 9.2.9         | Net time wiring                                 | 186  |

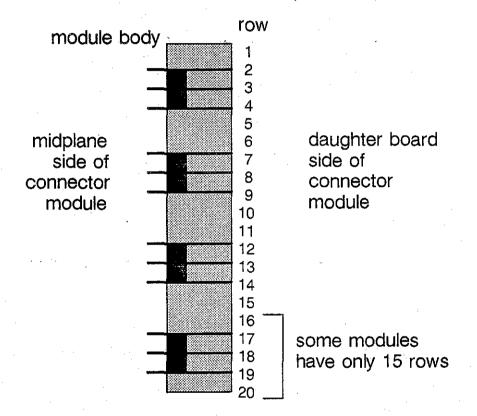

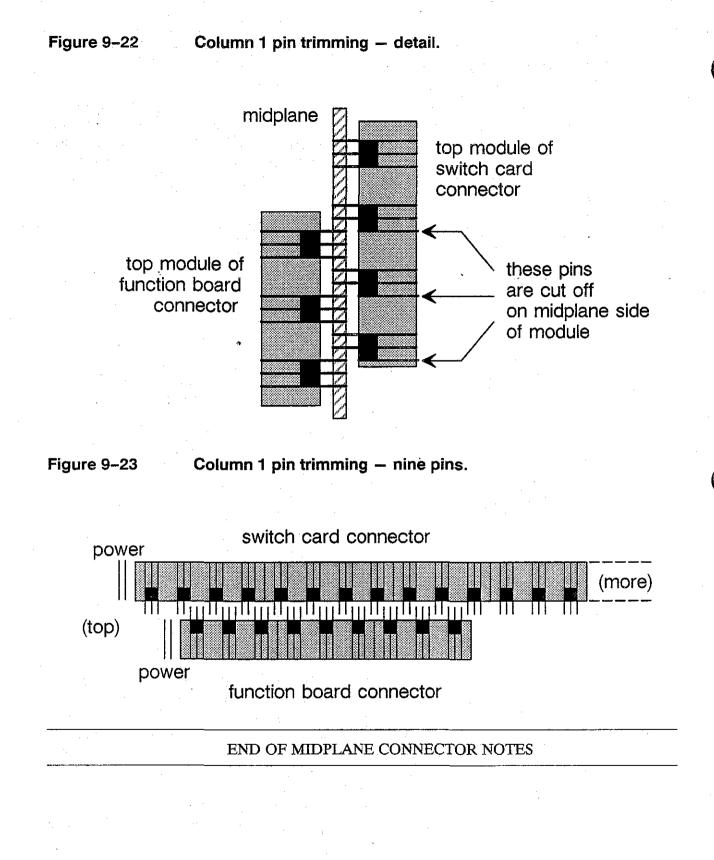

|          | 9.2.10        | Midplane connector pinouts                      | 188  |

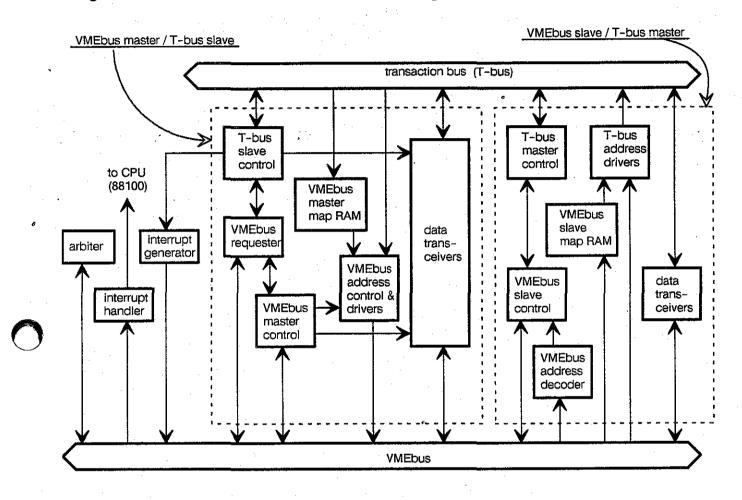

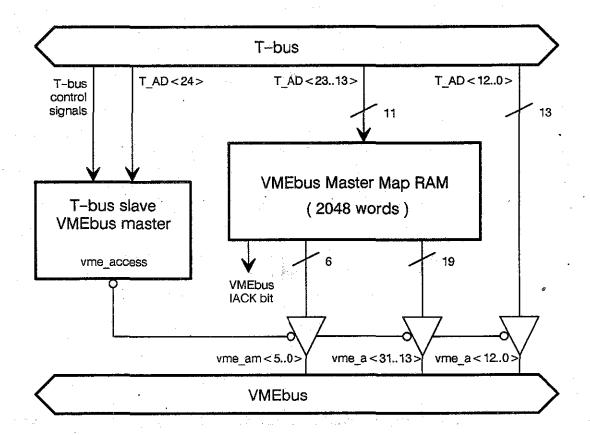

| 9.3      |               | ly II Switch Cards (B2SR, B2SS)                 | 207  |

| -        | 9.3.1         | Introduction                                    | 207  |

|          | 9.3.2         | Glossary                                        | 209  |

| ÷        | 9.3.3         | Function                                        | 210  |

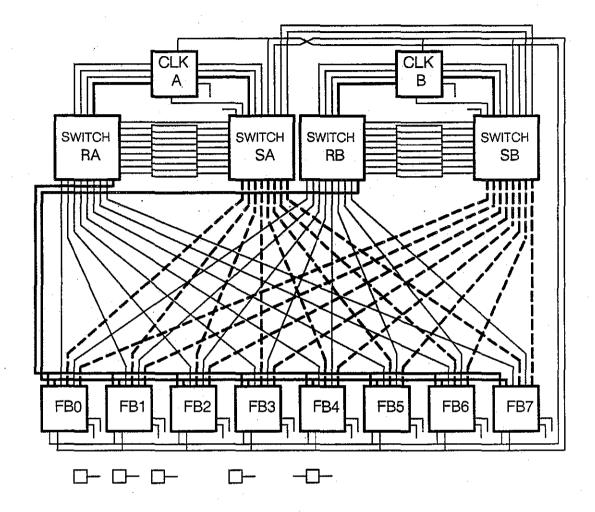

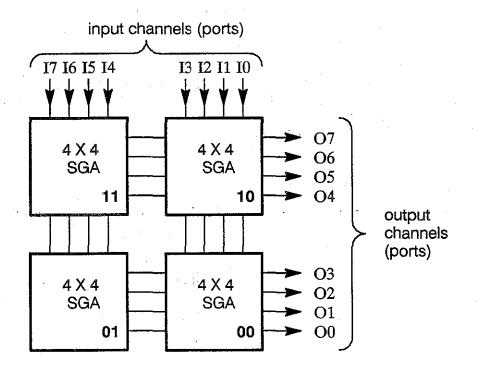

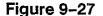

|          | 9.3.4         | Crossbar                                        | 210  |

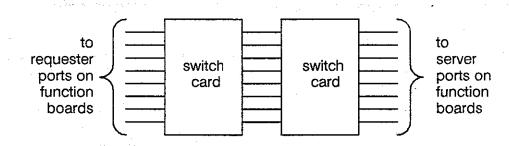

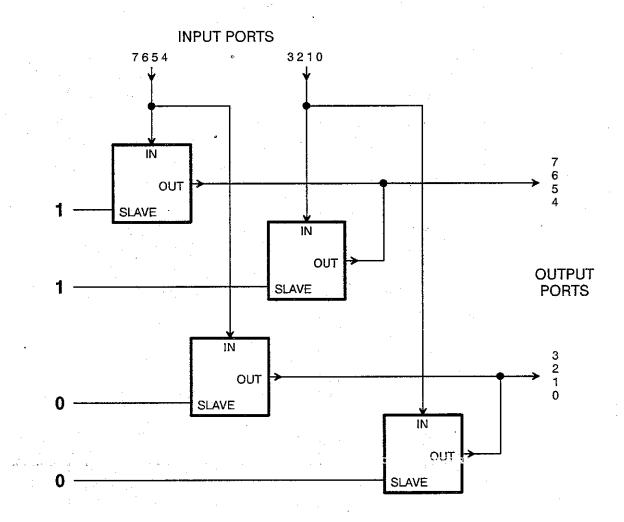

|          | 9.3.5         | Card Pairs                                      | 212  |

|          | 9.3.6         | Switch Support Circuits                         | 213  |

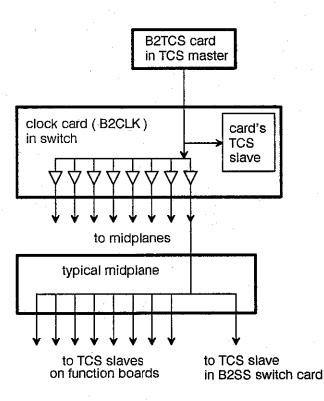

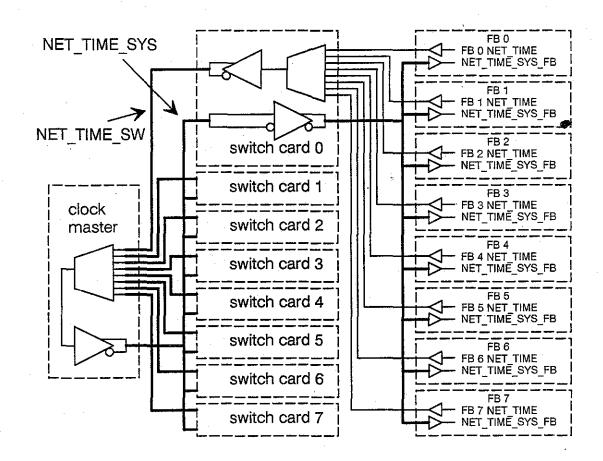

|          | 9.3.7         | System Clock Distribution                       | 213  |

|          | 9.3.8         | NET_TIME                                        | 215  |

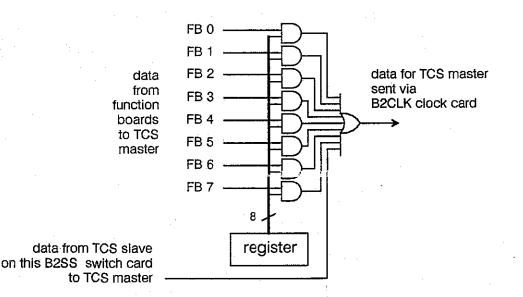

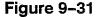

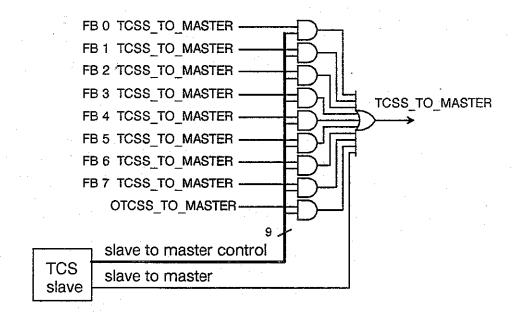

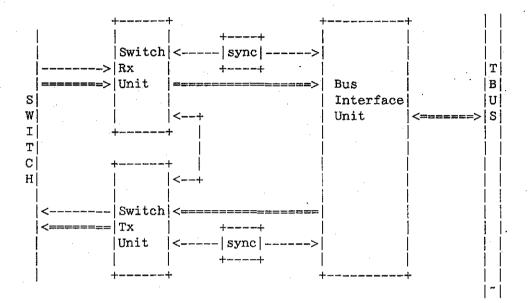

|          | 9.3.9         | TCS Slave – Communication                       | 216  |

| 1        | 9.3.10        | TCS Slave – Control                             | 218  |

|          | 9.3.11        | TCS Slave — Monitor Functions                   | 219  |

|          | 9.3.12        | TCS Slave — Card Identity                       | 220  |

|          | 9.3.13        | 65-millisecond Pulse                            | 220  |

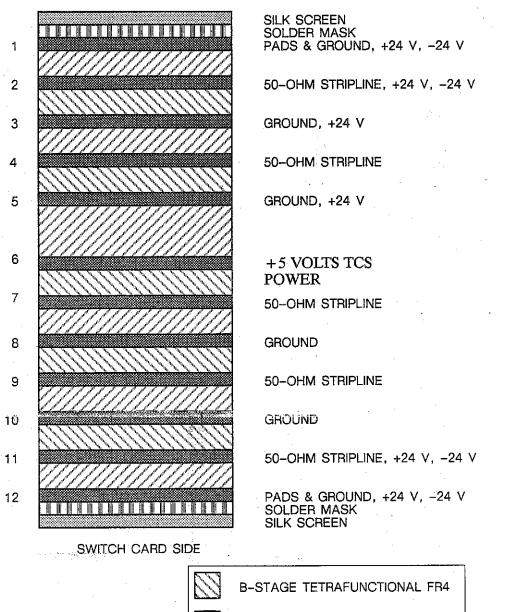

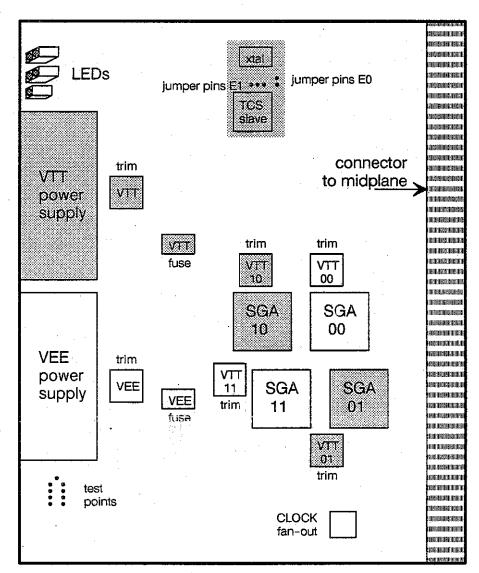

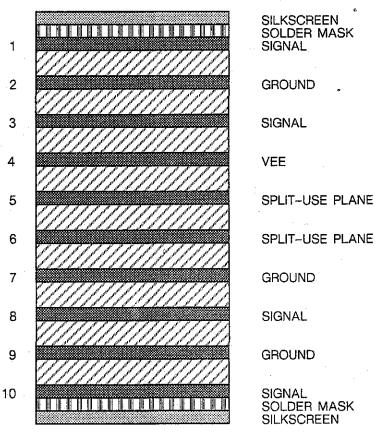

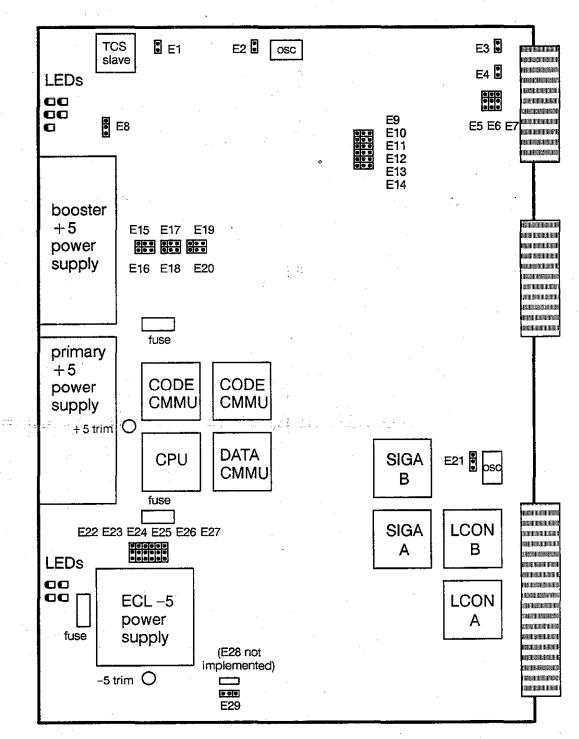

|          | 9.3.14        | Printed Circuit Board                           | 220  |

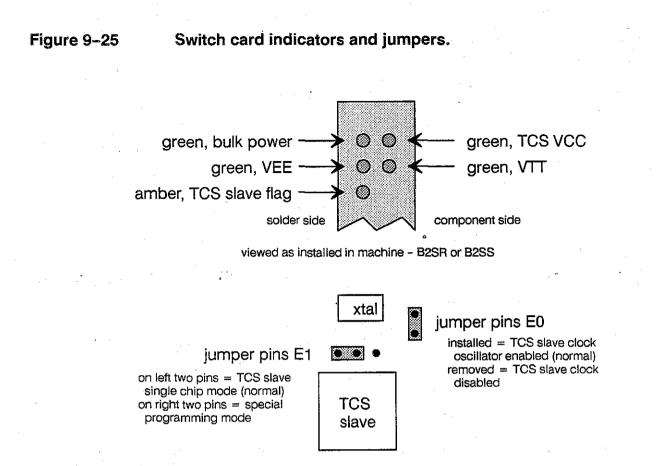

|          | 9.3.15        | Displays and Switches                           | 222  |

|          | 9.3.16        | Signal Lists                                    | 222  |

|          | 9.3.17        | Power                                           | 224  |

| 9.4      | The Br        | itterfly II Clock Card (B2CLK)                  | 225  |

## February 14, 1990

## **BBN ACI Proprietary**

vii

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.1   | Introduction                                      | 225   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.2   | Overview                                          | 225   |

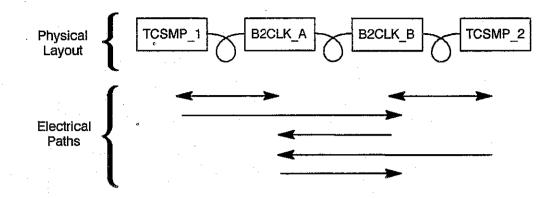

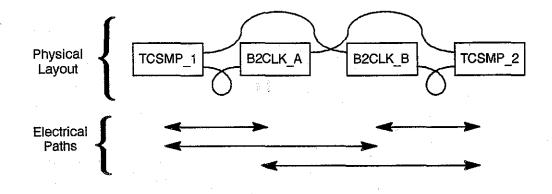

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.3   | Fallback Techniques                               | 226   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.4   | Fixed Crystal Clock Generation                    | 227   |

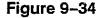

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.5   | Frequency-synthesized Clock Generation            | 227   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.6   | Clock Selection and Buffering                     | 233   |

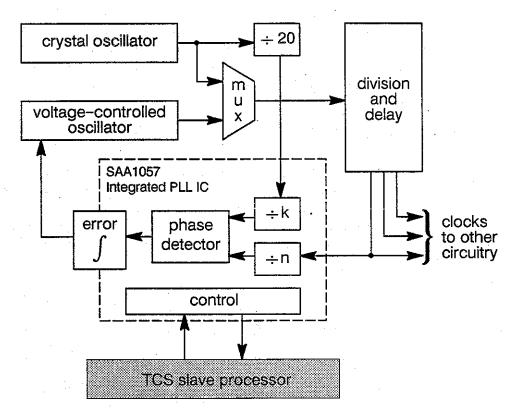

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.7   | Timing Interface Circuitry                        | 233   |

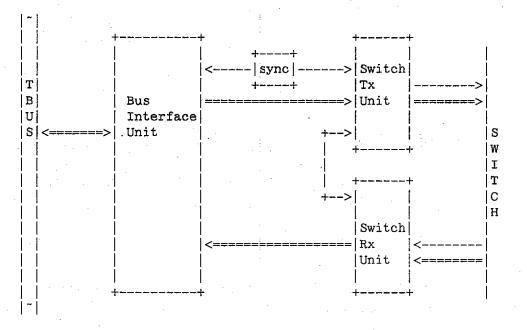

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.8   | Generation of 65 Milliseconds and Hold            | 238   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.9   | Net Time Selection and Buffering                  | 239   |

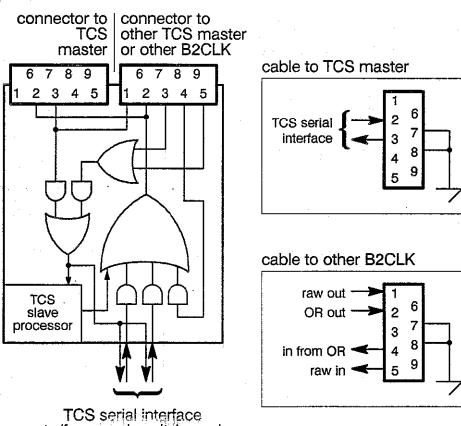

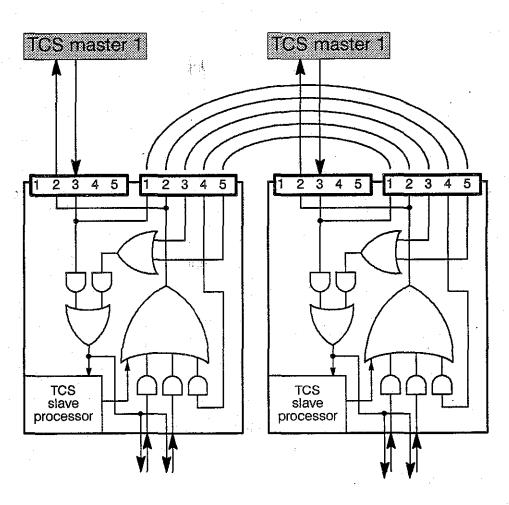

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.10  | TCS Serial Lines                                  | 239   |

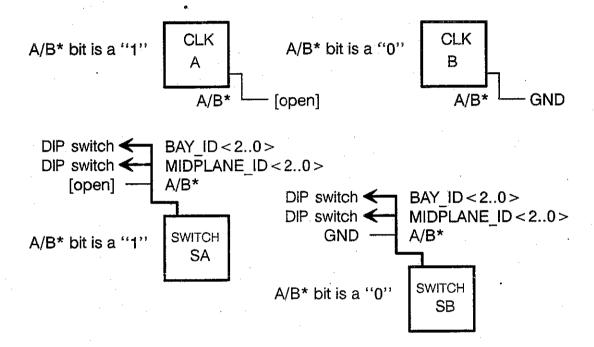

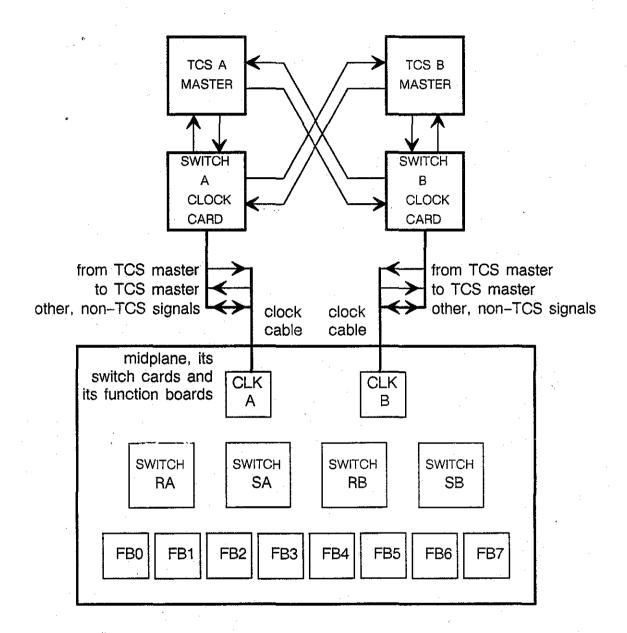

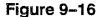

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.4.11  | Power                                             | 244   |