# AE6 Hardware External Reference Specification

Version 1.0 October, 1986 Richard Hausman Mark Hoke

.

3Com Corporation 1365 Shorebird Way P.O. Box 7390 Mountain View, California 94039 USA

# AE6 External Reference Specification

# Contents

|                                                                                                                                                                                                                                                                                                                        | Page                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                           | 2                                                        |

| Overview                                                                                                                                                                                                                                                                                                               |                                                          |

| Resources                                                                                                                                                                                                                                                                                                              | 3                                                        |

| Architecture                                                                                                                                                                                                                                                                                                           | 3                                                        |

| Network Interface Controller                                                                                                                                                                                                                                                                                           | 3                                                        |

| Local Memory                                                                                                                                                                                                                                                                                                           | 3                                                        |

| Address Assignments                                                                                                                                                                                                                                                                                                    | 4                                                        |

| NIC Register Addresses                                                                                                                                                                                                                                                                                                 | 5                                                        |

| Technical Specifications                                                                                                                                                                                                                                                                                               |                                                          |

| NuBus line usage<br>Voltage Tolerance<br>Isolation Voltage<br>Power Dissipation<br>Temperature Variation<br>Humidity<br>Transceiver Selection; BNC Mode<br>External Transceiver Mode<br>Jumper Pin Block<br>BNC Pin Assignments<br>15 Pin D Connector diagram<br>15 Pin D Connector signals<br>Programmatic Guidelines | 6<br>6<br>6<br>6<br>6<br>6<br>7<br>7<br>7<br>7<br>8<br>8 |

| Programmatic Recommendations and Notes                                                                                                                                                                                                                                                                                 | 9                                                        |

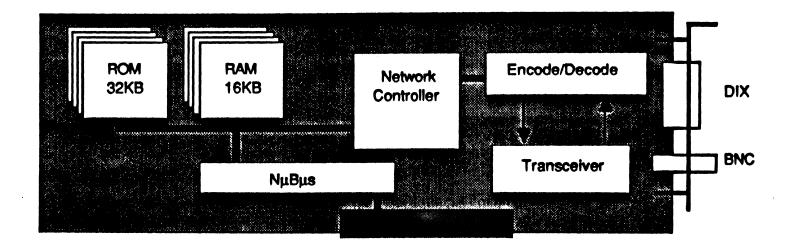

| Recommended Programming Sequences:<br>Initialization<br>Transmit<br>Receive<br>AE6 Block Diagram                                                                                                                                                                                                                       | 10<br>11<br>12<br>13                                     |

| ALO DIOCK DIAYIAM                                                                                                                                                                                                                                                                                                      | ТЭ                                                       |

# AE6 External Reference Specification

# Contents

| Introduction                                                                                                                                                                                                                                                                                                           | 2                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Overview                                                                                                                                                                                                                                                                                                               |                                                |

| Resources                                                                                                                                                                                                                                                                                                              | 3                                              |

| Architecture                                                                                                                                                                                                                                                                                                           | 3                                              |

| Network Interface Controller                                                                                                                                                                                                                                                                                           | 3                                              |

| Local Memory                                                                                                                                                                                                                                                                                                           | 3                                              |

| Address Assignments                                                                                                                                                                                                                                                                                                    | 4                                              |

| NIC Register Addresses                                                                                                                                                                                                                                                                                                 | 5                                              |

| Technical Specifications                                                                                                                                                                                                                                                                                               |                                                |

| NuBus line usage<br>Voltage Tolerance<br>Isolation Voltage<br>Power Dissipation<br>Temperature Variation<br>Humidity<br>Transceiver Selection; BNC Mode<br>External Transceiver Mode<br>Jumper Pin Block<br>BNC Pin Assignments<br>15 Pin D Connector diagram<br>15 Pin D Connector signals<br>Programmatic Guidelines | 6<br>6<br>6<br>6<br>6<br>7<br>7<br>7<br>8<br>8 |

| Programmatic Recommendations and Notes                                                                                                                                                                                                                                                                                 | 9                                              |

| Recommended Programming Sequences:<br>Initialization<br>Transmit<br>Receive<br>AE6 Block Diagram                                                                                                                                                                                                                       | 10<br>11<br>12<br>13                           |

| -                                                                                                                                                                                                                                                                                                                      |                                                |

Page

# Introduction:

The AE6 is a non-intelligent Ethernet adapter for the Apple NuBus personal computer. It makes use of a 3 chip LAN chipset from National Semiconductor Corp. The 3 chips are a Network Interface Controller (NIC), Serial Network Interface (SNI), and a Coax Transceiver Interface (CTI).

This document provides both technical specifications for the adapter card and programatic guidelines specific to the AE6 implementation. The document may be used in conjunction with National's specification document titled <u>DP8390/NS32490 Network</u> <u>Interface Controller</u> (preliminary edition dated July, 1986).

#### <u>Overview</u>

#### Resources:

- 16K bytes of RAM

- \* 32K bytes of ROM

- \* Apple NuBus interface

- \* on-board 'Thin Net' transceiver

- \* multipacket buffering

- \* 'Thick Net' tranceiver connection

#### Architecture:

The AE6 is a low cost Ethernet adapter designed to provide the Apple PC to Ethernet connection. It supports back to back packet reception with multi-packet buffering using a 16K byte dual ported local memory. The adapter is structured to allow host access for fault isolation.

#### Network Interface Controller:

The Network Interface Controller (NIC) performs all Media Access Control (MAC) layer functions for transmission and reception of Ethernet packets. The NIC provides buffer management that supervises storage of received packets to the local memory. During packet transmission, the NIC will insert preamble and sync to the transmitted packet, and optionally compute and append CRC bytes. Upon packet reception, the NIC accomplishes network address decoding and filtering, and performs CRC checking.

The NIC supports serial data transfers to the SNI and byte parallel register transfers to the host.

#### Local Memory:

The local memory consists of 16K bytes of static RAM segmented into transmit and receive buffers by setting NIC registers. Each segment is further divided into 256 byte pages. The Transmit Start Register points to the first page in the transmit buffer, and the Page Start and Page Stop registers define the page boundaries of the receive buffer. See National's specification <u>DP8390/NS32490 Network</u> <u>Interface Controller</u>, sections '7.0 Packet Reception' and '8.0 Packet Transmission' for details of buffer initializations, receive ring management, packet header structure, and transmission sequences.

3Com Corporation - Proprietary and Confidential AE6 External Reference Specification

page 3 of 13 10/07/86 Address Assignments:

The following addresses are to be used in accessing the AE6.

byte f Address Map F (ID) X F 7FFF +----------ROM (32 K bytes) + + + (word readable at every word @) + F (ID) x F 0000 F (ID) x E 0000 -----------+--------------NIC Control Registers 16 1-byte registers + + 16 1-byte registers + + + (byte readable at every 4th byte @) + + (reg 0 at 3C, 1 at 38, ... f at 00) + F (ID) x E 003C +-----F (ID) X D 3FFF Local Memory (16 K bytes) + + + + + (word addressable at every word @) + F (ID) x D 0000 | | 5th thru 8th (lowest order 16 bits) - address | 4th - 'D' = RAM, 'E' = NIC, 'F' = ROM3rd - a don't care nibble 2nd - NuBus slot ID character ('9' thru 'E': 6 slots) 1st (highest order) - always 'F', indicating card space

Note that the 8 nibbles (4 bits each) of address are interpreted as above.

# NIC Register Addresses:

On the AE6, the NIC's registers are addressed as follows:

| <u>Address</u> | RAO-RA3     | <u>Page 0 read</u>    | <u>Page 0 write</u>          |

|----------------|-------------|-----------------------|------------------------------|

| E003C          | <b>0</b> 0h | Command Register      | Command Register             |

| E0038          | 01h         | CLDA0                 | PSTART                       |

| E0034          | 02h         | CLDA1                 | PSTOP                        |

| E0030          | 03h         | Boundary              | Boundary Register            |

| E002C          | 04h         | Transmit Status       | Transmit Page Start          |

| E0028          | 05h         | NCR                   | TBCR0 Register               |

| E0024          | 06h         | FIFO                  | TBCR1 Register               |

| E0020          | 07h         | Interrupt Status      | Interrupt Status             |

| E001C          | 08h         | CRDA0                 | RSARO                        |

| E0018          | 09h         | CRDA1                 | RSAR1                        |

| E0014          | OAh         | reserved              | RBCRO                        |

| E0010          | OBh         | reserved              | RBCR1                        |

| E000C          | 0Ch         | <b>Receive Status</b> | <b>Receive</b> Configuration |

| E0008          | ODh         | CNTRO                 | Transmit Configuration       |

| E0004          | OEh         | CNTR1                 | Data Configuration           |

| E0000          | OFh         | CNTR2                 | Interupt Mask Register       |

Assignments for page 1 and page 2 NIC registers follow the same RAO-RA3 to address translation (into E0000 - E003C range) as above list for page 0. The contents of the 2 highest order bits in the command register (PSO and PS1) define which page of registers is being read and written to thru addresses E0000 - E003C at any given time.

# Technical Specifications:

The following table lists characteristics of the input/output pins:

| NuBus Signal  | Sink Current | Source Current |

|---------------|--------------|----------------|

| ACK*          | 24mA         | - 0.5mA        |

| AD31* - AD16* | 64mA         | - 0.5mA        |

| AD15* - AD8*  | 24mA         | - 0.5mA        |

| AD7* - AD0*   | 24mA         | - 0.4mA        |

| CLK*          | 0            | - 1.4mA        |

| ID3* - ID0*   | 0            | - 1.1mA        |

| NMRQ*         | 24mA         | 0              |

| RESET*        | 0            | - 1.05mA       |

| START*        | 0            | - 0.75mA       |

| TMO*          | 24mA         | - 0.20uA       |

| TM1*          | 24mA         | - 0.25mA       |

### Voltage Tolerance

+5 Volts +/- 10% +12 volts +/- 5%

#### Isolation Voltage

500 Volts RMS (using onboard transceiver)

# Power Dissipation

€ +5 Volts 6.5 watts € +12 Volts 3.6 watts

#### **Temperature Variation**

0 - 50 degrees Celsius (operating)

### Humidity

10% - 90% non-condensing

page 6 of 13 10/07/86

# Tranceiver selection

### BNC Mode

To transmit and/or receive on " Thin Net " (RG-58 coax) place the blue jumper shorting block in position P5/P4. To confirm your selection verify that the LED (CR12) is illuminated.

# External Transceiver Mode

To transmit and/or receive on " Thick Net " place the blue jumper shorting block in position P5/P6.

# Jumper pin block

|       |        |            | RNAL<br>CEIVER | BNC<br>MODE |

|-------|--------|------------|----------------|-------------|

| Pin # | :      |            |                |             |

|       | •      | 1          | $\setminus$ /  | Υ.          |

| 7     |        | o          | 0              | 0           |

| 6     |        | 0          | ο              | 0           |

| 5     |        | ο          | ο              | 0           |

| 4     |        | 0          | 0              | 0           |

| 3     |        | 0          | ο              | 0           |

| 2     |        | 0          | 0              | 0           |

| 1     |        | ο          | Ο              | 0           |

|       | Label: | <b>P</b> 6 | <b>P</b> 5     | P4          |

### BNC Pin Assignments

| Pin # | P6          | <b>P</b> 5 | P4            |

|-------|-------------|------------|---------------|

|       |             |            |               |

| 7     | o (D +12v)  | o (+12v)   | o (BNC +12v)  |

| 6     | o (D coll+) | o (coll+)  | o (BNC coll+) |

| 5     | o (D coll-) | o (coll-)  | o (BNC coll-) |

| 4     | o (D rec+)  | o (rec+)   | o (BNC rec+)  |

| 3     | o (D rec-)  | o (rec-)   | o (BNC rec-)  |

| 2     | o (D xmit+) | o (xmit+)  | o (BNC xmit+) |

| 1     | o (D xmit-) | o (xmit-)  | o (BNC xmit-) |

| 15 Pin D Connector diagram: |           |          |           |          |           |          |           |          |           |          |           |          |          |          |

|-----------------------------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|----------|----------|

| (8)<br>0                    |           | (7)<br>0 |           | (6)<br>0 |           | (5)<br>0 |           | (4)<br>0 |           | (3)<br>0 |           | (2)<br>0 |          | (1)<br>0 |

|                             | (15)<br>0 |          | (14)<br>0 |          | (13)<br>0 |          | (12)<br>0 |          | (11)<br>0 |          | (10)<br>0 |          | (9)<br>0 |          |

| <u>Pin</u>                  | ŧ         | S        | ignal     |          | e         |          |           |          |           |          |           |          |          |          |

| 1                           |           |          | Grou      |          |           |          |           |          |           |          |           |          |          |          |

| 2<br>3                      |           | D coll+  |           |          |           |          |           |          |           |          |           |          |          |          |

| 3                           |           | D xmit+  |           |          |           |          |           |          |           |          |           |          |          |          |

| 4<br>5                      |           |          | Grou      |          |           |          |           |          |           |          |           |          |          |          |

| 5                           |           | D rec+   |           |          |           |          |           |          |           |          |           |          |          |          |

| 6                           |           | Ground   |           |          |           |          |           |          |           |          |           |          |          |          |

| 7                           |           | nc       |           |          |           |          |           |          |           |          |           |          |          |          |

| 8<br>9                      |           | Ground   |           |          |           |          |           |          |           |          |           |          |          |          |

| 9                           |           | D coll-  |           |          |           |          |           |          |           |          |           |          |          |          |

| 10                          |           | D xmit-  |           |          |           |          |           |          |           |          |           |          |          |          |

| 11                          |           |          | Grou      | nđ       |           |          |           |          |           |          |           |          |          |          |

| 12                          |           |          | D re      | c-       |           |          |           |          |           |          |           |          |          |          |

|                             |           |          |           | -        |           |          |           |          |           |          |           |          |          |          |

D +12v Ground

nc

13 14 15

# Programmatic Guidelines

### Programatic Recommendations and Notes:

- A. As setup for the Apple NuBus interface, direct access to local memory is provided to the host processor, and as such no use is made of the NIC's remote DMA channel nor of the NIC's Send Packet command for automatic unloading of the receive ring.

- B. Programming Sequences recommended below assume 16K bytes of local memory, segmented into transmit and receive buffers with the first 2 K bytes (D0000 - D07FF) assigned as transmit buffer and the remaining 14 K Bytes (D0800 - D3FFF) as a receive ring.

- C. The Interrupt Status Register is reset by writing FFh to itself. This results in the clearing of the 7 low order bits. Individual bit level resets are not currently possible. After each ISR reset, the IMR should be restored.

- D. In handling the removal of packets from the receive ring and the freeing of buffer space for additional packets, the Boundary pointer is used. Exercise care to make certain that the boundary register lags at least one behind the last freed buffer page.

- E. Interrupts to the host processor are masked off or enabled via the Interrupt Mask Register. The cause of the interrupt is presented in the Interrupt Status Register, whether the host interrupt is masked or enabled. This allows event servicing either via an interrupt service routine which checks the ISR to determine interupt cause, or via polling of the ISR.

- F. Special care should be taken in modifying the NIC Command Register. In particular, only a single command function may be modified on a single write to the Command Register. Thus, to change from Stop Mode (21h in the CR) to Start Mode with Transmit Packet (26h in the CR) one must first write 22h (changes from Stop to Start Mode) and then write 26h (adds the TXP, Transmit Packet command).

#### Recommended programming sequences:

#### A. Initialization Sequence:

- 1 Set Command Register to 21h (stop mode, page 0 registers).

- 2 Set Data Configuration Register to 29h.

- 3 Set Transmit Configuration Register to 00h.

- 4 Set Receive Configuration Register to 20h, Monitor mode.

- 5 Set Page Start Register to 08h.

- 6 Set Page Stop Register to 40h.

- 7 Set Boundary Register to 3Fh.

- 8 Set Command Register to 61h (move to page 1 registers).

- 9 Set Current Register to 08h.

- 10 Set 6 Physical Address Registers to the node's assigned address.

- 11 Set 8 Multicast Address Registers to the node's assigned multicast bits.

- 12 Set Command Register to 21h (back to page 0).

- 13 Reset Interrupt Status Register by writing FFh.

- 14 Set Interrupt Mask Register to enable desired interrupts.

- 15 Ready host software to receive interrupts.

- 16 Set Command Register to 22h (start mode).

- 17 Set Receive Configuration Register to desired packets.

#### B. <u>Transmit Sequence:</u>

- 1 Load the packet into the transmit buffer beginning on a 256 byte page boundary.

- 2 Set the Transmit Configuration Register (to 0 for normal operation).

- 3 Set the Transmit Page Start Register to point to the beginning of the packet in the transmit buffer.

- 4 Load the Transmit Byte Count Registers (low and high bytes) to the length of the packet to be transmitted.

- 5 Set the Interrupt Mask Register transmit interrupt bit(s), if an interrupt routine is to handle completed and/or errored transmissions.

- 6 Set the Command Register to 22h to start the NIC, if it is not already started. Then set the Command register to 26h to initiate transmission of the packet.

- 7 Upon completion, status indications are available in the ISR and the Transmit Status Register, and interrupts as programmed into the IMR will occur.

#### C. <u>Receive Sequence:</u>

- 1 Be certain buffer ring inits are completed as in Initialization Sequence above.

- 2 Set the Interrupt Mask Register receive interrupt bit(s), if an interrupt routine is to handle completed and/or errored receptions.

- 3 Set the Receive Configuration Register to receive desired packet types only while NIC is already started. (NIC should be in Monitor mode when started.) Reception will commence with the first packet sensed with appropriate destination address after setting the RCR.

- 4 Upon receipt of a packet, status indications are available in the ISR, the Receive Status Register, and the first byte of the ring packet header.

- 5 When all data for the packet has been processed, and local memory containing the packet may be freed for additional packets, set the Boundary Register to point to the last page of this finished packet. (This keeps Boundary 1 behind where we expect to next find a packet.)