Writing Device Drivers with GPIO Calls 000959-A00

apollo

# Writing Device Drivers with GPIO Calls

Order No. 000959-A00

Apollo Computer Inc. 330 Billerica Road Chelmsford, MA 01824 Confidential and Proprietary. Copyright © 1981, 1982, 1983, 1984, 1985, 1986, 1987, 1988 Apollo Computer, Inc., Chelmsford, Massachusetts. Unpublished -- rights reserved under the Copyright Laws of the United States. All Rights Reserved.

First Printing:November 1981Latest Printing:July 1988

This document was produced using the Interleaf Technical Publishing Software (TPS) and the InterCAP Illustrator I Technical Illustrating System, a product of InterCAP Graphics Systems Corporation. Interleaf and TPS are trademarks of Interleaf, Inc.

Apollo and Domain are registered trademarks of Apollo Computer Inc.

3Com is a registered trademark of 3Com Corporation.

ETHERNET is a registered trademark of Xerox Corporation.

IMAGEN is a registered trademark of IMAGEN Corporation.

MULTIBUS is a trademark of Intel Corporation.

PC AT and PC XT are registered trademarks of International Business Machines Corporation.

UNIX is a registered trademark of AT&T in the USA and other countries.

VERSATEC is registered trademark of VERSATEC, Inc.

3DGMR, Aegis, D3M, DGR, Domain/Access, Domain/Ada, Domain/Bridge, Domain/C, Domain/ComController, Domain/CommonLISP, Domain/CORE, Domain/Debug, Domain/DFL, Domain/Dialogue, Domain/DQC, Domain/IX, Domain/Laser-26, Domain/LISP, Domain/PAK, Domain/PCC, Domain/PCI, Domain/SNA, Domain X.25, DPSS, DPSS/Mail, DSEE, FPX, GMR, GPR, GSR, NLS, Network Computing Kernel, Network Computing System, Network License Server, Open Dialogue, Open Network Toolkit, Open System Toolkit, Personal Supercomputer, Personal Super Workstation, Personal Workstation, Series 3000, Series 4000, Series 10000, and VCD-8 are trademarks of Apollo Computer Inc.

Apollo Computer Inc. reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should in all cases consult Apollo Computer Inc. to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF APOLLO COMPUTER INC. HARDWARE PRODUCTS AND THE LICENSING OF APOLLO COMPUTER INC. SOFTWARE PROGRAMS CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN APOLLO COMPUTER INC. AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS PUBLICATION, INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY APOLLO COMPUTER INC. FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY BY APOLLO COMPUTER INC. WHATSOEVER.

IN NO EVENT SHALL APOLLO COMPUTER INC. BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATING TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF APOLLO COMPUTER INC. HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

THE SOFTWARE PROGRAMS DESCRIBED IN THIS DOCUMENT ARE CONFIDENTIAL INFORMATION AND PROPRIETARY PRODUCTS OF APOLLO COMPUTER INC. OR ITS LICENSORS.

## Preface

Writing Device Drivers with GPIO Calls describes how to write device drivers for Domain® nodes, using the General Purpose Input/Output (GPIO) software package.

## Audience

This manual is intended for programmers who must write drivers for devices that Apollo $^{\textcircled{B}}$  does not support. Readers of this manual should be familiar with the hardware of the I/O device and with its software requirements, and should have a working knowledge of Pascal or C.

#### Organization

We've organized this manual as follows:

| Part 1    | I/O Hardware and Software                                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Describes the MULTIBUS* interface with Domain nodes, address translation between MULTIBUS memory and processor memory, and the rules for configuring MULTIBUS controllers. |

| Chapter 2 | Describes the VMEbus and its interface with our system to help you to write drivers for VMEbus devices.                                                                    |

<sup>\*</sup> MULTIBUS is a trademark of the Intel Corporation.

| Chapter 3  | Describes the PC AT* compatible bus and its interface with our system to help you to write drivers for PC AT devices.          |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4  | Provides an overview of the major components of I/O software (that is, the application, GPIO software, and the device driver). |

| Part 2     | Writing a Driver                                                                                                               |

| Chapter 5  | Describes the different types of insert files that you can include in your driver and how to set them up.                      |

| Chapter 6  | Describes the call side of the driver and how to write the routines that belong there.                                         |

| Chapter 7  | Describes how to transfer data using DMA, memory mapped I/O, and programmed I/O.                                               |

| Chapter 8  | Describes the interrupt side of the driver and different approaches to processing interrupts.                                  |

| Chapter 9  | Describes how to construct a global driver.                                                                                    |

| Chapter 10 | Describes how to bind and debug the driver.                                                                                    |

| Chapter 11 | Describes how to build the device descriptor file.                                                                             |

| Chapter 12 | Describes how to acquire and release the device.                                                                               |

| Part 3     | Reference Information                                                                                                          |

| Appendix A | Describes the GPIO commands that the user invokes to run the driver.                                                           |

| Appendix B | Describes the calling format and parameters of the GPIO routines.                                                              |

| Appendix C | Provides some tips on setting up the CSR page and using data types in C.                                                       |

| Appendix D | Provides performance and timing information that relates to driver execution on our operating system.                          |

| Appendix E | Provides a program listing of a device driver coded in C.                                                                      |

| Appendix F | Provides a program listing of a device driver coded in Pascal.                                                                 |

|            |                                                                                                                                |

A glossary of terms appears at the back of the manual.

<sup>\*</sup> PC AT is a registered trademark of International Business Machines Corporation.

#### **Summary of Technical Changes**

This manual has been revised for Software Release 10.

#### **Related Manuals**

The file /install/doc/apollo/os.v.latest software release number\_\_\_manuals lists current titles and revisions for all available manuals.

For example, at SR10.0 refer to /install/doc/apollo/os.v.10.0\_manuals to check that you are using the correct version of manuals. You may also want to use this file to check that you have ordered all of the manuals that you need.

(If you are using the Aegis environment, you can access the same information through the Help system by typing help manuals.)

Refer to the *Domain Documentation Quick Reference* (002685) and the *Domain Documentation Master Index* (011242) for a complete list of related documents. For more information on GPIO, refer to the following documents:

The Aegis Command Reference (002547) manual describes the command environment as well as the function and format of the commands that users can invoke.

The DN5xx-T Workstations and DSP500-T Server Technical Reference (009491) manual and the DN5xx-T Workstations and DSP500-T Server Hardware Architecture Handbook (009490) describe our implementation of the VMEbus.

The *Domain Binder and Librarian Reference* (004977) manual describes how to use the Domain binder to combine several object modules (for example, a call library and an interrupt library) into one executable object module.

The Domain C Language Reference (002093) and Domain C Library (CLIB) Reference (005805) manuals describe our implementation of the C language.

The Domain Distributed Debugging Environment (Domain/DDE) Reference (011024) manual describes how to use DDE.

The *Domain/OS Calls Reference* manuals, Volume 1 (007196) and Volume 2 (012886) describe the calling syntax for the system services that your driver can call.

The Domain Pascal Language Reference (000792) manual describes our implementation of the Pascal language. Appendix C lists our extensions to Standard Pascal.

The Domain Personal Workstations and Servers Technical Reference (008778) and the Domain Personal Workstations and Servers Hardware Architecture Handbook (007861) describe our implementation of the PC AT compatible bus.

The *IEEE Standard Microcomputer System Bus* (IEEE-796 specification) provides detailed information about the MULTIBUS.

The Installing Input/Output (I/O) Devices for Domain Nodes (008268) manual describes the hardware requirements for attaching peripheral devices to the Domain system bus.

The *Managing SysV System Software* (010851) manual describes how to create the SysV network environment, protect network software, and maintain and troubleshoot the network.

The Microsystem Components Handbook (230843) is published by Intel.

The *Programming with Domain/OS Calls* (005506) manual describes the general purpose Domain/OS system calls that you can use to perform system services for your driver.

The Using the OPEN System Toolkit to Extend Your Domain Streams (008863) manual describes how to extend the Streams facility so that it performs input and output for new types of files and devices.

#### **Problems, Questions, and Suggestions**

We appreciate comments from the people who use our system. To make it easy for you to communicate with us, we provide the Apollo Problem Reporting (APR) system for comments related to hardware, software, and documentation. By using this formal channel, you make it easy for us to respond to your comments.

You can get more information about how to submit an APR by consulting the appropriate Command Reference manual for your environment (Aegis<sup>M</sup>, BSD, or SysV). Refer to the **mkapr** (make apollo problem report) shell command description. You can view the same description online by typing:

\$ man mkapr (in the SysV environment)

% man mkapr (in the BSD environment)

**\$ help mkapr** (in the Aegis environment)

Alternatively, you may use the Reader's Response Form at the back of this manual to submit comments about the manual.

## **Documentation Conventions**

Unless otherwise noted in the text, this manual uses the following symbolic conventions:

| literal values       | Bold words or characters in formats and command descriptions<br>represent commands or keywords that you must use literally.<br>Pathnames are also in bold. Bold words in text indicate the first<br>use of a new term. |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| user–supplied values | Italic words or characters in formats and command descriptions represent values that you must supply.                                                                                                                  |

| example user input   | In examples, information that the user enters appears in bold.                                                                                                                                                         |

| output               | Information that the system displays appears in this typeface.                                                                                                                                                         |

| [ ]                  | Square brackets enclose optional items in formats and command descriptions. In sample Pascal statements, square brackets assume their Pascal meanings.                                                                 |

| { }                  | Braces enclose a list from which you must choose an item in for-<br>mats and command descriptions. In sample Pascal statements,<br>braces assume their Pascal meanings.                                                |

| 1                    | A vertical bar separates items in a list of choices.                                                                                                                                                                   |

| < >                  | Angle brackets enclose the name of a key on the keyboard.                                                                                                                                                              |

| CTRL/                | The notation CTRL/ followed by the name of a key indicates a control character sequence. Hold down <ctrl> while you press the key.</ctrl>                                                                              |

|                      | Horizontal ellipsis points indicate that you can repeat the preced-<br>ing item one or more times.                                                                                                                     |

|                      | Vertical ellipsis points mean that irrelevant parts of a figure<br>or example have been omitted.                                                                                                                       |

|                      | This symbol indicates the end of a chapter.                                                                                                                                                                            |

# Contents

## Chapter 1I/O Bus Structures: the MULTIBUS

| 1.1 MULTIBUS Compliance Levels                            | 1–2  |

|-----------------------------------------------------------|------|

| 1.1.1 Bus Control                                         | 1-3  |

| 1.1.2 Data Path                                           | 1-3  |

| 1.1.3 Memory Address Path                                 | 1-3  |

| 1.1.4 I/O Address Path                                    | 1-4  |

| 1.1.5 Interrupt Request Lines                             | 1-4  |

| 1.1.6 Bus Request Arbitration Resolution                  | 1-4  |

| 1.2 MULTIBUS Address Translation                          | 1-4  |

| 1.2.1 Address Translation from Processor to MULTIBUS      | 1-4  |

| 1.2.1.1 Programmed I/O                                    | 1-5  |

| 1.2.1.2 Memory–Mapped I/O                                 | 1-6  |

| 1.2.2 Address Translation from MULTIBUS to Processor: DMA | 1-6  |

| 1.3 Configuring MULTIBUS Controllers                      | 1–7  |

| 1.3.1 Nodes With a 16-Bit MULTIBUS                        | 1-8  |

| 1.3.1.1 Assigning CSR Addresses                           | 1-8  |

| 1.3.1.2 Configuring Controller Memory                     | 1-10 |

| 1.3.1.3 Configuring Controller Address Lines              | 1-10 |

| 1.3.1.4 Using Interrupt Request Lines                     | 1-10 |

| 1.3.2 Nodes With a 20-Bit MULTIBUS                        | 1–11 |

| 1.3.2.1 Assigning CSR Addresses                           | 1–11 |

| 1.3.2.2 Configuring Controller Memory                     | 1–11 |

| 1.3.2.3 Configuring Controller Address Lines              | 1-12 |

| 1.3.2.4 Using Interrupt Request Lines                     | 1–12 |

| 1.4 Byte Swapping                                         | 1–12 |

## Chapter 2 I/O Bus Structures: the VMEbus

| 2.1   | Address Space Allocation           | 2–2 |

|-------|------------------------------------|-----|

| 2.2   | Bus Grant Level                    | 2–2 |

| 2.3   | Address Modifiers                  | 2-2 |

| 2.4   | Interrupt Level                    | 2-3 |

| 2.5   | Status/ID Byte                     | 2-3 |

| 2.6   | Software Considerations            | 2-3 |

| 2.6.1 | Wiring for DMA: pbu_\$wire_special | 2-4 |

| 2.6.2 | Creating a DDF for a VMEbus Device | 2-4 |

## Chapter 3 I/O Bus Structures: the IBM PC AT Compatible Bus

| 3.1   | PC AT Compatible Address Space               | 3-2  |

|-------|----------------------------------------------|------|

| 3.1.1 | I/O Address Space                            | 3-2  |

| 3.1.2 | Memory Space                                 | 3-5  |

| 3.2   | Unit Numbering                               | 3-6  |

| 3.3   | Testing for Controller Presence              | 3-8  |

| 3.4   | DMA and IRQ Lines                            | 3-8  |

| 3.5   | Byte Swapping                                | 3-9  |

| 3.6   | Software Considerations                      | 3-10 |

| 3.7   | Creating a DDF for a PC AT Compatible Device | 3-11 |

## Chapter 4 Overview of I/O Software

| 4.1     | Application Program                            | 4-2 |

|---------|------------------------------------------------|-----|

| 4.2     | Streams Manager                                | 4-2 |

| 4.3     | GPIO Commands and Routines                     | 4-3 |

| 4.4     | Device Driver                                  | 4-4 |

| 4.4.1   | Driver Functions                               | 4-4 |

| 4.4.2   | Major Components of a Driver                   | 4-4 |

| 4.4.3   | Operation of a Driver: A Dry Run of bm_example | 4-6 |

| 4.4.3.1 | Initialization                                 | 4-7 |

| 4.4.3.2 | Command Processing                             | 4-7 |

| 4.4.3.3 | Interrupt Handling                             | 4-8 |

| 4.4.3.4 | Cleanup                                        | 4-8 |

| 4.4.4   | Driver Checklist                               | 4–9 |

## Chapter 5 Insert Files

| 5.1     | System Insert Files          | 5-2 |

|---------|------------------------------|-----|

| 5.2     | Driver-Specific Insert Files | 5-2 |

| 5.2.1   | Private Insert File          | 5-3 |

| 5.2.1.1 | CSR Page                     | 5-3 |

| 5.2.1.2 | Driver Control Block         | 5-5 |

| 5.2.1.3 | Internal Driver Routines     | 5-6 |

| 5.2.2   | Public Insert File           | 5-6 |

## Chapter 6 Call–Side Routines

| 6.1     | Initialization                                       | 6-2  |

|---------|------------------------------------------------------|------|

| 6.1.1   | Initialization Routine Format                        | 6-3  |

| 6.1.2   | Initializing Driver Internal Storage                 | 6-4  |

| 6.1.3   | Testing for Device Presence                          | 6-4  |

| 6.1.4   | Initializing Controller Data Structures              | 6-6  |

| 6.1.4.1 | Allocating Hard-Wired Control Blocks on the MULTIBUS | 6-7  |

| 6.1.4.2 | Defining Page-Aligned Control Blocks                 | 6-7  |

| 6.2     | Command Processing                                   | 6-8  |

| 6.3     | Waiting for Device Interrupts                        | 6-10 |

| 6.3.1   | Using pbu_\$wait                                     | 6-10 |

| 6.3.2   | Using pbu_\$get_ec and ec2_\$wait                    | 6-12 |

| 6.4     | Performing Cleanup Functions                         | 6-14 |

## Chapter 7 Transferring Data

| 7.1     | DMA Transfers                                | 7–2  |

|---------|----------------------------------------------|------|

| 7.1.1   | Using the I/O Map to Perform DMA Transfers   | 7–2  |

| 7.1.1.1 | Allocating Bus Address Space                 | 7–2  |

| 7.1.1.2 | Wiring I/O Buffers                           | 7–3  |

| 7.1.1.3 | Setting Up the I/O Map                       | 7-4  |

| 7.1.1.4 | Preallocating I/O Resources                  | 7–5  |

| 7.1.1.5 | Dynamic Resource Allocation                  | 7-6  |

| 7.1.1.6 | Scatter-Gather Operations                    | 7-6  |

| 7.1.2   | Starting and Stopping a DMA Operation on the |      |

|         | PC AT Compatible Bus                         | 7-8  |

| 7.1.2.1 | DMA Transfers Without the I/O Map            | 7-9  |

| 7.1.2.2 | DMA Transfers With the I/O Map               | 7-14 |

| 7.1.3   | Releasing I/O Resources After a DMA Transfer | 7-15 |

| 7.1.3.1 | Deallocating the I/O Map                     | 7-15 |

| 7.1.3.2 | Unwiring the I/O Buffer                      | 7-16 |

| 7.1.4   | Releasing I/O Resources During Faults        | 7-16 |

| 7.2   | Memory–Mapped Transfers       | 7–17 |

|-------|-------------------------------|------|

| 7.2.1 | Referencing Controller Memory | 7-18 |

| 7.2.2 | Mapping Controller Memory     | 7–19 |

| 7.2.3 | Unmapping Controller Memory   | 7–20 |

| 7.3   | Programmed I/O                | 7–21 |

## Chapter 8 Interrupt–Side Routines

| 8.1     | Interrupt Side Restrictions                      | 8-1 |

|---------|--------------------------------------------------|-----|

| 8.2     | Interrupt Routine                                | 8-2 |

| 8.2.1   | Interrupt Routine Format                         | 8-3 |

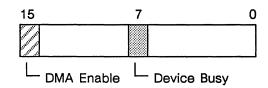

| 8.2.2   | Enabling and Disabling Device Interrupts         | 8-3 |

| 8.2.3   | Processing Device Interrupts                     | 8-4 |

| 8.2.3.1 | Processing by the System Interrupt Handler       | 8-5 |

| 8.2.3.2 | Processing by the User–Written Interrupt Routine | 8-5 |

| 8.2.4   | Faults in User–Written Interrupt Routines        | 8-6 |

| 8.2.5   | Mapping Buffers from the Interrupt Routine       | 8-7 |

| 8.3     | Starting an I/O Operation                        | 8-7 |

## Chapter 9 Global Drivers

| 9.1   | Controlling Multiple Processes | 9-2 |

|-------|--------------------------------|-----|

| 9.1.1 | Mutual Exclusion               | 9-2 |

| 9.1.2 | Synchronization                | 9-3 |

| 9.2   | Global Memory                  | 9-4 |

| 9.3   | Initialization and Cleanup     | 9-4 |

| 9.4   | Fault Handling                 | 9-4 |

| 9.5   | Loading and Unloading          | 9-5 |

| 9.6   | Multiple-Device Drivers        | 9-5 |

## Chapter 10 Building and Debugging

| 10.1 Building the Device Driver           | 10-1 |

|-------------------------------------------|------|

| 10.1.1 Compiling the Device Driver        | 10-1 |

| 10.1.2 Binding the Device Driver          | 10-2 |

| 10.1.2.1 Using Bind to Page Align Buffers | 10-3 |

| 10.1.2.2 System Globals                   | 10-4 |

| 10.2 Debugging the Device Driver          | 10-4 |

| 10.3 Debugging the Global Driver          | 10-6 |

## Chapter 11 Device Descriptor File

| 11.1   | Building a DDF in a Shell Script                    | 11-3 |

|--------|-----------------------------------------------------|------|

| 11.2   | Version 2 DDF                                       | 11-4 |

| 11.3   | Version 3 DDF                                       | 11–5 |

| 11.3.1 | DDF for a PC AT Compatible Device                   | 11-6 |

| 11.3.2 | DDF for a VMEbus Device                             | 11–7 |

| 11.3.3 | DDF for a Device Accessed Through a Streams Manager | 11-8 |

## Chapter 12 Acquiring and Releasing the Device

| 12.1   | Acquiring the Device                         | 12-1 |

|--------|----------------------------------------------|------|

| 12.1.1 | Using aqdev                                  | 12-2 |

| 12.1.2 | Acquiring a Device in Your Application       | 12-2 |

| 12.1.3 | Acquiring a Device with pbu_\$acquire_stream | 12-3 |

| 12.2   | Releasing the Device                         | 12-5 |

## Appendix A GPIO Commands

## Appendix B GPIO Routines

| B.1 | Data Types                    | <b>B-1</b>   |

|-----|-------------------------------|--------------|

| B.2 | GPIO Procedures and Functions | B-11         |

| B.3 | Error Messages                | <b>B-</b> 78 |

## Appendix C Programming Information

| C.1   | CSR Page                                 | C-1 |

|-------|------------------------------------------|-----|

| C.2   | Programming in C                         | C-3 |

| C.2.1 | Insert Files                             | C-3 |

| C.2.2 | Type int                                 | C-3 |

| C.2.3 | Boolean Values                           | C-3 |

| C.2.4 | Universal Pointer Type                   | C-4 |

| C.2.5 | Defining Globals                         | C-4 |

| C.3   | Considerations for Compiler Optimization | C-5 |

## Appendix D Performance Information

| D.1 | DMA Bandwidth                 | D-1 |

|-----|-------------------------------|-----|

| D.2 | Interrupt Processing Overhead | D-2 |

| D.3 | Setting Up DMA Buffers        | D-3 |

| D.4 | Timing Information            | D-4 |

## Appendix E Sample Driver in C

# E.1 bm.h E-2 E.2 bm\_lib.c E-7 E.3 bm\_int\_lib.c E-17 E.4 makefile E-21

## Appendix F Sample Driver in Pascal

| F.1 | bm.pvt.pas     | F-2  |

|-----|----------------|------|

| F.2 | bm.ins.pas     | F-4  |

| F.3 | bm_lib.pas     | F-6  |

| F.4 | bm_int_lib.pas | F-15 |

## Glossary

#### Index

## Figures

| 1-1 | Relationship Between a Domain Node and Peripheral Controllers | 1–1 |

|-----|---------------------------------------------------------------|-----|

| 1–2 | Mapping CSR Pages to MULTIBUS I/O Space                       | 1-5 |

| 1-3 | Mapping Processor Address Space to MULTIBUS Memory Space      | 1-6 |

| 1-4 | Mapping MULTIBUS Address Space to Processor Address Space     | 1–7 |

| 1–5 | 8-Bit Controller CSR Assignment                               | 1–9 |

| 2-1 | Relationship Between a Domain Node and Peripheral Controllers | 2–1 |

| 3–1 | Relationship Between a Domain Node and Peripheral Controllers | 3–2 |

| 3–2 | CSR Mapping Scheme for PC AT Compatible Devices               | 3-4 |

| 3–3 | Mapping a 16-Bit PC AT Address to Processor Address Space     | 3–5 |

| 4-1 | Interaction of I/O Software                                   | 4–2 |

| 4–2 | Driver Routines in bm_example                                 | 4–6 |

| 7–1 | Mapping Discontiguous Buffers                                 | 7–7 |

## Tables

| 1-1        | MULTIBUS Implementations on Node Models                                                                              | 1-2               |

|------------|----------------------------------------------------------------------------------------------------------------------|-------------------|

| 1-2<br>1-3 | MULTIBUS Address Space Used by Domain System-Supplied Devices<br>Allocation of Interrupt Request Lines               | 1-8<br>1-10       |

| 2-1        | Address Space Allocated for DN5xx-T VMEbus Devices                                                                   | 2–2               |

| 3–1<br>3–2 | I/O Address Space Allocated for Domain System–Supplied Devices<br>DN3000/DN4000 Physical Memory Allocated for Domain | 3–3               |

| 3–3<br>3–4 | System-Supplied DevicesAllocation of Unit Numbers on the DN3000Allocation of Unit Numbers on the DN4000              | 3-6<br>3-7<br>3-7 |

| 4-1        | GPIO Software                                                                                                        | 4-3               |

| 5-1        | System Insert Files                                                                                                  | 5-2               |

| 6-1        | pbu_\$wait Actions When Asynchronous Faults Are Inhibited/Enabled .                                                  | 6-12              |

| 11-1       | Required Options for Different DDF Versions                                                                          | 11–2              |

| B-1        | GPIO Procedures and Functions                                                                                        | B-11              |

| D-1<br>D-2 | CPU Times During Interrupt Processing<br>Timing for DN560, DSP80, DSP160, DN660, DN5xx-T,                            | D-2               |

|            | DN3000, and DN4000 Workstations                                                                                      | D-5               |

# Chapter 1 I/O Bus Structures: the MULTIBUS

This chapter describes MULTIBUS implementations currently available for Domain nodes, the theory of MULTIBUS address translation, how to configure a MULTIBUS controller, and byte swapping. For detailed information about the MULTIBUS, refer to the *IEEE Standard Microcomputer System Bus* (IEEE-796 specification). See the Preface for a complete list of related manuals and their order numbers.

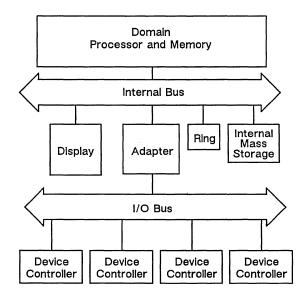

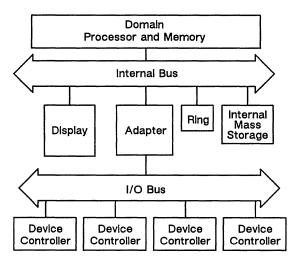

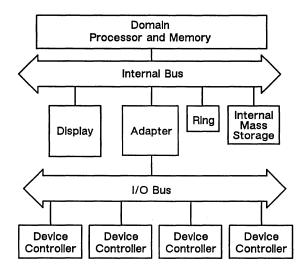

The I/O bus is the network of signal routes through which device controllers and the processor address one another and transfer data. The bus is, therefore, the key hardware component of a computer system's I/O structure. Figure 1–1 shows the relationship of the I/O bus to a Domain node and a set of controllers. The processor, memory, and memory management (address translation) subsystems are linked by an internal bus. Interface hardware connects this internal bus to the I/O bus. User-supplied and Domain systemsupplied device controllers attach to the I/O bus and, through the bus, link to the node.

Figure 1-1. Relationship Between a Domain Node and Peripheral Controllers

#### **1.1 MULTIBUS Compliance Levels**

The MULTIBUS supports compliance levels that allow for the varying capabilities of different computer systems. The levels are described in the *IEEE Standard Microcomputer System Bus* (IEEE-796 specification). To know the implementation available for a particular node model, refer to the section on MULTIBUS interfaces in the peripheral installation instructions or refer to the operating guide for the node model, if one is shipped with the node. If the peripheral installation instructions provide interface information for your node model, you will find the MULTIBUS implementation level available and specific hardware information for that node type. For node models that have an operating guide, you will find the same information in the guide. Table 1-1 lists the MULTIBUS implementation levels that we currently support for various node models.

| Node Type        | MULTIBUS Implementation                        | Compliance Level        |

|------------------|------------------------------------------------|-------------------------|

| DN660,<br>DSP160 | 16-bit MULTIBUS, serial arbitration priority   | MASTER D16 M16 I16 V0 L |

| DSP80<br>DSP90   | 20–bit MULTIBUS, parallel arbitration priority | MASTER D16 M20 I16 V0 L |

| DN5xx, DN5xx-T   | 20-bit MULTIBUS, serial arbitration priority   | MASTER D16 M20 I16 V0 L |

| Table 1-1. MULTIBUS Implementations on Node | Models |

|---------------------------------------------|--------|

|---------------------------------------------|--------|

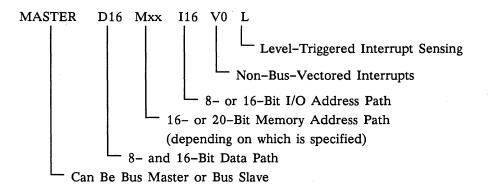

The notation used to specify the compliance level is interpreted as follows:

The following sections explain the compliance levels more fully, particularly the two levels that we currently support:

- MASTER D16 M16 I16 V0 L

- MASTER D16 M20 I16 V0 L

#### **1.1.1 Bus Control**

A device controller is bus master when it acquires control of the bus, and bus slave when it carries out commands or decodes addresses presented by another device acting as bus master. Domain nodes with 16-bit MULTIBUS implementation allow both the central processor and any attached controller to act as bus masters:

- When the processor is bus master, it can address 32 KB of MULTIBUS I/O space and 32 KB of MULTIBUS memory space (0-7FFF).

- When a controller is bus master, the processor must be the only slave; it responds to addresses in the range 0-FFFF (64K).

Domain nodes with 20-bit MULTIBUS implementations also allow either the processor or the controllers to act as bus masters:

- When the processor is bus master, it can address 64 KB of MULTIBUS I/O space and 1 MB of MULTIBUS memory space.

- When a controller is bus master, either the processor or another controller on the MULTIBUS may be the slave; up to 1 MB of address space is available.

- NOTE: Although the full 64 KB of I/O address space is implemented on nodes with a 20-bit MULTIBUS, user Control and Status Register (CSR) page addresses are restricted to the first 16 KB of MULTIBUS I/O space (see Subsection 1.3.2).

#### 1.1.2 Data Path

For all Domain nodes, the MULTIBUS supports either an 8- or a 16-bit bidirectional data path (D16) for the transfer of data from MULTIBUS memory or I/O addresses. The bus master drives the data lines on a write operation, and the slave drives them on a read operation (memory or I/O).

#### 1.1.3 Memory Address Path

Under compliance level MASTER D16 M16 I16 V0 L, the MULTIBUS supports 16-bit memory addresses on the memory address path; whereas under compliance level MASTER D16 M20 I16 V0 L, the MULTIBUS supports 20-bit memory addresses. We use the terms *16-bit MULTIBUS* or 20-bit MULTIBUS to describe nodes whose I/O hardware supports 16- or 20-bit memory addresses.

**NOTE:** If a node with a 20-bit MULTIBUS is fully configured with 3 MB of memory, the upper half (512 KB) of the address space is unavailable for memory-mapped operations.

#### 1.1.4 I/O Address Path

For all Domain nodes, the MULTIBUS I/O address path supports 8-bit or 16-bit I/O addresses (I16).

#### **1.1.5 Interrupt Request Lines**

The MULTIBUS provides eight interrupt request lines: line 0 is the highest priority line and line 7 the lowest. A device generates an interrupt by activating its assigned interrupt request line. The MULTIBUS on all Domain nodes uses nonbus-vectored interrupts (V0). With this type of interrupt, the device raises its interrupt line without sending its interrupt vector address over the bus; the I/O hardware generates the interrupt vector address to identify the interrupting device to the processor.

#### 1.1.6 Bus Request Arbitration Resolution

MULTIBUS devices can arbitrate for bus control by using serial or parallel priority resolution. All Domain 16-bit MULTIBUS implementations use a serial scheme. Some 20-bit implementations use a parallel scheme and others use a serial scheme. See the peripheral installation instructions for the priority resolution scheme used by each node type.

With serial resolution, device controllers are daisy-chained together. The first device in the daisy-chain has highest priority. With parallel resolution, arbitration logic in the I/O hardware determines the device that gets highest priority, instead of the device's position relative to other controllers. See the node's operating guide or peripheral installation instructions for the priority assignments supplied by our I/O hardware for nodes that use parallel arbitration resolution.

#### **1.2 MULTIBUS Address Translation**

Device drivers on nodes with a 16-bit MULTIBUS can allocate up to 32 pages of processor address space to reference MULTIBUS address space; drivers on nodes with a 20-bit MULTIBUS can allocate up to 1024 pages of processor address space. On any node, the I/O hardware translates addresses between MULTIBUS and processor memory in units of 1024-byte pages. The method of translation depends upon whether processor addresses are to be translated into MULTIBUS addresses (initiated by the processor) or MULTIBUS addresses into processor addresses (initiated by the controller).

#### **1.2.1 Address Translation from Processor to MULTIBUS**

When the processor acts as bus master, it initiates a read or write to MULTIBUS address space, and the I/O hardware automatically translates the virtual address that refers to processor address space into a physical address.

This physical address refers to either one of two separate address spaces supported by the MULTIBUS, depending on the kind of I/O operation:

- I/O space: Used for programmed I/O data transfers

- Memory space: Used for memory-mapped data transfers

Much of what follows concerning processor-to-MULTIBUS address translation depends on this concept of two separate MULTIBUS address spaces.

#### 1.2.1.1 Programmed I/O

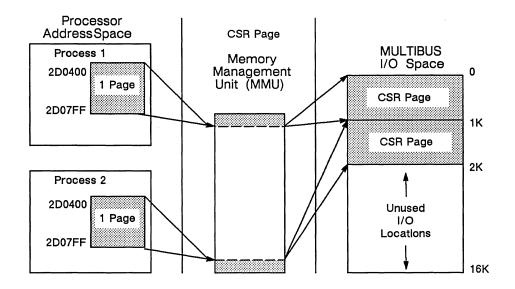

In programmed I/O, data is transferred as single words or bytes by means of Control and Status Registers (CSRs) on the controller. Device drivers pass or reference data by using these CSRs.

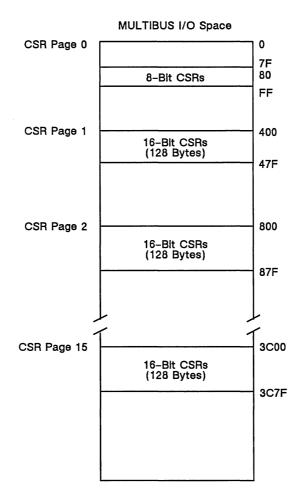

References to the MULTIBUS I/O space are actually references to a controller's CSRs. A page from MULTIBUS I/O space is allocated to them and becomes the controller's CSR page. Section 1.3 describes how to allocate pages of MULTIBUS I/O space for controller CSRs.

When the device is acquired, the GPIO device acquisition routine, **pbu\_\$acquire**, automatically maps the CSR page to processor address space (that is, establishes a correspondence between MULTIBUS I/O space and processor address space) and passes a pointer to the driver initialization routine. The device driver can then obtain controller status and activate the controller by using the pointer to read and write to the mapped CSRs. Figure 1–2 shows how CSR pages mapped to processor address space correspond to MUL-TIBUS I/O locations.

Figure 1-2. Mapping CSR Pages to MULTIBUS I/O Space

#### 1.2.1.2 Memory-Mapped I/O

In memory-mapped I/O, the controller appears to the processor as so many memory locations, and the processor performs I/O operations by storing data to or fetching it from controller memory.

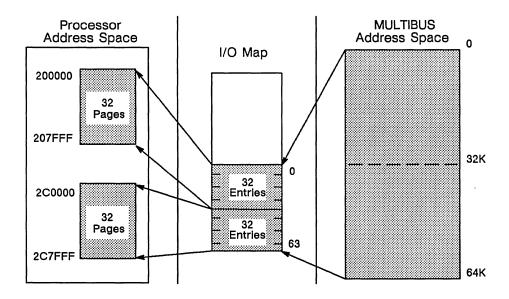

Device drivers gain access to areas of MULTIBUS memory space by calling GPIO routines. These routines map areas of processor address space and particular sections of MULTI-BUS memory space. Device drivers next call the GPIO routines that map a controller's memory to processor address space. The drivers can then read and write to controller memory through reads and writes in processor address space. Figure 1-3 illustrates how controller memory is mapped to processor address space.

Figure 1-3. Mapping Processor Address Space to MULTIBUS Memory Space

#### 1.2.2 Address Translation from MULTIBUS to Processor: DMA

A Direct Memory Access (DMA) operation contrasts with programmed I/O and memory mapping in the following ways:

- The controller is the bus master.

- Address translation proceeds from the MULTIBUS to the processor.

- A bus address (referred to as an *iova*) is translated into a physical address in processor memory.

Once activated by its device driver, a DMA controller can transfer large amounts of data directly between processor memory and MULTIBUS address space. The job of translating references to MULTIBUS address space into references to processor address space is performed by a data structure called the I/O map. The I/O map contains entries that each map one page of processor memory. The device driver calls GPIO routines to allocate I/O map entries for the DMA. Chapter 7, Section 7.1 describes these GPIO routines in more detail.

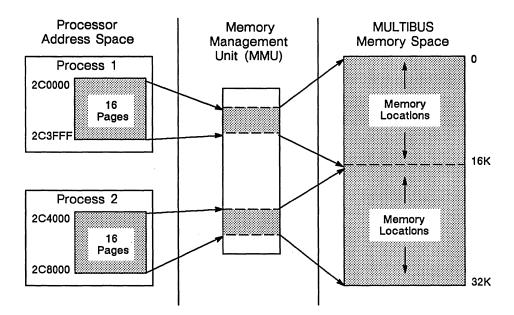

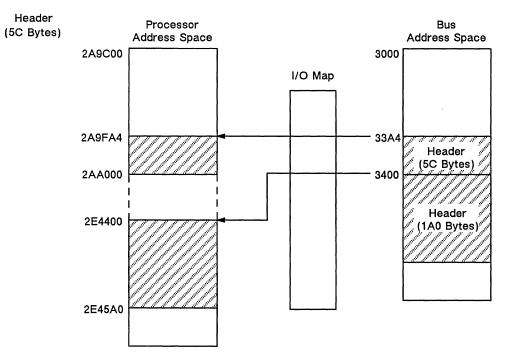

For nodes with a 16-bit MULTIBUS, controllers can transfer up to 64 pages of data between the MULTIBUS and the processor at one time. For nodes with a 20-bit MULTI-BUS, controllers can transfer up to 1024 pages at one time. Figure 1-4 illustrates a DMA transfer of 64 pages of MULTIBUS address space to two different areas of processor address space.

Figure 1-4. Mapping MULTIBUS Address Space to Processor Address Space

## **1.3 Configuring MULTIBUS Controllers**

When you supply your own MULTIBUS controllers for use with a Domain node, you must observe basic configuration rules. The following subsections summarize controller configuration rules for nodes with a 16- or 20-bit MULTIBUS. Table 1-2 lists the address ranges reserved for Domain system-supplied devices.

| Table 1–2. MULTIBUS  | Address Space      | e Used by | Domain | System-Supplied Devices |

|----------------------|--------------------|-----------|--------|-------------------------|

| 10000 1 2. 110211200 | 1 August 000 Optac | 0 0000 09 | 20     |                         |

| Devices                                                                                                                                                                                                                      | Addresses Used                                                                                                                                                                                                                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Domain/ComController ™                                                                                                                                                                                                       | Memory pages 4000 to 7F00 and I/O page 0800 are always in use on a 16-bit MULTIBUS.                                                                                                                                                                                            |  |

| ETHERNET* Interlan Board                                                                                                                                                                                                     | Uses three dynamically allocated memory pages for DMA I/O address space 080-08F every 256 bytes (180-18F, 280-28F, 380-38F, etc.).                                                                                                                                             |  |

| FSD-500                                                                                                                                                                                                                      | Memory pages F400 and F800 on a 16-bit MULTIBUS or<br>memory pages 6F400 and 6F800 on a 20-bit MULTIBUS are<br>used by the mnemonic debugger, then released during operating<br>initialization. The operating system uses two dynamically allo-<br>cated memory pages for DMA. |  |

| Magtape                                                                                                                                                                                                                      | Uses 19 dynamically allocated memory pages for DMA, plus memory page FC00 (used during initialization, then released).                                                                                                                                                         |  |

| Storage Module Device (SMD)                                                                                                                                                                                                  | Memory pages F400 and F800 on a 16-bit MULTIBUS or<br>memory pages 6F400 and 6F800 on a 20-bit MULTIBUS are<br>always reserved, whether or not SMD is in use.                                                                                                                  |  |

| VERSATEC** and IMAGEN***<br>Printers                                                                                                                                                                                         | Uses five dynamically allocated memory pages for DMA; I/O page 400 reserved.                                                                                                                                                                                                   |  |

| X.25                                                                                                                                                                                                                         | Pages 7000–7C00 are always in use.                                                                                                                                                                                                                                             |  |

| <ul> <li>* ETHERNET is a registered trademark of the Xerox Corporation.</li> <li>** VERSATEC is a registered trademark of VERSATEC, Inc.</li> <li>*** IMAGEN is a registered trademark of the IMAGEN Corporation.</li> </ul> |                                                                                                                                                                                                                                                                                |  |

#### 1.3.1 Nodes With a 16-Bit MULTIBUS

You can connect only one 8-bit controller to a 16-bit MULTIBUS; the others must be 16-bit controllers.

#### 1.3.1.1 Assigning CSR Addresses

Each controller is allocated one page of MULTIBUS I/O space for its set of CSR addresses. MULTIBUS I/O space is divided into two 16-page sections. The lower 16-page section is reserved for the CSR pages of user-supplied controllers; the top 16-page section is reserved for the CSR pages of controllers that Apollo supplies. You can assign the CSR addresses of a 16-bit controller to any page within the 16 pages of MULTIBUS I/O space (0-3FFF hex) allocated to user-supplied controllers. Word (2-byte) and longword (4-byte) registers must reside on even-byte addresses. If an 8-bit controller is present on your system, its CSR addresses should fall between 80 and FF (hex) on the first page (page 0) of the allocated I/O address space. Of the remaining pages (1-15), 16-bit controllers must occupy only the first 128 bytes (0-7F) of each page. This arrangement is necessary because 8-bit controllers respond to any address in the range 0-FF, modulo 255. For example, an 8-bit controller CSR at address 80 responds to page 0 addresses of 80, 180, 280, 380; page 1 addresses of 480, 580, 680, 780; and so on. By restricting 8-bit controller CSRs to the range 80-FF, all addresses in the range 0-7F become available to 16-bit controllers. Refer to Chapter 11, Section 11.2 for a description of how to set the address of an 8-bit controller CSR.

If you do not have an 8-bit controller on your system and never plan to add one, you can configure a 16-bit controller to respond to any addresses (0-3FF) on its CSR page. Again, word and longword registers must reside on even-byte addresses.

Figure 1-5 illustrates the allocation of CSR addresses when an 8-bit controller is present.

Figure 1-5. 8-Bit Controller CSR Assignment

#### **1.3.1.2 Configuring Controller Memory**

Drivers call GPIO routines to map a controller's memory to processor address space so that programs can refer to the controller's memory directly. When configuring controller memory on nodes with a 16-bit MULTIBUS, the following rules apply:

- Controller memory must begin on a page boundary and must reside completely in the first 32 KB (0-7FFF) of MULTIBUS memory space.

- Because of hardware restrictions, the part of the MULTIBUS memory space occupied by controller memory is permanently unavailable for DMA to or from any controller on the bus.

- Programs can access controller memory through the MULTIBUS, but other controllers on the bus cannot do so (see Chapter 7, Subsection 7.2.1).

#### **1.3.1.3 Configuring Controller Address Lines**

On a node with a 16-bit MULTIBUS, up to 64 pages of MULTIBUS address space can be mapped (through the I/O map) to processor memory. Controller references to MULTIBUS addresses above 64K are wrapped; the top four bits of addresses on the bus are driven to 0. For example, a controller reference to 65K appears as a reference to 1K. Consequently, when you have the choice of configuring a controller to a 16-bit or a 20-bit address path, configure for a 16-bit address path.

#### **1.3.1.4 Using Interrupt Request Lines**

Of the eight interrupt request lines available on the MULTIBUS, the highest priority line (line 0) is reserved for customer devices. The remaining seven interrupt lines are reserved for devices that we supply. Table 1-3 lists the allocation of bus interrupt request lines.

| Line | Owner                                                                             |

|------|-----------------------------------------------------------------------------------|

| 0    | Customer devices                                                                  |

| 1    | COM-ETH product controller                                                        |

| 2    | COM-X.25 product controller and<br>Domain/ComController product                   |

| 3    | Magtape controller                                                                |

| 4    | Storage module or FSD-500 product controller                                      |

| 5    | VERSATEC printer/plotter controller and IMAGEN printer with MULTIBUS option       |

| 6    | Parallel output/line printer (only on 16-bit MULTIBUS; unused on 20-bit MULTIBUS) |

| 7    | Reserved                                                                          |

Table 1-3. Allocation of Interrupt Request Lines

Because line 6 is used for parallel I/O, it is unavailable for your use. Lines 1 through 5, though reserved for our use, are available to user-supplied controllers. However, if you assign your device to one of lines 1 through 5 and later acquire one of our supported devices assigned to that line, conflicts will result. Line 0 is reserved for customer devices and will never be used by Domain devices.

A single controller can be configured to request interrupts on more than one request line, but each line can handle only one controller.

On nodes with a 16-bit MULTIBUS, the processor is solely responsible for acknowledging peripheral device interrupt requests. Device controllers should never respond to interrupt requests from other peripheral devices on the bus.

#### 1.3.2 Nodes With a 20-Bit MULTIBUS

Nodes with 20-bit MULTIBUS implementations can also handle 8-bit or 16-bit controllers. Of the devices that can be attached to such nodes, only one can be an 8-bit controller; the others must be 16-bit controllers.

#### 1.3.2.1 Assigning CSR Addresses

On nodes with a 20-bit MULTIBUS, 64 pages of MULTIBUS I/O space are available; however, user devices are restricted to the first 16 pages because Domain system-supplied devices occupy the second 16 pages and addresses 8000-FFFF are reserved for future use. Each controller is allocated one page of the first 16 pages of I/O address space for its set of CSRs (if any). You can assign the addresses of a 16-bit controller to any page within the first 16 pages (0-3FFF hex). Word (2-byte) and longword (4-byte) registers must reside on even-byte addresses. If an 8-bit controller is present in your configuration, assign its CSRs according to the rules outlined in Subsection 1.3.1.

#### 1.3.2.2 Configuring Controller Memory

If a node with a 20-bit MULTIBUS is fully configured with 3 MB of memory, the upper half (512 KB) of the address space is available for DMA operations only. Also, if your configuration includes both 16-bit and 20-bit memory-mapped controllers, you must use caution when configuring 20-bit controller memory into MULTIBUS memory space to avoid possible conflicts with 16-bit controller memory. For example, a 16-bit controller configured to respond to memory address C000 will also respond to addresses 1C000, 2C000, ... FC000. In this case, you must ensure that the MULTIBUS addresses assigned to the 20-bit controller do not equal C000, modulo 64K.

#### **1.3.2.3 Configuring Controller Address Lines**

Nodes with a 20-bit MULTIBUS implementation can map up to 1024 pages of MULTIBUS address space through the I/O map to processor memory. As in 16-bit MULTIBUS systems, controller references to MULTIBUS addresses above 1 MB are wrapped. Consequently, when you have the choice of configuring a controller to a 24-bit or a 20-bit address path, configure for a 20-bit address path.

#### **1.3.2.4 Using Interrupt Request Lines**

Nodes with a 20-bit MULTIBUS allocate interrupt request lines in the same way as nodes with a 16-bit MULTIBUS, except that lines 6 and 7 are also available (although they are reserved for Domain system-supplied devices). Again, the processor is solely responsible for acknowledging peripheral device interrupt requests; device controllers should never respond to interrupt requests from other peripheral devices on the bus. Table 1-3 lists the allocation of bus interrupt lines.

#### **1.4 Byte Swapping**

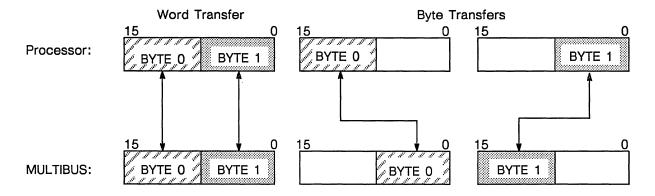

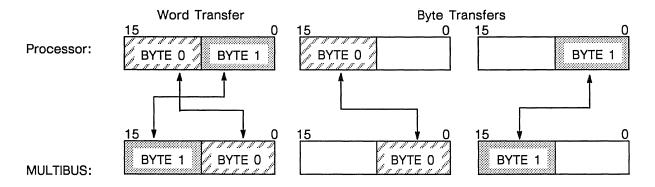

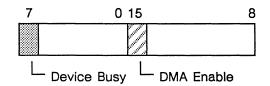

The necessity for byte swapping (exchanging the left and right bytes of a word) arises from the fact that the Domain processor, which is based on the Motorola 68000 family, orders bytes within a word the opposite of the way Intel processors order them on MULTIBUS controllers.

This is how our processor does it:

This is how MULTIBUS does it:

| 15     | 87     | 0 15 | 8      | 7      | 0 |

|--------|--------|------|--------|--------|---|

| BYTE O | BYTE 1 |      | BYTE 1 | BYTE 0 |   |

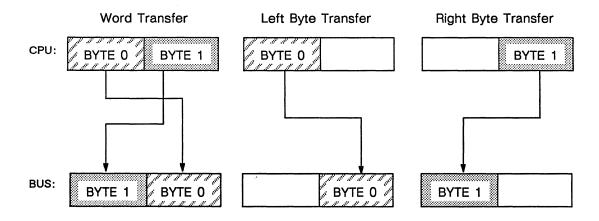

We deal with this incompatibility by swapping bytes in hardware during byte transfers. Effectively, character strings copied as bytes and integers copied as words are preserved, but character strings copied as words (and words copied as bytes) are byte swapped. The following illustrates this strategy:

Note that this strategy uses the following byte/word arrangements:

- Pointers to words must be even.

- Pointers to processor left bytes (byte 0) must be even.

- Pointers to processor right bytes (byte 1) must be odd.

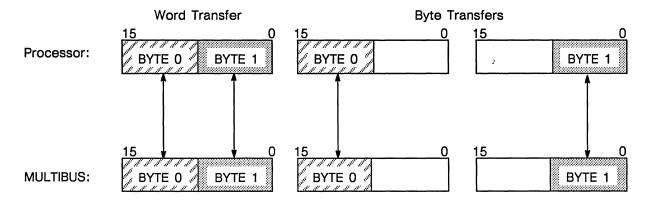

The GPIO call **pbu\_\$control** is available for 20-bit MULTIBUS implementations (refer to Appendix B for a description of the call). This call gives you control over the byte-swapping hardware so that you can specify other byte/word arrangements than those just spelled out (the **pbu\_swap\_off** option gives you the arrangement described previously). By specifying the **pbu\_swap\_words** option with this call, you ensure that all character strings have their byte order preserved regardless of whether they are copied as words or bytes and that integers are always byte swapped. The following illustrates byte swapping when **pbu\_swap\_words** is specified:

By specifying the **pbu\_swap\_bytes** option with the **pbu\_\$control** call, you ensure that integers have their byte order preserved regardless of whether they are copied as words or bytes and that character strings are always byte swapped. The following illustrates byte swapping when **pbu\_swap\_bytes** is specified:

It should be noted that single byte transfers always occur on MULTIBUS data lines 0 through 7 and that word transfers use all 16 data lines.

# Chapter 2 I/O Bus Structures: the VMEbus

This chapter presents information you need to know about the VMEbus in order to use GPIO software to write device drivers for VMEbus devices, specifically, address space allocation. grant levels, use of address modifiers, interrupt levels, and software considerations. For additional information about the VMEbus, refer to the DN5xx-T Workstations and DSP500-T Server Technical Reference manual and the Motorola VMEbus Specification Manual, Rev. C.1 or IEEE P1014/D1.2.

The I/O bus is the network of signal routes through which device controllers and the processor address one another and transfer data. The bus is, therefore, the key hardware component of a computer system's I/O structure. Figure 2–1 shows the relationship of the I/O bus to a Domain node and a set of controllers. The processor, memory, and memory management (address translation) subsystems are linked by an internal bus. Interface hardware connects this internal bus to the I/O bus. User-supplied and Domain systemsupplied device controllers attach to the I/O bus and, through the bus, link to the node.

Figure 2-1. Relationship Between a Domain Node and Peripheral Controllers

#### 2.1 Address Space Allocation

Because there is no mapping mechanism between the VMEbus and a customer VMEbus device, there must be agreement as to what VMEbus addresses are reserved for your controllers. In addition, you must be aware that as our allocation of the physical address space on existing and future workstations changes, it may be necessary for you to modify your controllers to respond to different addresses on different workstations.

The address layout for the DN5xx-T is listed in Table 2-1.

| Physical Addresses                      | Resource                             | Address/Data Lines                                                         |  |  |

|-----------------------------------------|--------------------------------------|----------------------------------------------------------------------------|--|--|

| 0000-7FFF                               | VMEbus CSRs                          | 16-Bit Addressing, 16-Bit Data Path                                        |  |  |

| C000-DFFF                               | VMEbus CSRs                          | 24-Bit Addressing, 16-Bit Data Path                                        |  |  |

| 80000-FFFFF                             | User VMEbus                          | 24-Bit Addressing, 16-Bit Data Path                                        |  |  |

| 200000-2FFFFF                           | User VMEbus                          | 24-Bit Addressing, 16-Bit Data Path                                        |  |  |

| 310000-3FFFFF                           | User VMEbus                          | 24-Bit Addressing, 16-Bit Data Path                                        |  |  |

| 600000-7FFFFF                           | User VMEbus                          | 24-Bit Addressing, 32-Bit Data Path                                        |  |  |

| 800000-FFFFFF<br>3000000-300FFFF        | User VMEbus*<br>VMEbus I/O<br>(CSRs) | 24–Bit Addressing, 32–Bit Data Path<br>32–Bit Addressing, 32–Bit Data Path |  |  |

| 3200000-3FFFFFF                         | User VMEbus                          | 32–Bit Addressing, 32–Bit Data Path                                        |  |  |

| *Available only on DN570-T workstation. |                                      |                                                                            |  |  |

Table 2-1. Address Space Allocated for DN5xx-T VMEbus Devices

#### 2.2 Bus Grant Level

VMEbus devices should use bus grant level 2.

#### **2.3 Address Modifiers**

The current DN5xx-T VMEbus interface defines the following address modifiers for all references to VMEbus controllers:

- 2D: 16-Bit Addressing

- 3D: 24–Bit Addressing

- 0D: 32-Bit Addressing

Domain system-supplied controllers also use these address modifiers for DMA activity.

Apollo recommends that the address modifiers that a device uses be held in two programloadable registers, one for slave responses and the other for master requests. In the initial power-on/reset state of the device, it should be possible to load these registers by using any address modifier.

#### 2.4 Interrupt Level

Customer VMEbus devices are currently assigned to VMEbus interrupt level 5. The VMEbus interrupt level used by a customer device should be jumperable to allow for possible changes in interrupt level allocation on future workstations.

#### 2.5 Status/ID Byte

A VMEbus controller presents a status/ID byte during a VMEbus interrupt acknowledge cycle. The operating system uses this byte to distinguish between multiple VMEbus devices and by GPIO as the unit number identifying the device. Status/ID bytes F8 through FE (corresponding to unit numbers 8 through 14) are available for customer devices; status/ID bytes F0 through F7 and FF are reserved.

The Device Descriptor File (DDF) for a VMEbus device defines the bottom nibble of the status/ID as the device unit number.

#### 2.6 Software Considerations

GPIO software supports memory-mapped I/O, programmed I/O, and DMA operations on the VMEbus.

**NOTE:** Apollo provides two kinds of calls, **pbu\_\$** and **pbu2\_\$**, for several GPIO operations. When referring to either kind interchangeably, we use the term **pbu[2]** *\$routine name*.

There is no DMA address translation hardware (I/O map) for the VMEbus; the following GPIO calls are, therefore, not applicable to drivers that support VMEbus devices:

- pbu[2]\_\$allocate\_map

- pbu[2]\_\$free\_map

- pbu[2]\_\$map

- pbu[2]\_\$unmap

In addition, the following GPIO calls are not applicable to VMEbus devices and cannot be used in drivers for VMEbus devices:

- pbu\_\$device\_interrupting

- pbu\_\$disable\_device

- pbu\_\$enable\_device

- pbu\_\$control

- pbu[2]\_\$dma\_start

- pbu[2]\_\$dma\_stop

Otherwise, you use GPIO software when writing drivers for VMEbus devices just as you would for MULTIBUS devices. Extensions to the GPIO package to accommodate the VMEbus in no way limit the current facilities of GPIO.

#### 2.6.1 Wiring for DMA: pbu\_\$wire\_special

Since there is no mapping hardware between the customer's device and the VMEbus, device drivers should call **pbu\_\$wire\_special** (instead of **pbu[2]\_\$wire**) to wire buffers for DMA operations. This call returns a list of physical (VMEbus) addresses at which the buffer is located. The customer's driver or controller hardware uses the addresses to perform the necessary scatter-gather operations. Refer to Appendix B for a full description of this call.

#### 2.6.2 Creating a DDF for a VMEbus Device

To create a DDF for a VMEbus device, you must specify the -vme option with the crddf command. This option indicates to GPIO that the device in question resides on the VMEbus. It is recommended that this option be the first specified when building a new DDF. Valid unit numbers when the -vme option is specified are in the range 8 to 14 (pbu\_\$min\_vme\_unit to pbu\_\$max\_vme\_unit).

If the -vme option is specified, the specification of a CSR page is optional. If a CSR page is specified, it must be page-aligned and in the range 0000-7C00 (A16) or C000-DC00 (A24).

Refer to Appendix A for a full description of the **crddf** command and the **-vme** option and to Chapter 11, Subsection 11.3.2 for an example of the **crddf** command with the **-vme** option.

# Chapter 3

## I/O Bus Structures: the IBM PC AT Compatible Bus

This chapter presents information about the IBM PC AT compatible bus in order to use GPIO software to write device drivers for PC AT compatible devices, specifically: I/O address and memory space allocation, unit numbering, testing for device presence, DMA and interrupt lines, byte swapping, and software considerations. For additional information about the PC AT compatible bus, refer to the *Domain Personal Workstations and Servers Technical Reference* manual.

**NOTE:** Apollo provides two kinds of calls, **pbu\_\$** and **pbu2\_\$**, for several GPIO operations. When referring to either kind interchangeably, we use the term **pbu[2]\_\$**routine\_name. The I/O bus is the network of signal routes through which device controllers and the processor address one another and transfer data. The bus is the key hardware component of a computer system's I/O structure. Figure 3-1 shows the relationship of the I/O bus to a Domain node and a set of controllers. The processor, memory, and memory management (address translation) subsystems are linked by an internal bus. Interface hardware connects this internal bus to the I/O bus. User-supplied and Domain system-supplied device controllers attach to the I/O bus and, through the bus, link to the node.

Figure 3-1. Relationship Between a Domain Node and Peripheral Controllers

## **3.1 PC AT Compatible Address Space**

The physical address space on the PC AT compatible bus that is available to the user consists of I/O address space (reserved for device CSRs), and memory address space (reserved for memory-mapped controllers). The following subsections describe these two address spaces in detail. For additional information on the PC AT compatible bus address space, refer to the *Domain Personal Workstations and Servers Hardware Architecture Handbook*.

#### 3.1.1 I/O Address Space

The I/O address space (0-3FF) is reserved for device CSRs. Table 3-1 lists the address ranges within this area that are reserved for Domain system-supplied devices and those that are available for customer devices. If your system is not configured with the system-supplied device that occupies a particular address range, then you may use that range for your own device.

| Bus Address (Hex) | Device                                                 |

|-------------------|--------------------------------------------------------|

| 000-0FF           | Reserved                                               |

| 100–19F           | Customer Devices                                       |

| 1A0-1A7           | Disk Controller                                        |

| 1A8-1FF           | Customer Devices                                       |

| 200-207           | Tape Controller                                        |

| 208–21F           | Customer Devices                                       |

| 220-23F           | Apollo Token Ring Network Controller-AT                |

| 240-2F7           | Customer Devices                                       |

| 2F8-2FF           | Serial-Parallel Expansion (SPE) option — Serial Line 2 |

| 300-307           | 802.3 Network Controller-AT                            |

| 310-317           | 802.3 Network Controller-AT (Alternate)                |

| 320-33F           | Apollo Token Ring Network Controller-AT                |

| 340-377           | Customer Devices                                       |

| 378-37F           | SPE option — Parallel Port                             |

| 380-3AF           | Customer Devices                                       |

| 3B0-3BF           | Monochrome Graphics (Alternate Color)                  |

| 3C0-3CF           | Customer Devices                                       |

| 3D0-3DF           | Color Graphics (Alternate Monochrome)                  |

| 3E0-3EF           | Customer Devices                                       |

| 3F0-3F7           | Disk Controller                                        |

| 3F8-3FF           | SPE — Serial Line 1                                    |

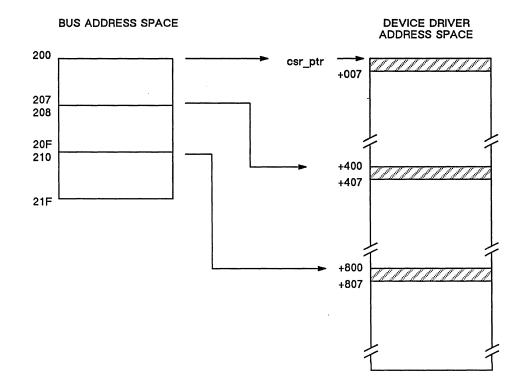

To provide protection for system devices and virtual memory support, addresses in the PC AT compatible I/O address space are mapped differently from addresses in MULTIBUS and VMEbus address spaces. Ten-bit consecutive addresses in the I/O address space are mapped into processor address space in groups of eight bytes, and each group is assigned the first eight bytes of a different, but consecutive, page (1024 bytes). Thus, the first 1024 addresses in PC AT compatible address space (0-3FF) map to 128 physical pages (40000-5FFFF) in processor address space.

A PC AT compatible controller using three 8-byte CSR addresses might have the following type declaration:

```

typedef struct csr_page_t {

char first_eight[7];

char next_eight[7];

char last_eight[7];

} csr_page_t #attribute[device];

```

In Apollo systems, however, the type declaration should be as follows:

```

typedef struct csr_page_t {

char first_eight[8];

char pad1[bytes_per_page-8];

char next_eight[8];

char pad2[bytes_per_page-8];

char last_eight[8];

char pad3[bytes_per_page-8];

} csr_page_t #attribute[device];

```

Figure 3-2 illustrates the mapping scheme for the preceding example (csr\_ptr is the pointer that **pbu\_\$acquire** passes to the device initialization routine after mapping the CSR page(s) into driver address space).

Figure 3-2. CSR Mapping Scheme for PC AT Compatible Devices

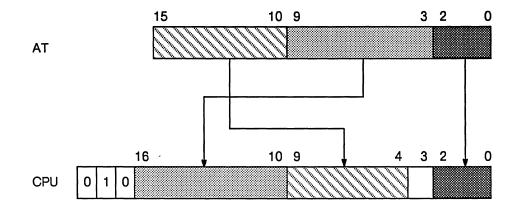

Sixteen-bit addresses (so-called PC AT addresses, which are not supported on the PC AT compatible bus) extend the address range beyond the 1 KB (0-3FF) range of 10-bit addresses up to 64 KB (0-FFFF). Such addresses are "folded" and mapped to different locations on the same set of 128 physical pages as are occupied by 10-bit addresses.

Figure 3–3 shows how the 16 bits of an PC AT compatible I/O address are translated to a processor physical address.

Figure 3-3. Mapping a 16-Bit PC AT Address to Processor Address Space

Apollo provides the cvt\_at command to return the iova for 10- and 16-bit addresses. The cvt\_at command also reports any conflict between the address you specify for your device and the address of any system-supplied devices. Refer to Appendix A for the syntax and usage.

#### 3.1.2 Memory Space

The PC AT compatible memory space is used for memory-mapped and bus-master devices. Addresses are mapped one-to-one to processor physical address space. Controllers are mapped and unmapped using the GPIO routines pbu2\_\$map\_controller and pbu2\_\$unmap\_controller.

Table 3-2 lists the address ranges that are reserved for Domain system-supplied devices as well as those that are available for customer devices. If your system is not configured with the system-supplied device that occupies a particular address range, then you may use that range for your own device. For a more detailed map of memory space usage, refer to the *Domain Personal Workstations and Servers Hardware Architecture Handbook*.

# Table 3-2. DN3000/DN4000 Physical Memory Allocated for DomainSystem-Supplied Devices

| Physical Address (Hex)                                                                          | Device                                                                            |  |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| 000000-03FFFF                                                                                   | Reserved for the System                                                           |  |

| 040000-05FFFF                                                                                   | I/O Address Space (see Table 3-1)                                                 |  |

| 080000-09FFFF                                                                                   | Available for Customer Devices                                                    |  |

| 0A0000-0BFFFF                                                                                   | Color or Alternate Monochrome Graphics                                            |  |

| 0C0000-0DFFFF                                                                                   | Alternate Monochrome Graphics or Apollo Token<br>Ring (0D0000-0DFFFF)             |  |

| 0E0000-0FFFFF                                                                                   | Alternate Color Graphics or Alternate or Second Single-Board Ring (0E0000-0EFFFF) |  |

| 100000-8FFFFF*                                                                                  | Main Memory                                                                       |  |

| 900000-BFFFFF                                                                                   | Available for Customer Devices                                                    |  |

| C00000-CFFFFF                                                                                   | PC Coprocessor                                                                    |  |

| D00000-DFFFFF                                                                                   | PC Coprocessor Alternate                                                          |  |

| E00000-F9FFFF                                                                                   | Available for Customer Devices                                                    |  |

| FA0000-FDFFFF                                                                                   | Monochrome Graphics                                                               |  |

| FE0000-FFFFFF                                                                                   | Available for Customer Devices                                                    |  |

| *On the DN4000, this area is not occupied by main memory and is available for customer devices. |                                                                                   |  |

## 3.2 Unit Numbering

The unit number of an PC AT compatible device is identical with the Interrupt Request (IRQ) line. There are 16 possible unit numbers; unit number 0 has the highest priority. However, since Domain system-supplied devices also use this range, not all unit numbers are available for customer devices. The current allocation of unit numbers as well as the interrupt priority (from highest to lowest) assigned to each unit number are listed in Table 3-3 for the DN3000 and in Table 3-4 for the DN4000.

**NOTE:** In Table 3–3 and Table 3–4 the phrase "or User Device" means that the IRQ reserved for a device that is not present on the system can be used for another device.

| Unit No.<br>and IRQ                                                      | Interrupt<br>Priority | Device                                         |

|--------------------------------------------------------------------------|-----------------------|------------------------------------------------|

| 0*                                                                       | 1                     | Timer                                          |

| 1*                                                                       | 2                     | Keyboard                                       |

| 2*                                                                       | -                     | Reserved                                       |

| 3                                                                        | 3                     | Apollo Token Ring Network Controller-AT        |

| 4                                                                        | 12                    | SPE — Serial Line 1 or User Device             |

| 5                                                                        | 13                    | Tape Controller                                |

| 6                                                                        | 14                    | Disk Controller or User Device                 |

| 7                                                                        | 15                    | SPE — Parallel Line or User Device             |

| 8*                                                                       | 4                     | Calendar – Serial Lines 1 and 2                |

| 9                                                                        | 5                     | ETHERNET 2, SPE — Serial Line 2 or User Device |

| 10                                                                       | 6                     | ETHERNET 1 or User Device                      |

| 11                                                                       | 7                     | PC Coprocessor or User Device                  |

| 12                                                                       | 8                     | User Device                                    |

| 13*                                                                      | 9                     | Reserved                                       |

| 14                                                                       | 10                    | Disk Controller                                |

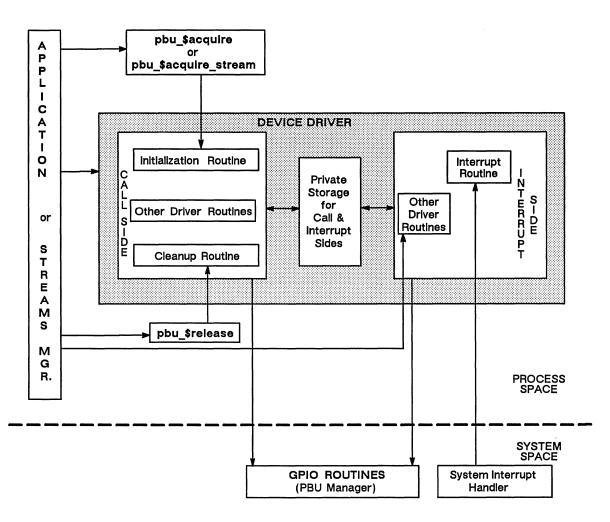

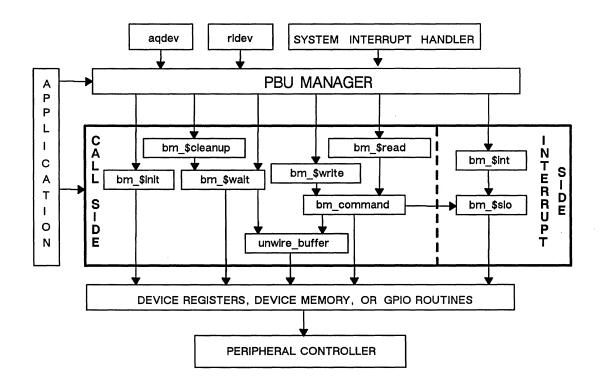

| 15                                                                       | 11                    | PC Coprocessor Alternate or User Device        |