# **DAP Series**

# APAL Language

(man005.03)

AMT endeavours to ensure that the information in this document is correct, but does not accept responsibility for any error or omission.

Any procedure described in this document for operating AMT equipment should be read and understood by the operator before the equipment is used. To ensure that AMT equipment functions without risk to safety or health, such procedures should be strictly observed by the operator.

The development of AMT products and services is continuous and published information may not be up to date. Any particular issue of a product may contain part only of the facilities described in this document or may contain facilities not described here. It is important to check the current position with AMT.

Specifications and statements as to performance in this document are AMT estimates intended for general guidance. They may require adjustment in particular circumstances and are therefore not formal offers or undertakings.

Statements in this document are not part of a contract or program product licence save in so far as they are incorporated into a contract or licence by express reference. Issue of this document does not entitle the recipient to access to or use of the products described, and such access or use may be subject to separate contracts or licences.

Technical publication man005.03

First edition June 1987 Second edition October 1987 Third edition 3 October 1988

Copyright © 1988 by Active Memory Technology

No part of this publication may be reproduced in any form without written permission from Active Memory Technology.

AMT will be pleased to receive readers' views on the contents, organisation, etc of this publication. Please make contact at either of the addresses below:

A 4

Publications Manager Active Memory Technology Ltd 65 Suttons Park Avenue Reading Berks, RG6 1AZ, UK

Tel: 0734 661111

Publications Manager Active Memory Technology Inc 16802 Aston St Suite 103 Irvine California, 92714, USA

Tel: (714) 261 8901

# Preface

This manual describes the Array Processor Assembly Language (APAL), which represents the lowest level at which a DAP-series machine can be programmed; the manual covers the use of APAL with all models in the DAP-series range.

Although this manual is a definitive reference for the syntax of APAL, chapters 1 to 12 are intended to be read serially as an introduction to the language (although you should preferably have some experience of assembly language programming in general); appendix F describes the APAL instruction set in alphabetical order. After you have studied chapter 1, you may find it helpful to look at the examples in appendix C, to get an impression of the style and level of programming of APAL before you continue with the detailed description in chapter 2 and onwards.

Descriptions of features of the language are given in two parts: the first part is a formal syntactic definition of the language feature, and the second part is a description of its semantics.

Chapter 1 describes the architecture of a DAP-series machine. Chapter 2 describes the format of APAL source text. Chapter 3 describes the structure of an APAL source module. Chapter 4 describes the declaration and initialisation of data. Chapter 5 describes the declaration of code sections. Chapter 6 describes the APAL instruction set. Chapter 7 describes the various modes of addressing possible in APAL. Chapter 8 describes the run-time tracing facility. Chapter 9 describes code section conventions and mixed language programming with FORTRAN-PLUS, the superset of FORTRAN 77 implemented on DAP-series machines. Chapter 10 describes miscellaneous assembly-time facilities such as listing control. Chapter 11 describes assembly-time facilities such as conditional assembly and textual substitution. Chapter 12 describes the APAL macro facility.

The preparation of a DAP program involving APAL routines is described in the AMT manual DAP Series: Program Development; consult the version of the manual appropriate to your host system.

Other relevant AMT manuals are:

DAP Series: Introduction to FORTRAN-PLUS

DAP Series: FORTRAN-PLUS Language

#### Syntax and semantics

Both the syntax and the semantics of the various APAL code statements are covered in the manual at the appropriate places. To get a full understanding of how to use a particular statement you need to read both the syntax and semantics sub-sections covering the statement.

iii

(man001)

(man002)

iii

iv

The formal syntax of APAL is defined using Backus-Naur form (BNF), with the following extensions:

- <entity >? means that <entity > is optional; <entity > may occur once, or not at all

- <entity >\* means that <entity > may occur several times, or not at all

As usual with BNF notation, items printed in capitals in the syntax (terminals) are to be included in your code exactly as they are stated in the syntax; items printed in lower case and enclosed within <>' - such as <entity>' above (non-terminals) – are to be replaced in your code by an appropriate terminal.

In the semantics of a statement, terminals are also printed in capitals, non terminals in italics.

For example, the semantics of the data header statement is given in section 4.1 as:

DATA section-name name-property common-property write-property

An actual data header you might have in your APAL code might be:

DATA FREIDA HOST COMMON WRITE

where:

FREIDA is the name of your data section

You are specifying a name property of HOST; that is that you want the data to be available for reference in a call in a host program interface subroutine

You are specifying the common-property COMMON; that is that the data in the section is to occupy a common area in store with other data sections in different code modules, but which have the same data section name and have the COMMON property

You are specifying that you want write as well as read access to the data

See chapter 4 for fuller details of data headers!

# Contents

| 1 | The  | architecture of DAP-series machines    | 1  |

|---|------|----------------------------------------|----|

|   | 1.1  | The DAP series                         | 1  |

|   | 1.2  | The PE matrix                          | 4  |

|   | 1.3  | The DAP code memory                    | 4  |

|   | 1.4  | The DAP array store                    | 4  |

|   | 1.5  | Data mapping and number representation | 6  |

|   | 1.6  | Processor element functions            | 8  |

|   | 1.7  | The MCU                                | 8  |

|   | 1.8  | MCU registers and the edge register    | 10 |

|   | 1.9  | DO loops                               | 11 |

|   | 1.10 | C- and V-flags                         | 11 |

|   | 1.11 | Array edge dimensions                  | 12 |

| 2 | AP   | AL source program format               | 13 |

|   | 2.1  | Character set                          | 13 |

|   |      | 2.1.1 Syntax                           | 13 |

|   |      | 2.1.2 Semantics                        | 14 |

|   | 2.2  | Identifiers                            | 15 |

|   |      | 2.2.1 Syntax                           | 15 |

|   |      | 2.2.2 Semantics                        | 15 |

|   | 2.3  | Form         | at of data values                           | . 16 |

|---|------|--------------|---------------------------------------------|------|

|   |      | 2.3.1        | Integer values                              | . 16 |

|   |      | 2.3.2        | Real values                                 | . 17 |

|   |      | 2.3.3        | Hexadecimal values                          | . 18 |

|   |      | 2.3.4        | Character values                            | . 18 |

|   | 2.4  | Conti        | inuation lines                              | . 19 |

|   | 2.5  | Com          | nents                                       | . 19 |

|   |      | 2.5.1        | Syntax                                      | . 19 |

|   |      | 2.5.2        | Semantics                                   | . 19 |

| • | 4.10 |              |                                             |      |

| 3 | AP.  | AL SOI       | urce program structure                      | 21   |

|   | 3.1  | Declar       | ring an APAL module                         | 21   |

|   |      | 3.1.1        | Syntax                                      | 22   |

|   |      | 3.1.2        | Semantics                                   | 22   |

|   | 3.2  | Scope        | of identifiers                              | 23   |

| 4 | n.   | n soat       | ions, declarations and identities           |      |

|   | Dai  |              |                                             | 27   |

|   | 4.1  | Declar       | ring a data section                         | 27   |

|   |      | 4.1.1        | Syntax                                      | 27   |

|   |      | <b>4.1.2</b> | Semantics                                   | 28   |

|   | 4.2  | Declar       | ring data                                   | 29   |

|   |      | 4.2.1        | Syntax                                      | 29   |

|   |      | 4.2.2        | Semantics                                   | 30   |

|   |      | 4.2.3        | Representation of values in the array store | 35   |

|   | 4.3  | Data i       | dentities                                   | 37   |

|   |      | 4.3.1        | Syntax                                      | 38   |

|   |      | 4.3.2        | Semantics                                   | 39   |

vi

vi

.

.

| 5 | Cod | ode sections 43 |                                              |    |

|---|-----|-----------------|----------------------------------------------|----|

|   | 5.1 | Declar          | ing a code section                           | 43 |

|   |     | 5.1.1           | Syntax                                       | 43 |

|   |     | 5.1.2           | Semantics                                    | 44 |

|   | 5.2 | Code            | section contents                             | 44 |

|   |     | 5.2.1           | Declaring entry points                       | 44 |

|   |     | 5.2.2           | APAL instructions                            | 45 |

|   | 5.3 | Mixed           | sections                                     | 45 |

|   |     | 5.3.1           | Syntax                                       | 46 |

|   |     | 5.3.2           | Semantics                                    | 46 |

| • |     |                 |                                              | 47 |

| 6 |     |                 | tructions                                    |    |

|   | 6.1 |                 | ction fields                                 | 47 |

|   |     | 6.1.1           | The OPERATION field                          | 48 |

|   |     | 6.1.2           | The MCUR field                               | 48 |

|   |     | 6.1.3           | The MOD field                                | 49 |

|   |     | 6.1.4           | The ADDR, INT and WORD fields                | 49 |

|   |     | 6.1.5           | The INCREMENT/DECREMENT and STEP TYPE fields | 49 |

|   |     | 6.1.6           | The DIRECTION and GEOMETRY fields            | 50 |

|   |     | 6.1.7           | The LITERAL field                            | 50 |

|   |     | 6.1.8           | The CODE ADDRESS field                       | 51 |

|   | 6.2 | The i           | nstruction set                               | 51 |

|   |     | 6.2.1           | Introduction                                 | 51 |

|   |     | 6.2.2           | Group 0                                      | 52 |

|   |     | 6.2.3           | Group 1                                      | 52 |

|   |     | 6.2.4           | Group 2                                      | 52 |

|   |     | 6.2.5           | Group 3                                      | 53 |

|   |     | 6.2.6           | Group 4                                      | 53 |

|   |     | 6.2.7           | Group 5                                      | 54 |

ج,

vii

| 6.2.8 Group 6                                                                                                                                                | 54 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                              |    |

| 6.2.9 Group 7                                                                                                                                                | 54 |

| 6.2.10 Group 8                                                                                                                                               | 54 |

| 6.2.11 Group 9                                                                                                                                               | 55 |

| 6.2.12 Group 10                                                                                                                                              | 55 |

| 6.2.13 Group 11                                                                                                                                              | 56 |

| 6.2.14 Group 12                                                                                                                                              | 56 |

| 6.2.15 Group 13                                                                                                                                              | 56 |

| 6.2.16 Group 14                                                                                                                                              | 57 |

| 6.2.17 Group 15                                                                                                                                              | 58 |

| 6.2.18 Pseudo instructions                                                                                                                                   | 58 |

|                                                                                                                                                              |    |

|                                                                                                                                                              | 61 |

|                                                                                                                                                              | 61 |

| 7.1.1 Mode A : ADDR, INT evaluated separately                                                                                                                | 63 |

| 7.1.2 Mode B : carry propagates from INT to ADDR                                                                                                             | 65 |

| 7.1.3 Mode C : word address $\ldots \ldots $ | 66 |

| 7.1.4 Mode D : direction, geometry and count $\ldots \ldots \ldots$                           | 68 |

| 7.1.5 Mode E : DO loop count                                                                                                                                 | 69 |

| 7.1.6 Mode F: EXIT instruction                                                                                                                               | 69 |

| 7.2 Modifier register formats                                                                                                                                | 69 |

| 7.2.1 Array store plane and row, column, word or bit number modifier 6                                                                                       | 69 |

| 7.2.2 Direction, geometry and count modifier                                                                                                                 | 70 |

| 7.2.3 DO count modifier                                                                                                                                      | 70 |

| 7.2.4 Instruction address modifier                                                                                                                           | 71 |

| 7.3 Addressing constructs                                                                                                                                    | 71 |

|                                                                                                                                                              | 71 |

| 7.3.2 Specifying DO loop stepping                                                                                                                            | 72 |

|                                                                                                                                                              | 72 |

.

.

|   |            | 7.3.4                                                                                                                              | Register bit addresses   | 74                                     |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------|

|   |            | 7.3.5                                                                                                                              | Code store addresses     | 75                                     |

| 8 | Tra        | cing fa                                                                                                                            | cilities                 | 77                                     |

|   | 8.1        | The T                                                                                                                              | RACE statement           | . 77                                   |

|   |            | 8.1.1                                                                                                                              | Syntax                   | 77                                     |

|   |            | 8.1.2                                                                                                                              | Semantics                | 78                                     |

|   | 8.2        | Forma                                                                                                                              | at of items to be TRACEd | 81                                     |

|   |            | 8.2.1                                                                                                                              | WORDPACK format          | 81                                     |

|   |            | 8.2.2                                                                                                                              | ROWPACK format           | 81                                     |

|   |            | 8.2.3                                                                                                                              | VERTICAL format          | 82                                     |

|   | 8.3        | Exam                                                                                                                               | ples                     | 82                                     |

|   |            |                                                                                                                                    |                          |                                        |

| 9 | Cod        | le sect                                                                                                                            | tion conventions         | 83                                     |

|   |            |                                                                                                                                    |                          |                                        |

|   | 9.1        | Introd                                                                                                                             | luction                  | 83                                     |

|   | 9.1        | Introd<br>9.1.1                                                                                                                    | luction                  | 83<br>83                               |

|   | 9.1        |                                                                                                                                    |                          |                                        |

|   | 9.1<br>9.2 | 9.1.1<br>9.1.2                                                                                                                     | Run-time structure       | 83                                     |

|   |            | 9.1.1<br>9.1.2                                                                                                                     | Run-time structure       | 83<br>84                               |

|   |            | 9.1.1<br>9.1.2<br>Entry                                                                                                            | Run-time structure       | 83<br>84<br>84                         |

|   |            | 9.1.1<br>9.1.2<br>Entry<br>9.2.1                                                                                                   | Run-time structure       | 83<br>84<br>84<br>84                   |

|   | 9.2        | <ul> <li>9.1.1</li> <li>9.1.2</li> <li>Entry</li> <li>9.2.1</li> <li>9.2.2</li> <li>9.2.3</li> </ul>                               | Run-time structure       | 83<br>84<br>84<br>84<br>85             |

|   | 9.2        | <ul> <li>9.1.1</li> <li>9.1.2</li> <li>Entry</li> <li>9.2.1</li> <li>9.2.2</li> <li>9.2.3</li> </ul>                               | Run-time structure       | 83<br>84<br>84<br>84<br>85<br>85       |

|   | 9.2        | 9.1.1<br>9.1.2<br>Entry<br>9.2.1<br>9.2.2<br>9.2.3<br>Areas                                                                        | Run-time structure       | 83<br>84<br>84<br>85<br>85<br>85       |

|   | 9.2        | <ul> <li>9.1.1</li> <li>9.1.2</li> <li>Entry</li> <li>9.2.1</li> <li>9.2.2</li> <li>9.2.3</li> <li>Areas</li> <li>9.3.1</li> </ul> | Run-time structure       | 83<br>84<br>84<br>85<br>85<br>86<br>86 |

ix

ix

.

|    | 9.4  | Calling another code section |                                                 |    |

|----|------|------------------------------|-------------------------------------------------|----|

|    |      | 9.4.1                        | Creating a name space                           | 87 |

|    |      | 9.4.2                        | Calling the routine by name                     | 88 |

|    |      | 9.4.3                        | Calling the routine by address                  | 88 |

|    |      | 9.4.4                        | Complete example                                | 89 |

|    | 9.5  | Calling                      | g an APAL code section from a host routine      | 90 |

|    |      | 9.5.1                        | Passing data between the host and APAL routines | 90 |

|    | -9:6 | User-d                       | efined conventions                              | 91 |

| 10 | Min  | 11                           |                                                 |    |

| 10 |      |                              | eous facilities                                 | 93 |

|    | 10.1 | Access                       | ing standard bit patterns                       | 93 |

|    |      | 10.1.1                       | 'BINARY_CHOP                                    | 94 |

|    |      | 10.1. <b>2</b>               | 'UD_BASE                                        | 94 |

|    |      | 10.1. <b>3</b>               | 'UNIT_DIAG                                      | 94 |

|    |      | 10.1.4                       | 'TRAIL_DIAG                                     | 95 |

|    |      | 10.1.5                       | 'ALTERNATE                                      | 95 |

|    |      | 10.1.6                       | 'LOWER_TRI                                      | 96 |

|    |      | 10.1.7                       | 'SHUFFLE                                        | 96 |

|    |      | 10.1.8                       | 'UNSHUFFLE                                      | 96 |

|    | 10.2 | Incorpo                      | orating source from alternative files           | 97 |

|    | 10.3 | Reques                       | sting stack space                               | 97 |

|    |      | 10.3.1                       | Syntax                                          | 97 |

|    |      | 10.3.2                       | Semantics                                       | 97 |

|    | 10.4 | Contro                       | lling the output listing                        | 98 |

|    |      | 10.4.1                       | The LIST statement                              | 98 |

|    |      | 10.4.2                       | The NOTE statement                              | 99 |

х

$\Delta MT$

| 11 Substitutions and conditional assembly                                                                               | 101   |

|-------------------------------------------------------------------------------------------------------------------------|-------|

| 11.1 Assembly-time values                                                                                               | 101   |

| 11.1.1 Syntax                                                                                                           | 102   |

| 11.1.2 Semantics                                                                                                        | 102   |

| 11.2 Assembly-time variables                                                                                            | 104   |

| 11.2.1 The VAR statement                                                                                                | 105   |

| 11.2.2 The SET statement                                                                                                | . 106 |

| 11.3 Substitutions                                                                                                      | . 106 |

| 11.3.1 Syntax                                                                                                           | . 107 |

| 11.3.2 Variable substitutions $\ldots$ | . 107 |

| 11.3.3 Expression substitutions                                                                                         | . 109 |

| 11.3.4 Section substitutions                                                                                            | . 110 |

| 11.3.5 Plane substitutions                                                                                              | . 110 |

| 11.3.6 Row substitutions                                                                                                | . 111 |

| 11.3.7 Column substitutions                                                                                             | . 112 |

| 11.3.8 Word substitutions                                                                                               | . 112 |

| 11.3.9 Substring substitutions                                                                                          | . 113 |

| 11.3.10 Length substitutions                                                                                            | . 117 |

| 11.3.11 Repeated substitutions                                                                                          | . 118 |

| 11.3.12 Concatentation within substitutions                                                                             | . 119 |

| 11.4 Conditional assembly                                                                                               | . 120 |

| 11.4.1 The IF construct                                                                                                 | . 121 |

| 11.4.2 Assembly-time conditions                                                                                         | . 123 |

|                                                                                                                         | 127   |

| 12 Macros                                                                                                               |       |

| 12.1 Defining macros                                                                                                    |       |

| 12.1.1 Syntax                                                                                                           |       |

| 12.1.2 Semantics                                                                                                        |       |

| 12.1.3 The ERASE statement                                                                                              | . 131 |

xi

xi

I

|     | 12.2 | Calling macros                                 | 131          |

|-----|------|------------------------------------------------|--------------|

|     |      | <b>12.2.1</b> Syntax                           | 131          |

|     |      | 12.2.2 Semantics                               | 131          |

|     |      | 12.2.3 System variables associated with macros | 134          |

|     | 12.3 | Leaving macros                                 | 134          |

|     |      | 12.3.1 The MEND statement                      | L <b>3</b> 4 |

|     |      | 12.3.2 The MEXIT statement                     | 35           |

|     |      | 12.3.3 The MQUIT statement                     | 135          |

|     | 12.4 | Parameter substitutions                        | 35           |

|     |      | 12.4.1 Syntax                                  | .36          |

|     |      | 12.4.2 Semantics                               | 36           |

|     | 12.5 | Macro variables                                | .38          |

|     |      | 12.5.1 The MVAR statement                      | .38          |

|     |      | 12.5.2 The MSET statement 1                    | 39           |

|     | 12.6 | The CYCLE construct                            | 40           |

|     |      | 12.6.1 Syntax                                  | 40           |

|     |      | 12.6.2 Semantics                               | 40           |

|     | 12.7 | Macro comments                                 | 42           |

|     |      | 12.7.1 Syntax                                  | 42           |

|     |      | 12.7.2 Semantics                               | 42           |

|     | 12.8 | Example of a simple macro 1                    | 43           |

| ۵   | ۸PA  | AL Keywords                                    | 4 22         |

| • * |      | -                                              | 45           |

|     |      | APAL instruction mnemonics                     |              |

|     | A.2  | System variables and functions 1               | 46           |

|     | A.3  | Other keywords                                 | 47           |

хіі

J

| В | Character set                                                    | 149         |

|---|------------------------------------------------------------------|-------------|

| С | Examples of APAL code                                            | 151         |

|   | C.1 Code fragment for matrix addition                            | 151         |

|   | C.2 Code fragment to extract and broadcast rows from array store | 152         |

|   | C.3 A fragment using macro facilities                            | 153         |

|   | C.4 Complete program: Conway's Game of Life                      | 153         |

| D | APAL syntax                                                      | 161         |

|   | D.1 Basic elements                                               | 161         |

|   | D.2 Comments                                                     | 16 <b>2</b> |

|   | D.3 Substitutions                                                | 16 <b>2</b> |

|   | D.4 Assembly-time values                                         | 163         |

|   | D.5 Assembly-time statements                                     | 164         |

|   | D.6 Macros                                                       | 166         |

|   | D.7 Values                                                       | 168         |

|   | D.8 Identifiers                                                  | 168         |

|   | D.9 Modules                                                      | 168         |

|   | D.10 Data identities                                             | 169         |

|   | D.11 Data sections                                               | 169         |

|   | D.12 Mixed sections                                              | 170         |

|   | D.13 Code sections                                               | 170         |

|   | D.14 Trace statements                                            | 171         |

|   | D.15 Addresses and instruction fields                            | 172         |

| E | Derivation of APAL instruction mnemonics                         | 175         |

| F | APAL instructions                                                | 179         |

|   | Index                                                            | 381         |

xiii

man005.03

-

xiii

xiv

# Chapter 1

# The architecture of DAP-series machines

This chapter describes the architecture of the whole range of DAP-series machines, and in particular those components of the architecture that are relevant to a programmer using the Array Processor Assembly Language (APAL).

# 1.1 The DAP series

The AMT DAP series of machines is the latest generation of a parallel processing architecture based on a 'distributed array of processors' (DAP). A DAP-series computer is connected to its host machine as an attached processor. A simulation system is also available, which enables you to develop and run programs in the absence of DAP-series hardware.

(In order to help you make easy reference to the accompanying figures, the text starts again on the next page.)

Chapter 1: The architecture of DAP-series machines

1.1: The DAP series

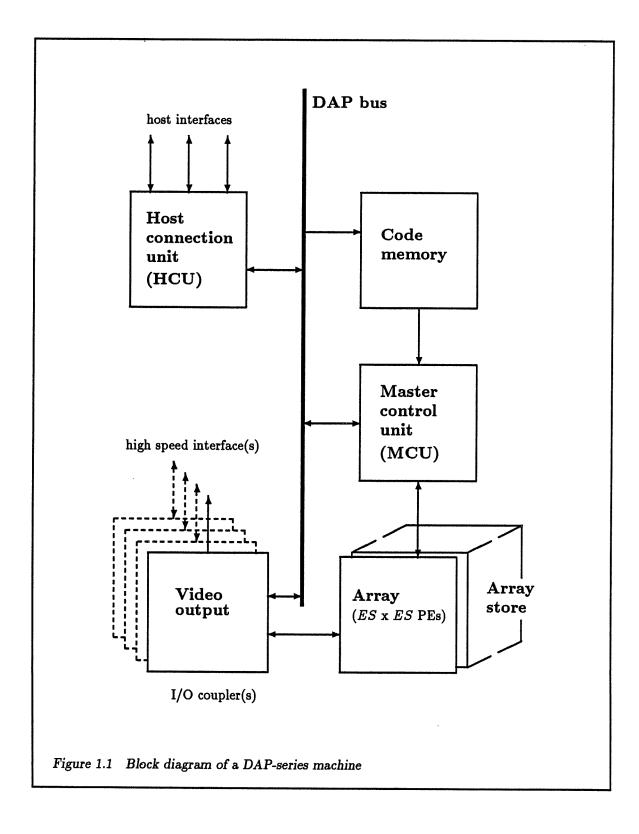

Figure 1.1 is a block diagram of a DAP-series machine. The backbone of all DAP-series machines is the DAP bus, an internal synchronous 32-bit multiplexed bus, into which the various component parts of the machine are connected.

The main computing resource in the DAP is the array or matrix of processor elements (PEs), which is closely connected to an array store that holds the data to be processed. A DAP-series machine achieves its high performance by having each processor element operate in parallel with all other processor elements; each element operates on its local data, subject to local (or activity) control when required.

The processors are arranged in a square matrix; the number of processors on one side of the square gives the edge size of the machine; AMT uses ES to signify edge size. The different ranges of machines in the DAP series are characterised by the value of ES. For the DAP 500 range, the array is a square matrix of 32 by 32 PEs – an ES of 32; for the DAP 600 range, ES is 64, and so on. Note that the edge size is a power of 2, the exponent being the first digit in the DAP model number (the other digits in the model number being the clock speed in MHz, with the memory size in Mbytes after the hyphen) so the DAP 600 range has an array size of  $2^6$  by  $2^6$  PEs, and so on for other ranges in the DAP series.

The array (the array of PEs or PE array) acts under the control of the master control unit (MCU). The MCU fetches and decodes instructions held in the separate code memory, broadcasting address and control information to all the PEs in parallel, along with data in some cases. The MCU also has facilities for integer scalar operations. Typically, the code memory is 0.5 Mbytes or more; the array store is  $ES^2 \ge 32$  K-bits or more, 16 Mbytes for the DAP 600 range for example.

The interconnection to the host computer is controlled by the host connection unit (HCU). Connection to the host is via any one of the 3 host interfaces, with the other 2 being available for low and medium speed data input and output. Communication between the host and your DAP program is managed for you by AMT-supplied library routines (see DAP Series: Program Development for further details), so the presence of the HCU is invisible to you as a user.

The design of the DAP-series caters for up to 4 high speed interfaces, for video or other high bandwidth requirements, with an available bandwidth of 50 Mbytes/sec, or higher in some situations. The set of I/O couplers fitted to any particular machine will depend on customer requirements. Note that the high speed input/output capability allows you to transfer data in and out of the array store at high speed, but it does not allow high speed transfers onto the DAP bus which only supports data transfers up to a few Mbytes/sec.

A program which runs on a DAP-series machine is called a DAP program. An associated program written in a conventional language is used on the host. This host program is entered first and is then responsible for starting the execution of the DAP program, and for data transfers to and from the DAP-series machine, using special interface subroutines. The preparation of a DAP program, and the interface subroutines, are described in the AMT manual DAP Series: Program Development. Different versions of this manual are available for each of the host operating systems under which AMT supports DAP operation.

Facilities also exist for a DAP program to read or write host filestore, and to communicate with peripherals connected directly to the DAP-series machine; consult AMT for further details.

You can write a DAP program in APAL, which is the subject of this manual, or in FORTRAN-PLUS (see DAP Series: FORTRAN-PLUS Language), or in a mixture of the two. If an APAL code section communicates with FORTRAN-PLUS or a host program, there are certain conventions to be followed; these are given in chapter 9. You can write the host program in any language or mixture of languages supported by the host operating system; however, if you want to use the special AMT-provided interface subroutines, you will find things are simplified if you write the calling sections in FORTRAN. For generality, the term FORTRAN as used in this manual is intended to include FORTRAN 77.

As with many other computer systems, more than one user program can be resident in the DAP at the same time, although only one program can be running at any given time. Each user program is allocated a contiguous range of code memory addresses and a contiguous range of array store addresses. Allocation of these resources is made by the HCU, and the running of individual user programs – on a time-slice-per-user-program basis – is scheduled by a supervisor program resident in the MCU. For further details of DAP's multi-programming facilities see DAP Series: Program Development.

# 1.2 The PE matrix

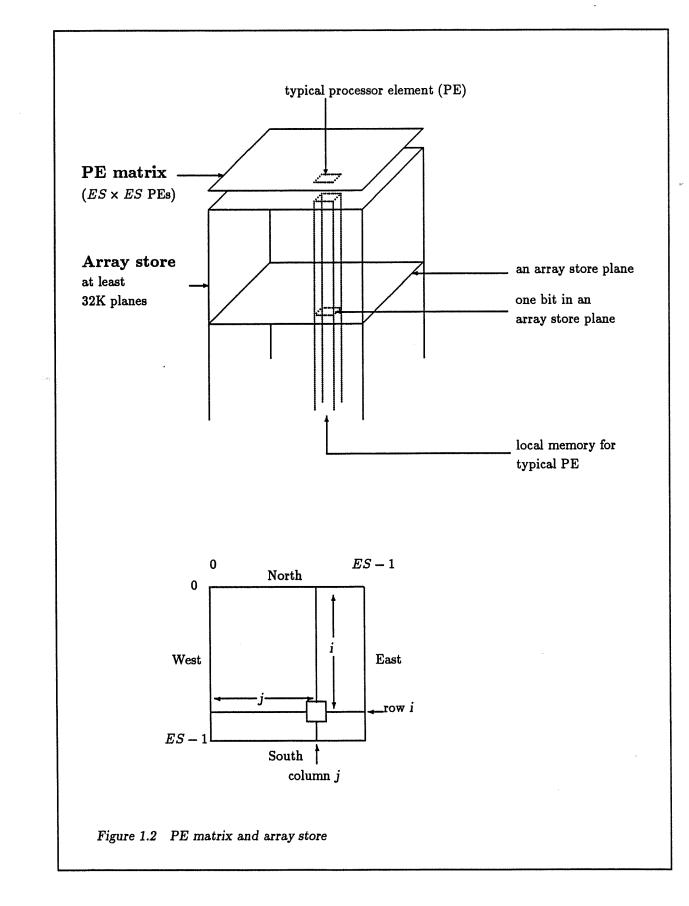

Figure 1.2 opposite shows a simple conceptual diagram of a DAP. As described briefly above, the parallel processing capability of a DAP-series machine is provided by a square matrix of ES by ES processor elements (PEs), with ES taking the value 32 for the DAP 500 range, 64 for the DAP 600 range, and so on. Each PE is capable of performing arithmetic and logical operations on operands that are single bit values.

In APAL the rows and columns of the PE matrix are each numbered from 0 to ES-1, as shown in the figure. (In FORTRAN-PLUS they are numbered 1 to ES). The edges of the array are referred to as North (row 0), East (column ES-1), South (row ES-1), and West (column 0).

Each PE is connected to the four neighbouring PEs in the north, south, east and west directions. Using these connections, data can be shifted from a register of each PE into the corresponding register of a neighbouring PE; a north shift means that data is shifted to the north.

# 1.3 The DAP code memory

The object code of a DAP program derived from APAL or FORTRAN-PLUS source resides in a separate code memory. The code area of a DAP program is delineated by hardware datum and limit registers, which are inaccessible to you, the user. You are concerned only with instruction addresses relative to the datum. If you try to use instruction addresses above the value in the limit register, or negative memory addresses (below the value in the datum register), you will cause a run-time error. The actual size of the code memory depends on the actual DAP-series machine concerned, but it will hold at least 128K instructions (512 Kbytes).

# 1.4 The DAP array store

Each of the ES by ES PEs has a local memory whose size depends on the actual DAP-series machine concerned, but is at least 32K (= 32,768) bits. The sum total of this PE storage is referred to as the array store, and is at least  $ES^2 \times 32$  K-bits, 4 Mbytes for the DAP 500 range for example.

5

The array store is best regarded as a three dimensional array of bits, as shown in figure 1.2, and consists of at least 32K memory planes.

A DAP word is 32 bits, so each memory plane can be looked on as ES rows of either ES bits or ES/32 words. Alternatively, an array plane can be considerd as ES columns of ES bits or ES/32 words. For example, for the DAP 600 range of machines, each memory plane can be described as 64 by 64 bits, or 64 rows of 64 bits each, or 64 rows of 2 words each, or 64 columns of 64 bits, and so on. Word 0 of each row is the most significant 32 bits of the row, so for example, on DAP 600 word 0 is bits 0 to 31 of the row, and word 1 is bits 32 to 63. The PE array maps onto the array store in such a way that the local memory for PE<sub>i,j</sub> consists of bit<sub>i,j</sub> of each memory plane.

Data can be transferred between the host and the array store in units of words, with one row of array store consisting of ES/32 words. The last (or only) word of each row is regarded by both DAP and host as immediately preceding the first word of the next row. The last word of a memory plane is regarded by both the DAP and the host as immediately preceding the first word of the next memory plane.

The array store holds the data of the DAP program. A single user program has a block of contiguous memory planes in array store; this block is delineated by hardware datum and limit registers which are inaccessible to you, the user. You are concerned only with memory addresses relative to the datum, that is, memory planes are numbered from zero, starting with the plane addressed by the datum register. If you try to access data outside the range defined by datum and limit, you will cause a run-time error.

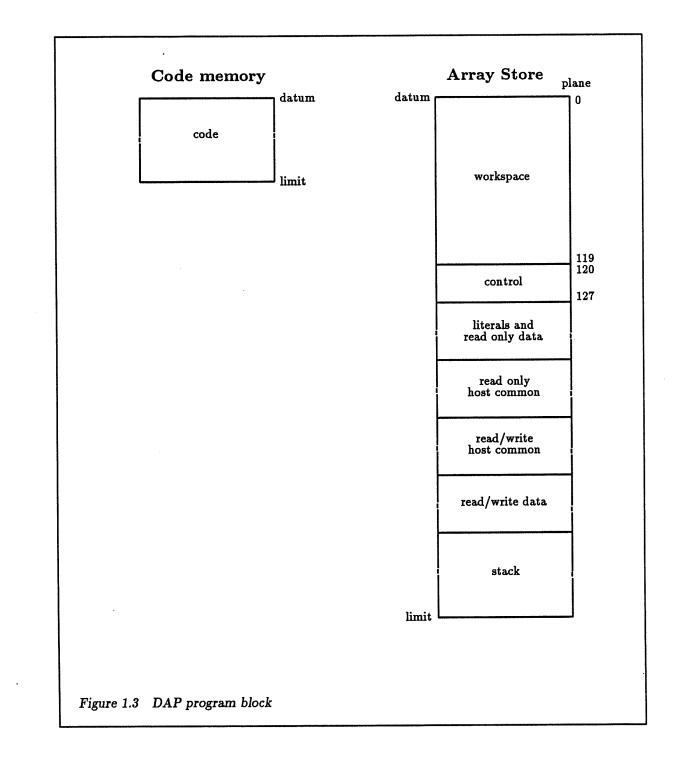

The two blocks of code and array stores assigned to your DAP program are known collectively as the DAP program block; its structure is shown in figure 1.3.

You can use planes 0 to 119 freely as workspace. Planes 120 to 127 are reserved for the run-time system and must not be written to. Certain literal values (created implicitly by some of the APAL instructions) occupy plane 128 onwards along with any APAL or FORTRAN-PLUS data sections declared to be read-only.

The stack area is managed by software according to conventions described in chapter 9. The size of the stack area is determined during the consolidation phase; it can be controlled by parameters input by you at consolidation time (for more details see the version of DAP Series: Program Development relevant to your host system).

# **1.5** Data mapping and number representation

You control the mapping of data onto the array store. Two mappings that are particularly well suited to the structure of DAP-series machines are:

- Vector (or horizontal) mode, in which successive bits of a data item are mapped onto successive bits of a single store row

- Matrix (or vertical) mode, in which successive bits of a data item are mapped onto the same bit position in successive store planes

These mappings correspond to FORTRAN-PLUS vector and matrix storage modes respectively (see DAP Series: FORTRAN-PLUS Language).

6

Because of the bit orientation of its hardware, a DAP-series machine is not committed to any particular representation of data. In general, a DAP-series machine regards data simply as arrays of bits, the interpretation of which (as fixed or floating point numbers, for example) is entirely dependent on software. However, you should note the following exceptions to this independence:

- The hardware supports arithmetic operations on 32-bit signed integers (2's complement) in the MCU registers

- The hardware supports the parallel addition of ES pairs of up to ES-bit integers held in the array

# **1.6 Processor element functions**

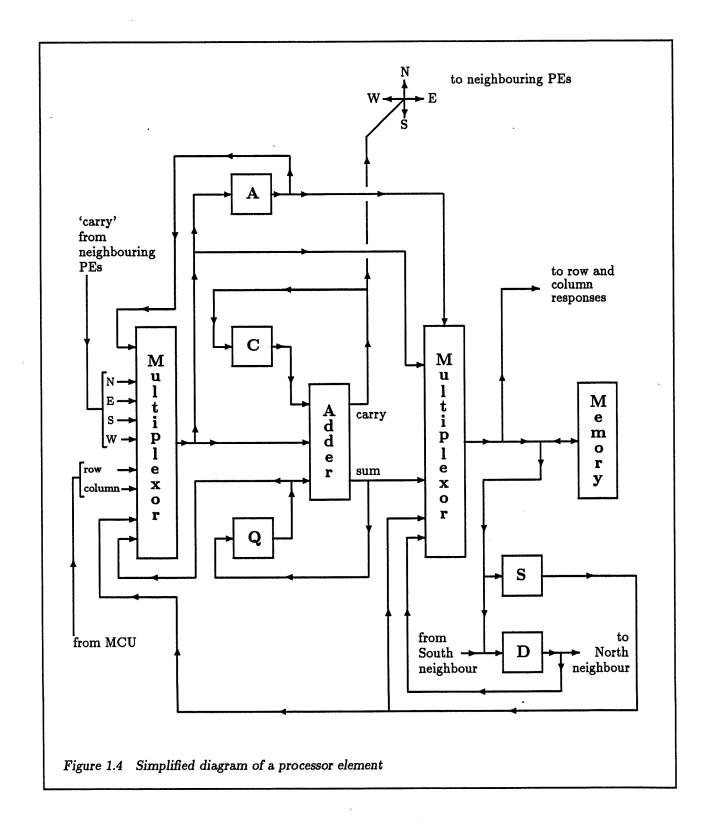

Figure 1.4 is a simplified diagram of one processor element (PE) showing its main functional components.

Each PE has three one-bit registers, denoted A, C and Q, each of which can be clocked or not, depending on the instruction.

The C- and Q-registers are input to an adder. Depending on the specific instruction either or both of these inputs can be treated as False (using AND gates, not shown in the figure).

The third adder input is selected by a multiplexor and can come from the PE's memory via the S register, the outputs of the Q- or A-registers, data broadcast by the MCU in either 'row' or 'column' orientation, or the carry output of a neighbouring PE. For each of these input sources, except the neighbour carry output, there is the option of inverting the multiplexor output using an Exclusive-OR gate (not shown in the figure).

The A-register also receives its input from this multiplexor, and it may either be written in directly or AND-ed (masked) with the existing A-register contents; this gating at the input to the A- register is not shown.

PE outputs may be written to memory, and in some instructions this writing is conditional on the value in the A-register, which thus acts as an activity control. With some instructions, there is the option of writing to just one row or one word of memory rather than to the entire plane.

The D-register shown in the PE diagram does not appear explicitly in the APAL programmers model of the PE, but is used for input or output under control of the fast input/output hardware.

Instructions that perform activity-controlled write-to-memory achieve their effect by performing a memory read-modify-write sequence. Clearly a register is needed somewhere in this path; the details are implementation dependent, but an example of such a register is shown as S in the diagram; again this register does not appear in the APAL programmer's model.

# 1.7 The MCU

The Master Control Unit (MCU) performs the following functions:

• Instruction fetching, decoding, and address generating

- Executing certain instructions, and broadcasting other instructions to the PE matrix for simultaneous execution by all PEs

- Providing fourteen 32-bit MCU registers to hold program data and addresses (see section 1.8)

- Transmitting data between the array store or the PE array, and the MCU registers

- Providing hardware support for APAL DO loops (see section 1.9)

- Supporting data transfers between the DAP and the host filestore or attached peripheral devices

## **1.8** MCU registers and the edge register

The MCU has fourteen 32-bit general-purpose registers that are visible to the low level programmer. There is another register, the *edge* register, whose size matches the size of the array edge (that is, *ES* bits). For example, in a DAP 600, the edge register is 64 bits wide.

Registers can be loaded in various ways from the array store or PE array, or a register's contents can be supplied as data to the memory or PEs. Logical and arithmetic operations are available to operate on the registers. Instructions can test the registers and SKIP on certain conditions, or use them to hold link values for subroutine entry and exit.

You can use a register's contents to modify addresses or values; a register being used in this way is referred to as a modifier register.

In more detail, the functions of the registers are:

- M0 to M13 are general purpose registers, which can hold link values or data, and be operated upon by MCU arithmetic or logical functions. You can also transfer the contents of these registers to or from the array

- M1 to M7 can always be used as modifiers. Register M0 is not generally available as a modifier, since value 0 in the instruction modifier field is interpreted as no modification; the exception is EXIT, where an instruction address rather than a data address is modified. For the DO instruction, you can use registers M1 to M13 as modifiers for the loop count. Instructions J and JE can use M1 to M13 as modifiers

- ME is the edge register, and is matched in size to the array edge size of ES bits. In a DAP 500 range machine, ME is the same size as the other registers; in all other ranges of DAP machine, ME is larger than the other registers. The ME register is regarded as being part of the array and can be used as the source or destination of data transferred to or from the array; it cannot in general take part in MCU arithmetic or logical operations or act as a modifier register

Registers M0 to M13 are referred to as MCU registers. You should NOT regard register ME, the edge register, as an MCU register.

In any DAP-series machine, the bits within an MCU register are numbered 0 to 31; within the edge register they are numbered 0 to ES - 1. Bit 0 is the most significant bit for both the edge

and MCU registers. When data is copied from a register to an array plane, the least significant bit in the register is aligned with the least significant bit in the row or column of the plane, and the register bits transferred across to similarly positioned bits in the row or column. When an MCU register is being used, the remaining ES - 32 bits (if any) in the row or column are zero-filled; when the edge register is used, no zero filling is necessary.

When data is transferred between an array plane and a register you can write the entire ES bits into the edge register, but only the least significant 32 bits into an MCU register (the most significant ES - 32 bits, if any, are discarded). Some instructions allow you to address a 32 bit word in the array and to transfer the contents of that word to or from an MCU register (but not to or from the edge register).

# 1.9 DO loops

A 'DO loop' is a sequence of instructions, invoked by a hardware DO instruction, which is executed a specified number of times, unless a premature exit is taken.

Instructions in a 'DO loop' can, on successive iterations of the loop, access successive bit-planes, rows, columns or words of memory, or bits in an MCU register or the edge register. This process is referred to as 'address stepping'. It is implemented by adding the DO loop iteration number to, or subtracting it from, addresses or values (which can also have the contents of a modifier register added) to give the addresses or values that are 'effective' for that particular execution of the instruction. The result of address generation can thus have 'effective ADDR' (that is, bitplane number), 'effective INT' (that is, row, column or bit number) and 'effective word address' components. The address generation process is fully described in section 7.1. The iteration number used for address stepping is zero in the first pass of the loop and is incremented at the end of each pass of the loop. Some instruction types can apply this stepping in one of two ways - see section 7.1.2 for more details.

# 1.10 C- and V-flags

Each of the C-flag (Carry) and V-flag (Overflow) is a 1-bit flag written to by MCU scalar instructions; the flags are normally thought of as holding Boolean values.

The C-flag is affected as follows, the operands being regarded as 32-bit unsigned values:

- For addition, the C-flag is the same as the Carry-out of the most significant bit of the sum

- For subtraction, if operand 2 is less than or equal to operand 1, the C-flag is set to True (that is, 1); otherwise it is set to False (that is, 0). Hence C is the inverse of 'borrow'

Some variants of add and subtract also use the C-flag as the carry-in or inverted borrow-in respectively.

The V-flag is also set according to the result of the above instructions, the operands and result being regarded for this purpose as 32-bit signed (2's complement) integers:

• For addition, if the two operands have the same sign, then the V-flag becomes True if the result sign is different; in all other cases, the V-flag becomes False

• For subtraction, if the two operands have different signs, then the V-flag becomes True if the result sign is different from that of the first operand; in all other cases, the V-flag becomes False

Some of the multiply instructions that return only a single length result set the V-flag according to the discarded most significant half of the product. For further details see the entries for the MPY32V and MPYU32V instructions in appendix F at the back of this manual.

## 1.11 Array edge dimensions

This manual is general to the whole range of DAP-series machines. The design of APAL is such that you can write source code that is portable across the whole range of DAP-series machines.

The main aspects of the strategy to achieve this edge-size independence are:

- MCU registers are fixed at 32 bits. Thus, when an edge-sized response is returned to the MCU, all but the least significant 32 bits are discarded. Similarly when data is broadcast, the MCU register contents are normally extended on the left (more significant end) with zeros

- The edge register grows in size to match the array dimension

- A DAP word is a 32-bit data item. On DAP 500, words and rows are equivalent; on larger sized arrays, a word is part of a row, and instructions that transfer a single word to or from an MCU register are available. If you want to make sure your DAP code is portable between all edge-sizes of DAP, you should use word addressing rather than row addressing for accessing scalars and addresses held in array store

- Addresses held in modifier registers are always stored in the format of a word address, regardless of whether the modifier is used by a word access instruction or a row access instruction. Thus on the larger edge-size arrays, one or more word-within-row address bits are inserted at the least significant end of the modifier register. In the case of a row access, any word-within-row bits of the modifier are ignored.

If you want your code to be portable between all edge sizes of DAP, rather than trying to specify address modifiers directly as literals, you should use instructions **RAX** and **RAW** to construct modifier values that are edge size dependent, and so give you the results you want for all edge sizes

• The Assembler permits the size of array for which the code is being assembled to be accessed at assembly time (see section 11.4.2)

# Chapter 2

# **APAL** source program format

This chapter covers a number of general points concerned with writing a source program in the Array Processor Assembly Language (APAL).

The characters that can be used in an APAL source program are described in section 2.1.

The format of identifiers in APAL is described in section 2.2.

The format of the various types of data values that can be written in APAL are described in section 2.3.

Continuation lines and comments are described in sections 2.4 and 2.5.

### 2.1 Character set

#### 2.1.1 Syntax

<character> ::= <basic character> | <special character>

$\begin{array}{l} < \text{basic character} > ::= < \text{letter} > | < \text{digit} > | [ | ] | . | < | = | > | + | - | / | ( | ) | _ | , | \\ & : | \& | \# | \pounds | \$ | < \text{star} > | @ | ; | \setminus | `(\text{single quotes}) | < \text{space} > | \\ & < \text{question} > | < \text{vertical bar} > | { | } | ` (\text{grave}) | ~ (\text{tilde}) \\ \end{array}$

<special character> ::= ! | ^ | % | "

$\begin{array}{l} < letter > ::= A \mid B \mid C \mid D \mid E \mid F \mid G \mid H \mid I \mid J \mid K \mid L \mid M \mid \\ & N \mid O \mid P \mid Q \mid R \mid S \mid T \mid U \mid V \mid W \mid X \mid Y \mid Z \mid \\ & a \mid b \mid c \mid d \mid e \mid f \mid g \mid h \mid i \mid j \mid k \mid l \mid m \mid \\ & n \mid o \mid p \mid q \mid r \mid s \mid t \mid u \mid v \mid w \mid x \mid y \mid z \end{array}$

<digit> ::= 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

<alphanumeric character> ::= <letter> | <digit> | '

Chapter 2: APAL source program format

$\langle star \rangle ::= *$

14

<vertical bar> ::= |

<question> ::= ?

#### 2.1.2 Semantics

You can write the source text of an APAL program using any of the characters listed in section 2.1.1. The internal hexadecimal representations of these characters are listed in appendix B at the back of this manual.

You can use a comma as a separator between syntactic constructs in the same way as a space.

For example:

FRED: 0 1 3.14 10

can also be written as:

FRED: 0, 1, 3.14, 10

Note, however, that in certain cases commas are obligatory.

The escape character, ^, can be used to alter the way in which certain special characters are interpreted by the assembler.

The underscore character, \_, can appear anywhere in the source text. If it appears within a character value (see section 2.3.4), it is significant; that is, the assembler treats it like an alphanumeric character. If underscore appears in any other context, it is removed by the assembler. For example, the following are all equivalent:

ABCD AB\_CD AB\_C\_D

whereas the following character values are all distinct:

"ABCD" "AB\_CD" "AB\_C\_D"

Certain APAL instruction mnemonics are commonly written with an underline character to aid clarity, but this is unnecessary; for example the following are equivalent:

QT\_CF QTCF

Note that the symbols # and  $\pounds$  are equivalent; # is used in this publication.

# 2.2 Identifiers

#### 2.2.1 Syntax

<identifier> ::= <letter> <alphanumeric character>\* | '<alphanumeric character>\*

#### 2.2.2 Semantics

Identifiers are user-defined names that represent instances of various types of entity in APAL. An identifier is a string of up to 32 characters, the first of which must be either a letter or a single quotes symbol. Note however, that by convention only system variables and functions (see sections 10.1 and 11.4.2) begin with a single quote. The single quote, the ' characater, is also known an apostrophe, and has the ASCII value of hexadecimal 27.

The remaining characters in the identifier can be any of the alphanumeric characters described in section 2.1.1. The following are all examples of valid identifiers:

NAME THIS\_IS\_AN\_IDENTIFIER 'PCOUNT VAR123A

Note that two identifiers that differ only in the presence of underscore characters are considered by the assembler to be equivalent.

Identifiers can be used to represent the following APAL entities:

- Modules and module aliases

- Code, data, and mixed sections

- Entry points within code sections

- Data identities

- Data variables

- Code labels

- Assembly-time variables

- Macros, macro parameters, and macro variables

APAL contains no reserved words, although a number of APAL keywords have special significance within an APAL program; examples of these keywords include instruction mnemonics and assembly-time statements. APAL keywords are listed in appendix A.

Since APAL keywords are not reserved words you can use them as identifiers, although in the interests of clarity you are recommended not to use them. In particular, you should be aware of the consequences of declaring a macro whose name is the same as an instruction mnemonic or assembly-time statement (see chapter 12).

The assembler considers upper and lower case characters to be equivalent in identifiers and APAL keywords. For example, the following are equivalent:

END\_MODULE Endmodule

16

## 2.3 Format of data values

This section describes how the various types of data value that can be manipulated by the assembler are written within an APAL statement.

You can write integer, real, hexadecimal, or character values in an APAL statement. The internal representation of these values is described in chapter 4.

You can also write values that are to be manipulated at assembly time; assembly-time values are described in chapter 11.

#### 2.3.1 Integer values

2.3.1.1 Syntax

<integer value> ::= <unsigned integer> | <signed integer> | <hexadecimal value>

<unsigned integer> ::= <basic integer> | <basic integer>I<basic integer>

<signed integer> ::= <sign>?<unsigned integer>

<basic integer> ::= <digit><digit>\*

< sign > ::= + | - |

#### 2.3.1.2 Semantics

An integer value, in general, can be:

- An unsigned integer value, consisting of a sequence of digits with no intervening spaces, referred to as a basic integer

- A signed integer value, which is an unsigned integer value that can optionally be preceded by a + or -

- Either form of the above forms of integer value can be followed by an *integer exponent* of the form:

I basic integer

which causes the preceding signed or unsigned integer value to be multiplied by  $10^n$ , where n is the value of *basic integer*.

• A hexadecimal value (see section 2.3.3)

man005.03

#### 2.3: Format of data values

#### Note

+359 is a signed integer; 359 can be considered as either a signed or unsigned integer. If +359 is included in an APAL statement where an unsigned integer is expected, you will get an assembly-time error.

#### Examples

| 2349  |                                                        |

|-------|--------------------------------------------------------|

| -812  |                                                        |

| +43I6 | (equivalent to 43,000,000; or 43 x 10 <sup>6</sup> $)$ |

| -912  | (equivalent to -900)                                   |

#### 2.3.2 Real values

#### 2.3.2.1 Syntax

```

<real value> ::= <sign>?<basic integer><exponent> |

<sign>?<basic integer>.<basic integer>?<exponent>? |

<sign>?.<basic integer><exponent>?

```

```

<exponent> ::= E<sign>?<basic integer>

```

#### 2.3.2.2 Semantics

A real value, in general, can be any of:

- An unsigned real value, consisting of two basic integer values separated by a decimal point. Either integer value, but not both, can be omitted

- A signed real value, which is an unsigned real value that can optionally be preceded by a + or -

- Either of the above forms of real value can be followed by an exponent of the form:

E sign basic integer

where sign is optional. This causes the preceding signed or unsigned real value to be multiplied by  $10^n$ , where n is the value of sign basic integer. If this form is used, then the decimal point can be omitted

#### Examples

| 18.      |                        |

|----------|------------------------|

| 427      |                        |

| 18.427E2 | (equivalent to 1842.7) |

| 142E–1   | (equivalent to 14.2)   |

| 92.E+2   | (equivalent to 9200.0) |

Chapter 2: APAL source program format

## 2.3.3 Hexadecimal values

2.3.3.1 Syntax

18

<hexadecimal value> ::= #<hexadecimal digit><hexadecimal digit>\*

<br/> <br/> <br/> <br/> <br/> digit> ::= <digit>  $\mid A \mid B \mid C \mid D \mid E \mid F \mid a \mid b \mid c \mid d \mid e \mid f$

#### 2.3.3.2 Semantics

A hexadeximal value is written as the # character followed by a sequence of hexadecimal digits. A hexadecimal value can be used wherever an integer value can appear.

Examples

| #9  | (equivalent to 9)  |

|-----|--------------------|

| #A  | (equivalent to 10) |

| #1F | (equivalent to 31) |

#### 2.3.4 Character values

#### 2.3.4.1 Syntax

<character value> ::= "<value character>\*"

<value character> ::= <basic character> | ^<special character>

#### 2.3.4.2 Semantics

A character value is written as a sequence of characters enclosed within double quotes ("). Any of the characters listed in appendix B can be included in a character value, except for the four characters:

! ^ % "

which have special significance for the assembler and are therefore called signifier characters. A signifier character can be included in a character value by preceding it with the escape character ^; the escape character itself is removed by the assembler and does not appear in the value. The escape character can also precede a character that is not a signifier character and will be removed by the assembler, but it cannot be the last character in a character value.

Examples

| "ABCD"       | (character value ABCD)     |

|--------------|----------------------------|

| "AB^%CD"     | (character value AB%CD)    |

| "AB^"CD"     | (character value AB"CD)    |

| "AB^ ^CD"    | (character value AB ^ CD)  |

| "AB^ ^ ^%CD" | (character value AB ^ %CD) |

# 2.4 Continuation lines

Any APAL statement, as defined in section 3.1, can be continued onto any number of succesive continuation lines. A line is recognised as a continuation line if it contains a hyphen in the first character position of the line. In the formal syntax of later chapters, the entity <newline> implies the new line character at the end of the last continuation line (if any) of the statement in question.

A source line or continuation line can contain at most 80 characters.

Note that an identifier, a value, a string, or a substitution (see chapter 11) must appear wholly on a single line.

## 2.5 Comments

#### 2.5.1 Syntax

<comment> ::= ! <comment character>\*

<comment character> ::= <basic character> | ^<special character>

#### 2.5.2 Semantics

An APAL program can be documented by the use of *comments*. The start of a comment is indicated by the ! character; a comment is always terminated by the end of the line. A line can consist entirely of comment. A comment can be used in a statement involving continuation lines but the comment is not itself continued, although further comments can be added to the continuation line(s). For example:

| SVAR = 12.6 + | <b>! PUTS 12.6 PLUS CONTENTS OF VARIABLES</b> |

|---------------|-----------------------------------------------|

| – SSTART +    | ! SSTART                                      |

| – SEND        | ! AND SEND                                    |

|               | ! INTO SVAR                                   |

A comment can include text consisting of any of the characters specified in section 2.1.1.

Note that the ! character is always recognised as signifying a comment, except in the following cases:

- When ! appears within a character value (see section 2.3.4)

- Within a string when it is preceded by ^ (see chapter 11)

Substitutions can take place within comments (see chapter 11).

Chapter 2: APAL source program format

# Chapter 3

# **APAL** source program structure

The APAL assembler processes files of APAL source. These files are first read by a pre-processor, which can insert the contents of other source files where specified by a file include statement. Such included files can include other files up to a maximum nesting level of 16. The interface to the assembler and the file include facility are described in DAP Series: Program Development; see the version of the manual relevant to your host system.

APAL source text can be interspersed with assembly-time variable definitions or expressions (see chapter 11) and macro definitions or calls (see chapter 12). These definitions are not considered to be part of a module declaration; however, after the effects of such statements have been taken into account, a module declaration must follow the pattern described in chapters 3 to 5. Note that the exact position of an assembly-time variable declaration or macro definition in the source text can affect its scope (see section 3.2).

Each APAL module declaration processed by the assembler results in one CIF module (Consolidator Input Format) as part of a CIF file suitable for input to the DAP linker. The output from the linker is a single DOF file (DAP Object Format) which can be loaded into the DAP code and array stores to form part of the user's DAP program block. Management of CIF files and use of the DAP Consolidator are described in DAP Series: Program Development.

This chapter describes:

- How you declare an APAL module

- The contents of an APAL module

- The scope of identifiers within an APAL source program

# 3.1 Declaring an APAL module

This section describes the declaration and contents of an APAL module.

#### 3.1.1 Syntax

22

<module declaration> ::= <module header><module body>\*<module end>

<module header> ::= MODULE<module name><alias>\*<newline>

<module name> ::= <identifier>

<alias> ::= <identifier>

<module body> ::= <data section> | (see chapter 4) <code section> | (see chapter 5) <mixed section> | (see chapter 5) <global data identity> (see chapter 4)

<module end> ::= ENDMODULE <module name>?<newline>

#### **3.1.2** Semantics

Each source file you present to the APAL assembler can contain APAL module declarations. An APAL module is the smallest unit of source for which the assembler will generate CIF output.

A module declaration begins with a module header of the form:

MODULE module-name alias<sub>1</sub> alias<sub>2</sub> ... alias<sub>n</sub>

where

module-name is the user-defined name given to the CIF module produced by the assembler for this module

Each of the  $alias_i$ , which are optional, is an alternative name for the module. The aliases of a module, together with the module name, comprise the module synonyms. The synonyms are used by the linker to satisfy outstanding unsatisfied external references (see DAP Series: Program Development)

An APAL source module is terminated by:

ENDMODULE module-name

where module-name, if given, must be the same name as that used in the module header.

You can include in an APAL module any of the following, in any order:

- Data sections, which allocate and optionally initialise areas of the DAP program block and allow these areas to be referred to by name (see chapter 4)

- Code sections, which contain APAL instructions (see chapter 5)

- Mixed sections, which consist of a data part followed by an associated code part (see chapter 5)

• Global data identities, which associate user-defined names at assembly time with addresses in the DAP program block, thereby permitting forward and external references to data (see chapter 4)

Comments can appear anywhere in a module.

# 3.2 Scope of identifiers

The scope of a user-defined identifier is that part of the APAL program to which the identifier is visible; that is, the part in which the name can be referenced in an APAL instruction or assembly-time statement.

The scope of an identifier can be:

- EXTERNAL External identifiers are visible to all modules. An external identifier can be any of the following:

- A module name or alias

- Section or entry point names with the HOST or DAP property (see chapters 4 and 5)

- The name of a macro defined outside a module

- The name of an assembly-time variable declared outside a module

- GLOBAL Global identifiers are visible throughout the module in which they are declared, but are not visible to any other module. A global identifier can be any of the following:

- Section or entry point names with neither HOST nor DAP properties (see chapters 4 and 5)

- The name of a macro defined in the same module

- The name of an assembly-time variable declared in the same module

- The name of a data variable declared in a data section in the same module

- The name on the left hand side of a global data identity (see section 4.3) in the same module

- LOCAL Local identifiers are only visible within the module, or part of the module, in which they are declared (for example, within a particular section). A local identifier can be any of the following:

- A macro parameter or macro variable (see chapter 12)

- A code label (see section 5.2)

- The name of a data variable declared in the data part of a mixed section (see chapter 5)

- The name on the left hand side of a local data identity

You must declare all identifiers before referencing them, with the following exceptions:

- Code labels

- Code sections and entry points

- Data section names used on the right hand side of global or local data identities

For the purposes of determining the uniqueness of identifiers, the following *classes* of identifiers are distinguished by the assembler:

- 1 Names of assembly-time variables

- 2 Names of macros

- 3 Names of macro parameters and macro variables

- 4 All other names (see section 2.2)

At any particular point in an APAL program, all the visible identifiers of any one of the above classes must be different. An identifier in one class can be the same as an identifier in another class; for example, a macro can have the same name as an assembly-time variable. Note that the assembler performs no checking of identifiers between modules; the visibility of external identifiers is a linker facility and an error will be flagged at linking time if a clash occurs.

The following table summarises the scope and uniqueness rules described above.

| Type of identifier                               | Scope    | Uniqueness                                                                                                                                                                                       |

|--------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assembly-time variable declared outside a module | External | The identifier must differ from all other assembly-time variables                                                                                                                                |

| Assembly-time variable declared within a module  | Global   | The identifier must differ from all other<br>assembly-time variables in the same mod-<br>ule and from any assembly-time variables<br>declared previously outside any modules<br>in this assembly |

| Macro defined outside a module                   | External | May be the same as any other identifier<br>(see note 1 below)                                                                                                                                    |

| Macro defined within a module                    | Global   | May be the same as any other identifier (see note 1 below)                                                                                                                                       |

| Macro parameter                                  | Local    | The identifier must differ from all other<br>parameter and variable names in the<br>same macro definition                                                                                        |

24

AMT

#### 3.2: Scope of identifiers

| Type of identifier                                        | Scope    | Uniqueness                                                                                                                                     |

|-----------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Macro variable                                            | Local    | The identifier must differ from all other<br>variable and parameter names in the<br>same macro definition                                      |

| Section or entry point names with<br>HOST or DAP property | External | The identifier must differ from all other<br>class 4 identifiers (as defined on the pre-<br>vious page)                                        |

| Other section or entry point<br>names                     | Global   | The identifier must differ from all other class 4 identifiers                                                                                  |