## 386 Series 2000 Field Service

# Altos Computer Systems

#### Document History

| Edition        | Part Number    | Date      |

|----------------|----------------|-----------|

| First Edition  | 690-20674-001A | May 1987  |

| Second Edition | 690-20674-001  | June 1987 |

#### **Copyright Notice**

Manual Copyright ©1987 Altos Computer Systems

Programs Copyright © 1987 Altos Computer Systems

All rights reserved. Printed in U.S.A.

Unless you request any received written permission from Altos Computer Systems, you may not copy any part of this document or the Software you received, except in the normal use of the Software or to make a backup copy of each diskette you received.

#### Trademarks

The Altos logo, as it appears in this manual, is a registered trademark of Altos Computer Systems.

UNIX\* is a registered trademark of AT&T.

UNIX System III<sup>™</sup> is a trademark of AT&T.

XENIX\* is a registered trademark of Microsoft Corporation.

MULTIBUS\* is a registered trademark of Intel Corporation.

IBM\* is a registered trademark of International Business Machines Corporation.

PC/AT\* is a registered trademark of IBM Corporation.

System 34 Double Density (MFM)' is a registered trademark of IBM Corporation.

Scotch<sup>™</sup> is a trademark of 3M Corporation.

3270/SNA is an Altos Implementation of ACCESS/SNA developed by Communications Solutions, Inc.

WorkNet\* is a registered trademark of Altos Computer Systems.

#### Limitations

Neither Altos nor its suppliers make any warranty with respect to the accuracy of the information in this manual. Altos Computer Systems reserves the right to make changes to the product described in this manual at any time and without notice.

#### FCC Warning

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Only devices certified to comply with the limits for a Class A computing device may be attached to this equipment. Operation with non-certified device(s) is likely to result in interference to radio and TV reception.

This equipment is intended for commercial use only and is not suited for operation in Class B environments.

The use of shielded I/O cables is required when connecting the equipment to any and all optional peripheral or host devices. Failure to do so may violate FCC rules.

## **About This Manual**

This manual contains detailed information for field-service personnel who are trained in digital electronics, microcomputers, and operating systems.

The purpose of this manual is to describe the operation of the Altos 386 Series 2000 Computer System and provide specific information to enable the field-service technician to effectively service the computer system at the customer site.

Careful attention to the maintenance information contained in this manual will ensure maximum trouble-free operation from the system.

This manual is organized into the following parts and chapters:

## Part I Overview

#### **Chapter 1 System Description**

- describes the features and capabilities of the system

- provides a hardware overview of the major circuits and peripherals

- lists and shows the location of the field replaceable assemblies comprising the system

- describes and shows the dedicated and recommended expansion plug-in printed circuit board locations

- describes and shows the locations of the front and rear-panel controls, connectors, and indicators

- discusses the software available for the system

#### Chapter 2 Subsystem Operation

- explains how the major subsystems interface to the system through the system bus

- describes how each major subsystem operates

## Part II Maintenance

#### **Chapter 3 Power-Up Checks**

- provides a guide for determining which diagnostic test procedures to use

- discusses troubleshooting techniques

- includes preliminary trouble analysis information for a dead system

- includes a discussion of the monitor program

- describes the power-up sequence

- provides a description of the power-up tests

- includes trouble-analysis information

#### **Chapter 4 Floppy-Based Diagnostics**

- provides instructions for booting the diagnostic floppy disks

- describes the system-confidence (SDX) tests

- describes the field-service (FDX) tests

- includes trouble-analysis information

#### Chapter 5 Monitor Debugger

• describes the monitor communication protocol and system calls

• describes the debugger tests

#### **Chapter 6 Removal/Replacement**

- provides procedures for removing and replacing the field-replaceable units (FRUs)

- includes instructions for shipping FRUs

#### **Chapter 7 Preventive Maintenance**

• provides cleaning procedures

#### Appendices

- A Jumpers and Switches. Describes the jumper and switch settings for the system.

- B Utilities. Includes procedures for using the utility programs available on the System Diagnostics Executive (SDX) and Field Diagnostics Executive (FDX) floppy disk.

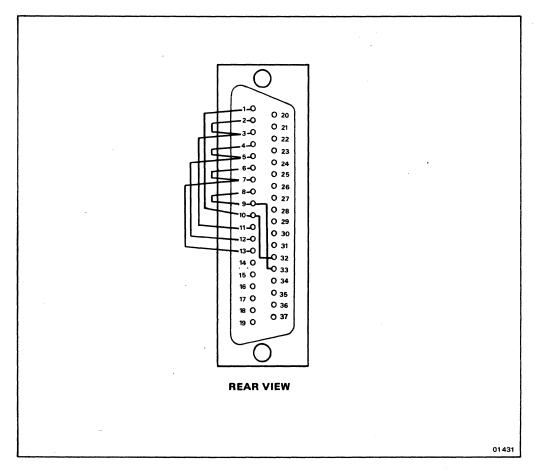

- C Loopback Connectors. Illustrates the proper jumper connections for assembling the loopback connectors required to perform the diagnostic procedures.

- D System Specifications. Lists the system electtrical, environmental, and physical specifications.

- E Storage Device Specifications. Lists detailed manufacturer's specifications for each qualified tape, floppy, and hard disk drive currently used in the system.

- F 115/230 VAC Conversion. Provides procedures for converting the system to 115 or 230 volt AC operation.

- G Multidrop Cables and Terminators. Provides information for making your own multidrop cables and terminators.

- H Power Consumption Chart. Provides power consumption information for the available Series 2000 configurations.

#### Glossary

Includes an alphabetical list and definitions of specialized terms and acronyms used in this manual.

## **RELATED PUBLICATIONS**

The following is a list of publications that contain information relating to the Series 2000 system. The Altos 386 Series 2000 Owner's Guide is shipped with the Series 2000. The remaining publications are optional and are divided into three types:

- basic (run-time) system manuals for installing and using the operating system

- development system manuals that include reference and tutorial material for programs available in the development system

- supplemental information manuals that are referenced in the text of this manual and contain additional information required to understand the operation of the system. (Includes maintenance manuals required to service the system.)

The publications listed here are available through an Altos distributor or directly from integrated circuit manufacturers.

## Shipped With Series 2000

Altos 386 Series 2000 Owner's Guide (Altos part no. 690-20351-xxx)

## **Basic System**

- Installing XENIX (Altos part no. 690-16630-xxx)

- XENIX/UNIX Using the AOM Menu System (Altos part no. 690-18055-xxx)

- XENIX Commands Directory (Altos part no. 690-16640-xxx)

## **Development System**

XENIX Development System Set (Altos part no. 690-18607-xxx)

## **Supplemental Information**

- Altos 386 Series 2000 Maintenance Manual (Altos part no. 690-20652-xxx)

- Altos 386 Series 2000 Illustrated Parts List (Altos part no. 690-xxxxx-xxx)

- Intel IAPX 386 Programmer's Reference Manual

- Intel IAPX 286 Programmer's Reference Manual

- Intel Microsystem Components Handbook

- Motorola 141868A Data Sheet

- Advanced Micro Devices 9517 Technical Data Sheet

- Zilog Data Handbook/Technical Manual

- Zilog Z8536 and Z8530 Technical Reference Manuals

- Siemans SAB82258 ADMA User's Manual

- Hitachi Microcomputer Data Book

- Hitachi HD68450 DMAC Application Notes Handbook

- National Cash Register 5385 SCSI Protocol Controller Data Sheet

- Archive QIC-02 1/4 Inch Tape Drive Interface

- Archive QIC-24 1/4 Inch Cartridge Tape Drive Format

- Archive QIC-36 Basic 1/4 Inch Cartridge Streaming Tape Drive Interface

- NEC Data Handbook

- ANSI X3T9.2/82-2 SCSI Small Computer System Interface

- National Cash Register Data Handbook

## SPECIAL SYMBOLS AND NOTATIONS

The following is a list of the special symbols and notations used in this manual:

| Symbol/<br>Notation | Description                                                                                                                   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| * (Asterisk)        | Used following a capitalized mnemonic or signal name<br>to indicate a "not" (complement) function or an<br>active low signal. |

|                     | Example: PERR*                                                                                                                |

| h                   | Used after a number to indicate that the number is a hexadecimal notation.                                                    |

|                     | Example: 25h                                                                                                                  |

| d                   | Used after a number to indicate that the number is a decimal notation.                                                        |

|                     | Example: 16d                                                                                                                  |

| b                   | Used after a number to indicate that the number is a binary notation.                                                         |

|                     | Example: 01b                                                                                                                  |

0

## (BLANK)

## x

## PART I OVERVIEW

1-9

1-9

- **1** SYSTEM DESCRIPTION

- 1-3 INTRODUCTION

- 1-3 Features

- 1-4 Architecture

- 1-4 Configurations

- 1-6 Networking

- 1-6 Communications

- 1-8 Terminal Cluster Units

- 1-8 Diagnostics

- 1-8 Power-Up Tests

- System-Confidence Tests

- Field-Service Diagnostics

- 1-9 CONTROLS, CONNECTORS, AND INDICATORS

- 1-11 Cabinet Front Panel

- 1-11 Cabinet Rear Panel

- 1-11 Multidrop Communications Board

- 1-12 SIO Communications Board

- 1-12 File Processor Board

- 1-12 Terminal Cluster Units

- 1-15 FIELD-REPLACEABLE UNITS

- 1-16 SYSTEM SOFTWARE

- 1-17 Operating System Programs

- 1-18 Diagnostics and Utilities

- 1-18 PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS

#### **2** SUBSYSTEM OPERATION

- 2-3 INTRODUCTION

- 2-3 BLOCK DIAGRAM DESCRIPTION

- 2-3 System Bus

- 2-4 Central Processing Unit (CPU)

- 2-5 80386 Address Map

| 2-8  | System Memory            |

|------|--------------------------|

| 2-9  | Multidrop Communications |

| 2-10 | SIO Communications       |

- 2-11 File Processor

- 2-12 ESDI Controller

- 2-12 Terminal Cluster Unit

## **PART II MAINTENANCE**

HOW TO USE THIS SECTION

#### **3 POWER-UP CHECKS**

- **3-3** INTRODUCTION

- 3-3 PRELIMINARY TROUBLE ANALYSIS

- 3-6 MONITOR COMMUNICATION PROTOCOL

- 3-7 SYSTEM POWER-UP SEQUENCE

- 3-10 POWER-ÚP TESTS

- 3-11 Communications (Multidrop or SIO) Power-Up Tests

- 3-12 CPU Power-Up Sequence

- 3-14 CPU Monitor Address Map

- 3-15 Global Descriptors

- 3-17 Universal Parameter Block

- 3-18 CPU Power-Up Tests

- 3-30 File Processor and Controller Power-Up Tests

- 3-33 CPU AND FILE PROCESSOR COMMUNICATION

- 3-33 Interrupt Signals

- 3-33 Communication Protocol

- 3-34 Boot Failures

#### 4 FLOPPY-BASED DIAGNOSTICS

- 4-3 SYSTEM-CONFIDENCE TESTS

- 4-3 Booting the SDX Disk

- 4-7 FIELD-SERVICE TESTS

- 4-7 Field Diagnostic Executive Menu

- 4-12 CPU Test Menu

- 4-21 File Processor and Controller Test Menu

- 4-26 SIO Test Menu

| 4-32 | File Processor Board Level Test Menu     |

|------|------------------------------------------|

| 4-36 | Multidrop Communications (MDC) Test Menu |

#### 5 MONITOR DEBUGGER

- 5-3 INTRODUCTION

- 5-4 MONITOR COMMUNICATION PROTOCOL

- 5-4 CPU Debugger Commands

- 5-5 Debugger Command Conventions

- 5-15 Special Control Keys

- 5-16 Communications Debugger Commands (Software Mode)

- 5-20 Multidrop Communications Debugger Commands (Hardware Mode)

- 5-33 SIO Communications Debugger Commands (Hardware Mode)

#### **6 REMOVAL/REPLACEMENT**

- 6-3 INTRODUCTION

- 6-3 HANDLING STATIC-SENSITIVE DEVICES

- 6-4 REMOVAL/REPLACEMENT PROCEDURES

- 6-4 Removing the Front Panel

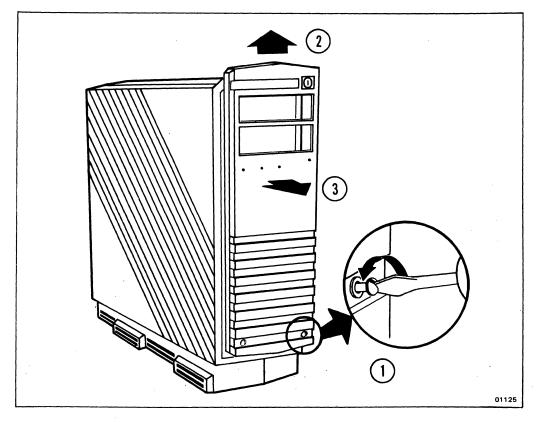

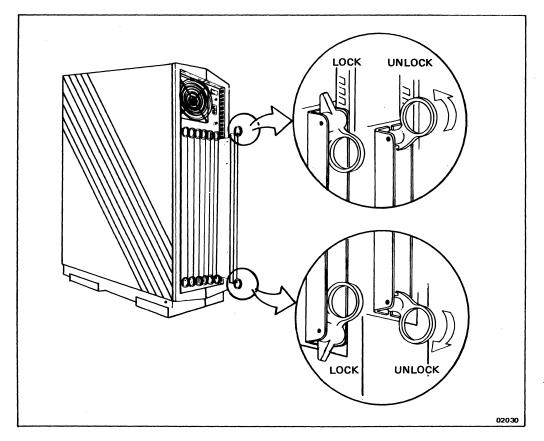

- 6-5 Removing the Side Panels

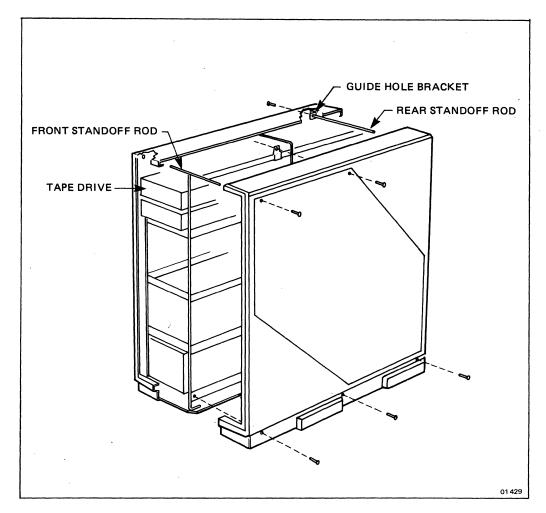

- 6-7 Removing the Tape Drive

- 6-9 Replacing the Tape Drive

- 6-10 Removing the Floppy Drive

- 6-12 Replacing the Floppy Drive

- 6-13 Removing the Hard Disk Drive

- 6-15 Replacing a Hard Disk Drive

- 6-16 Removing the Plug-In Printed Circuit Boards

- 6-18 Removing the Main Power Supply

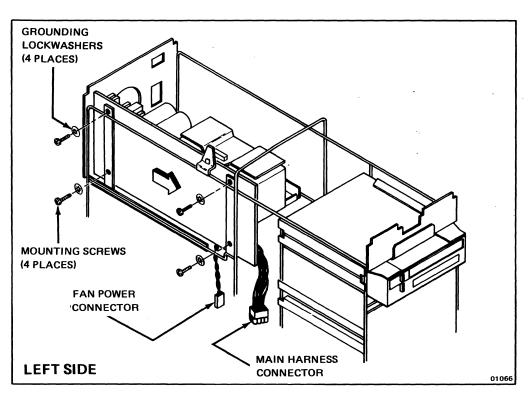

- 6-19 Removing the Backplane Board

- 6-21 Removing the LED Board

- 6-24 SHIPPING A FIELD-REPLACEABLE UNIT

- 6-24 Packaging the System Unit

- 6-25 Packaging Storage Devices

- 6-25 Packaging Printed Circuit Boards

#### 7 PREVENTIVE MAINTENANCE

- 7-3 INTRODUCTION

- 7-3 CLEANING

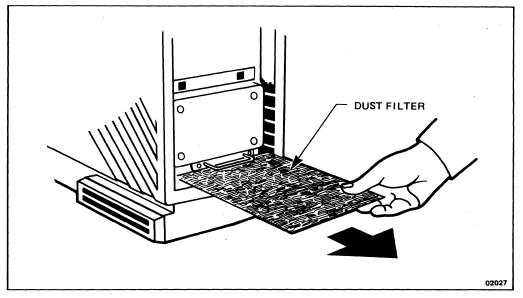

| 7-4 | Dust Filters      |

|-----|-------------------|

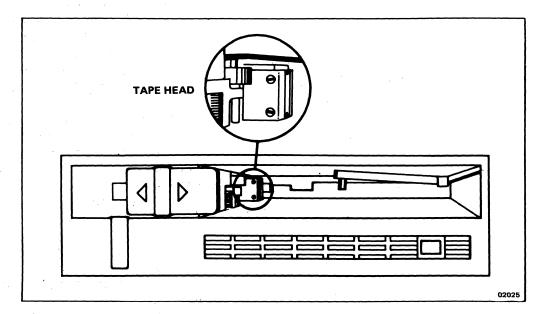

| 7-6 | Tape Heads        |

| 7-8 | Floppy Disk Drive |

| 7-8 | Exterior          |

7-9 Interior

## PART III REFERENCE INFORMATION

#### APPENDICES

- A JUMPER AND SWITCH SETTINGS

- A-3 INTRODUCTION

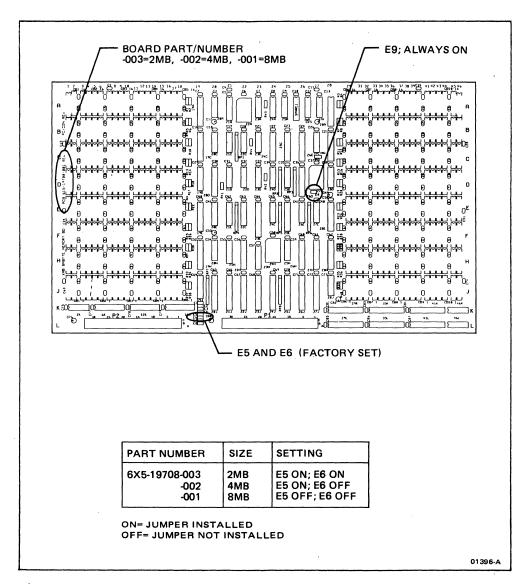

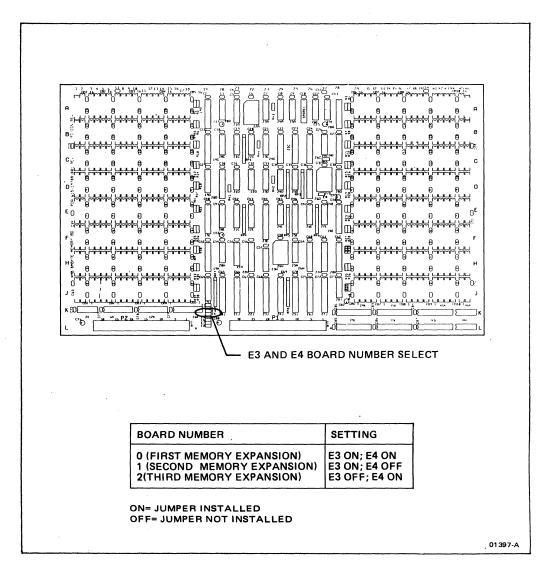

- A-4 MEMORY BOARD JUMPERS

- A-12 COMMUNICATIONS BOARD JUMPERS

- A-12 Multidrop Communications Board Jumpers

- A-20 SIO Communications Board Jumpers

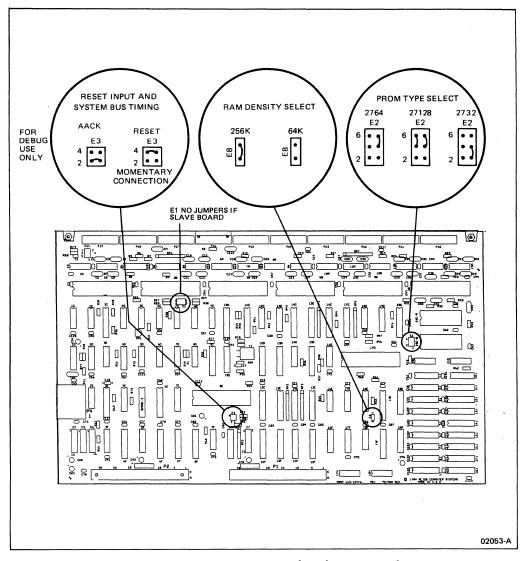

- A-27 CPU BOARD JUMPERS

- A-29 TERMINAL CLUSTER UNIT SWITCHES

- A-30 Station Address Selection

- A-33 Status Lights

#### B UTILITIES

- B-3 INTRODUCTION

- B-3 BOOTING THE FDX DISK

- B-6 FLOPPY FORMAT

- B-9 FLOPPY COPY

- B-11 WORKING WITH HARD DISK BAD SECTORS

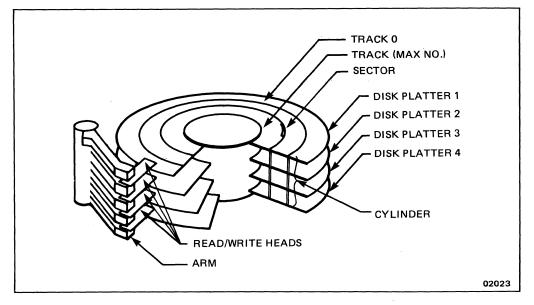

- B-11 Terminology

- B-13 Determining the Drive Number

- B-14 DISPLAY BAD SECTOR/CONFIGURATION TABLE

- B-16 FLAG HARD DISK BAD SECTORS

- B-16 Drive Serial Number

- B-17 Entry Mode

- B-19 REBUILD HARD DISK TABLES

- B-22 REFORMAT HARD DISK

- B-24 REAL TIME CLOCK UTILITIES

xiv

| С                                      | LOOPBACK CONNECTORS                                                                                                                                                       |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D                                      | SYSTEM SPECIFICATIONS                                                                                                                                                     |

| D-3<br>D-3<br>D-10<br>D-11             | INTRODUCTION<br>ELECTRICAL SPECIFICATIONS<br>ENVIRONMENTAL SPECIFICATIONS<br>PHYSICAL SPECIFICATIONS                                                                      |

| E                                      | STORAGE DEVICE SPECIFICATIONS                                                                                                                                             |

| E-3<br>E-3<br>E-4<br>E-4<br>E-5<br>E-6 | INTRODUCTION<br>CARTRIDGE TAPE DRIVE<br>Electrical Specifications<br>FLOPPY DISK DRIVE<br>Electrical Specifications<br>ESDI HARD DISK DRIVES<br>Electrical Specifications |

| F                                      | 115/230 VAC CONVERSION                                                                                                                                                    |

| F-3<br>F-3                             | INTRODUCTION<br>SELECTING 115/230 VAC OPERATION                                                                                                                           |

| G                                      | MULTIDROP CABLES AND TERMINATORS                                                                                                                                          |

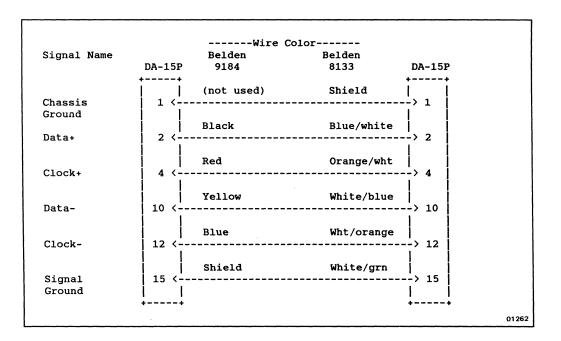

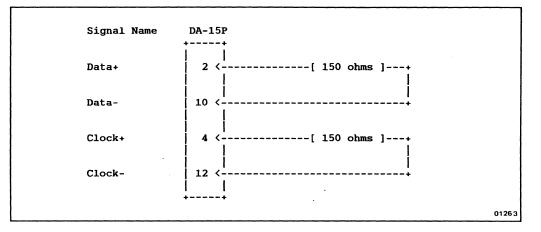

| G-3<br>G-3<br>G-4<br>G-7<br>G-8<br>G-9 | INTRODUCTION<br>SELECTING THE RS-232 CABLE LENGTHS<br>MAKING MULTIDROP CABLES<br>Making a 15-to-15 Pin Drop Cable<br>Making an Interconnect Cable<br>Making a Terminator  |

| н                                      | POWER CONSUMPTION CHART                                                                                                                                                   |

## GL GLOSSARY

$\bigcirc$

FIGURES

| Page                         | Figure                      | Title                                                                                                                                                 |

|------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-10<br>1-14                 | 1-1<br>1-2                  | Cabinet Controls, Connectors, and Indicators<br>Terminal Cluster Unit Controls, Connectors,<br>and Indicators                                         |

| 1-16<br>1-19                 | 1- <b>3</b><br>1-4          | Field-Replaceable Units<br>Plug-In Board Locations                                                                                                    |

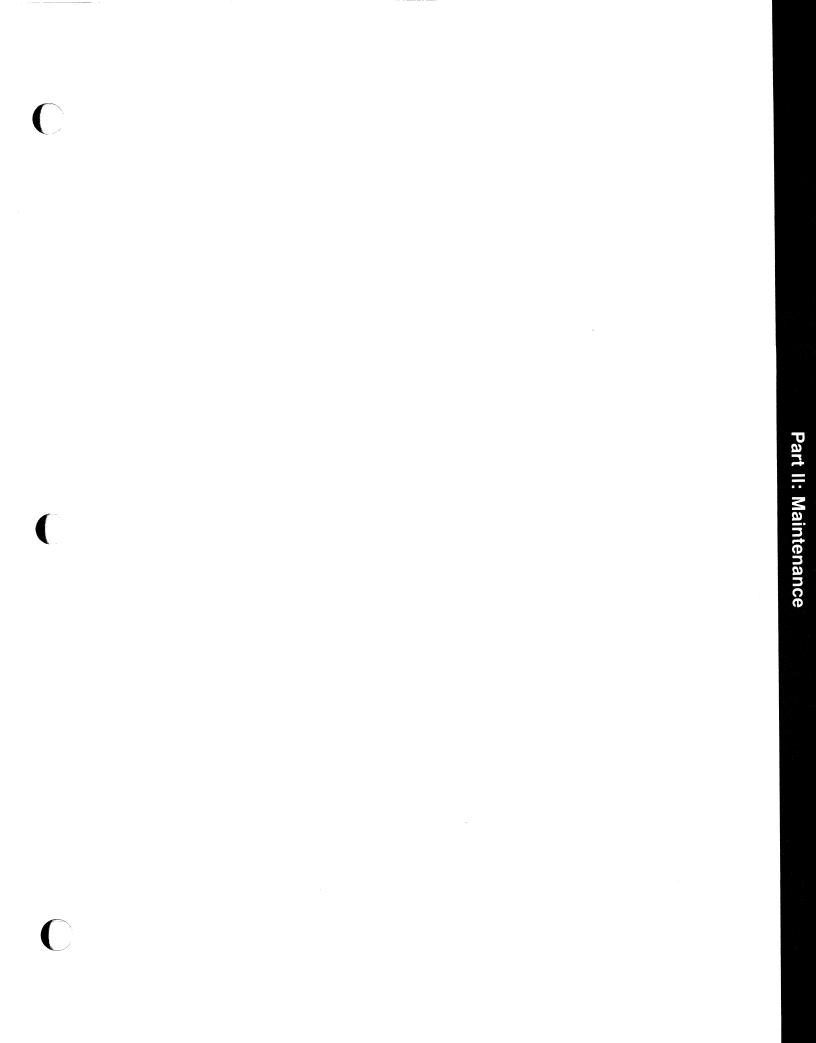

| 2-14                         | 2-1                         | Series 2000 System Block Diagram                                                                                                                      |

| 3-8                          | 3-1                         | System Power-Up Test Sequence                                                                                                                         |

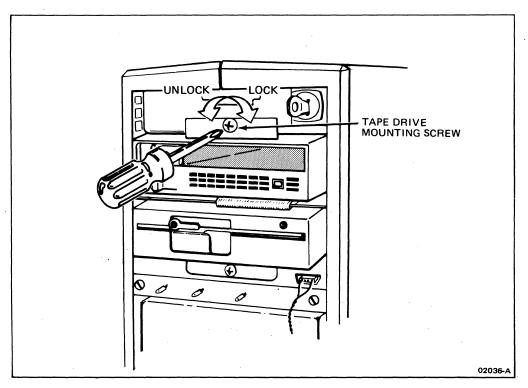

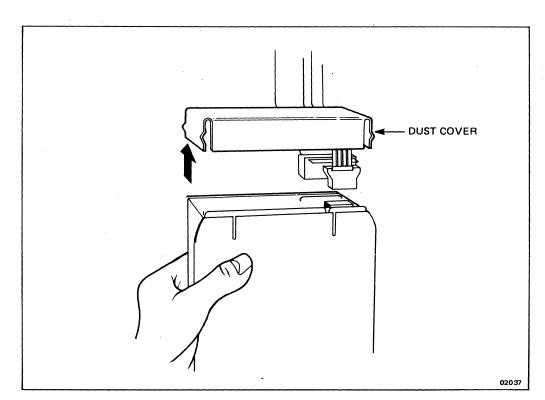

| 6-5<br>6-7<br>6-8            | 6-1<br>6-2<br>6-3           | Removing/Replacing the Front Panel<br>Removing/Replacing the Side Panels<br>Locking/Unlocking the Tape Drive Mounting                                 |

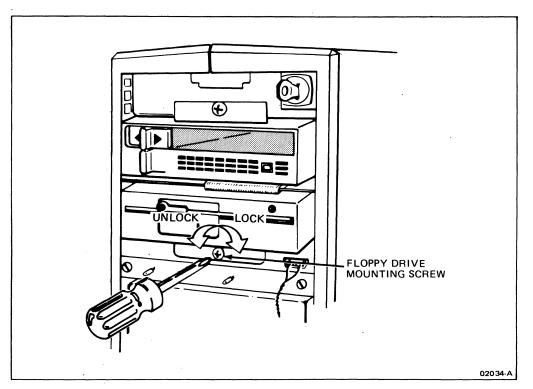

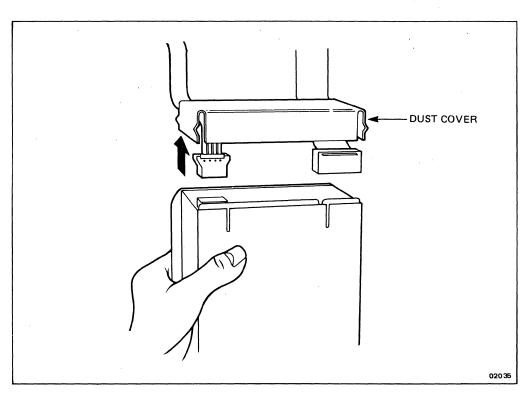

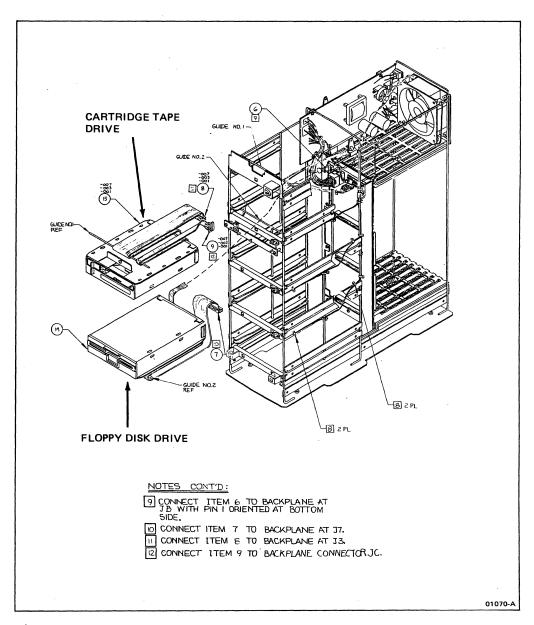

| 6-9<br>6-11                  | 6-4<br>6-5                  | Screw<br>Removing/Replacing the Tape Drive<br>Locking/Unlocking the Floppy Drive Mounting<br>Screw                                                    |

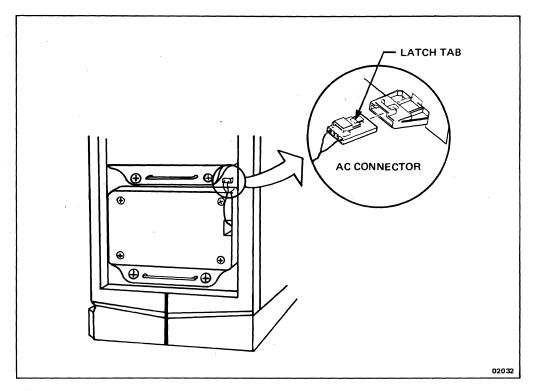

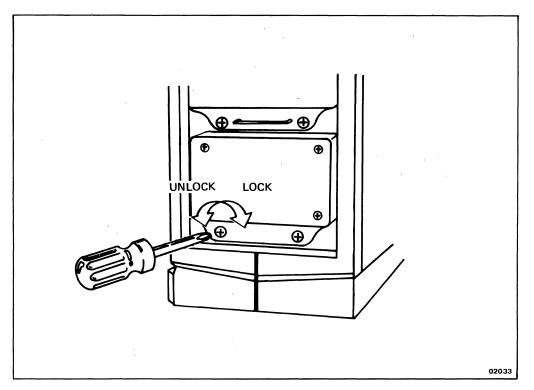

| 6-12<br>6-14<br>6-15         | 6-6<br>6-7<br>6-8           | Removing/Replacing the Floppy Drive<br>Removing/Replacing the Hard Disk AC Connector<br>Locking/Unlocking the Hard Disk Drive Mounting<br>Screws      |

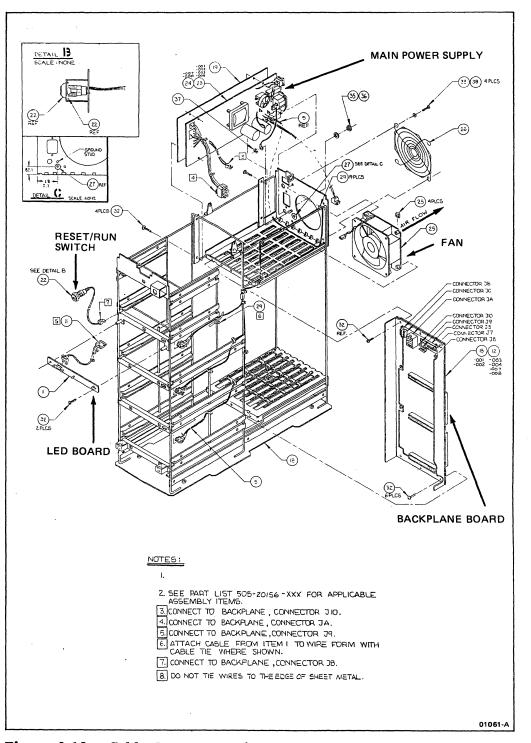

| 6-17<br>6-19<br>6-20<br>6-22 | 6-9<br>6-10<br>6-11<br>6-12 | Removing/Replacing the Plug-In Boards<br>Removing/Replacing the Main Power Supply<br>Removing/Replacing the Backplane Board<br>Cable Interconnections |

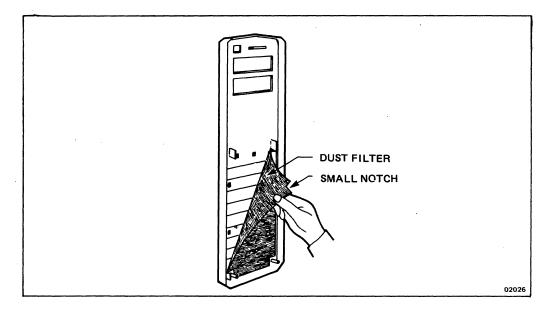

| 7-5<br>7-6<br>7-7            | 7-1<br>7-2<br>7-3           | Removing/Replacing the Front Panel Filter<br>Removing/Replacing the Bottom Filter<br>Cleaning the Tape Head                                           |

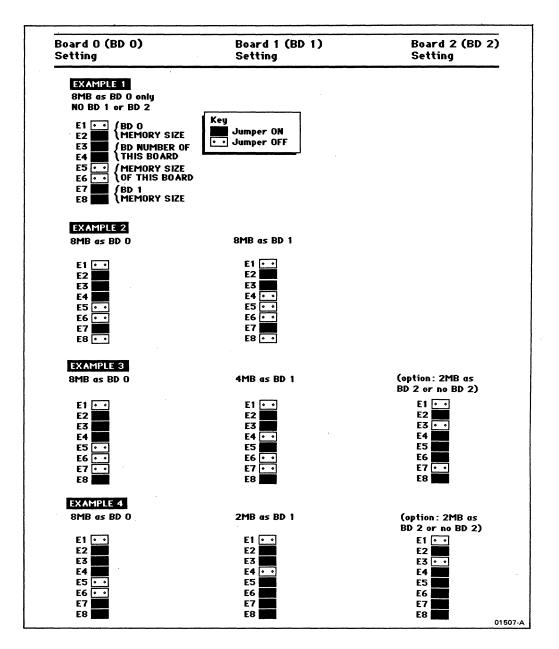

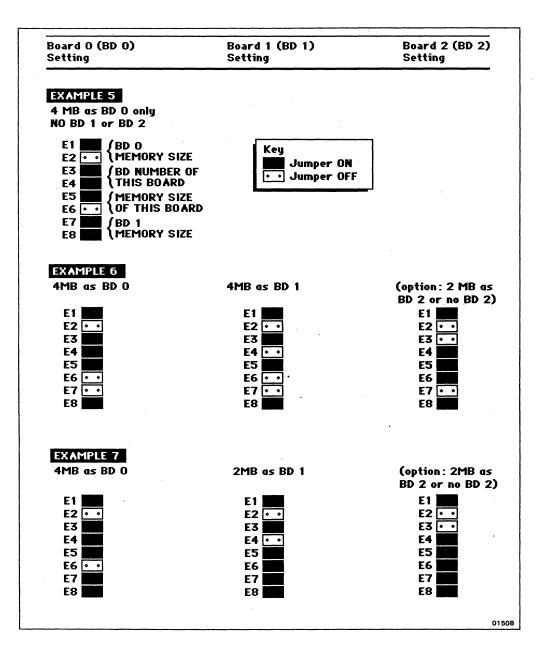

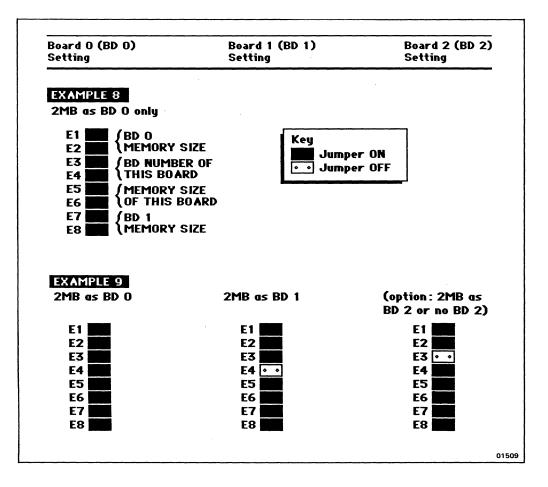

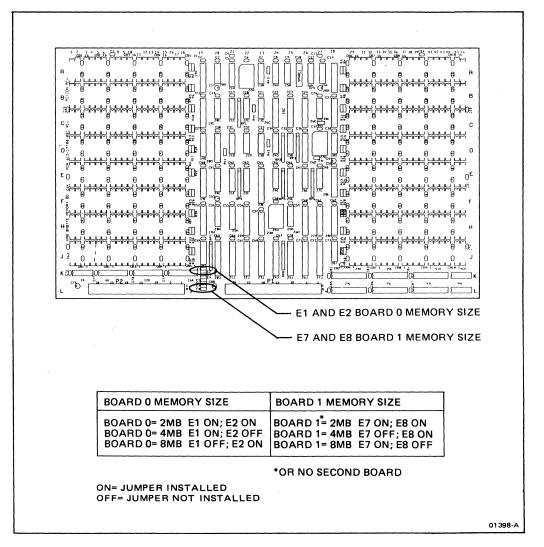

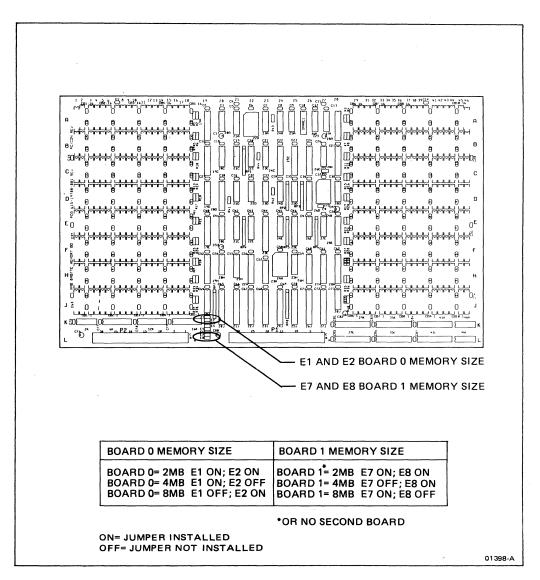

| A-5<br>A-6<br>A-10           | A-1<br>A-2<br>A-3           | Default Jumper Settings<br>Board Number Jumper<br>Memory Configuration Jumpers on Board 0, Board<br>1, And Board 2                                    |

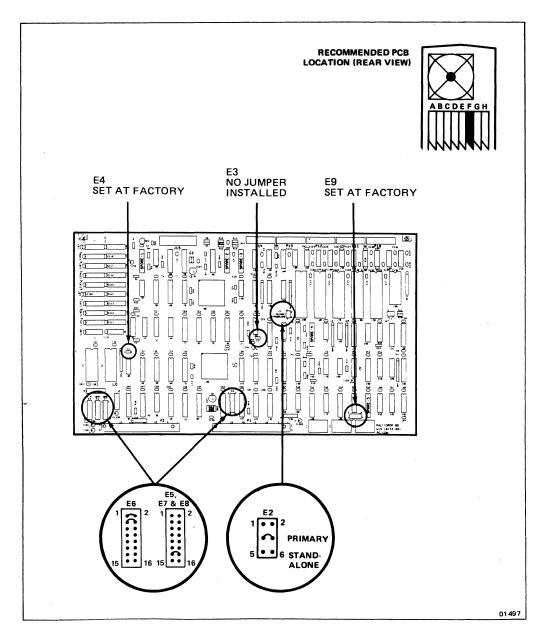

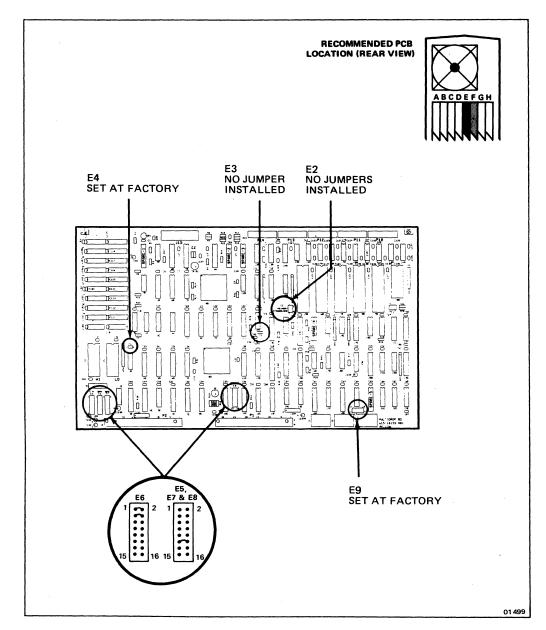

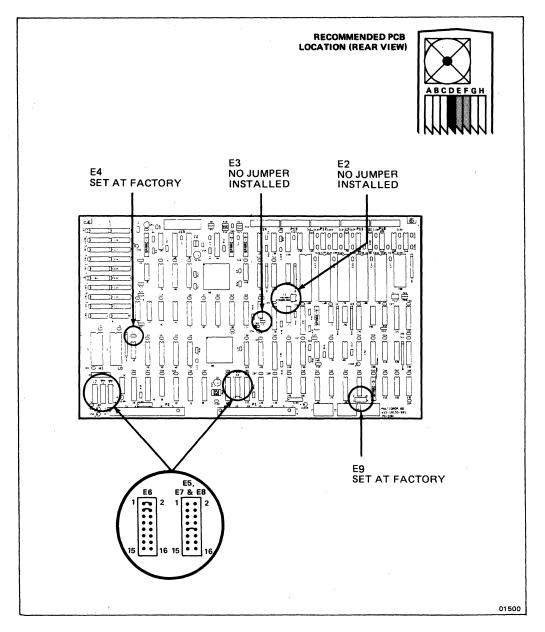

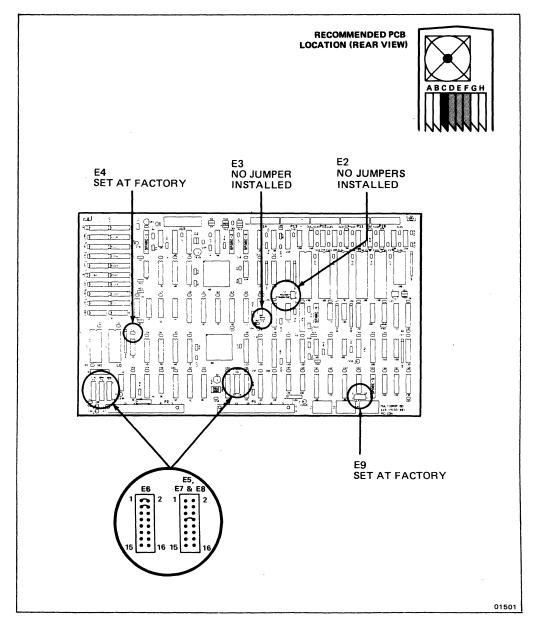

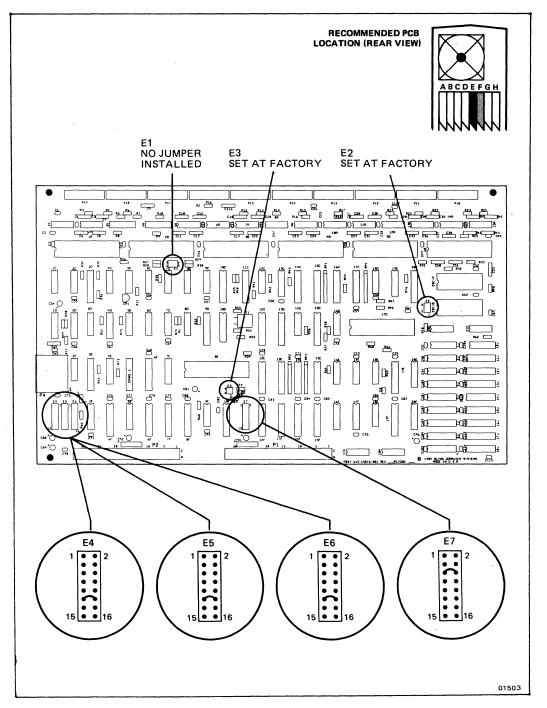

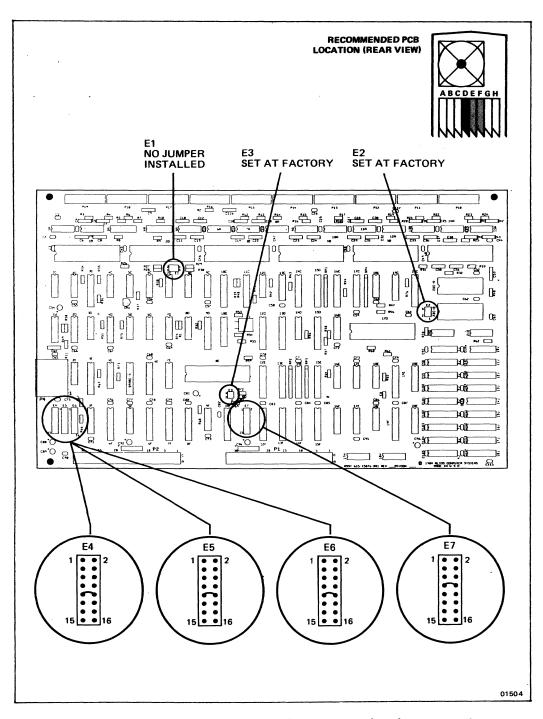

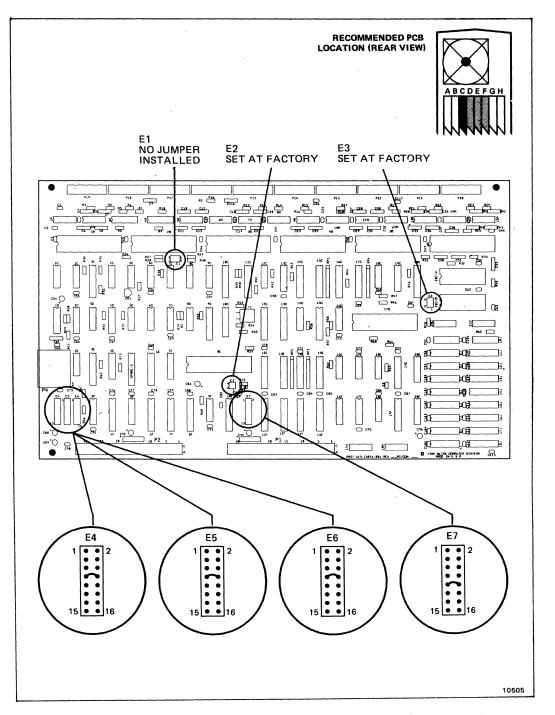

| A-11<br>A-15                 | A-4<br>A-5                  | An Example Memory Configuration<br>Jumpers For Multidrop Communications Boards<br>(Factory Setting)                                                   |

| A-16                         | A-6                         | Jumpers For Multidrop As Primary Communications<br>Board (COMM 0)                                                                                     |

|            |      | Board (COMM 1)                                                                                        |

|------------|------|-------------------------------------------------------------------------------------------------------|

| A-18       | A-8  | Jumpers For Multidrop As Third Communications                                                         |

|            |      | Board (COMM 2)                                                                                        |

| A-19       | A-9  | Jumpers For Multidrop As Fourth Communications<br>Board (COMM 3)                                      |

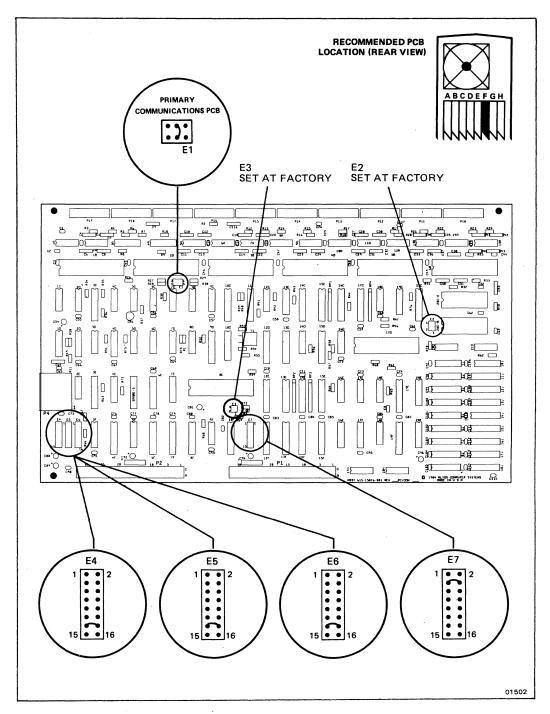

| A-21       | A-10 | Jumpers For SIO Communications Boards (Factory<br>Setting                                             |

| A-23       | A-11 | Jumpers For SIO As Primary Communications Board<br>(COMM 0)                                           |

| A-24       | A-12 | Jumpers For SIO As Second Communications Board<br>(COMM 1)                                            |

| A-25       | A-13 | Jumpers For SIO As Third Communications Board<br>(COMM 2)                                             |

| A-26       | A-14 | Jumpers For SIO As Fourth Communications Board<br>(COMM 3)                                            |

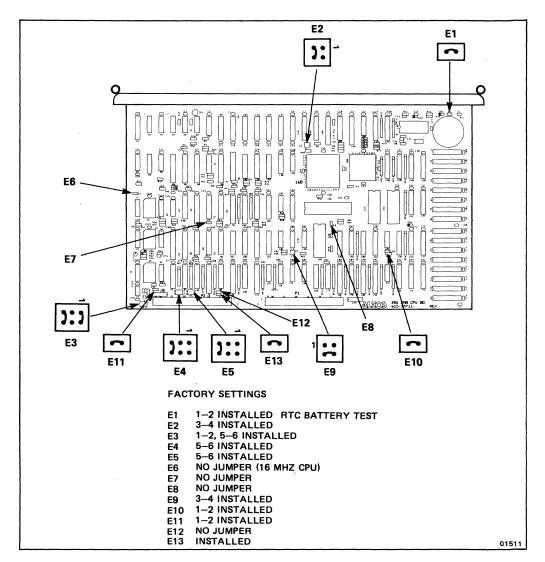

| A-29       | A-15 | Default Jumper Settings For the CPU Board                                                             |

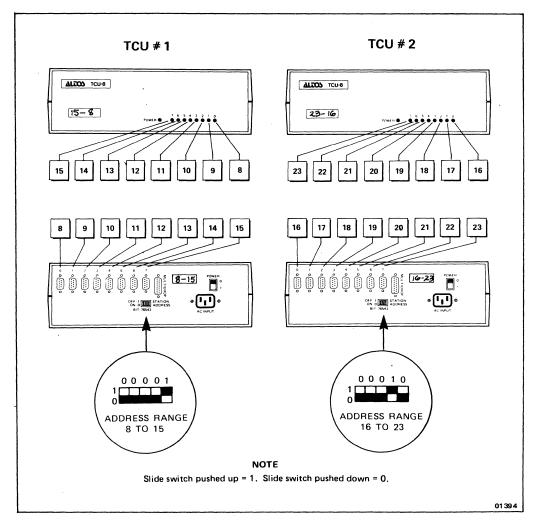

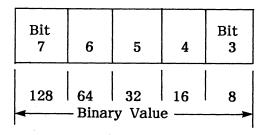

| A-31       | A-16 | Station Identification Switch to Port Address<br>Relationship                                         |

| A-31       | A-17 | Station Address Switch Bit Assignments                                                                |

| B-12       | B-1  | Hard-Disk Terminology                                                                                 |

| C-2<br>C-3 | -    | Parallel Printer Port Loopback Connector<br>Multidrop and/or SIO Communications Loopback<br>Connector |

Jumpers For Multidrop As Second Communications

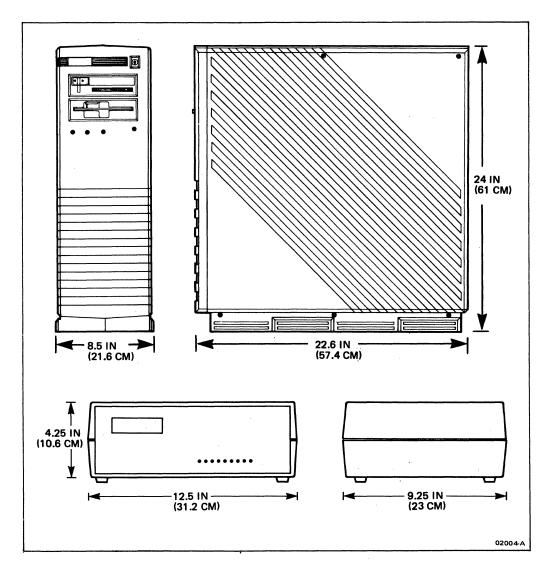

D-12 D-1 Maximum Overall Dimensions

(

A-17 A-7

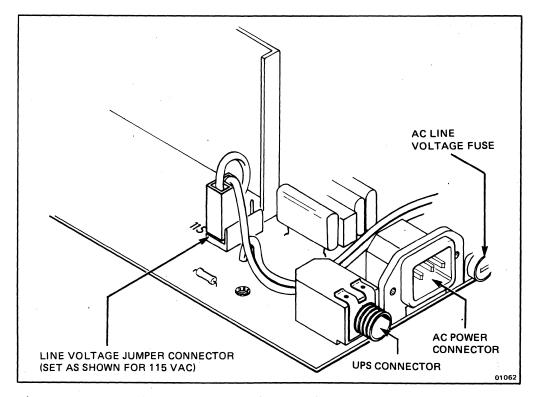

- F-4 F-1 115/230 VAC Selection (Main Power Supply)

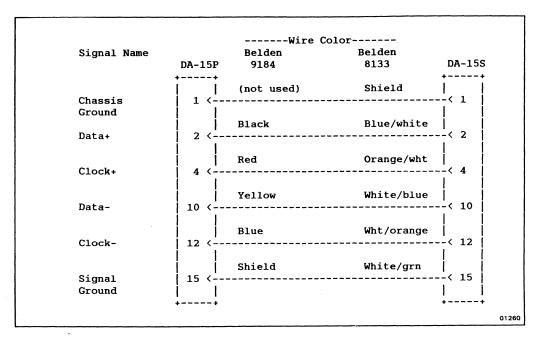

- G-7 G-1 Wiring Diagram For a 15-to-15 Pin Drop Cable

- G-8 G-2 Wiring Diagram For an Interconnect Cable

- G-9 G-3 Wiring Diagram For a Terminator

TABLES

| Page              | Table             | Title                                                                                             |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------|

| 2-6<br>2-7<br>2-7 | 2-1<br>2-2<br>2-3 | 80386 CPU Address Map<br>System Bus I/O Space (Reserved Locations)<br>Local Bus Useable Addresses |

| 2-8               | 2-4               | Real-Time Clock Useable Addresses                                                                 |

| 3-4               | 3-1               | Preliminary Trouble Analysis                                                                      |

| 3-6               | 3-2               | Power Supply DC Voltages                                                                          |

| 3-14              | 3-3               | Monitor Address Map                                                                               |

| 3-15              | 3-4               | Global Descriptors                                                                                |

| 3-17              | 3-5               | Universal Parameter Block Description                                                             |

| 3-24              | 3-6               | CPU Power-Up Test Status                                                                          |

| 3-26              | 3-7               | Power-Up Trouble Analysis                                                                         |

| 3-30              | 3-8               | CPU Failure Status at Output Latch                                                                |

| 3-36              | 3-9               | Hard-Disk Controller Error Register Bit<br>Descriptions                                           |

| 3-38              | 3-10              | Hard-Disk Controller Status Register Bit<br>Descriptions                                          |

| 3-40              | 3-11              | Floppy Disk Controller Status Register 0 Bit<br>Descriptions                                      |

| 3-41              | 3-12              | Floppy Disk Controller Status Register 1 Bit<br>Descriptions                                      |

| 3-43              | 3-13              | Floppy Disk Controller Status Register 2 Bit<br>Descriptions                                      |

| 3-44              | 3-14              | Floppy Disk Controller Status Register 3 Bit<br>Descriptions                                      |

| 4-44              | 4-1               | CPU and System Memory FDX Trouble Analysis                                                        |

| 4-51              | 4-2               | File Processor and Controller FDX Trouble Analysis                                                |

| 4-60              | 4-3               | SIO Communications FDX Trouble Analysis                                                           |

| 4-65              | 4-4               | File Processor and Controller (Board Level)<br>Trouble Analysis                                   |

| 4-72              | 4-5               | Multidrop Communications FDX Trouble Analysis                                                     |

| 5-24              | 5-1               | H Command Descriptions                                                                            |

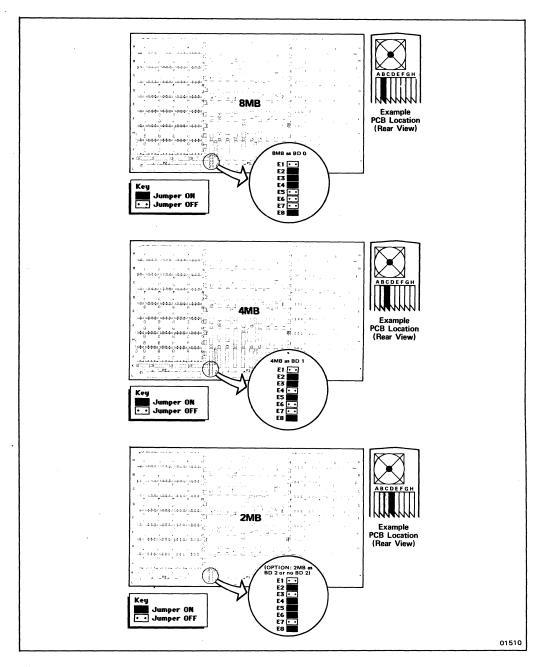

| A-7               | A-1               | Jumpers For 8M Byte Memory Boards Installed As<br>Board 0, Board 1, Or Board 2                    |

| A-8               | A-2               | Jumpers For 4M Byte Memory Boards Installed As<br>Board 0, Board 1, Or Board 2                    |

xviii

| A-9  | A-3 | Jumpers For 2M Byte Memory Boards Installed As<br>Board 0, Board 1, Or Board 2 |

|------|-----|--------------------------------------------------------------------------------|

| A-13 | A-4 | Multidrop Board Jumper Descriptions                                            |

| A-14 | A-5 | Jumper Connector Functions (E5-E8)                                             |

| A-20 |     | SIO Board Jumper Descriptions                                                  |

| A-27 |     | Jumper Descriptions                                                            |

| A-32 |     | Station Identification Switch Settings                                         |

|      |     |                                                                                |

| A-33 | A-9 | Using the Status Lights                                                        |

| D-3  | D-1 | Electrical Specifications                                                      |

| D-10 |     | Environmental Specifications                                                   |

| D-11 |     | Physical Specifications                                                        |

| D-11 | D-3 | Thysical Specifications                                                        |

| E-4  | E-1 | Cartridge Tape Drive Specifications                                            |

| E-5  | E-2 | Floppy Disk Drive Specifications                                               |

| E-6  | E-3 | ESDI Hard Disk Specifications                                                  |

| 20   | 20  |                                                                                |

| G-3  | G-1 | Maximum Recommended Cable Lengths                                              |

| G-4  | G-2 | Cable Manufacturer's Part Numbers                                              |

| G-6  |     | Cable Specifications                                                           |

|      | G-4 | 15-Pin Cable Pin Assignments                                                   |

| 0-0  | U-4 | 13-rin Cable rin Assignments                                                   |

| H-4  | H-1 | Power Consumption Chart (340 Watt Power                                        |

|      |     |                                                                                |

Supply)

Ĉ

## (BLANK)

## Chapter 1 System Description

COLORED IN

- 1-3 INTRODUCTION

- 1-3 Features

- 1-4 Architecture

- 1-4 Configurations

- 1-6 Networking

- 1-6 Communications

- 1-8 Terminal Cluster Units

- 1-8 Diagnostics

1-9

1-9

1-12

- 1-8 Power-Up Tests

- System-Confidence Tests

- Field-Service Diagnostics

- 1-9 CONTROLS, CONNECTORS, AND INDICATORS

- 1-11 Cabinet Front Panel

- 1-11 Cabinet Rear Panel

- 1-11 Multidrop Communications Board

- 1-12 SIO Communications Board

File Processor Board

- 1-12 Terminal Cluster Units

- 1-15 FIELD-REPLACEABLE UNITS

- 1-16 SYSTEM SOFTWARE

- 1-17 Operating System Programs

- 1-18 Diagnostics and Utilities

- 1-18 PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS

System Description

## (BLANK)

## INTRODUCTION

This chapter describes the Altos 386 Series 2000 Computer System. The Series 2000 is a compact floor-standing computer system designed for general processing, office automation, and network fileserver applications. The Series 2000 computer contains the following major subsystems:

- CPU board

- memory board

- multidrop and/or SIO communications boards

- file processor board

- ESDI controller board

- streaming tape drive

- floppy disk drive

- ESDI hard disk drive(s)

## **Features**

- modular architecture for easy system expansion

- major functions located on multiple plug-in printed circuit boards for easy service

- high-speed 32-bit expanded Multibus I<sup>®</sup>

- high-performance 16 MHz Intel 80386 microprocessor

- high-speed Intel 80387 floating-point numeric processor

- up to three 170M byte enhanced small device interface (ESDI) hard disk drives

- multidrop communications that supports multidropped terminals or terminal cluster units (TCUs)

- up to 16M bytes of system memory

- internal 60M byte streaming cartridge tape backup

- storage expansion beyond 510M bytes (unformatted) via a small computer system interface (SCSI) channel

- remote diagnostics available (with optional modem) for rapid fault isolation to field-replaceable units

## Architecture

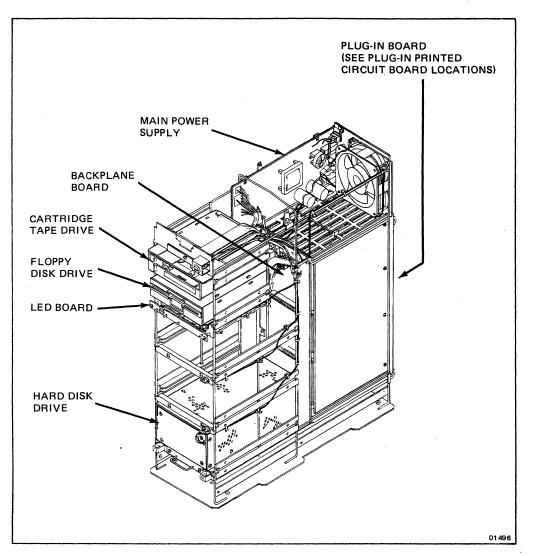

The modular system architecture allows convenient service and system expansion with a wide variety of configurations. The system can contain up to eight plug-in printed-circuit board subsystems and five storage device modules. Five boards are used for the standard system which leaves three spare board slots to use for system expansion.

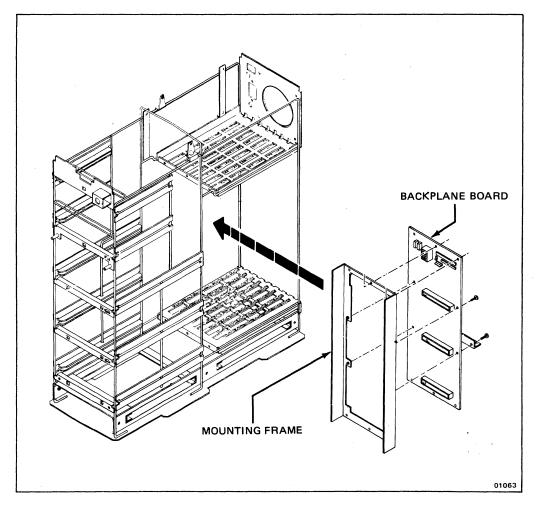

All of the plug-in boards slide into the back of the chassis and connect to the backplane located in the center of the chassis. The cartridge tape, floppy disk, and up to three hard disk drives are easily installed or replaced by removing the front panel and sliding the drives in or out of the chassis. The hard disk drives plug directly into the backplane.

The backplane serves as the medium for data interchange between the processors, system (RAM) memory, and storage devices.

## Configurations

The following three versions of the Series 2000 were available at the date of this publication:

#### System Description

|                     | Version |   |   |

|---------------------|---------|---|---|

| Subsystems          | 1       | 2 | 3 |

| 386 CPU             | х       | x | x |

| System Memory       |         |   |   |

| 4 MB                | Х       | Х |   |

| 8 MB                |         |   | Х |

| SCSI File Processor | х       | х | Х |

| ESDI Controller     | X       | Х | х |

| Communications      |         |   |   |

| SIO                 | х       |   |   |

| MDC                 | 43      | х | Х |

| ESDI Hard Disk      |         |   |   |

| 80 MB               | х       |   |   |

| 170 MB              |         | Х | Х |

| Floppy Disk         |         |   |   |

| 1 MB/1.6 MB         | Х       | Х | Х |

| Streaming Tape      |         |   |   |

| 60 MB               | х       | Х | Х |

| TCU-8               |         | х | х |

| 100 0               |         | Δ | Λ |

| Altos V Terminal    | х       | Х | Х |

A system can be configured with more than one SIO communications board for special applications to allow the system to run a variety of communications protocols, such as, 3270, 3780, X.25, and SNA at the same time (see "Communications" for additional information).

The number of RS-232 I/O ports and the size of the system memory and hard disk storage can be tailored for any particular application. For example, if many external I/O devices (terminals, printers, etc.) are required, but only a few are being used at one System Description

time, the I/O devices may be supported without adding disk storage or system memory.

The Intel 80387 floating-point numeric processor and large amounts of system memory can be used for environments where CPU intensive applications are run with large programs (it takes only two 8M byte memory boards to configure the system with 16M bytes of RAM memory).

Multiple fast-access ESDI hard disk drives can be used for applications that require a large number of disk transactions per second. By using multiple drives, the number of disk transactions per second goes up significantly because of the gains made using overlapped seeks. Thus, a system can be configured with a maximum unformatted storage capacity of 510M bytes.

## Networking

The system hardware supports optional local area networking (LAN). The networking hardware runs at 750K and 1.4M bits per second which allows the system to talk to a variety of Altos computer systems. A simple low-cost, twisted-pair, RS-422 interface provides the network media interface.

The Series 2000 can run WorkNet<sup>®</sup> software that is compatible with other Altos computer systems. The WorkNet software allows transparent remote file access and remote processor execution, which means that any user on the network can share and access files on other systems (as if the files were all on the local disk).

These features make it possible to build large computer installations that support hundreds of users. For example, a network of 10 systems can support 300 users and contain over 51G (giga) bytes of unformatted hard disk storage.

## Communications

The multidrop communications board supports multidropped terminals and/or asynchronous RS-232 devices interfaced through terminal cluster units (TCUs) via a 1M bit per second RS-422 interface. However, operating system licensing allows either 32 (standard) or 64 (optional) bidirectional devices (e.g., terminals) to be logged in at any one time. If more than 32 (or 64) terminals attempt to log in, a message will appear on the disallowed terminal to inform the user that the maximum number of terminals are already logged in.

Currently, up to 64 addressable devices (subject to operating system and license limitations), including the devices directly connected to the asynchronous ports, can be configured on any multidrop communications board. For example, if seven TCU-8s are configured on a single multidrop board, then all the possible addresses will be in use (the four asynchronous ports and the WorkNet port will always require five addresses which leaves 56 addresses for the RS-422 devices on the multidrop trunk line). The multidropped TCU-8 takes up eight of the available addresses even if less than eight RS-232 devices are connected to the TCU-8.

The multidrop communications board requires only one system board slot (instead of the three slots required for three 10-port SIO communications boards) which leaves up to two additional board slots for expansion.

The Series 2000 supports several communications protocols which are down-loaded to the SIO communications board(s). These communications protocols are run by the microprocessor on the communications board(s) which off-load this burden from the main CPU.

#### NOTE

Constant of

The multidrop communications board hardware is capable, with the SIO communications board, of running several communications protocols at the same time. However, this capability depends on the availability of the software. The software for running the communications protocols is down-loaded into the local RAM on the SIO communications board.

Altos currently offers bisynchronous communications (BSC) 3270 and 3780, X.25, and 3270 SNA software to run on the Series 2000 with the SIO communications board installed.

System Description

The system is capable of supporting asynchronous modems for dial-up data base services or off-site communications and synchronous modems for other emulations. Altos WorkNet I or II is supported through one port at a rate of 1.4M bits per second or 750K bits per second. The SIO communications board subsystem, configured with 128K bytes of RAM, supports certified X.25 or IBM/SNA software protocols.

## **Terminal Cluster Units**

The terminal cluster unit (TCU) connects to the multidrop communications board via a high-speed RS-422 interconnect scheme. The TCU provides a serial interface to any asynchronous RS-232 device at baud rates from 50 to 19,200.

### Diagnostics

The Series 2000 performs three major categories of diagnostic tests. The first category is the built-in hardware tests contained in the power-up monitor program. (Refer to "System Software" later in this chapter for additional diagnostics information.)

The second category of tests is the user system-confidence (SDX) tests. The third category is the field-service diagnostics (FDX) tests which can be run from a floppy disk which is available as part of a maintenance package from Altos Customer Support.

#### Power-Up Tests

The power-up tests are contained in the ROM-based firmware on the CPU, multidrop and/or SIO communications, and file processor boards. These power-up tests are always performed when power is applied to the system to check the minimum hardware configuration on its particular board, identify any missing or failed subassemblies, and then confirm communication with the system.

The CPU power-up tests include cache memory, tag RAM memory, counter/timer I/O (CIO), clock, floating-point numeric processor, interrupt, and system bus checks.

The file processor power-up tests include local RAM and PROM, interval timer, system bus, DMA controller, and storage device controller checks. The multidrop and SIO communications board power-up tests consist of local RAM and PROM, I/O integrated circuits, DMA controller, interrupts, and system bus checks.

#### System-Confidence Tests

The system-confidence (SDX) tests are menu driven and allow a non-technical user to test the operation of the system.

A full set of tests can be easily run from the system console. System utilities for handling system configuration and storage devices are also included.

#### **Field-Service Diagnostics**

More detailed and flexible tests are available for the more experienced user with the field-service (FDX) tests.

The field-service (FDX) tests are supplied on a floppy disk available as part of a maintenance package from Altos Customer Support.

In most multiboard systems, the CPU, system memory, controller, and communications boards must be working before field-service diagnostic testing can start. However, the multidrop or SIO communications board contains a full 16-bit microprocessor that acts as a diagnostic controller on the system bus. Thus, each board can be called up and tested separately, or the full system can be enabled and exercised to isolate and identify failures for repair or replacement.

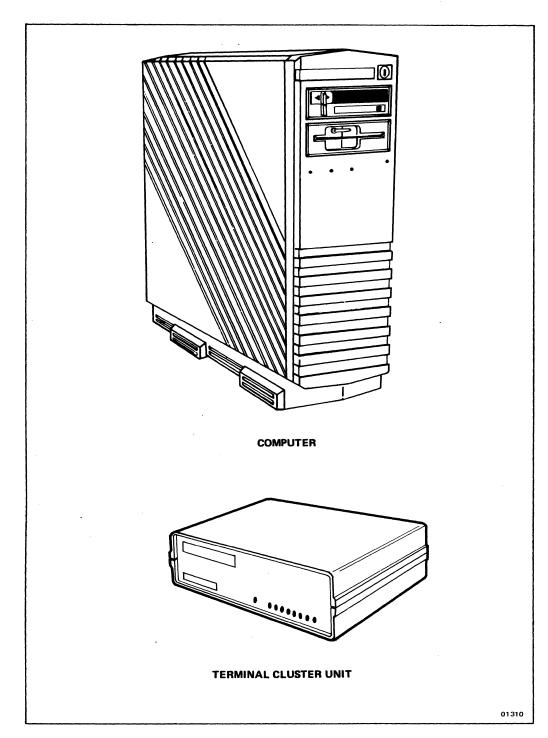

### CONTROLS, CONNECTORS, AND INDICATORS

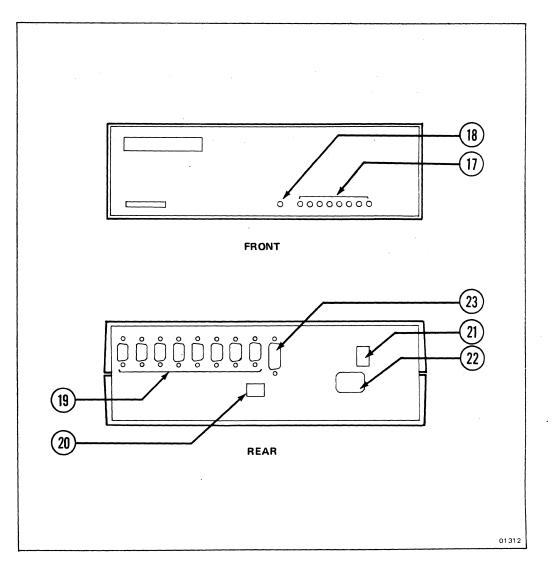

The following is a description of the Series 2000 computer and terminal cluster unit controls, connectors, and indicators indexed (by number) to the exploded-view illustrations in Figures 1-1 and 1-2.

System Description

Figure 1-1. Cabinet Controls, Connectors, and Indicators

## **Cabinet Front Panel**

- 1 RESET/RUN Switch. Key-operated switch that resets (boots) the system when turned to RESET and back to RUN. Allows normal system operation when set to RUN. If the key is turned to RESET and removed, the system will remain in the reset condition and will not operate.

- 2 POWER Indicator. Green light-emitting diode (LED) indicator that lights when power is applied to the system (i.e, rear panel POWER switch is in the on position).

- 3 HD 1, HD 2, and HD 3. Yellow LED indicators that light to indicate which hard disk drive is selected.

## Cabinet Rear Panel

- 4 POWER Switch. Rocker switch that applies power to the system when placed in the on position (green LED indicator on the front panel is lit). The system will boot when the POWER switch is placed in the off, then on, position while the RESET/RUN switch on the front panel is in the RUN position.

- **5** Fuse Holder. Holder that contains the main power fuse. Refer to the AC Power electrical specifications in Appendix F for the proper fuse ratings.

- 6 AC INPUT Connector. Three-pin AC connector for attaching an AC power cord to the system.

- 7 UPS Jack. Jack for connecting a power fail status signal from an external uninterruptable power source device to the Series 2000 system.

## **Multidrop Communications Board**

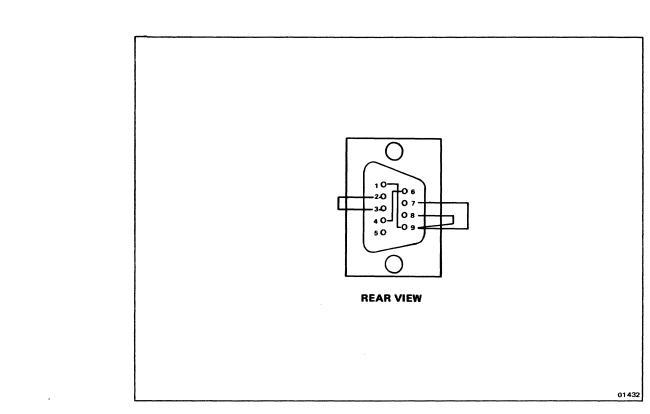

- 8 **Port 0 Connector.** Nine-pin connector for attaching the system console or other asynchronous RS-232 devices to the system.

- **9 Port 1 Connector.** Nine-pin connector for attaching asynchronous RS-232 devices or a remote diagnostics modem to the system.

- 10 Port 2 and 3 Connectors. Nine-pin connectors for attaching synchronous/asynchronous RS-232 devices to the system.

- 11 Port 4 Connector. Nine-pin connector for attaching either an asynchronous RS-232 device or WorkNet drop cable.

- 12 MULTIDROP Connector. Fifteen-pin connector for attaching multidropped terminals or TCUs to the system.

- 13 FAULT Indicator. Red light-emitting diode (LED) that lights if the multidrop board does not pass the power-up tests or a nonmaskable interrupt occurs.

## SIO Communications Board

14 Serial I/O Ports. Connectors 0 through 9 on the communications board provide 10 asynchronous RS-232 ports for connecting terminals or printers to the system. Refer to the SIO communications board operation in Part 2 for details on the serial I/O port capabilities.

## **File Processor Board**

- 15 PRINTER Connector. Connector for attaching a printer with a Centronics-type parallel interface to the system.

- 16 SCSI Connector (-002 Version Only). Connector for attaching SCSI peripherals to the system.

## **Terminal Cluster Units**

Refer to Figure 1-2 for the locations of the terminal cluster unit (TCU) front and rear panel controls, connectors, and indicators.

- 17 Port Status Indicators. Eight yellow light-emitting diode (LED) indicators that indicate the status of each port on the TCU.

- 18 POWER Indicator. Green light-emitting diode (LED) indicator that lights when AC power is applied to the TCU (i.e, POWER switch on the rear panel is placed in the ON position).

19 RS-232 Ports. Eight 9-pin ports for connecting RS-232 terminals and printers to the TCU.

- 20 STATION ADDRESS Switches. Five switches (3 through 7) for selecting a unique station address for the TCU.

- 21 POWER Switch. Rocker switch that applies AC power to the TCU when placed in the ON position (green LED indicator on the front panel is lit).

- 22 AC INPUT Connector. Three-pin AC connector for attaching an AC power cord to the TCU.

- 23 MULTIDROP Connector. Fifteen-pin connector for connecting the TCU to the multidrop cable.

System Description

Figure 1-2. Terminal Cluster Unit Controls, Connectors, and Indicators

System Description

# C

## FIELD-REPLACEABLE UNITS

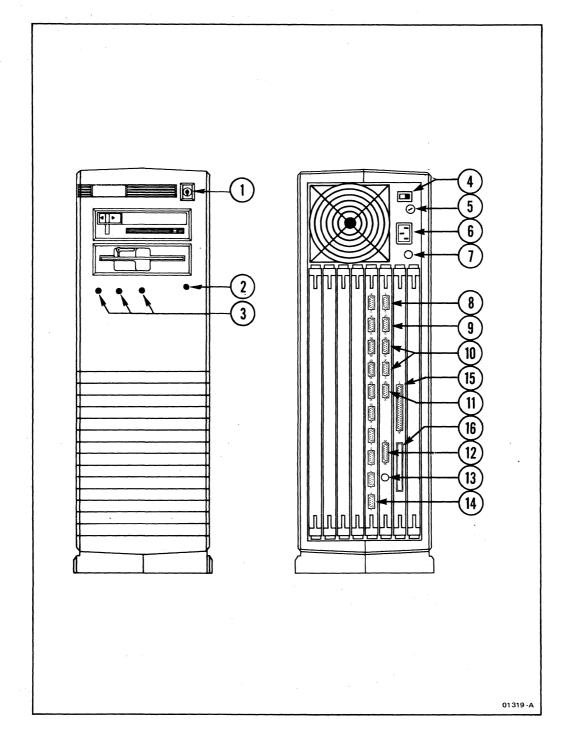

The following field-replaceable units are available on the Series 2000 (see Figure 1-3):

- central processing unit (CPU) board

- memory board

- multidrop (MDC) or serial input/output (SIO) communications board

- file processor board

- ESDI controller board

- backplane board

- LED board

- main power supply

- tape drive

- floppy disk drive

- hard disk drive

- external terminal cluster unit (TCU)

Figure 1-3. Field-Replaceable Units

# SYSTEM SOFTWARE

The system software supplied with the Series 2000 consists of the operating system, system-confidence (SDX) tests, and utilities.

# **Operating System Programs**

The Series 2000 is specifically designed for the XENIX operating system which is based on UNIX from AT&T. Altos has added many features to XENIX that support extended development tools, increased performance, and compatibility with existing systems. The XENIX operating system supports menu-driven installation and administrator procedures, and also shared data that allows programs to share a common memory space.

The system hard and floppy disks are controlled by the intelligent file processor board that off-loads much of the processing work from the main CPU. The main CPU uses the address translation logic on the system to improve performance as follows:

- Scatter Loading. Loads user programs into non-contiguous 4K byte pages of system memory for more efficient use with less swapping.

- Context Switching. When context switching, the per process data area is mapped by loading a table entry instead of copying the data around in memory as in standard XENIX.

- Dynamic Stack Growth. Programs do not preallocate stack space, so memory is not wasted with stack space that may never be used.

XENIX also uses disk management techniques to improve performance as follows:

- Disk-Data Organization. Altos XENIX supports an implementation of the UNIX file system that maximizes disk throughput, reduces the number of disk accesses, and uses partial blocks to minimize disk fragmentation.

- Disk Cache. Disk accesses are reduced by a buffer pool in system memory that acts as a disk cache. The disk cache has a hit ratio of 80% to 95%.

The system I/O ports are controlled by the multidrop and/or SIO communications boards that off-load interrupts and processing from the main CPU. Each communications board is down-loaded with code that handles the asynchronous ports, WorkNet, and any other communication protocols (e.g., SNA, X.25, and bisynchronous communications 3780 and 3270).

Application programs, floppy disks, and cartridge tapes are completely compatible with all Altos 80386 microprocessor-based machines. Also, floppy disks and cartridge tapes are compatible with many other Altos machines, including 8086 microprocessor based XENIX machines.

## **Diagnostics and Utilities**

The system diagnostic executive (SDX) diagnostic tests and utilities are on a floppy disk included with your system. The SDX program performs a series of user system-confidence tests and utilities.

Field-service diagnostics (FDX) tests are available as part of a maintenance package from Altos Customer Support. The FDX tests enable you to locate a faulty field-replaceable unit (FRU) and perform certain utilities.

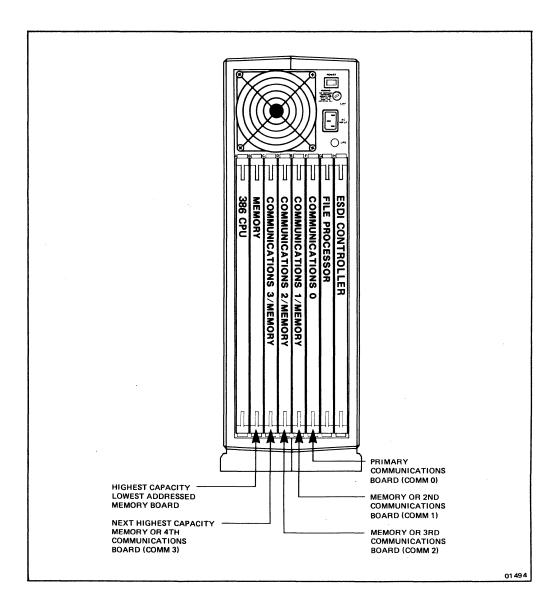

# PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS

The CPU, file processor, and controller boards are dedicated to slots A, G, and H respectively in the back of the Series 2000. The remaining slots, B through F, are electrically identical which allows memory and multidrop or SIO communications boards to be installed in any order in these five slots.

However, software requires that the memory and multidrop and/or SIO communications boards be jumpered according to their function in the system (see jumper description information in Subsystem Operation - Chapter 2 and Jumpers and Switches - Appendix A).

Thus, if system memory or communications boards are added to the system, Altos recommends that the boards be located as shown in Figure 1-4 to avoid extensive jumper changes on those boards that have already been installed.

Figure 1-4. Plug-In Board Locations

(BLANK)

# Chapter 2 Subsystem Operation

(

$\bigcirc$

| 2-3          | INTRODUCTION                  |

|--------------|-------------------------------|

| 2-3          | BLOCK DIAGRAM DESCRIPTION     |

| 2-3          | System Bus                    |

| 2-4          | Central Processing Unit (CPU) |

| 2-5          | 80386 Address Map             |

| 2-8          | System Memory                 |

| 2-9          | Multidrop Communications      |

| <b>2-</b> 10 | SIO Communications            |

| 2-11         | File Processor                |

| 2-12         | ESDI Controller               |

| 2-12         | Terminal Cluster Unit         |

Subsystem Operation

(BLANK)

Subsystem Operation

# INTRODUCTION

This chapter is a general block diagram description of the major circuits (subsystems) that comprise the Altos 386 Series 2000 Computer System. The Series 2000 is available with the following major subsystems:

- system bus

- central processing unit (CPU)

- system memory

- multidrop communications

- SIO communications

- file processor

- ESDI controller

- external terminal cluster unit (TCU)

The subsystem hardware is partitioned so that most major functions, except the system bus and terminal cluster unit (TCU), is contained on a single plug-in printed circuit board. The five required boards for the Series 2000 system are the CPU, system memory, communications, file processor, and controller. All of these boards, except the device controller, connect to the 32-bit system bus.

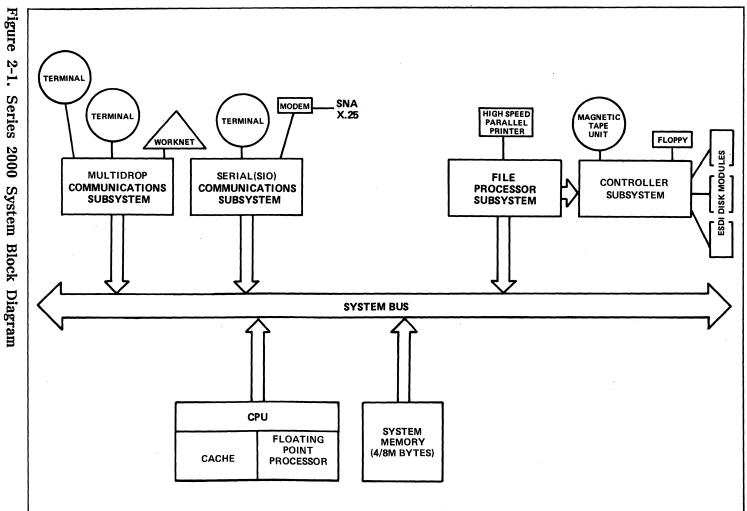

# **BLOCK DIAGRAM DESCRIPTION**

Refer to the system block diagram in Figure 2-1 to help understand the following block diagram description.

# System Bus

The Series 2000 system bus is a 32-bit data, 26-bit address bus which is an extension of the IEEE 796 system bus (Multibus I). The

system bus has separate memory and I/O address spaces and can handle asynchronous signal transfers between multiple masters or master and slave. A bus master can perform either single or unlimited system bus transfers. A bus slave decodes addresses and acts upon commands from bus masters. The memory board is the only slave.

Six bus masters (subsystem boards) are supported by prioritized parallel bus arbitration. A bus clock provides bus arbitration and general-purpose timing. Different master-slave subsystems can operate at different clock rates.

The CPU, file processor, and primary communications boards are bus masters which can acquire the system bus through bus exchange logic and generate command, address, and data signals (during writes).

The bus signals are divided into the following signal lines:

- control lines

- address lines

- data lines

- interrupt lines

- bus exchange lines

# Central Processing Unit (CPU)

The function of the CPU board is to execute all the system and applications programs. The CPU board uses an 80386 microprocessor, an 80387 80-bit floating-point numeric processor extension, PROM, cache and tag RAM, a calendar clock, and a system bus interface.

The CPU board contains the following four major circuits:

- 80386 microprocessor and 80387 numeric processor

- local bus interface with PROM, RTC, PIC, and CIO

- tag RAM memory interface

2-4

- cache RAM memory interface

- 32-bit system bus interface including write buffer

#### 80386 Address Map

The 80386 address map is listed in Table 2-1. The local peripherals include the calendar clock, interrupt controller, CIO (counter with parallel I/O), and PROM.

The address map also contains areas that include the cache memory and tag RAM. The accessibility of these RAMs provides the ability to perform cache diagnostics.

The two remaining areas in the address map are the system bus I/O space and the system bus memory space. When accessing the system bus I/O space, the I/O address is formed by using the lower 16 bits of the 80386 26-bit address. Table 2-2 lists the addresses for the system bus I/O space, Table 2-3 lists the local bus useable addresses, and Table 2-4 lists the real-time clock useable addresses.

Subsystem Operation

| Address              | Transfer<br>Length      | Description                |

|----------------------|-------------------------|----------------------------|

| FFFFFFFF             |                         |                            |

| F0000000             | Word                    | EPROM                      |

| 1BFFFFFF             |                         | Local I/O (LIO)            |

| 180007FF<br>18000600 | Word                    | Debug SCC                  |

| 180005FF<br>18000400 | Word                    | Counter/Timer/I/O (CIO)    |

| 180003FF<br>18000200 | Word                    | Interrupt Controller (PIC) |

| 180001FF             | Word                    | Real Time Clock (RTC)      |

| 4000000              | Dbl Word                | Bus Size RAM (CPIO)        |

| .0000000             | Byte, Word,<br>Dbl Word | Cache RAM (CIO)            |

| )FFFFFFF             | Dbl Word                | Tag RAM (TIO)              |

| )BFFFFFF<br>)8000000 | Dbl Word                | Cacheable Page             |

| 07FFFFFF<br>04000000 | Byte, Word              | System I/O (SMEM*,SBUS)    |

| )3FFFFFF             | Byte, Word,<br>Dbl Word | System Memory (SMEM,SBUS)  |

Table 2-1. 80386 CPU Address Map

2-6

| Address | Description                                       |

|---------|---------------------------------------------------|

| 0001h   | Communications board 1 (COMM 0) channel attention |

| 0002h   | Communications board 2 (COMM 1) channel attention |

| 0003h   | Communications board 3 (COMM 2) channel attention |

| 0004h   | Communications board 4 (COMM 3) channel attention |

| 000Eh   | File processor board channel attention            |

Table 2-2. System Bus I/O Space (Reserved Locations)

Table 2-3. Local Bus Useable Addresses

| Address  | Description               |  |

|----------|---------------------------|--|

| FFFFFFFF |                           |  |

| FFFF8000 | EPROM                     |  |

| 18000606 | Data Port - Debug SCC     |  |

| 18000604 | Control Port - Debug SCC  |  |

| 18000406 | CIO - Control Port        |  |

| 18000404 | CIO - Data A Port         |  |

| 18000402 | CIO - Data B Port         |  |

| 18000400 | CIO - Data C Port         |  |

| 18000202 | PIC - ICW2,ICW3,ICW4,OCW1 |  |

| 18000200 | PIC - ICW1,OCW2,OCW3      |  |

| 1800007E |                           |  |

| 18000000 | RTC - 64 byte locations   |  |

| Address           | Description      |  |

|-------------------|------------------|--|

|                   |                  |  |

| 18000074-1800007F | CPU Firmware     |  |

| 1800006C-18000073 | Operating System |  |

| 1800004C-1800006B | Reserved         |  |

| 1800001C-1800004A | System Users     |  |

| 1800001A          | Register D       |  |

| 18000018          | Register C       |  |

| 18000016          | Register B       |  |

| 18000014          | Register A       |  |

| 18000012          | Year             |  |

| 18000010          | Month            |  |

| 1800000E          | Date of Month    |  |

| 1800000C          | Day of Week      |  |

| 1800000A          | Hours Alarm      |  |

| 18000008          | Hours            |  |

| 18000006          | Minutes Alarm    |  |

| 18000004          | Minutes          |  |

| 18000002          | Seconds Alarm    |  |

| 1800000           | Seconds          |  |

Table 2-4. Real-Time Clock Useable Addresses

The 80386 microprocessor operates at 16 MHz and executes code out of either PROM, cache memory, or system (RAM) memory. The microprocessor mainly operates from the cache memory which eliminates most wait states.

The local bus on the CPU board transfers address, data, status, and control signals to/from the PROM, calendar clock, interrupt controller, and counter/timer with parallel I/O (CIO).

# System Memory

The memory board contains 4M or 8M bytes of  $256K \times 1$  RAM. Memory is organized into 64-bit double-long words. Data transfer is in 8, 16, 24, or 32-bit quantities.

# **Multidrop Communications**

慶得

The multidrop communications board supports 30 multidropped terminals and/or asynchronous RS-232 devices interfaced through a terminal cluster unit (TCU) via a 1M bit per second RS-422 interface.

The multidrop communications board also supports multidropped terminals that have integral RS-422 synchronous interfaces. The Altos terminal cluster unit (TCU) converts the high-speed RS-422 synchronous protocol from the multidrop communications board to an asynchronous RS-232 protocol for use by any standard asynchronous RS-232 peripheral (e.g., terminals and printers).

The multidrop communications board also supports WorkNet, two asynchronous/synchronous, and two asynchronous-only RS-232 ports.

The multidrop port (at 1M bit per second) is supported by one dedicated serial channel and associated direct-memory access (DMA) channel.

Altos WorkNet (at 750K or 1.4M bits per second) is supported by a second dedicated serial channel and DMA channel. The two asynchronous/synchronous channels are software configurable to support synchronous protocols.

When running in asynchronous mode, the synchronous/asynchronous ports are intended to support modems or serial printers up to 19,200 baud. The remaining asynchronous-only ports are intended for the system console and a diagnostic modem, or additional serial printer(s).

The multidrop communications board is based upon an Intel 80286 microprocessor running at 6 MHz. The 80286 input/output processor (IOP) can communicate with the system and local buses.

The IOP's interface insures that the local bus is not tied up when the IOP is communicating with the system bus. There is 16K to 32Kbytes of initial program load (IPL) PROM and 512K bytes of local RAM. The IPL PROM contains power-up tests, the ability to boot an operating system, and the necessary support for remote diagnostics. Local RAM is used to hold multidrop communications down-load code (from the operating system) and data buffers for all port input/output (I/O). Four 8530 serial communication controllers (SCCs) support the six I/O channels. Each serial port is DMA-driven to minimize the frequency of interrupts. One-half of an SCC links the multidrop port while another half of an SCC drives the WorkNet port. The other SCCs support the RS-232 synchronous and asynchronous ports and run other communications products. All RS-232 ports can be simultaneously DMA-driven (on both transmit and receive) to increase the performance of communication protocols.

An 8536 counter/timer/parallel I/O (CIO) provides three counter timers for software use, and also provides miscellaneous I/O flags and strobes.

The multidrop communications board interconnects the multidropped terminals and/or the terminal cluster units (TCUs) to the system bus.

Multidrop cabling is electrically similar to and uses the same cables as Altos WorkNet, but with entirely different software protocols which prevents interconnecting WorkNet and multidrop. The maximum trunk length (distance from the computer to the farthest terminal) is approximately 1500 feet extendable by repeaters up to a maximum of 4500 feet. All terminals are polled and the multidrop controller supervises all line usage to eliminate collisions.

The multidrop communications board's on-board firmware has several diagnostic functions that provide power-up confidence tests of all local functions and low-level tests on other parts of the system (on the system bus), including system memory.

## **SIO Communications**

The SIO communications board is an intelligent input/output (I/O) processor that relieves the CPU of all communications functions. The SIO communications board contains an 8086 microprocessor, a system bus interface, a four-channel DMA controller, a local bus controller, 32K to 512K bytes of dynamic RAM, 16 to 256K bytes of PROM, a general-purpose counter/timer, and up to 10 serial ports.

Seven of the serial ports are dedicated to RS-232 asynchronous communications, one is independently software selectable between asynchronous RS-232 and synchronous RS-422 networks, and the

remaining two can support either asynchronous or synchronous RS-232 communications.

Functionally, the SIO communications board is a complete computer with the necessary initial program load (IPL)/diagnostic firmware, RAM, and serial I/O ports.

The SIO communications board's on-board firmware has several diagnostic functions that provide power-up confidence tests of all local functions and low-level tests on other parts of the system (on the system bus), including system memory.

# **File Processor**

The file processor board is an intelligent controller that manages data flow to/from the following:

- floppy disk drive

- cartridge tape drive

- up to three hard disk drives

- Centronics-type parallel printer interface

- additional drives through the small computer system interface (SCSI) channel

The file processor board contains the following circuit elements:

- 8086 microprocessor

- four-channel DMA controller

- system bus interface

- local bus controller

- 128K bytes of dynamic RAM

- 16K bytes to 32K bytes of PROM

- counter/timer

- disk and printer interface

- SCSI controller

## **ESDI** Controller

The Series 2000 uses an enhanced small device interface (ESDI) controller board. The controller board contains three independent controllers for streaming tape, floppy disk, and hard disk drives. All controllers receive commands from the file processor board.

The tape drive controller supports Altos cartridge tape drives with QIC-36 interfaces, and uses the QIC-24 format to input data on the tape.

The floppy disk controller supports one internal, dual-speed, double-density, double-sided, 96 track per inch (TPI), floppy disk drive.

The hard disk controller on the ESDI controller board can support three internal ESDI hard disk drives. The hard disk controller can accommodate serial data rates to 10M bits per second and is capable of seek-overlap operation when multiple devices are used.

# **Terminal Cluster Unit**

The terminal cluster unit (TCU) is based upon multiple Intel 8044 microcontrollers or remote universal peripheral interfaces (RUPIs) which are single-chip microcontrollers operating at 9.83 MHz. The RUPI contains an 8051 microprocessor core, two counter timers, an interrupt controller, a high-speed DMA controller, 192 bytes of dual-ported RAM, 4K of mask ROM, and a serial interface unit (SIU) capable of supporting synchronous communications. The 8051 CPU and SIU can run concurrently.

There is one 8044 dedicated to driving each RS-232 serial port. The 8044's SIU is designed to perform serial communications to the multidrop communications board with little CPU involvement. Much of the synchronous data link control (SDLC) protocol handling is implemented on-chip. The SIU transmits data at 983K bits per second, and can receive at rates up to 2M bits per second (determined by the transmit rate of the multidrop communications board - typically 1M bits per second). The line protocol is carrier-sense, multiple access (CSMA), polled.

傳

A single-channel UART (Motorola MC2661 enhanced programmable communications interface - EPCI) is used to provide communications between the RUPI and the RS-232 serial device. All RS-232 communications parameters (i.e., baud rate, number of stop bits, hand-shaking, etc.) are under software control via the RUPI.

A switch on the TCU sets the station identification addresses, which allows the multidrop communications board to uniquely address each RS-232 serial device.

2-14

# Subsystem Operation

# How to Use This Section

This maintenance section provides troubleshooting, removal/ replacement, and preventive maintenance information. Preventive maintenance consists of cleaning the component parts of the system. Also included are instructions for shipping field-replaceable units to the factory or service center for repair or replacement.

Before you begin to troubleshoot, look at the following troubleshooting guide to help you determine which of the troubleshooting procedures in Chapters 3 through 5 will quickly locate the problem.

| Troubleshooting | Procedure | Guide |

|-----------------|-----------|-------|

|-----------------|-----------|-------|

| Trouble Symptom                                                                        | Procedure                                                                                                                                                                                |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System does not appear<br>to have power                                                | 1. Use Power-Up Checks - Chapter 3                                                                                                                                                       |

| Power-up cycle does not                                                                | 1. Use Power-Up Checks - Chapter 3                                                                                                                                                       |

| complete or ther is an error message                                                   | 2. Use Monitor Debugger - Chapter 5                                                                                                                                                      |

| Power-up cycle completes<br>but system does not boot                                   | <ol> <li>Use Power-Up Checks - Chapter 3</li> <li>Use Floppy-Based Diagnostics -</li> </ol>                                                                                              |

|                                                                                        | Chapter 4                                                                                                                                                                                |

| Power-up and boot are<br>ok but processing<br>fails (operating<br>system error message | <ol> <li>Use Monitor Debugger - Chapter 5</li> <li>Refer to Operating System manual<br/>to determine if failure is<br/>software or hardware related.<br/>If hardware related:</li> </ol> |

|                                                                                        | 2. Use Floppy-Based Diagnostics -<br>Chapter 4                                                                                                                                           |

|                                                                                        | 3. Use Monitor Debugger - Chapter 5                                                                                                                                                      |

# Chapter 3 **Power-Up Checks**

- 3-3 INTRODUCTION

- 3-3 PRELIMINARY TROUBLE ANALYSIS

- 3-6 MONITOR COMMUNICATION PROTOCOL

- 3-7 SYSTEM POWER-UP SEQUENCE

- 3-10 POWER-UP TESTS

- Communications (Multidrop or SIO) Power-Up Tests 3-11 3-12

- CPU Power-Up Sequence

- 3-14 CPU Monitor Address Map

- 3-15 **Global** Descriptors

- 3-17 Universal Parameter Block

- 3-18 CPU Power-Up Tests

- 3-30 File Processor and Controller Power-Up Tests

- 3-33 CPU AND FILE PROCESSOR COMMUNICATION

- 3-33 **Interrupt Signals**

- Communication Protocol 3-33

- 3-34 **Boot** Failures

Power-Up Checks

(BLANK)

# INTRODUCTION

This chapter contains power-up troubleshooting information for locating a faulty field-replaceable unit (FRU) on the Altos 386 Series 2000 Computer System. However, if problems persist after performing the power-up checks described in this chapter, refer to Floppy-Based Diagnostics - Chapter 4 for additional test information.

# PRELIMINARY TROUBLE ANALYSIS

If the system fails to power-up or boot, use Table 3-1 to help determine the cause of the problem. Most of these preliminary checks do not require qualified service personnel.

## CAUTION

Before attempting to troubleshoot, be sure that the main power supply is set for the proper AC line voltage. (Refer to 115/230 VAC Conversion -Appendix F for the main power supply AC conversion instructions.)

| Symptom                                        | Probable Cause                          | Corrective Action                                                                              |

|------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|

| 1. No display<br>appears on<br>system console. | a. Reset/Run switch<br>is in Reset      | Set Reset/Run<br>switch to Run                                                                 |

| System console.<br>System seems<br>dead.       | b. Screen has<br>cycled off             | Press Retn key                                                                                 |

|                                                | c. Brightness or<br>contrast too low    | Adjust console ter-<br>minal brightness<br>and contrast<br>controls                            |

|                                                | d. Terminal cable<br>loose or defective | Check/replace cable<br>from port 0 of<br>primary communica-<br>tions board (COMM 0)            |

|                                                | e. No AC power from receptacle          | Check for AC to<br>receptacle. Check/<br>replace AC recep-<br>tacle                            |

|                                                | f. Power cord loose<br>or defective     | Check/replace power cord                                                                       |

|                                                | g. Fuse blown                           | Check/replace fuse<br>(replace with<br>proper value)                                           |

|                                                | h. Faulty power<br>supply               | Replace power<br>supply                                                                        |

| 2. Fuse blows repeatedly                       | a. Short circuit<br>in system           | Remove all drives<br>and plug-in boards.<br>Replace fuse and<br>apply power - see<br>cause (b) |

|                                                | b. Faulty main<br>power supply          | Check/replace main power supply                                                                |

# Table 3-1. Preliminary Trouble Analysis

| Symptom                                | Probable Cause                       | Corrective Action                                                                                                                                             |

|----------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. Fuse blows<br>repeatedly<br>(Cont.) | c. Faulty plug-in<br>board subsystem | Install one plug-in<br>board. Replace fuse<br>and apply power.<br>Repeat for each<br>plug-in board until<br>faulty board is<br>found. Replace<br>faulty board |

| 3. Display appears but no response     | a. System "hung"                     | Reset system                                                                                                                                                  |

| from keyboard                          | b. Terminal or<br>system trouble     | Check terminal by<br>plugging into<br>another system, or<br>check other term-<br>inals on the system                                                          |

Table 3-1. Preliminary Trouble Analysis (Cont.)

#### WARNING

Hazardous voltages are present in the power supply. Use extreme caution when measuring voltages.

### NOTE

The power supply is a switching type. Check under load to ensure accurate results.

c. Power supply DC voltages out of tolerance

Check power supply voltages with a digital voltmeter. Refer to Table 3-2 for power supply DC output voltages)

| Voltage* | Measured At | Range          |

|----------|-------------|----------------|

| +5       | JB, Pin 4   | +5.0 to +5.2   |

| +12      | JB, Pin 1   | +11.4 to +12.6 |

| -12      | JA, Pin 9   | -11.4 to +12.6 |

| Gnd      | JB, Pin 2   |                |

Table 3-2. Power Supply DC Voltages

\* Measure the power supply output voltages with a precision DC voltmeter. Connectors JA and JB are located along the top of the backplane board. Make the measurements with the tape and floppy drives connected.

If the power supply output voltages are out of tolerance, return the power supply to the factory for repair or replacement. Refer to Removal/Replacement - Chapter 6 for specific removal and replacement procedures.

## MONITOR COMMUNICATION PROTOCOL

Monitor communication between the CPU, communications, and file processor firmware is accomplished through groups of parameter blocks in the system memory. All communication requires CPU intervention except during power-up. Thus, no direct communication between controllers is allowed.

For example, if the file processor needs to print a message, it must send the print command to the CPU board, which will then route the request to the communications board for actual display.

During power-up time, the primary communications board firmware assigns each controller (e.g., file processor, up to three other communications boards, and the CPU board) a 320 byte space in system memory (64 bytes for the parameter block and 256 bytes for the buffer) to be used as the parameter block and message buffer. Subsequently, all communications are done on a one-to-one basis between the CPU and file processor, or between the CPU and the individual communications boards.

# SYSTEM POWER-UP SEQUENCE

な温度

The power-up tests use the ROM-based diagnostic tests contained on the CPU, communications, and file processor boards. The power-up tests are always performed when power is applied or the system is reset. Refer to Figure 3-1 for a block diagram of the power-up test sequence. These tests check the hardware configuration on each board, identify any missing or failed assemblies, and then confirm communication with the system as follows:

- communications tests check local RAM and PROM, I/O integrated circuits, DMA controller, interrupts, system bus, and initialize memory

- CPU tests check the PROM, cache RAM, counter/input/output (CIO), tag RAM, clock, floating-point processor, interrupts, and system bus o file-processor tests check the local RAM and PROM, interval timer, system bus, DMA controller, and storage device controllers

## Power-Up Checks

Figure 3-1. System Power-Up Test Sequence

During power-up, the primary communications board firmware proceeds in the following sequence:

- 1. After internal verification, the primary communications board firmware sends a COMMUNICATIONS BOARD POWER-UP TESTS message to port 0 (main console).

- 2. After internal verification, the primary communications board checks for remote diagnostics.

- 3. After internal verification, the primary communications board tests the system memory.

- 4. After the internal and external tests are completed, the primary communications board sets up a firmware protocol block and sends a channel attention to the CPU board. The primary communications board will timeout if the CPU does not respond in a few seconds.

- 5. After receiving acknowledgement from the CPU board, the primary communications board displays its power-up test results on the main console (port 0).