# TECHNICAL MANUAL **AM-420** DISK DRIVE CONTROLLER CIRCUIT BOARD

DWM-00420-00 REV. A00

1. 30

## **FIRST EDITION**

OCTOBER, 1981

## **REVISIONS INCORPORATED:**

EDITION

0

DATE

#### **PROPRIETARY NOTICE**

This document and the information herein disclosed is the proprietary property of ALPHA MICRO, 17881 Sky Park North, Irvine, California 92714. Any person or entity to whom this document is furnished or having possession thereof, by acceptance, assumes custody thereof and agrees that the document is given in confidence and will not be copied or reproduced in whole or in part, nor used or revealed to any person in any manner except to meet the purposes for which it was delivered. Additional rights and obligations regarding this document and its contents may be defined by a separate written agreement with ALPHA MICROSYSTEMS, and if so, such separate written agreement shall be controlling.

## TABLE OF CONTENTS

## Paragraph

## Page

## SECTION I

## GENERAL DESCRIPTION

| 1.0 | Introduction              | 1-1 |

|-----|---------------------------|-----|

| 1.1 | Circuit Board Description | 1-1 |

| 1.2 | Application               | 1-1 |

## SECTION II

#### OPERATING DATA

| 2.0   | Introduction                    | 2–1  |

|-------|---------------------------------|------|

| 2.1   | Capabilities and Specifications | 2–1  |

| 2.2   | Installation And Start-Up       | 2-4  |

| 2.2.1 | Installation                    | 2-4  |

| 2.3   | Interface Description           | 2-12 |

| 2.3.1 | S-100 Bus Interface             | 2–12 |

| 2.3.2 | Disk Drive Interface            | 2-12 |

| 2.4   | User Options                    | 2-13 |

| 2.4.1 | Address Code                    | 2-13 |

| 2.4.2 | Interrupt Lines                 | 2-13 |

| 2.4.3 | Boot Option                     | 2-13 |

| 2.4.4 | AM-100 Preparation              | 2-13 |

i

## SECTION III PROGRAMMING

| 3.0      | Introduction                        | 3-1  |

|----------|-------------------------------------|------|

| 3.1      | Unique Software Considerations      | 3-1  |

| 3.2      | Addressing                          | 3-1  |

| 3.3      | Initialization                      | 3-2  |

| 3.4      | Command Register                    | 3-2  |

| 3.5      | Status Register                     | 3-4  |

| 3.6      | Interrupt Mode                      | 3-4  |

| 3.7      | Handshake Sequence                  | 3-4  |

| 3.8      | DMA Buffer                          | 3-7  |

| 3.8.1    | DMA Buffer Operation For Disk Write | 3-7  |

| 3.8.2    | DMA Buffer Operation For Disk Read  | 3-10 |

| 3.8.3    | Physical Address                    | 3-11 |

| 3.9      | Restore Command                     | 3-12 |

| 3.10     | Status Check                        | 3-12 |

| 3.11     | Special Commands                    | 3-13 |

| 3.11.1   | Type I Commands                     | 3-14 |

| 3.11.2   | Type II Commands                    | 3-14 |

| 3.11.2.1 | Read Revision Level (OF Hex)        | 3-14 |

| 3.11.2.2 | RAM Test (1F Hex)                   | 3-14 |

| 3.11.2.3 | Sequence Up Drive (2F Hex)          | 3-15 |

| 3.11.2.4 | Sequence Down Drive (3F Hex)        | 3-16 |

| 3.11.2.5 | Reset Drive (4F Hex)                | 3-16 |

| 3.11.2.6 | Read Drive ID (5F Hex)              | 3-16 |

| 3.11.2.7 | Read Drive Sector Size (6F Hex)     | 3-17 |

| 3.11.2.8 | Read Current Cylinder (7F Hex)      | 3-17 |

| 3.11.2.9 | Read Drive Status (8F Hex)          | 3-17 |

## SECTION IV

FUNCTIONAL THEORY OF OPERATION

| 4.0   | Introduction            | 4-1  |

|-------|-------------------------|------|

| 4.1   | Circuit Board Operation | 4-1  |

| 4.1.1 | Power-Up Reset          | 4-16 |

ii

## SECTION IV

## FUNCTIONAL THEORY OF OPERATION (Con't)

| 4.1.2    | Addressing                         | 4-16 |

|----------|------------------------------------|------|

| 4.1.3    | CPU Output                         | 4-16 |

| 4.1.3.1  | Command Data                       | 4-17 |

| 4.1.3.2  | Command Types                      | 4-17 |

| 4.1.3.3  | Output Data                        | 4-22 |

| 4.1.4    | CPU Input                          | 4-22 |

| 4.1.4.1  | Status Register                    | 4-22 |

| 4.1.4.2  | Status Word Formats                | 4-23 |

| 4.1.4.3  | Input Data Register                | 4-23 |

| 4.1.5    | Boot Load Procedure                | 4-23 |

| 4.1.6    | Interrupts                         | 4-25 |

| 4.1.7    | Byte Clock Counter                 | 4-25 |

| 4.1.8    | Disk Transfer Logic                | 4-26 |

| 4.1.9    | Sector Counter                     | 4-26 |

| 4.1.10   | Data Write Logic                   | 4-26 |

| 4.1.10.1 | Disk Drive Controls                | 4-27 |

| 4.1.11   | Input From Disk Drive              | 4–27 |

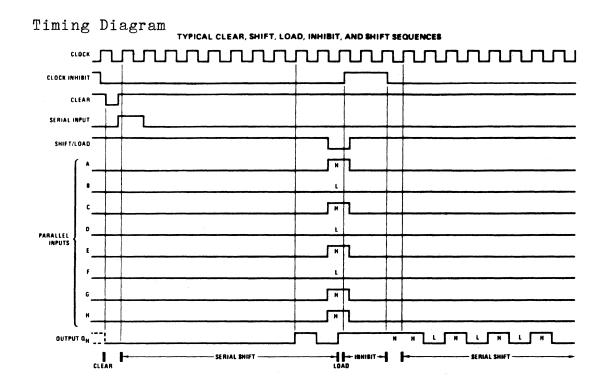

| 4.1.12   | AM-420 Board Operations and Timing | 4-27 |

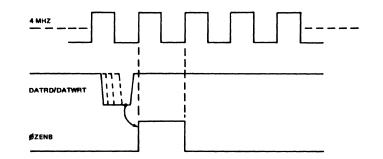

| 4.1.12.1 | Data Transfer Operations           | 4-27 |

| 4.1.12.2 | Disk Transfer Operations           | 4-28 |

| 4.1.12.3 | Disk Read Clocks                   | 4-29 |

| 4.1.12.4 | Disk Write Clocks                  | 4-30 |

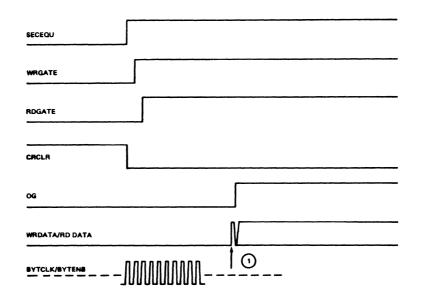

| 4.1.12.5 | Sector Beginning Format Operations | 4-30 |

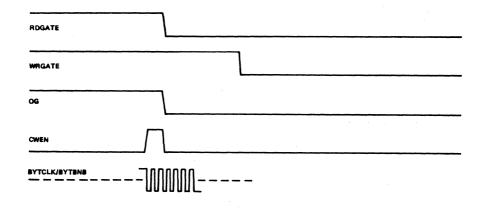

| 4.1.12.6 | Sector End Format Operations       | 4-31 |

| 4.1.12.7 | DMA Transfer Operations            | 4-32 |

| 4.2      | Circuit Module Description         | 4-33 |

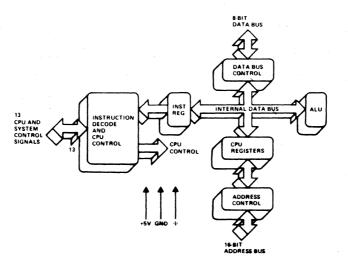

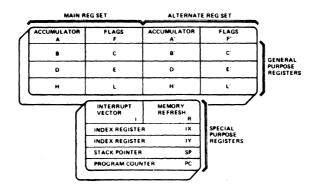

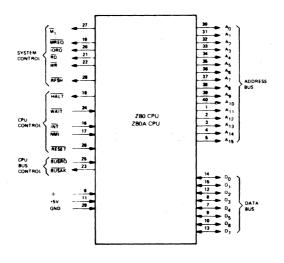

| 4.2.1    | CPU Microprocessor (U11)           | 4-33 |

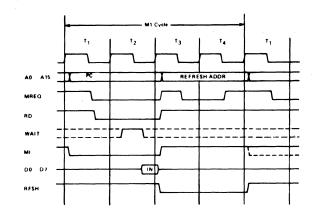

| 4.2.1.1  | Instruction Op-Code Fetch          | 4-39 |

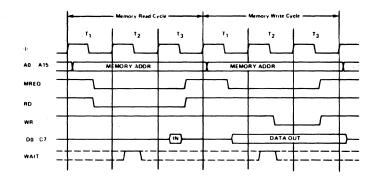

| 4.2.1.2  | Memory Read Or Write Cycles        | 4-40 |

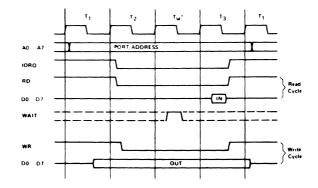

| 4.2.1.3  | Input Or Output Cycles             | 4-41 |

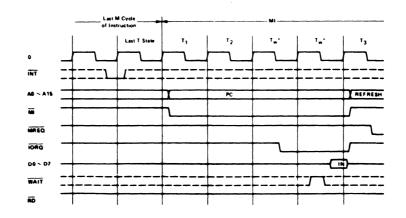

| 4.2.1.4  | Interrupt Request/Acknowledge      | 4-41 |

| 4.2.1.5  | CPU Instruction Set                | 4-42 |

## SECTION IV

FUNCTIONAL THEORY OF OPERATION (Con't)

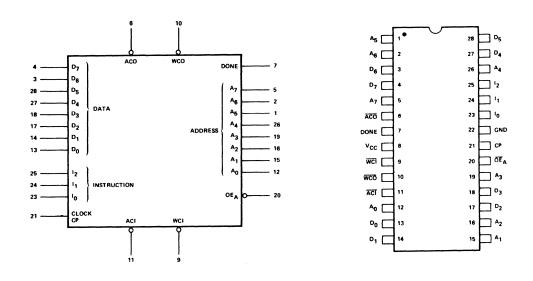

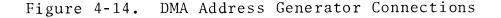

| 4.2.2   | DMA Address Generator (U10, U21)                    | 4-47          |

|---------|-----------------------------------------------------|---------------|

| 4.2.2.1 | Architecture                                        | 4-48          |

| 4.2.2.2 | Control Modes                                       | 4-51          |

| 4.2.2.3 | Instructions                                        | 4-52          |

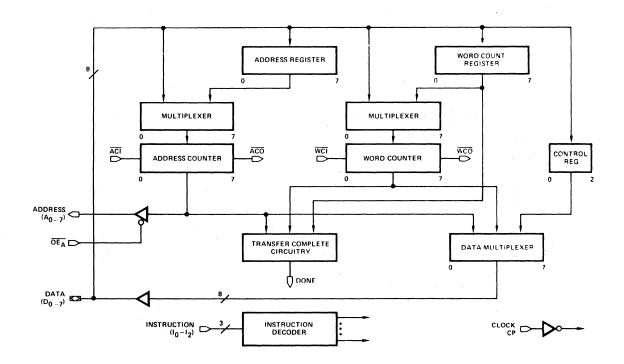

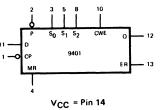

| 4.2.3   | Cyclic Redundancy (CRC) Generator/Checker (U15)     | 4-53          |

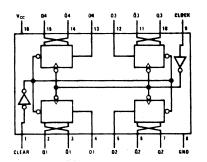

| 4.2.4   | Positive-Edge-Triggered Flip-Flops with Preset      |               |

|         | and Clear (U5, U14, U53, U55, U62)                  | 4-57          |

| 4.2.5   | Dual J-K Negative-Edge Triggered Flip-Flops with    |               |

|         | Preset and Clear (U17)                              | 4-57          |

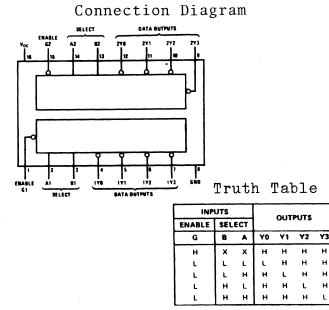

| 4.2.6   | Decoder (U25, U26, U71)                             | 4-58          |

| 4.2.7   | Decoder/Demultiplexer (U30)                         | 4 <b>-</b> 59 |

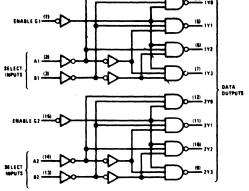

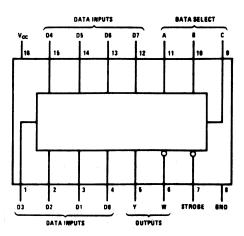

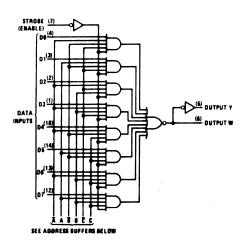

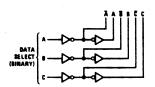

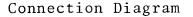

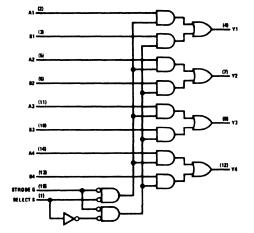

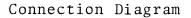

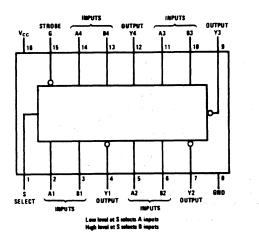

| 4.2.8   | Data Selector/Multiplexer (U13)                     | 4-60          |

| 4.2.9   | Quad Two-Line to One-Line Data Selector/            |               |

|         | Multiplexer (U61)                                   | 4-60          |

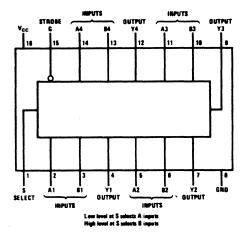

| 4.2.10  | Quad Inverting Two-Line to One-Line Data Selector/  |               |

|         | Multiplexer (U18, U19)                              | 4-62          |

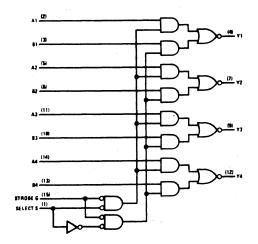

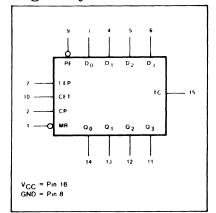

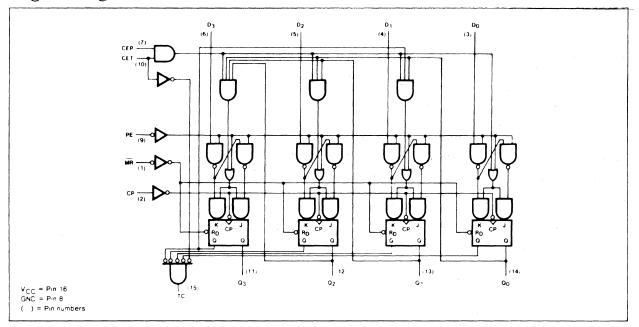

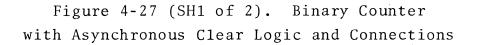

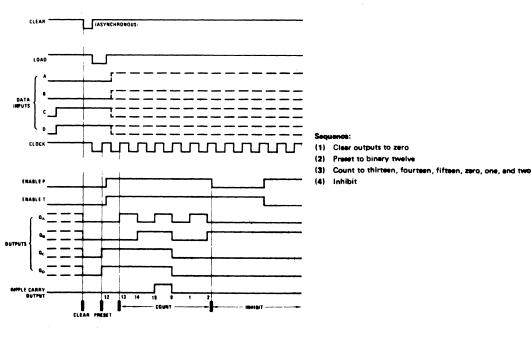

| 4.2.11  | Four-Bit Binary Counter With Asynchronous Clear     |               |

|         | (U75)                                               | 4-63          |

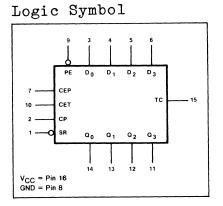

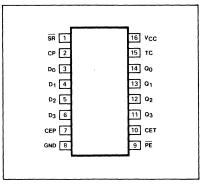

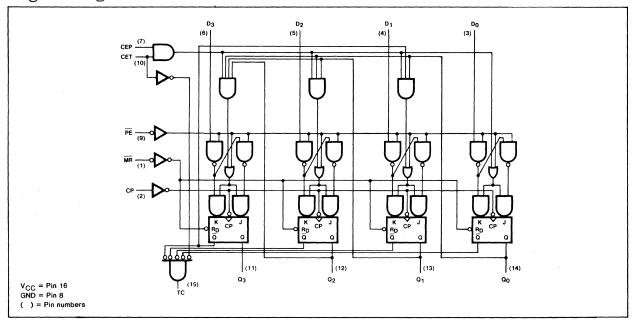

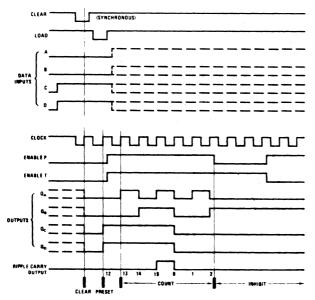

| 4.2.12  | Four-Bit Binary Counter With Synchronous Clear      |               |

|         | (U23, U24, U74)                                     | 4-66          |

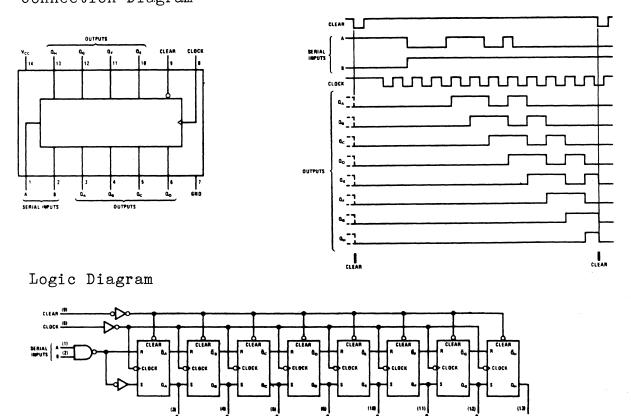

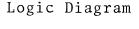

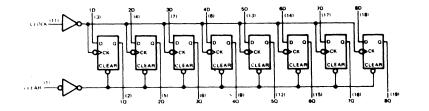

| 4.2.13  | Eight-Bit Serial In/Parallel Out Shift Register     |               |

|         | (U66)                                               | 4-69          |

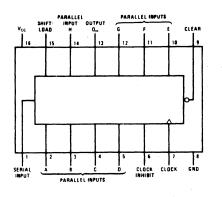

| 4.2.14  | Eight Bit Parallel In/Serial Out Shift Register     |               |

|         | (U67)                                               |               |

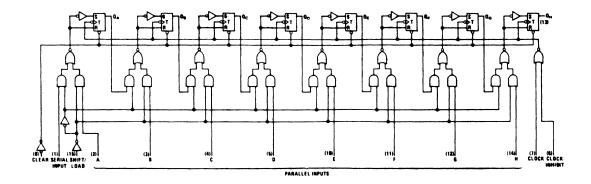

| 4.2.15  | Quad D Flip-Flops With Clear (U63)                  | 4-72          |

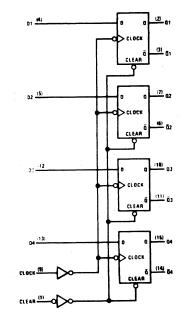

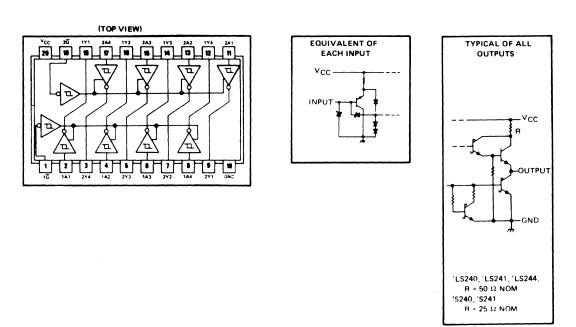

| 4.2.16  | Inverting Tri-State Buffer (U34, U65, U72)          |               |

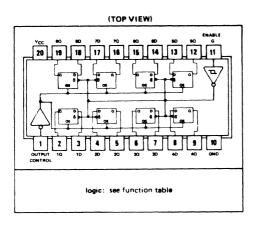

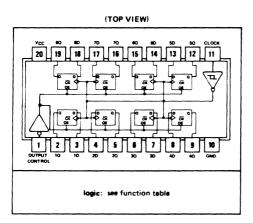

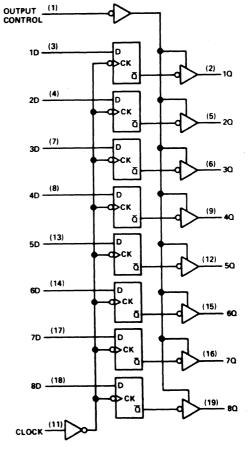

| 4.2.17  | Octal D-Type Flip-Flop With Clear (U35, U79)        | 4-74          |

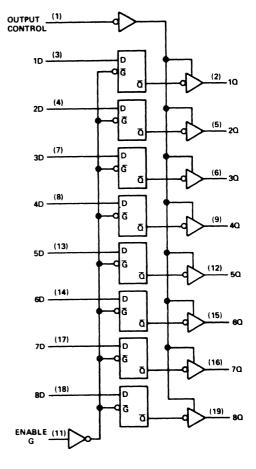

| 4.2.18  | Octal D-Type Transparent Latch (U39)                | 4-75          |

| 4.2.19  | Tri-State D Flip-Flops (U37, U48, U40, U76, U77,    |               |

|         | U80)                                                | 4-76          |

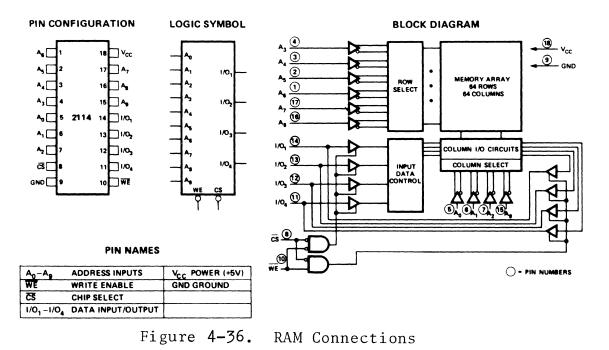

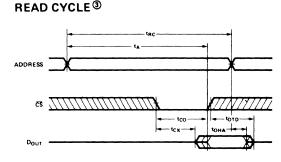

| 4.2.20  | 1024 X 4-Bit Static Random Access Memory (U41, U42) |               |

| 4.2.21  | Bus Comparator (U27, U68)                           |               |

| 4.2.22  | Tri-State Octal Buffers (U36)                       | 4-79          |

| 4.2.23  | Bidirectional Transceiver (U43, U64)                | 4-80          |

#### SECTION V

## MAINTENANCE AND TROUBLESHOOTING

| 5.0 | Introduction           | 5-1 |

|-----|------------------------|-----|

| 5.1 | Circuit Board Checkout | 5-1 |

| 5.2 | Warranty Procedures    | 5-2 |

## SECTION VI

PARTS LIST AND SCHEMATIC

## LIST OF ILLUSTRATIONS

Figure

| 1 – 1 | AM-420 Simplified Block Diagram                       | 1-2  |

|-------|-------------------------------------------------------|------|

| 2–1   | Disk Drive Interface Cabling                          | 2-5  |

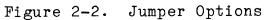

| 2-2   | Jumper Options                                        | 2-14 |

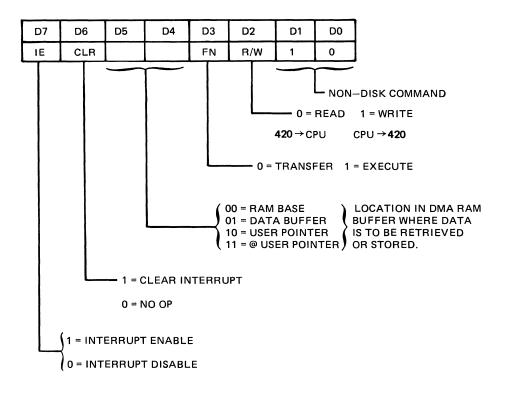

| 3–1   | System Commands                                       | 3-3  |

| 3-2   | AM-420 Status Words                                   | 3-5  |

| 3-3   | DMA Buffer Operation                                  | 3-6  |

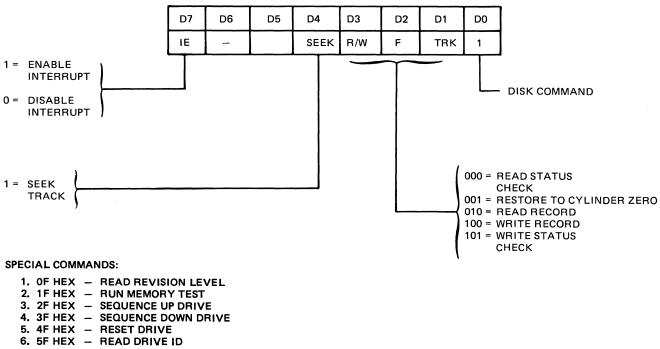

| 3-4   | Handshake Sequence                                    | 3-8  |

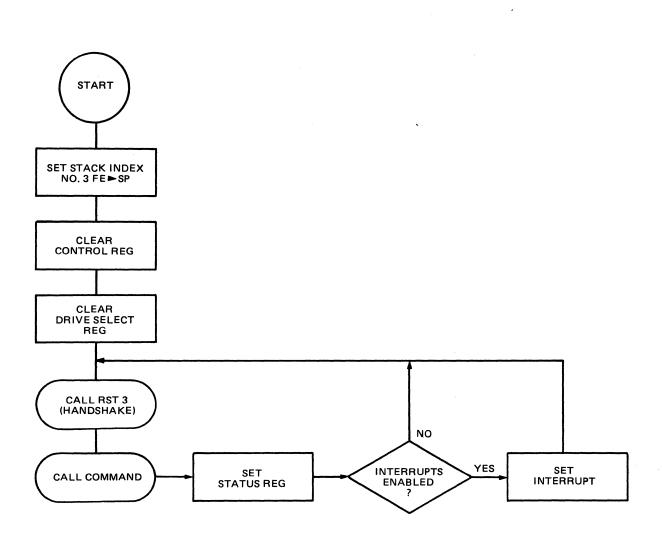

| 3-5   | DMA Transfer Sequence                                 | 3-9  |

| 4-1   | AM-420 Functional Block Diagram                       | 4-2  |

| 4-2   | AM-420 Functional Block Diagram                       | 4-3  |

| 4-3   | Status Word Formats                                   | 4-24 |

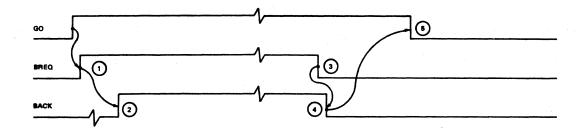

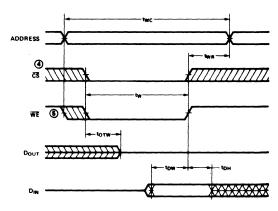

| 4-4   | Data Transfer Timing                                  | 4-28 |

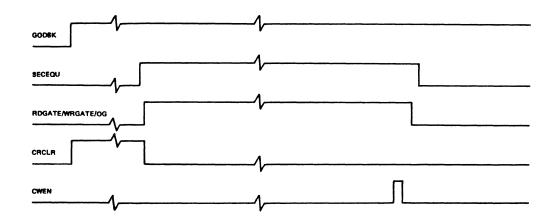

| 4-5   | Disk Transfer Timing                                  | 4-29 |

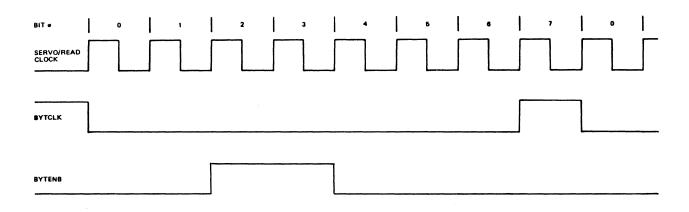

| 4-6   | BYTCLK-BYTENB Timing                                  | 4-29 |

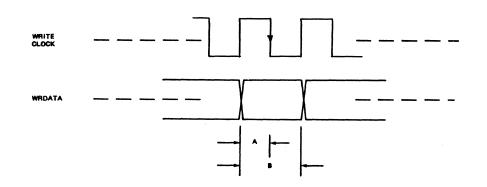

| 4-7   | Disk Write Timing                                     | 4-30 |

| 4-8   | Sector Beginning Timing                               | 4-31 |

| 4-9   | Sector End Format Timing                              | 4-32 |

| 4–10  | DMA Transfer Timing                                   | 4-33 |

| 4-11  | CPU Block Diagram                                     | 4-34 |

| 4-12  | CPU Registers                                         | 4-34 |

| 4-13  | CPU Pin Configuration                                 | 4-34 |

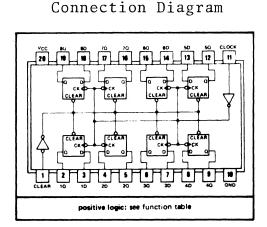

| 4-14  | DMA Address Generator Connections                     | 4-47 |

| 4–15  | DMA Address Generator Block Diagram                   | 4-48 |

| 4–16  | Control Register Format Definition                    | 4-49 |

| 4-17  | CRC Checker Connections                               | 4-55 |

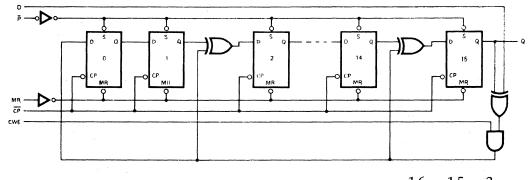

| 4-18  | CRC Equivalent Ciruit For $X^{16} + X^{17} + X^2 + 1$ | 4-56 |

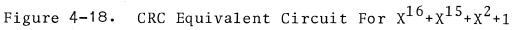

| 4-19  | CRC Check Word Generation                             | 4-56 |

| 4–20  | Dual D Flip-Flop Connections                          | 4-57 |

| 4-21  | Dual J-K Flip-Flop Connections                        | 4-57 |

| 4-22  | Decoder Connections                                   | 4-58 |

| 4-23  | Decoder/Demultiplexer Connections                     | 4-59 |

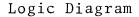

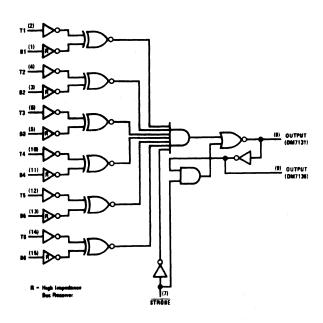

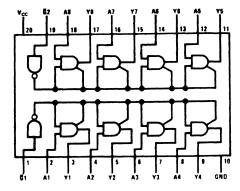

| 4-24  | Data Selector/Multiplexer, Logic and Connections      | 4-60 |

## LIST OF ILLUSTRATIONS (Con't)

| 4–25 | Quad Two-Line to One-Line Data Selector/Multiplexer |      |

|------|-----------------------------------------------------|------|

|      | Connections                                         | 4-61 |

| 4-26 | Quad Inverting Two-Line to One-Line Data Selector/  |      |

|      | Multiplexer Connections                             | 4-62 |

| 4–27 | Binary Counter With Asynchronous Clear, Logic and   |      |

|      | Connections (Sh 1 of 2)                             | 4-64 |

| 4-27 | Binary Counter with Asynchronous Clear, Logic and   |      |

|      | Connections (Sh 2 of 2)                             | 4-65 |

| 4–28 | Binary Counter With Synchronous Clear, Logic and    |      |

|      | Connections (Sh 1 of 2)                             | 4-67 |

| 4–28 | Binary Counter With Synchronous Clear, Logic and    |      |

|      | Connections (Sh 2 of 2)                             | 4-68 |

|      |                                                     |      |

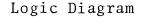

| 4-29 | Eight-Bit Shift Register, Logic and Connections     | 4-69 |

| 4-30 | Eight Bit Parallel In/Serial Out Shift Register,    |      |

|      | Logic and Connections (Sh 1 of 2)                   | 4-70 |

| 4-30 | Eight Bit Parallel In/Serial Out Shift Register,    |      |

|      | Logic and Connections (Sh 2 of 2)                   | 4-71 |

| 4-31 | Quad D Flip-Flops With Clear, Logic and Connections | 4-72 |

| 4-32 | Inverting Tri-State Buffer, Logic and Connections   | 4-73 |

| 4-33 | Octal D-Type Flip-Flop With Clear, Logic and        |      |

|      | Connections                                         | 4-74 |

| 4-34 | Transparent Latch, Logic and Connections            | 4-75 |

| 4-35 | Tri-State D Flip-Flop Connections                   | 4-76 |

| 4-36 | RAM Connections                                     | 4-77 |

| 4-37 | Bus Comparator Connections                          | 4-78 |

| 4-38 | Tri-State Octal Buffers, Logic and Connections      | 4-79 |

| 4-39 | Bidirectional Transceiver, Logic and Connections    | 4-80 |

.

## LIST OF TABLES

Table

## Page

1

| 2-1 | AM-420 Specifications 2             | 2-2          |

|-----|-------------------------------------|--------------|

| 2-2 | Alpha Micro Bus Interface Signals 2 | 2-6          |

| 4-1 | AM-420 Signals List 4               | 1-4          |

| 4-2 | Non-Disk Command Bits 4             | <b>1–</b> 18 |

| 4-3 | Non-Disk Command Formats 4          | <b>1–</b> 19 |

| 4-4 | Disk Command Bits 4                 | 1-20         |

| 4-5 | Disk Command Codes 4                | 1-21         |

| 4–6 | CPU Signal List 4                   | 1-35         |

| 4-7 | CPU Instruction Set 4               | 1-43         |

| 4-8 | DMA Register Instructions 4         | 1-52         |

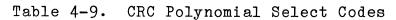

| 4-9 | CRC Polynomial Select Codes 4       | 1-56         |

#### 1.0 INTRODUCTION

This manual provides operating and maintenance instructions for the AM-420 Winchester Disk Drive Controller circuit board manufactured by Alpha Microsystems Inc., located in Irvine, California. Circuit board description, operating and usage instructions, programming, theory of operation, and maintenance instructions are included to provide the user with the information necessary to utilize this circuit board to its full capability.

#### 1.1 CIRCUIT BOARD DESCRIPTION

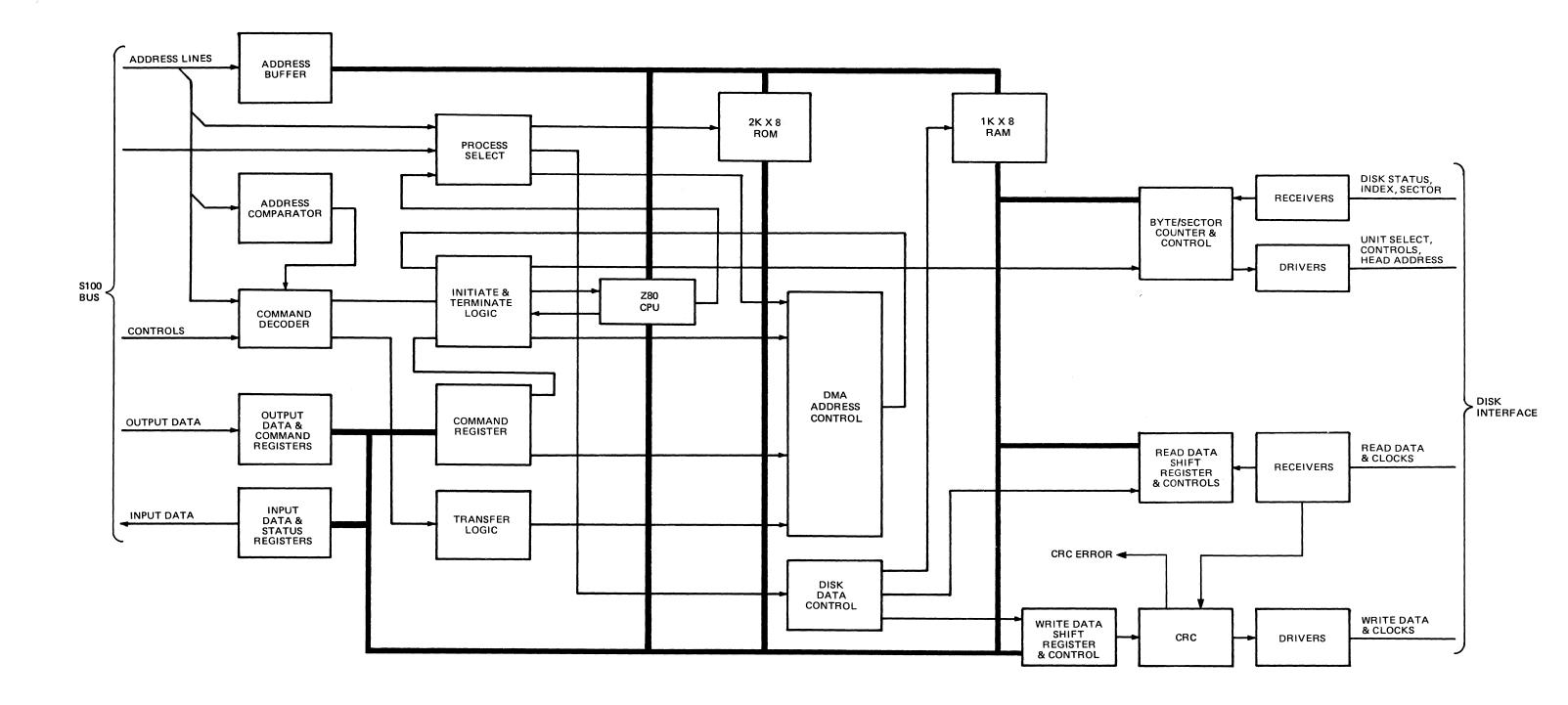

The AM-420 Wincheter Disk Drive Controller circuit board provides data processing, control and interface capability between a standard S-100 Bus system and one to four PRIAM Winchester hard disk drives. A CPU microprocessor, a DMA address generator, a Random Access Memory (RAM) with associated control logic provide the sophisticated data processing necessary for control of up to four PRIAM Winchester disk drives. A 2K Read Only Memory (ROM) is contained on the board to provide a bootstrap load program and also to contain the microcode necessary for the CPU module operation.

A simplified block diagram of the circuit board is shown in Figure 1-1. For a complete detailed description of circuit board operation, see Section IV of this manual. For programming requirements, see Section III of this manual.

#### 1.2 APPLICATION

This circuit board provides the data processing and interface capability necessary for operation of up to four PRIAM Winchester hard Data is transferred at an average rate of 8 MHz between disk drives. the controller and drives. See Section II of this manual for wiring For complete instructions and system interface information. information on the disk drive, see the appropriate PRIAM Hardware Maintenance Manual.

Figure 1-1. AM-420 Simplified Block Diagram

#### 2.0 INTRODUCTION

This section contains information on the use of the AM-420 Disk Controller circuit board. Capabilities, specifications, interface wiring, and user option descriptions are provided for the successful integration of the AM-420 into the user's system.

#### 2.1 CAPABILITIES AND SPECIFICATIONS

This circuit board operates from the standard S-100 Bus structure to interface with the PRIAM Winchester hard disk drive. The board can interface with up to four disk drives. Detailed specifications are contained in Table 2-1.

## Table 2-1. AM-420 Specifications

| PARAMETER                                 | SPECIFICATIONS                                                                                                                               |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Interface                             | Standard S-100 Bus                                                                                                                           |

| Drives per Controller                     | 1-4                                                                                                                                          |

| Printed Circuit Boards                    | 1                                                                                                                                            |

| Data Transfer Modes                       | Programmed Multi-Level<br>Interrupts, Full Sector<br>Block Transfers.                                                                        |

| Data Transfer - Controller<br>to Disk     | Serial                                                                                                                                       |

| Data Transfer - Controller<br>to Computer | 8-bit bytes Parallel                                                                                                                         |

| Data Transfer Format                      | 512 bytes per sector, plus<br>CRC and sentinel check bytes.                                                                                  |

| On-Board Buffer                           | 1024 bytes                                                                                                                                   |

| Error Checking                            | CRC Error Code                                                                                                                               |

| Input Power                               | +8 volts DC @2.0 amps                                                                                                                        |

| Interconnections                          | One mounting slot of an S-100<br>Bus chassis. One 50-pin cable<br>to first drive (25 feet max-<br>imum cumulative length on four<br>drives). |

| Dimensions                                | 9" x 10"                                                                                                                                     |

| PARAMETER                                          | SPECIFICATIONS                                             |

|----------------------------------------------------|------------------------------------------------------------|

| Environment (operating)<br>Temperature<br>Humidity | 60° to 104° F (15° to 40°C)<br>10% to 80% (non-condensing) |

Table 2-1 (Con't). AM-420 Specifications

#### 2.2 INSTALLATION AND START-UP

When the AM-420 circuit board is received, it is ready for use. No adjustment or calibration is required for operation. The hardware requirements for installation and use are described in this section and the software requirements are described in Section III.

#### 2.2.1 Installation

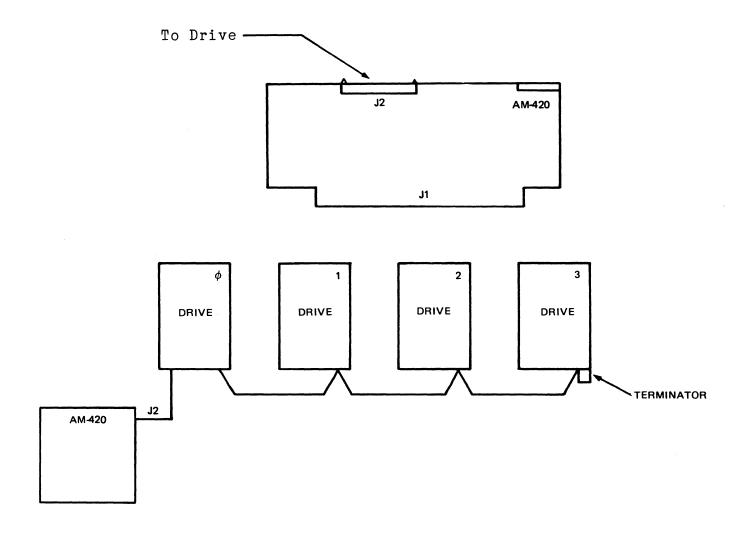

First ensure that the proper power wiring is available and that the correct voltages are connected to the disk drive and to the various pins of the circuit board as shown in Table 2-2. Connect the cables to the disk drives as shown in Figure 2-1.

Figure 2-1. Disk Drive Interface Cabling

| MNEMONIC | NAME                          | PIN NO. |

|----------|-------------------------------|---------|

| +7.5₹    | + 7.5vdc Power                | 1       |

| +16⊽     | + 16vdc Power                 | 2       |

| VI8      | Vectored Interrupt 8          | 3       |

| VIO      | Vectored Interrupt O          | 4       |

| VI1      | Vectored Interrupt 1          | 5       |

| VI2      | Vectored Interrupt 2          | 6       |

| VI3      | Vectored Interrupt 3          | 7       |

| VI4      | Vectored Interrupt 4          | 8       |

| VI5      | Vectored Interrupt 5          | 9       |

| VIG      | Vectored Interrupt 6          | 10      |

| VI7      | Vectored Interrupt 7          | 11      |

| RTC      | Real Time Clock, 50Hz or 60Hz | 12      |

| POWFAIL  | AC Power Failure Status       | 13      |

| VI9      | Vectored Interrupt 9          | 14      |

| A18      | Address 18                    | 15      |

| A16      | Address 16                    | 16      |

| A17      | Address 17                    | 17      |

| STATDSB  | Status Disable                | 18      |

| C/CDSB   | Command/Control Disable       | 19      |

| GND      | Ground                        | 20      |

Table 2-2. Alpha Micro Bus Interface Signals List

DWM-00420-00 REV. A00

ĺ

| MNEMONIC                           | NAME                                                                         | PIN NO.                          |

|------------------------------------|------------------------------------------------------------------------------|----------------------------------|

| IODIS                              | I/O Disable                                                                  | 21                               |

| ADDDSB                             | Address Disable                                                              | 22                               |

| DODSB                              | Data Bus Disable                                                             | 23                               |

| <b>ø</b> 2                         | Phase 2 Clock                                                                | 24                               |

| STVAL                              | Status and Address Valid                                                     | 25                               |

| PHLDA                              | DMA Request Acknowledge                                                      | 26                               |

| PWAIT                              | Processor Wait                                                               | 27                               |

| N/U                                | Not Used                                                                     | 28                               |

| A5<br>A4<br>A3<br>A15<br>A12<br>A9 | Address 5<br>Address 4<br>Address 3<br>Address 15<br>Address 12<br>Address 9 | 29<br>30<br>31<br>32<br>33<br>34 |

| DOUT 1/D1<br>DOUT 0/DO             | Data Bus Bit 1<br>Data Bus Bit O                                             | 35<br>36                         |

| A10                                | Address 10                                                                   | 37                               |

Table 2-2.(con't) Alpha Micro Bus Interface Signals List

| Table 2-2. | (con't) | Alpha | Micro | Bus | Interface | Signals | List |

|------------|---------|-------|-------|-----|-----------|---------|------|

|------------|---------|-------|-------|-----|-----------|---------|------|

| MNEMONIC                                                                   | NAME                                                                                                        | PIN NO.                          |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------|

| DOUT 4/D4<br>DOUT 5/D5<br>DOUT 6/D6<br>DIN 2/D10<br>DIN 3/D11<br>DIN 7/D15 | Data Bus Bit 4<br>Data Bus Bit 5<br>Data Bus Bit 6<br>Data Bus Bit 10<br>Data Bus Bit 11<br>Data Bus Bit 15 | 38<br>39<br>40<br>41<br>42<br>43 |

| SMI                                                                        | Bus Master OP Code Fetch                                                                                    | 44                               |

| SOUT                                                                       | I/O Output Cycle                                                                                            | 45                               |

| SINP                                                                       | I/O Input Cycle                                                                                             | 46                               |

| SMEMR                                                                      | Memory Read Cycle                                                                                           | 47                               |

| SHLTA                                                                      | HLT Acknowledge                                                                                             | 48                               |

| PERR                                                                       | Parity Error Pulse                                                                                          | 49                               |

| GND                                                                        | Ground                                                                                                      | 50                               |

| +7.5₹                                                                      | +7.5vdc Power                                                                                               | 51                               |

| -16V                                                                       | -16vdc Power                                                                                                | 52                               |

| GND                                                                        | Ground                                                                                                      | 53                               |

| SLAVECLR                                                                   | Reset Signal To All I/O Devices                                                                             | 54                               |

| MNEMONIC                 | NAME                                                 | PIN NO.              |  |  |

|--------------------------|------------------------------------------------------|----------------------|--|--|

| DMAO                     | DMA Controller Arbitration                           | 55                   |  |  |

| DMA 1                    | Lines For Use With Standard                          | 56                   |  |  |

| DMA2                     | S-100 Bus DMA System                                 | 57                   |  |  |

| SXTRQ                    | 16 Bit Cycle                                         | 58                   |  |  |

| A19                      | Address 19                                           | 59                   |  |  |

| N/U                      | Not Used                                             | 60                   |  |  |

| A20<br>A21<br>A22<br>A23 | Address 20<br>Address 21<br>Address 22<br>Address 23 | 61<br>62<br>63<br>64 |  |  |

| ADVAL                    | Address Valid On Data Bus                            | 65                   |  |  |

| WRDIS                    | Write Disable                                        | 66                   |  |  |

| PHANTOM                  | PHANTOM ROM Memory Enable                            |                      |  |  |

| N/U<br>N/U               | Not Used<br>Not Used                                 | 68<br>69             |  |  |

| Gnd                      | Ground                                               | 70                   |  |  |

| N/U                      | Not Used                                             | 71                   |  |  |

| PRDY                     | Processor Ready                                      | 72                   |  |  |

Table 2-2.(con't) Alpha Micro Bus Interface Signals List

| MNEMONIC  | NAME                               |    |  |  |  |  |  |

|-----------|------------------------------------|----|--|--|--|--|--|

| N/U       | Not Used                           | 73 |  |  |  |  |  |

| PHOLD     | DMA Request                        | 74 |  |  |  |  |  |

| PRESET    | Preset                             | 75 |  |  |  |  |  |

| PSYNC     | Processor Sync, Start of Bus Cycle | 76 |  |  |  |  |  |

| PWR       | Write Strobe                       | 77 |  |  |  |  |  |

| PDBIN     | Data Bus Input Command             | 78 |  |  |  |  |  |

| AO        | Address O                          | 79 |  |  |  |  |  |

| A1        | Address 1                          | 80 |  |  |  |  |  |

| A2        | Address 2                          | 81 |  |  |  |  |  |

| A6        | Address 6                          | 82 |  |  |  |  |  |

| Α7        | Address 7                          | 83 |  |  |  |  |  |

| 88        | Address 8                          | 84 |  |  |  |  |  |

| A13       | Address 13                         | 85 |  |  |  |  |  |

| A14       | Address 14                         | 86 |  |  |  |  |  |

| A11       | Address 11                         | 87 |  |  |  |  |  |

| DOUT 2/D2 | Data Bus Bit 2                     | 88 |  |  |  |  |  |

| DOUT 3/D3 | Data Bus Bit 3                     | 89 |  |  |  |  |  |

| DOUT 7/D7 | Data Bus Bit 7                     | 90 |  |  |  |  |  |

| DIN 4/D12 | Data Bus Bit 7                     | 91 |  |  |  |  |  |

| DIN 5/D13 | Data Bus Bit 13                    | 92 |  |  |  |  |  |

| DIN 6/D14 | Data Bus Bit 14                    | 93 |  |  |  |  |  |

| DIN 1/D9  | Data Bus Bit 9                     | 94 |  |  |  |  |  |

| DIN O/D8  | Data Bus Bit 8                     | 95 |  |  |  |  |  |

Table 2-2.(con't) Alpha Micro Bus Interface Signals List

| MNEMONIC | NAME                   | PIN NO. |

|----------|------------------------|---------|

| SINTA    | Interrupt Acknowledge  | 96      |

| SWO      | Bus Master Output      | 97      |

| ERROR    | Memory Error Interrupt | 98      |

| BERR     | Bus Error              | 99      |

| GND      | Ground                 | 100     |

Table 2-2.(con't) Alpha Micro Bus Interface Signals List

#### 2.3 INTERFACE DESCRIPTION

The AM-420 Disk Controller Circuit board provides interface capability between the standard S-100 Bus and the PRIAM Winchester disk drives.

#### 2.3.1 S-100 Bus Interface

The AM-420 circuit board is fully S-100 Bus compatible. The board and its associated disk drives are addressed through the address lines and data is transferred through the standard data-in and data-out ports. The S-100 bus connections are made via the bottom edge connector and are listed in Table 2-2. For a complete description of these signals and their operation in the AM-420, see Section IV of this manual.

#### 2.3.2 Disk Drive Interface

One AM-420 Circuit Board accommodates a maximum of four PRIAM disk drives. Interface connections are made through one cable connecting to all four drives in a daisy-chain (50 pin ribbon cable). Pin 1 on the daisy chain cable is identified by a stripe wire along one edge. Connect pin 1 of the cable to pin 1 of the connector on both the drive and the AM-420. Terminate only the last drive in sequence on the daisy-chain cable using the terminator card provided with the drive.

Interface cabling is shown in Figure 2-1. For further information on operation of the AM-420 interface, see Section IV of this manual.

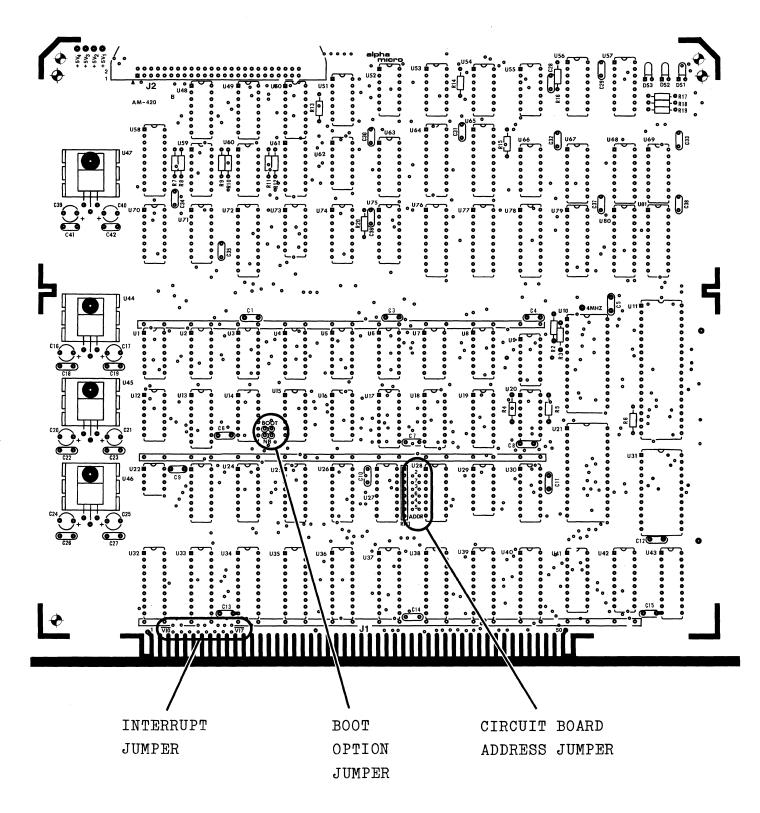

#### 2.4 USER OPTIONS

Some features of the AM-420 can be changed by selection of jumpers at the user's option. Location of the jumper pads is shown in Figure 2-2.

#### 2.4.1 Address Code

Circuit board addressing can be selected at the user's option for any address block (in increments of four) on the address lines AD2-AD7. The standard address (C4 Hex) is contained in etch when the circuit board is manufactured. To change the address, cut the desired etch and leave open for pull up, jumper or ground to generate the desired board address.

#### 2.4.2 Interrupt Lines

Interrupt compatibility for any S-100 bus system is provided with jumpers to any of the vectored interrupt lines VIO-VI7. Attach the jumper wire from the pad located as shown in Figure 2-2 to the desired interrupt line. The standard interrupt line is VI5 which is contained in etch. Cut this jumper to change the interrupt.

#### 2.4.3 Boot Option

The AM-420 contains a bootstrap loader program contained in an internal PROM that the user may utilize. If the user decides to boot from another source, the boot feature must be disabled with a jumper block as shown in Figure 2-2. When using the AM-420 with the AM-100/T CPU, always disable the boot feature. Various boot PROM's exist to allow booting from various backup devices. Consult the Alpha Micro International Support/Services Group for additional details.

#### 2.4.4 AM-100 Preparation

If the Alpha Micro AM-100 CPU is used in the system, the interrupt jumper must be added on the CPU board at VI5 for compatibility with the AM-420.

#### 3.0 INTRODUCTION

This section describes the programming requirements for the AM-420 circuit board. Circuit board addressing, bootstrap loader, and AM-420 internal programming are described for complete system compatibility.

When the AM-420 circuit board is received, it is ready for use with the PRIAM disk drive as described in Section II of this manual. The bootstrap loader and the microcode contained in internal firmware is designed only for these disk drives.

#### 3.1 UNIQUE SOFTWARE CONSIDERATIONS

One of the most important differences between the Winchester drives and lower capacity conventional drives is that the software must accept media flaws. The track and bit densities are so great with these high capacity memory disks that it is impossible to manufacture platters with no media flaws. Therefore, software consideration is made for these faulty blocks.

The technique used to detect and flag these tracks writes to and reads from every track and flags any tracks that are faulty. To accommodate this technique, a new program called "CRT420" is included. New versions of old programs have also been included.

#### 3.2 ADDRESSING

The AM-420 and associated disk drives are addressed through the S-100 bus address lines. The circuit board address is jumper selectable by the jumpers connected to U27. Pull-ups to either +5V or ground jumpers select the board address on S-100 bus address lines AD2-AD7. Address C4 (Hex) is etched in the board to occupy I/O ports C4 and C5 (Hex).

#### 3.3 INITIALIZATION

On initial power-up or reset, the AM-420 goes into a dormant state waiting for initialization. With the boot option enabled, the phantom signal is activated, disabling any phantom controlled memory. The S-100 bus is enabled to access the bootstrap loader contained in the AM-420 PROM.

The 2K x 8 EPROM (U31) contains both the bootstrap routine and the controller microcode. The microcode resides in the first 1K bytes, and the bootstrap routine resides in the second 1K bytes of this PROM. The current bootstrap routine is written in AM-100 code. However, other user codes may be used.

NOTE: If the user code contained in the AM-420 EPROM is changed from the current boot routine, the microcode in the first 1K of memory must be duplicated exactly.

Initialization of the AM-420 is accomplished by writing a zero byte into the AM-420 command register during system initialization. The on-board CPU finishes initialization of the disk controller and releases the Phantom signal.

#### 3.4 COMMAND REGISTER

The command register receives AM-420 commands from the S-100 bus. It is accessed by writing to the selected address. The base addresses are in multiples of four from the first address FFOO (Hex) to FFFC (Hex) in increments of four. A software handshake sequence must be used for the command transfer (see paragraph 3.7). FFC4 (Hex) is the base address when it is shipped from the factory.

There are three basic types of commands used for operation of the AM-420 system; non-disk commands, disk commands and special commands. All three types are described in Figure 3-1.

NON-DISK COMMANDS:

DISK COMMANDS:

- 7. 6F HEX READ SECTOR SIZE

- 8. 7F HEX READ CURRENT CYLINDER 9. 8F HEX READ DRIVE STATUS

Figure 3-1. System Commands

#### 3.5 STATUS REGISTER

The status register is used to determine the current status of the AM-420 controller. It is accessed from the S-100 bus by reading from the user selected base address of the circuit board FFC4 (Hex). The format of the status register is described in Figure 3-2.

#### 3.6 INTERRUPT MODE

The interrupt mode in the AM-420 can be selected by both disk and non-disk commands. If the interrupt mode is selected, the interrupt occurs at the completion of the current AM-420 command. The interrupt must be cleared by the user by setting bit 6=1 of any non-disk command.

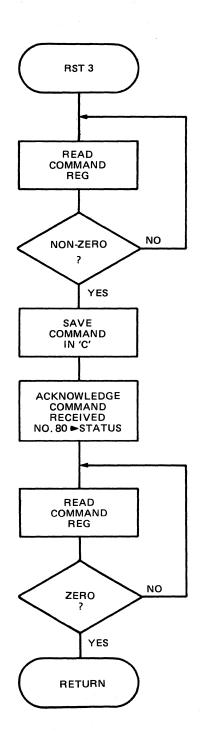

#### 3.7 HANDSHAKE SEQUENCE

A handshaking type interaction is required between the AM-420 circuit board and the CPU any time a command is sent to the AM-420. This handshaking is a software operation that uses bit 7 of the Status Register. Handshake operations proceed in the following sequence:

- 1. A command is sent from the S-100 bus to the Command Register.

- 2. The system software waits for bit 7 of the Status Register to become a 1 to guarantee that the AM-420 has received the command.

- 3. The system software writes a zero into the Command Register to clear the previous command.

- 4. The system software waits until bit 7 of the Status Register becomes a O indicating that the Command Register has been cleared and the command has been executed.

This completes the handshake operation and the program continues.

#### STATUS REGISTER BITS (PORT)

| D7               | D6 | D5 | D4 | D3 | D <b>2</b> | D1 | D0 |  |

|------------------|----|----|----|----|------------|----|----|--|

| CR               |    |    |    |    |            |    |    |  |

| DISK ERROR CODES |    |    |    |    |            |    |    |  |

| 02 | (HEX) | = | DRIVE SEQUENCING UP                |

|----|-------|---|------------------------------------|

| 03 | (HEX) | = | SPECIAL COMMAND ERROR              |

|    |       |   | (UNKNOWN SPECIAL COMMAND RECEIVED) |

| 04 | (HEX) | = | RAM SELF TEST ERROR                |

| 05 | (HEX) | = | DISK NOT READY                     |

| 0B | (HEX) | = | DISK WRITE PROTECTED               |

| 0F | (HEX) | = | DISK FAULT (THE CODE FOR THE FAULT |

|    |       |   | IS LOCATED IN THE DATA REGISTER    |

|    |       |   | (BASE ADDRESS +1)                  |

| 40 | (HEX) | = | READ CRC ERROR                     |

|    |       |   |                                    |

#### DATA REGISTER BITS FOR DISK FAULTS ONLY (PORT + 1)

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CRJ | WPR | FLT | BSY | UNK | SKF | UNK | RDY |

| CRJ | - | COMMAND REJECT  | - | A COMMAND WAS SENT TO THE DRIVE WHILE<br>IT WAS ALREADY PROCESSING ONE |

|-----|---|-----------------|---|------------------------------------------------------------------------|

| WPR | _ | WRITE PROTECT   |   | DRIVE IS WRITE PROTECTED                                               |

| FLT | _ | DRIVE FAULT     | - | DRIVE FAULT                                                            |

| BSY | - | DRIVE BUSY      | - | DRIVE IS BUSY PROCESSING COMMAND                                       |

| SKF | - | SEEK FAULT      | _ | A DRIVE SEEK COMMAND CAUSED AN ERROR                                   |

| RDY |   | 3-5 DRIVE READY | _ | DRIVE IS READY                                                         |

| UNK | _ | UNKNOWN         | _ | BITS MAY BE IN ANY STATE                                               |

Figure 3-2. AM-420 Status Words

Figure 3-3. DMA Buffer Operation

#### 3.8 DMA BUFFER

The DMA buffer is the 1K RAM in the AM-420. All data transfers to or from the disk must pass through this buffer and are handled by the DMA logic.

The DMA buffer is accessed by addressing the AM-420 base address plus one and all data between the AM-420 and the S-100 bus must pass through this single port. No DMA type operations occur between the AM-420 and system memory because they are handled on a programmed basis only. The microcode initializes the buffer and sets the DMA channels for proper operation as shown in Figure 3-3. The Handshake sequence is shown in Figure 3-4, and the data transfer sequence is shown in Figure 3-5.

The starting location within the buffer is determined by bits 4 and 5 of non-disk commands. The RAM base address (D5=0, D4=0) points to the first location in the DMA buffer. The first eight locations of this buffer are used to store information regarding retry count, drive select, and cyclinder/sector/head select.

The data buffer address (D5=0, D4=1) points to the start of 512 data bytes within the buffer and begins at the ninth byte. The user pointer address (D5=1, D4=0) points to a location within the DMA buffer which may be loaded by the user to point to other buffer memory locations for data transfer or the start of user defined microcode. The actual location is the last two bytes of the 1K RAM used for the DMA buffer. The user pointer (D5=1, D4=1) is used to make indirect data transfers or jumps to microcode using the user pointer.

3.8.1 DMA Buffer Operation For Disk Write Transferring data to the DMA buffer and then performing disk write operations takes place as follows:

1. Send DMA write command O6 (Hex) to the AM-420 command register and perform a handshake.

Figure 3-4. Handshake Sequence

6

Figure 3-5. DMA Transfer Sequence

- 2. Send retry count to AM-420 DMA buffer (normally 8).

- 3. Send disk unit number (0-3) to DMA buffer (see note).

- 4. Write physical address plus two bytes of zeros (6 bytes total), sector, head, cylinder (2 bytes).

- 5. Send data (0-512 bytes) to DMA buffer.

- 6. Send disk write command 19 (Hex), or 99 (Hex) for interrupt, to AM-420 command register and perform a handshake.

- 7. Read AM-420 status register and check for zero condition indicating no error.

- 8. Continue with next command if no errors are detected.

NOTE: Disk unit number is sent as a radial select. i.e. Unit 0=0001 binary Unit 1=0010 binary Unit 2=0100 binary Unit 3=1000 binary

3.8.2 DMA Buffer Operation For Disk Read Transferring data from the disk into the DMA buffer and then reading the DMA buffer is performed as follows:

- 1. Send a DMA write command O6 (Hex) to the AM-420 command register and perform a handshake.

- 2. Write retry count into the DMA buffer.

- 3. Write disk unit number (0-3) into the DMA buffer.

- 4. Write physical address plus two bytes of zeros (six bytes total), sector, head, cylinder (2 bytes).

- 5. Write disk read command 15 (Hex), or 95 (Hex) for interrupt, to the AM-420 command register and perform a handshake.

- 6. Read AM-420 status register and check for zero condition indicating that no errors have occurred.

- 7. Assuming that no errors occurred during the disk read, send the DMA read command 12 (Hex), or 92 (Hex) for interrupts to the AM-420 command register and perform the normal handshake.

- 8. Read one byte of data from the DMA buffer and discard it (the first byte is always invalid data).

- 9. Read the valid data (1 to 512 bytes) from the DMA buffer.

#### 3.8.3 Physical Address

The term physical address refers to a four byte block pointing to the cylinder/sector/head within the drive. The user enters these four bytes in the following order:

- 1. Sector (1 byte)

- 2. Head (1 byte)

- 3. Cylinder (2 bytes)

A valid sector number is between zero and the maximum number of sectors around a disk track. A valid head number is between zero and the maximum number of heads in the drive. A valid cylinder number is a two byte number between zero and the maximum number of cylinders within a drive.

## 3.9 RESTORE COMMAND

The restore command is used to reset the disk logic and force the disk head to return to track zero. The user may force a restore command with a disk command 3 (Hex), or the microcode will exercise the restore command on its own following certain errors.

If a disk fault occurs, the microcode attempts one restore and then checks the fault status again. If the fault still exists, the microcode aborts the command operation and reports an error to the CPU.

#### 3.10 STATUS CHECK

The Read and Write Status check commands are used to access specific status information from the disk drive.

The Write Status check command is used to determine if the currently addressed disk is write protected. It does not attempt to actually write any data. If the addressed disk is write protected, error code ØB (Hex) is placed in the status register.

The Read Status check command (if SEEK bit 4 is on) seeks for the currently addressed track and then returns. Data is not read from the disk. If an error occurred, an error code is placed in the status register.

# 3.11 SPECIAL COMMANDS

The third class of commands are special feature commands. There are two types of these commands which will be discussed in paragraphs 3.11.1 and 3.11.2.

- 1. Read Microcode Revision Level This command will return the revision level of the microcode. This is a Type II Command.

- 2. Execute Internal RAM Test This command will execute an internal RAM Test. It takes about 5 seconds to run. This test is run at power up, but not at reset automatically. This is a Type II Command.

- 3. Sequence Up Drive Will sequence up the selected drive (Type I Command).

- 4. Sequence Down Drive Will sequence down the addressed drive (Type I Command).

- 5. Reset Drive Will reset fault on selected drive.

- 6. Read Drive Type Command Will return type of drive currently selected (Type II Command).

- 7. Read Drive Sector Size Will return number of bytes per sector on selected drive (Type II Command)

- 8. Read Current Cylinder Will return position of head on selected drive (Type II Command).

- 9. Read Drive Status Returns drive status on selected drive (Type II).

DWM-00420-00 REV. A00

3.11.1 Type I Commands Type I commands return no information.

3.11.2 Type II Commands Type II commands return information through both the Status Register and the on-board RAM Buffer.

A detailed listing of commands, their usage and how they return data is described in the following paragraphs.

3.11.2.1 Read Revision Level (OF hex)

- 1. Write a OF hex to command port.

- 2. Perform handshake sequence.

- 3. Write a 12 hex to command port.

- 4. Perform handshake.

- 5. Read one byte from the DMA buffer and discard (first byte is invalid data).

- 6. Read three ASCII characters from the DMA buffer. These will be the revision level of the Prom.

3.11.2.2 RAM Test (1F hex)

- Write command and perform handshake. It will take approximately 5-6 seconds for the RAM test and the completion of the handshake. If the test failed, a 4 hex will be returned in the status register at the end of the handshake. If no error, terminate.

- 2. If test fails write 12 hex to command port.

- 3. Perform handshake.

- 4. Read one byte from data port and discard.

- 5. The next four bytes contain:

- a. Error address Lo.

- b. Error address Hi.

- c. Byte Written.

- d. Byte read.

- 3.11.2.3 Sequence Up Drive (2F hex)

- 1. Write a 6 hex to command port.

- 2. Perform handshake.

- 3. Write a zero to data port.

- Write unit number to data port in a radial select fashion, i.e. Unit 0=01

- 5. Write a 2F hex to command port.

- 6. It is recommended that the drive status command be used to wait for the drive to become ready (see paragraph 3.1.2.9).

DWM-00420-00 REV. A00

3.11.2.4 Sequence Down Drive (3F hex)

1. Perform steps 1-4 as in Sequence Up Drive command.

2. Write a 3F hex to command port.

3. Perform handshake.

3.11.2.5 Reset Drive (4F hex)

1. Perform steps 1-4 as in Sequence Up Drive command.

2. Write a 4F hex to command port.

3. Perform handshake.

3.11.2.6 Read Drive ID (5F hex)

1. Perform steps 1-4 as in Sequence Up Drive command.

2. Write a 5F hex to command port.

3. Perform handshake.

4. Write a 12 hex to command port.

5. Perform handshake.

6. Read one byte from data port and discard.

7. Read byte from data port, this byte is the drive ID. Refer to the manual on the particular drive to determine the drive ID.

3.11.2.7 Read Drive Sector Size (6F hex)

- 1. Perform steps 1-4 as in Sequence Up Drive command.

- 2. Write a 6F hex to command port.

- 3. Perform steps 3-6 of Read Drive ID. command.

- 4. The next two bytes read from the data port are the number of bytes per sector stored at Low byte and High byte.

3.11.2.8 Read Current Cylinder (7F hex)

- 1. Perform steps 1-4 as in Sequence Up Drive command.

- 2. Write a 7F hex to command port.

- 3. Perform steps 3-6 as in Read Drive ID. command.

- 4. The next two bytes read from the data port are the current cylinder stored Low byte, High byte.

3.11.2.9 Read Drive Status (8F hex)

- 1. Perform steps 1-4 as in Sequence Up Drive command.

- 2. Write an 8F hex to command port.

- 3. Perform steps 3-6 as in Read Drive ID. command.

DWM-00420-00 REV. A00 3-17

4. Read drive status byte. Bits are as follows:

Bit O = Drive up to speed and ready

Bit 1 = Seek completed

Bit 2 = Seek fault

Bit 3 = Head on cylinder zero

Bit 4 = Drive processing command

Bit 5 = Drive unsafe condition

Bit 6 = Drive write protected

Bit 7 = Command received while busy

## SECTION IV

#### FUNCTIONAL THEORY OF OPERATION

# 4.0 INTRODUCTION

The AM-420 Disk Controller circuit board contains integrated circuit elements for the data processing necessary for the performance of the functions described in Sections I,II and III of this manual. This section describes the functional theory of operation of the circuit board and also provides information for each of the integrated circuit elements.

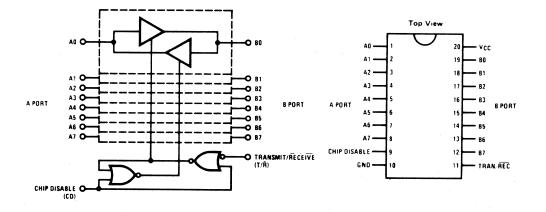

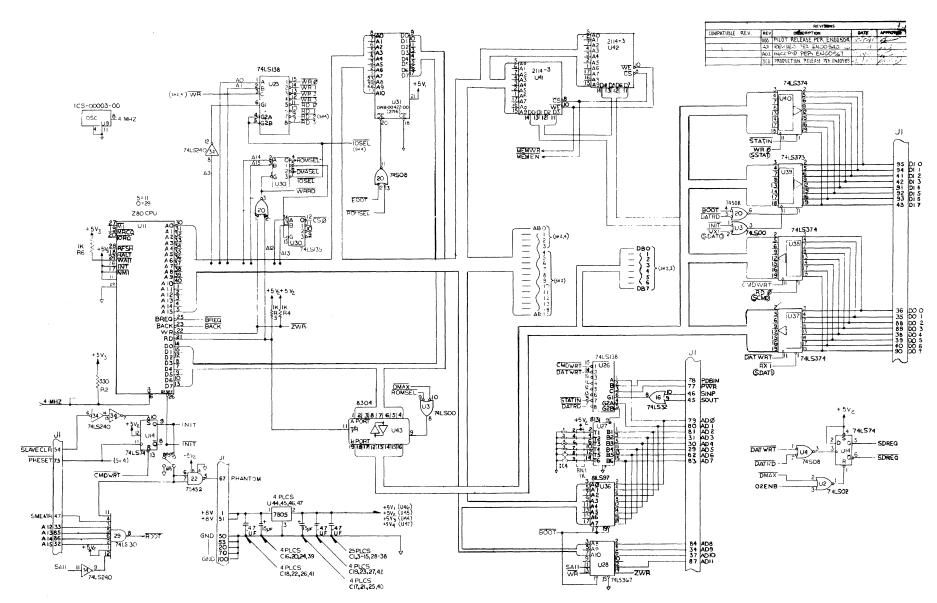

#### 4.1 CIRCUIT BOARD OPERATION

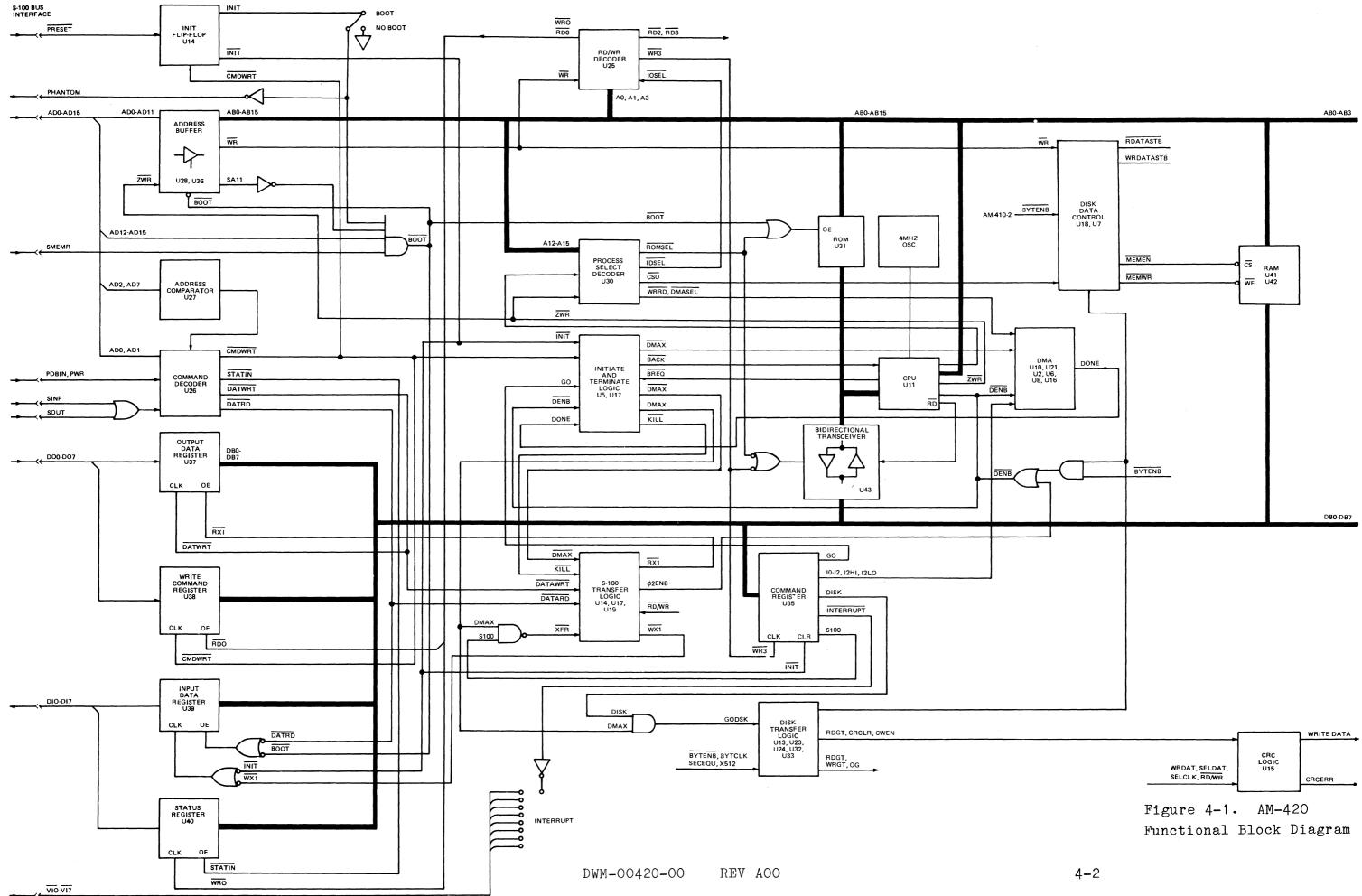

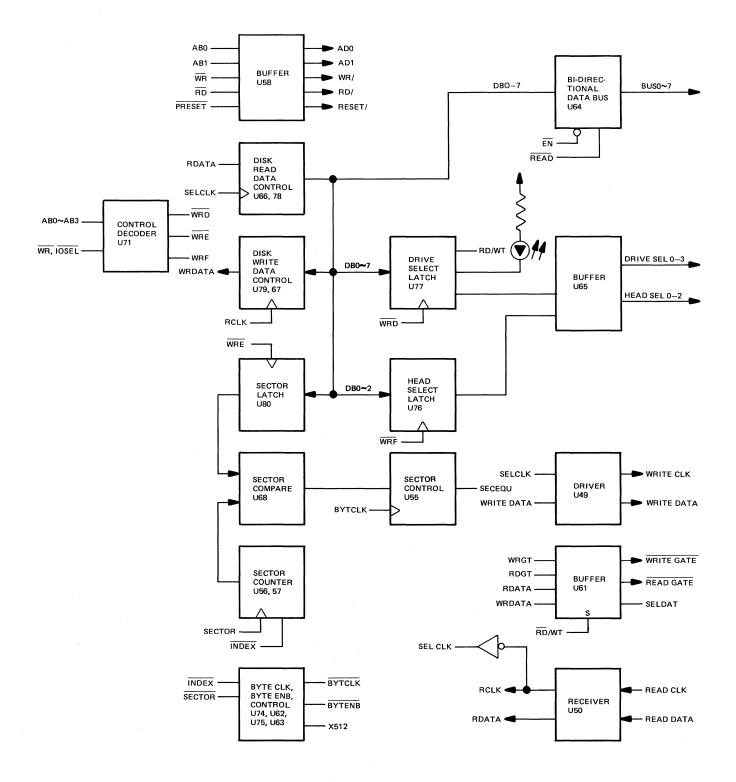

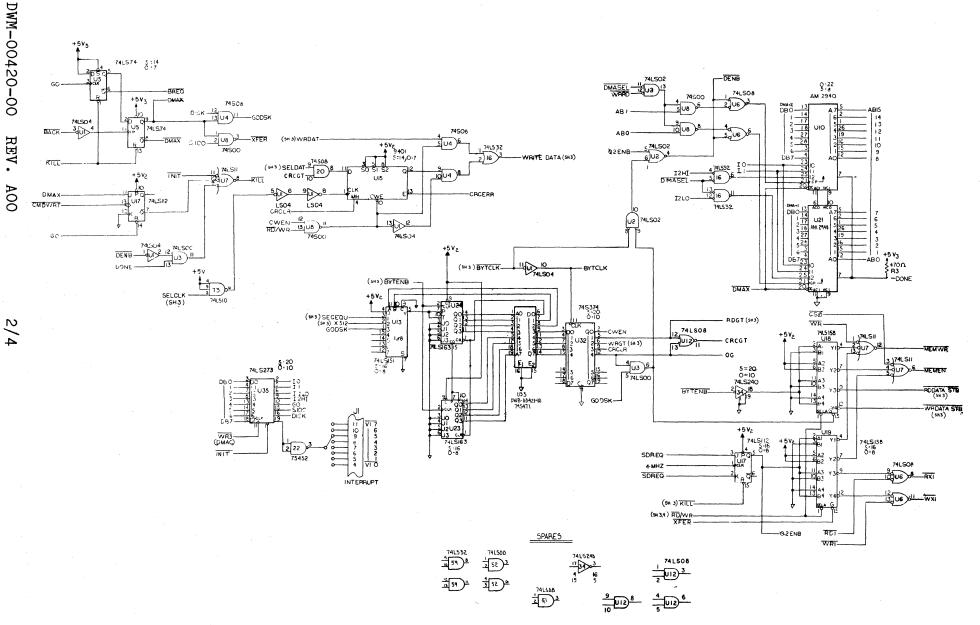

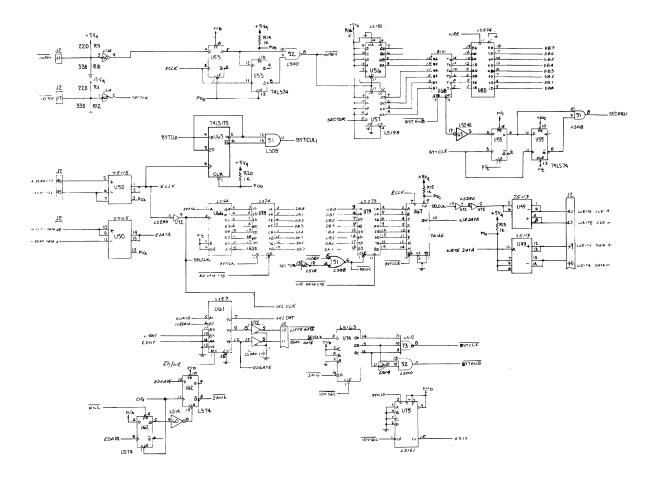

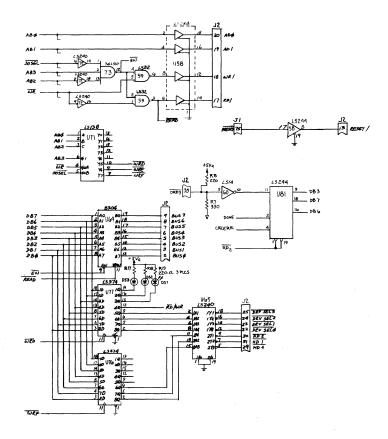

This circuit board provides control and interface capability between the S-100 bus and the PRIAM Winchester hard disk drive. The functional block diagrams of the circuit board are shown in Figures 4-1 and 4-2. The circuit board schematics, parts lists, and component cross reference lists are contained in Section VI of this manual. Table 4-1 contains a list of the signals used in these circuit boards with descriptions of their functions.

Figure 4-2. AM-420 Functional Block Diagram

Table 4-1. AM-420 Signals List

| SIGNAL           | NAME                 | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                                                                                |

|------------------|----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABO-AB15         | Address Bus          |                         | 16 Bit Tri-state address bus. Provides<br>addressing for memory, data exchanges<br>and I/O device exchanges.                                                                               |

| BACK             | Bus Acknow-<br>ledge | SH1                     | CPU module output indicating that the<br>CPU module address bus, data bus, and<br>tri-state control bus signals have been<br>set to their high impedance state.                            |

| BOOT             | Bootstrap<br>Load    | SH1                     | Generated when the bootstrap program has<br>been selected. Enables the ROM, Address<br>Buffer and Input Data Register.                                                                     |

| BREQ             | Bus Request          | SH1                     | CPU module input requesting that the CPU<br>module set its address bus, data bus,<br>and tri-state control bus to the high<br>impedance state.                                             |

| BYTCLK<br>BYTCLK | Byte Clock           | SH3                     | Generated by the Byte Clock Counter at<br>the end of each byte of data written or<br>read. Used to control the Shift/ Load<br>of the write data shift register and<br>disk transfer logic. |

DWM-00420-00 REV. A00

4-4

~ ~

| Table 4-1 (Con't). | AM-420 Signals List |

|--------------------|---------------------|

|--------------------|---------------------|

| SIGNAL     | NAME          | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                                             |

|------------|---------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| <br>BYTENB | Byte Enable   | SH3                     | Byte clock counter output at the same<br>frequency as BYTCLK but twice the<br>duration. Used by the disk transfer<br>logic and disk data control logic. |

| CMDWRT     | Command Write | SH1                     | Output of the Command Decoder to clock<br>command data into the Write Command<br>Register and set up the initiate logic.                                |

| CRCERR     | CRC Error     | SH2                     | Output of the CRC checking module indicating an error in the data.                                                                                      |

| CRCLR      | CRC Clear     | SH2                     | Master reset input to the CRC checking module.                                                                                                          |

Table 4-1 (Con't). AM-420 Signals List

| SIGNAL | NAME                 | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                             |

|--------|----------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------|

| CSO    | Chip Select          | SH1                     | Output of the process select decoder and<br>is one of the signals that enables the<br>RAM.                              |

| CWEN   | Check Word<br>Enable | SH2                     | Generates the enable signal to the CRC<br>checker allowing the check word to be<br>generated and written onto the disk. |

| DATRD  | Data Read            | SH1                     | Command Decoder output to enable the<br>Input Data Register and to generate<br>S-100 transfer signals.                  |

| DATWRT | Data Write           | SH1                     | Command Decoder output to enable the<br>Output Data Register and to generate<br>S-100 transfer signals.                 |

| DENB   | DMA Enable           | SH2                     | Provides clock input to the DMA Address<br>Generator modules. DMA enable begins<br>each cycle of the DMA.               |

|           | , ,      |        |         |                 |

|-----------|----------|--------|---------|-----------------|

| Table 4-1 | (Con't). | AM-420 | Signals | $\mathtt{List}$ |

| SIGNAL            | NAME                 | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                                                         |

|-------------------|----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMASEL DMA Select |                      | SH1                     | Output of the process select decoder to<br>enable the selected DMA address<br>generator. Used to write data into or<br>read data from the DMA address<br>generator. |

| DMAX<br>DMAX      | DMA Access<br>Grant  | · SH2                   | Indicates that the on-board CPU is off<br>the busses and that control of those<br>busses may now pass to the DMA logic.                                             |

| DISK              | Disk Command         |                         | Output of the Command Register to set up<br>a disk operation with DMA Access Grant<br>signal.                                                                       |

| DONE              | Process<br>Command   | SH2                     | Output of the DMA Address Generator<br>indicating completion of the current<br>operation.                                                                           |

| DO-D7             | Data Bus<br>Bits 0-7 | SH1                     | Internal eight-bit tri-state data bus.                                                                                                                              |

•

| SIGNAL           | NAME         | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                                                |

|------------------|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GO<br>           | Go           | SH2                     | Start command output from Command<br>Register. Initiates the transfer of bus<br>control from the on-board CPU to the DMA<br>logic.                         |

| GODSK            | Go Disk      | SH2                     | Initiates disk operations under DMA<br>logic control.                                                                                                      |

| IDXSEC<br>IDXSEC | Sector Reset | SH3                     | Reset command to byte clock counter to reset count to beginning of each sector.                                                                            |

| INDEX            | Disk Index   | SH3                     | Index pulse from disk drive. Occurs<br>once per revolution of the disk to<br>define the beginning of sector zero.                                          |

| INIT<br>INIT     | Initialize   | SH1                     | Internal reset signal generated from S-100 bus PRESET signal.                                                                                              |

| IOSEL            | I/O Select   | SH1                     | Generated from either Read or Write<br>output from the CPU microprocessor when<br>address lines A14 and A15 from the<br>internal address bus are both one. |

# Table 4-1 (Con't). AM-420 Signals List

Table 4-1 (Con't). AM-420 Signals List

| SIGNAL        | NAME                 | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                          |

|---------------|----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| IO, I1        | Instruction<br>Codes | SH2                     | Instruction code inputs to the DMA<br>Address Generator from the Command<br>Register.                                                |

| I2LO,<br>I2HI | Instruction<br>Codes | SH2                     | Instruction code to either the upper<br>eight bits or lower eight bits of the<br>DMA Address generator from the command<br>register. |

| JAMG          | Preset Six           | SH3                     | Presets byte clock counter to a count of six to synchronize the read timing.                                                         |

| KILL          | Terminate            | SH2                     | Terminates the operation in process.                                                                                                 |

| MEMEN         | Memory Enable        | SH2                     | Enables the RAM for read or write operations.                                                                                        |

| MEMWR         | Memory Write         | SH2                     | Controls read or write operations of the RAM. Low = write, High = read.                                                              |

| OG            | Output Gate          | SH2                     | Allows transfer of data into or out of<br>the disk drive.                                                                            |

| Table | 4- | 1 (( | Con' | t). | AM-420 | Signals | List |

|-------|----|------|------|-----|--------|---------|------|

|       |    |      |      |     |        |         |      |

|       |    |      |      |     |        |         |      |

| SIGNAL     | NAME                  | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                        |

|------------|-----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| RDATA      | Read Data             | SH3                     | The data recovered from the disk in NRZ form.                                                                                      |

| RDDATA STB | Read Data<br>Strobe   | SH2                     | Generated by the Disk Data Control logic<br>to transfer a byte of read data from the<br>buffer register to the data bus DBO-DB7.   |

| RDGATE     | Read Transfer<br>Gate | SH3                     | Instructs the disk drive to gate the<br>read data onto the interface. It occurs<br>for any disk transfer cycle (read or<br>write). |

| RDGT       | Read Gate             | SH2                     | Same as RDGATE but only during a read disk transfer (gated by $\overline{RD}/WR$ ).                                                |

| RD/WR      | Read/Write            | SH4                     | Generated from bit 4 of command word to<br>set either disk Read or Write<br>processing.                                            |

| RDO-RD3    | Read O -<br>Read 3    | SH1                     | Read select outputs from the Read/Write<br>decoder to enable read operations.                                                      |

Table 4-1 (Con't). AM-420 Signals List

| SIGNAL         | NAME                    | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                                                                                      |

|----------------|-------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMSEL         | ROM Select              | SH1                     | Generates the output enable of the ROM.                                                                                                                                                          |

| RX1            | Output Data<br>Transfer | SH2                     | Output from the S-100 bus Transfer logic<br>to transfer data from the Output Data<br>Register to the Internal data bus DBO-<br>DB7 (logical OR of RD1 and the read<br>pulse from the DMA logic). |

| SA11           | S-100 Address<br>Bit 11 | SH1                     | Buffered S-100 address bit 11.                                                                                                                                                                   |

| SDREQ<br>SDREQ | S-100 Data<br>Request   | SH2                     | Generated from DATWRT or DATRD for S-100<br>bus data transfers.                                                                                                                                  |

| SECEQU         | Sector Equal            | SH3                     | Pulse output of the Sector Counter and<br>Control logic when the sector counter is<br>equal to the sector latch indicating<br>that the requested sector is under the<br>read/write head.         |

| SIGNAL | NAME              | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                   |

|--------|-------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SECTOR | Sector Pulse      | SH3                     | Sector pulse that occurs at the<br>beginning of each disk sector except<br>sector zero which is marked by the INDEX<br>pulse. |

| SELCLK | Selected<br>Clock | SH3                     | Data Clock                                                                                                                    |

| SELDAT | Selected          | SH3                     | Either read data or write data depending on state of read/write command.                                                      |

| STATIN | Status In         | SH1                     | Output of the command decoder to enable<br>the Status Register.                                                               |

| S100   | S-100 Select      | SH2                     | Command Register output to enable an<br>S-100 bus data transfer.                                                              |

| WR     | Write             | SH1                     | Generated from on-board CPU Write (ZWR)<br>signal.                                                                            |

| WRDATA | Write Data        | SH3                     | Serial write data from the shift register into the CRC generator.                                                             |

DWM-00420-00 REV. A00

| SIGNAL     | NAME                     | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                         |

|------------|--------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| WRDATA STB | Write Data<br>Strobe     | SH2                     | Generated by the Disk Data Control logic<br>to clock the write data from the data<br>bus DBO-DB7 into the write buffer<br>register. |

| WRGT       | Write Trans-<br>fer Gate | SH2                     | Instructs the drive to write data onto<br>the selected surface. It occurs for<br>both read and write disk transfer<br>cycles.       |

| WRITE GATE | Write Gate               | SH3                     | Same as WRGATE but only during a write disk transfer (gated by $\overline{\text{RD}}/\text{WR}$ ).                                  |

| WRITE DATA | Disk Write<br>Data       | SH3                     | Disk write data from the CRC checker<br>logic applied to the write data drivers.                                                    |

| WRRD       | Write-Read               | SH1                     | Read pulse or write pulse from the on-board CPU.                                                                                    |

# Table 4-1 (Con't). AM-420 Signals List

| SIGNAL             | NAME                           | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                                                                                                                                   |

|--------------------|--------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRO-WR3<br>WRD-WRF | WriteO-Write3<br>WriteD-WriteF | SH1                     | Write select outputs from the Read/Write<br>decoder that enable write operations to<br>selected latches.                                                      |

| WX1                | Write 1                        | SH2                     | The logical OR of WR1 and the write pulse from the DMA logic.                                                                                                 |

| XFER               | Transfer                       | SH2                     | Generated from DMAX and S-100 to strobe<br>the S-100 Transfer Logic to transfer<br>data from the Input and Output Data<br>Registers to the internal data bus. |

| X512               | Times 512                      | SH1                     | Used by the DMA logic to indicate when<br>all data has been written or read and<br>that CRC data is next.                                                     |

| ZWR                | CPU Write                      | SH1                     | Indicates that the CPU Module holds<br>valid data to be stored in the addressed<br>memory.                                                                    |

DWM-00420-00 REV. A00

| Table 4- | 1 (Con't | ). AM-42 | 20 Signals | s List |

|----------|----------|----------|------------|--------|

|----------|----------|----------|------------|--------|

| SIGNAL | NAME                | SCHEM PAGE<br>OF SOURCE | DESCRIPTION                                              |

|--------|---------------------|-------------------------|----------------------------------------------------------|

| 4 MHZ  | 4 MHz Clock         | SH1                     | 4 MHz clock from oscillator U9.                          |

| 02ENB  | S-100 Trans-<br>fer | SH2                     | Clock signal for every cycle of the S-100 data transfer. |

The major processing components of this board are the CPU microprocessor (U11) and the DMA Address Generator (U10 and U21). The ROM (U31) contains the bootstrap load routine and also contains the microcode necessary for operation of the microprocessors.

#### 4.1.1 Power-Up Reset

On initial power-up, the circuit board is in a dormant state waiting for initialization. The PRESET signal from the S-100 bus sets the INIT flip-flop U14 to activate the PHANTOM signal to disable any main memory under phantom control and to enable the bootstrap gate. INIT generally resets logic on the circuit board to initial conditions.

#### 4.1.2 Addressing

Address data is received from the S-100 bus on address lines ADO-AD15. This address data is transferred to the internal address bus during boot loading for use by the controllers and memories within the circuit board and is also used for direct addressing of the circuit board. Buffers on U28 and U36 gate the addresses to the internal bus when enabled by bootstrap signal BOOT.

Address lines AD2-AD7 are wired directly to comparator U27 for circuit board addressing. The other inputs come from circuit board etch or jumper wires to either +5V pull-ups or ground to produce the desired address. The output of the comparator U27 is asserted when the data from the address lines compare with the address of the AM-420. This generates read and write signals from decoder U26. The address in etch is C4 (Hex) and other addresses can be selected as described in Section II.

## 4.1.3 CPU Output

CPU output data is transmitted to the AM-420 for circuit board control and data transfer by the S-100 bus data and control lines. Data is received by the AM-420, by the Output Data Register U37, and the Write Command Register U38. The Input to these data registers comes from the S-100 bus data lines D00-D07 and the output, when enabled, goes to internal data bus DB0-DB7.

# 4.1.3.1 Command Data

Data from the S-100 bus data lines is clocked into the Write Command Register by Command Write signal CMDWRT from the Command Decoder U26. This takes place when address lines ADO and AD1 are zero and I/Ooutput signal SOUT from the S-100 bus is asserted. Signal CMDWRT also resets the INIT flip-flop U14 and resets the initiate logic.

When the CPU microprocessor issues a write command (ZWR) and address lines AB14 and AB15 from the internal address bus are both one, IOSEL is asserted to enable the Read/Write decoder U25. Signal ZWR is also applied to buffer U28 to generate WR which is an input to the Read/Write decoder. When address bits ABO and AB1 from the internal bus are zero, the RDO output from the Read/Write decoder transfers the contents of the write command register to the internal data bus.

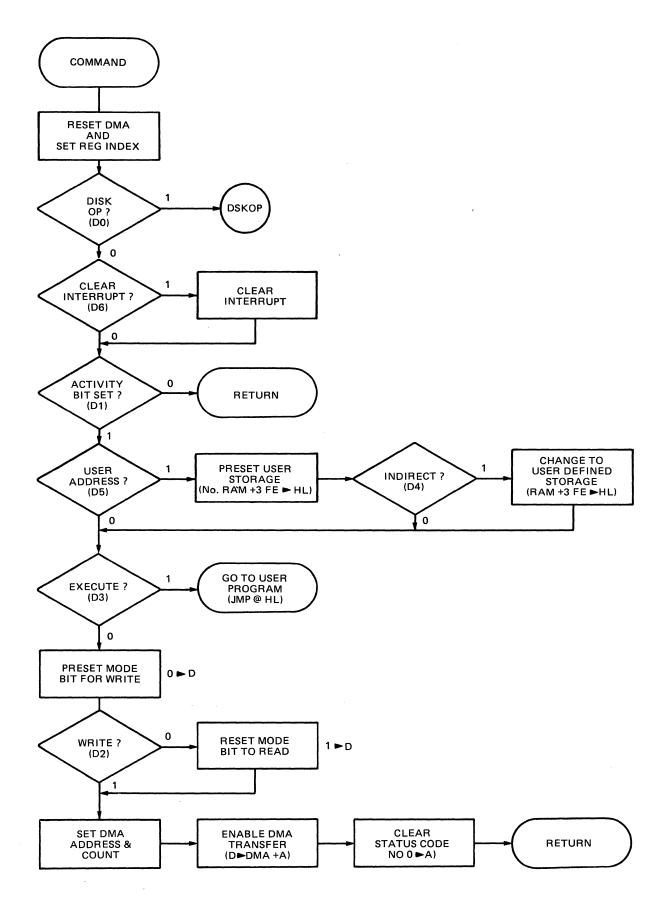

#### 4.1.3.2 Command Types

The non-disk commands issued to the AM-420 are used for control and operation of the logic internal to the circuit board. The bit functions are listed in Table 4-2 and the commands are listed in Table 4-3. Disk Commands are used to control the disk drive and access status information from the drive. Disk command bit functions are listed in Table 4-4, and disk command codes are listed in Table 4-5.

# Table 4-2. Non-Disk Command Bits

| ·      | * • •      |                                                                     |                  |                  |                                                                               |  |  |

|--------|------------|---------------------------------------------------------------------|------------------|------------------|-------------------------------------------------------------------------------|--|--|

| BIT    | NAME       |                                                                     |                  |                  | FUNCTION                                                                      |  |  |

| 0<br>1 | 0<br>1     |                                                                     |                  |                  | ates non-disk command<br>ity Bit.                                             |  |  |

| 2      | R/W        | Read/Write O=read (AM-420 to CPU),<br>1= write (CPU to AM-420).     |                  |                  |                                                                               |  |  |

| 3      | FN         | Command Function O=transfer 1=execute                               |                  |                  |                                                                               |  |  |

| 4<br>5 | BUF<br>DMA | Location in DMA buffer where data is to<br>be retrieved or stored.* |                  |                  |                                                                               |  |  |

| 6      | CLR        | Clear current interrupt O=nop 1=clear                               |                  |                  |                                                                               |  |  |

| 7      | IE         | Interrupt Enable O=disable 1=enable                                 |                  |                  |                                                                               |  |  |

|        |            | *                                                                   | В                | it               | Location                                                                      |  |  |

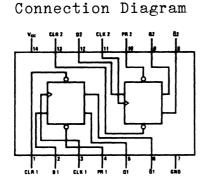

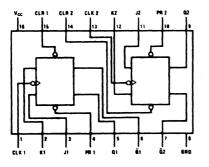

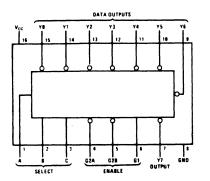

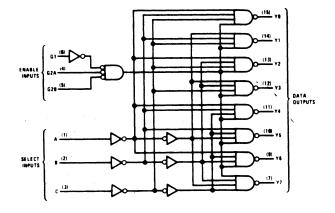

|        |            |                                                                     | 5                | 4                |                                                                               |  |  |