# 1986 Proceedings FALL JOINT COMPUTER CONFERENCE

November 2-6, 1986—INFOMART®—Dallas, Texas Sponsored by **ACM and Computer Society of the IEEE**

## 1986 Proceedings FALL JOINT COMPUTER CONFERENCE

November 2-6, 1986—INFOMART<sup>®</sup>—Dallas, Texas Sponsored by **ACM and Computer Society of the IEEE**

Harold S. Stone, Proceedings Editor and Program Chairman Stanley Winkler, Conference Chairman

> Computer Society Order Number 743 Library of Congress Number 86-81582 IEEE Catalog Number 86CH2345-7 ACM Order Number 401860 ISBN 0-8186-0743-2

(acm) Association for Computing Machinery

AND ELE

RICAL COMP NEERS INC SOCIE PRESS

SOCIETY D

The papers appearing in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and are published as presented and without change, in the interests of timely dissemination. Their inclusion in this publication does not necessarily constitute endorsement by the editors, IEEE Computer Society Press, or the Institute of Electrical and Electronics Engineers, Inc.

> Published by IEEE Computer Society Press 1730 Massachusetts Avenue, N.W. Washington, D.C. 20036-1903

> > COVER DESIGNED BY JACK I. BALLESTERO

IEEE Computer Society Order Number 743 Library of Congress Number 86-81582 IEEE Catalog Number 86CH2345-7 ACM Order Number 401860 ISBN 0-8186-0743-2 (paper) ISBN 0-8186-4743-4 (microfiche) ISBN 0-8186-8743-6 (case)

#### Prices (1986) ACM or IEEE Members: \$60.00 prepaid All others: \$120 prepaid

Additional copies of the 1986 Proceedings may be ordered prepaid from:

ACM Order Department Post Office Box 64145 Baltimore, MD 21264

IEEE Service Center 445 Hoes Lane Piscataway, NJ 08854 Computer Society of the IEEE Post Office Box 80452 Worldway Postal Center Los Angeles, CA 90080

Computer Society of the IEEE Ave. de la Tanche 1160 Brussels, Belgium

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 29 Congress Street, Salem, MA 01970. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For other copying, reprint or republication permission, write to Director, Publishing services, IEEE, 345 E. 47 St., New York, NY 10017. All rights reserved. Copyright © 1986 by The Institute of Electrical and Electronics Engineers, Inc.

This 1986 edition of the proceedings of the Fall Joint Computer Conference, published on the 50th anniversary of the writing of the paper

"On Computable Numbers, with an Application to the Entscheidungs Problem,"

is dedicated to the memory of

## ALAN M. TURING

who wrote:

"My contention is that machines can be constructed which will simulate the behaviour of the human mind very closely. They will make mistakes at times, and at times they may make new and very interesting statements, and on the whole the output of them will be worth attention to the same sort of extent as the output of a human mind."

How close are we to his vision today?

## **Conference Committee**

#### **1986 Fall Joint Computer Conference**

Stanley Winkler Conference Chairman

Harold S. Stone Program

David C. Wood Finance

Harry M. Kepner Operations

Carla Elfeld Samuel Fleming M. Alex Harkins Deanna Kirchoff. Charlotte Lin Peter Maverick George Weinreich

Dennis J. Frailey Registration and Conference Advisor

Bruce Anderson Publications

La Joyce Doran

William Lively Resources

Rosetta L. Winkler Conference Secretary Joan W. Golden

## **FJCC Steering Committee**

Dick B. Simmons Chairman James H. Aylor Roy L. Russo President, Computer Society of the IEEE William Habingreither Wendy Chin

Toni Shetler Professional Development

Karen Duncan Helen Takacs Judi Paulos Kermit Paulos Beth Stinnette **Executive Education Coordinator**

David M. Hyatt Industrial Liaison A.T. Landberg

Alex A.J. Hoffman Society Liaison

Karen Duncan Conference Management

Thomas A. D'Auria Special Events

Adrian J. Basili Technical Advisor

Tim Durkin Exhibits Cynthia Cegelski

Lynda Rosenthal

Seymour J. Wolfson Past Chairman James Iverson

Paul W. Abrahams President, Association for Computing Machinery James Adams Pegotty Cooper

## **Program Committee**

## **1986 Fall Joint Computer Conference**

Harold S. Stone, **Program Chairman** Maureen Ferraro, **Executive Program Coordinator**

Lionel Baldwin Laszlo Belady Domenico Ferrari Norman Gibbs C. Lee Giles William Howden Kai Hwang Laurel Kaleda Elaine Kant John Kender David Kincaid Kenneth Kolence Jerome Kurtzberg Stephen Lavenberg Tony Marsland John Meyer

Cleve Moler Ryoichi Mori Kenji Naemura Anil Nigam Arthur Parry Richard Paul James Peterson Paul Purdom David Rine Daniel Siewiorek Jack Stankovic John White Robert Wilensky Michael Willett Michael Wozny

## Referees

## **1986 Fall Joint Computer Conference**

Tokoro, M. Tokuda, H. Tomita, S. Townsley, D. Tripathi, S. Tsujii, J. Turn, R. Valduriez, P. Varman, P.J. Vernon, M.K. Waddle, V. Wagner, K. Wah, B. Wang, H. Wang, P. Whang, K.Y. White, J.R. Willett, M. Williamson, C. Wolberg, G. Wong, M. Wozny, M. Yemini, Y. Yokota, M. Yonezawa, A. Young, H. Yuba, T. Zahorjan, J. Zicari, R.

| Adams, S.David, R.HyAgarwal, R.De Jong, K.IbAgarwal, V.K.Driscoll, J.R.IhAida, H.Duchamp, D.IslAikens, J.Eager, D.L.IslAllen, P.Ezzat, A.IyAlonso, R.Freitas, R.JhAmmann, A.Ferrari, D.JoBabaoglu, O.Friedman, D.KaBern, Y.Friedman, M.KaBenjamin, J.Furthgott, D.KaBernett, B.T.Gagliardi, R.KiBerghel, H.Gangopadhyay, D.KjBirman, K.Garcia-Molina, H.KaBose, P.Gerasch, T.KaBrandenberg, J.Gilbert, R.KaCarey, M.Goto, A.KaCarlsson, G.E.Graham, D.KaChen, C.Y.Hansen, W.J.KaChikayama, T.Hassner, D.LeCook, J.Hayes, J.P.MCoopeland, G.Hillyer, B.MCox, G.Homan, T.M | wang, K.T.<br>prahim, H.<br>hara, H.<br>higuro, M.<br>hizuka, M.<br>ver, B.R.<br>ha, N.<br>phnson, M.S.<br>aneda, Y.<br>awaoka, T.<br>ender, J.<br>ing, R.<br>jell, B.<br>obayashi, S.<br>okubu, A.<br>oo, R.<br>orth, H.<br>rishna, M.<br>ung, H.T.<br>uper, G.<br>urose, J.<br>andwehr, C.E.<br>ee, I.<br>IcCall, T.<br>IcCluskey, E.J.<br>Ialek, M.<br>Ialhotra, A. | Melamed, A.<br>Mitra, D.<br>Mirchandaney, R.<br>Mok, A.<br>Moler, C.<br>Molina, H.G.<br>Morita, Y.<br>Mourad, S.<br>Mullarkey, P.<br>Muraoka, Y.<br>Murthy, S.<br>Nataraj, K.S.<br>Newman, T.<br>Neumann, P.G.<br>Ng, Y.W.<br>Nicola, V.<br>Nitta, K.<br>Norris, E.<br>Okada, Y.<br>Okugawa, S.<br>Omori, K.<br>O'Neill, D.M.<br>Patel, J.<br>Preparata, F.P.<br>Ramamritham, K.<br>Rashid, R.<br>Reddy, S.M. | Robinson, J.<br>Rosenberg, A.L.<br>Sabbah, D.<br>Sakai, K.<br>Sanders, W.H.<br>Sarin, S.<br>Sauer, C.H.<br>Scott, D.<br>Sekino, A.<br>Seth, S.C.<br>Sevick, K.C.<br>Sha, L.<br>Shibayama, E.<br>Shibayama, E.<br>Shin, K.G.<br>Siewiorek, D.P.<br>Silberschatz, A.<br>Singh, A.<br>Smith, E.<br>Stankovic, J.<br>Stephenson, P.<br>Stewart, B.<br>Stone, H.S.<br>Sturgis, H.<br>Suwa, M.<br>Sylvester, J.<br>Tamaki, H.<br>Tanaka, Y.<br>Toda, M. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## Table of Contents

| Dedication to Alan M. Turing                                |

|-------------------------------------------------------------|

| Conference Committeev                                       |

| Program Committee                                           |

| Referees                                                    |

| FJCC '86—A Conference for the Profession—Stanley Winklerxxi |

| FJCC '86—A New Beginning—Harold S. Stone                    |

| Conference-at-a-Glancexxvi                                  |

## EDUCATION ARENA

| TRACK ED-1: New Te<br>Technological Univers | chnology in Education. Track Chair: Lionel Baldwin, President, National ity    |

|---------------------------------------------|--------------------------------------------------------------------------------|

| Session 1 - Educa<br>Technological U        | tion by Satellite. Session Chair: Lionel Baldwin, National<br>Jniversity (1-B) |

| AMCEE Prog                                  | ramming for Computer Professionals, J. T. Fitch, AMCEE                         |

| *                                           | er Engineering Program, F. J. Mowle, D. G. Meyer, and P. H.<br>due University  |

| NTU Comput                                  | er Science Program, S. Sahni, University of Minnesota                          |

| Session 2 - Comp<br>Consultant (4-E         | uters in Education. Session Chair: Arthur Melmed,                              |

|                                             | at Carnegie Mellon, B. A. Sherwood, Carnegie Mellon                            |

|                                             | oring Systems for Professionals, A. M. Lesgold, University of                  |

## SOFTWARE SYSTEMS ARENA

.

| TRACK SS-1: Software Engineering. Track Chair: Laszlo Belady, MCC                                                       |

|-------------------------------------------------------------------------------------------------------------------------|

| Session 1 - Object-Oriented Software. Session Co-Chairs: Clarence Ellis and<br>Ted Biggertsaff, MCC (2-C)               |

| An Approach to Type Safety in a Traits System, G. Curry, Sequent Computer Systems 25                                    |

| Object-Oriented Programming for Macintosh Applications, L. Rosenstein,<br>K. Doyle, and S. Wallace, Apple Computer, Inc |

| Classes versus Prototypes in Object-Oriented Languages, A. H. Borning,<br>University of Washington                      |

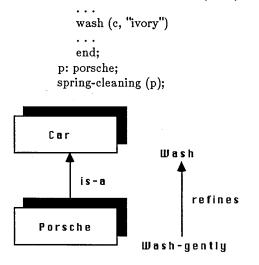

| Why Properties Are Objects or Refinements of "is-a," S. B. Zdonik, Brown         University                             |

| TRACK SS-4: Programming Languages, Compilers and Environments. Track<br>Chair: John R. White, Xerox Corporation                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 5 - Programming Languages. Session Chair: John White, Xerox<br>Corporation (7-B)                                                                                                                  |

| A Systolic Parsing Algorithm for a Visual Programming Language, A. W.<br>Bojanczyk and T. D. Kimura, Washington University                                                                                |

| Learning, Research and the Graphical Representation of Programming, R. P.<br>Taylor, N. Cunniff, and M. Uchiyama, Columbia University                                                                     |

| Command Language Support for Application Programs, C. C. Genet,<br>Grumman Data Systems Corp                                                                                                              |

| ARTIFICIAL INTELLIGENCE ARENA                                                                                                                                                                             |

| TRACK AI-2: Computer Vision. Track Chair: John Kender, Columbia University                                                                                                                                |

| Session 2 - Model-Based High-Level Vision. Session Chair: John Kender,<br>Columbia University (5-1)                                                                                                       |

| Survey of Image Quality Measurements, I. E. Abdou and N. J. Dusaussoy,<br>University of Delaware                                                                                                          |

| A Spatial Knowledge Structure for Image Information Systems Using<br>Symbolic Projections, S-K. Chang and E. Jungert, University of Pittsburgh<br>and FFV Elektronik AB                                   |

| Document Image Understanding, S. N. Srihari, State University of of New<br>York at Buffalo                                                                                                                |

| TRACK AI-3: Robotics. Track Chair: Richard Paul, University of Pennsylvania                                                                                                                               |

| Session 1 - Robot Perception. Session Chair: Takeo Kanade, Carnegie Mellon<br>University (6-I)                                                                                                            |

| Living in a Dynamic World, R. L. Andersson, AT&T Bell Laboratories                                                                                                                                        |

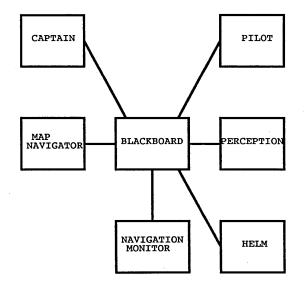

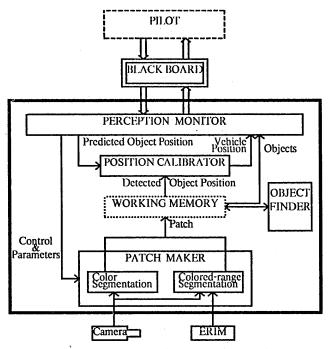

| <ul> <li>CMU Sidewalk Navigation System: A Blackboard-Based Outdoor</li> <li>Navigation System Using Sensor Fusion with Colored-Range Images, Y. Goto,</li> <li>K. Matsuzaki, I. Kweon, and T.</li> </ul> |

| Obatake, Carnegie Mellon University                                                                                                                                                                       |

| Carnegie Mellon University                                                                                                                                                                                |

| Session 2 - Task-Level Robot Programming. Session Chair: Tomas Lozano-<br>Pérez, MIT (7-G)                                                                                                                |

| Automatic Grasp Planning: An Operation Space Approach, M. T. Mason and<br>R. C. Brost, Carnegie Mellon University                                                                                         |

| Planning Stable Force-Closure Grasps, VD. Nguyen, MIT                                                                                                                                                     |

| Off-Line Planning for On-Line Object Localization, T. Lozano-Pérez and<br>W. E. L. Grimson, MIT                                                                                                           |

| Session 3 - Real-Time Robot Programming. Session Chair: Russell Taylor,<br>IBM T. J. Watson Research Center (8-G)                                                                                         |

| AML/X: A Programming Language for Design and Manufacturing, L. R. Nackman, M. A. Lavin, R. H. Taylor, W. C. Dietrich, Jr., and D. D.                                                                      |

| Grossman, IBM T. J. Watson Research Center                                                                                                                                                                |

|     | The Meglos User Interface, R. D. Gaglianello and H. P. Katseff, AT&T Bell                                                                                                                                                   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Laboratories                                                                                                                                                                                                                |

| • . | A Robot Force and Motion Server, H. Zhang and R. P. Paul, University of<br>Pennsylvania                                                                                                                                     |

|     | CK AI-4: Rule-Based Systems. Track Chair: David C. Rine, George Mason<br>iversity                                                                                                                                           |

|     | Session 1 - Software Engineering Methods for Rule-Based Systems. Session<br>Chair, David C. Rine, George Mason University (5-C)                                                                                             |

|     | Software Engineering for Rule-Based Software Systems, R. J. K. Jacob and<br>J. N. Froscher, Naval Research Laboratory                                                                                                       |

|     | Session 3 - Rule-Based Models and Applications. Session Chair:<br>Elaine Kant, Schlumberger Doll Research Center (8-C)                                                                                                      |

|     | An Organizational Framework for Comparing Adaptive Artificial<br>Intelligence Systems, T. A. Blaxton and B. G. Kushner, BDM Corp                                                                                            |

|     | An Object/Task Modeling Approach Based on Domain Knowledge and<br>Control Knowledge Representation, Q. Chen, Research Institute of<br>Surveying and Mapping, Beijing China                                                  |

|     | A Plant Intelligent Supervisory Control Expert System, M. Ali and E. S.<br>Washington, University of Tennessee Space Institute                                                                                              |

|     | <ul> <li>A Knowledge-Based Layout Design System for Industrial Plants, K.</li> <li>Yoshida, Y. Kobayashi, Y. Ueda, Hitachi, Ltd., and H. Tanaka, S. Muto, and</li> <li>J. Yoshizawa, Tokyo Electric Power Co. Inc</li></ul> |

|     | Session 4 - Prolog and Frame-Based Methods. Session Chair: Kenneth De<br>Jong, George Mason University (9-C)                                                                                                                |

|     | A Logic Programming Approach to Frame-Based Language Design, H-H.<br>Chen, I-P. Lin, and C-P. Wu, National Taiwan University                                                                                                |

|     | Interfacing Prolog to Pascal, K. Magel, North Dakota State University                                                                                                                                                       |

|     | Knowledge-Based Optimization in Prolog Compiler, N. Tamura, IBM Japan,<br>Ltd                                                                                                                                               |

|     | CK AI-5: Natural Language Processing. Track Chair: Robert Wilensky,<br>iversity of California at Berkeley                                                                                                                   |

|     | Session 1 - User Interfaces. Session Chair: Robert Wilensky, University of California<br>at Berkeley (1-I)                                                                                                                  |

|     | Communication with Expert Systems, K. R. McKeown, Columbia<br>University                                                                                                                                                    |

|     | Language Analysis in Not-So-Limited Domains, P. S. Jacobs, General<br>Electric Corporate Research and Development                                                                                                           |

|     | Providing Expert Systems with Integrated Natural Language and Graphical<br>Interfaces, P. J. Hayes, Carnegie Group, Inc                                                                                                     |

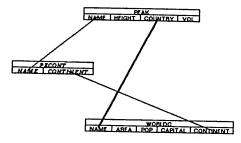

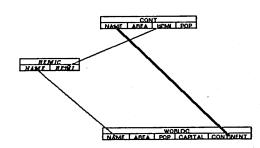

|     | TEAM: An Experimental Transportable Natural-Language Interface, P.<br>Martin, D. E. Appelt, B. J. Grosz, and F. Pereira, SRI International                                                                                  |

|     | Martin, D. E. Appen, D. J. Glosz, and T. Petena, SKI international                                                                                                                                                          |

•

## SUPERCOMPUTING ARENA

| TRACK SC-1: Parallel Computation. Track Chair: Kai Hwang, University of<br>Southern California                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 1 - Parallel Processing for AI. Session Chair: Kai Hwang, University of Southern California (1-D)                                                                                                         |

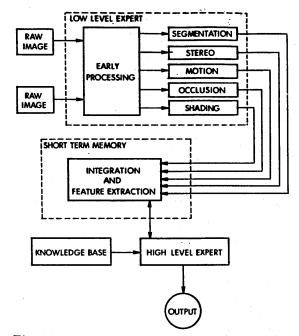

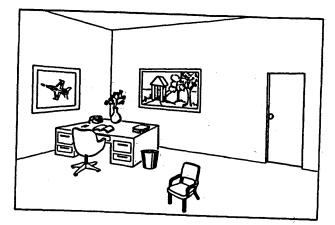

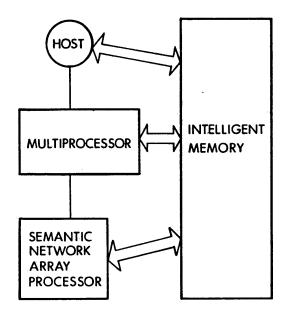

| Parallel Processing of a Knowledge-Based Vision System, D. I. Moldovan<br>and C. I. Wu, University of Southern California                                                                                         |

| A Fault Tolerant, Bit-Parallel, Cellular Array Processor, S. G. Morton, ITT<br>Advanced Technology Center                                                                                                         |

| <ul><li>Implementation of Parallel Prolog on Tree Machines, H. Miura, Fujitsu Ltd.,</li><li>M. Imai, Toyohashi University, M. Yamashita, Hiroshima University, and</li><li>T. Ibaraki, Kyoto University</li></ul> |

| Optimal Granularity of Parallel Evaluation of AND Trees, G-J. Li and B. W.<br>Wah, University of Illinois at Urbana-Champaign                                                                                     |

| Session 2 - Parallel Algorithms for Supercomputing. Session Chair: Benjamin<br>Wah, University of Illinois at Urbana-Champaign (2-D)                                                                              |

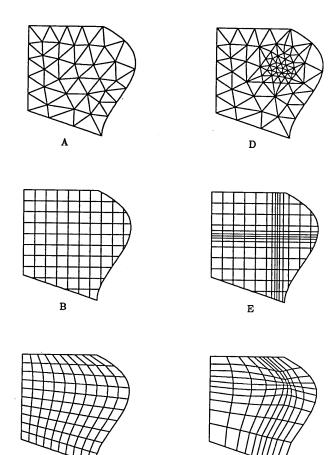

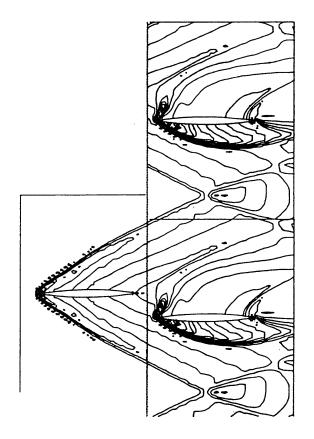

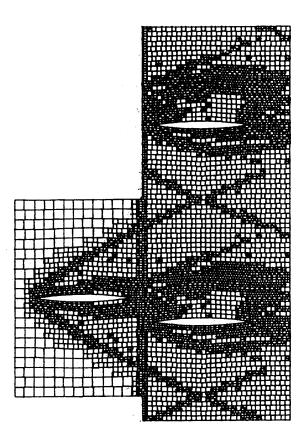

| Parallel Preprocessing and Postprocessing in Finite-Element Analysis on a<br>Multiprocessor Computer, P. S. Tseng, Carnegie Mellon University, and<br>K. Hwang, University of Southern California at Los Angeles  |

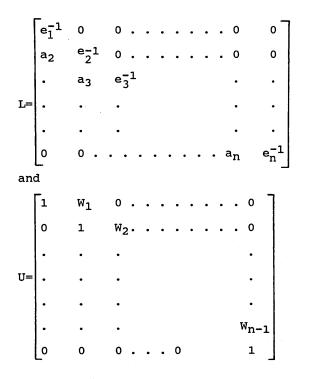

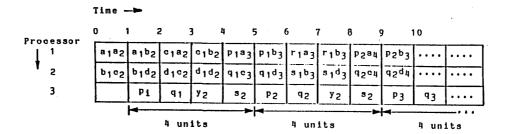

| A New Class of Parallel Algorithms for Solving Linear Tridiagonal Systems,<br>S. Lakshmivarahan and S. K. Dhall, University of Oklahoma                                                                           |

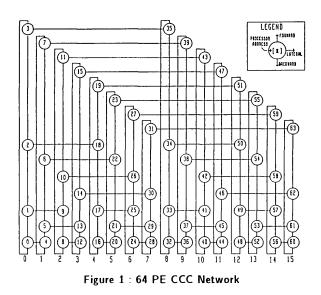

| A Parallel Computer Based on Cube-Connected Cycles for Wafer-Scale<br>Integration, M. J. Chung, E. J. Toy, and A. Gupta, Rensselaer Polytechnic<br>Institute                                                      |

| TRACK SC-3: Multiprocessors. Track Chair: Daniel Siewiorek, Carnegie Mellon<br>University                                                                                                                         |

| Session 1 - Multiprocessors I. Session Chair: Zary Segall, Carnegie Mellon<br>University (4-D)                                                                                                                    |

| MUPPET - A Programming Environment of Message-Based<br>Multiprocessors, H. Muehlenbein, F. Limburger, S. Streitz, and S. Warhaut,<br>GMD, West Germany                                                            |

| Distributed Functions Allocation for Reliability and Delay Optimization, S.<br>Hariri and C. S. Raghavendra, University of Southern California at Los                                                             |

| Angeles                                                                                                                                                                                                           |

| Japan                                                                                                                                                                                                             |

| Microelectronics and Computer Technology Corporation (5-D)                                                                                                                                                        |

| Evon: An Extended von Neumann Model for Parallel Processing, WM.<br>Ching, IBM T. J. Watson Research Center                                                                                                       |

| Optimal Code Generation for Expressions on Super Scalar Machines, P.<br>Bose, IBM T. J. Watson Research Center                                                                                                    |

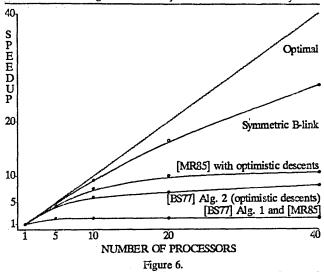

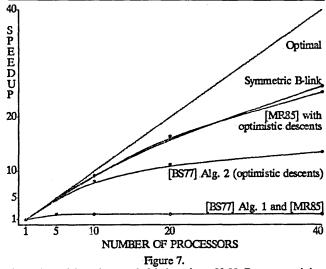

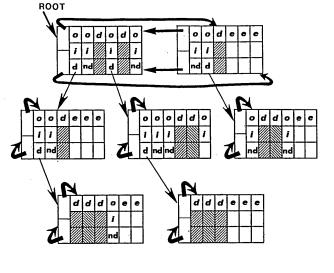

| A Symmetric Concurrent B-Tree Algorithm, V. Lanin and D. Shasha,<br>Courant Institute, New York University                                                                                                        |

|   | Session 3 - High-Speed Techniques. Session Chair: William Brantley, IBM T.<br>J. Watson Research Center (6-D)                                                                                 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

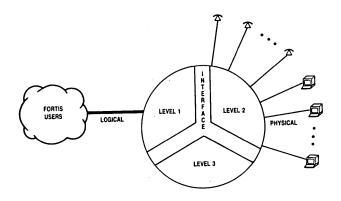

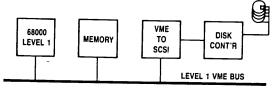

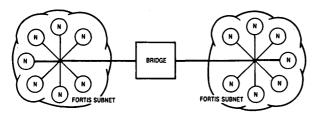

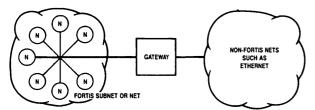

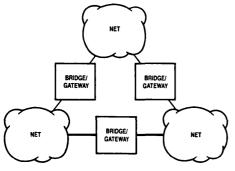

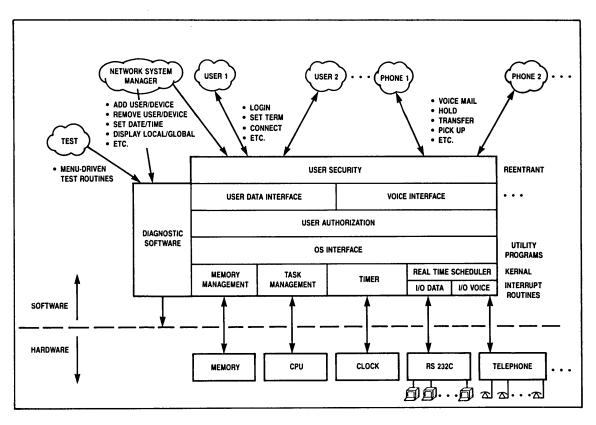

|   | Architecture of a Fiber Optics Based Distributed Information Network<br>FORTIS: Local Area Network, P. C. Barr, Northeastern University, and<br>S.G. Krishnamoorthy, Framingham State College |

|   | On the Design of Fault-Tolerant Systolic Arrays with Linear Cells, C. Y.<br>Chen and J. A. Abraham, University of Illinois at Urbana                                                          |

|   | The Design and Development of a Very High Speed System BusThe<br>Encore Multimax Nanobus, D. J. Schanin, Infinity Systems, Inc                                                                |

| Т | RACK SC-4: Optical Computing. Track Chair: C. Lee Giles, AFOSR/NE                                                                                                                             |

|   | Session 1 - Optical Computers. Session Chair: John Caulfield, University of Alabama (1-A)                                                                                                     |

|   | Optoelectronic Devices for Computing, F. J. Leonberger, UT Research                                                                                                                           |

|   | Center                                                                                                                                                                                        |

|   | Corporation                                                                                                                                                                                   |

|   | Session 2 - New Directions in Optical Computing. Session Chair: C. Lee Giles,<br>AFOSR/NE (2-A)                                                                                               |

|   | Optical Realizations of Neural Network Models, D. Psaltis, C.I.T                                                                                                                              |

|   | Optical Symbolic Computing, B.G. Kushner, BDM Coproration, and J. Neff, DARPA                                                                                                                 |

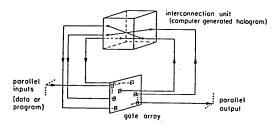

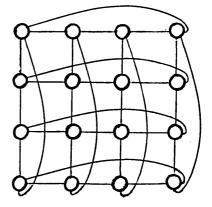

|   | An Extendible Optically Interconnected Parallel Computer, A. D. McAulay,<br>Texas Instruments, Inc                                                                                            |

|   | Session 3 - Optical Interconnections for Computing. Session Chair: John Neff,<br>DARPA/DSO (3-A)                                                                                              |

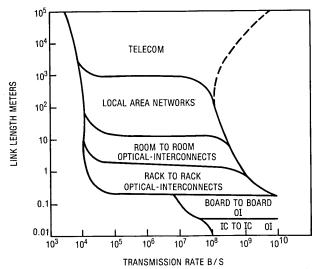

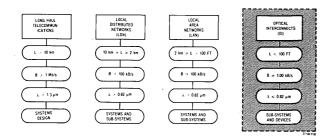

|   | Optical Interconnect Technology Developments, L. D. Hutcheson,<br>CyberOptics Corporation                                                                                                     |

|   | Optical Interconnection Systems for Digital Parallel Processors, A. A.<br>Sawchuk, University of Southern California                                                                          |

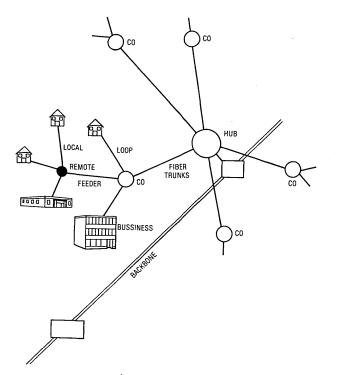

|   | Optical Interconnection Technology in the Telecommunications Network, D.<br>H. Hartman, Bell Communications Research                                                                          |

| Т | RACK SC-5: Networks. Track Chair: Michael Willett, IBM Corporation                                                                                                                            |

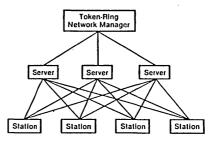

|   | Session 1 - Implementing a Token-Ring Local Area Network, Session Chair:<br>Michael Willett, IBM Corporation (4-A)                                                                            |

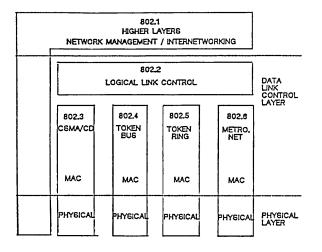

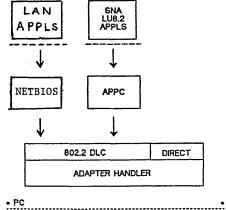

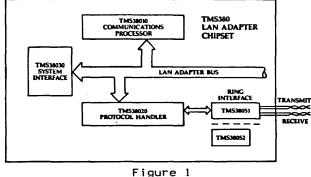

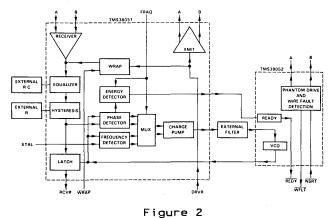

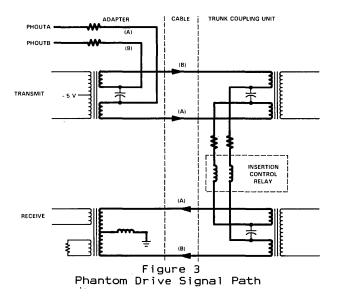

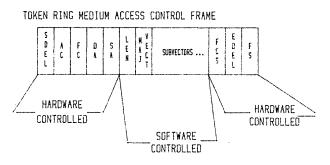

|   | Standards and Architecture for Token-Ring Local Area Networks, J. Winkler<br>and J. Munn, IBM Corp                                                                                            |

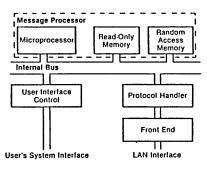

|   | The IBM Token-Ring Network: A Functional Perspective, Michael Willett,<br>IBM Corp                                                                                                            |

|   | Implementing the IEEE 802.5 Token-Ring Standard, M. C. Hamner and J. J. Carlo, Texas Instruments, Inc                                                                                         |

|   | The Fiber Distributed Data Interface: A Bright Future Ahead, S. P. Joshi,<br>Advanced Micro Devices                                                                                           |

### ALGORITHMS ARENA

~

| TRACK AL-1: Artificial Intelligence Algorithms. Track Chair: Tony A. Marsland,<br>University of Alberta                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 1 - Computer Chess Techniques. Session Chair: Tony A. Marsland,<br>University of Alberta (3-H)                                                               |

| Phased State Space Search, T. A. Marsland and N. Srimani, University of                                                                                              |

| Alberta                                                                                                                                                              |

| Improved Parallel Alpha-Beta Search, J. Schaeffer, University of<br>Alberta                                                                                          |

| TRACK AL-2: Numerical Methods. Track Chair: David R. Kincaid, University of Texas at Austin                                                                          |

| Session 1 - Vector and Parallel Algorithms. Session Chair: David R. Kincaid,<br>University of Texas at Austin (7-D)                                                  |

| New ADI Model Problem Applications, N. S. Ellner and E. L. Wachspress,<br>University of Tennessee                                                                    |

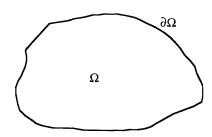

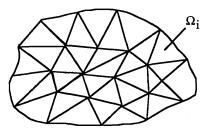

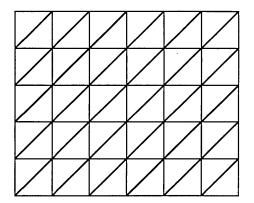

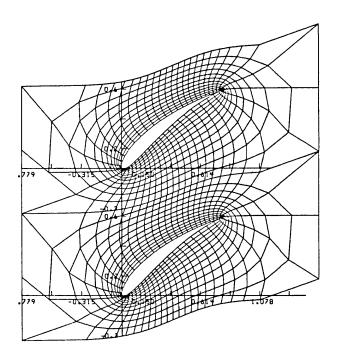

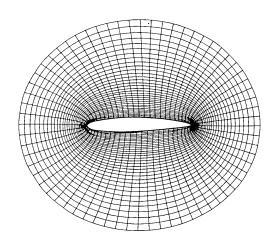

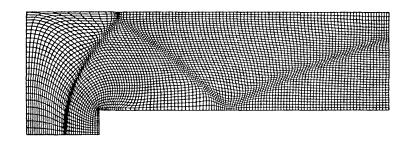

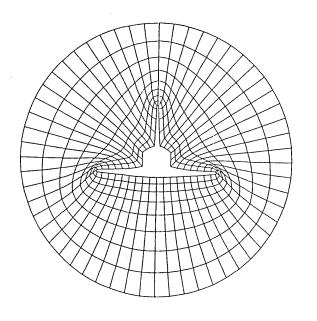

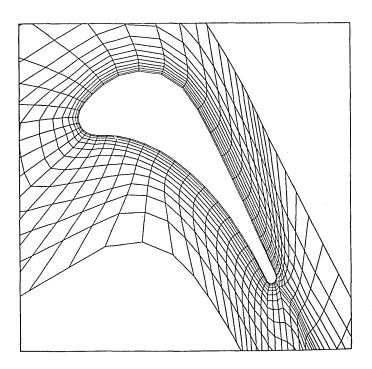

| Finite Element Analysis Using Advanced Processors, G. F. Carey and E.<br>Barragy, University of Texas at Austin                                                      |

| Parallelism in Solving PDEs, J. R. Rice, Purdue University                                                                                                           |

| Geophysical Modeling - Migration Viewed as a Spectrum of Supercomputer<br>Applications, O. G. Johnson and O. Lheman, University of Houston                           |

| Session 2 - Finite Differences, Finite Elements, and Grid Generation — A<br>Tutorial. Session Chair: Linda J. Hayes, University of Texas at<br>Austin(8-D)           |

| A Tutorial on Finite-Difference Methods and Ordering of Mesh Points, D. M.<br>Young and D. R. Kincaid, University of Texas at Austin                                 |

| Finite Element Methods, J. T. Oden, University of Texas at Austin                                                                                                    |

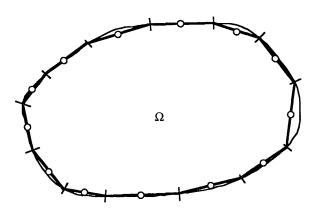

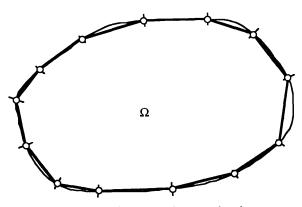

| Boundary Element Methods, S. R. Kennon, University of Texas at<br>Austin                                                                                             |

| A Comparison of Grid Generation Techniques, S. R. Kennon, University of<br>Texas at Austin, and G. S. Dulikravich, Pennsylvania State University                     |

| TRACK AL-3: General Algorithms. Track Chair: Paul Purdom, Indiana University                                                                                         |

| Session 1 - Searching. Session Chair: Cynthia Brown, Northeastern<br>University (7-1)                                                                                |

| Intelligent Backtracking Using Symmetry, C. Brown, L. Finkelstein,<br>Northeastern University, and P. W. Purdom, Jr., Indiana University                             |

| Time-Space Tradeoffs for Tree Search and Traversal, D. A. Carlson,<br>University of Massachusetts at Amherst                                                         |

| A Fast Probabilistic Algorithm for Four-Coloring Large Planar Graphs, R. A.<br>Archuleta and H. D. Shapiro, University of New Mexico                                 |

| Session 2 - Data Structures. Session Chair: Michael Loui, University of<br>Illinois (8-1)                                                                            |

| Techniques for Collision Resolution in Hash Tables with Open Addressing, J.<br>I. Munro and P. Celis, University of Waterloo                                         |

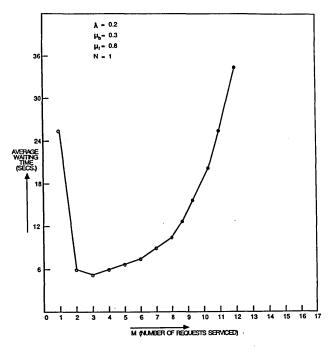

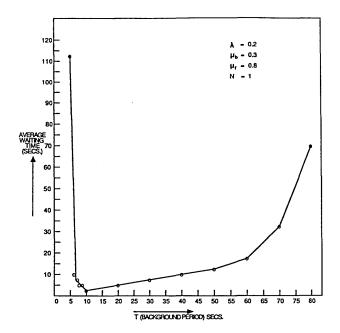

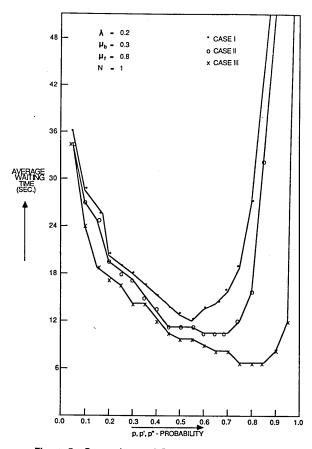

| Performance Analysis of Concurrent Maintenance Policies for Servers in a<br>Distributed Environment, F. B. Bastani, W. Hilal, and IR. Chen,<br>University of Houston |

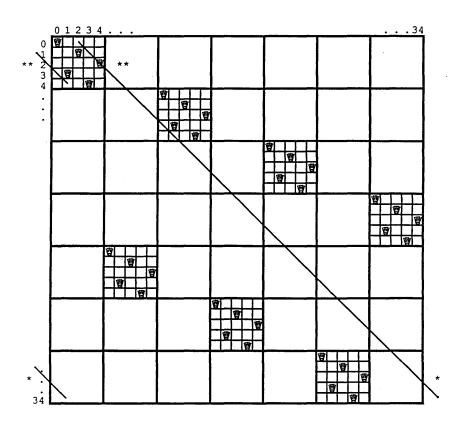

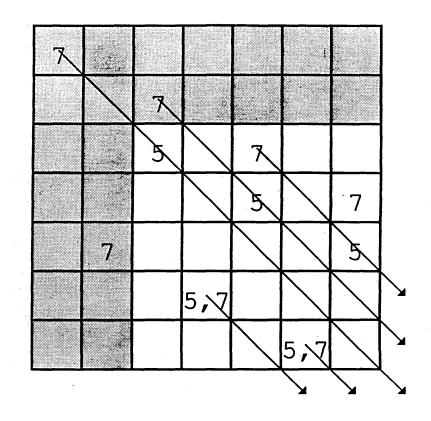

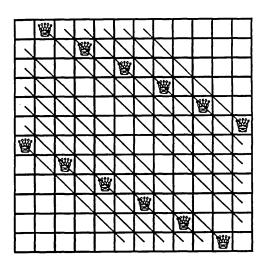

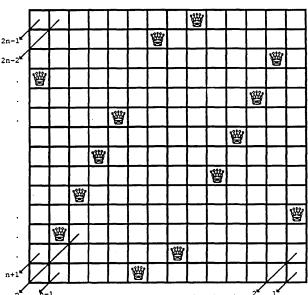

| Construction Through Decomposition: A Divide-and-Conquer Algorithm for<br>the N-Queens Problem, B. Abramson and M. M. Yung, Columbia<br>University                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 3 - Optimization. Session Chair: Larry Russo, University of<br>Washington (9-1)                                                                                                                                                               |

| Two Flow Routing Algorithms for the Maximum Concurrent-Flow Problem,<br>J. Biswas, University of Texas at Austin, and D. W. Matula, Southern<br>Methodist University                                                                                  |

| A Least-Cost Partition Algorithm, T. J.Marlowe, Jr., Seton Hall<br>University                                                                                                                                                                         |

| A Polynominal Determination of the Most Recent Property in Pascal-Like<br>Programs, D. Armbruster, University of Stuttgart                                                                                                                            |

| MODELING AND MEASUREMENT ARENA                                                                                                                                                                                                                        |

| TRACK MM-1: Performance Modeling and Measurement. Track Chair: Stephen<br>Lavenberg, IBM T. J. Watson Research Center                                                                                                                                 |

| Session 1 - Performance Modeling and Measurement. Session Chair: Stephen<br>Lavenberg, IBM T. J. Watson Research Center (1-G)                                                                                                                         |

| Frame Caching in Menu-Driven Videotex Systems, S. Lakshmi, S. Calo, and<br>P. Gupta, IBM T. J. Watson Research Center                                                                                                                                 |

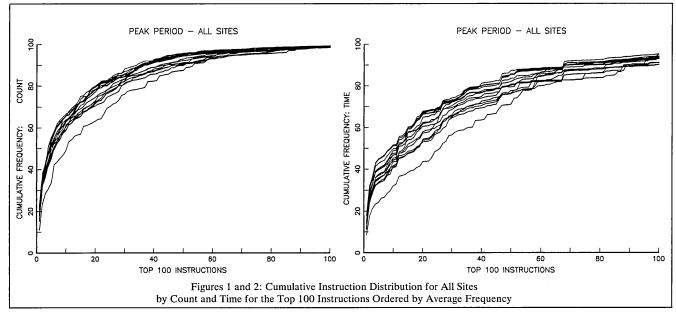

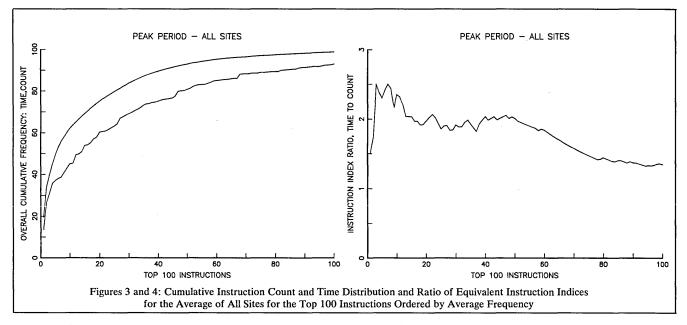

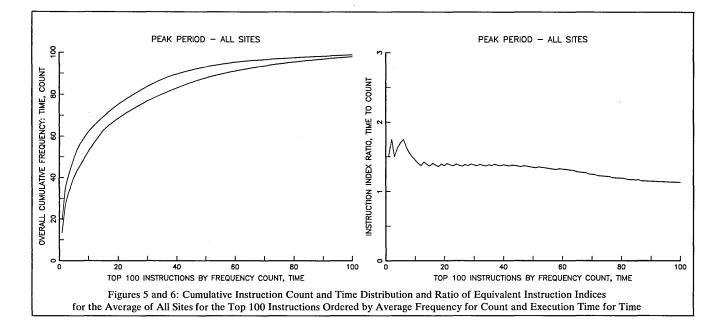

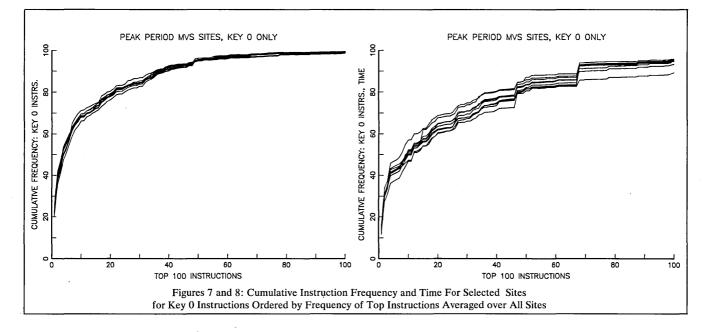

| The Contribution to Performance of Instruction-Set Usage in System/370, O.<br>R. LaMaire and W. W. White, IBM T. J. Watson Research Center                                                                                                            |

| Dynamic Load Sharing in Distributed Database Systems, P. S. Yu, S.<br>Balsamo, and Y. H. Lee, IBM T. J. Watson Research Center                                                                                                                        |

| A Load Index for Dynamic Load Balancing, D. Ferrari and S. Zhou,<br>University of California at Berkeley                                                                                                                                              |

| Session 2 - Performance Modeling Methods. Session Chair: Stephen<br>Lavenberg, IBM, T. J. Watson Research Center (2-G)                                                                                                                                |

| An Approximation of the Processing Time for Random Graph Model of<br>Parallel Computation, E. Gelenbe, University of Paris, R. Nelson, T.<br>Philips, and A. Tantawi, IBM T. J. Watson Research Center                                                |

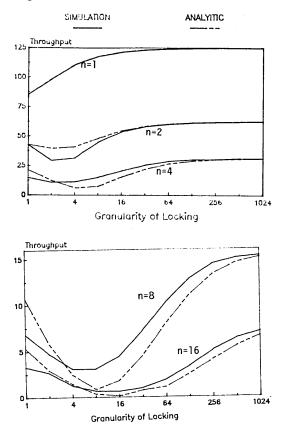

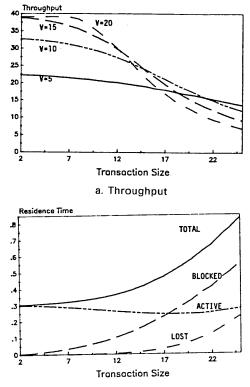

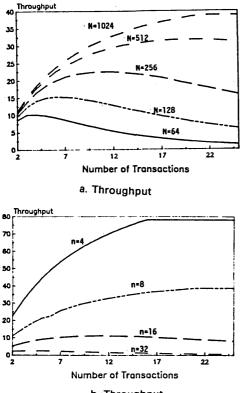

| Performance Analysis of Dynamic Locking, I. K. Ryu, University of<br>Southern California, and A. Thomasian, IBM T. J. Watson<br>Research Center                                                                                                       |

| Session 3 - Performance Modeling Workstations. Session Chair: Stephen<br>Lavenberg, IBM T. J. Watson Research Center (3-B)                                                                                                                            |

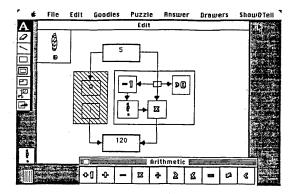

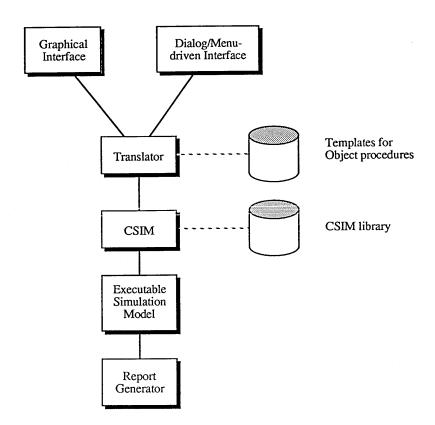

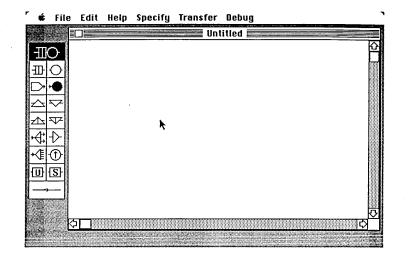

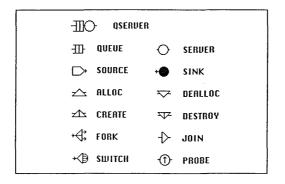

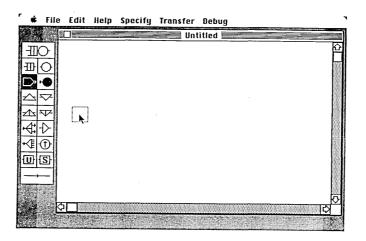

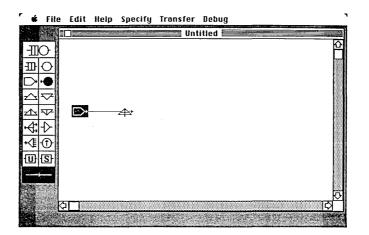

| A Graphical Interface for Specification of Extended Queueing Network<br>Models, J. B. Sinclair and S. Madala, Rice University                                                                                                                         |

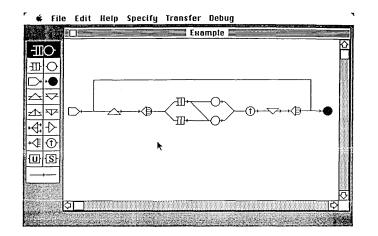

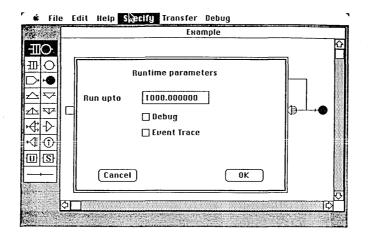

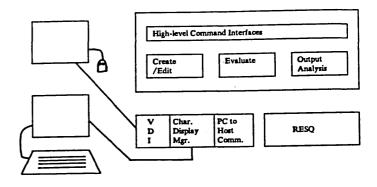

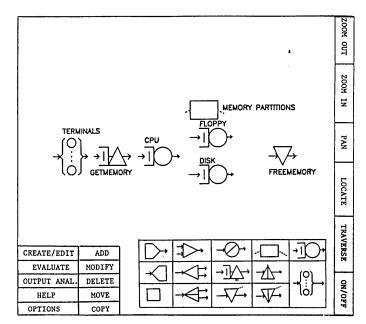

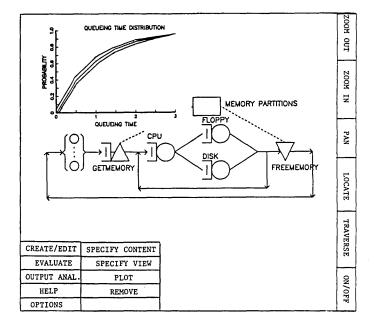

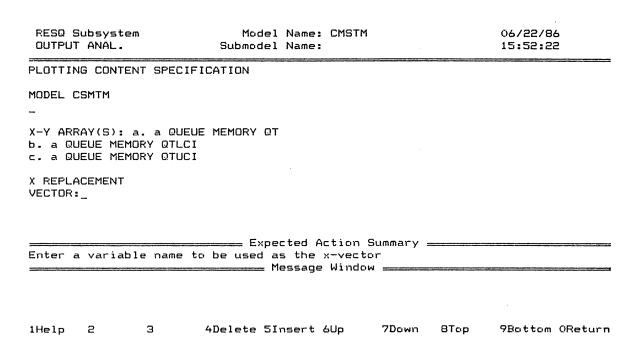

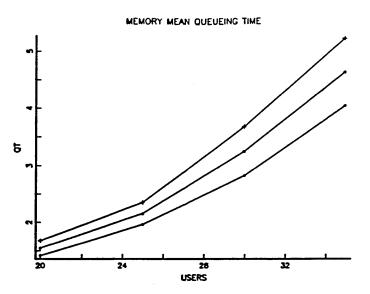

| A Graphics-Oriented Modeler's Workstation Environment for The RESearch<br>Queueing Package (RESQ), J. F. Kurose, K. J. Gordon, University of<br>Massachusetts, and R. F. Gordon, E. A. MacNair, and P. D. Welch, IBM<br>Hawthorne Research Laboratory |

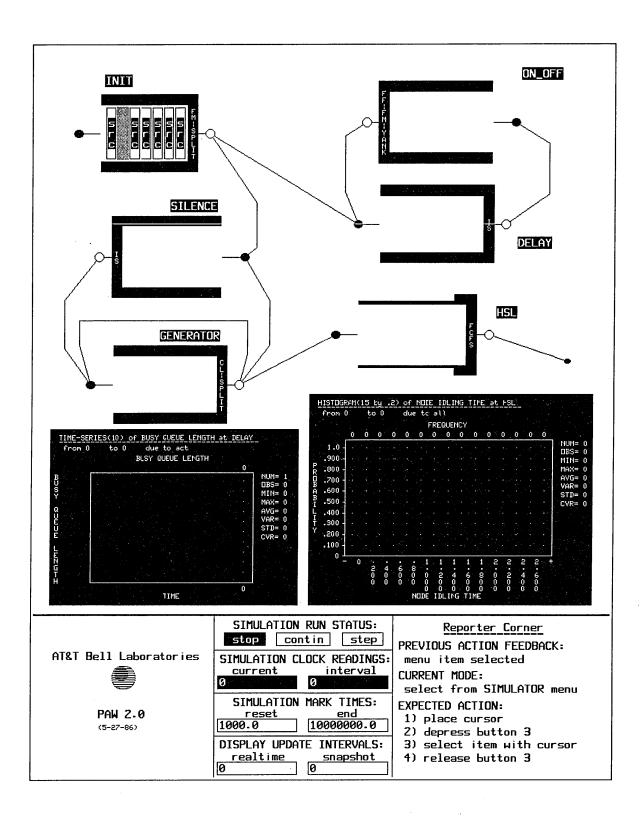

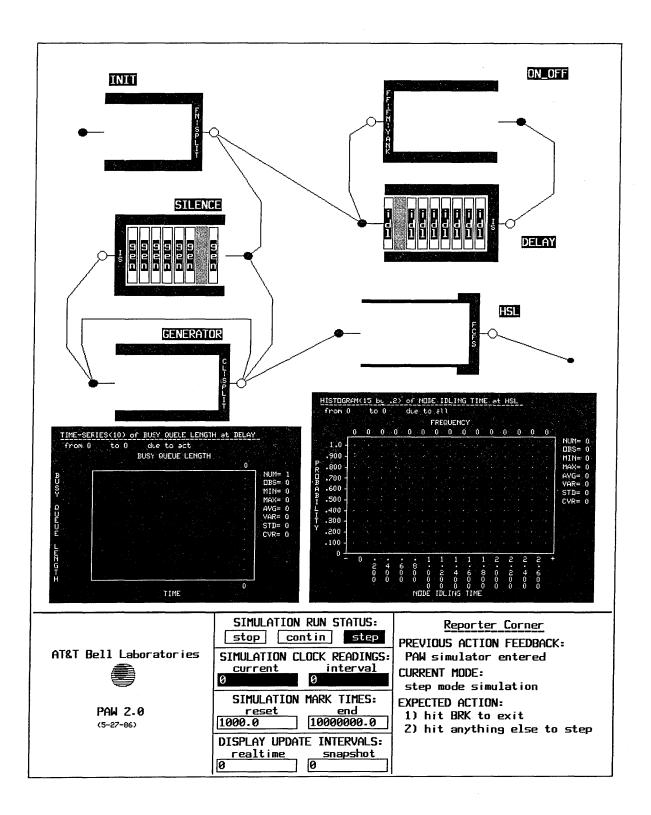

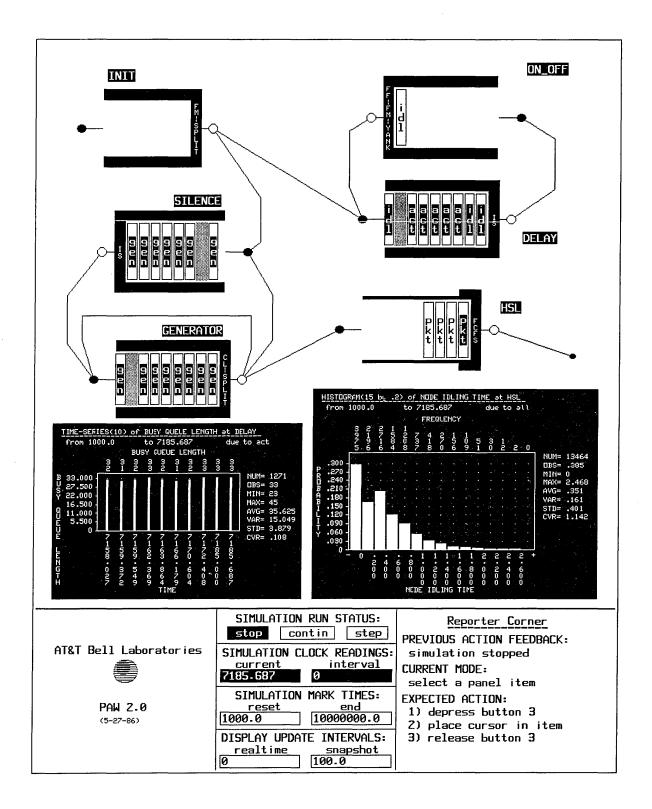

| The Performance Analysis Workstation: An Interactive Animated Simulation<br>Package for Queueing Networks, B. Melamed, AT&T Bell<br>Laboratories                                                                                                      |

| : | Session 1 - Capacity Management 1. Session Chair: Kenneth Kolence,<br>Kolence Associates (3-G)                                  |

|---|---------------------------------------------------------------------------------------------------------------------------------|

|   | An Overview of the Capacity-Management Process, K. W. Kolence, Kolence<br>Associates                                            |

|   | An Overview of Performance and Predictions for MVS Systems and SNA<br>Networks, J. P. Buzen, BGS Systems, Inc                   |

|   | A Survey of the State of Art and Practice in I/0 Subsystem Modeling and<br>Analysis, B. J. Smith, IBM General Products Division |

| ; | Session 2 - Capacity Management 2. Session Chair: Kenneth Kolence,<br>Kolence Associates (4-G)                                  |

|   | The Evolving Role of Software Products in Capacity Management: A Survey,<br>P. C. Howard, EDP Performance Review                |

|   | The Evolution of Workload Management in the Data Processing Industry: A Survey, T. L. Lo, McDonnell Douglas                     |

|   | The Evolution of Software Performance Engineering: A Survey, C. U. Smith,<br>L & S Computer Technology, Inc.                    |

| TRACK CD-1: Fault-Tolerant Computing. | Track Chair: John Meyer, | University of |

|---------------------------------------|--------------------------|---------------|

| Michigan                              |                          |               |

.

| Session 2 - Evaluation. Session Chair: Kishor S. Trivedi, Duke University (5-E)                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Performability Analysis of Operation Modes of Configurable Duplex<br>Systems, B. R. Iyer, D. M. Diaz, and P. S. Yu, IBM T. J. Watson Research<br>Center   |

| Recognition of Error Symptoms in Large Systems, R. K. Iyer, L. T. Young,<br>and V. Sridhar, University of Illinois at Urbana-Champaign                    |

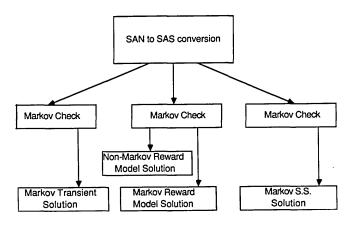

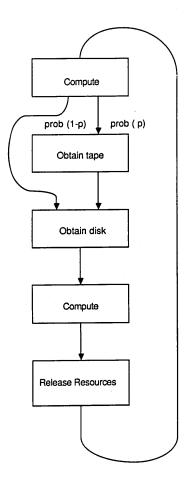

| METASAN: A Performability Evaluation Tool Based on Stochastic Activity<br>Networks, W. H. Sanders and J. F. Meyer, Industrial Technology                  |

| Institute                                                                                                                                                 |

| A Hierarchical, Combinatorial-Markov Method of Solving Complex<br>Reliability Models, R. A. Sahner, Gould CSD, and K. S. Trivedi, Duke<br>University      |

| Session 3 - Testing. Session Chair: Edward J. McCluskey, Stanford<br>University (6-E)<br>Design of Systems with Concurrent Error Detection Using Software |

| Redundancy, K. A. Hua and J. A. Abraham, University of Illinois                                                                                           |

| at Urbana                                                                                                                                                 |

| Stuck-At Fault Detection in Parity Trees, S. Mourad, J. L. A. Hughes, and<br>E. J. McCluskey, Stanford University                                         |

| A Two-Level Guidance Heuristic for ATPG, T. Kirkland, MCC, and M. R.                                                                                      |

| Mercer, University of Texas at Austin                                                                                                                     |

| TRACK CD-2: VLSI Design and Test: Theory and Practice. Track Chair: Jerome<br>M. Kurtzberg, IBM T. J. Watson Research Center                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 1 - VLSI Techniques of Design Automation. Session Chair: Sheldon<br>Akers, University of Massachusetts at Amherst (1-E)                                                                                                 |

| Automatic Intra-Device Pin and Element Reassignment (AIDPER)<br>Algorithm, H. A. Hershey and T. A. Onitiri, AT&T Bell Laboratories                                                                                              |

| A Knowledge-Based TDM Selection System, X. Zhu and M. A. Breuer,<br>University of Southern California at Los Angeles                                                                                                            |

| Deriving Module Interconnectivity from Behavioral Specifications and<br>Coupling a VLSI Layout Editor for Error-Free Routing, G. C.<br>Opalakrishnan, N. C. Lee, D. R. Smith, and M. K. Srivas, State University of<br>New York |

| Session 2 - VLSI Research in Universities. Session Chair: Timothy N. Trick,<br>University of Illinois at Urbana (2-E)                                                                                                           |

| Recent Results in VLSI CAD at MIT, R. E. Zippel, P. Penfield, Jr., L. A. Glasser, C. E. Leiserson, J. L. Wyatt, Jr., and J. Allen, Massachusetts Institute of Technology                                                        |

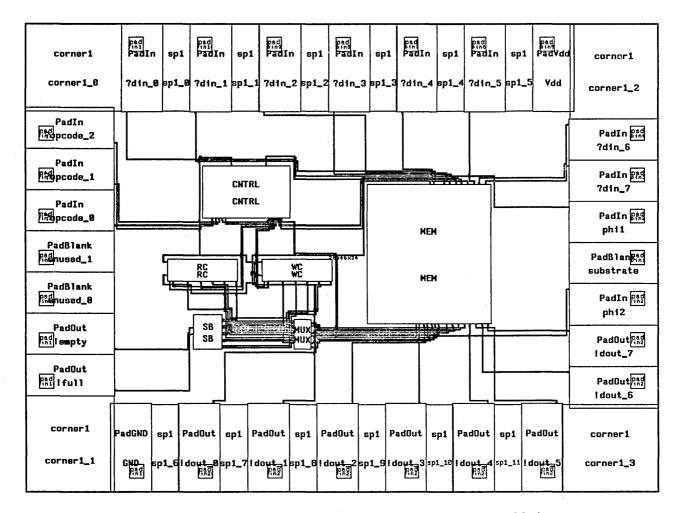

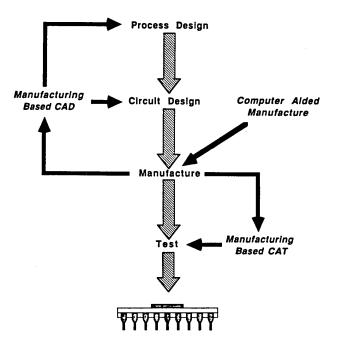

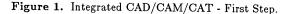

| Highlights of CMU Research on CAD, CAM, CAT of VLSI Circuits, J. P.<br>Shen, Carnegie Mellon University                                                                                                                         |

| Research in Reliable VLSI Architectures at the University of Illinois, J.<br>A. Abraham, University of Illinois at Urbana-Champaign                                                                                             |

| Highlights of VLSI Research at Berkeley, C. H. Sequin, A. R. Newton, and<br>A.L. Sangiovanni-Vincentelli, University of California at Berkeley                                                                                  |

| Session 4 - Expert Systems for Design and Test. Session Chair: Pradip Bose,<br>IBM T. J. Watson Research Center (7-E)                                                                                                           |

| DEFT: A Design for Testability Expert System, J. A. B. Fortes and M. A. Samad, Purdue University                                                                                                                                |

| Experiences in Prolog-Based DFT Rule Checking, G. Cabodi, P. Camurati,<br>and P. Prinetto, Politecnico di Torino                                                                                                                |

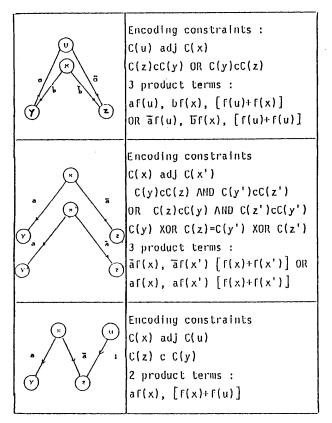

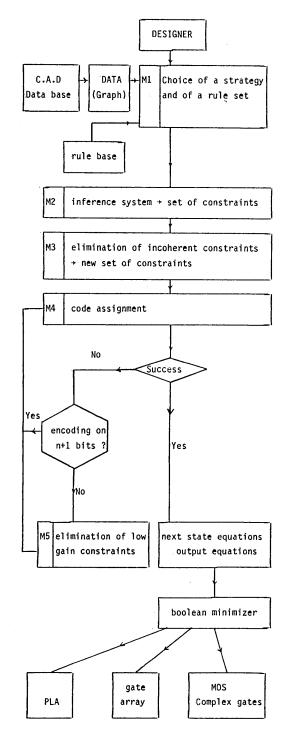

| A Rule-Based System for the Optimal State Assignment of Controllers, E.<br>Dupont, J. Idt, and G. Saucier, Lab. Circuits et Systems                                                                                             |

| TRACK CD-3: Computer Graphics. Track Chair: Michael Wozny, Rensselaer<br>Polytechnic Institute                                                                                                                                  |

| Session 1 - Computer Geometry. Session Chair: Louis Doctor, Raster<br>Technologies, Inc. (8-E)                                                                                                                                  |

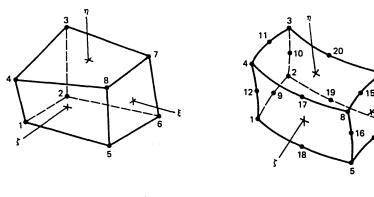

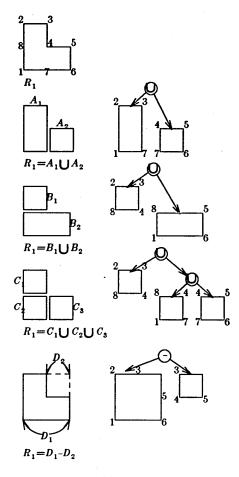

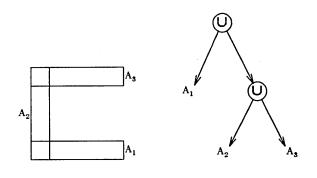

| Constructive Solid Geometry: A Symbolic Computation Approach, L. L. Leff<br>and D. Y. Y. Yun, Southern Methodist University                                                                                                     |

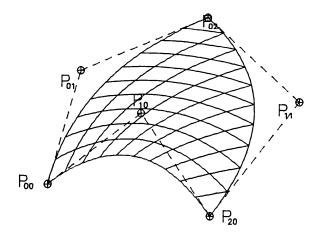

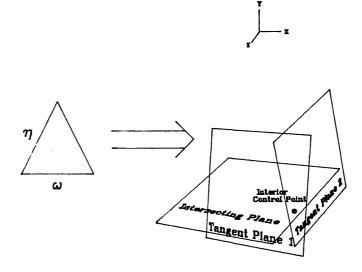

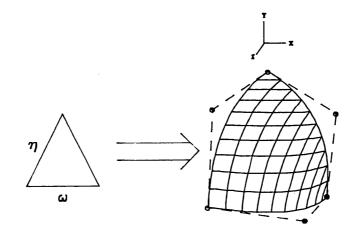

| Creation and Smooth-Shading of Steiner Patch Tessellations, D. E. Breen,<br>Rensselaer Polytechnic Institute                                                                                                                    |

| Algorithms for Normal-Vector Interpolation on Polygonal Surfaces, P. H.<br>Getto, Rensselaer Polytechnic Institute                                                                                                              |

## INTERNATIONAL DEVELOPMENT ARENA

| TRACK ID-1: Computer Developments in Japan. Track Chair: Ryoichi Mori,<br>University of Tsukuba, Track Secretariat: Mr. Kenji Naemura, NTT Electrical<br>Communications Laboratories |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 1 - Fifth Generation Computers I: Language Architecture. Session<br>Chair: Koichi Furukawa, ICOT (4-F)                                                                       |

| Guarded Horn Clauses and Experience with Parallel Logic Programming, J.<br>Tanaka, K. Ueda, T. Miyazaki, A. Takeuchi, Y. Matsmoto, and K.<br>Furukawa, ICOT Research Center          |

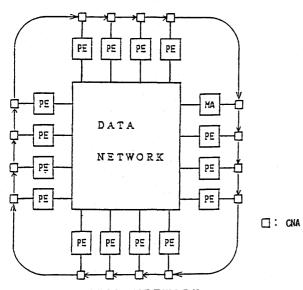

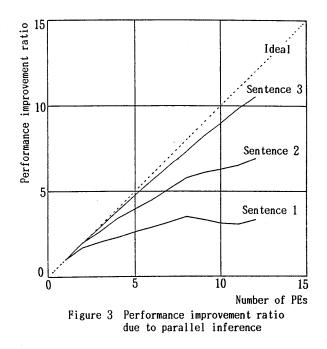

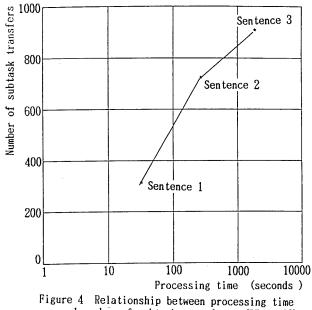

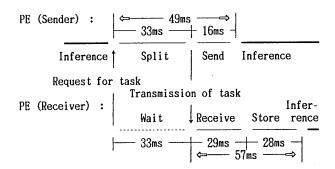

| "Kabu-Wake" Parallel Inference Mechanism and It's Evaluation, H.<br>Masuzawa, K. Kumon, A. Itashiki, K. Satoh, and Y. Sohma, Fujitsu Ltd                                             |

| A Very Fast Prolog Complier on Multiple Architectures, T. Kurokawa, N.<br>Tamura, Y. Asakawa, and H. Komatsu, IBM Japan                                                              |

| A Relational-Database Machine Based on Functional Programming<br>Concepts, Y. Kiyoki, K. Kato, and T. Masuda, University of Tsukuba                                                  |

| Session 2 - Fifth Generation Computers II: Applications. Session Chair:<br>Koichi Furukawa, ICOT (5-F)                                                                               |

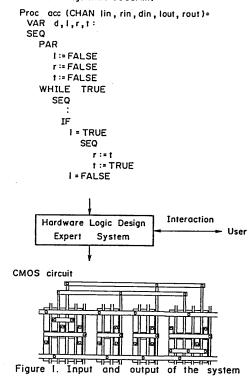

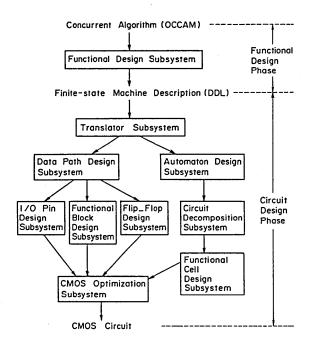

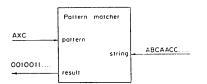

| Knowledge-Based Expert System for Hardware Logic Design, T. Mano, F.<br>Maruyama, K. Hayashi, T. Kakuda, N. Kawato, and T. Uehara, Fujitsu,<br>Ltd                                   |

| Research Activities on Natural Language Processing of the FGCS Project, T.<br>Yokoi, H. Miyoshi, K. Mukai, and Y. Tanaka, ICOT                                                       |

| ARGOS/V: A System for Verification of Prolog Programs, T. Kanamori, H.<br>Fujita, H. Seki, K. Horiuchi, and M. Maeji, Mitsubishi Electric                                            |

| Session 3 - Advanced Microcomputer Developments. Session Chair: Iwao<br>Morishita, University of Tokyo (6-F)                                                                         |

| A 32-Bit CMOS Microprocessor with Six-Stage Pipeline Structure, H.<br>Kaneko, Y. Miki, S. Nohara, K. Koya, and M. Araki, NEC Corp                                                    |

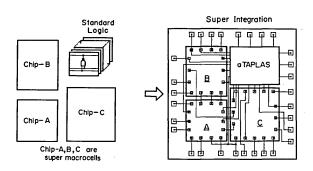

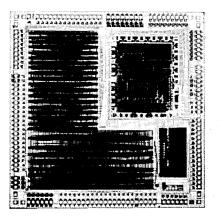

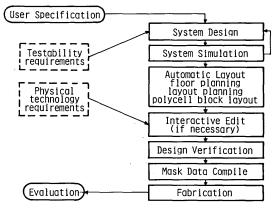

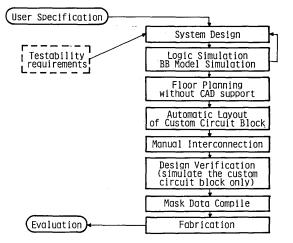

| Advanced Super Integration, T. Saito, T. Yamamoto, T. Shigematsu, K.<br>Nagao, S. Takeda, and Y. Suzuki, Toshiba Corp                                                                |

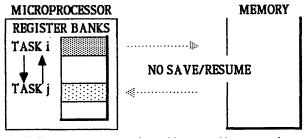

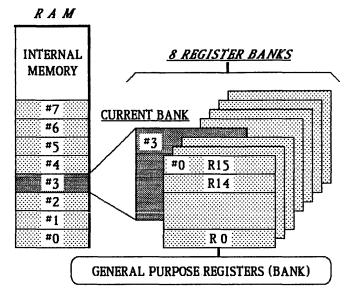

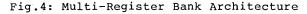

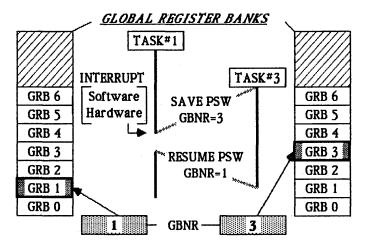

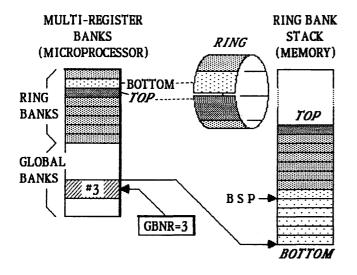

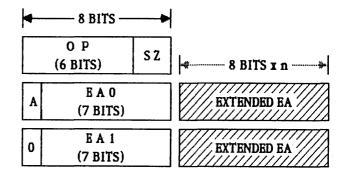

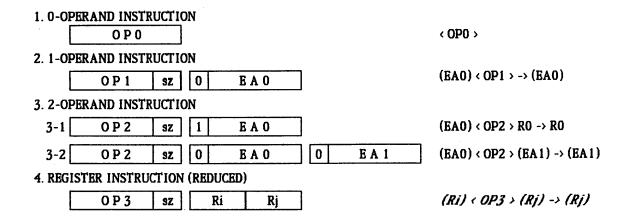

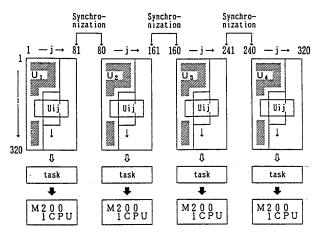

| A 16-Bit Microprocessor with Multi-Register Bank Architecture, H.<br>Maejima, H. Kida, T. Watanabe, S. Baba, and K. Kurakazu, Hitachi,<br>Ltd                                        |

| Session 4 - Supercomputing Systems. Session Chair: Yoshikuni Okada,<br>Electrotechnical Laboratory (7-F)                                                                             |

| Software-Oriented Approach for Supercomputer Design, K. Miura, Y.<br>Tanakura, and S. Kamiya, Fujitsu America                                                                        |

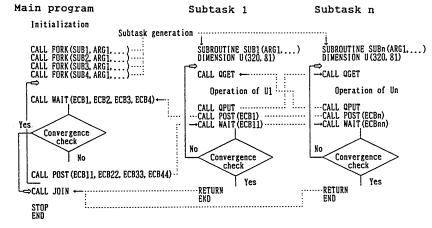

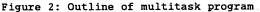

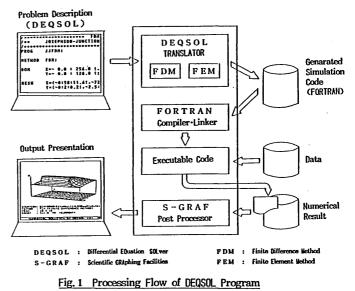

| Advanced Implicit-Solution Function of DEQSOL and Its Evaluation, C.<br>Kon'no, M. Saji, N. Sagawa, and Y. Umetani, Hitachi, Ltd                                                     |

| Fortran and Tuning Utilities Aiming at Ease of Use of a Supercomputer, H.<br>Katayama and M. Tsukagoshi, NEC Corp                                                                    |

| The IX Supercomputer for Knowledge-Based Systems, T. Higuchi, T.<br>Furuya, H. Kusumoto, K. Handa, and A. Kokubu, ETL                                                                |

| Session 5 - Interworking Systems. Session Chair: Kenji Naemura, NTT<br>Electrical Communications Laboratories (8-F)                                                                  |

| Methods for Achieving Integrated Operation in a High-Performance Optical<br>Loop Inter computer Communications System, M. Kurata, S. Tsuruho, T.<br>Isogawa, and H. Nakashima, NTT   |

.

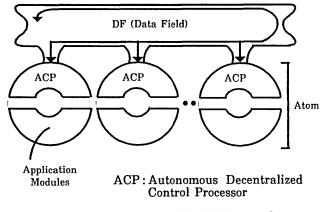

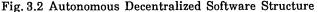

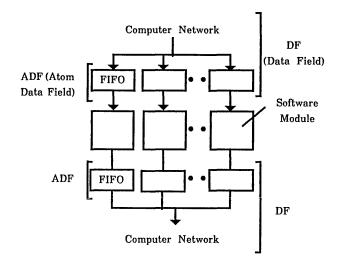

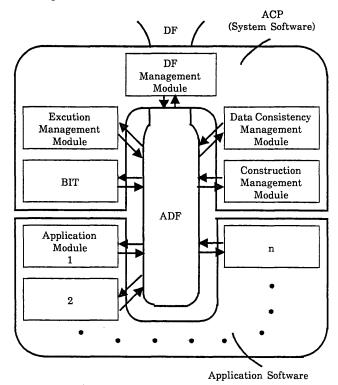

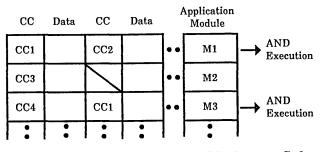

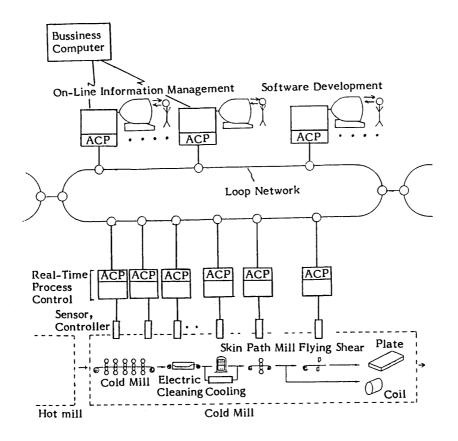

| <ul> <li>Autonomous Decentralized Software Structure and Its Application, K. Mori,</li> <li>H. Ihara, Y. Suzuki, K. Kawano, M. Koizumi, M. Orimo, K. Nakai, and</li> <li>H. Nakanishi, Hitachi Ltd</li></ul>  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

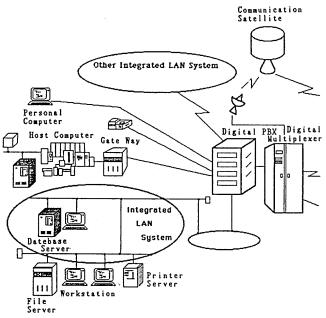

| Approaches to an Integrated Office Environment, M. Yoshida, M. Kotera, K.<br>Yokoyama, and S. Hikita, Oki Electric                                                                                            |

| OPERATING SYSTEMS AND DATA BASES ARENA                                                                                                                                                                        |

| TRACK OSDB-1: Operating Systems. Track Chair: James Peterson, MCC                                                                                                                                             |

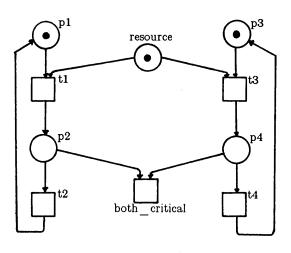

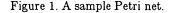

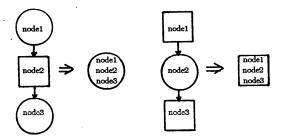

| Session 1 - Applications of Petri-Nets. Session Chair: Paul Reynolds,<br>University of Virginia (7-H)                                                                                                         |

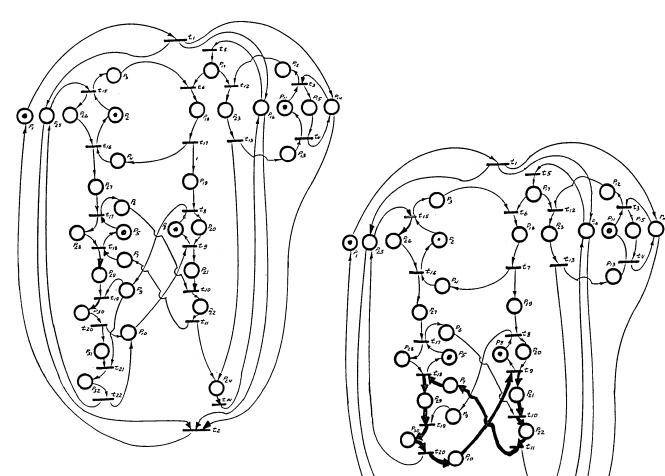

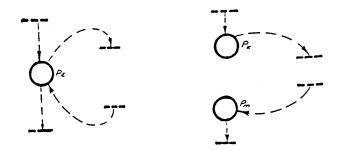

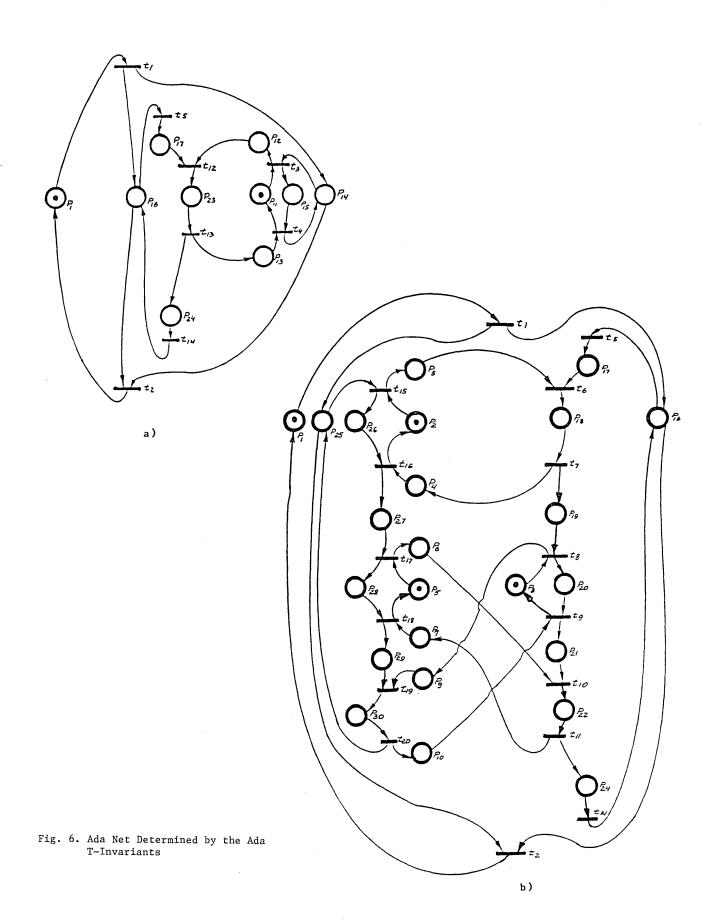

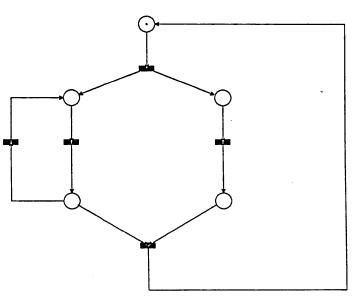

| Use of Petri-Net Invariants to Detect Static Deadlocks in Ada Programs, B.<br>Shenker, T. Murata, and S. Shatz, University of Illinois at Chicago                                                             |

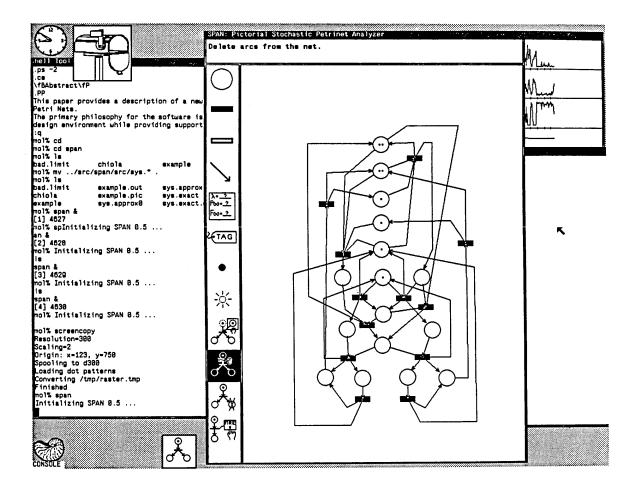

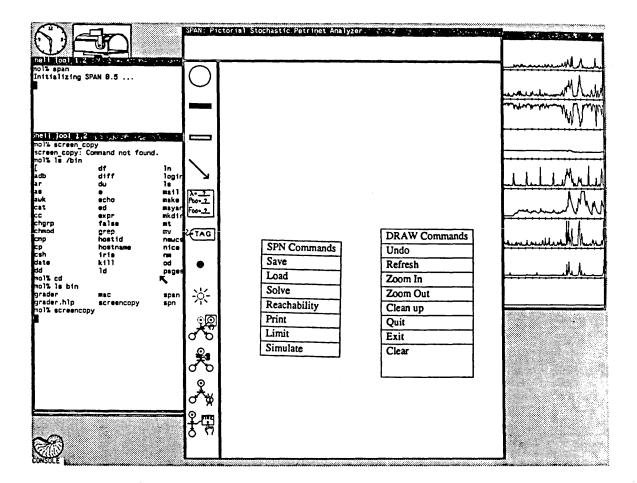

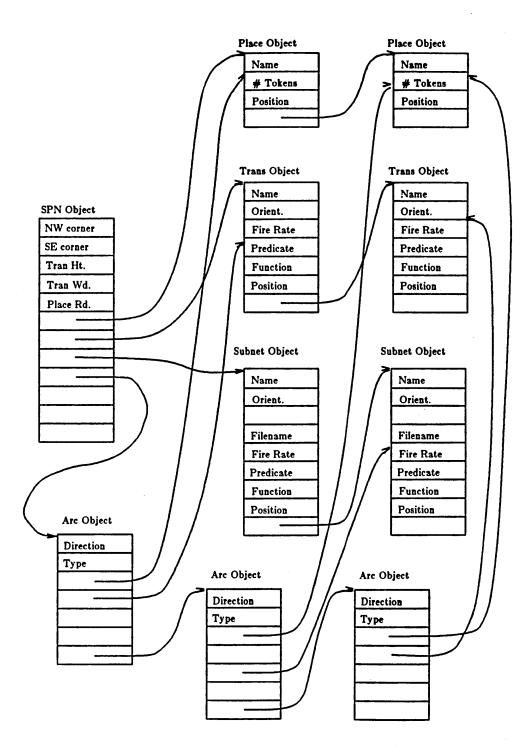

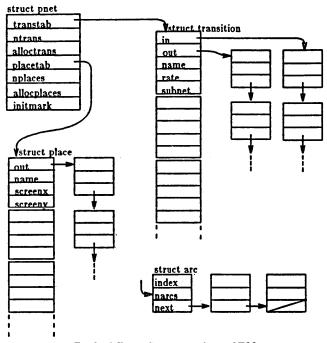

| A CAD Tool for Stochastic Petri-Nets, M. K. Molloy, Carnegie Mellon<br>University                                                                                                                             |

| Petri — A UNIX Tool for the Analysis of Petri-Nets, I. R. Forman,<br>Microelectronics & Computer Technology Corp                                                                                              |

| The GTPN Analyzer: Numerical Methods and User Interface, M. A.<br>Holliday, Duke University, and M. K. Vernon, University of Wisconsin                                                                        |

| at Madison                                                                                                                                                                                                    |

| Session 2 - Security and Protection in Computer Systems. Session Chair:<br>James Peterson, MCC (8-H)                                                                                                          |

| Security and Privacy Requirements in Computing, R. Turn, California State<br>University at Northridge                                                                                                         |

| Analyzing the Security of an Existing Computer System, M. Bishop, NASA<br>Ames Research Center                                                                                                                |

| A Network Technique to Achieve Program and Data Security with Nominal<br>Communications Overhead, J. Driscoll, H. Srinidhi, University of Central<br>Florida, and T. S. Chesser, Martin Marietta Data Systems |

| TRACK OSDB-2: Distributed Operating-Systems. Track Chair: Jack Stankovic,<br>Carnegie Mellon University                                                                                                       |

| Session 1 - Distributed-Operating Systems. Session Chair: Jack Stankovic,<br>Carnegie Mellon University (5-H)                                                                                                 |

| From RIG to Accent to Mach: An Evolution of a Network Operating System,<br>R. F. Rashid, Carnegie Mellon University                                                                                           |

| Load Balancing in NEST: A Network of Workstations, A. K. Ezzat, AT&T<br>Bell Laboratories1138                                                                                                                 |

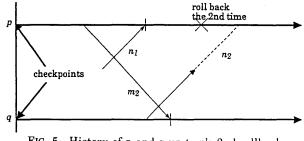

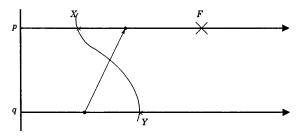

| Checkpointing and Rollback-Recovery for Distributed Systems, R. Koo and<br>S. Toueg, Cornell University                                                                                                       |

| The Gutenberg Operating System Kernel, P. Chrysanthis, K. Ramamritham,<br>D. Stemple, University of Massachusetts, and S. Vinter, BBN<br>Laboratories                                                         |

| Session 2 - Distributed Databases. Session Chair: Hector Garcia-Molina,<br>Princeton University (6-H)                                                                                                         |

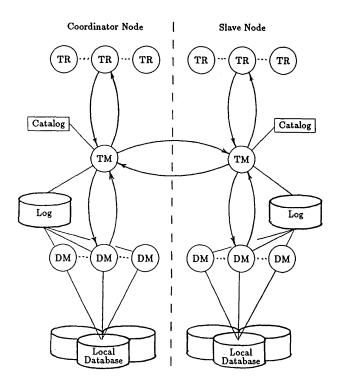

| CARAT: A Testbed for the Performance Evaluation of Distributed Database<br>Systems, W. H. Kohler and B-C. Jenq, University of Massachusetts                                                                   |

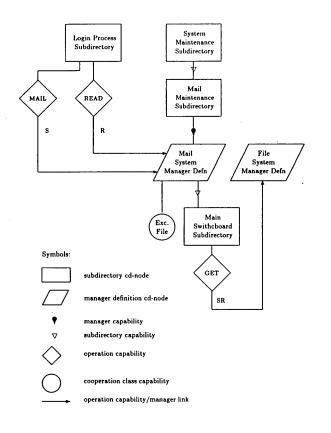

| Request II — A Distributed Database System for Local Area Networks, M.<br>Rusinkiewicz and D. Georgakopoulos, University of Houston                                                                           |

| A Protocol for Failure and Recovery Detection to Support Partitioned<br>Operation in Distributed Database Systems, J. K. Kim and G. G.<br>Belford, University of Illinois Urbana-Champaign |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Replication in Distributed Systems: The Eden Experience, J. D. Noe, A. B.<br>Proudfoot, and C. Pu, University of Washington                                                                |

| TRACK OSDB-3: Data Bases. Track Chair: Anil Nigam, IBM T. J. Watson<br>Research Center                                                                                                     |

| Session 1 - Data Bases, Session Chair: Anil Nigam, IBM T. J. Watson<br>Research Center (1-H)                                                                                               |

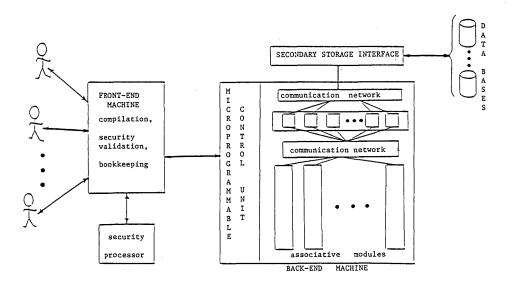

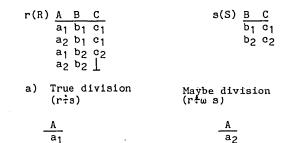

| MAYBE Algebra Operators in Database Machine Architecture, L. L. Miller,<br>Iowa State University, and A. R. Hurson, Pennsylvania State<br>University                                       |

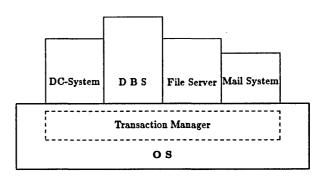

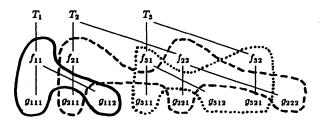

| Pros and Cons of Operating System Transactions for Database Systems, G.<br>Weikum, Technical University of Darmstadt, West Germany                                                         |

| Main Memory Database Recovery, M. Eich, Southern Methodist University                                                                                                                      |

| A Relational-Database Machine Organization for Parallel Pipelined Query<br>Execution, M. Hirakawa, T. Tsuda, M. Tanaka, and T. Ichikawa,<br>Hiroshima University                           |

| Index to Authors                                                                                                                                                                           |

## The 1986 Fall Joint Computer Conference— A Conference for the Profession

#### Stanley Winkler Conference Chairman

A professional, technical conference is the term we have used to describe the 1986 Fall Joint Computer Conference (FJCC '86). It was our aim to prepare the finest conference of the decade. Sponsored by two great professional computer associations, the Association for Computing Machinery (ACM) and the Computer Society of the IEEE, the FJCC was conceived as a conference-for-all-members. Specifically, the FJCC combines two meetings of the Societies customarily held in the fall season: The ACM National Conference and the COMPCON Fall meeting of the Computer Society of the IEEE. The ACM Council and the Computer Society Governing Board will meet during FJCC '86, as will various Boards and Committees, following the tradition of conducting Society business during the annual Fall Meeting.

Professional, technical conferences in the United States have a long and honorable history that can be traced back to the Mechanics Institutes of the 1800s. These Institute meetings, made necessary by the rapid technical advances of the Industrial Revolution, allowed professionals in the field of engineering to gather together and share problems and experiences. As the workforce became more specialized, it was no longer adequate for industry to rely on the transfer of technical knowledge from father to son or from master to apprentice. Today, in the computer field, professional conferences remain an important, if not the most important, means of exchange of ideas, information, and knowledge within the profession. While classroom education can provide the basis for entry into the profession, the essential continuing education is best acquired by interaction with one's peers. This interaction among peers is at once the function and the *raison d'être* of professional, technical conferences.

Of course, times have changed, and our computing profession has changed with it. Thirty-five years ago at the first joint meeting, in Philadelphia, the topics discussed encompassed most of the field as it was known then. That completeness would be impossible to accomplish today. Nonetheless, it seemed important to try, during FJCC '86, to provide a broad-based review of the most significant topics that confront the computing profession and industry. The salient feature of the 1986 Fall Joint Computer Conference is its broad-based nature. Equally important is the fact that, broad-based though it is, FJCC '86 presents full in-depth discussions of the topics selected. The technical program for FJCC '86, so ably developed under the leadership of Harold S. Stone, is a cornucopia of technical delights prepared by experts for their fellow practitioners of the art of computing.

In his introduction to the FJCC '86 technical program (in this volume), Harold S. Stone refers to FJCC '86 as "a new beginning." Since by definition all beginnings are new, one cannot quarrel with this phrase. I think, however, that the French saying "the more things change, the more they remain the same" also applies. I had the pleasant and comfortable feeling, on first seeing the finished FJCC '86 technical program, that the program is a return to the best traditions of the past. It is, indeed, a thoroughly modern program, broad-based and in full detail. It displays, without compromise, the current state-of-the-art. A casual look at the Conference-at-a-Glance confirms this assertion. But the technical program of the 1986 Fall Joint Computer Conference does more than provide a static snapshot of the world of computing today. It describes and represents the directions that the leaders of the computing profession are taking.

This illumination of the directions that the computing profession is taking is the most important function of an FJCC. Significantly, this illumination is not a prediction of the future gained by gazing into a crystal ball, or by the reading of tea leaves. It is, in fact, a self-fulfilling prophecy. The participants in FJCC '86, the speakers, panelists, discussants, and attendees, are not just talking about professional leadership in the 1990s—they are making it happen. They can make it happen because "they" are the leaders, the top, key people in the profession and in the industry. The content of

FJCC '86 in its breadth and depth is outstanding—probably exceeding that of any conference held in the last decade. This unprecedented breadth and depth is achieved through the nine conferences that are held simultaneously during FJCC '86.

Each of these nine conferences is a front-line, major event of its own. The nine conferences are: Artificial Intelligence, Supercomputing, Software Systems, Algorithms, Modeling and Measurement, Computer Design, Computer Developments in Japan, Operating Systems and Data Bases, and Education.

The fact that these nine conferences are going on at the same time is a significant added dimension to the FJCC '86 experience. Not only can FJCC participants meet the experts in their own specialty, but they can interact with the leaders in other specialties. This provides an enrichment for the individual, and, at the same time, is very good for the profession. The interpersonal communication among specialists in various fields of computer science and engineering stimulates thinking and creativity. This "cross-cultural" communication induces the propagation of ideas and concepts from one field into another, adding robustness and vibrancy to our profession.

This Proceedings provides a permanent record of the technical papers presented at the Conference. As such, it is a valuable addition to the shelves of our personal and organizational libraries. It does not, however, capture the other dynamic and exciting aspects of FJCC '86; absent are the discussions following each presentation of a technical paper, the poster sessions where last minute ideas are put forth, and the conversations in the hallways and lounges during coffee breaks and after sessions. Also not reflected in the Proceedings are the special events such as the world class Chess Tournaments—the 17th North American Computer Chess Championship and the 6th World Microcomputer Chess Championship.

The FJCC was designed to provide a complete educational experience. Complementing the technical program, Toni Shetler and her committee arranged an unparalleled Professional Education Program (PEP) and a very interesting Exhibitor Technical Forum. The Professional Education Program, which took place during the first two days of the Conference, gave attendees the opportunity to learn new skills and to sharpen old ones. There were one- and two-day courses, many of the hands-on variety. The Exhibitor Technical Forums provided the opportunity for vendors to discuss and explain the technology imbedded in their principal products. All of these activities were part of the effort to attain the objective of FJCC '86: to expand the professional horizons and capabilities of the conference attendees.

It was my privilege to chair a Conference Committee of capable, dedicated individuals, who contributed their time and effort in the service of the profession by creating the FJCC '86. They are listed elsewhere in this volume. To each of these friends I want to say, "Thank you." There were many others who helped us and to all of them I want to express my sincere appreciation. And finally, I want to thank the participants because, in the final analysis, it is they who are the Conference.

## The 1986 Fall Joint Computer Conference – A New Beginning

Harold S. Stone Program Chairman

#### The Conference Role

The 1986 Fall Joint Computer Conference is a conference of the future and of the past. The future is embodied by the conference theme - Exploring the Knowledge-Based Society - and the past by its popular predecessor conference of the 1960s. In looking forward, the conference offers technical papers, panels, and tutorials to cover the topical areas that form the technology base for the next decade. Such areas as Artificial Intelligence, supercomputers, design automation, computer graphics, and networks are among the topics of special attention. In looking backward to the FJCC's of 20 years ago, the vast changes in the discipline are evident, which underscores the importance of providing state-of-the-art information in subject areas destined to form the core of the field in coming years.

Consider the change in the hardware technology from the 1960s to the 1980s. The supercomputers of the 1960s are the micros and minis of the 1980s. Who would believe then that such computing power would be available on the desk tops of virtually every researcher, analyst, programmer, and student. The workhorse of a typical scientific installation in 1960 had 128K of 10 microsecond memory. A low-cost microprocessor of 1986 has 256K of 150 nanosecond memory. A supercomputer of 1965 had 2M bytes of 1 microsecond memory. A typical workstation of 1986 has 4M bytes of 120 nanosecond memory. The dramatic improvements in cost and performance made possible through VLSI technology were truly unimaginable in the days of the former FJCC.

The impact of such changes on the computing field are not yet fully assimilated, but the trends are clear. In days of expensive hardware, software was viewed to be inexpensive, more or less by default. Where hardware was too costly to commit to a special-purpose job, or where the functional requirements were too vague to lock into hardware, the often-used solution was to build hardware to do approximately what was desired, and to leave the final tailoring to software. That is, constrain the major cost by freezing the hardware at some stage, and fill in the remainder of the implementation with "inexpensive" software. All too often this approach had costly surprises in store for the system developers. With hardware frozen, the only freedom available to make such systems work was in software development, enhancements, and maintenance. Software costs climbed continually during the life of systems since software costs never ceased. In long-lived systems, software costs eventually dwarfed the hardware investment. Moreover, the inherent flexibility attributed to software became a myth, as changes to existing large-scale software became substantially more difficult and eventually impossible to implement. On the other hand, hardware became far more flexible, as each new generation of computers was succeeded by faster and less expensive generations, each upward compatible with its predecessors. The relative flexibility of hardware and software as viewed in the 1960s had turned upside down by the 1970s.

To improve the software situation, substantial efforts in high-level languages increased programmer productivity, but, productivity as measured in lines of code, failed to attain high multiples that was once viewed necessary to prevent the massive cost of software production from swamping the industry. Who would have predicted how this view would change after widespread introduction of the microprocessor? With millions of potential users instead of hundreds, the sales price of software could be kept relatively low per user, in spite of high costs for development. Moreover, as new microprocessors were introduced, it was totally impractical to rewrite a new software base for each new offering. Survivability of the microprocessor was largely tied to the ability to move a complete software base to the microprocessor, and this in turn created the market for portable software. With relatively little effort, it is possible today to move a complete operating system plus compilers, editors, and supporting tools to a totally new microprocessor with a unique instruction set.

Instead of writing new code that reinvents old software, the field has developed techniques to reuse software that does the job. The net result is that most software has become inexpensive on a per-user basis. Expensive software still exists, however, where user communities are small, and where techniques are embodied in software for the first time.

Having reflected on the changes in computing technology from when the FJCC was at its former height to the present time when the FJCC has been reborn, can we conceive of the changes that will take place in the next several years? For example, what will happen to programming as a profession? Will it be a profession that supports a population that seems to grow exponentially? Or will there be a limit to that growth that holds the population constant? Or will the numbers collapse? All three of these models are possible, depending on how the field places computer power in the hands of the user. The exponential growth models the growth in the number of computers, and is a model in which each computer system requires individual programming. The constant-population model is a model in which a fixed pool of people is able to supply a growing population of machines, and is probably an accurate reflection of the industry in the next few years as portable software becomes more widely used in place of specially tailored software. The last model in which fewer programmers are able to supply a growing pool of machines is one in which a relatively few "super" systems created by highly skilled programming teams account for large fractions of software use. The remaining software can be supplied by a much smaller pool of programmers under the first or second models.

The potential for this last model clearly exists today. If the model eventually becomes reality, the industry will be far different from the one we know. Are we ready for that event?

The 1986 FJCC is a conference where we can examine the recent trends, hear the projections, discuss the possibilities with the experts in each field, and then prepare for the future. The key to the FJCC is the technical focus. We must be an informed profession, and we must look forward in technology.

The growth of the computer profession has brought diversity, and the diversity has splintered the profession a hundred ways into the SIGs and TCs that form the technical leadership of the disciplines within the profession. The diversity has created journals, newsletters, conferences, and workshops with single themes directed to the experts in the various areas. Each of these activities has had its positive benefits within the narrow focus area, but the single-focus activities cannot provide for advances that require the synthesis of ideas from multiple disciplines. The FJCC is, by design, a multiple-focus conference. Its purpose is to bring together the experts across a range of disciplines so that the mix of ideas can provide impetus for new projects attaining new plateaus that are not readily achievable within any one discipline.

Consider, for example, four different ways of

representing information. Individually, we might have information represented as

- text,

- voice,

- graphics, or

- data base.

For each representation we can build a discipline that deals with that representation exclusively, and we create such disciplines as publishing, telephony, computer graphics, and on-line information utilities. Now reconsider the four representations, and consider what happens when you join any two together. A whole new discipline is created. If you join text and voice, you obtain the voice-operated typewriter, voice-data communications networks, or spoken output from written text. If you combine graphics and text, you create computer publishing, intelligent copiers, and electronic encyclopedias. But there is no need to focus on just the four data representations. Pick any collection of specialinterest areas and consider what new challenges can be formed by combining any two or three areas. This gives an inkling of what can happen when you bring together active thinkers from a variety of areas and let the pot boil. This is the FJCC.

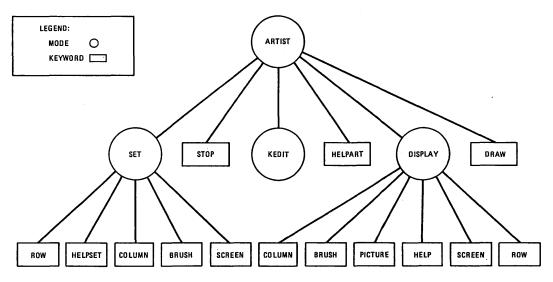

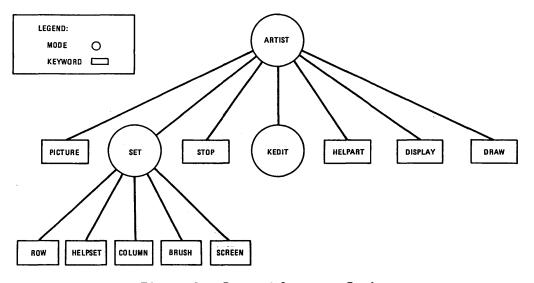

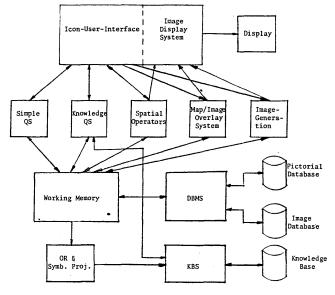

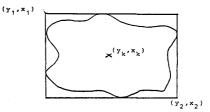

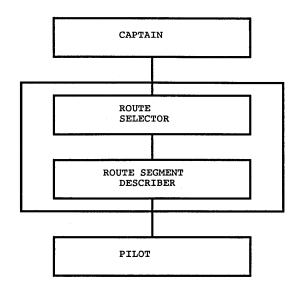

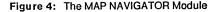

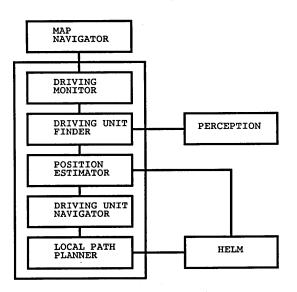

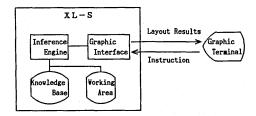

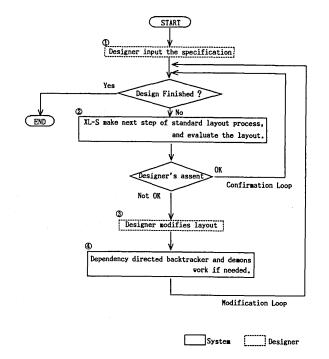

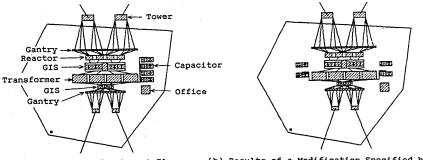

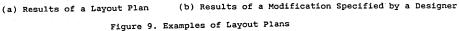

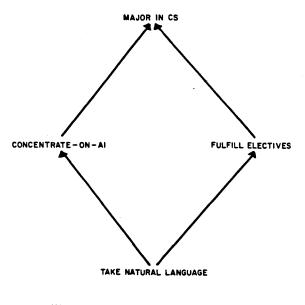

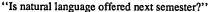

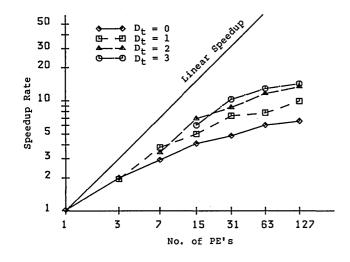

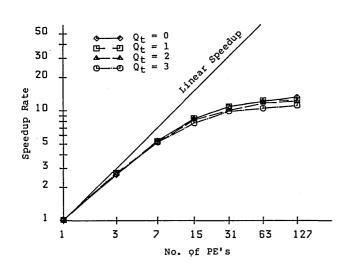

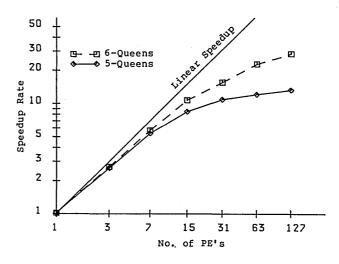

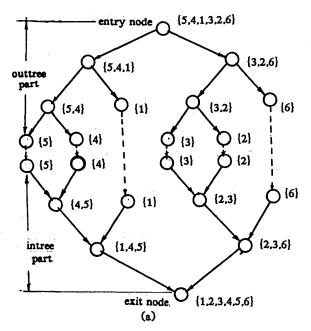

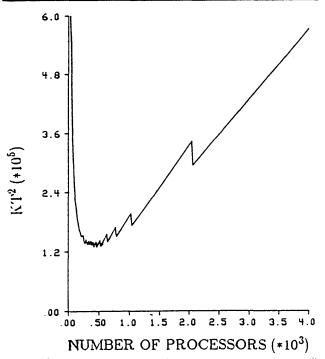

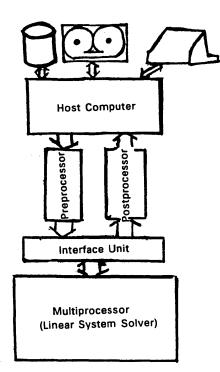

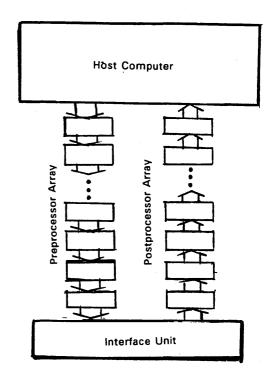

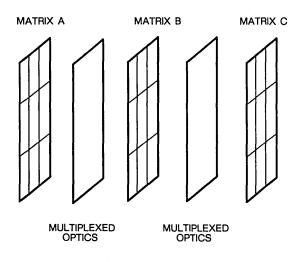

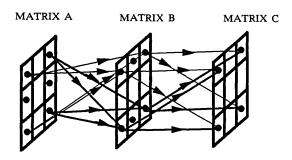

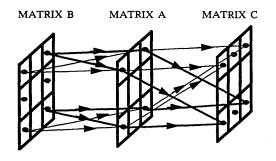

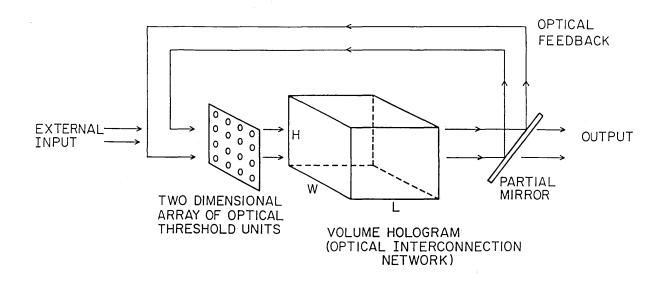

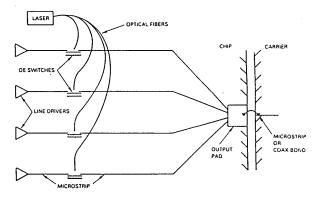

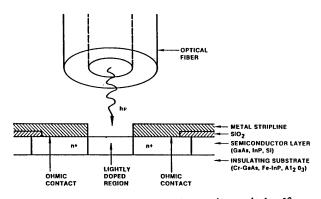

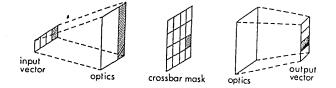

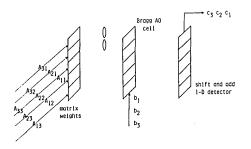

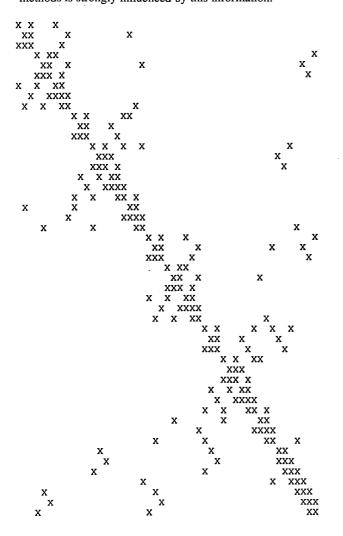

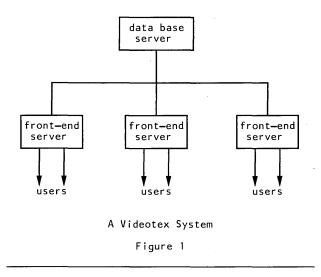

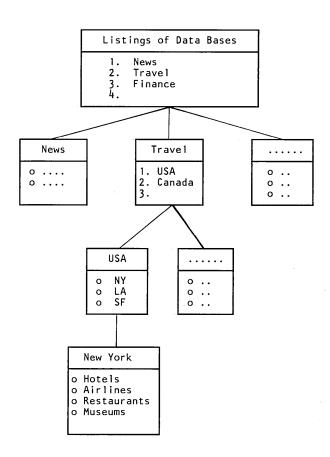

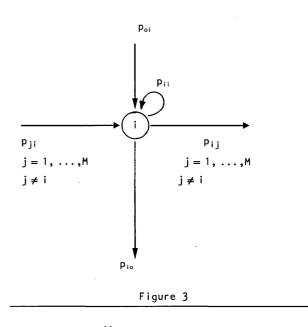

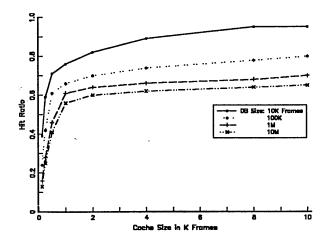

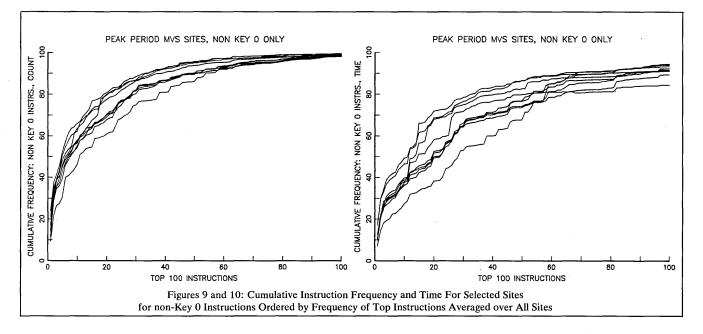

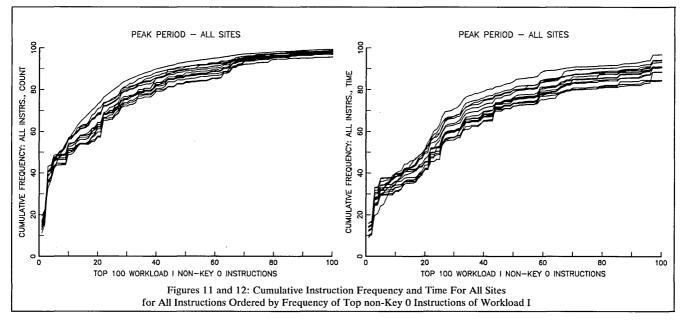

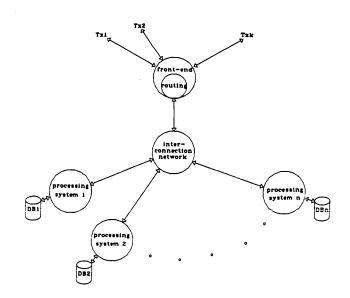

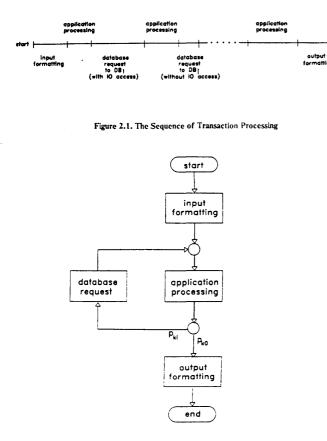

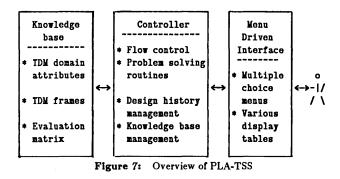

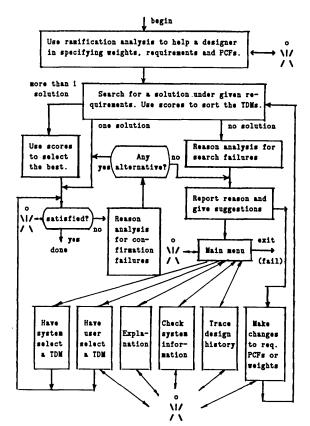

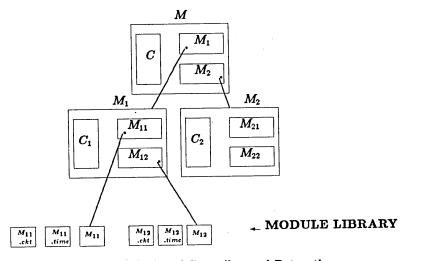

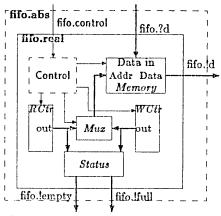

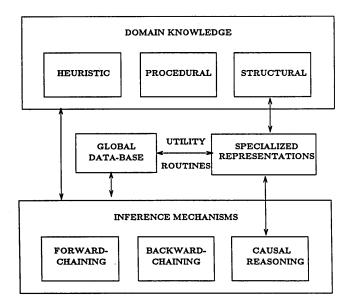

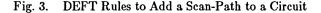

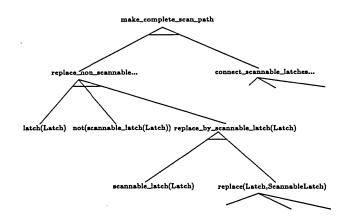

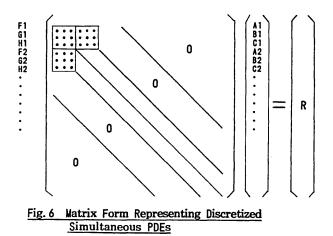

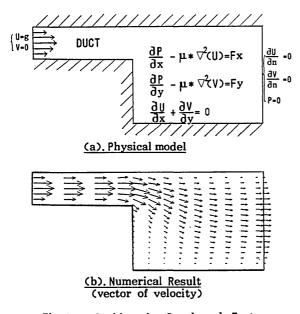

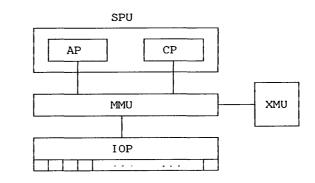

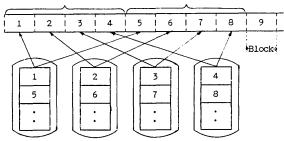

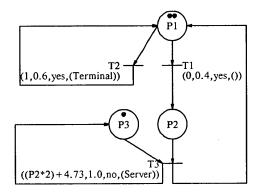

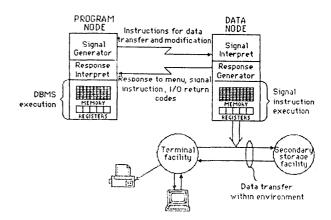

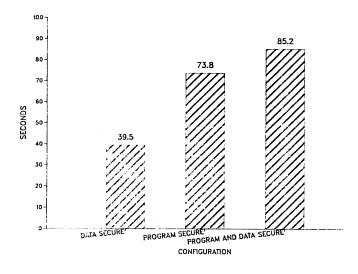

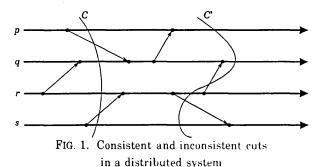

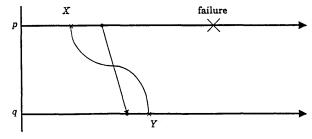

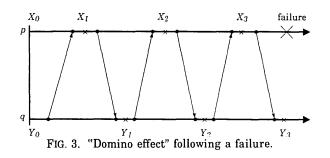

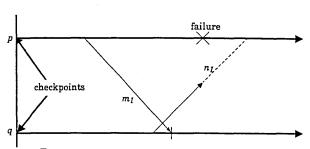

#### **Conference Management**