ALEX ORDEN Editor and Program Chairman

> MARTHA EVENS Co-Editor

ALBERT K. HAWKES Conference Chairman

# **AFIPS** CONFERENCE PROCEEDINGS

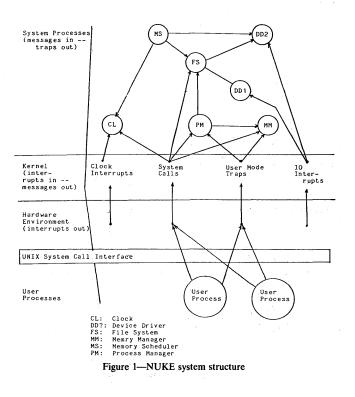

# **1981** NATIONAL COMPUTER CONFERENCE

May 4–7, 1981 Chicago, Illinois

AFIPS PRESS 1815 NORTH LYNN STREET ARLINGTON, VIRGINIA 22209 The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1981 National Computer Conference or the American Federation of Information Processing Societies, Inc.

Library of Congress Catalog Card Number 81-65717 AFIPS PRESS 1815 North Lynn Street Arlington, Virginia 22209

© 1981 by AFIPS Press. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) reference to the AFIPS Proceedings and notice of copyright are included on the first page. The title and abstract may be used without further permission in computer-based and other information-service systems. Permission to republish other excerpts should be obtained from AFIPS Press.

Printed in the United States of America

This edition of the *Proceedings* of the National Computer Conference is dedicated to J. Presper Eckert and to the late John W. Mauchly, whose pioneering efforts extended the frontiers of technology for the good of all mankind.

## Preface

#### ALBERT K. HAWKES 1981 NCC Chairman

The National Computer Conference is an institution of the U.S. computer industry. Each year at the NCC, thousands representing companies, government agencies, and universities gather, and a forum is provided for hundreds of them. Much of what occurs is of course ephemeral, a great deal is of current and very practical value, and some lasts for many years. The *Proceedings* of the NCC is a principal element of that set of things from the conference with lasting value.

This 1981 Conference *Proceedings*, the fiftieth volume in the series, is an exhibit of the labors of Dr. Alex Orden, Program Chairman of the 1981 NCC. The myriad of details connected with organizing a program of this scope are treated in Professor Orden's introduction, and the reader will be wise to use that section as a road map before beginning to traverse the extensive volume. Authors of papers appearing here have contributed a greatet deal also, as have referees, session organizers, panelists, and other presenters of information at the conference whose contributions could not be made fully apparent in this volume. Another person who must be mentioned is the one who shepherded production of this *Proceedings*, Elizabeth G. Emanuel of AFIPS Press; her work was excellent and in keeping with the fine tradition at AFIPS established by Nelle W. Morgan many years ago.

It is an honor to prepare this preface to the lasting record of the 1981 NCC. In the same sense, it also is a rare privilege to be Conference Chairman. Having served on the NCC Committee starting nearly ten years ago, and serving as its chairman for two years covering the first and second NCCs, I did induce a number of friends and colleagues to serve as conference chairmen—Stephen S. Yau in 1974 and Carl Hammer in 1976. Thus it was a signal duty this year to try to put a National Computer Conference together for the Chicago area, which has been my home for the best part of my life.

One realizes early in planning an NCC that appointing a strong and able Conference Steering Committee is the only way to assure that this NCC institution can renew itself each year. These competent and willing volunteers who put this NCC together include Drs. Orden, Yau, and Hammer and Richard B. Wise (Director of Operations), Marvin W. Ehlers

(CSC Secretary and Special Projects Manager), M. Mildred Wvatt (Communications and Promotion), Sam Papa (Personal Computing, whose cochairman James Gerdes produced a companion PC Digest, which complements this volume for NCC '81), George Eggert (Professional Development Seminars), Fred Harris (Special Activities, including a very great step forward in NCCs by improving access to the conference for handicapped persons), Robert C. Spieker (NCC Liaison), Charles W. Schmidt (NCC '81 Fiscal Officer), Raymond Dash and Anthony S. Wojcik (the two Chicago area Vice-Chairmen of Professor Orden's Program Committee serving on the NCC '81 CSC), Joseph Leubitz (Registration), and Forest Mayberry (Conference Facilities). Serving ex-officio on the CSC over the two years that work was done on this conference and its planning were many AFIPS staff members. Principal thanks are due particularly to Paul J. Raisig, Executive Director; James H. Kroell, Director of Conferences, and his predecessor Gerard Chiffriller; Betty Lou Cooke, Conference Manager, and her predecessor Carol Sturgeon; Sam Lippman, Conference Operations Manager; and Christopher Hoelzel, AFIPS Press Manager. In addition, when trying to think of those who contributed a great deal to this conference and to establishing another mark in a excellent tradition, two of my mentors from the National Computer Conference Committee should be named. Over many years, Dr. Morton M. Astrahan and Jerry L. Koory stand out for their encouragement, support, and kindly advice given freely.

The idea of the NCC as an institution, which I mentioned previously, does remind one of what Benjamin Disraeli said over a century ago: "Individualities may form communities, but it is institutions alone that can create a nation." This great nation is known for its industry, and there are few more telling examples of American ingenuity producing something good and possibly great than what computer science and technology are today. The NCC, as an institution, has helped computing in the United States and in the world. May it go on, ever eclipsing those of us honored to be part of the tradition, so that NCCs always serve what is best in the U.S.A.

## Introduction

#### ALEX ORDEN 1981 NCC Program Chairman

Since 1951 the National Computer Conferences have provided a forum for presentation of advances on all fronts of the computer field: research, development, and application. The *Proceedings* of the meetings give an unparalleled history of the field.

The *Proceedings* of 1976 include an interesting memoir by Herb Grosch on the history of the conferences, entitled "Conference Maketh a Ready Man, or Twenty-Five Years in the Better Joints." From 1954 to 1972, except in 1965, there were two conferences a year. From time to time the name has been changed—from 1951 to 1981 the series has consisted of

- 2 Joint Computer Conferences

- 1 Western Computer Conference

- 9 Eastern Joint Computer Conferences

- 8 Western Joint Computer Conferences

- 10 Spring Joint' Computer Conferences

- 11 Fall Joint Computer Conferences

- 9 National Computer Conferences

#### —50 in all.

In recent years important developments in the history of digital computation have been commemorated by conference sessions and other special events on a day designated "Pioneer Day." This year's theme for that day is the completion 30 years ago of the first UNIVAC I system. Two historic events thereby coincided: (1) The emergence of computers from the laboratory machines of those days into the marketplace marked the birth of the computer industry. (2) Since the UNIVAC was the first machine designed for data processing rather than for mathematical computation, its development was the first major step toward the enormous development in computer-based data processing that has since occurred. It's all too easy in the 1980's to overlook the difficulties and doubts that had to be overcome back then. On that account, this volume is dedicated to J. Presper Eckert and the late John Mauchly, whose vision in the development of the UNIVAC made possible the penetration of computers into almost every field of human endeavor.

For 30 years, as the computer industry and the computer field have become ever larger and more complex, the National Computer Conferences have had a unique role in bringing together the computer R&D community, industry representatives, educators, application and facility systems analysts, DP managers, and end users to survey ongoing developments and examine new directions. Each year the formation of a new Program Committee sets the stage for a fresh assessment of trends in the field and an independent effort to assemble a well-balanced program. Drawing on several hundred paper submissions and session proposals-some invited by the members of the Committee, some independently submitted-the Committee sets up a program, which tends to consist of about one-third refereed papers, which appear in the Proceedings; one-third prepared talks on topics that do not lend themselves well to formal publication; and one-third panel discussions on trends and opinions.

For this year's NCC, in order to provide a framework in which all aspects of the computer field might be considered, the Program Committee was initially organized (about a year before the Conference) as five groups, each covering a wide area: (1) computer hardware and architecture, (2) software, (3) information processing management, (4) applications, and (5) social and economic implications. We knew of course that some important topics would straddle two or more of these areas. Indeed, as development of the program progressed, some members of the Committee freely ignored the area boundaries.

The identification of significant current trends emerged in part when we converted the initial five broad areas into a ten-track program. In the hardware/architecture area we found emphasis on microcomputer design, on developments in microprogramming, and on fault-tolerant computing; and from that general area we spun off five sessions as a separate track on network technology, with developments in local nets predominant. In the software area we found a strong emphasis on reliability, software validation techniques, and quality control. From software we extracted a six-session track on database systems, with emphasis on distributed databases. In information processing management we developed coordinated groups of sessions on DP project management, on management of transitions to new technology and methodology, on application systems audit and quality control, on the DP production process, and on personnel; and we formed a separate five-session track, Capacity and Performance Analysis. In the Applications area we separated out a track called Visuals, Natural Language Processing, and Artificial Intelligence, leaving-under the rubric Computers at Work-sessions in such still budding application areas as law, hospitals, energy, and simulation modeling. Since there seemed to be no clear dividing line between sessions on diverse issues in computer education and sessions on computer-related social issues, and since most social issues have much to do with the diffusion of knowledge, we formed a track called Education and Societal Issues. Finally, although there is now an annual AFIPS Conference on Office Automation, those rapid developments should nevertheless be included in the NCC. Therefore we provided the track entitled Automating the Office.

The published record of recent advances in the computer field, as seen at NCC '81, resides in the papers appearing in this volume. Since there was much more to the Conference, a condensed view of the entire program—in the "Conference at a Glance" form that appeared in the Program Brochure—is attached to this introduction.

It has been a challenging experience to coordinate this complex activity. It would not have been possible without the devotion and hard work of the Program Committee, the referees of the papers, and the AFIPS staff. Their names appear elsewhere in this volume. I particularly thank Liz Emanuel, who managed the editorial work on the *Proceedings* at AFIPS with great competence; and Martha Evens of the Illinois Institute of Technology, who joined me in dealing with the refereeing and selection of papers.

| PRINCIPAL TRACKS                                                        | 1:3            | 0 to 3:00 PM                                                                                          | 3:1 | 5 to 4:45 PM                                                                                      |

|-------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|

| HARDWARE &<br>ARCHITECTURE                                              | 1.1            | <b>Design Tools for System</b><br>Architectures<br>George Kraft                                       | 1.2 | <b>Innovative Architecture &amp; Commercial Computers</b><br>Krishna M. Kavi                      |

| NETWORK TECHNOLOGY<br>AND<br>CAPACITY &<br>PERFORMANCE ANALYSIS         | \$.1           | Transport and Session Protocols in<br>the Context of the ISO Reference<br>Model<br>Leslie Jill Miller | 2.2 | <b>Packet Speech</b><br>Danny Cohen                                                               |

| SOFTWARE                                                                |                | <b>Programming Languages for Small<br/>Systems</b><br>Leon Levy                                       | 3.2 | <b>Software Development Tools</b><br>R. Stockton Gaines                                           |

| INFORMATION<br>PROCESSING<br>MANAGEMENT                                 | ¥              | System Implementation Strategy<br>Ken Zoline                                                          | 4.8 | Audit and Control in a Database<br>Environment<br>Steven Ross                                     |

| EDUCATION &<br>SOCIETAL ISSUES                                          | 5              | Survey and Comparison of Model<br>Curricula for Information Systems<br>Education<br>Thomas Ho         | 5.2 | Joint Business-University<br>Professional Development and<br>Research Programs<br>Robert A. Rouse |

| AUTOMATING THE OFFICE<br>AND<br>COMPUTERS AT WORK                       | ARENARY<br>6.1 | Integrated Word- and Data-<br>Processing Systems<br>Robert Elliott                                    | 6.2 | Office Automation Technology:<br>Futures<br>James Carlisle                                        |

| DATA BASE SYSTEMS<br>AND<br>COMPUTERS AT WORK                           | 7.1            | <b>Distributed Database Management<br/>Systems — Transaction<br/>Environment</b><br>James Swager      | 7.2 | Database Machines<br>C. Robert Carlson                                                            |

| VISUALS, NATURAL<br>LANGUAGE PROCESSING<br>& ARTIFICIAL<br>INTELLIGENCE | 8.1            | <b>Image Analysis</b><br>K. S. Fu                                                                     | 8.2 | Pictorial Database Models & Query<br>Languages<br>K.S.Fu                                          |

| TUESDAY, MAY 5 — NATIONAL COMPUTER CONFERENCE                           |                                                                                                               |                                                                                 |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| PRINCIPAL TRACKS                                                        | 8:30 to 10:00 AM                                                                                              | 10:15 to 11:45 AM                                                               |

| HARDWARE &<br>ARCHITECTURE                                              | <ul> <li>1.3 Microprocessor Architectures —<br/>What Next?</li> <li>K. Vairavan and Tadao Ichikawa</li> </ul> | 1.4 Perspectives on the History of<br>Computing<br>Paul Armer                   |

| NETWORK TECHNOLOGY<br>AND<br>CAPACITY &<br>PERFORMANCE ANALYSIS         | <b>2.3 Local Networks and the ETHERNET in</b><br><b>Particular (I)</b><br>Gregory T. Hopkins                  | 2.4 Local Networks and the ETHERNET in<br>Particular (II)<br>Gregory T. Hopkins |

| SOFTWARE                                                                | 3.3 Functional Capabilities of Dictionary<br>Systems<br>Belkis Leong-Hong                                     | 3.4 Operating Systems<br>Joseph Leung                                           |

| INFORMATION<br>PROCESSING<br>MANAGEMENT                                 | 4.3 Technology Transfer:<br>Management Issues<br>Conrad Weisert                                               | 4.4 Flanning for Technology Transfer<br>Robert Scheer                           |

| EDUCATION &<br>SOCIETAL ISSUES                                          | 5.3 Computers and the Future of Literacy<br>Frederick Goodman                                                 | 5.4 Issues Concerning National Computer<br>Literacy in 1985<br>Robert Seidel    |

| AUTOMATING THE OFFICE<br>AND<br>COMPUTERS AT WORK                       | 6.3 Word Processing in Litigation &<br>Information Retrieval<br>Haley Fromholz                                | 6.4 Computer Applications in Law Firm<br>Management<br>Haley Fromholz           |

| DATA BASE SYSTEMS<br>AND<br>COMPUTERS AT WORK                           | 7.3 Distributed Database Architecture<br>Hal Uhrbach                                                          | 7.4 Database Practicum<br>Susan Rosenbaum                                       |

| VISUALS, NATURAL<br>LANGUAGE PROCESSING<br>& ARTIFICIAL<br>INTELLIGENCE | 8.3 Intelligent Computer-Aided<br>Instruction<br>Mark Fox                                                     | 8.4 Computer-Based Educational Aids<br>Arthur Melmed                            |

|                    | 1:30 to 3:00 PM                                                                                    | 3:15 to 4:45 PM                                                                                   |

|--------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                    | 1.5 Fault-Tolerant Computing Systems<br>Gerald Masson                                              | 1.6 Contemporary Fault-Tolerant<br>Computer Designs<br>William C. Carter                          |

|                    | <b>2.5 Management of Capacity Planning</b><br>Leonard Lipner                                       | 8.6 Network Capacity Planning<br>Jeffrey A. Bloom                                                 |

|                    | 3.5 Software Reliability in Real-Time<br>Systems<br>Bharat Bhargava and David Clapp                | <b>3.6 PASCAL: Standardization and Extension</b><br>A. Winsor Brown                               |

| PLENARY SESSION    | 4.5 Implementing Technology Transfer<br>Denny O. Wallace                                           | 4.6 Systems Assurance: A Step Beyond<br>EDP Audit<br>James Krause                                 |

| 12:00 NOON-1:00 PM | 5.5 Effects of Computers on Personal Life<br>Abbe Mowshowitz                                       | 5.6 Where is the Story?: A Journalists<br>Panel on Trends in Computing<br>Brad Schultz            |

|                    | <b>6.5 Simulation of Natural Systems</b><br>Roger M. Firestone                                     | 6.6 Future Office Systems<br>Tom Sinopoli                                                         |

|                    | 7.5 Research & Development in<br>Distributed Database Systems<br>Cory Devor                        | 7.6 Database Systems Advances in<br>Medical Systems<br>Meera Blattner                             |

|                    | 8.5 Communicating with Computers in<br>Natural Languages —<br>Current Capabilities<br>Martha Evens | 8.6 Communicating with Computers in<br>Natural Language — Future Promises<br>Norman K. Sondheimer |

| WEDNESDAY, MAY C                                                        | 3 — NATIONAL COMPUTER CONFE                                                                             | irenue                                                                                        |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| PRINCIPAL TRACKS                                                        | 8:30 to 10:00 AM                                                                                        | 10:15 to 11:45 AM                                                                             |

| HARDWARE &<br>ARCHITECTURE                                              | 1.7 Microprogramming — The Challenge of<br>the 1980's (1)<br>Samir S. Husson                            | 1.8 Microprogramming — The Challenge of<br>the 1980's (II)<br>Samir S. Husson                 |

| Network technology<br>And<br>Capacity &<br>Performance analysis         | 2.7 Capacity Planning in a Production<br>Environment<br>James Cooper                                    | 2.8 Simulation of Computer Systems:<br>Software & Hardware<br>Norman Schneidewind             |

| OFTWARE                                                                 | 3.7 Software Maintenance<br>Stephen S. Yau                                                              | <b>3.8 Quantitative Measures for the Quality<br/>of Systems and Programs</b><br>Carma McClure |

| INFORMATION<br>PROCESSING<br>MANAGEMENT                                 | 4.7 Production Process in the Eighties<br>Russ Melton                                                   | 4.8 Business Communication; Security &<br>Vulnerability<br>John Donovan                       |

| EDUCATION &<br>SOCIETAL ISSUES                                          | 5.7 Protection of Proprietary Interests<br>in Software<br>Susan Nycum                                   | 5.8 Planning Agenda for a National Health<br>Information System<br>Marion Ball                |

| AUTOMATING THE OFFICE<br>AND<br>COMPUTERS AT WORK                       | 6.7 Combining Office Automation and Data<br>Processing —<br>Its Technology and Usefulness<br>Dan Zatyko | 6.8 Form Processing in the Office<br>Environment<br>Mitch Zolliker                            |

| DATA BASE SYSTEMS<br>AND<br>COMPUTERS AT WORK                           | 7.7 The Impact of Computing on the<br>Handicapped in the Eighties<br>Samuel C. Lee                      | 7.8 Simulation: A Tool for Business<br>Decision-Making<br>Suresh K. Jain                      |

| VISUALS, NATURAL<br>LANGUAGE PROCESSING<br>& ARTIFICIAL<br>INTELLIGENCE | 8.7 Artificial Intelligence Applications to<br>Electronic Circuit Design<br>Tom Mitchell                | 8.8 Prospects for Artificial Intelligence<br>Application in Industry<br>N. S. Sridharan       |

|                    | 1:30 to 3:00 PM                                                                                                     | 3:15 to 5:15 PM                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|                    | 1.9 Higher Level Microprogramming<br>Languages and Optimization (I)<br>Bruce Shriver                                | 1.10 Higher Level Microprogramming<br>Languages and Optimization (II)<br>Bruce Shriver                  |

|                    | 2.9 Special Session: Pioneer Day —<br>Univac I<br>Carl Hammer                                                       | 2.10 Special Session: Pioneer Day —<br>Univac I<br>Nancy Stern and Henry Tropp                          |

|                    | 3.9 Maintenance of Programs & Systems<br>Ned Chapin                                                                 | <b>3.10 Software Development Facilities</b><br>Louis Brocato                                            |

| PLENARY SESSION    | 4.9 Data Entry Productivity<br>Lawrence Feidelman                                                                   | 4.10 Special Project Management<br>Clifton Merry                                                        |

| 12:00 NOON-1:00 PM | 5.9 Private Sector Policy Issues on the<br>Use of Computer Technology in the<br>Healthcare Industry<br>Karen Duncan | 5.10 Alternative Data Processing<br>Strategies for Hospital Information<br>Systems<br>David Mishelevich |

|                    | 6.9 Definition & Measurement of<br>Application Software Productivity<br>Benn Konsynski                              | 6.10 Electronic Mail: Current<br>Developments<br>Walter Ulrich                                          |

|                    | 7.9 Computer-Assisted Analysis in<br>Energy/Economic Models<br>Harvey Greenberg                                     | 7.10 Large Scale Database Applications<br>Eugene Kozik                                                  |

|                    | <b>8.9 Imaging &amp; Computers</b><br>Diana Merry                                                                   | 8.10 Educational Uses of Personal<br>Computers<br>Michael Tempel                                        |

| PRINCIPAL TRACKS                                                        | 8:30 to 10:00 AM                                                                      | 10:15 to 12:15 PM                                                                                       |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| HARDWARE &<br>ARCHITECTURE                                              | 1.11 Adaptable Architectures<br>Svetlana Kartashev and<br>Steven I. Kartashev         | 1.13 Architecture of Specialized Hardware<br>Systems<br>William E. Farley                               |

| NETWORK TECHNOLOGY<br>AND<br>CAPACITY &<br>PERFORMANCE ANALYSIS         | 8.11 Implementations of Experimental<br>Local Networks<br>William Lidinsky            | 2.12 Local Networks: The Fundamental<br>Technology of Office Automation<br>Harvey Freeman               |

| SOFTWARE                                                                | 3.11 Quality Assurance — An Emerging<br>Technology<br>Gene Altshuler                  | 3.12 The User Interface<br>Howard Lee Morgan                                                            |

| INFORMATION<br>PROCESSING<br>MANAGEMENT                                 | 4.11 Motivation of Computer Personnel<br>J. Daniel Couger                             | 4.18 Recruitment, Retention, &<br>Gertification of Data Processing<br>Professionals<br>Thomas A. Browdy |

| EDUCATION &<br>SOCIETAL ISSUES                                          | <b>5.11 Computer Professional as an Expert</b><br>Witness<br>Alex Hoffman             | 5.12 Library & Business Computer Use:<br>What's the Difference?<br>Peter Lykos                          |

| AUTOMATING THE OFFICE<br>AND<br>COMPUTERS AT WORK                       | 6.11 The Electronic Office: A Futuristic<br>Forecast<br>Richard Federico              | 6.12 Office Automation: The Federal<br>Experience<br>Ira W. Cotton                                      |

| DATA BASE SYSTEMS<br>AND<br>COMPUTERS AT WORK                           | 7.11 Computing & Energy Technology<br>Assessment<br>Ellen M. Leonard                  | 7.18 Automated Testing for Increased<br>Productivity<br>Leonard Gardner and John Savage                 |

| VISUALS, NATURAL<br>LANGUAGE PROCESSING<br>& ARTIFICIAL<br>INTELLIGENCE | 8.11 Recent Computer Advances in<br>Legislative Reapportionment<br>Lee Papayanopoulos | 8.12 Applications of Artificial<br>Intelligence to Law<br>L. Thorne McCarty                             |

| PRINCIPAL TRACKS                                                        | 1:30 to 3:00 PM                                                                              | 3:15 to 4:45 PM                                                                                   |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| HARDWARE &<br>ARCHITECTURE                                              | 1.13 Single Chip Computers — Where Are<br>They Headed?<br>K. S. Padda                        | 1.14 The Application of Peripheral Array<br>Processors<br>Walter J. Karplus                       |

| NETWORK TECHNOLOGY<br>AND<br>CAPACITY &<br>PERFORMANCE ANALYSIS         | 2.13 Use of Models in Capacity Planning<br>Satish K. Tripathi                                | 8.14                                                                                              |

| Software                                                                | 3.13 The Public Release of Smalltalk-80<br>Daniel H. Ingalls, Jr.                            | 3.14 Computer-Based Tools for Software &<br>Systems Engineering<br>Gerald Estrin and Ray Houghton |

| INFORMATION<br>PROCESSING<br>MANAGEMENT                                 | 4.13 User Requirements Analysis<br>Raymond Yeh                                               | 4.14 A Survey of Project Management<br>Software Packages<br>Linda Taylor                          |

| EDUCATION &<br>SOCIETAL ISSUES                                          | 5.13 Developing Software Engineers in<br>Industry<br>Pei Hsia                                | 5.14 Developing Software Engineers in<br>the Universities<br>Frederick E. Petry                   |

| AUTOMATING THE OFFICE<br>AND<br>COMPUTERS AT WORK                       | 6.13 Choosing a Computer Language for a<br>First Problem-Solving Course<br>Robert J. McGlinn | 6.14                                                                                              |

| DATA BASE SYSTEMS<br>AND<br>COMPUTERS AT WORK                           | 7.13 Computing Applications in Magnetic<br>Fusion Energy Research<br>John T. Hogan           | 7.14 Computational Methods in Inertial<br>Confinement Nuclear Fusion<br>Keith A. Taggart          |

| VISUALS, NATURAL<br>LANGUAGE PROCESSING<br>& ARTIFICIAL<br>INTELLIGENCE | 8.13 Expert Systems and Knowledge<br>Engineering<br>N. S. Sridharan                          | 8.14                                                                                              |

# CONTENTS

| Preface                                                                                                                           | v   |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| IntroductionAlex Orden                                                                                                            | vi  |

| COMPUTER HARDWARE AND ARCHITECTURE                                                                                                |     |

| Software sympathetic chip set design<br>Richard F. Hobson                                                                         | 3   |

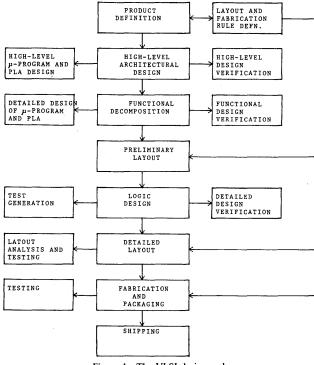

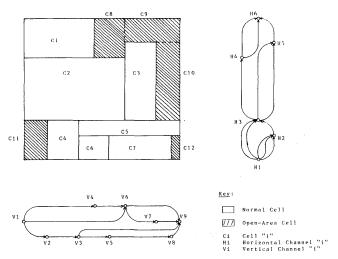

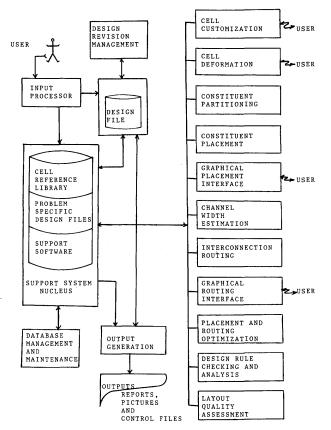

| A computer-aided VLSI layout system<br>W. A. Dees, K. M. Parmar, A. Goyal, R. Y. Tsui, B. D. Rathi, and R. J. Smith, II           | 11  |

| A multiprocessor description language<br>William T. Overman, Stephen D. Crocker, and Vittal Kini                                  | 19  |

| Fault tolerance by means of external monitoring of computer systems                                                               | 27  |

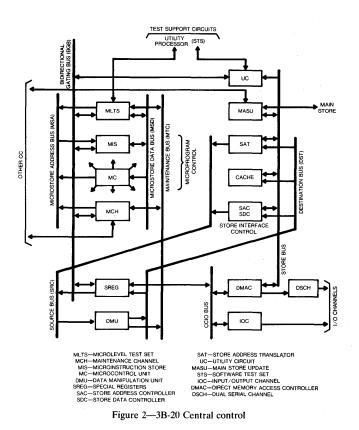

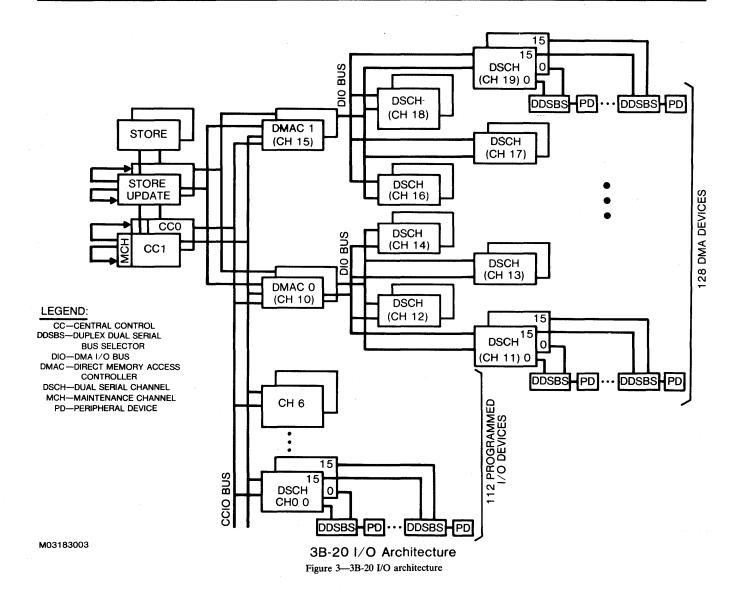

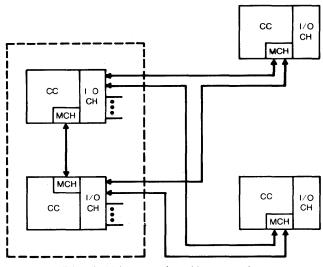

| The fault-tolerant 3B-20 Processor<br>L. E. Gallaher and W. N. Toy                                                                | 41  |

| Firmware engineering: Methods and tools for firmware specification and design                                                     | 49  |

| New directions for micro- and system architectures in the 1980s                                                                   | 57  |

| Microprogramming—The challenges of VLSI<br>Alice C. Parker and Wayne T. Wilner                                                    | 63  |

| Vertical and outboard migration—A progress report<br>Andrew Heller and Andries van Dam                                            | 69  |

| Firmware testing and test data selection                                                                                          | 75  |

| Specifying target resources in a machine independent higher level language<br>Scott Davidson and Bruce D. Shriver                 | 81  |

| The design of a firmware engineering tool: the microcode compiler                                                                 | 87  |

| Microcode compaction: Looking backward and looking forward<br>Joseph A. Fisher, David Landskov, and Bruce D. Shriver              | 95  |

| V-Compiler: A next-generation tool for microprogramming<br>Dave Patterson, Ross Goodell, Michael D. Poe, and Simon G. Steely, Jr. | 103 |

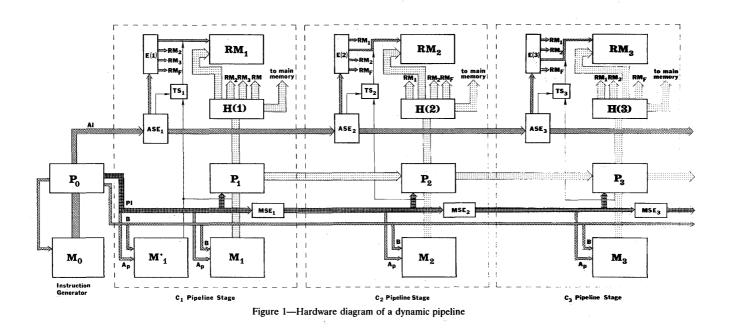

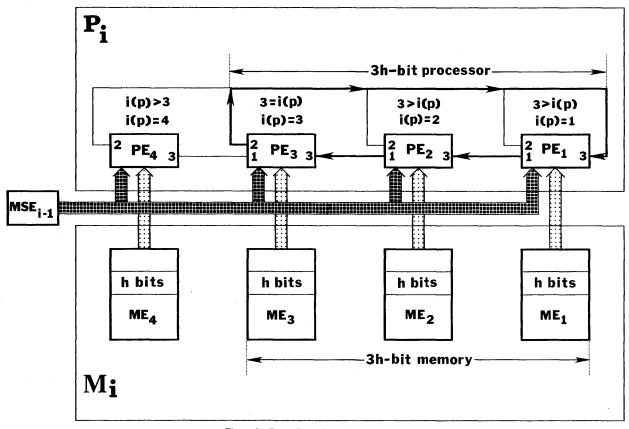

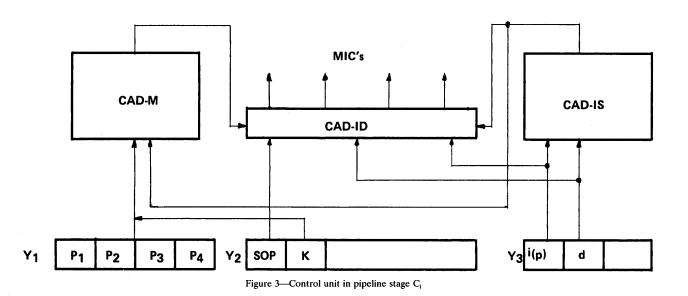

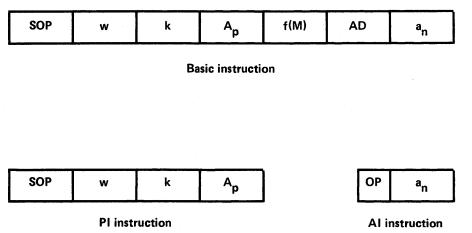

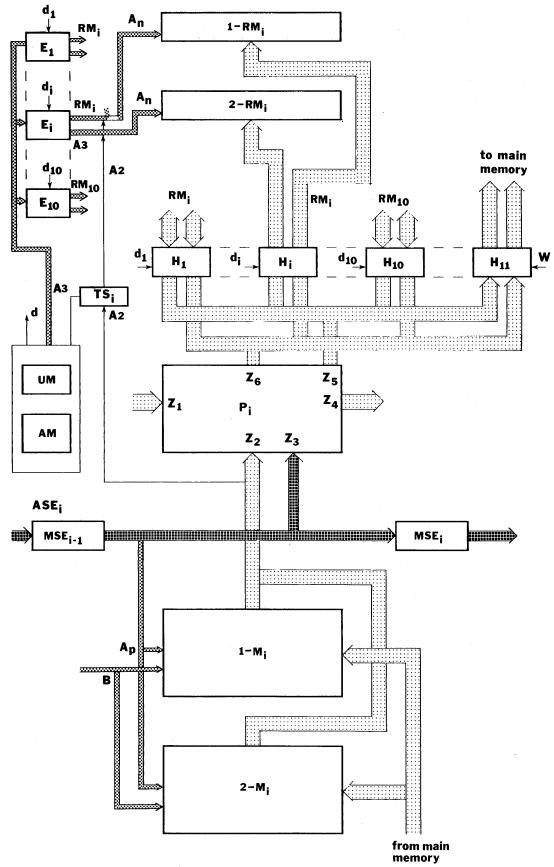

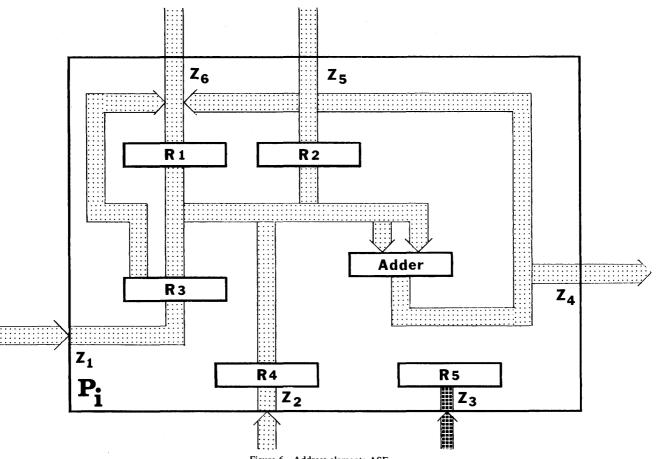

| Adaptable pipeline system with dynamic architecture<br>Svetlana P. Kartashev and Steven I. Kartashev                              | 111 |

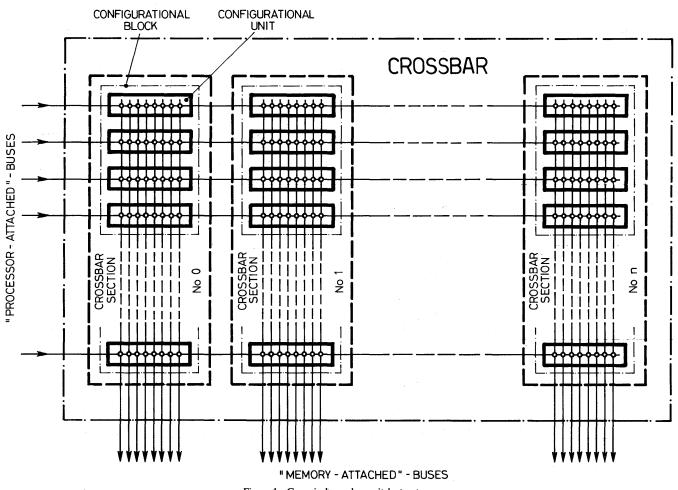

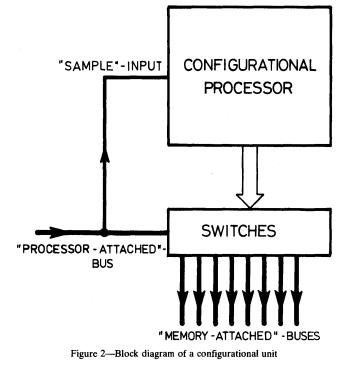

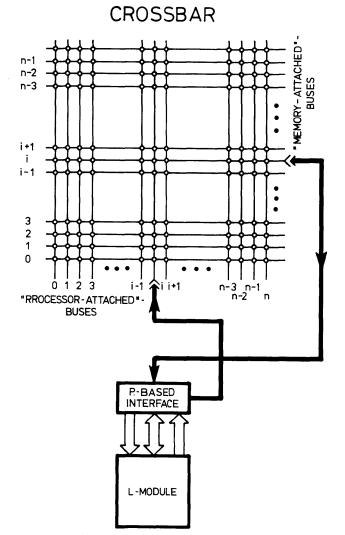

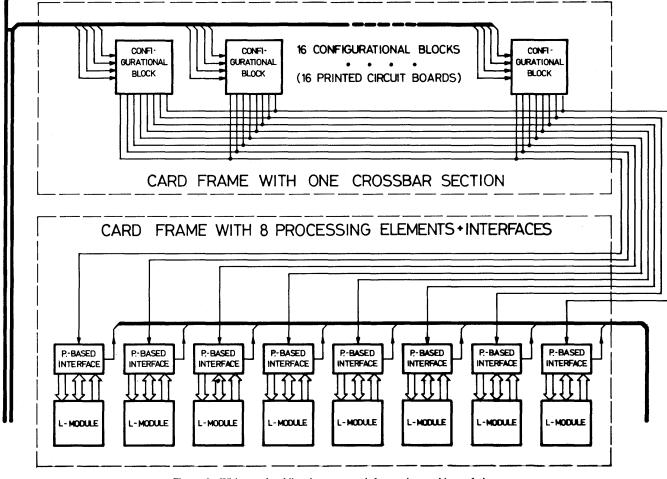

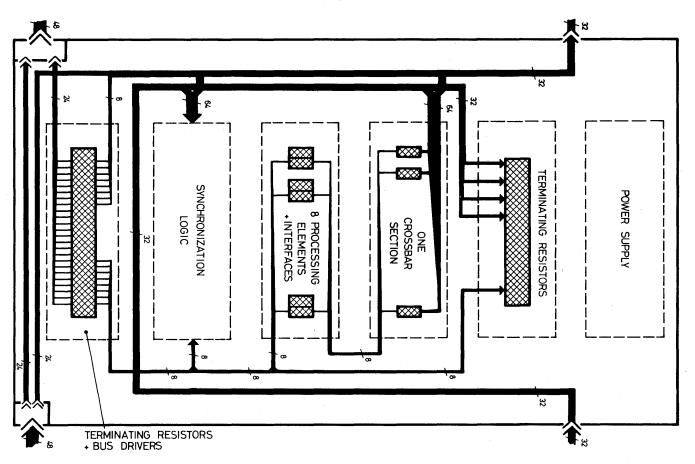

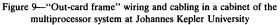

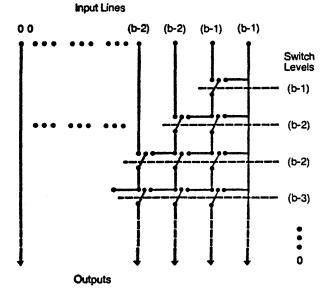

| Modular crossbar switch for large-scale multiprocessor systems—Structure and implementation<br>Bernhard Quatember                 | 125 |

| Some potential deadlocks in layered communications architectures<br>Joseph Hellerstein and Wesley W. Chu                          | 137 |

| General-purpose integrated indexing circuits—A proposalA. C. D. de Figueiredo                                                     | 141 |

| The VALI (Variable Language Interpreter) James D. Mooney                                                                                    | 145 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| The architecture of MANIP—A parallel computer system for solving NP-<br>complete problems                                                   | 149 |

| Parallel sorting machines: Their speed and efficiency<br>Leon E. Winslow and Yuan-Chieh Chow                                                | 163 |

| NETWORK TECHNOLOGY                                                                                                                          |     |

| Packet communication of online speech<br>Danny Cohen                                                                                        | 169 |

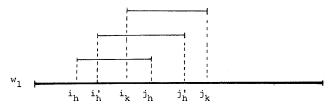

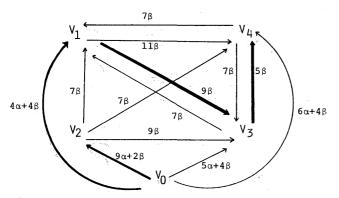

| Highlights of a group effort in algorithmic development for packet-switched voice networks                                                  | 177 |

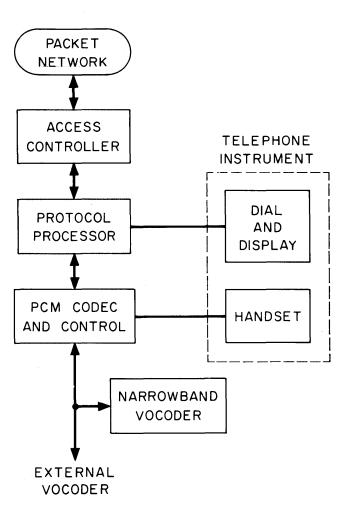

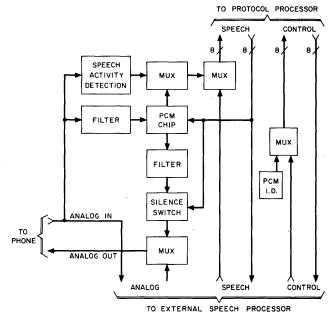

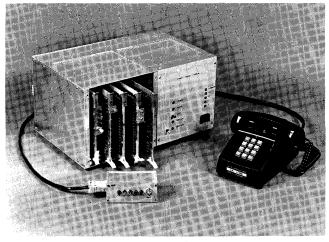

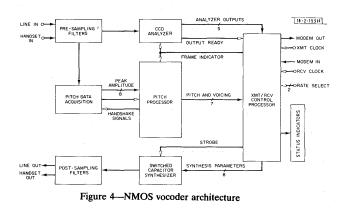

| A modular approach to packet voice terminal hardware design<br>G. C. O'Leary, P. E. Blankenship, J. Tierney, and J. A. Feldman              | 183 |

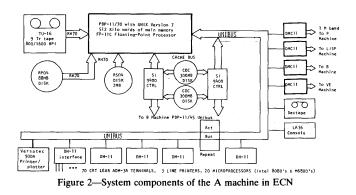

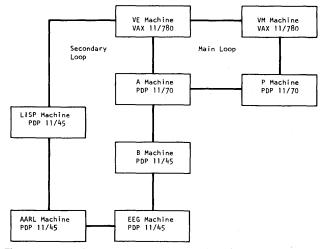

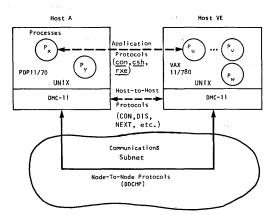

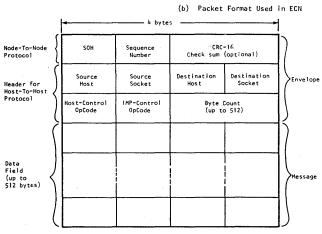

| Engineering computer network (ECN): A hardwired network of UNIX computer systems                                                            | 191 |

| A protocol for a new double-loop computer network and its implementation<br>S. Leventis, G. Papadopoulos, S. Koubias, and J. Constantinides | 203 |

| ILLINET—A 32 Mbits/sec. local-area network<br>W. Y. Cheng, S. Ray, R. Kolstad, J. Luhukay, R. Campbell, and J. W-S. Liu                     | 209 |

| SOFTWARE                                                                                                                                    |     |

| A survey of currently implemented Pascal extensions<br>T. N. Turba and S. H. Costello                                                       | 217 |

| A standard tool for information resource management                                                                                         | 225 |

| SAGA: A system to automate the management of software production                                                                            | 231 |

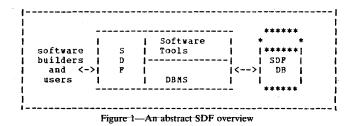

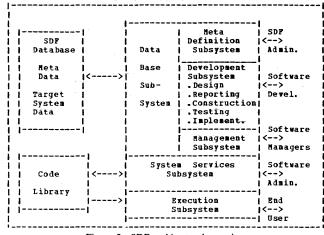

| The development facility approach to improved software development<br>David W. Johnson                                                      | 235 |

| CARL—Experience of an application using clusters<br>E. Levinson, L. S. Levy, and J. B. Salisbury                                            | 241 |

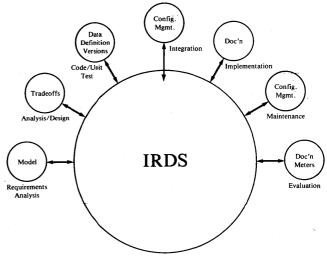

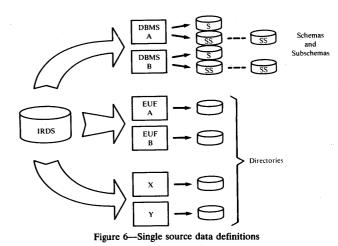

| The software configuration management database<br>Edgar H. Sibley, P. Gerard Scallan, and Eric K. Clemons                                   | 249 |

| EUCLID—A language for compiling quality software<br>David B. Wortman, Richard C. Holt, James R. Cordy, David R. Crowe, and Ian H. Griggs    | 257 |

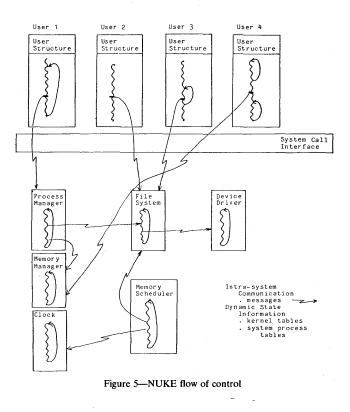

| The design and implementation of a new UNIX kernel<br>Charles Crowley                                                                       | 265 |

| A security policy for a profile-oriented operating system<br>Charles R. Young                                                               | 273 |

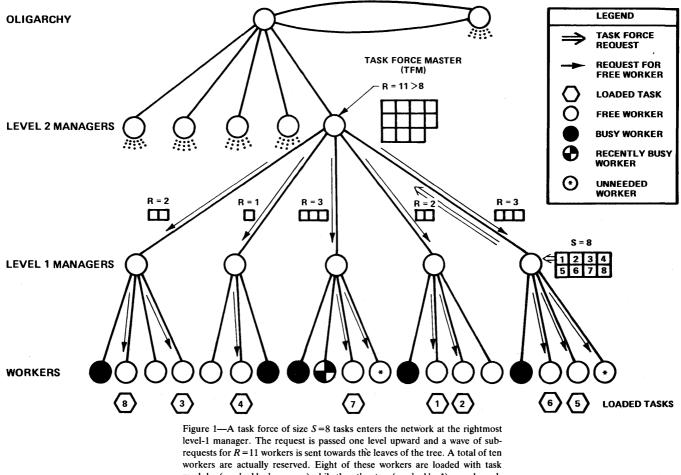

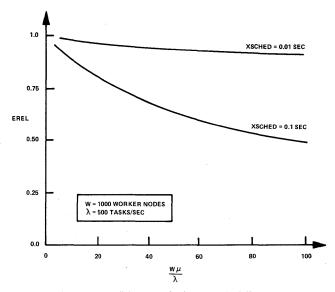

| Distributed task force scheduling in multi-microcomputer networks                                                                           | 283 |

| The assignment of computational tasks among processors in a distributed system                                                              | 291 |

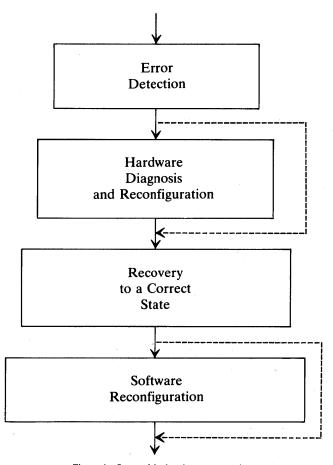

| Software reliability in real-time systems                                                                                                   | 297 |

| A state- and time-dependent error occurrence-rate software reliability model with imperfect debugging<br>J. G. Shanthikumar                 | 311 |

.

| On the complexity of measuring software complexity<br>G. Michael Schneider, Robert L. Sedlmeyer, and Joe Kearney              | 317 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Quantitative measures of MIS quality assurance during hardware conversion                                                     | 323 |

| Taking the measure of program complexity         Jean Cochrane Zolnowski and Dick B. Simmons                                  | 329 |

| Salvaging your software asset (tools based maintenance)<br>Michael J. Lyons                                                   | 337 |

| Maintenance is a management problem and a programmer's opportunity                                                            | 343 |

| Productivity in software maintenance                                                                                          | 349 |

| Improving software testing in large data processing organizations                                                             | 353 |

| Compiler validation—An assessment                                                                                             | 361 |

| An approach to transfer verification and validation technology                                                                | 367 |

| Easy interactive access to batch image analysis software                                                                      | 375 |

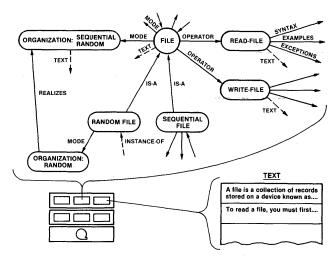

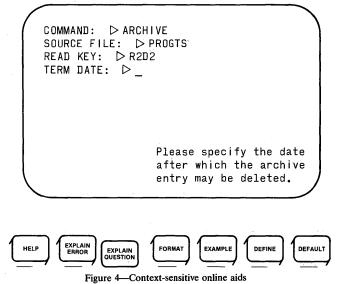

| A unified approach to online assistance<br>Nathan Relles, Norman K. Sondheimer, and Giorgio Ingargiola                        | 383 |

| An experimental system to support a very high level user interface                                                            | 389 |

| Principles of good software specification and their implications for specification languages                                  | 393 |

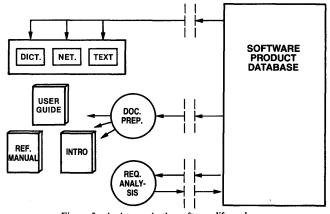

| Modular documentation: A software development tool                                                                            | 401 |

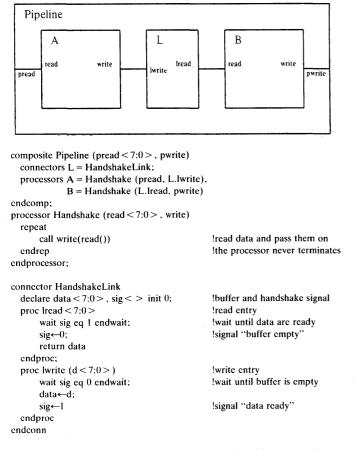

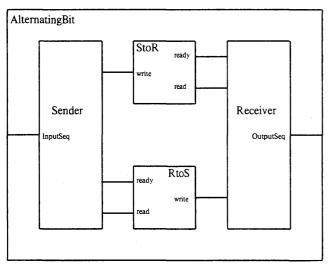

| Specification technique for parallel processing: Process-data representation                                                  | 407 |

| A tiny portable language-independent macroprocessor and some applications                                                     | 415 |

| CAPACITY AND PERFORMANCE ANALYSIS                                                                                             |     |

| Finite queueing approximation techniques for analysis of computer systems<br>Dimitris A. Protopapas                           | 423 |

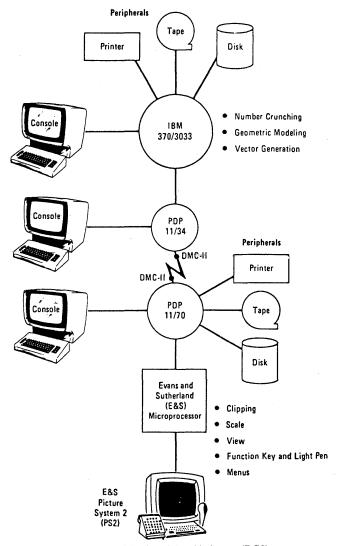

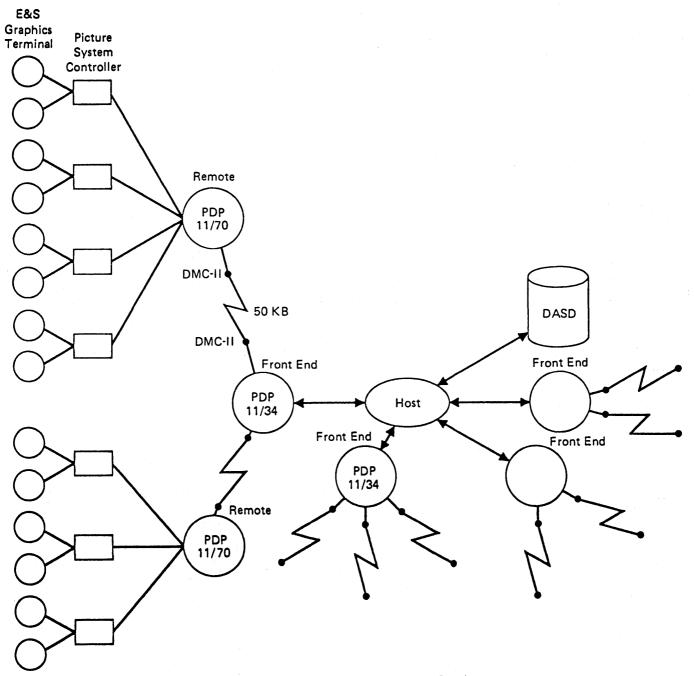

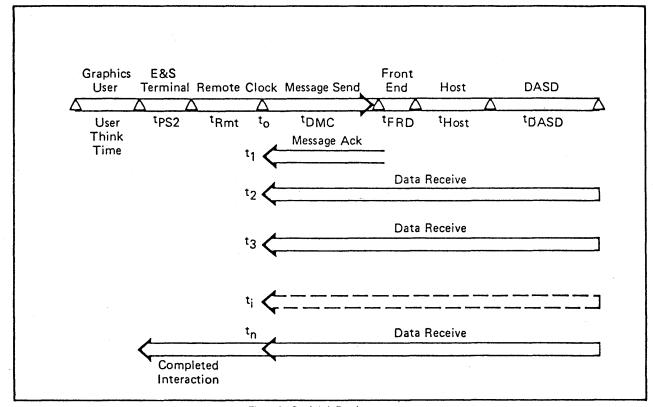

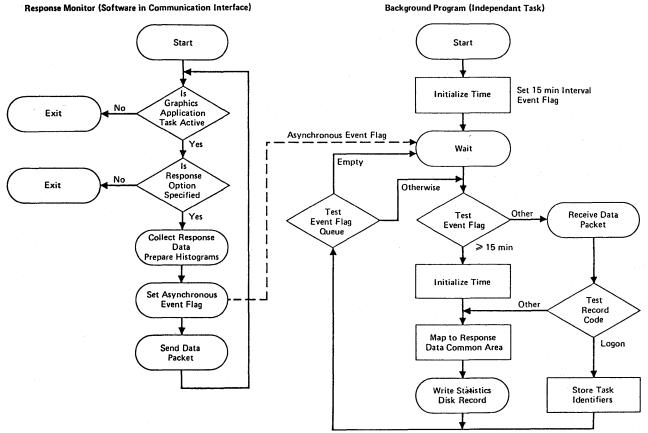

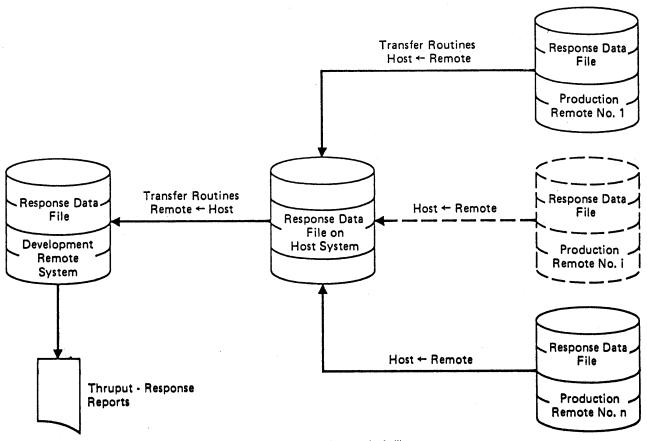

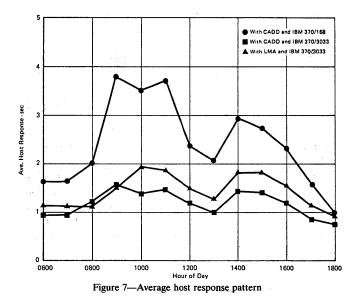

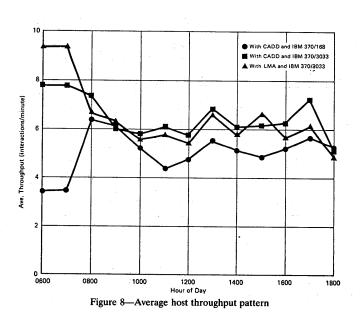

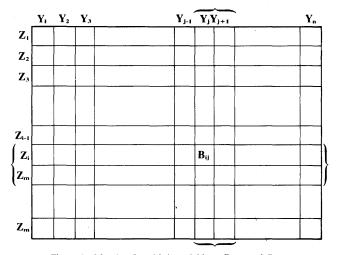

| Throughput-response measurements in a distributed CAD/CAM processing network                                                  | 431 |

| DATABASE SYSTEMS                                                                                                              |     |

| Effective inference control mechanisms for securing statistical databases                                                     | 443 |

| Using partitioned databases for statistical data analysis<br>Ruven Brooks, Meera Blattner, Zdzislaw Pawlak, and Eamon Barrett | 453 |

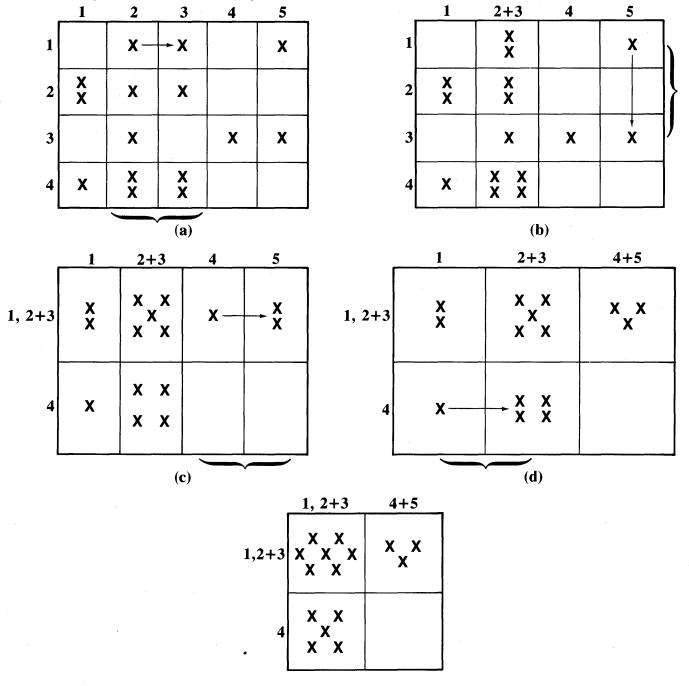

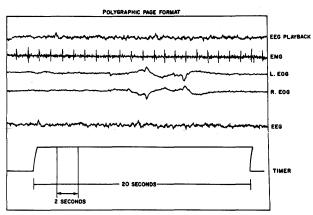

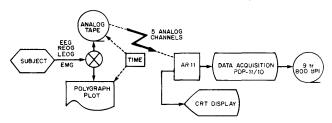

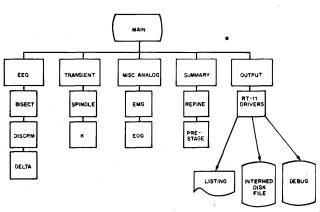

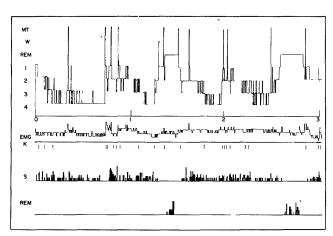

| Development of an automatic sleep EEG analysis and staging system                                                             | 459 |

•

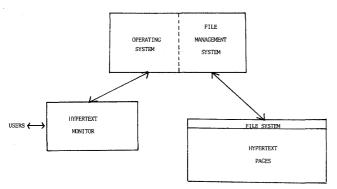

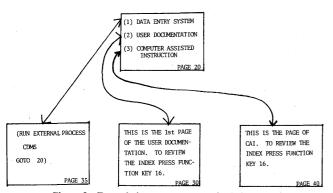

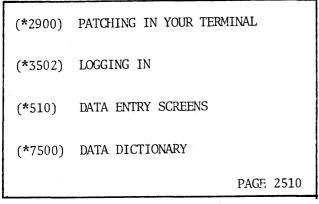

| Embedding an information system within a generalized network environment<br>Darrell L. Ward                                                                                                 | 463 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| The design of the Clinical and Research Information System for Psychiatry<br>Ruven Brooks                                                                                                   | 469 |

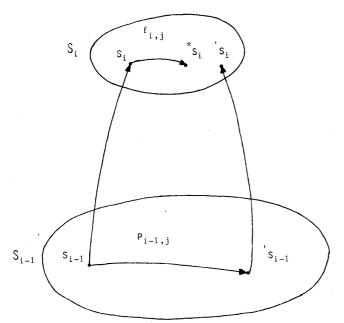

| A concurrency control algorithm in a distributed environment<br>Paul Decitre                                                                                                                | 473 |

| An alternative approach to distributed database updatingRichard J. Greene                                                                                                                   | 481 |

| Multibase—integrating heterogeneous distributed database systems<br>John Miles Smith, Philip A. Bernstein, Umeshwar Dayal, Nathan Goodman, Terry Landers,<br>Ken W. T. Lin, and Eugene Wong | 487 |

| Architecture of a distributed database information resourceJames R. Swager                                                                                                                  | 501 |

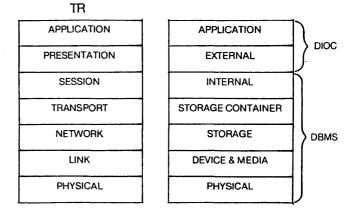

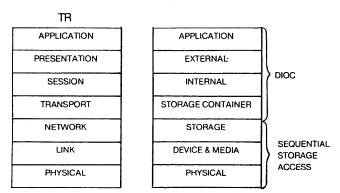

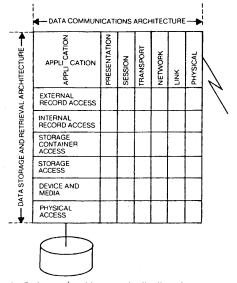

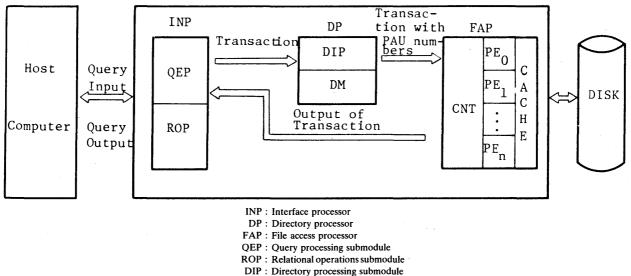

| Optimization of the file access method in content-addressable database access machine (CADAM)<br>Sadayuki Hikita, Haruaki Yamazaki, Kiyoshi Hasegawa, and Yutaka Matsushita                 | 507 |

| Parallel sort and join for high speed database machine operations                                                                                                                           | 515 |

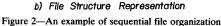

| Highly parallel associative search and its application to cellular database machine design                                                                                                  | 521 |

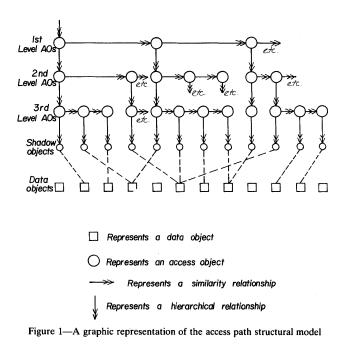

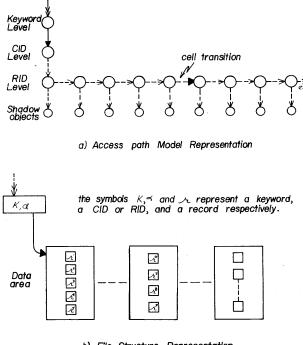

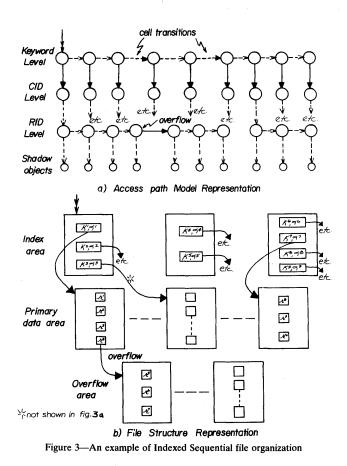

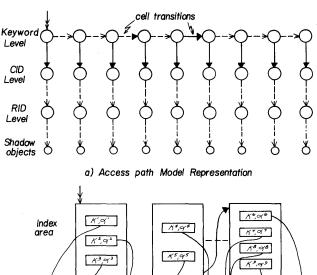

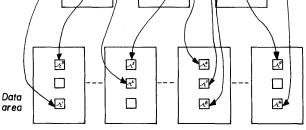

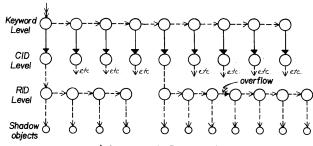

| A generalized database access path model                                                                                                                                                    | 529 |

| Database programming with data abstractions                                                                                                                                                 | 537 |

| Feature analysis of selected database recovery techniques                                                                                                                                   | 543 |

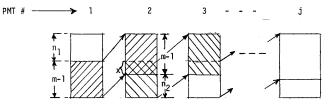

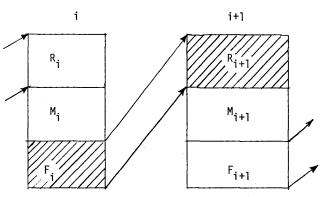

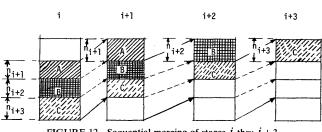

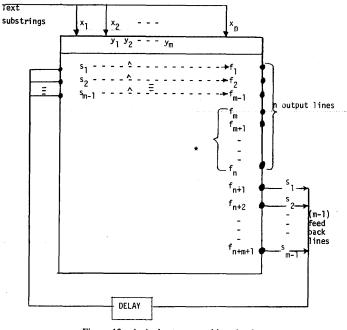

| Data compression procedures utilizing the similarity of data<br>Yahiko Kambayashi, Narao Nakatsu, and Shuzo Yajima                                                                          | 555 |

| INFORMATION PROCESSING MANAGEMENT                                                                                                                                                           |     |

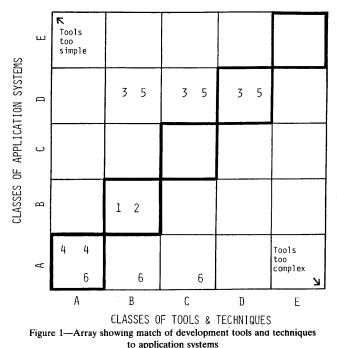

| Choosing application development tools and techniques<br>V. Kevin Whitney and Jane G. Morse                                                                                                 | 565 |

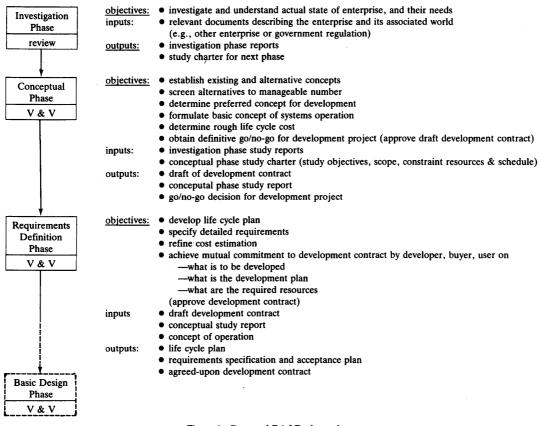

| A software requirements analysis and definition methodology for business data processing<br>Isao Miyamoto and Raymond T. Yeh                                                                | 571 |

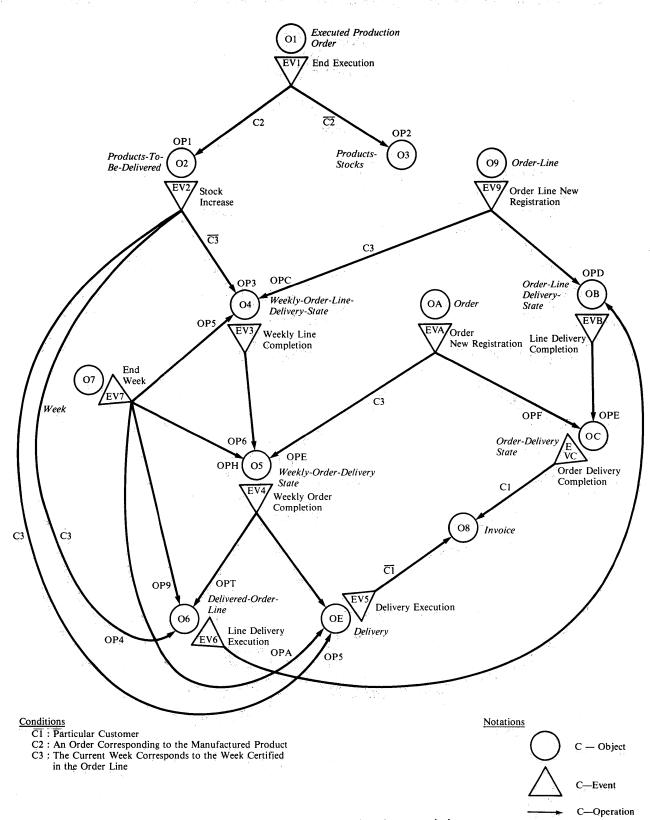

| A methodology for information system design<br>Colette Rolland                                                                                                                              | 583 |

| EDUCATION AND SOCIETAL ISSUES                                                                                                                                                               |     |

| CSDP: A model for continuing education in data processing<br>Dennis M. Oliver, Robert A. Rouse, and Robert J. Benson                                                                        | 593 |

| People teaching people: A cooperative education venture<br>Edwin F. Kerr                                                                                                                    | 597 |

| Computers and the future of literacy<br>Frederick L. Goodman                                                                                                                                | 601 |

| COMPUTERS AT WORK                                                                                                                                                                           |     |

| Keeping CAI humane in the humanities                                                                                                                                                        | 605 |

•

| The effects of computers on library staff and users: How can the administrator cope?                                                                                                                                                 | 609 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Libraries as local database producers                                                                                                                                                                                                | 613 |

| Data files as library materials: Policies, procedures, and politics                                                                                                                                                                  | 617 |

| Computerized weighted voting reapportionment<br>L. Papayanopoulos                                                                                                                                                                    | 623 |

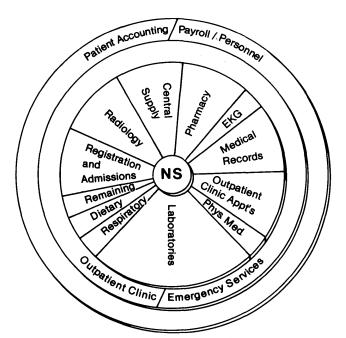

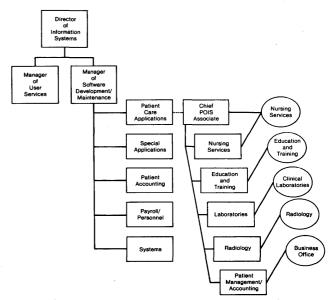

| Hospital information systems tutorial: A guide for computer scientists and practitioners                                                                                                                                             | 631 |

| VISUALS, NATURAL LANGUAGE PROCESSING, AND ARTIFICIAL INTELLIGENCE                                                                                                                                                                    |     |

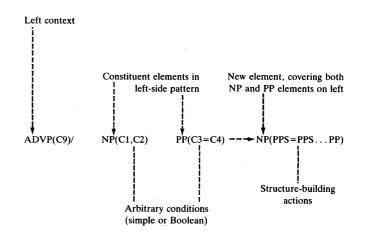

| Issues in the development of natural language front-ends<br>James Hendler, Thomas P. Kehler, Paul Roller Michaelis, Brian Phillips, Kenneth M. Ross,<br>and Harry R. Tennant                                                         | 643 |

| Text-critiquing with the EPISTLE system: An author's aid to better syntax<br>Lance A. Miller, George E. Heidorn, and Karen Jensen                                                                                                    | 649 |

| Shifting to a higher gear in a natural language system<br>Bozena Henisz Thompson and Frederick B. Thompson                                                                                                                           | 657 |

| Computer speech for people with cerebral palsy Jay Hewitt                                                                                                                                                                            | 663 |

| GRASS3, a language for interactive graphics                                                                                                                                                                                          | 665 |

| VISION II: A dynamic raster-scan display<br>Robert Rocchetti                                                                                                                                                                         | 671 |

| The development of the reactor safety film                                                                                                                                                                                           | 677 |

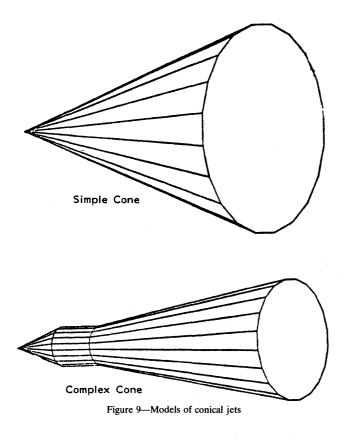

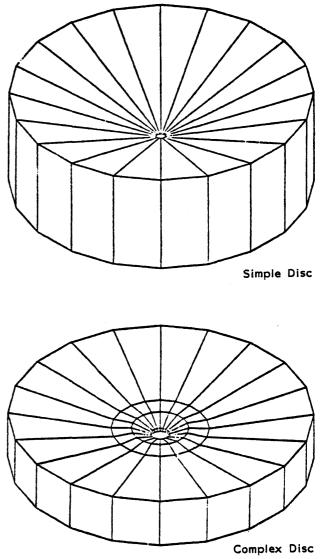

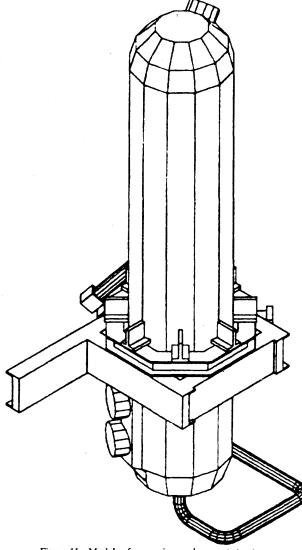

| The MODEL/IMAGES2 system: An application of computer graphics and three-dimensional geometric modeling to the jet impingement problem                                                                                                | 681 |

| The applications of artificial intelligence to law: A survey of six current projects<br>Sandra Cook, Carole D. Hafner, L. Thorne McCarty, Jeffrey A. Meldman, Mark Peterson,<br>N. S. Sridharan, James A. Sprowl, and D. A. Waterman | 689 |

| An automated reasoning system<br>L. Wos, S. K. Winker, and E. L. Lusk                                                                                                                                                                | 697 |

~

7

## COMPUTER HARDWARE AND ARCHITECTURE

### Software sympathetic chip set design

by RICHARD F. HOBSON Simon Fraser University Burnaby, British Columbia

#### ABSTRACT

The current status of special function unit (SFU) use in microcomputer systems is reviewed. Also outlined are areas where more sophisticated SFUs can be used to improve low- and high-level software environments in a microcomputer system. A structured machine model is presented to help containerize and control classes of software and hardware artifacts.

#### INTRODUCTION

With the 1980's comes an era wherein hardware modularity, specialization, and structure are closing in on the software territory of the 1970's. To simplify and speed up complex microcomputer software systems, more functionality and control are being packaged in hardware or firmware controlled specialized function units (SFUs). SFUs are appearing either as isolated performance enhancement devices or as part of an announced chip set. Ad hoc microcomputer hardware module expansion may lead to more of the architecture irregularities plaguing software engineers. To avoid this, we should look seriously at architectures based on a coherent structure of such modules.

In this article we review the current status of SFU use in microcomputer systems. We also outline areas where more sophisticated SFUs can be used to improve low- and highlevel software environments in a microcomputer system. To this end, a model system is described. The model is partially motivated by an evaluation of the potential of a scientific arithmetic processor chip relative to a typical first-generation microcomputer (see Appendix I). While a performance factor increase of 3 or 4 was expected, the actual factor was closer to 10. More recently, the Intel 8087 has raised this factor to 100. Speed notwithstanding, we must strive to avoid strikingly awkward software sequences, whether to perform operations on data types that are not natural to a microprocessor (e.g., floating-point data) or to interface one chip with another. One cannot just glue LSI chips together and retain, at the VLSI level, the same software appeal that each chip may have enjoyed individually.

The status of language-oriented computer design is briefly reviewed in Appendix II.

#### CURRENT TRENDS

LSI specialized function units have become the dominant choice for arithmetic processing, floppy- and hard-disk control, CRT refresh and control, communication protocol, DMA control, and memory management.<sup>1</sup> Single-chip computers with on chip ROM and RWM also fall into this category. The latter are best suited for small dedicated tasks.<sup>2</sup> With such "support staff" potential, a central processor can have more time to execute higher-level control functions for an operating system or an application package. Code sections will also be shorter, more to the point, and more reliable.

The latest microprocessors have been enhanced in a variety of ways over their precursors.<sup>3-7</sup> Prominent 16-bit contenders portray traditional register architecture philosophy more than HLL architecture philosophy (see Table I). Their new bussharing protocols are significant because multiple SFUs can be set up with a variety of processor interconnection schemes.

The main mode of communication between microprocessors and special devices is via I/O sequences of the type described in Appendix I (see also Wakerly<sup>8</sup>). The next most common mode would be a message buffer, with cooperating processors either sharing the same buses or separated by bus arbitration hardware.<sup>9</sup> Ultimately we would like to be able to configure a microcomputer system with a collection of SFUs in such a way that the instruction set can be dynamically expanded to include new functions. The Intel 8086's ESCAPE mechanism is such a technique.

What we have seen so far is a packaging of clearly identifiable functions. What is not clearly identifiable as a function, notably high-level program and environment control, has been left over for the general-purpose microprocessor and the programmer. The next step is to identify hardware control, program control, data control, operating system control, and language interpretation as functional areas; hence potential candidates for LSI modules. Research is needed to iron out communication and high-level language/environment support problems before functional module unification will be achieved.

|                             |              | Processors |             |

|-----------------------------|--------------|------------|-------------|

| Features                    | <b>I8086</b> | M68000     | Z8000       |

| Base relative addressing    | Т            | Т          | Т           |

| Memory management           | F            | New chip   | New chip    |

| Memory segmentation         | Partial      | Partial    | Partial     |

|                             |              | (New chip  | , New chip) |

| Multiprocessor bus          | Т            | Т          | Т           |

| Dedicated coprocessors      | Т            | F          | F           |

| State marking (on stack)    | F            | Т          | Т           |

| Unused opcode trap          | F            | Т          | Т           |

| Opcode expansion            | F            | Via trap   | Via trap    |

| Supervisor state            | F            | Т          | Т           |

| Floating-point instructions | F            | To come    | F           |

| Floating-point processor    | New chip     | F          | F           |

| Channel processor           | New chip     | F          | F           |

| Instructions/data separate  | Optional     | Optional   | Optional    |

#### TABLE I—Some architecture features employed in prominent new LSI microprocessors

#### TOWARD A PHILOSOPHY FOR CHIP SET SPECIALIZATION

Basic computer organization is often introduced in terms of logical functional units for input, output, memory, arithmetic and logic, and control. In general we do not think of these units as constituting a multiple-processor or distributedprocessor machine. Nor, for the most part, do we care. Enter LSI technology. Now digital systems must be packaged as functional units for cost effectiveness and design simplicity.

How should the logical functions be distributed? What range of functions is relevant?

Since high-level-language (HLL) notation is the preferred way to describe an application, one technique is to identify separable activities that all or many HLLs require for runtime support. These requirements may then influence the resulting architecture,<sup>10</sup> but only part of the architecture. Since languages are simply tools, we should not look exclusively at their requirements. Some applications have requirements that may not be adequately representable with known HLLs. Text editing or word processing, for example, have data structure and real-time interaction requirements that are difficult to describe effectively with conventional HLL techniques. Real-time operating system functions also form a special class. We have heard it said that a semantic gap often exists between machine architecture and programming language features.<sup>39</sup> It is also clear that such a gap exists for programming environments as well. It is the total programming environment that should be considered when designing a multiple-processor chip set-hence, computer architecture that is oriented to a high-level-programming environment rather than to an HLL.

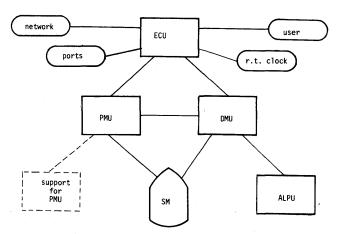

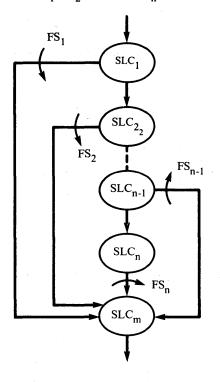

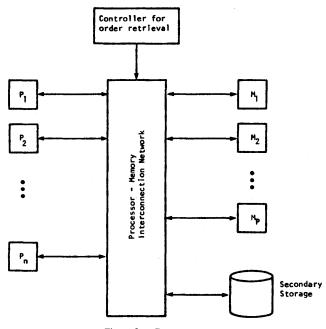

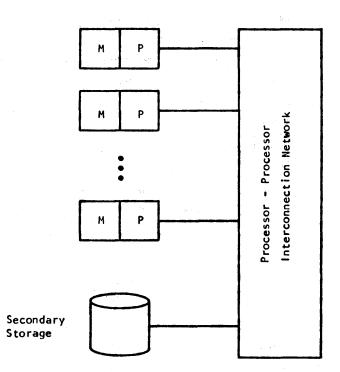

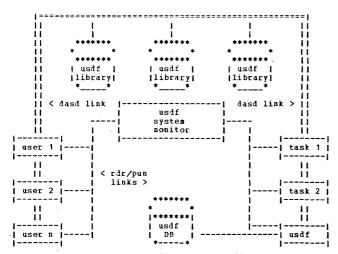

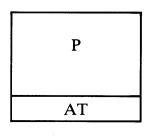

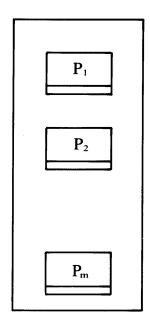

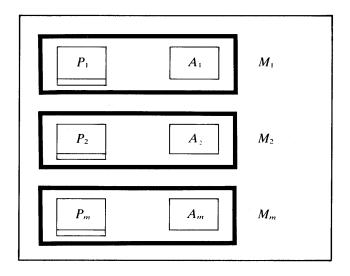

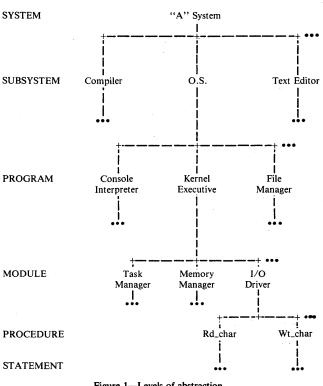

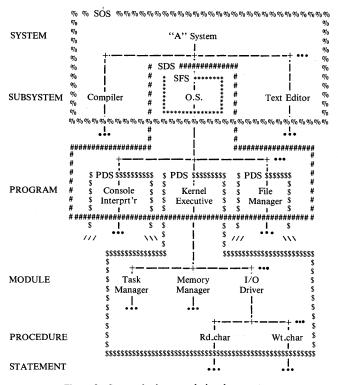

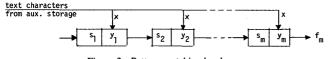

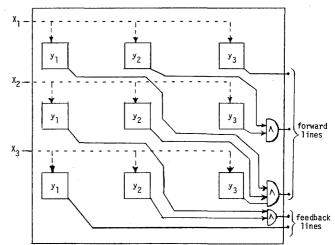

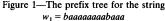

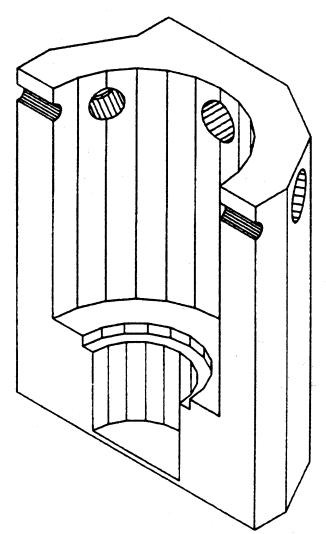

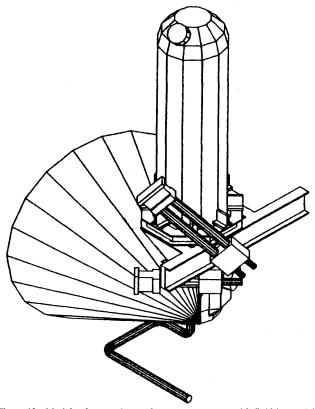

Traditional logical partitioning remains essentially valid. It is the degree of specialization, the sophistication of instructions, and the physical separation of units that is outdated. To begin with, input and output belong to one (or more) separate processor modules, as do other specialized operations. A programming environment is also destitute without sophisticated memory management. Finally, for control, the environment should be managed by a small real-time control processor. To illustrate, consider a specialized unit model (SUM.4) consisting of four units: environment control unit (ECU), program management unit (PMU), data management unit (DMU), and arithmetic/logic processor unit (ALPU). They represent an SFU system hierarchy, as depicted in Figure 1. The following subsections describe some of the functions required for these units to support an HLL-oriented programming environment. The main objectives are

- 1. To reduce the complexity of system software by providing a variety of high-level functions as software primitives or built-in tasks

- 2. To promote structured machine design

- 3. To provide better single user run-time support for a variety of high-level languages and real-time applications

#### ECU

The environment control unit provides operating system functions and high-level I/O interpretation (see Table II).

A small real-time operating system runs in the ECU, the application control system (ACS). ACS contains fixed tasks for all devices that may be attached to SUM.4, e.g., for network control, console graphics, or editing. Provision must be made for transient or user support tasks that may be required to augment the functional capabilities of ACS for different applications—in particular, high-level-language I/O interpretation tasks. Interface "pipes" or tasks for PMU and DMU communication are important parts of ACS.

ECU architecture must be oriented toward variable interval interrupt servicing and I/O translation needs. Many of the existing microprocessors have appropriate features for an ECU, but in terms of LSI rather than VLSI. A user microgrammable or custom VLSI ECU could contain firmware for a complete operating system nucleus.

Figure 1-Block diagram showing the SUM.4 hierarchy

PMU

The program management unit is unique in terms of current microcomputer architecture in that it is the first of several possible processors that may contribute to the interpretation and execution of user code.

In an interpretive mode (e.g., for debugging or supporting a language such as APL), some internal form of the source code is fetched from segment memory (SM), checked for syntax errors, and translated into formatted, directly executed language (DEL) instructions for the DMU to execute. Operations modifying the execution environment, such as proure call, are partially handled by the PMU.

The value of a separate PMU is not so clear for compilable languages. However, if we can get enough overlap between interpretation and execution of a compilable language, there is little reason to compile. Interpreters permit advantages, such as interactive debugging, execution environment protection, and run-time recovery, that cannot reasonably be matched by compilation. Microprocessors have been successfully used to interpret UCSD P-code machine instructions.<sup>36</sup> This experiment gives confidence that two or more "simple" processors with appropriate firmware can be very efficient at interpreting a suitably chosen intermediate form of Pascal, an easily compiled language. Greater benefits should result from more complicated languages. The key phrase here is "suitably chosen intermediate form." As long as run-time errors can be trapped and tied to the offending source statement expression through "reverse compilation," compilation per se is tolerable. Thus, even for compilable languages, the PMU can play an important role.

PMU activities are language-oriented. For multilingual support a user microprogrammable processor is required. This processor needs to manipulate code streams and communicate effectively with segmented memory. Additional special function support may be added to the PMU (see Figure 1).

#### DMU

A data management unit is mainly responsible for controlling operations on various data aggregates. Instructions or instruction bursts are normally fetched from the PMU interface. If the DMU is equipped to execute them directly, it does so; otherwise DMU action centers around providing operand data for the ALPU or ECU to manipulate. Before operation execution is permitted, operand validity must be checked. Such verification is facilitated by the use of data tags.

DMU and PMU design requirements are similar: Both are language dependent; both manipulate data aggregates (assuming that various forms of a program constitute data aggregates). The same processor architecture may thus be used for DMU and PMU units; only their microcode is different.

#### ALPU

Arithmetic and logical functions that the DMU cannot handle efficiently are provided by one or more specially designed units constituting the ALPU. This unit should operate only on

| TABLE | II—A | possible | partitioning   | of   | functions | performed | by |

|-------|------|----------|----------------|------|-----------|-----------|----|

|       |      | vario    | ous specialize | ed 1 | units     |           |    |

| · · · · · · · · · · · · · · · · · · ·                            |

|------------------------------------------------------------------|

| ECU                                                              |

| -Task initiation (with PMU).                                     |

| -Single-step control (with PMU).                                 |

| -User command interpretation.                                    |

| -Service special events (e.g., errors).                          |

| -HLL data formatting.                                            |

| -Peripheral communication.                                       |

| -Special device control (e.g. graphics).                         |

| -Text editing and command input.                                 |

| -Real-time clock control.                                        |

| -Execute I/O subtasks.                                           |

| -Load microcode.                                                 |

| -Test other modules.                                             |

| PMU                                                              |

| -Interpret HLL programs (or a suitable intermediate form).       |

| -Execute procedure CALLs.                                        |

| -Establish environments, manage tasks.                           |

| -Help maintain segmented memory.                                 |

| -Service exceptional conditions.                                 |

| DMU                                                              |

| -Execute DEL instructions from the PMU or ECU interface.         |

| -Verify data operations (e.g., bounds checking).                 |

| -Manipulate operand data for the ECU and ALPU.                   |

| -Perform some functional operations (e.g., data rearrangements). |

| -Help maintain segmented memory.                                 |

| -Report conditions to PMU.                                       |

| ALPU                                                             |

| -The usual scientific calculator functions.                      |

| -Logical functions on strings.                                   |

|                                                                  |

-Adjust automatically to data size change (necessary for APL).

atomic or scalar items and need not have memory-accessing skills if the DMU interface is properly designed. The Intel 8087 is a good example of functional sophistication in this class, but it is too dependent on the Intel 8086.

#### SM

Segmented memory is not treated as a separate unit in this scenario. Memory modeling is, however, an important consideration in the quality of a programming environment. Variable-length containers for procedures and data aggregates greatly simplify run-time memory management firmware. Beyond that, segments can be associated with property lists for database content identification and protection. SM interfacing functions are divided among the DMU and PMU in SUM.4. Memory management is an integral part of interpretation, whereas a separate system is required to be interfaced with compiled code.

#### The unit interface

A number of multimicroprocessor communication schemes have been described in the literature.9, 12-15 For system modu-

```

program EX1 (output);

H = 34; D = .0625; S = 32.; L = 32;

const

SEPARATOR = '-----';

procedure PLOT (var XS, YS: real;

var XO, LIM: integer);

const TWOPI = 6.28318;

X,Y: real; I, N: integer;

var

begin for I: = 0 to LIM do

begin X := XS^*I;

Y:= EXP (-X)^*SIN (TWOPI^*X);

N := ROUND (YS^*Y) + XO;

repeat WRITE (' '); N := N - 1;

until N = 0;

WRITELN ('*');

end;

```

end; {plot}

Figure 2-Pascal program example (see text)

larity and simplicity, I recommend using two or three port memories with an asychronous wait when there is memory contention. Semaphores can be implemented by having a "hog" mode, permitting a processor to retain memory selection beyond one cycle. There are no bus contention problems with this model. Memory port multiplexing can be combined with refresh control and address translation in one cascadable LSI module.

Messages are received indirectly by poling status word locations or directly through signal interrupts.

#### Example

To work with Pascal a user asks the ECU to load the Pascal firmware/software assist package (or it may be loaded implicitly). Figure 2 shows a simple Pascal program adapted from Jensen and Wirth.<sup>17</sup> The program causes a damped sine wave to be plotted along a vertical axis according to supplied scaling parameters. A source operand recoverable, internal format is used to store the program. Variable name literals are stored in a master symbol table for run-time recovery.

The ECU conveys execution requests to the PMU, which then sets up an execution environment, allocates variables, initializes values, and begins sending code to the DMU. An implementer would probably use individual segments for data aggregates such as sets, arrays, and records, whereas scalars would be kept in the variable-length program segment. Environments for more complicated languages can easily be managed.

Built-in procedures such as WRITE and WRITELN are implemented through a task in the ECU. More interesting I/O procedures, such as a plot package, might be entirely implemented through the ECU. This facility permits a smooth interface between language, environment, and hardware.

There are many interesting implementation problems to be solved. For example, should I, the FOR loop variable in Figure 2, be incremented and tested by the PMU or the DMU? Control is simpler if the PMU performs decision-making operations and maintains iteration counters. This means that control variables, such as I, can only be modified by the DMU with the PMU's permission. We see an opportunity here to improve program structure by distinguishing control from action.

To implement time-shared multitasking, timekeeping duties go to the ECU, which notifies the PMU to switch environments. In this case task maintenance is a PMU responsibility.

#### Implementation

Once an instruction set has been chosen, implementation details are irrelevant to most users. In a research environment, one favors microprogrammability because new primitives can easily be added to upgrade a unit. With custom chip fabrication nearing the grasp of lower-volume applications, we can visualize chip sets designed specifically to support a structured architecture.<sup>18, 19</sup> As wafer-scale integration becomes economical, we will probably see the equivalent of these chip sets laid out as individual modules on a single wafer. Indeed, large hardware projects, like large software projects, must be divided into a number of coherent pieces with well-defined interfaces. In the VLSI era, multiple-processor systems will be essential for design simplicity as well as for greater throughput.

With modular hardware design, units can be developed by teams of specialists without relying heavily upon each other. Prototype modules can be implemented on a single PC board with the intention of gradually combining them into a single hybrid package and finally onto one chip.

#### CONCLUSION

The current proliferation of microcomputer hardware needs a focus. As a greater variety of SFUs are produced, we will be faced with organizational problems such as befell software in the past decade. The remedy? Structured architecture. We should think of hardware as a kind of petrified production software system. Hardware design therefore qualifies for all of our software engineering experience.

A structured model has been presented to help containerize and control classes of software and hardware artifacts. I am presently engaged in building a SUM.N (N = 4-6) prototype to study performance, function distribution, communication techniques, and language/environment support.

#### ACKNOWLEDGMENTS

Research support from NSERC of Canada and from a Simon Fraser University President's Research Grant is gratefully acknowledged.

#### APPENDIX I-THE CASE FOR SPECIALIZATION

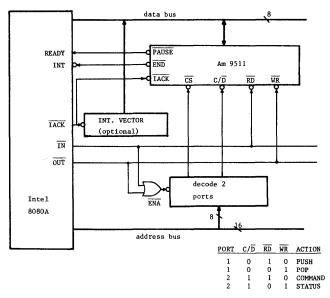

Specialized LSI processor chips have been available for several years. Only recently, however, have microprocessor vendors begun to realize their potential. This section compares the performance of an Intel 8080A microprocessor (MP) with that of Advanced Micro Devices' Arithmetic Processor Unit, the AM9511.<sup>20, 21</sup> Floating-point addition is the benchmark operation. This exercise demonstrates the desirability of LSI special function units because they are much faster than general-purpose processors of the same technology and because, with a well-designed interface, software problems can be greatly reduced.

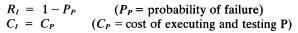

Benchmark data have a 24-bit normalized (sign magnitude form) binary mantissa and a 7-bit 2's complement exponent. FADD, our 8080A floating-point addition subroutine, contains 263 instructions (loops were avoided for speed) and assembles into 361 bytes of code. Operand pointers for the expression Z = X + Y are passed in stream following the CALL. The simplest cost formula for FADD, assuming two positive numbers, can be represented as follows:

| Entry overhead and setup         | : | 76 (8080A clock                         |

|----------------------------------|---|-----------------------------------------|

| Fetch X                          | : | 233 cycles)                             |

| Overhead                         | : | 32                                      |

| Fetch Y                          | : | 233                                     |

| Comparison of exponents and      |   |                                         |

| overhead                         | : | 113                                     |

| Assuming $\exp X - \exp Y = N$ , |   |                                         |

| adjust Y N bits                  | : | 93N + 52 (align                         |

| ,                                |   | mantissas)                              |

| Operation overhead               | : | 400                                     |

| Mantissa addition (no carry)     | : | 125 (no                                 |

| · · · · · ·                      |   | renormalization)                        |

| Mantissa addition (carry)        | : | 225 (1 bit                              |

|                                  |   | renormalization)                        |

| Store results                    | : | 231                                     |

| Exit overhead                    | : | 41                                      |

|                                  |   |                                         |

| typical add                      | : | 1286 (carry, but no                     |

|                                  |   | alignment shift)                        |

| "Fastest" add (without           |   | - , , , , , , , , , , , , , , , , , , , |

| argument passing)                | : | 509 clock cycles                        |

FADD is neither expressive nor conceptual, and it is certainly not software-sympathetic. Fetching the operands requires eight successive sequences of the form

LDAX B STAX D INX B INX D,

consuming 24 clock cycles each. With a block move instruction the movement should only require 10 clock cycles per byte, i.e., five cycles each direction (the 8080A does a twobyte POP in 10 cycles and a two-byte PUSH in 11 cycles<sup>19</sup>). This leads to an improvement factor of 2.4 for operand handling. Another awkward operation for the 8080A is the calculation of 2's complement overflow, although most MPs do include an overflow flag.

For a contrast to the above, consider Advanced Micro Devices' Am9511 arithmetic processing unit (henceforth, the APU). This chip is made from similar *N*-channel silicon gate MOS technology and is rated at the same clock speed (2 MHz). The APU has an 8-by-16- or 4-by-32-level cascading

| TABLE III—A summary | of | AM | 9511 | instructions |

|---------------------|----|----|------|--------------|

|---------------------|----|----|------|--------------|

| (Single, double, | , floating): ADD, SUB, MUL, DIV.                          |

|------------------|-----------------------------------------------------------|

| (floating): SQR  | T, SIN, COS, TAN, ASIN, ACOS, ATAN, LOG,                  |

| LN,              | EXP, PWR.                                                 |

| (other): NOP     |                                                           |

| FIXS             | (convert top of stack [TOS] to single precision integer), |

| FIXD             | (convert TOS to integer double), FLTS, FLTD,              |

| CHSS             | (change sign of integer single on TOS), CHSD, CHSF,       |

| PTOS             | (push integer single TOS to NOS etc.), PTOD, PTOF,        |

| POPS             | (pop integer single NOS to TOS etc.), POPD, POPF,         |

| XCHS             | (exchange integer single NOS with TOS), XCHD, XCHF,       |

| PUPI             | (push floating point constant pi onto stack).             |

arithmetic stack in reverse Polish notation calculator tradition. As can be seen from Table III, an impressive list of fixed or floating-point operations are available in comparison to an MP instruction set. Floating-point addition for the APU has a listed execution time range of 56-350 clock cycles (not counting argument passing). The lower figure is comparable to our above figure for the fastest add (not counting argument passing), 509 clock cycles. At the other extreme, the APU can do any addition within 350 clock cycles. Our benchmark requires up to 2748 clock cycles to add two positive numbers, including a 23-bit exponent equalization shift. If mixed signs are permitted, renormalization requires an additional 126 cycles per bit. Not counting operand fetch and store (for either unit), the APU is an order of magnitude faster than an 8080A at floating-point addition! The APU obtains this advantage through an optimized register level architecture and because irrelevant instruction fetches are avoided. Because more storage, stack operations, and instruction fetches are involved, other APU operations should also be considerably faster than equivalent 8080A operations. Operand passing is equally bad for both benchmarks because the 8080A was not equipped for block data transfer. Recently, the Intel 8087 arithmetic processor stretched this difference in performance by another order of magnitude!<sup>40</sup>

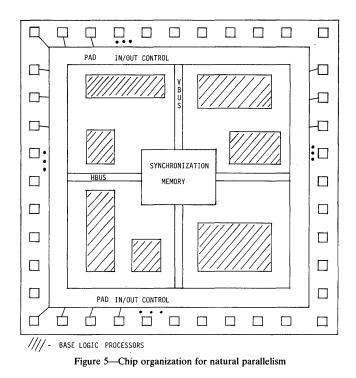

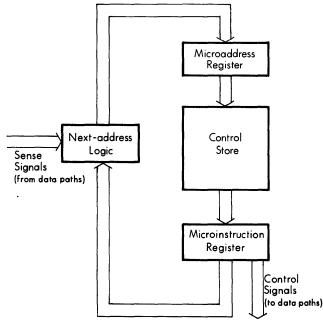

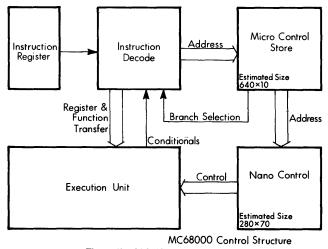

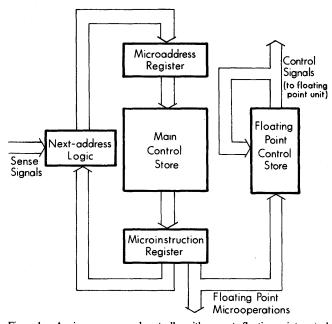

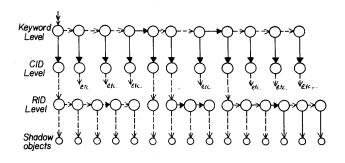

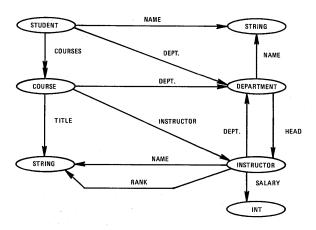

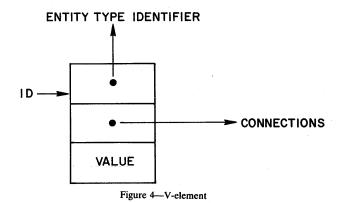

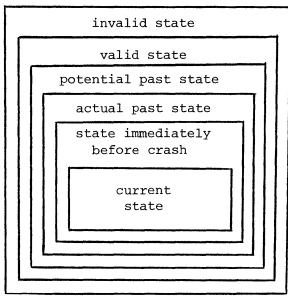

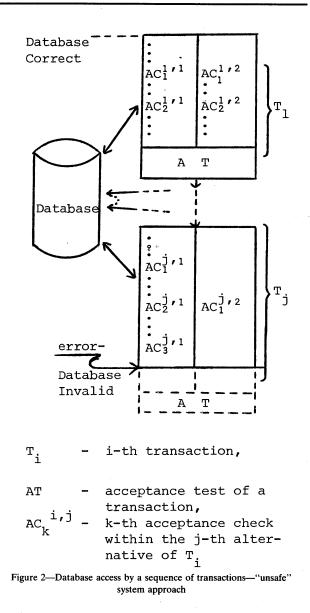

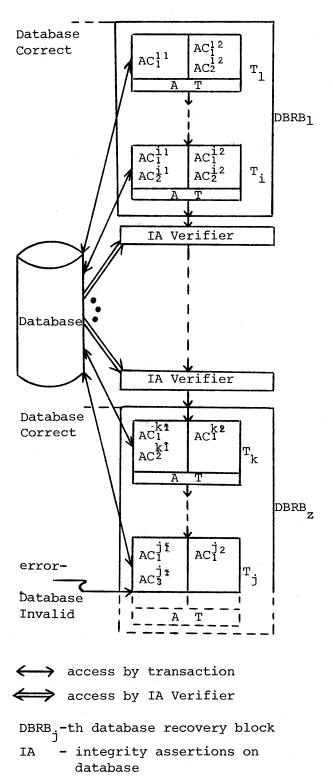

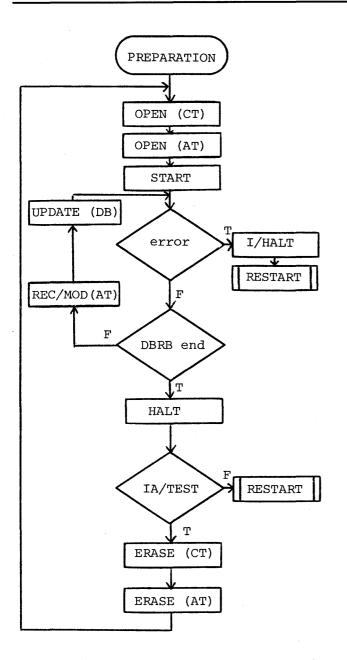

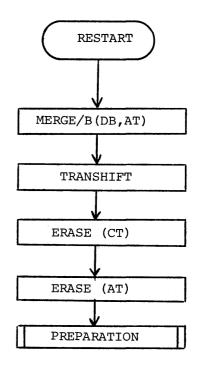

#### Chip Communication