# **AFIPS**

# CONFERENCE PROCEEDINGS

# VOLUME 49

# 1980

# NATIONAL COMPUTER CONFERENCE

### DON MEDLEY Editor and Program Chairman

ELLEN MARIE RANDALL Editorial/Production Specialist

> HERBERT SAFFORD Conference Chairman

## AFIPS PRESS 1815 NORTH LYNN STREET ARLINGTON, VIRGINIA 22209

# **AFIPS** CONFERENCE PROCEEDINGS

# **1980** NATIONAL COMPUTER CONFERENCE

May 19-22, 1980 Anaheim, California The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1980 National Computer Conference or the American Federation of Information Processing Societies, Inc.

> Library of Congress Catalog Card Number 80-66206 AFIPS PRESS 1815 North Lynn Street Arlington, Va. 22209

© 1980 by AFIPS Press. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) reference to the AFIPS Proceedings and notice of copyright are included on the first page. The title and abstract may be used without further permission in computer-based and other information-service systems. Permission to republish other excerpts should be obtained from AFIPS Press.

Printed in the United States of America

## Preface

HERBERT B. SAFFORD 1980 NCC Chairman

The Proceedings of the 1980 National Computer Conference is the most comprehensive review of the current developments in the computing industry. This record of the 1980 NCC Program now becomes a part of the industry's history, and stands as a tribute to Program Chairman Dr. Donald Medley and his committee. With the usability of the computer as an underlying theme of the program, Dr. Medley's committee, the authors whose papers are included in this volume, and many others devoted considerable time and energy during the past year to assure that this program would be useful and informative to all attendees. They are to be commended for their efforts. Special recognition should be given, also, to the many panelists and speakers who participated in the 1980 NCC Program in a manner that went beyond the formal paper presentations included in these Proceedings. It is my sincere hope that you were able to attend some portion of the program at the 1980 NCC, and that this volume of the Proceedings will be a useful source of information for you for many years to come.

### Introduction

DONALD B. MEDLEY 1980 NCC Program Chairman

A group of very bright and dedicated computing professionals have labored long and hard to develop a high quality technical program for the 1980 National Computer Conference that demonstrates the dynamics of the computing industry. These Proceedings represent the printed record of the result of over a year's efforts of many, many individuals.

With the usability of the computing tool as the base, the 1980 NCC Program has been oriented to three audiences: the user, the technician and management. Program sessions have been developed for each of these communities within specific topic areas including: the architecture of software and hardware, communications, social impacts, data base management, management support, simulation modeling and image processing, applications considerations and general interest topics. In each of these areas the Program Committee has developed sessions that are educational in nature, sessions that are oriented to the technical details of the topic, sessions that address the management aspects of the topic and sessions for the user of that phase of technology.

A special feature of the 1980 NCC is a group of sessions dealing with the use of the computing tool in the entertainment industry. These sessions describe areas from the generation of music or art to the control of television and movie production. Additionally, in response to the ever growing interest in the use of computers by the non-professional, a special group of sessions will be presented under the banner of the 1980 NCC Personal Computing Festival, which will cover areas of interest in personal computing. A separate publication will include papers presented in this section of the program.

These Proceedings contain a printed record of the papers presented in the technical program. Summary statements for the many panel sessions were not included due to volume limitations; however, summary statements for each session are published in the conference attendance brochure. The individual area directors have prepared a general summary statement concerning selected groups of sessions and those summaries are in the Proceedings.

The planning and organization of the 1980 NCC Program required the dedicated efforts of many individuals: area directors, session organizers and leaders, panelists and presenters of technical papers, and referees who helped us select the papers to be presented in this volume. I wish to extend my sincere appreciation to all these individuals and, most especially, to the Program Committee. Without their efforts the 1980 NCC Program and these Proceedings would not have been a reality. It is our sincere hope that the program itself proves useful and enjoyable to all those who are able to attend the 1980 NCC and that the Proceedings provide a useful reference source for many years to come.

## CONTENTS

**、**·

٩,

| Preface                                                                                                                                               | iii |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction<br>Donald B. Medley                                                                                                                      | iv  |

| APPLICATIONS                                                                                                                                          |     |

| A conversational decision support system for resource allocation without explicit objective function<br>Fumihiko Mori, Hiroshi Tsuji and Takashi Sato | 1   |

| Decision support systems: a practical application—Branch office structure<br>John R. Wetmiller                                                        | 7   |

| On development tools for small systems: the challenge of economically automating a filing cabinet<br>David D. Raber                                   | 13  |

| A structured information system design for a newspaper organization: a case study<br>Mohan R. Tanniru                                                 | 23  |

| SID: a system for interactive design<br>Tosiyasu L. Kunii and Minoru Harada                                                                           | 33  |

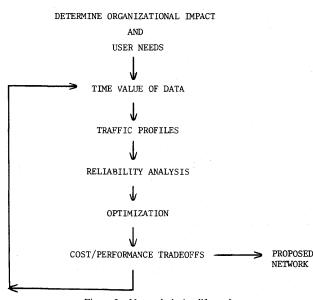

| An overview of a network design system<br>W. E. Bracker and B. R. Konsynski                                                                           | 41  |

| COMPUTERS AND ENTERTAINMENT                                                                                                                           |     |

| Area Director Summary<br>Suzanne Landa                                                                                                                | 49  |

| A minicomputer system for audio-animatronics show data generation<br>Philip C. Stover and R. David Snyder                                             | 51  |

| Computers and sports: a natural marriage<br>Thomas A. Eifler                                                                                          | 55  |

| Computers helping dance notation help the dance: a vision<br>Stephen W. Smoliar                                                                       | 67  |

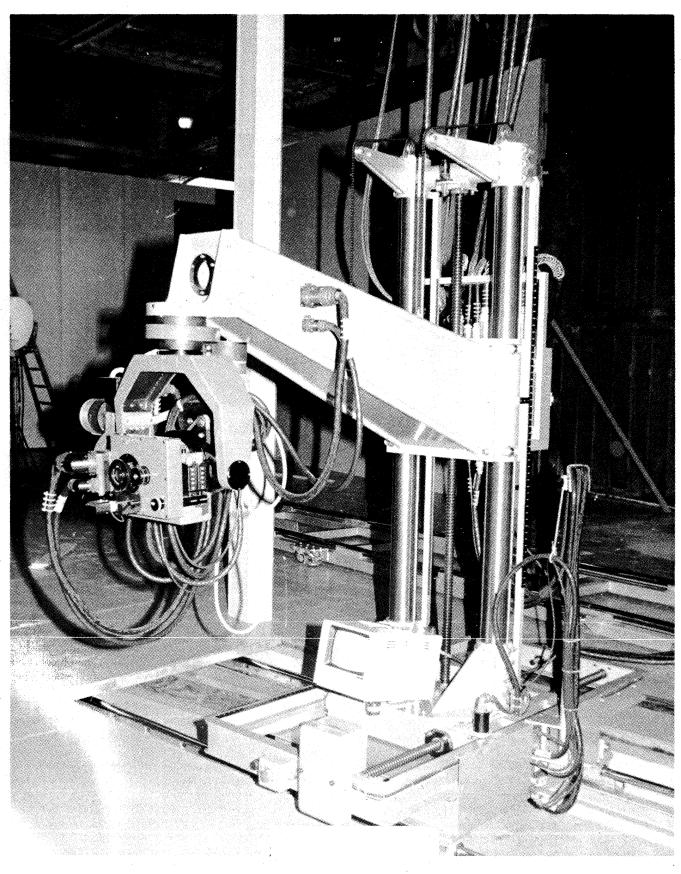

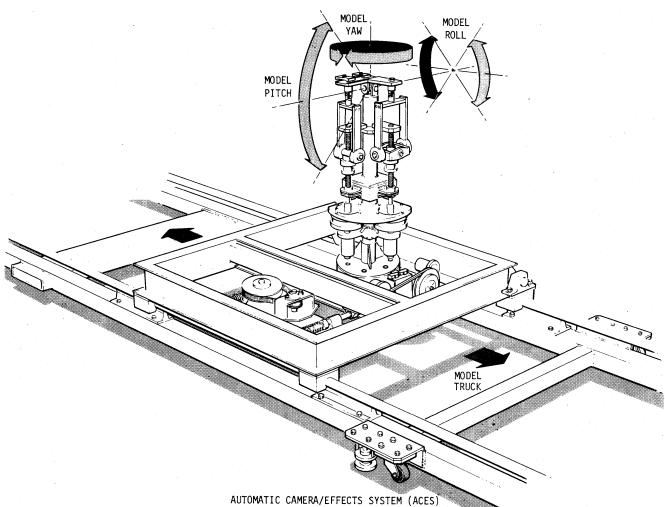

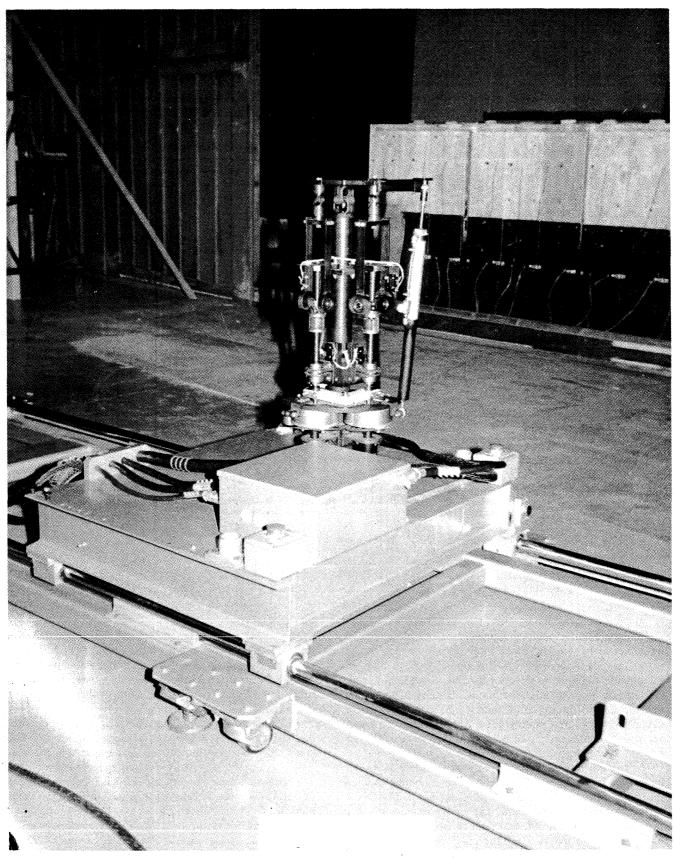

| Automatic Camera Effects System (ACES)<br>Steven N. Crane and R. David Snyder                                                                         | 73  |

| Automated computer controlled editing sound system (access)<br>William R. Deitrick                                                                    | 83  |

| The use of computer technology in Magicam slave camera systems<br>Dan Slater, Rob King and John Gale                                                  | 87  |

| COMMUNICATIONS                                                                                                                                        |     |

| Area Director Summary<br>Kenneth J. Thurber                                                                                                           | 91  |

| Distributed network and multiprocessing minicomputer state-of-the-art capabilities<br>Douglas J. Theis                                                | 93  |

| ARQ performance in SNA networks<br>Martin A. Reed and Terence D. Smetanka                                                                             | 105 |

Contents

| Computer communication in NTT remote computing services<br>Masatoshi Iwayama and Atsumu Fujiwara                                                                                                     | 113 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Local area data distribution<br>Thomas G. Albright and Robert J. Wallace                                                                                                                             | 121 |

| COMPUTER ARCHITECTURE                                                                                                                                                                                |     |

| Area Director Summary<br>Wesley Chu                                                                                                                                                                  | 127 |

| The control data loosely coupled network lower level protocols<br>William C. Hohn                                                                                                                    | 129 |

| LCN—A loosely coupled network system<br>Lowell H. Schiebe                                                                                                                                            | 135 |

| Derivation and use of a survivability criterion for DDP systems<br>Richard E. Merwin and Mohammed Mirhakak                                                                                           | 139 |

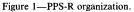

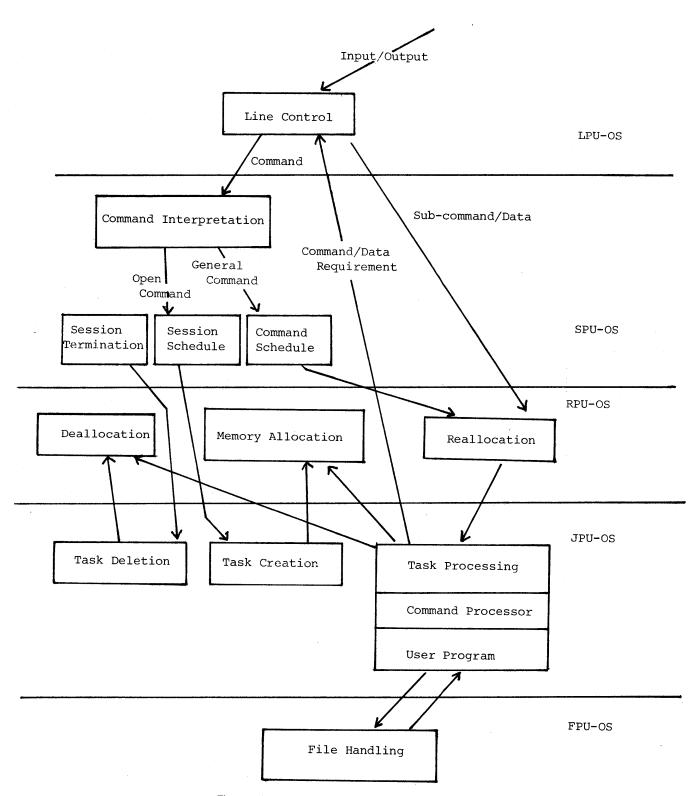

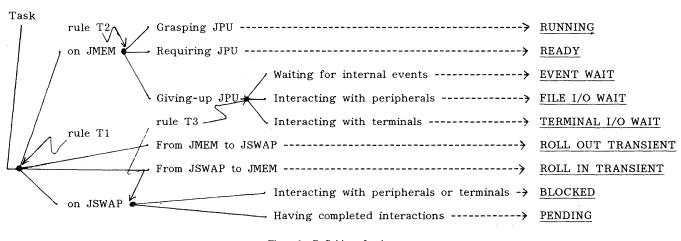

| An operating system kernel mechanism for the poly-processor system PPS-R<br>Makoto Amamiya, Naohisa Takahashi, Yutaka Ogawa and Kenji Koyama                                                         | 147 |

| Measures for distributed processing network survivability                                                                                                                                            | 157 |

| Architectures for supersystems of the '80s<br>Svetlana P. Kartashev and Steven I. Kartashev                                                                                                          | 165 |

| The highly-parallel supercomputers: definitions, applications and predictions<br>Hubert H. Love, Jr.                                                                                                 | 181 |

| Database machines and some issues on DBMS standard<br>Stanley Y. W. Su, Hsu Chang, George Copeland, Paul Fisher, Eugene Lowenthal and Stewart Schuster                                               | 191 |

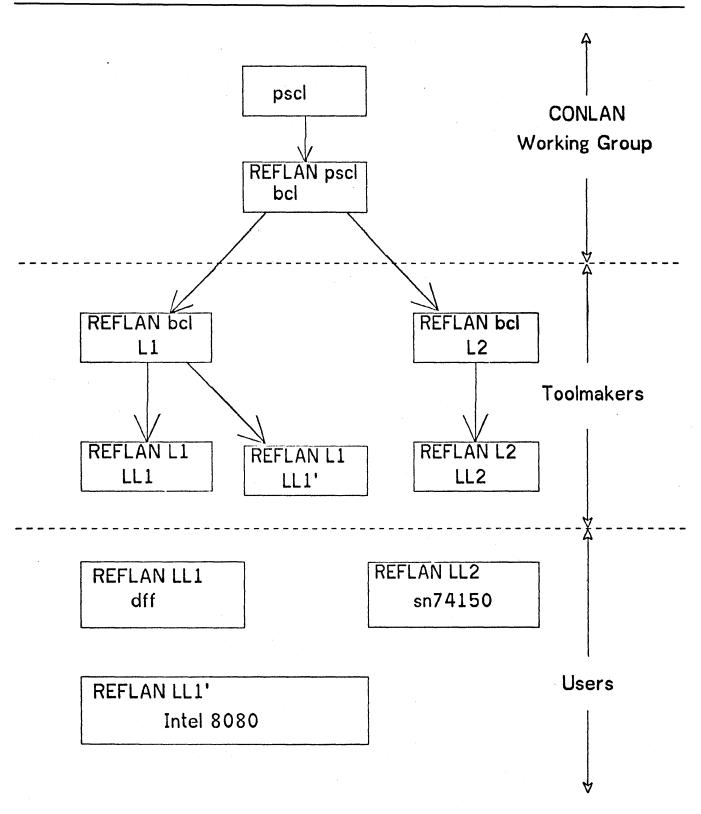

| CONLAN—A formal construction method for hardware description languages: basic principles<br>Robert Piloty, Mario Barbacci, Dominique Borrione, Donald Dietmeyer, Fredrick Hill and Patrick Skelly    | 209 |

| CONLAN—A formal construction method for hardware description languages: language derivation<br>Robert Piloty, Mario Barbacci, Dominique Borrione, Donald Dietmeyer, Fredrick Hill and Patrick Skelly | 219 |

| CONLAN—A formal construction method for hardware description languages: language application<br>Robert Piloty, Mario Barbacci, Dominique Borrione, Donald Dietmeyer, Fredrick Hill, Patrick Skelly   | 229 |

| Design decisions for the intelligent database machine<br>Robert Epstein and Paula Hawthorn                                                                                                           | 237 |

| DIALOG—A distributed processor organization of database machine<br>Benjamin W. Wah and S. Bing Yao                                                                                                   | 243 |

| DATA BASE MANAGEMENT                                                                                                                                                                                 |     |

| Area Director Summary<br>Alyce Jackson                                                                                                                                                               | 255 |

| System deadlocks resolution                                                                                                                                                                          | 257 |

| Database semantic integrity for a network data manager<br>Elizabeth Fong and Stephen R. Kimbleton                                                                                                    | 261 |

| Concurrency coordination in a locally distributed database system<br>Gruia-Catalin Roman                                                                                                             | 269 |

| An introduction to computed chaining<br>Kuo-Chung Tai and Alan L. Tharp                                                                                                                              | 275 |

#### vi

| A federated architecture for database systems                                                                                      | 283         |

|------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Dennis McLeod and Dennis Heimbigner                                                                                                |             |

| Area Director Summary<br>Linda Taylor                                                                                              | 29          |

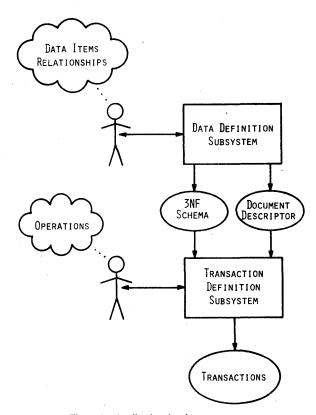

| Definition of database transactions by the casual user<br>Fred J. Maryanski and C. Steven Roush                                    | 293         |

| Programming with data frames for everyday data items<br>David W. Embley                                                            | 301         |

| Implementing data management<br>Daniel S. Appleton                                                                                 | 307         |

| Area Director Summary<br>Vincent Lum                                                                                               | 317         |

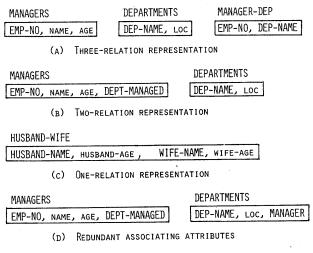

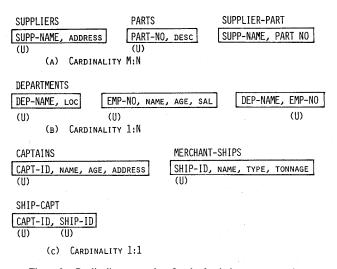

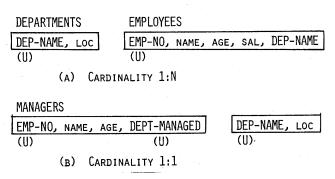

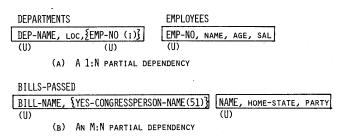

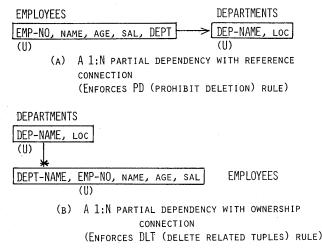

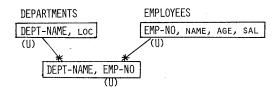

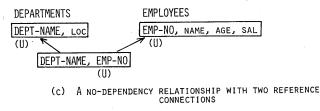

| Properties of relationships and their representation                                                                               | 319         |

| EARTH RESOURCES                                                                                                                    |             |

| Area Director Summary<br>Leigh Rosenberg                                                                                           | 327         |

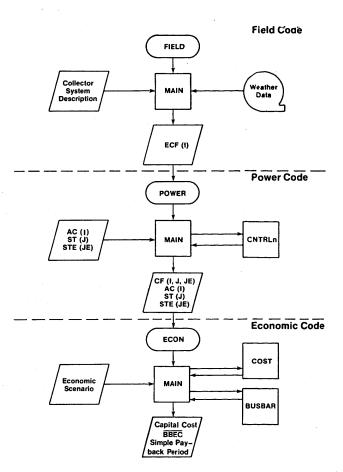

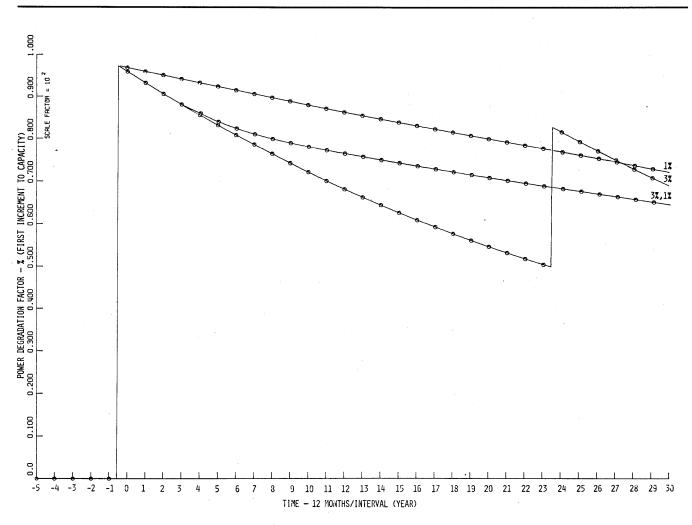

| BALDR-1: a solar thermal system simulation<br>Joseph G. Finegold and F. Ann Herlevich                                              | 329         |

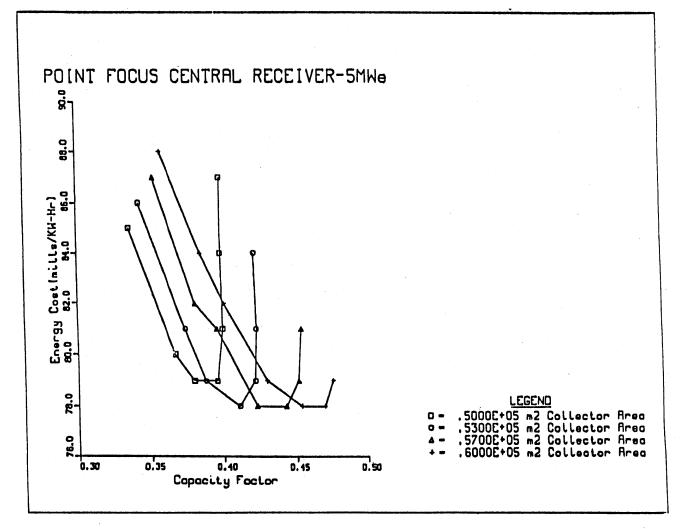

| Overview of the alternative power system economic analysis model<br>Richard B. Davis and Jerome V. V. Kasper                       | 335         |

| Computer simulation of the operations of utility grid connected photovoltaic power plants<br>Chester S. Borden                     | 341         |

| Computer simulation of solar electric generating plants in a utility grid<br>S. Young, O. Merrill, R. Knowles and Y. Gupta         | 347         |

| Area Director Summary<br>Roger Firestone                                                                                           | 355         |

| Numerical algorithms for parallel computers<br>David K. Stevenson                                                                  | 357         |

| Design of an interactive matrix calculator<br>Cleve Moler                                                                          | 363         |

|                                                                                                                                    |             |

| IMAGE PROCESSING                                                                                                                   |             |

| Area Director Summary<br>Andrew Tescher                                                                                            | 369         |

| Derivation of invariant scene characteristics from images<br>Berthold K. P. Horn                                                   | 37          |

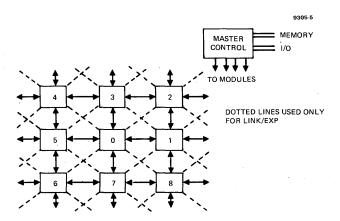

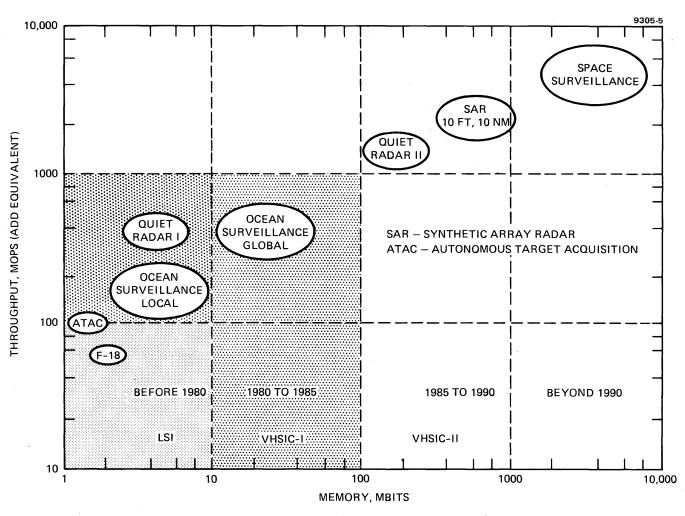

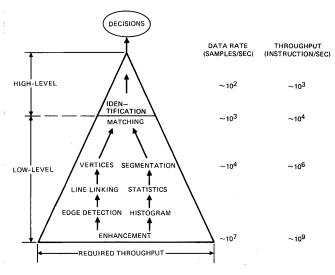

| Image understanding architectures<br>Graham R. Nudd                                                                                | 377         |

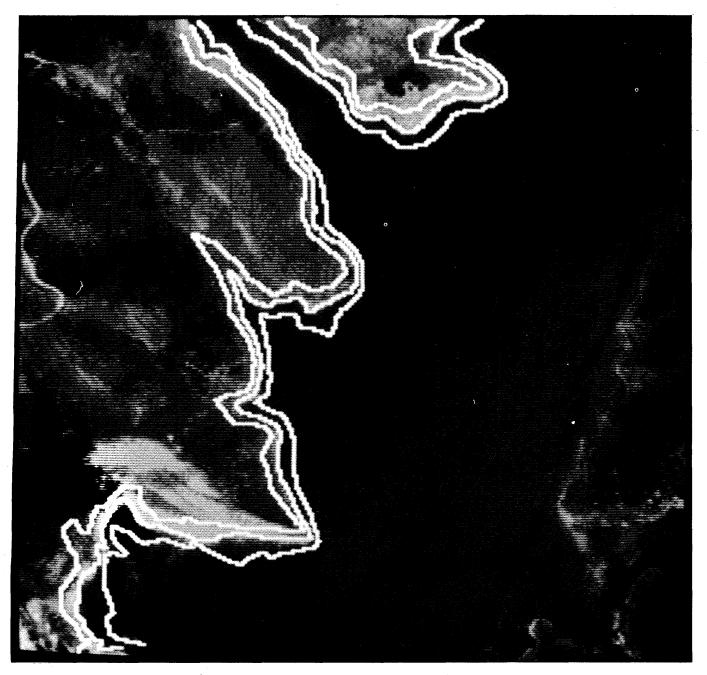

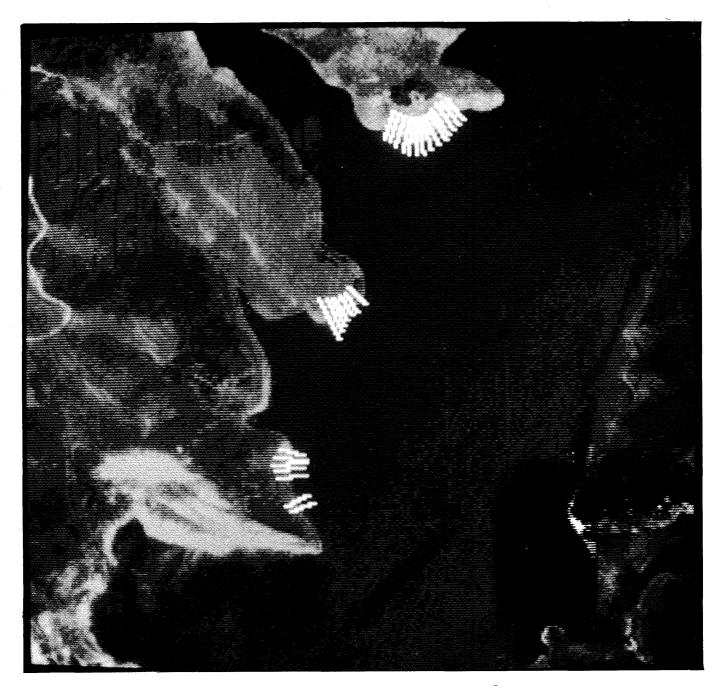

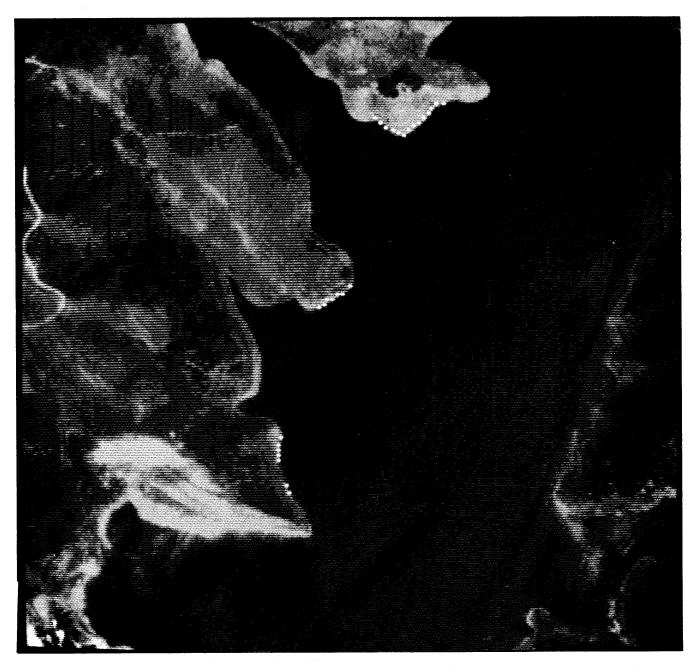

| Map-guided interpretation of remotely-sensed imagery<br>J. M. Tenenbaum, H. G. Barrow, R. C. Bolles, M. A. Fischler and H. C. Wolf | <b>39</b> 1 |

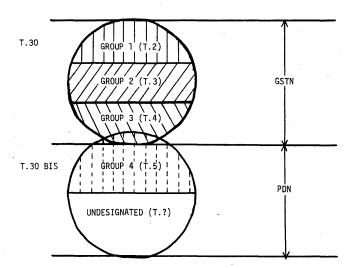

| CCITT standardization for digital facsimile<br>T. L. McCullough                                                                    | 409         |

| The application of optical character recognition techniques to bandwidth compression of facsimile data                             | 415         |

The application of optical character recognition techniques to bandwidth compression of facsimile data ...... Patrice J. Capitant and Robert H. Wallis

Contents

vii

| Facsimile image coding<br>Joan L. Mitchell                                                                                                                                             | 423 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| MEDICAL IMAGING AND EDUCATION                                                                                                                                                          |     |

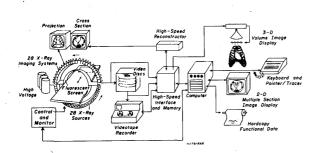

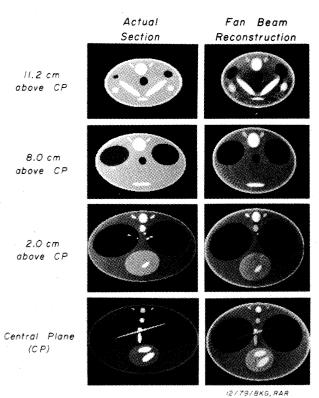

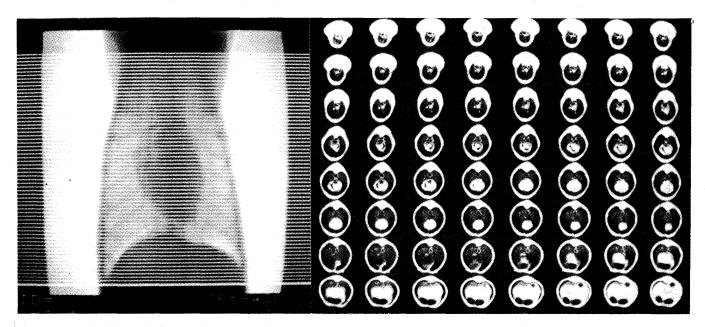

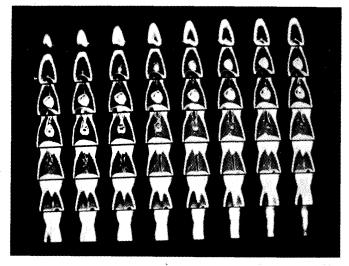

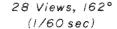

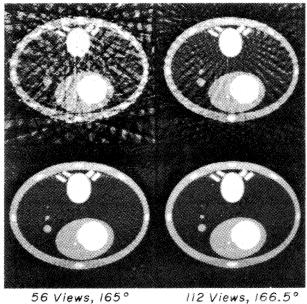

| Description and evaluation of a system for high-speed, three-dimensional computed tomography of the body:<br>the dynamic spatial reconstructor<br>Richard A. Robb and Barry K. Gilbert | 427 |

| 3-D viewer for interpretation of multiple scan sections<br>Brent Baxter                                                                                                                | 437 |

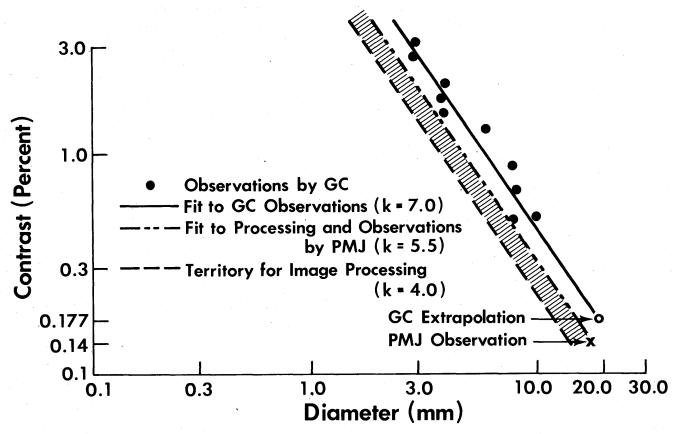

| Absolute limits on image processing<br>David G. Brown, Robert F. Wagner and Mary Pastel Anderson                                                                                       | 441 |

| Generalized methodology for the comparison of diagnostic imaging instrumentation<br>Leon Kaufman and Dale Shosa                                                                        | 445 |

| MANAGEMENT                                                                                                                                                                             |     |

| Balancing processor shares of scheduling classes through controlled allocation of memory<br>K. V. Sastry                                                                               | 453 |

| Area Director Summary<br>John C. Biddle                                                                                                                                                | 457 |

| Applications of exemplary programming<br>William S. Faught                                                                                                                             | 459 |

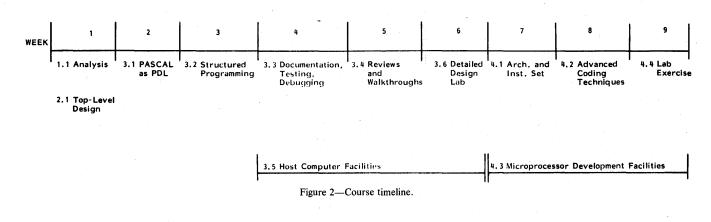

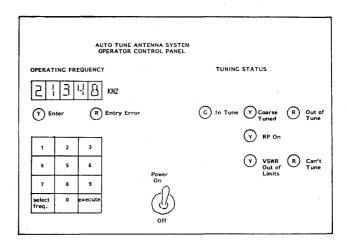

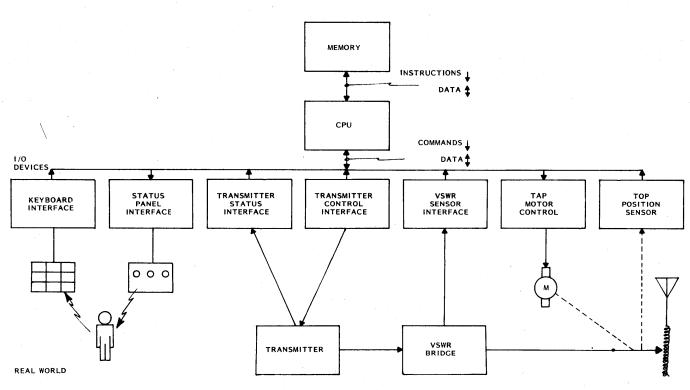

| Multiprocessor software engineering training: a case study<br>Christine L. Braun                                                                                                       | 465 |

| Development of a microprocessor support facility for large organizations<br>Bruce E. Stock and Miguel A. Ulloa                                                                         | 473 |

| Future management concerns regarding office automation<br>Gary D. Beamer                                                                                                               | 479 |

| OFFICE AUTOMATION                                                                                                                                                                      |     |

| Area Director Summary<br>Walter E. Ulrich                                                                                                                                              | 483 |

| Introduction to electronic mail<br>Walter E. Ulrich                                                                                                                                    | 485 |

| Implementation considerations in electronic mail<br>Walter E. Ulrich                                                                                                                   | 489 |

| Experiences of an electronic mail vendor<br>Jeffrey B. Holden                                                                                                                          | 493 |

| Electronic message system as a function in the integrated electronic office<br>Harold E. O'Kelley                                                                                      | 499 |

| The growing use of electronic mail by airlines<br>James C. Goodlett                                                                                                                    | 503 |

| Metamorphosis: facsimile communications, electronic mail and office productivity<br>John E. Cochran                                                                                    | 509 |

| Texas Instruments computer communication network and its support for the automated office<br>John W. White                                                                             | 515 |

| Implementing electronic mail in a telephone system: more than just talk                                                                                                                | 527 |

| Contents | ix |

|----------|----|

| contents | IA |

| An office form flow model<br>Ivor Ladd and D. C. Tsichritzis                                                                                                                                 | 533 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Design principles of an office specification language<br>Michael Hammer and Jay S. Kunin                                                                                                     | 541 |

| Automated workflow control: a key to office productivity<br>L. S. Baumann and R. D. Coop                                                                                                     | 549 |

| Streamlining office procedures—An analysis using the information control net model<br>Carolyn L. Cook                                                                                        | 555 |

| Area Director Summary<br>James Carlisle                                                                                                                                                      | 567 |

| Provisions for flexibility in the Linköping office information system (LOIS)<br>Erik Sandewall, Göran Hektor, Anders Ström, Claes Strömberg, Ola Strömfors, Henrik Sörensen and Jaak<br>Urmi | 569 |

| SECURITY AND PRIVACY                                                                                                                                                                         |     |

| Area Director Summary<br>Rein Turn                                                                                                                                                           | 579 |

| Privacy protection and transborder data flows<br>Rein Turn                                                                                                                                   | 581 |

| Transborder data flow: legal persons in privacy protection legislation<br>Susan H. Nycum and Susan Courtney-Saunders                                                                         | 587 |

| SIMULATION                                                                                                                                                                                   |     |

| Area Director Summary<br>Lance A. Leventhal                                                                                                                                                  | 595 |

| Using preliminary Ada in a process control application<br>M. E. Gordon and W. B. Robinson                                                                                                    | 597 |

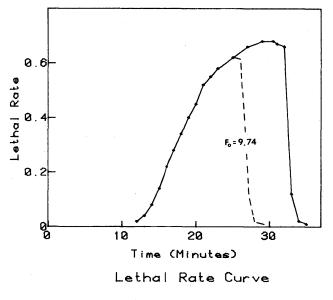

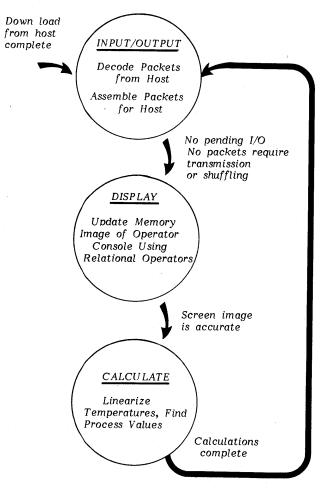

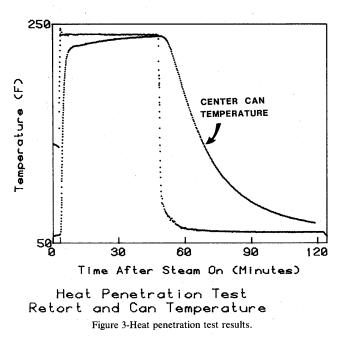

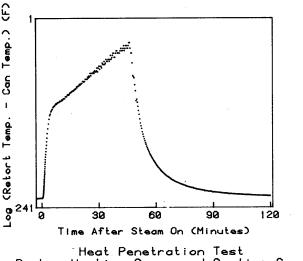

| Computer aided heat penetration tests for the food canning industry<br>Paul Sagues                                                                                                           | 607 |

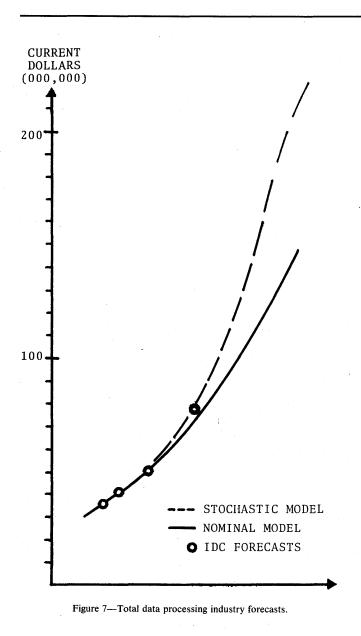

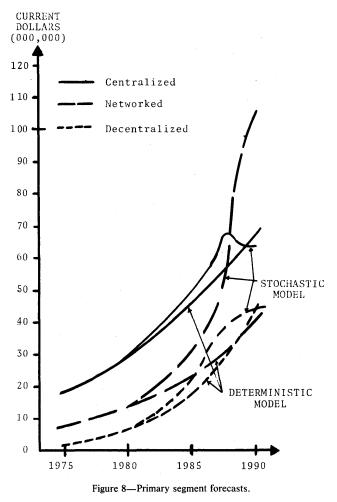

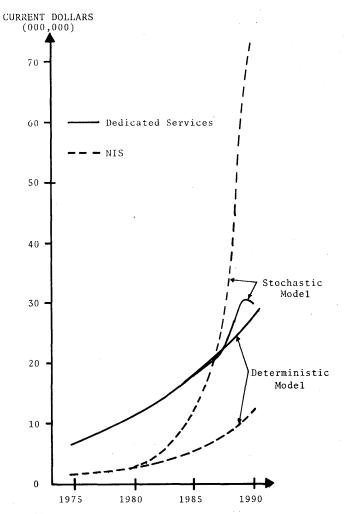

| A cross-impact simulation forecast of the data processing industry<br>Paul Herbert Rosenthal                                                                                                 | 613 |

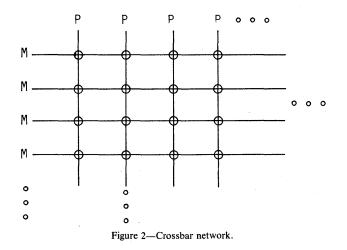

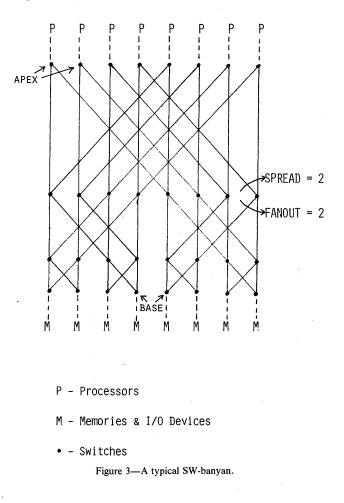

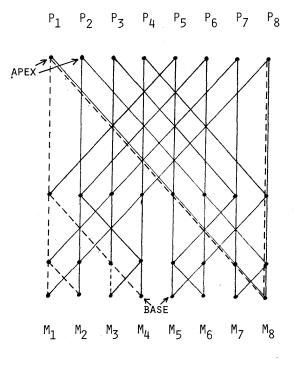

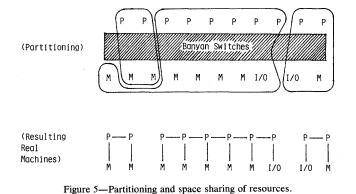

| Organization of the TRAC processor-memory subsystem<br>R. N. Kapur, U. V. Premkumar and G. J. Lipovski                                                                                       | 623 |

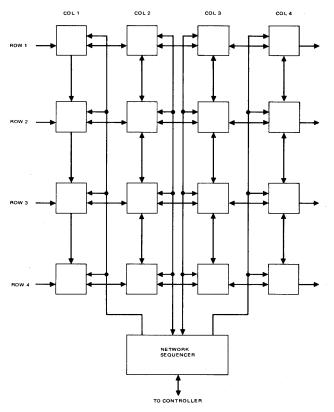

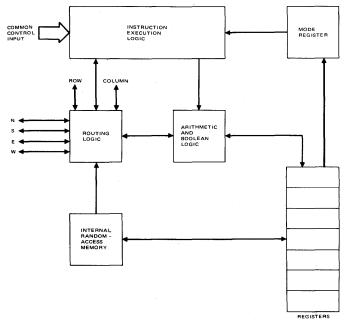

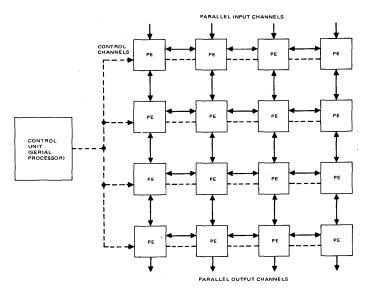

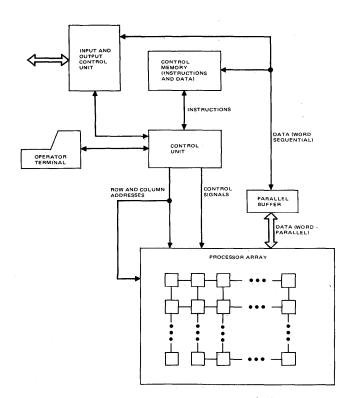

| An overview of the Texas Reconfigurable Array Computer<br>Matthew C. Sejnowski, Edwin T. Upchurch, Rajan N. Kapur, Daniel P. S. Charlu, and G. Jack Lipovski                                 | 631 |

| Design and implementation of the banyan interconnection network in TRAC<br>U. V. Premkumar, R. Kapur, M. Malek, G. J. Lipovski and P. Horne                                                  | 643 |

| SOCIAL IMPACT                                                                                                                                                                                |     |

| The advent of trusted computer operating systems<br>Stephen T. Walker                                                                                                                        | 655 |

| SOFTWARE MANAGEMENT                                                                                                                                                                          |     |

| Area Director Summary<br>Donald Reifer                                                                                                                                                       | 667 |

| C | ont | en | ts |

|---|-----|----|----|

|   |     |    |    |

| SOFTWARE ENGINEERING TECHNOLOGY TRANSFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Area Director Summary<br>Lorraine Duvall                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 669                             |

| An integrated support software network using NSW technology<br>Richard A. Robinson and Emily A. Krzysiak                                                                                                                                                                                                                                                                                                                                                                                                          | 671                             |

| The role of an information analysis center in software engineering technology transfer<br>Jon Martens and Lorraine Duvall                                                                                                                                                                                                                                                                                                                                                                                         | 677                             |

| Considerations in the transfer of software engineering technology<br>Michael J. McGill                                                                                                                                                                                                                                                                                                                                                                                                                            | 683                             |

| SOFTWARE TOOLS AND TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |

| A technique for comparative assessment of software development management policies<br>Brendan D. L. Mulhall and Steven M. Jacobs                                                                                                                                                                                                                                                                                                                                                                                  | 687                             |

| SOFTWARE RELIABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

| Area Director Summary<br>Herbert Hecht                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 695                             |

| Standard error classification to support software reliability assessment<br>John B. Bowen                                                                                                                                                                                                                                                                                                                                                                                                                         | 697                             |

| What makes a reliable program—few bugs, or a small failure rate?<br>B. Littlewood                                                                                                                                                                                                                                                                                                                                                                                                                                 | 707                             |

| Software reliability and advanced avionics                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 715                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

| SOFTWARE LANGUAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

| SOFTWARE LANGUAGES<br>Area Director Summary<br>Russell J. Abbott                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 721                             |

| Area Director Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 721<br>723                      |

| Area Director Summary<br>Russell J. Abbott<br>A linguistic comparison of MUMPS and COBOL                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

| Area Director Summary<br>Russell J. Abbott<br>A linguistic comparison of MUMPS and COBOL<br>Thomas Munnecke<br>The design of PLAIN—Support for systematic programming                                                                                                                                                                                                                                                                                                                                             | 723                             |

| Area Director Summary<br>Russell J. Abbott         A linguistic comparison of MUMPS and COBOL<br>Thomas Munnecke         The design of PLAIN—Support for systematic programming                                                                                                                                                                                                                                                                                                                                   | 723<br>731                      |

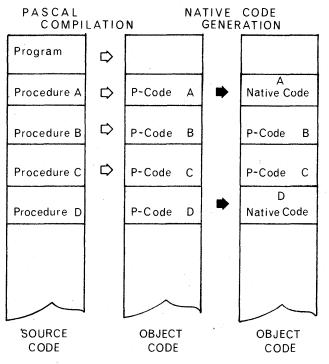

| <ul> <li>Area Director Summary<br/>Russell J. Abbott</li> <li>A linguistic comparison of MUMPS and COBOL<br/>Thomas Munnecke</li> <li>The design of PLAIN—Support for systematic programming<br/>Anthony I. Wasserman</li> <li>Some practical experiences with the Pascal language<br/>G. G. Gustafson, T. A. Johnson and G. S. Key</li> <li>UCSD Pascal<sup>™</sup>: a portable software environment for small computers</li> </ul>                                                                              | 723<br>731<br>741               |

| Area Director Summary<br>Russell J. Abbott         A linguistic comparison of MUMPS and COBOL<br>Thomas Munnecke         The design of PLAIN—Support for systematic programming<br>Anthony I. Wasserman         Some practical experiences with the Pascal language<br>G. G. Gustafson, T. A. Johnson and G. S. Key         UCSD Pascal <sup>™</sup> : a portable software environment for small computers<br>Mark Overgaard         SOFTWARE QUALITY ASSURANCE         Area Director Summary<br>Kurt F. Fischer  | 723<br>731<br>741               |

| Area Director Summary<br>Russell J. Abbott         A linguistic comparison of MUMPS and COBOL         Thomas Munnecke         The design of PLAIN—Support for systematic programming         Anthony I. Wasserman         Some practical experiences with the Pascal language         G. G. Gustafson, T. A. Johnson and G. S. Key         UCSD Pascal <sup>™</sup> : a portable software environment for small computers         Mark Overgaard         SOFTWARE QUALITY ASSURANCE         Area Director Summary | 723<br>731<br>741<br>747        |

| <ul> <li>Area Director Summary</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 723<br>731<br>741<br>747<br>755 |

| C                                                                                                                                         | ontents        | xi  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|

|                                                                                                                                           |                |     |

| SOFTWARE ENGINEERING EDUCATION                                                                                                            |                |     |

| Area Director Summary<br>Barry Boehm                                                                                                      | ••••••<br>•••• | 781 |

|                                                                                                                                           |                |     |

| SPECIAL TOPICS                                                                                                                            |                |     |

| Area Director Summary<br>Gene Smith                                                                                                       | •••••          | 783 |

| Technology development, severed ventures, and other aspects of corporate venture capital<br>Jean E. de Valpine                            |                | 785 |

| Recommendations for increasing the availability of capital<br>Richard C. Pflager                                                          |                | 791 |

| Corporate venture capital in the computer industry<br>Kenneth W. Rind and Gene I. Miller                                                  |                | 795 |

| Structured procedure for comparison and selection of computer system designs<br>Antonio Vallone                                           |                | 801 |

| PAPER FAIRE                                                                                                                               |                |     |

| Extracting unique rows of a bounded degree array using tries<br>Douglas Comer                                                             |                | 807 |

| A look at making the ADP procurement process more efficient—Temporary regulation 46<br>Roger J. Gorg, George N. Baird and Judith A. Parks | •••••          | 811 |

| An information base for procedure independent design of information systems<br>Levent Ormancioglu                                         |                | 817 |

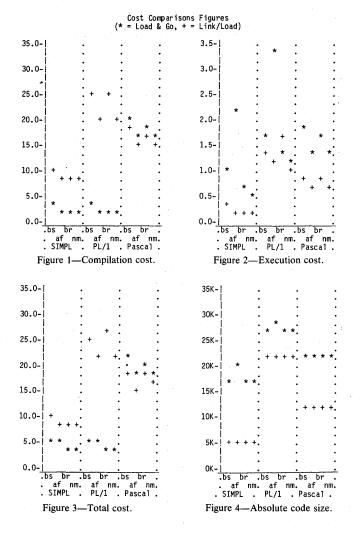

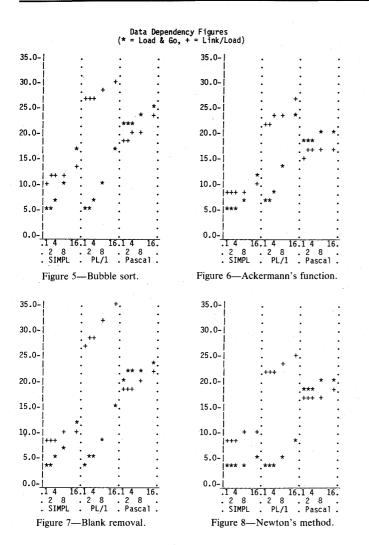

| Comparing load & go and link/load compiler organizations<br>William L. Wilder                                                             |                | 823 |

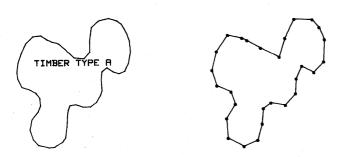

| A link between polygon and grid representations of land resource information systems<br>Devon Nickerson                                   |                | 827 |

| Risk analysis in the 1980's<br>Jerome Lobel                                                                                               |                | 831 |

| A mathematical model of character string manipulation                                                                                     |                | 837 |

| Policy, values and EFT research: anatomy of a research agenda                                                                             |                | 841 |

| A linear programming model for optimal computer network protocol design<br>John F. Heafner and Frances H. Nielsen                         | •••••          | 855 |

| Extracting service features from protocol documents<br>John F. Heafner, Frances H. Nielsen and M. Wayne Shiveley                          | •••••          | 863 |

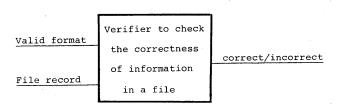

| Verification of information in a file<br>Jainendra K. Navlakha                                                                            |                | 871 |

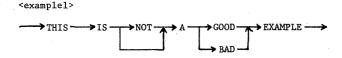

| Translating non-standard extensions to standard Pascal<br>Viswanathan Santhanam                                                           |                | 877 |

| The flexible console—FLEXICON<br>David L. Steinberg                                                                                       |                | 883 |

| The INTEL <sup>®</sup> 8087 numeric data processor<br>John F. Palmer                                                                      | ,              | 887 |

|                                                                                                                                           |                |     |

| Home computing—A vision in search of a marketplace: areas of needed research | 895 |

|------------------------------------------------------------------------------|-----|

| John E. Ruchinskas, Charles W. Steinfield and Lynne L. Svenning              |     |

| 1980 National Computer Conference Committees                                 | 903 |

| NCC '80 Area Directors                                                       | 905 |

| NCC '80 Session Chairmen                                                     | 906 |

| NCC '80 Referees                                                             | 909 |

| NCC '80 Speakers and Panelists                                               | 911 |

| American Federation of Information Processing Societies                      | 914 |

| Author Index                                                                 | 918 |

## A conversational decision support system for resource allocation without explicit objective function

by FUMIHIKO MORI, HIROSHI TSUJI and TAKASHI SATO Hitachi, Ltd. Ohzenji, Kawasaki, Japan

#### **INTRODUCTION**

This paper presents a conversational multiobjective decision support system. The system is called RAINBOW: Resource Allocation in Business Operation under Uncertain Worth. Our focus in the design and development of RAINBOW is placed on the loosely structured decision situation where the objective functions are given only implicitly and, as such, should be approximated by the decision maker as the decision making process proceeds.

In the following, we first describe the specific decision problem treated here. This is the loans budgeting decision in a bank in Japan. Next we will see that the budget allocation procedure which had been employed in the bank prior to the design and implementation of RAINBOW can be represented by a set of simple linear equations. Basically RAIN-BOW supports the process of convergence to a preferred alternative budget plan by giving the decision maker helpful information for him to form consistent evaluations of the utility function, the objective functions and the solution for the budget allocation plan. Description of the functions of RAINBOW will be the main part of this paper. Lastly we will comment on RAINBOW in the framework of the multiple objective programming.

#### AN ILLUSTRATIVE DECISION PROBLEM

Direct motivation for the development of RAINBOW came from the problem of allocating the loans budget to branch offices of a bank, although RAINBOW is applicable to general resource allocation problems.

This section describes the specific problem of loan budgeting as a rationale for the functional design of RAINBOW.

Executives in the loan department of a bank annually or biannually allocate loan budget to each of its branch offices. The planning is a routine decision making task, but it is a difficult and time consuming problem. In many cases the total amount of the budget is determined by the total deposit in the bank and financial policy of the government at the time. Therefore the total budget is usually not a decision variable but a constraint on the upper bound of the sum of the allocatable resources. If we are to formulate the problem as an optimization problem, we will have a mathematical programming problem of the following form:

maximize  $u = f(u_1, u_2, \dots, u_N)$  (1)

s.t.  $u_1 + u_2 + \dots + u_N \leq S$  (2)

$$u_i \ge 0$$

, for  $i = 1, ..., N$  (3)

where

N = number of branch offices,

S = upper bound on the sum of budgets,

$u_i$  = budget allocated to the *i*th branch,

u = expected utility as a function of budget plan,  $(u_1, u_2, ..., u_N)$ .

At first we considered an approach by some mathematical programming model such as above. But, through extensive interviews with the mangers in the loan department of the bank, it became clear that explicit identification of a suitable objective function was a difficult and thankless task.

The fact that, for instance, one dollar allocated to branch i and j, respectively, will yield the same return on investment, provided that such factors as average interest rate, average operation cost per transaction and risk are the same in both branches, would illustrate the difficulties in the model formulation in the form of equation (1). Although these factors do differ among the branches, corporate-strategic considerations other than these quantifiable factors play a larger part in budget allocation. For example, a branch with high operation cost ratio may be a newly opened one and the policy of the bank may be to expand its territory, in spite of its relatively high cost at present, by aggressive operation in the financial market of the particular locality. A branch in a densely inhabited district may not need a big budget in spite of its large amount of deposits, since its expected role is collection of deposits from the households in its territory. The necessity to take account of these strategic considerations is the rule rather than the exception.

The budgeting procedure, then, depends on a number of factors which are difficult to quantify. The factors involved include, among others, the geographical and strategic location of the branch and its position and expected role in the overall corporate strategy of the bank.

The kind of decision situation described above occurs quite often in daily operations of any business and other organizations. It requires many subjective and intuitive judgments as to the utility gained from each of the alternative actions. Evaluations of other factors relevant to the problem are also bound to be subjective to a certain degree.

An approach we can take in these decision situations is to try to help the thinking process of the decision maker.

An important function of the budget planning is to express the policy of the organization and to get the consensus of the people involved in order to assure well-coordinated organizational activity. Then, an important requirement in the development of a decision support system is to help the decision maker to express his views, judgments and evaluations, albeit subjective or intuitive, and to make them something objective in that they have been expressed and now are the objects of discussion, criticism and modification. It will be our concern in this loosely structured decision situation to facilitate this dialectical process of subjectivity and objectivity.

Many researchers in the field of multiobjective decision making have been working on this standpoint. The Surrogate Worth Tradeoff (SWT) method by Haimes and Hall<sup>1.2</sup> is effective when the decision makers can evaluate the marginal tradeoffs among objective functions. Multiattribute Utility Theory (MAUT) by Keeney and Raiffa<sup>3</sup> gives a method of constructing a utility function based on preference structure and indifferent curves of each pair of objectives. These methods have been applied to large-scale regional development planning.<sup>4.5</sup> Geoffrion et al.<sup>6</sup> proposed a method of conversational decision support system based on the Frank-Wolfe algorithm.

Many of those multiobjective decision making systems, of which only very few are mentioned above, depend heavily on the tradeoff concept. Decision makers who want to use either the SWT method or MAUT method must be ready to evaluate the tradeoffs among conflicting objectives explicitly and quantitatively. It is a task of system designer to make it easy for the decision maker to articulate the tradeoff evaluations.

#### ANALYSIS OF BUDGET DECISION MAKING PROCESS

As mentioned in the previous section, it became clear that formulation of the allocation problem in a mathematical programming problem with scalar objective function as in equations (1)-(3) was not suited to this case. The problem is multiobjective. Generating noninferior solutions was not possible since managers in the loan department felt they had trouble in identification and quantification of the objectives. Then, as the first step of the system design, efforts were made to model the actual budget allocation procedure.

Interviews with the managers revealed that the budget allocation procedure actually taken in the bank could be summarized as follows.

#### Step 1

Managers select "evaluation elements" or "allocation elements." These are items for the evaluation of the branch offices. Typical examples of the element are "basic evaluation," "branch characteristics," "growth potential" and "strategic consideration."

#### Step 2

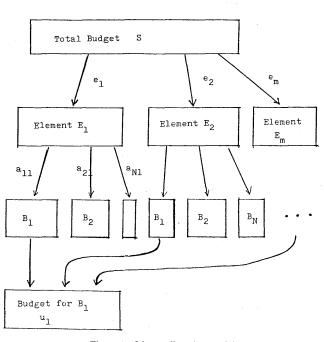

The total budget S is allocated to the elements at first. If the managers have selected m elements  $E_1, E_2, ..., E_m$  in Step 1 above, and give weight  $e_j$  to the element  $E_j$ , then  $E_j$  receives  $e_j S$  out of the total S. The weights should satisfy

$$e_1 + e_2 + \ldots + e_m = 1.0$$

(4)

$$e_j > 0$$

, for  $j = 1, ..., m$ . (5)

Step 3

Managers evaluate branches with respect to each of the evaluation elements. Let  $B_1, B_2, ..., B_N$  denote N branches, and let  $a_{ij}$  denote the numerical evaluation of the branch  $B_i$  with respect to the element  $E_j$ . According to these evaluations branch  $B_i$  receives  $a_{ij}e_jS$  out of the amount  $e_jS$  allocated to the evaluation element  $E_j$  in Step 2. Since negative value of  $a_{ij}$  can result in negative allocation to  $B_i$  when  $e_j$  is quite large,  $a_{ij}s$  are assumed to satisfy the nonnegativity condition:

$$a_{ii} \ge 0$$

, for  $i = 1, ..., N$  and  $j = 1, ..., m$ . (6)

Also

$$a_{1i} + a_{2i} + \dots + a_{Ni} = 1.0 \tag{7}$$

Step 4

The budget allocated to branch  $B_i$  is just the sum of  $a_{ij}e_jS$  over j=1,...,m. Let  $u_i$  denote the budget for  $B_i$ , then

$$u_i = a_{i1}e_1S + a_{i2}e_2 + \dots + a_{im}e_mS,$$

(8)

for i = 1, ..., N.

In matrix notation, equation (8) is

$$\underline{u} = A\underline{e}S \tag{9}$$

where

$$u = (u_1, u_2, \dots, u_N)^t$$

(10)

$$\underline{e} = (e_1, e_2, \dots, e_m)^t \tag{11}$$

$$A = (\underline{a}_1, \underline{a}_2, \dots, \underline{a}_m) \tag{12}$$

$$\underline{a}_{i} = (a_{1i}, a_{2i}, \dots, a_{Ni})^{t}, \text{ for } i = 1, \dots, m$$

(13)

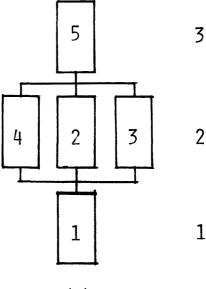

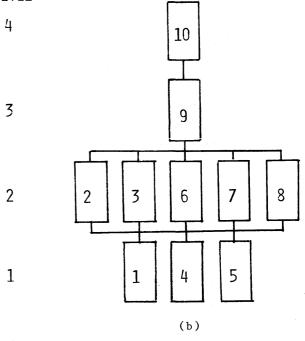

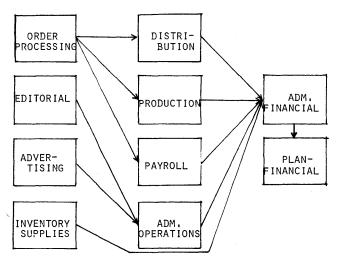

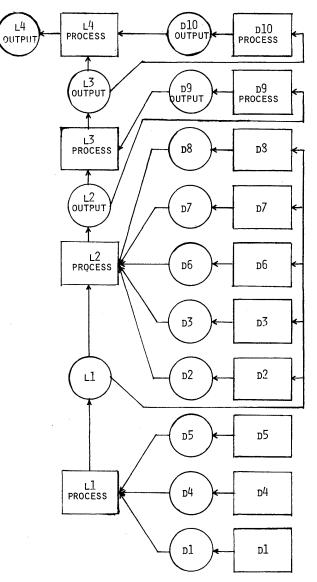

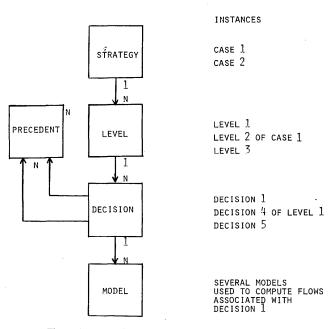

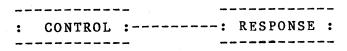

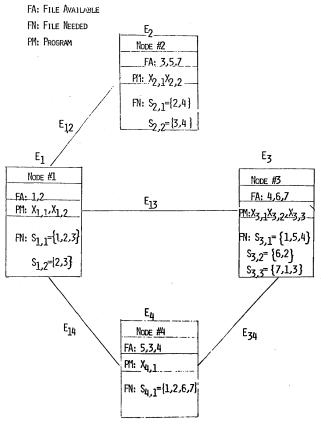

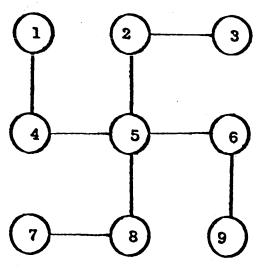

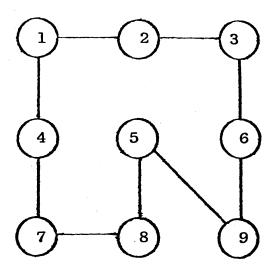

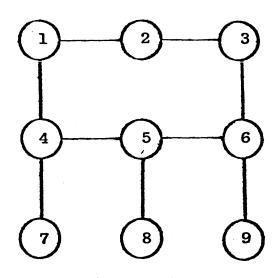

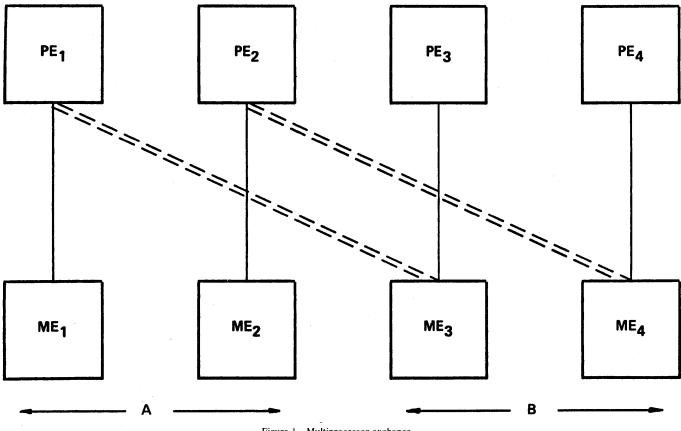

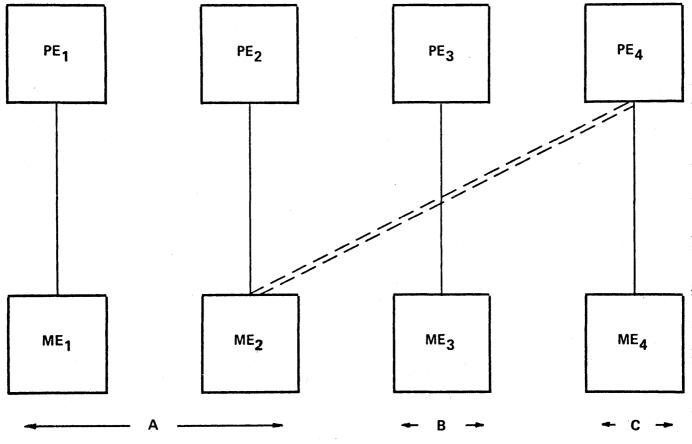

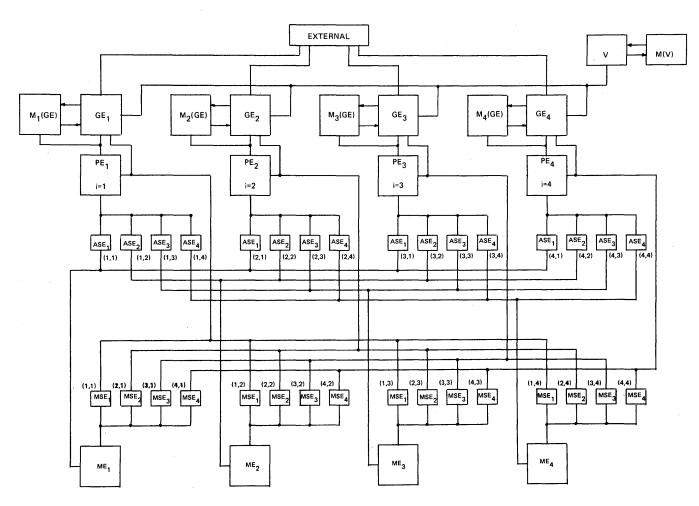

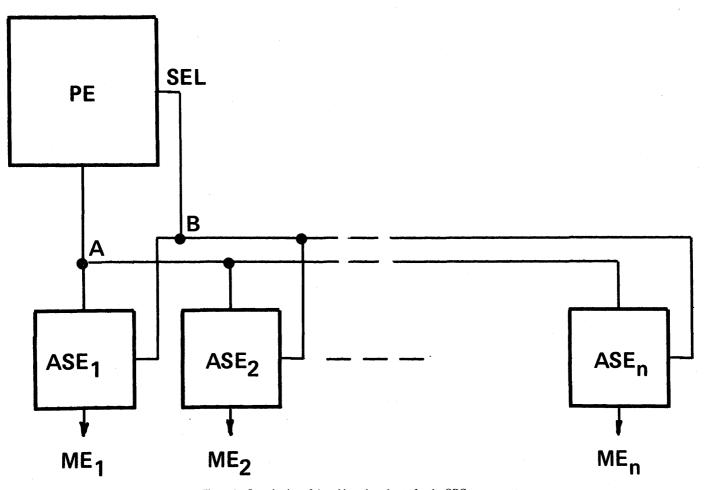

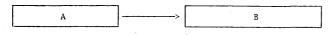

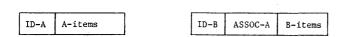

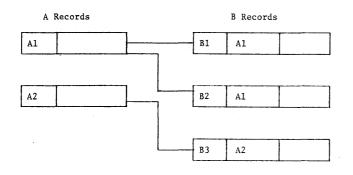

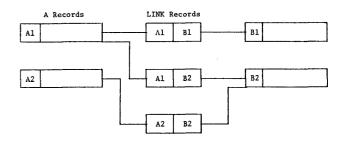

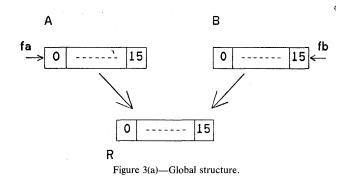

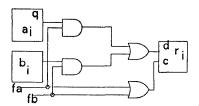

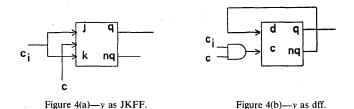

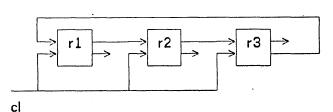

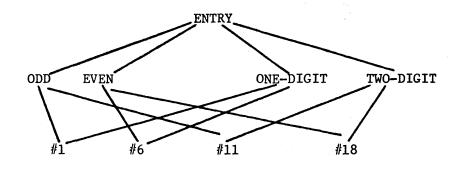

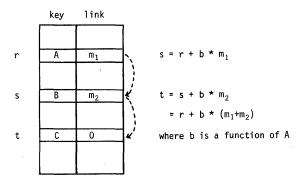

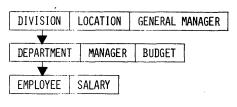

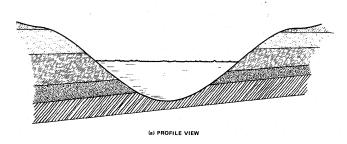

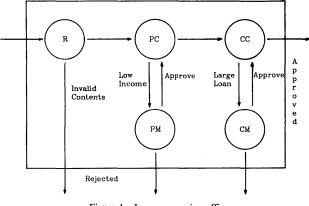

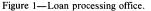

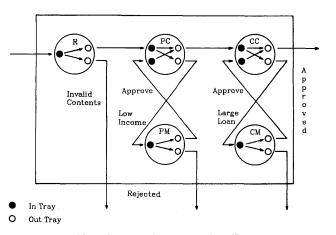

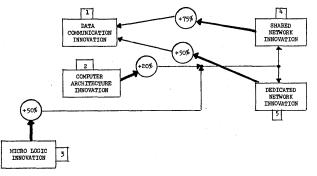

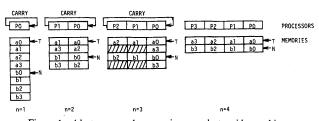

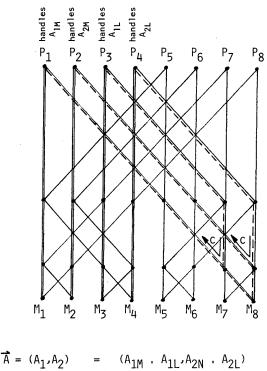

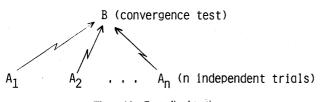

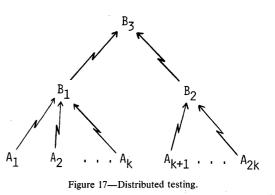

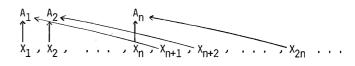

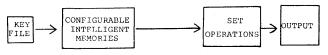

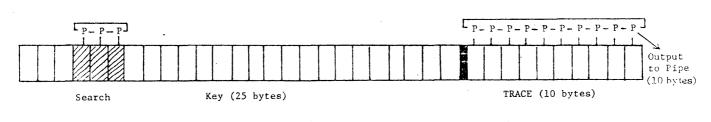

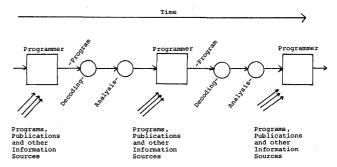

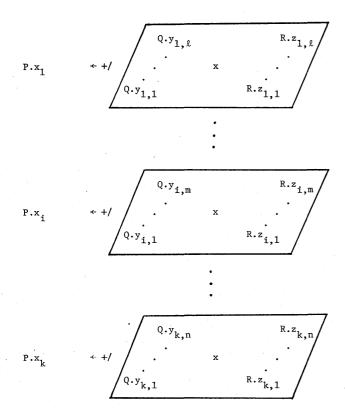

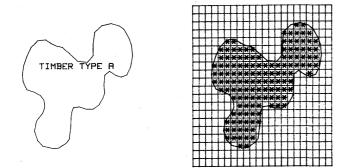

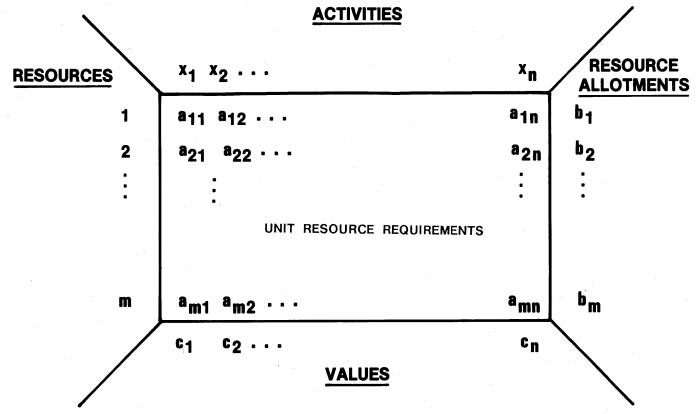

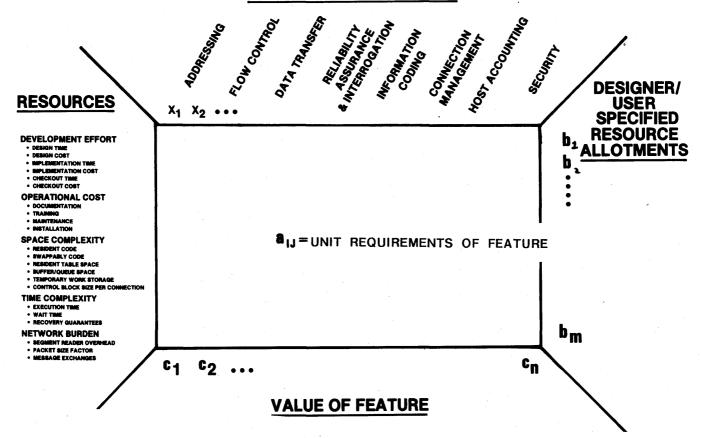

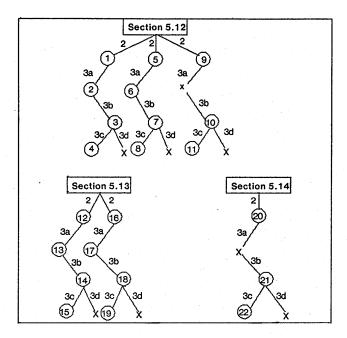

with t denoting the transpose. The procedure represented in equation (9) is illustrated in Figure 1.

Figure 1-Linear allocation model.

#### RAINBOW: A CONVERSATIONAL DECISION SUPPORT SYSTEM

Basically speaking, when he uses the allocation method of equation (9), the decision maker has only to select a set of evaluation elements  $\{E_1, E_2, \ldots, E_m\}$  and determine the values of the weight vector <u>e</u> and the evaluation matrix A. But the problems of (1) selection of the evaluation elements, (2) determination of suitable weights for the elements, and (3) evaluation of the branch offices with respect to each of the evaluation elements, all required considerable time and efforts.

Managers felt that they might not have identified all of the significant evaluation elements. They wanted to try various alternative sets of evaluation elements, but the number of branches, in this case more than 100, prohibited them from trying more than a few sets of elements. The weights, even for the same set of elements, should change according to the changes in social and business environment; but again they were in need of tools for finding adequate values for the weights. Evaluation of the branches was also a tedious and difficult task.

Discussion with the managers revealed the general view that these problems were not to be solved uniquely by some set of fixed criteria, but to be solved through an iteration of trial-and-error simulation, out of which an admissible solution was expected to emerge. Then, the support system should help the decision maker to observe the change in the allocation plan corresponding to the changes in the set of evaluation elements, modifications of the element weights and re-evaluations of the branches.

Another need which the results of the requirement analysis (the SADT: Structural Analysis and Design Technique<sup>7</sup> was used) revealed was the inverse computation of the element weight vector  $\underline{e}$  and the branch evaluation matrix A. In many cases the mangers have, or they think they have, an *a priori* solution to the question, "What is the best allocation plan?" Similarly the decision maker has his idea as to the most appropriate values of  $\underline{e}$  and A. But, without any reference values, i.e., tentative values of  $\underline{e}$  and A, it is often difficult for him to express it quantitatively. If a trial value is given to him, it is relatively easy for him to specify how it should be modified.

Let these "intuitive solutions" be denoted as  $\underline{\widetilde{u}}, \underline{\widetilde{e}}$  and Aat. It can be said that a necessary condition for the decision making process of budget allocation to come to an end is that these intuitive solutions, after undergoing the articulation-modification process, have become consistent in the sense that they satisfy:

$$\underline{\widetilde{u}} = \widetilde{A} \underline{e} S. \tag{14}$$

This consistency, or agreement, among the intuitive values of  $\underline{u}$ ,  $\underline{e}$  and A is hard to attain. One reason for this is that, as already mentioned, the number of branches is quite large. Another reason is that the managers did not have a means of finding values of  $\underline{e}$  and/or A corresponding to the allocation plan  $\underline{\tilde{u}}$  which they could specify.

In order to check the consistency condition of equation (14) and to facilitate the convergence to the set of values  $\underline{\widetilde{u}}, \underline{\widetilde{e}}$  and  $\overline{A}$  which satisfy equation (14), the decision support system should have the capability of inverse computation of  $\underline{e}$  and A corresponding to the allocation plan  $\underline{\widetilde{u}}$  given by the decision maker. On these grounds RAINBOW\_was designed as an on-line conversational system based on the three basic algorithms described below.

#### Algorithm 1

This is the direct application of equation (9), i.e., computation of the allocation vector  $\underline{u}$  when values of the branch evaluation matrix A and the element weight vector  $\underline{e}$  are specified by the decision maker. Schematically this is

#### $\underline{e}$ , A and $S \rightarrow \underline{u}$ .

Decision maker can use Algorithm 1 to analyze sensitivity of the allocation plan to changes in the values of  $\underline{e}$  and A.

#### Algorithm 2

This algorithm computes weight vector  $\underline{e}$  corresponding to the specified values of  $\underline{u}$ , A and S. Schematically this is

#### <u>u</u>, A and $S \rightarrow \underline{e}$ .

That is, the decision maker can use the Algorithm 2 to obtain answer to the question, "If I allocate the budget to branches like this value of  $\underline{u}$  vector, what value does it mean I am assigning to the weight vector  $\underline{e}$ ? If that value of  $\underline{e}$  does not deviate much from the value I can accept, I might be able to say that my evaluations of the three decision variables,  $\underline{u}, \underline{e}$  and A, are in agreement with each other and I am in business. If it does not, I have something further to think about."

The least-squares solution for  $\underline{e}$  is given by

$$\begin{bmatrix} e_1 \\ e_2 \\ e_m \\ \lambda/2 \end{bmatrix} = \begin{bmatrix} (\underline{a}_1, \underline{a}_1) (\underline{a}_1, \underline{a}_2) \dots (\underline{a}_1, \underline{a}_m) 1 \\ (\underline{a}_2, \underline{a}_1) (\underline{a}_2, \underline{a}_2) \dots (\underline{a}_2, \underline{a}_m) 1 \\ (\underline{a}_m, \underline{a}_1) (\underline{a}_m, \underline{a}_2) \dots (\underline{a}_m, \underline{a}_m) 1 \\ 1 & 1 & \dots & 1 & 0 \end{bmatrix} \begin{bmatrix} (\underline{a}_1, \underline{u})/S \\ (\underline{a}_2, \underline{u})/S \\ (\underline{a}_m, \underline{u})/S \\ 1 \end{bmatrix}$$

(15)

where (,) denotes the inner product and  $\lambda$  is the Lagrange multiplier for the constraint (4). Here we note that, in general,  $N \ge m$ , and the use of the least-squares estimation is justified in the statistical sense.

The weight vector  $\underline{e}$  obtained from equation (15) does not necessarily satisfy the positivity condition (5). If the estimated weight  $e_j$  for some element  $E_j$  is nonpositive, it indicates strong inconsistency between the specified values of  $\underline{u}$  and A. Also the inverse matrix in the equation (15) does not exist when vectors  $\underline{a}_j$  in matrix A are linearly dependent. This means that the set of elements  $\{E_1,..,E_m\}$  has redundancy in the sense that evaluation vector  $\underline{a}_j$  of certain element  $E_j$  can be represented as a combination of evaluation vectors for other elements. RAINBOW gives warning messages when the nonpositivity or the redundancy phenomena occurs.

There can be a case where a decision maker does not want to eliminate the redundancy in the evaluation elements; or the least-squares method gets ill-posed and cannot find positive solution for  $\underline{e}$  vector when only a slight change in  $\underline{u}, \underline{e}$  or A would be sufficient to give positive e. Then the decision maker can obtain estimation of  $\underline{e}$  which satisfies both conditions (4) and (5) by solving the following nonlinear programming problem:

$$minimize \|\underline{u} - A\underline{e}S\| \tag{16}$$

s.t.

$$e_1 + e_2 + \dots + e_m = 1.0$$

(17)

$$e_j > 0$$

, for  $j = 1, \dots, m$ , (18)

where  $\| \|$  denotes Euclidean norm of vectors. A random search method, called the hyperconical random search,<sup>8</sup> is used to avoid the numerical difficulty which may be caused by the linear dependency.

#### Algorithm 3

Since it is not possible to estimate all elements of the matrix A at one time, this algorithm performs the task of inverse computation in a limited way, schematically shown as

where  $A^{(j)}$  denotes the submatrix of A formed by deleting  $\underline{a}_j$  from A. That is, we assume that only the evaluation vector  $\underline{a}_j$  with respect to evaluation element  $E_j$  is unknown and

compute  $\underline{a}_i$  uniquely using the following equation:

$$a_{ij} = (u_i/S - \sum a_{ik}e_k)/e_j$$

(19)

for i=1,...,N. Here the summation is taken for k=1,...,mexcept for k=j. That is, the decision maker can obtain an answer to the question, "If I allocate the budget like in this vector  $\underline{u}$ , and evaluate the elements like in this vector  $\underline{e}$ , and if I am uncertain as to the appropriateness of my present evaluation of branches with respect to this particular evaluation element  $E_j$ , then what is the  $\underline{a}_j$  corresponding to my  $\underline{u}$  and  $\underline{e}$ , provided that, of course, my evaluations for the other elements are tentatively considered appropriate? If I can accept the value for  $\underline{a}_j$ , I am in a good shape; if not I must think further."

Again, when there is strong inconsistency among the specified values of  $A^{(i)}$ , <u>e</u> and <u>u</u>,  $a_{ij}$ s of equation (19) do not necessarily satisfy the nonnegativity condition (6). A warning message is given in this case also.

The following is a scenario of the decision making process in which RAINBOW is used to select a budget plan.

#### Step 1

Decision maker selects evaluation elements tentatively, evaluates them by assigning weights he considers suitable and evaluates branch offices with respect to each of the elements.

#### Step 2

Decision maker allocates the total budget to branches using the Algorithm 1.

Decision maker checks the tentative budget plan displayed on the terminal. If he feels that it is appropriate and he can accept it, he terminates the session. If he feels that it should be modified, or that he should try other values of  $\underline{e}$  and/or A, he goes to Step 4.

#### Step 4

Decision maker determines what should be modified: (1) if the decision maker feels that the evaluation elements  $\{E_1, \ldots, E_m\}$  should be changed, he goes to Step 1; (2) if he feels that the element weights should be re-evaluated, he goes to Step 5; (3) if he feels that the branches should be re-evaluated, he goes to Step 6; (4) if he feels that both the elements and the branch offices should be re-evaluated, he goes to Step 1.

#### Step 5

Decision maker selects one of the following alternatives: (1) if he wants to modify the element evaluation, he specifies new  $\underline{e}$  and goes to Step 2, or (2) if he wants to modify the budget  $\underline{u}$  and observe the corresponding element weight  $\underline{e}$ , he gives new  $\underline{u}$ , compute  $\underline{e}$  using the Algorithm 2, and goes to Step 7.

#### Step 6

Decision maker selects one of the following alternatives: (1) if he wants to modify the branch evaluation matrix A, he specifies new A and goes to Step 2, or (2) if he wants to modify the budget  $\underline{u}$  and observe the corresponding branch evaluation, he first selects  $\underline{a}_{j}$  which should be computed, computes  $\underline{a}_{j}$  using the Algorithm 3, and goes to Step 8.

#### Step 7

If the decision maker feels that the element weight vector  $\underline{e}$  computed by the Algorithm 2 is appropriate, he goes to Step 2, otherwise he goes to Step 5.

#### Step 8

If the decision maker feels that the branch evaluation vector computed by the Algorithm 3 is appropriate, he goes to Step 3, otherwise he goes to Step 6.

The above scenario is only an example of a session with RAINBOW. Users of RAINBOW can use any of the three algorithms at any stage of the session.

#### DISCUSSION AND CONCLUDING REMARKS

In this final section we review the decision support system RAINBOW in the general framework of multiple objective programming.

A general form of multiobjective programming problem based on the utility concept is:

$$\underset{\underline{x} \in X}{\text{maximize}} \quad U[g_1(\underline{x}), g_2(\underline{x}), \dots, g_m(\underline{x})]$$

(20)

where  $\underline{x} = (x_1, \dots, x_N)^t$  and X is a subset of  $\mathbb{R}^N$ . Functions  $g_j$  are objective functions and U gives the utility as a function of  $G_j$ s.

If both U and  $g_{i}$ s are explicitly known, the gradient vector of U with respect to x is:

$$\nabla_{\underline{x}} U = \sum_{j=1}^{m} \left( \frac{\partial U}{\partial g_j} \right) \nabla_{\underline{x}} g_j.$$

(21)

Geoffrion et al.<sup>6</sup> presented a conversational decision support

method for the case where  $g_{js}$  are explicitly given but U is known only implicitly. Their method is called IFW (Interactive Frank-Wolfe) method and employs the Frank-Wolfe algorithm to solve the direction problem which is specified when the underlying utility function U is locally approximated by the decision maker.

As indicated in this paper, there are cases in the real-world decision situation in which not only the underlying utility function U but the objective functions  $g_j$  are not given explicitly and must be locally approximated as the decision making process proceeds. The Multiattribute Utility Theory is an attempt to cope with such situations.

Since linear approximation is one of the most elementary methods of function approximation, let us assume that the decision maker can supply a local linear approximation

$$g_{j}(x) = a_{1j}x_{1} + a_{2j}x_{2} + \dots + a_{Nj}x_{N} + b_{j}$$

(22)

for each of the "true"  $g_{js}$  in the neighborhood of any nominal solution  $\underline{x}$  in X. Here the coefficients  $a_{ij}$  depend on the incumbent solution  $\underline{x}$  and therefore they should be locally restimated in the iterative process of decision making.

When the objective functions  $g_j$  are given in their linearly approximated form of equation (22), equation (21) is written in the form of matrix-vector multiplication as

$$\nabla_{\underline{x}}U = \nabla_{x}g\nabla_{g}U \tag{23}$$

where  $g = (g_1, \dots, g_m)^t$  and

$$\nabla_{\underline{g}} U = \left( \frac{\partial U}{\partial g_1}, \frac{\partial U}{\partial g_2}, \dots, \frac{\partial U}{\partial g_m} \right)$$

(24)

Also,  $\nabla_x g$  is just the A matrix given in equation (12).

It is not difficult to notice the correspondence between the evaluation elements in the allocation procedure and the "attributes," or objective functions, in the theory of multiple objective decision making. Then the correspondence between equation (9) and (23) is also clear. Since  $\nabla_g U$  represents sensitivities of U to the changes in the objective functions  $g_j$ , it corresponds to the element weight vector  $\underline{e}$ . The correspondence between the branch evaluation matrix A and the gradient matrix  $\nabla_x g$  is apparent when we consider  $\underline{x}$  as the allocation vector  $\underline{\mu}$ .

From these observations we know that equation (9) is actually the gradient  $\nabla_x U$  when objective functions  $g_j$  are given in linearly approximated form. Equation (9) means that, under the constraint of (2), the total fund S should be allocated exactly proportionately to the ratio of the elements of the gradient vector.

Then, RAINBOW is a decision support system for the case where not only the underlying utility function U but the objective functions  $g_j$  cannot be given except in the local approximations. RAINBOW helps the decision maker to estimate the two gradients  $\nabla_{g}g$  and  $\nabla_{g}U$  in a trial-and-error manner.

Since we assumed that  $g_j$ s are only implicitly known we have lost the assurance of local optimality we can expect when we locally fix an evaluation of the utility function. This is the price to be paid for loosening the assumptions as to the type of decision situations to be covered. In place of the algorithm for solving the local optimization problem, RAIN-BOW is equipped with the three algorithms to help the decision maker to form the consistency among his answers to the question, "What are the most appropriate values for  $\underline{e}$ ,  $\underline{u}$  and A?"

Clearly this is not the only means of decision support in these loosely structured situations. Other approaches must be experimented.

As our concluding remark we want to point out that the development of RAINBOW was not initiated by the theoretical considerations discussed above; it was based on the analysis of the actual behavior, or procedure, of the decision makers in the bank. It seems that the importance of the behavioral analysis of the actual decision procedure increases when we are to design a decision support system under the loosely structured situation.

#### REFERENCES

- 1. Haimes, Y. Y. and Hall, W. A., "Multiobjectives in Water Resource Systems Analysis: The Surrogate Worth Trade-off Method," Water Resources Research, vol. 10 no. 4, 1974, pp. 615-624.

- Hall, W. A. and Haimes, Y. Y., "The Surrogate Worth Trade-off Method with Multiple Decision Makers," in *Multiple Criteria Decision-Making*: Kyoto 1975, M. Zelney (ed.), Springer-Verlag, New York, 1976, pp. 207-233.

- 3. Keeney, R. L. and Raiffa, H., Decisions with Multiple Objectives: Preferences and Value Tradeoffs, J. Wiley, New York, 1976.

- Haimes, Y. Y., Das, P., and Sung, K., "Multiobjective Analysis and Related Land Resources Planning," in *Water Resources and Land Use Planning*, P. Laconte and Y. Y. Haimes (eds.), 1979.

- de Neufville, R. and Keeney, R. L., "Use of Decision Analysis in Airport Development for Mexico City," in *Analysis of Public Systems*, A. W. Drake, R. L. Keeney and P. M. Morse (eds.), M.I.T. Press, 1972.

- Geoffrion, A. M., Dyer, J. S., and Feinberg, A., "An Interactive Approach for Multi-criterion Optimization, with an Application to the Operation of an Academic Department," *Management Science*, 19(4), 1972, pp. 357-368.

- Dickover, M. E., McGowan, C. L., and Ross, D. T., "Software Design using SADT." in *Proceedings of the ACM National Conference*, Seattle, Washington, October 1977.

- 8. Wozny, M. J. and Heydt, G. T., "Hyperconical Random Search," Journal of Dynamic Systems, Measurement and Control, March 1972, pp. 71-77.

## **Decision support systems: a practical application—Branch** office structure

by JOHN R. WETMILLER Digital Equipment Corporation Maynard, Massachusetts

#### INTRODUCTION

As the decade of the 1980s approaches, it is generally agreed that computer companies will stress not technology, but rather customer service functions as a means to differentiate themselves from one another. Consequently, the need to understand the customer's service requirements and to plan for them is tantamount.

Simply stated, the purpose of a computer service organization is to provide maintenance services to customers with computer equipment. The primary objective of the organization is to minimize the down-time of that customer equipment and thereby minimize customer inconvenience. At the same time the service organization seeks to operate as cost effectively as possible which, of course, minimizes the service cost to the customer. To provide the maintenance services required, computer service organizations will generally establish a branch office to supply the needs of customers within a certain geographical region. In order to effectively structure that office three fundamental questions need to be answered:

- What types of service engineers should the office have (i.e., should the engineers be generalists, specialists, or some combination);

- 2.) How large should the branch office be (i.e., how many service engineers are required); and

- 3.) How should service requests or calls of different types be scheduled and which engineer types should be assigned (e.g., first-come-first-served, shortest-expected-service-time; generalist, specialist).

For our company the task of addressing these questions was given by our upper level management to our internal management science consulting group. In the discussions that follow in this paper, I will indicate our findings specifically with regard to question 1. Although some of the numerical results of our studies must remain proprietary, I will indicate the overall conclusions reached and note the pilot test plans that have resulted from our work. I will comment briefly about questions 2 and 3 throughout my discourse on question 1. The complete answers to those questions are still being determined; perhaps, in the future, they can be incorporated into papers similar to this one.

#### SUMMARY RESULTS

At the outset it was generally felt amongst the members of the analysis team that the proper use of engineer specialization could generate significant branch savings over an all engineer generalist environment. To define terms, an engineer specialist is an individual who can perform *certain* repair tasks in less time than the average engineer generalist who is able to perform *any* repair task. Our findings confirmed that, indeed, engineer specialization can result in considerable savings to a branch office. These savings may be expressed as lower response time or increased call handling (or call rate) capability, with no increase in personnel nor in cost. If the proper conditions are present at the branch, specialization can even possibly result in reduced personnel and lower costs.

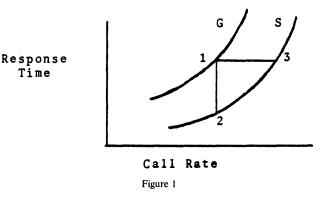

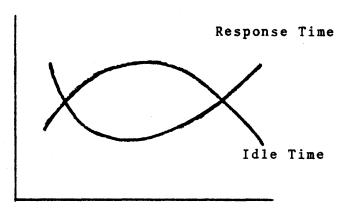

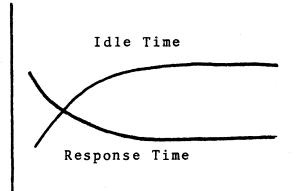

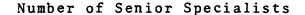

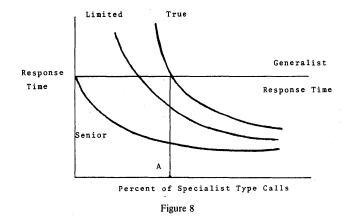

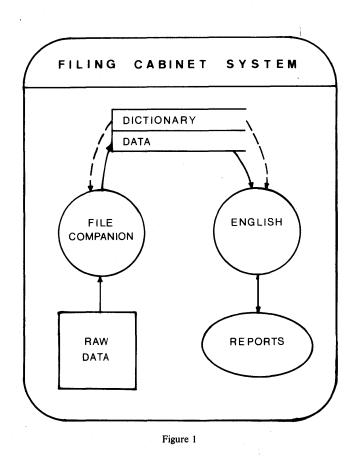

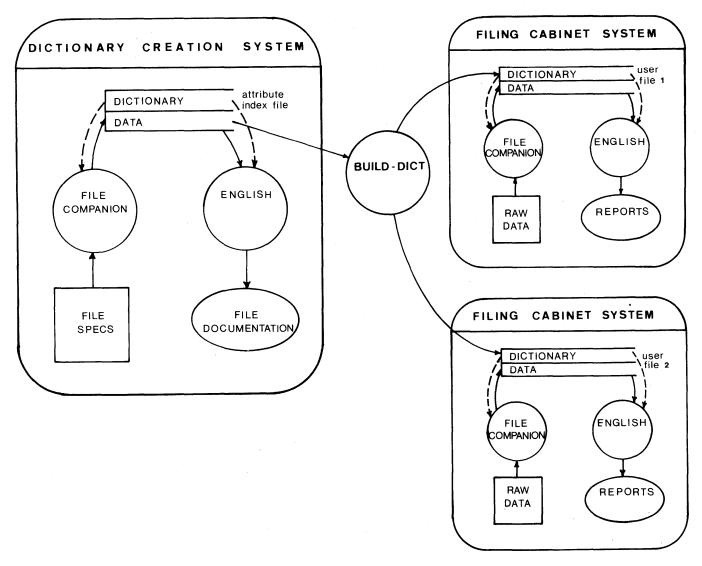

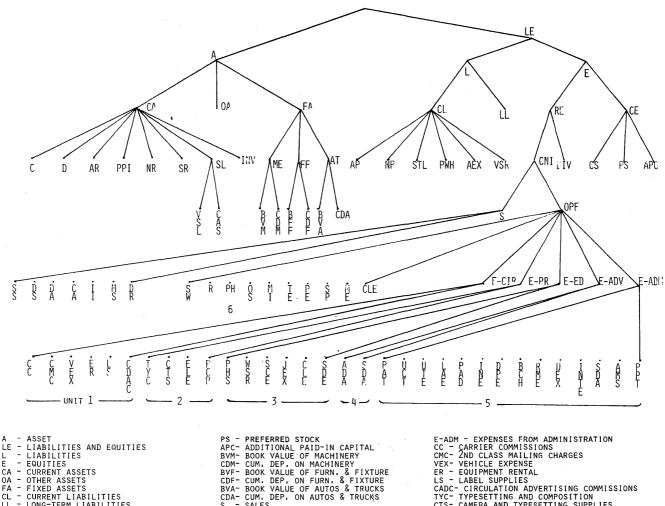

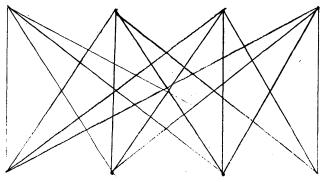

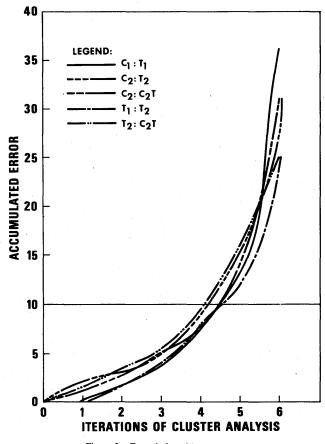

Figure 1 shows two plots of response time versus call rate. The one to the left is for an all generalist office (no specialization) while the one to the right is for an office with some specialization. Note that the response time/call rate curve for the specialist office lies below and to the right of the non-specialist office.

The implications of this shift are summarized in Table I and discussed below.

Table I

|                     | From Point 1<br>to Point 2 | From Point 1<br>to Point 3 |

|---------------------|----------------------------|----------------------------|

| Response Time       | Decrease                   | Constant                   |

| Mean-Time-To-Repair | Decrease                   | Decrease                   |

| Call Rate Capacity  | Constant                   | Increase                   |

| Engineer Idle Time  | Increase                   | Decrease                   |

| Engineer Salary     | Decrease                   | Decrease                   |

| Engineer Training   | Decrease                   | Decrease                   |

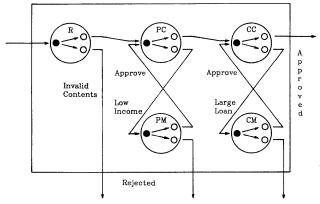

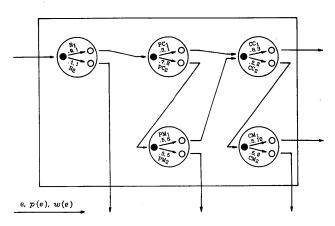

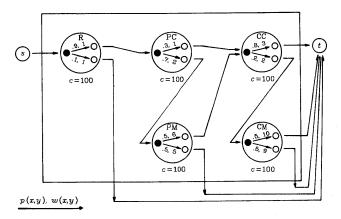

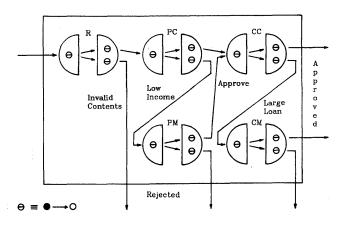

|                     |                            |                            |