# **AFIPS** CONFERENCE PROCEEDINGS

# **1979** NATIONAL COMPUTER CONFERENCE

June 4-7, 1979 New York, New York The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1979 National Computer Conference or the American Federation of Information Processing Societies, Inc.

> Library of Congress Catalog Card Number 55-44701 AFIPS PRESS 210 Summit Avenue Montvale, New Jersey 07645

$\bigcirc$  1979 by AFIPS Press. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) reference to the AFIPS Proceedings and notice of copyright are included on the first page. The title and abstract may be used without further permission in computer-based and other information-service systems. Permission to republish other excerpts should be obtained from AFIPS Press.

Printed in the United States of America

### Preface

MERLIN SMITH Conference Chairman

The Proceedings of the 1979 National Computer Conference represents the most comprehensive, in-depth treatment of computing developments available today. It stands as a lasting credit to Richard Merwin and his program committee, and to the many authors, session chairpersons, reviewers and other contributors recognized on these pages.

Data processing has rapidly become one of the more vital factors in the economic and personal well being of all. The NCC program was directed to these many new interests of participants. Such an objective required many panel and discussion sessions beyond the formal papers, and the limits of this Proceedings. We owe a special debt to these participants who helped make our conference a success. Their names are recorded herein.

We appreciate this opportunity to be a part of recorded computer history.

### Introduction

RICHARD E. MERWIN NCC '79 Program Chairman

The NCC '79 technical program was planned to be a learning experience for all attendees. A broad range of paper and panel sessions was selected to emphasize social implications of computers, management issues, technical developments and applications. Each of these areas is represented by both paper and panel sessions which are designed to bring the attendees of this "biggest of all" computer conference to the forefront of knowledge of each specialty.

A major attempt has been made to broaden the scope of the NCC '79 technical program by including three mini-conferences covering the application of computers to financial transactions, law and health services. Thirty-two sessions dealing with these topics will expand the coverage of NCC '79 to an audience of specialists in fields which are increasingly becoming allied with data processing techniques.

The urge to participate in the NCC '79 technical program was overwhelming. Because of a limitation on the size of this Proceedings, the number of papers that could be accepted for publication was curtailed. A large number of proposals were received for panel sessions and a selection of the best of these was made. This trend for more and more participation in both the technical program and the exhibition of the latest computer products mirrors the tremendous growth of the computer industry, especially in the areas of microprocessors. In response to the wide interest in the use of computers by the non-professional, a special set of sessions and a separate publication devoted to personal computing has been organized to augment the technical program and regular exhibits. The interest in this aspect of the computer industry has increased rapidly and represents a major factor in this industry.

This Proceedings is organized by specialized areas including Applications, Social Implications, Architecture, Data Base Management, Computer Technology, Networking and Software Techniques, in that order. Unfortunately, we had to eliminate overview statements by topical area organizers along with descriptions of panel sessions to maximize the number of technical papers that could be published. I regret these omissions but feel that our policy of publishing only technical papers best serves the technical goals of the conference.

The planning and organization of the NCC '79 technical program involved a number of area coordinators, session organizers and leaders and the panelists and presenters of technical papers. I want to extend my sincere appreciation to all those who supported the organization of this outstanding technical program. Special thanks is due to the hundreds of referees who helped us select the best papers. Finally, I want to thank the program committee staff who tirelessly worked with all participants to make this conference a success.

## CONTENTS

| Preface                                                                                                                                    | iii |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction                                                                                                                               | iv  |

| APPLICATIONS                                                                                                                               |     |

| Computer technology in the movie industry<br>Suzanne Landa                                                                                 | 1   |

| The system architecture evaluation facility—An emulation facility at Rome Air Development Center<br>N. Bruce Clark and Michael A. Troutman | 7   |

| Teaching and research experiences with an emulation laboratory<br>Steven F. Sutphen                                                        | 13  |

| Simulating the delay in logic networks for large, high-speed computers                                                                     | 19  |

| Languages for operating systems description, design and implementation                                                                     | 29  |

| The simulation language SIML/I                                                                                                             | 39  |

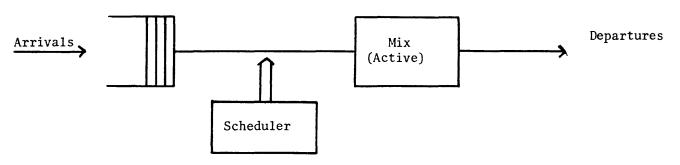

| Mix-dependent job scheduling—An application of hybrid simulation<br>Steve Tolopka and Herb Schwetman                                       | 45  |

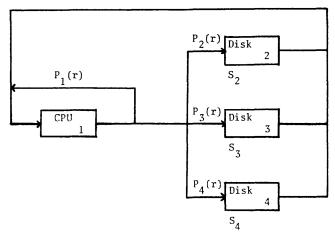

| Parametric instabilities in computer system performance prediction<br>Lawrence W. Dowdy and Ashok K. Agrawala                              | 51  |

| Aids to the development of network simulators<br>Imrich Chlamtac and W. R. Franta                                                          | 57  |

| A stochastic state space model for prediction of product demand<br>William C. Cave and Evelyn Rosenkranz                                   | 67  |

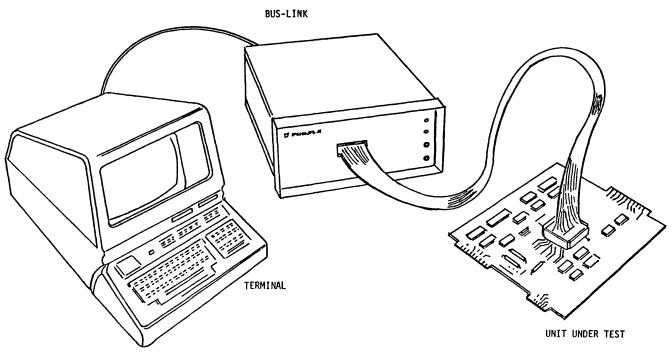

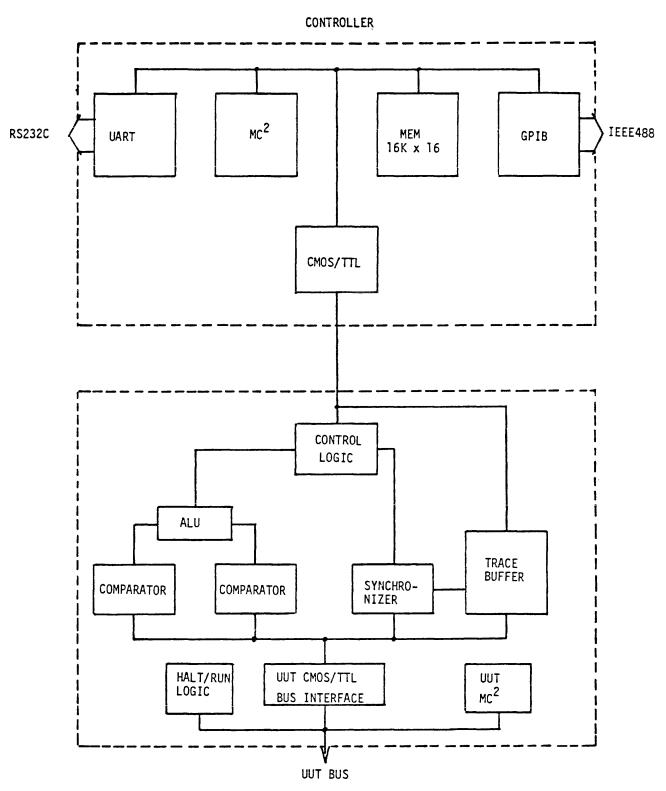

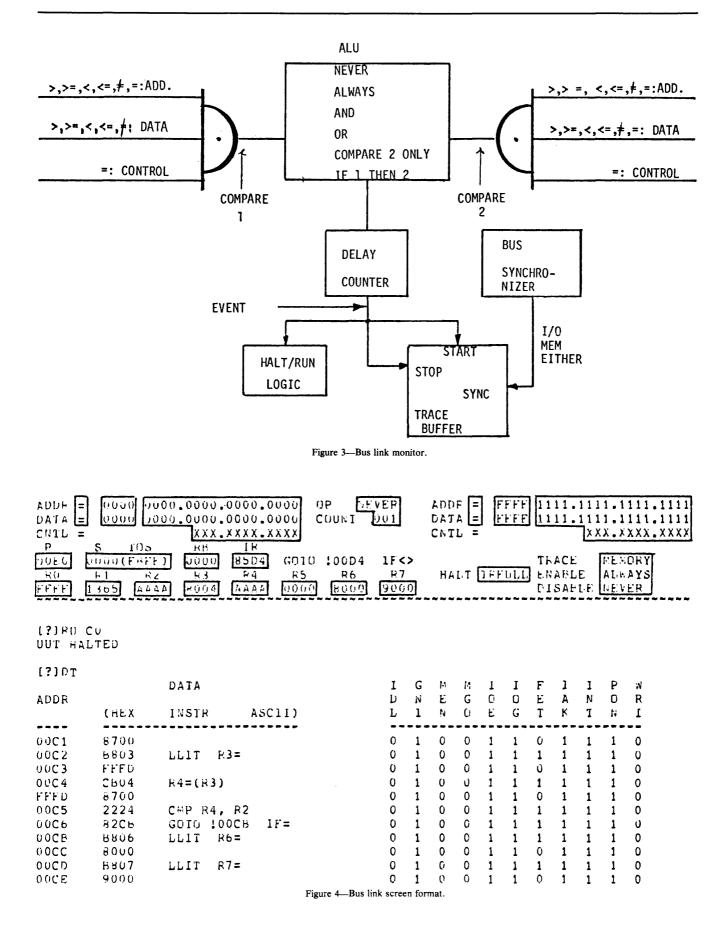

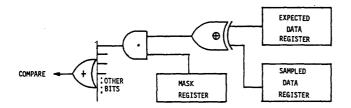

| The Bus Link—A microprogrammed development tool for the CMOS/SOS processor system<br>Avner Ben-Dor, Paul Baker and Jon Selden              | 73  |

| A computer analysis tool for structural decomposition using entropy metrics                                                                | 83  |

| Interactive modeling systems for managers—Semantic models should underlie quantitative models<br>Rand B. Krumland                          | 89  |

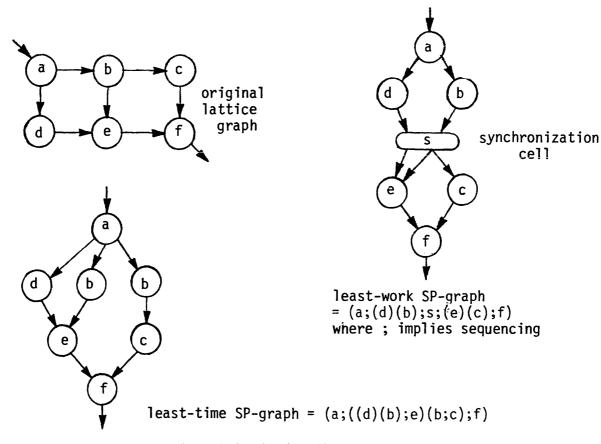

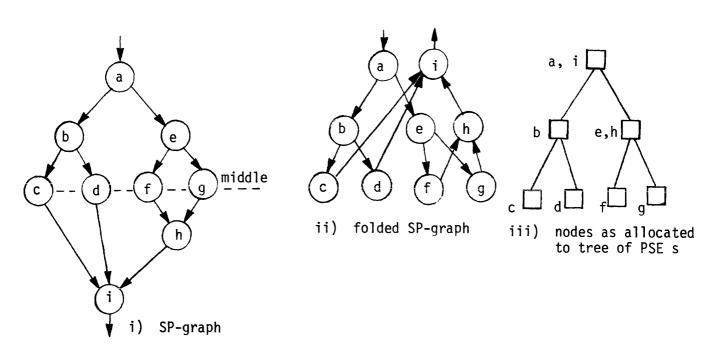

| Modeling regular, process-structured networks<br>Bruce W. Arden and Hikyu Lee                                                              | 95  |

| The City of New York's integrated financial management system—From mandate to working system in 18 months                                  | 103 |

| Recurrent dilemmas of computer use in complex organizations                                                                                | 107 |

| Project management through the Accomplishment Value Procedure (AVP)                                                                        | 117 |

| Textfax—Principle for new tools in the office of the future                                                                                                       | 125 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Microcomputer programming skills<br>C. Wrandle Barth                                                                                                              | 135 |

| Program conversion—One successful paradigm<br>Charles Lynn, Jr., Jean Risley and Robert Wells                                                                     | 139 |

| A generalized zooming technique for pictorial database systems<br>S. K. Chang, B. S. Lin and R. Walser                                                            | 147 |

| An approach to real-time scan conversion<br>Franklin C. Crow                                                                                                      | 157 |

| The evolution and architecture of a high-speed workstation for interactive graphics                                                                               | 165 |

| A mathematical model for distributed free space<br>Y. H. Chin and S. H. Yu                                                                                        | 175 |

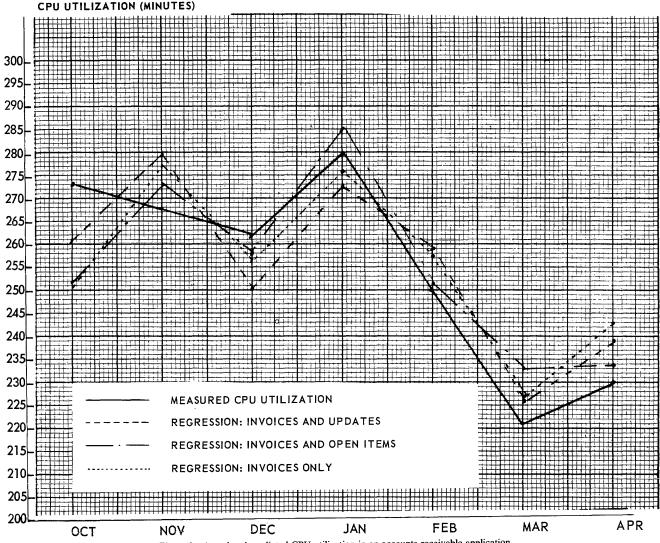

| Forecasting computer resource utilization using key volume indicators<br>David E. Y. Sarna                                                                        | 185 |

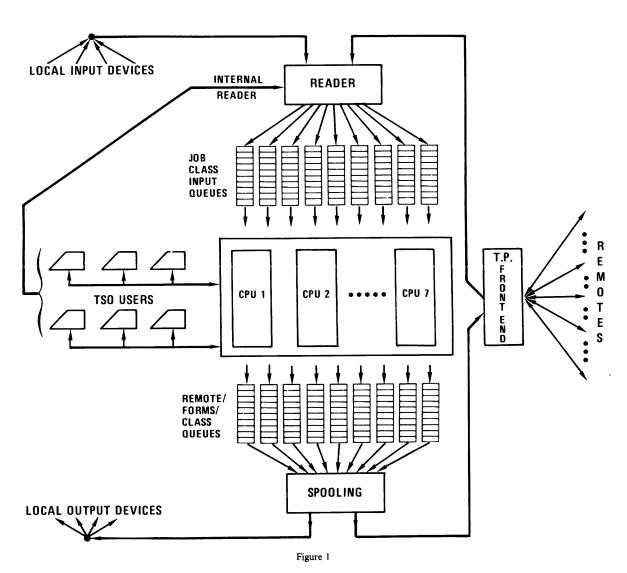

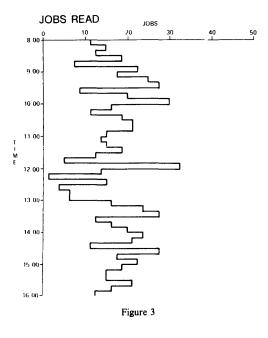

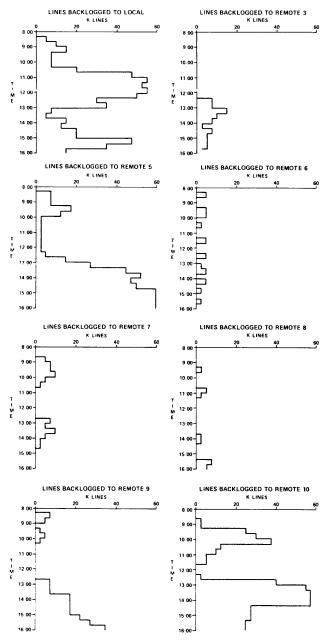

| Workflow—A technique for analyzing JES systems                                                                                                                    | 193 |

| MMPS—A reconfigurable multi-microprocessor simulator system                                                                                                       | 199 |

| A (31,15) Reed-Solomon code for large memory systems<br>Raymond S. Lim                                                                                            | 205 |

| English dictionary searching with little extra space                                                                                                              | 209 |

| New indices for bibliographic data and their applications<br>Yahiko Kambayashi, Shuzo Yajima, Osamu Konishi and Takaki Hayashi                                    | 217 |

| Visual inspection of metal surfaces                                                                                                                               | 227 |

| Monitoring the earth's resources from space—Can you really identify crops by satellite?                                                                           | 233 |

| Digital image shape detection                                                                                                                                     | 243 |

| PM <sup>4</sup> —A reconfigurable multiprocessor system for pattern recognition and image processing<br>Fayé A. Briggs, King-Sun Fu, Kai Hwang and Janak H. Patel | 255 |

| Transportable image-processing software<br>R. G. Hamlet and A. Rosenfeld                                                                                          | 267 |

| A data-handling mechanics of on-line text editing system with efficient secondary storage access<br>Sakti Pramanik and Edgar T. Irons                             | 273 |

| SOCIAL IMPLICATIONS                                                                                                                                               |     |

| How do we best control the flow of electronic information across sovereign borders?                                                                               | 279 |

| Privacy and security in transnational data processing systemsRein Turn                                                                                            | 283 |

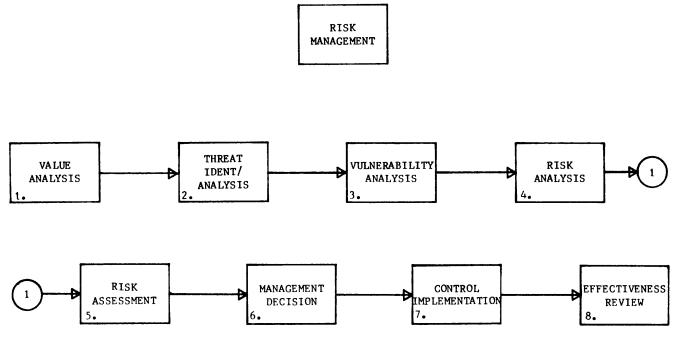

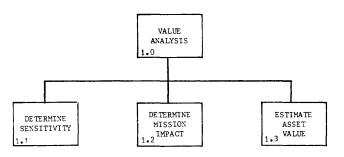

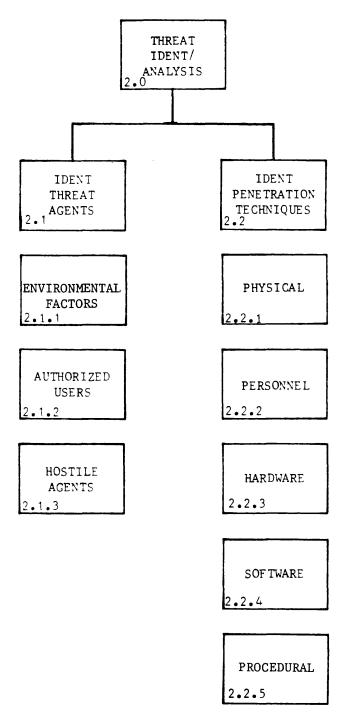

| A modular approach to computer security risk management<br>Robert P. Campbell and Gerald A. Sands                                                                 | 293 |

| The design and operation of public-key cryptosystems<br>Eric H. Michelman                                                                                         | 305 |

| Safeguarding cryptographic keys<br>G. R. Blakley                                                                              | 313 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Applications for multilevel secure operating sytems<br>John P. L. Woodward                                                    | 319 |

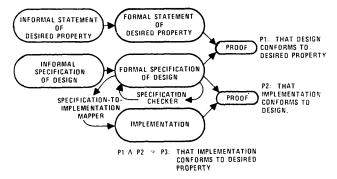

| The foundations of a provably secure operating system (PSOS)<br>Richard J. Feiertag and Peter G. Neumann                      | 329 |

| A security retrofit of VM/370<br>B. D. Gold, R. R. Linde, R. J. Peeler, M. Schaefer, J. F. Scheid and P. D. Ward              | 335 |

| KSOS—The design of a secure operating system<br>E. J. McCauley and P. J. Drongowski                                           | 345 |

| UCLA Secure UNIX                                                                                                              | 355 |

| KSOS—Development methodology for a secure operating system<br>T. A. Berson and G. L. Barksdale, Jr.                           | 365 |

| KSOS—Computer network applications<br>M. A. Padlipsky, K. J. Biba and R. B. Neely                                             | 373 |

| Considerations in the employment of blind computer professionals<br>James A. Kutsch, Jr., and Kimberly B. Kutsch              | 383 |

| Hiring a deaf computer professional                                                                                           | 385 |

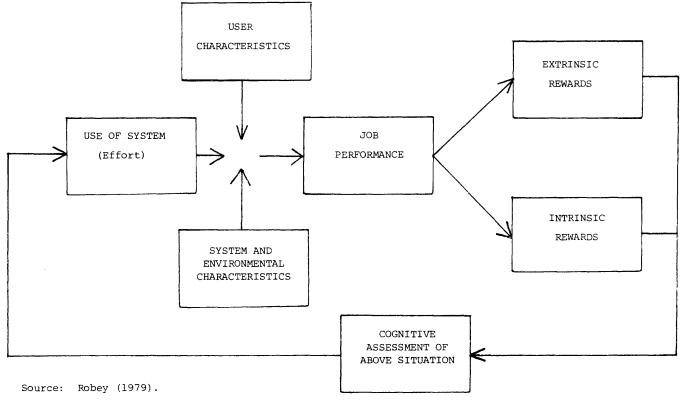

| MIS effects on managers' task scope and satisfaction<br>Daniel Robey                                                          | 391 |

| Some neglected outcomes of organizational use of computing technology—And their implications for systems designers            | 397 |

| An academic meets industry—Rethinking computer-based education and personalized systems of instruction<br>Kenneth L. Modesitt | 403 |

| Recent developments in computers and society research and education<br>Richard H. Austing and Gerald L. Engel                 | 407 |

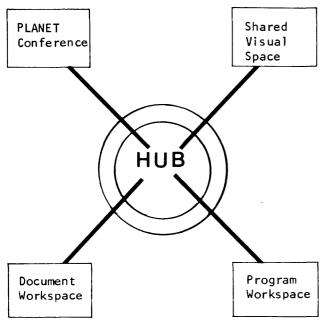

| Interactive monitoring of computer-based group communication<br>Kathleen Spangler, Hubert Lipinski and Robert Plummer         | 411 |

| The status of women in health science computing<br>Lynn L. Peterson                                                           | 415 |

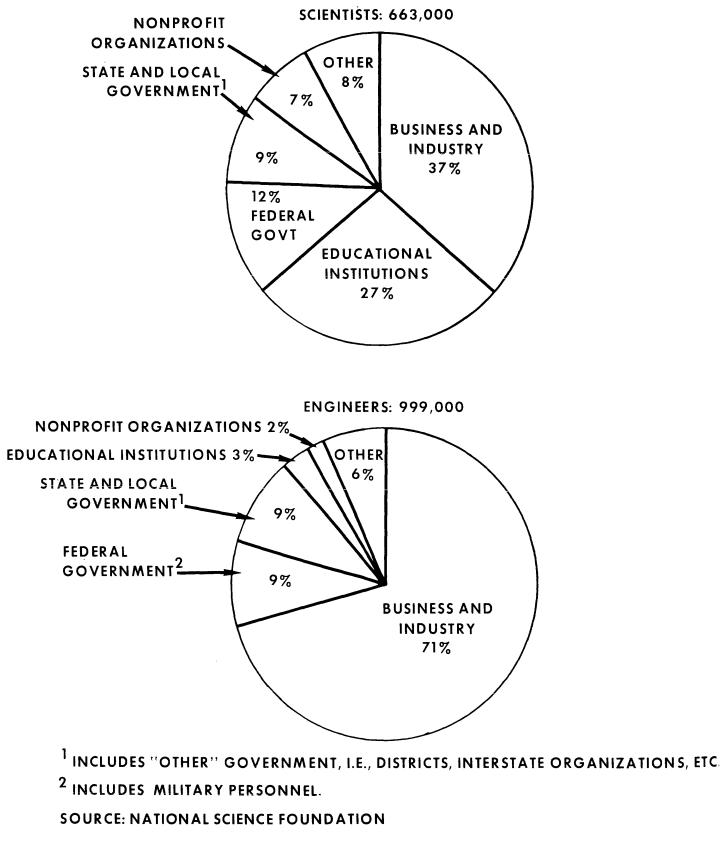

| Women and minorities in the computer professions                                                                              | 419 |

| Computers in judicial administration<br>Charles L. Aird and Barbara H. Todd                                                   | 425 |

| Police and computer technology—The expectations and the results                                                               | 443 |

| ARCHITECTURE                                                                                                                  |     |

| Distributed algorithms for global structuring<br>Raphael A. Finkel, Marvin Solomon and Michael L. Horowitz                    | 455 |

| The tree-structured distributed network front-end processor architecture                                                      | 461 |

| Analysis of real-time control systems by the model of packet nets                                                             | 469 |

Mohamed Gawdat Gouda

| Performance and economy of a fault-tolerant multiprocessor<br>Jaynarayan H. Lala and Charles J. Smith                             | 481 |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Serviceability features of the HP 300 small business computer<br>Curtis R. Gowan                                                  | 493 |

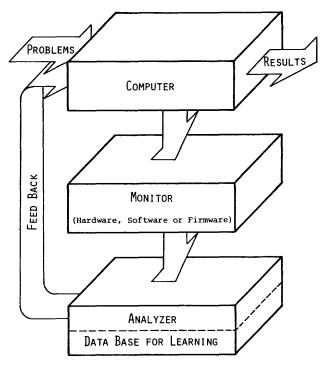

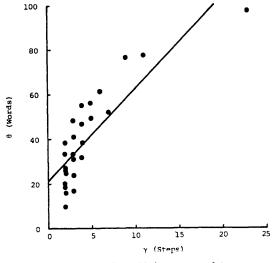

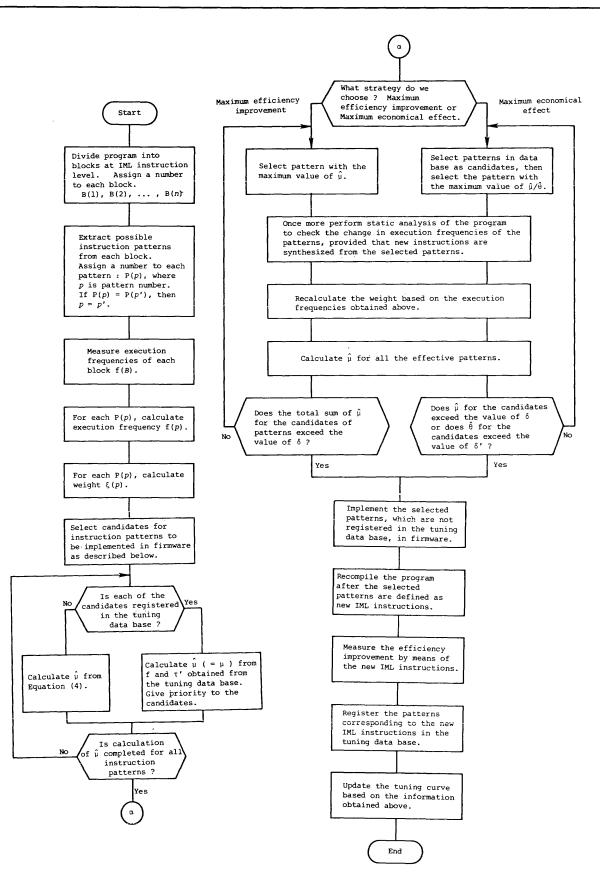

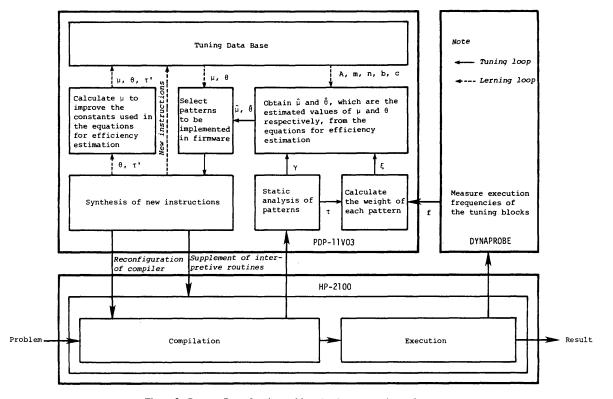

| Automatic tuning of computer architectures<br>Ken Sakamura, Tatsushi Morokuma, Hideo Aiso and Hajime Iizuka                       | 499 |

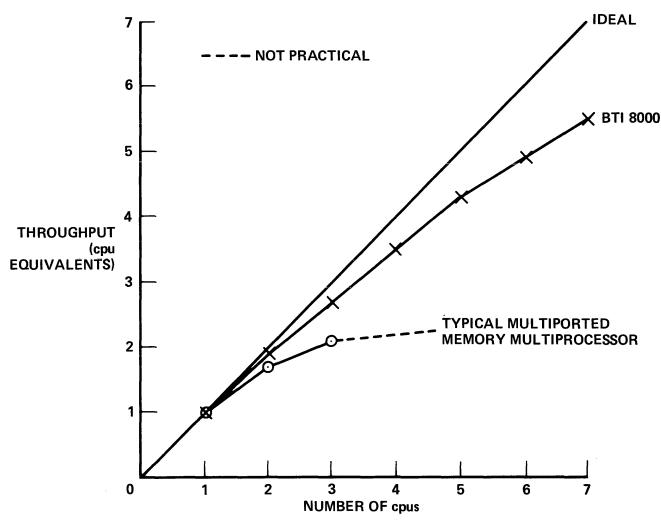

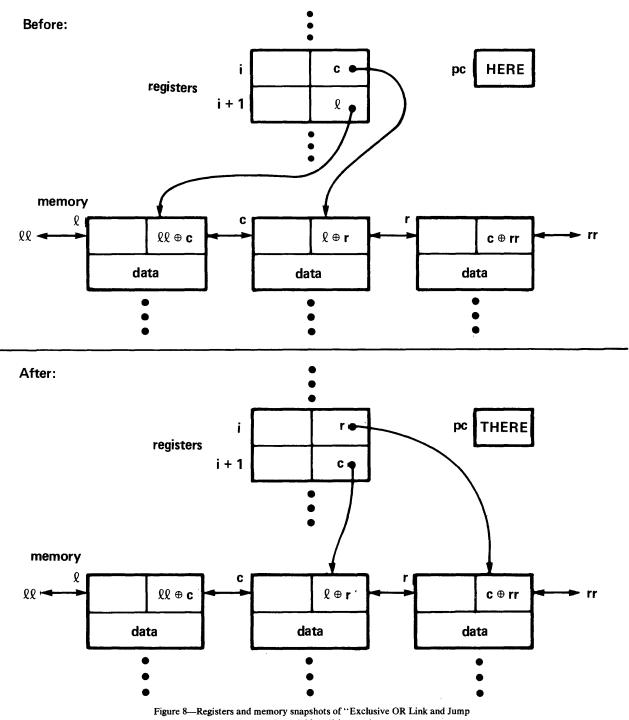

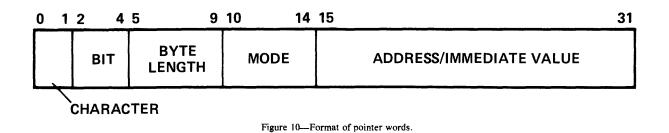

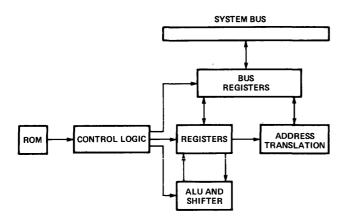

| The BTI 8000—Homogeneous, general-purpose multiprocessing<br>George R. Lewis, J. Shirley Henry and Brian P. McCune                | 513 |

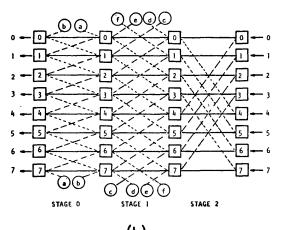

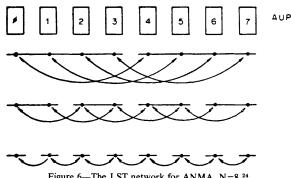

| A survey of interconnection methods for reconfigurable parallel processing systems                                                | 529 |

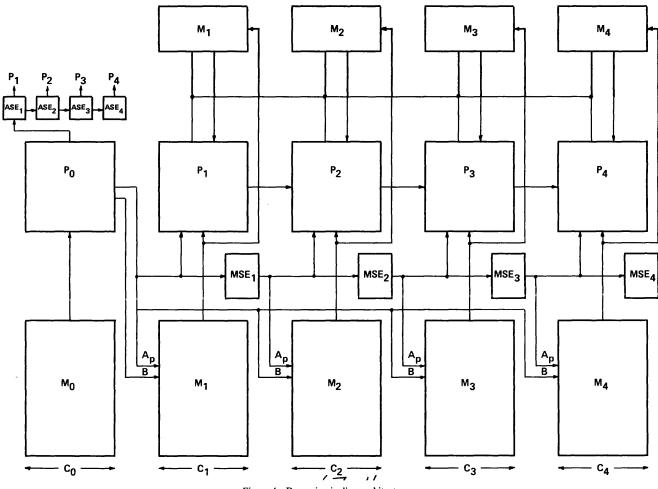

| Adaptation properties for dynamic architectures<br>Steven I. Kartashev, Svetlana P. Kartashev and C. V. Ramamoorthy               | 543 |

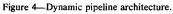

| Architectural considerations of the NEC mass data file subsystem<br>Akira Sekino and Takuo Kitamura                               | 557 |

| Erròr-oriented architecture testing<br>Larry Kwok-Woon Lai                                                                        | 565 |

| A survey of methods for intermittent fault analysis<br>Yashwant K. Malaiya and Stephen Y. H. Su                                   | 577 |

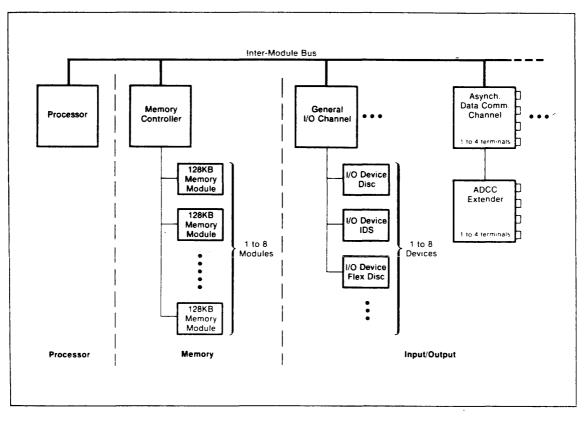

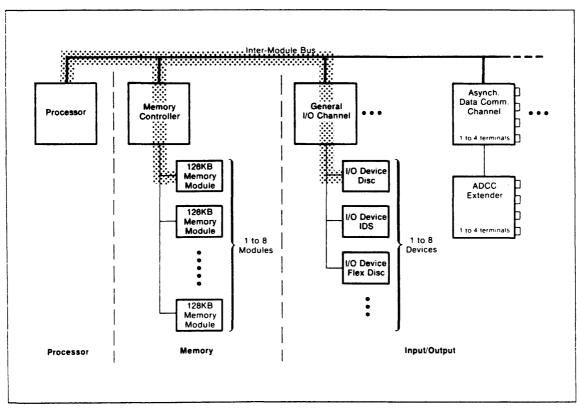

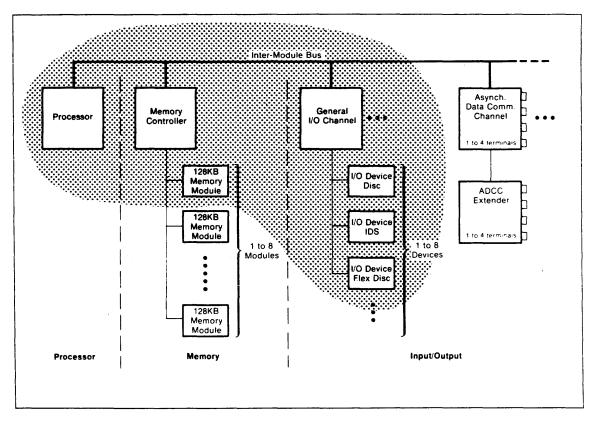

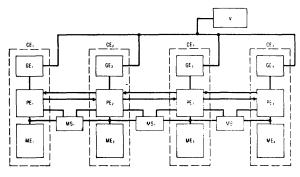

| Architectural and design perspectives in a modular multi-microprocessor, the DPS-1                                                | 587 |

| Work flow view of a distributed application                                                                                       | 595 |

| The use of self-inverse program primitives in system evaluation<br>John E. MacDonald, Jr.                                         | 605 |

| A loosely-coupled applicative multi-processing system<br>Robert M. Keller, Gary Lindstrom and Suhas Patil                         | 613 |

| A prototype data flow computer with token labelling<br>Ian Watson and John Gurd                                                   | 623 |

| A view of dataflow<br>Kim P. Gostelow and Robert E. Thomas                                                                        | 629 |

| A hardware-independent virtual architecture for PASCAL<br>Viswanathan Santhanam                                                   | 637 |

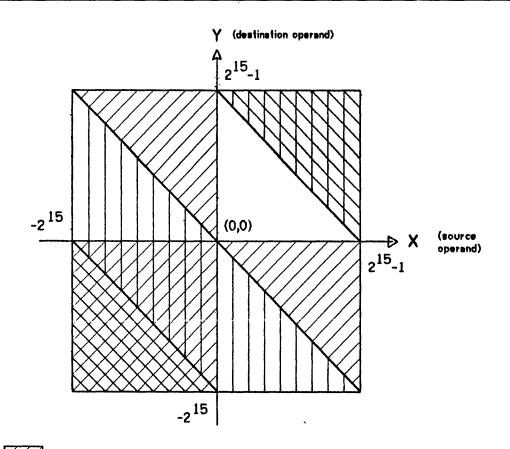

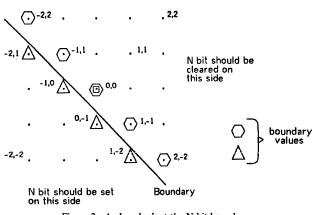

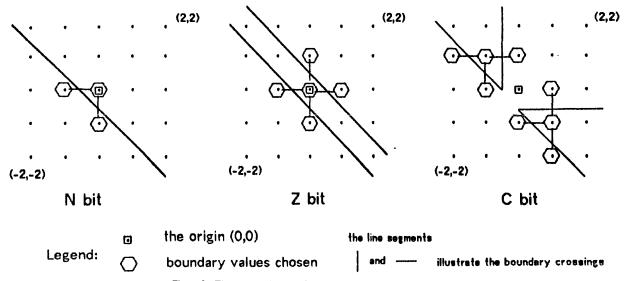

| Design of a high-level language machine<br>G. J. Battarel and R. J. Chevance                                                      | 649 |

| A programming language for high-level architecture<br>Yaohan Chu and Edward Ray Cannon                                            | 657 |

| DATA BASE MANAGEMENT                                                                                                              |     |

| Data management in distributed data bases<br>C. V. Ramamoorthy and Benjamin W. Wah                                                | 667 |

| A unified architecture for data and message management                                                                            | 681 |

| Design of a prototype ANSI/SPARC three-schema data base system                                                                    | 689 |

| On the implementation of a conceptual schema model within a three-level DBMS architecture<br>Shamkant B. Navathe and Johann Lemke | 697 |

| The practice of data base administration<br>Jay-Louise Weldon                                                                                      | 709 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| An approach to automatic maintenance of semantic integrity in large design data bases                                                              | 713 |

| On query-answering in relational data bases<br>E. L. Lozinskii                                                                                     | 717 |

| ASTROL—An associative structure-oriented language<br>James F. Wirth                                                                                | 721 |

| An associative search language for data management                                                                                                 | 727 |

| Updating defined relations<br>I. M. Osman                                                                                                          | 733 |

| Performance enhancement for relational systems through query compilation                                                                           | 741 |

| COMPUTER TECHNOLOGY                                                                                                                                |     |

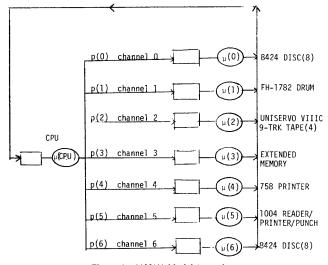

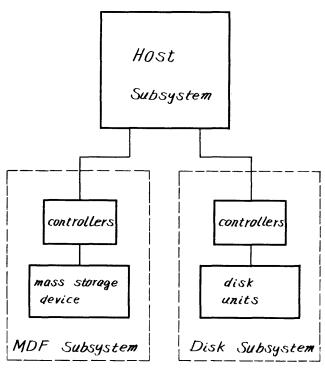

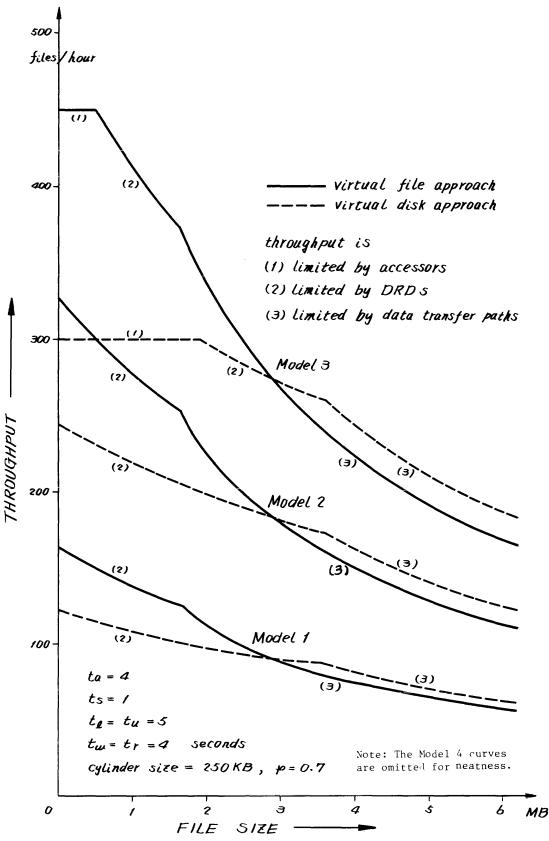

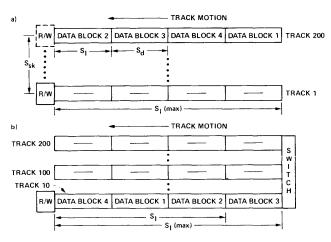

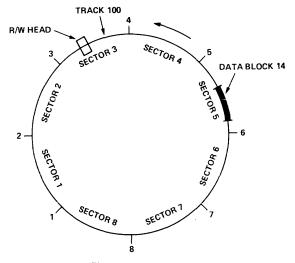

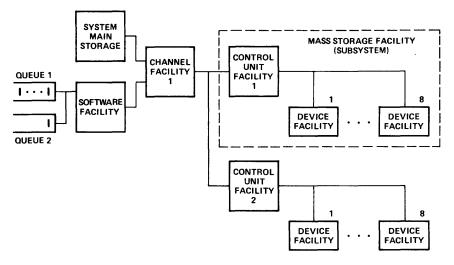

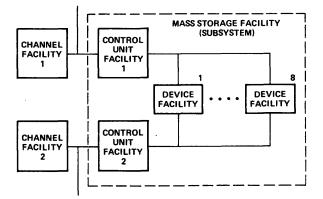

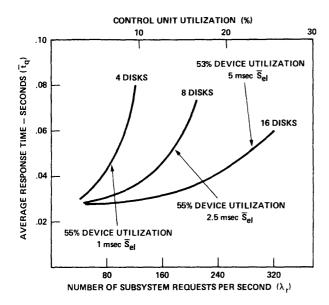

| System considerations for predicting mass storage subsystem behavior<br>E. J. McBride, A. B. Tonik and G. R. Finnin                                | 749 |

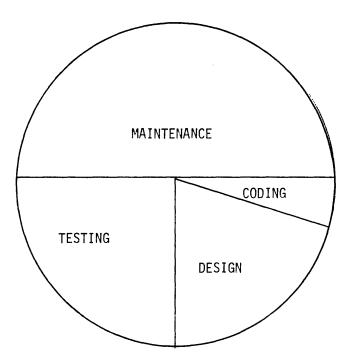

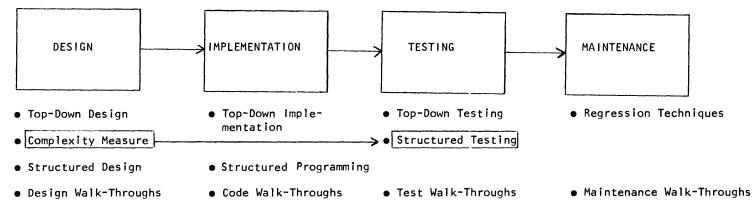

| A software reliability study using a complexity measure                                                                                            | 761 |

| A Markovian model for reliability and other performance measures of software systems                                                               | 769 |

| Partial match retrieval for non-uniform query distributions<br>V. S. Alagar and C. Soochan                                                         | 775 |

| NETWORKING                                                                                                                                         |     |

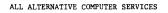

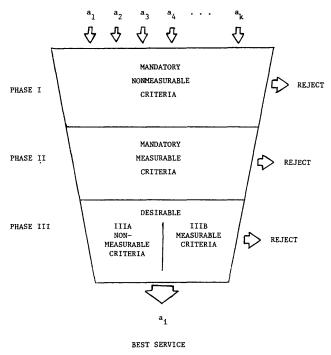

| Comparing interactive computer services—Theoretical, technical and economic feasibility<br>S. A. Mamrak and P. D. Amer                             | 781 |

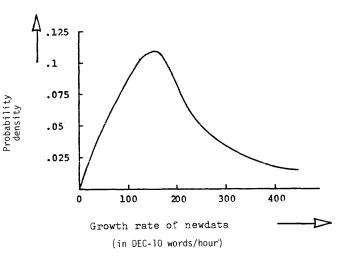

| Characterizing a workload for the comparison of interactive services                                                                               | 789 |

| Control of computing funds and resources in a networking environment<br>Beverly O'Neal and Ronald Segal                                            | 797 |

| The economic impact of network affiliation upon institutions of higher learning                                                                    | 805 |

| Approaches to concurrency control in distributed data base systems                                                                                 | 813 |

| Access control mechanisms for a network operating system                                                                                           | 821 |

| Public key vs. conventional key encryption<br>Charles S. Kline and Gerald J. Popek                                                                 | 831 |

| SIGMA—An interactive message service for the Military Message Experiment<br>Robert Stotz, Ronald Tugender, David Wilczynski and Donald Oestreicher | 839 |

| The SIGMA experience—A study in the evolutionary design of a large software system<br>David Wilczynski, Ronald Tugender and Donald Oestreicher     | 847 |

| The terminal for the Military Message Experiment<br>Robert Stotz, Paul Raveling and Jeff Rothenberg                                                | 855 |

| On-line tutorials and documentation for the SIGMA message service                                                                                               | 863  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Maintaining order and consistency in multi-access data                                                                                                          | 869  |

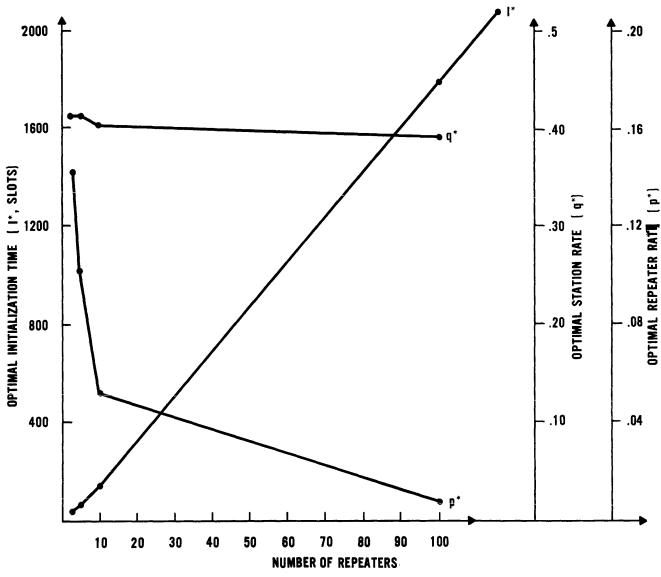

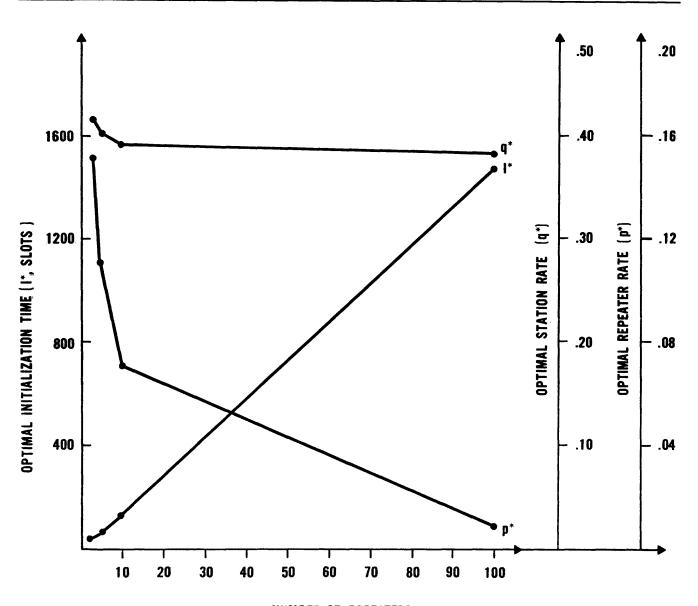

| Exact solution for the initialization time of packet radio networks with two station buffers                                                                    | 875  |

| Fixing timeout intervals for lost packet detection in computer communication networks                                                                           | 887  |

| Comparison of some end-to-end flow control policies in a packet-switching network                                                                               | 893  |

| Alternatives for providing highly reliable access to X.25 networks<br>Richard J. Chung and A. M. Rybczynski                                                     | 905  |

| A fail-safe distributed local network for data communication<br>Jane W. S. Liu, Izumi Suwa, Robert Stepp, Sergio M. Hinojosa and Tsutoma Utsuqi                 | 917  |

| An analysis of a distributed switching network with integrated voice and data in support of command and control<br>Daniel Schutzer                              | 927  |

| The exploratory system control model multi-loop network                                                                                                         | 935  |

| SOFTWARE TECHNIQUES                                                                                                                                             |      |

| Software reliability measures applied to systems engineering<br>John D. Musa                                                                                    | 941  |

| Verification procedures supporting software systems development                                                                                                 | 947  |

| A language for distributed processing<br>Ronald J. Price                                                                                                        | 957  |

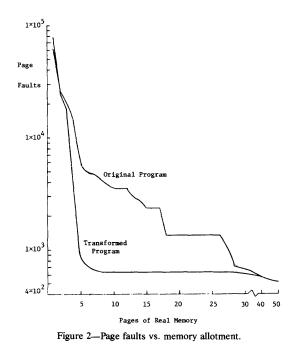

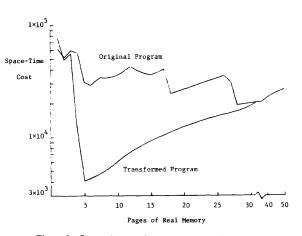

| Automatic program transformations for virtual memory computers<br>W. Abu-Sufah, D. Kuck and D. Lawrie                                                           | 969  |

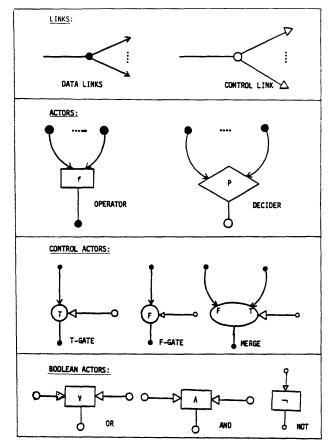

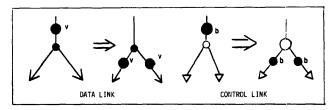

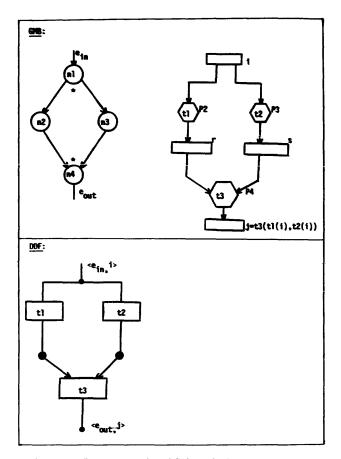

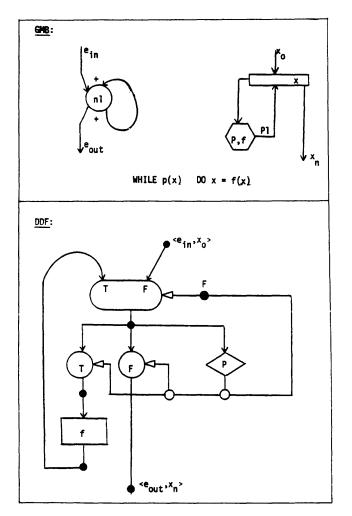

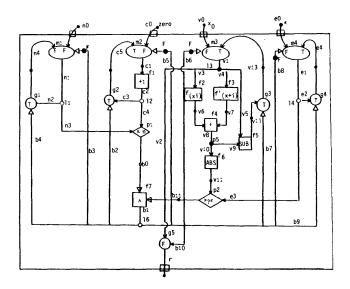

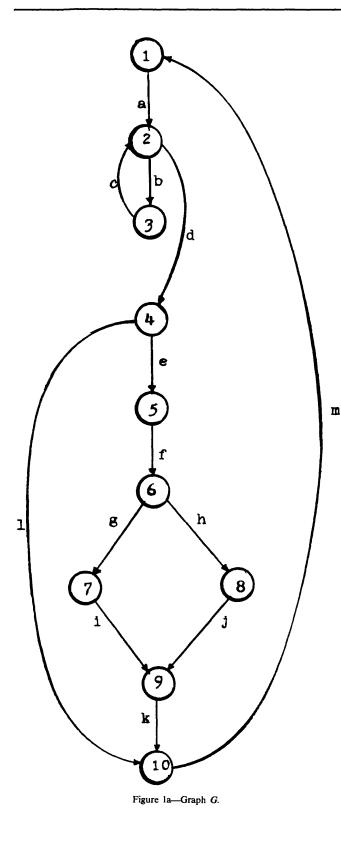

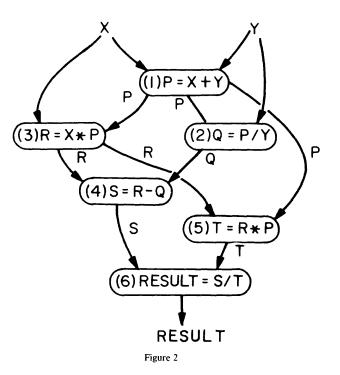

| Analysis of data flow models using the SARA graph model of behavior                                                                                             | 975  |

| Software metrics for aiding program development and debugging<br>N. F. Schneidewind                                                                             | 989  |

| A measure of software complexity<br>Ned Chapin                                                                                                                  | 995  |

| Relating computer program maintainability to software measures<br>A. R. Feuer and E. B. Fowlkes                                                                 | 1003 |

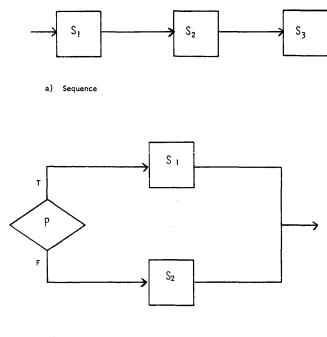

| Program forms and program form analysers for high-level structured design<br>Jayashree Ramanathan and Meera Blattner                                            | 1013 |

| First-year results from a research program on human factors in software engineering<br>Sylvia B. Sheppard, Bill Curtis, Phil Milliman, M. A. Borst and Tom Love | 1021 |

| The use and abuse of a software engineering system<br>D. J. Pearson                                                                                             | 1029 |

| The integrated control/distributed power software development shop                                                                                              | 1037 |

| On the fate of software enhancements                                                                                                                            | 1043 |

| Experiences in building and using compiler validation systems                      | 1051 |

|------------------------------------------------------------------------------------|------|

| rau olivei                                                                         |      |

| Automatic program synthesis via synthesis of loop-free segments                    | 1059 |

| Semantic similarity analysis—A computer-based study of meaning in noun phrases     | 1063 |

| Heuristic control of design-directed program transformations<br>Christina L. Jette | 1071 |

| A data flow evaluation system based on the concept of recursive locality           | 1079 |

| Data flow languages<br>William B. Ackerman                                         | 1087 |

### Computer technology in the movie industry

by SUZANNE LANDA The Rand Corporation Santa Monica, California

#### INTRODUCTION

The movie industry uniquely provides the opportunity to combine the creativity of the artist with the technology of science. It was in fact the marriage of art and science that gave birth to filmmaking. While many advances and discoveries have been made in the tools used to make movies, support their production and distribution, and enhance their exhibition, perhaps none since the camera will have the pervasive effect of the computer. Both behind the scenes and on the screen the ubiquitous computer is beginning to have an impact on the movie industry.

This paper follows a movie from its initial conception through production, distribution, exhibition, preservation and redistribution, surveying current and planned applications of computer technology and identifying areas requiring further research. It purposely focuses on the problems of motion picture production amenable to computer application and not on specific technical solutions. The latter will be provided in the session by guest speakers from the movie industry. With the emphasis on movies for this session, computer applications unique to television and other related fields have been excluded.

#### CONCEPT

A movie begins with an idea. The source of the idea may be an individual's fantasy, an article or book, a newspaper story, or even the preferences of thousands of people compiled and analyzed by computer. Sunn Classics Productions, Inc. has successfully applied the latter approach to come up with the idea for "The Lincoln Conspiracy," "In Search of Noah's Ark," and other box office successes.<sup>1</sup> Their extensive computer analysis approach, which involves not only idea but also story generation, has only been applied to movie making for special audiences (family entertainment). Successful application for general audiences has not yet been ascertained.

However, once an idea exists, studios do use market research and computer analysis to estimate its potential for success. For example, after producing several successful disaster films, Twentieth-Century Fox relied on market research to indicate when audiences had reached a saturation point for that genre.<sup>2</sup> Market research with computer analysis for this type of general information is expected to increase.

A movie idea is given life by the writer who turns it into a screenplay. Script writing remains primarily an individual art form centered around the typewriter with occasional forays to the library or other information sources. While the task of typing dialogue lends itself to automated text editing, the author is aware of only one screenwriter who has invested in such a system. Within several years, as the costs of personal computer systems (particularly peripherals) drop, repair support increases, and computerized library and periodical services become more accessible over communications networks, the personal computer will undoubtedly become a valuable aid in screenwriting.

Starting with the purchase of a script and continuing through the distribution and exhibition of a movie, payment to employees is accomplished through a payroll system more complex than any in other industries. The continually changing rules and regulations of over 65 unions and guilds must be handled. Many workers must be paid within 24 hours of the time labor was terminated. If a worker's job is upgraded during the day, his pay for the entire day may have to be adjusted and also the payments to those who worked with him. Depending on when, what, and where he is working, he may earn up to eight times his regular pay. Each union's definition of a work week also varies. Not only must union regulations be tracked, but also the tax structure of every state since the studio must provide a W2 form for every state in which an employee has worked. Another factor contributing to the complexity of the payroll system is that the size of the work force is constantly changing. While a studio may employ 3500-7000 people permanently, total annual employment may easily exceed 50,000 with the total number of checks issued ten times greater. Predominately COBOL written, batch-oriented systems provide payroll support for producers. These services are available from the major studios, e.g. Universal and Warner Bros., and from service bureaus.

In addition to payroll, contracts are issued and modified during all stages of production. This task is handled in Disney's and Fox's legal departments through the use of word processing systems. Interconnectivity of these systems with other departments and those of external concerns, e.g. law firms, has been limited to homogenous systems because of problems with nonstandard communication protocols.

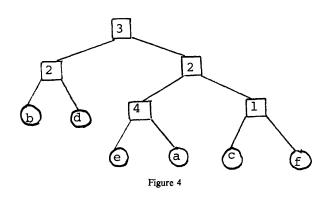

#### PRE-PRODUCTION

Once a shooting script has been prepared, the pre-production activities of budget and schedule planning commence. These tasks are compounded by the problem that scripts are not shot chronologically. A shooting schedule depends on the availability of actors, sound stages, locations, props, etc. It also depends on economics. For example, since an actor filmed on Monday and Friday must be paid for the entire week, economics dictate that his scenes be shot at closer intervals. Outdoor scenes are usually filmed before interiors because uncontrollable environmental factors reflected in outdoor scenes may impact the indoor scenes. In addition to schedule planning, scene requirements for sets, props, technical equipment, etc. must be estimated before a budget can be set. It is not unusual for a feature film budget to consist of many thousands of separate items. Both scheduling and budgeting are basically manual processes today with some automated support through data entry systems using formatted displays. However, at the University of New South Wales, an interactive system is being designed for film budgeting, the generation of an economic shooting schedule and the breakdown of individual scene requirements. During the pre-production phase of scheduling and costing, the system will accept as data the script breakdown and all relevant costs. Output will be an initial draft schedule and a total cost estimate. When cast, locations, and budgets have been determined, a detailed shooting schedule is then generated through a tree search. Such an approach does not produce the optimum schedule, but experience with other industrial scheduling situations have indicated to the developers that schedules at least as good as those generated by experienced people could be expected.<sup>3</sup> While production people have shown interest in this type of total system approach, computer aided budgeting and scheduling will probably expand first through subtask application.

One of the requirements determined for each scene is the number and types of extras. The casting of extras presents a particularly formidable problem. At Universal, for example, between 50 and 2000 extras are required daily to appear as background and atmosphere people in productions. Requests are usually very specific: five men with black beards between 20-30 years old, 5'10"-6'2", who can ride horses and duel with swords. It is even better if they own their own horses and swords. Universal uses an interactive system which accesses a data base containing the names of available extras and information about their skills, attributes, costumes, props, etc. When the next day's casting requirements are released, potential extras who best fit the part can be selected online. A similar system for creative talent, i.e. producers, writers, directors, and actors, will be available at Universal in 1979. A producer may then ask to see, for example, a list of directors who specialize in feature westerns and whose credits have grossed over \$30,000,000.

Once the budget and schedule have been determined and actors, locations, equipment, and crews selected, the director, art director and cameraman must design the sets. Sets are usually overbuilt because they are designed for all contingencies. For example, only two-thirds of a \$3,000,000 set may appear in the final print. In this case, \$1,000,000 was spent on a set that will never be seen by the audience. To avoid this waste, those at Robert Abel & Associates involved in full-scale spaceship set designs for the movie "Star Trek" (to be released December, 1979) are using computer graphic aids to determine the parts of each set which must be built. Line drawn versions of sets and people are entered into an Evans & Sutherland Picture System 2 through a tablet. For each set, camera angles and moves are executed using the System 2 controls. In this way, those portions of a set that need not be built because they will never be visible can be determined. It is also possible to identify areas of a set that may be visible but are amenable to matte effect in place of construction.

For movies which include animation or special effects sequences, storyboards outlining the action are developed during pre-production. At Universal's new special effects facility (Universal Hartland), a computer graphics system on a stand-alone microcomputer is being used to create the storyboard for "Buck Rogers." Since storyboards only include sketches of key actions, during the actual filming it may be discovered that the pacing required to move from one sketch to the next varies from that planned. To avoid this problem in the making of "Star Trek," Robert Abel's is using the Evans & Sutherland to preview action sequences in real-time before filming begins.

#### PRODUCTION

The actual shooting of a movie may occur at the studio, on location, or a combination of both. Through computer support, producers at the major studios get daily reports on the previous day's expenditures for a particular feature. Overruns are immediately visible so that modifications can be made in the remaining stages of production to absorb or minimize the extra costs. In some cases, early cost excesses result in a project's termination.

Location shooting presents severe cost control and payroll problems. At Paramount, timely and accurate cost information and local payroll capabilities are provided on location by a minicomputer-driven terminal system. Universal is currently implementing a similar minicomputer-based system. At Disney, a microcomputer system with dual-diskettes and printer will be tested on location in Hawaii in early 1979. Disney also expects to use the system on stage at the studio for backlot production sequences. These reporting systems are used during the day on location to record transactions. At night the daily records are transmitted to the central processor. Reports, updated master files, and data discrepancies are then returned to the location for next-day availability. The decrease in reporting time through use of onlocation computer support is as much as ten to one. A capability to be added in the future will allow the location auditor to explore the costs of various courses of action when an unforeseen event occurs. For example, should a storm break, with an expected duration of two weeks, the location auditor would like to determine the costs of keeping

everyone on location versus sending them home, paying required penalties and bringing them back later.

Computer technology is also used during production to assist in the generation of the animated images seen on the screen. Animation techniques can be divided into two categories: 2-D animation, involving the use of hand-drawn images, and 3-D animation, involving the manipulation of models and puppets. Both techniques make use of storyboards which are subject to computer application as described under *Pre-Production*. 3-D animation using models will be discussed under *Post-Production*, as it is traditionally associated with the post-production area of special effects.

For 2-D animation, like those of Disney and Hanna Barbera, the first production step requires an artist's rendition of key frames in each scene. The next step calls for an assistant animator or "inbetweener" to fill in the action by providing transition frames between the key frames. Each of these drawings is then photographed, shot onto celluloid, and painted. Finally, each cel or the required combination of cels is placed on an animation stand for filming. For feature films, the only step involving a computer today is the last: Camera settings required to simulate movement are computed and provided to the cameraman filming off the animation stand. However, by mid-1979, several research efforts will have systems commercially available to aid in all these steps of animated feature film production. The systems allow for input of key frames by an artist using a light pen and tablet with the computer performing inbetweening. The artist then "paints" the stored frames interactively with light pen and color selectors. To obtain consistency in scene and character colorization, the systems will allow for the storing and retrieving of colors by picture elements. The need for celluloids is eliminated since frames will be filmed directly off a CRT.<sup>4</sup> A major difficulty in providing computer aids to the animator has been to provide him with input tools with which he feels as artistically free as with conventional methods. The designers of these systems feel they have overcome the problem by providing paintbrush, pencil, and spraygun options to the artist through software. The other area still open to question for commercial application is whether these systems will produce the high-quality, high-resolution animation required for feature films. An answer to this should be forthcoming in 1979 when at least one production company plans to make a full-length animated movie using this type of computer system.

The use of computers to aid live-action filming premieres this year with the release of "The China Syndrome" (Michael Douglas Productions). For story realism and for legal protection, it was necessary in this movie to duplicate precisely the interior of a nuclear power plant during the various stages of an alert. This required the operation of 131 circuits controlling 2500 instrument panel lights in differing sequences and in differing states (off, slow-flash, fast-flash, solid-on) for each stage of the alert, synchronized with liveaction performances. The task was compounded by the need to restart the sequences at any point for retakes and for daily continuity. A combination of manual and electronic methods to handle this type of operation has proved in the past to be costly and unpredictable. To avoid these problems for "The China Syndrome," Eyewitness, Ltd. programmed a microcomputer in assembly language to allow accurate, flexible, and reliable operation of the panel lights in coordination with the actors' performances.

Computers, of course, have been known to appear or even star in a movie. Usually, however, what is seen are whirling tape drives and a card sorter or maybe a terminal flashing Christmas tree lights. Universal has taken steps to remedy the situation by creating realistic computer environments and systems for production shots. For example, simulated interactive hospital and law enforcement systems are available for use as dictated by a script.

A print of the original camera footage must be made each day for viewing the following day. The automation used to print dailies is part of the systems used for post-production processing in film laboratories which is discussed in the next section.

#### **POST-PRODUCTION**

The post-production phase of movie making consists of creating and adding special visual effects and titles, adding music and sound effects, and, finally, processing, editing, and printing the finished product in the motion picture laboratory.

Special visual effects using models have become well known through such movies as "2001: A Space Odyssey" and "Star Wars." Contrary to popular opinion and some press reports, special-purpose, hard-wired machines, not computers, were used to control cameras and models in these and other recent movies. Not until 1979 with the release of "Buck Rogers" (Universal), "The Black Hole" (Disney), and "Star Trek" (Paramount) will the public view special effects created with the aid of computer-controlled cameras and models.<sup>5-7</sup> Computer-control is a solution to the problem of repeatability of camera movements for long, intricate shots and movements of the model or objects being photographed. In addition, the automated camera is expected to make some effects possible which were not either physically possible or economically feasible before. Input to the microcomputer-based system may be from a walkthrough with the camera or from stored data previously entered via keyboard. At Disney, a cameraman will either manually or electronically operate the camera through the initial shot using a hand-held or small console control unit. Subsequent shots will be repeated automatically from the stored data. At Universal Hartland, designers are using their stand-alone microcomputer system to graphically plan the shots within a scene, calling up stored images of the models, setting model size, roll, pitch, and yaw and grid location together with lens size. At Robert Abel's, with the Evans & Sutherland system, the process is carried one step further: The shots may be played beforehand in real time. For both these systems, the stored data is used to control the microcomputer-driven camera system.

An alternative approach to 3-D animation is computergenerated imagery which eliminates the need to build and manipulate models. This approach was used for a 40-second sequence in the movie "Futureworld" in which a mask-like image of Peter Fonda's head is seen spinning through space.<sup>8</sup> While 3-D graphics have been successfully employed in television commercials, the level of complexity and detail required for high-quality, high-resolution feature films currently limits its cost-effective application.

In addition to images, a movie almost always has a musical score and special sound effects. While computer-generated music has not yet been used in a theatrical release, proponents feel that the computer will enable the musician to create scores not otherwise obtainable and that these, like computer synthesized images, will expand the medium of filmmaking. For the time being, however, musical scores for movies are still totally created by composers and arrangers. The use of original music always introduces the possibility of copyright infringement. To minimize the problem at Universal, new scores are translated by an operator into codes which are matched against a stored database of copyright music. Matches exceeding the legally acceptable number of bars are flagged.

Sound editing, like film editing, is a particularly tedious, time-consuming and therefore costly task. The sound editor views a reel of film, noting the sounds and footage required. From a library index, he selects a tentative list of sounds. A technician retrieves the sounds and transfers them to tape. The editor then begins the cutting and modifying process. If the sound he needs is too short he must create a physical loop of the tape so the sound repeats without obvious repetitious characteristics. Synchronizing the sound to the film is literally a cut-and-try process. The assembled edited cuts are mixed down onto a final track and then mixed with music and dialogue. Sound quality is degraded with each transfer from library master to work copy to final mix. The Automated Computer Controlled Editing Sound System (ACCESS) developed by Mini-Micro Systems, Inc. for Neiman-Tillar Associates eliminates manual handling of tape and allows electronic synchronization. It provides immediate availability of sound effects which have been digitized and stored on magnetic disk packs. Sounds may also be modified via computer-assisted controls. While cutting editing time by 80 percent, use of ACCESS has also improved the quality of sound produced. The microcomputer-based system was used for the sound editing of "I Want To Hold Your Hand," "Sorcerer," "The Island of Dr. Moreau" and other feature films.9

Final print production involves cutting the original negative, adding special optical effects, and performing color correction. Computers probably first entered the motion picture production cycle in the film processing laboratories which perform these functions. Academy Awards for contributions to movie making that involved the use of computers were first earned by these labs. In 1972 DeLuxe General, Inc. received a Class III (Technical Achievement) Academy Award for a computer system that performs color positive process analysis. Using photographic test results and considering interlayer effects, the system compares sample densities to the laboratory reference densities. In the same year. Consolidated Film Industries received a Class II (Science and Engineering) Academy Award for the development of an on-line computerized light valve monitor system.<sup>10</sup> While these systems used minicomputers, MGM Labs has recently implemented a microcomputer system to operate the optical printers and control the firing of the light valves.<sup>11</sup>

Also at MGM Labs, a system is under development to automatically track and retrieve the myriad of film pieces with which the negative cutter must work. Many hours are spent searching through thousands of feet of film for just the right spot to cut and splice together other cut pieces in building up scenes. Each piece must be carefully labelled and stored for possible later use. A major cost in this operation is the time it takes to search and keep track of all the heads and tails for possible later trimming. The new system will use codes on film to allow automated tracking and retrieval of film segments.

#### DISTRIBUTION

Long before prints become available, an analysis of where and when to release the film is conducted and advertising campaigns are organized. Computer analysis of revenue and advertising expenditures for previous, similar films by geographical area is used by several studios to help formulate the distribution and advertising plans for new films. Revenue reporting on distributed prints is supported at most studios by online systems. A more comprehensive approach has been taken by Buena Vista Distributors in implementing a microcomputer-based system to automate the following functions: bidding, print control, booking, grosses, box office reports, cash reporting, advertising, and messages. Near the release date of a film, standard letters with specific film details will be produced by the central computer and communicated to the branches for issuance to local exhibitors. Bids received will be entered into the system at the branch offices, and prints assigned based on availability. Previously, branch offices have been limited to the print inventory initially assigned to them. With the automated system, the nearest available print may be located. Revenue reports will be entered daily, providing timely information needed to direct exhibition and advertising. An electronic bulletin board and memo system will aid communication among branch offices and the studio.

#### **EXHIBITION**

While theatres make use of data processing for normal business applications, computer technology is not yet used for the actual control of movie theatre operations and equipment. Rather, lights, drapes and projectors operate electronically. Within a year, however, manufacturers like RCA expect to incorporate microprocessors into their advanced projector systems. Eventually we may see computer technology used to provide operational and environmental control in movie theatres as in other buildings and businesses. But even beyond the common applications, the decreasing cost and increasing capability of computers may enable movie theatres to create total visual and audio environments similar to those available today at special-purpose theatres such as the Space Theatre in San Diego. At this theatre, over 60 pieces of equipment are operated and controlled by microcomputer to create special effects for up to five different shows daily. As a first step towards the expanded theatre concept, but not yet using computer control, Universal is installing special equipment to produce lightning, thunder, and other natural sounds and effects in theatres which will be showing "Weather Wars."<sup>5</sup>

#### PRESERVATION AND RESTORATION

Eventually (or sometimes very soon) a movie is removed from distribution and stored in a film library. Since film degenerates, there is interest in storing movies digitally to preserve them until actively destroyed. To store a 90-minute, high-quality, color film digitally would require tens of trillions of bits of storage. Data compression techniques exist that might reduce this amount 20-30%, but the storage requirement still remains excessively large for today's technology. At the current rate of advancement, digital storage of films may be feasible within five years.

A film may become damaged during any of the steps described, including storage. Methods of restoration are currently being explored and there is interest in using the computer to analyze previous and successive good frames in order to reconstruct the in-between damaged frames. Similarly, the analysis of good areas within a frame may be used to reconstruct damaged or missing parts. However, computer-aided film restoration must await the availability of digital storage of films or other methods for handling the high-resolution requirement.

Computer-aided restoration has been successfully applied to films transferred to tape. For example, "Gone With the Wind" was reconstructed on videotape from a 1956 Technicolor dye transfer print by Image Transform, Inc. The minicomputer-based system resolved outlines, restored color intensities, and reduced noise.<sup>12</sup>

#### REDISTRIBUTION

A film never dies—it is just recycled to foreign markets and television. The recycling process takes the film back to the post-production process where the original parts are reedited to meet television and foreign time, censorship and film size requirements. Residuals must be paid to writers, actors, etc. whenever a film is recycled and this is handled automatically at most studios. Once a film enters the realm of television, another story of automation begins which is beyond the scope of this paper.

#### SUMMARY

This survey, while not exhaustive, does identify the major areas of current computer usage and the key areas for future applications in the movie industry. Until recently, computer applications primarily focused on:

- 1. Batch-oriented accounting support for payroll, costing, residuals, and statistical support for market research;

- 2. Minicomputer systems for process control;

- 3. Very limited application of computer graphics for special effects.

Current and planned applications include, in addition:

- Broader computer use for market research and corporate information systems;

- 2. Word processing support for script preparation and contracts;

- 3. Interactive system support for budgeting and scheduling subtasks, for resource information retrieval, for sound editing, and for film processing;

- 4. Computer graphic aids for set design, storyboarding, and animation with increased use for special effects;

- 5. Expanded use of on-location reporting systems;

- 6. Functional expansion of automated distribution systems to include print control, bidding and booking, and electronic mail;

- Computer control of cameras, projectors, and lab processing equipment;

- Computer control of set elements for live action filming.

In fact, in 1979 several movies will be released whose creation will have involved the first uses of computers in camera-control, set design, storyboarding, animation, and live action filming.

The one development most responsible for the current growth in computer applications in the movie industry is the microcomputer. For business data processing, it is appearing on stage, on location, and in distribution offices. As part of text editing systems, the microcomputer is now in legal departments and will soon enter the script preparation stage. For equipment control, microcomputers are being used in film processing labs, to operate special effects cameras, and will be used in the near future in projectors. As an aid in scene design, stand-alone microcomputer-based graphics systems are now in use. For live-action filming, microcomputers are controlling parts of sets in synchronization with live performances. The high processing power required to generate images by computer may soon be provided through arrays of microprocessors.

Automated techniques for film editing, storage, and restoration still require further research and development in mass storage and image processing.

In any discussion of computer technology and movie making, the question arises as to the possibility that someday movies will be made without actors or cameras but rather totally by computer. The answer is, I think, an undeniable "yes," but whether movies produced by computer will be competitive in cost and quality to those produced by the traditional process with computer aids remains highly questionable.

#### CREDITS

As with a movie, this paper is the result of contributions by many people. In particular, the following individuals are acknowledged for their valuable inputs: William Eberly, Walt Disney Productions; Al Jerumanis and Paul McManus, MCA Inc.; Charles C. Tucker, Twentieth-Century Fox; Harold Steintrager, Warner Bros., Inc.; Bob Johnson, Hanna Barbera; Jerry Jeffress and Colin Cantwell, Universal Hartland; Don Miskowich, Robert Abel & Associates; Richard Hollander, Eyewitness, Ltd.; William Dietrich, Mini-Micro Systems, Inc.; Michael Chewey, MGM Labs; Mike Scully, IBM; Toni Shetler, Xerox; and Gary Martins and David Leinweber, The Rand Corporation.

#### REFERENCES

à

- Simpson, Janice, "Studio Cleans Up By Marketing Films, Like Selling Soap," Wall Street Journal, June 6, 1978, pp. 1+.

- 2. Kinney, Harrison, "BOFFO: That's Hollywood for big at the box office. And now it's the computer that's boffo in movieland," *Think*. May/June 1977, pp. 4-9.

- McMahon, Graham, "Report on Film Scheduling and Costing by Computer," unpublished, May, 1977. For information, write Dr. McMahon, Computer Science Dept., The University of New South Wales, P.O. Box 1, Kensington, New South Wales, Australia, 2033.

- Crow, Franklin, "Shaded Computer Graphics in the Entertainment Industry," Computer, March 1978, pp. 12-22.

- 5. Barron, Frank, "Universal Building Hartland as Special Effects Shop-Supreme," *The Hollywood Reporter*, October 30, 1978, pp. 1+.

- 6. "New Camera Designed for Walt Disney Pic," Variety, Nov. 17, 1978.

- 7. Purvis, John, "Levi's to Star Trek: Special Effects Star at Robert Abel & Associates," *Millimeter*, September, 1978, pp. 38+.

- Sutherland, Don, "How 'Futureworld' Movie Technicians Use A Computer To Recreate 'Life' On Film," *Popular Photography*, December 1976, pp. 106+.

- 9. Deitrick, William R., "Automated Computer Controlled Editing Sound System," to be published in the *Journal of the Society of Motion Picture* and Television Engineers, 1979.

- Solow, Sidney, "The History of the Motion-Picture Film Laboratory," Journal of the Society for Motion Picture and Television Engineers, July 1976, p. 513.

- 11. Chewey, Michael, Walter Eggers and Allen Hecht, "Controlling Optical Printers by Microprocessor," to be published in the *Journal of the Society* for Motion Picture and Television Engineers, 1979.

- Kuttna, Mari, "Computers Behind the Screen," Sight and Sound, Spring 1977, p. 85.

## The System Architecture Evaluation Facility—An emulation facility at Rome Air Development Center

by N. BRUCE CLARK and MICHAEL A. TROUTMAN Rome Air Development Center Griffiss AFB, New York

#### INTRODUCTION

Military requirements for data processing systems with unusual characteristics to perform specialized jobs have led to research into advanced architectures by the Department of Defense (DoD). Some of the requirements for systems have no counterpart in the civilian industry. Command, control and communications systems are typically complex and must be reliable and available with a high degree of certainty. This places great stress on the development of new data processing systems. The architecture, as the bedrock of all systems, must be continually improved in order to accomplish the increasingly complex software functions now demanded. Spaceborne automated systems simply cannot have an onboard team of vendor maintenance engineers to diagnose problems and replace components; a fault tolerant architecture is needed. Advanced radar surveillance systems provide a tremendous potential for information gathering but must be supported by parallel architectures which are still in the research phase. The DoD is actively involved in research and development of advanced architectures for tomorrow's data processing needs and the System Architecture Evaluation Facility (SAEF) is an example of the use of microprogrammable (and other special purpose) computers to reduce the cost and improve the efficiency of this research.

Direct experimentation with unique hardware architectures is extremely expensive and time-consuming. It is also wasteful of resources, as the prototypes are rarely usable systems and must be discarded. Rather than actually build hardware components, they can be emulated by microprogrammable computers. Emulation is similar to a simulation of hardware, but with an important difference. Software simulation of hardware has existed for years, but traditionally has been limited in its use because of the time versus detail tradeoff. If the architecture is modeled at a very high (or gross) level then that simulation executes very fast. As more and more detail is included down towards the register or gate level of machine design, the simulations become excruciatingly slow, running tens of thousands of times slower than the proposed design will actually execute. The development of computers which are microprogrammable allows a "simulation" to be written in a different way.

Instead of the traditional software programs, the microprograms which determine the actual control signals generated for machine language instructions are modified (or rewritten) to execute a different instruction set, the one for the "simulated" machine. In effect, the microprogrammable computer is molded to look and act like the proposed design at the instruction set (machine language) level. Thus, machine level programs written for the proposed design will execute on the microprogrammable machine.

It is an arguable position that this is still a software simulation, since microprogramming is just a lower level of programming. The difference is that the level of detail being used to describe the target machine is lower than the level it is describing. This is in contrast to using assembly language or a higher order language to simulate the instruction set of a computer. This gives a tremendous advantage in the time versus detail tradeoff, and thus this type of simulation is usually referred to by the special designation of emulation. Well written emulations of most architectures can execute within one order of magnitude of "real-time" for the proposed design. Thus a software function which takes one minute of execution time in the target machine might take 10,000 to 100,000 minutes (one to ten weeks of 24-hour days) on a detailed simulation, but only ten minutes on an emulation. Obviously these figures vary widely depending on the architecture being emulated and the computer being used to emulate, but are representative of the speed advantages gained with emulation over simulation.

#### SAEF ELEMENTS

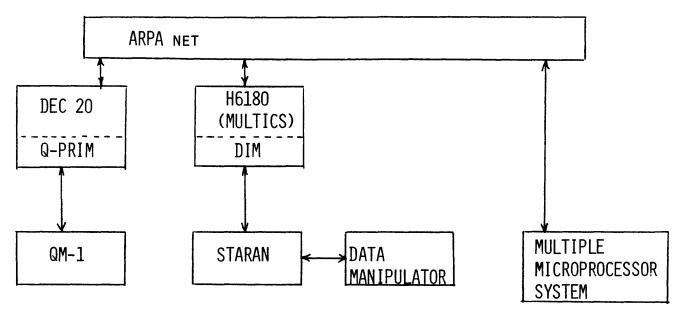

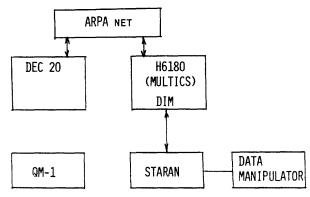

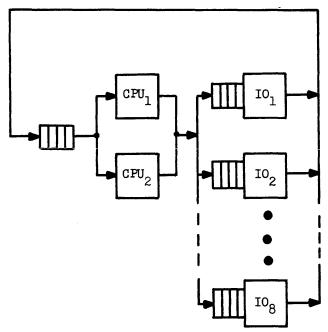

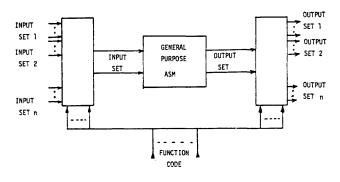

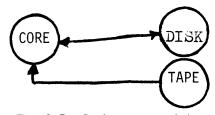

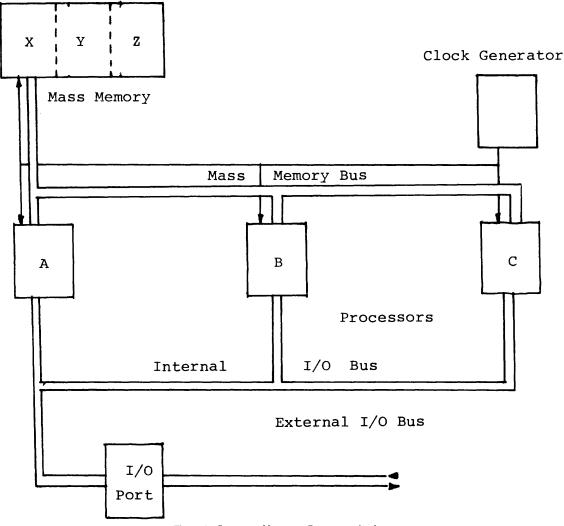

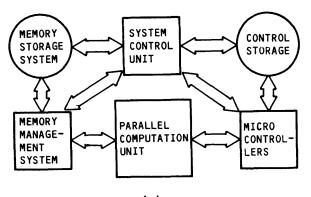

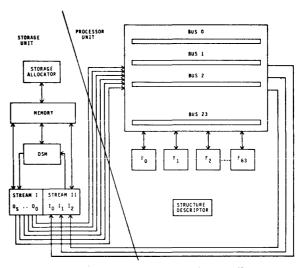

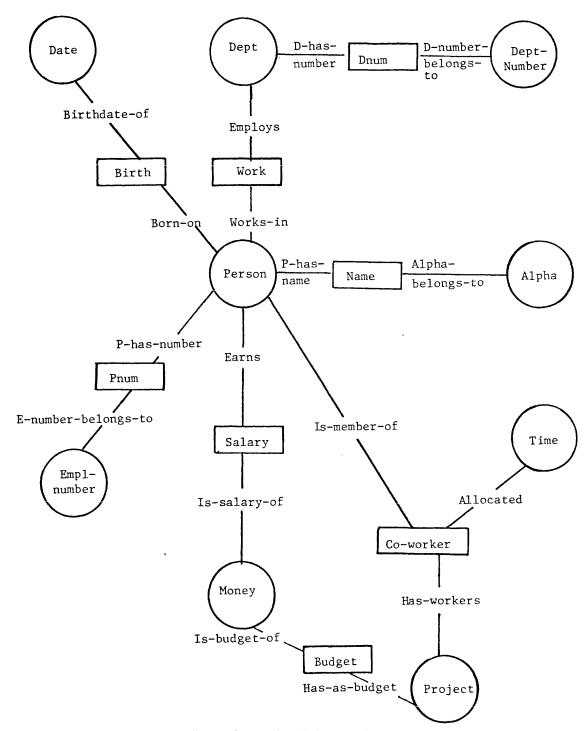

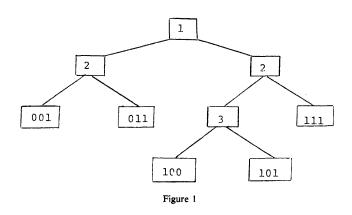

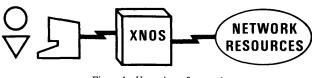

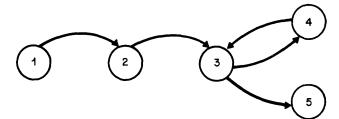

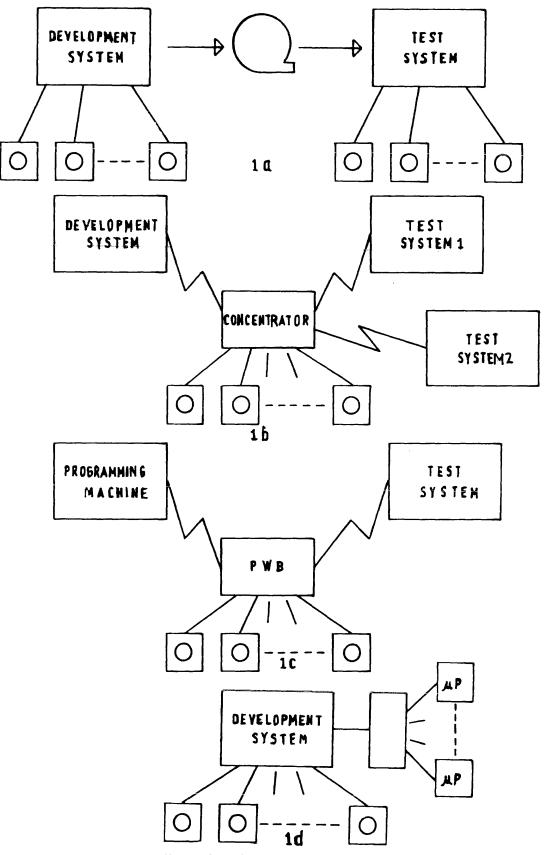

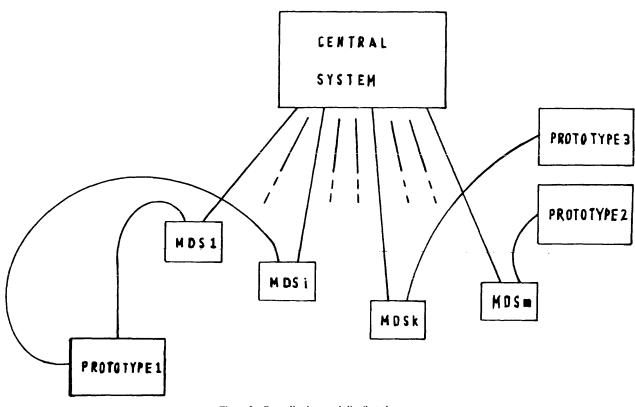

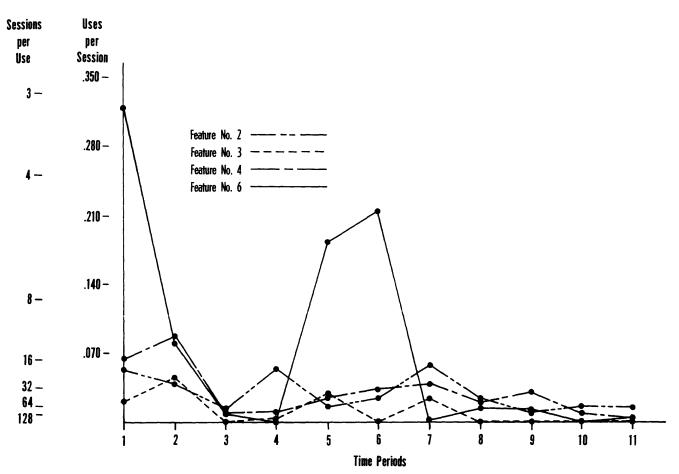

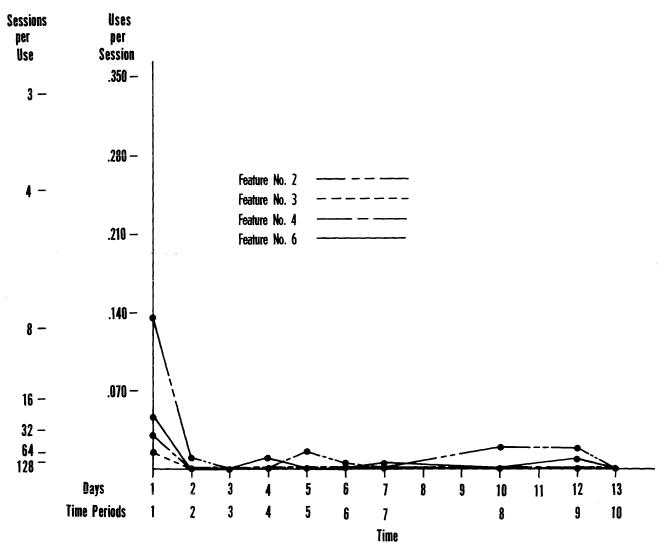

To provide the emulation capabilities described, the core of SAEF consists of two microprogrammable computers, the Nanodata QM-1 and the Multiple Microprocessor System (MMS) (Figure 1). Also included is a Goodyear Staran Associative Processor which will aid in evaluating singleinstruction stream-multiple-data stream (SIMD) architectures. A larger general purpose computer will be used for the hosting of software tools to be used in connection with SAEF. Finally, all of these elements will be connected via the ARPAnet to facilitate intercommunication.

#### SYSTEM ARCHITECTURE EVALUATION FACILITY (SAEF)

Figure 1-Projected facility.

#### QM-1

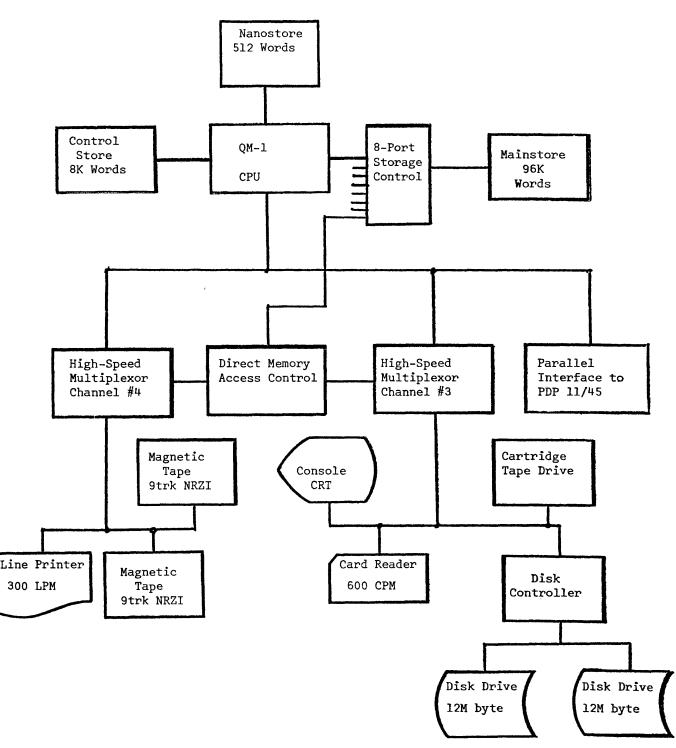

The QM-1 is a high-speed general purpose digital computer that operates under two levels of microprogram control.<sup>1</sup> These two levels provide extreme flexibility in machine definition and allow the advantages of both vertical and horizontal control. Machine instructions resident in Main Store are executed and defined by microprograms in Control Store. Control Store is a vertical level which is in turn implemented by Nanoprograms in Nanostore. The Nano level is a true horizontal architecture which has ultimate control over the total resources of the machine.

The OM-1 is primarily composed of a hierarchy of stores. At the lowest level is Nanostore consisting of 1K of 360 bit words with an access time of 75 ns. One nanoword is made up of a 72-bit K vector and four 72-bit T vectors (only one T vector is in control at any one time). Nanostore is a true read/write memory giving the programmer the ability to dynamically change its contents. Sharing control of the QM-1 with nanostore is F Store. F store consists of 32 six-bit registers which are used for residual control purposes. These registers determine the bus connections between the various units of the QM-1 as well as maintain the state of the machine. Moving away from the low level control of the QM-1, local store consists of 32 18-bit registers. The majority of these registers are general purpose but several of them have specific functions such as microinstruction registers and microprogram counters. External store is a group of 32 18bit registers which provides specific functions including I/O interfacing, special main store addressing and generation of addresses for interrupts. Control store is a 16K by 18-bit read/write memory having an access time of 75 ns. This memory can be used for data storage and target register storage in addition to the vertical microinstructions. At the next level up is main store consisting of a maximum 256K 18-bit words. This is a read/write core memory having an access time of 750 ns.

The QM-1 contains several other functional units which are not considered part of the store hierarchy. These include a full 16-function 18-bit ALU, a 36-bit double shifter/shifter extension, an Index ALU for fast indexing and logical operations on local store, an RMI unit for rotating/masking/ indexing the output of main store, and an ALU for operating on the six-bit F store.

The QM-1 is operable in both a stand-alone mode and in a time share mode connected to a DECsystem-20. In standalone, the QM-1 supports a full complement of peripherals. An operating system is available which maintains control over these devices as well as providing editor, assemblers and other useful routines. Also included are complete emulation debug and support packages which are independent of the operating system. These packages provide simple interfaces between an emulation and QM-1 resources and allow highly interactive sessions between an emulation and its user/developer. While in a stand alone mode, the QM-1 is directly usable by a single user thru the system console. When several users wish simultaneous access to the QM-1 it can be operated in a time-share mode.

In time-sharing the QM-1, it is connected to a DECsystem-20 via a common main store and the DECsystem-20 I/O bus. This system, which is known as Q-PRIM, provides an interactive microprogrammable environment in much the same way as when the QM-1 is stand-alone.<sup>2</sup> However, in this case the QM-1 is treated as an I/O device by the DEC-system-20 operating system, TOPS-20. In this mode the QM-1 will have no peripherals of its own but will rely on TOPS-

20 to provide all its I/O capabilities. This resource will also be available to remote users because of the ARPAnet connection to the DECsystem-20.

The Q-PRIM software consists of four major modules. These are the QM-1 supervisor or "microvisor," the TOPS-20 QM-1 driver, Q-PRIM Exec and Q-PRIM debugger. The QM-1 microvisor interacts directly with the user's emulation and the TOPS-20 QM-1 driver. It is a small module which communicates between the QM-1 and the DECsystem-20. The microvisor provides context switching capabilities and handles the virtual memory addressing and paging from the QM-1 side. Accessing the QM-1 from TOPS-20 processes is done through the QM-1 driver. The driver communicates with the microvisor and TOPS-20 system calls. It is responsible for initializing the microvisor, controlling, scheduling, and swapping users, accumulating accounting data, and passing along I/O requests. The Q-PRIM Exec provides an environment on the DECsystem-20 which supports each of the emulations executing on the QM-1. The Exec provides a variety of commands that allow a user to build and interact with his emulated system. The Q-PRIM debugger is a tabledriven, interactive, symbolic debugger that permits a user to debug target-machine programs in terms of symbols defined for the target machine. Data representations are controllable, thus allowing the user to tailor the emulation interface to more closely match the target machine.

#### MMS

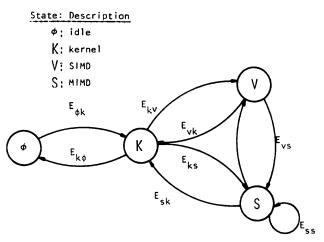

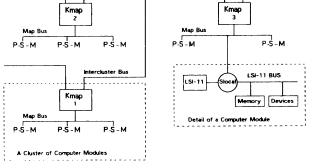

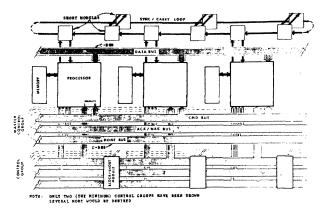

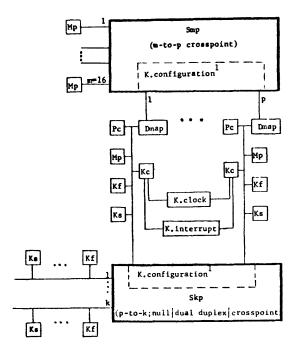

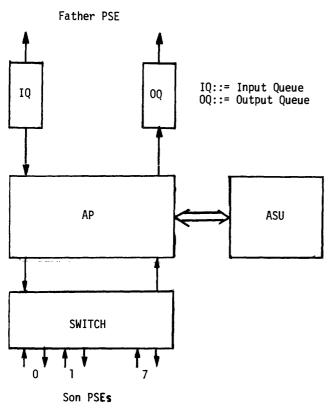

Another key component of SAEF will be the MMS which is currently in the design phase. The MMS will consist of 64 microprogrammable microprocessors each operating autonomously or connected as part of an SIMD or MIMD architecture. It will contain a highly flexible and versatile interconnection system under software control which facilitates communication between MMS processors. The MMS will be able to effectively emulate shared memory, bus oriented, and crossbar switch interconnection schemes used in distributed multiprocessor systems. Control over the MMS will be accomplished by a Facility Control Processor (FCP) which is expected to be a minicomputer. This system will be usable in both a stand alone mode with the user communicating directly with the FCP, and in a remote mode via its connection to the ARPAnet. For the purpose of this discussion the MMS can be broken down into four sections-(1) FCP, (2) Emulation Engine Support, (3) Processing Elements and (4) Memory Subsystem.

The primary function of the FCP is to maintain control over the operation of the MMS. The FCP will provide both user and ARPAnet interfaces to the MMS. It will contain a host of run time tools which will allow the loading, modification, and control of individual PEs. Other support tools will include microassemblers, assemblers, compilers and software packages for processing of performance data. In its job of control over the MMS, the FCP is aided by the emulation engine support.

Emulation engine support is broken into four areas. The Time Align Controller maintains master pseudo time for the MMS. The Emulated Local I/O Processor will create an I/O environment for each individual PE. The job of the Shared Resource Controller is to manage memory and communication paths. Last, the function of the Performance Monitor Processor is to collect all Performance Monitor System (PMS) event data from the PEs and emulation support and store this data on mass storage for processing by the FCP. Each of these four devices communicates with controllers which are distributed among the PEs.

Each of the 64 PEs in the MMS will consist of a microprogrammable microprocessor and control hardware for I/O, memory, pseudotime, and messages. The microprocessors will be composed of microstore and an RALU based on bit slice architecture. A 16-bit RALU is the most likely size, with hardware aid for more efficient emulation of smaller word size architectures. Emulation of larger machines will be done with multiple instruction cycles. The I/O and memory controllers work in unison to provide an environment with memory mapped and I/O space I/O, local memory and shared memory. The pseudotime controller coordinates with the master time align controller for keeping PEs in step and the message controller handles communication between the local I/O memory unit and the appropriate emulation support processor.

The memory subsystem is partitioned into 64 each 32K word blocks each associated with a particular processing element. Individual blocks may be subpartitioned in any manner desired between local and global memory. Arbitration for the memory is handled by a portion of the shared resource controller and a local arbitration unit. The memory was partitioned in this way so as to give each PE fast access to 32K local words. Nonlocal accesses will be slower, because they take place through a shared bus.

The MMS as described allows for very detailed system emulations. In addition to emulating the computer architecture and peripherals as usual, one also has the capability to emulate the exact protocols of interprocessor communication and memory accessing. This is made possible by the programmable nature of many of the controllers located throughout the MMS. These features also enable the efficient emulation of I/O devices and virtual memory because the microprogrammable microprocessors are not burdened with these tasks, they can actually be done in parallel by the programmable controllers.

#### STARAN

Although not an emulation machine, a Goodyear Aerospace Corporation STARAN S-1000 associative processor interfaced to the HIS 6180 Multics system is included in SAEF as an aid in evaluating SIMD architectures. The associative processor can be operated in two modes, a standalone mode and an on-line mode to the Multics time-sharing system. In the latter mode, a Multics user is able to control the STARAN from his terminal as he would if he were using the STARAN in stand-alone mode. He can create program and data files using the capabilities of Multics and transmit them to STARAN. Currently the associative processor cannot be time-shared; that is, only one user at a time may utilize the STARAN. All communications between STARAN and Multics are via a 12-bit parallel buffered I/O channel.

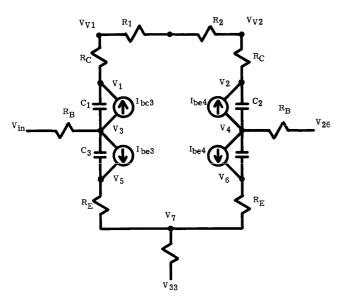

The STARAN basically consists of a conventionally addressed control memory for program store and data buffering, four associative memory arrays, a control logic unit for sequencing and decoding instructions from control memory, and a control logic unit associated with a special parallel I/O (PIO) capability.<sup>3</sup> The associative array memories are the heart of the STARAN system. The array memories provide content-addressability and parallel processing capabilities. Each array consists of 65,536 bits of multi-dimensional access (MDA) memory organized as a matrix of 256 words by 256 bits with parallel access to up to 256 bits at a time in either word (horizontal) direction, bit-slice (vertical) mode or mixed mode (combination of the two). In addition to the MDA memory, each array contains 256 bit-serial processing elements. These processing elements provide the parallel processing capabilities for each array. Processing in the STARAN system can be overlapped with some arrays performing I/O while others are executing arithmetic and logic instructions.

The sequential control portion of STARAN consists of a PDP-11/20 minicomputer with 8K of memory and associated peripherals. The sequential processor also contains logic to interface with other STARAN elements. It runs system software programs such as the assembler and macro preprocessor, operating system, file handling programs, diagnostic programs and debugging routines.

#### Data manipulator

Another element of SAEF is the Data Manipulator which provides a flexible bit manipulation capability.<sup>4</sup> The basic approach follows that described by Dr. Tse-Yun Feng of Wayne State University.<sup>5</sup> Currently the Data Manipulator is attached to STARAN and allows the programmer to establish a relationship between input and output words such that, for each of the bit positions in the output word, any bit location in the input word may be specified as its data source. In addition, both input and output data can be masked.

#### Host computers

In order to provide many of the support tools required by SAEF a larger host computer must be included. At the present we will be using the Honeywell 6180 Multics and DECsystem-20 time share systems located at RADC. These two computers will provide capabilities otherwise unattainable on the other elements of SAEF, either because of their small size or specialized nature. Hosting tools on a common computer also has the added benefit of reducing the number of operating systems the user has to learn. This is a primary concern as ease of use is the most important factor for SAEF. Because these hosts provide multiprogramming environments, several users of SAEF may be working on some aspect of a system emulation concurrently. Other obvious advantages are access to the ARPAnet and the amount of mass storage available on these computers. The host computers will communicate with the remainder of SAEF through the local ARPAnet connections.

#### **Progression of SAEF**

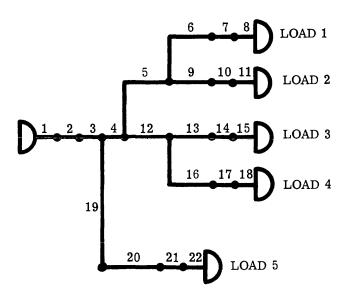

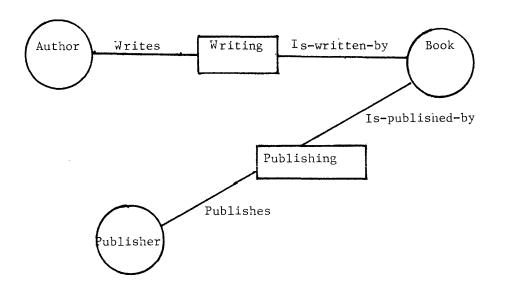

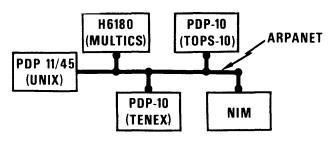

SAEF as described above will be developed over the next several years. At the present, SAEF consists of the DECsystem-20 and HIS 6180 both connected to the ARPAnet, the STARAN and Data Manipulator with their connection to Multics, and the QM-1 in a stand-alone mode (Figure 2). Multics is the primary support host with its Meta Assembler, compilers, and editors. A 1200-baud serial line exists from Multics to the QM-1 for downloading purposes. The DECsystem-20 currently supports a preliminary PRIM system utilizing a resident simulation environment instead of emulation by the QM-1. The Q-PRIM system is expected to be operational near the end of 1979. The MMS is currently in the design phase and is projected to be built by the end of 1981.

#### SUPPORT TOOLS

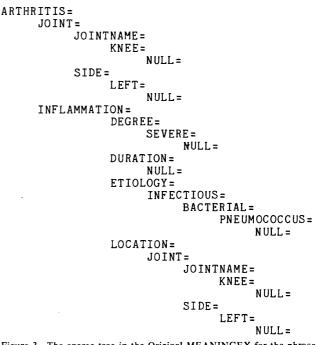

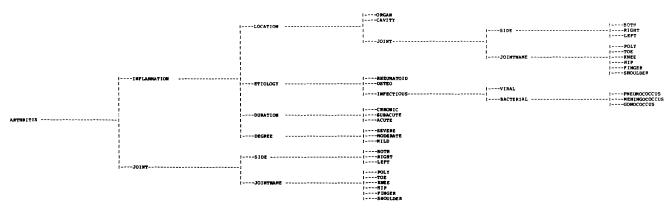

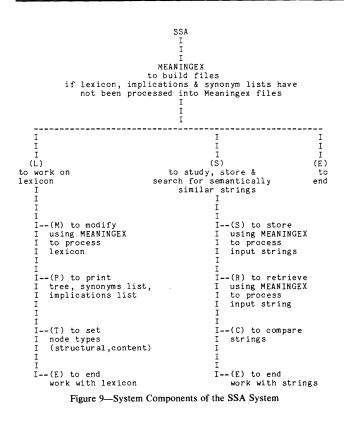

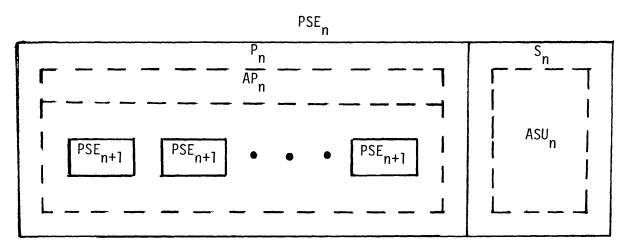

The hardware elements and software directly supplementing those elements are the core of SAEF. Several additional software support tools are in being or currently under development for use in SAEF, but are not exclusively limited to the facility and may, in fact, be most beneficial in contexts other than SAEF. Specifically, this section discusses the development of a hardware description language called SMITE for writing emulations, and study on the concepts of an automatically retargetable compiler which will accept machine descriptions written in a hardware description language like SMITE and produce an emulation of the machine.