# **AFIPS** CONFERENCE PROCEEDINGS

**1977** NATIONAL COMPUTER CONFERENCE

> June 13-16, 1977 Dallas, Texas

The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1977 National Computer Conference or the American Federation of Information Processing Societies, Inc.

> Library of Congress Catalog Card Number 55-44701 AFIPS PRESS 210 Summit Avenue Montvale, New Jersey 07645

© 1977 by the American Federation of Information Processing Societies, Inc., Montvale, New Jersey 07645. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publisher.

Printed in the United States of America

# Preface

# by PORTIA ISAACSON

Conference Chairman The University of Texas at Dallas Richardson, Texas

To chair the National Computer Conference is a rare opportunity to contribute to one's profession. I could never have passed it by. As is common with opportunities, however, this one has not been without its challenges. Those challenges have been well met by the 1977 NCC Steering Committee. The recruitment of that team of professionals has been by far my greatest contribution to the 1977 National Computer Conference. Their dedication and enthusiasm for the enormous task we faced surpassed even my expectations.

The National Computer Conference is unique in our industry—not just because it is our largest conference—but because it does not restrict itself to a narrow view of the industry; each year, it bends and reaches to point to new and different directions. One of the most important challenges of each steering committee, I believe, is to determine the directions of reach for the NCC in a particular year, while retaining the broad base of the conference.

Thus each NCC is unique, bearing the imprint of the particular group of people that brought it to fruition. The 1977 NCC is no exception. While reinforcing the NCC tradition of providing a broad technical program, the 1977 NCC has added its own innovations. Among the unique features of this conference are the program of Professional Seminars, the Programming Contest, and the Personal Computing Fair and Exposition.

A National Computer Conference is an enormous project. Without the hundreds of individual volunteers and many supporting companies, we could not have such a conference. We must especially thank our Conference Steering Committee, which is responsible for the design and much of the implementation of the conference. AFIPS Headquarters' staff has provided top-notch support, with an obviously successful exhibit sales program, innovative communications plan, and a multitude of other tasks. The NCC Board and NCC Committee have generously donated their time to provide the overall guidance necessary to make the NCC happen.

It is an especially difficult task to assemble a program of technical sessions with sufficient breadth of coverage to be worthy of a conference that calls itself the National Computer Conference. However, as difficult as it is, Dr. Robert Korfhage has been more than equal to the challenge as evidenced by these proceedings.

The National Computer Conferences have established a strong tradition of excellence. We are proud to have contributed to that tradition.

. . . . . . .

# Introduction

by ROBERT R. KORFHAGE

Program Chairman Southern Methodist University Dallas, Texas

If you are ever tempted to project ahead a quarter century or so, you should first look back an equal span of time, and observe the changes that have taken place, particularly within the world of computing, in that time. Each National Computer Conference stands at this juncture between an existing past, and an even more exciting future. Thus the Conference not only represents computing as it has come to be, but also projects an image of where we are going.

Where *are* we going? For better or worse, computing is now involved in every type of human activity. Thus we take it as the mission of the 1977 NCC Program to reflect this involvement and to point out promising directions. Gone are the "good old days" of the esoteric, highly technical major conference. In the first place, the field has expanded far too much for anyone to have a sound and deep technical knowledge of all aspects. In the second place, many highly specialized conferences now exist at which various subsets of computer practitioners can discuss the intricacies of their particular area of interest. Thus we see the National Computer Conference as presenting a broader view of computing-in a sense a "world's fair" of computing, with presentations ranging from tutorials and seminars aimed at those who have just heard of a given topic, to technical presentations that will hold the interest of those more deeply involved. We hope that you will see the conference in this way. Not everything will interest you. Select what you will-but read the papers, attend the sessions, participate, and enjoy four days of the best in computing!

Roughly half of the program this year is technical in nature, with the major topics being computer architecture and database management. This portion of the program is well represented by papers in the Proceedings. The less technical portion of the program is less heavily represented within these pages. This is due to the fact that roughly one third of this portion consists of "management briefings" presentations without formal written papers, that are aimed at present and aspiring managers in the computer field. However, within this half of the program there are also papers on management problems, on a variety of interesting applications, and on the exploding field of personal computing.

Putting together a program for this large a conference involves more than a thousand people. Most evident of course are the speakers and the session chairmen. But we tend to forget the other authors—both the coauthors who never appear "on stage," and the authors whose work we have not been able to use, despite the efforts that they have put in. Hundreds of referees devoted many hours to reading all of these papers. If, indeed, one benefits in proportion to the effort put in, then the referees will gain much from the Conference.

Finally, I would like very specially and personally to acknowledge the work done by the small core of people who have been involved in the entire program production the Program Committee, my staff in Dallas, and the AFIPS staff in Montvale. When we started this effort I told the Program Committee that they would get the credit and I would get the blame—and that's the way it is. Because of the enthusiasm and hard work of this small core, the whole production has gone very smoothly. The few difficulties that we have had are indeed traceable directly to my desk.

# **CONTENTS**

| Preface<br>Portia Isaacson                                                                                                       | iii       |

|----------------------------------------------------------------------------------------------------------------------------------|-----------|

| Introduction                                                                                                                     | v         |

| DATA BASE ADMINISTRATION                                                                                                         |           |

| Data base administration—Classical pattern, some experiences and trends<br>Jean-Paul De Blasis and Thomas H. Johnson             | 1         |

| Data dictionary—More on the impossible dream                                                                                     | 9         |

| COMPUTER SYSTEMS ARCHITECTURE                                                                                                    |           |

| Fault tree analysis of computer systems<br>C. V. Ramamoorthy, Y. W. Han and G. S. Ho                                             | 13        |

| An overview of fault tolerant digital system architecture<br>Stephen Y. H. Su and Richard J. Spillman                            | 19        |

| COMPUTER SECURITY TECHNIQUES                                                                                                     |           |

| The use of passwords for controlling access to remote computer systems and services                                              | 27        |

| A microprocessor selective encryption terminal for privacy protection<br>John H. Carson, John K. Summers and James S. Welch, Jr. | 35        |

| COMPUTER GRAPHICS                                                                                                                |           |

| MIDAS—A compositional modeling system<br>James R. Warner                                                                         | 39        |

| A system for automatic acquisition of three-dimensional data                                                                     | 49        |

| CLINICAL APPLICATIONS OF THE COMPUTER                                                                                            | 04 - 15 Y |

| Strategies for the successful introduction of computer technology in a mental health care setting—The problem                    |           |

| of change                                                                                                                        | 55        |

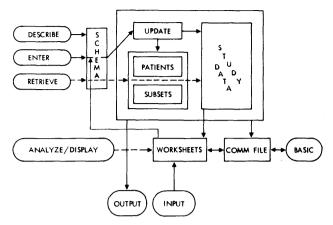

| Database management for clinical trials<br>John M. Long and Joseph R. Brashear                                                   | 59        |

| Database management for clinical research<br>W. L. Sibley, M. D. Hopwood, G. F. Groner, W. H. Josephs and N. A. Palley           | 63        |

| DATA MODELS AND THEIR APPLICATIONS                                                                                               |           |

| Why restrict the modelling capability of CODASYL data structure sets?                                                            | 69        |

| The entity-relationship model—A basis for the enterprise view of dataPeter Pin-Shan Chen                                         | 77        |

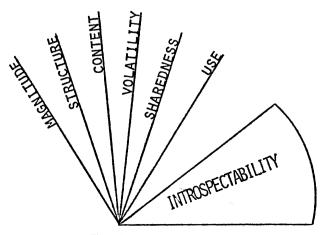

| Data architecture and data model considerations<br>Edgar H. Sibley and Larry Kerschberg                                                                                | 85  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| COMPUTER SECURITY RISK ASSESSMENT                                                                                                                                      |     |

| Security risk assessment in electronic data processing systems                                                                                                         | 97  |

| Problem areas in computer security assessment<br>Steve Glaseman, Rein Turn and R. Stockton Gaines                                                                      | 105 |

| COMPUTER-BASED INFORMATION SYSTEMS FOR THE SMALL FIRM                                                                                                                  |     |

| Computer-based information systems for the small firm—Why? cost? caveats, functional needs, contracts<br>Frederick F. Newpeck                                          | 113 |

| SELF-ORGANIZING/SELF-OPTIMIZING DATA BASES                                                                                                                             |     |

| Storage utilization in a self-organizing data base                                                                                                                     | 119 |

| Self-adaptive automatic data base design<br>Michael Hammer                                                                                                             | 123 |

| SELECTION METHODS FOR A FAMILY OF COMPUTER ARCHITECTURES                                                                                                               |     |

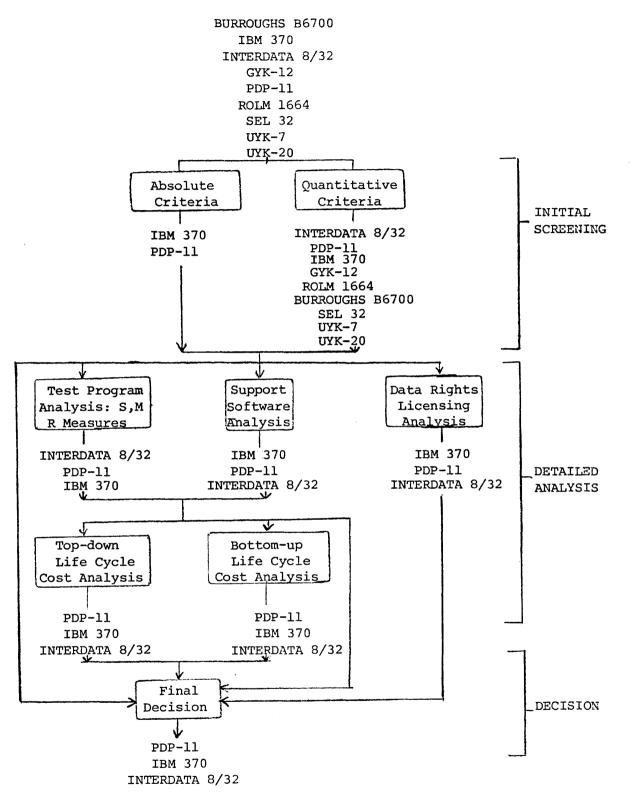

| Overview of the military computer family architecture selection<br>William E. Burr, Aaron H. Coleman and William R. Smith                                              | 131 |

| Initial selection and screening of the CFA candidate computer architectures<br>Samuel H. Fuller, Harold S. Stone and William E. Burr                                   | 139 |

| Evaluation of computer architectures via test programs<br>Samuel H. Fuller, Paul Shaman, David Lamb and William E. Burr                                                | 147 |

| An architectual research facility—ISP descriptions, simulation, data collection                                                                                        | 161 |

| Evaluation of the software bases of the candidate architectures for the military computer family<br>James Wagner, Edward Lieblein, Jorge Rodriquez and Harold S. Stone | 175 |

| Life cycle cost models for comparing computer family architectures<br>John J. Cornyn, William R. Smith, Aaron H. Coleman and William R. Svirsky                        | 185 |

| MICROPROCESSOR ARCHITECTURES                                                                                                                                           |     |

| A microprocessor architecture for digital device implementation                                                                                                        | 201 |

| A hybrid computer interface for microprocessors<br>Joseph P. Heid                                                                                                      | 207 |

| PM/II—Multiprocessor oriented byte-sliced LSI processor modules<br>Mario Tokoro, Taisuke Watanabe, Katsura Kawakami, Jun Sugano and Katsuhiko Noda                     | 217 |

| An organization for optical linkages between integrated circuits<br>G. Jack Lipovski                                                                                   | 227 |

| UNIX on a micro-processor                                                                                                                                              | 237 |

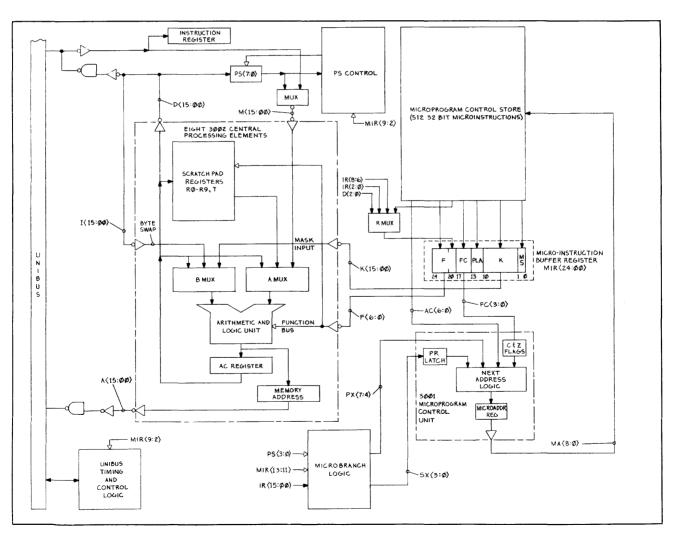

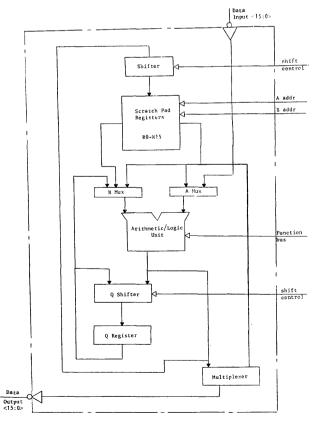

| Using LSI processor bit-slices to build a PDP-11—A case study in microcomputer design<br>T. M. McWilliams, S. H. Fuller and W. H. Sherwood                             | 243 |

| SOFTWARE MANAGEMENT—PLANNING FOR A NEW SOFTWARE DEVELOPMENT PROJECT                                                                                                    |     |

| Organizing and training for a new software development project—That big first step<br>Daniel Freedman, Donald C. Gause and Gerald M. Weinberg                          | 255 |

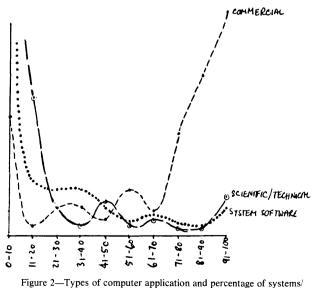

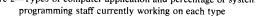

| The choice of new software development methodologies for software development projects                                                                           | 261 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Software development tools-acquisition considerations<br>Leon G. Stucki                                                                                          | 267 |

| Understanding the developmental life cycle                                                                                                                       | 269 |

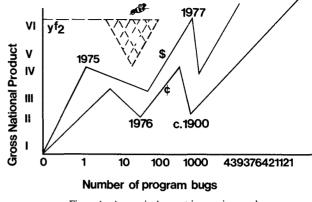

| Management of large scale computer program production                                                                                                            | 277 |

| Test Planning<br>R. Dean Hartwick                                                                                                                                | 285 |

| COMPUTER SYSTEMS IN HEALTH CARE DELIVERY AND MEDICAL LABORATORIES                                                                                                |     |

| NODAS—The network-oriented data acquisition system for the medical environment<br>Shelly I. Saffer, David J. Mishelevich, Shirley J. Fox and Victor B. Summerour | 295 |

| A system for priming a clinical knowledge base<br>Randal L. Walser and Bruce H. McCormick                                                                        | 301 |

| A proposed study to access the impact of microprocessors on health care delivery                                                                                 | 309 |

| ADVANCED CONCEPTS IN DATA BASE MANAGEMENT                                                                                                                        |     |

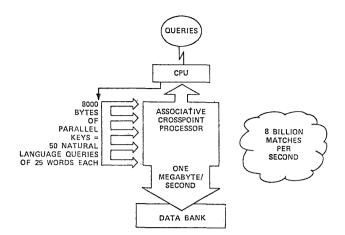

| Natural language knowledge processing<br>Christine A. Montgomery                                                                                                 | 313 |

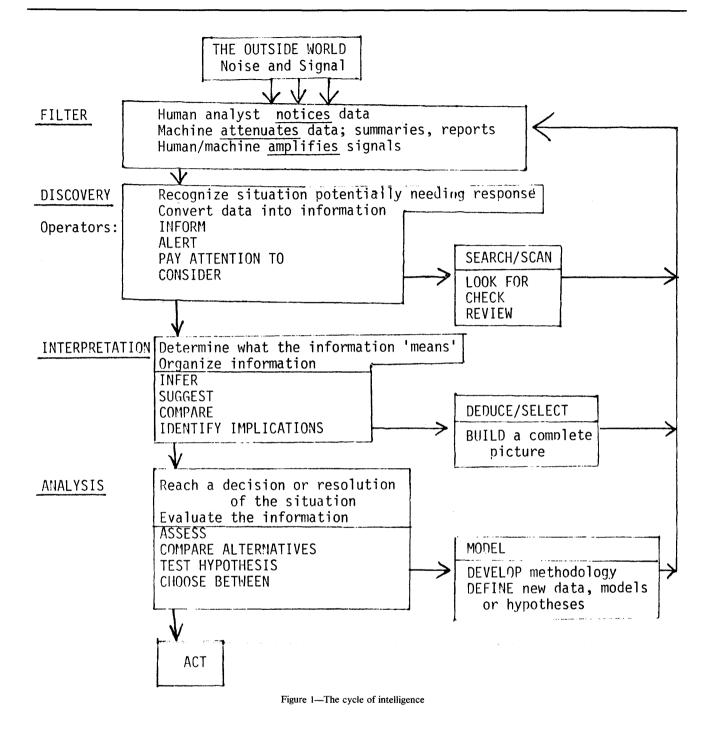

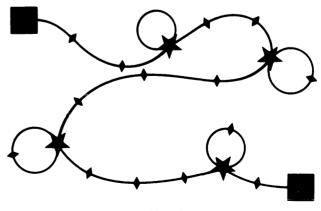

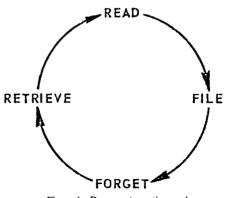

| The intelligence cycle—A differential perspective of information processing<br>Peter G. W. Keen                                                                  | 317 |

| EDUCATION FOR MEDICAL INFORMATION SCIENCE                                                                                                                        |     |

| Plans for a program in medical information science<br>Allan H. Levy and Thomas T. Chen                                                                           | 321 |

| The health care computer user—Where will we find the integrators?                                                                                                | 327 |

| COMPUTER HARDWARE DESIGN                                                                                                                                         |     |

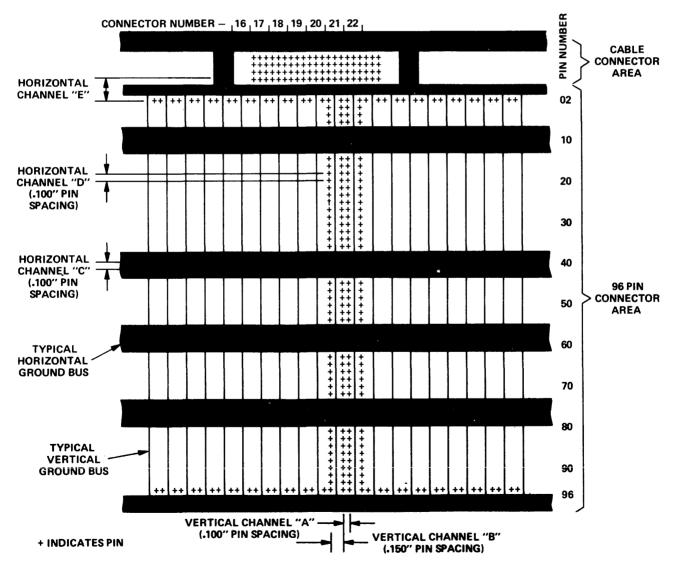

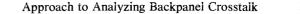

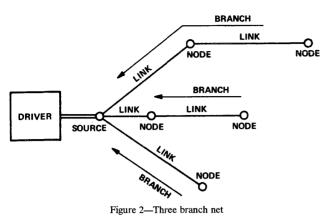

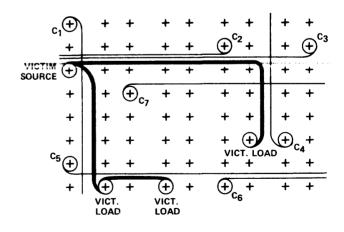

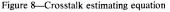

| NAA—An approach to analyzing backpanel crosstalk<br>J. S. Hebhardt, C. F. Groves and R. Bardas                                                                   | 331 |

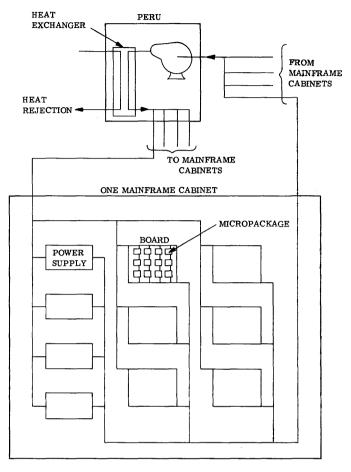

| True liquid cooling of computers                                                                                                                                 | 341 |

| OUTPUT—RESULTS AND RHETORIC                                                                                                                                      |     |

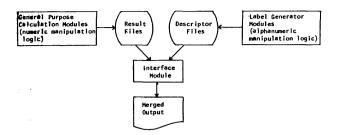

| GO System—Design and implementation of an output generator<br>Roland R. Bonato and Kenneth C. Yang                                                               | 349 |

| A talking computer terminal<br>James A. Kutsch, Jr.                                                                                                              | 357 |

| Hard-copy computer output and its future<br>Irving L. Wieselman                                                                                                  | 363 |

| DATA STRUCTURES                                                                                                                                                  |     |

| Variable-length hash area entries                                                                                                                                | 371 |

| Decomposition of data flow graphs on multiprocessors<br>W. C. Brantley, Jr., G. W. Leive and D. P. Siewiorek                                                     | 379 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Implementation and application of a function data type<br>Mark B. Wells                                                                                          | 389 |

| MAN-MACHINE INTERFACE                                                                                                                                            |     |

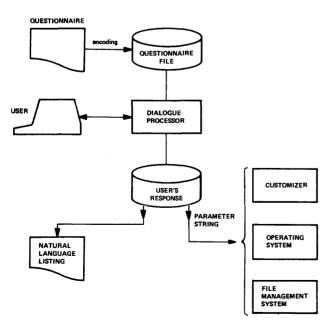

| A general-purpose dialogue processor<br>James L. Black                                                                                                           | 397 |

| A study in man-machine interaction<br>Lawrence H. Miller                                                                                                         | 409 |

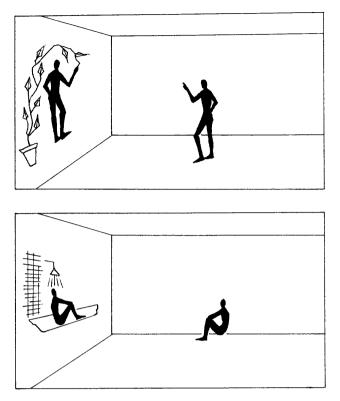

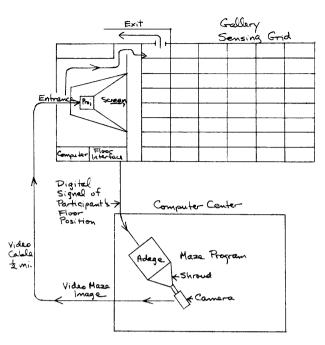

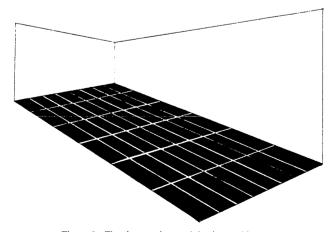

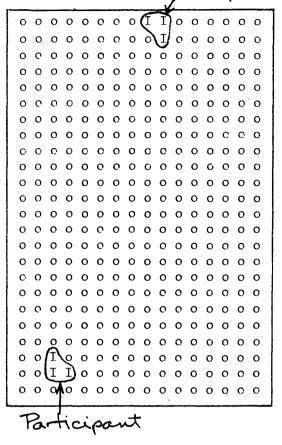

| Responsive environments                                                                                                                                          | 423 |

| COMPUTER TECHNOLOGY IN THE INFORMATION/LIBRARY FIELD                                                                                                             |     |

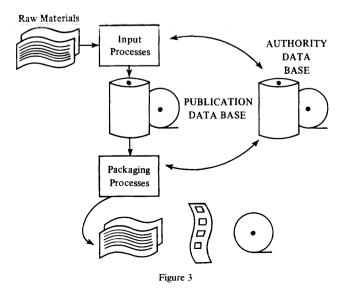

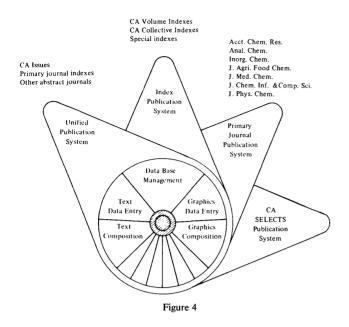

| Computer technology in data-base publishing<br>D. B. Baker and R. E. O'Dette                                                                                     | 435 |

| Improving corporate information services in an automated word-processing network                                                                                 | 443 |

| A subject-content oriented retriever for processing information on-line (SCORPIO)<br>Charlene A. Woody, Michael P. Fitzgerald, Francis J. Scott and D. Lee Power | 449 |

| APPLICATIONS OF COMPUTER NETWORKS                                                                                                                                |     |

| Comparing equivalent network services through dynamic processing time prediction                                                                                 | 455 |

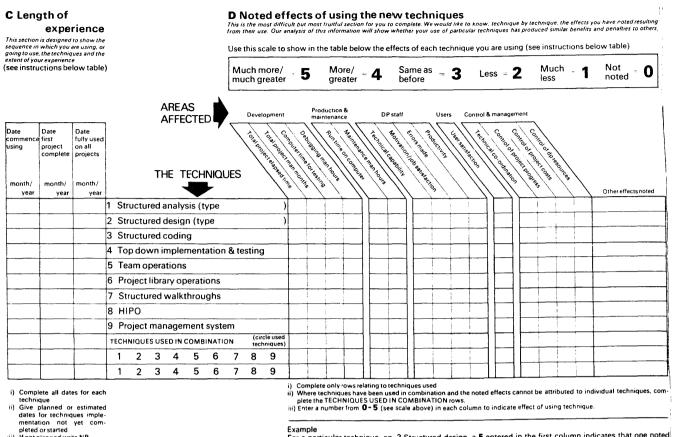

| A structured data base computer conferencing system<br>George W. Arnold and Stephen H. Unger                                                                     | 461 |

| COMPUTER SYSTEMS—A GLOBAL VIEW                                                                                                                                   |     |

| An analytic model for parallel computation                                                                                                                       | 469 |

| Dominance relations in computing systems<br>Daniel G. Hays                                                                                                       | 475 |

| CONTINUING EDUCATION FOR THE COMPUTER SPECIALIST                                                                                                                 |     |

| Structured training—A common sense approach to developing ADP skills for improved job performance<br>Alexander P. Grant and Jack L. Stone                        | 481 |

| The role of a formal training program in attracting and developing computer professionals<br>Lawrence F. Lunetta, Jr.                                            | 487 |

| PERSONAL COMPUTING—HISTORY AND FORESEEABLE FUTURE                                                                                                                |     |

| Personal computing—An overview for computer professionals<br>Jim C. Warren, Jr., Mark E. Deppe and James P. Fry                                                  | 493 |

| DATA BASE STRUCTURE AND ORGANIZATION                                                                                                                             |     |

| Operational software for restructuring network data bases<br>Donald E. Swartwout                                                                                 | 499 |

| A multi-level procedure for design of file organizations<br>Eivind Aurdal and Arne Solvberg                                                                      | 509 |

# SOFTWARE VALIDATION

| An effective method for measurement and analysis of system software performance<br>John R. Rumsey and David W. Abmayr | 523 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| The Navy Fortran validation system<br>Patrick M. Hoyt                                                                 | 529 |

| A two-step approach to the validation of software engineering methodologies                                           | 539 |

# COMMUNICATION AND EDUCATION

| Surveying the billion dollar chasm—How educational differences continue to force corporate and data |     |

|-----------------------------------------------------------------------------------------------------|-----|

| processing executives apart                                                                         | 545 |

| A community of individuals—Cooperation and individualization in computer science education          | 561 |

| New perspectives for information systems education                                                  | 569 |

# DATA BASE APPLICATIONS

| Petroleum data system—A network of energy information                                     | 575 |

|-------------------------------------------------------------------------------------------|-----|

| Applications of SPARCOM data base concepts to a crime combating environment<br>Ron Ashany | 579 |

| Integrated data base concepts and structures for combat models                            | 595 |

# INTERNATIONAL NETWORKS AND PACKET-SWITCHING

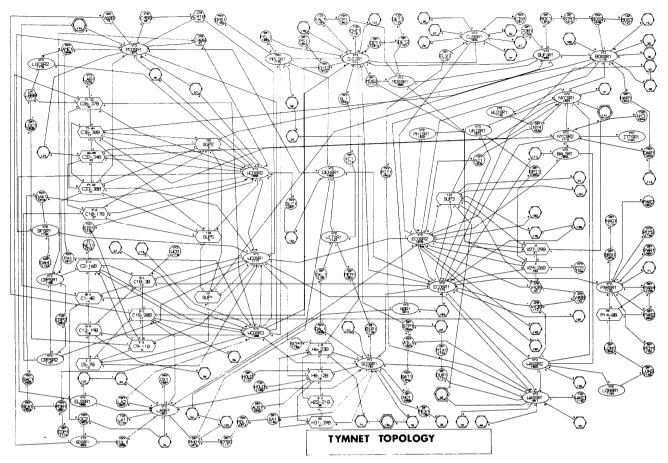

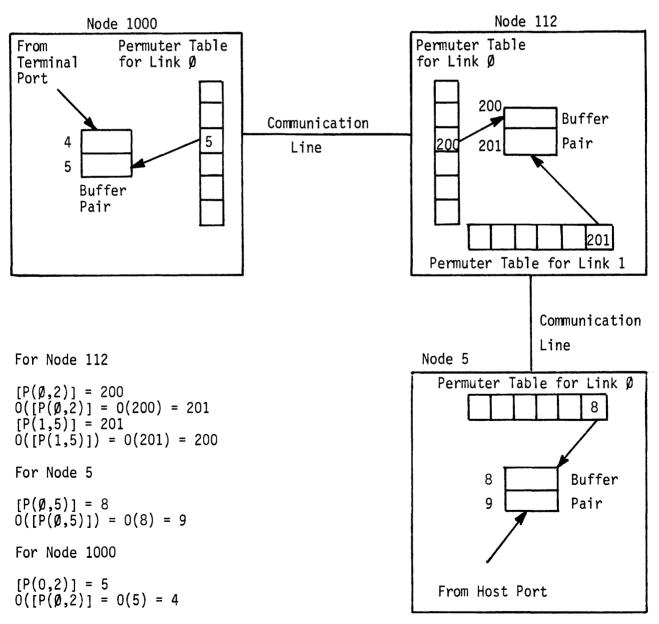

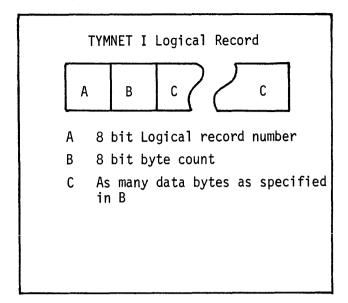

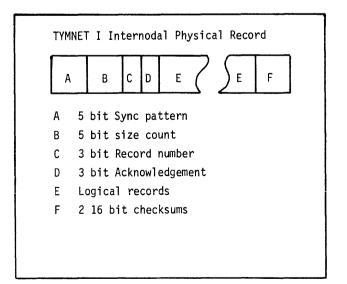

| Routing and control in a centrally directed network                                                 | 603 |

|-----------------------------------------------------------------------------------------------------|-----|

| TYMNET as a multiplexed packet network<br>John Kopf                                                 | 609 |

| Packet switched network in Japan<br>Toshiharu Takatsuki, Jiro Iimura, Masato Chiba and Masayuki Abe | 615 |

# PROGRAMMING LANGUAGES—HIGH-LEVEL PROGRAMMING FOR LOW-LEVEL MACHINES 623 Modular programming conventions in assembly languages 623 Shy-Ming Ju 7 The design and implementation of a simple programming language for microcomputers 629

# The design and implementation of a simple programming language for microcomputers ...... J. C. Cleaveland and C. D. Satten

# Cm\*—A MULTI-MICROPROCESSOR COMPUTER SYSTEM

| <ul> <li>Cm*—A modular, multi-microprocessor</li> <li>R. J. Swan, S. H. Fuller and D. P. Siewiorek</li> <li>The implementation of the Cm* multi-microprocessor</li> <li>R. J. Swan, Andy Bechtolsheim, Kwok-Woon Lai and John K. Ousterhout</li> <li>Software management of Cm*—A distributed multiprocessor</li> <li>Anita K. Jones, Robert J. Chansler, Jr., Ivor Durham, Peter Feiler and Karsten Schwans</li> </ul> | 637 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                         | 645 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | 657 |  |

| PROGRAMMING LANGUAGE THEORY                                                                            |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Using assertions to improve language translators<br>Arthur Pyster                                      | 665 |

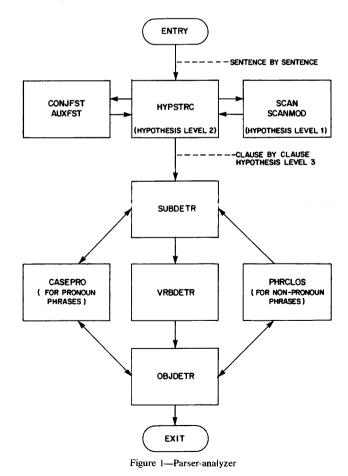

| A parser analyzer of empirical design for question-answering                                           | 669 |

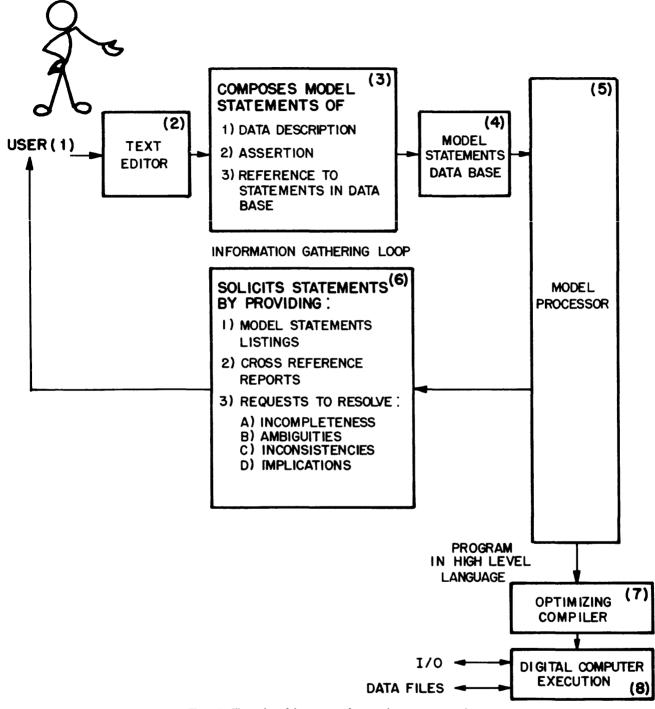

| Automatic generation of computer programs                                                              | 679 |

| ARCHITECTURE FOR DATA BASE MANAGEMENT                                                                  |     |

| Sorting with associative secondary storage devices<br>C. S. Lin                                        | 691 |

| A specialized architecture for textural information retrieval<br>Lee A. Hollaar and W. H. Stellhorn    | 697 |

| FAULT-TOLERANT COMPUTING—I                                                                             |     |

| Fault-tolerant modularized arithmetic logic units         T. R. N. Rao and H. J. Reinheimer            | 703 |

| The design of self-checking multi-output combinational circuits<br>D. C. Ko and M. A. Breuer           | 711 |

| REMOTE TERMINAL EMULATION                                                                              |     |

| Remote terminal emulation in the procurement of teleprocessing systems                                 | 723 |

| Application of remote terminal emulation in the procurement process                                    | 729 |

| Remote terminal emulator development and application criteria                                          | 733 |

| SOFTWARE FOR USERS AND MANAGERS                                                                        |     |

| A survey of structured programming practice<br>I. St. J. Hugo                                          | 741 |

| An interactive system for aiding management decision making<br>Robert C. Gammill and Hebert J. Shukiar | 753 |

| ADP ACQUISITIONS—CONTRACTING, FINANCING, INVESTING, THIRD-PARTY MAINTENANCE                            |     |

| An overview of independent, third-party computer maintenance                                           | 761 |

| A perspective of standard form contracts in the data processing industry                               | 765 |

| Small computers and small investors                                                                    | 771 |

| APPLICATION OF DIVERSE TECHNOLOGY AND ITS RELATION TO OCR SYSTEMS                                      |     |

| Non dedicated interprocessor communications discipline<br>David J. Bastyr                              | 775 |

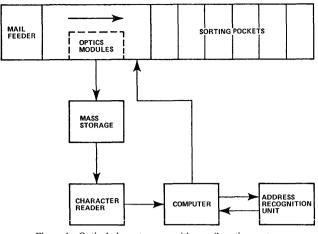

| An approach to address identification from degraded address data                                       | 779 |

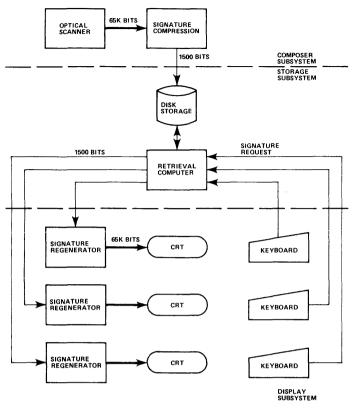

| Signature and facial image compression by boundary encoding                                            | 785 |

# TEXT PROCESSING SYSTEMS

| An interactive text-editing system in support of Russian translation by machine<br>David A. Luther, Christine A. Montgomery and Ronald M. Case                        | 789 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Computer generation of conference presentations                                                                                                                       | 791 |

| FAULT-TOLERANT COMPUTING II                                                                                                                                           |     |

| Design of a diagnosable and fault-tolerant input/output controller                                                                                                    | 795 |

| Modular redundancy without voters decreases complexity of restoring organ<br>P. T. DeSousa and F. P. Mathur                                                           | 801 |

| A study of intermittent faults in digital computers<br>Omur Tasar and Vehbi Tasar                                                                                     | 807 |

| PERFORMANCE EVALUATION                                                                                                                                                |     |

| A "calibration-prediction" technique for estimating computer performance<br>C. A. Rose                                                                                | 813 |

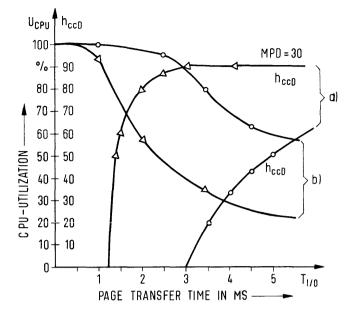

| CPU-utilization and secondary-storage performance—The demand for a new secondary-storage technology<br>Peter Schneider                                                | 819 |

| DISCRETE MATHEMATICAL MODELS                                                                                                                                          |     |

| Non-linear parameter estimation for probabilistic finite-state automata<br>Fred J. Maryanski and Kuang Chan Wu                                                        | 827 |

| A comparison between two paradigms of intelligent systems—An exampleAbraham Waksman                                                                                   | 833 |

| Concatenated group theoretic codes for binary asymmetric channels<br>Serban D. Constantin and T. R. N. Rao                                                            | 837 |

| DATA BASE—EXTENSIONS AND APPLICATIONS                                                                                                                                 |     |

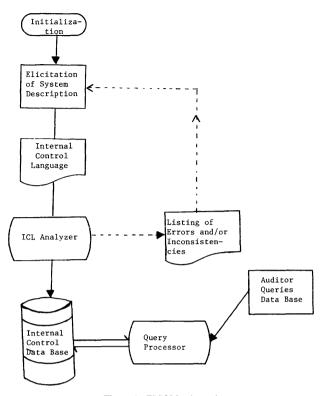

| The TICOM model—A network data base approach to review and evaluation of internal control systems<br>James I. Cash, Jr., Andrew D. Bailey, Jr. and Andrew B. Whinston | 843 |

| Design and implementation of an information base for decision makers<br>Robert H. Bonczek, Clyde W. Holsapple and Andrew B. Whinston                                  | 855 |

| APPLICATIONS OF COMPUTER SYSTEMS                                                                                                                                      |     |

| Laboratory automation via a VM/370 teleprocessing virtual machine                                                                                                     | 865 |

| Computer typesetting of technical journals on UNIX<br>Michael E. Lesk and Brian W. Kernighan                                                                          | 879 |

| The computer in manufacturing—Reduction of scrap by computer monitoring<br>Patricia E. Gober                                                                          | 889 |

| INFORMATION SYSTEMS-PERFORMANCE ORIENTED DESIGN AND EVALUATION                                                                                                        |     |

| A methodology for multi-criteria information system design<br>John S. Chandler and Thomas G. DeLutis                                                                  | 895 |

| Automated control of concurrency in multi-user hierarchical information systems                                                                                       | 907 |

| COMPUTER ARCHITECTURE DESIGN                                                                                                                                |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Techniques for requirements—Oriented design                                                                                                                 | 919 |

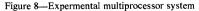

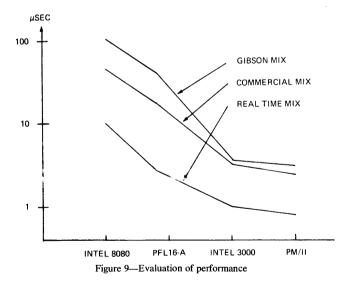

| A multi-microprocessor approach to a high-speed and low-cost continuous-system simulation<br>Ryoichi Yoshikawa, Tatsuo Kimura, Yasuhiro Nara and Hideo Aiso | 931 |

| Instrumented architectural level emulation technology                                                                                                       | 937 |

| SPECIAL MEMORY ARCHITECTURES                                                                                                                                |     |

| ARES—A memory, capable of associating stored information through relevancy estimation<br>Tadao Ichikawa, Ken Sakamura and Hideo Aiso                        | 947 |

| Cache memory systems for multiprocessor architecture<br>O. P. Agrawal and A. V. Pohm                                                                        | 955 |

| THE COMPUTER IN MANAGEMENT AND BUSINESS                                                                                                                     |     |

| Choosing a medical billing system<br>Jeffrey Rothmeier                                                                                                      | 965 |

| Designing software for the minicomputer business data processing environment—A case history<br>John M. Hemphill and Ronald L. Lancaster                     | 969 |

| What to look for in distributed (source) data processing<br>W. Harry Vickers                                                                                | 973 |

| SIMULATION METHODS                                                                                                                                          |     |

| RESQ—A package for solution of generalized queueing networks<br>C. H. Sauer, M. Reiser and E. A. MacNair                                                    | 977 |

| An approach to simulation of multilevel production systems<br>J. F. Clark and D. M. Cohen                                                                   | 987 |

| PERSONAL COMPUTING SYSTEMS                                                                                                                                  |     |

| Low cost data acquisition and control systems for the computer hobbyist                                                                                     | 991 |

| Diskomania—A small-system floppy disk operating system                                                                                                      | 995 |

| TRENDS IN COMPUTER STORES                                                                                                                                   |     |

| Neighborhood computer stores—The answer to microcomputer marketing                                                                                          | 999 |

# Data base administration—Classical pattern, some experiences and trends

by JEAN-PAUL DE BLASIS

*Centre d'Enseignement Superieur des Affaires* Jouy-en-Josas, France

and

THOMAS H. JOHNSON

The Wharton School University of Pennsylvania Philadelphia, Pennsylvania

# ABSTRACT

This three part paper covers the growth and classical patterns of data base administration along with a survey of some currently practicing data base administrators. As a result, some trends and evolutions of the data base administrator position are presented.

After a brief historical introduction, the paper first sets forth basic definitions and organizational considerations for the DBA function. Interfaces, both internal and external are defined and the associated problems are discussed. The functions and responsibilities of the DBA are presented along with the tools available for carrying them out as recommended by various committees including CODA-SYL, GUIDE/SHARE and other reports.

Then, a survey of organizations utilizing data base administrators is presented. The survey looks at organizations of varying sizes and commitments to data base technology. The results of the survey try to show how the previous recommendations are reflected in reality. An attempt to rationalize the plans and the actual status of the DBA in an organization is carried out.

Finally, from the survey results and from projections provided by the data base administrators themselves, some trends in the evolution of their functions are outlined. In light of these projections an attempt is made to review some of the recommendations currently put forward.

# INTRODUCTION

Does the data base administrator portrayed in the current literature exist in practice? What are the differences, and what are the trends for the DBA function? This paper attempts to answer these questions by briefly reviewing the literature, discussing actual practice, and outlining the trends in the data base administrator's role.

We developed a central thesis from pre-screening inter-

views and literature search to focus our research on the data base administrator. In testing this thesis, we uncovered areas for future research and application emphasis. After posing the central problem, we reviewed the definitions and functions of the DBA as defined in current literature to frame our discussion. Next, we focused on the current state of the DBA, summarizing interviews of over twenty practitioners. We present results in the form of evolutionary trends occurring in this area and conclude with opportunities for research suitable to the support of practitioners.

The central thesis is:

The data base administrator now, and in the future, is an individual who performs the function of planning, designing, operating and controlling the data base of an organization at both the policy and operational level.

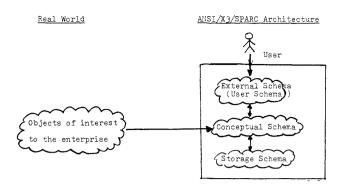

In order to frame the results from our study, we must first establish the definition, function and organization proposed for data base administrators. We have synthesized proposals and reports from both committees studying the area and authors publishing in the area. Committees include GUIDE-SHARE,<sup>12,13</sup> CODASYL,<sup>6,7</sup> and ANSI-SPARC.<sup>1</sup> They are very active in the DBA area, especially GUIDE-SHARE which has advocated recent expansions of the DBA role to data administrator and put forward techniques for focusing on data resource policy.

# **DEFINITIONS AND FUNCTIONS**

# Definitions of the data base administrator's function

The individual introduced in both Codasyl and Share Reports, called the data base administrator, is a person meant to solve many of the problems in file integration and in maintenance of any organizational data base. He is supposed to be familiar with computerized systems, with data management, and above all, with every aspect of the corporate data base. The DBA function has been previously defined as a human function, responsible for the coordination of all data related activities.<sup>4,17</sup> The following is an extended definition specifying some of the generic areas of the DBA's functional responsibility. The data base administrator is the individual providing the coordination, perspective, and administration of the data base by exercising specific responsibilities. His responsibilities should include the definition, organization, protection, efficiency, and documentation of the data base. He should also be responsible for defining the rules by which data is to be accessed and stored.

To decide where to place the DBA involves trade-offs almost always because of the distinct organizational characteristics in which every systems environment operates. The answer provided by the literature is generally that the DBA should report to the highest full-time information systems manager.<sup>17,20,21</sup> Practically, however, there are very few DBA's who are aligned this way, as shown by some field studies.<sup>10,14,19</sup>

# Interfaces

The data base administrator generally interfaces directly with three groups within the organization. The systems administration group is the first. This group is concerned with the operation, maintenance and performance of the information systems equipment. This includes the performance of data base management systems, as well as security, recovery and re-start of these systems. They are also concerned about the throughput of the system and the running of production systems in the most effective manner.

Another interface exists between the data base administrator and systems development. Systems development is considered to include the planning, analysis, design, and implementation of application processes. The data base administration would participate in the design effort and make determination of technical and economic feasibility in seeking to satisfy the data requirements of the applications processes. The data requirements of new systems may be satisfied by using data already collected and stored or by extending the definition of the data base to include new data requirements.

In cooperation with users, the data base administrator is supposed to seek to determine what data to collect and store and the criteria to use in validating input data and stored data. It has been suggested that the correctness of data is the responsibility of the user, while the protection of data is the responsibility of the data base administrator.<sup>18</sup> A Diebold Research Report<sup>11</sup> notes a trend towards "placing responsibility for data accuracy, validity, and so forth, in the hands of the user who will be served by the data base." The report suggests the appointment of a "Prime Responsible Authority" (PRA) for each data base from its primary user division. The PRA interfaces with all users on one side and with the data base administrator on the other. In other words, the "prime responsible authority," working in a user division rather than in the data base administrator's organization, would be responsible for content, integrity and use of the data base with respect to all users within the organization, both within and outside of his own using organization.

An Auerbach document<sup>2</sup> lists ten areas of functional responsibility for the data base administrator as it can be seen in Table I. Rather than discussing those ten areas, we shall focus on the unique functions of data base administration, which are: definition, storage and update of data; making the data base available to the using environment; informing and servicing users; maintaining data base integrity; and operations and performance.

# Definition, storage, and update of data

The process of data definition begins in response to stated data requirements from the using environment. The first step in definition process is to design the logical data structure, incorporating as much as possible of the natural structure inherent in the data. In a sense, a logical data structure should model selected aspects of the operations and entities as they really exist. This is pointing out that to date very little work has been done on developing formal methodologies to aid in the process of data base design which is really needed though, with perhaps the exception of some current efforts in that direction being in progress. Once the logical data structure is developed, it is formalized in the Data Definition Language (DDL) of the particular data base management being used. Things that the data describe in logical data structure will eventually be stored physically in the computer system. Having defined some data to the system, the next step is to set up the mechanisms to acquire the new data and to bring it into the system.

Finally, the last step in the process is to execute management policies regarding update of data. Even if the value of data diminishes over time, it is not desirable to aggregate older data. An updating mechanism should be set up to store the older in off-line archival files for example.

# Establishing data availability

One of the functions of the data administrator is to assist users in their search for data to satisfy their application

TABLE I-Areas of Data Base Administration Responsibility

- 1. Data Definition

- 2. Data Base Design and Implementation

- 3. Data Base Access

- 4. Data Base Standards Control

- 5. Documentation

- 6. Operations

- 7. Monitoring

- 8. Data Base Management Systems Enhancements

- 9. Education

- 10. Vendor Enhancements

requirements. He should maintain a Data Base Directory (DBD), in which are recorded the record types, and set types currently available to users. The DBD will then be the initial source for information relative to data availability. If it happens some data elements are not available within the confines of the existing data base, the data administrator will arrange the interface with the necessary data sources to satisfy the demands of the users. Such demands, of course, should remain within the cost constraints controlling the user and the data base administrator.

Some additional factors to be included when considering data availability are the following:

- 1. Present form and location of data.

- 2. Access techniques to be used.

- 3. Intended use of data in relation to its present accuracy, completeness and timeliness.

- 4. Need for modification of data.

- 5. Present authorizing agent for use of data.

- 6. Cost of providing the data.

# Maintain data base integrity

The protection of the data base is an essential responsibility of the data base administrator. The data base represents a large dollar investment, and data contained in it is vital to all who use it. Alteration, destruction or disclosure of the data base may represent an enormous and irrevocable loss in time and money. Although complete integrity protection is never possible, a high level of protection should be kept as much as possible.

The general problem areas in data base protection are:

- 1. Data base access and manipulation;

- 2. Data base integrity;

- 3. Safe recovery/restart.

# Data base documentation

In addition to being an organizer and an administrator of the data in the data base, the DBA is the prime documentarian and educator with regard to the Data Base Management System (DBMS) at his installation, and he should provide for the recording of procedures, standards, guidelines, and data base descriptions for proper use of the data base.<sup>3</sup>

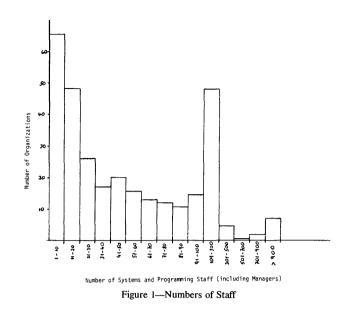

# STUDY RESULTS

Over twenty Data Base Administrators' groups have been studied to date. Their companies ranged in size from \$3 billion to \$20 million in revenues and data bases ranging in size from 100 billion characters to a few hundred thousand characters. Despite the range of application and size of companies, we found remarkable similarities among approaches, problems, and successes. The results are presented here in summary form to support the main thesis. The detailed survey is being published in working paper form.<sup>14</sup>

Recall the primary thesis we set out to prove:

The data base administrator now and in the future is an individual who performs the functions of planning, designing, operating, and controlling the data base at both policy and operational levels.

#### Operations vs. policy

Critical in the thesis statement are the dual tasks of operations and policy making. This conflict, we found, is one area where the position statement breaks down. The data base administrator is said to be responsible for the definition, storage, and update of data; making the data base available to the using environment; informing and servicing users; maintaining data base integrity, operations and performance. The data base administrator is also said to be responsible for corporate data base policy; access authorities; definition of data base content and organization; selection of data to collect and store input; criteria to use in validating input; and conflict mediation among users, system designers, and computer operations.<sup>23</sup>

These latter functions required the DBA to be high enough in the organization's management, so that the position has authority to set and enforce policy. The former functions, more operational, required less top management involvement and usually meant a lower position in the organization. Furthermore, the operational dimension caused the DBA to bias the broader policy issues affecting many groups in favor of his own operations.

# Evolution of the DBA

As the study began, we uncovered another framework which shed considerable light on the DBA. A definite maturing of the DBA function occurs within an organization. The newer DBA's were often focusing on problems that the more established DBA's had already resolved. DBA's at different stages of development did not articulate the stages that we observed. They related primarily to the current problem and to a continuum they were currently traversing.

Our formulation of these evolutionary steps made observation of DBA's much simpler and more logical. First, it helped separate the progress of a particular DBA group and the progress of the field as a whole. By classifying each DBA group according to their development stage, we could study that group's state relative to the stage and not to the general population. For instance, the DBA just getting started with a three person staff has significantly more support than the DBA in the height of development with three people. We then could ask if the problem definition phase is receiving greater attention instead of observing the gross state of the group.

We outlined five stages in the evolution of the data base administrator function: Introduction, initiation, integration, operation, and maturation.

Introduction generally took the form of either a study group or a manager's individual recommendation and decision to go with a data base management system. Although we did not take much specific data on this phase, most earlier introductions seemed to discover a need for a data base administrator after using a DBMS, while more recent introductions also discovered a need for the DBA to parallel or precede a DBMS.

Next, the initiation of a DBA consists of developing one or two data base systems. As much as total system design or top down approach may be touted, the corporate data base was never built in this phase, it was always started as one or two application data bases. Most often the DBA's speed of success rested on how well these applications were performed (we say speed of success because despite severe negative benefits in some systems, data bases are becoming essential to most business organizations and the question is generally how fast). It is in this stage lasting one or two years that the DBA spends a considerable amount of time and money to establish a base for future growth. Correct choice of system, personnel, applications, etc. are critical here.

Integration, the joining of several systems together into the corporate data base, is a development phase of several years duration. It really never stops, but we have established an (arbitrary) turning point into maturity when the DBA has control of data base's definition, design, access, and standards along with having a large majority of DP application systems on the DBMS. This points out the two maturation phases going on during integration phases. One is the actual integration of data into the data base, the other is the acceptance of the DBA as the group in control, mainly operational control, of the data base.

Maturity sees the focus of effort move from development to operations. It also means a focus of the DBA role as the center of data base systems responsibility from design to operation. Some organizations might believe they have matured with only one or two subsystems operating, but until the DBA is involved from the beginning in all data base work and also has the final power to make the operational decisions, the group has not matured.<sup>22</sup> In fact, during our survey we found very few mature groups.

# General experiences

For the study, we outlined several questions to help us establish a more logical pattern to our research. Some questions were posed directly to the subject; others were broken down in more detail and synthesized here.

- Is there a measure of the size of the DBA's organization?

- What are the qualifications needed to fill the DBA position?

- Which of the ten functions does the DBA perform?

- Where does the DBA report in the organization?

- What is the cost of the DBA and where are the economies?

- What is the biggest problem faced by the DBA?

# Size of DBA function

The size of the DBA group is proportional to the size of the data base up to a point. With one exception, the DBA group increased with the size of the data base. The increase was not linear, because the high initial cost to support the system causes a rapid growth initially followed by a more gradual but noticeable increase. The largest group interviewed had 14 people in the DBA group; the smallest had one. Economies of specialization and scale took over as the data base grew, and the staff became organized, usually functionally, but sometimes in project teams. We learned that the start-up effort can be substantial. The analyst/ programmer training consumed a large portion of the DBA's time during the first two years of operation, but fell drastically after user acceptance. In many cases, training and marketing DBMS went together, so the work load further increased start-up staff size.

Once application systems arrived at an operational level, the group did not shrink because of required data base and program updates and other support functions. Surprisingly, all those interviewed who had been operational for sometime, sighted more man-hours consumed on system problems than data structure updates. As major applications became operational, the role of the DBA staff grew more operational and tended to increase, usually in support personnel.

There was one strategic milestone for staffing which passed quickly in some cases and never in others, and that is commitment to data base technology. With the commitment given, staff size no longer was a problem. Without it, the DBA found mustering resources, like staff, difficult. A few groups were able to overcome this obstacle by performing well despite resource constraints; one group disbanded, several more are not beyond this milestone.

Two final notes: first, staff size is not a measure of the quality of a data base group, but it can be a measure of the data base size. There may be a relationship between the size/complexity of a data base and the size of the DBA group.<sup>14</sup> Next, there appears to be little relationship between the type of DBMS and the size of the DBA group. Though this finding came as a surprise since different technologies would require different staffing, it now seems logical because the technologies are not all that different and the major problems requiring staff are fairly similar. There may also be a measure of technology improvement and staff size if these findings are verified.

### What are the requirements for a DBA

It was felt by those interviewed that the primary requirements for a person to be a DBA or join the DBA group were both technical skills and knowledge of the company, administrative capability ranked a weak second.

Sixty percent of the current administrators had lengthy experience within their companies' DP department, not necessarily with DBMS. The others were DBMS experts brought in for the job. The overwhelming majority of the administrator's non-clerical staff were technically trained in DBMS. The large majority of administrators suggested that their replacement should have both technical training and a minimum of two to five years with the company. Their staff members were required to have a strong technology background before being considered for hiring or transfer from an application area being implemented under the DBMS.

The technical skills requirement was even more pronounced in the more mature groups. They were finding a greater demand on the part of analysts and users for more detailed systems assistance. In all of the mature groups, the DBA group found themselves spending a large amount of time in the system support function. Frequently, they were supporting applications programmers as systems programmers because the applications people considered the data base part of the operating system.

Administrative skills were secondary qualifications to three-fourths of the DBA's. A person with a Master's in computer sciences and with company acquired skills is much preferred as a DBA over someone having a Master's in Business with technical skills. It was felt that administrative skills could be learned on the job. This opinion held for the very large DBA groups and the very small ones.

# DBA JOB FUNCTION

The DBA function among organizations is remarkably similar in the long run, but start-up situations were crucially different. The actual job descriptions, the 30 percent we were able to see, came directly from the DBA literature.

We were very surprised that generalization about the DBA function could be made between different-size companies using different DBMS products. Each company and package have difficulties unique to itself, but histories, problems, and operational organizations were similar. The literature explained the functional areas for setting up operation, and the DBA's generally read these major sources for advice. The DBA groups we found were primarily operational functions whose objectives were technical support for applications analysts. The organizations tended to grow more support-oriented with time.

Of the ten tasks outlined earlier, implementation, access, DBMS enhancements, education, and vendor enhancements were the five major areas of concentration found in young groups, in the initiation phase. In this phase, data definition and design were not relinquished by the applications analysts. Control, documentation and monitoring were not institutionalized very well in the DBA functions. Operations were almost always delegated to the company's operations department under advisory relationships with the DBA. Often backup recovery was a major headache for the newly initiated data base group until operations had accepted responsibility for its execution.

These young DBA groups were brought in at the last stages of applications development to "make this a data base system." The applications analyst would have done all the work, built the system, and as a last touch, attached the DBMS. Education, in the form of data base techniques and data base design principles, became a major consumer of the DBA group's time. The education served three purposes: sell DBMS as a concept, sell the need for involvement of the DBA early in the application design, and teach the analyst how to use the DBMS.

The evolution towards involvement of the DBA in application design became evident in the large majority of mature systems. The groups generally gained this involvement via user acceptance, not by fiat. As the groups matured, internal controls, documentation and monitoring became a part of daily operation. Backup and security was one area of responsibility serviced from the start. The DBMS generally voided normal file backup operations, yet, the operation was required. The DBA set up procedures for the operations group to follow to back up the DBMS.

Vast differences did occur in initiating the DBA function and bringing it to mature operation. These differences appear in organizational consideration, top level commitment to the DBA's, and interfaces with operations, applications, development and users. There is genuine need for further research in this area to support the start-up and evolution of a DBMS and the DBA, especially relating to these areas.

# Where the DBA report in the organization

Data base administrators rarely report to the highest systems' administrator, but more frequently report to the manager of systems analysts.

Current authors in an attempt to improve the DBA position's strength have an extensive list of policy roles for the group to play. These roles do not yet occur in the practical world. Being the mediator and direct advisor to the chief systems administrator on data policy has been recently proposed.<sup>14,19,24</sup> In practice, we have not seen this occurring in the person of the data base administrator. The DBA is most frequently a senior analyst or group leader in applications or systems development organizations. In only two cases did the data base administrator report to the top level of systems management.

We recognize the need for better data base policy in organizations. But from the history of current DBA's, this policy maker would probably be another individual with the DBA serving as an important part of policy implementation. In fact, historically, there generally was an individual or group of individuals who took on this policy role. They instituted or supported the policy to use a DBMS and to initiate the DBA function. The creation of a position to plan and control the use of data resources is one way to institute data base policy. The formalization of a committee is another way to institute policy. Either way, it appears to be a job separate from the DBA's job.

# Cost and economies of the DBA

Two facts stood out in our survey in this area. First, the organizations had little idea what the direct cost of the DBMS or the DBA were. Second, the organizations recognized that they required a DBMS and the DBA to economically operate their data processing system.

It is astounding how poorly the cost and economies of DBMS are measured, for that matter it is astounding how poorly the computer resources are measured. In general, an astute applications group within these companies should immediately take advantage of the DBA and attempt to use the data base because the charges for these resources were not accounted for directly. In some cases operations cost, computer run time, was charged back to the user, and served as a deterent to using the data base. But generally the DBA groups were an overhead item, a necessary expense to keep the system operational.

The rush to be "on the data base" did not occur. However, the costs or economies were rarely the reason given for not using the DBMS.

No good data about the economies of these data base systems came out of the study. At most it can be said that they are expensive to build and to run. A DBMS needs a group of experts, the DBA, to run and maintain it in order to keep the unaccounted for costs down to some unknown amount. Organizations are willing to pay some proportion of the budget to support the systems and the staff. And, the organizations who had committed to the use of a DBMS felt they were getting good results from the change.

# The major problem stated by the DBA

Administrative problems, or organizational issues surfaced as the most important problems in the great majority of groups studied. After insisting on technical people to staff the group, the DBA manager cited his critical problems occurred in a variety of administrative areas. These problems were often a function of the point of evolution of the group.

The groups just starting up cited top management support, cooperation from user groups, and training or education as their most frequent problems. The more mature groups cited control and coordination problems along with evolving technology difficulties. The younger groups generally felt satisfied with the technology, but felt constrained by the environment, while the older groups although still bothered by administrative problems had technical difficulties as frequently mentioned as organizational ones.

For the DBA in the initiation phase the major problem revolved around either introducing a new technology into the organization or the creation of this cross organization body that the DBA represented. We expected to find these groups were highly critical of the technology or with an extensive list of needed advances.<sup>24</sup> Instead we found general satisfaction with the DBMS product they used and frustration with its users. Sometimes the problems appeared to be the overanxiousness of the DBA who had been mandated to put in an application and was trying to install the total corporate system. More often the reasons were problems with the education and training of others outside the DBA on proper approach. Most typically the young group was seeking the responsibility for design and development instead of just the programming of the DDL or DML. This interface with the users, the establishment of educational programs, the convincing of top management was the slowest and most painful effort, yet generally a successful one.

The mature groups had achieved these responsibilities and were established as a necessary component in any new development. Here we did find complaints about technology: a lack of a data dictionary, or better recovery control, or a solution to the on-line update problem. We also found more administrative control problems surfacing. Their concerns about participating in system change decisions and about data control problems were more pronounced. There was a distinct interest in establishing responsibility for the data but at the same time an unwillingness to take the responsibility. They also expressed concern about control over changes to the data base and its structure. Finally they were searching for people with the qualifications and the ability to work in the DBA group.

# CONCLUSION

The DBA is a necessary part of any data base management system effort. No corporation should attempt to form a "corporate data base" without this individual or group to manage its internal operations. The DBA is not however the policy maker that we see in the literature. Corporations do not really view data as a resource nor do they view the DBA as a manager of a valuable corporate resource.

The DBA's we surveyed are highly qualified technical teams or individuals that first bring a new technology to bear on data processing problems and then make the technology operate with the maximum effectiveness possible. They are in a unique position of bridging various applications and have an extraordinarily difficult time bringing the available capabilities to potential users, but they seem to perform this job reasonably well. The DBA group now and in the future needs well qualified technical people who can interface with their users and colleagues. At the same time they need to attract those individuals who have a knowledge of the organization's problems and who can interface with the users from a different perspective.

The DBA is an entity with a future. We see it as a training ground for managers who need a broad view of the company's information system problems, yet who need to have the technical capabilities to manage some user groups. The DBA seems to naturally focus more and more on the technical issues which are within its control and which grow as the position grows. The DBMS technology is being applied to more and more problems in more and more organizations. As the organizations continue to utilize information systems the DBA will provide the data base support necessary, probably on a more expanded technical front.

As far as data base policy is concerned, we see a different individual or group becoming concerned with this problem. The DBA would be the most important implementer of the policy, but not the policy maker. The corporate information managers will need staff or support people who can advise them on policy matters without the vested interest of the DBMS implementation. These policy makers would be concerned with the data resource as one of the corporate resources. They would draw on the DBA group for talent and individuals to move into the advisory wing, but this would probably not be the same group.

The DBA will be involved with technology growth problems as well as the growth of his data base. The systems studied showed that most DBMS systems operate in batch oriented systems. Of those that don't, only a few allow sophisticated on-line update and access to the data base. Most of the systems were not using the operational data for more expanded MIS purposes, either. We expect the demand for on-line update, and the demand for more MIS applications to grow along with the introduction of more sophisticated data base techniques like distributed data bases.<sup>8</sup> The DBA's technology growth will also force the group to become highly technical in nature and highly specialized.

Further research and assistance is needed for the DBA and the user, who will be interfacing more with the DBA in the future. More automated design tools must be developed for the user to be able to present his design to the DBA in a clear manner both at initial development and at operation time. Very few of the DBA's had the time to monitor and optimize the use of the data base. More research into modeling and optimizing would aid in this area. The problem of an MIS still has not been solved in these systems. The data bases become so complex that managers are more lost than ever, and research on an effective way for true management use of complex DBMS systems is needed.<sup>19</sup> Research in the economics of DBMS and their staffing is clearly needed. Organizational issues and administrative structuring seem to be a must for expanded research. For those who claim that data is a resource the last two issues are clearly a critical area to justify that position. Finally, the impact of the new technologies on the DBA must be a constant concern.

# REFERENCES

- ANSI/X3/SPARC, "Study Group on Data Base Management Systems," Interim Report 75-02-08, *FDT—Bulletin of ACM-SIGMOD*, Vol. 7, No. 2, February 1975.

- Auerbach, "Data Base Administrator," Part 1, Doc No. 3-06-04, Auerbach Publishing Company, Philadelphia, 1975.

- 3. Cagan, C., Data Management Systems, J. Wiley, Inc., New York, 1973.

- Canning, Richard G., "The Data Base Administrator's Function," EDP Analyzer Vol. 10, No. 11, November 1972.

- Canning, Richard G., "The Cautious Path to Data Base," EDP Analyzer Vol. 11, No. 6, June 1973.

- CODASYL Programming Committee, "Data Base Task Group Report," ACM, New York, April 1971.

- 7. CODASYL Systems Committee, "Feature Analysis of Generalized Data Base Management Systems," ACM, New York, May 1971.

- Comba, Paul G., "Needed: Distributed Control," Proceedings of the International Conference on Very Large Data Bases, ACM, New York, September 1975.

- 9. Date, C. J., An Introduction to Data Base Systems, Addison-Wesley, Reading MA, 1975.

- De Blasis, J. P. and T. H. Johnson, "Data Base Administrators: Review of Current Recommendations vs. Current Practice," Decision Sciences Department Working Paper 76-03-03, The Wharton School, University of Pennsylvania, Philadelphia, 1976.

- Diebold Research Program, "Organizing for Data Base Management," The Diebold Group Inc., Doc. S16, New York, December 1974.

- 12. Guide-Share Data Base Requirements Group, "Data Base Management System Requirements," Share Inc., New York, November 1970.

- Guide-Share, "The Data Base Administrator," Data Base Administration Project, IBM DB/DC Systems Center, Palo Alto CA, November 1972.

- 14. Johnson, T. H. and J. P. De Blasis, "Data Base Administrators: A Report From Survey," Decision Sciences Working Paper 76-04-04, The Wharton School, University of Pennsylvania, Philadelphia, 1976.

- Johnson, Thomas and J. P. De Blasis, "Very Large Data Base Administration: Organizational Implications From a Survey," Decision Sciences Working Paper 76-04-06, The Wharton School, University of Pennsylvania, Philadelphia, 1976.

- Katzan, Harry, Computer Data Management and Data Base Technology, Van Nostrand, New York, 1975.

- Lyon, John K., "The Role of the Data Base Administration," Data Base Vol. 3, No. 4, ACM-SIGMOD, New York, Winter 1971.

- Martin, James, Computer Data Base Organization, Prentice-Hall Publishing Company, Englewood Cliffs NJ, 1975.

- 19. Morgan, Howard L., "Report on The Very Large Data Base Conference," Communications of the ACM, New York, November 1975.

- Nolan, Richard L., (Editor), Managing the Data Resource Function, West Publishing Company, 2074.

- Sanders, Donald H., Computers and Management, McGraw-Hill, New York, 1975.

- Sanfield, Stuart H., "Data Base Administration: One Approach," Internal Report, Wyeth Laboratories, Philadelphia, 1976.

- Secrest, Richard, "The Data Base Administrator," in *The Information System Handbook* by F. W. McFarland and R. L. Nolan (Ed.), Dow Jones, Irwin, Homewood IL, 1975.

- Weldon, Jay-Louise, "Data Base Administration: Theory and Practice," NYU Working Paper 75-75, New York, 1975.

.

# Data dictionary—More on the impossible dream

by MICHAEL EHRENSBERGER Cincom Systems, Inc. Cincinnati, Ohio

# ABSTRACT

This paper discusses the role of Data Dictionary software in the computing function. It specifically discusses the evolutionary process which brings about the need for a Data Dictionary. It goes on to describe the major components and requirements of Data Dictionary software along with its interaction with data base and the data base administration function.

The advantages, benefits, and potential drawbacks from the misuse of this software are also examined.

# INTRODUCTION

Since the initiation of computing, the data processing industry has been preoccupied with hardware selection, programming techniques, project management, and the like. Computing, like other emerging disciplines, tended to orient its management philosophies around the physical hardware rather than the function the hardware performs. Recently, this concept of computer management has taken on a new meaning. The computing industry is no longer preoccupied with computing; rather, it is concerned with the management of a vital corporate resource—data. For that reason, whenever we speak about management in the context of data processing or computing, it's important that we realize that data is the thing that we're managing.

This paper will deal with the acceptance of a new tool used to control that data—The Data Dictionary. At the same time, it will try to address managerial techniques whereby we can more effectively manage the data within our own department.