VOLUME 26 PART II

# 1964

FALL JOINT COMPUTER CONFERENCE

## VERY HIGH SPEED COMPUTER SYSTEMS

Sponsored by: Association for Computing Machinery Institute of Electrical and Electronics Engineers Simulation Councils, Inc. American Documentation Institute Association for Machine Translation and Computational Linguistics

## **AFIPS** conference proceedings

VOLUME 26 PART II

# 1964

## FALL JOINT COMPUTER CONFERENCE

## VERY HIGH SPEED COMPUTER SYSTEMS

#### Sponsored by:

Association for Computing Machinery Institute of Electrical and Electronics Engineers Simulation Councils, Inc. American Documentation Institute Association for Machine Translation and Computational Linguistics

© 1965 by the American Federation of Information Processing Societies, 211 E. 43rd St., New York, N. Y. 10017. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publishers.

The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1964 Fall Joint Computer Conference Committee or the American Federation of Information Processing Societies.

> Library of Congress Catalog Card Number 55-44701 Spartan Books, Inc. 1106 Connecticut Avenue, N.W. Washington, D. C.

Sole distributors in Great Britain, the British Commonwealth and the Continent of Europe: Macmillan and Co., Ltd. St. Martins Street London W.C.2

## CONTENTS

| · · · · · · · · · · · · · · · · · · ·                                                                                     |                                                              | Page |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|

| Preface                                                                                                                   |                                                              | v    |

| The Keynote Address                                                                                                       | DAVID SARNOFF                                                | 3    |

| The Luncheon Address                                                                                                      | GERARD PIEL                                                  | 13   |

| The Harry Goode Memorial Award Presentation<br>Synopsis<br>The Medalist<br>The Award<br>The Decomposition F. L. Hender    |                                                              | 25   |

| The Presentation, E. L. Harder<br>The Acceptance, Howard Aiken<br>The Presentation to Mrs. Harry Goode, Isaac L. Auerbach |                                                              |      |

| The AFIPS Prize Paper Award                                                                                               |                                                              | 31   |

| TECHNICAL SESSION—VERY HIGH-SPEED                                                                                         | COMPUTERS                                                    |      |

| Parallel Operation in the Control Data 6600                                                                               | JAMES E. THORNTON                                            | 33   |

| An Operating System and<br>Programming Systems for<br>the 6600                                                            | B. B. CLAYTON<br>E. K. DORFF<br>R. E. FAGEN                  | 41   |

| Remote Time Sharing of a Centralized 6600                                                                                 | B. B. CLAYTON<br>E. K. DORFF<br>R. E. FAGEN<br>J. D. JOHNSON | 59   |

| The Model 92 as a Member of the System/360 Family                                                                         | G. M. AMDAHL                                                 | 69   |

| The Overlap Design of the IBM System/360 Model 92<br>Central Processing Unit                                              | T. C. CHEN                                                   | 73   |

| System Aspect: System/360 Model 92                                                                                        | CARL CONTI                                                   | 81   |

| A Philco Multiprocessing System                                                                                           | H. S. BRIGHT                                                 | 97   |

| Index                                                                                                                     |                                                              | 143  |

### PREFACE

Volume 26 of the AFIPS Conference Proceedings is a permanent record of the papers presented at the 1964 Fall Joint Computer Conference. Part I, called AFIPS I, was distributed at the Conference; this book, which is Part II, hence AFIPS II, includes information which, because of its nature and timeliness, could not be made available for publication prior to the time of the Conference.

This departure from the usual pattern of a single volume for the Conference Proceedings reflects the unique character of the sessions whose papers comprise the major portion of this book. In recent Conferences, computer systems have been described in bits and pieces, and properly so. The technical programs were carefully organized to avoid inclusion of material which might have had other than technical interest or motivations. Furthermore, since technical sessions are generally organized around particular areas of specialization, only those specific features of new computer systems which were within the specialty area and which were intrinsically of interest could be presented. This approach, it is believed, is proper and should be maintained, but it has the effect of eliminating overall descriptions of computer systems, as often presented at earlier Joint Computer Conferences.

Consequently, as an experiment, the 1964 FJCC Program Committee under David R. Brown, Program Chairman, decided to sponsor, on an experimental basis, some sessions devoted to computer systems, permitting discussion of an entire system, regardless of whether or not each feature under discussion was unique or new. Attempts were made to present a complete description of each system—the underlying concepts, the hardware, the software, and the problems encountered in arriving at a final design.

The sessions were called Very High Speed Computers, 1964 —The Manufacturers' Point of View. These sessions were organized and chaired by Dr. Sidney Fernbach. The major stipulation placed on each system to be described was that it should be new and that it must be capable of executing approximately one million instructions per second. While the manufacturers' point of view is represented, it is perhaps more relevant to note that this view is shaped predominantly by the designers of each system.

Publishing a post-Conference volume presented the unusual opportunity of including a record of some of the events which transpired there. Hence, the Keynote Address by David Sarnoff and the Luncheon Address by Gerard Piel are also in this book. The opinions advanced by these distinguished individuals should form the basis for further discussion and consideration and are representative of the broadening influence and impact of the information processing field.

Additionally, these pages contain a full account of the background of the Harry Goode Memorial Award and of its presentation to its first recipient, Howard H. Aiken. It is especially fitting that, at this stage in its growth, the information processing field should establish the means for honoring those who make notable contributions to it. In that vein, also, a notation of the awarding of the 1964 FJCC Prize Paper Award is included in this book.

In keeping with the recently completed effort to index the papers presented in earlier Joint Computer Conferences, an index of terms applicable to the papers in this book is included at the end.

As previously noted, AFIPS I is already in publication and has been widely distributed. It contains, as do the other volumes in the series, all of the papers presented at the usual technical sessions. These papers were carefully selected from the excellent material available and cover a wide variety of topics. The Session Chairmen, together with the Program Committee, performed an outstanding function in coordinating the choice and presentation of papers ranging through hardware, software and applications.

In retrospect, the 1964 FJCC was, in many respects, a stimulating experience. Its major permanent contribution, however, is represented by the information contained in the two parts of the Proceedings, and the contributors to these Proceedings are to be commended for their efforts and for the contributions they have made to the rapid advance and diversification of the information processing sciences.

Pichand D. Danaka

General Chairman 1964 Fall Joint Computer Conference

#### KEYNOTE SPEAKER

Brig. Gen. David Sarnoff was the Keynote Speaker for the 26th AFIPS Joint Computer Conference. General Sarnoff is Chairman of the Board of the Radio Corporation of America. His life-long association with science, technology, and industry has resulted in a unique and unparalleled record of accomplishment, and the chronicle of his career is itself representative of many of the significant effects of science on society.

## The Keynote Address THE PROMISE AND CHALLENGE OF THE COMPUTER

#### David Sarnoff

Chairman of the Board Radio Corporation of America October 27, 1964

California has always been synonymous in my mind with innovation and progress, and the past year has given me fresh reason to think so.

Seven months ago, at the NBC studios in Burbank, I had the pleasure of presiding at the inauguration of a new dimension in business communications. By means of two-way, closed-circuit color television, two large assemblies of RCA's shareholders—one in California and the other in New York—were brought into instant visual and verbal communication at our 45th Annual Meeting. Despite their continent-wide separation, the two groups were as effectively unified as though they were meeting under one roof.

Three months later, the sense of participation was almost as direct and immediate with the successful performance of Ranger VII. Again, this was an accomplishment that spanned the continent. RCA cameras and transmitters built in New Jersey, aboard a spacecraft built in California, completed their historic mission at a third point—the moon.

Today, I am glad to be in California and to experience again this sense of participation in progress. It is expressed this time in a gathering of more than 4,000 scientists and engineers from a new and dynamic industry that traces its line of descent directly to the beginning of the art and science of electronics. The modern electronic computer is the precocious offspring of wireless telegraphy and radio telephony, and it is creating a new dimension of progress through the high-speed handling of electronic signals.

Since the birth of RCA in 1919, our principal efforts have been concentrated on transmitting, receiving, and recording information by electronic means. It was natural, therefore, that our scientists and engineers were among the first to begin the study of electronic computing techniques, and I believe their contributions to this new art have been significant.

Six years ago, when we entered the computer field commercially, it was the logical extension of everything we had been doing up to that point. We are making good progress—in technology, programming, service, sales, and revenue—and we will soon announce some significant new product developments which we believe will contribute to the industry's future growth. Last month, we crossed over into the promised land of computer profits. While the trip was rugged, we found the new terrain to our liking, and we expect to stake out a permanent profit claim.

#### THE LESSON OF STANDARDS IN ELECTRONICS

During my 58 years in electronics, I have seen several dynamic industries emerge from conceptual beginnings in the laboratory. The most memorable were radio communications, radio broadcasting, sound-movies, black-and-white television, and color television. While their origins differed in detail, all shared a common experience that has a distinct parallel today in the rise of computers as another major member of the electronics family.

All were intensely competitive from the beginning and have remained so. But they began fulfilling their potential only after agreement had been achieved for technical standards prescribing the kind and quality of service to the public. A pattern for progress was thus fashioned without sacrificing the vital stimulus of competition in developing newer, better, and more economical equipment, and in furnishing more efficient service to the user.

I am convinced that this same process must occur in the computer industry. Even now, the computer is stirring a revolution of the brain just as steam power stirred a revolution of the muscle. The potential effects are almost incalculable—but their full realization calls for the same definition of ground rules that permitted the growth of the older electronics industries.

When sight was added to sound with black-and-white television, the need for technical standards as the basis for orderly growth was clearly recognized. The receiver in the home and the transmitter in the studio had to be built to operate on the same standards. A committee representing all major elements of the industry obtained practical unanimity on such standards as a precondition to the establishment of a public television service. It was on this foundation that black-and-white television grew so phenomenally in the post-war era.

Again, in the early 1950s, the industry underwent the long and difficult process of reaching agreement on a workable service to the public. This time the issue was color television, and two sharply different systems and standards were in dispute. One was based on a mechanical "color wheel" which could produce color images but whose transmissions could not be received by the blackand-white receivers in the nation's homes. It was therefore incompatible with existing equipment. The other was an all-electronic compatible system which could be seen in black-and-white on any TV set in the home. It was evident that, if the incompatible mechanical standards were to be adopted, the industry would be saddled with an inferior system and the public with an inferior, more costly product. To adapt the 10 million sets then in existence in order to receive a degraded picture in black-and-white would have cost the public approximately \$500 million. Without an adaptor, the TV screen would simply go blank.

Clearly, there were many inherent advantages in adopting an electronic rather than a mechanical system of color television. For the industry, the basic issue came to this: should the millions of dollars already invested by television set owners be jeopardized by an incompatible color television system?

Once more, an industry group was formed to draft signal specifications and standards. The result, after 32 months of work, was a complete set of compatible color signal specifications closely following those that had been developed through long years of laboratory research and engineering. These ultimately became the basis for color television in the United States—a business that now stands with data processing in the forefront of the nation's industrial growth.

The industry committee did its work so thoroughly that every subsequent advance in the color television art has been put into service with no change whatever in the original standards.

#### THE NEED FOR STANDARDS IN COMPUTERS

The phenomenal rise of data processing bears certain resemblances to that of color television. It is confronted in similar fashion by a question of compatibility. The investment of the user is again a primary consideration. The issue becomes more acute as the growing computer industry intensifies its competitive drive for new and more ingenious ways to accommodate the user.

From the two-score or so machines in existence barely a dozen years ago, there are now some 17,000 general-purpose computers in the United States alone, and the number is increasing at a rate of more than 500 a month. Within the coming decade, the computer population can increase enormously.

Whether it realizes its full growth potential depends in very large degree, however, on the measures we undertake now to establish the basis for orderly development. The interests of the industry and the needs of the user demand a far greater measure of compatibility and standardization among the competing makes of computers and the means by which they receive and transmit information.

Neither the operators nor the machines we have built for the processing and transmission of information can yet speak to each other in a commonly understood and accepted language. The means of preparing data, of forwarding and entering data in the machine, and of instructing the machine in its use differ sufficiently from one make of equipment to the next so that none can readily accept the product of another.

We function today in a technological "Tower of Babel." There are, by conservative count, more than 1,000 programming languages. And there are languages within languages—in one instance, 26 dialects, and in another, 35 dialects. There are eight computer word-lengths in use. There are hundreds of character codes in being, at a ratio of one code for every two machines marketed. Four magnetic tape sizes are employed with at least 50 different tape tracks and codes.

Standards have not been accepted even for commonly used symbols, instruction vocabulary, or program development procedures. Words which have currency throughout the industry assume different meanings, depending on whether a man has trained in Pasadena, Poughkeepsie, or Camden. We have yet to produce a universally accepted computer glossary.

No means have yet been perfected for a program in one basic language to be run efficiently into computers of different makes. The result has been needless duplication, delay, and waste—both to the manufacturer and to the user—in cost, in equipment, in operating efficiency, and in manpower and skills.

Incompatibility has compelled the manufacturer to build optional choices into peripheral equipment for the input and output of data. It has required him to maintain various types of the same equipment, or to build to a customer's specifications on each order. It has diverted needed engineering and programming talent from the vital work of new product and systems development.

The burden of incompatibility has been even more onerous to the user. It has meant the extra cost of providing hardware and programs to handle the differences between incompatible systems, the cost of extra machine time to process data set for another computer, the cost of training people to do things differently, the cost of not being able to do the job immediately.

Last year, an estimated \$2 billion was spent by American business and government for privately developed computer programs, representing thousands of man-years of effort. Yet, when a change to new equipment is made, portions of this effort must be thrown away because they have no validity to another make of machine, or they are retrievable only at further cost.

I have heard it said that even a degree of standardization and compatibility might inhibit the progress of the art. In my judgment, this argument is without substance. The nature of a computer is such that its operation is governed far less by its internal construction than by the program that is given to it.

The effort to bring order to the flow of computer intelligence need not affect competition either in creating programs or in seeking new generations of increasingly efficient machines. On the contrary, the result could be a greater concentration of effort toward this primary goal.

#### PRELIMINARY STEPS TOWARD INDUSTRY STANDARDS

During the past four years, certain essential preliminary steps have been taken toward industry standards and compatibility, largely under the aegis of the American Standards Association and the Business Equipment Manufacturers Association. Representatives of the industry, of users, and of technical groups have proposed industry-wide standards in such areas as data transmission, information exchange, and character recognition.

Working with a committee of the International Standards Organization representing the computer interests of 13 foreign countries, they have recommended world-wide standards which would make it possible for a credit card or invoice produced in any country to be read by equipment anywhere in the world. Another recommendation, for information interchange, would make it possible for computers in all countries to talk to each other in a common language, when it is adopted and implemented by the manufacturers.

#### FURTHER ACTION ON STANDARDS IS ESSENTIAL

That phrase—when adopted and implemented by manufacturers—is central to the resolution of the problem. For in our country, at least, the action is voluntary, and until these and other standards are put into general use they remain little more than statements of hope.

Today, Western Europe is energetically seeking to close the computer gap and is moving toward the establishment of standards. During the next five years, the use of computers in European industry and government is expected to develop at an accelerating rate. Ten years from now, the foreign market might well equal that of the United States.

Unless we achieve some coherence in our own ranks, we may find ourselves following instead of initiating standards.

All of us, in computer manufacturing, in communications, and among the user groups—at the technical as well as the managerial level—share a common interest in the free interchange of information, and the media and equipment through which it flows.

This demands that we give compatibility the urgent consideration which it merits but which it has not yet received. It requires the wholehearted support by all of us of the standardization work that is now going forward, and implementation of the results with all deliberate speed. It will require that we submerge our differences, through fair and equitable compromise, to achieve greater ends.

I do not suggest that existing systems be discarded. That would be unrealistic as well as costly. Even today's computer has reached maturity in one basic respect: its average time between failures, measured in minutes only a decade ago, is now measured in months. This is a level of operating reliability far beyond that of either the automobile or the airplane.

But new generations of systems are coming, and the time to bring order into progress is now, before they have fully arrived. Standards can be established which, if planned with thought and foresight, can guide us in the future, linking our separate efforts and facilitating the common evolution of our industry. Such standards are indispensable to continued progress.

#### THE COMPUTER'S IMPACT ON THE FUTURE

As the shape of tomorrow's technology takes form, the

volume and accessibility of data stored in the computer will play a decisive role. All information as to what to do, how to do it, and what data to do it with, resides in the memory of the machine. With larger and faster memories there are few limits to the tasks that can be solved or the speed with which they are completed.

The time is soon coming when these memories will be capable of storing up to 100 million bits of information, retrievable in fractional millionths of a second. For external memories, the goal is a trillion bits, possibly advancing later to capacities that are many times greater. By these means we can hope to store all of the information that is presently contained in all the world's libraries.

Tomorrow's standard computers and their peripheral equipment will instantly recognize a handwritten note, a design or drawing which they will store and instantly retrieve in original form.

The computer of the future will respond to commands from human voices in different languages and with different vocal inflections.

Its vocabulary will extend to thousands of basic words in the language of its country of residence, and machines will automatically translate the speech of one country into the spoken words of another.

The computer itself will become the hub of a vast network of remote data stations and information banks feeding into the machine at transmission rates of a billion or more bits of information a second.

Laser channels will vastly increase both data capacity and the speeds with which it is transmitted.

Eventually, a global communications network handling voice, data, and facsimile will instantly link man to machine—or machine to machine—by land, air, underwater, and space circuits.

We will see computer switchboards in space, similar to those presently in operation on the ground, routing in milliseconds any communication to and from virtually any point in the world.

The interlocking world of information toward which our technology leads us is now coming closer to realization. It will be possible eventually for any individual sitting in his office, laboratory, or home to query a computer on any available subject and within seconds to receive an answer—by voice response, in hard copy or photographic reproduction, or on a large display screen.

We will see the emergence of national and global information processing utilities, serving tens of thousands of subscribers on a time-sharing basis. These utilities will accommodate the specialized needs of researchers and engineers, lawyers, medical men, sociologists, or the general needs of the public.

The ordinary citizen may well carry an individual credit card for use anywhere to charge his bank account electronically over a worldwide data communications network that would link up with the telephone systems of all nations.

Such an arrangement could employ simple input units located in all retail establishments—service stations, restaurants, hotels, and other public facilities. These would be in direct and instantaneous communication with a system of banking computers to permit the transfer of funds without the many duplicate bookkeeping and mailing steps that characterize the present credit card system.

A scientist will be able to discuss a problem by two-way television with a colleague anywhere on the globe, and both of them will be able to query a computer at another terminal point for assistance in finding the solution.

Private corporations, many of which will be international in ownership and operation, will have instant access to production and market information from data stations positioned around the globe.

Similar systems will operate on a vastly larger scale for government agencies—military, diplomatic, and economic.

The computer will evaluate and offer alternate courses of action, taking into account all the known and probable variables of a given situation.

This emerging pattern inevitably will set in motion forces of change within the social order, extending far beyond the present or presently predictable applications of the computer. It will affect man's ways of thinking, his means of education, his relationships to his physical and social environment, and it will alter his ways of living.

I believe, for example, that television in a vastly expanded form will become our major instrument for communicating general or specialized information. The same broadband channels that accommodate the TV picture signal can also transmit masses of computer data at ultrahigh speed for instant display.

One day, we will receive our newspapers and technical publications, photocomposed by a computer, by direct display on a wall screen in the home or office. If we wish to retain any part of them for further reading or reference, it can instantly be produced in electrophotographic copy.

As computers become amenable to simple commands, they will become as indispensable to education as the reference library. Indeed, they will become tomorrow's reference library, used by every student from the upper elementary levels through university.

Far from eliminating the need for intense intellectual effort, they will permit young people to undertake mental explorations far beyond the boundaries of the present classroom world.

The computer already is opening areas of knowledge long denied us by the sheer magnitude of the mathematics involved. The implications are no less fundamental for the social and life sciences than for the physical disciplines.

By correlating vast quantities of data and uncovering new relationships we can for the first time obtain significant information on social and human behavior—from the destructive tendencies of some to the learning power of all.

#### THE ULTIMATE CHALLENGE POSED BY THE COMPUTER

The ultimate implication of the computer is that it provides a means of releasing the productive powers of the human brain to an almost limitless degree. Yet the computer imposes as a precondition the sternest discipline to which the mind has yet been subjected.

Even to use the machine, we must apply clear and precise logic to situations which heretofore were assumed to be beyond analysis. We must state precisely what we know or do not know, and what we wish to know.

If we are to develop the computer to its full potential as a reference storehouse of human knowledge, we face the immense intellectual challenge of researching every major field of human activity, of assembling, analyzing, and identifying its documents, and reducing the information to acceptable machine form.

Before the end of the century, I believe that these codification efforts will coalesce into what unquestionably will become the greatest adventure of the human mind. We shall achieve a far more comprehensive understanding than we have today of man and his environment. We shall do so through the orderly compilation of accumulated knowledge and wisdom, beginning with the days of clay tablets and papyrus scrolls. The human horizon will then encompass all that man has ever known, and all that his science will enable him to know.

But how swiftly we scale these heights depends upon the steps we take today to bring order and compatibility to our art. It is an urgent task to which all of us who bear the responsibility for leading this industry into the future must turn our efforts.

It was Socrates who said: "Let him who would move the world move himself." His words have particular pertinence at this time and in this place. For we of the computer industry must surmount today's challenge before we can advance to tomorrow's promise.

Let me conclude on a personal note. Whether your individual role is large or small, the significance and scope of this new science and industry are such that in a genuine sense you are making history. The impact of your knowledge and talents will echo down the corridors of time. The quality and content of life on this planet will be profoundly affected—indeed are already being affected by your labors.

I am grateful for the opportunity to have shared a few thoughts with you.

#### LUNCHEON SPEAKER

The Conference Luncheon Speaker was Gerard Piel, Publisher of Scientific American. As publisher of a magazine with broad appeal to the scientific community, Mr. Piel has contributed to the difficult task of describing and interpreting the sometimes bewildering developments in the fields of science and engineering. He has chosen for the title of his subject, "The Computer as Sorcerer's Apprentice." Mr. Piel is a graduate of Harvard University (magna cum laude) and holds honorary doctorates from Lawrence College, Colby College, Rutgers University, Columbia University, Tuskegee Institute, and the University of Bridgeport. Prior to building the new Scientific American, he was for six years Science Editor of Life magazine.

## The Luncheon Speech THE COMPUTER AS SORCERER'S APPRENTICE

#### Gerard Piel Publisher, Scientific American October 28, 1964

The computer is the engine of this latest phase in the acceleration of the industrial revolution. The role of the computer cannot be measured in the simple terms of the number of computers at work in the American economy or even in the extraordinary variety of functions in which the computer has found work to do—from accounting routines to industrial process control to creative enterprise in mathematics itself. More significantly, computer technology gathers in and brings to intense focus the most diverse discoveries on the frontiers of knowledge—from investigation into the nature of matter to speculations at the foundation of knowledge. It is the agency through which the advance of human understanding now finds its way to the control of natural forces in time intervals that grow shorter year by year and month by month.

Because the time lag between invention and application now diminishes so swiftly, it becomes possible—and necessary—to forecast the ethical, social, and economic implications of this development. Today in our country and in certain other industrial nations, men are compelled to recognize and give assent to a profound transformation in human values. Technological change has already largely eliminated people from production; it has sundered the hitherto socially essential connection of work to consumption. The citizens and the institutions of these nations must accommodate themselves to the law of material abundance: each individual can secure increase in his own well-being only through action that secures increase in the well-being of others.

This novel dispensation stands in contrast to the law of scarcity which, in the words of Alexander Herzen (1812-1870), declares: "Slavery is the first step toward civilization. In order to develop, it is necessary that things should be much better for some and much worse for others; then those who are better off can develop at the expense of the others."

The iron law of scarcity underlies the ethical dilemma of political economy which has sought for nearly three centuries to discover or to rationalize equity in social institutions long ago designed to secure the inequitable distribution of goods in scarce supply. Adam Smith, the first great systematizer of economic theory, was foremost a moral philosopher. In his Theory of Moral Sentiments, published in 1759 and the work which brought him his principal contemporary fame, he traced the roots of moral action to the "passion of sympathy"-"which leads us into the situations of other men and to partake with them in the passions which those situations have a tendency to excite." It was later, in the Wealth of Nations published in 1776, that he undertook to explore "those political regulations which are founded, not upon the principles of justice, but that of expediency, and which are calculated to increase the riches, the power and the property of the state." Against the princely mercantilism of the autocratic continental powers, Smith asserted the labor theory of value: "Labour is the real measure of the exchangeable value of all commodities. . . . Equal quantities of labour at all times and places are of equal value to the labourer. . . . Labour alone, therefore, never varying in its own value, is alone the ultimate and real standard by which the value of all commodities can at all times and places be estimated and compared." In the free play of supply and demand in the open market, the products of human labor found the just and equitable price at which they were to be exchanged. In the market, labor, itself a commodity in consequence of the division of labor, also found its fair price. Under the sure guidance of the "invisible hand" each man could seek his private interest, confident in the knowledge that he thereby secured the public weal.

For the generations that launched the industrial revolution in 18th century England, Adam Smith and his successors in political economy furnished not only the guidelines to practical action but the moral assurance necessary to the taking of action. Before the middle of the 19th century, however, it had become impossible to conceal—in the blight laid upon green England by the carboniferous phase of industrialization—the failure of their enterprise. Benjamin Jowett, Master of Balliol and translator of Plato, spoke for the alienation of the humanities from the sciences when he said: "I have always felt a certain horror of political economists since I heard one of them say that the famine in Ireland would not kill more than a million people, and that would scarcely be enough to do much good."

Even as Jowett wrote, the first phase of the industrial revolution had made such computations obsolete as well as patently immoral. In 1864, the year of the Emancipation Proclamation, mechanical horsepower generated by steam engines in the U.S. economy exceeded for the first time the output of biological horsepower by horses and men. As early as 1900, only 75% of the U.S. labor force was employed as "producers of goods"; more than half of these producers were engaged in farming and the next largest percentage in unskilled labor functions. By 1960, human muscle had been all but eliminated from the production process. The census for that year shows that less than half (46%) of the labor force was now employed as producers of goods; farmers (7%) and unskilled laborers (5%) were approaching statistically negligible percentages of the labor force. More than half of the producers were classified as "operatives," that is, human nervous systems still interposed in process control feedback loops not yet completely closed by electronics.

In the present phase of acceleration, as is well known, the industrial revolution is eliminating nervous systems from the production process. Robots—artificial sensory organs and mechanical controllers linked by feedback circuits—have been taking over from human workers in all of the fluid process industries. In at least 85 plants in the U.S., computers at the center of control networks have transformed the process streams into truly selfregulating systems. The computer and the feedback control loops have now begun a corresponding transformation of the discontinuous processes of the metalworking industry. The same revolution in technology—for example, transcontinental pipeline transportation of fluid commodities under computer and feedback-loop controls—is under way or impends in all of the production sectors of the economy.

During the past decade, blue collar employment in American manufacturing has actually declined, while the output of these industries has nearly doubled. The rate of increase in productivity in the production sectors of the economy, which has averaged 5.6% over the decade and has been accelerating, is grossly understated by productivity figures applied to the entire labor force. These, the figures given widest circulation, have shown an annual improvement of only about 2.5 to 3%.

Until recently, increase in employment in trade and distribution and in the services has compensated for disemployment from production. The computer, however, finds application even more readily in the functions that employ human beings in these sectors. The "white collar" computer, equipped with a typewriter on its input and output side, is conceptually a much simpler organism than the computer equipped with sensory organs and muscles that displaces the blue collar worker. A conservatively estimated million-fold increase in the data-processing capacity of organizations equipped with computers as compared to organizations manned by human beings and assigned to comparable tasks has already been demonstrated in military command and control systems. Although computer technology has just begun to find its way into trade and distribution and the services, increase in employment in these sectors has already begun to slacken. In the private sector of the economy it now barely offsets disemployment from the production industries. During the five-year period from 1957 through 1962, the private enterprise economy generated less than 300,000 additional new jobs.

The creation of new jobs in the economy as a whole has now lagged the growth of the labor force for more than a decade. This is a polite way of saying that the economy is afflicted with a constant and insidious increase in unemployment. Ever since 1952, the rate of unemployment has been larger at the peak of each ripple or boomlet in the economic cycle, and each recession has left a larger percentage of the labor force high on the beach.

Debate continues as to whether the country's rising unemployment is "cyclical" or "structural." Classical economists-and nowadays Keynesian economists are "classical"-assure us that the unemployment is cyclical. They point to the history of the past 60 years in stubborn support of the thesis that the labor-saving effect of technological progress merely frees labor from one task for employment in another. It is conceded that frictions make for unemployment in this turnover of the labor force, especially when progress goes forward rapidly. But sooner or later new jobs, generated by ever greater economic activity and an ever-expanding Gross National Product, soak up the unemployed. By tried and tested and now generally sanctioned counter-cyclical measures-for example, by the recent Federal tax cut-the fluctuations of the system can be damped and the peaks and valleys of unemployment smoothed out. When the Kennedy Administration took office, its official economists were arguing that unemployment at the rate of 4% could be regarded as normal. Despite the tax cut and the prolongation of the present boom, unemployment now ranges above 5%.

Increase in unemployment accompanying expansion of economic activity would seem to indicate that a rising percentage of the unemployment is indeed structural—that people, in other words, are being displaced from the economic system in ever larger numbers by mechanization, more specifically by the computer and its accessory and allied technologies. Consider, for example, the computer industry itself, thus broadly defined. If employment were to expand in any industry during this period of intensive mechanization, one would think first of the payroll of the industry that is doing the mechanizing. What is more, the technology of electronics that furnishes your hardware has been notably, if paradoxically, highly labor-intensive. Until a few years ago, labor would represent up to 60% of the production cost of a piece of electronic hardware. Engineering would constitute the major investment; materials would be a minor cost and capital equipment a negligible item on the balance sheet. In these respects electronics was like the garment industry: a business anybody could get into, providing he had a bright idea and could finance his payroll long enough to get his product on the market. Within the last 10 years, as I need not tell you, electronics has gone solid state. The transistor and the micromodule are even now yielding to the integrated circuit. With this development, acre after acre of work benches at which housewives and high school girls wield pliers and soldering irons has been disappearing. Labor cost is vanishing in the economics of electronics. Material costs have now become significant; engineering and plant costs, transcendent.

In other words, the prevailing relationships among the factors of production in electronics are being turned 180 degrees around. With people being exiled from the computer industry as rapidly as the computer itself is promoting the disengagement of people from jobs in other sectors of the economy, the expansion of this industry will not generate anything approaching a corresponding buildup of its payroll.

It cannot be said, any longer, that the industrial revolution is the same old story. The acceleration of technological change, driven by the accelerating advance of human understanding, reaches to the very heart of the institutions of our society; that is, to the value system upon which those institutions rest.

The unemployment figures present a profoundly misleading measure of the degree to which our capacity to produce material abundance has outrun the capacity of our institutions to secure the distribution of that abundance. It must be reckoned, in the first place, that some eight million persons are employed in the war economy and contribute nothing whatever to the flow of material abundance from the cornucopia of our non-military productive system. If the production workers in the war economy are subtracted from the productive work force, then the percentage employed as producers of goods falls below 40%. But this figure still overstates the truth because most of the goods circulating in commerce and consumed by American citizens are produced by the very much smaller percentage of the labor force that is employed by our most efficient production organizations.

Consider, for example, our farms. Some 85% of the food that moves from the farms to the markets comes from less than one million farms; and the same is true of industry. The few large and efficient corporations in each industry, with their relatively smaller payrolls, produce the overwhelming percentage of our industrial output. If a small minority of our working force is today doing most of the production, then, in the future, we can expect to see an even smaller minority of our working force account for all of the production of goods in our economy. The sorcerer's apprentice has thrown the switch. The great test of our democracy is to find ways to distribute or dispose of the mounting flood of abundance.

Actually, by the kind of improvisations that are so characteristic of democracy, we have had some success in coping with this task starting from the turn of the century. In 1900, 40% of the adults of our country were not employed; that is to say, they were either unemployed or they were not in the labor force. In those good old days, 57% of the adults of the country were employed in the private sector of the economy. Our country still approximated the description it gave of itself in the Declaration of Independence, as a people engaged in the pursuit of happiness—in the pursuit of private interest, either their own or that of their employers. Only 3% of the American people were on the public payroll. In 1960, the same 40% of our population was not employed, either unemployed or not in the labor force. But only 40% of the population was now employed in the private sector of the economy. A full 20% of the American people found their employment either directly on the public payroll or indirectly through the increasingly huge expenditures of governmental agencies for the product and services of private corpoartions—not only in the war economy but in the construction of highways and other major public works ventures. In

other words, one-third of the working force now owes its employment to public expenditure.

Direct employment in the public sector has been increasing at five times the rate of increase in the private sector. During the past five years the public sector generated more than a million of the less-than-1.5 million new jobs in the economy. Since the Federal payroll remained constant during this period, this gain must be credited to state and local governments. It can be declared with pride, furthermore, that the biggest part of the gain was in the payroll of our public education system. This, in turn, may be taken as an indication of the responsiveness of our value system to the evolutionary pressure of abundance.

The national accounts also indicate, however, that the evolution of our social institutions is falling further and further behind the accelerating pace of technological change. It turns out that the magnificent industrial apparatus of America has been producing as much poverty as wealth. Poverty is now officially acknowledged to be the lot of at least 25% of our population. Contemporary American poverty is selective, as Michael Harrington has pointed out. It tends to settle in places where it disappears from sight—hidden away geographically, for example, in Appalachia and in the central cities from which more fortunate members of our society have fled to set up their new settlements in the suburbs. In New York and Chicago, the third generation of families on relief has already begun its blighted existence.

Poverty is selective also with respect to age. Unemployment rates, which for the labor force as a whole are officially acknowledged to exceed 5%, exceed that rate among the youth by at least twice, and among Negro youths it exceeds the rate among white youths by more than twice again. In fact, the prevailing rate of unemployment among Negro youths in the ghettos of our central cities runs from 40 to 50%. The high-school drop-out may spend five years or more in empty limbo between school and his first job. Out of such alienation of so many of our young people has come the rise in juvenile delinguency, and out of the rejection of our Negro youth came the riots in the streets of the north during the past summer. Poverty is equally selective with respect to age at the other end of life. The 40% of our adult population not counted in the labor force now includes several million men and women retired to live on the pittance of monthly social security checks, under contract not to seek gainful employment.

Such are the shameful facts that confront us in the midst of the most prolonged boom since the crash of 1929. Forecasters predict the boom will hold up well into the first quarter of the new year. Against the expectations of myself as well as a few other pessimists, the tax cut has had a strongly stimulating effect on the economic system. It has encouraged a remarkably high rate of investment by industry in new capital equipment—one-third of the investment going to modernization thereby also accelerating the rate of mechanization. Through the action of the familiar Keynesian multiplier, these expenditures on the capital investment side have helped to sustain consumer expenditures at new highs. The argument that fiscal measures may help to reduce unemployment, therefore, finds support in the current movement of the economy. Although these measures and the prolongation of the boom have not actually reduced unemployment below the 5% line, a catastrophic increase in unemployment has been forestalled.

The financial pages all agree, however, that this boom has a terminal date; most set it around the end of the first half of 1965. As the boom runs out, the application of mere counter-cyclical measures—a further cut in Federal taxes, for example—will be of no avail. At the same time, responsible citizens and public officials must face up to the question of the armaments budget. Even in advance of that distant date when we may see some substantial measure of disarmament, the military budget must be cut back. Our country long since acquired the capability of overkill, counting all the targets in China as well as in the U.S.S.R. Yet, with the business cycle turning downward, it will take brave men to cope with the fact that eight million jobs hang directly upon the size of the military budget.

Plainly, the termination of the present boom will require not a tax cut but, on the contrary, a considerable expansion in public expenditure. That expansion has got to come, moreover, in the Federal budget. It is perfectly plain that the payrolls of local governments are not equal to short run challenges; they cannot respond as flexibly and with the same massive effect as Federal expenditures can. The next Administration will be compelled to seek, therefore, a vigorous expansion in Federal expenditures on public works and public welfare.

I don't think I betray the security of the present Administration at this point in the national election campaign by telling you that task forces in every department in Washington are at work on the question of how to spend increased sums on non-military undertakings of the Federal Government. The house economists of the Kennedy Administration observed some time ago that the nation had accumulated a backlog of demand for public works and welfare equal in magnitude to the backlog of demand for consumer goods and capital goods at the end of World War II. According to the National Planning Association, such neglected tasks as urban redevelopment, mass transportation, control of environmental pollution, and restoration of natural resources could absorb additional public investment at a rate of \$60 billion per year. The Arms Control and Disarmament Agency, which is principally responsible for analyzing the prospective impact of disarmament on the economy, predicts an easy transition from huge outlays for warfare to huge outlays for welfare—it points to this backlog of unmet public needs. Soviet economists join their American colleagues in assuring us that capitalism is equal to the task.

All of this is cheering to hear. And it is especially considerate of the Soviet economists to give us their encouragement. But, against a value system that stoutly resists every increase in Federal expenditure except those that carry the absolute sanction of the national defense, any effort to increase public expenditures for public welfare will encounter heavy political opposition. The backward state of our value system is suggested by the following figures describing the condition of our society: America has, in fact, the highest rate of unemployment among all the industrial nations of the world. If the maintenance of adequate nutrition is taken to establish the poverty line, then Department of Agriculture studies show that not one-quarter but one-third of our fellow citizens remain not only ill-fed but ill-clothed and ill-housed as well. Our country has the lowest ratio of public to private expenditures, even with our gigantic war budget. In the public sector—in Federal, state and local budgets—our economy turns over 25% of its Gross National Product. The lowest figure you find in any other industrial society is 30%. America has the lowest rate of public expenditure on public welfare and public works; it comes to something less than 10% for the country as a whole. The lowest figure in any other industrial nation is nearly three times this percentage.

Last spring, the Johnson Administration took its first tentative steps to meet the impending short-run economic crisis. It assembled from already on-going and funded activities of the Federal Government an anti-poverty program. Meanwhile private institutions and individuals were attempting to draw the lines of long-run perspective. One committee of concerned citizens—the self-styled Ad Hoc Committee on the Triple Revolution, which included political economists, historians, former public officials, labor leaders, civil rights workers, and at least two men who have met payrolls—looked rather more deeply into the widening gap between the productive capacity of our industrial system and the effective demand of our consumer economy. In one conclusion to their analysis, they envisioned a day when "Society, through its appropriate legal and governmental institutions, must undertake an unqualified commitment to provide every individual and every family with an adequate income as a matter of right."

The idea of paying people incomes whether they work or not captured attention in newspaper city rooms all across the country. It seems scarcely necessary to add that the idea also won a great deal of unfavorable comment. Setting aside the ephemeral essays of the commentators and pundits who explain the news to the rest of us, the comments of two distinguished public figures are illuminating. The Secretary of Labor, Willard Wirtz, declared: "I think the analysis is right but the prognosis and the prescription is wrong." He added: "I don't believe the world owes me a living and I don't believe it owes anyone else a living."

The other comment comes from a man who was, at the time, candidate for the Republican Presidential nomination. You may recognize his voice. He said: "Our job as Republicans is to get rid of people who will even listen to people who say we should pay people whether they work or not!"

These two statements, taken together, speak faithfully for the austere premises of classical political economy and the tenacity of their grip upon the conscience of many members of our society. Yet the preposterous notion of a guaranteed annual income (or G.A.I., as it has come to be called) has found its way onto the agenda of public issues. Upon deeper reflection over the summer, for example, *Life* magazine returned to the subject for the second time on its editorial page. This time, *Life* conceded that there is technological disemployment: "... experts can't agree whether technological unemployment is growing by 4,000 or 40,000 jobs a week. But it is growing fast enough to see that the seeming logic of the ... plan for free incomes, or instant socialism, may grow too."

Having frightened itself with this prospect, *Life* goes on to say that there can be "more than one radical alternative" and puts forward one of its own: "It is private capitalism, after all, that has brought us to the brink of this daunting affluence, and there is an obvious capitalist solution to the problem that the success of capitalism is creating. It lies in the ownership of the machines and the processes that are destroying the old jobs and creating the new wealth." *Life's* proposal is that the ownership be spread—to everybody! Endorsing the analysis set forth in *The New Capitalists* by Mortimer Adler and Louis Kelso, *Life* would "... guarantee bank loans for new stock acquisitions through a Capital Diffusion Insurance Corporation modeled on FHA."

Let us tarry a moment, here, to contemplate the prospects of instant capitalism. The figures indicate that it would be much more difficult to achieve *Life's* worthy purpose by instant capitalism than by what it calls instant socialism. Consider these disparities in the wealth of our citizenry: As is well known, the bottom 20% of our population gets only 5% of the national income -at the summit of society these percentages are precisely reversed. The bottom 20% thus does poorly enough as income earners. But they show up even worse as capitalists: they hold no liquid assets whatever, except the cash they may happen to have in their jeans. The next 30% of the population above holds liquid assets not exceeding \$500 per family. So the bottom 50% of our society holds less than 3% of our liquid assets. It scarcely need be added that these people have no equity or debt interest in the productive system of our land; for 87% of the people have no such stake in the system. As for real property, 50% of our population have an equity of less than \$1,000 in the homes in which they live. You have to go to the top 10% of income earners before you find people whose assets begin to equal their annual income; you have to go to the top 1% before you find people whose equity and property holdings keep them in the style to which they are accustomed. Plainly the proposal that we seek a more equitable distribution of affluence through the redistribution of ownership presents a more radical alternative than the achievement of that end by the redistribution of incomes.

Life is not alone in its concern with the question of how American society might now go about the equitable distribution of the abundance that overburdens institutions framed for the opposite purpose. That soft-spoken quarterly, *The American Scholar*, the journal of Phi Beta Kappa, devotes most of this quarter's pages to a symposium on "the problems that unite us." Out of six articles in this symposium, four plainly reflect thoughtful consideration of the possibility of guaranteeing incomes to people. 21

I will quote from one author, August Heckscher, a perceptive and sensitive student of American life who served the Kennedy Administration as the President's special assistant in cultural affairs. He begins by saying: "The objections to this approach [that is, the guaranteed annual income] are obvious," and declares: "The very idea of large populations doing nothing but pleasing themselves goes against the American grain." Nonetheless, he comes forward with a radical alternative of his own: "Suppose the monetary rewards of society went, as now, to those who work —and also to those who study. Would this not be a means of assuring their being saved from a bored and barren existence?"

This author then goes on to suggest other ways in which the surplus of human capacity might be soaked up: "At the simplest level one can readily conceive efforts to organize personal or household services more imaginatively so that the work can be done more efficiently. Hours can be made regular and wages can be more nearly commensurate with those earned in other fields." A little later in his analysis, touching on the question of how these increased wages to domestics are to be financed, he comes up with a truly radical alternative: "The salaries . . . could be supplemented [from the public treasury] so as to keep the supply adequate and yet not put the wage out of reach of those who require such services. To supplement in a similar way the rate which people are ready to pay handymen or gardeners could substantially cut relief rolls."

This surely goes beyond either instant socialism or instant capitalism; you might call it instant feudalism. In fact the vision of instant feudalism comes clearer in this author's next, still "more far-reaching" suggestion: "It assumes retirement from the industrial work force at a considerably earlier age than now, together with pensions and social security which would be clearly conceived as 'deferred wages.' . . . From such a pool we could draw a host of talents and services which would make our common life more various, colorful, and pleasant. . . . We can indeed conceive a whole second economy—the economy of craftsmanship and service —growing up alongside the economy of the machine."

Probably, this vision could be more swiftly and effectively realized in certain of the underdeveloped countries where the economy of craftsmanship still exists and where it is threatened by destruction through the infectious spread of the industrial revolution. In America we would have to reconstruct the economy of craftsmanship from the ground up.

Before we start designing Utopias or building the Great Society, it seems to me, we ought to turn to a more searching and possibly painful re-examination of our inexplicit premises—our values. A good way to begin is to ask what we mean by work and what we mean by leisure. With these two words we precipitate the crisis. The proposal of a guaranteed annual income presses the underlying issue in its sharpest and most uncomfortable form.

The objection to the Heckscher vision of the dual craftsmanship-machine society rests upon its hierarchical character, implicit in the compulsion that relates the services of the handyman and the gardener to "us." This defect could, in fact, be cured by the guarantee of an annual income, paid as a matter of right and not in compensation for services rendered. There would then be no reason why the cultures of craftsmanship and machines could not flourish side by side in moral parity. And there could even be a third culture—of leisure, which would include, I hope, dry-fly fishing.

On the other hand, criticism of the G.A.I. notion from the left expresses the dark suspicion that this is a middle class stratagem to tranquilize the proletariat by putting the poor on the dole. Apparently, most people are deeply troubled by the thought of what other people might or might not do with their leisure time!

Except for the attention it has so recently won in public discussion, there is nothing very novel or profound about the idea of a guaranteed annual income. Nor is it so novel in practice. A substantial portion of our society is already living not on a guaranteed and not on a securely annual income but on an income from the public treasury. The people get these incomes on the most humiliating and degrading terms. They get their dole because they present themselves for certification by the appropriate authorities as indigents or paupers; or they get their monthly checks from Uncle Sam because they take an oath not to go back to work and earn more than a stated percentage of their Social Security income. In other words, the American society today offers an income without work to a large number of its members but makes the offer on terms that shame us all. The ugly transactions involved derive their ethical justification from the deep unconscious of societyfrom the institutional memory of the days when the lash drove 80% of the population to work in the fields and mines in order that the few might get on with the high occupations of making history and civilization. The cruelty and inhumanity that persists in our system from those days must be extirpated if we are to resolve successfully the issues that confront us in the tide of abundance set running in America by the present culmination of the industrial revolution.

In my opinion, the issues must be met under two major headings. First, we must recognize that economic and social institutions are man-made and so subject to human will. We can't see the invisible hand because, in truth, it isn't there! The enormous power conferred upon modern societies by industrial technology must be brought under the witting and rational control of democratic institutions still to be perfected.

Second, we must recognize that abundance sets the foundations of an entirely new ethical and moral order. The cultural deprivation that blights the life of a single child in the racial ghettos of our central cities ultimately exacts its cost in the lives of every other citizen. The prolongation of the agony of economic development threatens to destroy the frail parliamentary institutions of India and bring that poverty-stricken nation into the nuclear club under a military dictatorship.

At this turn in human affairs it is plain that each man's well being can increase only to the degree that the well being of all other men is increased. The work of the world still remains in large part to be done. But the instruments to accomplish it are now in our hands. The work that needs most to be done, especially here in America, is in tasks that enrich society as generously as the individuals who undertake them.

### 1964 HARRY GOODE MEMORIAL AWARD

Presentation to Howard Hathaway Aiken at the FJCC—October 28, 1964—Jack Tar Hotel San Francisco

#### Synopsis

The presentation of the Harry Goode Memorial Award to Dr. Howard H. Aiken marked the first time the American Federation of Information Processing Societies signally honored an outstanding contributor to the field of computers and information processing. In conjunction with this first presentation, a Silver Medal was presented to Mrs. Harry H. Goode in recognition of the late Mr. Goode's invaluable contributions to the information processing sciences.

#### The Medalist

For more than 25 years Howard H. Aiken has given continuing momentum to the growth of computer technology. As a student, he proposed an automatic calculating machine and collaborated with IBM engineers in the design of Mark I, the first large-scale, automatic digital computer, completed in 1944. In the following years, Dr. Aiken was instrumental in perfecting computers, adapting them to nonnumerical applications, and in guiding students to productive careers in the computer sciences.

Howard Hathaway Aiken received the S.B. degree in electrical engineering from the University of Wisconsin in 1923. From 1923 to 1932 he was associated with Madison Gas and Electric, Westinghouse, and the Line Material Company, and he studied physics at the University of Chicago. He received the S.M. in physics in 1937 and the Ph.D. in 1939 from Harvard University. In 1941, after two years as instructor in physics, he became an associate professor in applied mathematics.

Following Mark I, Dr. Aiken built three other machines: Mark II, in 1947, largely an electromechanical machine, was operable not only as one machine solving one problem but as two machines solving two problems simultaneously; Mark III, completed in 1950, utilized magnetic tape drives and magnetic drums to store binary-coded decimal numbers and instructions; Mark IV, completed in 1952, relied heavily on solid-state components. It included magnetic core storage, selenium rectifiers to perform all arithmetic and control functions, index registers, and an encoding device which permitted the writing of programs in an algebraic notation quite similar to that normally used.

With the practicality of computers firmly established, Dr. Aiken concentrated on establishing sound scientific bases for the arts of computing and machine design, investigating nonnumerical applications and establishing an educational program in the computing field. Dr. Aiken gave his first course in the computer field at Harvard University in the academic year 1947-48. Largely through his leadership, Harvard became one of the first universities to have extensive graduate and undergraduate programs leading to degrees in the computer field.

Dr. Aiken encouraged his students to seek adequate mathematical methods for investigating the functional behavior of electronic control circuits and to venture into such fields as control systems engineering, data processing, mathematical linguistics, and applied discrete mathematics.

Dr. Aiken was Director of Harvard University's Computational Laboratory for twelve years. He is presently Professor Emeritus of Harvard University and Director of the University of Miami's Institute of Informational Science. Dr. Aiken's achievements have received international recognition. He was one of the first members of the National Research Council's Committee on High-Speed Calculating Machines. He is a Fellow of the American Academy of Arts and Sciences, the Association for the Advancement of Science, and of the Institute of Radio Engineers, and he is a member of the Swedish Ingeniors Vetenskaps Academien. In France, he is a Chevalier de la Legion d'Honneur, and in Spain, he is a Consejero de Honor del Consejo Superior de Investigaciones Cientificas. He received the Testimonial of Eminent Professional Services from the University of Wisconsin, his alma mater, and he holds an honorary doctorate from Germany's Technische Hochschule at Darmstadt. He was awarded Belgium's Officer's Cross of the Order of the Crown, the U.S. Navy's Distinguished Public Service Award, and the U.S. Air Force's Decoration for Exceptional Civilian Service.

#### The Harry Goode Memorial Award

Harry H. Goode, born in New York City on July 1, 1909, was a pioneer and leader in the field of system engineering. One of the first scientists to fully comprehend the powers and abilities of computers, he formulated many principles of system engineering and developed techniques for the design, analysis and evaluation of large-scale systems. He was instrumental in initiating early systems projects, including the Typhoon and Whirlwind computers at MIT. Among other activities, he participated in the study which led to the Bomarc missile, and he conceived and developed the Air Defense Integrated System Project.

In addition to his scientific contributions, Mr. Goode ad-

vanced the information processing sciences through his teaching at the University of Michigan and his many publications on statistics, stimulation and modeling, vehicular traffic control, and system design. One of his most important achievements was coauthoring the first book on *System Engineering* which classified and regularized systems and their design processes.

Mr. Goode, statistician, mathematician, electrical and chemical engineer and professor, was a member of the IRE (now IEEE) professional group on electronic computers and of the computer advisory committee of the Society of Automotive Engineers. As chairman of the National Joint Computer Committee, he led this group in creating an expanded and strengthened organization, AFIPS, to help meet the needs arising from the rapidly growing information processing technology. Mr. Goode died in an automobile accident before AFIPS was formally chartered.

The Harry Goode Memorial Award has been established in recognition and appreciation of Mr. Goode's invaluable contributions to the information processing sciences. Its purposes are to encourage further development of the field and to acknowledge and honor outstanding contributions to the information processing sciences.

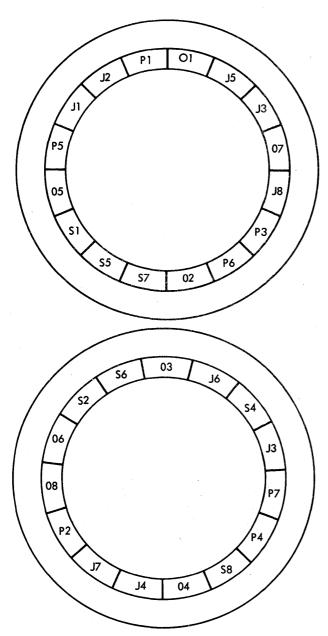

The Scribe Accroupi, the famous Egyptian statue in the Paris Louvre, inspired the noted European sculptor, Andras Beck, in the conception of the Harry Goode Memorial Medal. In the sculptor's own words, *The Scribe* allegorizes man's intellectual effort, while the AFIPS emblem symbolizes the machine that aids and supports human effort in this field. The arrow is the signature of the Hungarian-born sculptor, former Professor of Sculpture at the Budapest Academy of Fine Arts, who has resided in France since 1957.

#### The Award Presentation to Howard Aiken

#### E. L. Harder

#### Chairman, American Federation of Information Processing Societies

Shortly after the formation of AFIPS from the Joint Computer Committee, work started on the creation of an award which could be bestowed on the very few individuals who had made the greatest contribution to this profession. This award, which now exists, and the first presentation of which will be made today, has been named the Harry Goode Memorial Award because of the unique part played by the late Harry Goode in the organizing and teaching of the computer and system engineering science and because of his outstanding leadership in creating this American Federation of Information Processing Societies itself.

Very fittingly, the Committee has selected as the first recipient the one man in the world who earliest, and with great vision and foresight and enormous strength of purpose and perseverance, led the way straight to the goal of the computers that we have today. This man is Howard Aiken and he is here today, although his fame is so great that you might expect he only existed in fairy tales. Also, this is a very special day in that Mrs. Harry Goode, the wife of the man in whose name this medal stands, is here to witness this first occasion on which it will be bestowed—on this illustrious pioneer of today's computers.

The place that Harry Goode held in the estimation of his fellows, his impact on the science of system engineering and of information processing, can hardly be more forcibly conveyed to you than by the fact that his fellows have chosen to engrave, with his image, this medal signifying the highest honor that the computer societies of America are able to give to any man.

Now, let me tell you about the man who has been selected. As with all legendary characters, you all know something about him, but let me put some of the pieces in perspective—something which is getting a little easier to do as the years roll on. For now we can associate his work not only with an important scientific venture but with a great profession and a great industry which he played a very leading part in creating. This very association, AFIPS, exists for the purpose of exchanging technical information upon which the progress of our profession and of our industries and scientific institutions depends. It exists for the purposes to which Howard Aiken devoted a good part of his life and in which he led the way. He set a pattern in visualizing what needed to be done and what was possible, in persevering in doing it, and in seeing to it, in a very real way, that this technology became available to humanity. This he did through organizing the teaching of it in the universities and by gathering together groups from all over the world at Harvard to work personally with him in the carrying through of the Mark I, Mark II, Mark III, and Mark IV programs. As you travel the world over today, you encounter leaders in the computer profession and in the industries who got their early start through an invitation to come to Harvard and work with Dr. Aiken on the development of these machines. This will give you some idea of the breadth of the vision and of the force and vigor with which it was carried out.

Dr. Howard Aiken, Professor Emeritus of Harvard University, you have been honored by many scientific institutions and by many countries, including your own. It is now the computer and information processing profession itself, which you helped so greatly to create, that wishes to do you honor. It is the very great privilege of the American Federation of Information Processing Societies to bestow upon you, as first recipient, the Harry Goode Memorial Award—the citation for which I would now like to read in the presence of these several hundred members of this new profession—of *your* profession.

#### The Citation for the award follows:

#### To HOWARD HATHAWAY AIKEN

for his original contribution to the development of automatic computers that led to the first large-scale, general-purpose, automatic digital computer ever to be put into operation; for his continuous work in the field of digital computers as an Engineer;

and for the knowledge and inspiration imparted to many as a Teacher.

#### DR. HOWARD AIKEN

Recipient of the Harry Goode Memorial Award to be made at the 1964 Fall Joint Computer Conference in San Francisco.

#### The Reply of the Medalist

Dr. Howard Aiken