- 1. 1951 Joint AIEE-IRE Computer Conference, Philadelphia, December 1951

- 2. 1952 Joint AIEE-IRE-ACM Computer Conference, New York, December 1952

- 3. 1953 Western Computer Conference, Los Angeles, February 1953

- 4. 1953 Eastern Joint Computer Conference, Washington, December 1953

- 5. 1954 Western Computer Conference, Los Angeles, February 1954

- 6. 1954 Eastern Joint Computer Conference, Philadelphia, December 1954

- 7. 1955 Western Joint Computer Conference, Los Angeles, March 1955

- 8. 1955 Eastern Joint Computer Conference, Boston, November 1955

- 9. 1956 Western Joint Computer Conference, San Francisco, February 1956

- 10. 1956 Eastern Joint Computer Conference, New York, December 1956

- 11. 1957 Western Joint Computer Conference, Los Angeles, February 1957

- 12. 1957 Eastern Joint Computer Conference, Washington, December 1957

- 13. 1958 Western Joint Computer Conference, Los Angeles, May 1958

- 14. 1958 Eastern Joint Computer Conference, Philadelphia, December 1958

- 15. 1959 Western Joint Computer Conference, San Francisco, March 1959

- 16. 1959 Eastern Joint Computer Conference, Boston, December 1959

- 17. 1960 Western Joint Computer Conference, San Francisco, May 1960

- 18. 1960 Eastern Joint Computer Conference, New York, December 1960

- 19. 1961 Western Joint Computer Conference, Los Angeles, May 1961

- 20. 1961 Eastern Joint Computer Conference, Washington, December 1961

- 21. 1962 Spring Joint Computer Conference, San Francisco, May 1962

- 22. 1962 Fall Joint Computer Conference, Philadelphia, December 1962

Conferences 1 to 19 were sponsored by the National Joint Computer Committee, predecessor of AFIPS. Back copies of the proceedings of these conferences may be obtained, if available, from:

- Association for Computing Machinery, 14 E. 69th St., New York 21, N. Y.

- American Institute of Electrical Engineers, 345 E. 47th St., New York 17, N.Y.

- Institute of Radio Engineers, 1 E. 79th St., New York 21, N. Y.

Conference 20 and up are sponsored by AFIPS. Copies of AFIPS Conference Proceedings may be ordered from the publishers as available at the prices indicated below. Members of societies affiliated with AFIPS may obtain copies at the special "Member Price" shown.

| Volume         | List<br>Price           | Member<br>Price        | Publisher                                                                                                                                                                 |

|----------------|-------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20<br>21<br>22 | \$12.00<br>6.00<br>8.00 | \$7.20<br>6.00<br>4.00 | Macmillan Co., 60 Fifth Ave., New York 11, N. Y.<br>National Press, 850 Hansen Way, Palo Alto, Calif.<br>Spartan Books, 6411 Chillum Place, NW, Washing-<br>ton 12, D. C. |

The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1962 Fall Joint Computer Conference Committee or the American Federation of Information Processing Societies.

Library of Congress Catalog Card Number: 55-44701

Copyright © 1962 by American Federation of Information Processing Societies, P.O. Box 1196, Santa Monica, California. Printed in the United States of America. All rights reserved. This book or parts thereof, may not be reproduced in any form without permission of the publishers.

> Manufactured by McGregor & Werner, Inc. Washington, D. C.

### CONTENTS

Page

Page

| v        | Preface                                                                             |                                                                 | v        |

|----------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|

| 1        | Processing Satellite Weather Data - A Status Report -<br>Part I                     | Charles L. Bristor                                              | 1        |

| 19       | Processing Satellite Weather Data - A Status Report -<br>Part II                    | Laurence I. Miller                                              | 19       |

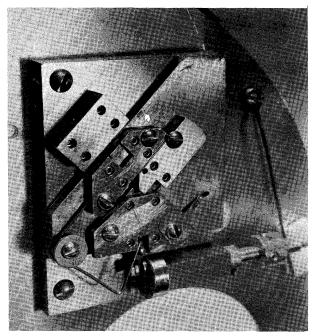

| 27       | Design of A Photo Interpretation Automaton                                          | W. S. Holmes<br>H. R. Leland                                    | 27       |

| 36       | Experience with Hybrid Computation                                                  | G. E. Richmond<br>E. M. King                                    | 36       |

| 00       |                                                                                     | R. Gelman                                                       | •••      |

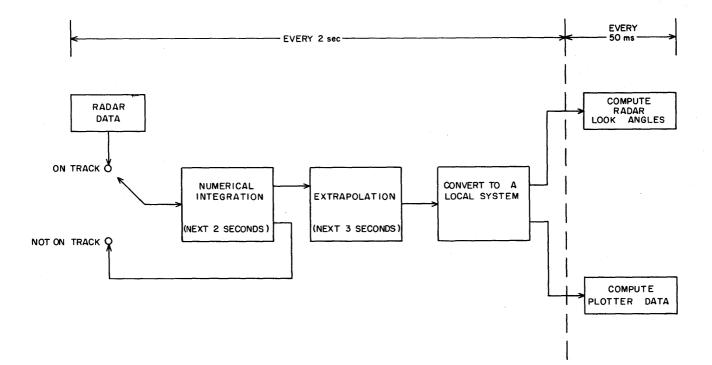

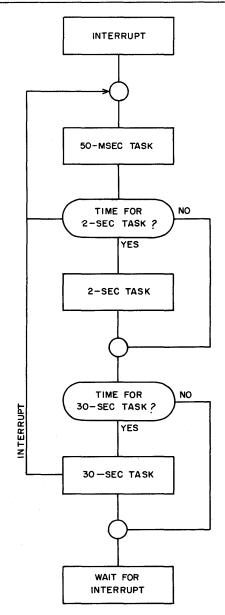

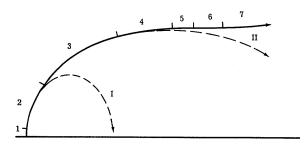

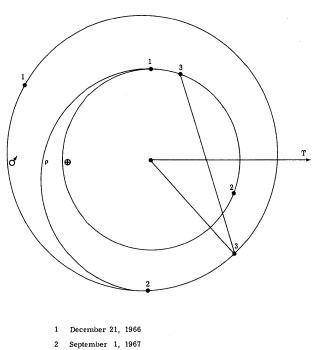

| 44       | Data Handling at an AMR Tracking Station                                            | K. M. Hoglund<br>P. L. Phipps                                   | 44       |

|          |                                                                                     | E. J. Block                                                     |          |

|          |                                                                                     | R. A. Schnaith<br>J.A. Young                                    |          |

| 56<br>71 | Information Processing for Interplanetary Exploration<br>EDP As A National Resource | T. B. Steel, Jr.                                                | 56<br>71 |

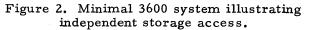

| 73       | Planning the 3600                                                                   | Charles T. Casale                                               | 73       |

| 86       | D825 - A Multiple-Computer System for Command &<br>Control                          | James P. Anderson<br>Samuel A. Hoffman<br>Joseph Shifman        | 86       |

|          |                                                                                     | Robert J. Williams                                              |          |

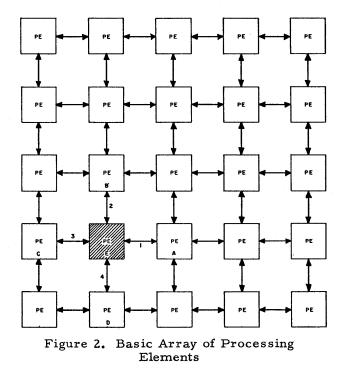

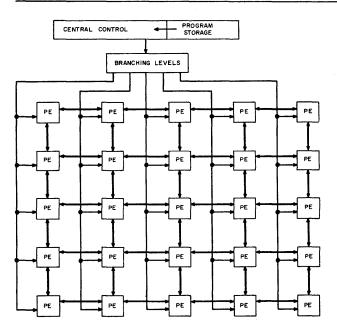

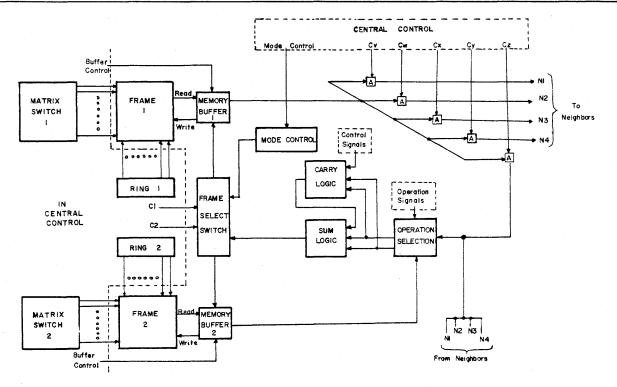

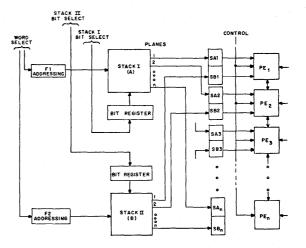

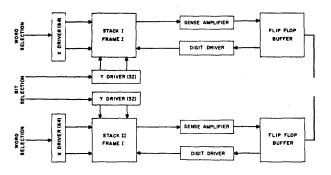

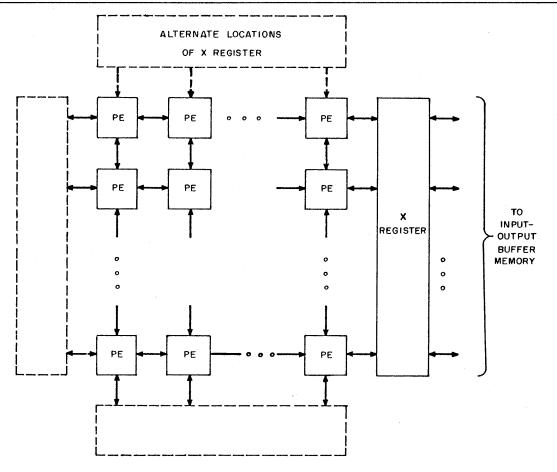

| 97       | The Solomon Computer                                                                | Daniel L. Slotnick<br>W. Carl Borck                             | 97       |

|          |                                                                                     | Robert C. McReynolds                                            |          |

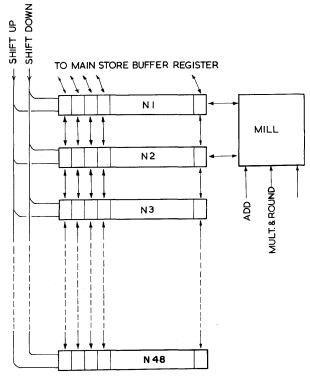

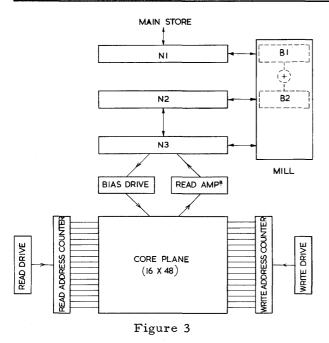

| 108      | The KDF.9 Computer System                                                           | A. C. D. Haley                                                  | 108      |

| 121      | A Common Language for Hardware, Software, and<br>Applications                       | Kenneth E. Iverson                                              | 121      |

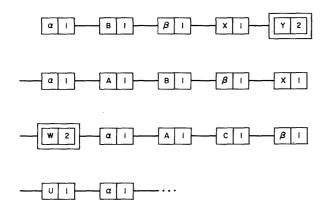

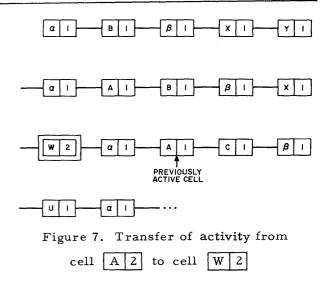

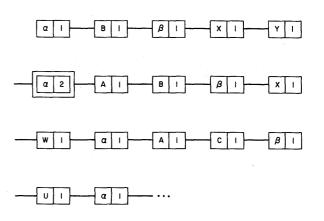

| 130      | Intercommunicating Cells, Basis for a Distributed<br>Logic Computer                 | C. Y. Lee                                                       | 130      |

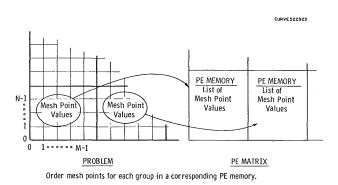

| 137      | On the Use of the Solomon Parallel-Processing<br>Computer                           | J. R. Ball<br>R. C. Bollinger<br>T. A. Jeeves                   | 137      |

|          |                                                                                     | R. C. McReynolds<br>D. H. Shaffer                               |          |

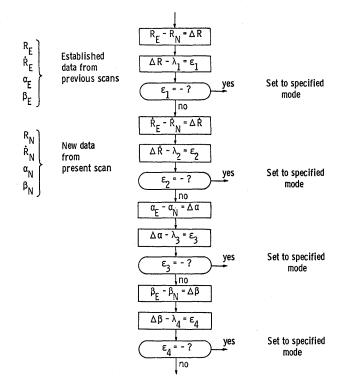

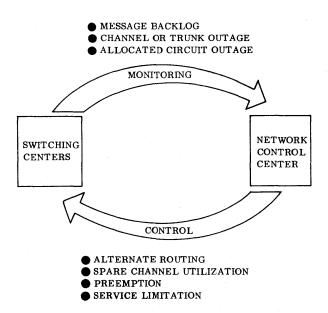

| 147      | Data Processing for Communication Network Mon-<br>itoring and Control               | D. I. Caplan                                                    | 147      |

| 154      | Design of ITT 525 "Vade" Real-Time Processor                                        | Dr. D. R. Helman<br>E. E. Barrett<br>R. Hayum<br>F. O. Williams | 154      |

#### Page Page 161 On the Reduction of Turnaround Time H. S. Bright 161 B. F. Cheydleur 170 Remote Operation of a Computer by High Speed G. L. Baldwin 170 Data Link N. E. Snow 177 Standardization in Computers and Information C. A. Phillips 177 Processing R. E. Utman 184 **High-Speed Ferrite Memories** H. Amemiya 184 H. P. Lemaire R. L. Pryor T. R. Mayhew 197 Microaperture High-Speed Ferrite Memory R. Shahbender 197 T. Nelson R. Lochinger J. Walentine 213 Magnetic Films-Revolution in Computer Memories C. Chong 213 G. Fedde 225 Hurry, Hurry, Hurry Howard Campaigne 225 229 The Case for Cryotronics? W. B. Ittner, III 229 232 **Cryotronics - Problems and Promise** Martin L. Cohen 232234 Some Experiments in the Generation of Word and Gerard Salton 234**Document Associations** 251 D. F. Gorman 251 A Logic Design Translator J. P. Anderson 262 Comprotein: A Computer Program to Aid Primary Margaret Oakley Dayhoff 262 **Protein Structure Determination** Robert S. Ledley 275 William H. Dodrill Using Gifs in the Analysis and Design of Process 275 Systems A Data Communications and Processing System 280 280 M. D. Balkovic for Cardiac Analysis C. A. Steinberg P. C. Pfunke C. A. Caceres 285 Gilbert Kaskey 285 **Cluster Formation and Diagnostic Significance in Psychiatric Symptom Evaluation** Paruchuri R. Krishnaiah Anthony Azzari 304 Spacetracking Man-Made Satellites and Debris Robert W. Waltz 304 B. M. Jackson 310 310 List of Reviewers 1962 Fall Joint Computer Conference Committee 311 311 313 American Federation of Information Processing 313

Societies (AFIPS)

### PREFACE

The theme of the 1962 Fall Joint Computer Conference is <u>Com-</u> <u>puters in the Space Age</u>. Today there is a two-way street in which computing equipment has contributed vitally to the success of space age technology, but the space-age demands have had their major effects on the design of computers. Of these we can readily discern three outstanding results: (1) development of more efficient interfacing between man and machine, (2) radical reduction of the size of systems, and (3) the maturing of the theory and implementation of cooperative systems, including multi-point operating complexes.

Naturally these achievements are irrevocably to be reflected in the stationary equipment that benefits business and science. We already know that for the purposes of the Space Age, computing equipment is to provide facility for command-decision and for control of a new order of complexity. But we are just becoming aware of the products of this progress. The social implications of advances in the precise selection of information via recursive interplay between man and machine—though barely perceptible at the present time—are rapidly assuming major influence on the structure of the near future.

Altogether, the interaction of the space age and computer technologies has brought about a rich growth in new and potent national resources. Indeed, the record of the United States in the field of information and data processing systems is pre-eminent in the present world. It is helping therefore very directly to give us pre-eminence in space.

> J. Wesley Leas Chairman 1962 Fall Joint Computer Conference

### PROCESSING SATELLITE WEATHER DATA -A STATUS REPORT - PART I

Charles L. Bristor U. S. Weather Bureau Washington, D. C.

#### SUMMARY

Less than 500 radiosonde observations are available for the current twice daily three dimensional weather analysis over the Northern Hemisphere-a coverage far less than is required for short term advices and for input to numerical prediction computations. Global observations from operational satellites as a complement to existing data networks show promise of filling this need. TIROS computer programs now being used for production of perspective geographic locator grids for cloud photos, and other programs being used to calibrate, edit, locate and map infrared radiation sensor measurements, have provided a background of experience and have indicated the potentialities of a more automated satellite data processing system. The tremendous volume of data expected from the Nimbus weather satellite indicates the need for automatic data processing. Each pass around the earth will produce ninety-nine high resolution cloud pictures covering about ten percent of the earth from pole to pole and infrared sensors will provide lower resolution information but on a similar global basis. Indications are that machine processing of the 280-odd million binary bits of data from each orbit can materially reduce the human work load in producing analyzed products for real time use. The main programming packages in support of the presently developing automatic data processing systems are explained under ingestive,

digestive, and productive headings. Tasks under these headings are explained for both the photo and infrared data. The individual program modules and subroutines are discussed further in an appendix. Reference is made to the second part of this report which expands on the logical design of the digital and non-digital data handling system complex and extends the discussion into data rates, command and control concepts and the executive program which manages the overall process.

#### INTRODUCTION

The need for more meteorological data is an old refrain which is almost constantly being revived. Why do we always desire more data? Among the many very good answers to this question are some which are pertinent to the subject of meteorological satellites. A most generalized answer might be expressed in two parts:

1. because as the scope of human activities increases, new applications of weather information arise and new needs for meteorological advice are generated and

2. because potential economic gains provide a tremendous impetus for attempting to improve the quality and scope of our present weather services.

Within the category of the first answer one may cite the expansion of global air travel over routes that are practically devoid of weather observations of any kind and the similar deployment of air and sea defense forces to remote areas. Even the man in space program is generating a need for global weather information. In the thirties and into World War II a marked expansion of weather observing networks took placemainly through expansion of weather communications to communities where observations facilities could be installed. Because of communications and logistics costs, this type of expansion cannot take place indefinitely to fulfill the ever growing need for detailed observations on a global scale. However, within the scope of the first answer, such a global network would be extremely valuable merely as a means of providing current weather information and very short term warnings and advisories.

Beyond immediate operational advice is the need implied by the second answer—the problem of weather prediction. The American Meteorological Society (1962) has recently restated its estimate of current skills in weather forecasting.

"...For periods extending to about 72 hours, weather forecasts of moderate skill and usefulness are possible. Within this interval, useful predictions of general trends and weather changes can be made...."

Few would deny the economic importance and increased application of more precise 3-day forecasts.

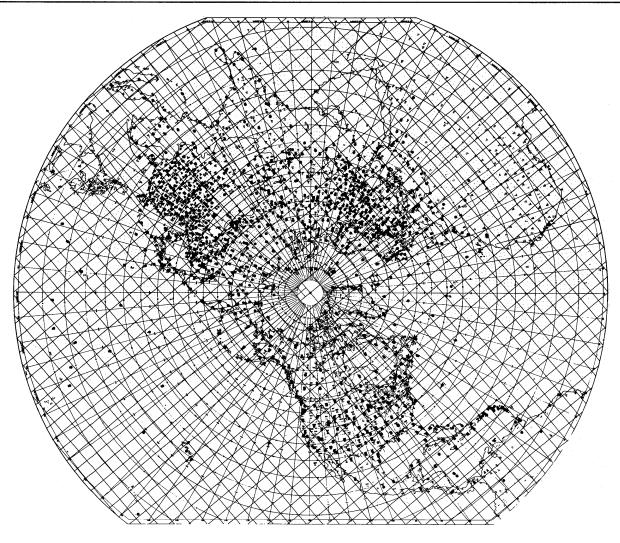

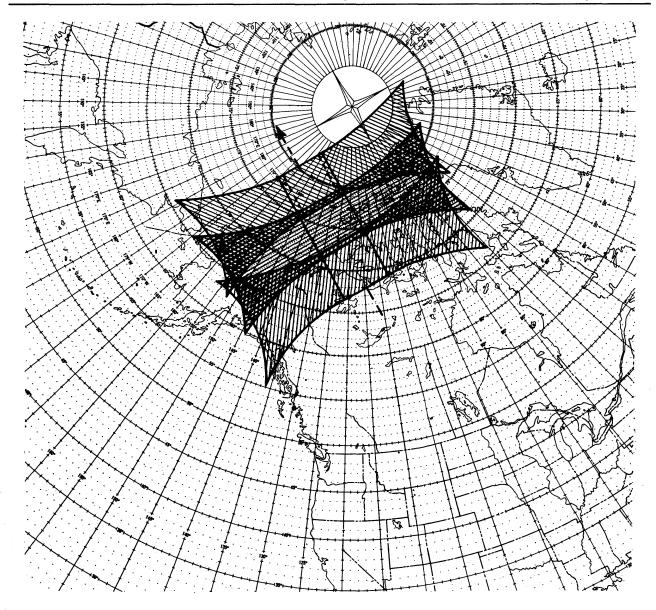

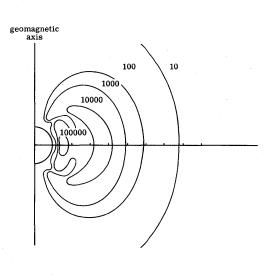

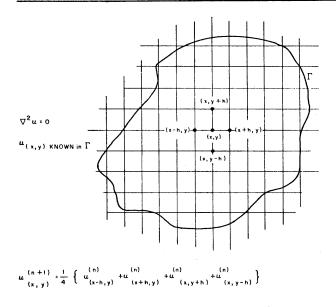

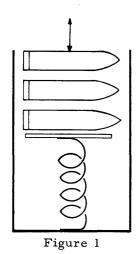

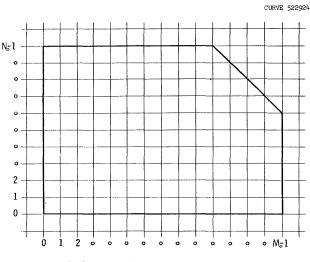

Since the mid-fifties numerical weather prediction has had a significant influence on the level of skill in weather forecasting generally. The method involves a mathematical description of the atmosphere in three dimensions utilizing the hydrodynamic equations of motion and the laws of thermodynamics. The partial differential equations of such a "model" are arranged in a prognostic mode such that only time dependent partials remain on the left side. The finite difference version of such an equation set is then integrated in short time steps to produce prognostic images of the various data fields which served to describe the initial state of the fluid. Phillips (1960) has summarized the current view which delimits the potential of numerical weather prediction-to the extent that lack of observations prevents adequate description of the atmosphere on a global basis. Figure 1 indicates the present network of observing stations which provide the current three dimensional description of the atmosphere together with a grid overlay indicating intersections at which information is required concerning the current state of the fluid in order that the finite difference equations may be integrated. Obviously a poorly distributed collection of less than 500 observations cannot adequately establish values for nearly two thousand grid points. Areas the size of the United States are indicated without any upper air soundings whatsoever. The situation in the Southern Hemisphere is much worse.

This brief discussion of the meteorological data problem points up the need for a detailed global observational network and offers the real challenge to meteorological satellites. Can indirect sensing via satellite fill the need for global weather data? D. S. Johnson (1962) has summarized the meteorological measurements carried out thus far by satellites and discussed others planned and suggested for the future.

Indications are that, whereas satellite observations will likely never supplant other data networks, they hold great promise in providing complementary data on a truly global basis. Limited experience with satellite weather data already obtained is very encouraging.

The following is a description of current efforts in processing the ever growing volume of this data. First, limited computer processing of TIROS data is discussed. The latter portion of this report and the second paper in this two part series describe in some detail the current status of computer programming in support of the truly automated real time data processing systems under construction for the Nimbus satellite system.

#### EXPERIENCES WITH TIROS

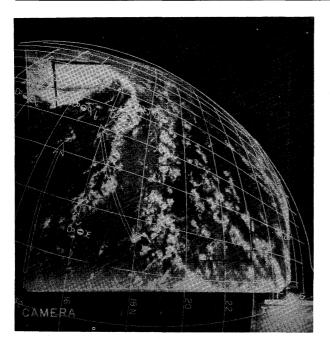

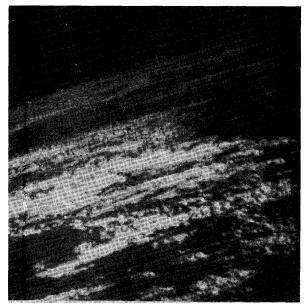

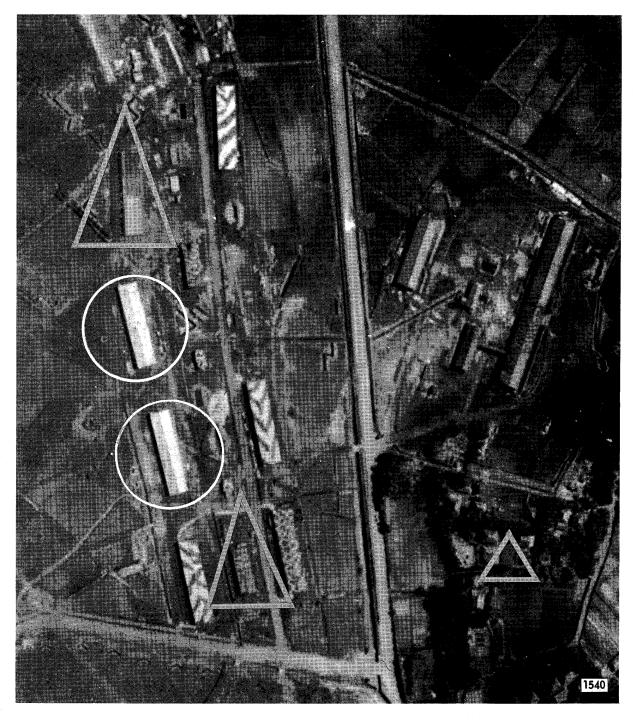

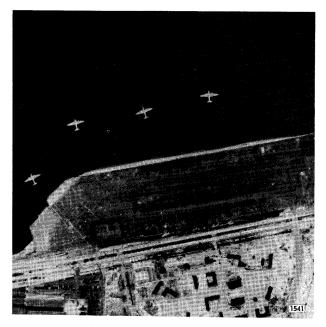

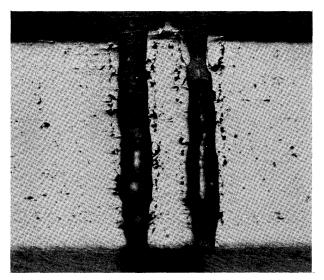

Since April, 1960 cloud photos from TIROS satellites have been made available to the meteorological community on an intermittent operational basis. Details of the satellites' construction including its slow scan cameras have been given elsewhere along with an account of certain difficulties in geographically locating the cloud photos because of meandering in the spin axis (NASA - USWB, 1960). A cloud photo sample is presented in Figure 2. Even without a meteorological background, one would likely concede, on the basis of intuition, that such cloud patterns could provide

Figure 1. Northern Hemisphere map showing upper air reporting stations and computation grid used in objective weather map analysis and numerical prediction. The Weather Bureau's National Meteorological Center uses a somewhat denser grid of more than 2300 points. Less than 500 of these reports are routinely available for specification of quantities at the grid points.

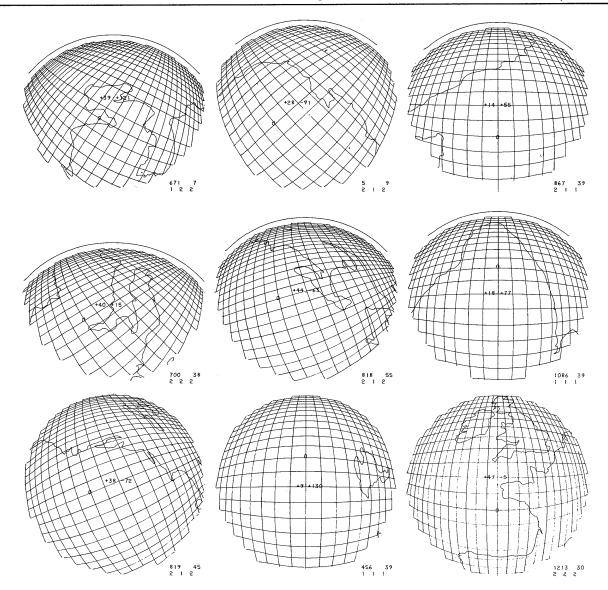

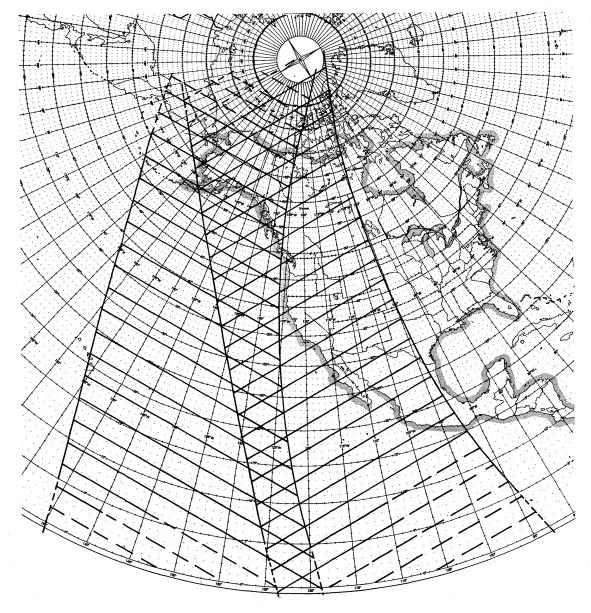

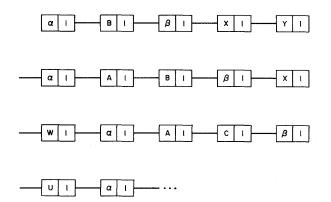

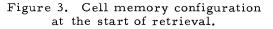

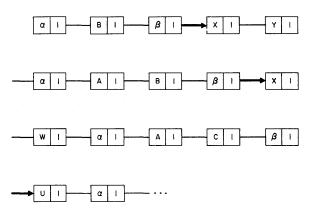

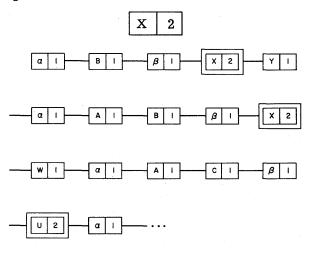

valuable observational evidence concerning the state of the atmosphere. A considerable research effort is now going on in an effort to extract quantitative information from such images (NASA - USWB, 1961). For the present, computer processing has been confined largely to the production of geographic locator grids as an aid to further interpretation of the cloud patterns. The locator grid superimposed on the picture in Figure 2 and the sample grids shown in Figure 3 are produced at a rate of 10 seconds per grid on the IBM 7090 (Frankel & Bristor, 1962). Line drawn output is produced on an Electronic Associates Data Plotter or, alternately, by General Dynamics High Speed Microfilm Recorder.

Input for each grid includes latitude and longitude of the sub-satellite point, altitude of the satellite as well as azimuth and nadir and spin angles which describe the attitude and radial position of the camera with respect to the earth. An auxiliary program is required for the production of image to object ray distortion tables. These tables correct for symmetric and asymmetric distortions due to the lens and the electronics of the system and are produced from pre-launch calibration target photos taken through the entire camera system. An additional feature of the gridding program is the large dictionary of coastline locations from which transformations to the perspective of the image

#### 4 / Processing Satellite Weather Data - A Status Report - Part I

Figure 2. Sample cloud picture with perspective geographic locator grid. This photo, taken by TIROS III, shows hurricane Anna near 12°N, 64°W (lower left) on July 20, 1961 together with large streamers projecting toward another vortex pattern to the east (right).

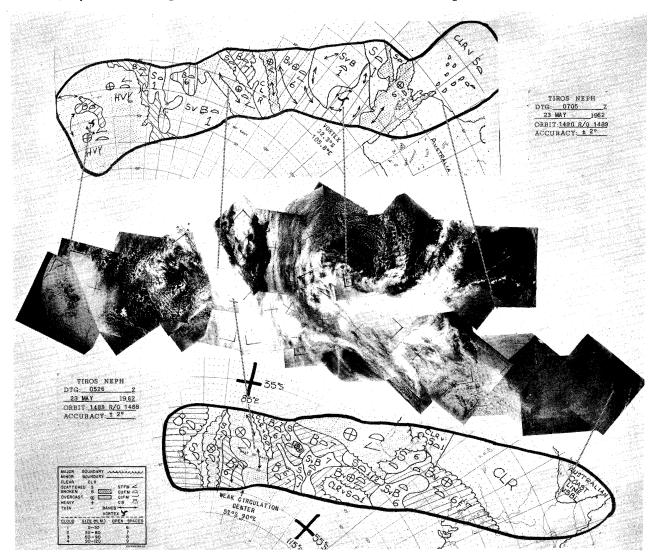

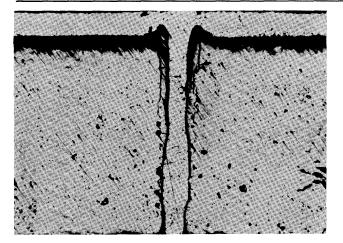

are made as an aid in mating the cloud image and grid. Some 10,000 such grids have been produced thus far for selected cloud photos taken by TIROS I and TIROS III and are available in an archive, along with the pictures, for research applications. A somewhat less detailed but similar gridding procedure is being utilized on a smaller Bendix G-15 computer at the TIROS readout sites for the current real time hand processing of the picture data (Dean, 1961). A typical example of such a nephanalysis (cloud chart) composed from a group of photos is shown in Figure 4. Features from the several images are replotted in outline form or reduced to symbolic form on a standard map base for facsimile transmission to the weather analysts and forecasters.

Starting with TIROS II in November, 1960, infrared sensors have furnished experimental radiation measurements in five selected wavelength intervals (NASA - USWB, 1961 and Bandeen, 1962). Although these data have not been available in real time, an extensive 7090 program has been produced for their reduction to a usable form. The IR information has been utilized in a quantitative manner in several research studies. Fritz and Winston (1962) have demonstrated its usefulness in cloud top determinations and Winston and Rao (1962) have used it in connection with energy transformation investigations on the planetary scale.

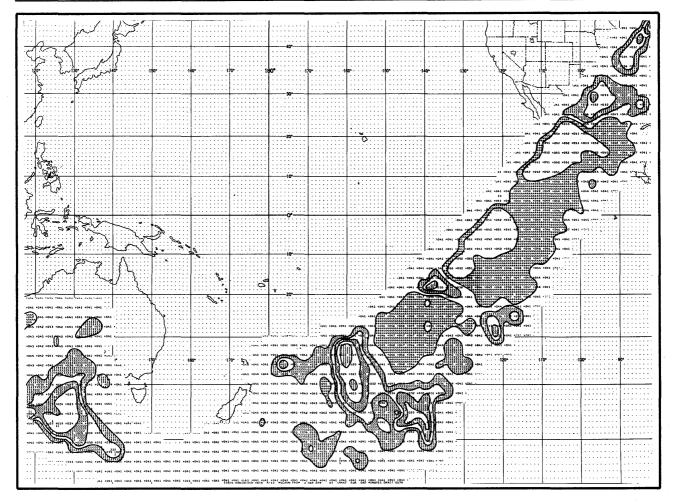

The data reduction program accepts raw digitized sensor values read out from the satellite, rejects space viewed samples, converts the earth viewed responses to proper physical quantities through a calibration procedure and finally combines the data with orbit and attitude information to create a final meteorological radiation tape (FMRT). Data from one orbit is thus reduced to an archivable file on magnetic tape by the 7090 in less than twenty minutes. This tape becomes the data source for other programs which have been produced for the purpose of mapping selected samples of such data on standard maps for use with other meteorological charts. A sample is shown in Figure 5.

The above discussion indicates the nature of the data obtained thus far by meteorological satellites and the kinds of computer support provided. Experience gained in programming the earth location of sensor measurements obtained from satellites, the conversion to standard maps, the calibration and logical sorting of raw data and the experience gained with distortion and attitude programs have all provided background for programs now being produced for direct application in an automatic system. Meanwhile research with TIROS data is suggesting new uses which are likely to lead to a requirement for more kinds of products and interpretations. Experience from past efforts is thereby supporting present efforts in developing an automated, real time system for the processing of global data coverage which will be coming from the Nimbus satellite series.

#### THE NIMBUS DATA PROCESSING TASK

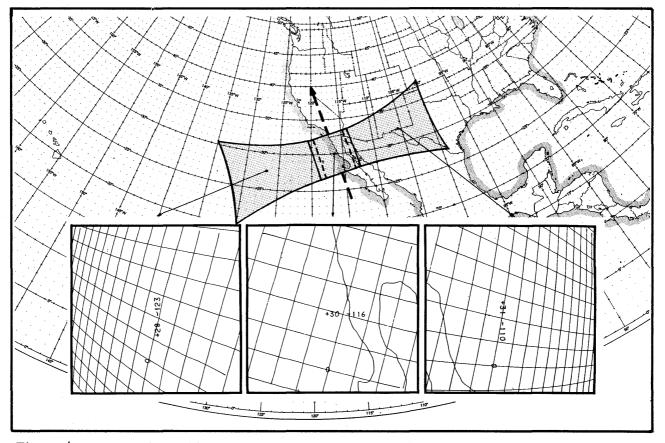

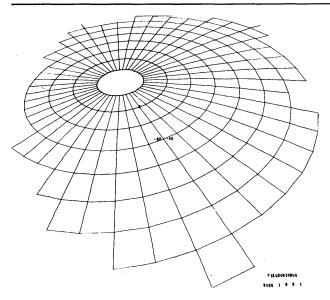

The Nimbus satellite represents a significant advancement over TIROS as an operational satellite. The spacecraft system (Stampfl and Press, 1962) provides more camera coverage of higher resolution, and earth stabilization assures maximum photo coverage. One downward and two oblique looking cameras will view a broad strip of the earth athwart the vehicle's path as shown in Figure 6. The three views overlap slightly.

Figure 3. TIROS grids with familiar coastline features. The set of digits bracketing a central intersection indicate the latitude (left-hand number, plus for North) and longitude (right-hand, plus for East) of that point. A zero is plotted along the meridian at the next intersection to the South. Legend in the lower right indicates orbit and frame number for the matching photo (top line, from left) as well as readout station, mode (taped or direct), and camera (single digits, from left). Horizon arc is indicated beyond the truncated grid pattern at the top where appropriate.

The extremely foreshortened region near the horizon is not viewed. Thirty-three such photo clusters will be obtained from each pass around the earth. Considerable overlap in the wings is obtained from cluster to cluster as shown in Figure 7. The near polar orbit will assure global coverage daily. Overlap from orbit to orbit is minimal at the equator but is very great near the poles (Figure 8). During the polar summer one would expect to see a view such as is covered in Figure 9 on every orbit. The slight inclination of the orbit in a retro sense (injection into orbit with a westerly direction component) will provide controlled illumination for the pictures in that local sun time will remain unchanged from orbit to orbit. Each slow scan TV camera (1" diameter Vidicon tube) contains 833 lines of picture information giving a maximum image resolution of about 1/2 mile when looking directly downward from a nominal orbit of 500 nautical miles. Such a picture will thus contain nearly 700,000 picture elements. If each of these scan spots is converted on a 16 segment gray scale into a 4 bit binary number, then the 99 pictures obtained from each 108 minute orbit will produce almost 275 million bits.

Scanning radiometers will provide IR information as does TIROS but again will obtain optimum scans from horizon to horizon athwart the vehicles's track. One narrow angle high resolution sensor (HRIR) will respond in a water vapor "window" portion of the infrared spectrum and will effectively provide cloud top temperatures or, in cloudless areas, surface temperatures. A mosaic of such scans on the dark portion of each pass will provide a night time cloud cover picture from pole to pole.

The first such HRIR sensor with a .5 degree viewing cone will provide maximum resolution of about 5 nautical miles. Since the earth will be viewed about one third of each scan revolution, 240 non-overlapping measurements can be obtained from each scan. Approximately 2800 non-overlapping scan swaths will be required to cover the dark half of the orbit. Since these sensors have a wider usable response range, each scan spot will occupy a 7 bit binary number. The HRIR response from each orbit will

Figure 4. Nephanalyses (cloud charts) prepared by TIROS readout station meteorologists. Features of the cloud patterns from two successive orbits are extracted in outline form and placed on a standard polar stereographic map base for facsimile transmission to weather analysts and forecasters. Vortex centers are located along with other distinctive features.

Figure 5. TIROS II infrared analysis. Part of the 8-12 micron water vapor "window" data read out on orbit 578 has been summarized in grid squares on a polar stereographic map base. Radiation coming essentially from cloud tops or from the surface is expressed in watts per square meter.

therefore contain more than 4.7 million bits.

Another 5 channel medium resolution infrared scanner (MRIR) will provide additional information throughout each orbit. The five degree view of the MRIR sensors will provide about 42 separate earth measurements per scan revolution from each channel. Approximately 700 non-overlapping scans are required for a full orbit so that (again using 7 bits per measurement) the MRIR response from each orbit will contain more than 1 million bits.

The volume of information expected from each pass is indeed impressive especially when one realizes that this information is to come night and day on a continuous basis for immediate real time utilization. A marked increase in the present number of TIROS data analysts and helpers is indicated for Nimbus data processing if present semihand procedures continue. With plans for higher resolution sensors of increasing variety, automatic processing of satellite weather data is becoming a necessity.

#### STATUS REPORT ON NIMBUS DATA PROCESSING PROGRAM

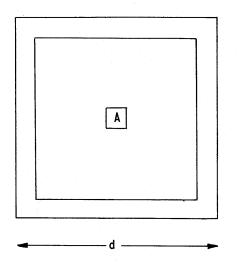

The automatic data processing system under construction will be located at the Weather Bureau's National Weather Satellite Center (NWSC), Washington, D. C. and will receive its input data from the command and data acquisition (CDA) facilities at Fairbanks, Alaska through multiple broad band microwave communication facilities. The system at NWSC contains a complex of components in addition to the digital computers. A detailed explanation of the system is beyond the scope of this report although a brief description from the computer oriented viewpoint is given in the second part. Let it suffice at this point to say that the system is evolutionary in design in that computations will continue in support of semi-hand processing procedures. For this purpose the system's IBM 7094 with attached 1401 will be utilized to produce a picture gridding tape. Information in the form of override signals at specified Vidicon scan line and scan spot numbers, when melded with the analogue picture signals, will produce a kinescope recording of the original cloud photo with a super-imposed dotted line locator grid such as Figure 10. A small CDC 160A computer, interruptable by Vidicon synch pulses, will synchronously meld the digital information from the gridding tape onto spare tracks of an analogue picture tape. Other non-digital devices will then combine the synchronized information on

this tape as it is fed into the kinescope recorder.

The 7094 program is being produced essentially as an extension of present TIROS programs. A simulated output of this program has provided check out facility for the 160A program which now awaits the unique non-digital hardware complex for final checkout. A complexity of supporting programs are involved in this effort as indicated in the appendix which briefly describes each program module. This effort will permit a TIROS type semi-hand processing of the photo data but with hand melding of grid and picture now automated.

The far greater task of the system involves duplication of the semi-hand processing by automatic means. In the beginning these efforts must be experimental in that application of the data is still exploratory. Methods of presentation, quantities to be extracted from the basic data, the scale of atmospheric phenomena to be described (resolution) are all in exploratory stages. A

Figure 6. Perspective grids and mapped coverage of Nimbus camera cluster as seen from a 500 nautical mile orbit. The central camera looks directly downward at the sub-satellite point. Side cameras are tilted 35 degrees to either side of the track.

Figure 7. Geographic coverage to come from Nimbus showing overlap between adjacent three camera clusters.

major effort is underway to create a hierarchy of data processing programs to activate the system and produce a variety of outputs in a flexible manner. These may be grouped as ingestive, digestive, and productive.

The ingestive programs are more than simple input routines in that some preprocessing of the data is accomplished. In the case of picture data, the entire volume mentioned previously is to be fed into storage in the computer. Some sorting is required before storage so that separate disk files are created containing data from each of the three cameras. As time permits, other pre-processing activities will also be accomplished. Light intensity signals over the face of each photo require normalization for angle of view before quantitative comparisons are valid. Also, for the same reason, solar aspect variation from equator to pole must be removed.

In the case of the incoming MRIR and HRIR data, the ingestive process is partly one of data editing. By recognition of pulses which provide knowledge of scanner shaft angle, almost two thirds of the incoming data which is non-earth viewing can be eliminated. Other raw housekeeping input information such as attitude error signals and sensor environment temperatures must be unpacked and translated through calibration in the ingestive process before they can be used in processing the meteorological data.

Final checkout of these programs must await activation of the complete hardware complex since only limited simulation is possible.

The digestive process takes the pertinent incoming data and converts it to a meteorologically usable form. A major task is the melding of this data with the orbit and attitude information to geographically locate the sensor information elements. In the case of the photos, part of this work is accomplished as an adjunct to the earlier mentioned program which produces the picture gridding tape. An open lattice of points selected by scan row and spot number are geographically located within each image. From these location "bench marks" the digestive program transforms the foreshortened, perspective photo image into a rectified equivalent on a standard map base. Figure 11 is an experimental

Figure 8. Geographic coverage envelopes to come from Nimbus showing overlap from orbit to orbit.

Figure 9. Sample perspective grid showing the polar region to be viewed by Nimbus.

example. The rectified image appears on a mercator map projection—in one view as a replotting of the original picture elements only. It demonstrates the futility of extending this process into extremely foreshortened image areas where a realistic rectified image would consist largely of interpolated filler.

After this step the rectified images are fitted together into a mosaic strip which is then available as a product source.

The digestive infrared data program is being patterned after that mentioned earlier which has been produced for the processing of TIROS radiation data. The calibrated and earth located data will similarly provide a product source through the archivable final meteorological radiation tape.

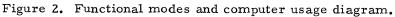

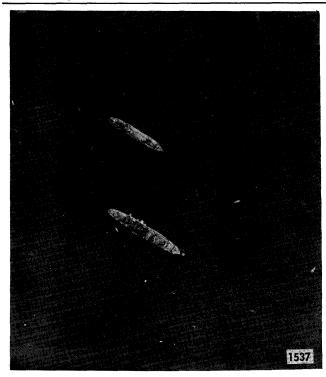

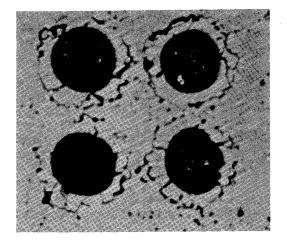

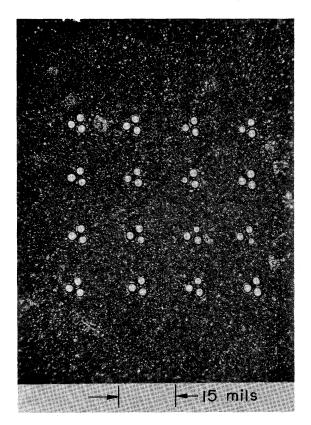

Programs for production of usable output material present the most problems. Full resolution photo mosaics rectified to polar stereographic or mercator maps are expected to find application over limited regions in connection with hurricane detection and tracking, for example. For other broadscale analysis problems, products having reduced resolution may be adequate. This implies searching these images by machine, editing and summarizing them as to percent cloud cover, brightness and pattern. Some interesting patterns are revealed in the TIROS photos of Figure 12, Although, as mentioned earlier, quantitative interpretations are only gradually emerging, the rings, spirals and streets seen in these photos will likely be subjects for identification through pattern recognition techniques. Cloud heights, provided indirectly from the IR data through

Figure 10. Cloud photo with melded grid (simulated): Original Hugo rocket photo (left) looking toward Bermuda from Wallops Island, Virginia at 85 miles altitude and 100 scan line digitization of the original picture (right) played back through a digital CRT (SC-4020) with 15 unit gray scale produced by programmed time modulation. Certain picture elements have been replaced by grid signals before playback to produce latitude/longitude lines.

Figure 11. Rectified cloud photo: Digitized picture elements from figure 10 replotted on a Mercator map base without filler (below) and with filler (above) to produce a rectified pictorial image.

cloud top temperatures, present an added output. The MRIR package will yield other derived products such as maps of the net radiation flux. There is thus a family of derived products available from the digested material. A variety of output equipments including prototype cathode ray tube photo recording devices which are driven by digital tapes and somewhat similar photo quality facsimile machines, require additional conditioning of the output products to suit the formats specified.

The variety of production type programs are indicated in the appendix. It is likely that all such production varieties cannot be produced in real time from the data received on all passes of the satellite. The intent is that these products will be available for experimental utilization and that variations and modifications of those which prove to be most useful will assume an operational role.

#### CONCLUSION

This has been a brief attempt to present a background to the non-meteorologist explaining the need for more weather data, and the present and likely future role of weather satellites. The need for computers and automatic data processing is explained in terms of the kinds of data involved. Computer support of semi-hand methods is discussed along with current efforts toward a truly automated effort for Nimbus satellite data. As the variety of sensors and the volume of such data increases, a maximum degree of automatic processing and utilization of the data is indicated.

The scope has been limited to the data processing job as seen from the computer programmers viewpoint. Other groups within the Goddard Space Flight Center of NASA, the Weather Bureau's NWSC and their contractors have vital roles in the design, launch, command and readout of the satellite and the supplying of other important data in the form of sensor calibration and orbital information from tracking station data before the sensor data can be rendered meteorologically useful.

Only scant mention has been made of the entire data processing system. The second paper in this series will give additional details of the digital and non-digital data processing machine complex—again from the standpoint of the computer programmer. The role of the computer as manager of the process will be amplified in terms of command and control.

#### APPENDIX

The main program modules are listed below together with some details concerning each subroutine portion. The main section of each program module is indicated by an asterisk. Status of various portions is indicated as of September, 1962.

#### Executive Program

Details of the Executive Program are provided as part of the text of Part 2 of this paper.

Time - Attitude - Calibration Ingestion Program

\*Time/Attitude Sort: Engineering housekeeping data on "A" channel including pitch, roll and yaw attitude signals and certain vehicle temperatures used in IR sensor calibration are transmitted as pulse code modulation (PCMA). Shutter times from the

Figure 12. Sample TIROS cloud patterns. Convective clouds over Lower California (upper left) August 21, 1961. Classic hurricane symbol from cloud pattern of Hurricane Betsy (upper right) near 36°N, 59°W on September 8, 1961. Field of cellular clouds (lower left) near 25°S, 10°E on July 31, 1961. Cirrus cloud streamers off the Andes (lower right) passing eastward off the Argentine coast, August 3, 1961.

Advanced Vidocon Camera System (AVCST) are sent in similar format on another channel. This program will accept such information and sort it from an intermixed input format.

<u>PCMA Unpack and Monitor</u>: Unpacks the separate 7-bit raw count measurements and translates selected quantities into meaningful temperatures or angles. Items to be used are examined for quality and format with optional outputs for visual inspection.

<u>PCMA Output</u>: Organizes attitude, calibration temperature, and picture time information into tables and issues the information in a form suitable for use by the main data processing programs. <u>Time/Attitude Editor</u>: Optionally accomplishes some of the above duties as required in the event that this information is made available in semi-processed form as a direct digital message.

This section is in an active design status awaiting final format of PCMA data and decision on items to be transmitted from Fairbanks, Alaska.

Picture Grid Tape and Rectification Program

<u>Orbit</u>: Based upon a specified time request, this subroutine supplies satellite altitude and latitude/longitude of the subsatellite point. The information is generated as a prediction based upon periodically updated fundamental orbital elements which are supplied by the main NASA orbital determination through minitrack data.

<u>Picture Attitude</u>: Converts pitch, roll and yaw error signals into nadir and azimuth angles of each camera's principle line and also provides a radial displacement correction to the orientation of each raster.

Distortion: On the basis of prelaunch target photos, produces radial and tangential distortion corrections for a pre-selected family of image raster points so that, through interpolation, any image X, Y point can be expressed in terms of two component angles in object space.

<u>Geography</u>: Provides a large catalog of latitude/longitude points along all major coastlines of the world. The subroutine provides ordered groups of such points in short segments for quick selection. Such coastlines are optionally included with latitude/ longitude lines in grids melded to the photos.

\*Grid Meld and Rectification Locator: This is the main program segment. It includes the basic calculations which produce latitude and longitude from an X, Y image point. The subroutines above serve as input support. The primary output is approximately 1000 latitude/longitude locations from a pre-selected open lattice of image locations. These locations are available in table form for later interpolative rectification of the entire picture raster.

Grid Meld Output: For every sixth scan line of each picture raster, the locations of latitude/longitude line crossings are calculated. This information from one simultaneous three picture cluster is logically combined into a set of binary tape records containing a series of three-bit code groups and nine-bit count groups which tell where over-ride signals are to replace the picture signal and produce a dotted line grid.

One such orbit routine has been produced for TIROS. Revision awaits coordination with NASA orbital computation group as to mathematical model to be used for Nimbus. Geographic coastline tables from TIROS have been expanded to global coverage and are available for Nimbus. Other portions are active.

#### Line Drawn Grid Program

\*Grid Line Locator: A program similar to the above but intended primarily for emergency use. It computes X, Y image points from pre-selected latitude/longitude intersections.

Line Output: Generates a special format tape for a model 3410 Electronic Associates Data Plotter.

#### Cathode Ray Tube Grid Program

\*CRT Grid Locator: Essentially a duplicate of the Grid Line Locator above.

<u>CRT Output</u>: Generates a special format tape to guide the cathode ray tube beam to produce grids recorded on microfilm from devices such as the Stromberg Carlson Model 4020 Microfilm Recorder.

Both the line drawn and CRT grid programs have been completed as generalized versions of TIROS packages and are being used experimentally.

#### **Digital Picture Ingestion**

\*Picture Sort: Digitized pictures arriving from the analogue to digital converter through the external format control unit will enter the computer in packed words. Each 36-bit word will contain 4-bit intensity measurements from nine consecutive scan spots all from the same picture. A cyclic commutation intermixes such words from the three cameras. This program sorts the information for output into separate files each containing information from only one camera. The following subroutines support this task and carry on added preprocessing functions.

Picture External Communicator: Picture data is being recorded at 7-1/2 inches per second into a bin tape recorder and the digital conversion process consults this tape intermittently at 30 inches per second. The external communicator is really an extension of the executive routine which sends out commands to stop and start the read capstan on the bin tape recorder.

<u>Picture Monitor</u>: Provides superficial checks to see that a signal is present, that raster line synch marks are clear, etc.

<u>Unrectified Print</u>: Produced by IBM 1401 printer will produce a visual check of the raster and its relationship to the fiducial marks, a single character corresponding to each scan spot.

Solar Ephemeris: With time of photo, provides the latitude/longitude of the subsolar point from which usable sun angles may be generated for later interpretation of brightness, reflection properties and other attributes of the image.

Sun Glint: Used in conjunction with the Solar Ephemeris routine will earmark that part of any image where the response is primarily caused by sun glint.

Output to Storage: Will consist of routine output commands to the two disk channels but output of information is important insofar as efficient positioning of the write arm is concerned since a maximum net transfer rate is required.

Most parts of this module are active. The Solar Ephemeris has been completed as a more efficient version of a similar TIROS package. Input format and means of detecting ends of scan lines are being worked out in conjunction with final design specifications of the Format Control Unit.

**Picture Digestion and Production**

\*Picture Rectification: Utilizes the output of the rectification locator program. Separate picture scan spots are repositioned in sub-blocks of storage according to grid squares on a standard map base. The following supporting packages are utilized.

<u>Picture Selector</u>: Provides input/output selection capability. A picture will be specified by exposure time and as left, right or center camera. A specification of core buffer location and picture segment will result in movement of the required item to or from disk storage.

Brightness Normalizer: Adjusts the image response for variations due to the scan electronics and also adjusts for pole to equator illumination differences.

Background: Provides an updated background response from which current responses will be treated as anomalies. In this way partial discrimination between cloud and background will be possible.

Interpolate: Provides an efficient quadratic interpolation within a two dimensional array. This package will be used extensively in connection with transformations from x, y image locations to i, j map grids.

Indexing: A flexible subroutine which permits identification of storage location as a function of i, j location in square mesh grid which is to be superimposed on a map projection. Mosaicker: A routine which will combine rectified, summarized data in an overlap region based on priority selection rules.

Cloud Cover: Some 400 picture elements falling in a ten nautical mile grid square will be ranked as background, cloud or doubtful. Percentage cloud cover and average cloud cover brightness will be expressed as edited output.

Disjunction: Further interpretation of the data used for cloud cover analysis will express the areal variability of cloud cover thus distinguishing between scattered or broken cloud arrays in large contiguous masses as compared to other cases similar in net cloud cover but distributed in a more specular array.

Orientation: By comparing profiles of response within a ten mile square using samples taken from different radial orientations, certain streakiness and other features of the pattern can be deduced.

Stereo Map: Computer i, j coordinates on a specified square mesh grid on a polar stereographic map base for a given latitude/ longitude point on earth.

Mercator Map: Similar to above but using a Mercator map base.

Grid Print Output: Prints out on standard IBM printer the various summarizations discussed above by using a character for each 10 mile mesh interval (square type and ten line per inch carriage control are desirable). By coding character selection, both quantitative and pictorial output can be obtained.

Line Drawn Output: Contoured fields are produced from magnetic tape on an Electronic Associates Data Plotter, Model 3410. Cloud height analyses will likely be produced by this device.

<u>CRT Output</u>: Similar to grid print output but utilizing a device such as the SC 4020 microfilm recorder.

<u>Fax Output</u>: Similar to the above but utilizing digital tape directly to drive a facsimile scan device.

Most program segments are active. The interpolation routine is in operation. The background package will be self generating after Nimbus launch in that clear air earth views will be accumulated as background information. Stereo and Mercator mappers have been produced. An experimental unrectified print package has also been produced.

## MRIR Ingestion and Digestion Programs

<u>Scan Rate</u>: The scan shaft angle corresponding to a specific sensor sample can be deduced from a shaft angle reference pulse but is also dependent on knowledge of scan shaft spin rate and sampling frequency. This subroutine will be available on an optional basis to compute the spin rate by counting shaft reference pulses over a given number of cloud pulses.

\*MRIR Ingestion: Manages input, partial processing and places raw product in intermediate storage.

Scanner Attitude: Similar to picture attitude routine but supplies a series of nadir and azimuth angles along a scan swath.

<u>Space Cropper:</u> From height supplied by orbit routine and roll correction, provides identification of IR samples with respect to scan shaft reference pulse thus permitting rejection of all but earth viewing sample.

Earth Locator: An adaptation of the picture locator package which furnishes latitude/ longitude information from input provided by orbit and attitude routines.

Solar Sector: By using the solar ephemeris and location of viewed spot, provides solar angles for interpretation of data.

<u>MRIR Data/Format Monitor</u>: Inspects the raw data to detect format errors and to judge the general quality of the data (noise). Failure to pass acceptance tests causes visual output for further inspection.

\*MRIR Format and Output: Creates the archivable intermediate source tape from which various output products are derived. This main portion utilizes the routines below and some of those above which cannot be utilized for want of time during the ingestive phase.

<u>Calibration</u>: A step-wise two dimensional array interpolation which produces effective black body temperatures from raw sensor counts as a function of environmental temperatures adjacent to the sensors and in the electronic data transmission equipment.

Documentation: Places appropriate identification on the archivable product including orbit number, date, time, etc.

Parts of this package that are also used with HRIR are active. Earth Locator and Calibration will be minor revisions of TIROS routines. MRIR Production Programs

\*<u>MRIR Mapper</u>: Consults the final Meteorological Radiation tape produced by the digestive programs and generates fields of derived quantities as indicated below. Also supervises the various output packages.

<u>Cloud Height Analyzer</u>: With the aid of a temperature height analysis based upon existing observations and climatology, provides a map of height information based on water vapor window measurements. This information is now available in consort with cloud photo information for further interpretation.

Limb Darkening: Provides corrections to sensor response as a function of viewing angle (path length).

Net Flux: Creates a map indicating the net radiative flux (incoming short wave vs. outgoing long wave) through a functional combination of sensor responses.

Albedo: Produces a map of reflectivity of the cloud patterns.

<u>MRIR Print Output</u>: These output programs are minor revisions of those mentioned for cloud photos.

MRIR Line Drawn Output:

MRIR Fax Output:

MRIR CRT Output:

This portion is generally not active pending decisions on availability of portions of data in real time.

#### HRIR Ingestion and Digestion Programs

\*HRIR Ingestion and Format: A CDC 160A computer program which accepts packed raw count information, unpacks and edits the data with the help of the two routines below.

HRIR Space Cropper: A preliminary separation of earth and space viewing response is accomplished without specific height or attitude input in order to eliminate unwanted response without using a highly complex program on a small computer.

HRIR Format Monitor: Detects unsatisfactory quality of input data and optionally generates output for visual inspection (see similar MRIR routine).

\*HRIR Digestion: Provides intermediate calibrated and geographically located data as indicated above for MRIR. Many of the subroutines cited above for MRIR are also applied directly to HRIR.

HRIR Calibration: A simplified version of the similar MRIR routine.

HRIR Format and Output: Generates the archivable product source tape. Single channel sensor output is arranged in a format somewhat different from that used for the multi-channel MRIR.

This module is active. The ingestive portions using the 160A is being carried out by contract with National Computer Analysts (NCA), Princeton, N. J. An internal segment of the HRIR Digestion package which precisely defines the earth viewed data sample is in check out.

#### **HRIR Production Programs**

These programs borrow heavily from the MRIR cloud height analysis and the photo cloud cover routines described above. Output routines will also be minor variations of those discussed.

Some output routines await word format specifications and instruction sets for prototype output hardware. Special character chains for computer printer output are being considered.

#### Picture Grid Melding Program

\*CDC 169A Grid Meld: Provides synchronous recording of digital grid signals produced by IBM 7094 and the analog picture raster.

<u>Time Check</u>: Insures correspondence between gridding signals and pictures by input of PCM time groups direct from the analog picture tape and the comparable time information which accompanies the gridding signals.

Panel Documentation: Provides documentation information from the 7094 produced tape in proper format for output to the multitrack analgue picture tape such that a documentation panel is activated as the gridded picture is produced for film recording.

This segment is completed and awaiting non-digital equipment for final checkout. Details of Panel Documentation await final design specification of panel display device.

#### Simulation Support Programs

Certain non-operational programs are useful as feasibility and timing experiments while others produce interface input or output product samples which serve to check out segments of operational programs. Some of these have been produced:

AVCS Photo Rectification Study HRIR FMRT Output Simulation MRIR Raw Data Simulation Executive Routine Test

Various phases of the photo rectification study have been completed including gray scale experiments on a digital CRT, filler experiments and obtaining timing figures.

Other Simulation Programs Test Hardware:

Passive Switching Exerciser (7094)

Active Switching Exerciser (7094)

Control Logic Communicator (for 7094 and 160A)

Format Control Test (for 7094 and 160A) Analog to Digital Test (7094)

AVCS Picture Tape Test (160A)

These routines are awaiting final design specifications and specific control formats.

#### REFERENCES

- American Meteorological Society, 1962: Statement on Weather Forecasting. <u>Bul</u>letin A.M.S., Vol. 43, N. 6, June 1962, 251.

- Bandeen, W. R., 1962: <u>TIROS II Radiation</u> Data User's Manual Supplement. A & M Div., GSFC, NASA, May 15, 1962.

- Dean, C., 1961: Grid Program for TIROS II Pictures. Allied Research Associates, Inc. Contract No. Cwb 10023, Final Report, March 1961.

- Frankel, M. and C. L. Bristor, 1962: Perspective Locator Grids for TIROS Pictures. Meteorological Satellite Laboratory Report No. 11, U. S. Weather Bureau, 1962.

- Fritz, S. and J. S. Winston, 1962: Synoptic Use of Radiation Measurements from TIROS II. <u>Monthly Weather Review</u>, 90 (1), January 1962.

- Johnson, D. S., 1962: Meteorological Measurements from Satellites. <u>Bulletin A.M.S.</u>, Vol. 43, N. 9, September 1962.

- National Aeronautics and Space Administration and U. S. Weather Bureau, 1962: Final Report on the TIROS I Meteorological Satellite System. NASA Tech. Report No.  $\overline{R-131}$ .

- National Aeronautics and Space Administration and U. S. Weather Bureau, 1961; a: Abstracts and figures of Lectures and Reprints of Reference Papers. <u>The Inter-</u> <u>national Meteorological Satellite Work-</u> shop. Washington, D. C., Nov. 13-22, 1961.

- National Aeronautics and Space Administration and U. S. Weather Bureau, 1961; b: <u>TIROS II Radiation Data User's Manual</u>, August 1961.

- Phillips, N. A., 1960: Numerical Weather Prediction. Advances in Computers, Vol. I edited by Franz L. Alt, Academic Press, 1960, 43-51.

- Stampfl, R. A. and H. Press, 1962: The Nimbus Spacecraft System, to be published in Aerospace Engineering, 21 (7).

- Winston, J. S. and P. K. Rao, 1962: Preliminary Study of Planetary Scale Outgoing Long Wave Radiation as Derived from TIROS II Measurements. <u>Monthly</u> <u>Weather Review</u>, 90, August 1962.

# PROCESSING SATELLITE WEATHER DATA -A STATUS REPORT - PART II

Laurence I. Miller U. S. Weather Bureau Washington, D. C.

#### SUMMARY

Experience gained from earlier meteorological satellites provides a firm background for the basic design of the data processing center. Nevertheless, the almost limitless nature of the sampled data and some uncertainty as to the optimum forms of the final products dictate the need for providing the basic system with extreme flexibility and good growth potential. To achieve the desired versatility, the operation of the various portions of the system are being designed so that their functions are almost entirely programmable to facilitate rapid conversions to handle new types of data and cope with changing situations.

Maximum utilization of a computer's logical capabilities are stressed to avoid redundant construction of analog hardware and/or special "black boxes." An executive monitor program is designed to provide the necessary link between computer and external hardware. Emphasis is placed on the centralization of control and the modular design of the main programing packages.

#### INTRODUCTION

In Part I of this report reference has been made to the site of the data-processing center with only passing comment on the communication network and the system being designed to manage, edit, process and output

the enormous volume of data. The data processing plan for the operational meteorological satellite, Nimbus, is the result of a continuing research and development program begun after World War II with German and American rockets and more recently includes the highly successful TIROS satellites. It is beyond the scope of this report to provide a detailed description of the TIROS satellites; however, Table 1 provides a ready comparison between some of the more salient features of the two systems and furnishes a foundation for the ensuing more detailed description of the Nimbus data-processing system.

Limited computer processing of TIROS data was discussed in Part I, and details of the difficulty of "real-time" computer processing of the information have been given elsewhere, along with an engineering description of the first TIROS satellite and a meteorological analysis of some of the data [4]. Equally as important a consideration in not preparing elaborate data-processing codes to handle the TIROS data was the limitation in speed and storage capacity of existent digital computers when the TIROS design was considered. The time required to compute a reprojected image of one complete photograph approached the elapsed time of one entire orbit [5]. Although attention will be given to this problem in a subsequent section, it hardly seems redundant to point out that computers of the present generation are still barely adequate to this task.

#### Table 1

|                                   | TIROS           | Nimbus                 |

|-----------------------------------|-----------------|------------------------|

| Height (inches)                   | 19              | 118                    |

| Diameter (inches)                 | 42              | 57                     |

| Weight (pounds)                   | 300             | 650                    |

| Orbital Altitude (Nautical miles) | 380             | 500                    |

| Orbital Inclination               | 48° Equatorial  | 80° Polar              |

| Stabilization                     | Spin-Stabilized | Earth-Seeking (3 axes) |

| Earth Coverage (%)                | 10-25           | 100                    |

| Camera Raster (lines per frame)   | 500             | 833                    |

| TV Resolution (miles)             | 1               | 1/2                    |

| Maximum Power Available (watts)   | 20              | 400                    |

| IR Sensors (resolution, miles)    | MRIR (30)       | MRIR (30)-HRIR (5)     |

| Period (minutes)                  | App. 100        | App. 100               |

| No. of Cameras                    | 2               | 3                      |

| Command Stations                  | 2               | 1                      |

Comparison of Nimbus and TIROS

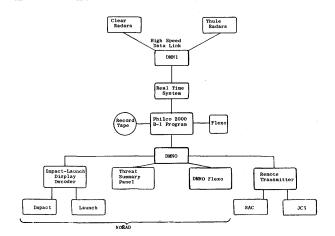

The second part of this paper serves three purposes: to examine the logical layout of the central computer with associated peripheral equipment and external hardware; to describe the functioning of the data processing system, emphasizing the logical capabilities of the computer; to discuss the vital link between computer and external hardware provided by an executive monitor program.

#### DATA TRANSMISSION

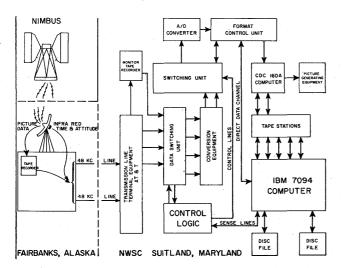

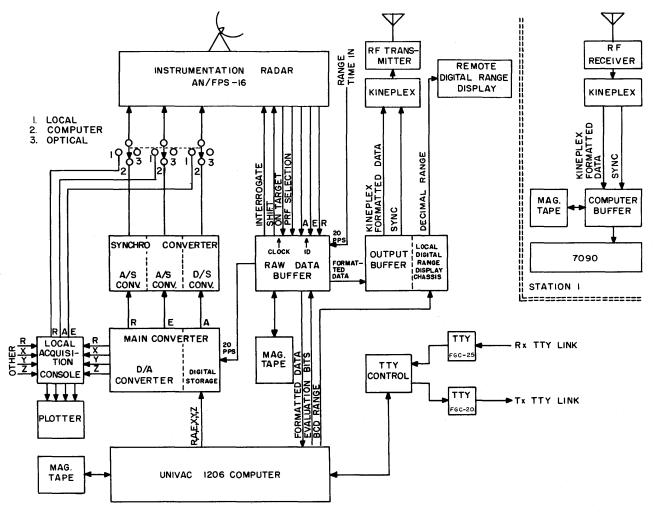

Figure 1 is a generalized schematic representation of the flow of data from Nimbus to the National Weather Satellite Center

Figure 1. Schematic representation of the flow of data from Nimbus to the National Weather Satellite Center.

(NWSC), Suitland, Md., via the command and data acquisition (CDA) station at Fairbanks, Alaska. The proposed transmission facility between Alaska and Suitland will utilize two 48 Kc lines, known commercially as Telpak B. The telemetry aboard the satellite provides information on the spacecraft environment and attitude as well as information from the three meteorological experiments. Data recorded on magnetic tape recorders aboard the vehicle are telemetered to the ground station using an FM-FM system to accommodate the considerable information bandwidth.

Somewhat different considerations apply to each of the multiple sensor and environmental signals as they are initially recorded on the spacecraft, telemetered to the ground and finally received at the transmission terminal equipment. These features are summarized as follows:

#### AVCS

Each of the three video cameras are simultaneously exposed for 40 milliseconds, scanned for 6.75 seconds and recorded on magnetic tape at 30 i.p.s. Although each exposure of the thirty-three frames (three picture set) are 108 seconds apart, only 3.7 minutes of actual recording time is required. Playback to ground is maintained at 30 i.p.s. but is recorded, still in FM form, at 60 i.p.s. Since the long line bandwidths are not sufficient to accommodate the frequency range, the ground tape is rewound and then relayed to the NWSC in 30.85 minutes at 7.5 i.p.s.

### HRIR

The narrow angle high resolution radiation sensor is active only during the dark southbound portion of the orbit of approximately 64 minutes. During this time data is recorded at 3.75 i.p.s. and then telemetered to the CDA station in 8.1 minutes at 30 i.p.s. The transmission is received at Suitland in 8.1 minutes; however, the data are recorded at 60 i.p.s.

#### MRIR

Five medium resolution radiation sensors scan from horizon to horizon during the entire orbit. An endless tape loop records the data continuously (except during readout) at 0.4 i.p.s.; increasing the playback speed by a factor of 30 reduces the readout time to 3.6 minutes. The data is recorded at Suitland at 30 i.p.s.

#### PCM

Space craft environmental signals, including attitude signals, vehicle temperatures and other housekeeping data, are transmitted as pulse code modulation (PCM). This information is also recorded during the entire orbit in a similar manner to the MRIR, discussed earlier.

The "real-time" aspects of the operation are accentuated by the undelayed transmission of the PCM and infrared data directly to the NWSC computers over the leased microwave facilities. The total time required for complete satellite interrogation is 8+ minutes; therefore, all but three to four orbits a day can be recorded at Fairbanks.\* Transmission of the video data to Suitland is delayed about 10 minutes while the computers convert the raw PCM data to useful parameters; therefore, all the data is not received at the center until approximately 40 minutes after the start of interrogation. Direct access of the data to the IBM computer is accomplished by means of a Direct Data Connection (DDC), which permits real time transmission between 7094 storage and external devices at rates up to 152,777 words per second.

The NASA Space Computing Center at the Goddard Space Flight Center supplies a set of orbital elements, which are periodically updated by information received from the world-wide Minitrack network. Prior to satellite interrogation these elements are converted to satellite latitude, longitude and height as a function of the orbit time.

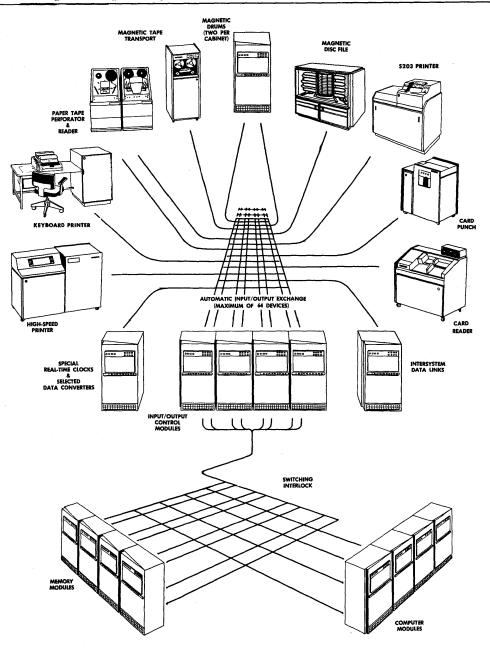

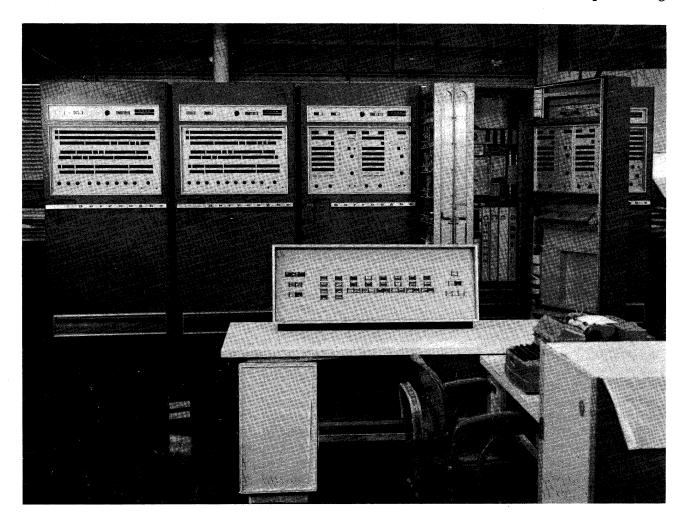

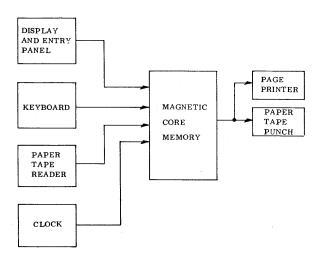

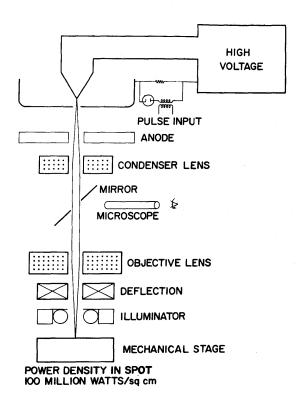

#### INPUT DATA

Before turning to a consideration of the high data rates as they pertain to the "realtime" system, let us briefly outline the presently proposed computer complex. The primary computer will be a 32,000 word core memory IBM 7094 equipped with the following elements: fourteen MOD V magnetic tape drives shared between two channels, two 1301 disk files each connected to a separate channel, one DDC attached to a tape channel, a core storage clock and interval timer, an online printer and card-reader. Two smaller scale computers will also be available, an IBM 1401 to serve primarily as an inputoutput device to the 7094, and a CDC 160A to be used in the picture-gridding program and to some degree as a preprocessor for the less voluminous MRIR and HRIR data.

Table 2 provides a summary of the volume and real-time rates (equivalent to 60 i.p.s. playback) of the experimental data, and Table 3 provides the data rates of the 7094 input-output equipment. From a consideration of the simultaneous input-output computing abilities of the 7094, and the effective use of optimum buffering techniques, it appears at first that the severest constraint to operational use of the data is imposed by the acceptance rates of the DDC and the temporary storage devices. However, closer examination of the basic machine cycle time (2.0 microseconds) and the frequency of main frame cycles borrowed by the input-output equipment reveals that insufficient editing, buffering and operational programming time would be available even if the basic acceptance and transfer rates could be appreciably increased.<sup>†</sup>

<sup>\*</sup>The east coast of North America is being considered as a site for a second CDA station.

<sup>&</sup>lt;sup>†</sup>The 7094 was selected as the result of a staff study which considered among other things delivery dates, performance and reliability, software, user groups, and especially speed and storage capacity.

#### Table 2

Satellite and Station Recording Rates

| Satellite                               |                   |             |            |             |  |

|-----------------------------------------|-------------------|-------------|------------|-------------|--|

| ``                                      | AVCS              | HRIR        | MRIR       | PCMA        |  |

| Record<br>(min.)<br>Speed               | 3.7<br>30         | 64.8        | 108<br>0.4 | 108<br>0.4  |  |

| (i.p.s.)<br>Playback<br>(min.)<br>Speed | 3.7               | 3.75<br>8.1 | 0.4<br>3.6 | 0.4<br>3.6  |  |

| (i.p.s.)                                | 30                | 30          | 12         | 12          |  |

|                                         | Fairbanks         |             |            |             |  |

| Speed<br>(i.p.s.)<br>Playback           | 60                | 60          | 60         | 60          |  |

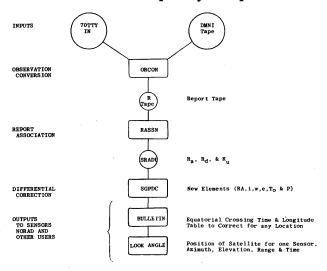

| (min.)<br>Speed                         | 30.85<br>7.5      | Direct<br>- | 3.6<br>60  | Direct<br>- |  |

| NSWC                                    |                   |             |            |             |  |

| Speed<br>(i.p.s.)<br>Playback<br>(min.) | 7.5<br>30 (Batch) | 60<br>8     | 7.5        | -           |  |

| Speed<br>(i.p.s.)                       | 30                | 60          | 60         | -           |  |

#### Table 3

| Volume and I | Real | Time | Data | Rates |

|--------------|------|------|------|-------|

|--------------|------|------|------|-------|

|                          | Binary Bits                                                      | Bits/second                                          |

|--------------------------|------------------------------------------------------------------|------------------------------------------------------|

| AVCS<br>HRIR<br>MRIR     | 275,000,000<br>14,700,000<br>3,600,000                           | 1,402,920<br>App. 59,000<br>134,400                  |

| (high<br>IBM 72<br>(high | 29 Mod IV<br>density)<br>29 Mod VI<br>density)<br>01 DISC<br>0DC | 375,000<br>540,000<br>App. 500,000<br>App. 1,000,000 |

The required high rate of data transmission is obtained by maintaining a continuous flow between the transmission line and the computers. The analog signals are detected, multiplexed and introduced to an analog-todigital converter which encodes the sampled values in digital form while preserving the integrity and rate of the data. In the case of the video signals the data are recorded at 7.5 i.p.s. in a special bin storage recorder which permits the information to be read into the computer in batches at 30 i.p.s., well within the data handling capabilities of the computer.

#### DESIGN CONSIDERATIONS

During all phases of the system design it has been vital for us to consider both the high degree of flexibility and growth potential inherent in the Nimbus Research and Development program and the implications of future programs of international cooperation in weather satellites. Further, as the system passes from the experimental phase to the truly operational stage the degree of automation will increase and eventually replace manually performed functions. The required balance between these practical considerations and the need to assume an immediate operational posture has been achieved by designing the structure of the combined digitalanalog complex as machine, not hardware, orientated.

To achieve the desired versatility, the operation of the various portions of the system are being designed so that their functions are almost entirely programmable to facilitate rapid conversions to handle new types of data and cope with changing situations. Emphasis has been placed on the modular concept so that substitution of one package for another does not have ramifications throughout the entire system. Maximum utilization of the computers logical capabilities have been stressed to avoid redundant construction of analog or special hardware. Wherever possible, major hardware units are standard, dependable general purpose equipment; and where it has been necessary to build special equipment, these are of the patch board variety.

#### CONTROL PHILOSOPHY

The Nimbus system has a common base with many other complex systems where computers are employed for such vital functions as information storage, retrieval and display. Inherent in most of these systems (e.g., BMEWS, SAGE, MERCURY) is a complex information processing problem which requires intervention of skilled personnel to make the ultimate decision. These systems serve to provide a broad basis of facts on which the dominant information processor, man, can make his decision. Whereas these systems have been designed because it is possible to differentiate between the normal and abnormal, no such clear-cut definition exists in our weather system. Logical uses of pattern recognition theory and meteorological research may well negate this last remark, but such techniques are beyond the state-of-the-art at this time.

A second difference arises when we consider that the ingestive program is not engaged throughout the entire processing cycle, i.e., the time between successive readouts. During the ingestive phase (phase I) the external hardware maybe completely active or passive or any combination of the two; during the non-ingestive process (phase II) the external hardware is predominantly passive. At any time during a processing cycle both diagnostic and management interrupts may occur, but the type of program control invoked must be considered in light of these two phases. Management interrupts which may occur at any time are caused by the normal transfer of data through the computer and must be given immediate priority. A component of the external hardware which monitors the system to prevent loss of quality or integrity of the information may also provide a diagnostic interrupt at any phase; however, the right to take action is reserved to the computer. During phase I the computer must be programmed to take immediate action; however, during phase II the suspected malfunction may be beyond the present logical flow of information, and the computer may merely advise a superviser and refuse to disturb the present operation. The monitoring and diagnostic control programs must be optimized as a function of the two phases.

At the time of initial launch when complete understanding of all possible system malfunctions is lacking, problems may arise which have not been anticipated. To cope with this situation a special manual mode of operation is provided which permits human intervention to apply recovery techniques. As a further "guard to the guards" a real time programmable clock senses the status of each phase and signals the present mode of operation. It appears that the regularity of the data and uniformity of time scale should best be served by an automated system with minimum human intervention. This philosophy is controlled by an executive program which also provides the link between the computer and external equipment.

#### EXECUTIVE PROGRAM

The actual machine program consists of five main sections:

1. Internal Control: Coordinates and ties together the other portions of the executive monitor. It also requests other program modules from the system file and provides for operator override.

2. Schedule: Accepts pre-readout information concerning the data to come and establishes the time schedule and sequence of program modules to be consulted for that orbit.

3. Interrupt Interpreter: Diagnoses the interrupt from the standpoint of source and reason and directs the computer to the appropriate action. Interrupts may come from the clock, from the direct data connection interrupt wire, from the external interrupt or from regular channel commands.

4. Logical External Communicator: On the basis of clock alarms or otherwise, sends commands to control the mode of operation of the nondigital hardware. This routine is linked to the interrupt interpreter.

5. Clock Manager: Provides the means for setting the interval timer and causing clock interrupts and also fulfills program requests for time information.

However, the executive program is more than a series of machine instructions which controls the flow of information through the computer and the interaction between the main program modules. It is, in fact, the guiding philosophy of the entire data processing system. The program consists of a rigid set of rules and controls which determine the manner in which the various resources available are utilized in the satisfaction of the system design characteristics. At first glance, it seems paradoxical that the Nimbus system, always on the side of growth and flexibility should make such precise demands at the very heart of the system. Nevertheless, without such a firm foundation our system would be at best unstable and at worst completely unable to meet the specific requirements of growth and flexibility from within the physical and environmental constraints imposed by the system. The original form of the executive program will be overlaid by many accretions, some of which may be major before we are through. The executive program will be the subject of a future paper.

#### SYSTEM DESCRIPTION

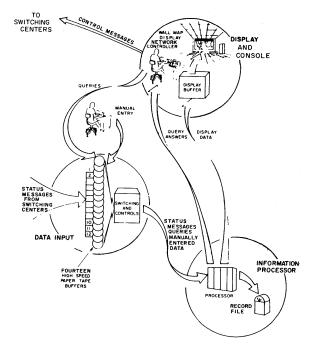

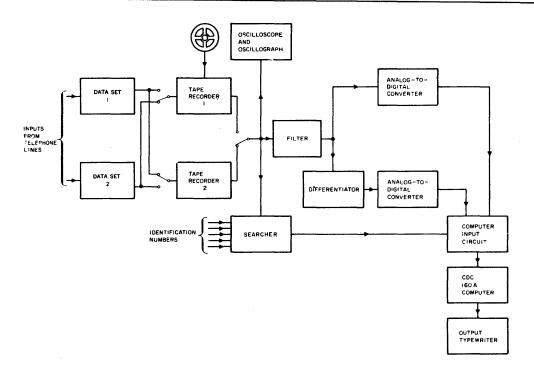

The functioning of the data processing system is best illustrated through a description of the events that occur during one orbital cycle. As the information is received at the common carrier terminal equipment, the data are directed into three main channels.

1. Into a monitor tape recorder which at all times records the input from the transmission lines at appropriate speeds. All data are stored as received providing a safeguard against loss of data in case of breakdown of the processing equipment. This tape also serves as an archive copy until replaced by the CDA master tape.

2. Into a picture gridding and reproduction branch, in which the analog AVCS signals can be directly reproduced in pictorial form, with the insertion of computed latitude, longitude and geographic boundary grids and appropriate legends.

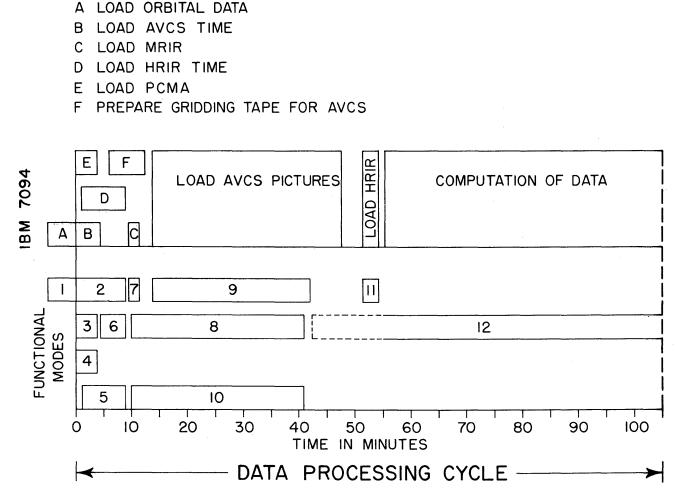

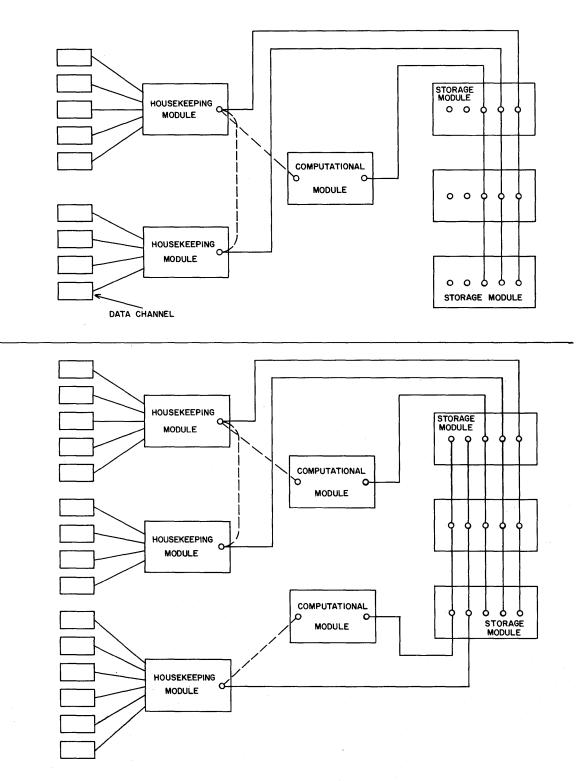

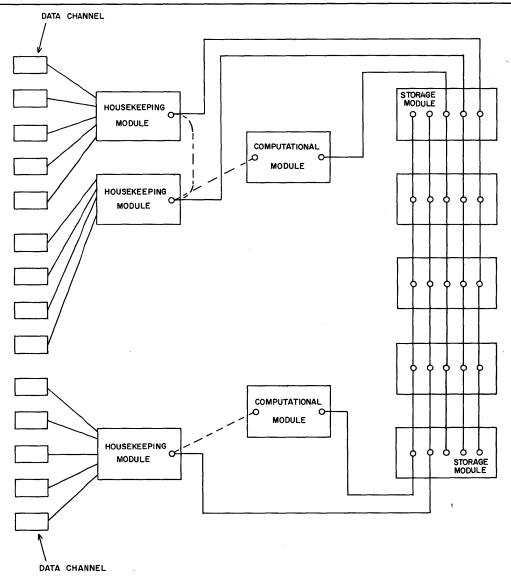

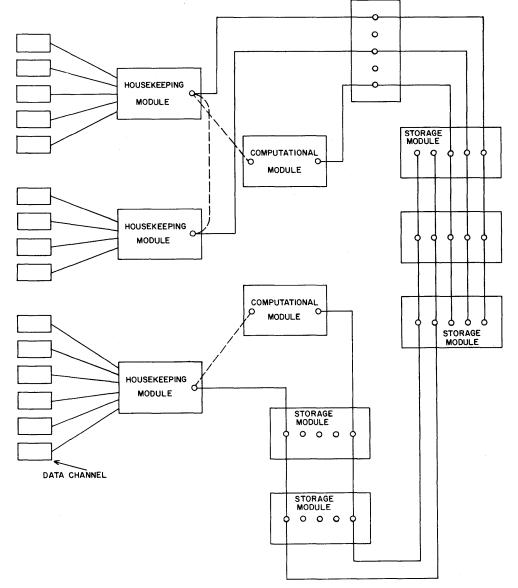

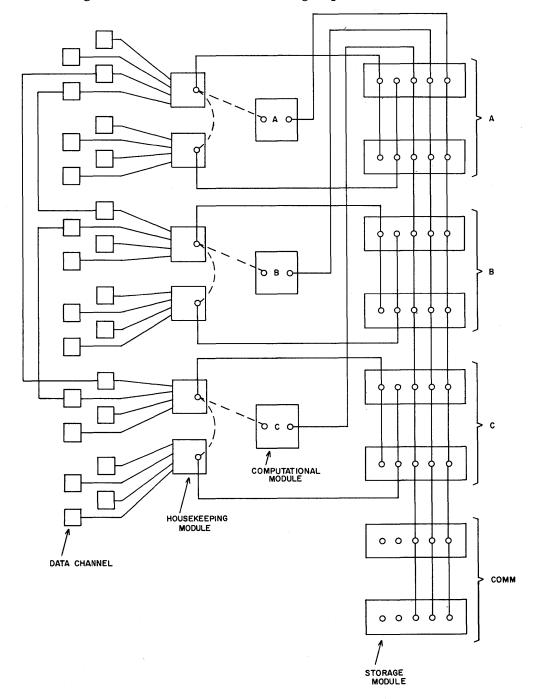

3. Into a digitizing subsystem where the incoming data are formated, converted from analog to digital and transferred to the computers.