# Proceedings of the

# WESTERN JOINT COMPUTER CONFERENCE

May 3-5, 1960 San Francisco, Calif.

Sponsors:

THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices THE ASSOCIATION FOR COMPUTING MACHINERY

# PROCEEDINGS OF THE WESTERN JOINT COMPUTER CONFERENCE

PAPERS PRESENTED AT THE JOINT IRE-AIEE-ACM COMPUTER CONFERENCE SAN FRANCISCO, CALIF., MAY 3-5, 1960

Sponsors

THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers

THE AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices

THE ASSOCIATION FOR COMPUTING MACHINERY

Published by

WESTERN JOINT COMPUTER CONFERENCE

## ADDITIONAL COPIES

Additional copies may be purchased from the following sponsoring societies at \$3.00 per copy. Checks should be made payable to any one of the following societies:

INSTITUTE OF RADIO ENGINEERS 1 East 79th Street, New York 21, N. Y.

AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS 33 West 39th Street, New York 18, N. Y.

ASSOCIATION FOR COMPUTING MACHINERY 2 East 63rd Street, New York 21, N. Y.

> © 1960 by National Joint Computer Committee

.

Manufactured in the U.S.A. by the National Press, Palo Alto, California

## LIST OF EXHIBITORS

| Aeronutronic Division of Ford Motor Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMP Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Ampex Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Anelex Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Automatic Electric Sales Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Beckman/Berkeley Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bendix Computer Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Benson-Lehner Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bryant Computer Products Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Burroughs Corp., Electrodata Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C-E-I-R, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C. P. Clare & Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Clary Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Computer Control Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Computer Systems, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Computronics, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Consolidated Electrodynamics Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Control Data Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cook Elec. Co., Data-Stor. Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Datamation, Magazine of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Di/An Controls, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Digital Equipment Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Digitronics Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Electronic Associates, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Electronic Engineering Co. of California                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fairchild Semiconductor Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ferranti Electric, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Friden, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Industrial Tubular Equipment Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| International Business Machines Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Laboratory for Electronics, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Librascope, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Minneapolis-Honeywell Regulator Co., Datamatic Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F. L. Moseley Co.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Moxon Electronics Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The National Cash Register Co., Electronics Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| North American Aviation, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pacific Telephone Co.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Packard-Bell Computer Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Philco Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Potter Instrument Co., Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Raytheon Mfg. Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Remington-Rand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Royal McBee Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Stromberg-Carlson Co.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| System Dev. Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Tally Register Corp.    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . <th< td=""></th<> |

| Telemeter Magnetics, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Teletype Corp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Thompson-Ramo-Wooldridge, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| John Wiley & Sons, Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Wright Engineering Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Newport Beach, California Harrisburg, Pennsylvania Redwood City, California Boston, Massachusetts Northlake, Illinois Richmond, California Los Angeles, California Santa Monica, California Springfield, Vermont Pasadena, California Arlington, Virginia Chicago, Illinois San Gabriel, California Los Angeles, California New York, New York Denver, Colorado Pasadena, California Minneapolis, Minnesota Skokie, Illinois Los Angeles, California Boston, Massachusetts Maynard, Massachusetts Albertson, L. I., New York Long Branch, New Jersey Santa Ana, California Mountain View, California Hempstead, New York San Leandro, California North Hollywood, California New York, New York Boston, Massachusetts Glendale, California Newton Highlands, Mass. Pasadena, California Beverly Hills, California Hawthorne, California El Segundo, California San Francisco, California Los Angeles, California Philadelphia, Pennsylvania Plainview, L. I., New York Waltham, Massachusetts New York, New York Port Chester, New York San Diego, California Santa Monica, California Seattle, Washington Culver City, California Chicago, Illinois Canoga, Park, California New York, New York Pasadena, California

## NATIONAL JOINT COMPUTER COMMITTEE

#### Chairman

H. H. Goode Bendix Systems Division Ann Arbor, Michigan

Secretary-Treasurer

Miss M. R. Fox National Bureau of Standards Department of Commerce Washington 25, D. C.

IRE Representatives

H. H. Goode Bendix Systems Division Ann Arbor, Michigan

F. E. Heart Lincoln Laboratories Lexington, Massachusetts

W. H. Ware RAND Corporation Santa Monica, California

W. Buchholz IBM Corporation Poughkeepsie, New York

### ACM Representatives

P. Armer RAND Corporation Santa Monica, California

W. M. Carlson E. I. Du Pont de Nemours Wilmington 98, Delaware

J. D. Madden System Development Corp. Santa Monica, California

H. R. J. GroschCorp. for Economic and Industry Research, Inc.Los Angeles 46, California

#### Headquarters Representatives

J. Moshman Corp. for Economic and Industry Research, Inc. Arlington 2, Virginia R. S. Gardner American Institute of Electrical Engineers New York 18, New York Vice-Chairman

P. Armer RAND Corporation Santa Monica, California

#### **AIEE Representatives**

R. A. Imm IBM Corporation Rochester, Minnesota

R. R. Johnson General Electric Co. Phoenix, Arizona

C. A. R. Kagan Engineering Research Center Western Electric Co., Inc. Princeton, New Jersey

S. Rogers c/o Convair, Mail Zone 6-156 San Diego, California

Ex-Officio Representatives

R. W. Hamming(ACM) Bell Telephone Laboratories Murray Hill, New Jersey

M. Rubinoff (AIEE) Philco Corporation Government and Industrial Div. Philadelphia 44, Pennsylvania

R. O. Endres (IRE) Rese Engineering Inc. Philadelphia, Pennsylvania

•

L. G. Cumming The Institute of Radio Engrs. New York 21, New York

# WESTERN JOINT COMPUTER CONFERENCE COMMITTEE

| General Chairman                | R. M. Bennett, Jr., IBM Corp., San Jose, California                                                                                                                                               |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vice-Chairman                   | G. A. Barnard, Ampex Corp., Redwood City, California                                                                                                                                              |

| Secretary-Treasurer             | J. P. Fernandez, Chairman, IBM Corp., San Jose, California<br>D. E. Eliezer, IBM Corp., San Jose, California                                                                                      |

| Technical Program               | <ul> <li>H. M. Zeidler, Chairman, Stanford Research Institute,<br/>Menlo Park, California</li> <li>J. E. Sherman, Lockheed M. S. D., Sunnyvale, California</li> </ul>                             |

| Publications                    | D. D. Willard, Chairman, IBM Corp., San Jose, California<br>E. T. Lincoln, IBM Corp., San Jose, California                                                                                        |

| Publicity                       | C. Elkind, Chairman, Stanford Research Institute,<br>Menlo Park, California<br>N. S. Jones, Friden, Inc., San Leandro, California                                                                 |

| Exhibits                        | H. K. Farrar, Chairman, Pacific Telephone Co.,<br>San Francisco, California<br>J. W. Ball, Pacific Telephone Co., San Francisco, California                                                       |

| Registration                    | <ul> <li>H. N. Wells, Chairman, General Electric Co.,</li> <li>General Electric Computer Lab, Palo Alto, California</li> <li>J. E. Stokdyk, Hewlett-Packard Co., Palo Alto, California</li> </ul> |

| Printing and Mailing            | R. A. Isaacs, Chairman, Philco Corp., Palo Alto, California<br>R. E. Wye, Philco Corp., Palo Alto, California                                                                                     |

| Women <sup>*</sup> s Activities | Miss Mary Fraser, Chairman, IBM Corp., San Jose, California<br>Mrs. Eleanor Schmidt, IBM Corp., San Jose, California                                                                              |

| Local Arrangements              | G. E. Morrison, Smith-Corona Marchant, Inc., Oakland, Calif.                                                                                                                                      |

# TABLE OF CONTENTS

| COMPUTER ORGANIZATION TRENDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| <ol> <li>1.1 "The Historical Development and Predicted State-of-the-Art of the General Purpose<br/>Digital Computer" By C. P. Bourne and D. Ford, Stanford Research Institute</li> <li>1.2 "The Harvest System" By P. S. Herwitz and J. H. Pomerene, IBM Corporation</li> <li>1.3 "Organization of Computer SystemsThe Fixed Plus Variable Structure Computer"<br/>By Gerald Estrin, University of California, Los Angeles</li> <li>1.4 "Horizons in Computer Systems Design" By W. F. Bauer, Ramo-Wooldridge Corporation</li> </ol> | 33             |

| DATA RETRIEVAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| <ul> <li>2.1 "A Multi-Level File Structure for Information Processing" By L. Miller, J. Minker,<br/>W. G. Reed, and W. E. Shindle, RCA</li> <li>2.2 "Symbolic Logic in Language Engineering" By H. M. Semarne, Douglas Aircraft Co., Inc.</li> <li>2.3 "The Fact CompilerA System for the Extraction, Storage, and Retrieval of Information"<br/>By Charles Kellogg, Ramo-Wooldridge Corporation</li> </ul>                                                                                                                          | 53<br>61<br>73 |

| COMPONENTS AND TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

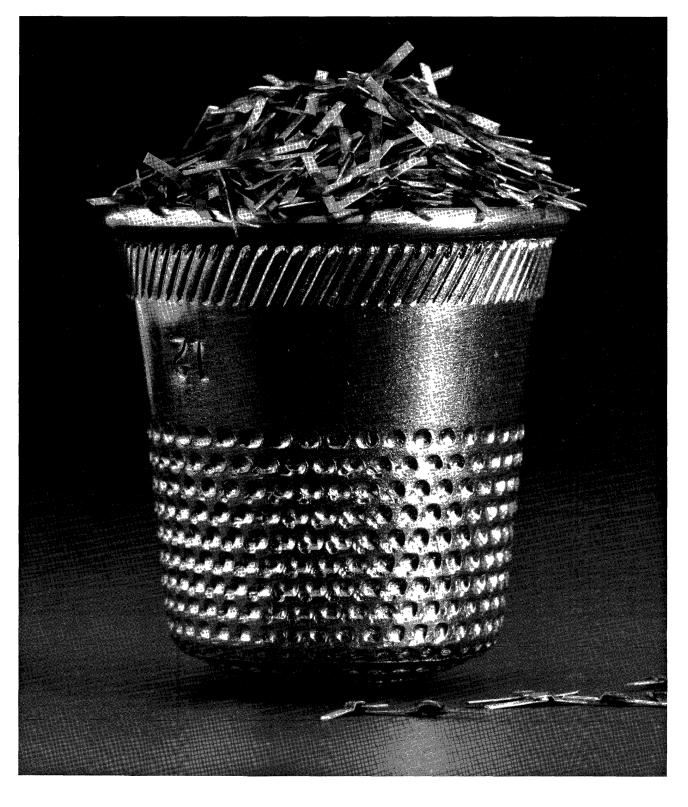

| <ul> <li>3.1 "A Word-oriented Transistor Driven Non-Destructive Read-Out Memory" By T. C. Penn and D. G. Fischer, Texas Instruments, Inc.</li> <li>3.2 "Unifluxor: A Permanent Memory Element" By A. M. Renard, Aeronutronics, and W. J. Neumann, Remington-Rand Univac.</li> <li>3.3 "Characteristics of a Multiple Magnetic Plane Thin Film Memory Device" By K. D. Broadbent, S. Shohara, and G. Wolfe, Jr., Hughes Aircraft Company</li> </ul>                                                                                   | 83<br>91<br>97 |

| ANALOG EQUIPMENT**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| <ul> <li>4.1 "Analog Time Delay System" By C. D. Hofmann and H. L. Pike, Convair Astronautics 4.2 "DAFT: A Digital/Analog Function Table" By R. M. Beck and J. M. Mitchell, Packard-Bell Computer Corp</li></ul>                                                                                                                                                                                                                                                                                                                     | 109            |

| LEARNING AND PROBLEM-SOLVING MACHINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100            |

| <ul> <li>5.1 "Recognition of Sloppy, Hand-printed Characters" By W. Doyle, Lincoln Laboratory, MIT.</li> <li>5.2 "Empirical Explorations of the Geometry Theorem Machine" By H. Gelernter, J. R. Hansen, and D. W. Loveland, IBM Corporation</li></ul>                                                                                                                                                                                                                                                                               |                |

| ANALOG TECHNIQUES**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| <ul> <li>6.1 "Analog Computer Techniques for Plotting Bode and Nyquist Diagrams" By G. A. Bekey and<br/>L. W. Neustadt, Space Technology Laboratories</li></ul>                                                                                                                                                                                                                                                                                                                                                                      | 173            |

| TRENDS IN COMPUTER APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| <ul> <li>7.1 "Data ProcessingWhat Next?" By J. M. Salzer, Ramo-Wooldridge Corporation</li> <li>7.2 "The Outlook for Machine Translation" By F. L. Alt, National Bureau of Standards</li> <li>7.3 "Computers for Artillery" By Lt. Col. L. R. van de Velde, U. S. Army Artillery &amp; Missile School, Fort Sill</li></ul>                                                                                                                                                                                                            | 203            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

\_\_\_\_\_

**<sup>\*\*</sup>**Participation by Simulation Councils, Inc.

# TABLE OF CONTENTS, continued

| LOGI         | CAL DESIGN                                                                                                                                                                                       | Page |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|              | "Communications Within a Polymorphic Intellectronic System" By G. P. West and R. J. Koerner, Ramo-Wooldridge                                                                                     | 225  |

| <u>8.2</u>   | "Encoding of Incompletely Specified Boolean Matrices" By T. A. Dolotta and E. J. McClus-<br>key, Jr., Princeton University.                                                                      | 231  |

| 8.3          | "A Built-in Table Lookup Arithmetic Unit" By R. C. Jackson, W. H. Rhodes, Jr., W. D. Winger, and J. G. Brenza, IBM Corporation.                                                                  | 239  |

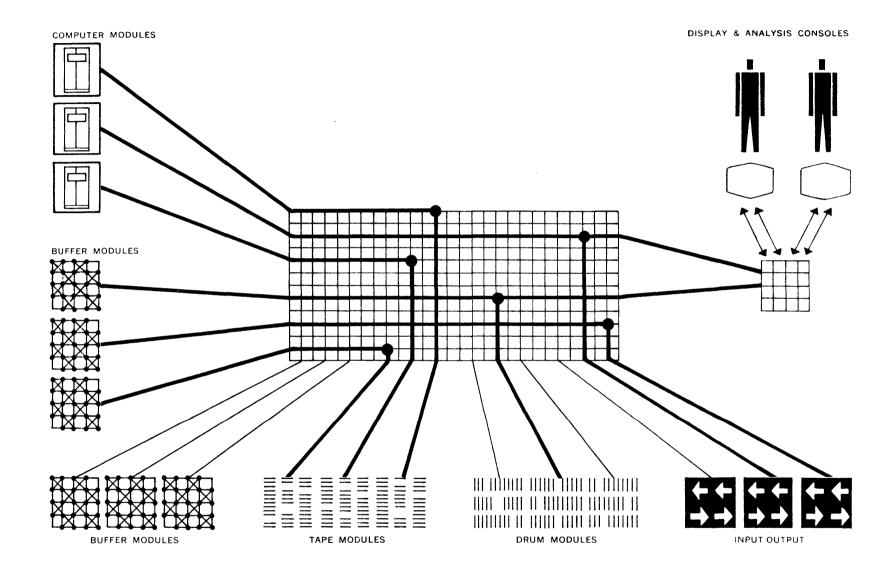

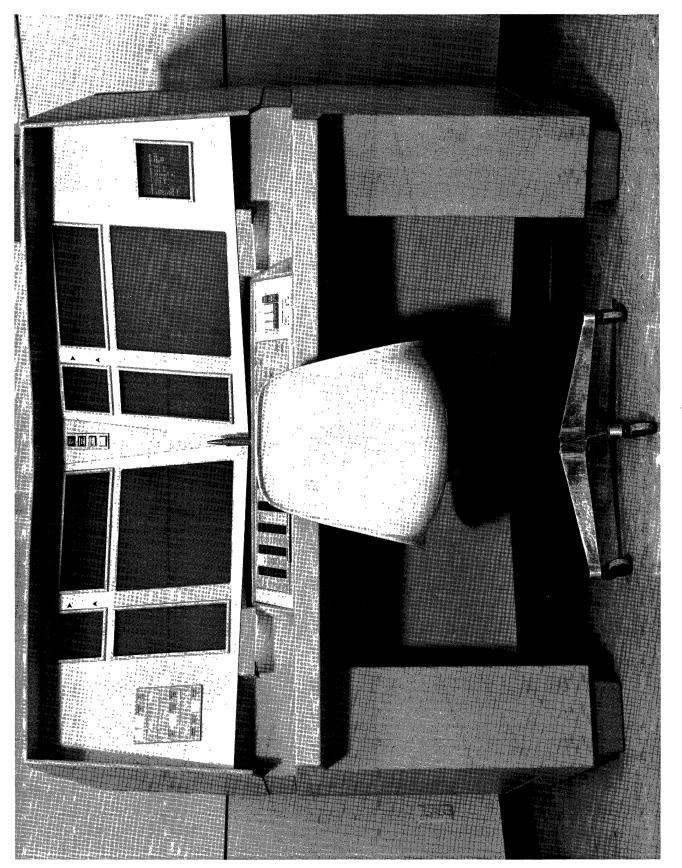

| DESI         | GN, PROGRAMMING, AND SOCIOLOGICAL IMPLICATIONS OF MICROELECTRONICS                                                                                                                               |      |

|              | <ul> <li>"On Microelectronic Components, Interconnections, and System Fabrication" By K. R.<br/>Shoulders, Stanford Research Institute</li></ul>                                                 | 251  |

|              | By J. H. Holland, University of Michigan                                                                                                                                                         | 259  |

|              | The Rand Corporation                                                                                                                                                                             | 267  |

|              | of California, Berkeley                                                                                                                                                                          | 283  |

| ANAI         | LOG APPLICATIONS**                                                                                                                                                                               |      |

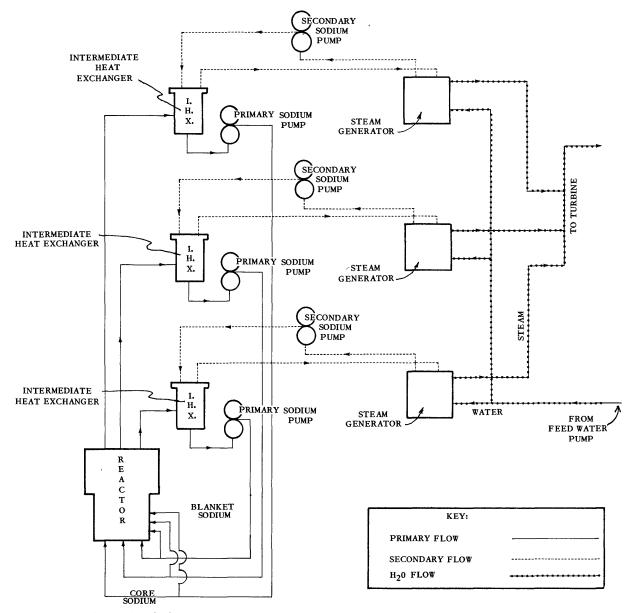

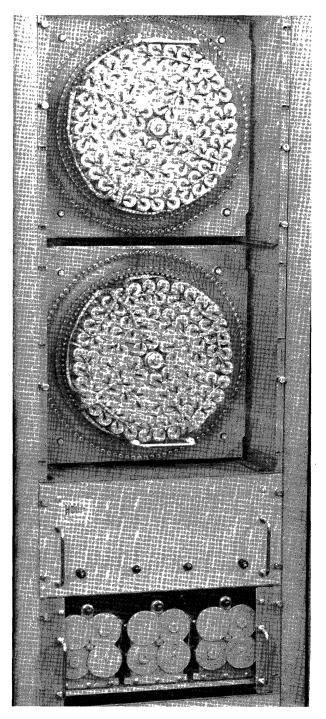

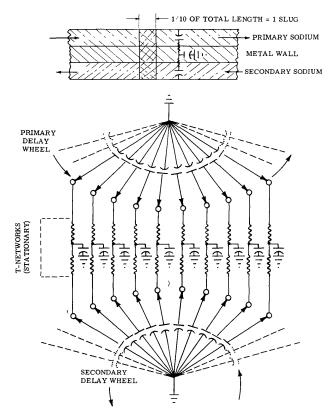

|              | "Real-Time Automobile Ride Simulation" By R. H. Kohr, General Motors Corporation<br>"Analog Computer Serves as Both Systems Analysis Tool and Operator Training Facility                         |      |

| 10.3         | for Enrico Fermi Atomic Power Plant" By S. N. Irwin and R. Kley, Holley Carburetor Co.<br>"ANATRANFirst Step in Breeding the DIGINALOG" By L. Ohlinger, Norair Division,<br>Northrop Corporation | 301  |

| PROG         | GRAMMING SYSTEMS                                                                                                                                                                                 | 010  |

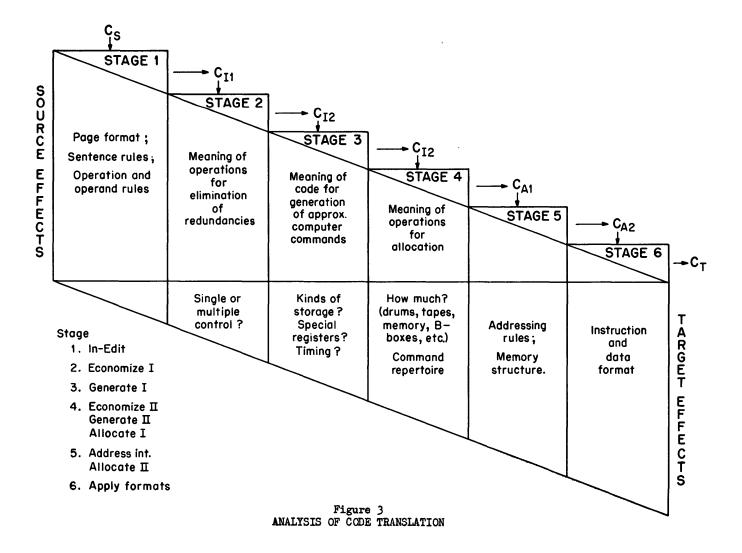

| ·····        | "Man-to-Machine Communication and Automatic Code Translation" By A. W. Holt, on leave                                                                                                            |      |

|              | from Remington-Rand Univac to the Moore School of Electrical Engineering, and                                                                                                                    |      |

|              | W. J. Turanski (deceased)                                                                                                                                                                        |      |

| 11.0         | Economic and Industrial Research, Inc.                                                                                                                                                           | 345  |

| INPU         | T-OUTPUT AND COMMUNICATIONS                                                                                                                                                                      |      |

| 12.1<br>12.2 | "A Line-Drawing Pattern Recognizer" By L. D. Harmon, Bell Telephone Laboratories "Automatic Store and Forward Message Switching System" By T. L. Genetta, H. P. Guerber,                         | 351  |

|              | and A. S. Rettig, RCA                                                                                                                                                                            | 365  |

|              | and J. J. Stone, A. B. Dick Company                                                                                                                                                              | 371  |

|              |                                                                                                                                                                                                  |      |

**\*\***Participation by Simulation Councils, Inc.

## FOREWORD

The 1960 Western Joint Computer Conference met in San Francisco for the third time. Interest in these conferences has been increasing steadily along with the impressive growth of the computer industry in the San Francisco Bay area. Manufacturing representation in the form of exhibits was the greatest in the history of the Western Joint Computer Conference.

In keeping with the theme of the 1960 Conference, "The Challenge of the Next Decade," the papers presented in the Proceedings were selected on the basis of trends in techniques and applications rather than descriptions of existing or about-to-be announced equipment. The philosophy of this year's conference committee was that of "taking stock" and attempting to "look ahead" to determine which way this dynamic industry is going. We have essentially reached a plateau where technology has given us a feel for the tremendous impact that this industry will have upon our everyday life. It seems desirable, occasionally, to pause and evaluate and, indeed, this in itself can justify the value of a conference.

This publication contains the papers presented at the 1960 Western Joint Computer Conference, and was available at the time of the Conference.

R. M. Bennett General Chairman 1960 Western Joint Computer Conference

#### THE HISTORICAL DEVELOPMENT, AND PREDICTED STATE-OF-THE-ART OF THE GENERAL-PURPOSE DIGITAL COMPUTER

By Charles P. Bourne and Donald F. Ford Computer Techniques Laboratory Stanford Research Institute Menlo Park, California

#### Summary

Some of the important characteristics of all the general-purpose digital computers that have ever been built, or are in the process of being built, have been collected together in order to show the changes in performance and characteristics during the passage of time. These collected data, as well as information regarding recent development work, have been used to extrapolate the characteristics and performance figures into the 1960-1965 era. The report considers such characteristics as add and multiply times, memory characteristics, pulse repetition rates, and internal system parameters.

The collected data seems to suggest that the majority of the computers developed between now and 1965 will show very little change in performance from that which was obtained during the last five years. However, a few research machines will definitely advance the technology, possibly as much as one order of magnitude for some of the characteristics. In appendix B there is a listing of approximately 300 different computers, in an attempt to provide an initial directory of the world's computers.

#### Introduction

This paper presents the results of a study that was conducted to answer the question, "What can be learned from a historical study of the development of general-purpose digital computers?" It was of interest to re-trace, in summary fashion, the development of the digital computer. It was also of interest to see if the development of any of the machine characteristics followed a pattern which would allow an extrapolation into the future. The study was restricted to the characteristics which describe the memory and central processor or arithmetic units, and did not consider input-output features.

The characteristics were examined from the viewpoint of a machine user, and not a machine designer or component specialist. That is, an attempt was made to describe the operational performance which the computer system provides the user, instead of concentrating on the details of the manner in which the logic is accomplished. For example, a comparison of typical execution times was studied, instead of looking at the switching times for the individual circuits. In a few instances, a study was made of some of the more hardware-oriented characteristics such as the pulse repetition rate or "clock" rate, and the type of high-speed memory component used. The machine characteristics were obtained from several summary publications<sup>1,2</sup>, as well as numerous journal articles and the literature of manufacturers. The data for approximately 180 of the machines was checked by letters of verification from the equipment designers or manufacturers.

The machine characteristics which were examined are listed below. The definitions for these characteristics are included in Appendix A.

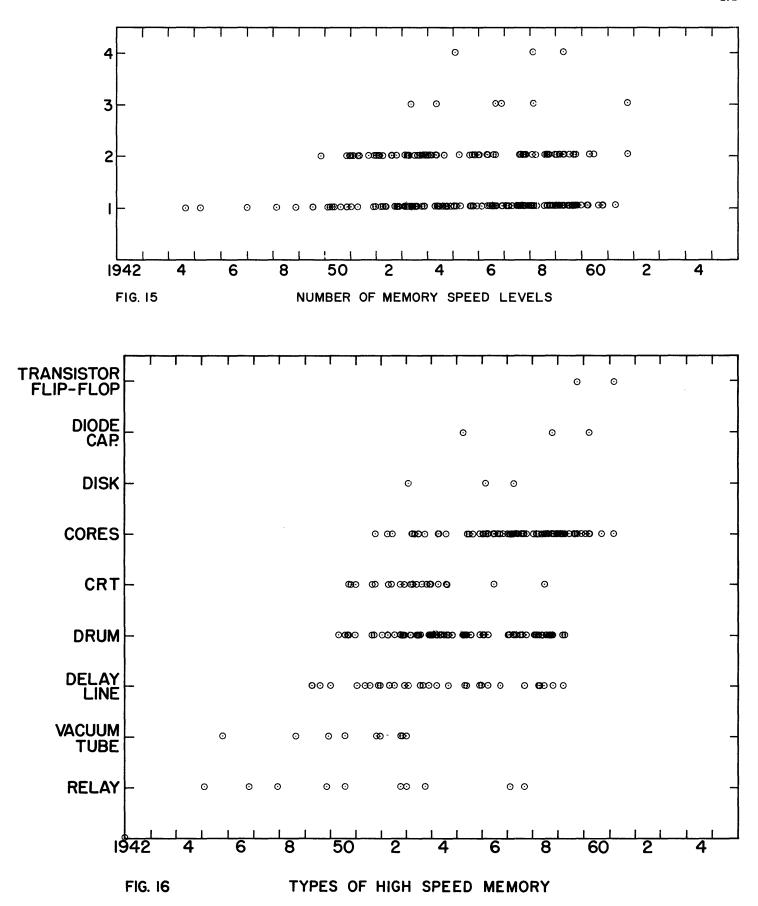

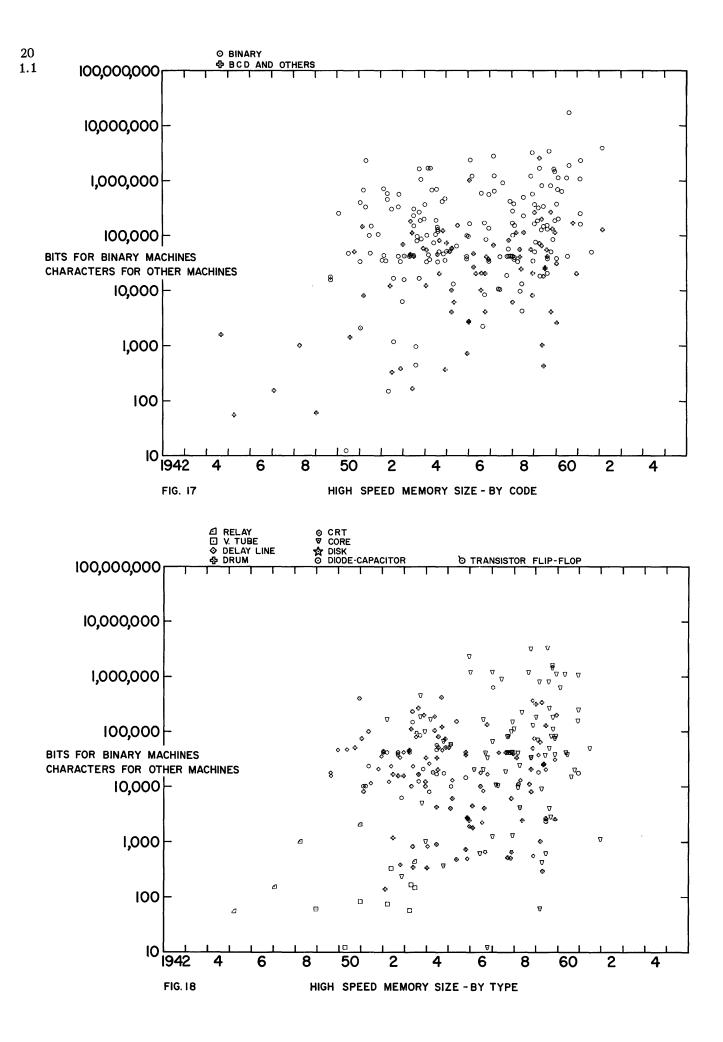

Number of addresses per instruction Number of index registers Number of decimal digits per instruction Number of decimal digits per data word Number of binary bits per instruction Number of binary bits per data word Internal clock rate Fixed point add time Fixed point multiply time Floating point add time Floating point multiply time Number of memory speed levels Types of high speed memory High speed memory size High speed memory access time Total internal memory size

#### Summary Comparisons of Computers to Date

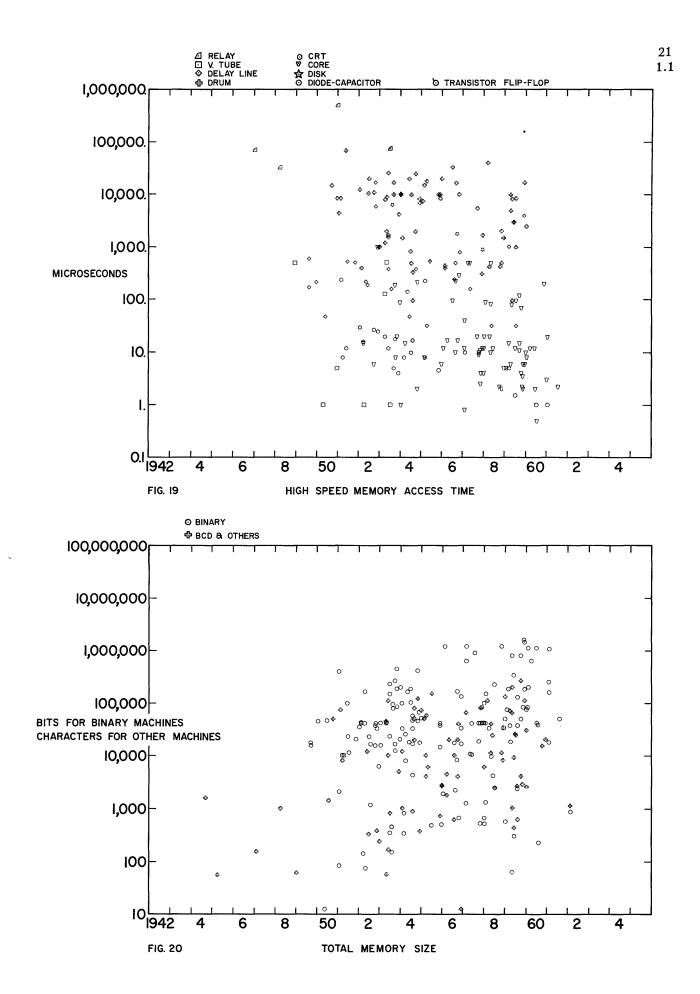

Each of the machine characteristics was plotted against a horizontal calendar scale in order to observe the changes and rates of change for the parameters. A single point was plotted for each different machine type to show the earliest date that the system performed with the described characteristics. Points were plotted for all the available data, however, in many cases, various parameters were not described in the literature. For this reason, all the plots do not contain the same number of points.

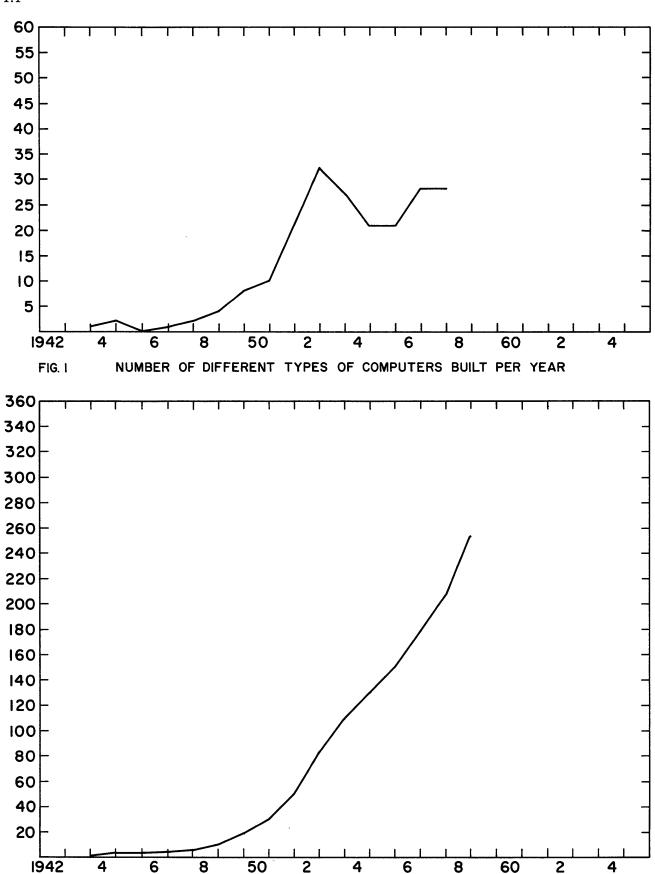

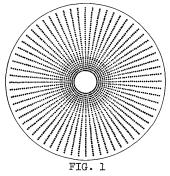

The actual growth curve to show the rate at which new computer models have been developed is shown in Fig. 1. Fig. 2 shows the cumulative number of different computers which have been developed. In addition to the computers which are shown on Fig. 1 and 2, approximately 65 machines were not plotted, since an accurate operational date could not be determined. It can be seen that new computer models are being developed in continually increasing numbers, and that this trend will probably continue into the future. The increasing number of new computer models is due to several factors, but it would appear that the major reasons are those which are listed below:

- 2 1.1

- 1. Parallel efforts by commercial organizations acting in the spirit of free enterprise, with each organization competing for a share of the market with its own particular model. This is fostered by the increasing market for computers.

- 2. Continued marketing pressures to improve the performance characteristics of a particular computer model, or to produce more competitive equipment.

- 3. Efforts by universities and some industrial concerns to build their own computers in order to develop a technical competence in this field, or to obtain an inexpensive computing facility.

- 4. The emergence of a computer industry in areas which were late in starting in this field. For example, Japan built no digital computers before 1953; since that time however, she has developed 29 different computers, and shows every indication of developing more. The European countries are also developing rapidly as computer manufacturers.

#### Internal Characteristics

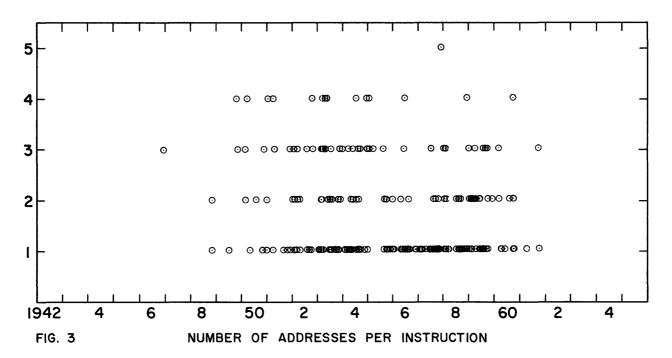

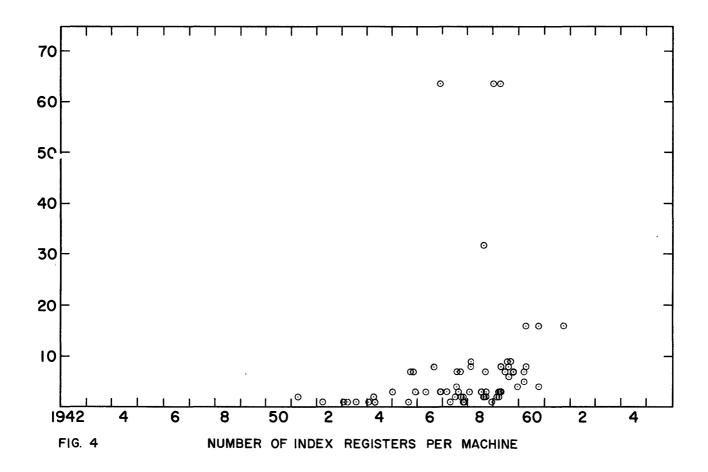

There has been very little uniformity or indication of trends for such internal characteristics as the number of addresses per instruction and the number of characters per data word or instruction. There have been some slight trends noticed in the number of index registers and the internal clock rate.

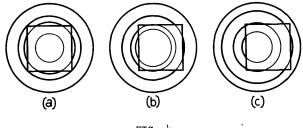

- 1. <u>Number of Addresses per Instruction</u> Figure 3 shows that the single-address instruction is used more than any other type, although a large number of systems have used two-andthree-address systems. The four-address systems are definitely a minority; however, there is one instance of a five-address system. Future computers will probably follow the same pattern, with predominantly singleaddress format.

- Number of Index Registers Figure 4 shows 2. that there is a definite trend toward providing index registers (or "B-boxes") in increasing numbers for each computer. The use of a single index register is first noted in 1951. The first system with multiple index registers is noted in 1954. From that time on, systems became available with a greater number of registers, and in some cases this went as high as 64, 99, and 1024 index registers per machine. A large percentage of the future computers will probably have at least one index register. Index registers have proven to be effective for applications in both business and scientific computations, and will probably appear more frequently on both types of systems.

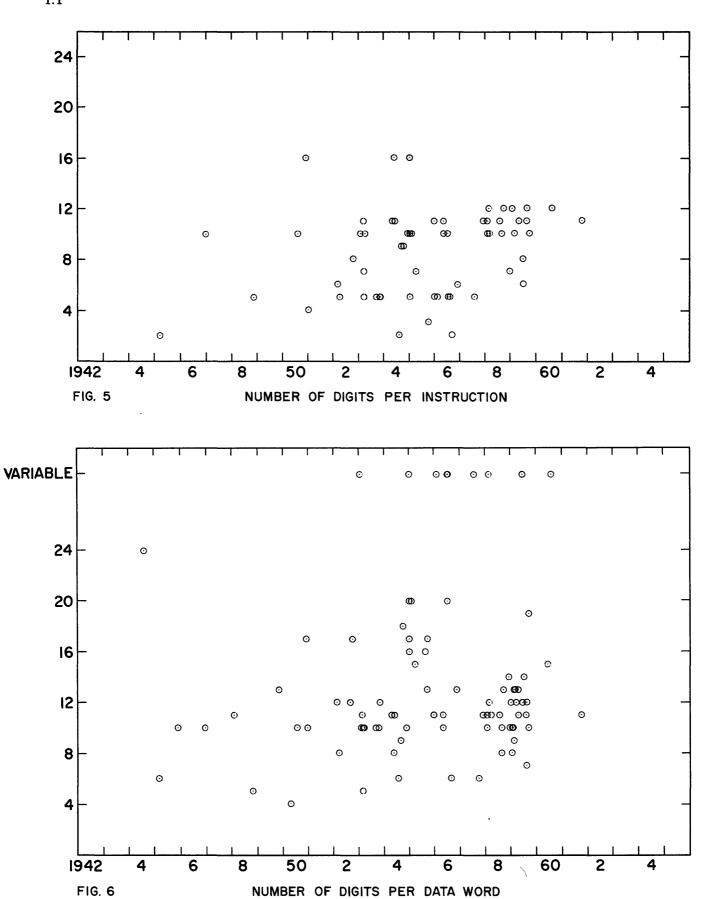

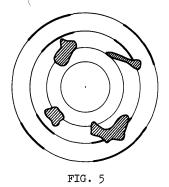

- 3. Decimal Digits per Instruction Figure 5 shows the data for the non-binary machines, to indicate the number of characters (decimal, octal, or alphabetic) per instruction. There does not appear to be any significant degree of uniformity, although more systems use 10 digits than any other number. Future computers will probably show the same large variety and lack of uniformity.

- 4. <u>Decimal Digits per Data Word</u> Figure 6 shows a large spread of values running from 4 to 24 digits. However, data words with 10, 11, or 12 digits appear to be the predominant choice. In 1953 the concept of a variable-length data word was introduced, and several systems utilized this feature after that. Future computers will probably continue to show a variety of values, but may use the 10, 11, or 12 digits more often than any other choice. There will probably be an increasing number of machines with variable-length data words.

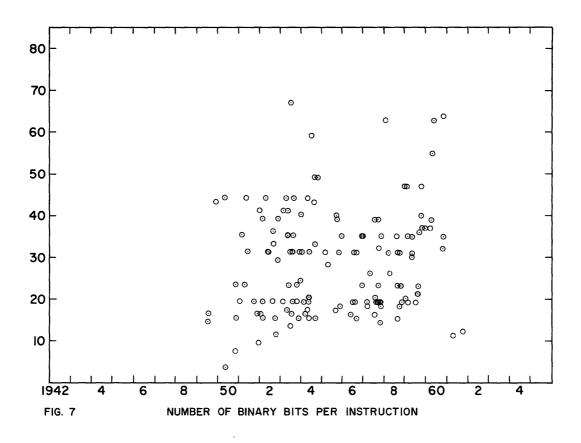

- 5. <u>Binary Bits per Instruction</u> Figure 7 shows the binary bits per instruction ranging from 4 to 68. There is a decided lack of uniformity, and no strong tendency toward a particular value. Future computers will undoubtedly follow the same large variety and lack of uniformity.

- 6. <u>Binary Bits per Data Word</u> Figure 8 shows the binary bits per data word ranging from 4 to 72. However, the majority of the systems have ranged between 30 and 50 bits per data word. Future computers will probably follow the same large variety and lack of uniformity.

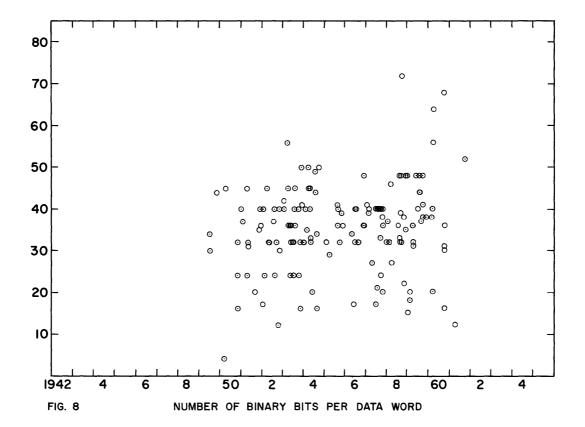

- Internal Clock Rate Figure 9 shows the in-7. ternal clock rate or pulse repetition rate. This is not a very good measure of the speed or power of a particular computer. This is because the great variety of ways in which the logic can be implemented (serial, parallel, and various combinations of serialparallel) can provide a large range of effective operating speeds. There are several examples of machines with nearly equal arithmetic speeds in spite of the fact that one of the machines has a clock rate which is five times slower than the clock rate of the other machine. Conversely, it might be noted that all of the IBM-700 series machines from 1953-1957 used a 1.0 Mc clock, even though there were marked differences in execution times. The clock rate data was included here to give an indication of the speeds of operation of the internal circuits. The fastest clock rate (10.0 Mc) is currently credited to the IBM-STRETCH, or Los Alamos computer, operates at speeds up to 500 Mc. The data shows, among other things, that people like round numbers, as indicated by the large number of 100 Kc and 1 Mc systems. The clock rates ranged from 200 cycles per minute to 10.0 Mc.

There are a moderate number of asynchronous systems (at least 28) which date back to the earliest machines. Because the asynchronous systems offer an inherent speed advantage over the clocked systems, they will probably find increasing use as better design techniques become available. There will be an increasing number of systems which use clock rates of 1 Mc or higher. There are already at least 47 systems which operate with pulse rates of 1 Mc or higher. These internal speeds can now be achieved fairly easily with current transistor and diode circuitry. However, because of the variety of possible applications, there will continue to be a large number of new systems with moderate internal speeds (100 - 500 Kc).

#### Arithmetic Speeds

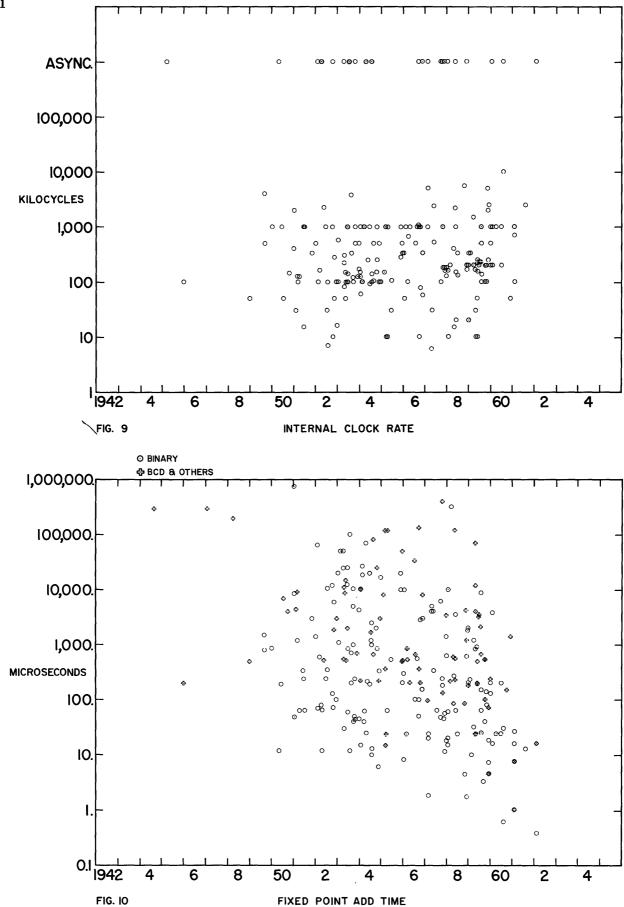

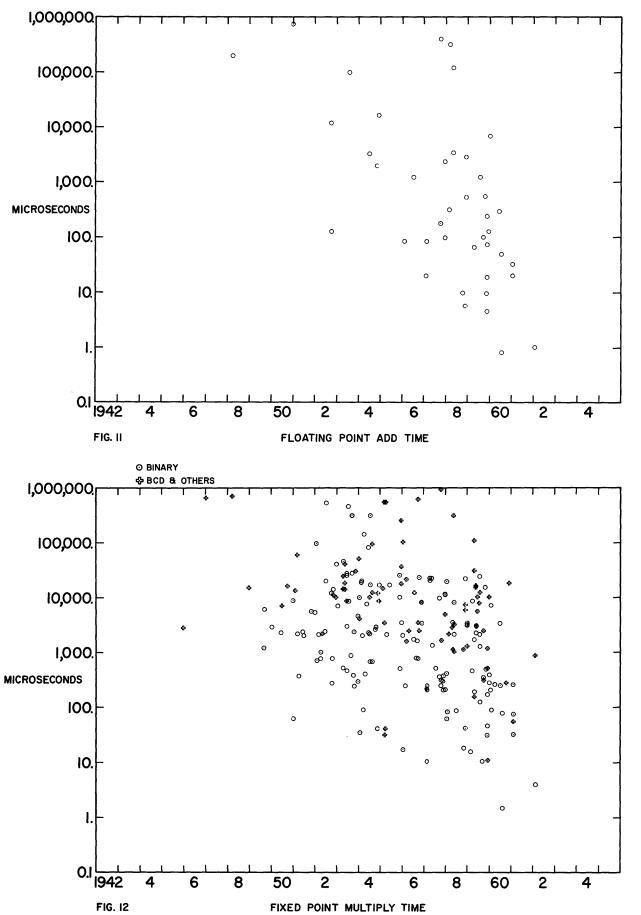

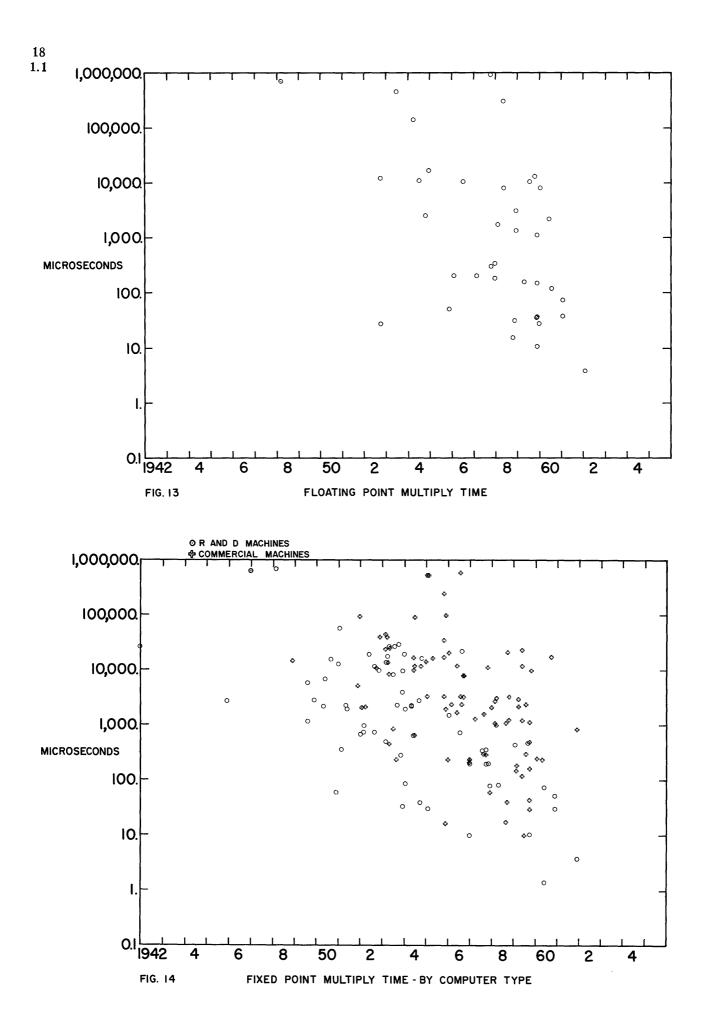

As defined in the Appendix, the execution times for the add and multiply operations are the effective operating times which a programmer would use in estimating the running time of a particular program. It can be seen from the pertinent figures (Fig. 10, 11, 12, 13) that there continues to be a wide range of execution times for all computers. This wide range of machine speeds, and characteristics, does not solely reflect the state-of-the-art or its trends. This range of values more accurately reflects the policy decisions and compromises which were made by each computer builder in his attempt to aim for a particular part of the commercial market, or produce (at minimum cost) a technical staff or computing facility. It is probably reasonable to state that not every builder tried to advance the state-of-the-art. Because of the fact that the collected data represented a heterogenous collection of intents and compromises, it was felt that it would be misleading to represent this data in some mathematical notation such as a yearly average or polynomial approximation.

The computers which have served to extend the state-of-the-art were primarily research and development machines, and were not designed primarily for commercial exploitation. The distinction in performance between systems which were built for research and systems which were built for commercial exploitation is shown in Fig. 14. This figure shows the fixed point multiply times for the machines in these two categories, and indicates that the state-of-the-art improvements were furnished entirely by the research machines. However, the commercial machines usually caught up with the fastest research machines in a matter of approximately five years.

Many builders have claimed the title of "world's most powerful computer" for their particular machine. It is impossible at this date to define accurately and unambiguously "computerpower". However, in an attempt to find out how long a machine could expect to retain this title, it was assumed that "computer-power" was proportional to the multiply time. With this assumption, it was a simple matter to determine the ten most powerful computers in each year from 1944 to the present. It was indeed an interesting observation to note that, on the average, a computer did not remain in the "top-ten" for more than three years.

For many reasons, there will be a continued effort to develop computers with faster execution speeds. However, it appears that faster speeds will not be achieved by extensions of the current hardware practices and techniques. It appears that new components and approaches must be developed if these speeds are to be attained. Meagher sums this up very nicely in the following paragraph.

"Let us first examine the need for new techniques which has resulted from our desire for higher speed. The existing circuits, with separate resistors, diodes, capacitors, and transistors, have a physical size which requires at least one cubic inch for a logical element. One such circuit has within itself a loop which constitutes an inductance with a shunt capacitance in the switching element. This LC circuit exhibits resonance. If the loop is about one-half inch in diameter, the inductance would be about 0.06 microhenry, and further, if the capacitance is 5 micro-micro-farad (both reasonable minimum values), the resulting resonant frequency would be about 300 Mc. Clearly it would be difficult to operate this circuit at an information frequency of more than about one-fifth the resonant frequency, or in other words, 60 Mc. We are already close to this frequency in some present computer circuits. Thus, faster circuits require either smaller size for "lumped-constant" techniques, or, alternatively, "distributed-constant" techniques. Low temperature circuit elements offer one possibility for extremely small size. Micro-wave techniques, the subject for the Symposium, offer the possibility of the distributedconstant approach.

To date, all of the circuits for storage and logic in the operating computers have employed a frequency band for pulse rates which starts at or near zero and extends to some upper limit. The upper limit for this base-band type of system appears to be about 50 Mc (see reference<sup>9</sup>). It would appear that some new techniques would have to be devised to achieve information pulse rates of greater than 50 or 100 Mc.

Microwave circuits for storage and logic functions have been demonstrated by Sterzer which operate at pulse rates of 100 Mc and a carrier frequency of 2,000 Mc; and by Ortel which operate with pulse rates of 500 Mc and a carrier frequency of 11,000 Mc. Ortel demonstrated a serial multiplier operating at a clock frequency of 160 Mc which multiplied two 8-digit binary numbers to form a 16-digit product in 1.6 microseconds. It was stated that it would be feasible to use the same microwave circuit with a clock frequency of 640 Mc to obtain a multiplication

time of 0.4 microseconds.

Billing<sup>6</sup> and Rudiger have stated that the use of the nonlinear capacitance of semiconductor diodes in parametron circuits also appear promising for high frequency operation. Experimental work has been conducted at frequencies up to 450 Mc, and theoretical studies seem to indicate that frequencies in the neighborhood of 30 Kmc should be possible.

Aside from economic problems, one of the major technical problems in achieving very high circuit speeds is that the time allocated to switch a signal through the circuit approaches the propagation time for any<sub>7</sub>electrical wave. This is stated very well by Leas<sup>7</sup> in the following paragraphs.

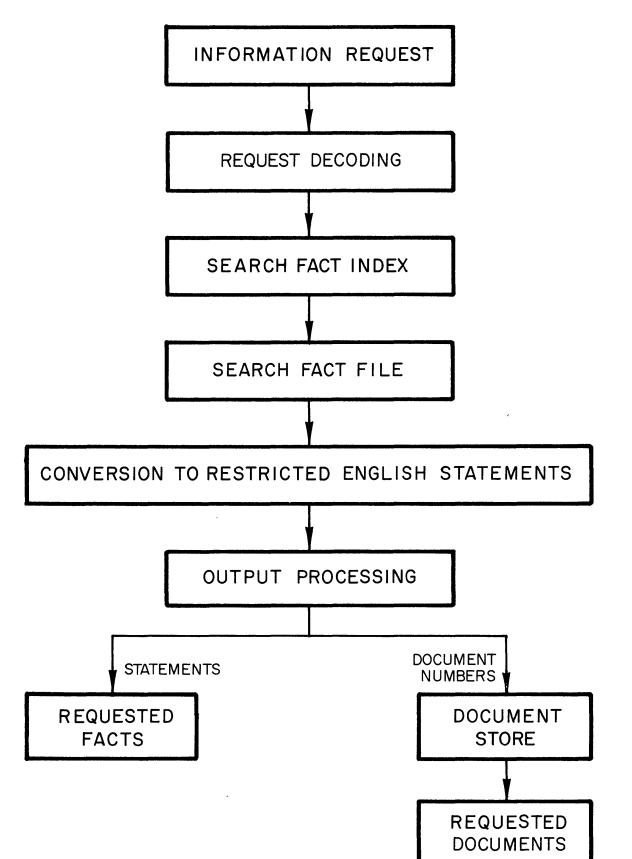

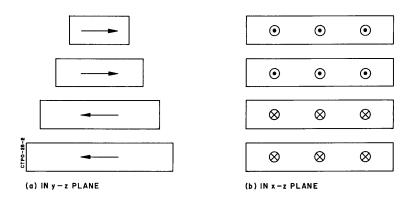

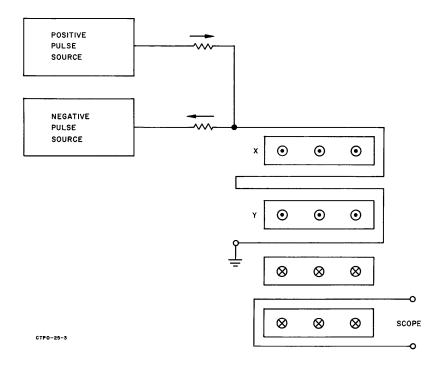

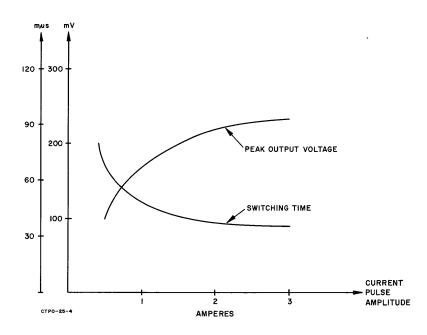

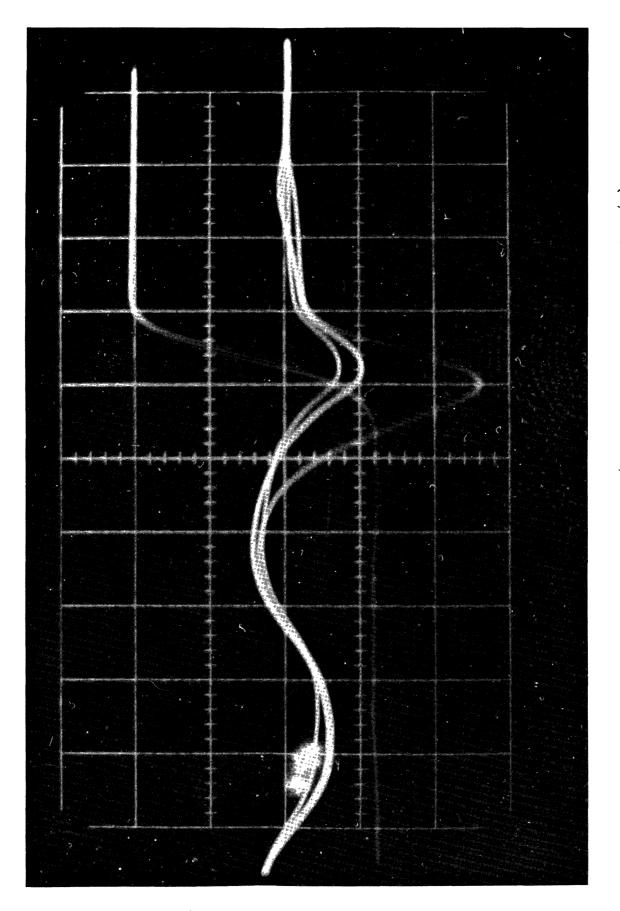

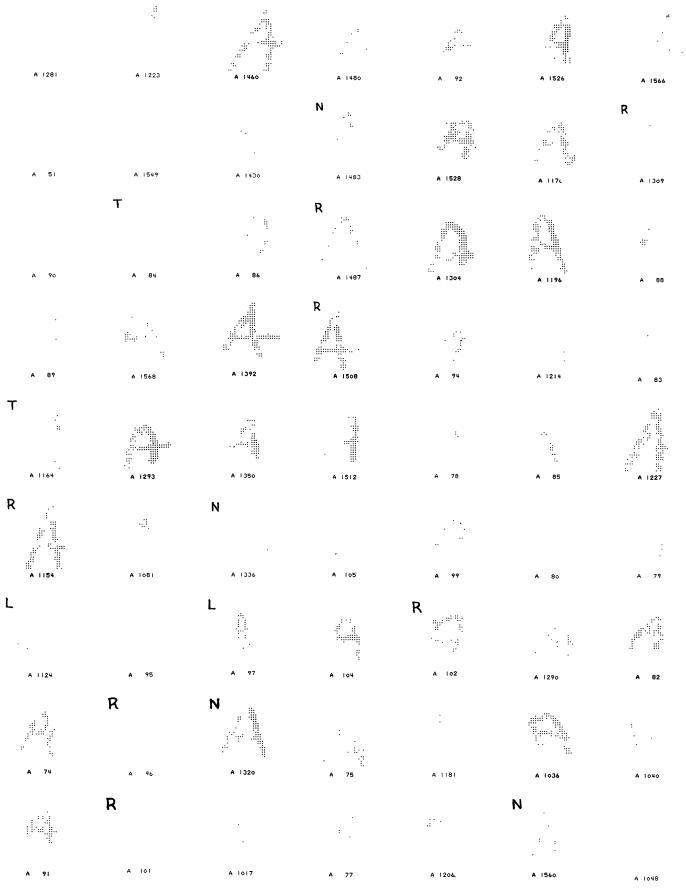

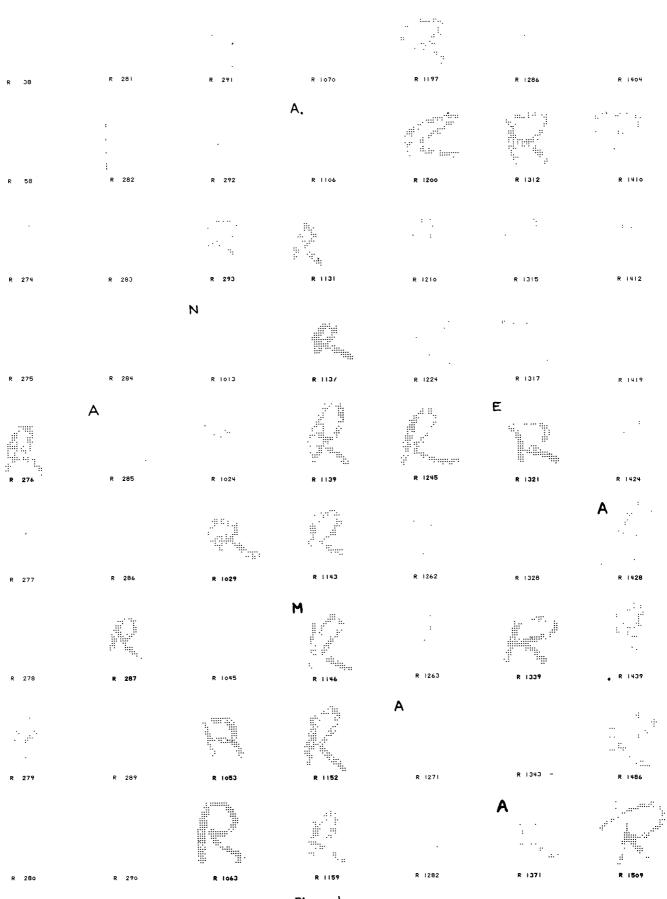

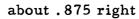

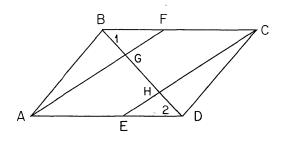

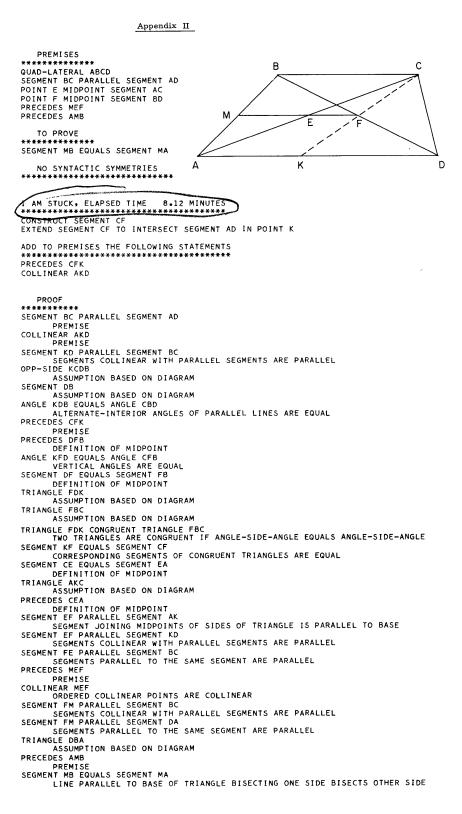

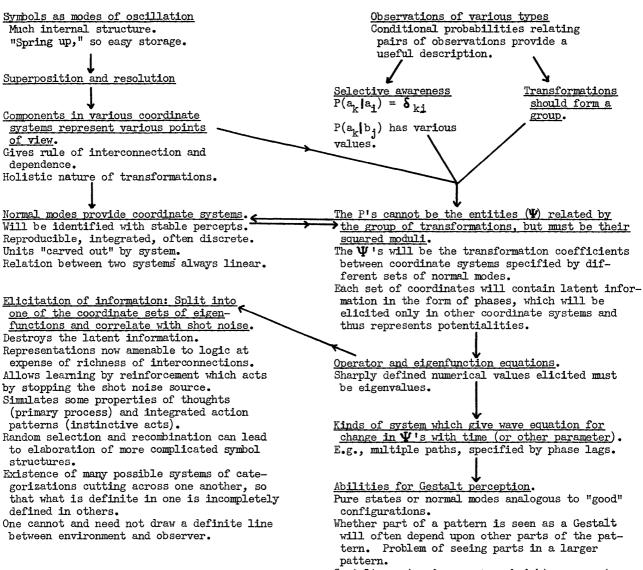

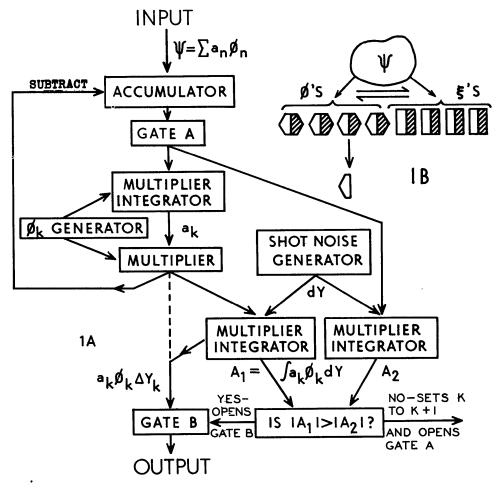

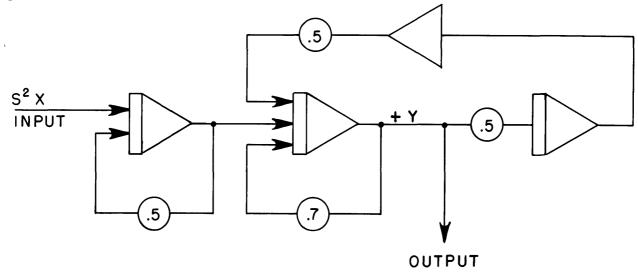

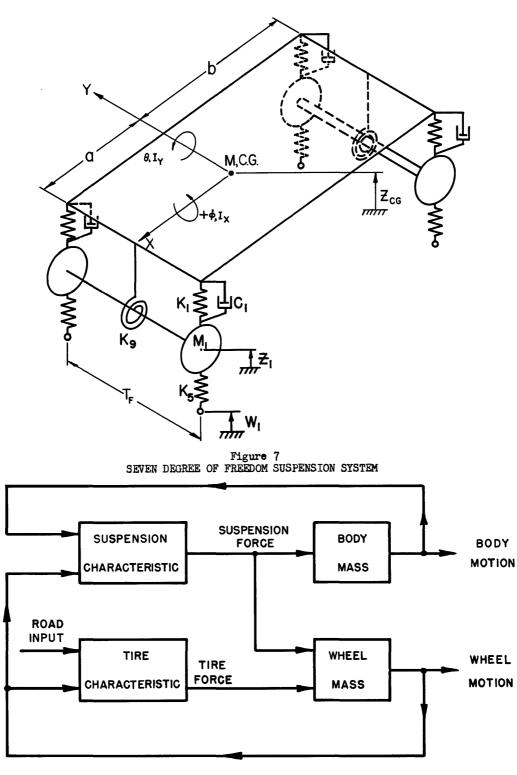

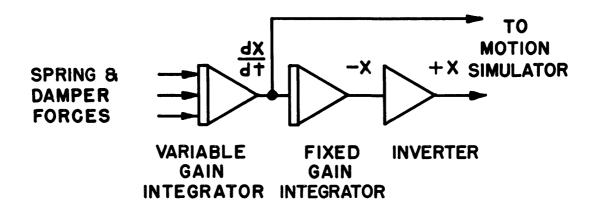

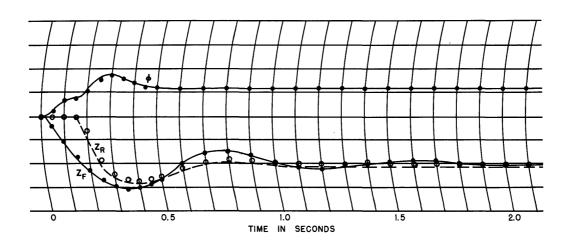

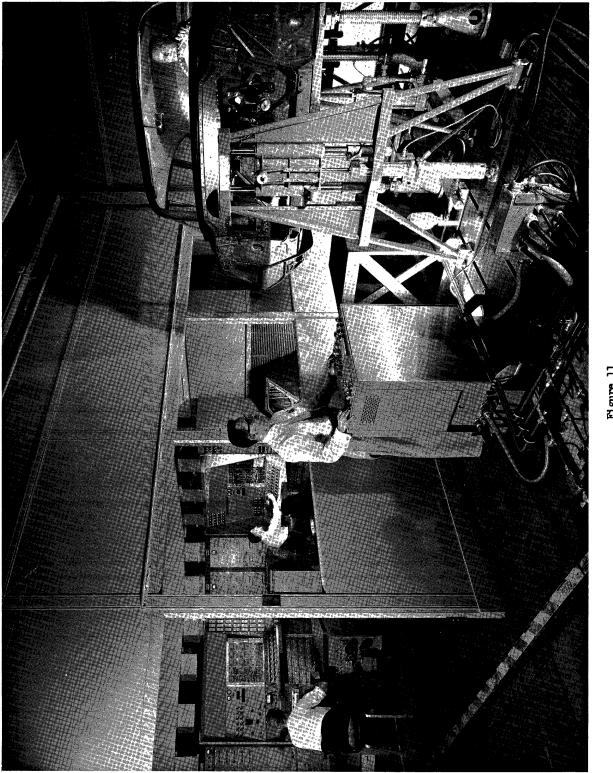

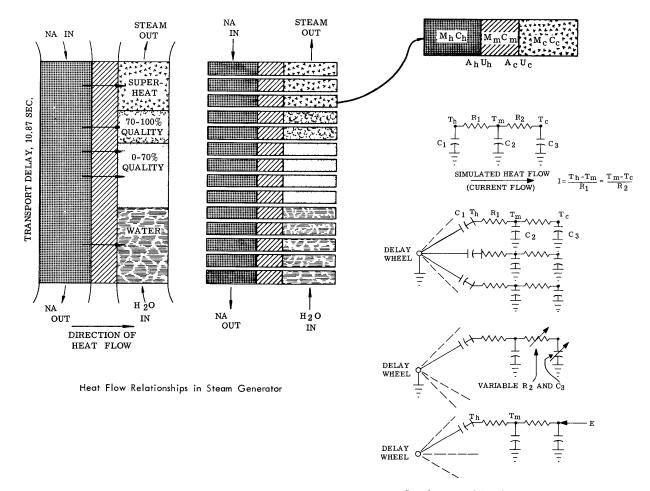

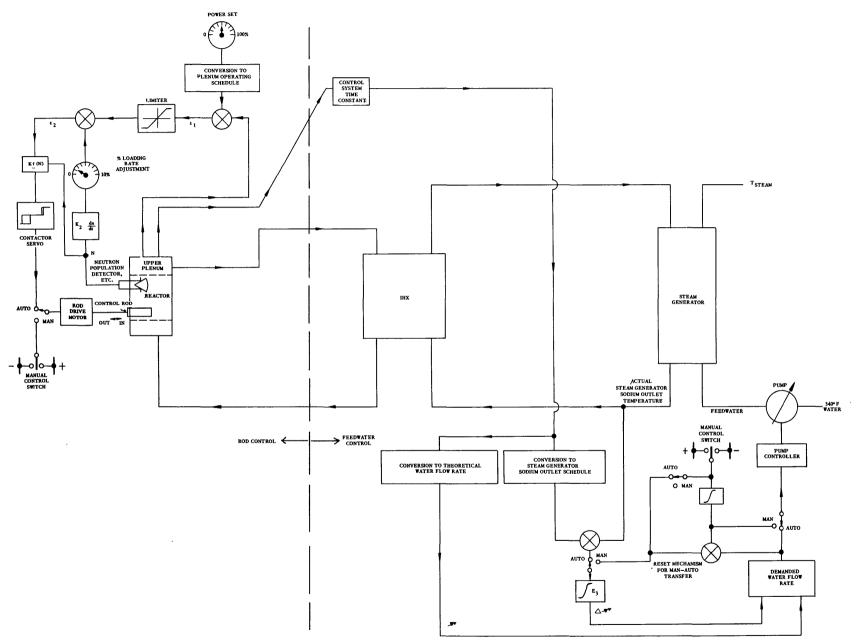

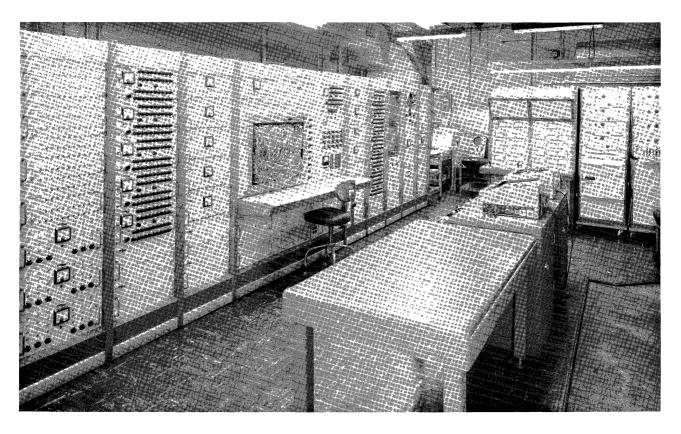

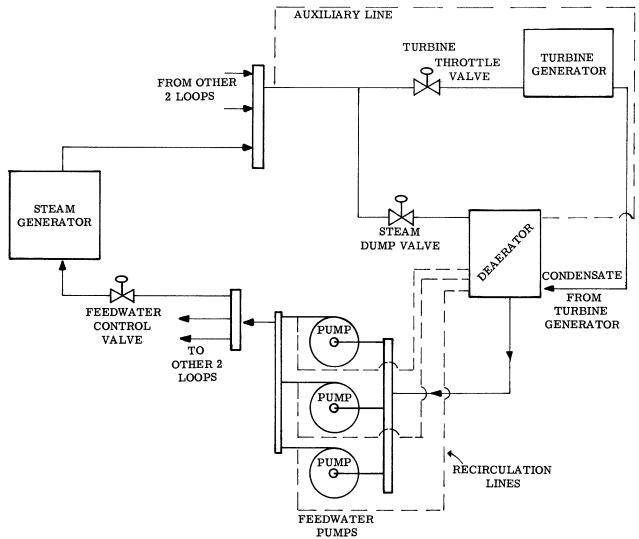

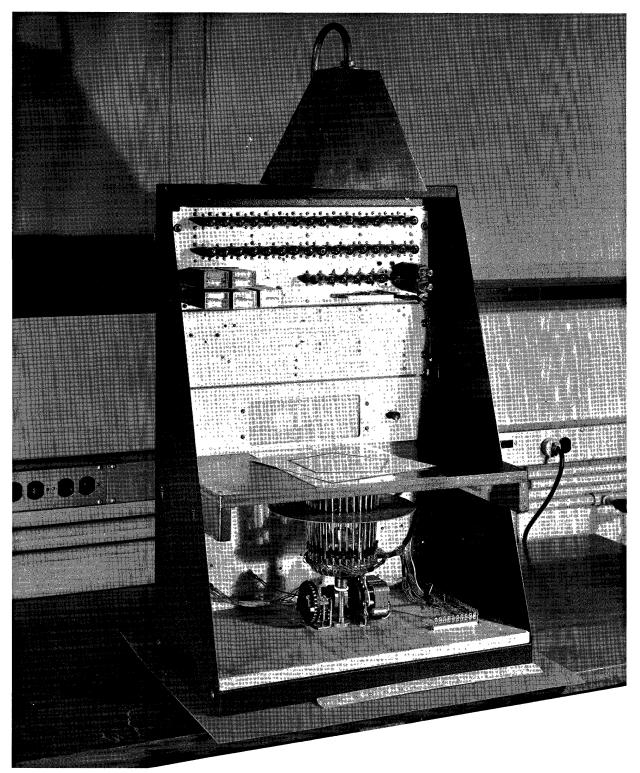

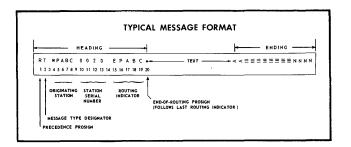

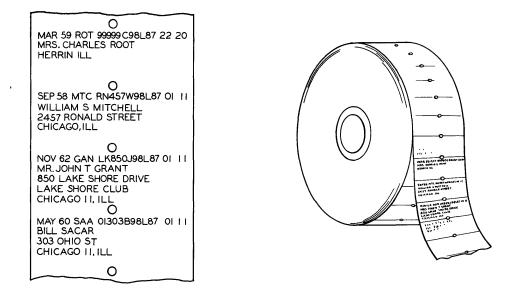

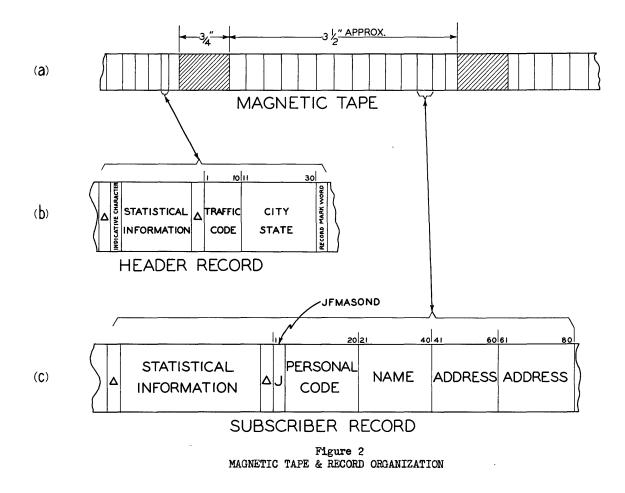

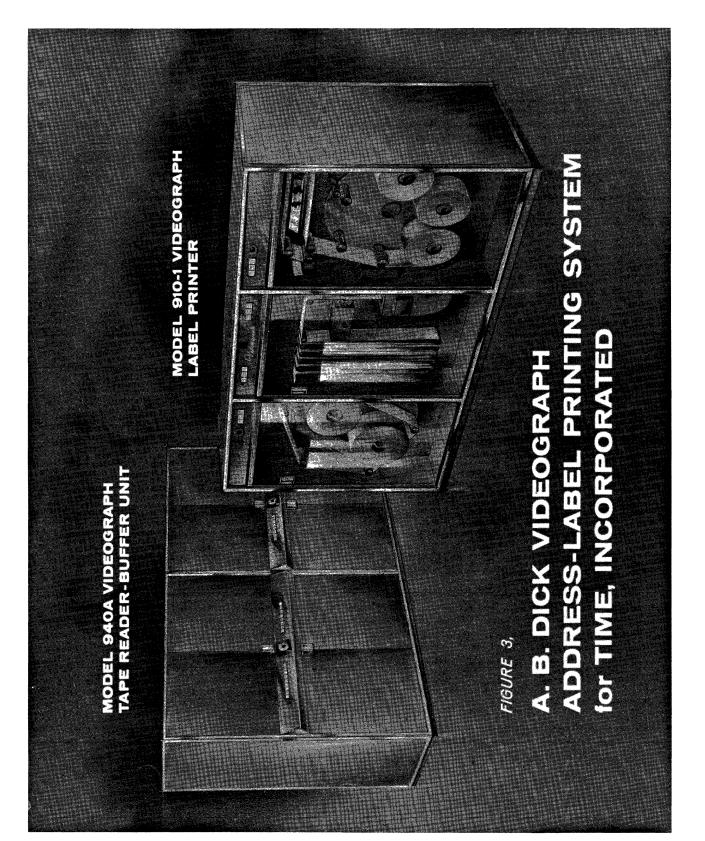

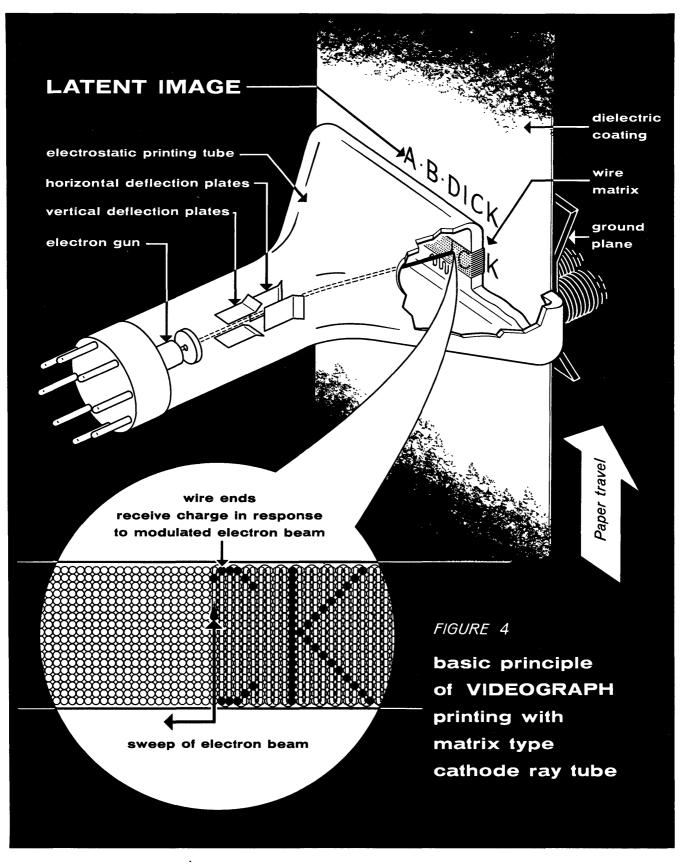

"To improve substantially upon the present computing speeds, manipulative elements for the basic functions of gating and storing binary signals are required which have extremely fast physical response, reckoned in nanoseconds (10<sup>-3</sup>) rather than microseconds (10<sup>-6</sup>). Furthermore, because large numbers of such elements must be used in systems sufficiently comprehensive to make significant use of their speed, these elements must be physically small in order that the machine itself be small enough not to cause prohibitive delays due to the finite propogation velocity of electrical signals.