## Proceedings of the

# EASTERN JOINT COMPUTER CONFERENCE

December 10–12, 1956

New York, N. Y.

THEME: NEW DEVELOPMENTS IN COMPUTERS

## Sponsors:

AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices THE ASSOCIATION FOR COMPUTING MACHINERY THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electric Computers

Printed in the United States of America

## ADDITIONAL COPIES

Additional copies may be purchased at \$3.00 per copy. Checks should be made payable to any one of the following sponsoring societies:

AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS 33 West 39th Street, New York 18, N. Y.

ASSOCIATION FOR COMPUTING MACHINERY 2 East 63rd Street, New York 21, N. Y.

INSTITUTE OF RADIO ENGINEERS 1 East 79th Street, New York 21, N. Y.

Copyright 1957

.

AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS

## PROCEEDINGS OF THE EASTERN JOINT COMPUTER CONFERENCE

PAPERS AND DISCUSSIONS PRESENTED AT THE JOINT COMPUTER CONFERENCE NEW YORK, N. Y., DECEMBER 10–12, 1956

## THEME: NEW DEVELOPMENTS IN COMPUTERS

SPONSORS AMERICAN INSTITUTE OF ELECTRICAL ENGINEERS Committee on Computing Devices THE ASSOCIATION OF COMPUTING MACHINERY THE INSTITUTE OF RADIO ENGINEERS Professional Group on Electronic Computers

ς.

ť

Published by American Institute of Electrical Engineers 33 West 39th Street, New York 18, N. Y.

## NATIONAL JOINT COMPUTER CONFERENCE

Chairman

M. M. ASTRAHAN, International Business Machines Corporation

Chairman for the Eastern Joint Computer Conference, 1956

J. R. WEINER, Remington Rand Univac

Chairman for the Western Joint Computer Conference, 1957

J. L. BARNES, Systems Laboratories Corporation

**AIEE Representatives**

J. G. BRAINERD, University of Pennsylvania H. F. MITCHELL, Sperry Rand Corporation P. L. MORTON, University of California, Berkeley D. C. ROSS, International Business Machines Corporation

Ex-Officio—E. L. HARDER Westinghouse Electric Corporation Chairman, AIEE Committee on Computing Devices Headquarters Representative—R. S. GARDNER Assistant Secretary, AIEE

#### **ACM** Representatives

J. L. BARNES, Systems Laboratories Corporation G. W. KING, International Telemeter Corporation R. J. GROSCH, General Electric Company A. PERLIS, Carnegie Institute of Technology

Ex-Officio—J. W. CARR III University of Michigan President, ACM Headquarters Representative—J. MOSHMAN Bell Telephone Laboratories Secretary, ACM

#### **IRE** Representatives

W. F. GUNNING, Beckman Instrument D. HAAGENS, Underwood Corporation W. S. SPEER, Nordan-Ketay Corporation J. R. WEINER, Remington Rand Univac

Ex-Officio—J. NOE Stanford Research Institute Chairman, IRE Professional Group on Electronic Computers Headquarters Representative—L. G. CUMMINGS Technical Secretary, IRE

The charter of the National Joint Computer Conference was revised on December 12, 1956, and appears on page 1.

## EASTERN JOINT COMPUTER CONFERENCE COMMITTEE 1956

Chairman: J. R. WEINER, Remington Rand Univac

## LOCAL ARRANGEMENTS COMMITTEE

Chairman: J. A. HADDAD, International Business Machines Corporation

Secretary: C. E. STEVENS, International Business Machines Corporation

Exhibits: A. D. MEACHAM, Remington Rand

Finance: A. R. MOHR, Waldorf Instrument Corporation Hotel: J. A. GRUNDY, Remington Rand

Inspection Trips: M. GRIESER, Underwood Corporation Printing: P. E. MAGDEBURGER, Underwood Corporation

Publicity: A. J. FORMAN, Tele-Tech and Electronics Industries Registration: W. P. HEISING, International Business Machines Corporation

### PROGRAM COMMITTEE

Chairman: J. W. LEAS, Radio Corporation of America

J. A. BAIRD, Bell Telephone Laboratories U. C. S. DILKS, Burroughs Corporation J. J. EACHUS, DATAmatic Corporation J. P. ECKERT, Jr., Remington Rand Univac R. D. ELBOURN, National Bureau of Standards W. HALSTEAD, Radio Corporation of America D. P. HEAPSUM National Coeb Pacietar Compu-

D. R. HEARSUM, National Cash Register Company R. E. MEAGHER, University of Illinois

J. A. O'BRIEN, Lincoln Laboratories, Massachusetts Institute of Technology

R. L. PALMER, International Business Machines Corporation

E. A. SMITH, Bureau of Ships, Navy Department T. T. PATTERSON, Radio Corporation of America

J. C. SIMS, Jr., Remington Rand Univac

### PUBLICATIONS COMMITTEE

Chairman: V. N. VAUGHAN, Jr., American Telephone and Telegraph Company

C. COLE, Radio Corporation of America J. W. GUPPY, Bell Telephone Laboratories

J. W. GOFFY, Ben Telephone Laboratories L. HOBBS, Remington Rand Univac A. KATZ, Radio Corporation of America W. R. SMITH, American Telephone and Telegraph Company W. F. STEAGALL, Remington Rand Univac

| Contents                                                                                    |           |

|---------------------------------------------------------------------------------------------|-----------|

| Organization of the National Joint Computer Committee                                       | Page<br>1 |

| Keynote Address                                                                             | 3         |

| Introduction James R. Weiner                                                                | 4         |

| New Computer Developments Around the World Everett S. Calhoun                               | 5         |

| Evaluation of New Computer Components, Equipments, and Systems for Naval UseL. D. Whitelock | 9         |

| The Transac S-1000 ComputerJ. L. Maddox, J. B. O'Toole, S. Y. Wong                          | 13        |

| Univac-Larc, the Next Step in Computer DesignJ. P. Eckert                                   | 16        |

| Design Objectives for the IBM Stretch Computer                                              | 20        |

| A New Large-Scale Data-Handling System, DATAmatic 1000                                      | 22        |

| The Tradic Leprechaun Computer                                                              | 29        |

| Functional Description of the NCR 304                                                       | 34        |

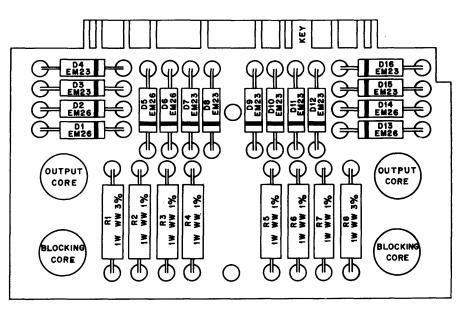

| A Technique for Using Memory Cores as Logical Elements L. J. Andrews                        | 39        |

| A Magnetically Controlled Gating ElementD. A. Buck                                          | 47        |

| A 2.5-Megacycle Ferractor Accumulator                                                       | 50        |

| High-Temperature Silicon-Transistor Computer Circuits                                       | 54        |

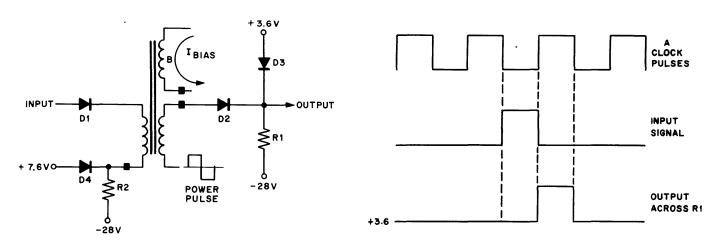

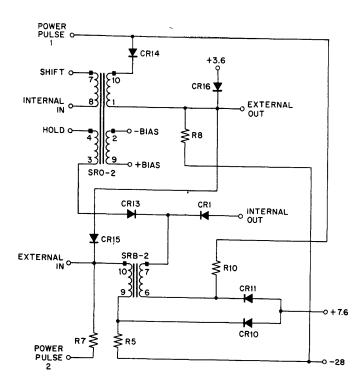

| A Saturable-Transformer Digital Amplifier with Diode Switching                              | 58        |

| High-Speed Transistor Computer Circuit Design R. A. Henle                                   | 64        |

| Are Computers Important?                                                                    | 67        |

| Automatic Input for Business Data-Processing Systems                                        | (0        |

|                                                                                             |           |

| The Burroughs Electrographic Printer-Plotter                                                | 73        |

| A Transistorized Transcribing Card Punch C. T. Cole, Jr., K. L. Chien, C. H. Propster, Jr.  | 80        |

| Apparatus for Magnetic Storage on Three-Inch Wide Tapes                                     | 84        |

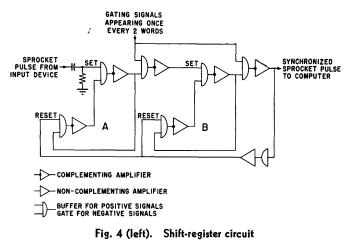

| Synchronization of a Magnetic Computer                                                      | 90        |

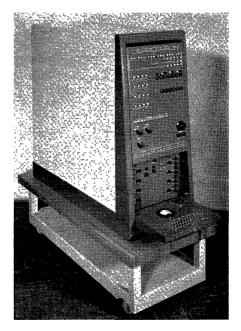

| TX-0, A Transistor Computer                                                                 | 93        |

| Recent Developments in Very-High-Speed Magnetic Storage Techniques                          | 101       |

| Megabit Memory                                                                              | 104       |

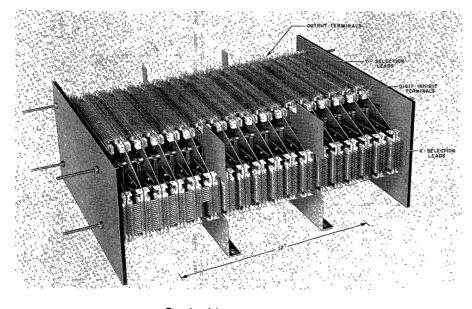

| Ferrite Apertured Plate for Random-Access Memory J. A. Rajchman                             | 107       |

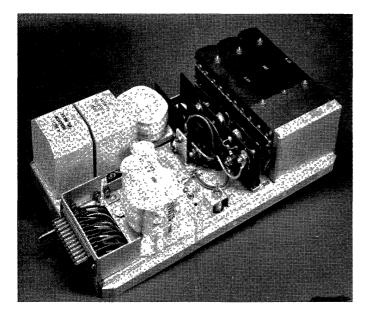

| A Cryotron Catalog Memory System A. E. Slade, H. O. McMahon                                 | 115       |

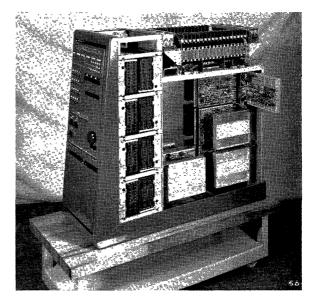

| A Compact Coincident-Current Memory                                                         | 120       |

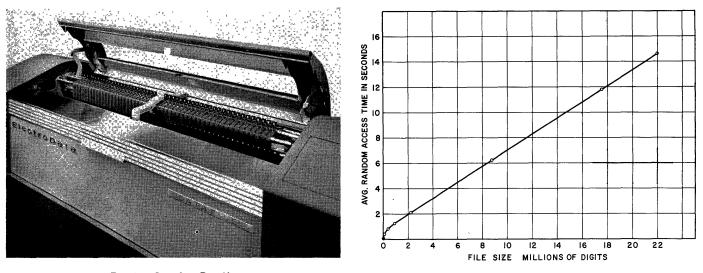

| Datafile—A New Tool for Extensive File Storage                                              | 124       |

| Quasi-Random Access Memory Systems                                                          | 128       |

| A Large-Capacity Drum-File Memory System                                                    | 136       |

| The RAMAC Data-Processing Machine                                                           | 139       |

| Conference Summary                                                                          | 147       |

7

## Organization of the National Joint Computer Committee

Resolution adopted by the National Joint Computer Committee, December 12, 1956, subject to ratification by the sponsoring societies

#### A. Name and Object

1. *Name*. This Committee shall be known as the National Joint Computer Committee, herein identified by the abbreviation "NJCC."

2. *Sponsorship.* The NJCC shall be jointly and equally sponsored by the following three organizations:

Association for Computing Machinery

- Committee on Computing Devices of the American Institute of Electrical Engineers

- Professional Group on Electronic Computers of the Institute of Radio Engineers, Inc.

3. *Object.* The Committee shall aid in the promotion of close cooperation and coordination in the activities of the sponsoring societies related to the field of computer engineering and allied arts and sciences. Its objects shall be scientific, literary, and educational in character and in harmony with the aims of its sponsors.

#### B. Field of Interest

1. Scope of NJCC. The general scope of the NJCC shall be that which stems from the scope of the Association for Computing Machinery, the Committee on Computing Devices of the AIEE, and the Professional Group on Electronic Computers of the IRE.

2. *Major Interests.* The major field of interest of the NJCC shall be the design, development, manufacture, and use of computers, but shall also include an interest in the various activities that contribute to this field or utilize the products or techniques of this field. The term "computers" shall be interpreted broadly to include data, and information handling and processing systems useful in scientific computation, business accounting, and industrial and military control problems.

#### C. Committee Formation and Management

1. Committee Structure. The NJCC shall derive its authority from the three sponsoring groups referred to in Section A2. The heads of these three groups,

namely, the President of the Association for Computing Machinery, the Chairman of the AIEE Committee on Computing Devices, and the Chairman of the IRE Professional Group on Electronic Computers, shall be ex officio voting members and shall each name four voting members in addition to themselves. They shall also designate one member or previous member as Chairman and another member as Vice-Chairman. The Chairman shall appoint a Secretary-Treasurer. In addition, the Technical Society representatives of the sponsoring societies shall be ex officio non-voting members of the NJCC. An important consideration in the selection of members shall be their ability and willingness to attend the committee meetings.

2. *Tenure.* The terms of office of the committee members appointed by the sponsoring societies shall be two years, two new members being appointed each year from each society.

In selecting committee members, each society shall attempt to secure a balanced geographic representation according to the needs of the NJCC and the society. The NJCC Chairman may recommend areas.

It is recommended that members from each area of the country be suggested by the respective active organizations in that area.

3. Terms of NJCC Officers. The officers' terms shall normally coincide with the calendar year and the incumbents shall continue to serve until their successors are selected. The selection of officers should be made as soon as expedient following the appointment of new committee members.

4. Committee Meetings. The NJCC shall meet at least twice a year, to set policies, make plans, and discuss problems within its field of interest. The meetings shall be distinct from meetings of the Steering Committees operating the Conferences.

5. *Executive Committee*. Questions of NJCC policy or NJCC decisions not conveniently settled at a meeting of the NJCC as a whole and not otherwise spe-

cifically delegated by the Charter or by the NJCC as a whole should be decided by the Executive Committee which shall consist of the heads of the three sponsoring groups and the NJCC Chairman.

6. *NJCC Chairman*. The NJCC Chairman, the chief executive officer of the NJCC, shall—be generally responsible for the implementation of NJCC policy or decisions—act as representative of the three societies in setting reasonable and consistent conference policies—call and preside over NJCC meetings—obtain clearance from the three societies for specific conference operations and fiscal plans—appoint and delegate individuals to carry out the work of the NJCC, such as the preparation of specialized unified mailing lists.

7. *Vice-Chairman*. The NJCC Vice-Chairman shall assist the Chairman in executive matters and shall act for the Chairman in his absence.

For the sake of continuity, it is recommended that the Vice-Chairman succeed the Chairman. It is further recommended that he be selected from a different geographical area from the Chairman.

8. Secretary-Treasurer. The NJCC Secretary-Treasurer shall record and circulate minutes of the NJCC meetings arrange for final summary reports of each conference to be sent to the NJCC members, to the three sponsoring societies, and to other interested parties—act as financial liaison between the Finance Chairman of each conference and the three sponsoring societies.

9. Voting Procedure. Questions submitted to the Committee for vote shall be decided by a majority of the voting members. The Chairman shall vote only if his vote will decide an otherwise inconclusive vote.

#### **D.** Committee Activities

1. *Conferences*. The NJCC shall sponsor annually one or more conferences. Such conferences are not to be considered as being in competition with or a replacement of the regular activities of the spon-

soring societies. Instead, the conferences are to represent the combined efforts of the sponsors to produce major technical meetings of a specialized nature. Each conference is to treat a selected theme in the computer field in a thorough and authoritative manner; inspection trips and exhibits are to be featured; formal and informal discussions are to be encouraged; and a conference report is to be published. The quality and coherence of the technical programs shall be such that the publications resulting from the conferences will be useful as current and authoritative text or reference books covering the various phases of the computer field.

The NJCC will concern itself with such conference questions as can best be considered on the national level. Examples of such questions might include:

Decision on location of conference;

- Decision on topic or theme of conference;

- Decision on scheduling of conference to optimize coordination with other conferences and to improve long-range planning;

- Recommendations of procedures and standards for publications, publicity, and exhibit policies of each conference.

At least a year in advance of a proposed meeting, the NJCC chairman with the advice of the committee shall appoint a general chairman to plan and operate each NJCC conference. The general chairman shall be responsible for forming a conference steering committee from interested and capable people in the geographical area of the conference. This steering committee will work with local organizations in the actual initiation and management of the conference. The steering committee shall consist of, in addition to the general chairman, a finance chairman, a local arrangements chairman, a technical program chairman, and a publications chairman.

(a) General Chairman. The general chairman shall have the general executive responsibility for the conference and shall have the power to appoint additional mem-

bers to the steering committee, where required, to carry out its work.

(b) *Finance Chairman*. The finance chairman shall be responsible for all financial transactions and accounts concerned with a particular conference.

(c) Technical Program Chairman. The technical program chairman shall be responsible for implementing all phases of the technical program. This includes selection of and arrangements with all speakers and session chairmen, and procurement of written material as required by the publication committee and local arrangements committee.

(d) Local Arrangements Chairman. The local arrangements chairman shall be responsible for all local arrangements, including registration, inspection trips, exhibits, hotel arrangements. He shall also be responsible for all conference publicity, both local and national.

(e) *Publications Chairman*. The publications chairman shall be responsible for the preparation of the Proceedings of the conference.

Other Activities. The NJCC may 2. establish other committees as required to carry out its work. Such committees may, for example, be established to study and recommend long-range coordinated plans for national and international conferences, exhibits, and publications in the computer field, to study and make recommendations concerning standardization in the computer field, or to study and make recommendations concerning education in the computer field. The sponsoring societies may also, if it is mutually agreeable, request the NJCC to undertake other projects in the computer field which may be particularly expedited through the joint and coordinated action of the committee.

#### E. Financial Considerations

1. Conference Financial Matters. The previous conferences and publications sponsored by the National Joint Computer Committee have been so successful from a monetary point of view that financial support of future conferences appears definite. However, in order to insure that the basic responsibility for the management of future conferences always springs from, and resides in, the three sponsoring societies, the National Joint Computer Committee shall treat each future conference as an independent project requiring separate approval and initial loans from, and financial accountability to, the sponsoring societies. The Finance Chairman of each conference will be responsible to these Societies through the NJCC Secretary-Treasurer for the financial affairs of his own group.

2. General Financial Procedure. Approximately one year in advance of a conference, the steering committee for the conference shall formulate a tentative plan of action together with a conference budget and submit this for approval to the Sponsoring Societies through the NJCC Chairman. If the plans are approved by the Sponsoring Societies, the NJCC chairman shall request an appropriate loan from each of the sponsors and forward the money to the Finance Chairman of the Conference Steering Committee.

3. Disposition of Surplus Funds. All surplus funds resulting from the operation of a conference shall be distributed equally to the three sponsors by the NJCC Secretary-Treasurer within one year after the date of the conference.

4. Committee Expenses. The NJCC shall formulate a budget of expenses which it expects to incur in connection with its activities, but not chargeable directly to a particular conference. As for instance, committee stationery, preparation of a unified maining list, and the like. This budget will be submitted to each of the sponsoring societies accompanied by a request for an appropriation from these sponsoring societies covering these expenses. These funds will be turned over to the Secretary-Treasurer, who will account for them to the sponsoring societies.

## Keynote Address

## H. T. ENGSTROM

AM deeply honored to be invited to furnish the keynote to this important conference. As a mathematician by training, I am perhaps somewhat misplaced in this role. However, by a curious sequence of circumstances, I have been in a position to observe the progress of electronic digital data handling since the beginning of World War II. Although the term "electronic computing" covers a wide range of equipment, I am using the term in the sense of the largescale internally programmed digital computers which have made so many contributions to the scientific and business life of the country during the past 5 years.

As you all know, the great impetus to this art came from the military during World War II. The impact of military needs on scientfic progress is not new. It probably began with Archimedes, who helped his cousin the tyrant of Syracuse to defend that city against the Romans in 212 B.C. I quote from Plutarch's *Life of Marcellus* in this regard:

The king prayed him to make him some engines, both to assault and defend, in all manner of sieges and assaults. So Archimedes made him many engines, but King Hieron never occupied any of them, because he reigned the most part of his time in peace without any wars.

The electronic computing engines were constructed during World War II, and some of them made significant contributions to our victory. However, it was not really until the end of World War II that the general-purpose electronic computing devices began to be delivered. The conviction of their practicality, and faith in the future rested principally among those people who had been working in the field for the military during the war. The Defense Department in general was convinced of the necessity of pursuing research and development in this area in the soluion of military problems. American industry in 1946, however, was not so convinced. As a result, in the post-war period, many individuals with faith in the future of the field established small independent companies which were financed by the Defense Department. I

do not need to name these companies since I am sure most of you are familiar with them. Some of the universities, such as Harvard, Princeton, and the University of Pennsylvania, also carried on research and development in the logical structure and component development in the field. Again, in these universities the program was stimulated essentially by individuals who had faith in the future of large-scale computing devices. University management was not convinced, and in some cases still remains unconvinced, that the field of logical structure design of computing devices was one with proper academic stature.

In 1950, many of the problems with respect to memories, input-output devices, and peripheral equipment had been solved so that well-balanced large-scale computing devices were put into operation. At this time, big business became strongly interested in the field. Many of the small companies who had had a difficult financial struggle to keep going, were merged with the large companies, so that in the early 1950's the electronic data-processing industry achieved a financial stability as well as a technical maturity. It is difficult to estimate the phenomenal growth of the industry. It is certainly true that the present volume of business in electronic data-handling equipment is in excess of one billion dollars per year. Speculations as to its ultimate position are difficult, but certainly the industry will not reach a saturation point before expanding by at least a factor of ten.

The delivery of many of these equipments to industry and government has opened up a tremendous activity in the field of applications. The most important aspect of electronic computation in the last several years has been precisely in the area of a better understanding of the value of this equipment in our scientific and business problems.

Although the industry has achieved technical reliability and financial stability, there are many areas in which serious problems still exist, and I should like to point out some of these areas which come to mind, and which the members of this Computer Conference can assist in clarifying.

The enthusiasm with which electronic data handling and automation possi-

bilities have been greeted is astonishing. I should not like to state categorically that the field has been much oversold, but I do think the overoptimism of engineers and scientists in connection with the field is a definite fact. This optimism causes serious complications. If an industry or the Department of Defense relies upon estimates of delivery and performance which are made by you engineers, they must have some degree of confidence in your technical and financial judgment. There have been too many cases of long delays in the delivery of vital equipment. Many of these delays could have been avoided had the project been less ambitious technically. It is better to have equipment on time, even though it may operate at only one half the speed which may be technically feasible. Another aspect of the industry, which I believe you should consider rather seriously, is that of engineering manpower. On the basis of scientific optimism, the Defense Department is pursuing many projects in electronic computing. These projects result in many contracts with private industry. The usual procedure following the award of one of these major contracts is for an industry to proselytize engineering personnel from its competitors. As a result, there is an inflationary spiral of salaries for engineering and scientific personnel. You may well say that a man is worthy of his hire. I do not subscribe completely to this point of view. The usurer who extracts excessive interest rates is not particularly admirable, nor is prostitution recognized as a reputable profession. I believe that it is within the power of you technical people to assist in rectifying this situation. I believe you have lost a great deal of dignity in participating so actively in this mad scramble for personnel. Engineers can be of great assistance to the national defense in assessing proposed employment changes, not only on the basis of salary, but on the basis of the technical merit of the projects concerned and your potential (technical) achievement. It is certainly your responsibility to see that our industrial and defense program is on a sound basis.

I hope you will not feel that these criticisms of overoptimism and personnel instability detract from your achievement over the past 10 years in the creation of a tremendous industry which is one of the important elements of our national defense. The many papers presented at this conference are a witness to the continued dynamic advance in the art as well as the industry. However, the soundness of your position in American economic life is clearly dependent upon

Full text of the keynote address presented at the Eastern Joint Computer Conference, New York, N. Y., December 10, 1956.

HOWARD T. ENGSTROM is with the National Security Administration, Washington, D. C.

your personal integrity, and I believe we should all give more attention to the two points I have tried to make, with respect to dependability in the matter of prediction of achievements in regard to time, money, and engineering manpower.

One of your previous speakers quoted the great German novelist, Thomas Mann, as follows:

What perplexes the world is disparity between the swiftness of the spirit and the immense unwieldiness, sluggishness, inertia, and permanence of matter.

As to the arts with which we are concerned, I think this statement may well be reversed. We have developed computing equipment of great speed and capacity, and what perplexes the industry and the Department of Defense is the sluggishness of the human spirit in participating in their fundamental problems.

## Discussion

**Eugene H. Jacobs** (Rand Corporation); Why doesn't the Defense Department stop giving new contracts to companies which do not have sufficient personnel on hand?

**H. T. Engstrom :** The situation is that there is no spare scientific and technical manpower available, so that whenever the Defense Department gives a contract, it is expected that the companies will get the personnel from some other source presumably from other occupations.

The program of the Defense Department is to put these people upon projects which we feel are more vital to the defense problem; some of the change in personnel is necessary, since there is no idle manpower. I might add, in this regard, that my agency in Washington is also looking for people.

**W. C. Richey** (Lockheed): Have you examined or found ways to use computer equipment to expedite security clearances?

**H. T. Engstrom:** J might explain that although my agency is the National Security Agency, it is not responsible for security clearances. However, to my knowledge, large-scale computing equipment has not been applied to the problem of security clearances.

## Introduction

#### JAMES R. WEINER

N BEHALF of the Joint Computer Committee and the three sponsoring societies, the American Institute of Electrical Engineers, the Institute of Radio Engineers, and the Association for Computing Machinery, I should like to welcome you to the sixth annual Eastern Joint Computer Conference. It would appear from our registration at this point, that this is our largest meeting to date. The major portion of the credit for the success of this conference should go to the three conference committees and their chairmen, J. W. Leas of the Program Committee, J. A. Haddad of the Local Arrangements Committee, and V. N. Vaughan of the Publication Committee. These men and the members of their committees have devoted a great amount of time to this conference, and we owe our thanks to them as well as to their employers who have encouraged them in their efforts.

As mentioned previously, this is the sixth annual Eastern Joint Computer Conference. The first was held in Philadelphia in December, 1951. It was sponsored by the same three societies, and the attendance was somewhat less than 1,000. Since that time, conferences have been held annually, both on the east and west coasts, and our meetings, originally known as the Joint Computer Conferences are now called Eastern in deference to meetings held in the West.

If we review the previous meetings we find their themes to be the following:

- 1951 Review of Electronic Digital Computers

- 1952 Review of Input and Output Equipment Used in Computing Systems

- 1953 Information Processing Systems-Reliability and Requirements

- 1954 Design and Application of Small Digital Computers

- 1955 Computers in Business and Industrial Systems

In addition, two West Coast conferences have been held: one on trends in computers, automatic control, and data processing; and another on tutorial sessions and discussions on digital and analog devices. At this conference, whose theme is "New Developments in Computers," we discuss some elements of each of the topics listed. Moreover, we may be starting a second cycle because we are concerned now primarily with the solidstate computer, utilizing either the transistor or the magnetic amplifier. It is quite possible that, except for certain specialized applications involving extreme ambient conditions, the role of the vacuum tube in digital data-processing equipment may be over in the near future. This has led to many new engineering and systems considerations, some of which are described at this conference.

Our conference is organized in the following manner: First, a session devoted to new computers and computer systems almost all of a solid-state nature; then two sessions essentially on new components and circuits interspersed with two sessions on input-output devices. The first component session is entitled Circuits and Components, and is concerned wholly with the sort of elements that would be used primarily in the arithmetic element of the central computer. The second component session is devoted to high-speed memories. The two input-output sessions cover first a rather diverse group of equipment and, second, some individual solutions to the random access file problem.

We hope you find the program both interesting and informative. We thank you for attending this conference which you believe to be of sufficient interest to attract you here from all parts of the civilized world.

JAMES R. WEINER, Chairman Eastern Joint Computer Conference, is with Remington Rand Univac, Division of the Sperry Rand Corporation, Philadelphia, Pa.

# New Computer Developments Around the World

### EVERETT S. CALHOUN

T HAS been an interesting assignment to travel during the past 4 months through 20 countries to observe the developments in electronic computers and office automation. Ninety-five visits have turned up over 35 different computers and a host of electromechanical devices for data recording.

Inasmuch as my primary interest was in automatic data-processing no special effort was made to visit analog computers laboratories or scientific computer installations. However, as in the United States, nearly all of the European computers were originally designed for military or scientific-mathematical purposes. To capture a share of the larger business data-processing market, most of these are now being altered to provide better inputoutput facilities.

The concepts of IDP (integrated dataprocessing) and EDP (electronic dataprocessing) and office automation are already accepted by big business abroad. Government bureaus, banks, insurance companies, manufacturers, department stores, and mail order houses eagerly await the day when automation will supply an answer to their rising office costs. Although salaries appear low compared to ours when converted to U.S. dollars, the percentage of clerical costs to total overhead is too high, and good clerks are scarce in Europe also. The knowledge is widespread that new business tools will soon be available which will not only do routine work automatically, but also provide management with better and quicker information.

Europe is undergoing a building boom that is unprecedented. Many parts of the world, particularly our former enemies, are approaching a prosperity similar to ours in the 1920's. New factories, stores offices, and apartments are replacing the bomb shattered obsolescence of the 1930's, and the most modern equipment is being installed. Business men speak about Univac and the 650 and Datatron with the same familiarity as in this country.

In the Far East most of the electronic developments are coming from Tokyo.

The Shibaura Electric Company built their first computer, the TAC (Tokyo automatic computer), for Tokyo University. This serial-digital binary machine has both electrostatic tube and magneticdrum storage. A second model is nearly completed. In the government electrotechnical laboratory a partly transistorized computer was demonstrated, called the ETL Mark III. Along with 55 vacuum tubes and 1,600 germanium diodes, 120 transistors are used. Stored in glass supersonic delay lines are 256 words, providing multiplication in less than one millisecond. Kyto University is also using a computer in its mathematical department, and several other firms are designing new machines. When entering the air-conditioned room where a large relay computer was in use at the telephone company the writer was asked to remove his shoes "to prevent the entry of dust." Removing shoes is of course a common occurrence in Japan, but perhaps some of our magnetic tape installation could adopt this plan as a cure for dropped bits.

The Statistical Institute of India has ordered a URAL computer from Russia. This decision followed a trip to the U. S. to investigate available equipment. Dr. Mahalinobis, the director, was not sure of the characteristics or specifications, nor the type of input and output equipment which would be furnished, but is appears to be in the class with a Univac no. 120 or an IBM no. 607 or a BULL Gamma.

Discussions with several people who have visited Russian computer developments indicate that the Russians have completed a number of designs of modern computers at several laboratories, the principal one being the BESM at the Institute of Exact Mechanics and Computing Techniques at the Academy of Sciences at Moscow. I heard a speech at the instruments and measurements conference in Stockholm by S. A. Lebedev of this organization. He described the installation of Williams tubes in the BESM, replacing the mercury-delay lines. He seemed rather disappointed that even the inventor of the tube agrees that the cathode-ray tube storage is becoming obsolete, and that every other speaker

was emphasizing the replacement of cathode-ray tubes with magnetic-core store. I have no doubt, however, that their reputed 30 million document library in Lomonosoff University, translated from every language by the 10,000 technical foreign language staff, has access to every process and patent published anywhere, including full data on ferrites. Mr. Lebedev also discussed the use of magnetic drums and tapes, and the existence of a rotary-wheel printer and another output device projecting 200 digits per second to photographic film. The BESM computer is reported to have an average operating speed of 7,000 to 8,000 3-address operations per second including access time.

A visit to the Leipzig Fair in East Germany proved fruitless as far as electronic machines were concerned. Eastern Germany was the location of the officeequipment industry before the war. Firms like Rheinmettal, Astra, Mercedes and others are still in operation, and doing considerable export business to all the world except the U.S. While the quality of these machines suffered as a result of poor quality steel after the war, most users now report very satisfactory quality in recent production. It was significant that not one word regarding Russia was included in the publicity, and not one display was marked "made in the USSR." In former years such products formed a prominent part of the huge trade fair.

An exciting documentary could be written about the reestablishment of the office equipment industry in Germany since 1945. Many plants were demolished in the war, and, particularly in Berlin, the remaining equipment was looted by the Russians and taken to their Zoné. Branch factories of large U. S. firms were left with only a shell of a building, and without a tool or even a light bulb. These plants have all been restored with modern tooling and machines now, and there is no evidence that the Russians ever put the pilfered equipment into production.

I talked with a number of East German factory executives who fled with microfilms and worthless marks across the line by bicycle. They reassembled, pooled their resources, acquired financing and personnel. Buildings were constructed for production of typewriters, adding machines, and bookkeeping machines to meet the needs of western Europe. The basic superiority and talent of German technicians in the mechanical arts has resulted in a surprising comeback, and has established Germany as the largest exporter of office equipment.

EVERETT S. CALHOUN is with the Stanford Research Institute, Menlo Park, Calif.

Computer developments in Germany have been sponsored by the Deutsche Forschungs Gemeinschaft (DFG) organization, with members representing various industries and branches of government. With a budget of many millions of marks for the advancement of science, they have allocated to several universities sufficient money to build electronic computers. Goettingen University was putting the finishing touches on Mark III when I was there, and they have been operating G-1 since 1952. G-1 and G-2 were built from U.S. war surplus for the most part, and are relatively slow; but G-3 is a ferrite-core storage parallel machine of much more ambitious proportions. The G-2 model includes a magnetic drum with 2,096 words of storage, and is serial in operation.

When one wishes to find out about computers in Germany he visits Prof. Alwin Walther at Darmstadt Technische Hochschule. His staff maintains the best library of computer information in Europe. Prof. Walther has been the inspiration in the design and construction of computers in several other schools in Germany, and his own group has nearly finished the DERA (Darmstadt electronic recorder automatic), which they will use in the mathematics department. Another group has been working for 4 years at the Munich Technical Highschool (6,000student enrollment, college level) on the PERM, a computer with an exceptionally fast drum, 15,000 rpm. Completion is being delayed by the replacement of 100,000 faulty connectors, a not-toouncommon complaint of current computers.

The only operation in Germany where a quantity of computers have been made and sold is in a barn in Neukirchen-Hunfeld where Dr. Konrad Zuse has built 12 relay analog machines. He is currently finishing the first digital-electronic magnetic-drum 'model, and reports thathe has a backlog of half-a-dozen orders. The price will be in the neighborhood of 100,000 marks (\$25,000). This can be better understood when salaries of \$100 per month and plant rent of perhaps \$100 per month are taken into account.

The center of full-fledged production of electronic computers in Germany will probably be at Stuttgart, a beautiful, thriving, modern industrial city of one million skilled people. International Business Machine Corp. has established its first no. 650 production-line here. Standard Electric Co., a subsidiary of International Telephone and Telegraph Corp., have formed the "Informatik" division of their 10,000-man operation to build transistorized computers. They are closely linked with large operations in Pforzheim, and in Belgium, where two computers have been built, one for an American buyer. In Britain, Standard Electric Co. is also mass producing a computer designed in Holland, and together with their communication facilities and teletypewriter subsidiary, Lorenz, A. G., the International Telephone and Telegraph Corp., operations are impressive.

The first installation of a large-scale electronic data-processing system in Europe is at the Battelle Institute in Frankfurt where Remington Rand have installed a Univac system. A new modern building, complete with air-conditioning and 60-cycle power source was built for this elaborate and new first-class facility. The machine will be used by industry and government as a computing center. I talked to people as far away as Madrid who were attending programming classes in Frankfurt, and many firms are planning to train personnel in the use of this equipment. International Business Machine Corp. will use a no. 650 at Stuttgart for computing service, and plans are being discussed for a no. 705 at some other location in the near future. One of the finest programs of technical development and group research is in the progressive Scandinavian countries. Here the various technical schools have cooperated and the result is an excellent high-speed computer called the BESK. To avoid maintenance requirements, increase its speed, and to enlarge its storage capacity, the Williams Tubes have recently been replaced by a 4,000-word ferrite-core store. These new core matrix boards were assembled at the technical school in Stockholm at minimum cost from cores of General Ceramics manufacture, and they were very proud that it worked perfectly 3 days after installation. Duplicates of this machine have been built at several commercial and governmental installations in Sweden, and a copy is nearing completion in Copenhagen. The University of Lund saved money on their copy by installing a magnetic drum initially.

One cannot help admiring the fact that, in spite of limited capital and resources, each of the smaller countries of Europe has some activity toward building computers. Norway has a small drum machine in the Central Institute at Blindern University, and partly as a result, the government is to receive the first Mercury Computer from Ferranti. The Mathematics Center at Amsterdam built a small relay computer four years ago. Now they have a new electronic core model, and they have built a duplicate for the Fokker Aircraft Company. Because of the interest created the Shell Company bought a Pegasus computer, and the government Telephone & Telegraph laboratory built a series of computers, one of them for mass production. This machine incorporates a novel system of programming, each instruction word includes a "long" and a "short" address plus up to 12 functional operations, each designated by one character.

The inspiration for a number of computer and electronic developments in Europe is the operation known as PTT (Postal, Telegraph and Telephone), which operates the banking system of the various governments. This is the largest single data-processing operation in the world, unless our Social Security tops it. Every day, in each large center in Europe, hundreds of thousands of postal checks are issued, and a statement is mailed each day to every depositor whose account is active. The problem of sorting the paper is a major one, and great interest is prevalent in magnetic ink character recognition. The Holland group is trying to find a method of reading handwriting. The Bull Company in Paris is demonstrating a magnetic-ink coded check sorter. In Switzerland they have punched 40 holes, 1/4 inch diameter, in the checks so they can be sorted, but the result looks like Swiss cheese. Some solution is bound to come to the problem before long.

Switzerland and Italy have no commercial developments in computers as yet. The Technical Highschool at Zurich had the Ermeth built for them by Hasler, A. G. in Bern. International Business Machine Corp. have just dedicated their new research laboratory in Zurich and the director is Dr. Speiser who designed the Ermeth machine. In Italy, Spain and Portugal, the business machines industry is dominated by Olivetti, and it will probably not be too long before some announcements in the electronic field will be forthcoming. Olivetti sponsored research is under way at Pisa University on electronic computer design. A Ferranti computer is in use at the University of Rome, and many Italian banks are using machines such as the Univac no. 120, the IBM no. 604 and the Bull Gamma, all punched-card-programmed electronic calculators.

If punched-card-programmed calculators are included, then the largest producer of electronic computers in Europe is the Compagnie des Machines Bull in Paris. This firm has installed several hundred Gamma machines, largely in banks, and is now starting to produce a new faster model incorporating a magnetic drum with 8,000 words of storage. Magnetic tapes will probably be added also, although there has been little if any effort to develop magnetic tape devices anywhere in Europe. At the other commercial computer factory in France, the Society for Electronics and Automation, Francois Raymond is installing Potter Tape units on the CAB no. 3,000, which is nearing completion, at a price of about \$250,000. A still faster model operating at 200-kc will perform multiplication in 0.21-ms, according to the announcements. I learned that a printer, called the "Numerograph," consisting of a cathode-ray tube projection on film, would be delivered on a business-data processing application in March, 1957, but the prototype had not been started as yet. This organization has produced, however, about 50 analog machines, mostly for machine tool control. I visited an installation of the first CAB no. 2,000 digital computer in a defense plant in Paris and I was told it had performed excellently for one year with only part-time maintenance.

There is little doubt that the principal commercial production of electronic computers, especially for export, will come from Great Britain. The Universities have produced an able group of electronic designers, and the knowledge of computer circuitry and component design is on a level with that in the U.S. A number of well financed manufacturers have passed the prototype building stages, and now have a backlog of orders which would probably total over \$10 billion. The government, through the National Research and Development Council, is stimulating and supporting developments in this field as evidenced by the granting, through the University Grants Committee, of six Ferranti computers to as many colleges for use in mathematics and research. Export sales to very remote countries are being made, and others considered, without fully considering the need for adequate maintenance facilities. Ferranti have sold machines in Italy, Canada, Sweden, Switzerland and South Africa, and Elliott Bros. will deliver machines in 1957 as far away as Australia from service facilities. Therefore we can assume there would be no hesitation to accept orders from the U. S. whose dollar credits are so very desirable at this time.

British electronics firms operating in their domestic market, are finding, however, that the lack of established sales and service facilities is a serious handicap, especially in the new field of business dataprocessing. They are following the lead of the U. S. by joining with business machines distributors whose knowledge of system selling and installation is based on sound experience. The machines of Ferranti will be sold by Powers-Samas, and Elliott Bros. have concluded a sales agreement with National Cash Register. British Tabulating Machine Co. has joined with Laboratory for Electronics in Boston. Standard Electric, Electrical and Musical Industries (EMI) Electronics, English Electric and Decca are still independent, but none has faced the sales problems as yet.

No report of British computer progress would be complete without some mention of LEO (Lyons Electronic Office). The Lyons Tea Co. is a large, diversified firm, with 250 bakeries and restaurants and 400 kinds of tea distributed house to house. Even so, it was quite a departure to start building an electronic data-processing machine in 1950. This 6,000tube machine with mercury delay-line store has been in operation on payrolls since early 1954, and now computes 30,000 checks semi-monthly for the bakeries. A separate subsidiary has been established to build the computers which other firms are ordering, and 70 people are employed. A large co-operative chain will be the first customer for the first of "Leo II" machines, which are four times faster because of a shortening of the mercury lines. Bull or Samas printers will be used for output.

A number of unique design features are included in British computers which we are not using in the U.S. One is nickel delay lines for fast storage, first used in the Nicholas computer built by Elliott Bros. and continued in their newer dataprocessing models, the no. 404 and no. 405. Nickel lines will be used in the new Ferranti Data-Processor and probably in the EMI transistorized computer. Bull of Paris has incorporated nickel lines in its newest drum Gamma. For bulk storage, however, Elliott Bros. have provided both a 4,096-word drum and a 16,-384-word aluminum disc, 1/2 inch thick and 19 inch diameter. This appears to be considerably more simple in construction than most of the magnetic drums which are in almost universal use. Elliott Bros. are also alone in using 35-mm film instead of plastic or mylar for magnetic tape storage, the film movement of 30 inches per second being controlled by the sprocket perforations. Two highspeed wire-matrix data printers are under development which will be used by the various computer manufacturers who wish faster speeds of output than the punchedcard tabulators. One by Samas has been demonstrated here by Underwood-Elecom, which represents Samas in the U. S.

In conclusion, I want to emphasize what I believe to be the most pressing problem in the computer industry, not only in all the countries I visited but here at home also. This is the lack of trained manpower to design, build, program, install, and maintain these rather complicated new business tools. I was sorry to see that the colleges and universities are buying machines rather than designing and building their own. It was by this process that all of our present progress was made, and from these design groups have come the electronics engineers who are now able to assist industry in the use of the systems.

I was disappointed to find business. machines firms funnelling the cream of all the university design groups into commercial product developments, lured by higher salaries of course. The entire group from BESK at Stockholm has recently moved to Atvidaberg, makers of Facit Calculators. The heads of the design groups at Darmstadt and Munich have gone to Standard, Telefunken, International Business Machines Corp. and Siemens. There is not sufficient training taking place to replace these pioneers, and some unfinished computer projects are left without experienced men to complete the work. The answer is to establish, at once, computer design and operation courses in our universities all over the world, and to increase the training given by manufacturers.

The electronic automation business, like most other highly scientific fields, recognizes few national boundary limitations. We should give technical assistance to less prosperous countries instead of robbing them of their best talent. This does not refer to temporary transfers or exchanges, which are most welcome. One of the most complimentary things I heard about the U.S. was that a college here granted the money to send a scientist over there to help them build an electron microscope. He stayed a year, made friends, and taught a group the techniques he was expert in. They like that much more than just money, and the whole world benefits any time knowledge is spread. Let us do it in the computer business. Let us have an international computer congress soon, and hold it in Europe, because the one thing they don't have is dollars. We have no monopoly on brains, and much can be learned from discussions with the wonderful group of dedicated engineers I met during my trip.

## Discussion

**Irving Cohen** Radio Corporation of America (RCA): What is the present status of the Gottingen machine?

**Mr. Calhoun:** The status of the Mark III was at the state that I am always told a machine is in when it can not be demonstrated. It is 80 per cent completed.

J. F. Swatton International Business Machine Corp. (IBM): What type transistors are being used in European machines and what comments have you heard on transistor reliability?

Mr. Calhoun: I have heard many remarks that the reliability was now sufficient to get equal results as with tubes. Most of them are buying transistors from Philips in Holland or from Mullard in England, and they are all junction type. They are buying them in Germany for 4 marks, which is about one dollar, each. I saw at least three transistorized computers under construction in Europe which are all going to use these transistors. Most engineers thought that it would be foolish to build a tube machine at this time.

**W. K. Halstead** (RCA): Can you give some more details of the British machine with the novel approach to programming?

Mr. Calhoun: Not too much. This machine is in paper form and not even in prototype form yet. It is, however, a development of Dr. Kosten and Dr. Van der Poel of the Hague, Holland. Dr. Kosten explained it to me; it follows the Ptera machine, which they built, in logic, but is quite improved. This 15-character portion of the instruction word does permit (according to Dr. Kosten, who has gone now to Delft University as a professor) up to 12 functional operations all combined in one instruction word. For instance, bring the figure from slow memory, put it in fast memory, put it in the accumulator, add it to something else and store it somewhere else, this can all be done in one instruction word. So while the machine is slow, the functional arrangement of the program, it seems to me, is unique, at this point anyway.

Leon Gamen (Sperry Rand Corporation): Without magnetic tapes, what type of data processing problem is typical of the European commercial installations?

Mr. Calhoun: It is similar to talking about data processing installations in the United States two years ago. I would say that's about the lag over there. The data processing installations there have been principally on punch-card-program machines, and 90 per cent of them at the beginning were in banks. 50 per cent of them are still in banks. The reason banks use them over there is not for processing vast quantities of checks, but because every check handled in a bank in Europe has to have the interest calculated on it. There is interest paid on every item in and out of the bank, even if it is one dayand at 1 per cent, it's still calculated on punch cards. So they have a different problem than we do.

**B. Housman** (IBM): What is the memory speed of the BESK?

Mr. Calhoun: It will perform about 20

additions or 3 multiplications per millisecond. Its memory was a cathode-ray tube and it was described as most resembling a no. 1103 in speed. It now has 40,000 bits of ferrite-core storage and operates at the normal speeds that would result from such design. The core store was built on principles that were pretty well known in this country, as I said.

By the way, this job was done by six completely inexperienced girls hired from a newspaper ad, who took the cores and the etched circuit boards and all the wires home with a soldering iron, and in 6 weeks all six of the women returned with finished matrix boards. They put them into the assembly, wired them laterally, all the boards together, and in three days after they brought them back this memory was working. They only had to replace one ferrite core in the whole 40,000. This is the way they do things over in Europe.

**B.** Housman (IBM): How strong is the basic research on solid state components such as transistors? Where is this work concentrated?

Mr. Calhoun: I can name a lot of companies. I would not want to rate them; I don't think it would be appropriate here. But the companies in the electronics industry, Philips, Mullard, Standard, Siemens, Lorenz, Telefunken, and IBM are companies who are certainly doing top-level work in this field. Then there are a great many university groups who are doing small amounts of work in the field. There are real, serious, efforts on solid state physics in every company in Europe which has an electronics laboratory. I would say that solid state physics is one of the major efforts of research, and they are developing reliable transistors.

**Professor Chorafas** (Catholic University): How do you evaluate Professor Piloty's approach in building the Perm with a drum for fast memory?

Mr. Calhoun: I, personally, am a little worried about the high-speed mechanical developments they are getting into in trying to achieve speed. This is just one of them. Some of our other large capacity data-storage devices with low access time also are worrying me. If you try to get a heavy drum to rotate at 15,000 rpm, and try to hold a 1 mill clearance with the head, you have a mechanical problem that can be very severe. They put the ball bearings under highpressure tension, in order to minimize the runout. They say it's working, that is, it's working in test, but I think that the first one will probably not work perfectly. I am personally afraid of driving mechanics to this extent, because maintenance may become a problem. As soon as we can arrive at non-mechanical methods of getting adequate capacities and speeds of memories, certainly we will have made a great stride.

**Professor Chorafas:** Do you think that a large business computer like Univac or 705 can develop from the actual European models?

**Mr. Calhoun:** They think ours are: a little too big. They think they would do better to have them just a little bit smaller. But they think their input-output facilities should be as large or better. And they look at our large computers, if I may say so, just a little bit like I looked at the Auto Show last night, and like the French newspapers are reporting it. They just think we do things a little bit too big. I was impressed that we have a little too much rear light on our cars.

**Mr. Graney** (Westinghouse Electric Corporation): What are the advantages of nickel delay lines over other types of memory devices?

Mr. Calhoun: They are cheaper.

**R. C. Dorp** (IBM): What future do magnetic drums seem to have in European computers?

**Mr. Calhoun:** Well, they are like the clutch pedal on a car. They are going, but they are still in everything. There is a magnetic drum on almost every computer I have seen. In every case they hope to replace them.

**Mr. Fischer** (Naval Training Device Center): Can you give more detail on the aluminum disc memory?

Mr. Calhoun: Yes. The magnetically coated disc revolves in a vertical plane at 1,500 rpm. It has about 40-milliseconds maximum access, and therefore, about 20-milliseconds minimum access. I think they break the records up into 100-character words and they have 64 tracks on each side of the disc. They read both sides of the disc.

The disc is made of a 1/2-inch thick piece of aluminum, 19 inches in diameter, revolving with fixed read-write heads on both sides. I think you can imagine the result. It is very simple; the bearings, mechanics, all are very simple.

**A. Steele** (IBM World Trade Corporation): Did you see any Ferranti magnetic tape operation, or 35 mm tape operation in England?

**Mr. Calhoun:** Yes, I think I mentioned that Elliott Bros. are using 35-mm coated film base tape and have used it for some little time. They also, however, are using a 1/4-inch mylar tape in the same system. Ferranti does have some tape operations, however. I believe they have selected the Electrodata tape unit rather than to try to develop their own.

**R. E. Montijo** (RCA): To what do you attribute the apparent lag in design and development of magnetic tape equipment in Europe?

**Mr. Calhoun:** I would say the lack of realization in Europe that business data processing is economically feasible. In other words, all the computers that have been built are either for mathematics departments or for scientific research, which did not require magnetic tape. We must admit that we have had only two years actual use of plastic magnetic tape for data processing in the United States, and many problems still remain.

They are just beginning to realize that business could use computers to an advantage. It must be remembered that, as short as five years ago, there was an article in a technical journal in London which stated that one large-scale electronic computer like those in the United States would do all of the computing necessary in England; therefore, there was certainly no need to make any. Now they are all embarrassed that this was actually thought to be true only five years ago. But England is building computers, and they are going to have lots of them. They will soon have a large business in data-processing equipment.

Harold Kantner (Armour Research Foundation): Can you describe briefly the machine referred to as the "Numerograph" which was attributed to a Paris company?

**Mr. Calhoun:** There is no prototype built yet. I do know, however, that it is a projection of a cathode-ray tube image in rapid sequence onto film, which is developed, and then printed on photographic paper in a continuous flow process.

**W. W. Davis** (Naval Ordnance Lab.): Did you see computers being used in industrial control applications?

Mr. Calhoun: No. I went to a number of places to find them also. I was told that Renault Automobile Company in Paris had the greatest automation in Europe. It has been written up as such. I spent a day there and I saw a wonderful example of electromechanical automation, but I did not see one bit of an electronic control. They don't believe in it; they think it's not reliable. They think electric relays and motors can be handled by the ordinary maintenance mechanic, but they are just very afraid of electronic controls. However, a number of firms are making electronic machine tools, individually controlled machine tools, but not very much in electronic process control.

**R. O. Skatrud** (IBM): Are European countries, or Asian for that matter, developing high-speed computers for applications to defense problems?

Mr. Calhoun: Oh yes, I would say that with most of the first computers, the sales are to defense plants, and to nuclear energy research organizations. In Paris I saw the machine that the Society for Electronics and Automation built for a defense plant, and in England there is some relationship between all the early computers and government defense. The first "Mercury" corememory computer built in England will be installed by Ferranti in a Norwegian defense establishment, at the Royal Academy of Science in Oslo. The man who will run that, by the way, is known to many of you, Dr. Ernst Selmer, who was the designer of the logic for the Electrodata-datatron.

**J. Reitman:** (Teleregister Corporation): Did you see any on-line applications in service or prospect?

Mr. Calhoun: The nearest to that would be in Nuremberg, where a large system is being installed in a mail order house, which processes up to 750,000 line items of sales per day. They will have fully transistorized price index, inventory, and billing machines operated direct from the keyboard input of the orders. Funnelled in the most clever manner I have ever seen, the merchandise comes down from five floors, through 25 elevators, to carrier belts; so that the entire order is automatically assembled at one wrapping desk, where the stamp is put on it and it goes to the post office. This is all done by complete automation. They are going to use an on-line operation. As the order arrives, they would code it on a printer-punch, and from the coding everything else-the filling of the order, the billing, the establishment of the proper price and so on-would be handled within an automatic cycle.

J. Reitman: Did you see any large drum storages? What was the largest drum storage you saw?

**Mr. Calhoun:** I think the largest drum storage was 16,000 words at Bull in Paris, which is the same number of words that are on the Elliott disc I described. Most of the other drums are 4,096 words. That seems to be a standard. I saw very few, if any, smaller drums being constructed, although there were some 2,000-word ones in use. Everyone is going to at least 4,000 or an 8,000 words, and, in the case of Bull, to 16,000 words of storage.

**S. Gorn** (Moore School of Electical Engineering, University of Pennsylvania): What

is the attitude in Europe to building in floating point?

**Mr. Calhoun:** Built-in floating point is accepted as a proper inclusion in a scientific machine and it is already in about at least 10 out of 35, I would say. I did not make a list of those. In all the new ones that are planned for data processing, of course they're eliminating expensive floating points. I think that's pretty much in line with our United States concept.

**Mr. Baker** (Rand Corporation): What progress has been made in automatic coding techniques?

Mr. Calhoun: I did not see very much progress in automatic coding. There has been much talk at meetings and discussion, but I was not told that anyone had accomplished automatic coding, which I take to mean putting a program into machme language automatically, not putting data into a coded form automatically. The question could be taken either way. I did see a lot of equipment for putting data into code-form automatically, and that would be automatic coding in one respect.

**M. L. Aitel** (RCA): Can the training courses in computer techniques be covered adequately by universities, or must industry participate to provide the manpower and money?

**Mr. Calhoun:** I think the industry must provide most of the money, computers, and some of the manpower, and I think the colleges must be encouraged and supported to do more of the teaching. But I think industry must take a very heavy responsibility in the training of people for the data processing industry, because it's going to take a lot of them.

Much of this will have to be done after college age also, but we must not fail to bring along a large group of basically trained people out of our universities, people capable of becoming technically trained in this specific art, at least. We must make high school mathematics and science courses more attractive, so that everyone won't just study sociology.

# Evaluation of New Computer Components, Equipments, and Systems for Naval Use

## L. D. WHITELOCK

**T**HE THEME of this conference, "New Developments in Computers" is most appropriate at this time as we enter the first generation of solid state computers, and an era of advanced systems design. Let us consider briefly why new developments occur. Some new developments

are made to meet a need expressed by a customer, or user; others are made to meet their anticipated needs. How well the user's needs are met in contrast with the capabilities and costs of available equipment determines the degree of success of any new development. However, the user's view of a new development is not always as enthusiastic as that of its creator. The user's evaluation of the suitability and acceptability of the new development may differ from that of the creator because of variations in the method of evaluation, in technical background, and in the scope of related information, such as "what is available from competitors." Fortunately, there are many prospective users of computers, and their needs differ to such an extent that the field of interest for new developments is very wide. There is a natural urge for the user to partially or fully evaluate all

L. D. WHITELOCK is with the Department of the Navy, Bureau of Ships, Washington, D. C.

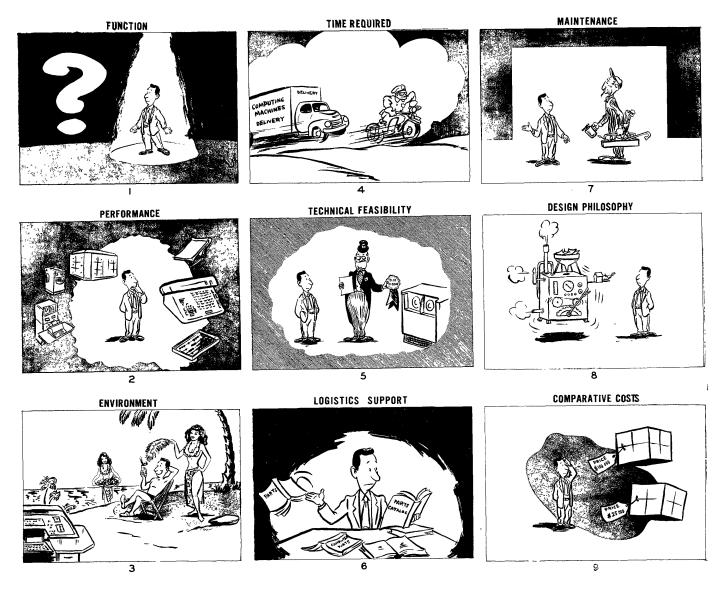

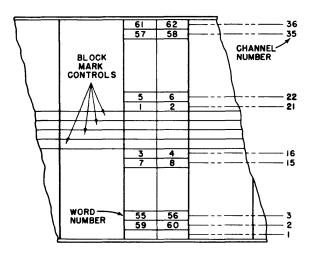

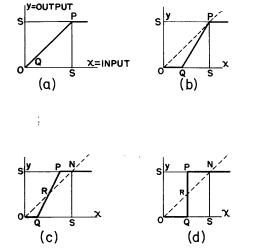

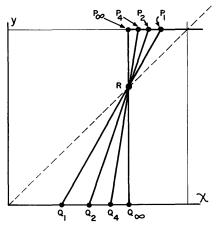

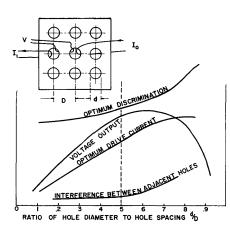

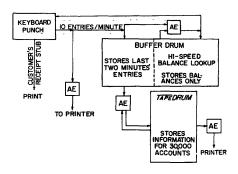

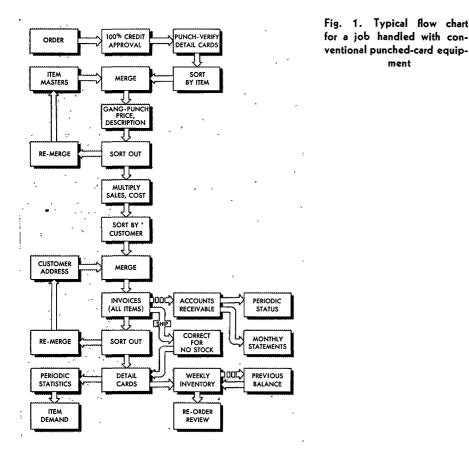

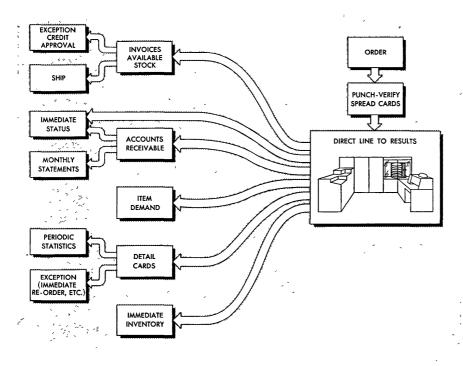

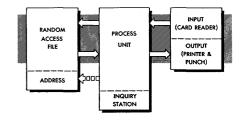

Fig. 1. Evaluation factors

new developments within his field of interest. Obviously, poorly conceived and poorly executed developments fall by the wayside because of lack of customer, or user acceptance.

It may be of interest to the relatively new computer industry to look at some brief examples, and to review the general philosophy of user evaluation and user needs. The user in this case is the Bureau of Ships. This Bureau is an extensive user of digital computer components, equipment, and systems in the following categories:

1. Shore based, commercial design.

2. Shore based, research, development and production to military performance specifications.

3. Shipboard, research, development and production to military performance specifications.

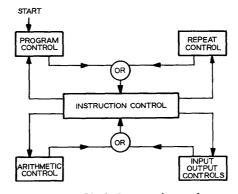

The same basic approach to evaluation is used regardless of the equipment category, and regardless of whether or not the equipment or system exists or has yet to be developed. The philosophy of approach is keyed to nine basic evaluation factors. For each specific evaluation, the basic evaluation factors are expanded by appropriate, carefully considered questions. The basic factors, Fig. 1, together with sample questions to illustrate the method are the following:

1. Function. What is the job to be done? Is it a necessary job? Can it be modified or combined with other functions to make the equipment less complex?

2. Performance. Is it clearly defined technically? Have we asked for too much? Too little? Are tolerances reasonable with respect to the intended use? Will commercial equipment do? Are there equipments with similar performance which should be considered? What is the efficiency of performance?

3. Environment. Will it be installed on shipboard? On shore? Indoors? Out-

doors? Does it meet the temperature, humidity, shock, vibration, and similar requirements for this application?

4. Time required. When must the equipment be delivered and installed? What delay can be tolerated? Is the available lead time realistic? What is time phasing with related items?

5. Technical feasibility. Has technical feasibility been proved? Have Navy laboratories evaluated the project? Is it expected to be proved with the test of equipment being produced under a research and development contract? Are there alternate approaches with more promise?

6. Logistic support. How many equipments are expected to be involved? Where and when will equipment be used? Where will major parts supplies be located? What is the lead time for ordering replacement parts?

7. Maintenance. Where will equipment be located? Who will maintain it? Are any unusual maintenance problems expected? Does the equipment design assure accessibility for maintenance? Are parts available? Is special training required for maintenance personnel?

8. Design philosophy. Is the design conservative? Critical? Reliable? How does it compare with the best in the industry? Are standard parts used where possible?

9. Comparative costs. What are the alternate approaches which appear to be technically feasible? What is the over-all cost of each approach? Is the over-all cost reasonable for the function to be performed? Should we buy or rent? Is the output the same for each alternative? What is the cost per unit of output for each alternative?

The foregoing factors, after collecting information and facts in the general areas indicated by the sample questions, will usually permit a sound choice with a minimum of deliberation. Many times the final choice is simplified by marked differences in costs of alternatives or by a drastic reduction of the number of alternatives. Two abbreviated examples are given in the following paragraphs.

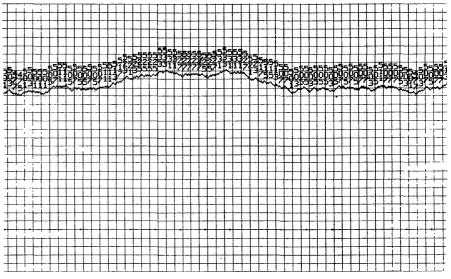

In the first example, an evaluation or analysis was made of equipment suitable for printing 1,000,000 lines per week, 120 characters per line, from magnetic tape. Equipment considered was either available or was available with a moderate amount of additional development. Equipment could be operated in three shifts if necessary. Of the seven initial alternatives, three were eliminated by the "time required" and "technical feasibility" factors, and further evaluationfactor analysis was made of the remaining four alternatives. After consideration of printing speed, efficiency, operating labor, maintenance labor, overhead, replacement parts, amortization (or depreciation) on a 10 year basis, night differentials, and the cost of developmental units where required, the over-all cost per week of each alternative was calculated with the results as shown in Table I.

Table I indicates that alternatives B and C are the only feasible selections, with final choice dependent on availability of funds, policy with respect to

#### Table I. Comparative Costs

Equipment to Print 1,000,000 Lines per Week from Magnetic Tape

| Cost | Alternative, Dollars |   |   |   |

|------|----------------------|---|---|---|

|      | A                    | В | С | D |

|      | 15,840.<br>823.680.  |   |   |   |

|      |                      |   |   |   |

C = high speed printer, purchase D = alternate multiple printers.

rental versus purchase, and similar factors.

In the second example, an evaluation was made of computers appropriate for the variety and volume of work indicated by a detailed survey of representative problems. The evaluation was made by a panel selected from personnel competent in the computer research, development, and production field, and from the computer application and programming field. The full details of this evaluation are considered to be beyond the scope of this paper. However, in summary, several alternatives were outlined and the evaluation-factor approach applied. Information was developed concerning estimated times to do the sample problems on each computer; total estimated volume of work and type of work load; availability of computer time on a rental basis; purchase versus rental of a computer; availability, price and operational cost of available computers; comparisons of hand, punched card and high-speed computer costs for sample jobs; and the relationship of total operational cost per hour to the cost of handling 1,000,000 characters of input. The latter relationship is summarized in Table II.

#### Table II. Computer Comparisons

| Com-<br>puter<br>Type | Input Speed<br>Characters/<br>Second |     | Cost, Dollars<br>to Process<br>1,000,000<br>Characters<br>of Input |

|-----------------------|--------------------------------------|-----|--------------------------------------------------------------------|

| A                     | 10,000 .                             |     | 3.05                                                               |

| В                     | 37                                   | 110 | 825.00                                                             |

| С                     | 8                                    | 10  | 406.00                                                             |

| D                     |                                      |     | 89.20                                                              |

\* Includes cost of programmers, operators and maintenance.

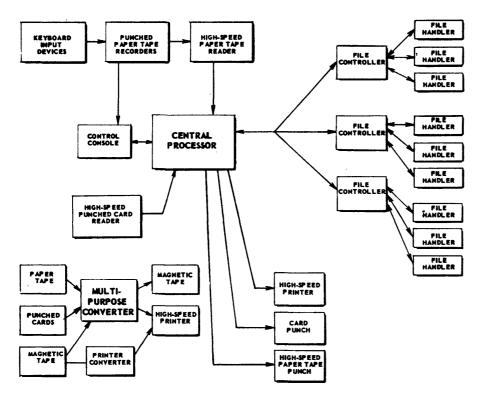

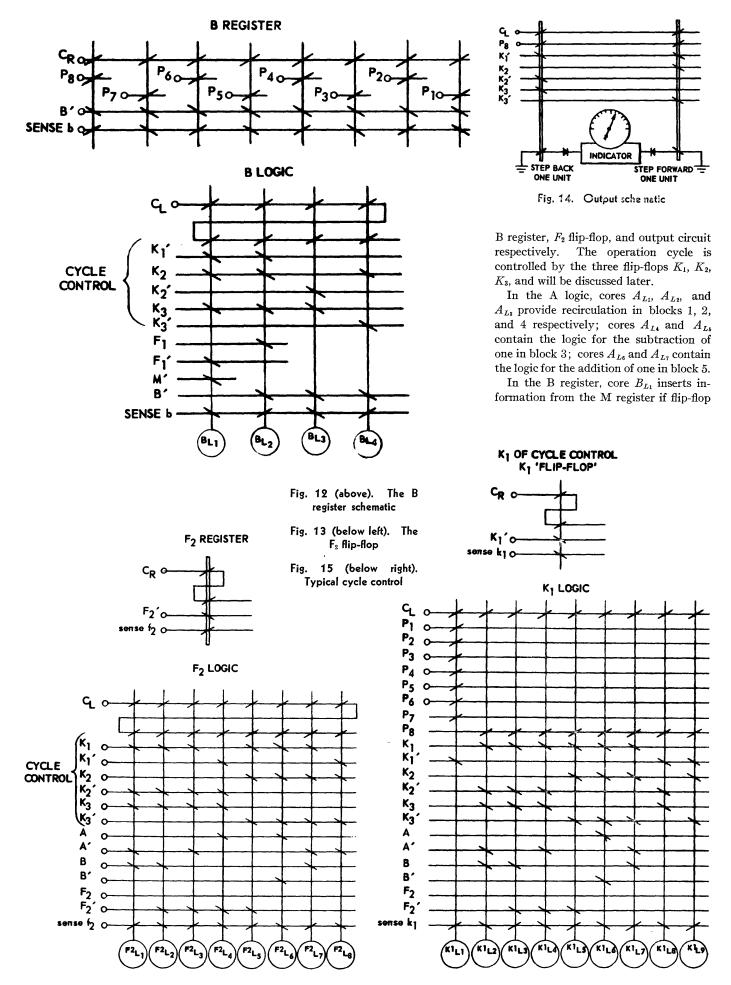

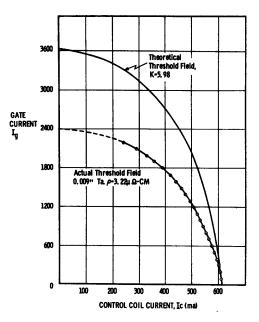

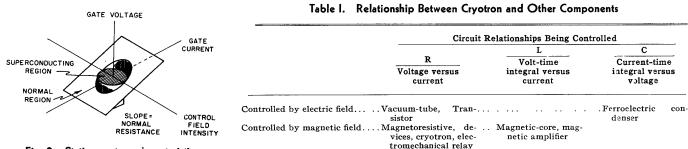

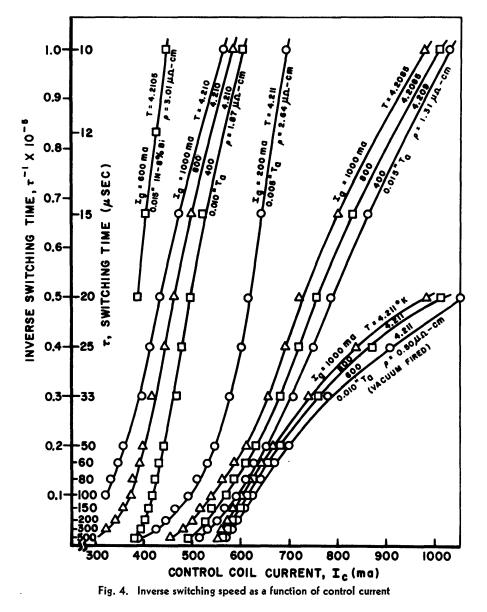

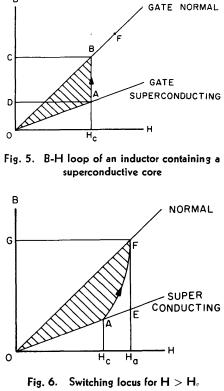

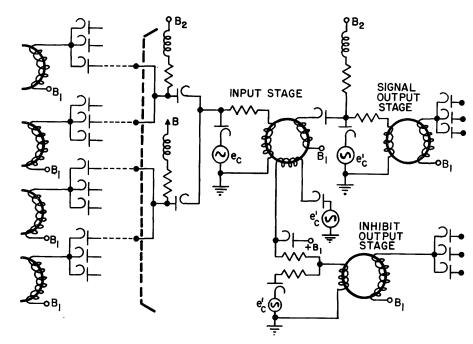

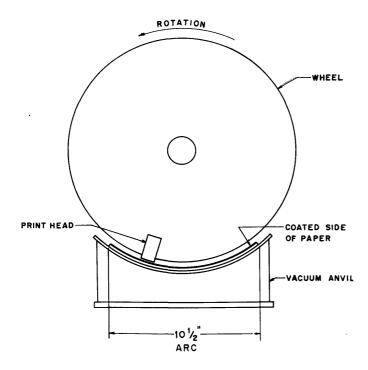

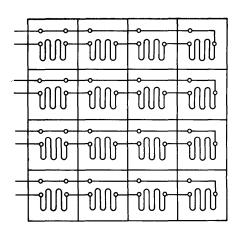

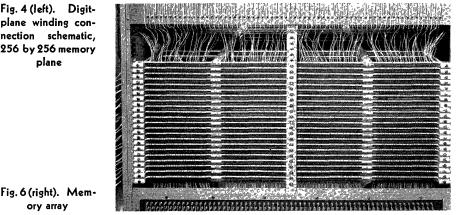

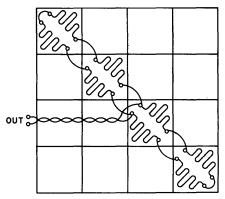

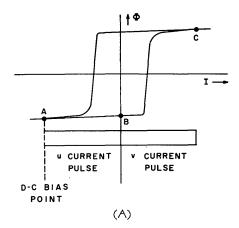

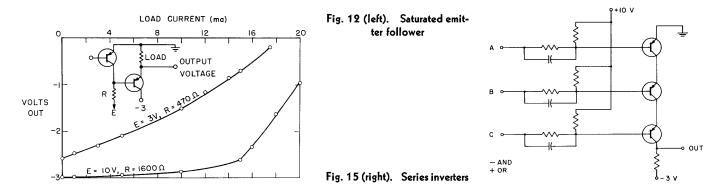

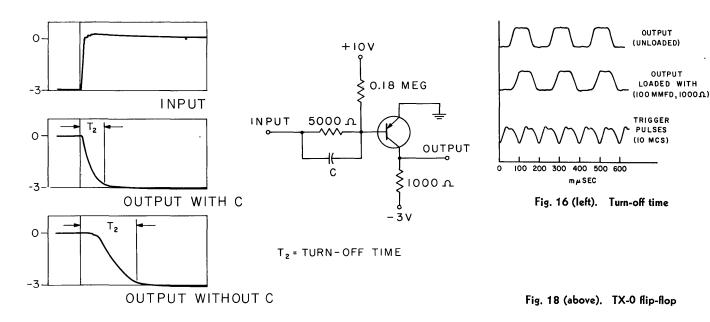

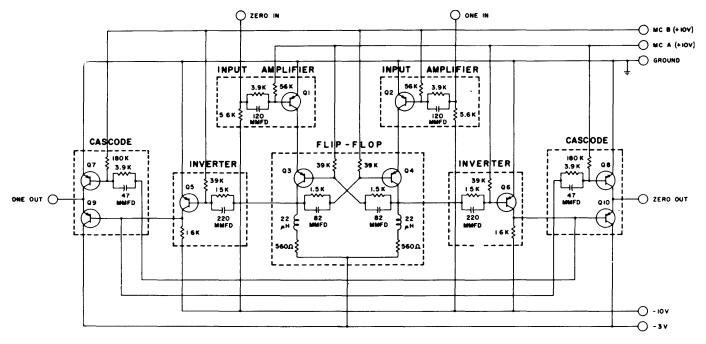

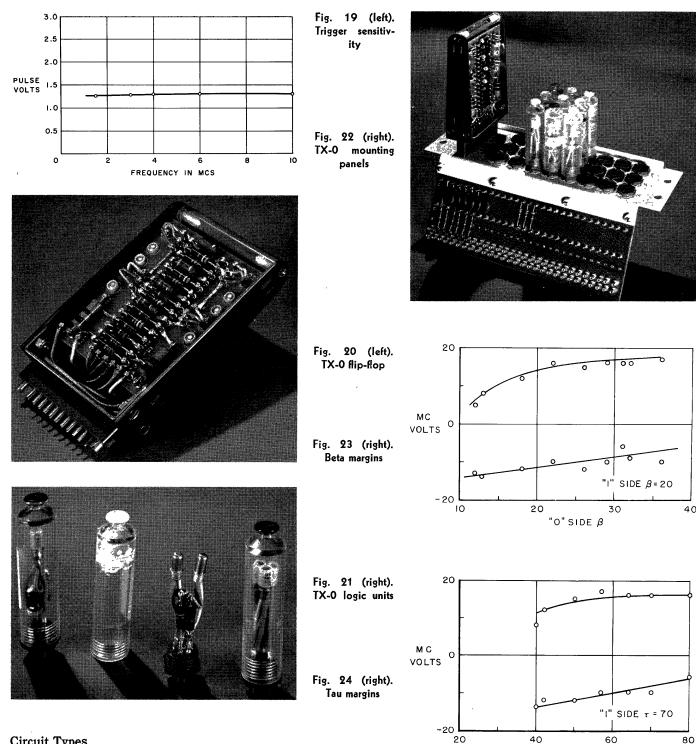

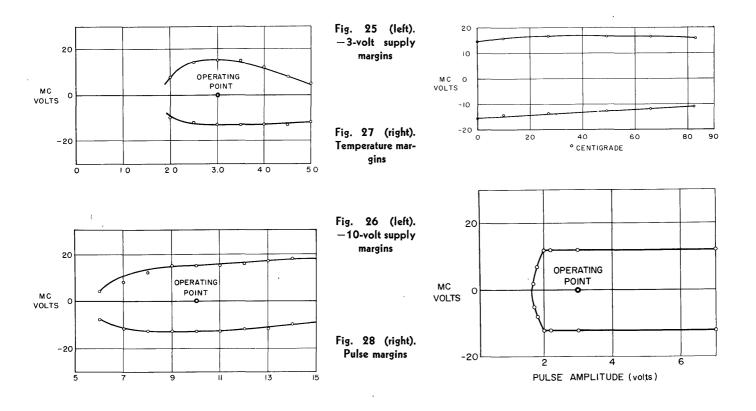

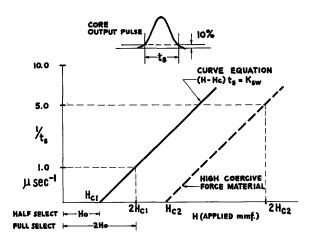

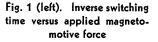

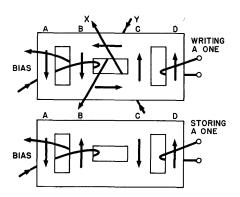

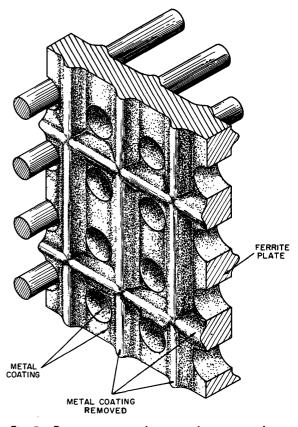

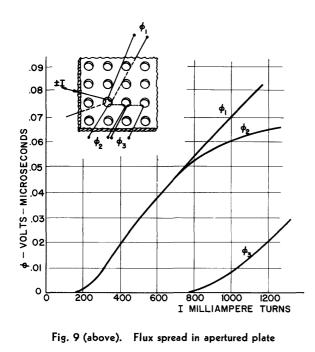

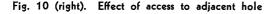

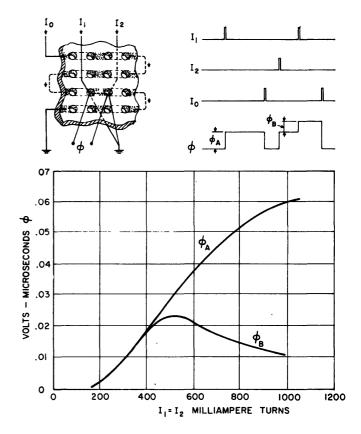

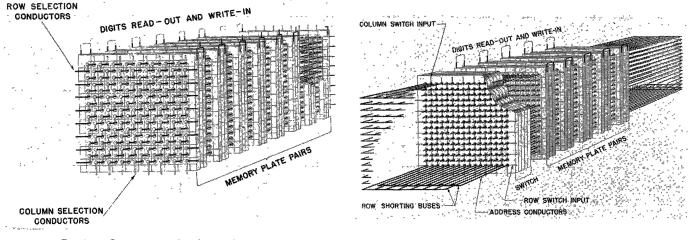

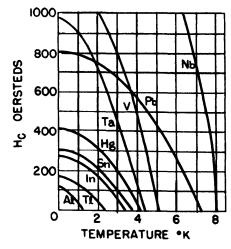

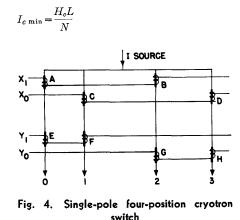

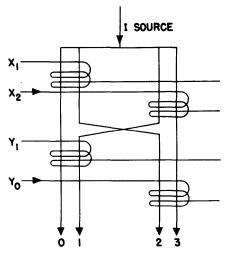

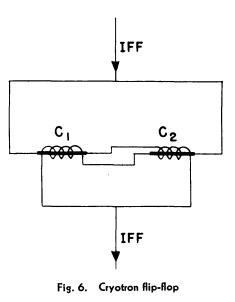

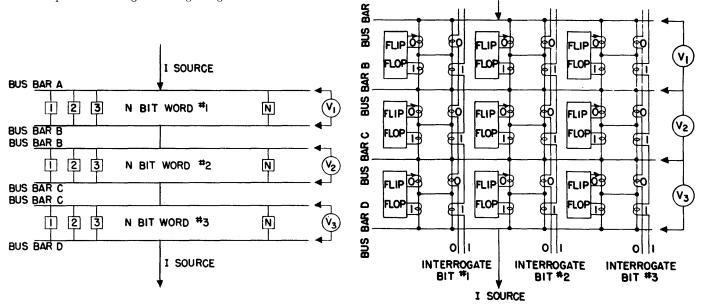

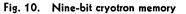

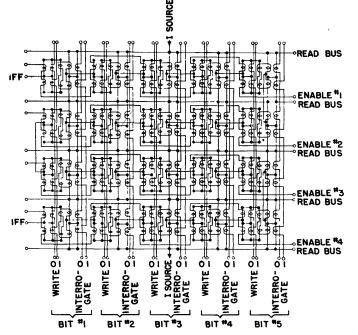

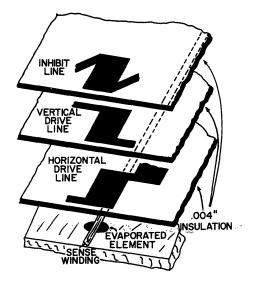

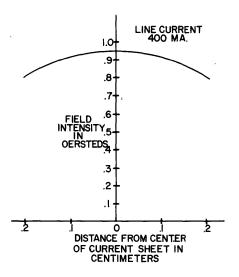

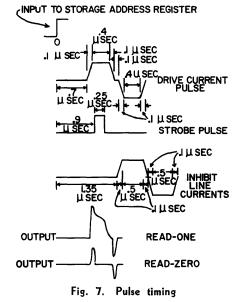

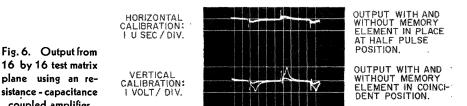

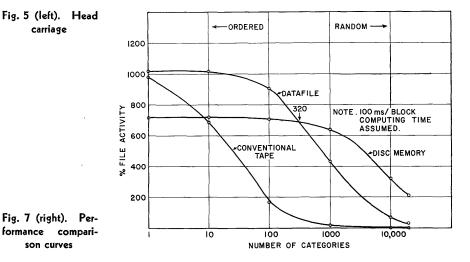

In the foregoing example, final evaluation-factor analysis resulted in a reduction of alternatives to only one logical choice.