plus

j.

AES-Plus Maintenance & Service Manual

Edition: October 1977

-Jan 79

# **Proprietary Notice**

This publication contains information proprietary and confidential to AES Data Ltd. Any reproduction, disclosure or use of this publication is expressly prohibited except as AES Data Ltd may otherwise authorize in writing

AES Data Ltd 570 McCaffrey St Laurent P Q. H4T 1N1 Tel: 341-5430 Telex: 05-826602

..

Publication #: A5-999-003101, Issue 00

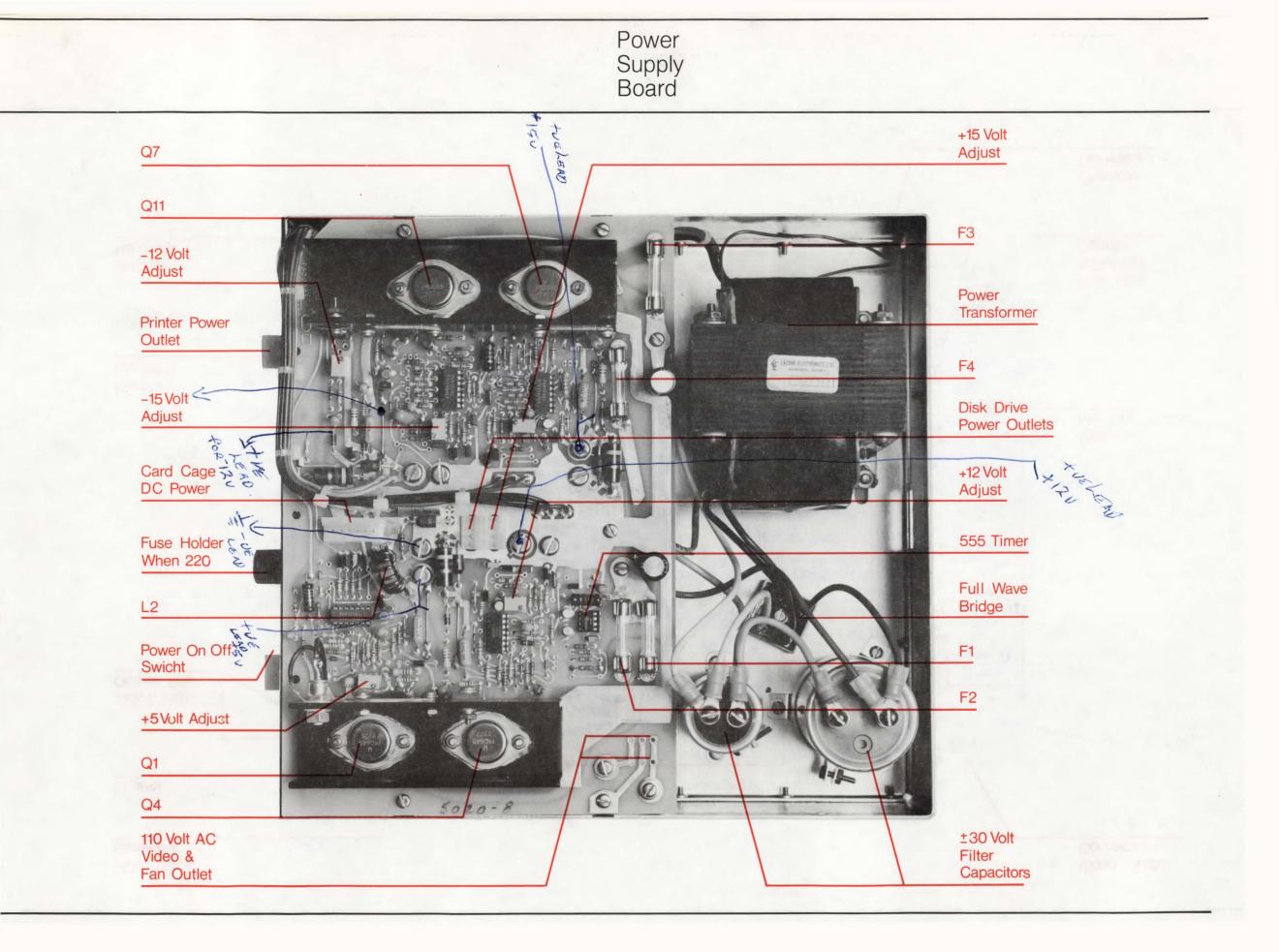

| 1   | Introduction &<br>General Description | 4              | Installation<br>& Maintenance                                     |

|-----|---------------------------------------|----------------|-------------------------------------------------------------------|

| 1.1 | Introduction                          | 4.1            | Installation                                                      |

| 1.2 | Specifications                        | 4.2            | Maintenance<br>& Diagnostic                                       |

| 1.3 | Theory of<br>Operation                | A)<br>B)<br>C) | Introduction<br>Diagnostic Procedures<br>Power Supply Adjustments |

| 2   | Boards<br>Analysis                    | 5              | Peripheral<br>Units                                               |

| 2.1 | Video<br>Board                        | 5.1            | Video<br>Monitor                                                  |

| 2.2 | Input / Output<br>Board               | 5.2            | Printer                                                           |

| 2.3 | C.P.U.<br>Board                       | 5.3            | Keyboard                                                          |

| 2.4 | Power<br>Supply                       | 5.4            | Disk<br>Drives                                                    |

| 3   | Mechanical<br>Configuration           | 6              | Addendum                                                          |

| 3.1 | Assembly                              |                |                                                                   |

3.2 Components

### SECTION 1

## 2. SCOPE OF MANUAL

## INTRODUCTION

#### 1. GENERAL DESCRIPTION

A text editor is presently the most effective means of converting spoken, handwritten and recorded information into typed copy for distribution. This conversion is called Word Processing. In essence, a text editor permits all information to be entered, recorded, verified, modified and edited before committing it to paper.

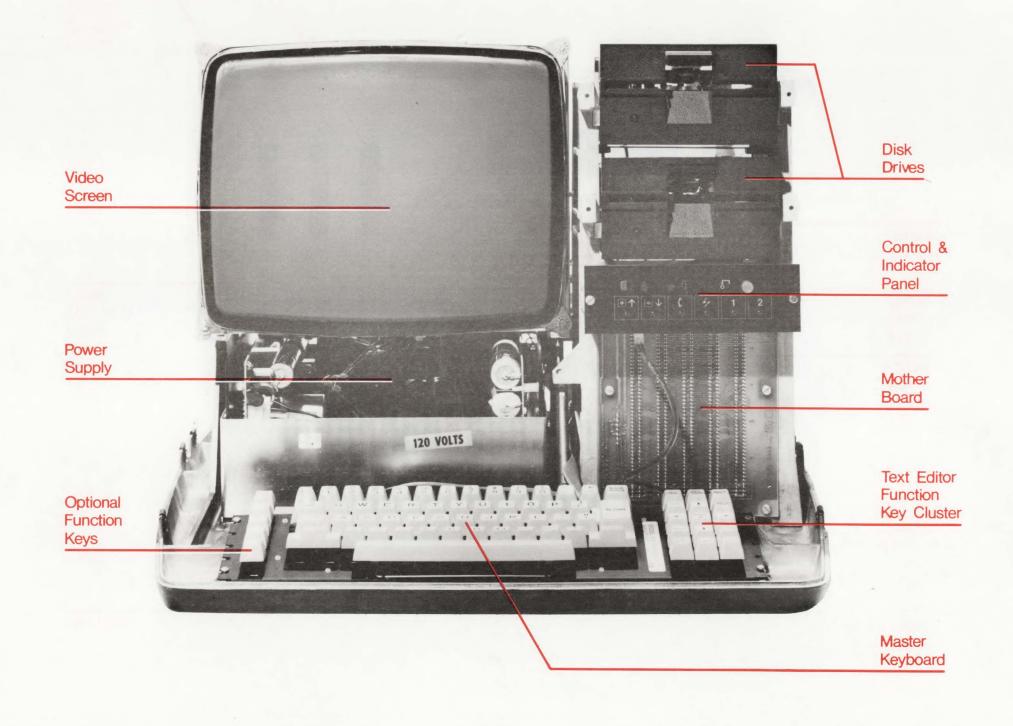

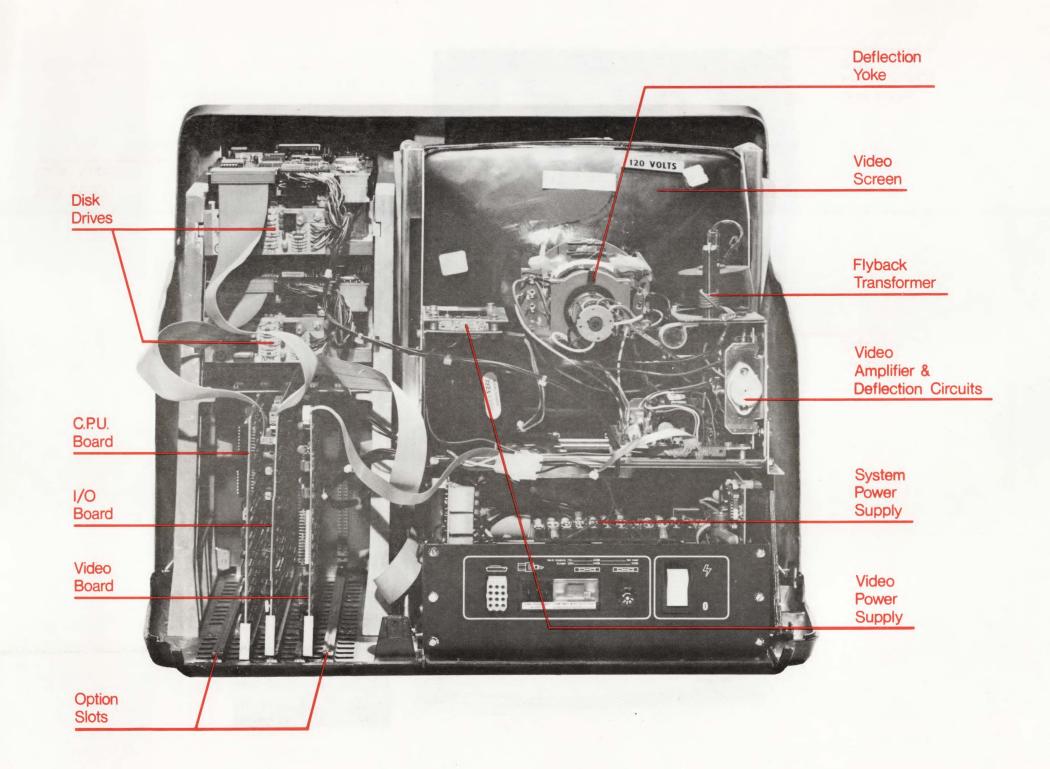

The AES-PLUS Text Editor brings new dimensions to the world of Word Processing. It is compact, consisting mainly of a CRT console and printing unit. It is also programmable, allowing the feasability o creating customer oriented software packages.

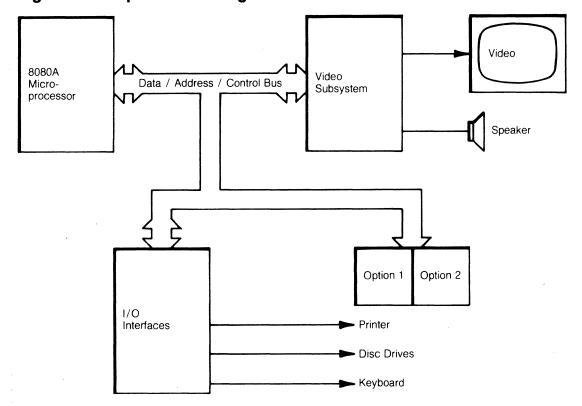

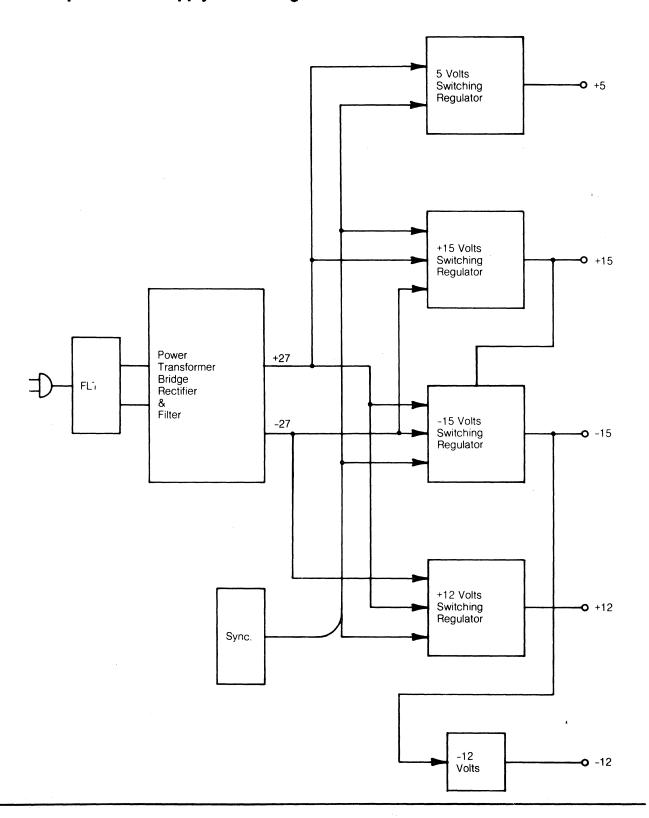

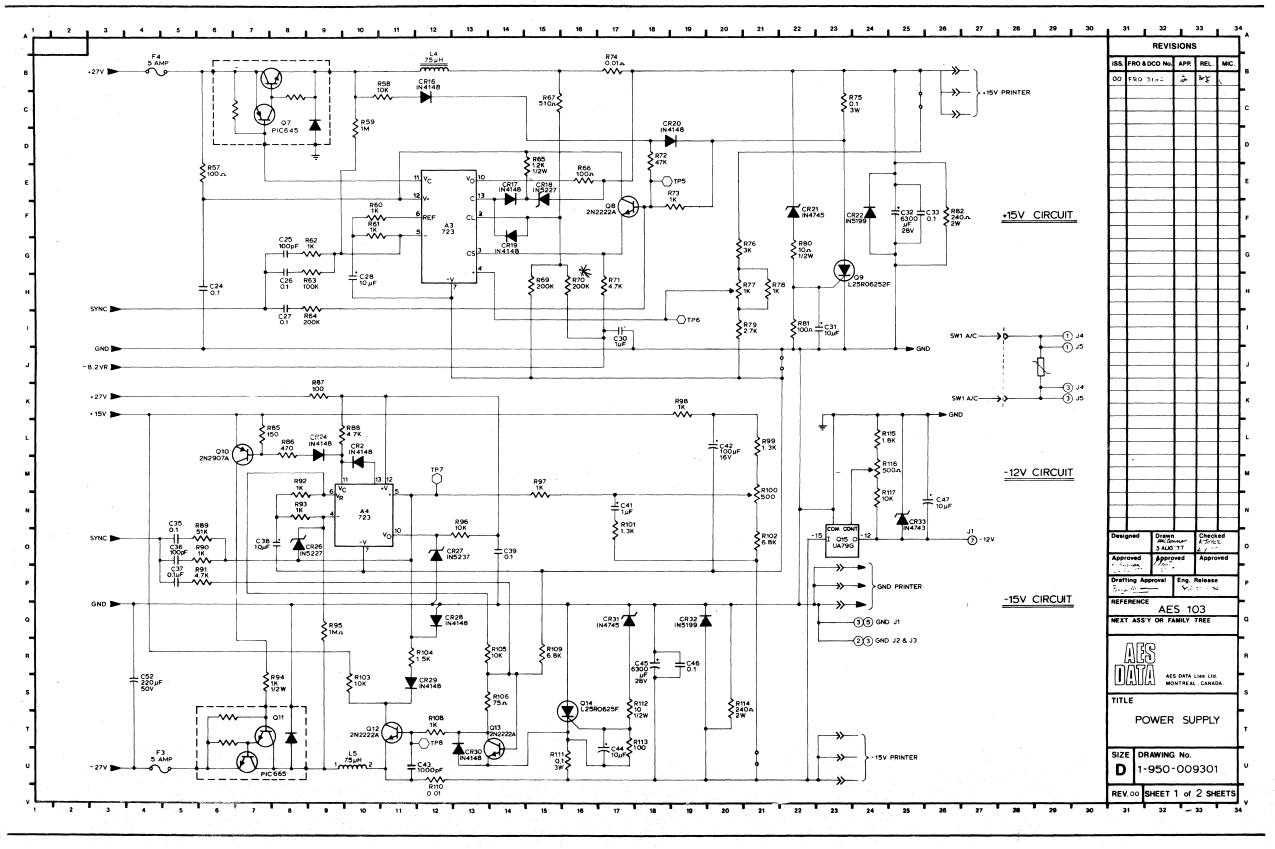

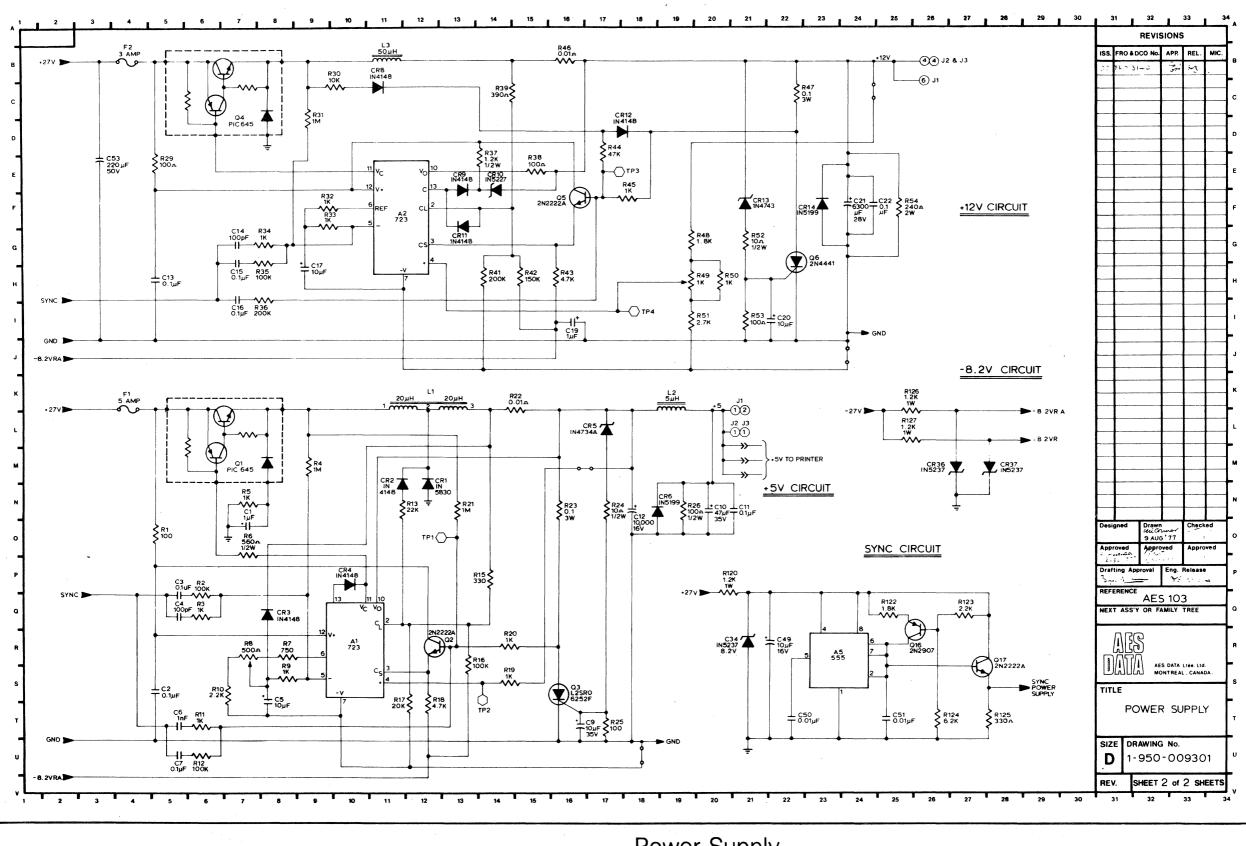

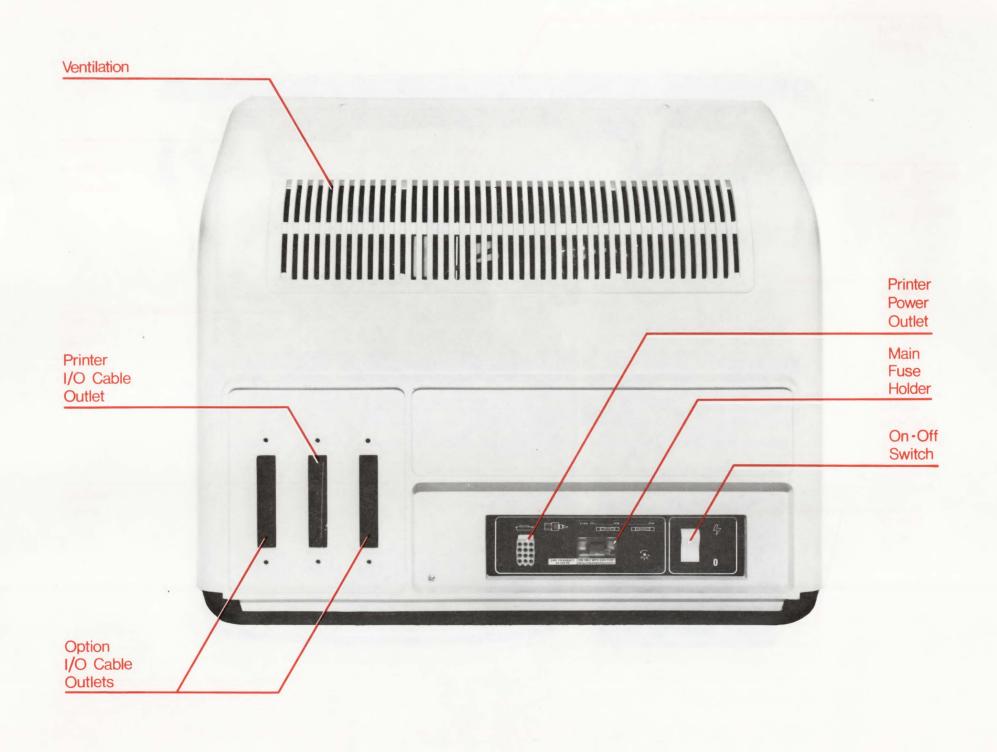

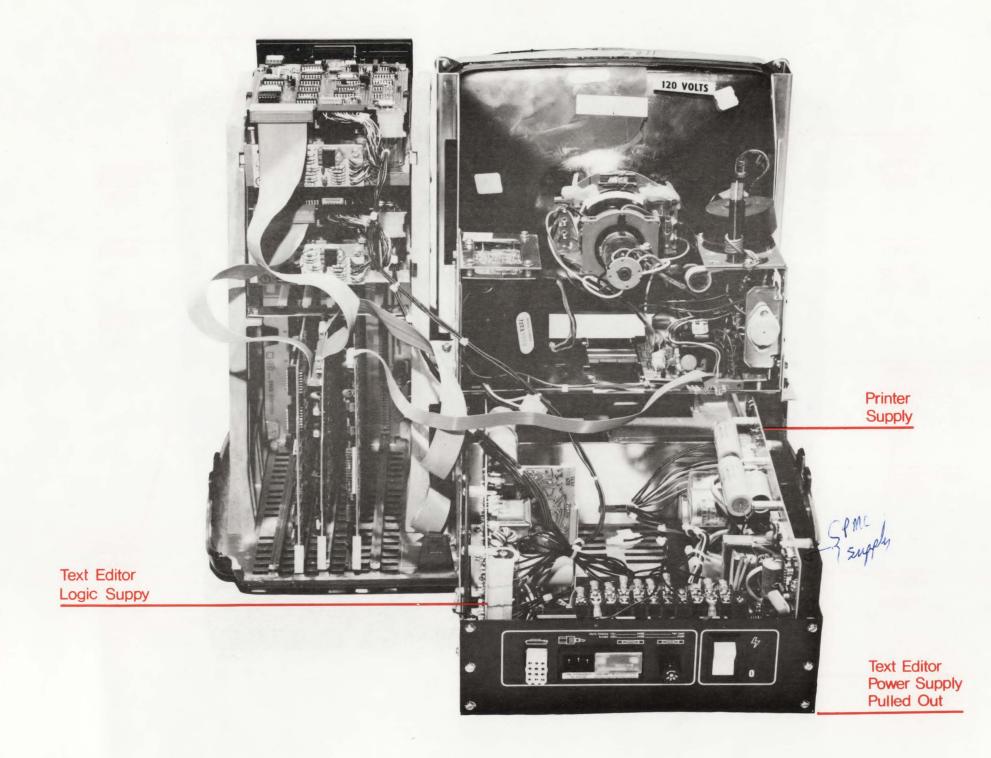

The AES-PLUS is designed around an integrated processor, the Intel 8080A, and utilizes the latest technological breakthroughs such as 16K dynamic random access memories. The design of this text editor was largely made possible by the use of software controlled functions, having an instruction memory with 32K of capacity, thus minimizing the electronics to the point where only three 12.5 x 7.5 inch printed circuit boards are needed. Two additional boards may also be added to the system as expansions where several options may be chosen. This manual contains all the necessary information on the AES-PLUS and provides maintenance procedures and field support. It contains five chapters where Chapter I outlines the Text Editor in its specifications and gives the Theory of operation. Chapter II gives a detailed description of each printed circuit board including the switching power supply. In Chapter III, a complete mechanical description is given with the aid of photographs and legends; a set of component data sheets also occupies that section.

Chapter IV gives general unpacking and installation procedures at the customer's site and also provides field maintenance and fault isolation with the aid of a diagnostic program. Chapter V concludes the manual with a detailed description of each peripheral unit.

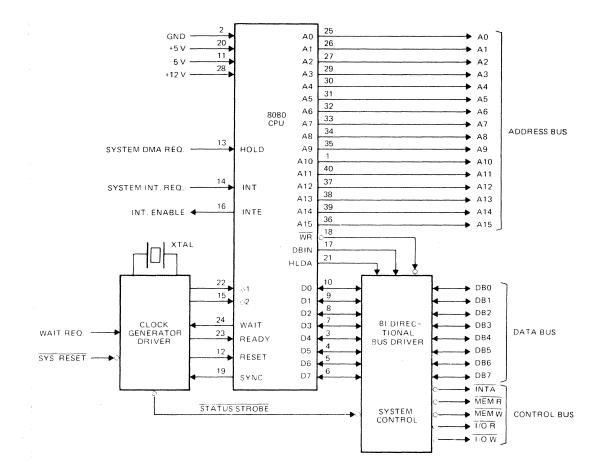

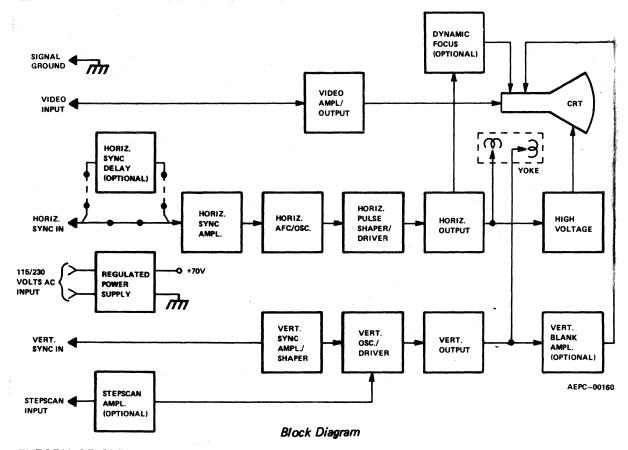

## Figure 1 AES plus Block Diagram

## SECTION II

## AES-PLUS TECHNICAL SPECIFICATIONS

| CONFIGURATION:<br>CRT DISPLAY: | Stand alone word processing system consisting<br>of: one cabinet containing a CRT, a keyboard<br>two magnetic mini-diskette drives and all the<br>electronics. A high-speed printer completes<br>the whole system.<br>35.56 centimeter (14 inch) viewable<br>diagonally; 100 sq. in. dark non-glare |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | screen with P39 green phosphor.                                                                                                                                                                                                                                                                     |

| VIDEO SCREEN CAPACITY:         | 2240 characters including control lines and 2080 without control lines.                                                                                                                                                                                                                             |

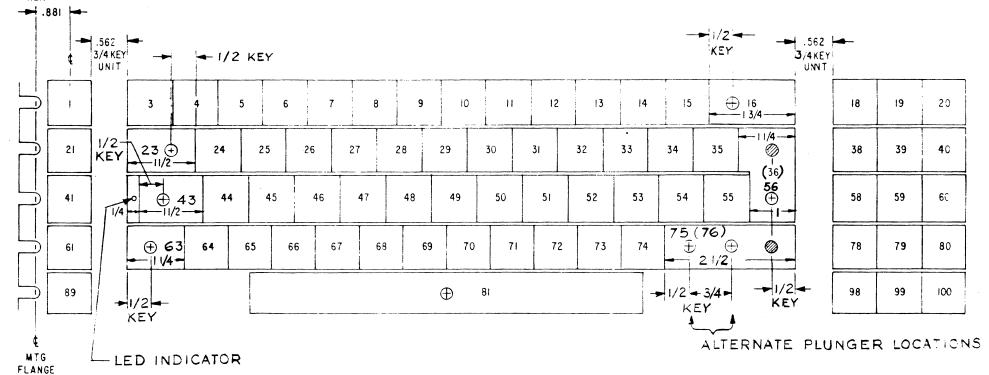

| KEYBOARD STRUCTURE:            | One electronic keyboard consisting of standard<br>typewriter keys and one 15-key function<br>cluster for filing and editing.                                                                                                                                                                        |

| CHARACTER REPERTOIRE:          | 66/70 keys for alphanumeric upper or lower case characters. Up to 53 special symbols.                                                                                                                                                                                                               |

| CHARACTER SPACING:             | Mono spaced.                                                                                                                                                                                                                                                                                        |

| SCANNING:                      | 262.5 lines in both interlaced A and B fields (312.5 lines for Europe).                                                                                                                                                                                                                             |

| VIDEO REFRESH RATE:            | 60 per second (50 for Europe).                                                                                                                                                                                                                                                                      |

| STANDARD DISPLAY<br>FORMATS:   | 28 lines of up to 80 characters in a single row.                                                                                                                                                                                                                                                    |

| CURSOR:                        | Half-tone software-controlled rectangle.                                                                                                                                                                                                                                                            |

| CURSOR MOVEMENTS<br>& SCROLL:  | Up to 15 different movements.                                                                                                                                                                                                                                                                       |

| FUNCTIONS:                     | Video format, Edit, File, Printer, dual-disc<br>and special purpose functions.                                                                                                                                                                                                                      |

| SIZE & WEIGHTS:         | 52.0cm (20.5")D x 48.26cm (19")H x 60cm<br>(24") W.<br>30.9 kgs (68 lbs). |

|-------------------------|---------------------------------------------------------------------------|

| POWER REOUIREMENTS:     | Approximately 400 watts.                                                  |

| OPERATING TEMPERATURE:  | 0°C to 40°C.                                                              |

| RELATIVE HUMIDITY:      | 10% to 90% non condensing.                                                |

| ELECTRONICS:            | Standard MOS and TTL, SSI, MSI and LSI circuit                            |

| VIDEO CONSOLE CONTROLS: | Screen brightness and bell volume.                                        |

| C.P.U:                  | 8080A Integrated processor.                                               |

| MEMORIES:               | Instruction Memory 32K x 8.<br>Bootstrap 512 x 8.                         |

Instruction Memory 32K x 8. Bootstrap 512 x 8. Video Memory 16K x 9.

1.2

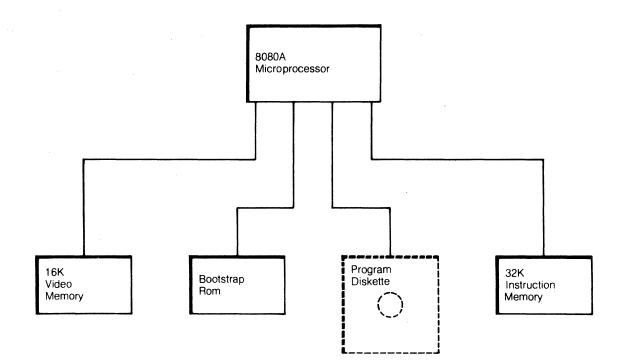

• <u>The Video Memory</u>: This memory has a capacity of 16K x 9 bits and employs 16K RAM devices. It is used to maintain keyboarded characters on the CRT at their specific location. Since a video page needs only 8K of memory, the current video page may be displayed while the additionnal 8K could contain a "background" page or any page desired. (This "background page" has not yet been included in the operating system).

## NOTE:

Several ROM memories are also found in the video subsystem; these are primarly used to generate algorithms related to character locations in the video memory.

## Figure 2 Memory Subsystem

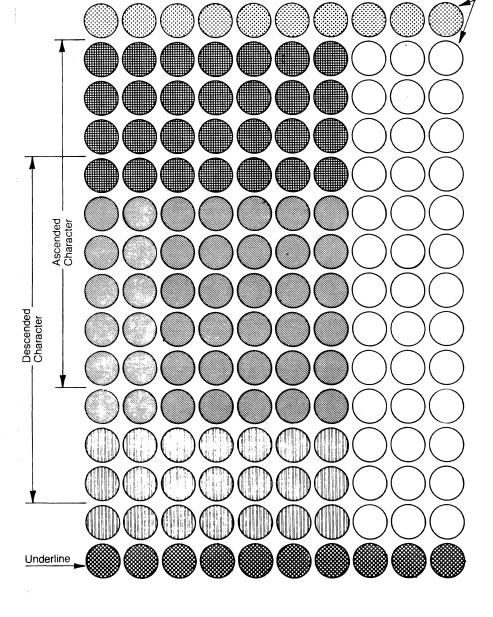

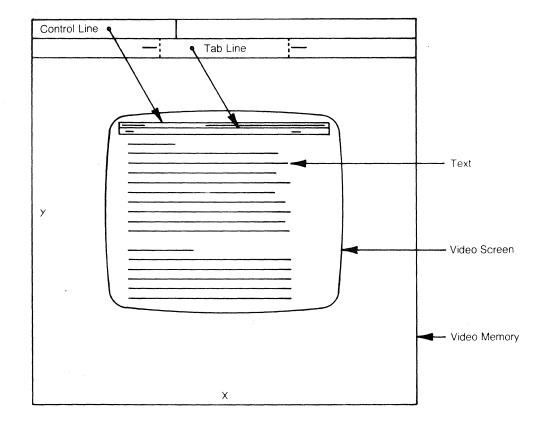

- 2.3 <u>Video Subsystem</u>: The Video Subsystem consists of the CRT, the Video Memory and associated control circuits. (FIG. 3)

- a) <u>The CRT Monitor and the Video Memory</u>: The CRT monitor displays 28 lines of information with 80 character locations per line. The top line is called "Control Line" and consists of a half-tone band on which appear messages and status indicators of the operating AES-PLUS Text Editor. The second line is the format line on which are displayed format information, tab locations, margin setting, indentation etc. The control line is not scrollable on the video screen and occupies the first Y address of the video memory. The format line, however, is scrollable from left to right on the video page, in other words it follows the video window throughout the video page in the X direction only and occupies the second Y address in the video memory.

The visible page of the display is an XY coordinate matrix. The X coordinate is divided into 80 character slots. The Y coordinate is divided into 28 lines. Thus the XY matrix determines one particular character location on the CRT by a specific number in X and Y. Each character slot is then allocated one position in the video memory and the correct character will always be displayed on the screen at the proper location.

\_

### SECTION III

### THEORY OF OPERATION

This section describes the theory of operation of the AES-PLUS Text Editor. A more detailed description is given in Chapter II, where the printed circuit boards are analyzed individually.

## 1. CONFIGURATION

The AES-PLUS consists of 6 subsystems: the integrated microprocessor, the memories, the video, the magnetic storage, the printer and the optional communication package.

#### 2. FUNCTIONAL DESCRIPTION

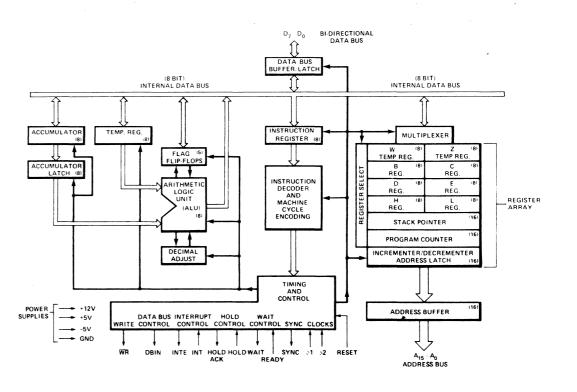

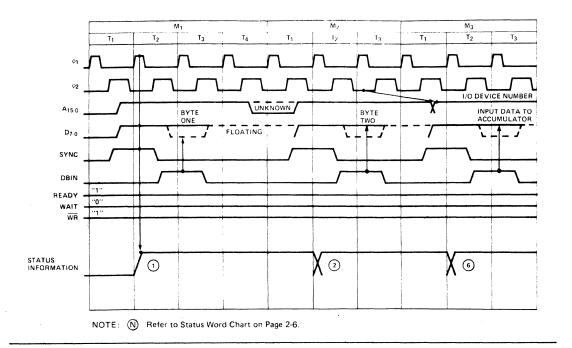

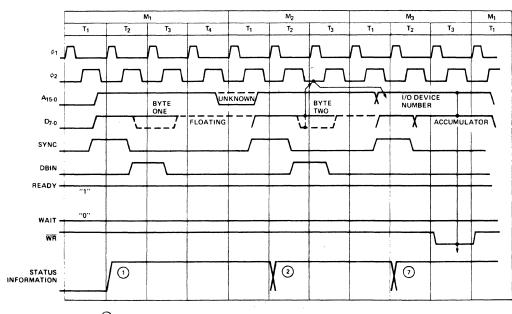

2.1 The 8080A Microprocessor: This device is a self-contained integrated CPU in a 40-pin DIP package and is designed to be interfaced with memories and I/O peripherals of all types. It is a "buss" oriented system where CPU and I/O peripherals read the data buss at certain predetermined periods. In the AES-PLUS Text Editor, it controls every operation performed from the keyboard for editing and filing of texts displayed on the video screen.

Every function is stored in a RAM memory from a program diskette when the machine is first turned on. All these functions are, however, in the form of instruction bytes which are decoded by the microprocessor. The process of loading a program into a RAM is called "BOOTSTRAP" and introduces flexibility in the machine operation. Several program Option packages are available and are tailored to meet customers requirements. The 8080A Microprocessor Module is interfaced with a Programmable DMA Controller which handles all data transfers from memory to floppy disc. The Microprocessor communicates with the video subsystem and the printer via the address buss, the data buss and five control lines.

All I/O decoding is performed from the address buss and allows the addressing of individual peripherals. Provisions have also been made to allow for two additional expansion boards, for instance the Communications or the IBM MAG Card interfaces.

2.2 <u>The Memory Sub-System</u>: The AES-PLUS employs three different memories for its operation and they are:

- The Instruction Memory.

- The "Bootstrap" Memory.

- The Video Memory.

• The Instruction Memory: This memory has a capacity of 32K x 8 bits and employs 16K RAM devices. The instructions are loaded from a program diskette when the AES-PLUS is first turned on; they are then processed by the 8080A CPU, which executes these in one machine cycle of 2 microseconds. These instructions are also part of a repertoire of commands associated with the filing and editing functions of the Text Editor.

• <u>The "Bootstrap" Memory</u>: This memory is a ROM and consists of a 512 x 8-bit device. It contains all the program loading instructions used when the text editor is first turned on.

The video memory has a capacity of 16K x 9-bits where the lower 7-bits define the ASCII characters, the 8th bit defines the underline and the 9th bit generates the halftone background video. The video page occupies a block of 8K of memory and, in the case of the AES-103, since 16K is available, a second video page may be accessed. The address of any location in this memory is produced by the generation of an X and a Y number, referring in that order to the character position and the line number. The address byte contains 16 bits and has the following format:

15

14

13

12

11

10

9

08

07

06

05

04

03

02

01

00

11

Y

X

X

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Bit 15 is decoded by the memory synchronization circuit when the CPU accesses the video memory.

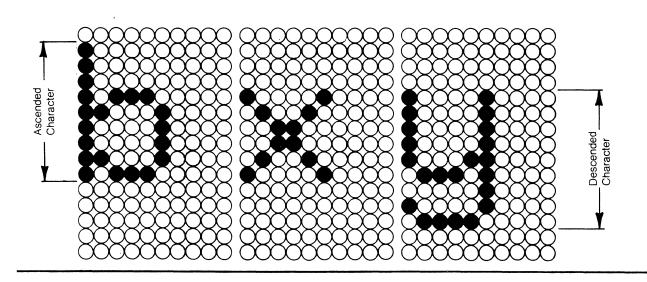

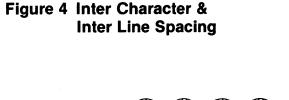

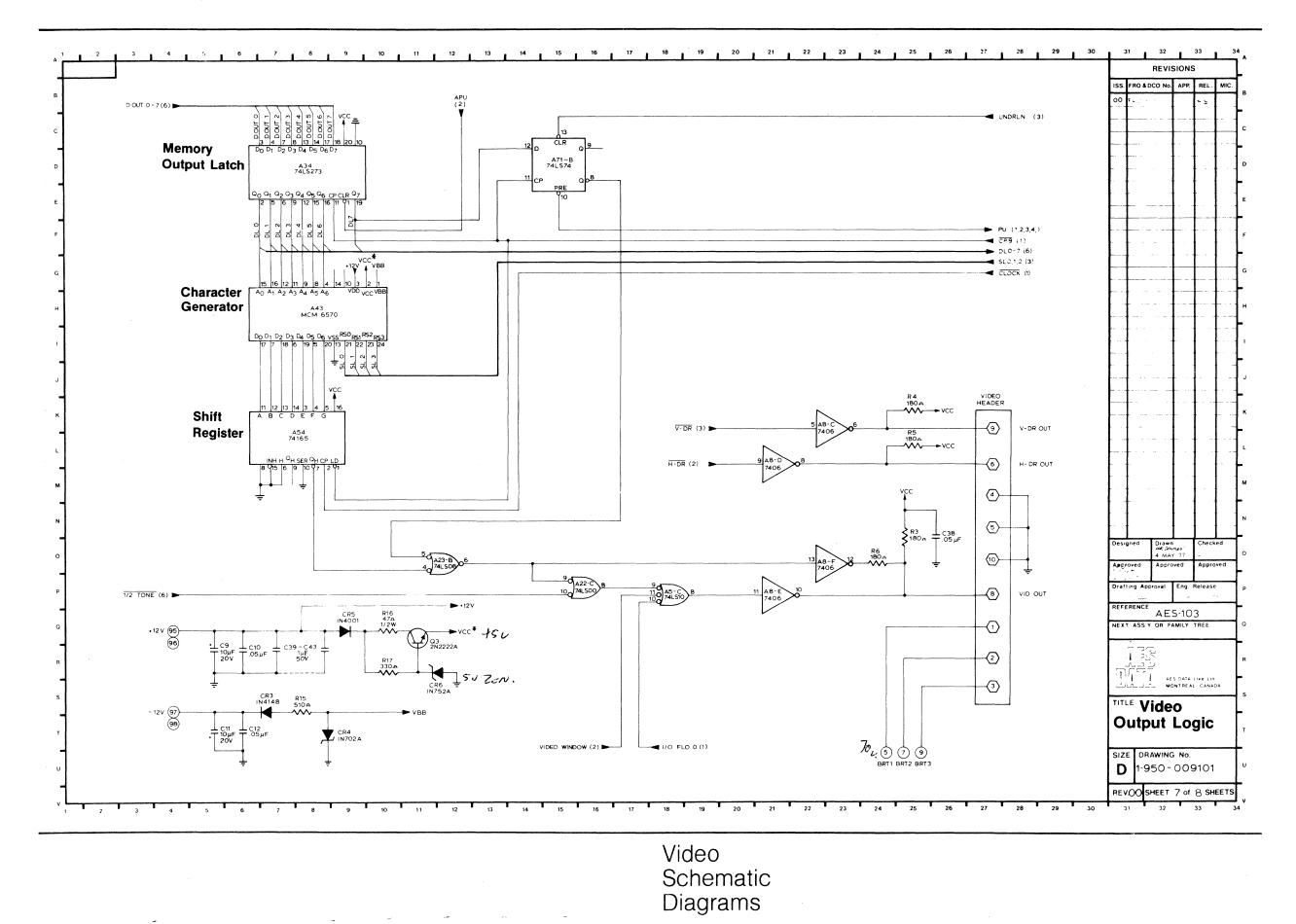

b) <u>Character Generation</u>: Each character is generated within a 7 x 13 dot matrix where normal and descending characters may be displayed. To provide inter character and interline spacing, a character block concept is used; such a character block consists of 10 dots in the horizontal plane and 15 dots in the vertical plane (see FIG. 4).

Blanks

-

$\sim$

Figure 3 Video Subsystem

-

The cursor is a software controlled character and consists of a half-tone rectangle which occupies the whole  $10 \times 15$  dot matrix.

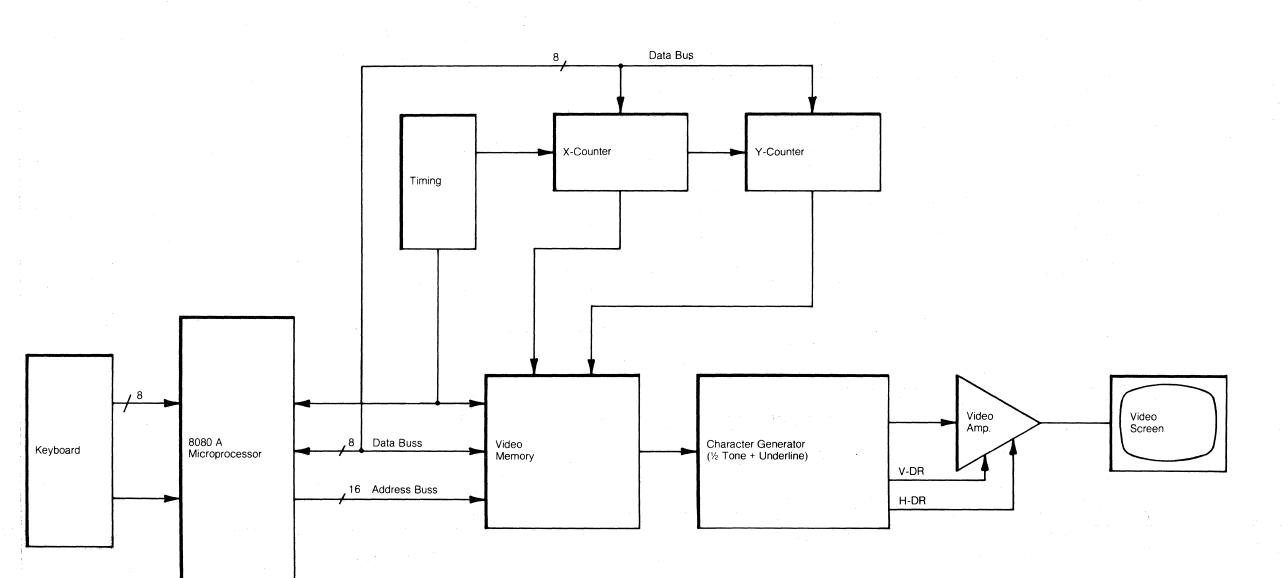

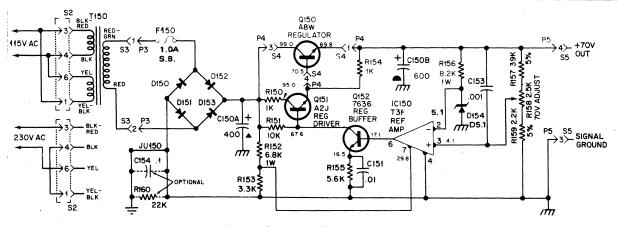

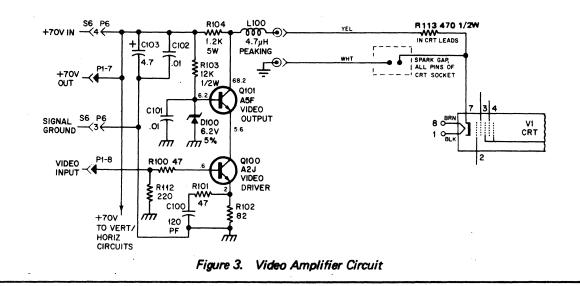

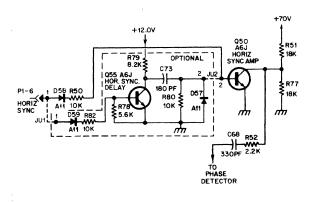

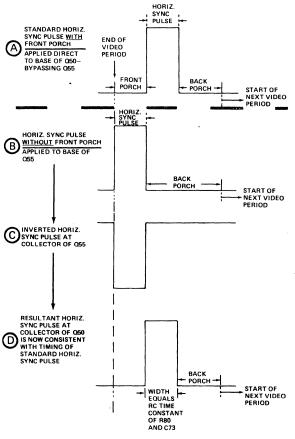

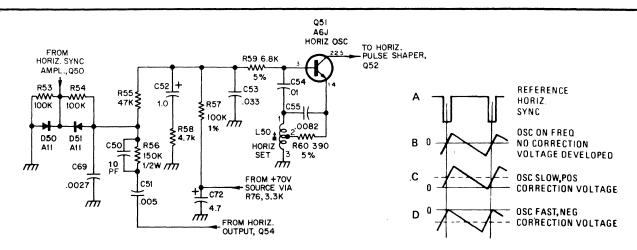

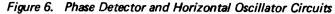

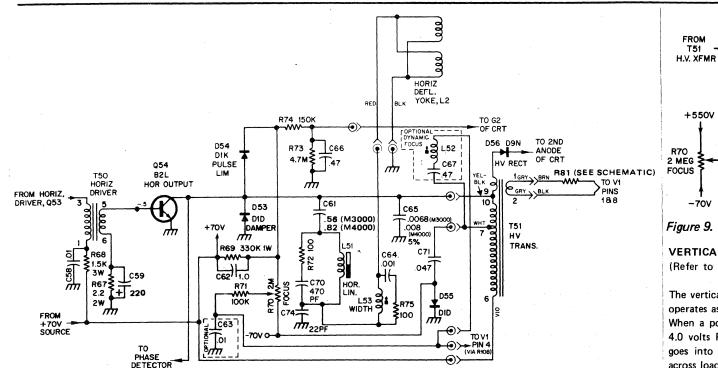

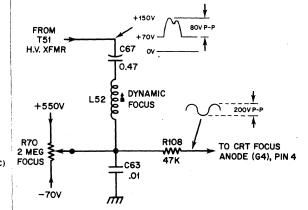

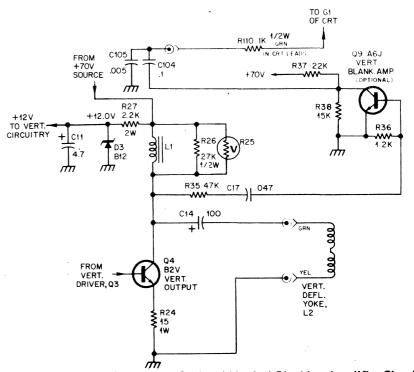

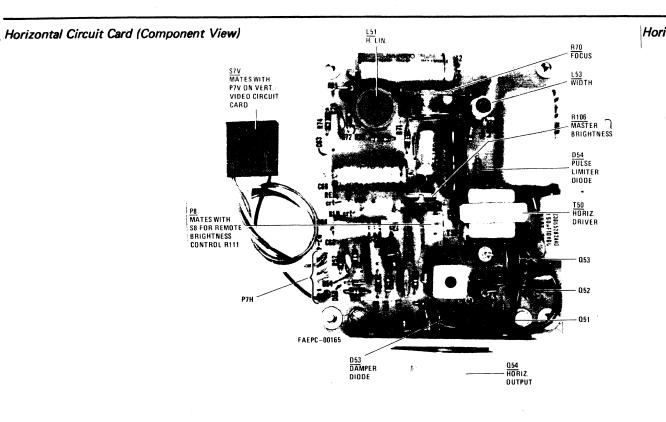

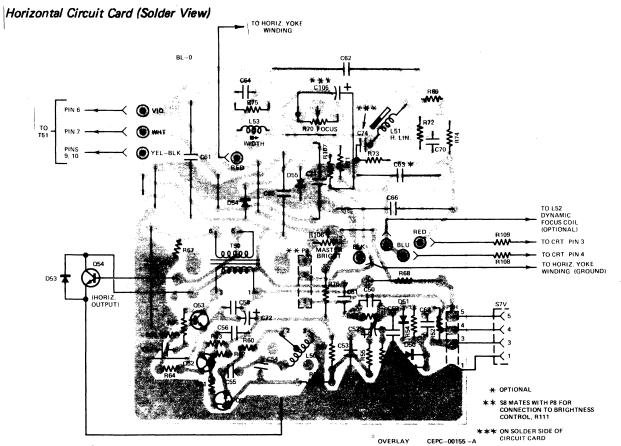

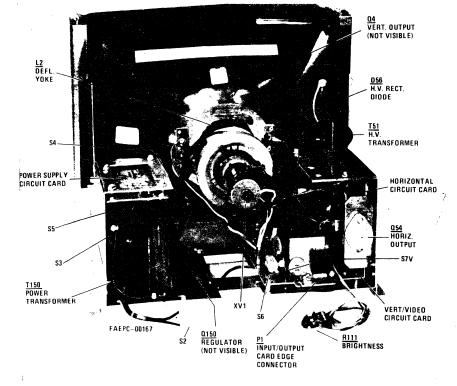

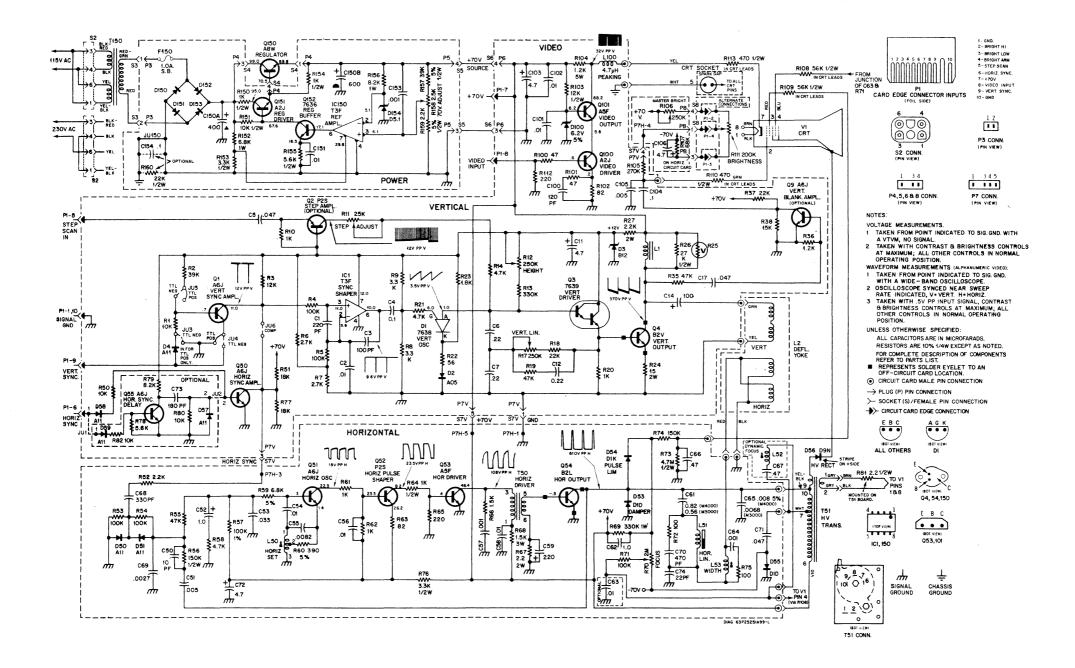

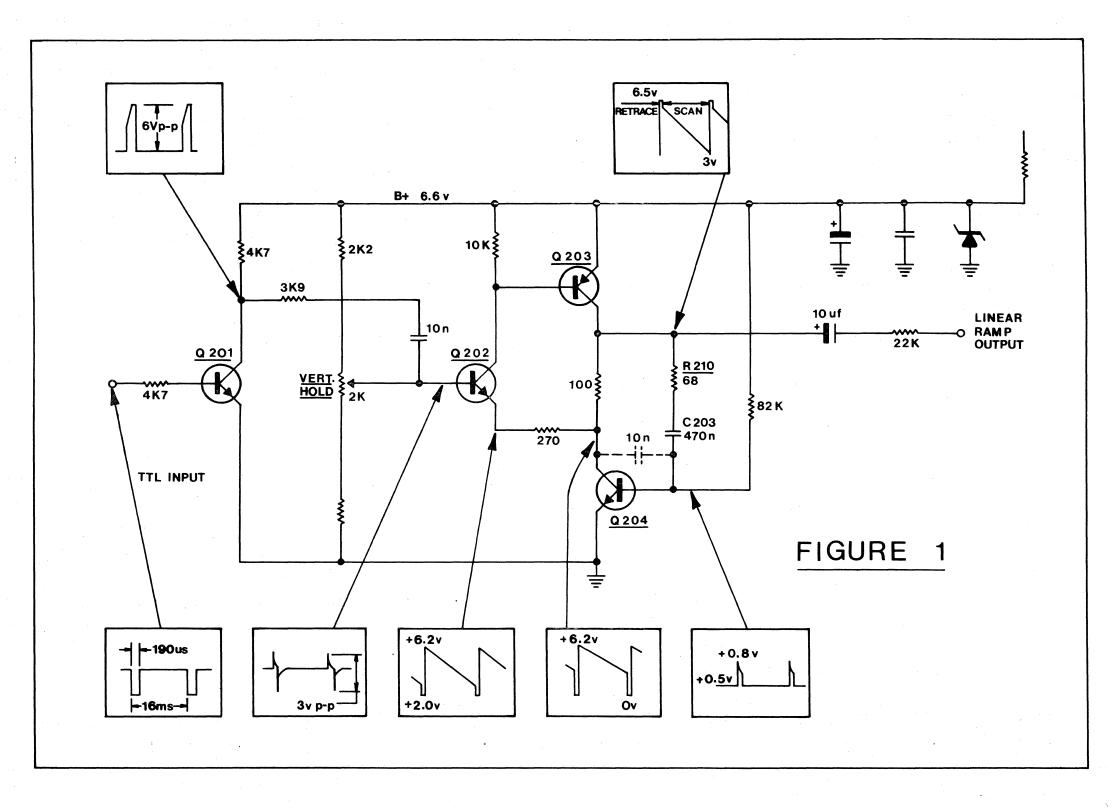

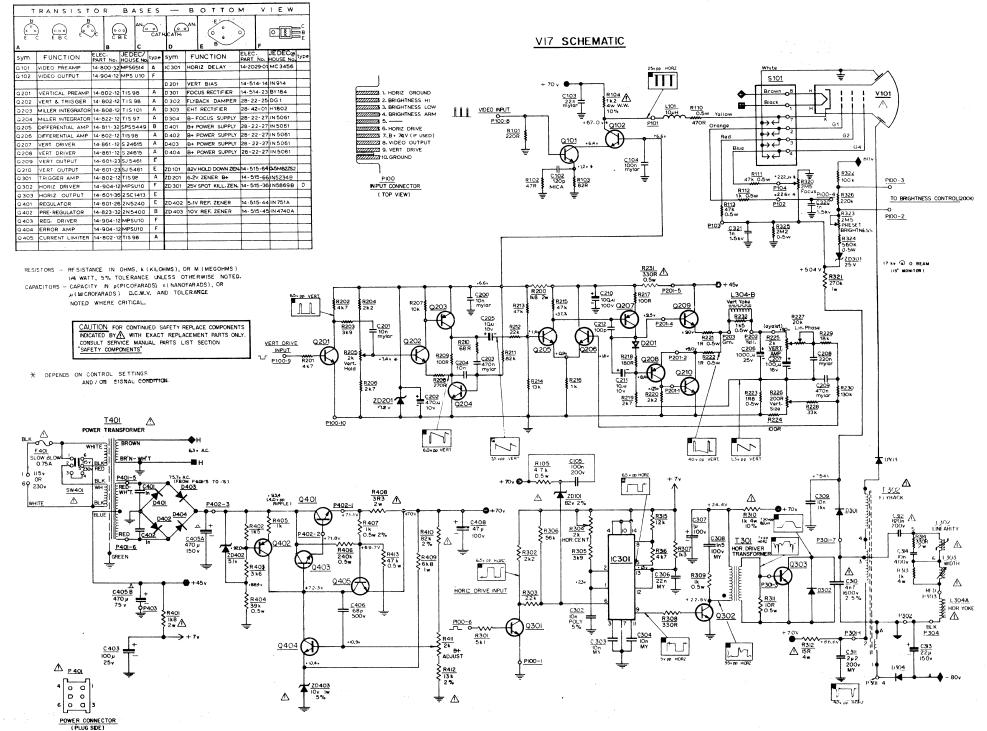

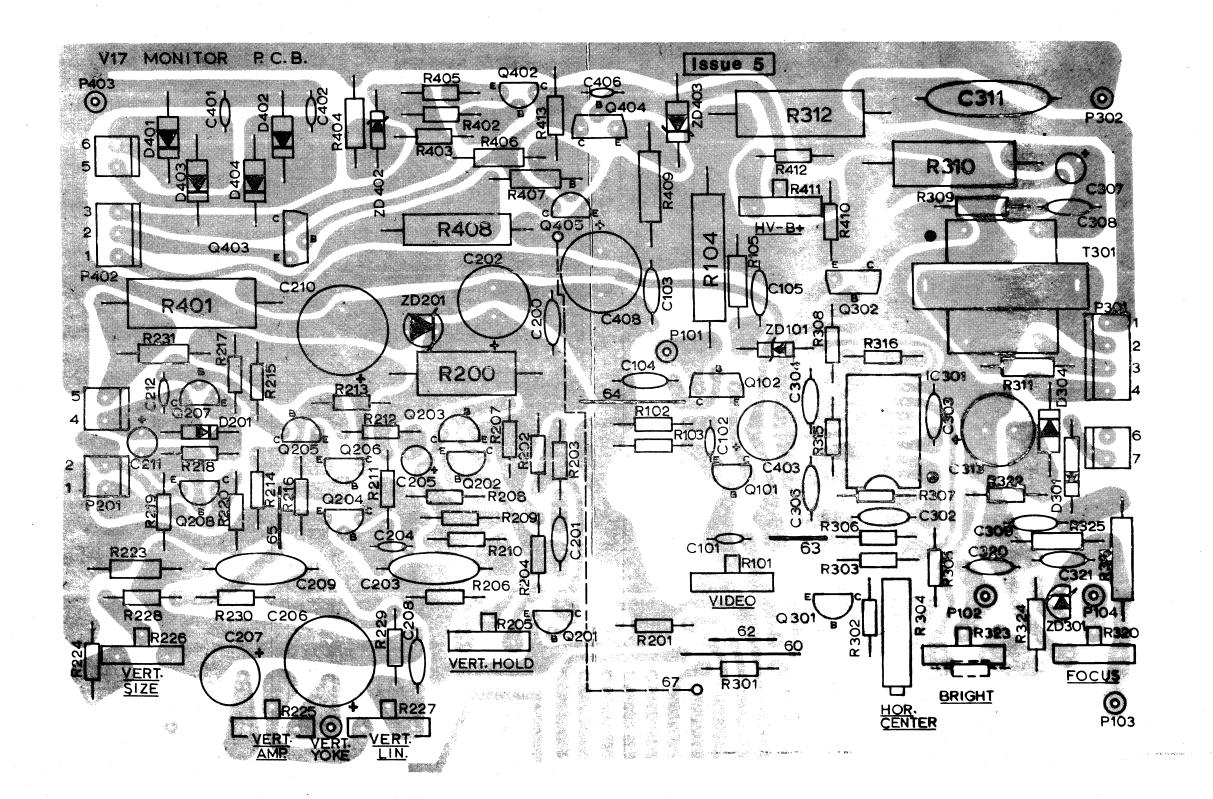

c) <u>Display Generation</u>: The CRT employs the standard 525 line-per -frame display (625 for Europe). The basic element of the display is the scan line which is generated by the horizontal oscillator, pulse shaper and output amplifier of the CRT's analogue circuitry. However, the freerunning frequency of the horizontal oscillator is synchronized by the horizontal synchronization amplifier which accepts the 8 microsecond H-DR pulse issued by the timing circuitry of the video board. The scan line has a period of 63.5 microseconds which includes the 12.7 microsecond flyback period for the next scan line.

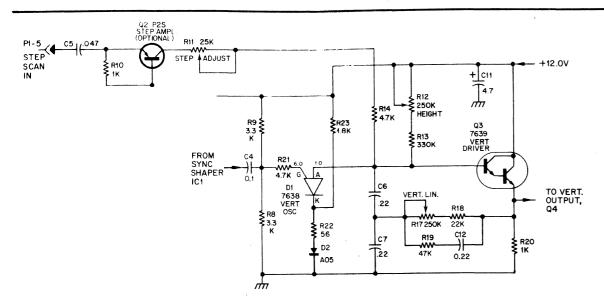

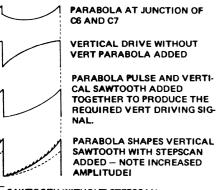

The vertical oscillator of the CRT circuitry is also free running and is synchronized in a similar manner as the horizontal oscillator. The video board generates a vertical drive signal (V-DR) which is applied to the vertical synchronization amplifier. This V-DR signal has the form of a pulse with a repetition rate of 60 per second (period of 16.66 milliseconds). The third signal involved in the display is the video pulse train and is responsible for displaying the dots on the CRT. This signal is fed directly to the cathode circuit of the CRT which modulates the electron beam.

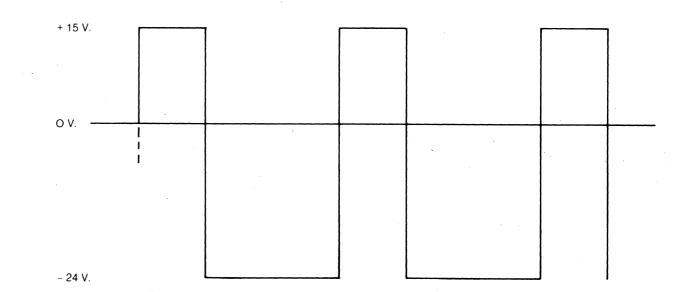

Since the AES-PLUS employs an interlace video frame composition system, the relative occurence of the vertical and horizontal drive pulses is critical. They interact in the following manner:

## Figure 5 Displays Signals

At the start of a video frame, the first vertical drive pulse appears simultaneously with a horizontal drive pulse and has a duration of 3 horizontal drive pulses. The second vertical drive pulse, however, starts halfway between two horizontal drive pulses and again has a duration of 3 horizontal drive pulses.

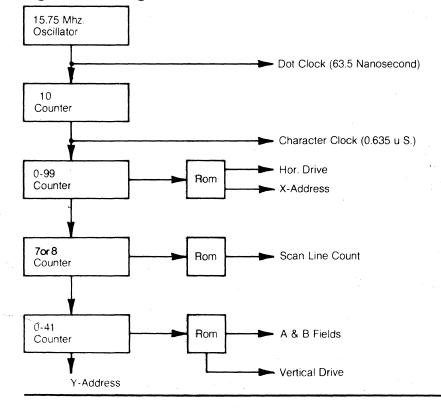

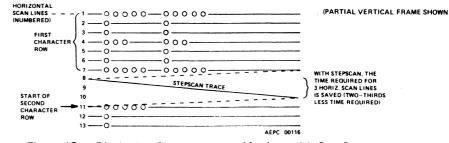

The simultaneous occurence of the vertical and horizontal drive pulses is called the "A" field whereas the trace where the vertical drive pulse starts midway between the three horizontal pulses is called the "B" field. Each field corresponds to 262.5 lines to form the 525 line standard frame (or 312.5 lines to form the 625 line european standard frame). Thus, interlacing provides high resolution but introduces flickering as the display is refreshed only 30 times per second. For this reason, P39 phosphor is employed to reduce this effect. d) <u>Timing Generation</u>: The timing clock signals are generated from a 15.75 Mhz (15.625 for Europe) oscillator whose output is fed to a series of frequency dividers generating all the different frequencies used in the system. For example, it provides horizontal and vertical sync pulses, video pulses, block address signals and so forth (see figure 6).

Timing in video is generated in different frequencies affecting specific occurences for display purposes. The character clock for instance is derived from a  $\div$  10 counter since a character is 10 dots wide. The number of block widths within a scan line constitutes the next frequency. By determining the number of characters in one scan line, the generation point of the horizontal drive pulse becomes evident. Therefore to provide an horizontal pulse of one scan period equivalent to 63.5 microseconds, a  $\div$  100 counter becomes necessary.

## Figure 6 Timing Generator

This counter is organized in such a way that count 0 corresponds to the left-most character position, count 1 corresponds to the second position and so forth. Consequently, the counter is used to address the memory as each character location corresponds to an X memory location. Since the video display consists of 80 characters, counts 80 to 99 are used for horizontal blanking.

In the vertical mode, a counter is also used to determine the height of the character. Thus, this counter is set to 7 or 8 scan lines, depending on whether the A or B fields are concerned or whether it will count an odd or even character line. In any case, the counter generates an output pulse each time a vertical character block has been completed.

The last required signal relates to the number of vertical character slots. In a similar manner to the horizontal system, the output pulse issued by the vertical line counter is applied to a block counter which assigns the number of blocks in the vertical field.

e) <u>ROM Character Generator</u>: The video signal will either turn on or off the electron beam of the CRT, allowing the display of a dot on the screen. A character on the video screen is simply a mosaic of dots whose outlines are determined by the ROM Character Generator, a single LSI integrated circuit. Within this chip, every character is stored on a line-by-line basis and is retrieved by a specific character addressing scheme. Thus, to generate a character on the screen, the video memory is addressed by the X and Y coordinate of the specific allocated position. The resulting character from the video memory is combined with the vertical scan line count to provide an address pointer to one of the lines of the character. The specific address of that line is fed to the character generator which retrieves the required dot pattern. This dot pattern is then fed to a shift register and, being clocked by the dot frequency, becomes the serial video signal applied to the CRT monitor.

- f) <u>Microprocessor to Video Subsystem Interface</u>: All the data to and from the Video Subsystem is channelled via the data buss. Data to be stored in the video memory is first assigned a specific address or location by the X and Y counters. The microprocessor then places a character on the data buss and sends a WRITE command to the video memory to place the character in the proper location. Special logic ensures that all Write functions are performed at the cursor position.

- g) <u>The Keyboard</u>: The keyboard consists of standard typewriter characters, a fifteen key control function cluster located at the right and five option keys located at the left. Each time a character key is depressed, a signal is sent to notify the microprocessor and the keyboard unloads an ASCII coded character onto the data buss via a buffer.

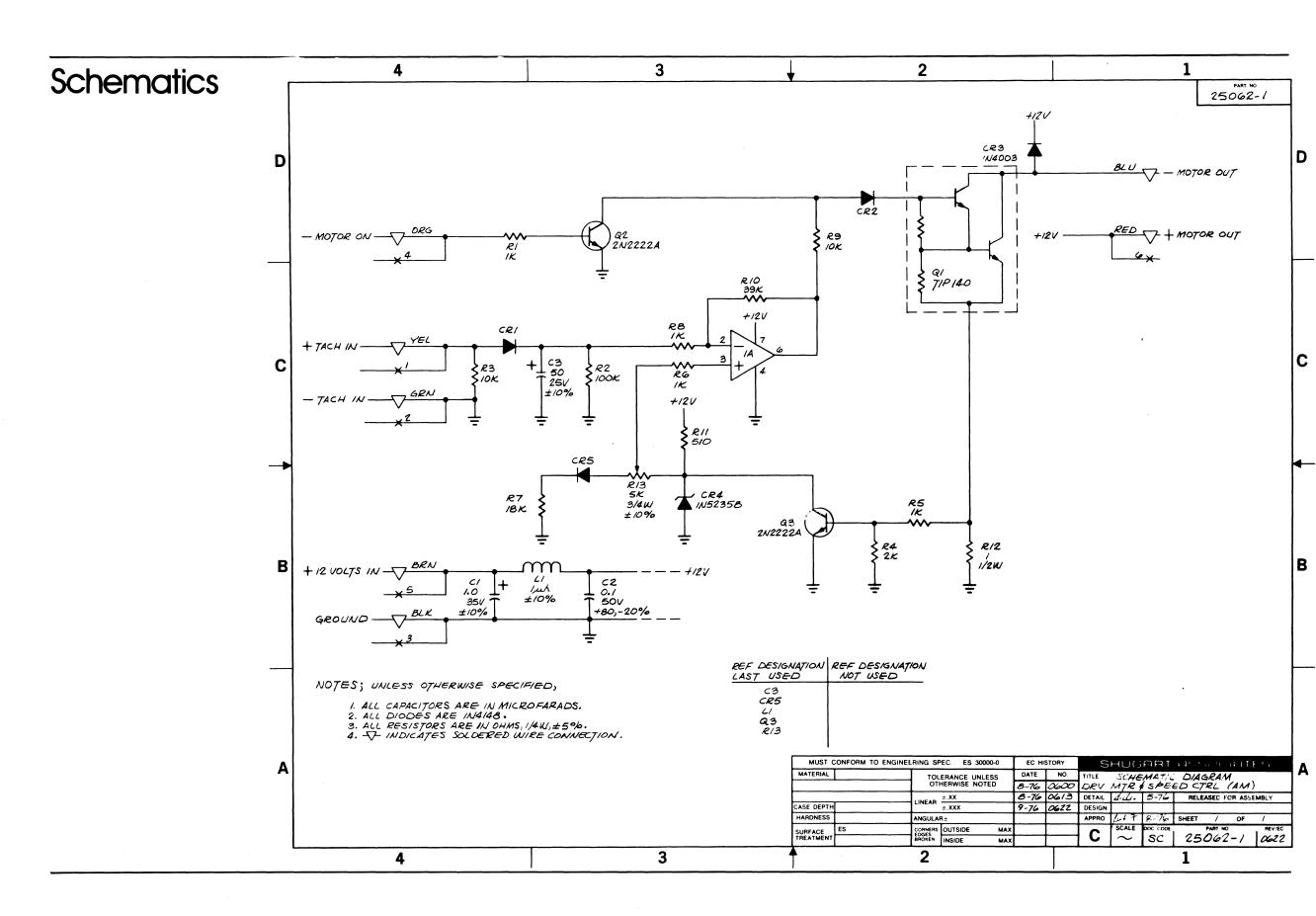

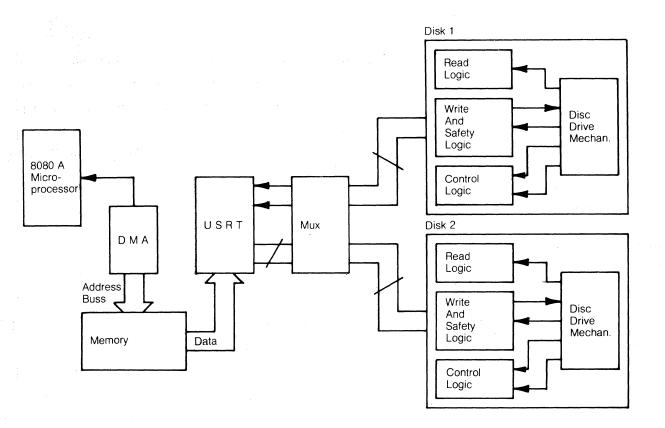

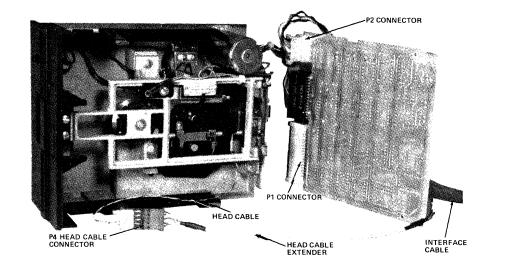

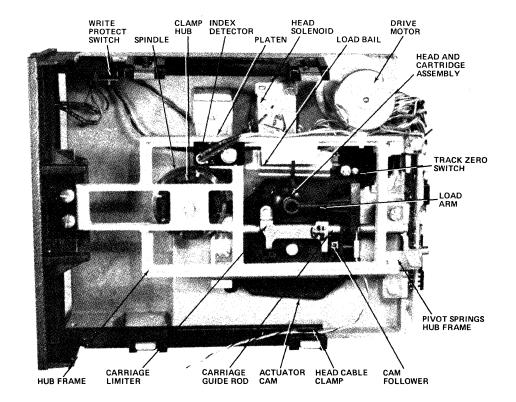

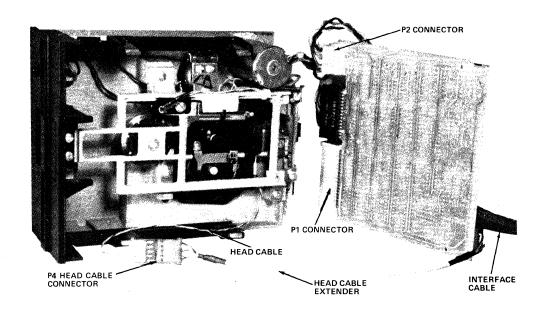

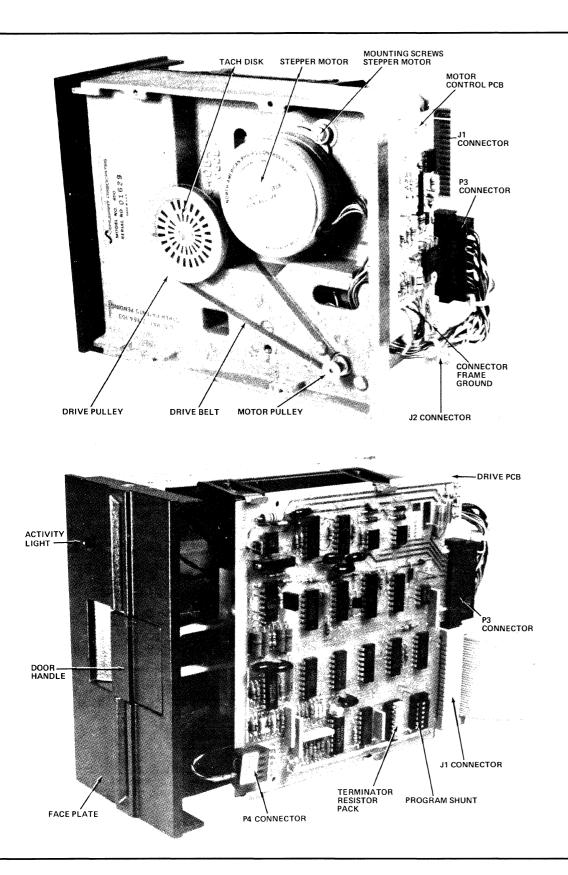

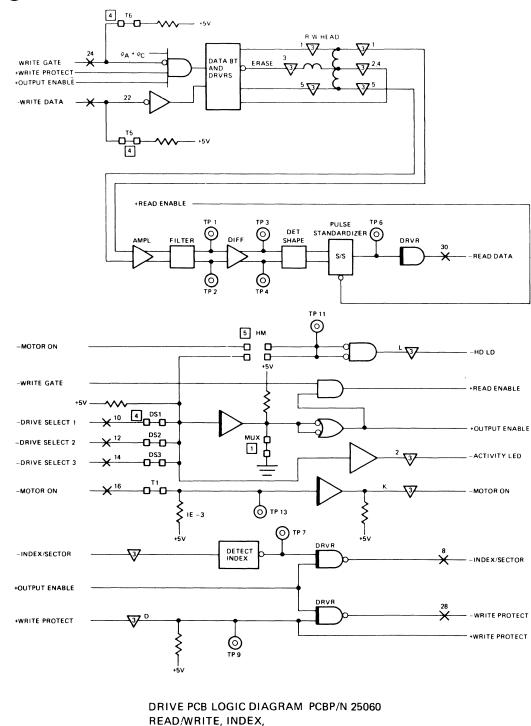

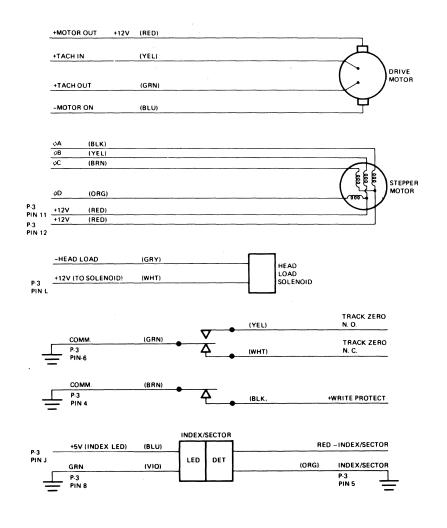

#### .4 THE DISC SUBSYSTEM

In the AES-PLUS Text Editor system, the Disc Subsystem (FIG.7) may either consist of a dual or a single floppy disc storage drive and one disc interface. The main functions of the storage drive are:

- a) To store text data magnetically for a later recall and, in the case of dual disc drives, the duplication of pages, texts or even entire disc files becomes possible. The dual system also incorporates a disc recovery function. This is accomplished by transferring all the good pages of the main disc to the secondary disc and systematically building a new directory with arbitrary page names.

- b) To buffer data to be printed so as to enable the overlapping of printing and editing.

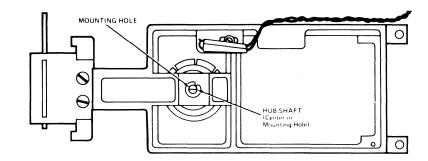

A single Shugart SA400 Disc Storage drive provides storage for 109.4 kilobytes of data with a data transfer rate of 125,000 bits/second. The disc drive consists of a drive mechanism and a read/write head positioned by a mechanism activated by electronics. The magnetic disc is divided into 35 tracks at 3125 bytes per track, 16 sectors, one index, 16 sector holes and one file protect notch.

The smallest section of a disc recognized by the microprocessor is one track sector or 1/16 of a track, with a storing capacity of 193 bytes, and can be addressed randomly. The data recording method is a frequency modulation technique.

One SA400 mini-diskette is capable of storing up to 69 pages of text (however if all pages occupy a full 8K of memory, the minidiskette will overflow).

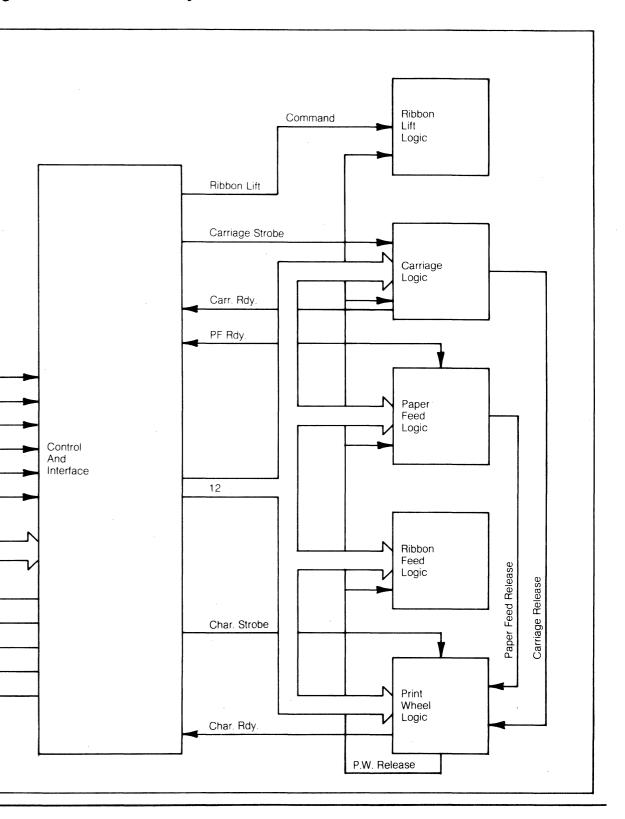

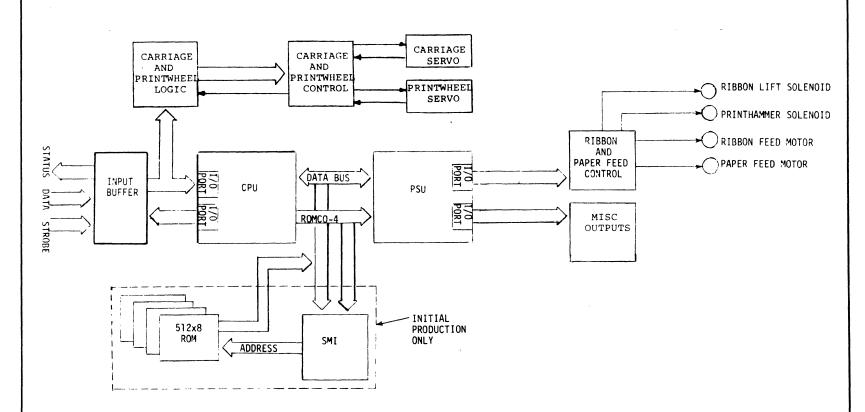

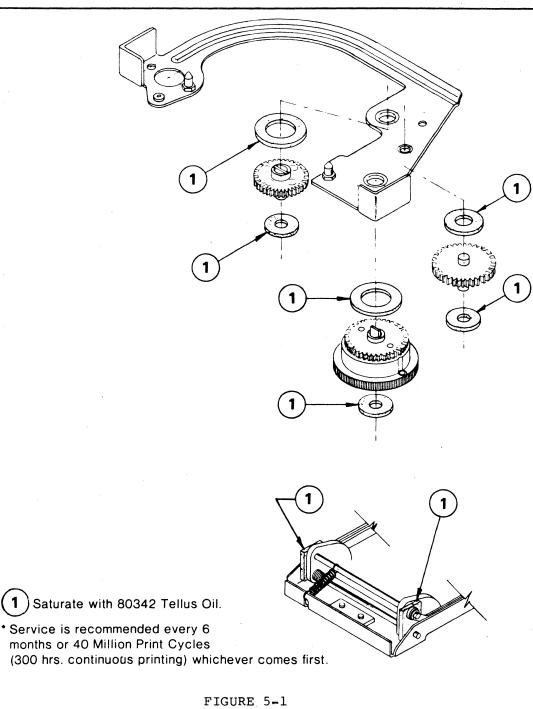

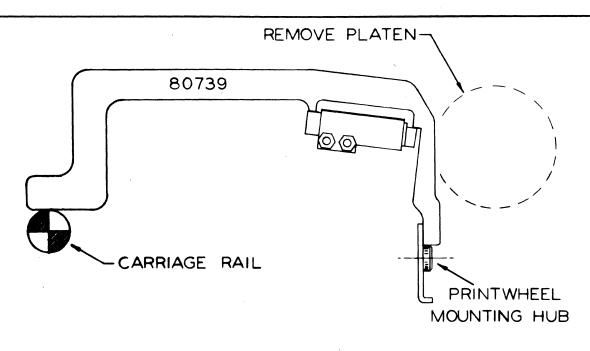

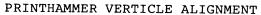

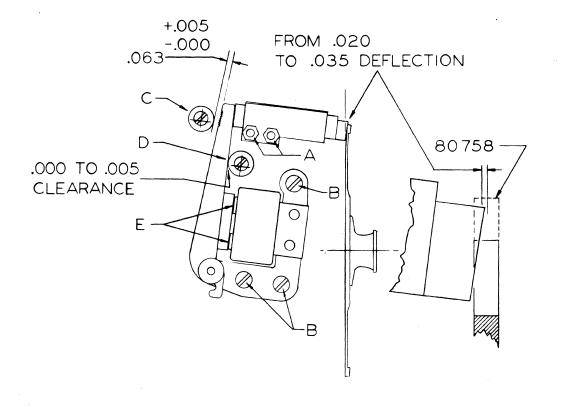

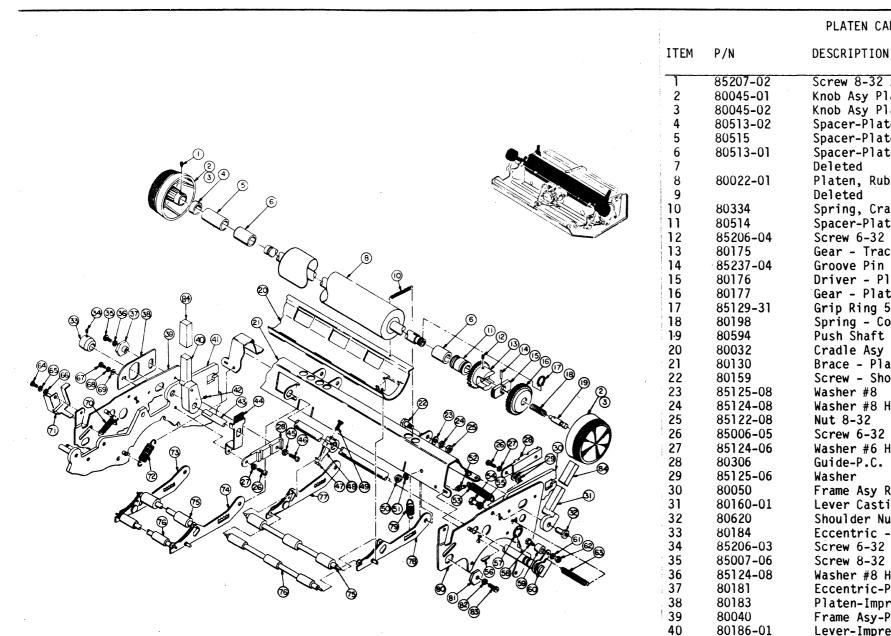

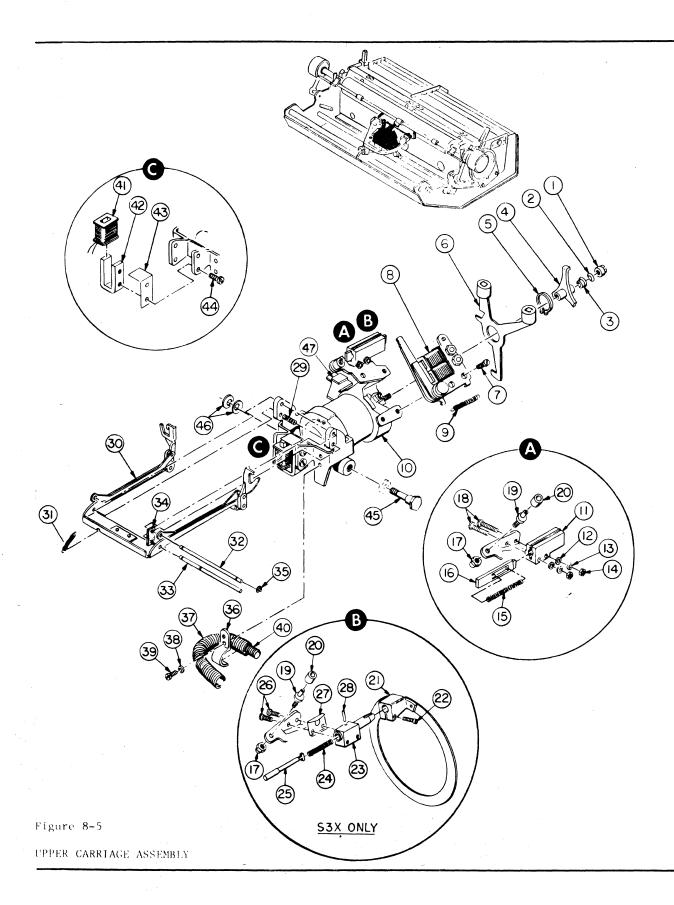

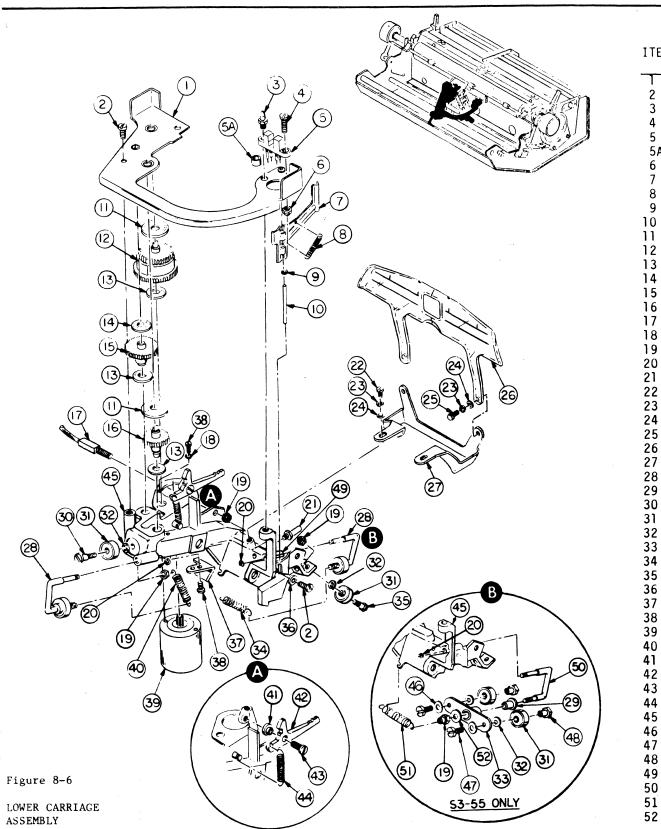

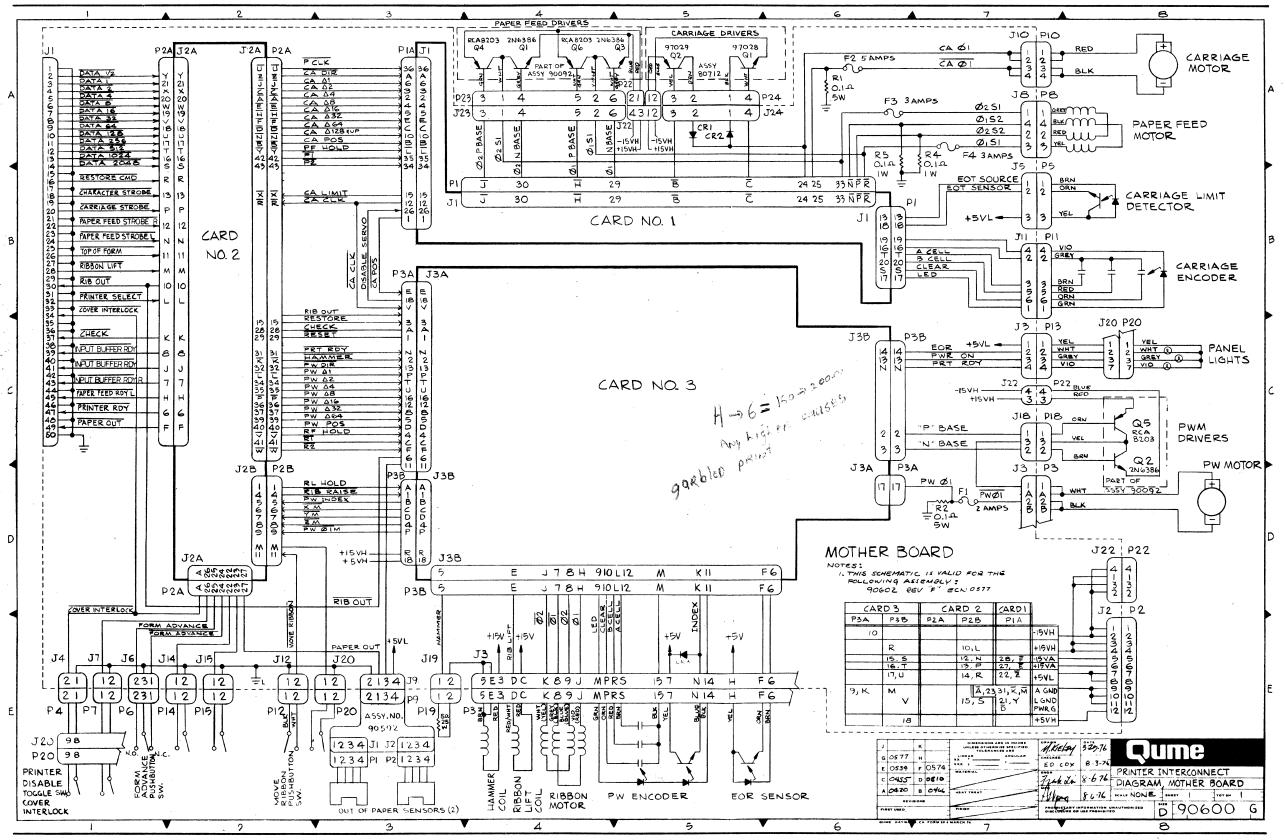

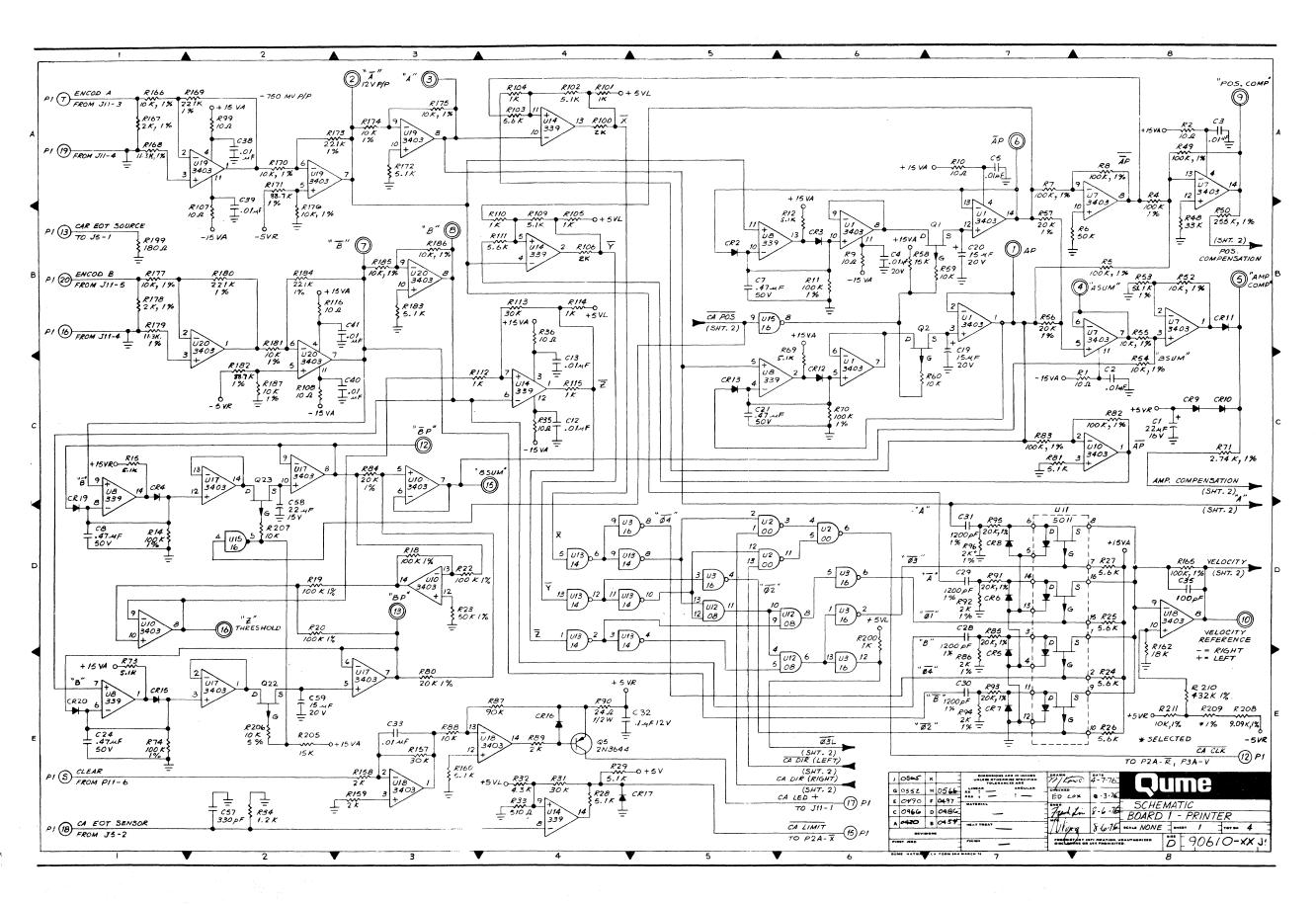

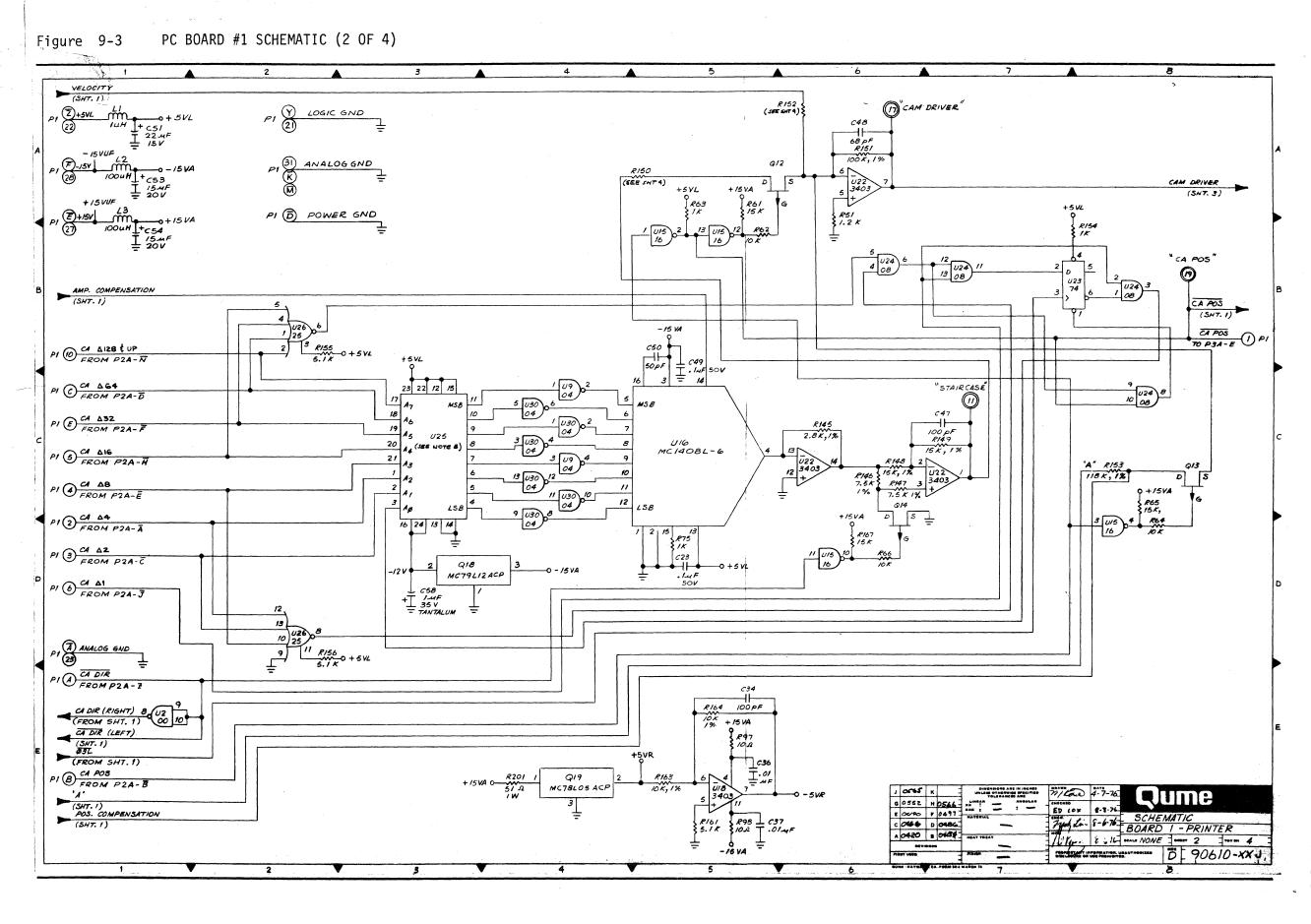

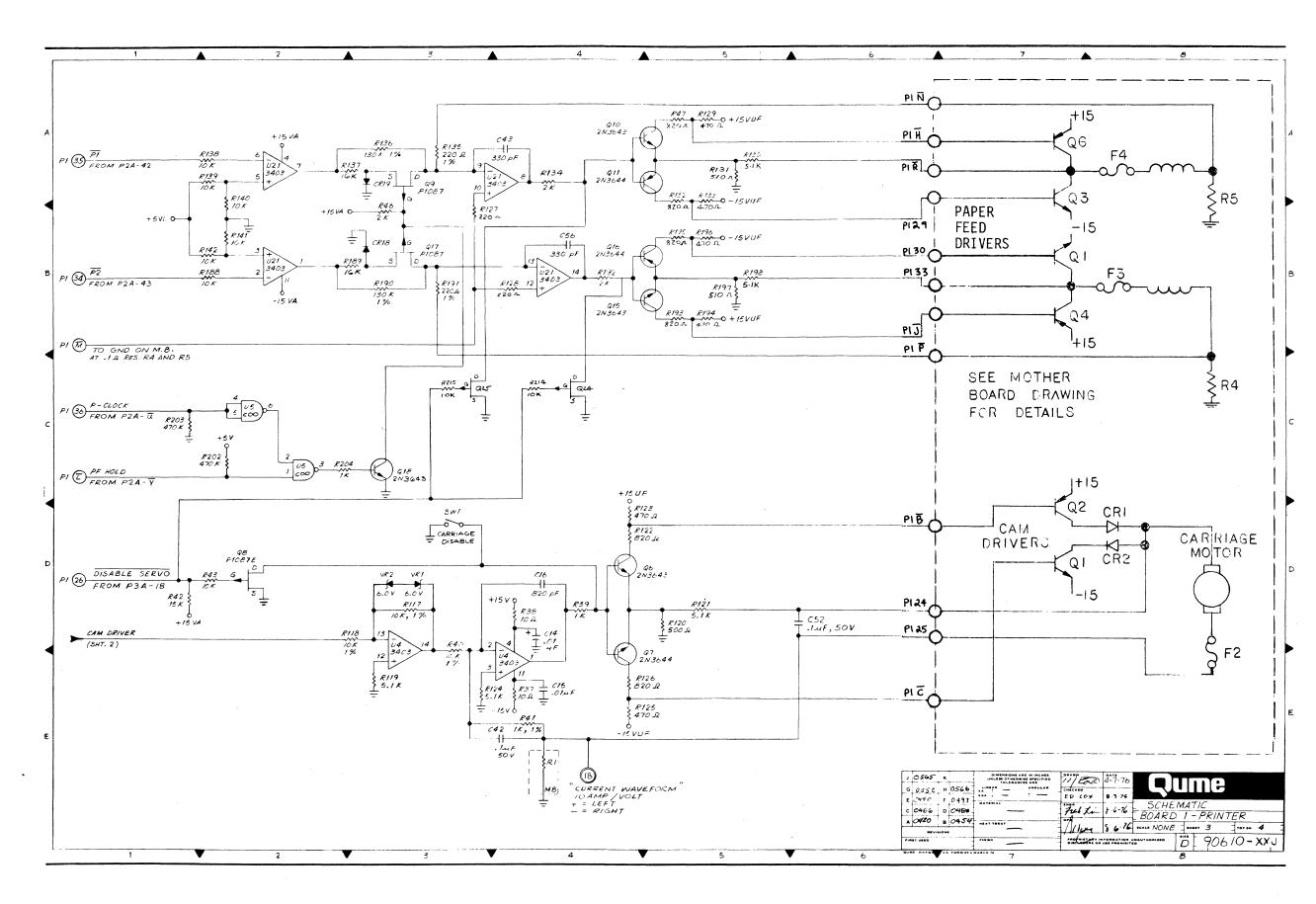

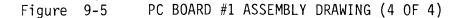

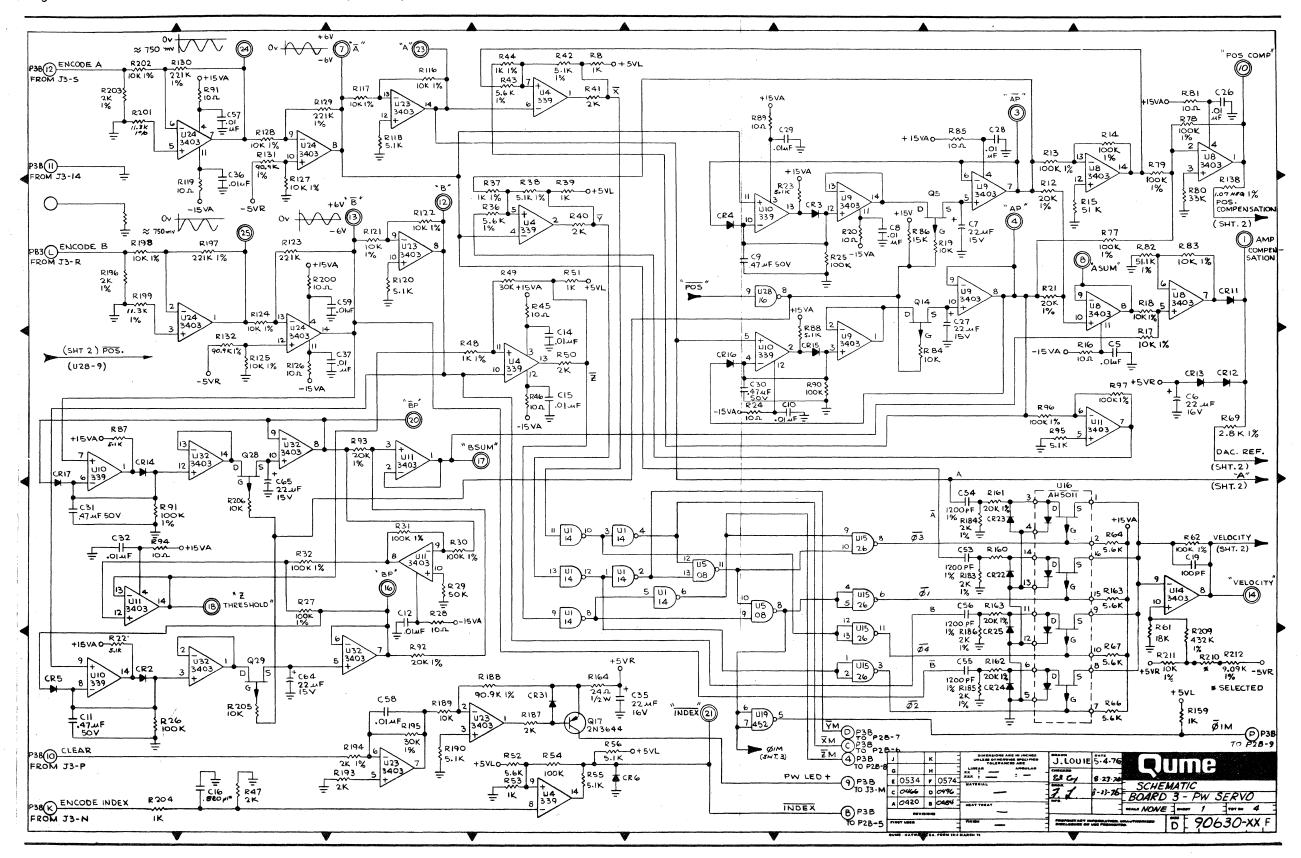

#### .5 THE PRINTER SUBSYSTEM

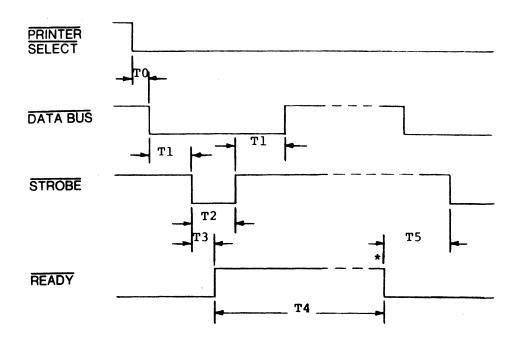

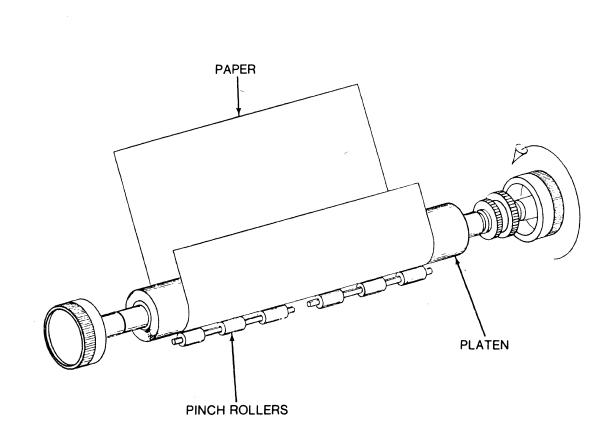

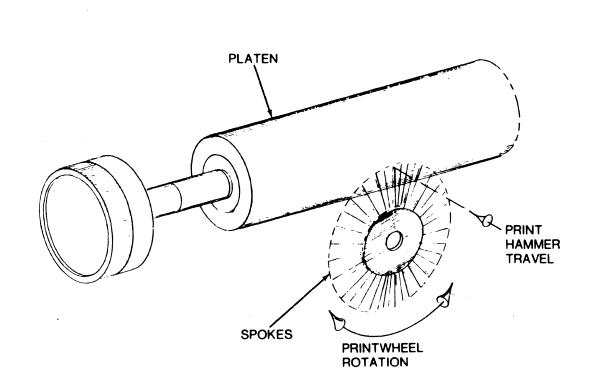

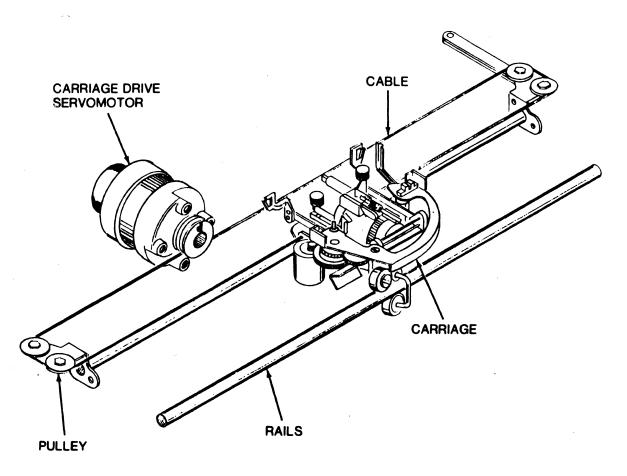

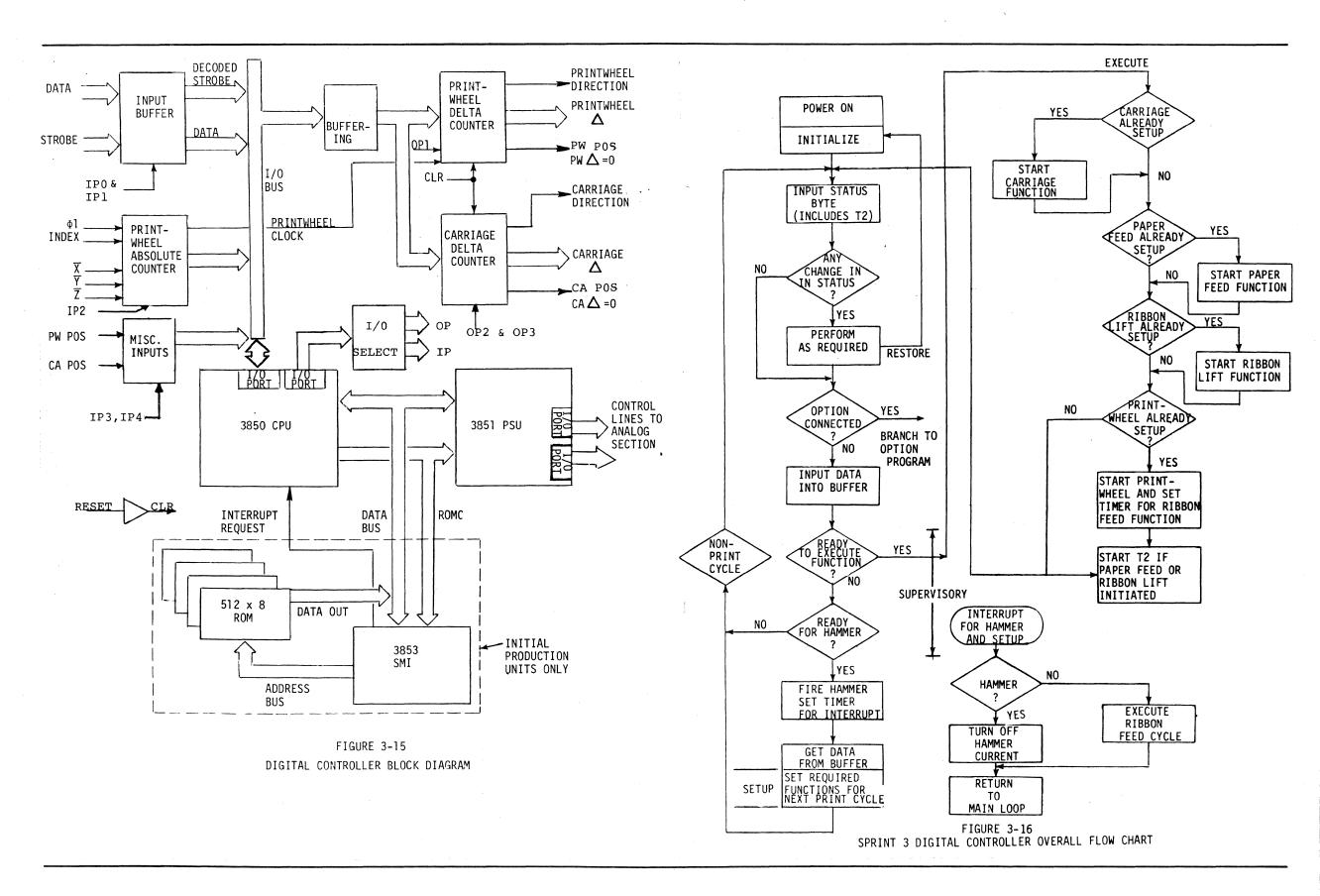

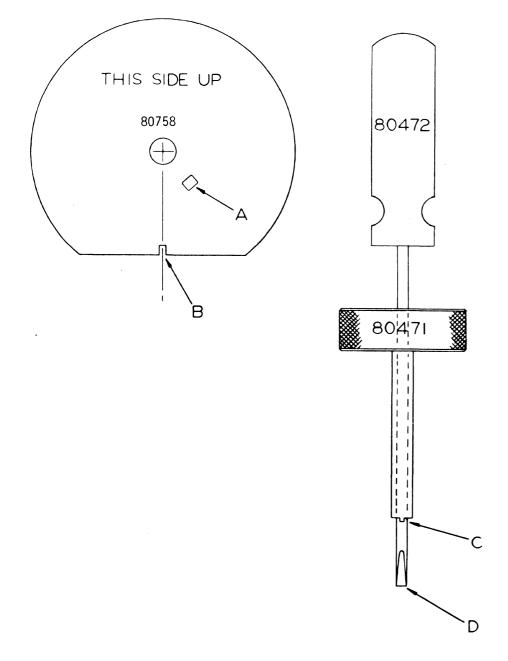

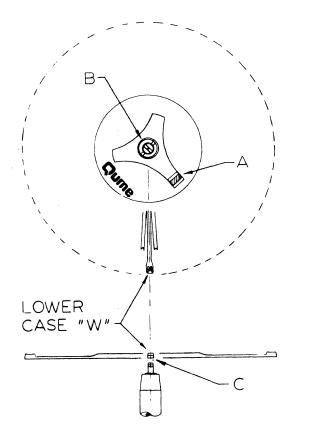

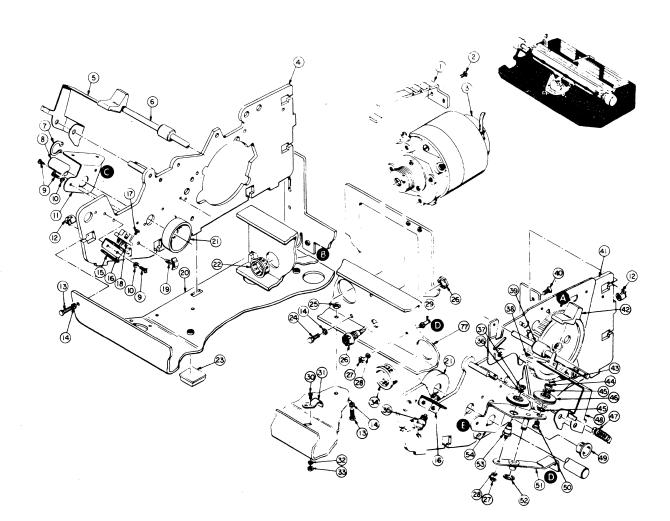

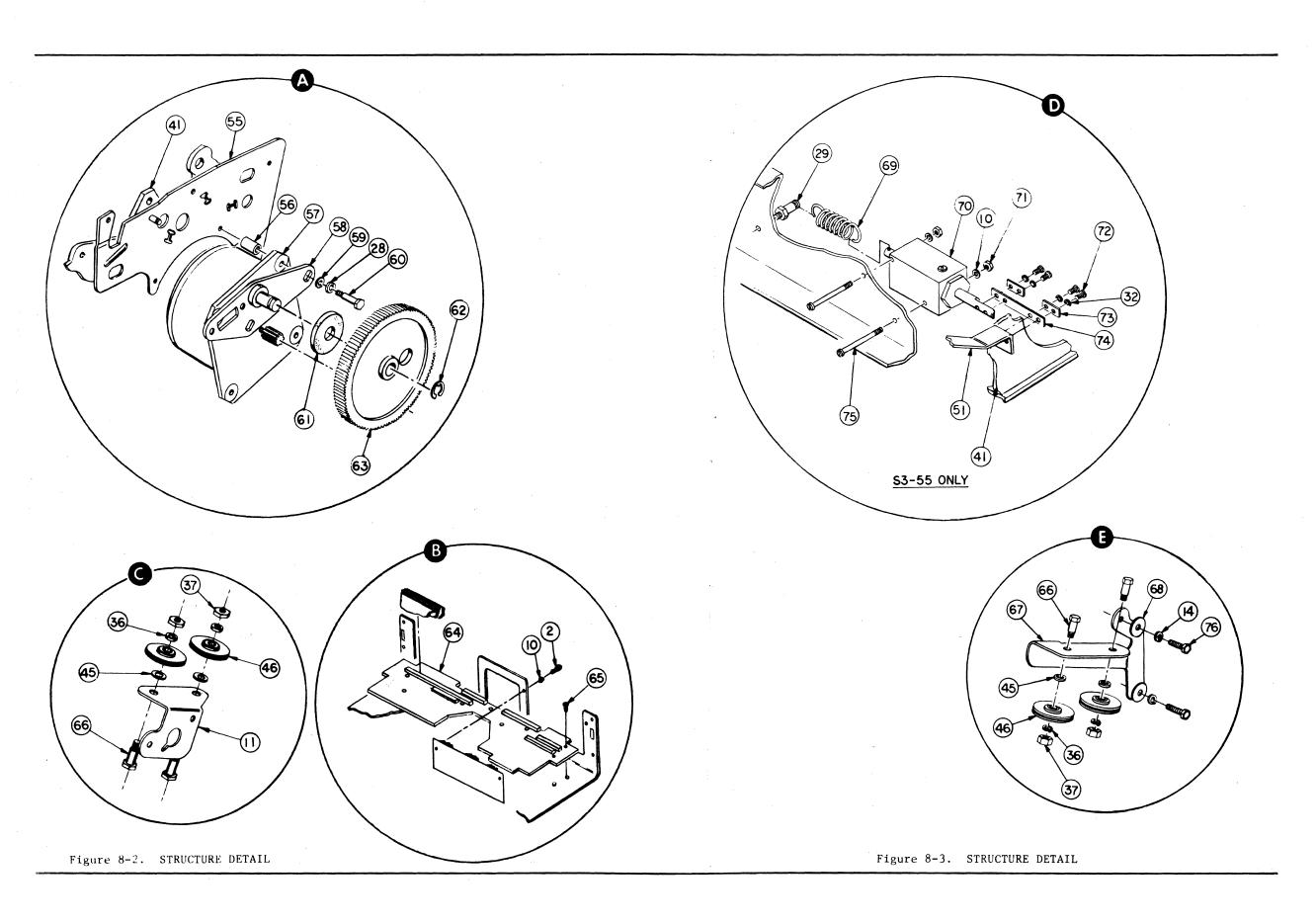

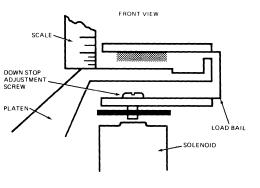

The Printer Subsystem (FIG.8) consists of two main units, the printer and the printer interface. It is utilized as an output device and allows the contents of the video page or the disc to be printed. The printer operates as a closed loop with the Microprocessor, accepting data only when certain flags allow it. <u>Printer Features</u>: The high speed character printer is designed to interface only with automatic data systems. This printer can achieve a print rate of 45 characters per second during normal text printouts.

The most significant feature of this device is its mechanical simplicity since most mechanical functions have been replaced by electronics and the remnant inertia of the mechanism has been minimized through the use of light weight components.

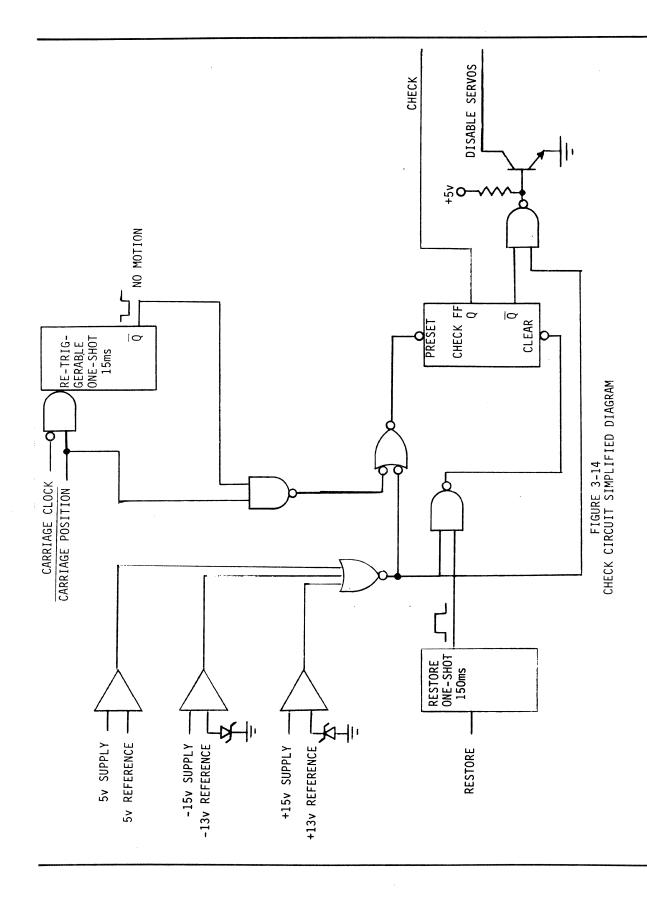

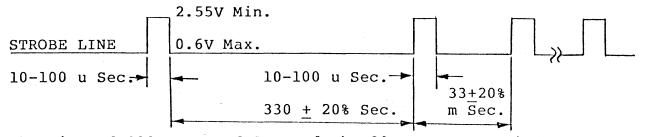

<u>Operation of the Printer</u>: The Printer accepts signals from the Microprocessor and acknowledges by issuing feedback status signals. When the printer is being addressed, the microprocessor issues the <u>Printer Select</u> strobe and the printer responds immediately by the <u>Printer Ready</u> strobe. Any malfunction of the printer at this time will be indicated by the CHECK strobe which disables the printer.

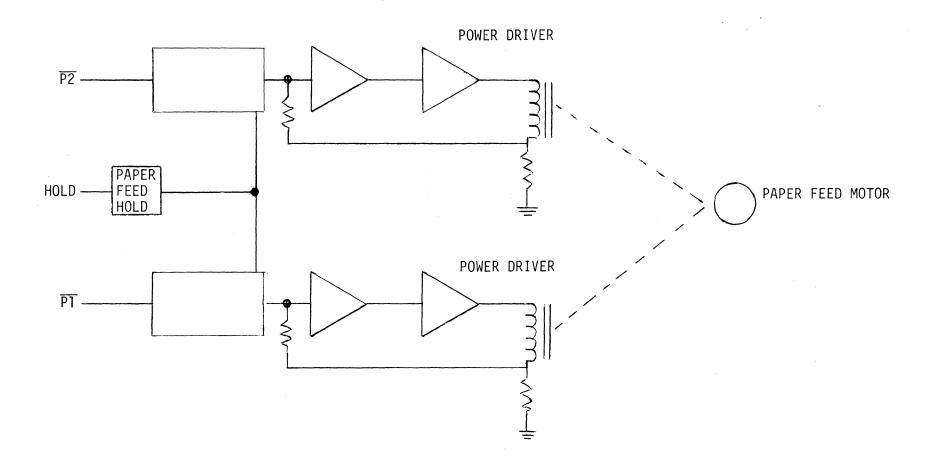

The Paper Feed function is controlled by the P.F.RDY (paper feed ready) and the P.F.STROBE (paper feed strobe) command lines. When the P.F.RDY is set HI, the printer's paper feed logic is cleared and can therefore accept a paper feed command. The paper feed command is protected by an automatic interlock which prevents paper motion when a character print cycle is in progress.

The Carriage Function is also controlled by two command lines, the CAR.STROBE and CAR.RDY. When the CAR.RDY status line is set HI, the printer carriage logic is cleared and can therefore accept a carriage strobe. The Character Print function follows the same rule as above. Two command lines are involved, the CHAR.STROBE and the CHAR.RDY. The character print logic is cleared when the CHAR.RDY line is set I, and can therefore accept the CHAR.STROBE.

Initialization of the printer takes place automatically following the application of power and thereafter when the printer's control logic issues a RESTORE command. A CHECK condition may also be cleared by the application of the RESTORE signal.

NOTE: For more detailed information on the printer, refer to the Interface board (Chapter 2, Sect. 2) or the Printer Maintenance Manual (Chapter 5).

IOR

IOW

Data

ſ

8080 A

Microprocessor

Printer Sel. Restore

Char. Strobe

Paper Feed St.

Ribbon Lift

Carriage St.

Char. Rdy. Carriage Rdy.

Paper Feed Rdy.

Printer Rdy.

Check

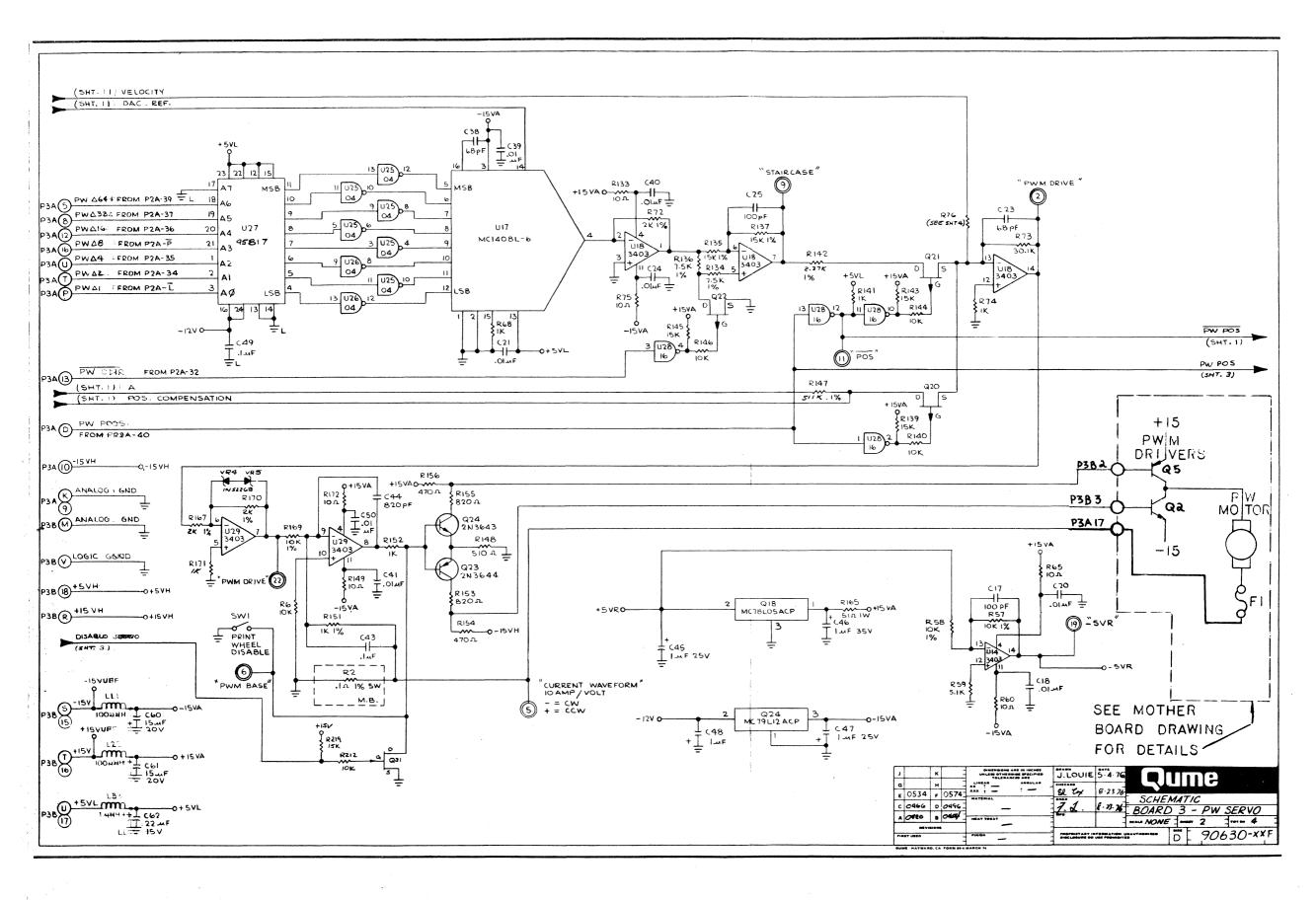

Qume

Interface

## Figure 8 The Printer Subsystem

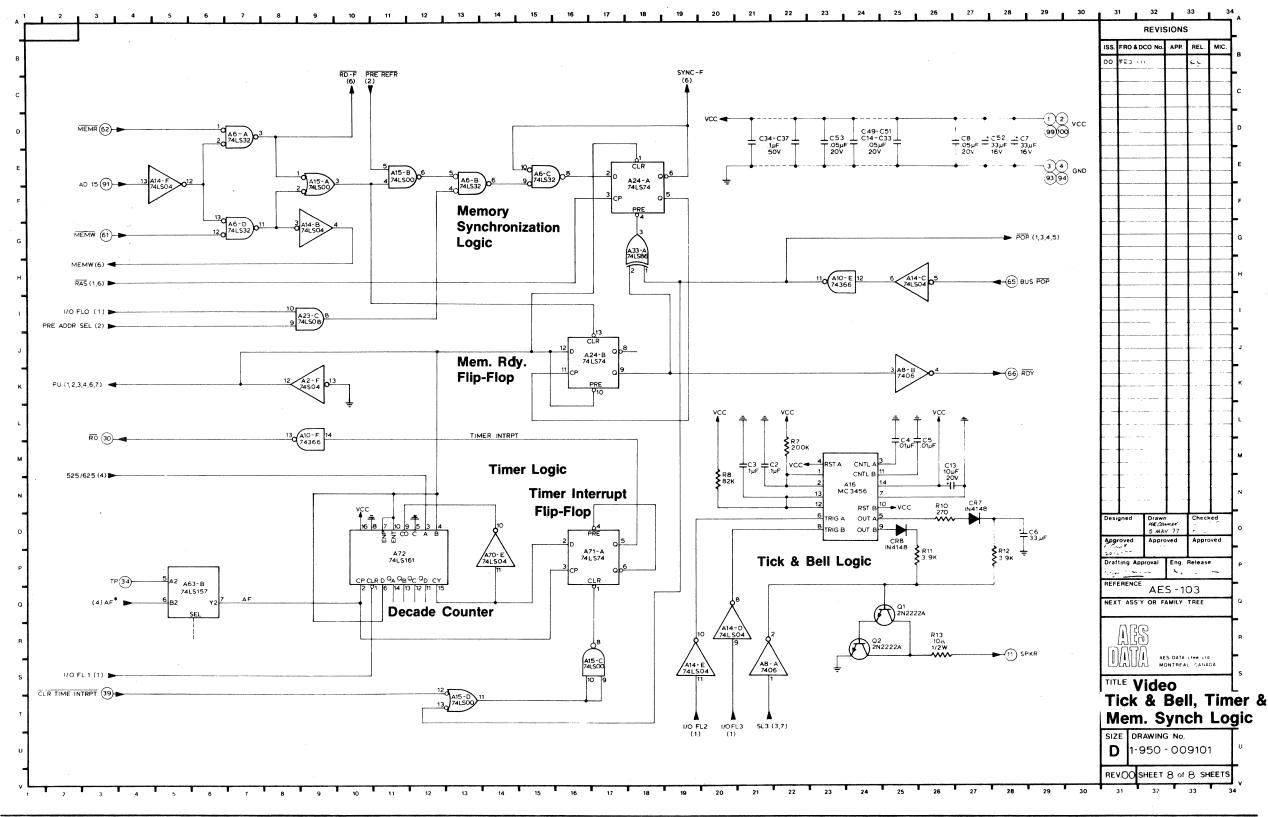

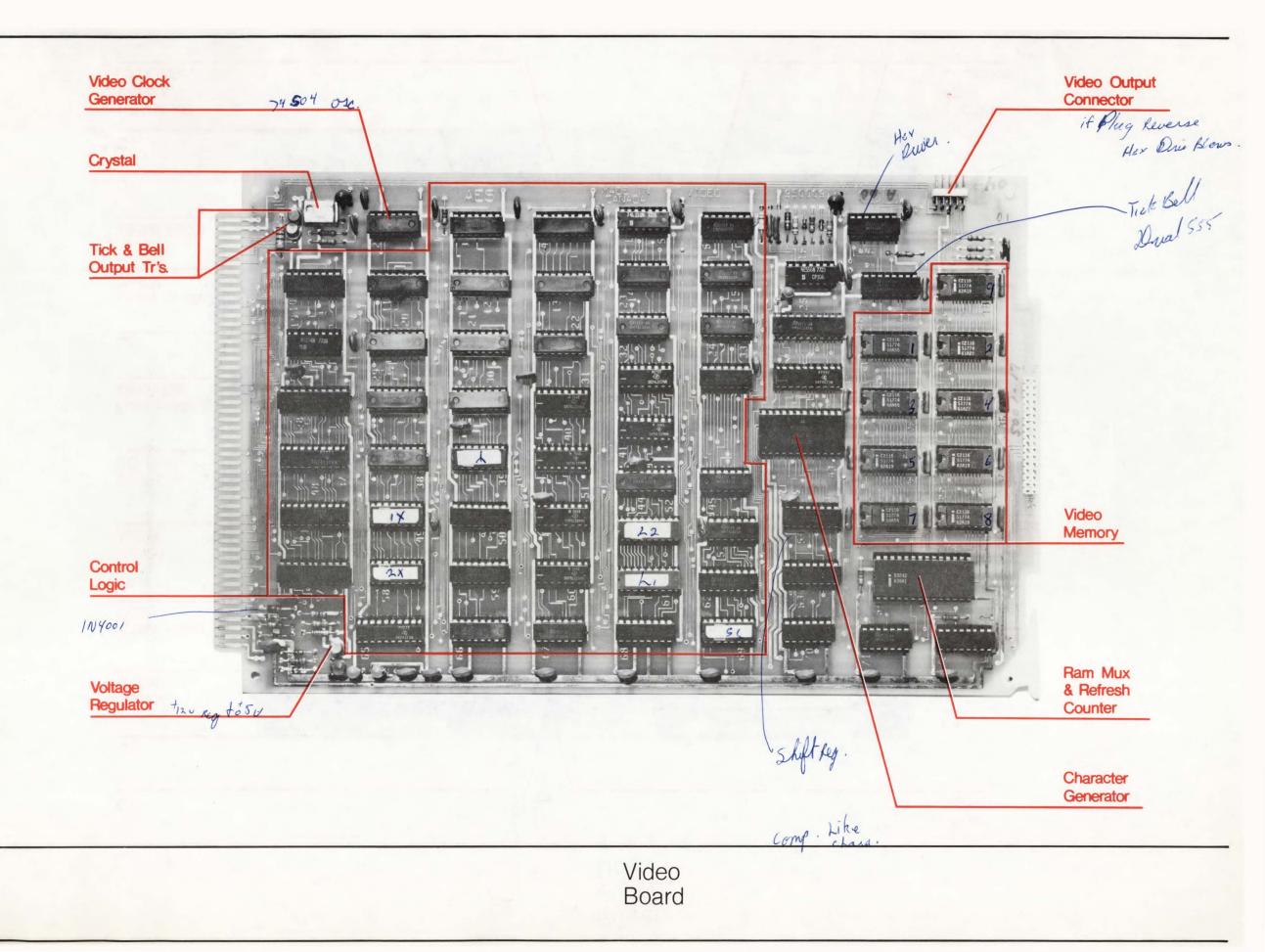

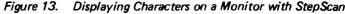

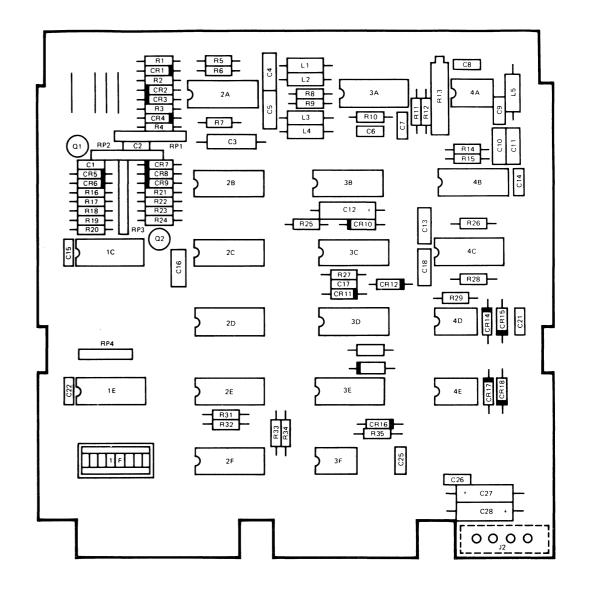

## VIDEO BOARD (1-950-009101-00)

## 1. INTRODUCTION

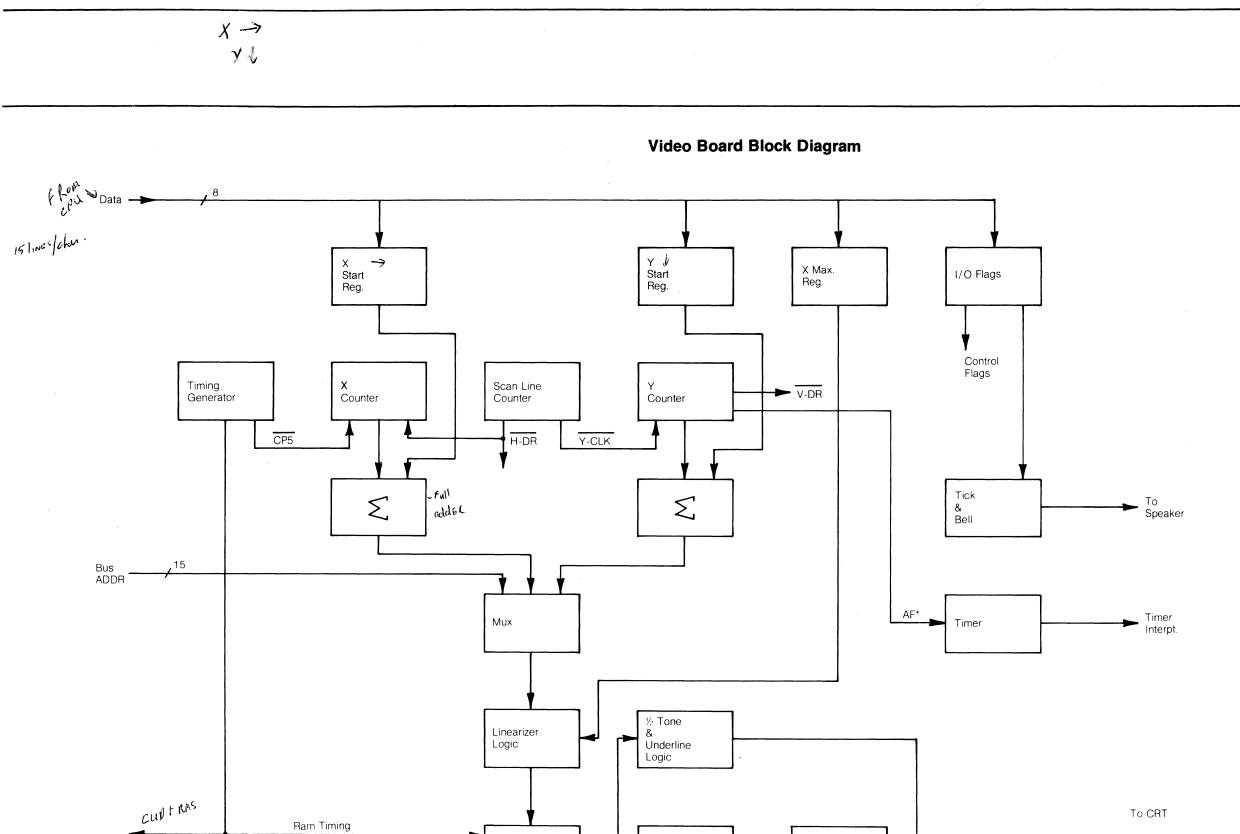

The Video Board comprises all the logic circuits to perform the following functions:

- Timing for the instruction memory (RAM).

- Storage of a page of text in a memory.

- Generate a video signal for display purposes.

- Generate a real time clock interrupt signal.

- Generate TICK and BELL sounds.

### 2. CONFIGURATION

The video board is divided into 9 subgroups:

- The X counter.

- The scan line counter.

- The Y counter.

- The address linearizer

- The video memory and video output.

- The memory synchronization circuit.

- The I/O flag register

- The TICK & BELL logic.

- The timer interrupt

## 3. FUNCTIONAL DESCRIPTION

## 3.1 The X-Counter

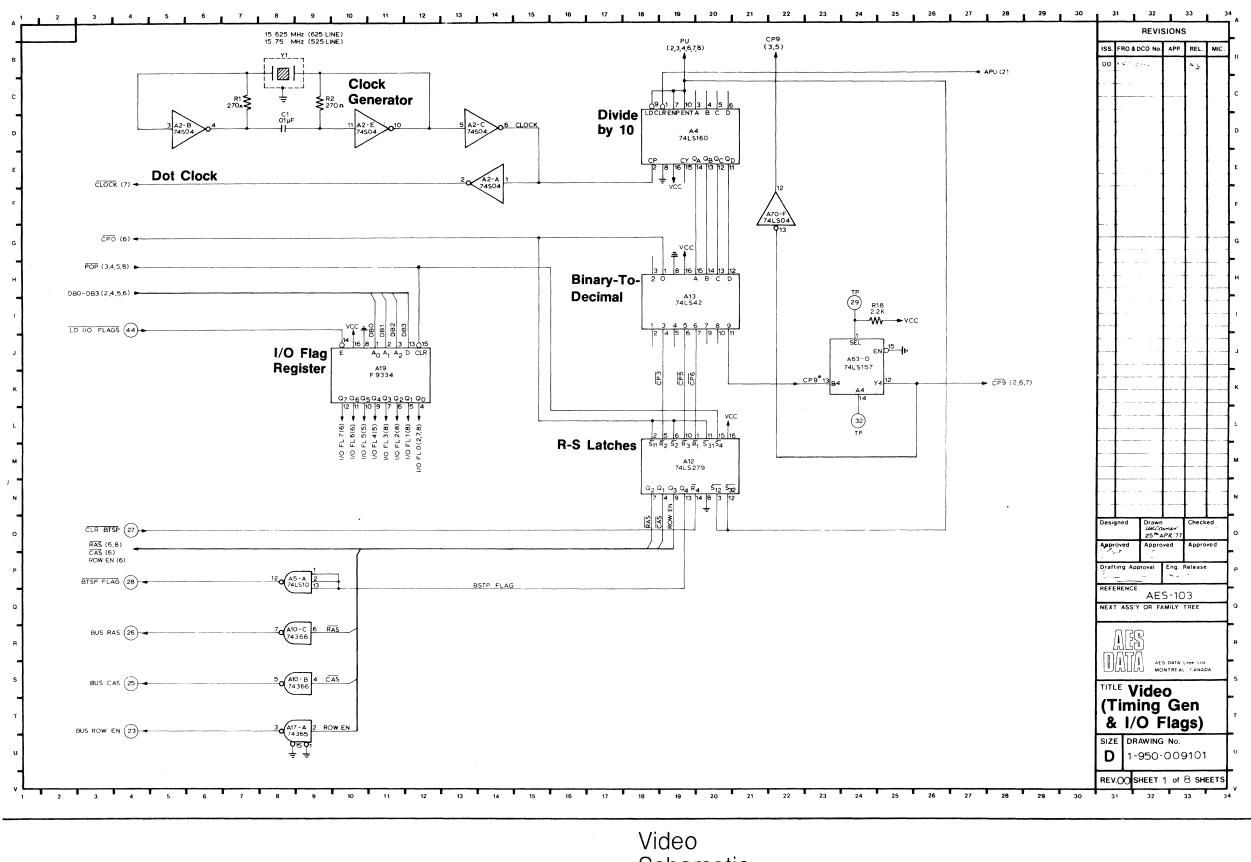

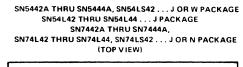

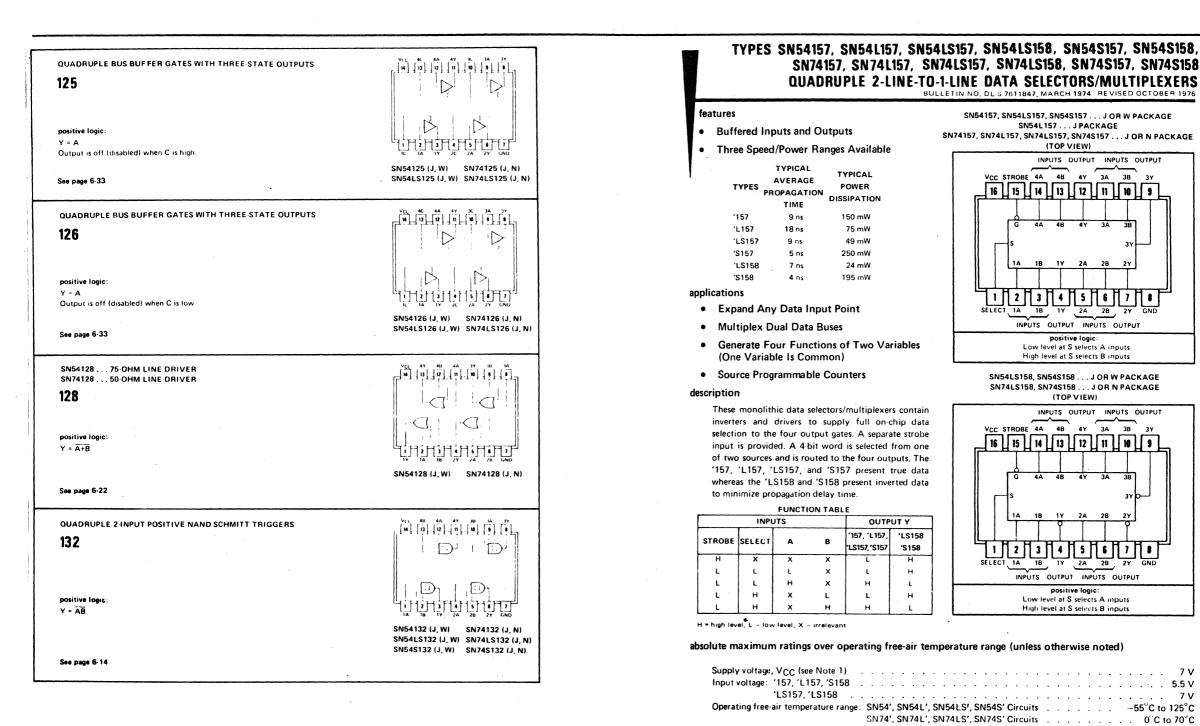

- a) <u>Clock Generator</u>: The clock generator consists of inverters A2-B, A2-E and a 15.75 MHz crystal (16.625 MHz for PAL). The output of the generator is the CLOCK signal, which is inverted by A2-A to form the dot clock with a period of 63.5 nanoseconds and is also applied to counter A4(74160) from which successive division of the clock signal is initiated. The binary outputof A4 is applied to Binary-to-Decimal converter A13(74LS42) from which clock pulses CPØ, CP3, CP5, CP6 and CP9 are produced. Clock pulse CP9 occurs every 635 nanoseconds, corresponding to the end of a character interval. Clock pulses CPØ, CP3, CP5 and CP6 are then applied to R-S latches Al2 which generates three major video and CPU memory timing signals, RAS\*, CAS\* and ROW EN\*.

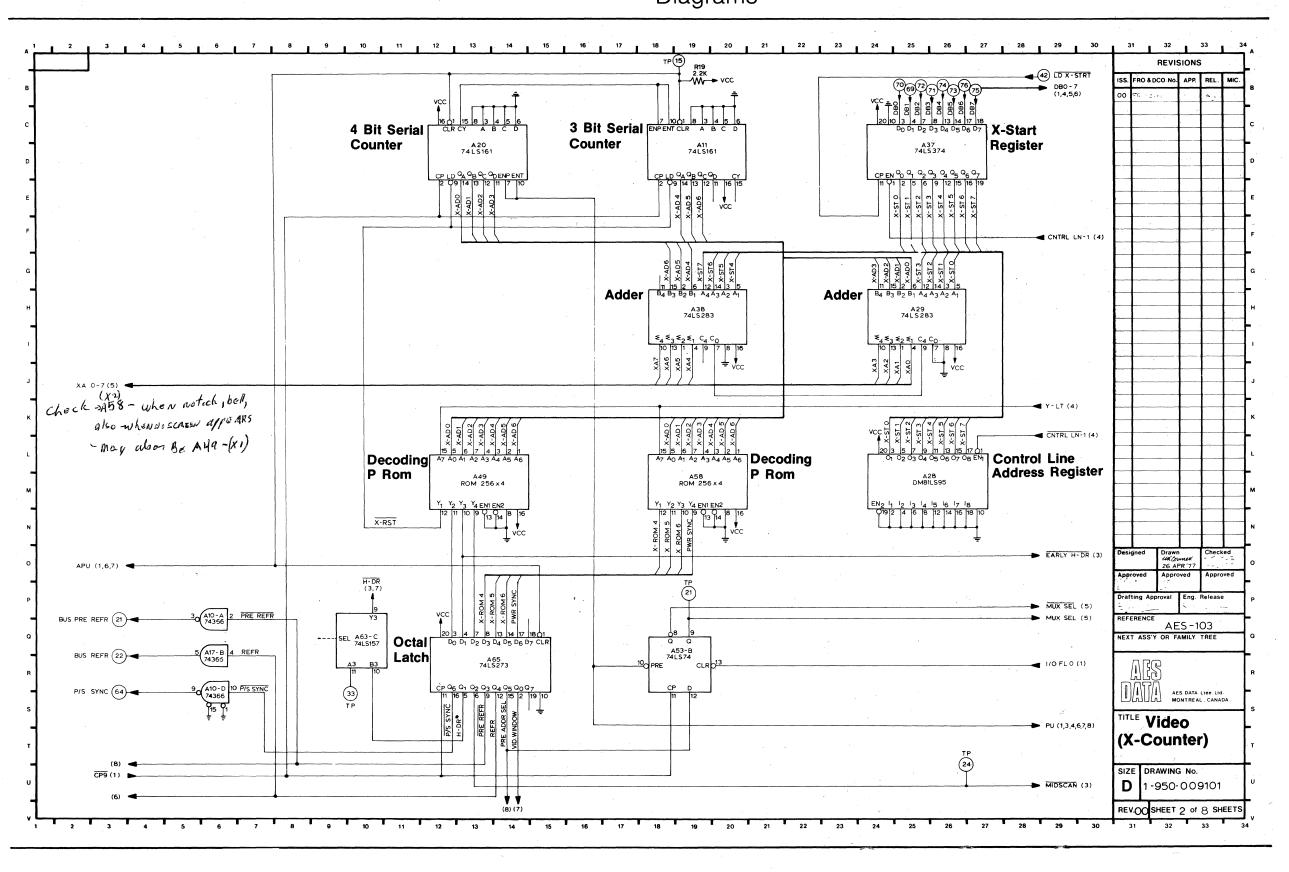

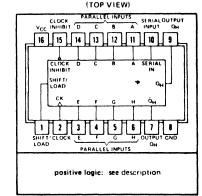

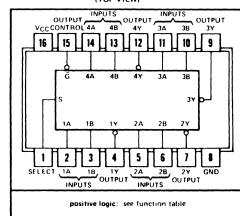

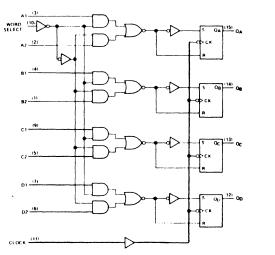

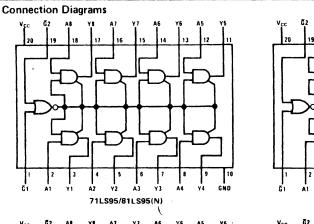

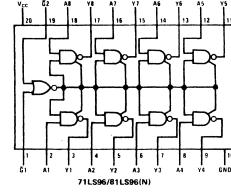

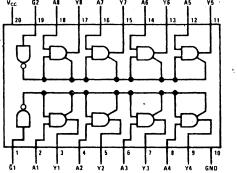

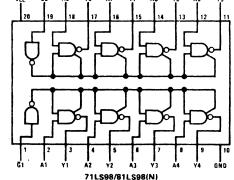

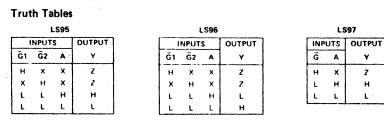

- b) <u>X-Counter</u>: The X-counter generates the X address to the display (the position of a character on a line). This counter consists of devices A20(74LS161), All(74LS161) A49, A58(6301) A65, A38, A28, A37 and A53-B.

The input circuit of the X-counter consists of A20 and All, forming a 7-bit serial counter, incremented by clock signal CP9. The serial counter counts from 0 to 99, giving the amount of X addresses necessary to fill the video screen. To determine the starting address of the video display, since the video page has a maximum capacity of 256 characters per line, an offset value is loaded into the X-start register from the CPU and this value is added to the X-counter value in devices A38 and A29 (4-bit full adders).

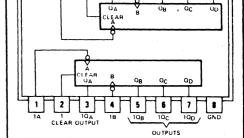

Video Board

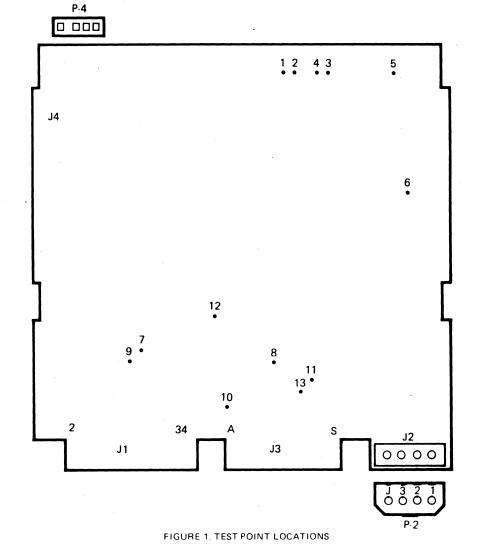

In displaying the control line, since it is never scrolled from the video display, a permanent location (address ØØØØØØØ) has been assigned for it in the memory. When a video frame is displayed, buffer A28 (DM51LS95) is enabled by the CNTRL LN-1 strobe for the first character row so as to force the offset to be zero; this scheme establishes a stationary video display for the control line. The X-Start register is enabled by the CNTRL LN-1 strobe, creating a shift in the display from addresses ØØØØØØØ of the control line to the address of the first line of text to be displayed. In figure 1, the scheme is clearly visualized.

## Figure 1 Control & Tab Line Location

The tab line is, however, scrollable to the left and the right of the video page. It occupies line 1 and scrolls from  $X = \emptyset$  to X MAX in an 80 character segment.

c) <u>Control Strobes</u>: The seven bits of the X-counter are also applied to two ROM's (MMI 6301-1). These ROM's track the character count to generate 8 control strobes, which are: X-RST, XROM1, 3, 4, 5 and 6, EARLY HOR.DR and Power Supply Synch. These strobes are latched through A65(74LS73) to eliminate skewing an "glitches".

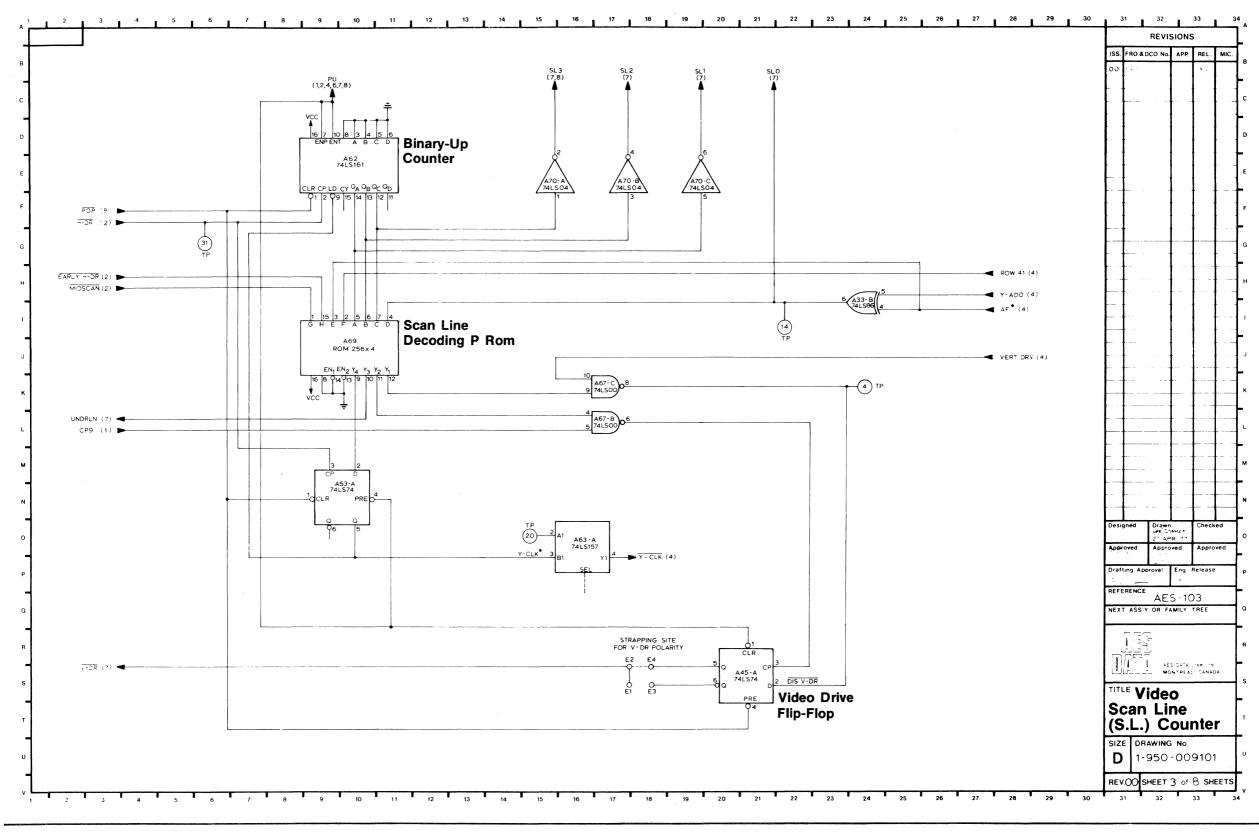

#### 3.2 SCAN LINE COUNTER

This counter consists of devices A62, A69, A53-A and A45-A. Its purpose is to keep track of the number of scan lines per character row (15 lines) and maintain the alternate 7 and 8 scan line count for the A and B fields (interlaced display).

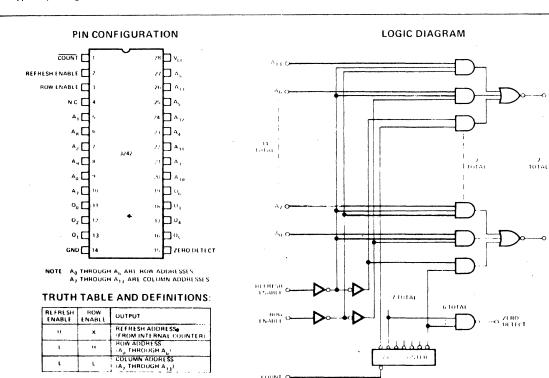

The input to the scan line counter consists of device A62(74SL161), configured as a binary up-counter. The horizontal drive signal (H-DR) increments the counter at the end of each scan line. The three bit binary outputs SL1, SL2 and SL3 are inverted and applied to the character generator as bits RS1, RS2 and RS3. Bit SL is a product of either bit Y-ADØ or AF\*, exclusive-ored by A33-B. Bit SLØ also serves as the 7 or 8 count selector bit, fed with SL1 to SL3, EARLY H-DR\*, MIDSCAN, AF, ROW 41 to a 256 x 4 bits ROM (6301). Two ROM outputs are then issued to flip-flop A45-A to form the V-DR strobe while UNDERLINE and Y-CLOCK constitute the others.

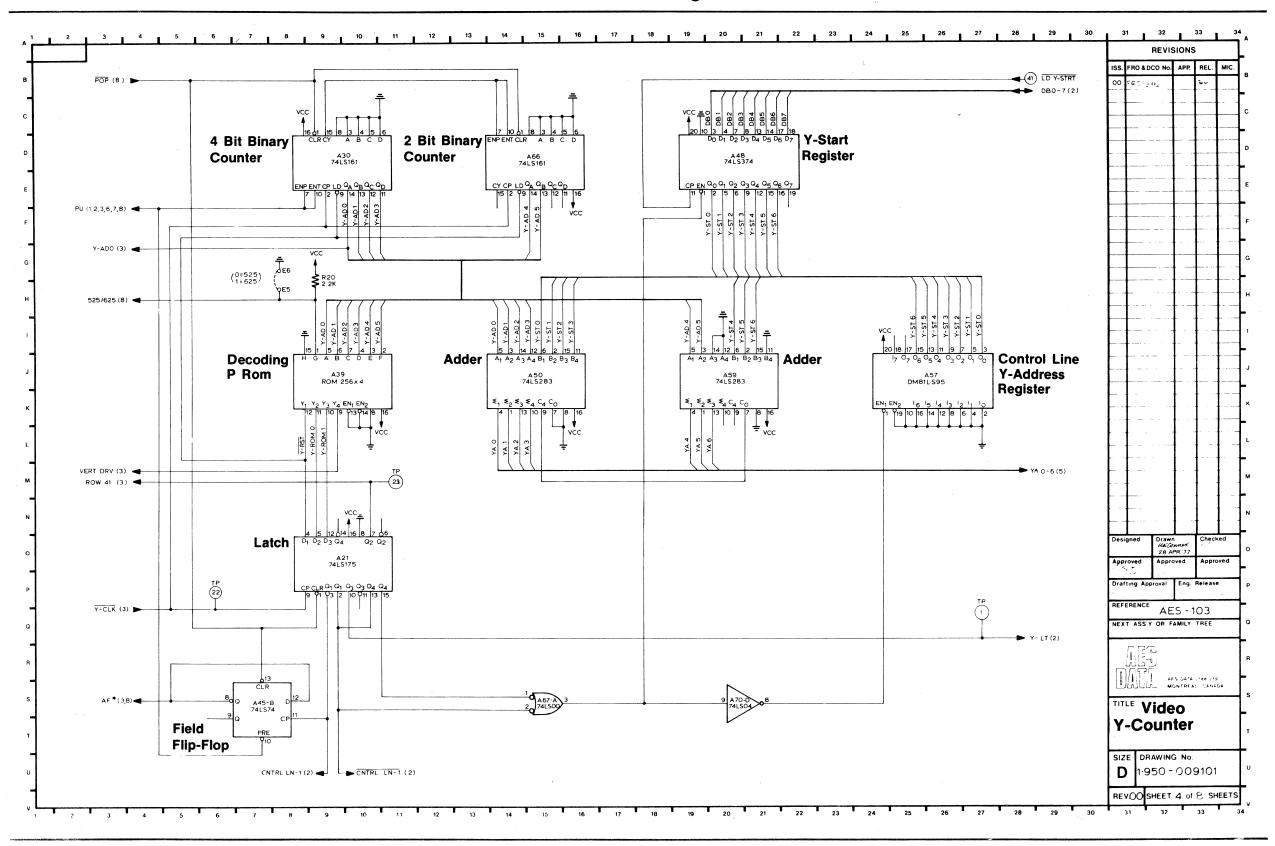

#### 3.3 THE Y-COUNTER

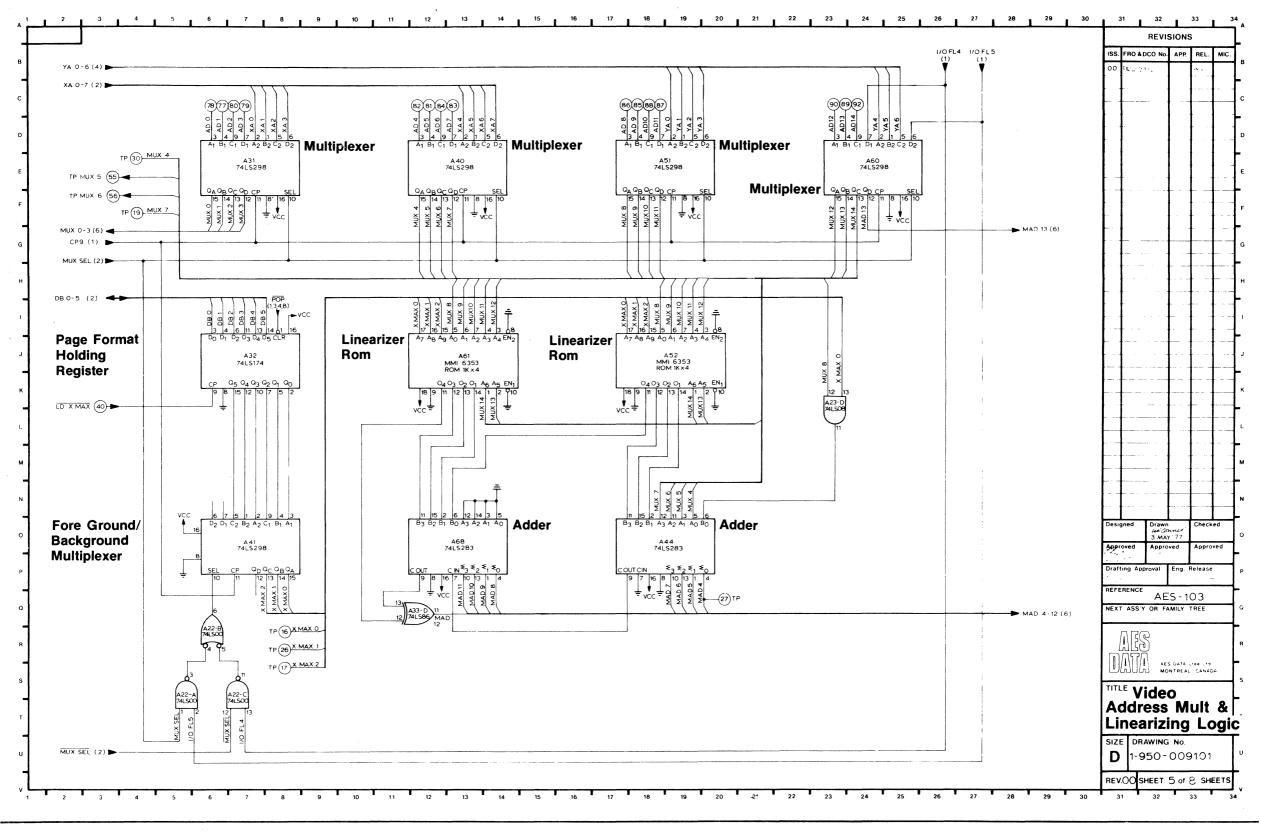

#### 3.4 THE ADDRESS LINEARIZER

This counter comprises devices A30, A39, A21, A66, A50, A48, A59 and A57. It generates the Y address of the display, meaning simply that its content corresponds to the character row count.

The basic counter consists of devices A30 and A66(74LS161) forming a 6-bit binary counter. The Y-CLK strobe, issued by scan line counter and occurring at the end of each character row, increments the counter. The Y-counter is configured similarly to the X-counter, where the Y-address of the video display is generated by the summation (A50 and A59) of the contents of Y-Start register A48(74LS374) and the contents of Y-Counter A30 and A66. The Y-Address for the control line is still located at  $\emptyset$  and accessed at tri-state register A57(74LS95) by strobe CNTRL LN-2. The outputs of the Y-Counter are also fed to decoding ROM A39(6301) from which are generated control strobes Y-RST, Y-ROMØ, Y-ROM1 and V-DR\*. The first three strobes are latched through A21(74LS175) while V-DR\* is brought to NAND gate A67-C and combined with CLR VDR, to form the V-DR pulse at flip-flop A45-A. A strapping option applied to ROM A29 selects the 525 or 625 line video display. This subgroup comprises integrated circuits A32, A41, A61, A52,A68, A44 and A33. The purpose of this subgroup is to transform the CPU, the X and Y addresses into a "linearized" format complying with the video memory address input.

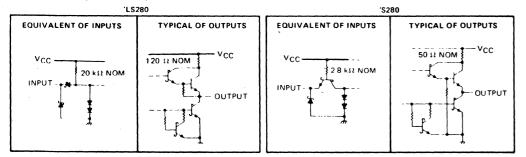

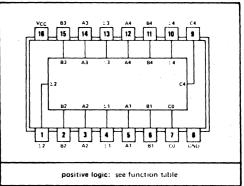

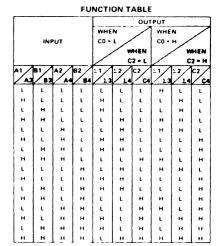

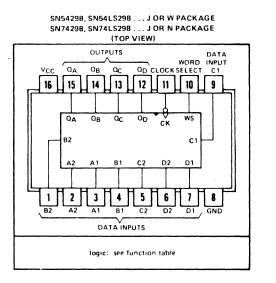

The AES-103 can display two video pages. In this case the current page occupying 8K of memory and another "background" page occupying the remaining 8K. The information format pertaining to either page to be displayed is obtained from the CPU and loaded into a holding register (A32) in a 6-bits format. The register is loaded by strobe LD XMX on the positive edge. The 6-bits are then multiplexed by A41 (74LS298), selecting whichever page is being accessed. The selected information is then fed to both ROMS (6351) as bits A7, A8 and A9. The remaining address bits AØ through A6 are issued by the X and Y address multiplexer.

At this stage, the ROMS perform a mathematical operation with the different variables appearing at its inputs, and this operation is a multiplication of the row number (Y address) by the maximum number of characters per row. The X component of the address is then added to the product by full-adders A68 and A44 (74LS293), e.g., if the maximum number of characters in a row is 80 and the row number is 57, the output of the ROM is 4560. The value of the X component may be any value between 1 and 80, so as to position a character on the video screen.

The 8 outputs (Mad 4-12) from the full-adders are then applied to the video memory controller chip. The 12th bit is issued from exclusive-or gate A33-D, being either the carry bit from A68 or A61's bit  $\emptyset$ 4.

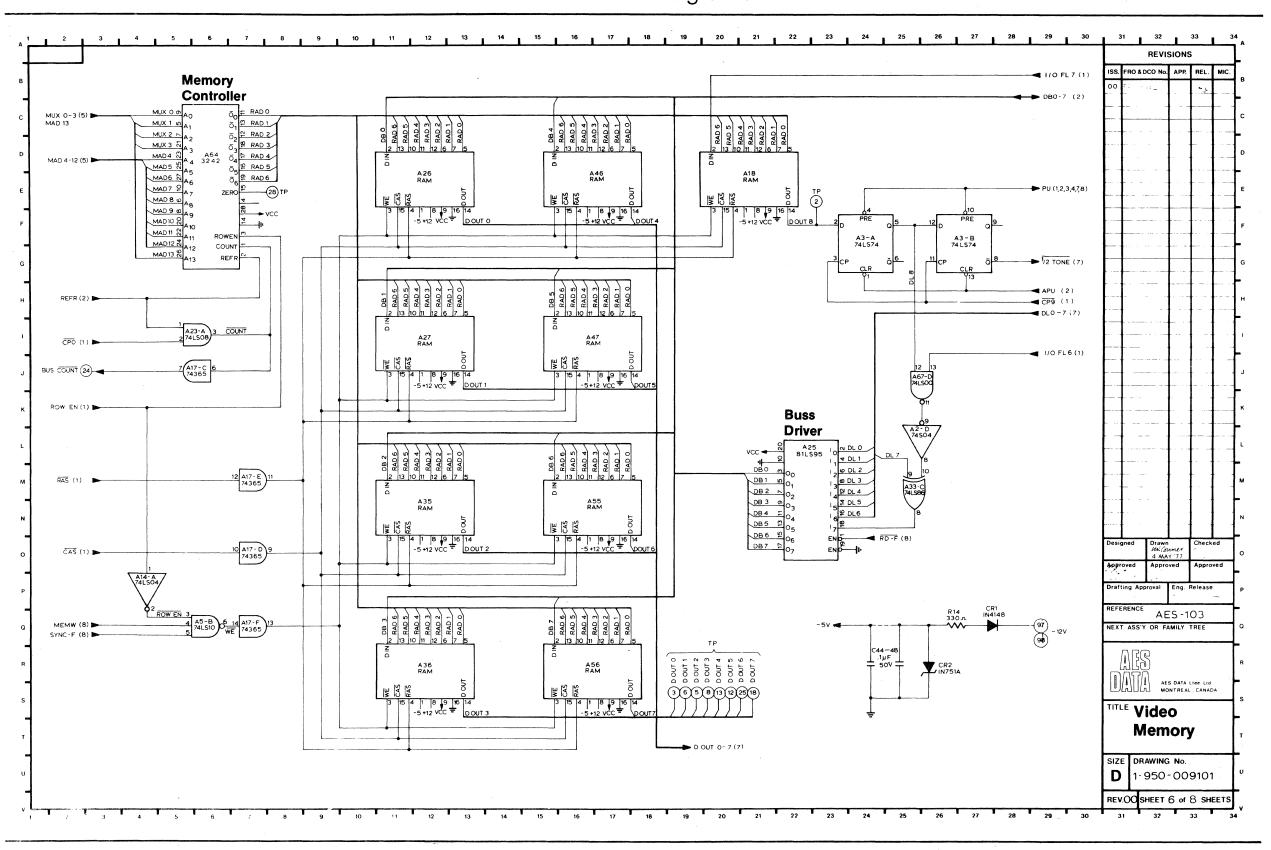

#### 3.5 THE VIDEO MEMORY AND VIDEO OUTPUT

- a) The Multiplexer: Consisting of devices A31, A40, A51 and A60 (74LS298), the multiplexer selects either the CPU bus address or the X and Y address lines. Each time a new character is to be displayed on the CRT, the MUX SEL strobe goes HI and allows the selection of the CPU buss address. The most significant bit of the CPU buss address is I/O FL5, called the Paging bit, which, when set, selects the video page located at the most significant addresses of the 16K video memory (one page equals 8K). The paging bit and the lower 4-bits of the multiplexer are applied directly to the refresh memory logic, that is memory controller chip A64(3442). The remaining bits are brought to the Linearizer circuit for further processing.

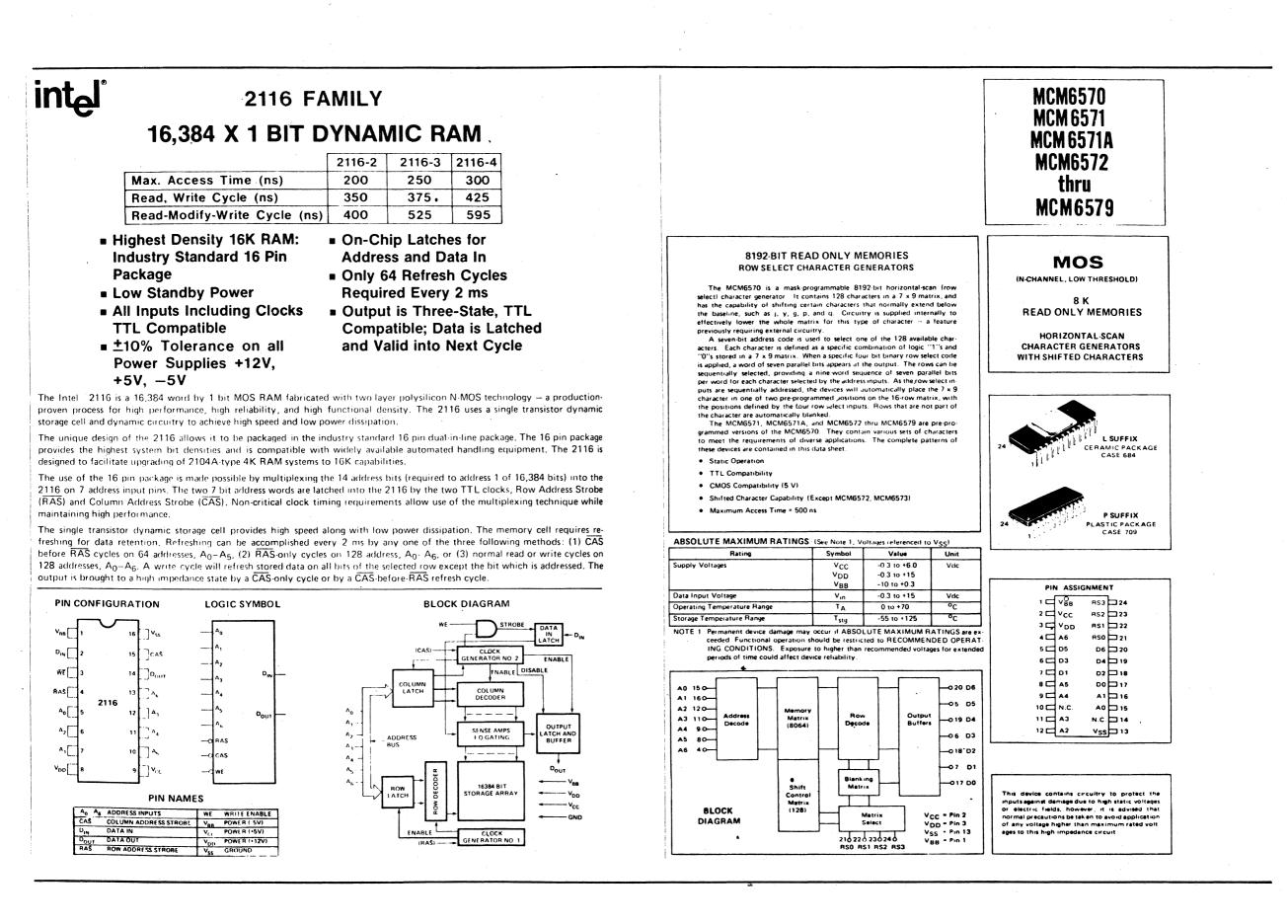

- b) <u>The Video Memory</u>: This memory comprises devices A64, A17, A23, A26, A27, A35, A36, A46, A47, A18, A25 and A3. The memory employs nine 16K devices (2116), eight of which are used as video memory and one as a buffer for half-tone character display information.

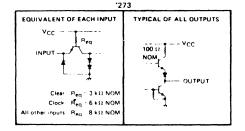

Linearized memory addresses are applied to memory controller chip A64(3242), which generates 14 addresses in 7 address segments, in a multiplexer fashion and also refresh addresses, since it contains its own refresh address counter. The memory controller is timed by three strobes called REFR, COUNT and ROWEN, all issued by the timing generator. The 16K RAM chips are strobed by RAS\* and CAS\*, allowing proper address loading and data transfer. The eight data bits to the RAM chips are obtained from the data buss via buss driver A25 and are written by RAM WE. The ninth RAM chip holds half-tone character information to be displayed. Its input is obtained from I/O FL7. c) <u>The Video Output Logic</u>: Devices A34, A43, A71-B, A22-C A23-B, A5-C, A8-C-D-F-E constitute the video output logic.

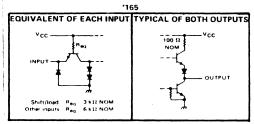

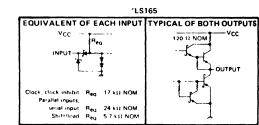

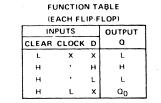

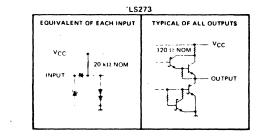

The memory data output consists of modified ASCII to meet special characters for video and printer purposes. Output character data supplied by the video memory is fed to memory latch A34 (74LS273). The code is then applied to character generator A43(MCM6570). The scan line counter outputs are also applied to A43 at inputs RSØ, RS1, RS2 and RS3, forming a binary code used to select one of the rows of the addressed character to appear at the seven output lines. The character generator outputs are then fed to parallel-to-serial shift register A54(74165) from which the serial data is brought to the video output via exclusive-or gates A23-B and A27-C, to three-input nand gate A5-C and finally to inverter A8-E. The eighth character underline bit, contained in D flip-flop A71-B, is nanded at gate A23-B. When half-tone background is displayed, the 1/2 TONE strobe coming from flip-flop A3-B goes active low. disabling inverters A8-E. The video signal now passes through inverter A8-F and therefore voltage divider R3 and R6. The video off-state is then generated at half amplitude (2.5V), thus creating the half-tone background.

Character

Generator

Shift Reg.

Ram Timing

CA.U. Data , 8

Refresh Memory

Video

Out

H-DR

. ....

3.6 THE MEMORY SYNCHRONIZATION CIRCUIT

This circuit comprises flip-flop A24, A6 and Al5; its purpose is to regulate the memory request cycle of the CPU and the refresh function.

.

When the CPU accesses the video memory, bit AD15 is set and strobes MEMR\* or MEMW\* are LO. These states are applied to A6-A, A6-D and A14F. Flip-flop A24-A D input will go LO if no Refresh cycle (PRE REFR) occurs or the video logic reads the memory (I/O FLØ 6 PRE ADDR SEL). The RAS\* signal thereafter clocks the flip-flop which issues the SYNC-F strobe. The memory is then read by the CPU via the CPU buss during the period the SYNC-F strobe is HI. At the next RAS\* pulse, the SYNC-F strobe goes LO which sets the memory flip-flop A24-B, issuing RDY\* via inverter A8-B.

When the MEMR\* or MEMW\* strobes go high again, the RDY\* flip-flop will be cleared.

## 3.7 THE I/O FLAG REGISTER

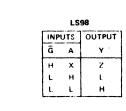

This register consists of integrated circuit Al9(9334), which distributes 8 flags (I/O FLØ - FL7). Strobe LD I/O enables it when LO. The register accepts a four-bit (DBØ DB3) binary number and distributes the decoded number on 8 lines.

## 3.8 THE TICK AND BELL LOGIC

This circuit consists of dual timer device Al6(3456), inverters Al4-E, Al4-D and A8-A and output transistors Ql and Q2.

When BELL and TICK sounds are required, I/O flags FL2 and FL3 are caused to pulse through inverters Al4-E or Al4-D. Device Al6 consists of a dual timer (similar to a 555) where each one is tuned to the specific pitch required for the bell and tic sounds. A 2 KHz signal appears at inverter A8-A, whose output is an open collector, connected to resistors Rll and Rl2. When timer output A or B goes high, the 2 KHz signal modulates the collector circuit of Darlington pair Ql and O2, which in turn drive the speaker.

## 3.9 THE TIMER

This circuit includes devices A72, A71-A, A10-F, A15-D and A15-C. Its purpose is to generate an interrupt every 200 milliseconds (used for software purposes).

The field rate, AF\*, issued by the Y-counter, is introduced to decade counter A72(74LS161), enabled by I/O FL1. The output of the counter is taken at the carry output and applied to D flip-flop A71A. Strobe CLR TIME INTRPT and the rate of AF\* control the flip-flop. The Q output forms the CPU interrupt, which is distributed by line driver A10-F.

Schematic Diagrams

~

,

.....

# 01 02 03 04 05

# 01 02 03 04 05

-

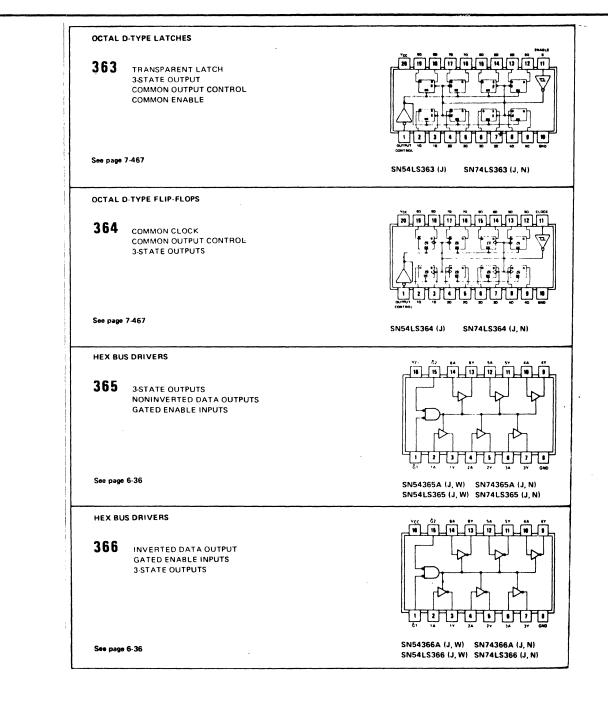

|                 | 1   | P.C.B. Drilling  | C6-955-009101 | A31,40,41,51,60      | 5      | SN74LS298N                   | 660-0237 |

|-----------------|-----|------------------|---------------|----------------------|--------|------------------------------|----------|

|                 | 2   | P.C.B. Extractor | 252-0102      | Al7                  | 1      | SN74365AN                    | 660-0238 |

|                 |     |                  |               | A10                  | 1      | SN74366AN                    | 660-0239 |

| A18,26,27,35,36 | 9   | Dynamic Ram      | A6-937-004801 | A37,48               | 2      | SN74LS374N                   | 660-0240 |

| 46,47,55,56     | -   |                  |               | A25,28,57            | 3      | DM81LS95N                    | 660-0241 |

| A49             | 1   | Rom 256X4        | 6-908-001801  | A64                  | 1      | 3242                         | 660-0250 |

| A58             | 1   | Rom 256X4        | 6-908-001802  | Al6                  | 1      | MC3456P                      | 660-0254 |

| A69             | 1   | Rom 256X4        | 6-908-001803  |                      | 1      |                              | 000 0204 |

| A39             | 1   | Rom 256X4        | 6-908-001804  | Q1,2,3               | 3      | Transistor 2N 2222A          | 620-0101 |

| A52             | 1   | Rom 1K X4        | 6-908-001901  | 2-1213               | 5      |                              | 020 0101 |

| A61             | -   | Rom 1K X4        | 6-908-001902  | CR5                  | 1      | Diode IN4001                 | 600-0112 |

| A54             | -   | SN 74165N        | 660-0114      | CR1,3,7,8            | 1<br>Δ | Diode IN4148                 | 601-0104 |

| A19             | 1   | F9334            | 660-0121      | CR4                  | 1      | Diode IN702A                 | 602-0100 |

| A2              | ĩ   | SN74S04N         | 660-0145      | CR2                  | 1      | Diode IN751A                 | 602-0100 |

| A8              | 1   | SN7406N          | 660-0202      | CR6                  | 1      | Diode IN752A                 | 602-0104 |

| A15,22,67       | 3   | SN74LS00N        | 660-0208      | Gito                 | Ĩ      | block invoza                 | 002-0105 |

| Al4,70          | 2   | SN74LS04N        | 660-0210      | C9,13,52             | 3      | Capacitor 10uF 20V. Tag.     | 164-0177 |

| A23             | 1   | SN74LS08N        | 660-0211      | C6,7,11              | 3      | Capacitor 33uF 16V. Tag.     | 164-0220 |

| A5              | 1   | SN74LS10N        | 660-0212      | C8,10,12,14-33,      | 28     | Capacitor .05uF              | 165-0251 |

| A6              | 1   | SN74LS32N        | 660-0215      | 38,49-51,53          | 20     | apacitor .05ar               | 103-0231 |

| Al3             | 1   | SN74LS42N        | 660-0217      | Cl,4,5               | 3      | Capacitor .01uF              | 165-0263 |

| A3,24,45,53,71  | 5   | SN74LS74AN       | 660-0219      | C2, 3, 34, 37, 39–48 | 16     | Capacitor .luF               | 165-0347 |

| A33             | 1   | SN74LS86N        | 660-0220      | 02/3/31/3//39 10     | 10     |                              | 103-0347 |

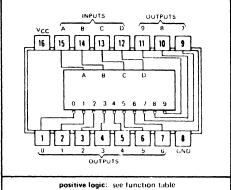

| A63             | -   | SN74LS157N       | 660-0225      | R3,4,5,6             | 4      | Resistor 180 OHMS 1/4W 5%    | 402-0181 |

| A4              | 1   | SN74LS160AN      | 660-0226      | R7                   | 1      | Resistor 200K OHMS 1/4W 5%   | 402-0204 |

| All,20,30,62    | -   | SN74LS161AN      | 660-0227      | R18,19,20            | 3      | Resistor 2.2K OHMS $1/4W$ 5% | 402-0204 |

| 66,72           | C C |                  |               | R1,2,10              | 3      | Resistor 270 OHMS $1/4W$ 5%  | 402-0271 |

| A32             | 1   | SN74LS174N       | 660-0228      | R14,17               | 2      | Resistor 330 OHMS $1/4W$ 5%  | 402-0331 |

| A21             | -   | SN74LS175N       | 660-0229      | R12,11               | 2      | Resistor 3.9K OHMS $1/4W$ 5% | 402-0392 |

| A34,65          | 2   | SN74LS273N       | 660-0233      | R15                  | 1      | Resistor 510 OHMS $1/4W$ 5%  | 402-0511 |

| A12             | 1   | SN74LS279N       | 660-0234      | R8                   | 1      | Resistor 82K OHMS $1/4W$ 5%  | 402-0823 |

| A29,38,44,50    | Ē   | SN74LS283N       | 660-0236      | R13                  | 1      | Resistor 10 OHMS $1/2W$ 5%   | 402-0823 |

| 59,68           | ~   |                  |               | R16                  | 1      | Resistor 47 OHMS $1/2W$ 5%   | 411-0100 |

| 00,000          |     |                  |               |                      | ±      | TOTTOOL HI OTHID T/2W JO     | 411-04/0 |

Video Parts List

|                                            |         |    |   |   |    |    |                                                                   |                                                 | Video<br>Parts List |    |    |    |    |                                                                   |                                                 |

|--------------------------------------------|---------|----|---|---|----|----|-------------------------------------------------------------------|-------------------------------------------------|---------------------|----|----|----|----|-------------------------------------------------------------------|-------------------------------------------------|

|                                            | 01      | 02 | 0 | 3 | 04 | 05 |                                                                   |                                                 |                     | 06 | 07 | 08 | 09 |                                                                   |                                                 |

| Video Sig. J2<br>Video Test Jl             | 1<br>1  |    |   |   |    |    | Connector 10 Pins<br>Connector 34 Pins                            | 290-0120<br>290-0123                            |                     | 1  | 1  | 1  | 1  | P.C.B. Assy<br>P.C.B. Assy<br>P.C.B. Assy                         | A2-950-009101<br>A2-950-009102<br>A2-950-009103 |

| A2,16<br>A18,26,27,35,36<br>39,46,47,49,55 | 2<br>13 |    |   |   |    |    | Socket DIL 14 Pins<br>Socket DIL 16 Pins                          | 698-0102<br>698-0103                            | Y1<br>Y1            |    |    |    |    | Crystal 15.75MHz (60Hz)<br>Crystal 15.625MHz (50Hz)               | 490-0115<br>490-0117                            |

| 56,58,69<br>A43<br>A52,61                  | 1<br>2  |    |   |   |    |    | Socket DIL 24 Pins<br>Socket DIL 18 Pins                          | 698-0106<br>698-0127                            | A43<br>A43<br>A43   | 1  | 1  | 1  | 1  | Character Generator<br>Character Generator<br>Character Generator | 6-907-000301<br>6-907-000201<br>6-907-000101    |

|                                            |         | 1  | 1 |   | 1  | 1  | P.C.B. Assy<br>P.C.B. Assy<br>P.C.B. Assy                         | A2-950-009101<br>A2-950-009102<br>A2-950-009103 |                     |    |    |    |    |                                                                   |                                                 |

| Y1<br>Y1                                   |         | 1  | 1 |   |    |    | Crystal 15.75MHz (60Hz)<br>Crystal 15.625MHz (50Hz)               | 490-0115<br>490-0117                            |                     |    |    |    |    |                                                                   |                                                 |

| A43<br>A43<br>A43                          |         |    |   |   | 1  | 1  | Character Generator<br>Character Generator<br>Character Generator | 6-907-000301<br>6-907-000201<br>6-907-000101    |                     |    |    |    |    |                                                                   |                                                 |

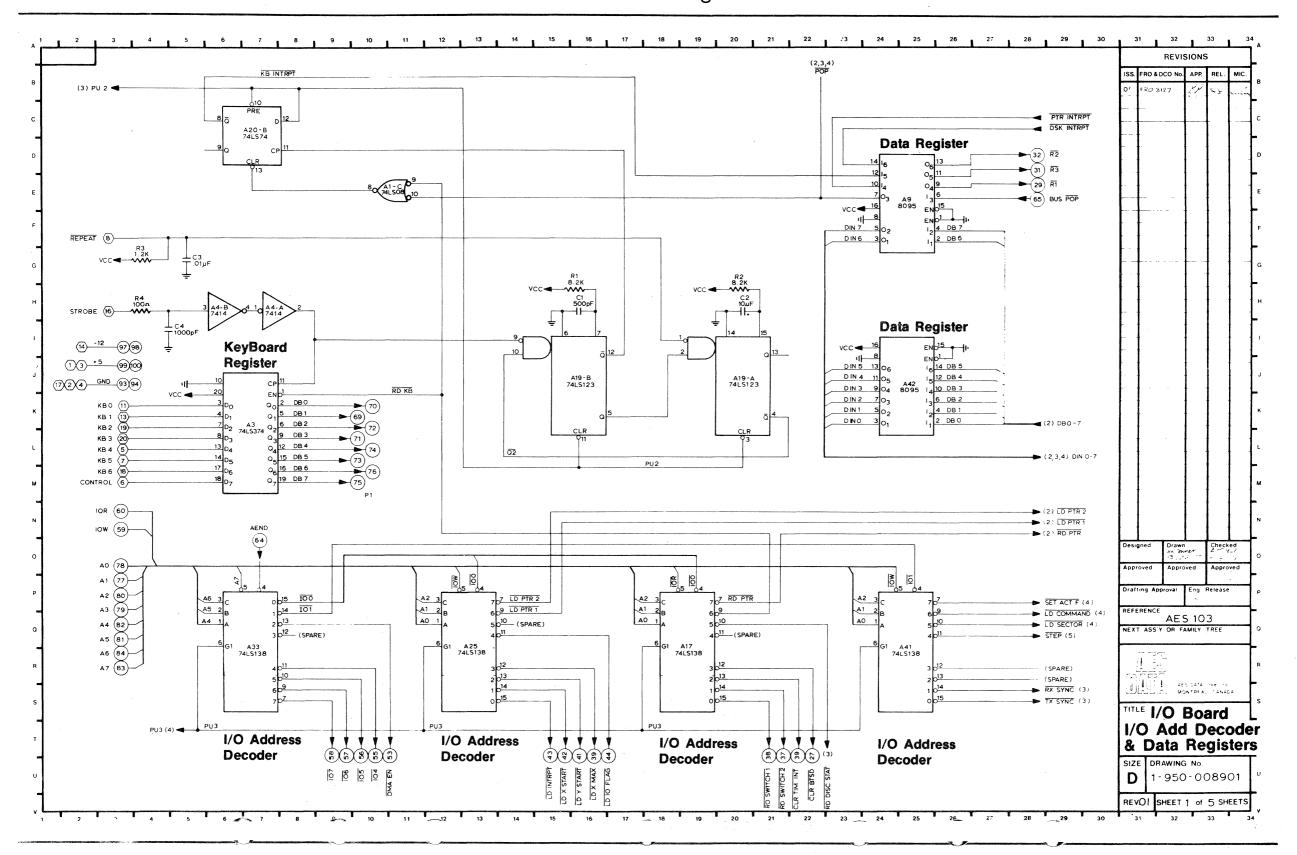

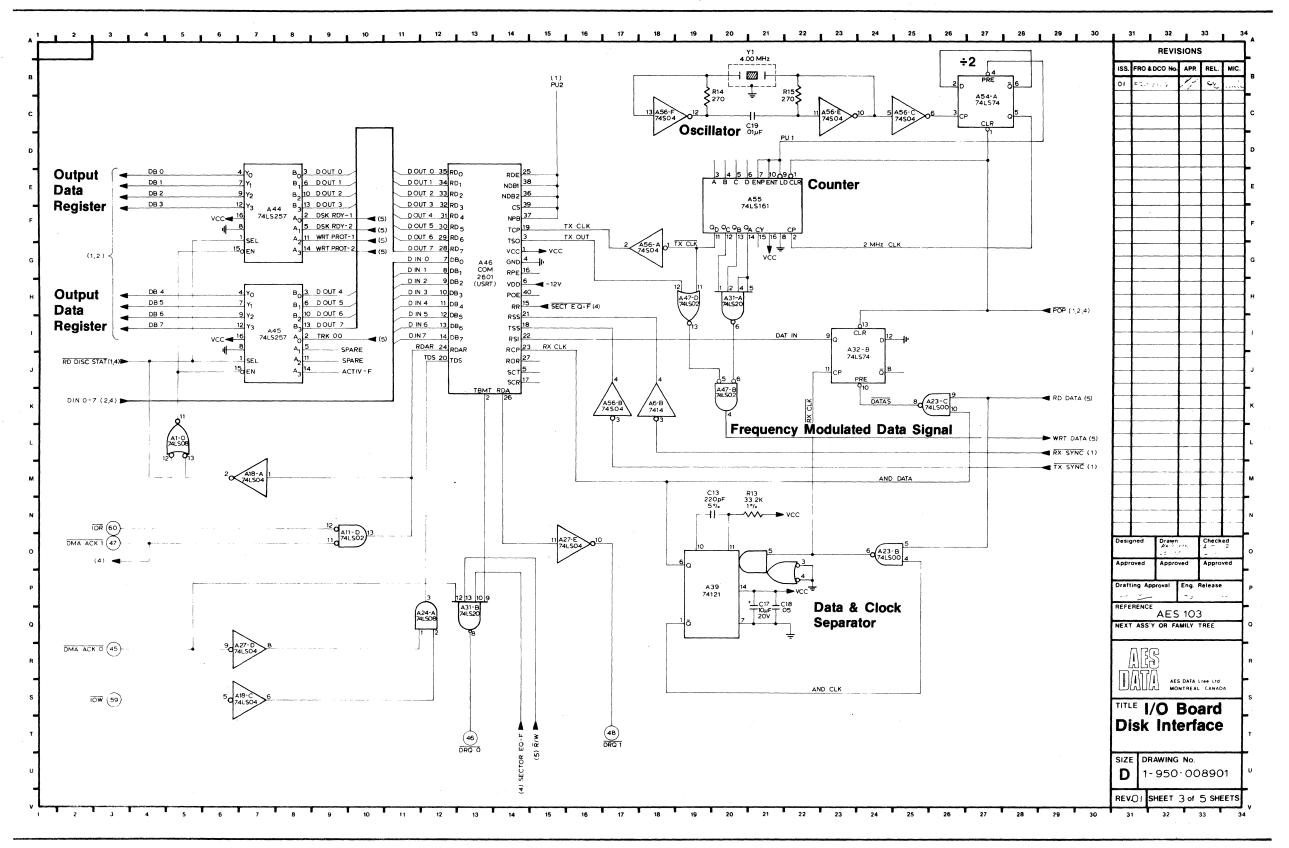

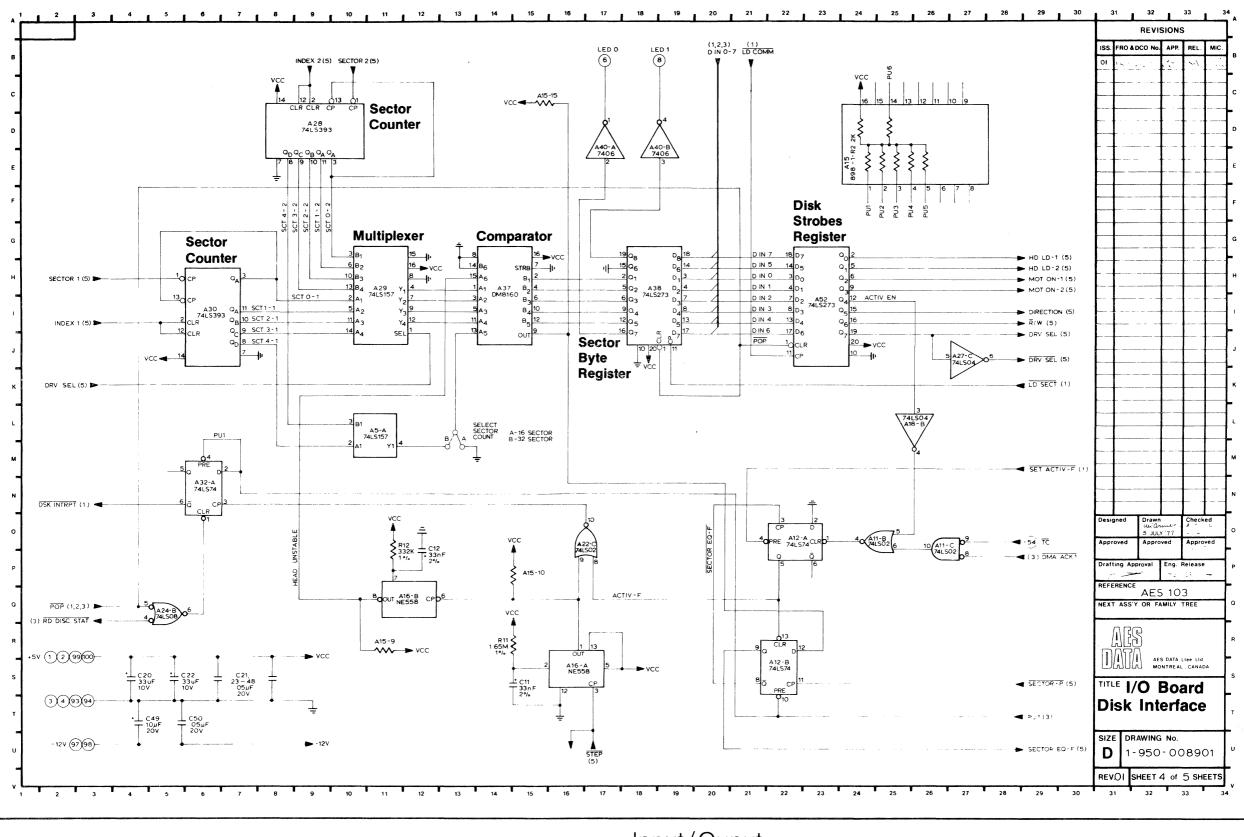

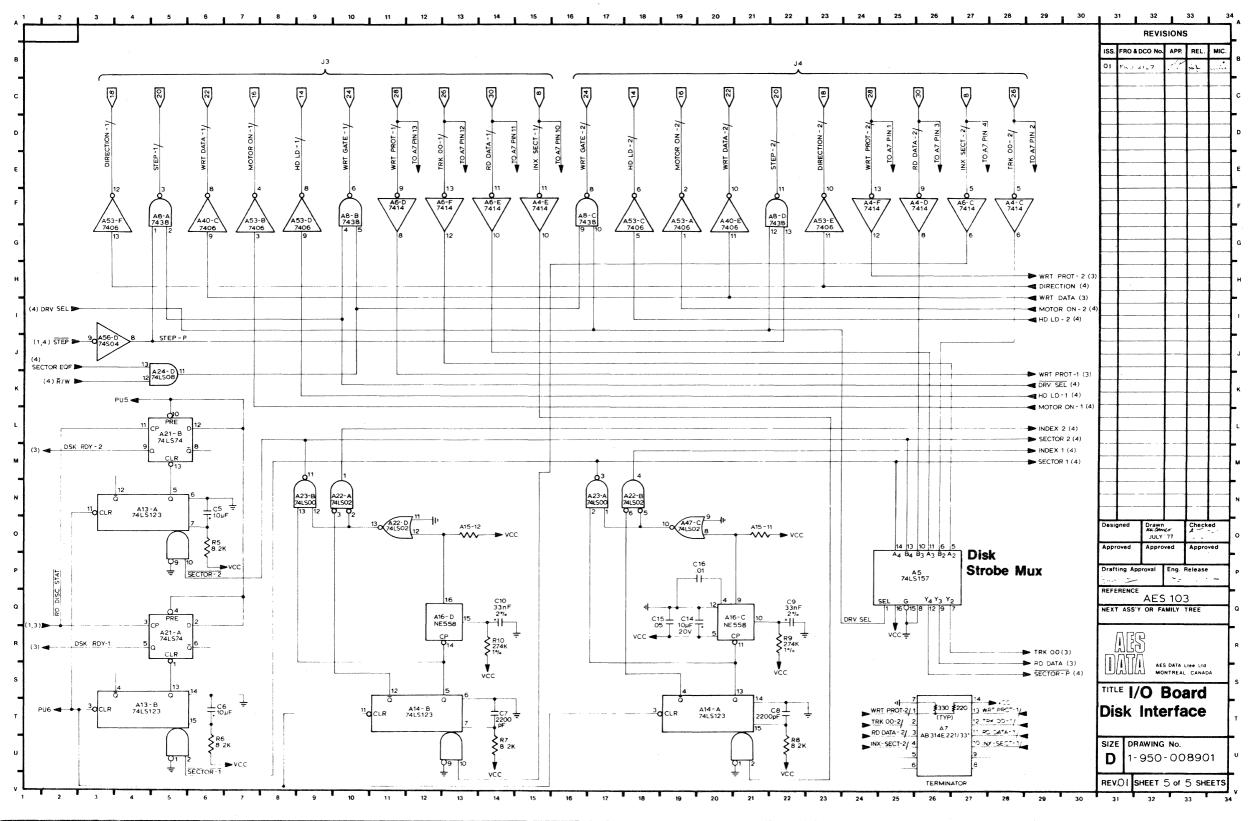

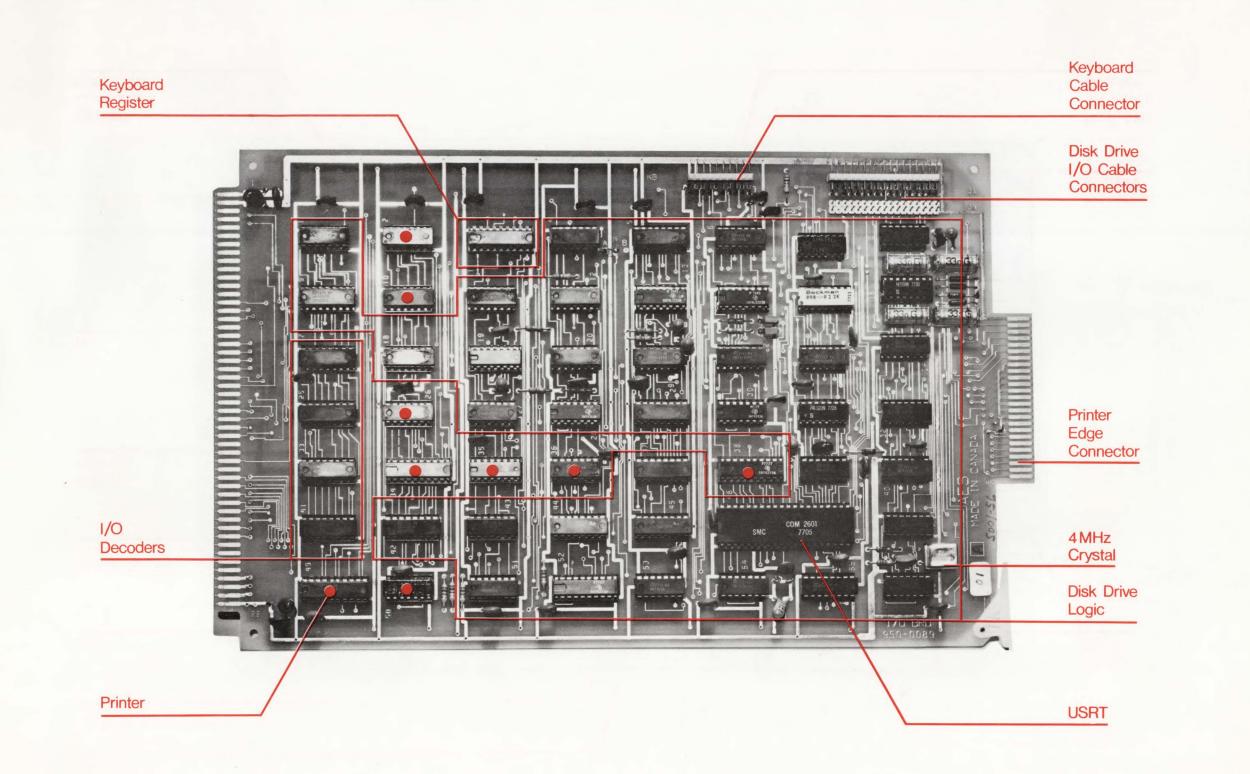

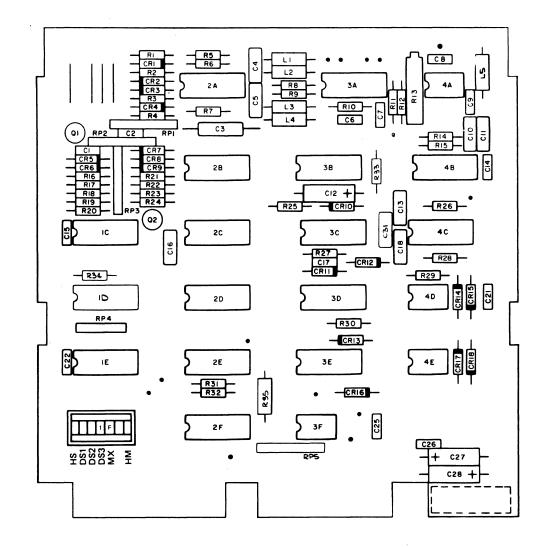

## THE INPUT/OUTPUT INTERFACE BOARD (D1-950-008901-00)

### 2.2 THE KEYBOARD INTERFACE

#### 1. INTRODUCTION

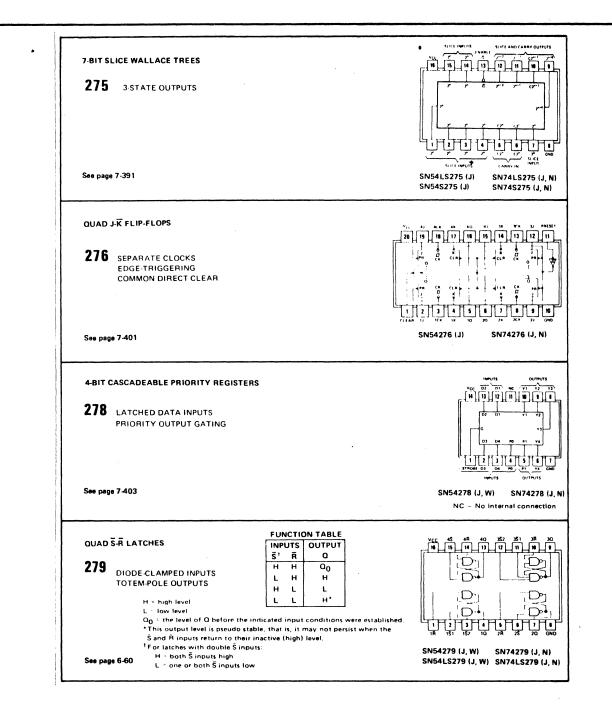

The I/O Interface Board includes all the necessary logic circuits to interface the CPU with the various peripheral devices. These peripherals include a high-speed printer, a keyboard, one or two floppy diskette drives, several internal functions and two optional expansion boards. The board is divided into four logical groups:

- The Address Decoder

- The Keyboard Interface

- The Printer Interface

- The Disc Interface

#### 2. FUNCTIONAL DESCRIPTION

## 2.1 THE ADDRESS DECODER

The decoder consist of 3-to-8 line decoders A33, A35, A17 and A41. It provides select signals for the peripherals including two sets of select lines for system expansion.

The decoder is fed by 7 address lines, AØ through A6, and two strobes, IOW and IOR. Decoder A33 issues address lines IO7, IO6, IO5 and IO4, used for system expansion, while the other three issue addresses for the printer, the keyboard and the disc drive. This circuit includes devices A3, A4-A, A4-B, A1-C, A20-B, A19-B and A19-20.

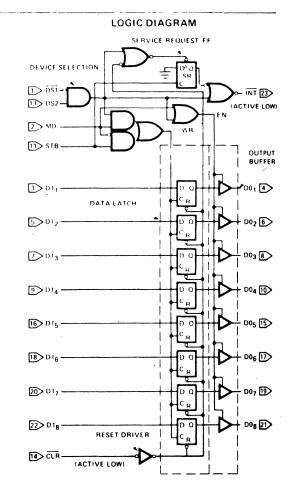

Keyboard data is generated in ASCII code and stored in tri-state register A43(74LS374) when a key is pressed, thus generating the STROBE signal. This signal also sets one-shot multivibrator A19-B which in turn sets INTERRUPT flip-flop A20-B. The keyboard data is read when the RD KB signal goes low and at the same time the INTERRUPT flip-flop is cleared via gate A1-C(74LS08). The REPEAT key is used whenever a specific character is displayed as a string on the video screen. When pressed simultaneously with a character key, the output of A19-A goes low and is fed back to A19-B. When the STROBE signal is received, both one-shots of A19 form an oscillator, causing flip-flop A20-B to send an interrupt to the CPU every 35 milliseconds.

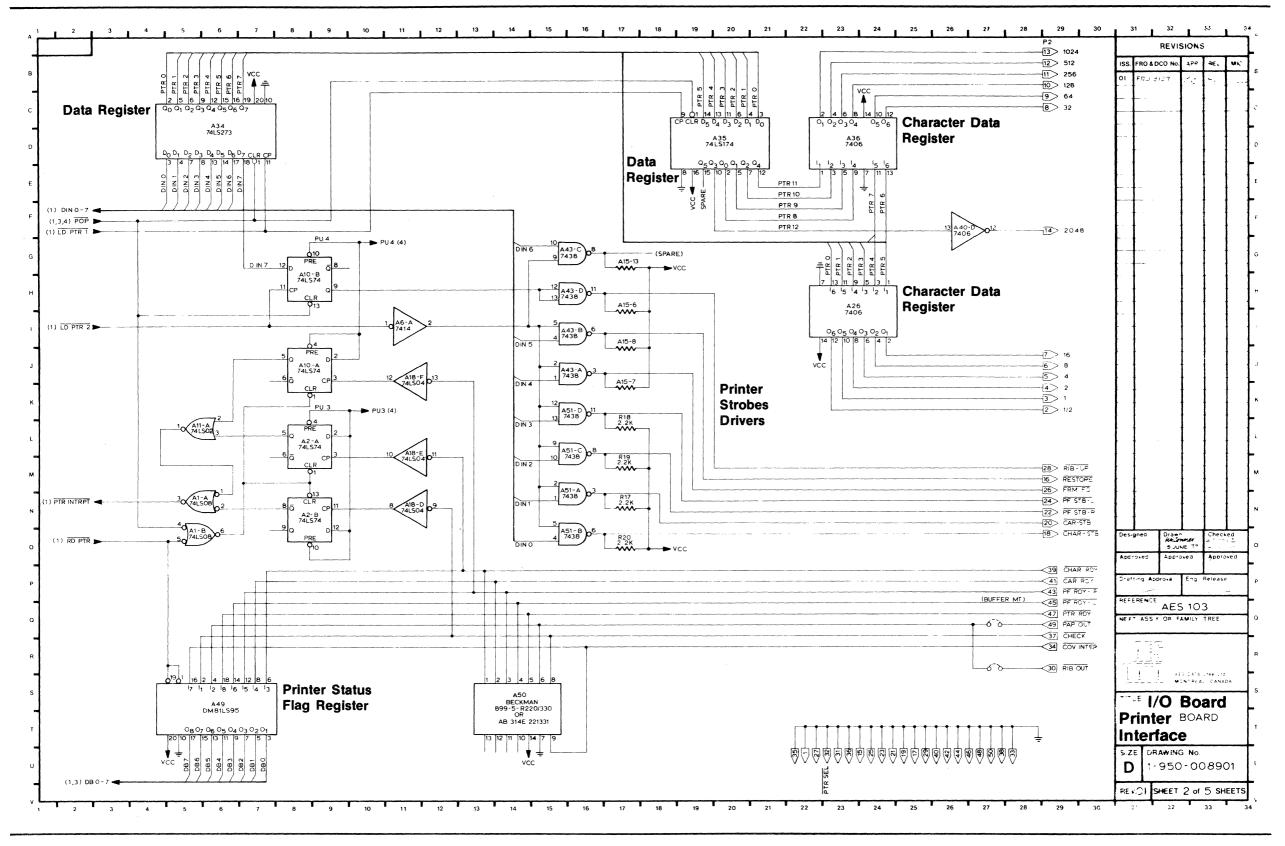

### 2.3 THE PRINTER INTERFACE

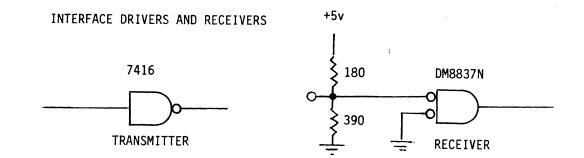

This interface allows the video memory contents to be printed. It comprises devices A9, A42, A34, A35, A36, A10, A2, A26, A43, A51, A49 and A50.

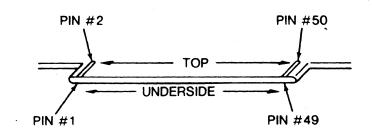

The operating principle of the interface consists of channelling data, read from the data buss, through buffers and then formatting them into the 12-bits buss required by the printer. Seven strobe signals are also fed to the printer. During the operation of the printer, ten status flags are returned to the interface so that the CPU may constantly assess the printing process.

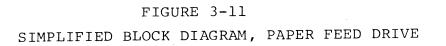

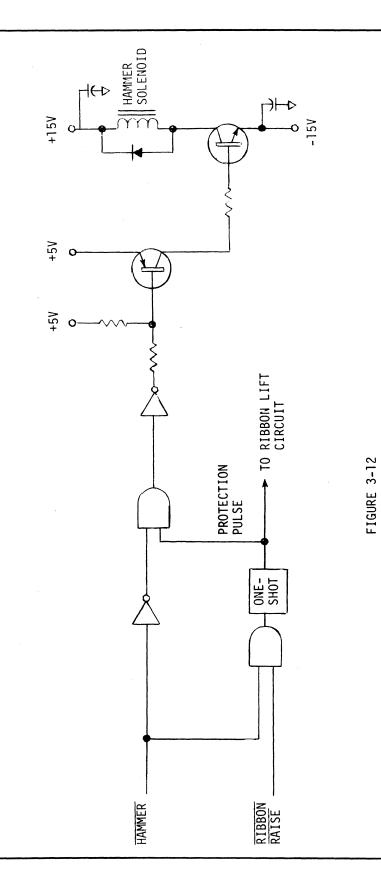

Data bits issued by the 8080A arrive at the interface through buffers A9 and A42(8095). The first six most significant bits (PTR 8 through PTR13) are loaded first into D-type latch A34 at the positive-going edge of the LDPTR-1 strobe at which time the original 6-bits are transferred to latch A35. The following eight bits are then loaded into A34 at a second LD PTRl strobe. The twelve bits formed are then fed to the printer via drivers A26 and A36. Strobe signals to the printer are issued by nand buffers A43 and A51. Data bit 7 is stored in flip-flop AlO-B and becomes the ribbon control bit. The ten-bit status lines supplied by the printer are terminated by resistor network A50 and applied to tri-state driver A49, delivering printer status to the data buss. Status lines CHECK, PAPER FEED RDY and CHAR RDY are inverted through Al8 and applied to flip-flop Al0A, A2-A and A2-B. Their outputs are ored by All-A and Al-A to issue the PTR INTRPT flag.

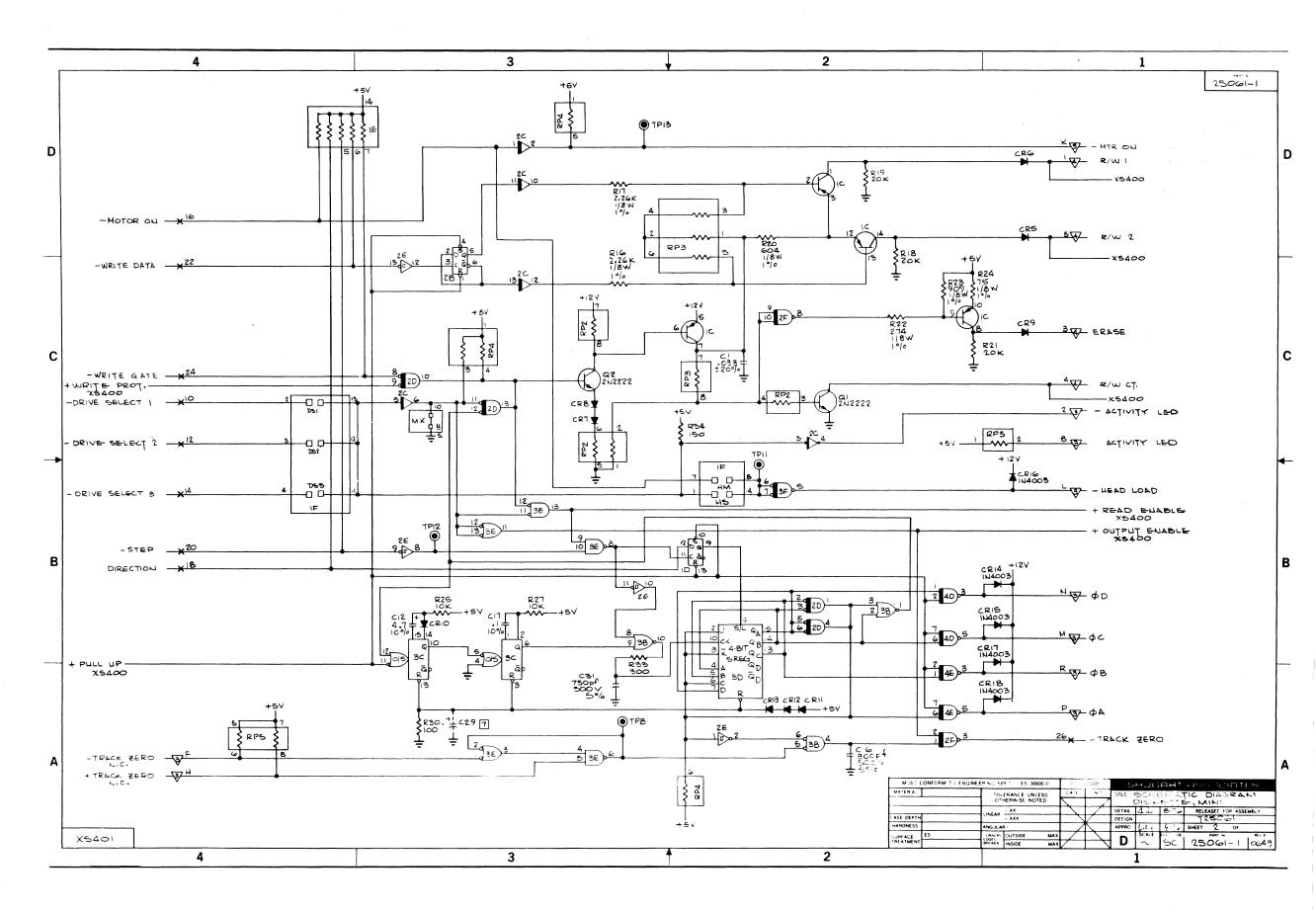

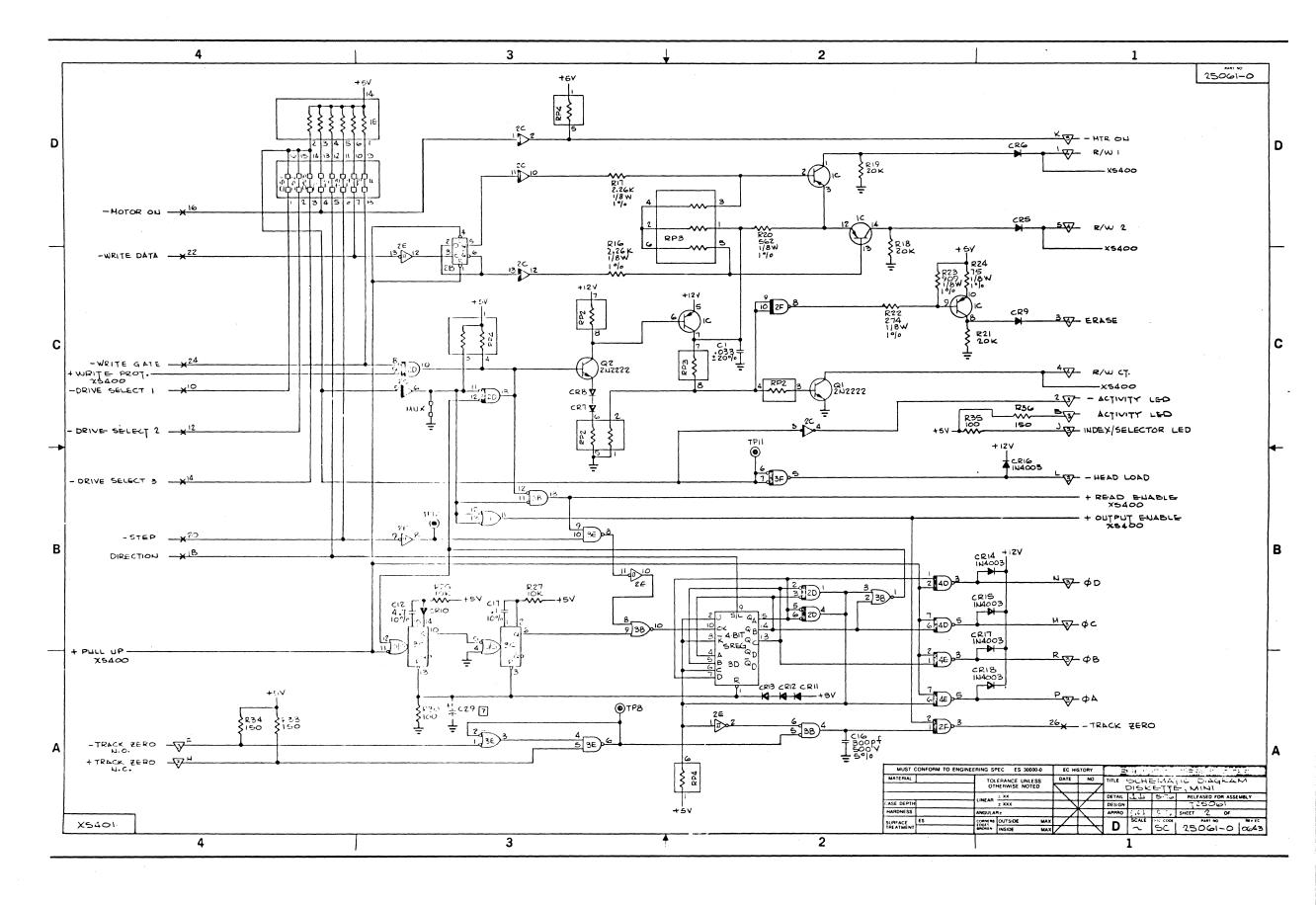

#### 2.4 THE DISC DRIVE INTERFACE

The AES-PLUS Text Editor allows the use of two miniature floppy disc drives of the Shugart Model 400 type. The two disc drives are controlled by two independent interfaces where selection is accomplished by multiplexers on the I/O board itself. Each drive has its own sector counter and ready flag signals.

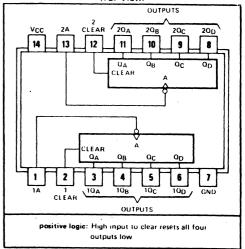

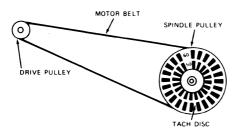

a) <u>Sector Search Scheme</u>: A photo-transducer, mounted on the disc drive mechanism, generates a pulse each time a hole appears on the magnetic disc. There are 16 holes punched on the inner circumference of the disc plus one index hole, therefore 17 pulses are generated. The sector pulses from both disc drives arrive at the I/O board and are applied to inverters A4-E and A6-C. These pulses are then brought to one-shot multivibrator Al4-A (for disc drive 1) where the specified time constant reduces their width. The separation of the index and sector pulses is produced by one-shot multivibrator Al6-A in conjunction with gates A47-C, A22-B and A23-A. The Q output of Al4-A is fed to pin 11 of Al6-A where each pulse is stretched to 9 milliseconds at the output, due to its long time constant. Since the rotating disc creates a 12.5 millisecond period between each sector pulse and the index hole is located at midpoint between two sector holes, the output of Al6-A will remain low during that entire period. The following index hole pulse is then issued by the Q output of Al4-A which will clear counter A30 via gate A22-B.

The 9 millisecond pulse is applied to Nand gates A22-B and A23-A. The Q output of Al4-A is also applied to A23-A which outputs clock pulses to 5-bits binary counter A30(74LS393).

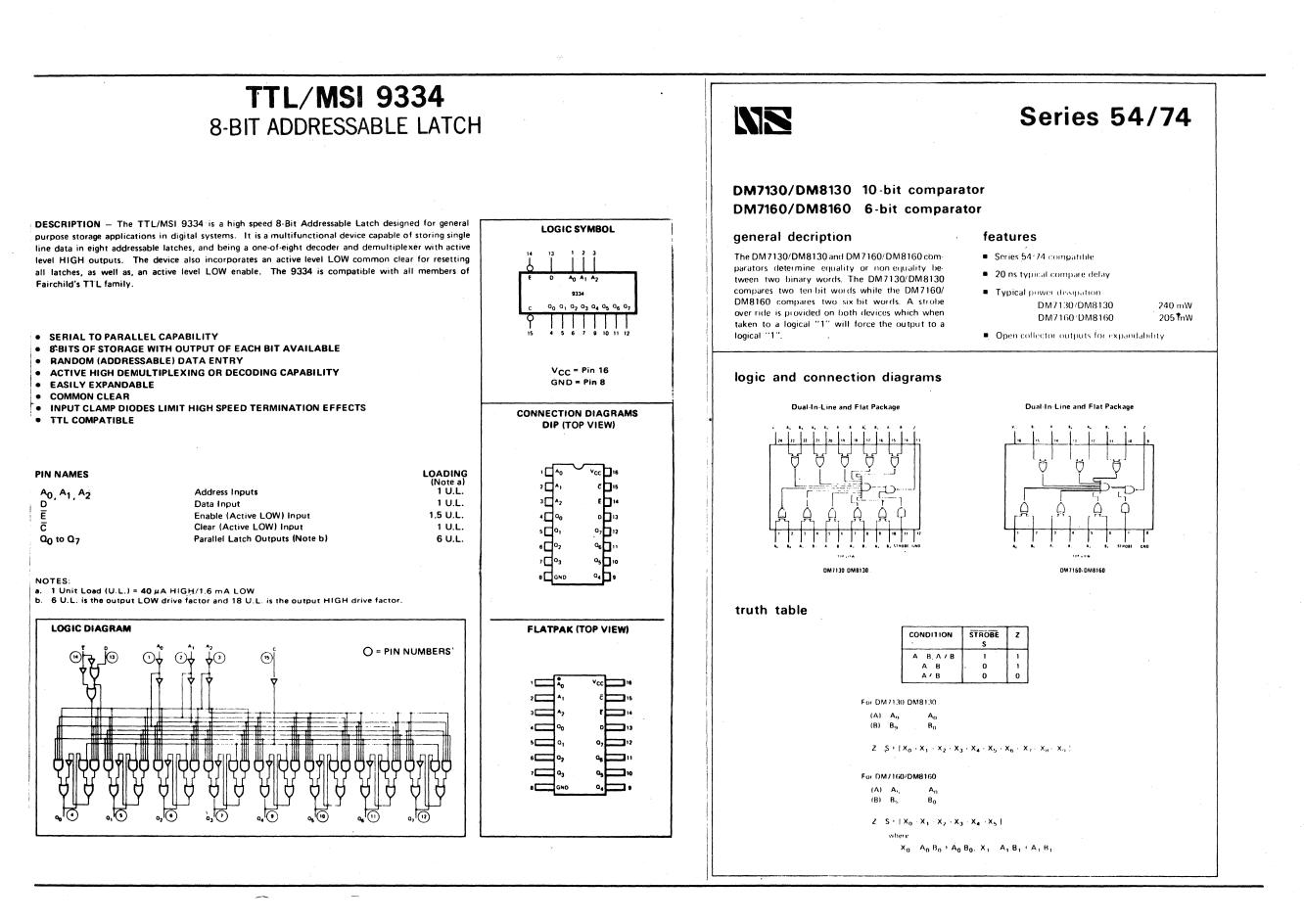

Since provision has been made for a 32 sector diskette, sector counter bit SCT4-1 is applied to one section of multiplexer A5 whose output is tied to a strapping pin, allowing for the option. The outputs of counters A28 and A30 are then fed to multiplexer A29, whose output is selected by the DRIVE SEL signal, and then to 6-bit comparator (DM8160) A37 where comparison occurs between the value of the sector to be addressed, stored in sector register A38(74LS273), and the output value of the sector counter. When both values become equal, the SECT EO signal is issued to flip-flop A12-A of the DMA (Direct Memory Access) logic. Sector register A38 also drives LED's Ø and 1, indicating the disc drive in service.

- b) <u>Track Access Logic</u>: This circuit generates the DIRECTION signal, defining the direction of motion of the R/W head and the STEP signal which moves the head in the selected direction. The direction signal is issued by the data buss through register A52(73LS273) while the STEP signal originates from the address decoder. Both signals are issued to the disc drive by drivers A53 and A8.

- c) <u>Disc Drive Select</u>: Selection of the disc drives is accomplished by the address decoder, multiplexer A29, data bits  $\emptyset$  and 1 for selecting the R/W head and bit 7 for the Drive Select strobe. After the selection, each disc drive receives its own WRT GATE, HEAD LD, MOTOR ON and WRITE DATA signals.

Each disc drive issues three status flags which are multiplexed by A5. These are the TRK $\emptyset \emptyset$ , the READ DATA an thed WRITE PROT. The status flag lines are terminated by resistor network A7.

Both DSK RDY strobes are derived from the sector pulse train. For instance, the output of gate A23-A is fed to one-shot multivibrator A13-B, where the pulse train is transformed into one pulse with a period of approximately 25 milliseconds and then applied to flip-flop A21-a.

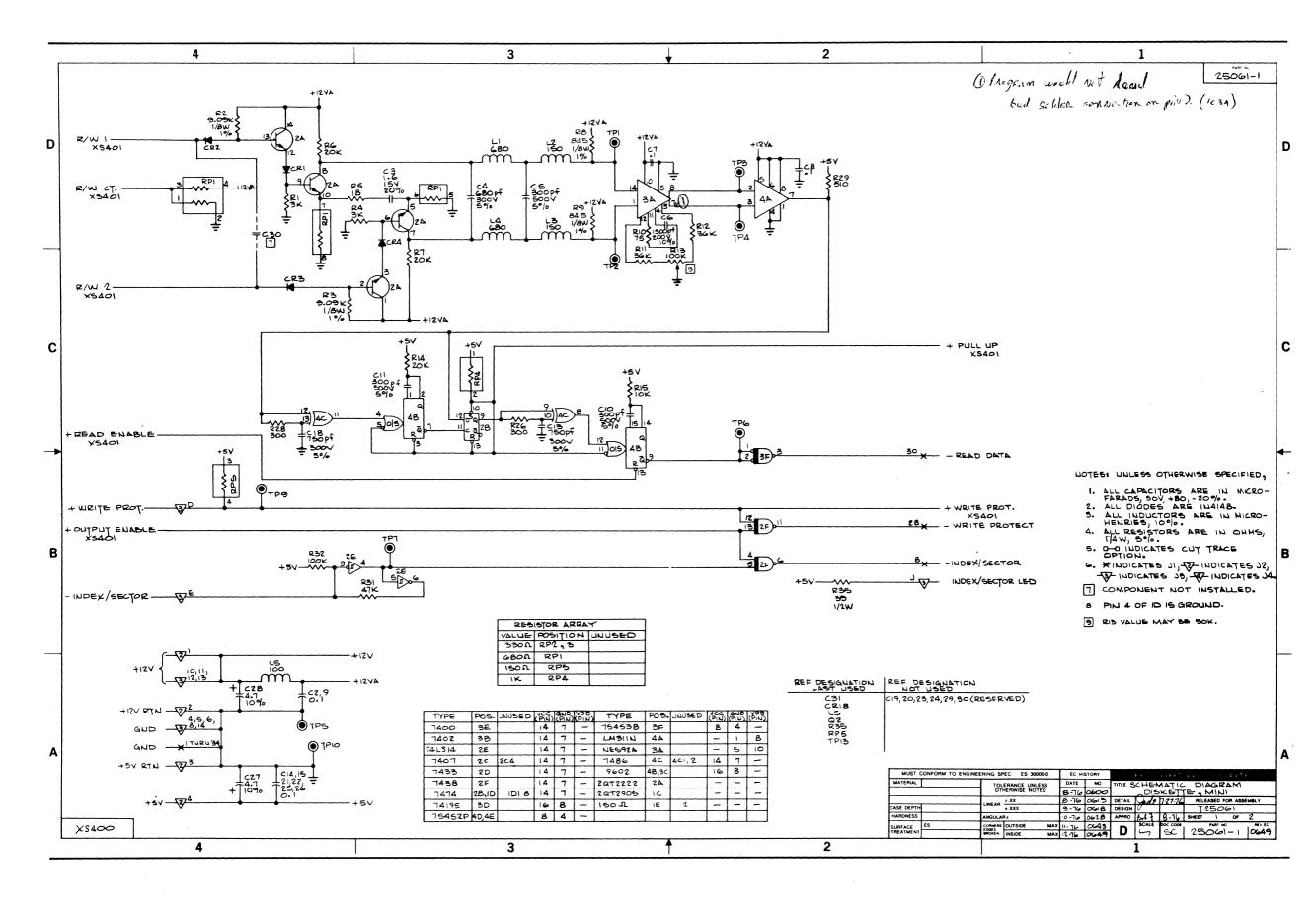

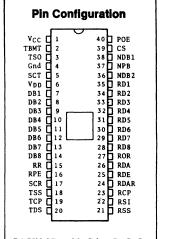

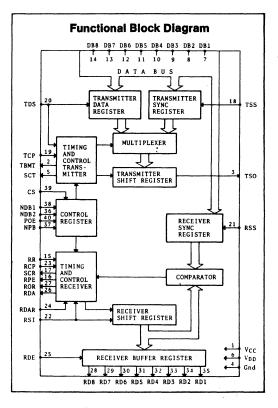

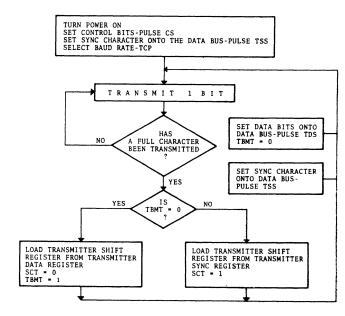

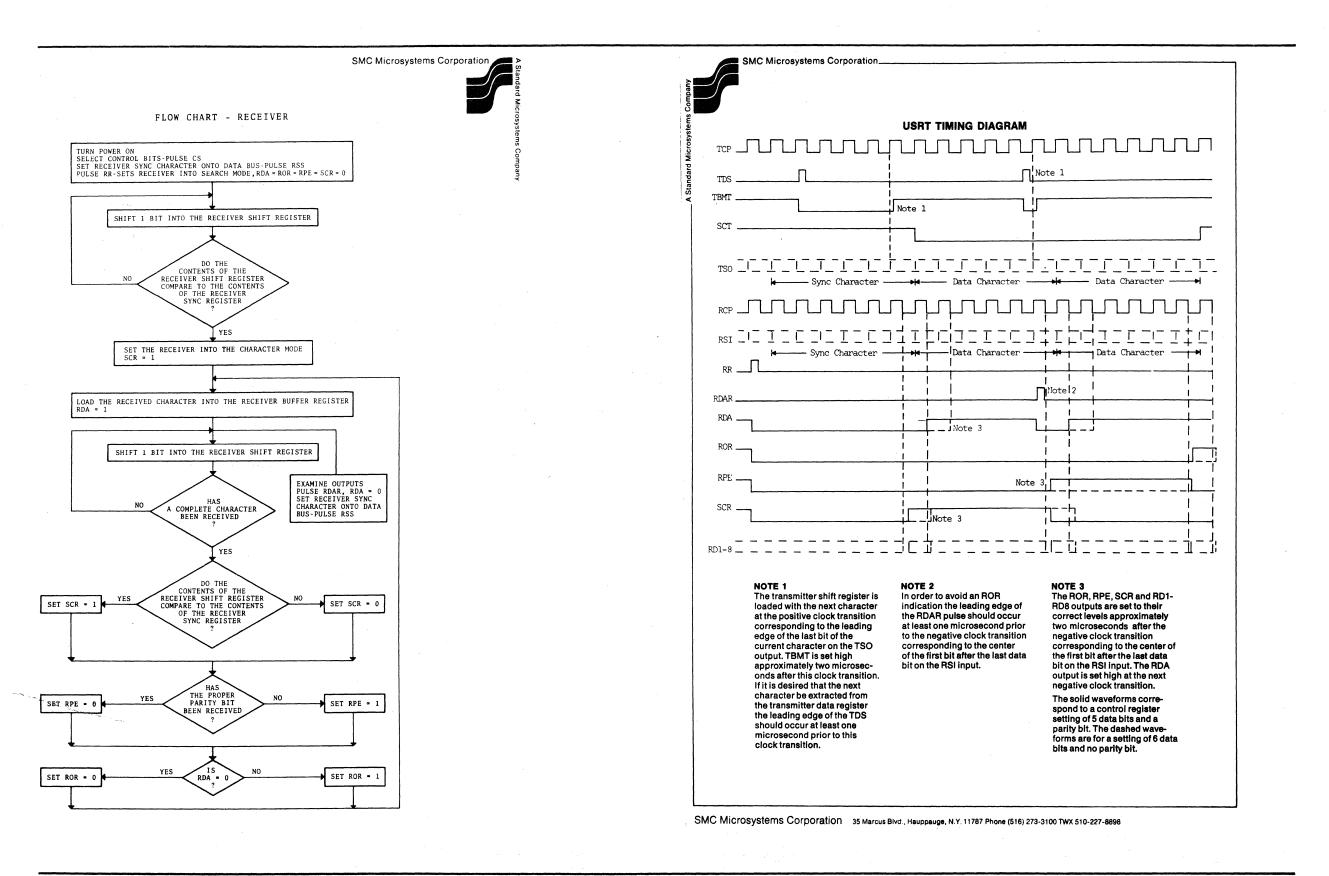

d) The USRT and Associated Logic: USRT A46 (COM 2601) operates in conjunction with devices A44, A45, A54, A31, A32, A23, A39, A24, A31 and A47. This logical subsystem performs all the transmitting and receiving functions of data between the disc drive and the AES-PLUS Text Editor.

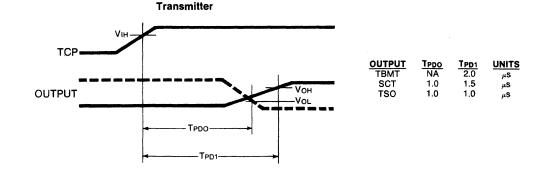

The transmitting rate of the USRT is derived from a 4 MHz crystal controlled clock oscillator, formed by inverters A56-E and A56-F, whose output is fed to flip-flop A54-A, where division by two occurs. The 2 MHz clock signal is then applied to counter A55, whose most significant output bit is inverted by A56-A and finally applied to the TCP (Transmitter Clock) input of the USRT. Data to be transmitted is fed to the USRT from the data buss and when the TSS (Transmitter Sync Strobe) input receives a high level issued by decoder A41, data is loaded into the transmitter sync register. At this moment in time, the transmitter sync register contains a header of zeroes, a flag character (DB) and data. Data transfer is inhibited until DB is transfered to the transmitter buffer register, this setting TDS. When TDS is set, data transfer is enabled. The flag character is immediately followed by a valid data byte, which is released serially from USRT serial output TSO (Transmitter Serial Output).

The data to be stored on the disk has to appear in the form of a modulated signal, usually in a dual frequency signal. This is achieved by using the three least significant bits of counter A55 and routing them to gate A31-A. Its output changes state at each count of 8 and is mixed with the USRT serial output at gate A7-B.

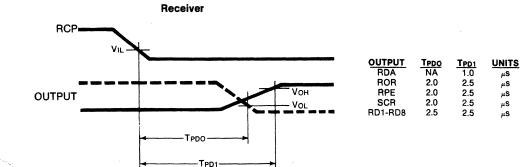

When the USRT is receiving data, the modulated data stream coming from the disc drive circuitry has first to be processed since it contains both the receiver clock signal and the data. This signal processing takes place at gate A23-B and A23-C, one-shot multivibrator A39 and flip-flop A32-B, where the clock signal and the data are separated. One-shot multivibrator A39 stretches the pulses coming from A23-B and feeds them to the RCP (Receiver Clock) input of the USRT. The combined receiver clock signal and the modulated data stream are applied to gate A23-C which issues the DATAS signal to the PRESET input of flip-flop A32-B. The output of A23-B also clocks A32-B and the resulting signal at its Q output is the valid serial data fed to the RSI (Receiver Serial Input) input of the USRT. When an entire character has been received, the RDA (Receiver Data Available) output flag goes high; the character is unloaded onto the data buss and then the RDAR resets the RDA to a lowlevel. The unloading of a character on the data buss is accomplished through tri-state multiplexers A44 and A45(74LS257), which are also used for disc drive status flag drivers.

e) The DMA (Direct Memory Access) Logic: The DMA circuit informs the CPU that data is to be exchanged between the disc and the video memory. The disc drive employs two DMA channels, one for the transmit function and one for the receive function of the USRT.

All disc activities are only allowed when the microprocessor has issued the disc activity flag. When this is so, the SECT EQ flip-flop Al2-B is enabled. As soon as the SECT EQ pulse is issued from comparator A37, the SECT EO F strobe from Al2-B goes high and is fed to gate A31-B which issues the DMA Request  $\emptyset$  (DRQ $\emptyset$ ) to the first channel of the DMA controller on the CPU board. The DMA Request is acknowledged by the DACK $\emptyset$  strobe arriving at inverter A27-D and then to gate A24-A, setting high its output which is then applied to the TDS (Transmitter Data Buffer Strobe) input of the USRT. Data is then loaded into the USRT data buffer for transmission to the disc and when the required number of bytes has been transferred, the TBMT output goes low and cancels the DMA Request. The ACTIV-F flag is reset when the next sector is encountered. In the Transmit mode, characters are loaded from the data bus into the USRT transmitter data buffer register. In this case, a character from the program memory is transferred to the USRT under the control of the DMA circuit chip on the CPU board. However, disc activities are allowed only when the CPU has set the disc activity flag (SET ACT F) via address decoder A41.

In the Receive mode, characters are retrieved from the disc sector. Once the Read function is established, the DMA cycle is initiated at the second channel (RDQ1 and DACK1) by the RDA (Receiver Data Available) output of the USRT and DMA acknowledgment is given at the RDAR (Receiver Data Available Reset) input of the USRT.

When a DMA cycle has terminated for a disc Read function, the DMA controller issues a TC (Terminal Count) flag, which appears at gate All-C and resets the ACTIV-F strobe of flip-flop Al2-A. Interrupt flip-flop A32-A is then set via gate A22-C and an interrupt flag is issued to the CPU. This flag is cleared later when the CPU reads the disc status.

# I/O Board Block Diagram

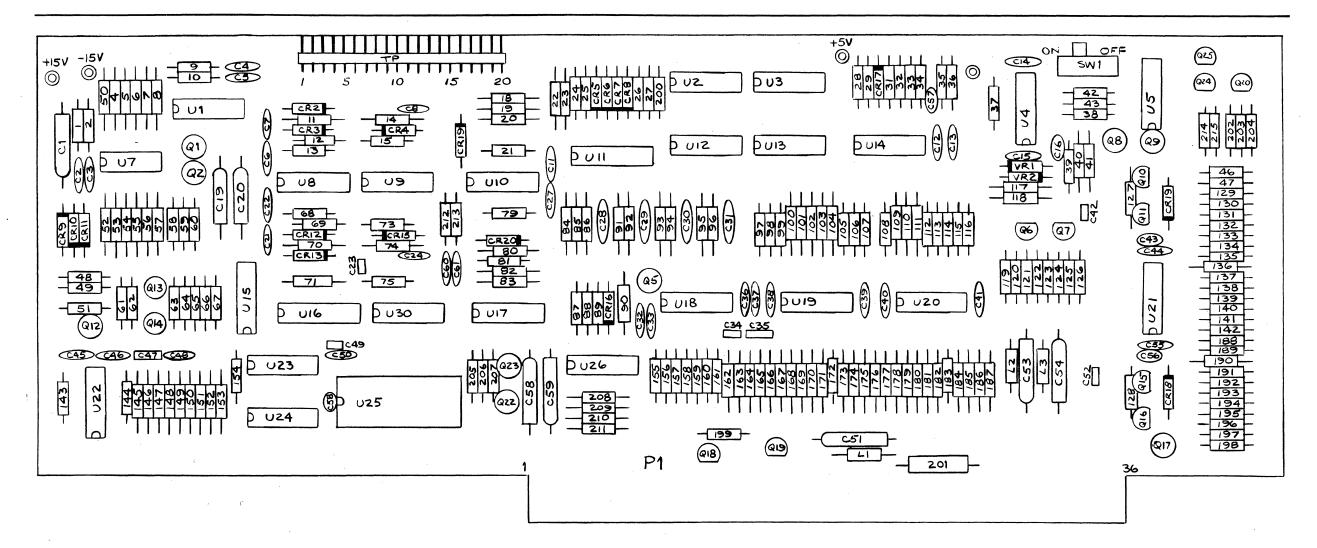

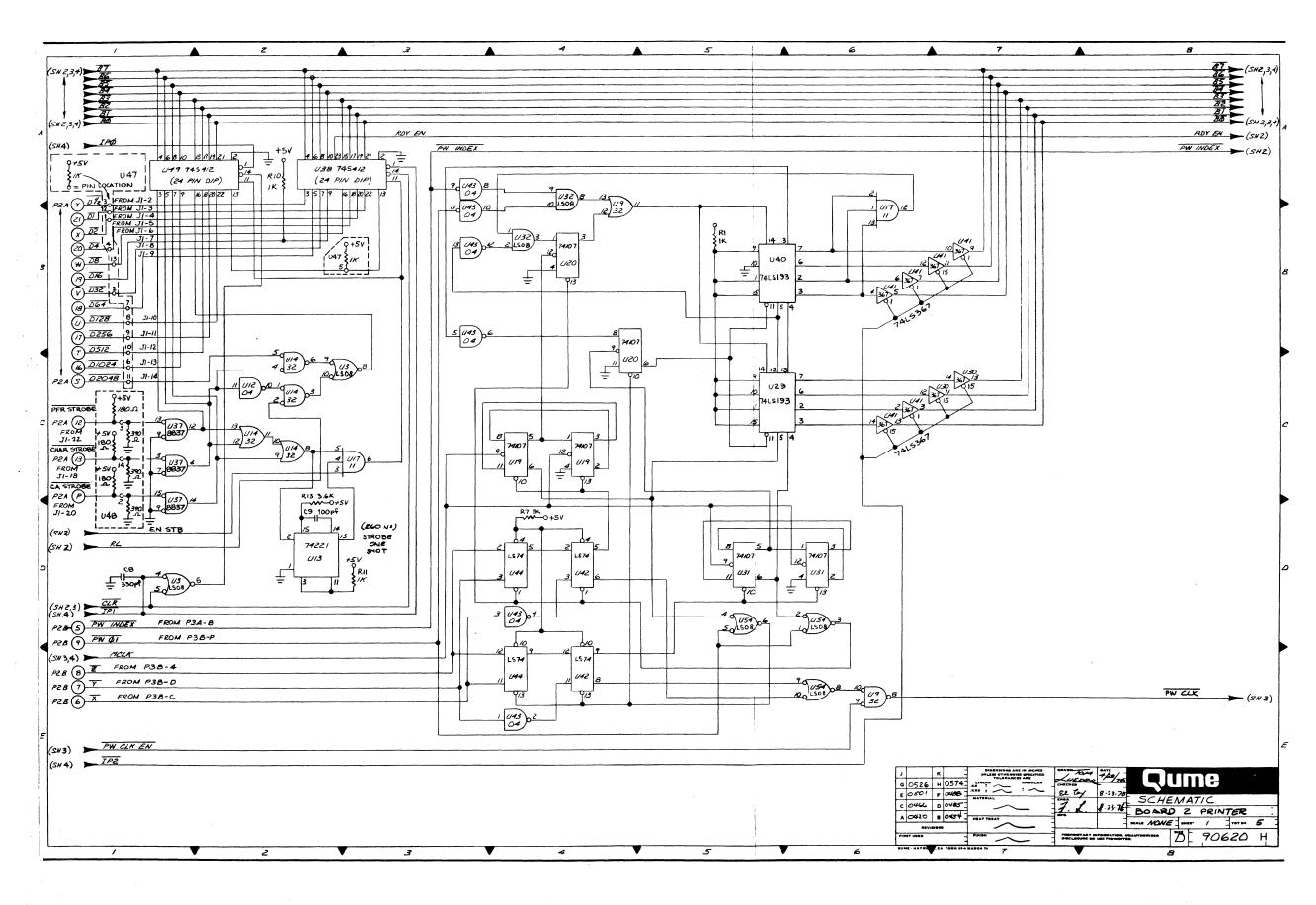

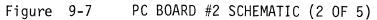

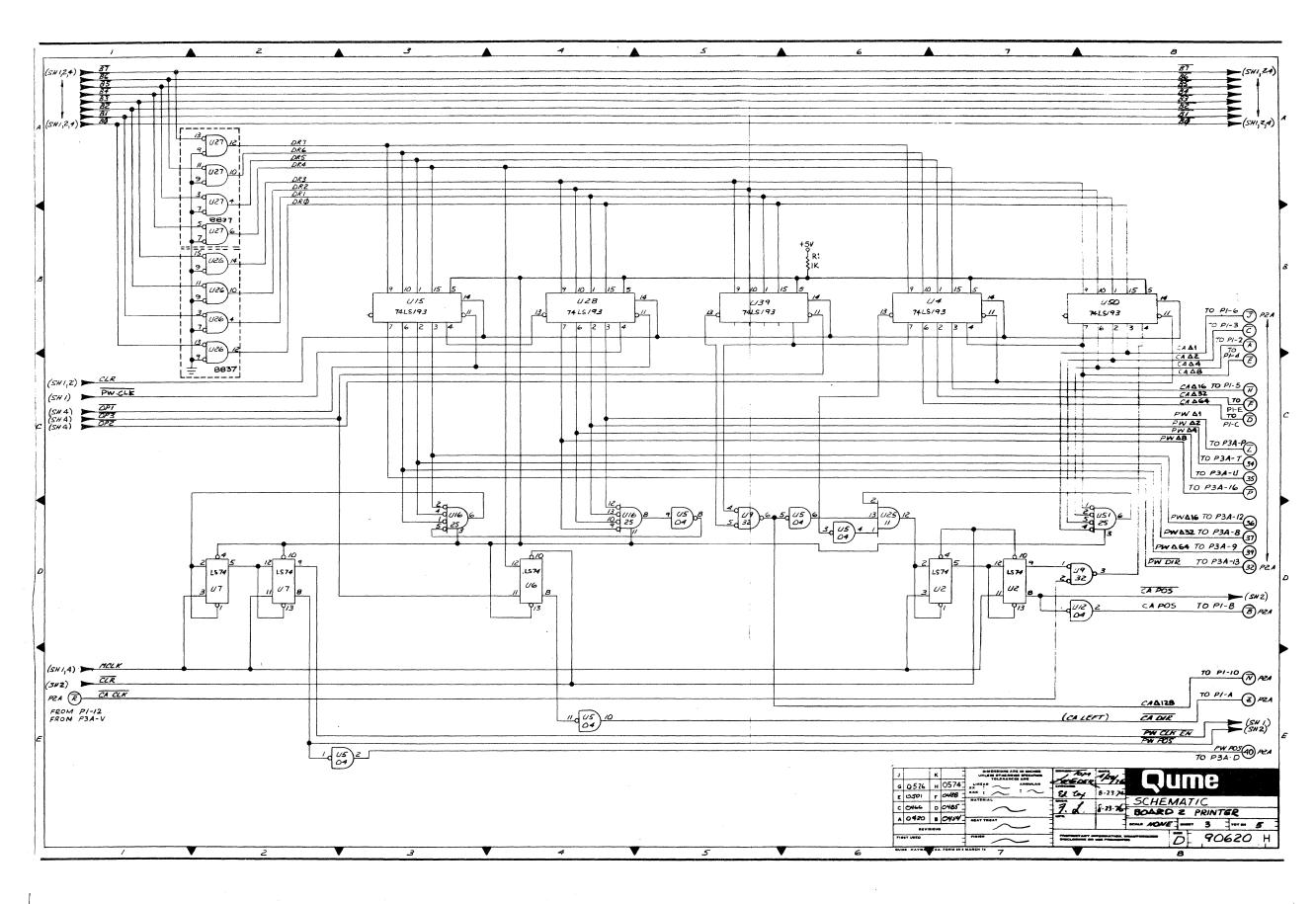

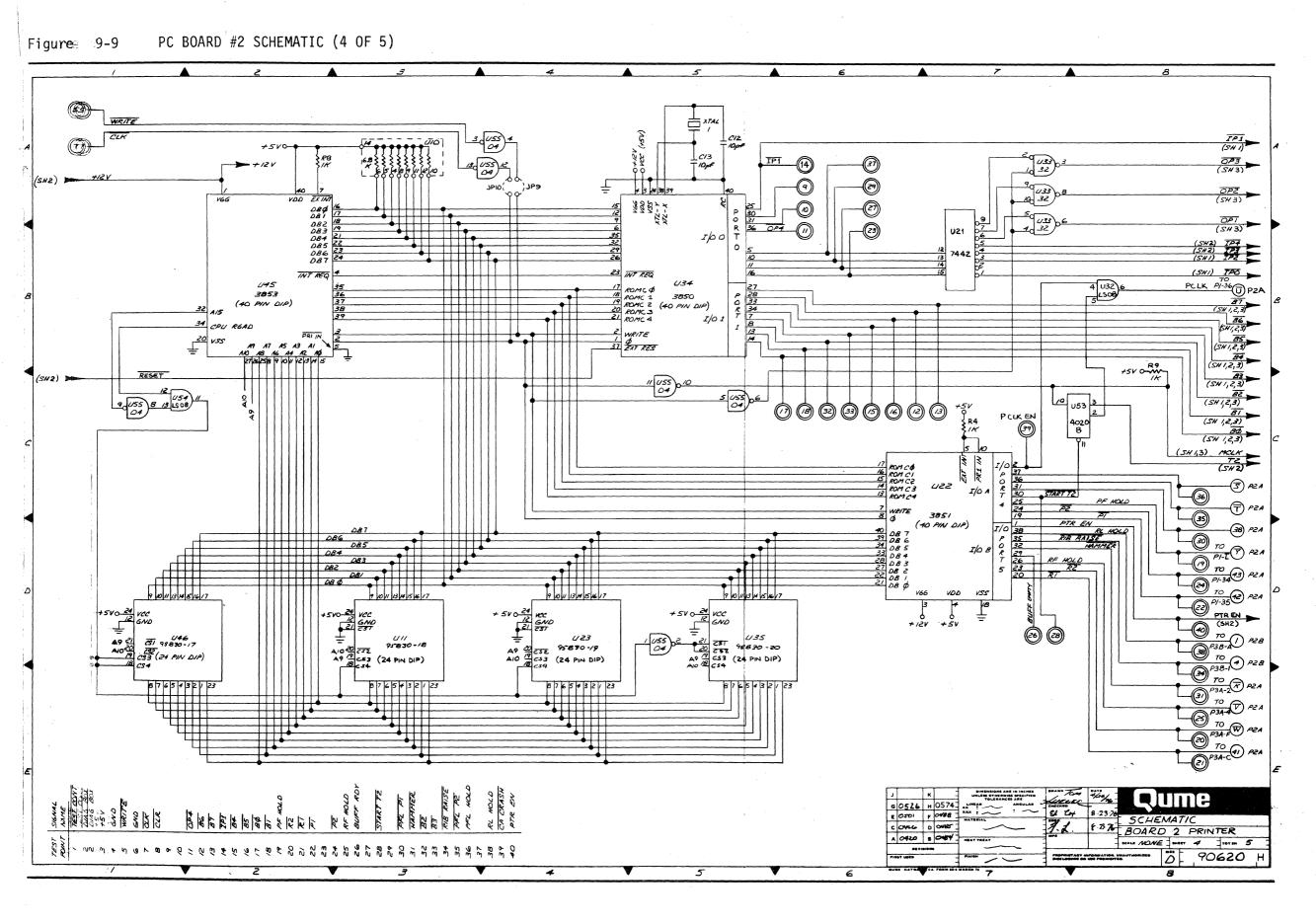

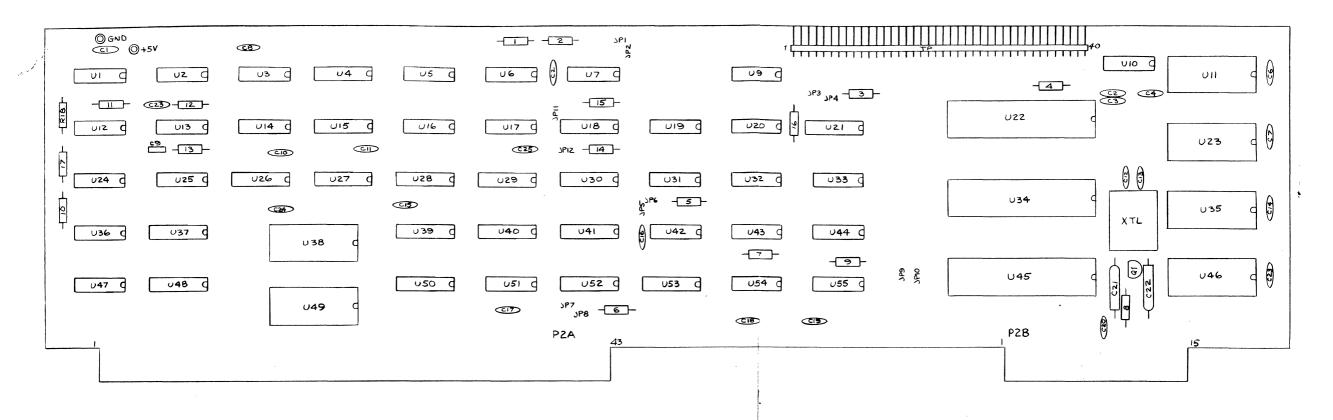

Input/Output Schematic Diagrams

Input/Output Schematic Diagrams

# Input/Output Schematic Diagrams

Input/Ouput Schematic Diagrams

Input/Output Schematic Diagrams

|                | 01 |                           |               |                     | 01 |                               |                   |

|----------------|----|---------------------------|---------------|---------------------|----|-------------------------------|-------------------|

|                | 1  | PCB Drilling              | C6-955-008901 |                     |    |                               | 1                 |

|                | 2  | PCB Ejector               | 252-0102      |                     | -  |                               |                   |

|                |    | 5                         |               | C13                 | Ţ  | Capacitor 220pf 5%            | 167-0100          |

| A56            | 1  | SN74S04N                  | 660-0145      | C9,10,11,12         | 4  | Capacitor .033uF 2%           | 162-0133          |

| A8,43,51       | 3  | SN7438N                   | 660-0129      | C2,5,6,14,17,49     | 6  | Capacitor 10uF 20V. Tag       | 164-0177          |

| A46            | 1  | COM 2601                  | 660-0142      | C20,22              | 2  | Capacitor 33uf 16V. Tag       | 164-0220          |

| A4,6           | 2  | SN7414N                   | 660-0162      | C1,7,8              | 3  | Capacitor 500pf               | 165-0207          |

| A17,25,33,41   | 4  | SN74LS138N                | 660-0192      | C15,18,21,23-48     | 29 | Capacitor .05uF               | 165-0251          |

| A26,36,40,53   | 4  | SN7406N                   | 660-0202      | 50                  |    |                               |                   |

| A23            | 1  | SN74LS00N                 | 660-0208      | C3,4,16,19          | 4  | Capacitor .01uF               | 165-0263          |

| All,22,47      | 3  | SN74LS02N                 | 660-0209      |                     |    |                               |                   |

| A18,27         | 2  | SN74LS04N                 | 660-0210      |                     |    |                               |                   |

| Al,24          | 2  | SN74LS08N                 | 660-0211      |                     | _  |                               |                   |

| A31            | 1  | SN74LS20N                 | 660-0214      | R4                  | 1  | Resistor 100 OHMS 1/4W 5%     | 402-0101          |

| A2,10,12,20,21 | 7  | SN74LS74AN                | 660-0219      | R3                  | 1  | Resistor 1.2K OHM 1/4W 5%     | 402-0122          |

| 32,54          | •  |                           | 000 0219      | R16-20              | 5  | Resistor 2.2K OHMS 1/4W 5%    | 402-0222          |

| A39            | 1  | SN74121N                  | 660-0221      | R14,15              | 2  | Resistor 270 OHMS 1/4W 5%     | 402-0271          |

| Al3,14,19      | 3  | SN74LS123N                | 660-0222      | R1,2,5-8            | 6  | Resistor 8.2K OHMS 1/4W 5%    | 402-0822          |

| A5,29          | 2  | SN74LS157N                | 660-0225      |                     |    |                               |                   |

| A55            | 1  | SN74LS161AN               | 660-0227      | R12                 | 1  | Resistor 332K OHMS 1/4W 1%    | 481-0651          |

| A35            | 1  | SN74LS174N                | 660-0228      | R9,10               | 2  | Resistor 274K OHMS 1/4W 1%    | 481-0730          |

| A44,45         | 2  | SN74LS257AN               | 660-0232      | R13                 | 1  | Resistor 33.2K OHMS 1/4W 1%   | 481-0551          |

| A34,38,52      | 3  | SN74LS273N                | 660-0233      | Rll                 | 1  | Resistor 1.65M OHM $1/4W$ 1%  | 481-0734          |

| A9,42          | 2  | SN74365AN                 | 660-0238      |                     |    |                               |                   |

| A3             | 1  | SN74LS374N                | 660-0240      |                     |    |                               |                   |

| A49            | 1  | DM81LS95N                 | 660-0241      |                     |    |                               |                   |

| A37            | ī  | DM8160N                   | 660-0255      |                     |    |                               |                   |

| A28,30         | 2  | SN74LS393N                | 660-0256      |                     |    |                               |                   |

| A16            | 1  | NE558                     | 660-0257      | KB                  | 1  | Connector PCB 20 Pins         | 290-0121          |

| AIU            | Ŧ  | NESSO                     | 000 0237      | J3                  | 1  | Connector PCB RT.Ang. 34 Pins | 2 <b>90-</b> 0122 |

|                |    |                           |               | J4                  | 1  | Connector PCB 34 Pins         | 290-0123          |

| A7,50          | 2  | Resistor Pack 314E221331  | 485-0110      |                     |    |                               |                   |

| A15            | 1  | Resistor Pack 898-1-R2.2K | 485-0111      |                     |    |                               |                   |

| AL3            | T  | RESISCOL PACK 090-1-RZ.ZK | 405-0111      |                     |    |                               |                   |

|                |    |                           |               | A39, A56            | 2  | Socket DIL. 14 Pins           | 698-0102          |

|                |    |                           |               | A13,14,16,19        | 4  | Socket DIL. 16 Pins           | 698-0103          |

|                |    |                           |               | A15,14,10,19<br>A46 | 1  | Socket DIL. 40 Pins           | 698-0118          |

|                |    |                           |               | A-10                | Ŧ  | DOLLET DITT. 40 LIUD          | 070 0110          |

|                |    |                           |               | Yl                  | 1  | Cystal 4.000 MHz              | 490-0112          |

|                |    |                           |               |                     |    |                               |                   |

Input/Output Parts List

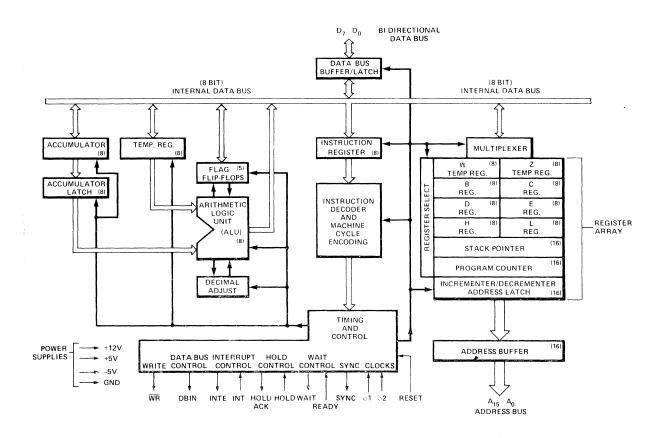

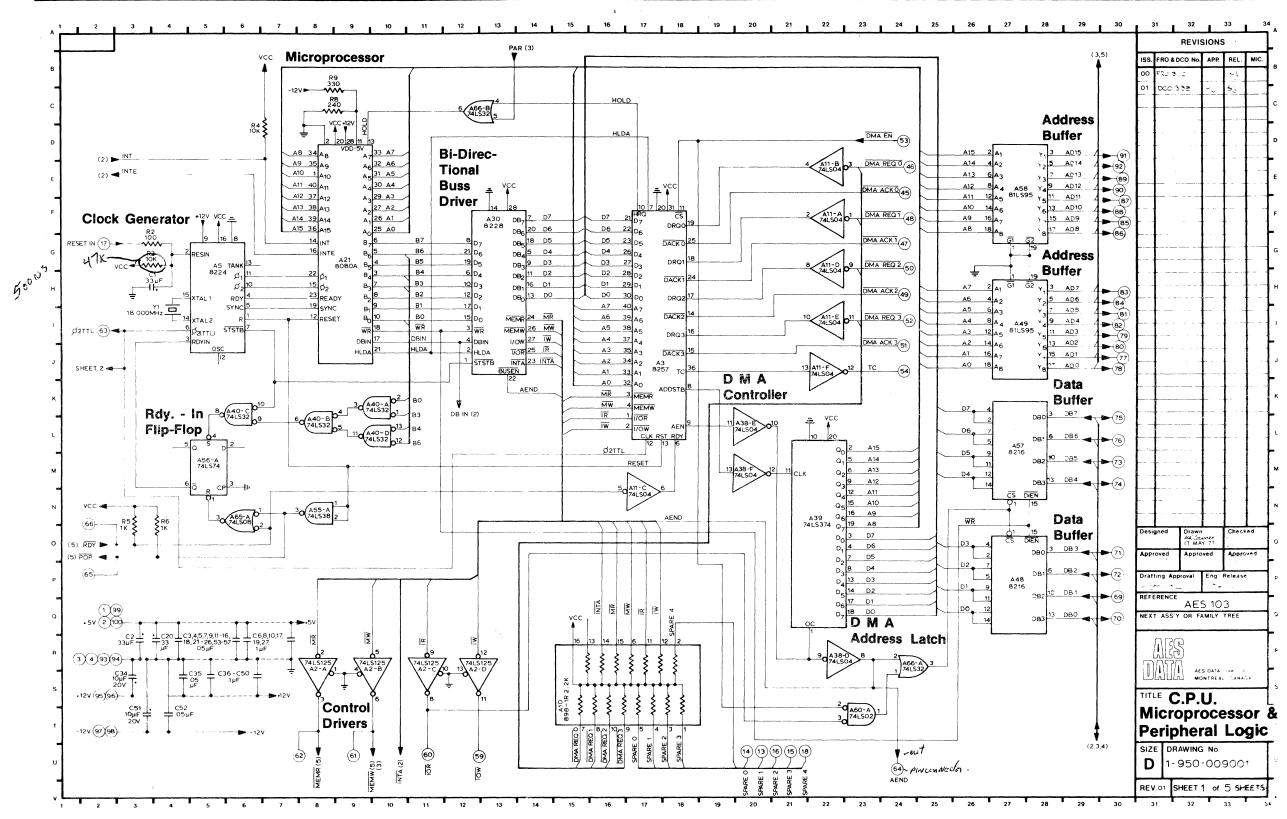

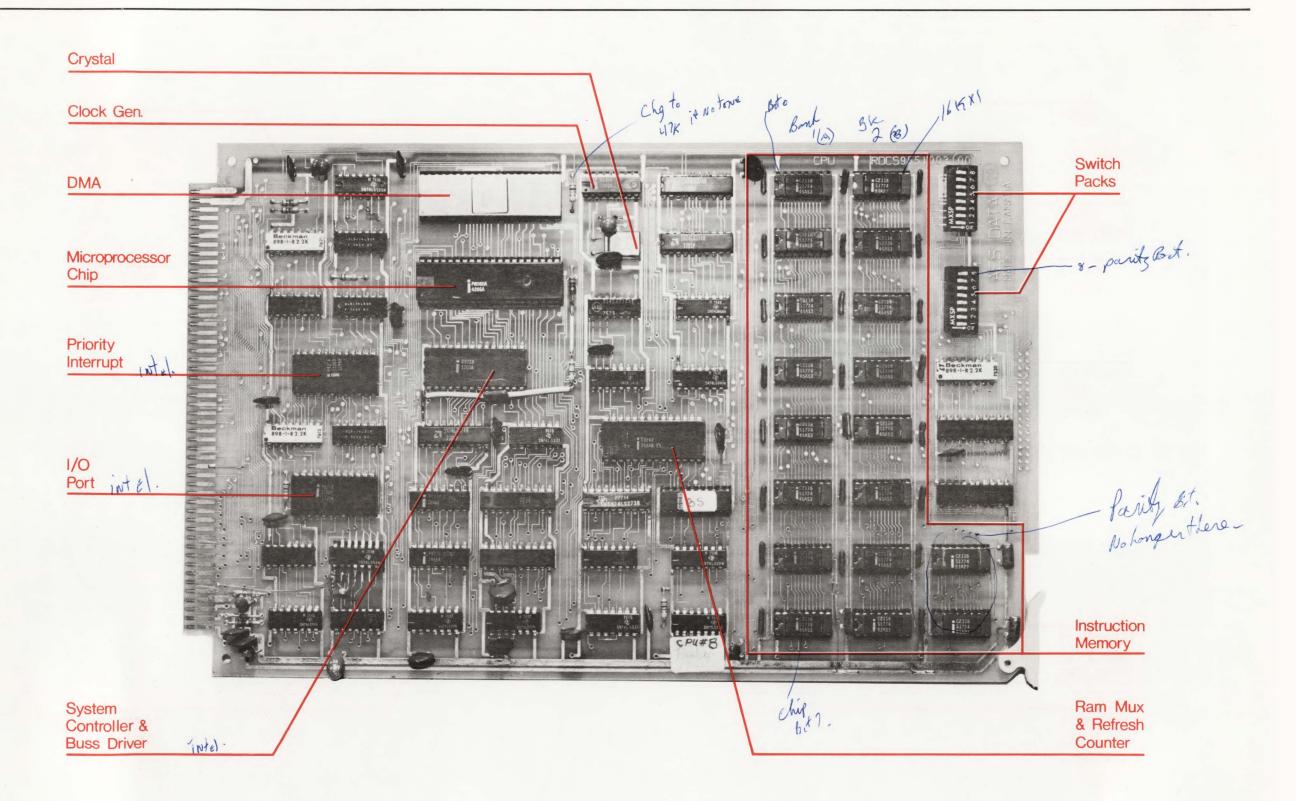

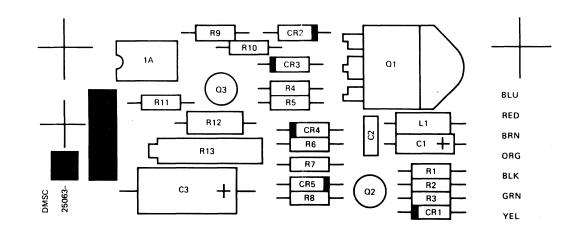

## CPU BOARD (D1-950-0090-01-00)

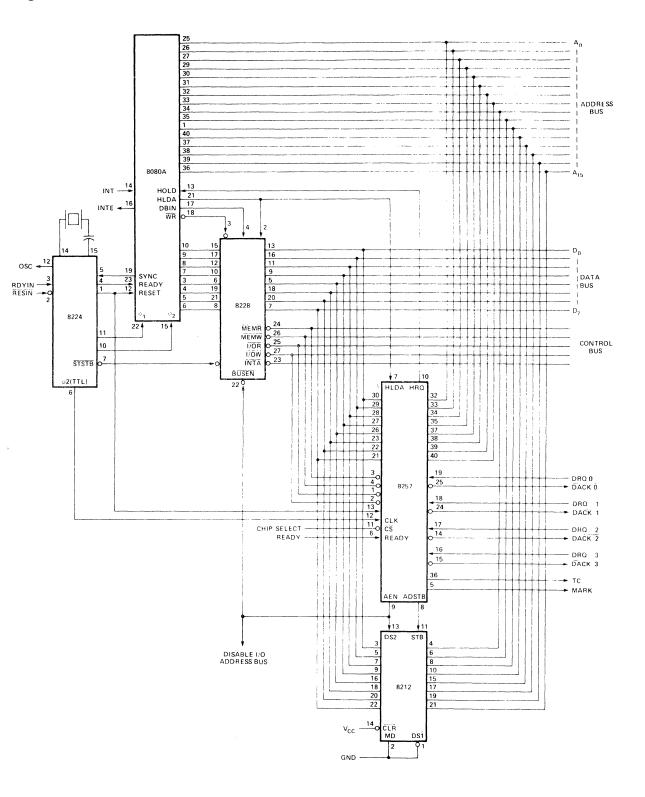

## Figure 1 The Microprocessor

### 1. INTRODUCTION

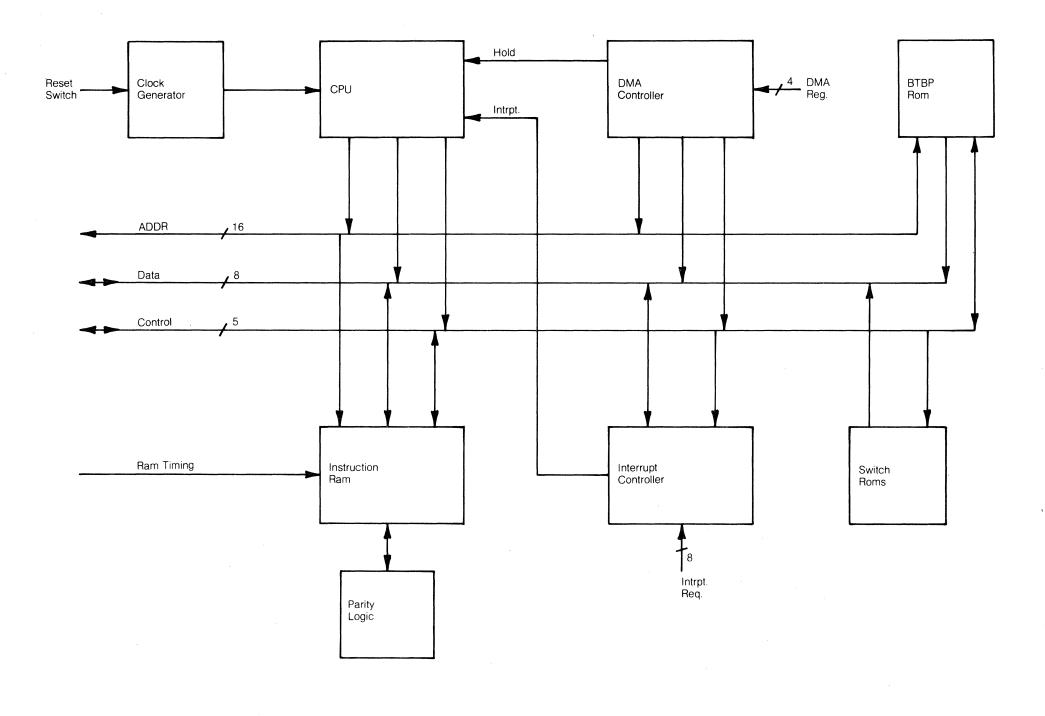

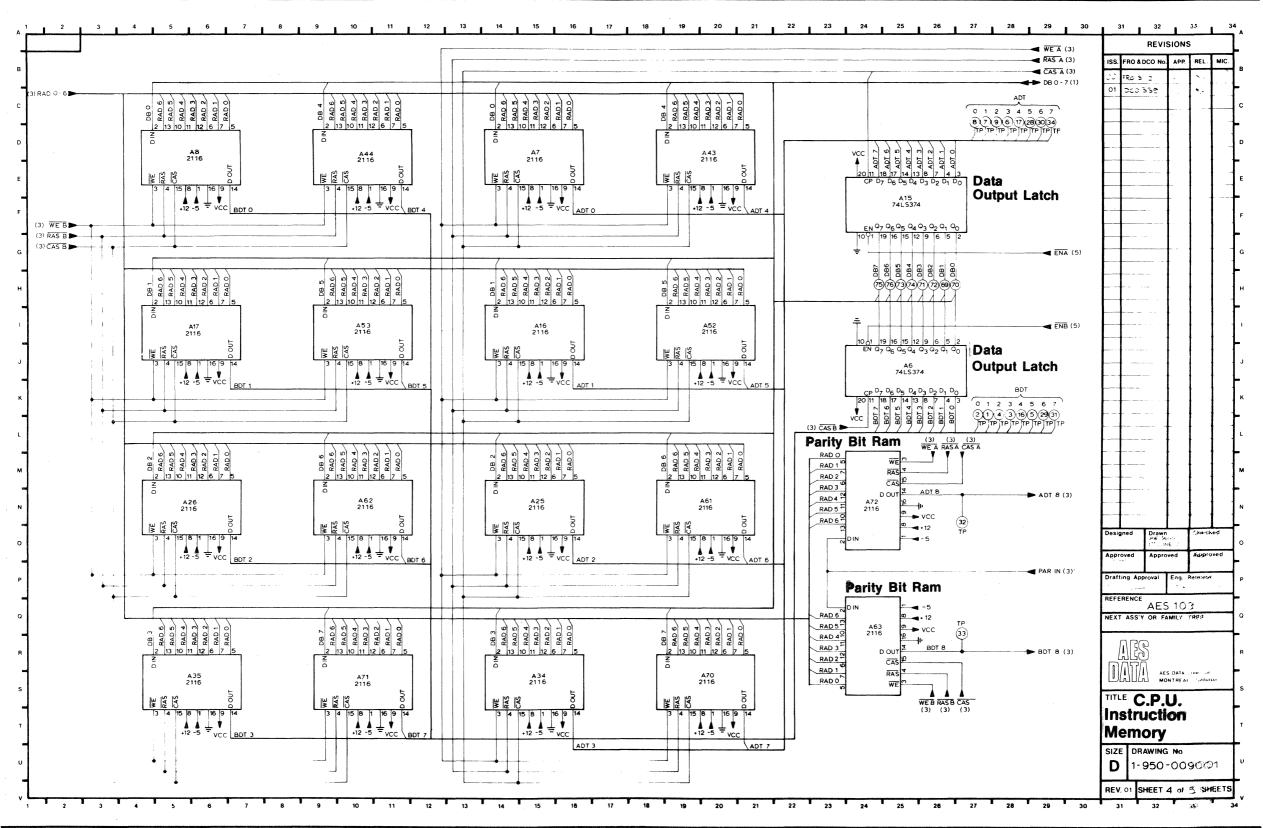

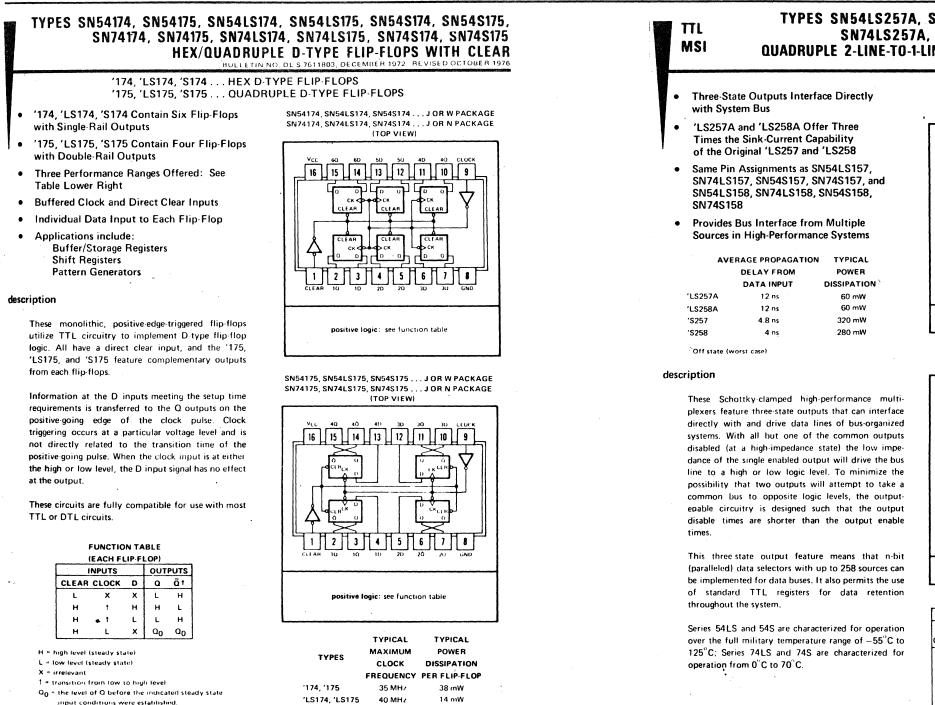

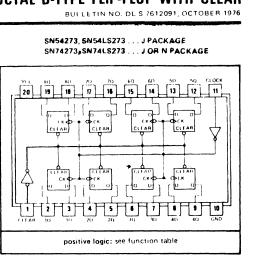

The Central Processing Unit of the AES-PLUS Text Editor is contained on a single printed circuit board. It includes an integrated microprocessor CPU (INTEL 8080), 32K of Instruction RAM (random access memory) small Bootstrap ROM (read-only memory), one 8-level priority interrupt controller and a 4-channel DMA (direct memory access) controller. Provision has been made for instruction bit parity check, in case of memory failure and also two 8 D.I.P. switch packs to determine the configuration of the system.

The board consists of the following subgroups:

- The 8080 Microprocessor

- The Interrupt Logic

- The DMA Controller

- The Instruction Memory

- The Memory Synchronization Circuit

- The Address Decoder

- The Program Switches

- The Parity Check Logic

#### 2. THE MICROPROCESSOR

The basic processor consists of an Intel 8080A Microprocessor chip, (see FIG.1) associated timing circuit and a buss driver. The 8080A is a complete 8-bit parallel central processing unit supplying a 16-line address buss, a separate 8-line bi-directional data buss and all the control signals to interface with the memory and Input/Output peripherals.

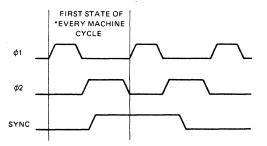

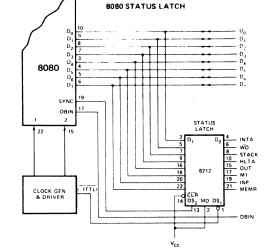

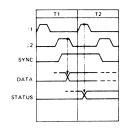

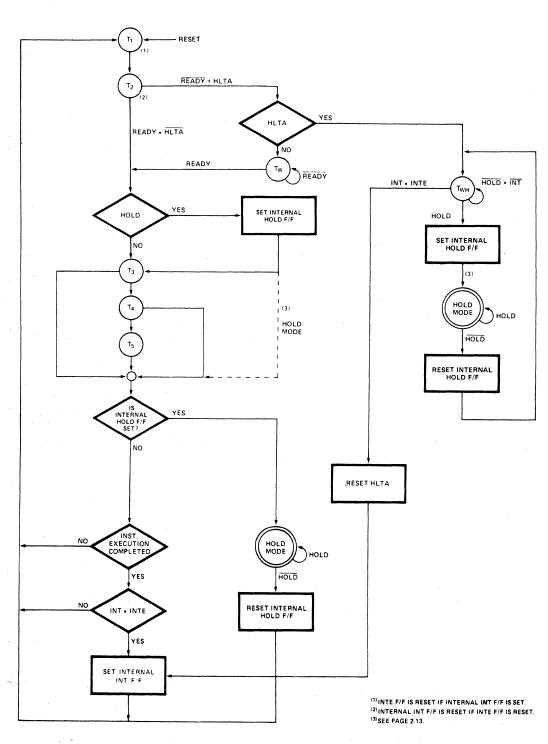

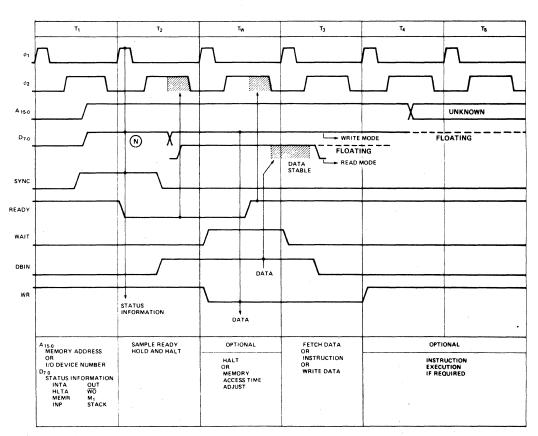

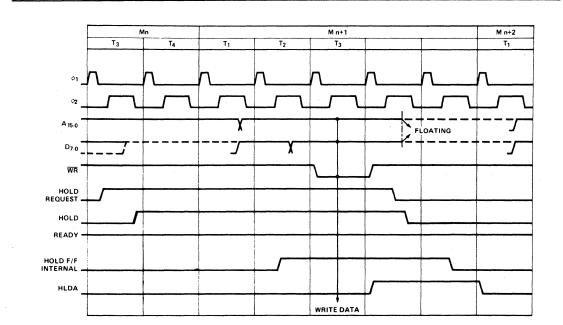

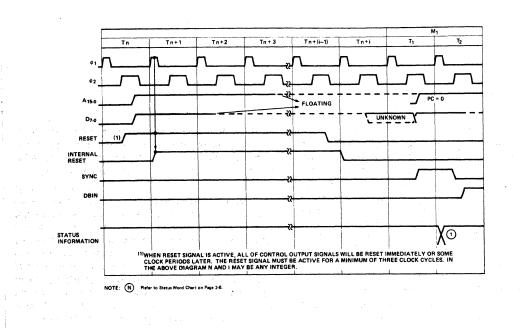

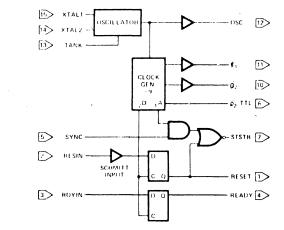

The 8080A Microprocessor chip is interfaced with Clock Generator A5-(8224) and a bi-directional data buss driver (8228) to form the CPU module. The clock generator is a single chip device, controlled by an 18.0 MHz crystal, supplying the two-phase clock signals  $\emptyset$ 1 and  $\emptyset$ 2 a power-up RESET, a READY flag and advance status strobe (STSTB). The READY flag is a product of the RDY IN in sync with phase  $\emptyset$ 2 while the STSTB strobe is formed by the SYNC strobe, issued by A30 and phase  $\emptyset$ 1 of the clock.

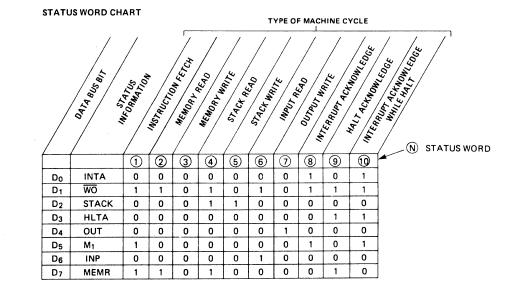

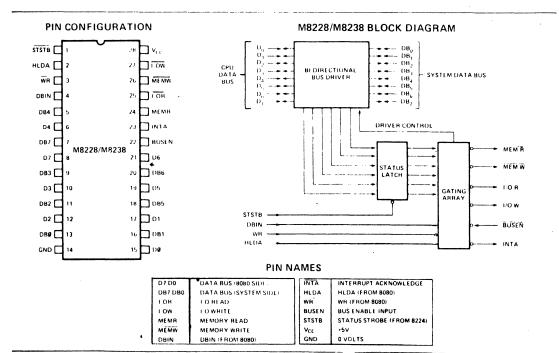

The bi-directional buss driver and system controller A30 (8228) generate all the signals required to interface with the Random Access Memory and I/O. The 8228 accepts the data buss from the 808 Microprocessor and distributes it to the system. It also generates strobe signals MEMR, MEMW, I/OR, I/OW and INT ACK.

## Figure 2 C.P.U. Module

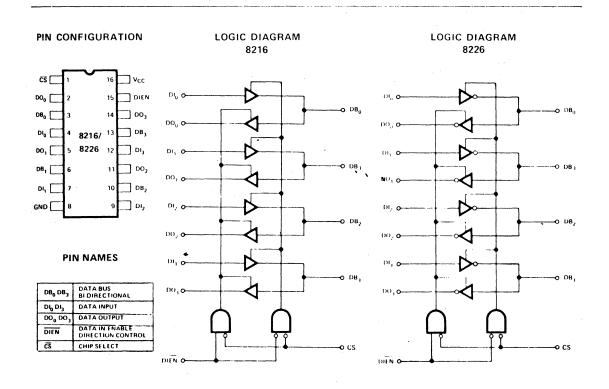

Figure 2 is representative of what constitutes the basic CPU module. The basic CPU Module communicates with the instruction memory, the DMA controller, the interrupt controller and bootstrap ROM via a 16-bit address buss, an 8-bit data buss and 5 control lines. The 16-bit address lines are buffered through A49 and A58 (81LS95) and brought to the memory logic. The eight data bits issued by A30 are buffered by drivers A57 and A48 (8216).

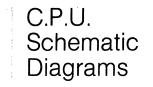

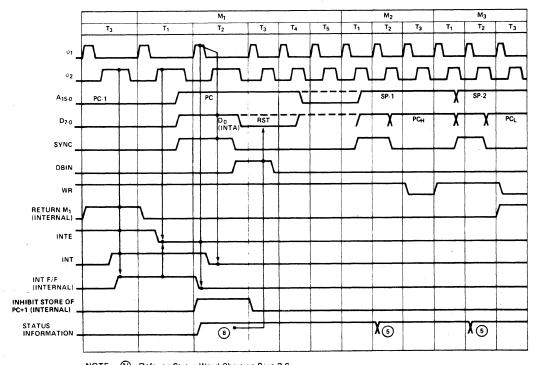

### 3. THE INTERRUPT LOGIC

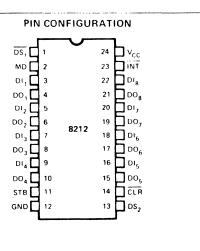

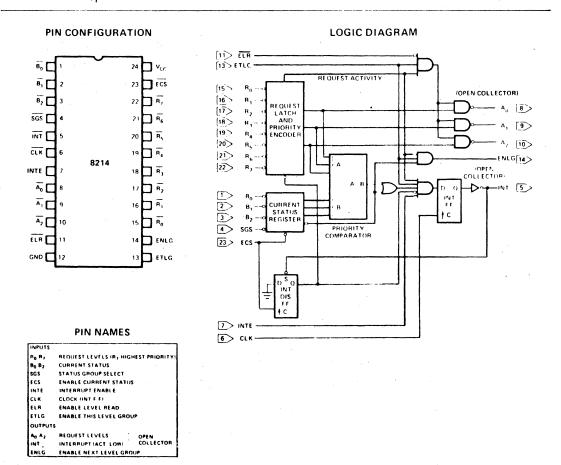

The Interrupt Logic consists of devices A28(8214), being an integrated priority interrupt control unit, and A46 (8212) which is an eight bit latch with tri-state output buffers. Eight interrupt requests are applied to A28 for the timer, the printer, disk, keyboard, option 1 and option 2, COM1 and COM2. These interrupt flags are encoded and compared to the contents of a status register, fed by bits DBØ to DB3 from the data buss. An interrupt is then issued along with vector information to I/O port A46. The Interrupt Controller is clocked by the Ø2TTL signal, issued by A5 and enabled by INTE (Interrupt Enable) coming from the microprocessor.

I/O port A46 accepts the three vector bits at its DI4, DI5 and DI6 inputs and the interrupt flag. Unloading data on the data buss is accomplished by the INTA (Interrupt Acknowledge) and DBIN strobes. The interrupt flag is then brought to the 8080A.

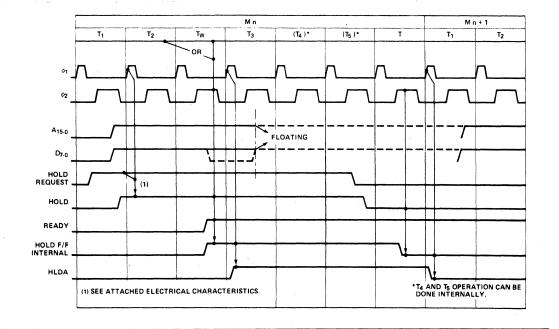

#### 4. THE DMA (DIRECT MEMORY ACCESS) CONTROLLER

Figure 3 C.P.U. Module With DMA

This subgroup consists of programmable DMA controller chip A3 (8257) and octal D-type latch A39(74LS374) (see FIG 3).

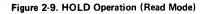

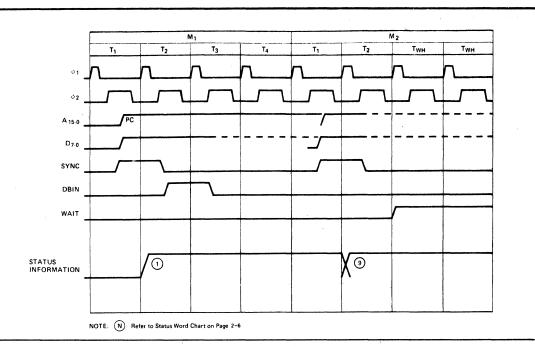

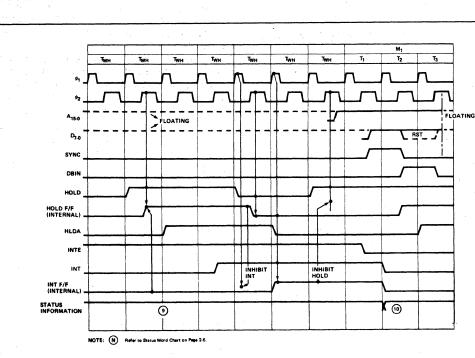

The DMA Controller generates a 16-bit address to the memory during the transfer of data from the memory to the disc storage media. When an I/O device requests the DMA, a priority selection occurs and a HOLD strobe is issued to the Microprocessor which responds with a HOLD ACK strobe. DMA chip A3 supplies four request channels, two of which are used for the disc Read and Write functions while the two others may be used for later expansion.

The DMA request appears in the form of a strobe signal at the DRQ  $\emptyset$  input of a channel and the request is then acknowledged by the return of a DACK strobe to the I/O. The 16-bit address is formed by the DMA chip, which generates the 8 least significant bits and 3-state octal latch A39, which generates the 8 most significant bits.

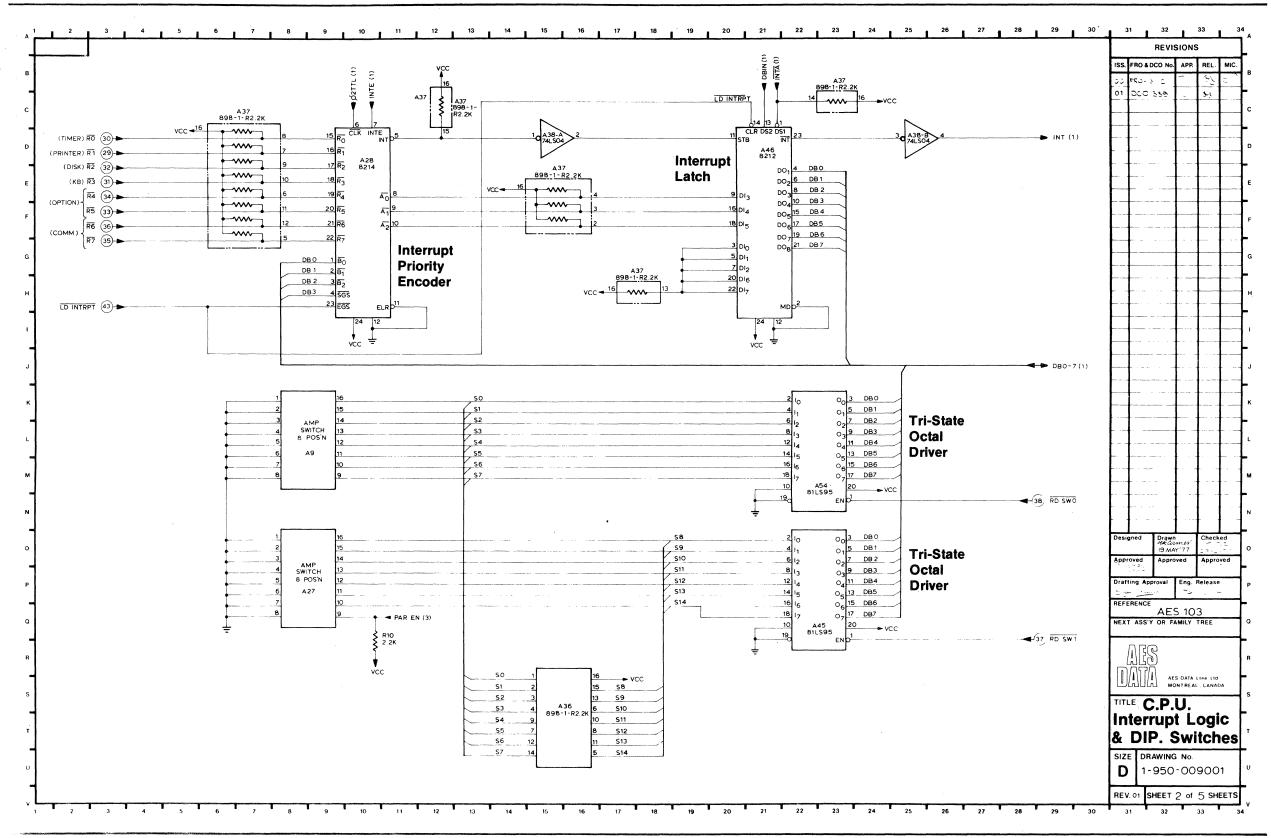

#### THE INSTRUCTION MEMORY

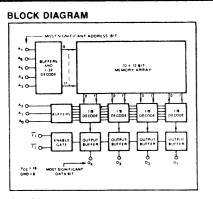

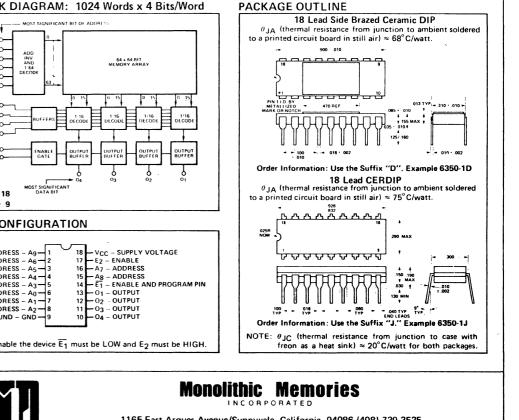

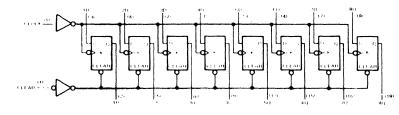

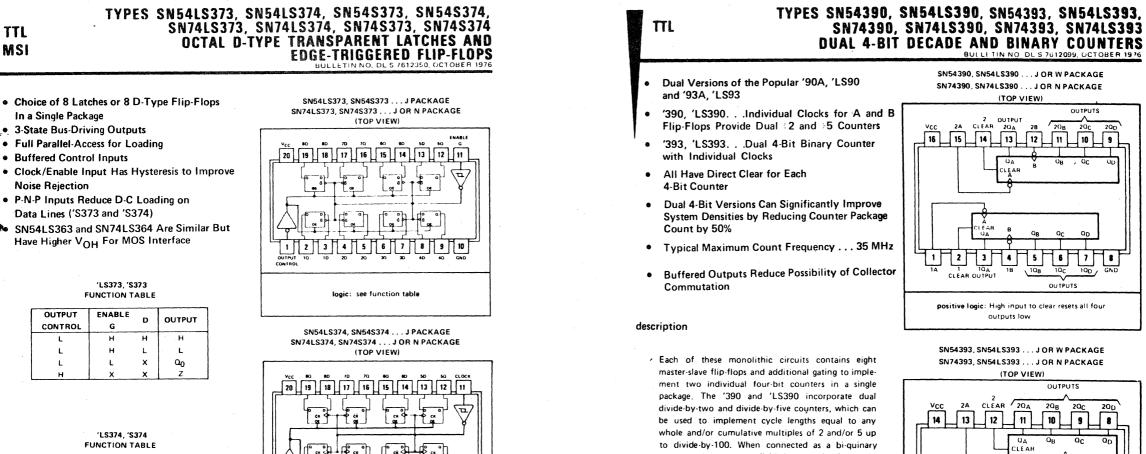

This memory has a capacity of  $32K \ge 9$  bits and utilizes 16K RAM devices. The memory is accessed through 16 address lines, issued by the microprocessor, and unloads 8-bit instruction bytes onto the data buss. The ninth bit is used internally for parity checking (error detection). A 512  $\ge$  8-bit instruction ROM (A51-74LS472) contains program loading instructions for Bootstrapping.

The 16-bit address buss accesses the memory via latches A50 (74LS273) and A59 (74LS174), both clocked by the RAS B signal.

When the AES-PLUS Text Editor is first turned on, memory instructions have to be loaded from a program diskette into the RAM. This is accomplished by a Bootstrap Flag issued by quadruple flip-flop Al2 on the video board. This flag is brought to OR gate A67-C whose output is fed to decoder A32(7442). The EN ROM signal is then issued to ROM A51, which in turn unloads instruction bytes onto the data buss. After the program is loaded into the RAM, address decoder A17 on the I/O board issues a CLR BTSP (clear bootstrap) strobe to quadruple flip-flop Al2.

Henceforth, the Microprocessor has access to the 32K RAM. The 16 address bytes are then brought to address multiplexer and refresh counter chip A41(3242) which distributes addresses to the RAM chips. Memory controller A41 contains its own refresh address counter, which is enabled by BUS REFR issued by octal latch A65 of the video board. Each RAM device is controlled by two addressing strobes called RAS\* (Row Address Strobe) and CAS \*(Column Address Strobe) also issued by the video board. These two strobes allow the loading of the row and column addresses in a sequential manner. The WE strobe (Write Enable) goes low during program loading.

Instruction bytes are, thereafter, loaded onto the data buss via tri-state latches A6 and Al5(74LS374).

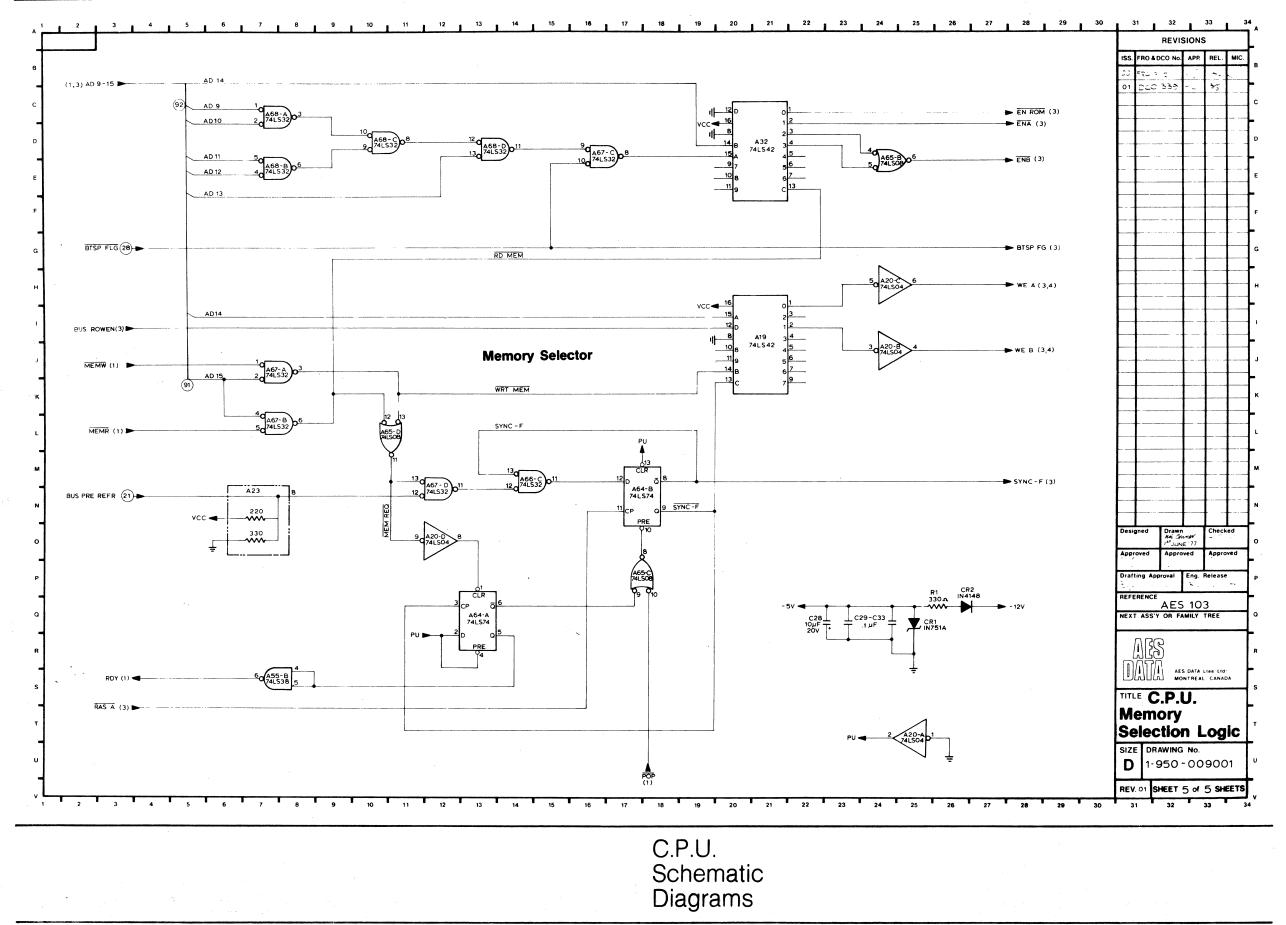

### 6. MEMORY SYNCHRONIZATION

This circuit consists of devices A67, A65, A55, A66 and A64. Its purpose is to control memory request from the Microprocessor between refresh cycles.

A memory request is started by bit 15 (when low) which enables gate A67-A in unison with a MEMR or MEMW strobe. If a memory PRE REFR strobe has not appeared at gate A-57D, the request is brought to flip-flop A64B which sets the SYNC-F strobe at the next edge of the RAS\* signal. From this point on, the memory is read until the next edge of the RAS\* signal clears the SYNC-F and sets memory flip-flop A64-A which in turn issues the MEM RDY signal on the data bus. When bit 15 of the address buss goes high again, flip-flop A64-A is cleared and the MEM RDY signal is removed.

#### 7. THE ADDRESS DECODER

Decoder A19 is a 4-to-10 line decoder (74LS42) and accepts the SYNC-F, the WRT MEM, the BUS ROWEN and address bit 14. The decoded signals produce a Write pulse to the appropriate bank of RAM chips (WEA or WEB). Decoder A32 accepts address bit 14 and decoded bits 9, 10, 11, 12 and 13 and issues an enabling strobe (ENA or ENB) to either banks of RAM chips or the EN ROM strobe to the bootstrap ROM.

#### 8. THE PROGRAM SWITCHES

4 5

6 Bootstrap Loader Enable

7 Parity Enable

These are two packages of 8 D.I.P switches followed by tri-state buss drivers A45 and A54(81LS95). The Microprocessor reads the switch status when strobes RD SW1 or RD SWØ are issued. The programm

# SWITCH BLOCK Ø

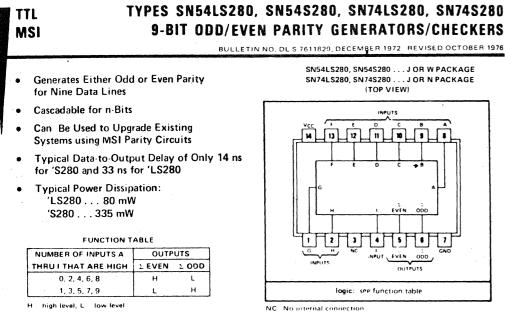

9. THE PARITY CHECK LOGIC

This circuit consists of devices A33, A72, A63, A69, A60, A56-B and A55-D. Its purpose is to constantly verify the validity of data read from the memory. The heart of the circuit consists of a 9-bit odd/even parity generator/checker, device A33(74LS280), and accepts at its input the 8-bit data buss. When data is written into the memory, A33 generates a parity bit (even parity) into 9th RAM chip A72, if enabled and addressed. When data is read from the memory, the parity is also read from A72 and is applied to parity chip A33 via a multiplexer (for Parity A or B) formed by gates A60-C, A60-B and A66-D. The EVEN output of the parity chip is inverted by A55-C and brought to flip-flop A56-B, which sets its Q output if an error is detected. Flip-flop A 56-B is clocked by PAR CLK issued by A69-B. The Q output is fed to OR gate A66-B. A detected error will force a HOLD request on the Microprocessor. The request will maintain the Microprocessor in a halt mode until the system is reset. A L.E.D on the front panel of the Text Editor turns on when the system is halted.

C.P.U. Board Block Diagram

<u>\_\_\_\_</u>

-

C.P.U. Schematic Diagrams

~

Schematic

Diagrams

\_\_\_\_\_

C.P.U. Parts List

|                   | 01  |                 |               |                   | 01  | •                          |          |

|-------------------|-----|-----------------|---------------|-------------------|-----|----------------------------|----------|

|                   | 1   | P.C.B. Drilling | C6-955-009001 |                   |     |                            |          |

|                   | 2   | PCB Extractor   | 252-0102      | A23               | 1   | Res. Pack 314E221331       | 485-0110 |

|                   |     |                 |               | A10,36,37         | 3   | Res. Pack 898-1-R2.2K      | 485-0111 |

| 47,8,16,17,25     | 18  | Dynamic Ram     | A6-937-004801 | A9, 27            | 2   | Switch Pack 8 Pos'n        | 533-0110 |

| 26,34,35,43,44    |     | 1               |               |                   |     |                            | 1        |

| 52,53,61-63,70-72 |     |                 |               | CR2               | 1   | Diode IN4148               | 601-0104 |

| A60               | 1   | SN74LS02N       | 660-0209      | CR1               | 1   | Diode IN751A               | 602-0104 |

| A11,20,38         | 3   | SN74LS04N       | 660-0210      | ·                 |     | ,<br>,                     |          |

| A65               | 1   | SN74LS08N       | 660-0211      |                   |     |                            |          |

| A40,66,67,68      | 4   | SN74LS32N       | 660–0215      |                   |     |                            |          |

| A55               | 1   | SN74LS38N       | 660-0216      | C28,34,51         | 3   | Capacitor, 10uF, 20V. Tag. | 164-0177 |

| A19,32            | 2   | SN74LS42N       | 660-0217      | C1,2,20           | 3   | Capacitor, 33uF, 16V. Tag. | 164-0220 |

| 56,64,69          | 3   | SN74LS74AN      | 660-0219      | C3-5, 7,9,11-16   | 20  | Capacitor, .05uF           | 165-0251 |

| 42                | 1   | SN74LS125N      | 660–0223      | 18, 21-26, 52,35  |     | -                          |          |

| 459               | 1   | SN74LS174N      | 660–0228      | C6, 8, 10, 17, 19 | 26  | Capacitor, .luF            | 165-0347 |

| 450               | 1   | SN74LS273N      | 660–0233      | 27,29-33,36-50    |     |                            |          |

| 433               | 1   | SN74LS280N      | 660–0235      |                   |     |                            |          |

| 424               | 1   | SN74366AN       | 660–0239      |                   |     |                            |          |

| 46,15,39          | 3   | SN74LS374N      | 660–0240      | R2                | - 1 | Resistor 100 OHMS 1/4W, 5% | 402-0101 |

| 45,49,54,58       | 4   | DM 81LS95N      | 660-0241      | R5,6              | 2   | " 1K OHM 1/4W, 5%          | 402-0102 |

| <b>\</b> 21       | 1   | 8080 <b>–</b> A | 660–0243      | R3,4              | 2   | " 10K OHMS, 1/4W, 5%       | 402-0103 |

| 446               | 1   | 8212            | 660–0244      | R7,10             | 2   | " 2.2K OHMS 1/4W, 5%       | 402-0222 |

| A28               | 1   | 8214            | 660–0245      | R8                | 1   | " 240 OHMS, 1/4W, 5%       | 402-0241 |

| 48,A57            | 2   | 8216            | 660–0246      | R1, R9            | 2   | " 330 OHMS, 1/4W, 5%       | 402-0331 |

| 45                | 1   | 8224            | 660–0247      |                   |     |                            |          |