# HDC-2001

# **Hard Disk Controller**

**Technical Manual**

USA OFFICE 5432 PRODUCTION DRIVE HUNTINGTON BEACH, CA 92649 TELEPHONE : (714) 891-4004 TELEX: 183210 ADVANCED HTBH UNITED KINGDOM OFFICE 27 PRINCESS STREET HANOVER SQUARE, LONDON W1R8NQ UNITED KINGDOM 409-0077 / 409-3351 TLX 265840 FINEST ADVANCED DIGITAL CORP. is proud to introduce its HDC-2001 hard disk controller board. The HDC-2001 is a single board controller with ECC(error correction) and CRC all on one board. It follows the IEEE-696 standards and will fit it to any S-100 Motherboard.

;

4

| 1. | INTRO                        | DUCTIONPage 1                                                                                                                                                                                                                                                                                                                                                                          |

|----|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1.<br>1.2.<br>1.3.<br>1.4. | General DescriptionPage 1<br>FeaturesPage 2<br>SpecificationsPage 3<br>Simplified System Block DiagramPage 4                                                                                                                                                                                                                                                                           |

| 2. | INTER                        | FACE CONNECTORSPage 5                                                                                                                                                                                                                                                                                                                                                                  |

|    | 2.1.<br>2.2.                 | Organization.Page 5Drive Control Signals.Page 52.2.1.RWCPage 52.2.2.Write GatePage 52.2.3.Seek CompletePage 52.2.4.Track000Page 52.2.5.Write FaultPage 52.2.6.HS0-HS2Page 52.2.7.SectorPage 62.2.8.IndexPage 62.2.9.ReadyPage 62.2.10.StepPage 62.2.11.Direction InPage 62.2.12.DS1-DS4Page 62.2.13.Control Driver/ReceiverPage 72.2.14.502.2.15.3434Pin Drive Control ConnectorPage 9 |

|    | 2.3.                         | Drive Data SignalsPage 9<br>2.3.1. Drive SelectedPage 9<br>2.3.2. Timing Clock+Page 9<br>2.3.3. Timing ClockPage 9<br>2.3.4. MFM Write Data +Page 9<br>2.3.5. MFM Read Data +Page 9<br>2.3.6. Drive Data ConnectorsPage 10<br>2.3.7. Differential Data Driver/ReceiverPage 10<br>FACE TIMINGPage 11                                                                                    |

| 3. | INTERF                       | FACE TIMINGPage 11 Drive Control TimingPage 11                                                                                                                                                                                                                                                                                                                                         |

|    | 3.2.                         | Drive Data TimingPage 18                                                                                                                                                                                                                                                                                                                                                               |

| 4. |                              | FILEPage 13                                                                                                                                                                                                                                                                                                                                                                            |

|    | 4.1.<br>4.2.<br>4.3.         | Task File Basics.Page 13Register Array.Page 13Register Definitions.Page 134.3.1. Command Register.Page 134.3.2. Status Register.Page 134.3.3. SDH Register.Page 134.3.4. Cylinder Number.Page 14                                                                                                                                                                                       |

|    |                              | 4.3.5.Sector Number.Page 144.3.6.Sector Count.Page 154.3.7.Error Register.Page 15                                                                                                                                                                                                                                                                                                      |

5.

6.

|             | 4.3.8. Write PrecompPage            | 15        |

|-------------|-------------------------------------|-----------|

|             |                                     | 15        |

| 4.4.        |                                     | 16        |

| 4.5.        | Status Registers Bits age           | 16        |

|             | 4.5.1. Error                        | 16        |

|             | 4.5.2. CorrectedPage                | 16        |

|             | 4.5.3. Data RequestPage             | 16        |

|             | 4.5.4. Seek CompletePage            | 16        |

|             | 4.5.5. Write FaultPage              | 16        |

|             | 4.5.6. Ready                        | 17        |

|             | 4.5.7. Busy                         | 17        |

| 4.6.        |                                     | 17        |

|             | 4.6.1. DAM Not FoundPage            | 17        |

|             | 4.6.2. TR000 Error                  | 17        |

|             | 4.6.3. Aborted CommandPage          | 17        |

|             | 4.6.4. ID Not FoundPage             | 17        |

|             | 4.6.5. CRC Error IDPage             | 17        |

|             | 4.6.6. UncorrectablePage            | 18        |

| •           | 4.6.7. Bad Block DetectPage         | 18        |

|             |                                     |           |

| COMMA       | ANDSPage                            | 19        |

|             |                                     |           |

| 5.1.        | Command SummaryPage                 |           |

|             | 5.1.1. Stepping RatesPage           |           |

|             | 5.1.2. DMA ReadPage                 |           |

|             | 5.1.3. Long Read and WritePage      |           |

| 5.2.        | Type I CommandsPage                 |           |

|             | 5.2.1. RestorePage :                |           |

|             | 5.2.2. SeekPage (                   |           |

| 5.3.        | Type II CommandsPage :              |           |

|             | 5.3.1. Read SectorPage              |           |

|             | 5.3.2. Multiple Sector ReadsPage a  |           |

| 5.4.        | Type III CommandsPage a             |           |

|             | 5.4.1. Write SectorPage a           |           |

| •           | 5.4.2. Format TrackPage             | 25        |

| nonco       | RAMMINGPage                         | <b>97</b> |

| PRUGR       | (MPRIING                            | - 1       |

| 6.1.        | Setting Up Task FilesPage           | ⊃a        |

| 0.1.        | 6.1.1. Cylinders and TracksPage (   |           |

| 6.2.        | Type I Command ProgrammingPage      |           |

| 0.1         | 6.2.1. Stepping RatesPage 3         |           |

|             | 6.2.2. Use of Busy BitPage          |           |

|             | 6.2.3. Use of InterruptsPage        |           |

|             | 6.2.4. Use of the Error BitPage     |           |

|             | 6.2.5. Use of the Corrected BitPage |           |

| 6.3.        | Type II Command ProgrammingPage     |           |

| .ar a kaf B | 6.3.1. DMA ModePage                 |           |

|             | 6.3.2. Block MovesPage              |           |

|             | 6.3.3. Using DMAPage                |           |

|             | 6.3.4. Multiple Sector Transfers    | 31        |

|             | 6.3.5. Simulated CompletionsPage    | 33        |

| 6.4.        | Type III Command ProgrammingPage    | 33        |

|             | 6.4.1. FormattingPage               |           |

|    |        | 6.4.2.           | InterleavingPage                    | 34  |

|----|--------|------------------|-------------------------------------|-----|

|    | 6.5.   | Bad Blo          | ock MappingPage                     | 35  |

|    |        | 6.5.1.           | Sector Pre-allocationPage           | 35  |

|    |        | 6.5.2.           | Alternate TracksPage                |     |

|    |        | 6.5.3.           | Spare SectorsPage                   |     |

|    |        | 6.5.4.           | Bad Block BitPage                   | 36  |

| 7. | THEORY | Y OF OPE         | ERATIONPage                         | 38  |

|    | 7.1.   | General          | l                                   | 38  |

|    | 7.2.   |                  | sor Functions                       |     |

|    |        | 7.2.1.           | Fast IO SelectPage                  | 39  |

|    |        | 7.2.2.           | Internal Bus ControlPage            |     |

|    |        | 7.2.3.           | Reset CircuitPage                   |     |

|    |        | 7.2.4.           | Processor Power SupplyPage          |     |

|    |        | 7.2.5.           | Read and Write PortsPage            |     |

|    |        | 7.2.6.           | Read/Write MemoryPage               |     |

|    |        | 7.2.7.           | Miscellaneous Control PortsPage     |     |

|    | 7.3.   |                  | Data SeparationPage                 |     |

|    |        | 7.3.1.<br>7.3.2. | Incoming Data SelectionPage         |     |

|    |        | 7.3.2.           | Reference ClockPage                 |     |

|    |        | 7.3.3.           | High Frequency Detector             |     |

|    |        | 7.3.5.           | Sample on Phase Detection           |     |

|    |        | 7.3.6.           | Error AmplifierPage                 |     |

|    |        | 7.3.7.           | VCDPage                             |     |

|    |        | 7.3.8.           | Window ExtensionPage                |     |

|    |        | 7.3.9.           | Clock DetectionPage                 |     |

|    | 7.4.   |                  | onversion and CheckingPage          |     |

|    |        | 7.4.1.           | AM DetectionPage                    |     |

|    |        | 7.4.2.           | Error Detection and Correction      | 47  |

|    |        | 7.4.3.           | Serial to Parallel ConversionPage   |     |

|    | 7.5.   | Serial           | Date GenerationPage                 |     |

|    |        | 7.5.1.           | Farallel to Serial ConversionPage   |     |

|    |        | 7.5.2.           | CRC/ECC GenerationPage              |     |

|    |        | 7.5.3.           | MFM GenerationPage                  |     |

|    | 7.6.   |                  | nterfacePage                        |     |

|    |        |                  | Wait EnablePage                     |     |

|    |        | 7.6.2.           | Bus GatingPage                      |     |

|    |        | 7.6.3.           | Register SelectionPage              |     |

|    |        | 7.6.4.           | Interrupts and DRQsPage             |     |

|    |        | 7.6.5.<br>7.6.6. | Address SelectPage<br>Boot PromPage |     |

|    |        | /.0.0.           | Boot PromPaye                       | 4   |

| 8. | MAINTE | ENANCE           | Page                                | 55  |

|    | 8.1.   | DRUN Ad          | ljustments                          | 56  |

|    | 8. e.  | Oscilla          | tor FrequencyPage                   | 56  |

|    | 8.3.   | Balance          | AdjustmentPage                      | 57  |

| А. | DISK I | RIVER E          | XAMPLEPage                          | 59  |

|    | A.1.   | Dolled           | Status Driver                       | 6.0 |

|    |        | A. 1. 1.         | InitializationPage                  |     |

|    |        |                  |                                     |     |

٠

•

|    |                              | A.1.2.Read Sector                                                                                                |

|----|------------------------------|------------------------------------------------------------------------------------------------------------------|

| в. | INTER                        | _EAVE CALCULATING UTILITYPage 65                                                                                 |

|    | B.1.                         | BASIC Interleave Calculating Program                                                                             |

| С. | SECTOR                       | R CALCULATING UTILITY                                                                                            |

|    | C.1.                         | BASIC Sectors per Track UtilityPage 68                                                                           |

| D. | PROGRA                       | AMMERS QUICK REFERENCE                                                                                           |

|    | D.1.<br>D.2.<br>D.3.<br>D.4. | Task FilePage 69<br>Valid CommandsPage 69<br>SDH Register FormatPage 70<br>Status and Error Register BitsPage 70 |

| E. | OPERA                        | TING SYSTEMSPage 71                                                                                              |

|    | E.1.                         | Operating Systems AvailablePage 71                                                                               |

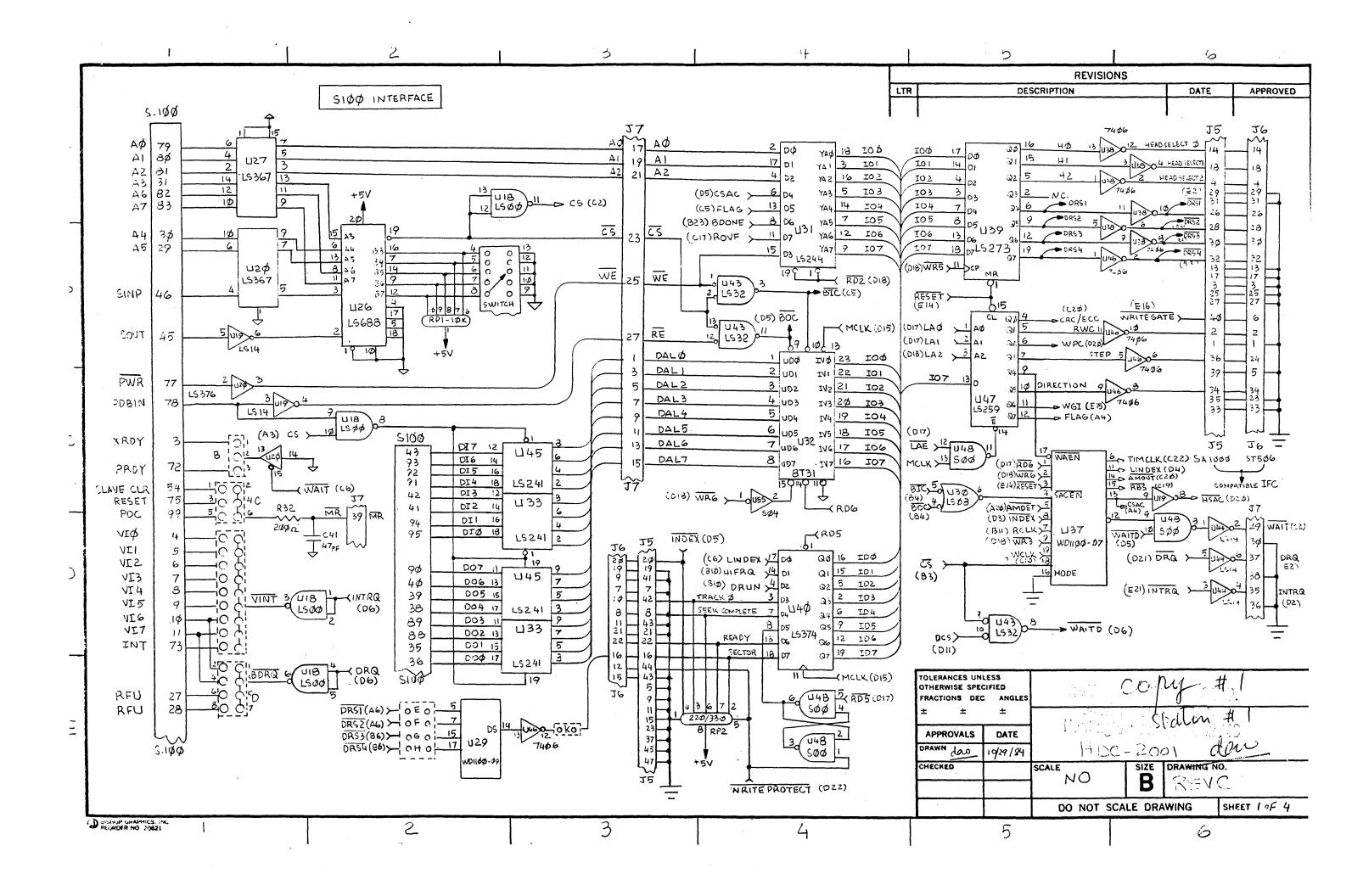

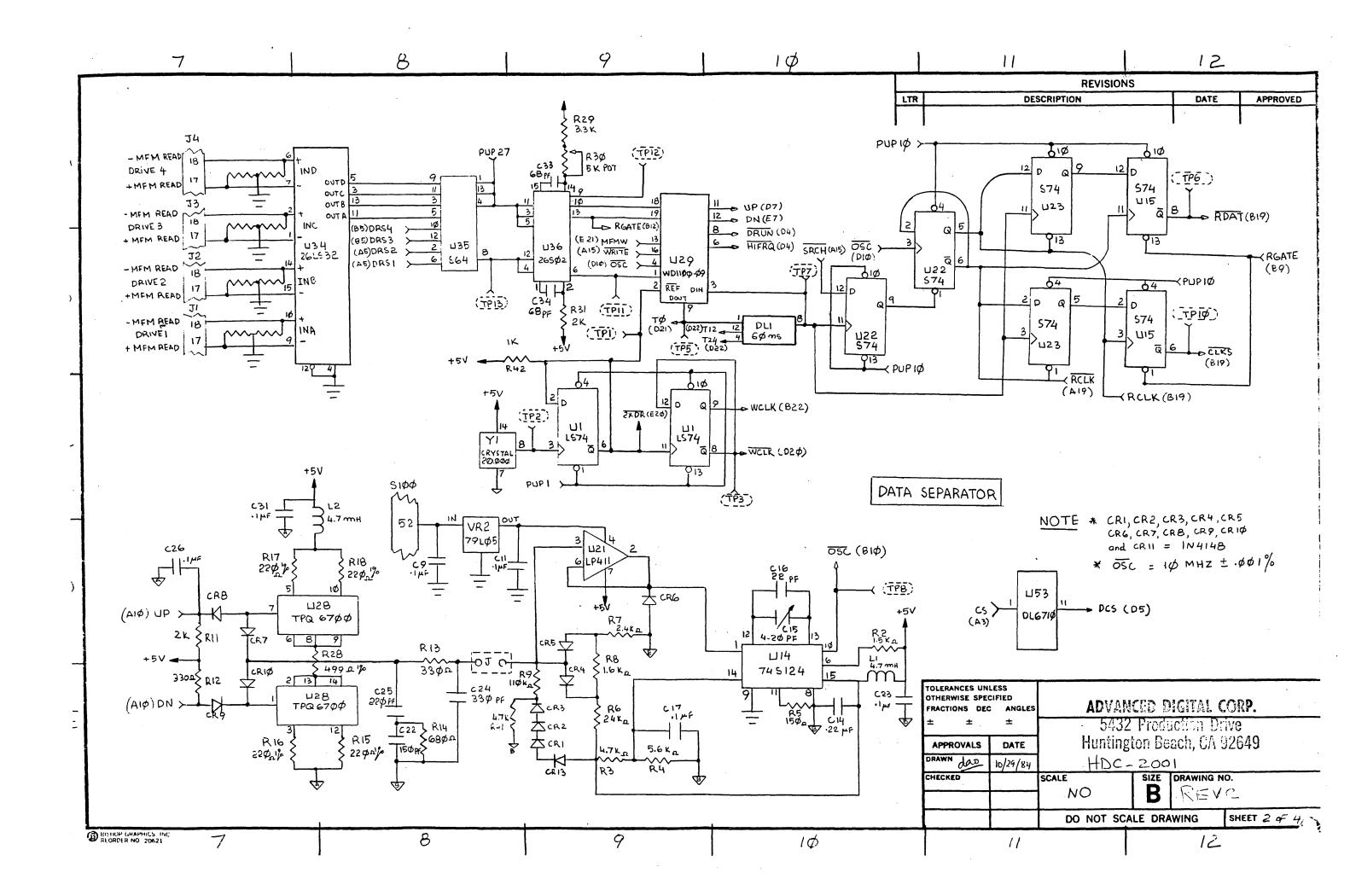

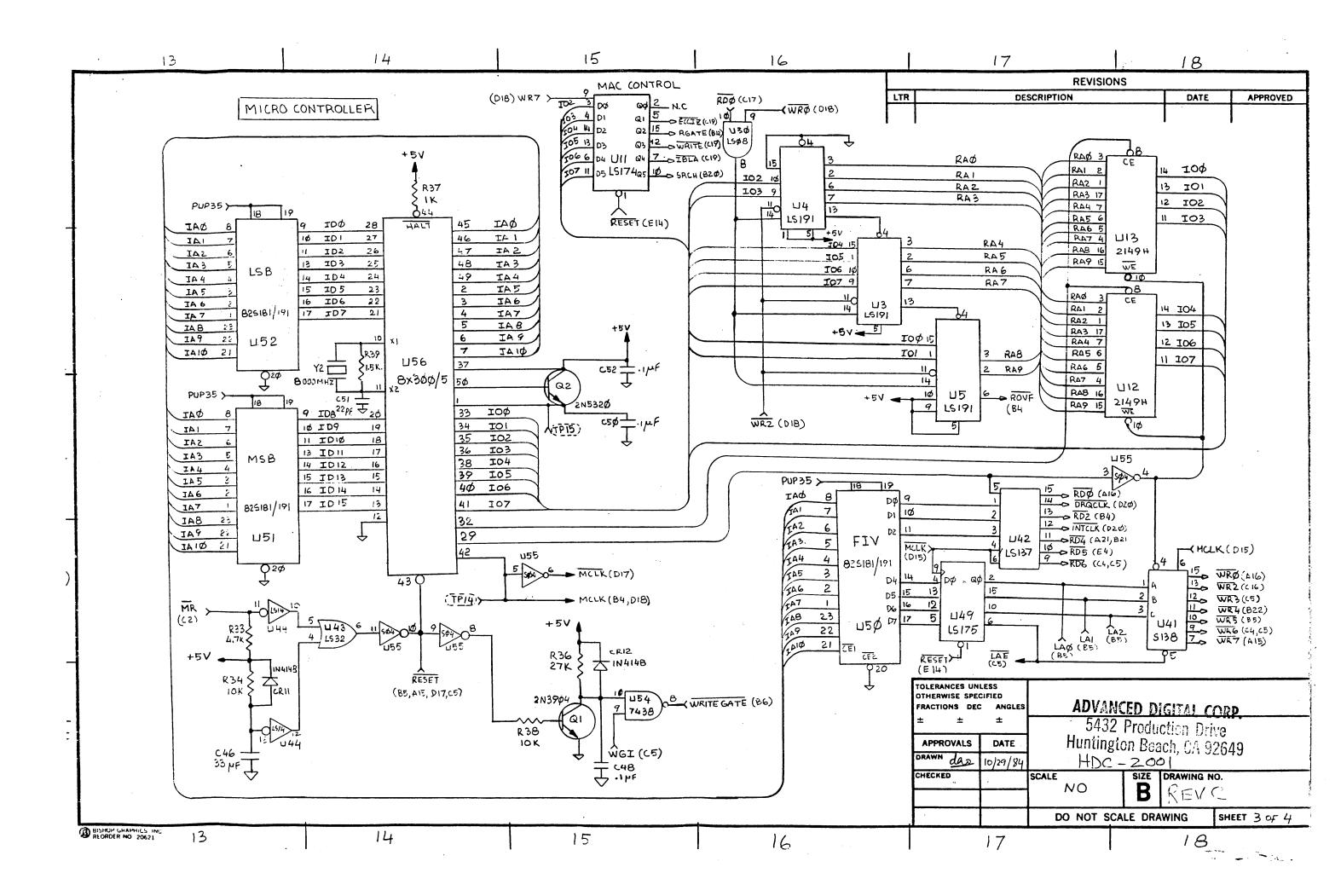

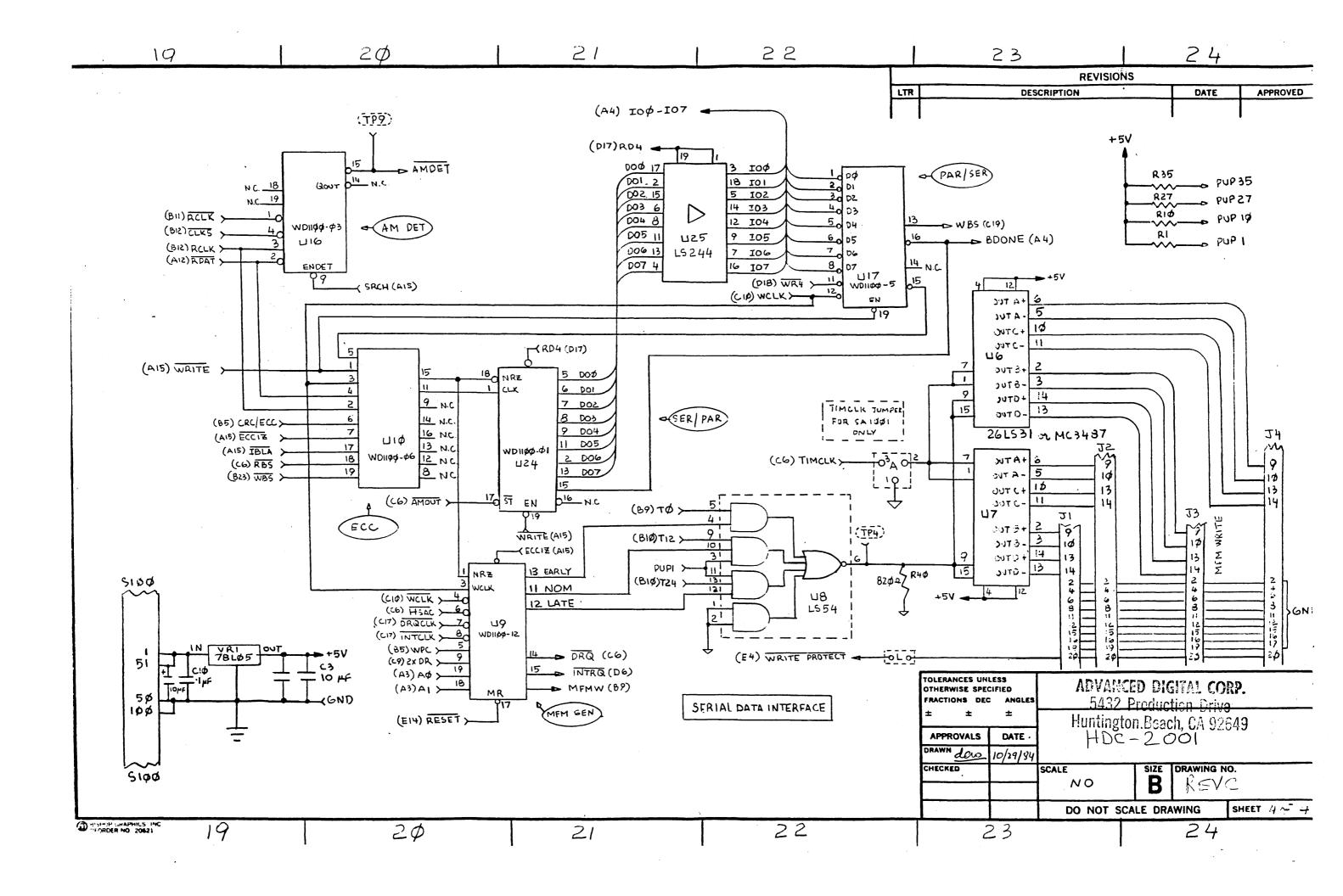

| F. | DRAWIN                       | NGSPage 72                                                                                                       |

|    | F.1.                         | Schematic                                                                                                        |

| G. | APPENI                       | DIXPage 78                                                                                                       |

|    | G.1.<br>G.2.<br>G.3.         | 8X300 CPUPage 78<br>ST506Page 79<br>SA1000 or 02000 SeriesPage 80                                                |

# 1. INTRODUCTION

# 1.1. General Description

The HDC-2001 is an S-100 bus Winchester Controller board with error correction (ECC) capabilities. It is designed to interface up to four Winchester disk Trives. There are two versions of the board, the HDC-1001-5/8. The HDC-2001-8 can operate 8" drives. The HDC- 001-5 is used with most 5-1/4" drives.

The drive signals are based upon the floppy look-alike interface available on the Shugart Associates' SA1000, the Seagate Technology ST506, and other compatible drives. All necessary buffers and receivers/drivers are included on the board to allow direct connection to the drive. Four 20 pin radial connectors are provided for data. Either a 34 pin (5-1/4" drive) or a 50 pin (8" drive) connector is provided for drive control.

All data to be written to or read from the disk, status information, and macro commands are transferred via the S-100 bus. An on board sector buffer allows data transfers to the host computer independent of the actual data transfer rate of the drive.

\*NOTE: In this manual the S-100 interface is called the "Host."

HDC-2001 HARD DISK CONTROLLER Technical Manual

INTRODUCTION

# 1.2. Eeatures

| * * * * * * * * * | S-100 IEEE 696<br>Single 8V Supply<br>Built-in Data Separator<br>Built-in Write Precompensation logic<br>Data rates up to 5 Mbits/sec<br>Control for up to 4 drives<br>Control for up to 4 drives<br>Control for up to 8 R/W heads<br>1024 cylinder addressing range<br>256 sector addressing range<br>CRC generation/verification |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *                 | Automatic formatting                                                                                                                                                                                                                                                                                                               |

| ¥                 | 128, 256, or 512 bytes per sector (User selectable)                                                                                                                                                                                                                                                                                |

| ¥                 | Unlimited sector interleave capability                                                                                                                                                                                                                                                                                             |

| ¥                 | Multiple sector reads and writes                                                                                                                                                                                                                                                                                                   |

| ¥                 | Overlap seek capability                                                                                                                                                                                                                                                                                                            |

| ×                 | Implied seek on all commands                                                                                                                                                                                                                                                                                                       |

| ¥                 | Automatic retries on all errors                                                                                                                                                                                                                                                                                                    |

| ¥                 | Automatic restore and re-seek on seek error                                                                                                                                                                                                                                                                                        |

| ¥                 | Error correction on data field errors                                                                                                                                                                                                                                                                                              |

| ¥                 | Diagnostic reads and writes for checking error correction                                                                                                                                                                                                                                                                          |

| *                 | Power Consumption +5V @ 2.5 amps                                                                                                                                                                                                                                                                                                   |

2

INTRODUCTION

# 1.3. Specifications

Encoding method: Cylinders per Head: Sectors per Track: Heads: Drive Selects: Step rate: Data Transfer Rate:

Write Precomp Time: CRC Polynomial: ECC Polynomial:

Reciprocal ECC Polynomial:

Miscorrection Probability:

Non-detection Probability:-2.3 E-10Correction Span:5 bitsSectoring:SoftHost Interface:8 Bit bi-directional BusDrive Capability:10 LS LoadsDrive Cable Length:10 ft. (3 M) max.Power Requirements:+8V, 3.0A Max (2.5A typ.)Ambient Operating Temperature:0 C to 50 C (32 F to 122 F)Relative Humidity:20% to 80%MTEF:10,000 POHMTTR:30 minutes

MFM Up to 1024 Up to 256 (512 byte sec) 8 4 35 uS to 7.5 mS (0.5 mS increments) 4.34 Mbits/sec (SA1000) 5.000 Mbits/sec (ST506) 12 nanoseconds X\*\*16+X\*\*12+X\*\*5+1 X\*\*32+X\*\*28+X\*\*26+X\*\*19+X\*\*17+X\*\*10+ X\*\*6+X\*\*2+1 X\*\*32+X\*\*30+X\*\*26+X\*\*22+X\*\*15+X\*\*13+ X\*\*6+X\*\*4+1 256 byte sector - (8.0 E-6 512 byte sector -  $\langle 1.5 E-5 \rangle$ -2.3 E-10 5 bits Soft 8 Bit bi-directional Bus 10 LS Loads 10 ft. (3 M) max. +8V, 3.0A Max (2.5A typ.) 20% to 80% 10,000 POH 30 minutes

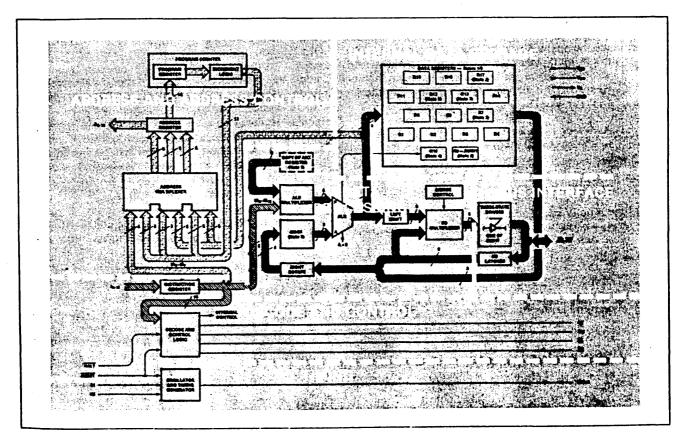

# 1.4. Simplified System Block Diagram

# 2. INTERFACE CONNECTORS

#### 2.1. Organization

The HDC-2001 has six on board connectors. These connectors consist of a two drive control connector, and four high speed data connectors.

The drive control cable is daisy-chained to each of the four drives.

The drive data connectors carry differential signals and are radially connected. Up to four drives can be accommodated by the HDC- 001.

#### 2.2. Drive Control Signals

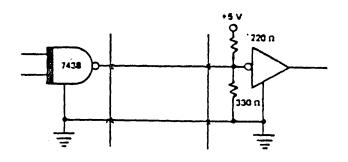

The Drive Control connector (J5 and J6) is a (relatively) low speed bus that is daisy chain connected to each of up to four drives in the system. To properly terminate each TTL level output signal from the HDC- 001, the last drive in the daisy chain should have a 220/330 ohm line termination resistor pack installed. All other drives should have no termination. Drive Control Signals are as follows:

2.2.1. RWC-

When the Reduce Write Current line is activated with Write Gate, a lower write current is used to compensate for greater bit packing density on the inner cylinders. The RWC- line is activated when the cylinder number is greater than or equal to four times the contents of the Write Precomp Register.

- 2.2.2. Write Gate-This output signal allows data to be written to the disk.

- 2.2.3. Seek Complete-Informs the HDC-2001 that the head of the selected drive has reached the desired cylinder and has stabilized. Seek Complete is not checked after a SEEK command, thus allowing overlapped seeks.

2.2.4. Track 000-Indicates that the R/W heads are positioned on the outermost cylinder. This line is sampled immediately before each step is issued.

2.2.5. Write Fault-

Informs the HDC-2001 that some fault has occurred on the slected drive. The HDC-2001 will not execute commands

2.2.6. HS0-HS2-

Head Select lines are used by the HDC-2001 to select a specific R/W head on the selected drive.

5

2.2.7. Sector-

For hard sectored drives, this line is used to indicate the sector boundries during formatting. Note that this line is not used unless special PROMs are installed to handle hard sectored drives.

2.2.8. Index-Is used to indicate the index point for synchronization during formatting and as a time out mechanism for retries. This signal should pulse once each rotation of the disk.

2.2.9. Ready-

Informs the HDC-2001 that the desired drive is selected and that its motor is up to speed. The HDC- 001 will not execute commands unless this line is true.

#### 2.2.10. Step-

This line is pulsed once for each cylinder to be stepped. The direction of the step will be determined by the Direction In- line. The step pulse period is determined by the internal stepping rate register during implied seek operations or explicitly during Seek and Restore commands. During auto restore, the step pulse period is determined by the Seek Completetime from the drive.

### 2.2.11. Direction In-

Determines the direction of motion of the R/W head when the step line is pulsed. A high on this line defines the direction as out and a low defines direction as in.

#### 2.2.12. DS1-DS4-

These four Drive Select lines are used to select one of four possible drives.

### 2.2.13. Control Driver/Receiver

The control lines have the following electrical specifications:

True=  $0.0 \vee to 0.4 \vee at Iin = 40 ma. (max.)$ False=  $2.5 \vee to 5.25 \vee at Iin = -0$  ma. (open)

· · · ·

# 2.2.14. 50 Pin Drive Control Connector

This Drive Control Connector (J5) is a 50 pin vertical header on tenth-inch centers that mates with Burndy #FRS50BS. The cable used should be flat ribbon cable or twisted pair with a length of less than 10 feet. The cable pin-outs are as follows:

.

| Signal Ground | 1     | Signal Pin | 1     | 1/0 | 1            | Signal Name     |

|---------------|-------|------------|-------|-----|--------------|-----------------|

| 1             | +<br> | 2          | +<br> | 0   | -+-<br>      | RWC-            |

| 3             | 1     | 4          | 1     | D   | 1            | Head Select 2-  |

| 5             | 1     | 6          | 1     |     | ł            | NC              |

| 7             | 1     | 8          | I .   | I   | I            | Seek Complete-  |

| 9             | 1     | 10         | 1     |     | 1            | NC              |

| 11            | I     | 12         | 1     | •   | 1            | NC              |

| 13            | 1     | 14         | 1     | 0   | I            | Head Select O-  |

| 15            | I     | 16         | 1     | I   | 1            | Sector-         |

| 17            | 1     | 18         | I     | 0   | I            | Head Select 1-  |

| 19            | I     | 20         | Į.    | I   | 1            | Index-          |

| 21            | ł     | 22         | 1     | · I | I            | Ready-          |

| 23            | 1     | 24         | I     |     | 1            | NC              |

| 25            | 1     | - 26       | I     | 0   | 1            | Drive Select 1- |

| 27            | 1     | 28         | I     | 0   | 6 <b>1</b> - | Drive Select 2- |

| 29            | 1     | 30         | Ł     | 0   | ł            | Drive Select 3- |

| 31            | ł     | . 32       | 1     | 0   | I            | Drive Select 4- |

| 33            | I     | 34         | I     | 0   | t i          | Direction In-   |

| 35            | 1     | 36         | Į.    | 0   | I            | Step-           |

| 37            | F     | 38         | 1     |     | 1            | NC              |

| 39            | 1     | 40         | 1     | 0   | 1            | Write Gate-     |

| 41            | 1     | 42         | 1     | I   | 1            | TR000-          |

| 43            | 1     | 44         | ł     | I   | 1            | Write Fault-    |

| 45            | 1     | 46         | 1     |     | ł            | NC              |

| 47            | I     | 48         | ł     |     | 1            | NC              |

| 49            | 1     | 50         | 1     |     | 1            | NC              |

\*\*

#### 2.2.15. 34 Pin Drive Control Connector

This Drive Control connector (J6) is a 34 pin vertical header on tenth-inch centers that mates with Burndy #FRS34BS. The cable used should be flat ribbon cable or twisted pair with a length of less than 10 feet. The cable pin-outs are as follows:

| Signal Ground | 1     | Signal Pin | 1 | ١١٥ | 1  | Signal Name     |

|---------------|-------|------------|---|-----|----|-----------------|

| 1             | +<br> | 2          | 1 | 0   | 1  | RWC-            |

| 3             | I     | 4          | t | O   | 1  | Head Select 2-  |

| 5             | I     | 6          | L | Ο   | I  | Write Gate-     |

| 7             | E     | 8          | 1 | I   | i  | Seek Complete-  |

| 9             | 1     | 10         | ł | I   | 1  | TR000-          |

| 11            | 1     | 12         | 1 | I   | 1  | Write Fault-    |

| 13            | 1     | 14         | ł | D   | I. | Head Select O-  |

| 15            | I     | 16         | 1 | I   | ł  | Sector-         |

| 17            | 1     | 18         | 1 | 0   | 1  | Head Select 1-  |

| 19            | 1     | 20         | 1 | I   | 1  | Index-          |

| 21            | 1     | 22         | I | I   | 1  | Ready-          |

| 23            | 1     | 24         | I | D   | 1  | Step-           |

| 25            | 1     | 26         | 1 | D   | 1  | Drive Select 1- |

| 27            | 1     | 28         | 1 | Ο   | I  | Drive Select 2- |

| 29            | 1     | 30         | ł | O   | 1  | Drive Select 3- |

| 31            | ł     | 32         | 1 | O   | 1  | Drive Select 4- |

| 33            | Ì     | 34         | 1 | Ō   | ł  | Direction In-   |

# 2.3. Drive Data Signals

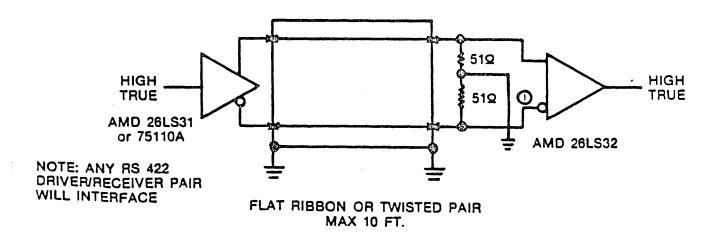

The Drive Data Connectors carry the high speed differential MFM data between the drive and the HDC-2001. Due to the loading characteristics of these differential lines, each of the drives have their own data connector. Drive Data Signals are as follows:

2.3.1. Drive Selected-

This signal is not used on the HDC-1001.

2.3.2. Timing Clock+

One half of the differential Timing Clock signal. This line contains a square wave signal equal to 1/64 the frequency of the write clock crystal.

2.3.3. Timing Clock-

This is the complimentary version of Timing Clock+.

2.3.4. MFM Write Data+-

Differential MFM data from the controller to the disk.

#### 2.3.5. MFM Read Data+-

Differential MFM data from the disk to the controller.

#### 2.3.6. Drive Data Connectors

Four Data connectors (J1-4) are provided for clock signals and data between the HDC-2001 and each drive. All lines associated with the transfer of data between the drive and the HDC-2001 system are differential in nature and may not be multiplexed. The Data connectors are 20 pin vertical headers on tenth-inch centers that mate with Burndy #FRS20BS. The cable used should be flat ribbon cable or twisted pair with a length of less than 10 feet. The cable pin-outs are as follows:

| Sig | gnal Ground | Sig | nal Pi | n I     | I/O  | 1  | Signal Name     |  |

|-----|-------------|-----|--------|---------|------|----|-----------------|--|

|     | 2           |     | 1      | +-<br>1 | I    |    | Drive Selected  |  |

| :   | 4           |     | З      | . 1     |      | 1  | NC              |  |

|     | 6           |     | 5      | Η·      | I.I. | 1  | Write Protect-  |  |

|     | 8           |     | 7      | l I     |      | 1  | NC              |  |

|     |             |     | 9      | 1       | 0    | 1: | Timing Clock+   |  |

|     | !           |     | 10     | ł       | O    | 1  | Timing Clock-   |  |

|     | 11          | Ì   |        | I.      |      | 1  | GND             |  |

|     | 12          | ]   |        | 1       |      | 1  | GND             |  |

|     |             | I   | 13     | l I     | O    | 1  | MFM Write Data+ |  |

|     |             | l   | 14     | · 1 ·   | 0    |    | MFM Write Data- |  |

|     | 15          | 1   |        | - I     |      | 1  | GND             |  |

|     | 16          |     |        | l       |      | 1  | GND             |  |

| •   |             |     | 17     | 1       | I    | ł  | MFM Read Data+  |  |

|     |             | İ   | 18     |         | I    | 1  | MFM Read Data-  |  |

|     | 19          |     |        | ł       |      | 1  | GND             |  |

|     | 20          |     |        | 1       |      | I  | GND             |  |

2.3.7. Differential Data Driver/Receiver

# 3. INTERFACE TIMING

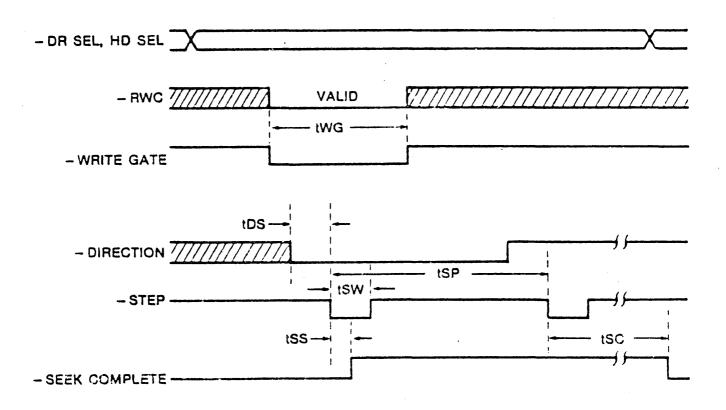

# 3.1. Drive Control Timina

| SYMBOL | CHARACTERISTIC               | MIN  | MAX     | STINC | 1 |

|--------|------------------------------|------|---------|-------|---|

| tWG    | Write gate pulse width 1 se  | etor | 2 rot 3 | +10n  | + |

| tDS    | Direction to step delay      | 250  |         | nS    | 1 |

| tSW    | Step pulse width             | 5(ty | oical · | uS    | 1 |

| tSP    | Programmed Step pulse period | 0.01 | 7.5     | uS    | t |

| tSS    | Step to Seek Complete false  |      | 9       | uS    | 1 |

| tSC    | Last Step to seek Complete   |      | 128     | Index | 1 |

|        |                              |      |         | times | 1 |

Notes:

- 1. Write gate pulse width will vary depending on the sector size and the rotation rate of the disk.

- Step pulse period will be equal to seek complete time during aut restore.

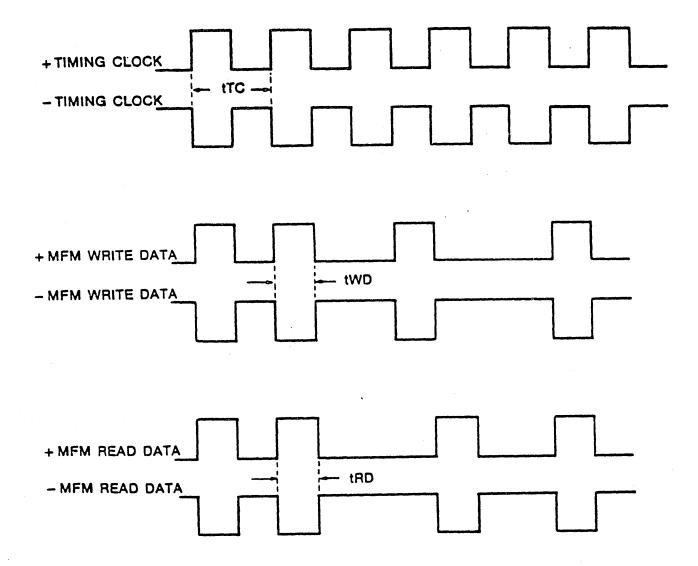

3.2. Drive data timing

| + | SYMBOL | CHARACTERISTIC                                                                                          | MIN                                                      | MAX                                   | UNITS | + |

|---|--------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------|-------|---|

| 1 | tTC    | Timing clock period                                                                                     | WCLK/16                                                  | (typical                              | )     | 1 |

| I | tWD    | Write data pulse width                                                                                  | 60                                                       | 120                                   | nS    | 1 |

| I | tRD    | Read data pulse width                                                                                   | 25                                                       |                                       | nS    | I |

| + |        | سر الحم الحم حتى بين وين عنى ويم وعن الما الحد عن عن بلن عن بجي الجا الحد عن مع عمو علي علي الحد الحد ا | ليو لدلت الجي دينيا جيبي الله بابن ويبر بلين باب البر ال | و بلک میں بین نیج ہیں ہیں اندا اندا ا |       | + |

# 4.1. IASK Eils Basics

The HDC-2001 performs all disk functions through a set of registers called the Task File. These register are loaded with parameters such as Sector Number, Cylinder Number, etc., prior to issuing a command. Individual registers are selected via A0-2. The following registers are available:

# 4.2. Register Array

| I CS | - 1 | AS | 1   | A1 | I | AØ | ł | RE-             | 1 | WE-              | 1 |

|------|-----|----|-----|----|---|----|---|-----------------|---|------------------|---|

| 1 1  | 1   | X  | 1   | X  | 1 | X  | 1 | Deselected      |   | Deselected       |   |

| 10   | 1   | Ø  | · 1 | 0  | Ł | ø  | 1 | Data Register   | ! | Data Register    | 1 |

| 1 0  | 1   | Ø  | ł   | Ø  | ł | 1  | 1 | Error Register  | 1 | Write Precomp    | 1 |

| 1 0  | 1   | Ø  | 1   | 1  | 1 | Ø  | ł | Sector Count    | 1 | Sector Count     | 1 |

| 1 0  | 1   | Ø  | 1   | 1  | 1 | 1  | 1 | Sector Number   | t | Sector Number    | 1 |

| 1 0  | ł   | 1  | ł   | 0  | 1 | Ø  | 1 | Cylinder Low    | 1 | Cylinder Low     | 1 |

| 1 0  | 1   | 1  | 1   | 0  | ł | 1  | 1 | Cylinder High   | 1 | Cylinder High    | 1 |

| 1 0  | 1   | 1  | ſ   | 1  | ł | 0  | 1 | Size/Drive/Head | 1 | Size/Drive/Head  | i |

| 10   | 1   | 1  | Ì   | 1  | 1 | 1  | 1 | Status Register | 1 | Command Register | 1 |

# 4.3. Register Definitions

#### 4.3.1. Command Register

All commands are loaded into this register after the task registers have been set. Writing to this register will cause the INTRQ Line to be reset. The Command register is a write-only register.

#### 4.3.2. Status Register

After execution of a command, the Status register is internally loaded with status information pertaining to the command executed. The host must read this register to determine successful execution of the command. The Status register is a read-only register; it cannot be written to by the host. If the busy bit is set, no other bits in this register are valid. Accessing this register will cause the INTRQ line to be reset.

#### 4.3.3. SDH Register

This register contains the ECC mode, sector Size, Drive select, and Head select bits. The SDH register is a

read/write register organized as follows:

| +   |        | برین برین بین سنه بین منت بین بین برین درد بخه بین پر |                                                       |

|-----|--------|-------------------------------------------------------|-------------------------------------------------------|

| 17  | 165    | 14312                                                 |                                                       |

| 1   | Size   | Drive  <br>  Select                                   | Head  <br>Select                                      |

| E=0 | CRC in | data field<br>data field                              | 1949 FANN 645 FANN ANN 675 FANN 646 FANN 6 <b>4</b> - |

| -+ |            |          |                                                                                                |      |    |          |          |                | +  |

|----|------------|----------|------------------------------------------------------------------------------------------------|------|----|----------|----------|----------------|----|

| 1  | Bit<br>6   | Bit<br>S | Sector Size                                                                                    | <br> | 1  | Bit<br>4 | Bit<br>3 | Drive Selected | 1  |

| +- | <u>ل</u> م | 0        | 256 Bytes                                                                                      | ·    | 1. | 0        | 0        | Drive Sel 1    | -+ |

| I  | Ø          | 1        | 512 Bytes                                                                                      | l    | ł  | Ø        | 1        | Drive Sel 2    | I. |

| 1  | 1          | 1        | 128 Bytes                                                                                      | 1    | 1  | 1        | 0        | Drive Sel 3    | 1  |

| +- |            |          | والمركز القالب والمركز |      | 1  | 1        | 1        | Drive Sel 4    | 1  |

|   | ected | Head Sele | Bit<br>Ø | Bit<br>1 | Bit<br>2 | 1 |

|---|-------|-----------|----------|----------|----------|---|

|   | 0     | Head      | 0        | 0        | 0        |   |

| ! | 1     | Head      | 1        | Ø        | Ø        | 1 |

| 1 | 2     | Head      | Ø        | 1        | Ø        | 1 |

| 1 | 3     | Head      | 1        | 1 -      | Ø        | 1 |

| 1 | 4     | Head      | Ø        | Ø        | 1        | 1 |

| I | 5     | Head      | 1        | Ø        | 1        | 1 |

| 1 | 6     | Head      | 0        | 1        | 1        | 1 |

| 1 | 7     | Head      | 1        | 1        | 1        | 1 |

# 4.3.4. Cylinder Number

These two read/write registers form the cylinder number where the head is to be positioned on a Seek, Read, Write, or Format command. Internally, a separate set of cylinder register values are maintained for each drive. The two least significant bits of the Cylinder High register form the most significant bits of the cylinder number as illustrated below:

|                | <u>Cylinder High</u> | <u>Cylinder Low</u> |

|----------------|----------------------|---------------------|

| Register bits: | 17161514131211101    | 17161514131211101   |

| Cylinder bits: | 1 1 1 1 1 1 19181    | 17161514131211101   |

#### 4.3.5. Sector number

This register is loaded with the desired sector number prior to a Read or Write command. The Sector Number register is a read/write register and may be read or written to by the host.

#### 4.3.6. Sector Count

This read/write register is loaded with the number of sectors to be processed. On Read or Write multiple commands, the number of sectors to be transferred is loaded into this register. During a Format command, this register is loaded with the number of sectors to be formatted. During the course of a command, the Sector Count register is decremented towards zero and should be re-loaded for each command.

#### 4.3.7. Error Register

This register contains specific fault information pertaining to the last command executed. This register is valid only if the Error bit in the Status register is set. The Error register is read only.

#### 4.3.8. Write Precomp

The Write Precompensation register holds the cylinder number where the RWC line will be asserted and Write Precompensation logic is to be turned on. This writeonly register is loaded with the cylinder number divided-by-4 to achieve a range of 1024 cylinders. For example, if write precompensation is desired for cylinder 128 (80 Hex) and higher, this register must be The Write Precompensation loaded with 32 (20 Hex). delay is fixed at 12 nanoseconds from nominal. On drives that require separate write precompensation and reduce write current cylinders, set the Write Precomp register to the cylinder where write current reduction is desired.

# 4.3.9. Data Register

This register is the user's window to the on-board full sector buffer. It contains the next byte of data to be written to or read from the internal sector buffer. The Data register is accessed once for each byte in the sector. When the DRQ (Data ReQuest) line is asserted, the sector buffer contains data in a read command, or is awaiting data to be written during a write command into the Data register. If the HDC- 001 is interfaced using programmed I/O, data transfers to this register can be implemented using block moves. This register may not be read from or written to except in the contex' of a valid command.

### 4.4. Status Registers

There are two registers in the HDC-2001 that are used to monitor the execution of commands. They are the Status register and the Error register. Each bit of these registers is used to define a particular type of status or error condition.

| Bit   | 1   | Status Register | 1 | Error Register       |  |

|-------|-----|-----------------|---|----------------------|--|

| <br>7 |     | Busy            | + | Bad Block Detect     |  |

| 6     | 1   | Ready           | 1 | Uncorrectable        |  |

| 5     | 1 - | Write Fault     | 1 | CRC Error - ID Field |  |

| 4     | 1   | Seek Complete   | I | ID Not Found         |  |

| З     | 1   | Data Request    | 1 | -                    |  |

| 2     | 1   | Corrected       | 1 | Aborted Command      |  |

| 1     | 1   | -               | 1 | TR000 Error          |  |

| Ø     | 1   | Error           | 1 | DAM Not Found        |  |

# 4.5. Status Register Bits

4.5.1. Error

When set, indicates that a bit is set in the Error register. It provides an efficient means of checking for an error condition by the host. This bit is reset on receipt of a new command.

#### 4.5.2. Corrected

Indicates that there was a read error condition either in the data field or the ECC check bits themselves, and that the controller was able to correct the condition.

#### 4.5.3. Data Request

Functions almost identically to the hardware DRQ `ine. When set, it indicates that the sector buffer is ready to accept data or contains data to be read out by the host. The Data Request bit is reset when the sector buffer has been fully read from or written to. Normally, the host need not consult this bit to determine if a byte should be transferred.

#### 4.5.4. Seek Complete

Indicates the condition of the Seek Complete line on the selected drive.

4.5.5. Write Fault

Indicates the condition of the Write Fault line on a

selected drive. The HDC-2001 will not execute any command if this bit is set.

# 4.5.6. Ready

Indicates the condition of the Ready line of the selected drive. The HDC-2001 will not execute any commands unless this bit is set.

# 4.5.7. Busy After issuing a command, this bit will be set, indicating that the HDC-2001 is busy executing a command. No other bits or registers are valid when this bit is set.

# 4.6. Error Register Bits

# 4.6.1. DAM Not Found Will be set during a Read Sector command if, after successfully identifying the ID field, the Data Address mark was not detected within 16 bytes of ID field.

# 4.6.2. TR000 Error

Will be set during a Restore command if, after issuing 1024 stepping pulses, the Track 000 line was not asserted by the drive.

#### 4.6.3. Aborted Command

Indicates that a valid command has been received that cannot be executed, based on status information from the drive. For example, if a write sector command has been issued while the Write Fault line is set, the Aborted Command bit will be set. Interrogation of the Status and/or Error registers by the host can be performed to determine the cause of failure.

#### 4.6.4. ID Not Found

When set, this bit indicates that an ID field containing a specified cylinder, head, sector number or sector size was not found.

#### 4.6.5. CRC Error ID

Indicates that a CRC error was encountered in an ID field.

#### 4.6.6. Uncorrectable

Indicates that an error was detected while reading the data field or ECC check bits and the error was so severe that the controller was not able to correct the condition.

#### 4.6.7. Bad Block Detect

Indicates that a Bad Block Mark has been detected in the specified ID field. If the command issued was a write sector command, no writing will be performed. If generated from a read sector command, the data field will not be read. Note that bad block will not be detected if the flaw is in the ID field unless multiple ID fields were written.

#### 5. COMMANDS

The HDC-2001 executes five easy to use macro commands. Most commands feature automatic 'implied' seek, which means the host system need not tell the HDC-2001 where the R/W heads of each drive are or when to move them. The controller automatically performs all needed retries on all errors encountered including data field errors. If the data field contains an error, the controller will perform a correction, if possible. If the R/W head mispositions, the HDC-2001 will automatically perform a restore and a re-seek. If the error is completely unrecoverable, the HDC-2001 will simulate a normal completion to simplify the host system's software.

Commands are executed by loading a command byte into the Command register while the controller is not busy. (Controller will not be busy if it has completed the previous command.) The task file must be loaded prior to issuing a command. No command will execute if the Seek Complete or Ready lines are false or if the Write Fault line is true. Normally it is not necessary to poll these signals before issuing a command. If the HDC-2001 receives a command that is not defined in the following table, undefined results will occur.

5.1. <u>Command Summary</u> For ease of discussion, commands are divided into three types which are summarized in the following table:

| - |      |   | ه همه مای این است این | <br>1 · |   |   |   | B | <br>[TS | <br> |           | · <b></b> . |

|---|------|---|-----------------------------------------------------------|---------|---|---|---|---|---------|------|-----------|-------------|

|   | TYPE | İ | COMMAND                                                   | 1       | 7 | 6 | 5 | 4 |         | 2    | 1         | Ø           |

|   | I    | 1 | Restore                                                   | 1       | Ø | 0 | Ø | 1 | r3      | r2   | <b>r1</b> | rØ          |

|   | I    | Î | Seek                                                      | +-<br>  | Ø | 1 | 1 | 1 | r3      | r2   | r1        | r0          |

|   | II   | 1 | Read Sector                                               | 1       | ø | 0 | 1 | Ø | D       | M    | L         | 0           |

| _ | III  | 1 | Write Sector                                              |         | Ø | Ø | 1 | 1 | 0       | м    | L         | Ø           |

| _ | III  | 1 | Format Track                                              | 1       | Ø | 1 | Ø | 1 | 0       | 0    | 0         | 0           |

L=Long Read/Write M=Multiple Sector

D=DMA Read Interrupt rX=Stepping Rate

5.1.1. Stepping Rates

|          |   | rð   | 3-rØ | - Ste | ppi | ng l | Rate | 2 |     |     |  |

|----------|---|------|------|-------|-----|------|------|---|-----|-----|--|

| <br>0000 | = | 35 ( | JS   |       | 1   | 1(   | 000  | = | 4.0 | mS  |  |

| 0001     | = | 0.5  | глS  |       | 1   | 10   | 001  | = | 4.5 | Сm  |  |

| 0010     | = | 1.0  | mS   |       | I   | 10   | 010  | = | 5.0 | mS  |  |

| 0011     | = | 1.5  | мS   |       | 1   | 10   | 811  | = | 5.5 | mS  |  |

| 0100     | = | 2.0  | nS   |       | 1   | 1:   | 100  | 3 | 6.0 | nıS |  |

| 0101     | = | 2.5  | mS   |       | 1   | 1    | 101  | = | 6.5 | мS  |  |

| 0110     | = | 3.0  | mS   |       | 1   | 1    | 110  | = | 7.0 | nıS |  |

| 0111     | = | 3.5  | мS   |       | ł   | 1 :  | 111  | = | 7.5 | mS  |  |

5.1.2. DMA Read

<u>D - DMA Read Mode</u>

$\emptyset$  = Programmed I/O Mode

1 = DMA Mode

The DMA bit is used to position INTRQ in relation to DROs during the read sector command. If the DMA bit is reset (D=0), the interrupt will occur before the first DRQ. This allows the programmed I/O host to intervene and transfer the data from the sector buffer. If the DMA bit is set (D=1), then the interrupt will occur only after the system DMA controller has transferred the entire buffer of data.

#### 5.1.3. Long Read and Write

If the Long bit is set, a special diagnostic read or write will be performed. During normal reads or writes, the ECC check bytes are not visible to the user. The Long bit allows the user to read and write these normally invisible bytes.

During a Read Long, the HDC-2001 will return a sector that is four bytes longer than the selected sector size. These four bytes will be the ECC check bits as recorded on the disk. During a Write Long, the host give the HDC-2001 a sector that is four bytes longer than normal. These four extra bytes are recorded in place of the ECC bytes that are normally written after each sector.

The Read and Write Long option may only be used when the HDC-2001 is in ECC mode.

#### 5.2. Type I Commands

These commands simply position the R/W heads of the selected drive. Both commands have explicit stepping rate fields. The lower four bits of these commands form the stepping rate which is stored for later Read, Write or format operations.

#### 5.2.1. Restore

The Restore command is used to calibrate the position of the R/W head on each drive by stepping the head outward until the TR000 line goes true. Upon receipt of the Restore command, the Busy bit in the Status Register is set. Cylinder High and Cylinder Low registers are cleared. The lower four bits of the command byte are stored in the stepping rate register for subsequent implied seeks. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted command bit in the Error register is set, the Error bit in the Status register is set, an interrupt is generated, and the Busy bit is reset.

If no errors are encountered thus far, the internal head position register for the selected drive is cleared. The TR000 line is sampled. If TR000 is true, an interrupt is generated and the Busy bit is reset. If TR000 is not true, stepping pulses at a rate determined by the stepping rate field are issued until the TR000 line is activated. When TR000 is activated, the Busy bit is reset and an interrupt is issued. If the TR000 line is not activated within 1024 stepping pulses, the TR000 Error bit in the Error Register and the Error bit in the Status Register are set, the Busy bit is reset, and an interrupt is issued.

#### 5.2.2. Seek

The Seek command positions the R/W head to a certain cylinder. It is primarily used to start two or more concurrent seeks on drives that support buffered stepping. Upon receipt of the Seek command, the Busy bit in the Status Register is set. The lower four bits of the command byte are stored in the stepping rate register for subsequent implied seeks. The state of Seek complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted command bit in the Error register is set, the Error bit in the Status register is set, an interrupt is generated, and the Busy bit is reset.

If no errors are encountered thus far, the internal head position register for the selected drive is updated, the direction line is set to the proper direction and a step pulse is issued for each cylinder to be stepped. When all stepping pulses have been issued, the Busy bit is reset and an interrupt is issued. Note that the Seek Complete line is not sampled after the Seek command, allowing multiple seek operations to be started using drives with buffered seek capability.

# 5.3. Type II Commands

This type of command is characterized by a transfer of a block of data from the HDC-2001 buffer to the host. This command has an implicit stepping rate as set by the last sestore or Seek command.

#### 5.3.1. Read Sector

The Read Sector command is used to read a sector of data from the disk to the host computer. Upon receipt of the Read command, the Busy bit in the Status register is set. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists. The Aborted Command bit in the Error register is set, the Error bit in the Status register is set, and a normal completion is simulated.

### Implied Seek

If no errors are encountered so far, a Seek command is executed. The Seek Complete line is sampled. If the Seek Complete line does not go true within 128 Index pulses, then the Aborted command bit in the Error register is set, the Error bit in the Status register is set, and a normal completion is simulated.

#### Retries

Once the head has settled over the desired cylinder, the HDC-2001 will attempt to read the sector. The HDC-2001 performs all retries necessary to recover the data during the read command. The controller attempts read the desired sector up to 16 times. It will attempt a retry if it  $\frac{1}{2}$

not find an ID, if the ID of that sector has a bad CRC, if the Data Address Mark (DAM) couldn't be found, or even if the data was actually read from the disk but was in error.

#### Error Correction

If an error was detected while reading the data field, the controller will attempt to correct the error, If the error was correctable, the Corrected bit in the status register will be set and the command resumed. If it was uncorrectable, the Uncorrectable Error bit will be set, the Error bit in the Status register is set, and a normal completion is simulated.

#### Auto Restore

Every time the controller encounters an error, it records the occurrence of that error in an internal register. If, after 16 retries, the controller was not able to get a match on the ID field, it assumes that the head was possibly mis-positioned and executes an auto-restore. During the autorestore, the stepping rate is implied to be equal to the Seek Complete period. If the TRK000 does not go true within 1024 steps, the TRK000 Error bit in the Error register is set, the Error bit in the Status register is set and a normal completion is simulated.

After the auto-restore has been successfully completed, the controller reseeks and attempts to read the sector once again. An auto-restore will be performed only once per read or write sector command.

#### Hard Errors

If the controller encounters a non-recoverable error, the controller examines its internal error history register. It then sets the bit in the Error Register of the highest severity error incorred. If the Uncorrectable bit is set, the data that last produced that error will be available in the sector buffer. The Error bit in the Status Register is set and a normal completion is simulated.

# Error Severity Levels

Although the HDC-2001 might encounter any number of errors in the course of executing a command, it only reports the most severe error. Errors are ranked from most severe to least severe as follows:

- 1. Aborted Command

- 2. TR000 Error

- 3. Bad Block\*

- 4. Uncorrectable

- 5. Data Address Mark Not Found

- 6. ID CRC Error

- 7. ID Not Found

- \* Bad Block will only be detected if there is no ID CRC Error or ID Not Found Error in the sector with the Bad Block bit set.

#### Normal Completion

If the HDC-2001 encountered no errors, it is considered a normal completion. The busy bit is reset. The status of the DMA bit in the command byte is examined. If this bit is reset (D=O; programmed I/O mode) then an interrupt is issued at this time. DRQs are then generated for each byte to be read from the buffer. (Note: It is recommended that programmed I/O transfers should take place as a block move without consulting the DRQ bit in the Status Register.) After all the data has been moved from the buffer, the DMA bit in the command byte is consulted again. If this bit is set (D=1; DMA mode) then an interrupt will be issued.

#### 5.3.2. Multiple Sector Reads

If the M bit in the command byte is set, then the HDC-2001 will attempt to read multiple sectors. After all the data has been transferred from the sector buffer to the host on a read, the Sector Number register is incremented, the Sector Count register is decremented, and if the Sector Count reaches zero or if a fatal error is encountered, the HDC- 001 will stop and interrupt the host.

When a Correctable error is encountered during a multiple sector read, the occurance of the error is logged, but no interrupts are generated. After the whole multiple transfer is complete, the host can read the Corrected bit of the Status register to determine if any automatic corrections have taken place.

#### 5.4. Type III Commands

This type of command is characterized by a transfer of a block of data from the host to the HDC- 001 buffer. These commands have implicit stepping rates as set by the last Restore or Seek command.

#### 5.4.1. Write Sector

The Write Sector command is used to write a sector of data from the host computer to the disk. Upon receipt of the Write command, the controller generates DRQs for each byte to be written to the buffer. (Note: It is recommended that programmed I/O transfers should take place as a block move without consulting the DRQ bit in the Status register.)

After all data has been sent to the sector buffer, the Busy bit in the Status register is set. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted Command bit in the Error register is set, the Error bit in the Status register is set, an interrupt is generated and the Busy bit is reset.

#### Retries

Once the head has settled over the desired cylinder, it will attempt to read the ID of the sector. The HDC-2001 performs all retries necessary to recover the Id during the write command. The controller attempts to read the ID of the desired sector up to 16 times. It will attempt a retry if it doesn't find an ID or if the ID of that sector has a bad CRC.

#### Auto Restore

Every time the controller encounters an error, it records the occurrence of that error in an internal register. If, after 16 retries, the controller was not able to get a match on the ID field, it assumes that the head was possibly mis-positioned and executes an auto-restore. During the autorestore, the stepping rate is implied to be equal to the Seek Complete period. After the auto-restore has been successfully completed, the controller re-seeks and attempts to write the sector once again.

#### Hard Errors

If the controller encounters a non-recoverable error, the controller examines its internal error history register. It then sets the bit in the Error register of the highest severity error incurred. The Error bit in the Status register is set, an interrupt is generated and the Busy bit is reset.

If the proper sector is located, the sector buffer is written to the disk, an interrupt is generated and the Busy bit is reset.

#### 5. .2. Format Track

Format Command is used for initializing the ID and data fields on a

particular disk. Upon receipt of the Format command, the controller generates DRQs for each byte of the interleave table to be written to the Information on setting up an interleave table can be found in buffer. In all cases, the number of bytes praneterred to the buffer Section 7. must correspond to the current sector size.

After all data has been set to the buffer, the Busy but in the Status register is set. The state of Seek Complete. Ready and Write Fault lines are sampled. If an error condition exists, the Aborted Command bit - the Error register is set, the Error bit in the Status register is set. an interrupt is generated and the Busy bit is reset.

#### Implied Seek

If no errors are encountered so far, a Seek command is executed. No verification of track positioning accuracy is performed because the t ck may not have any ID fields present. After the Seek operation has been performed, the Seek Complete line is sampled. If the Seek Complete line is not asserted within 128 Index pulses, the Aborted Command bit in the Error register is set, the Error bit in the Status register is set. an interrupt is generated and the Busy bit is reset.

Once the head has settled over the desired cylinder, the controller waits until the Index line is asserted. Once the index is found, a number of TD fields and nulled data fields are written to the disk. The number of sectors written is equal to the contents of the Sector Count Register. äs each sector is written the Sector Count Register is decremented, and consequently, must be applated before each format operation.

After the last sector is written, the controller back-fills the track with 4E's. When the next index pulse after the last sector is written is the format operation is terminated, an Interrupt is cenerated encountered, and the Busy bit is reset.

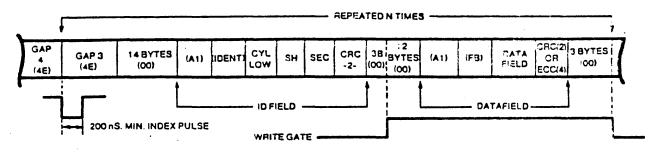

#### Track Format

The Format command formats the track using the following format:

NOTE:

5) The 2 LSB's of the IDENT twite are used for Cylinder high

- 11 When MSB of SH byte = 1, bad block is detected.

- 2) Write Gate tum-on is 3 bytes after the 1D field's CRC byte.

- Write Gate turn-off is 3 bytes after the Data 3) Field's check bytes.

- 4) 12 bytes of zeroes are re-written on a Data Field update.

26

These values are:

| FE 0 10 255     | -Minders  |

|-----------------|-----------|

| FF - 256 to 511 | cylinders |

| FC - 512 to 767 | cylinders |

| FD- (68 to 1023 | cvlinders |

#### 6. PROGRAMMING

Users familiar with floppy disk systems will find programming the HDC-2001 a pleasant surprise. A substantial amount of intelligence that was required by the host computer has been incorporated into the HDC-2001. The HDC- 001 performs all needed retries, even on head positioning errors. If there is an error in the data field, the HDC-2001 will attempt to correct Most commands feature automatic 'implied' seek which means that seek it. commands need not be issued to perform basic read/write functions. The HDC-2001 keeps track of the position of up to four read/write head assemblies, so the host system does not have to maintain track tables. A11 transfers to and from the disk are through an on-board full sector puffer. This means that data transfers are fully interruptable and can take place at any speed that is convenient to the system designer. In the event of an unrecoverable error, the HDC-2001 simulates a normal completion so that special error recovery software is not needed.

This section assumes that the user has read sections five (Task File) and six (Commands).

HDC-2001 HARD DISK CONTROLLER Technical Manual

# 6.1. Setting up Task Files

Before any of the five commands may be executed, a set of parameter registers called the Task File must be set up. For most commands, this informs the HDC-2001 of the exact location on the disk that the transfer should take place. For a normal read or write sector operation, the Sector Number, the Size/Drive/Head, Cylinder Number and Command register (usually in that order) will be written.

Note that most of these registers are readable as well as writable. These registers normally are not read from, but this feature is provided so that error reporting routines can determine physically where an error occurred without recalculating the sector, head and cylinder parameters.

Since the HDC-2001 can recall all the Task File parameters sent to it, it is recommended that Task File parameters be stored in the HDC-2001 as they are calculated. This will save the programmer a few instructions and microseconds by not maintaining two copies of the same information.

#### 6.1.1. Cylinders and Tracks

Since most hard disk drives contain more than one head per positioner, it is more efficient to step the R/W head assemblies of most disk drives by cylinders, not tracks. In other words, the disk driver software should be designed to read or write all data that is directly accessible by all the heads on a positioner before stepping to a new cylinder. The following example illustrates a cylinder-by-cylinder sequential file read on a four head, two platter disk drive:

| 1     | Physical<br>Cylinder | 1   | Logical<br>Head Number | 1 | Physical<br>Head Side | 1    | Physical<br>Platter |

|-------|----------------------|-----|------------------------|---|-----------------------|------|---------------------|

| ≁<br> | 25                   | 1   | 3                      | · | Тор                   | <br> | B                   |

| 1     | 26                   | - 1 | Ø                      | ì | Bottom                | 1    | A                   |

| 1     | 26                   | l   | 1                      | 1 | Тор                   | 1    | A                   |

| 1     | 26                   | :   | 2                      | ; | Bottom                | !    | В                   |

| 1     | 26                   | 1   | 3                      | I | Тор                   | 1    | в                   |

| 1     | 27                   | ì   | . 9                    | ţ | Bottom                | 1    | A                   |

#### 6.2. Type I Command Programming

Restore and Seek are Type I commands. These commands position the R/W heads of the selected drive and set the implied stepping rate register. No data is transferred to or from the Data Register. To execute a Type I command, the system software must do the following functions in this order:

1. Set up Task File and issue command with stepping rate

(HDC-2001 will attempt to execute Type I command)

- 2. Wait for interrupt or for Busy bit in Status Register to be reset

- 3. Check Error bit in Status Register for proper completion.

#### 6.2.1. Stepping Rates

Most drives that use the HDC-2001's 35 uS stepping rate require a slower rate (usually 3 mS or more) for Restore operations. This is why the HDC-2001 allows you to have explicit stepping rates on both Restore and Seek. Upon power up, it is good practice to issue a Restore command with a slower stepping rate to recalibrate the head assembly. After waiting for that operation to complete, issue a Seek command with the faster stepping rate to set the stepping rate for subsequent implied seeks.

#### 6.2.2. Use of Busy bit

There are two different ways to sense the completion of a command. The first way, for smaller single user systems, is to poll the Busy bit of the Status Register. The Bus bit (bit 7) is set whenever the controller starts a disk operation and is reset whenever the controller is ready to communicate with the host computer.

The HDC-2001 busy bit is located in the same place a the sign bit of many computers to simplify the polling process.

This is one way to poll this bit using 8080 code:

| WAIT: | IN  | STATUS | ;Input HDC-2001, update sign flag |

|-------|-----|--------|-----------------------------------|

|       | ANA | A      | ;Update 8080 sign flag            |

|       | JM  | WAIT   | ;Wait if busy (sign) bit set      |

#### 6.2.3. Use of Interrupts

Another more efficient way of notifying the CPU that the HDC-2001 has completed a command is through interrupts. The INTRQ line on the HDC-2001 makes a low to high transition whenever the disk controller requires CPU intervention. This allows the host CPU to run other tasks while the HDC-2001 is reading or writing data to the disk.

#### 6.2.4. Use of the Error bit

Since the HDC-2001 simulates normal completions, it acts the same whether or not errors are encountered. The only way to check error status is to check the Error bit in the Status register. The HDC-2001 Error bit is located so that it can be easily tested by rotating it into the carry bit of many processors. The contents of the Error register are not valid unless the Error bit is set. This is one way to check the Error bit using 8080 code:

| IN  | STATUS | ;Get status (if not already in A) |

|-----|--------|-----------------------------------|

| RAR |        | ;Rotate error bit into C          |

| JC  | ERROR  | ;Jump if error found              |

#### 6.2.5. Use of the Corrected bit

Correctable errors are usually quite benign and can almost always be ignored. However, some systems designers may wish to log their occurence. The Corrected bit is positioned in the Status register to facilitate error logging. Correctable and fatal errors can be detected with the following 8080 code:

| IN  | STATUS | ;Get HDC-2001 status               |

|-----|--------|------------------------------------|

| ANI | 5      | ;Mask off Error and Correct bits   |

| JNZ | SOMERR | ;Jump if we have either a correct- |

|     |        | ;able or fatal error               |

# 6.3. Type II Command Programming

The Read Sector command is the only Type II command. This command is characterized by the transfer of a block of data from the HDC-2001 buffer to the host. This command features implied seek with an implicit stepping rate. To execute a Type II single sector command in programmed I/O mode, the system software must do the following functions in this order:

- 1. Set up Task File and issue command with DMA bit reset (HDC-2001 will attempt to read sector)

- 2. Wait for interrupt or for Busy bit in Status Register to be reset

- 3. Do block move from HDC-2001 buffer to system memory

- 4. Check Error bit in Status Register for proper completion

Note: Steps 3 and 4 above can be reversed.

To execute a Type II single or multiple sector command in DMA mode with interrupts, the system software does the following:

- 1. Set up Task File and issue command with DMA bit set

- 2. Set up DMA controller (HDC-2001 will attempt to read single or multiple sectors) (DMA controller will move data from HDC-2001 to memory)

- 3. Wait for interrupt from HDC-2001

- 4. Check Error bit in Status register for proper completion

Note: The above sequence is preferred but steps 1 and 2 above can be reversed.

#### 6.3.1. DMA Mode

The DMA mode bit (D) in the above read sector examples is a special bit in

30

the command byte that is used to optimize the HDC-2001's interrupts during programmed I/O and DMA operations. If the DMA bit is reset (D=O) the interrupt will come before the buffer is transferred. This allows a programmed I/O host to intervene and transfer the buffer of data. If the DMA bit is set (D=1) then the interrupt will happen only after the data has been transferred. This allows the host to go uninterrupted until the entire buffer has been transferred.

#### 6.3.2. Block Moves

The HDC-2001 performs all transfers between it and the disk drive through an on-board full sector buffer. Once the disk has been read, the data is available to the host at any rate from DC to as high as a byte every 1.75 uS. In programmed I/O applications there is no need to consult the DRQ bit in the status register to determine if another byte is ready to be processed. Once an interrupt occurs or the busy bit is reset on a read, the host computer should do a block move of all the bytes in the sector.

The following 8080 code demonstrates a transfer from the HDC-2001 to system memory. The transfer address is in HL and the byte count is in B:

| READIT: | IN  | DATA   | ;Get data from HDC-2001 sector buffer   |

|---------|-----|--------|-----------------------------------------|

|         | MOV | м, А   | ;Store it in memory                     |

|         | INX | н      | ;Increment memory pointer               |

|         | DCR | В      | ;Decrement byte counter                 |

|         | JNZ | READIT | ;Do it again if whole sector not xfered |

The following Z-80 instruction does it all. The transfer address is in HL, byte count is in B and HDC-2001 data register address in C:

READIT: INIR

;Transfer buffer from HDC-2001 to memory

#### 6.3.3. Using DMA

There are several features in the HDC-2001 which simplify the use of DMA. Of course, there's the DRQ line that makes a low to high transition for each byte to be transferred. As mentioned earlier, there is a special bit in the Read Sector command which optimizes the HDC-2001 interrupts for DMA operation.

### 6.3.4. Multiple Sector Transfers

The HDC-2001 can transfer more than one sector per command if interfaced using DMA <u>and</u> interrupts. Transfers as large as an entire track can be executed. The Sector Count register holds the number of records to be transferred. (If Sector Count is zero then 256 records will be transferred.) The Sector Number register holds the starting sector of the transfer. When a multiple sector transfer is successfully completed, the Sector Count register will be equal to zero and the Sector Number register will be equal to the last sector transferred plus one.

31

PROGRAMMING

If a fatal error is encountered during a multiple sector transfer, the Sector Number register will be left pointing to the sector that contained the fatal error and the Sector Count register will hold the number of sectors that were not transferred.

If a correctable error is encountered during a multiple sector read, the corrected bit in the Status register will be set but the operation will not be terminated because correctable errors are not considered fatal.

### Partial Sector Transfers

The HDC-2001 allows partial sector transfers on read operations. This allows the user to read the first part of a sector and then discard the rest. During programmed I/O, the byte counter in the block move routine is set to the number of bytes to be read. During DMA operations, the DMA controller is set with the number of bytes to be transferred.

Normally the HDC-2.001 will interrupt the host after the sector has been transferred during a DMA read operation, but if a partial sector has been read, the HDC- $^{2}$ 001 will not know that the operation has been completed. For this reason, the 'transfer complete' interrupt must come from the DMA controller. There is, still, a problem. During write sector operations, the DMA controller will interrupt the system after the buffer has been transferred to the HDC- $^{2}$ 001 but before the data has been written. Some systems with advanced interrupt handling capabilities can easily mask off the spurious DMA interrupt. For those that can't, the HDC- $^{2}$ 001 has a provision built into its command structure to detect read operations.

#### Interrupt Source Selection

Bit 4 of all commands determines whether the operation will be a read sector operation or something else. Those commands that require the interrupt from the HDC-2001 have this bit set to a 1. The read sector command (the only one that might need the DMA controller's interrupt) has this bit set to a 0.

#### Clearing Hardware DRQ

During partial sector reads, the DMA controller will stop the DMA transfer before the HDC-2001 has a chance to issue its last data request. Because of this, the DRQ line may be set the next time transfer parameters are sent to the DMA controller. To avoid spurious (and often fatal) DRQ's, the user must do a hardware clear of the DRQ line. This is accomplished by reading or writing the Cylinder Low register. (This will only clear the DRQ line. The DRQ bit in the Status Register will be indeterminate.) This action is typically done before a subsequent read or write sector command in the normal course of updating the Task File. Care should be exercised to insure that the DMA controller has passed its parameters only after the Task File is updated.

#### 6.3.5. Simulated Completions