# How to maintain the CONSUL-580 and the MRD-380

pplied Digital Data Systems, Inc. 100 Marcus Boulevard, Hauppauge, N.Y., 11787

# HOW TO MAINTAIN THE CONSUL 580 & MRD 380

ADD8 Applied Digital Data Systems, Inc., 100 Marcus Blvd., Hauppauge, New York, 11787

### TABLE OF CONTENTS

- 1. INTRODUCTION

- 2. THEORY OF OPERATION

- 3. GLOSSARY OF SIGNAL NAMES

- 4. UNIT TEST PROCEDURE

- 5. PHYSICAL ACCESS FOR TEST AND REPAIR

- 6. TROUBLE SHOOTING CHART

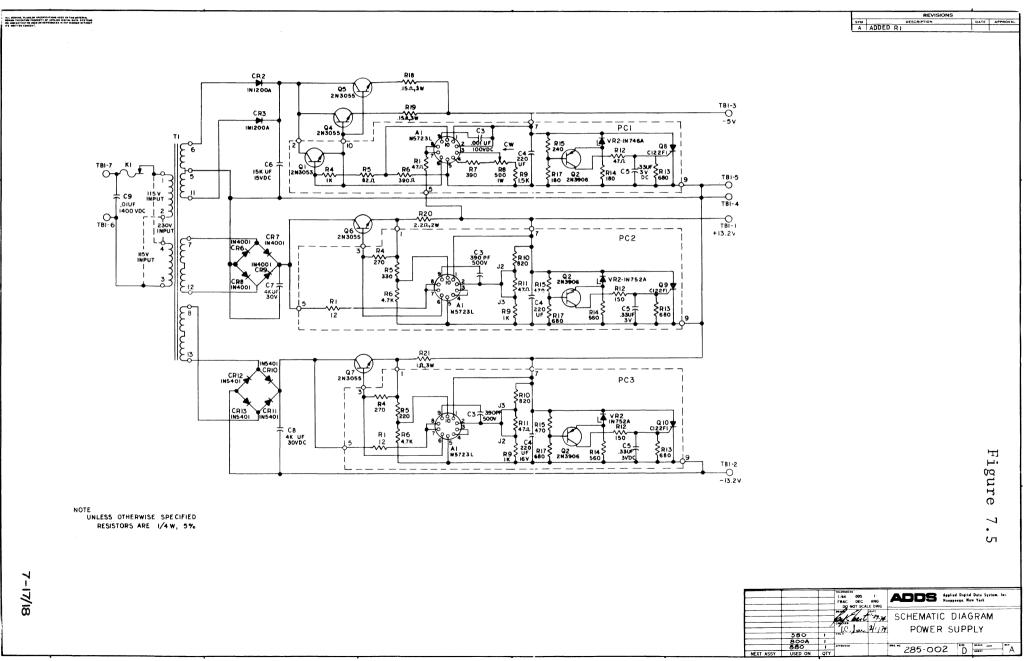

- 7. POWER SUPPLY SUBASSEMBLY

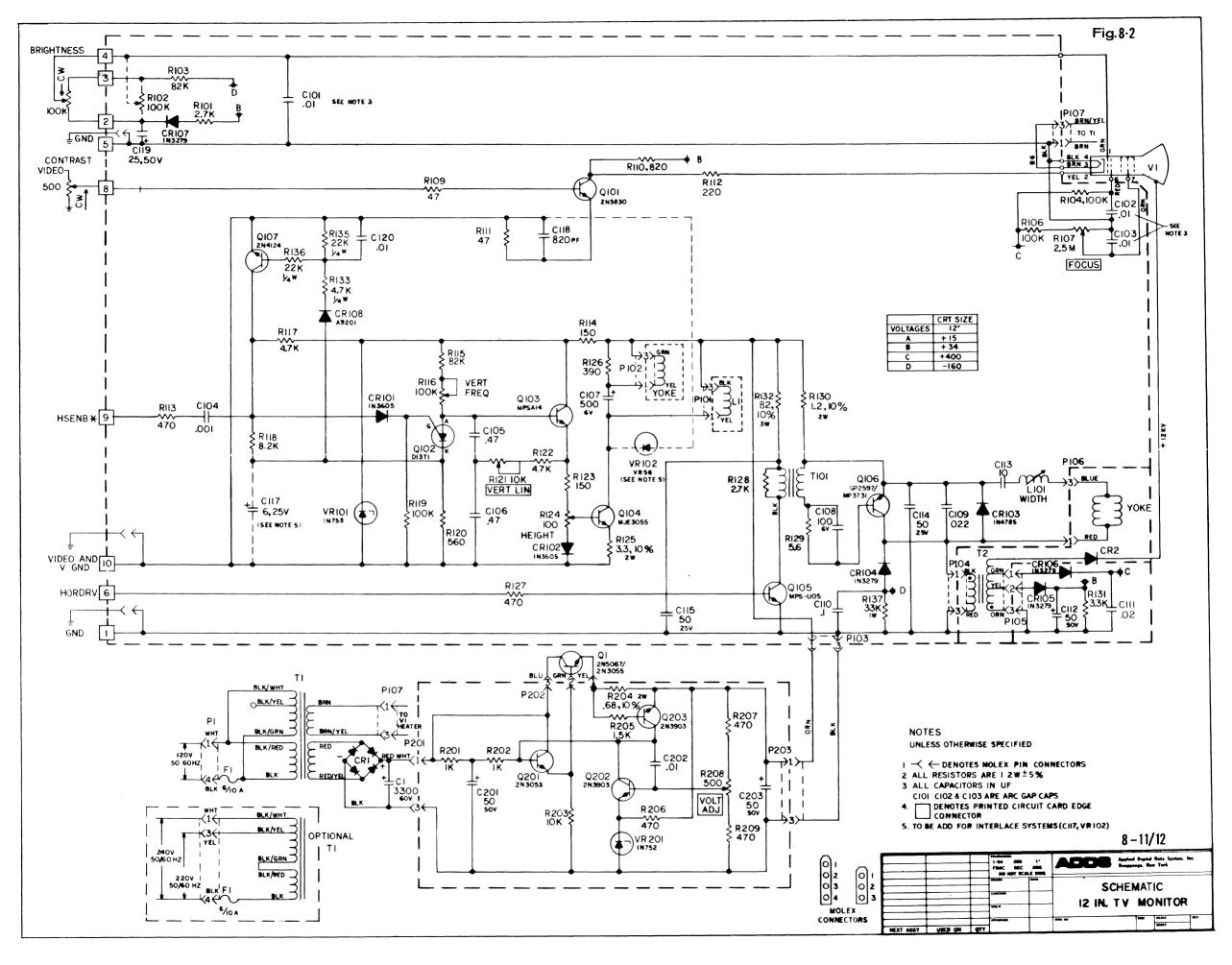

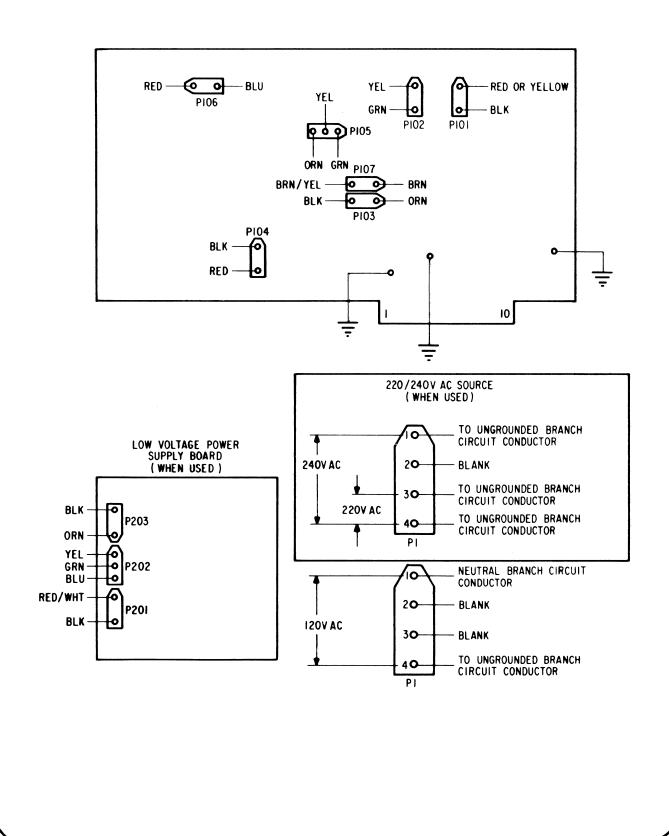

- 8. T.V. MONITOR SUBASSEMBLY

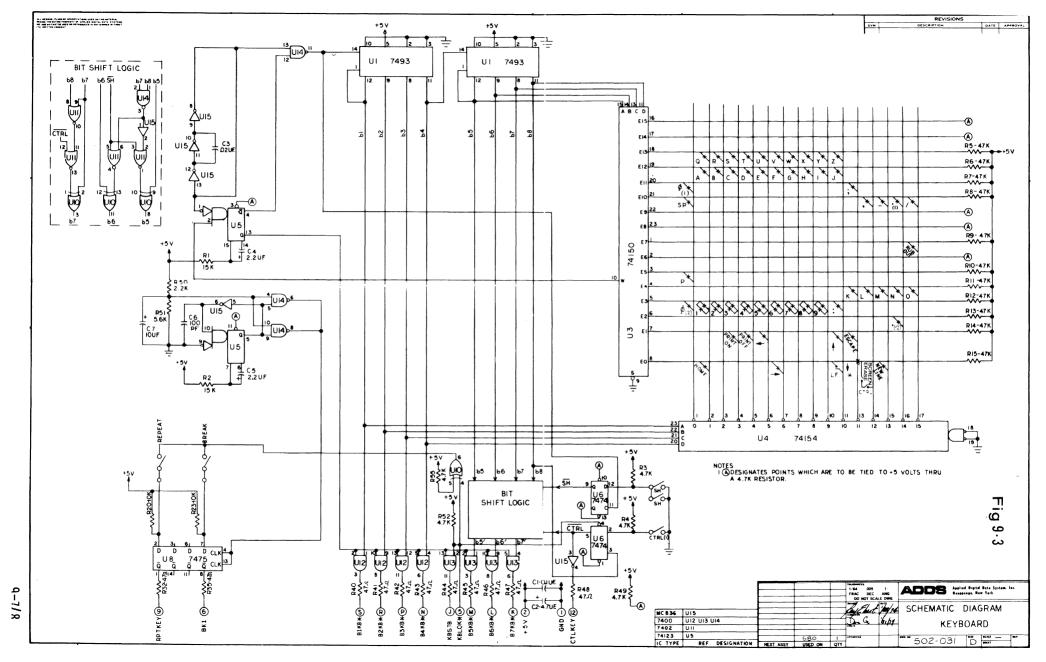

- 9. KEYBOARD SUBASSEMBLY

- 10. P.C. BOARDS SCHEMATIC AND ASSEMBLY DRAWINGS

- 11. WIRELIST AND HARNESS LIST

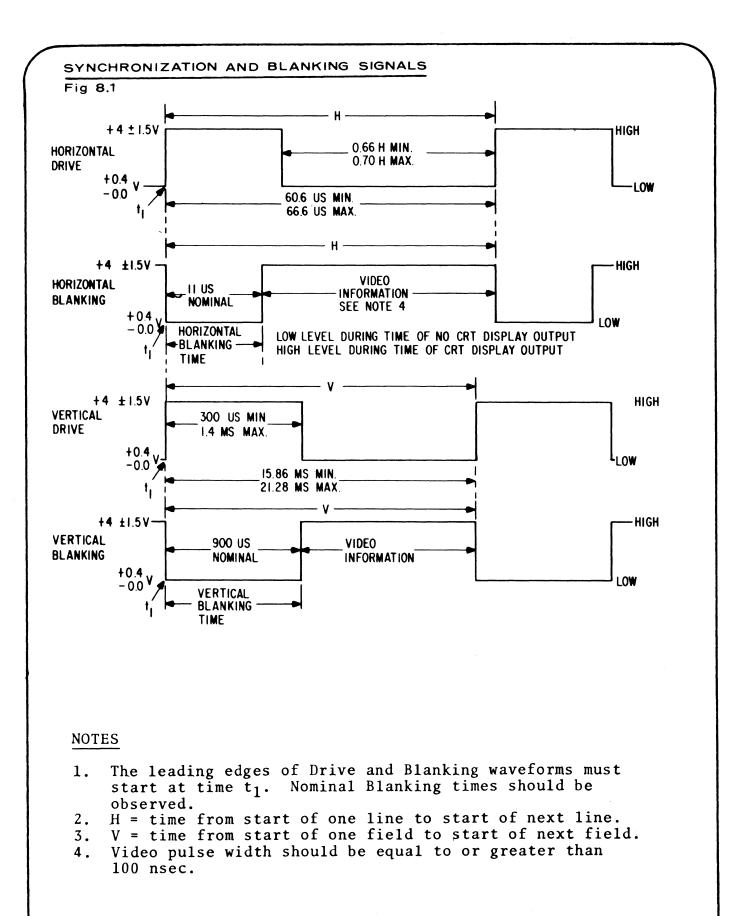

APPENDIX A - T.V. DISPLAY GENERATION

### 1. INTRODUCTION

This manual is intended for use by personnel who must perform fault diagnosis and repair of the Consul 580. The reader should be familiar with ADDS publication number 58-3000, <u>How to Use the</u> <u>Consul 580</u>, which presents complete operating instructions and interface information. Before proceeding with the theory of operation, salient terminal features are described below.

### 1.1 General Description

The Consul 580 is a low cost TTY compatible CRT display terminal. It is designed for users who wish to take advantage of a CRT's silent operation, fast transmission speed and inherent reliability. It is a self-contained desktop unit.

The 580 displays data in format of 24 lines with 80 characters per line - making a total of 1920 characters. Data is displayed as black characters on a white background. Communication with the data processing system or minicomputer takes place in a manner identical to that used by teletypewriters; a character at a time on a conversational basis.

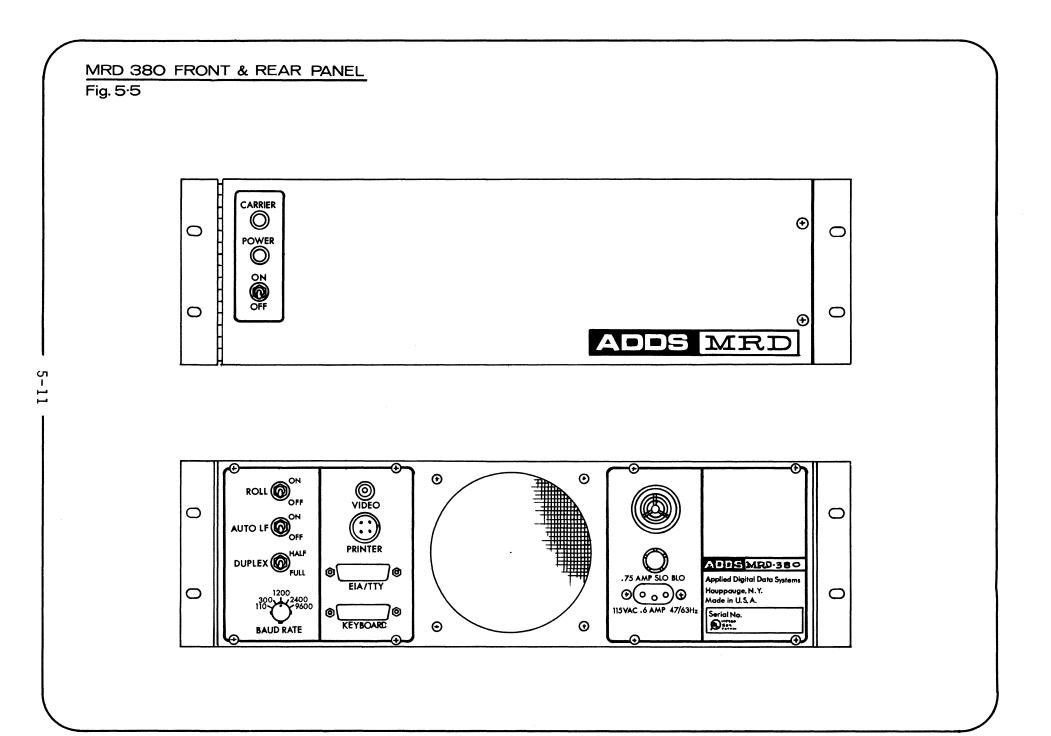

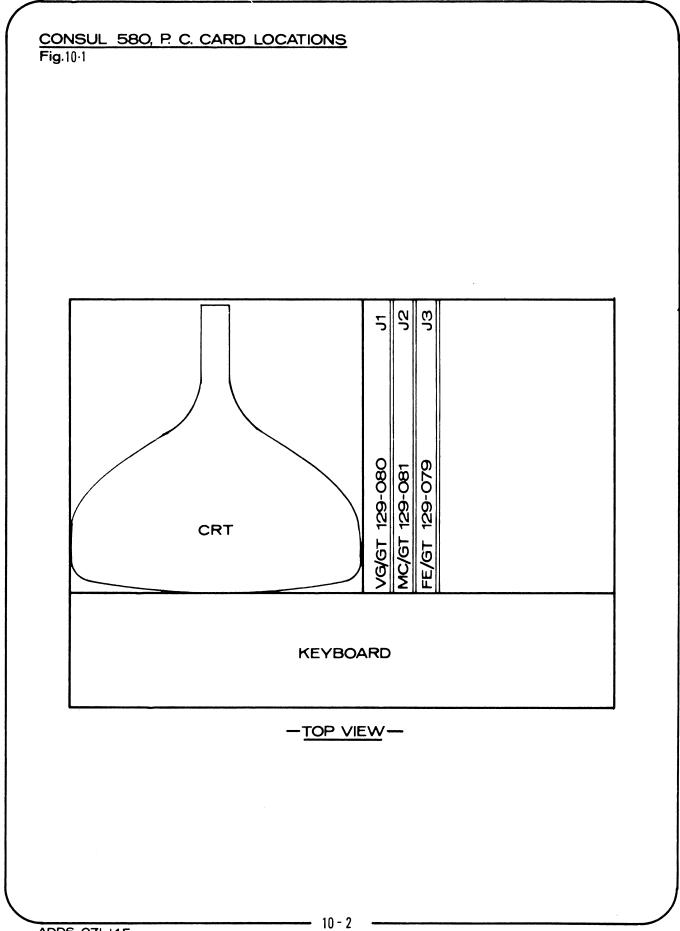

A rack-mountable version of the 580 is available; it is designated the MRD-380 Series. This equipment consists of:

- An electronics package which consists of the terminal electronics (same P.C. cards as the 580) in a chassis suitable for mounting in standard 19" RETMA racks. Vertical panel height is 5-1/4 inches.

- A separate keyboard, in its own housing, which plugs into the 380 electronics package.

- A TV monitor which connects via 75-0hm coaxial cable to the electronics package.

### 1.2 Summary of Terminal Features

### EIA and Current Loop Interfaces

An EIA RS232C voltage interface and a 20 milliampere current loop interface are standard; both are operational over the full speed range of the terminal - up to 9600 baud.

### Five Transmission Speeds

Transmission rates of 110, 300, 1200, 2400 or 9600 baud are

selectable by means of a switch on the rear panel of the 580.

### Selection of Half and Full Duplex

The operator's FULL DUP switch permits selection of full or half duplex operation.

### Automatic Line Feed Selection

A switch labeled AUTO LF allows the operator to inhibit or enable an automatic internal Line Feed after receipt of a Carriage Return code.

### Roll Mode Selection

The operator of a 580 can inhibit or enable the upward scrolling of data through use of the ROLL switch. Depressing this switch enables data to scroll upward if the cursor is in the bottom line and a Cursor Down or Line Feed command is received from the keyboard or CPU.

### Cursor Control

Cursor controls to position the cursor up, down, forward, backward and home are available. Home is the lower left corner of the screen when the 580 is scrolling data. When scrolling is inhibited, home is the upper left corner of the screen.

### Printer Interface

A printer interface allows attachment of any serial EIA printer. The operator can control the flow of data to the printer by using the PRINT ON and PRINT OFF keys on the 580 keyboard.

### Audible Alarm

The BEL code causes an audible alarm in the 580 to be activated.

### Remote Control

Remote control commands for the 580 are available to perform Carriage Return and Line Feed operations, erase the screen and move the cursor up, down, forward, backward and home. In addition, the CPU can lock and unlock the keyboard, activate the audible alarm and turn the printer interface on and off.

### Cursor Addressing

The computer can address the cursor to any given position on the screen. Addressing is provided by two command codes:

a Vertical Address command and a Horizontal Address command. Each of these commands is followed by a character that determines the desired cursor position. (This page intentionally left blank)

### 2. THEORY OF OPERATION

This section presents a block diagram overview of the 580 electronics, followed by a detailed circuit description at the chip level.

Diagrams which should be referenced when reading more than one page of the manual are designed as "fold-out" drawings to aid in following the discussion. An alphabetical Glossary of signal names is presented in Section 3 of this manual for convenience in following circuit descriptions.

- Note: Units delivered before January 15, 1974 differ in certain respects from units delivered after that date. Section 10 of this manual contains schematic drawings for both versions of the terminal. In areas where difference exist they are clearly called out in the circuit description. If any doubt exists about which version you have, put the terminal in Half-Duplex mode and press Control-G on the keyboard. If an audible alarm sounds you have the more recent version.

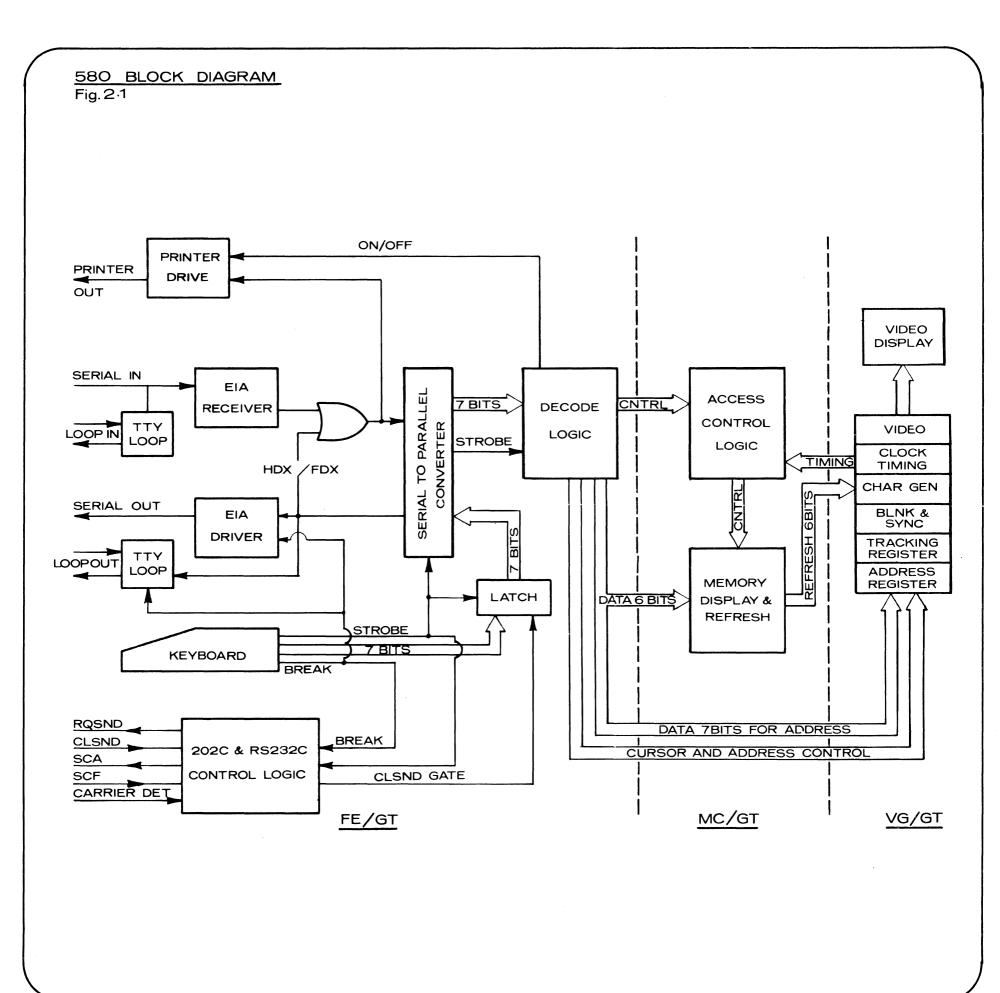

- 2.1 General Summary

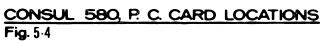

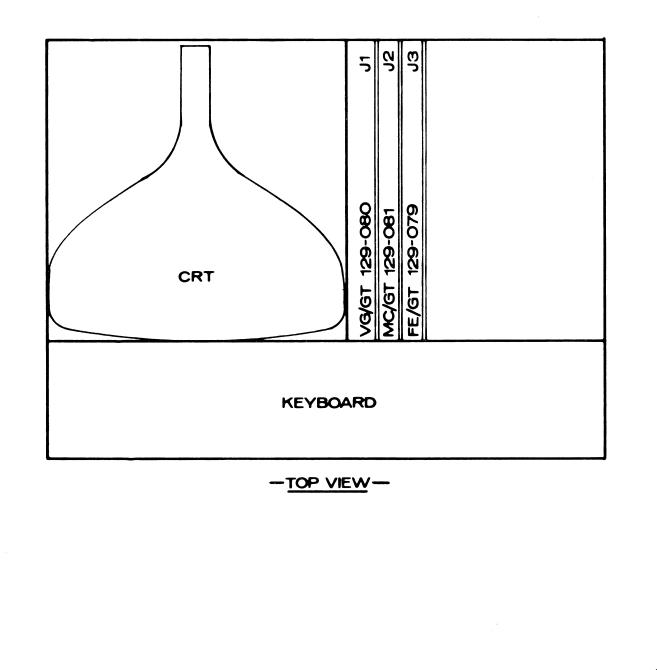

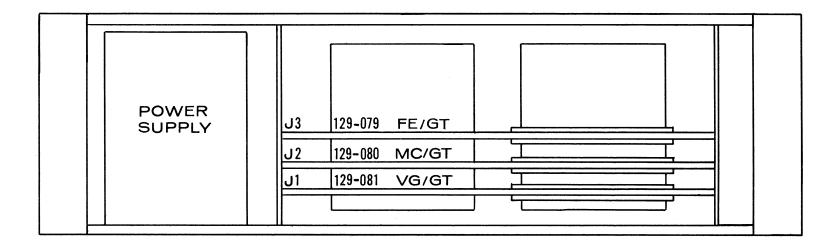

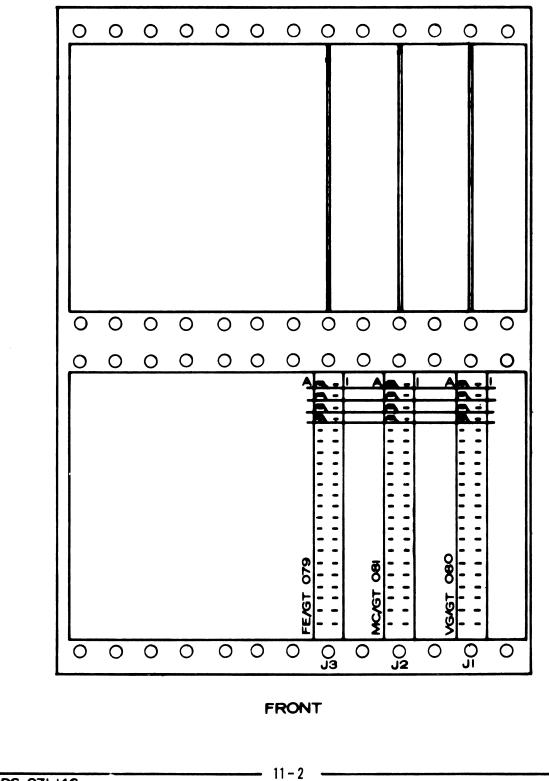

The Consul 580 electronics package is made up of three basic blocks, the Front End, the Memory and Control Logic and the Video Generator. Each block comprises one printed circuit card.

### 2.1.1 Front End

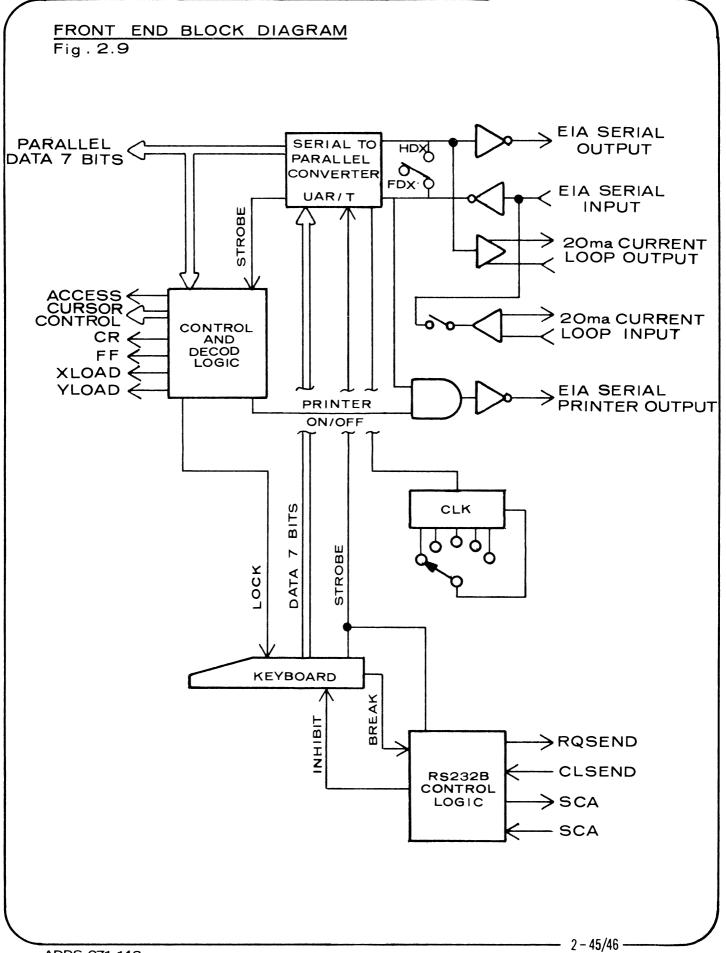

The Front End block contains the Serial to Parallel Converter, EIA level shifters, TTY current loop converters, keyboard interface, the control decoding logic, the baud rate clock, and the RS232C control logic.

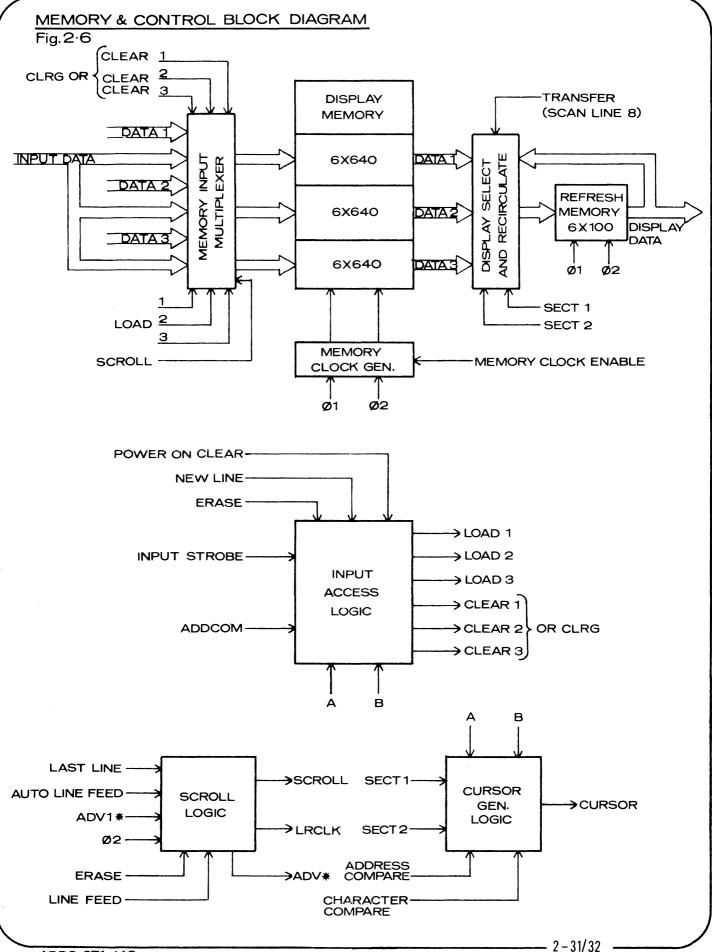

### 2.1.2 Memory and Control Logic

This block contains the Display Buffer memory, the one line Refresh Buffer memory, cursor generation logic, scroll logic, and the logic necessary to control access to the Display Buffer memory.

### 2.1.3 Video Generator

The Video Generator contains the master oscillator counters for controlling all video signals, the video amplifier and mixer, sync and blanking generator, Memory timing generator, character generator, Display Buffer address register, and the Address comparison circuitry for memory input. 2.2 Overall Block Diagram Description - (Figure 2.1, page 2-5/6)

The block diagram shows the three major sections divided by dashed lines.

### 2.2.1 Front End

### 2.2.1.1 Input Data Path

Input data to the Front End can be either current loop or EIA serial data. The serial data stream is converted to TTL levels and applied to the Serial to Parallel Converter (UAR/T, Universal Asynchronous Receiver/Transmitter) which changes the serial data to parallel data. The parallel data (a character) together with a strobe pulse is presented to the decoding and control logic. Ιf the character is displayable it is presented to the Memory and Control Logic for input to the Display Buffer memory. If the Character is an active control character (Erase, Carriage Return, Cursor Up, etc.) the control logic performs the proper task. If the character is from the sixth or seventh column on the ASCII chart (lower case) it is translated to columns 4 and 5 (upper case.) All other characters and Rubout are ignored by the CRT.

### 2.2.1.2 Output Data Path

Output data is generated only by the keyboard. When the user strikes a key, the ASCII code together with a strobe is presented in parallel to the output character latch. If the proper conditions exist at the RS232C control logic the character is passed on to the UAR/T with a strobe for parallel to serial conversion. The serialized character is then converted from TTL levels to EIA or current loop signals and passed on to the Modem or CPU.

### 2.2.1.3 Full/Half Duplex Modes

Full/Half Duplex is controled by a switch above the keyboard. In Full Duplex mode (switch depressed) the serial TTL output goes only to the level converters for output. When the FDX/HDX switch in the Half Duplex position (released) the TTL output data is applied to the serial input of the UAR/T. This causes the character from the keyboard to be treated as an input character from the CPU.

### 2.2.1.4 RS232C Control Logic

The RS232C Control Logic handles all the necessary control lines to and from the serial data connector. Request to Send is raised when the first character of a message is keyed. As soon as Clear to Send is true (from the Modem or CPU) the latched character is loaded into the UAR/T for transmission. The reverse channel signals SCF and SCA are also controlled by this logic.

### 2.2.2 Memory and Control Logic

### 2.2.2.1 Access Control

The Access Control accepts control signals from the Front End and performs the task requested. These tasks include data input, erase functions, and scrolling. In addition there is logic to generate the cursor and logic to handle the updating of the one line Refresh memory.

### 2.2.2.2 Display Buffer

The Display Buffer memory is composed of MOS shift registers that recirculate their contents at a 1.6 MHZ shift rate. The memory is modular in that it is divided into three sections. Each section has a capacity of 3840 bits or 640 6-bit characters.

### 2.2.2.3 Refresh Memory

The Refresh Memory has a capacity sufficient to hold 100 6-bit characters out of which only 80 are used for display. This MOS shift register is used to hold one line of characters during the time the Video Generator is generating that particular line of data on the T.V. screen. It is updated from the Display Buffer before the next line is to be displayed.

### 2.2.3 Video Generator

### 2.2.3.1 Character Generator

The Character Generator accepts one character at a time from the Refresh memory and then outputs the proper portion of the character to be displayed. The line of characters in the Refresh memory is presented to the Video Generator seven times to complete the display of that data line.

### 2.2.3.2 Blank and Sync Generators

The Blank and Sync generators mix their signals with the display video to produce the proper signals to frame the data and drive the T.V. monitor.

2.2.3.3 Clock and Timing Chain

The Clock and Timing Chain is used to generate all the timing concerned with the video presentation and the memories.

### 2.2.3.4 Address Register

The Address Register contains the address of the next location in which a character may be entered into the Display Buffer.

### 2.2.3.5 Tracking Register

The Tracking Register counts the shift pulses to the Display Buffer. Its contents at any given time contain the address of the Memory Buffer location that may be accessed.

### 2.3 Detailed Description - Video Generator

The Video Generator will be discussed first because a large portion of the overall timing and control is generated by this P.C. card.

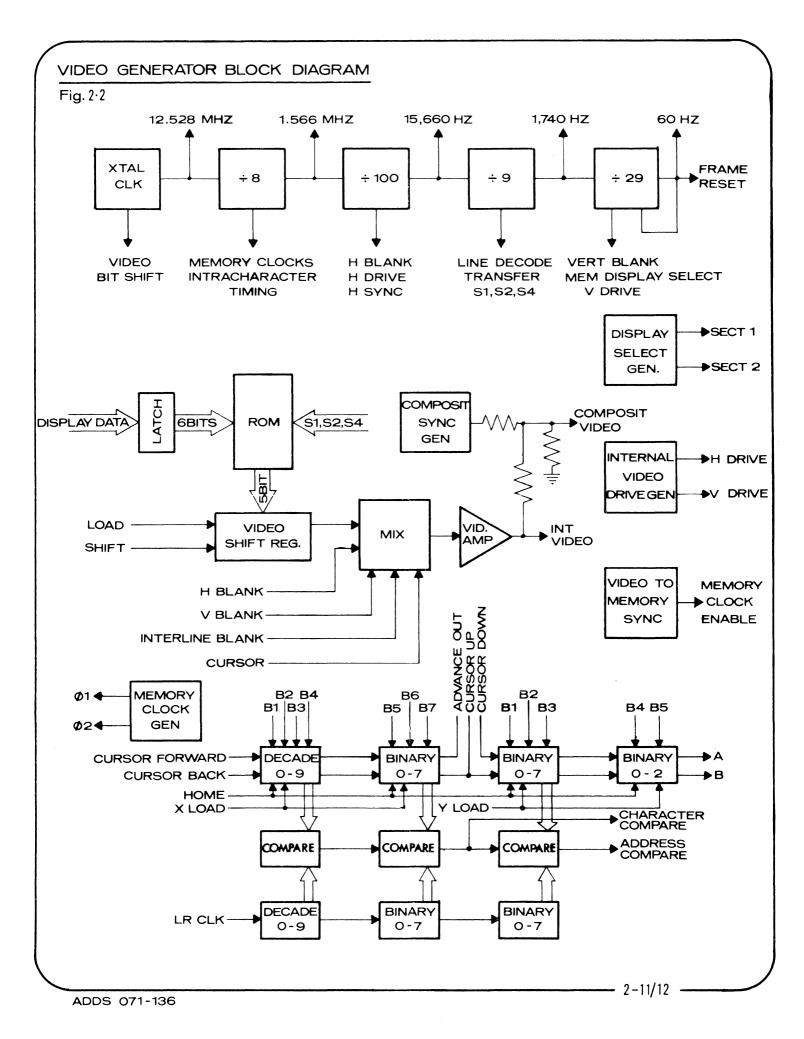

## 2.3.1 <u>Video Generator Block Diagram Description</u> (Figure 2.2, page 2-11/12)

### 2.3.1.1 Clock and Timing Chain

The heart of the Video Generator is the crystal clock and count down timing chain. The clock is a square wave generator with a frequency of 12.528 MHZ. This is the video shift frequency or the rate at which the individual bits of a character are written on the T.V. screen.

The first counter divides this by 8 to a frequency of 1.566 MHZ which is the rate at which complete characters are written on the screen. Timing is derived from this counter for all intracharacter clocks and strobes.

The character rate is then divided by 100 to produce the video scan line rate of 15,660 HZ. The signals Horizontal Blank, Horizontal Drive, and Horizontal sync are decoded from this counter.

The next counter divides by 9 to obtain the character line rate of 1740 HZ. Seven of the video scan lines are used to generate the data line and two are used for separation and the cursor mark. The counter outputs are used by the ROM (Read Only Memory) Character Generator to determine which one of the seven horizontal segments of a character should be output to the video.

The last counter divides down to the screen refresh rate of 60 HZ (50HZ for overseas models). Signals such as Vertical Blank, Vertical Drive and Memory Select are obtained by decoding this counter.

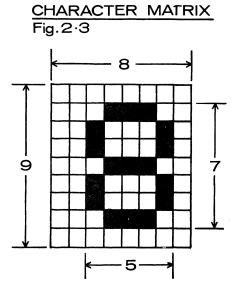

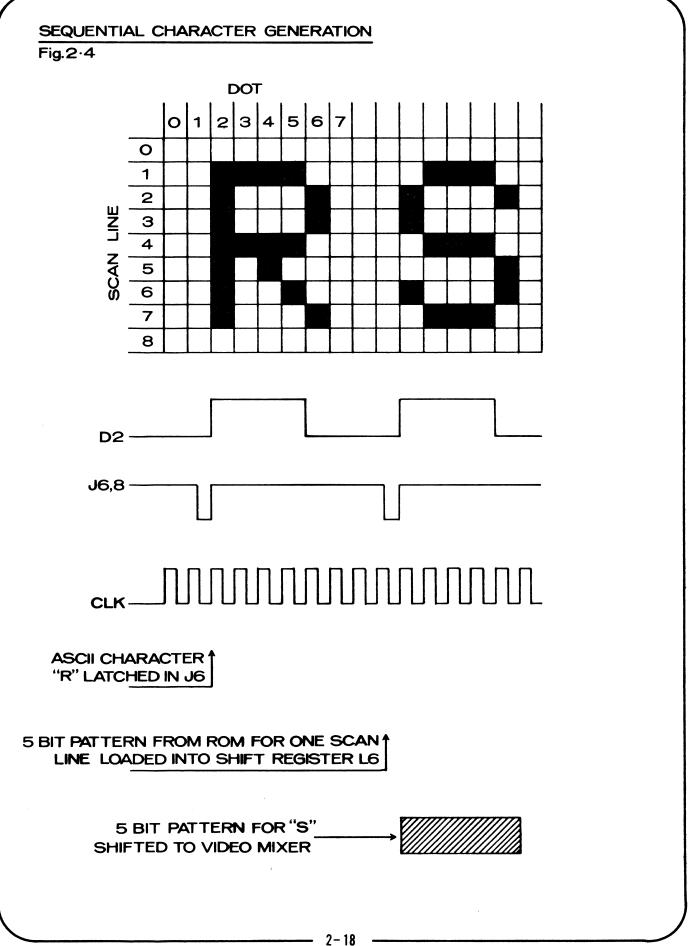

### 2.3.1.2 Character Generator

The 580 employs a 5 x 7 dot matrix to generate the 64 displayable characters. Each 5 x 7 character is displayed in an 8 by 9 field. (see Figure 2.3 at top of next page) This gives a three dot horizontal spacing between characters and a two scan line spacing between rows of characters.

To generate a character on the screen the Read Only Memory, ROM, must supply seven five-bit words to the video shift register, one for each of the seven scan lines used to display the character. During each scan line at the given character position the video shift register shifts the five bits to the video mixer at the 12.528 MHZ rate. These bits make the video black for ones and white for zeroes, assuming a normal black on white presentation.

The pattern in the ROM is selected by the 6-bit (1 of 64) character latched from the Refresh Buffer memory. This 6-bit word is used as an address to select one of the 64 possible dot patterns. The three inputs S1, S2, and S4 are bits from the scan line counter which select which one of the seven five-bit words is to be output by the ROM.

### 2.3.1.3 Video Mixer and Amplifier

The character bits from the video shift register are mixed with Horizontal Blank, Vertical Blank, Interline Blank and the cursor mark. The Horizontal and Vertical blank signals always cause the screen to be black. The interline blank causes the screen to be white for black-on-white characters and black for white-on-black characters. The cursor mark always inverts the contrast of the interline blank signal.

The video amplifier takes the mixed signal and drives the internal monitor with a 0 to +5V signal. This same output is also resistively mixed with a composite sync signal to generate a 1V. peak-to-peak composite video signal for external monitors.

### 2.3.1.4 Display Select Generator

Since the Display Buffer is divided into three modules the video generator must select from one of the three sections to request a new line of characters. The outputs SECT 1 and SECT 2 are used by the Memory and Control card to load the Refresh Buffer memory with the proper line of data. SECT 1 and SECT 2 are low for the top third of the screen. SECT 1 is high for the middle and SECT 2 is high for the bottom. These two signals are obtained from the last counter in the countdown chain which is counting groups of 9 scan lines, or data lines.

### 2.3.1.5 Internal Video Drive Generator

The internal monitor (Consul 580 only) requires separate signals for Vertical and Horizontal drive. These are TTL levels and are decoded from the timing chain.

### 2.3.1.6 Memory Clock Generator

All the timing for the memory shift registers is obtained from the Dot Counter. The two phases  $\emptyset 1$  and  $\emptyset 2$  are TTL level 25% duty cycle pulses.

### 2.3.1.7 Memory Address and Tracking Registers

The Memory Address register is made up of four counters. The first is a decade counter (0 - 9). The second is binary and counts from 0 to 7. These two counters together determine a single line (0 - 79 characters). The third counter counts from 0 to 7 which represents the number of 80-character lines in any one memory module. The last counter is a count of three (0 - 2) which determines which of the three memory modules is to be accessed. All four are synchronous up/down counters. The Address Counter is static and can be changed by the cursor controls or by direct addressing. The contents are automatically updated by an access to memory.

The Tracking Register is made up from three counters which are the same as the first three stages of the Address Register. This keeps track of the position of the circulating Memory Buffer registers. Since the three memory modules are running in parallel only eight lines of eighty characters (one module) have to be tracked. A comparison is made between the Tracking Register and the Address Register. When they have the same value it means that the Memory is at a position such that the character at the location indicated by the Address Register may be accessed. A sub-comparison of only the horizontal location (one of 80 positions) is also made and is used by the Memory and Control board to generate the cursor.

### 2.3.1.8 Video to Memory Sync Circuit

When the Video Generator finishes a complete scan of the screen the Display Buffer memory is not in sync with the video. The memory sync circuit causes the memory to pause every other scan line until the system is back in sync again.

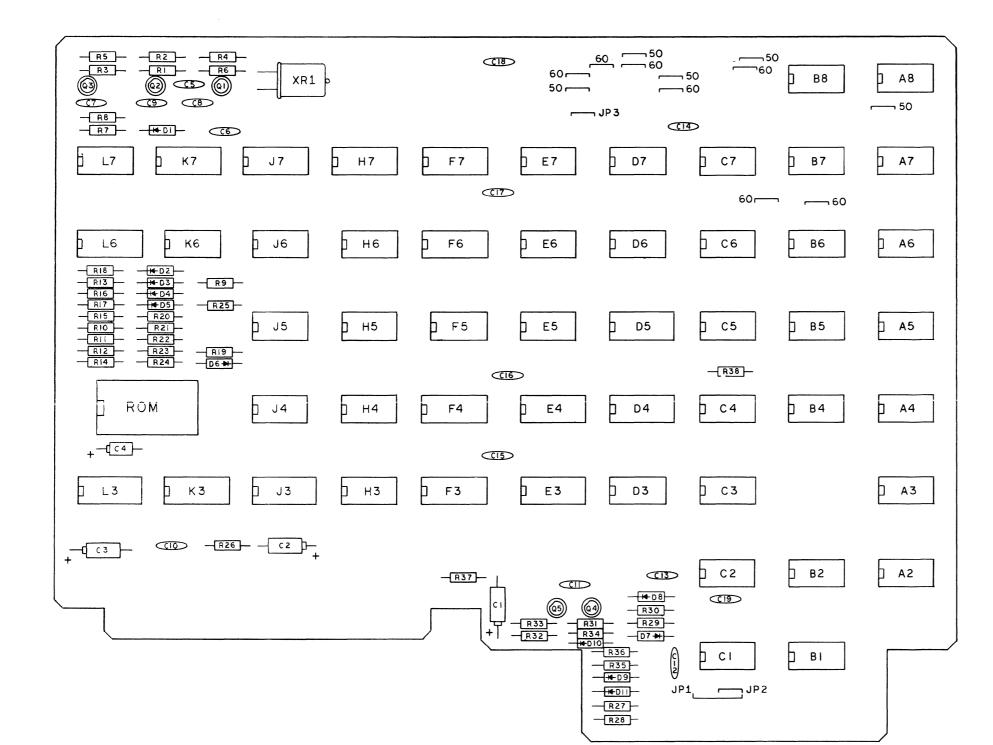

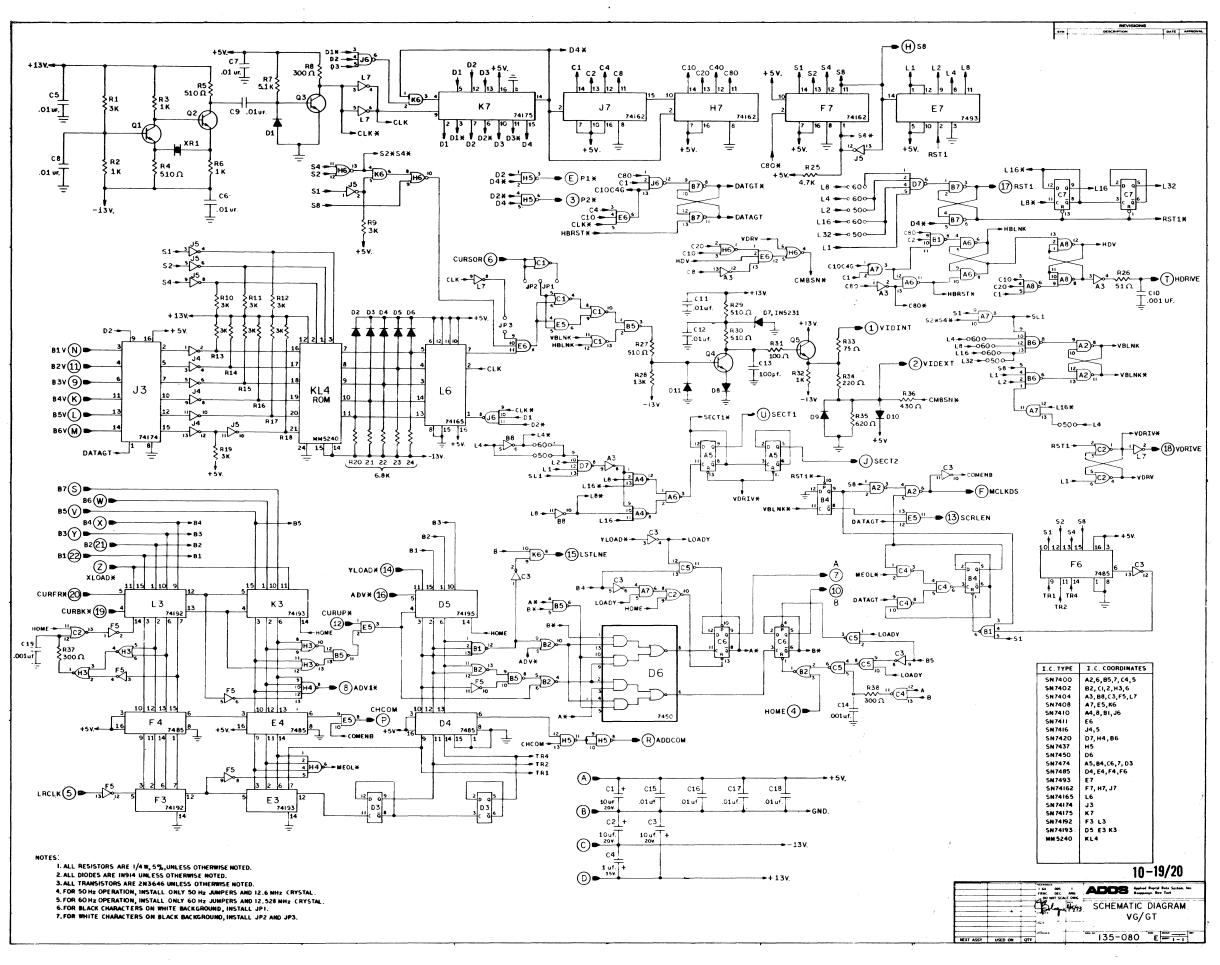

### 2.3.2 Circuit Description - Schematic #135-080

### 2.3.2.1 Clock and Timing Chain

The crystal oscillator is located in the upper left corner of the print. It consists of a common base amplifying stage Q1, driving an emitter follower, Q2, which drives the crystal in the feedback path. The output signal is picked off the collector of Q2 to avoid disturbing the oscillator circuit and drives Q3 in switching mode. The diode, D1, is used to insure a symmetrical load on Q2 and also to protect the base of Q3 from excessive negative voltage. The collector of Q3 drives two Schottky hex inverters (L7,3 and L7,5) in parallel to provide the main clock signal, CLK.

The signal, CLK (12.528 MHZ), drives the first stage of the timing chain K7. K7 is an SN74175N, a quad D-type flip-flop. K7, the Dot Counter, is used as a Johnson or Ring counter. The stages are wired as a shift register with the last stage's complimented output fed to the first stage input. This causes the register to sequentially fill with ones, then zeroes. An entire period takes eight clock pulses. Since only one stage changes state at a time, any state may be decoded with a two-input gate. The three-input nand gate, J6, is used to insure that no illegal state, such as 1010, may exist for more than one period. All intracharacter timing is derived from this counter.

The output of the Dot Counter, D4\* (1.566 MHZ or 639 nanoseconds) represents one character time and drives the decade counter chip J7. J7 is an SN 74162 which is a synchronous decade counter. The carry output from J7,15 and the clock, D4\* drive the next decade counter H7. These two chips, the Character Counter, perform a divide by 100 which represents one video scan line including Horizontal sync and blank times. The period of this counter is 63.9 microseconds or 15,660 HZ.

The output of H7 is inverted and applied as C80\* to the input of F7, another decade counter. This chip is wired such that the output S8 is inverted and fed to the synchronous clear input on pin 1. When S8 goes high, the next clock signal at pin 2 will clear the chip to all zeroes resulting in a divide by 9 function. This is the Scan Line Counter and its outputs S1, S2, S4, and S8 are used for timing within one data line of characters.

Finally, the output S8 drives a binary ripplethrough counter consisting of E7, an SN7493N, and C7, an SN7474 wired in toggle mode. This is the Data Line Counter. For 60 HZ devices it counts 29 data lines (261 scan lines) and then is reset to zero. For 50HZ the count is 35 data lines or 315 scan lines. The crystal frequencies 12.528MHZ for 60HZ devices and 12.6MHZ for 50HZ devices were picked to produce a 60HZ or 50HZ refresh rate, while keeping the number of scan lines an integral of 9.

The signal RST1 is the reset signal for the Data Line Counter and is generated by the cross-coupled latch B7,3 and B7,6. The latch is set by the four-input nand gate D7,5. Its output goes low for a count of 29 or 35, setting B7,3 high. The other half of the latch is driven by D4\* which has just gone true. One half character later D4\* goes false, resetting the latch. Meanwhile, RST1 has reset E7 and RST1\* has reset both halves of C7. K7, J7, H7, and F7 returned to zero when E7 and C7 reached the reset count.

### 2.3.2.2 Horizontal Timing

### 2.3.2.2.1 Horizontal Blank

The Horizontal Blank signal determines the size of the white page on the screen in the horizontal dimension. One character space is left at each end of the 80-character line to form a border resulting in an 18-character time blank signal. HBLANK (A6,6) is set true when a count of 97 (C80, C10, C4, C2, C1) is reached by B1,8 going false. C10C4G is a combination of C10 and C4 with a Strobe CLK\* (see three-input "and" gate E6,6). HBLANK resets at a count of 15, (C80\*, C10, C4, C1), resulting in a blank time of 18 characters.

### 2.3.2.2.2 Horizontal Drive

HDRIVE is used by the internal monitor to develop the horizontal sweep. It begins with HBLANK and ends at character position 31 (C20, C10, C1).

### 2.3.2.2.3 Horizontal Sync

This signal is needed by an external monitor in order to synchronize tis horizontal oscillator. It is contained within the combined sync circuit (section F-4) and is the output of E6,12. It starts during HDV when C8 returns false (character position 0) and lasts until C8 goes true again (C10 and C20 are low). When C8 goes false again, either C10 or C20 is high keeping E6,12 low. This results in a horizontal sync pulse lasting for 8 character times or 5.1 microseconds.

### 2.3.2.2.4 Data Gate

DATAGT is a signal lasting for 80 character times or 51 microseconds. This period is the time during which the Display Buffer memory shifts (80 shifts). During the balance of the scan line time (12.8 microseconds) the memory pauses. DATAGT is used to begin the shifting and also to gate one line of data from the Display Buffer to the one line Refresh Buffer.

DATAGT is the output of a cross-coupled latch (Section G-4) B7,11. Since there is a one character delay time through the ROM, DATAGT must start one character time before the first character is displayed on the screen. Since there is a one character boundary, DATAGT may begin when HBLANK ends. Note that B7,13 is driven low by the same signal that resets the HBLANK latch (HBRST\*). HBRST\* occurs at character position 15. For 80 characters therefore DATAGT must end at character position 95. Note that J6,12 will pulse low at location 95 (C80, C10, C4, C1, CLK\*). The input CLK\* is used as a strobe to insure no false clocking.

### 2.3.2.3 Vertical Timing

### 2.3.2.3.1 Vertical Blank

The vertical blank signal, VBLNK, (Section F-1) is generated by a cross-coupled latch A2,8. This signal determines the top and bottom borders of the white page. To allow for one scan line under the cursor in the bottom line, one scan line is added to the page after the last data line. To keep the page symmetrical, a scan line is also added to the top of the page, allowing two scan lines of white above and below the top and bottom data lines.

For 60HZ devices, VBLNK starts when scan line one, SL1, goes true during data line 28 (L16, L8, L4). VBLNK remains true until scan line 9 (S8 true) of data line 3 (L16\*, L2, L1) goes true.

For 50HZ devices, VBLNK begins during data line 32 and ends during data line 7.

2.3.2.3.2 Vertical Drive

VDRIVE (Section E-1) is used by the internal monitor and as part of combined sync by the external monitor to initiate the Vertical flyback. It starts with the reset pulse RST1 and ends when L1 returns true 9 scan lines later.

### 2.3.2.3.3 Memory Module Selection

Since the three sections of the Display Buffer memory are multiplexed at their outputs, the proper section must be selected for input to the one line Refresh memory. The signals SECT 1 and SECT 2 control this gating and are generated by the flip-flop pair A6 in Section E-4.

VDRIV\* is used to set both flip-flops to zero which selects Display Buffer module 1. The gating is done on the Memory and Control board. When the first eight data lines have been displayed, A4,12 pulses low (Data line 11 + Scan line 1) setting A5,9 true. This conditions the Memory and Control card to present the next 8 data lines from the second memory module. After 8 more data lines, A4,8 pulses low (Data line 19 + Scan line 1) resetting A5,9 and setting A5,5 which causes the Memory and Control card to present the last 8 data lines from the third memory module. For 50HZ, these decodes are all increased by 4 Data lines to center the display in the larger number of scan lines.

### 2.3.2.4 Character Generation and Video Mixing

### 2.3.2.4.1 Basic Dot Matrix

As mentioned earlier, the 580 uses a 5 X 7 matrix to generate the displayable char-

acters. (See Figure 2.4) The character field is an 8-dot wide by 9-scan line high "window". The character is generated within this field in dot positions 2 through 6 and scan lines 1 through 7. It is evident that the ASCII character information for R and S must be available for at least seven scan lines sequentially in order to generate the two characters or the entire line. Each time a scan line is swept across, a 5-dot portion of the character is generated.

The data line consists of 82 windows, 80 of which are used to display characters. The first and eighty-second windows are always spaces and are used as a margin for the white page. There are 24 such data lines in an entire page for a total of 1920 characters.

### 2.3.2.4.2 Read Only Memory (ROM)

An ROM (Section E-6) is used to store the 64 displayable patterns of 5 X 7 dots. Each pattern is broken down into seven 5-dot words or slices.

Each of the patterns or cells is associated with a 6-bit address (0-63). This address is the same as the ASCII code for the character. For example the ASCII code for an R is 010010-(bit 6 through bit one). This indicates cell #18 which contains the bit pattern for an R. Each five-dot word is addressed by three bits (0-7). The Scan Line Counter bits S1, S2, and S4 are used to address the proper word within a cell. For example, the third 5-bit word of an R pattern is 10001 and is addressed by S1 = 1, S2 = 1 and S4 = 0, which is the state of the Scan Line Counter during the third scan line. The ROM supplies the 5-bit word in parallel at its outputs that corresponds to the selected word in the selected cell.

The ROM used is a static design, which means that the word appears at the output as long as the input address remains stable. Upon an Address change, for instance from the R to the S, that output change is guaranteed to become stable within a maximum of 600 nanoseconds. The character change rate is 639 nanoseconds.

### 2.3.2.4.3 Generation of One 5-bit Character "Slice"

Since the worst case delay through the ROM is 600 nanoseconds, a one character delay is used to allow time for the first character in a line to set up. Using the S as an example in Figure 2.4, note that the ASCII code for S is latched in the holding register J3 by the signal D2; DATAGT became true on the leading edge of D1 allowing D2 to clock the flip-flops. The 5-bit word for the scan line determined by S1, S2, and S4 is stable at the inputs of L6 prior to the load pulse at J6,8. When J6,8 pulses low the 5-bit word is transferred to the shift register L6. The next clock pulse (CLK) on L6,2 shifts the bit pattern by one stage and applies the first bit of the word to the output pin 7. A one in the bit pattern will produce a high level in the shift register and a zero will produce a low level. For the fourth scan line, the 5-bit word would be 01110 which would produce the horizontal middle three dots of the "S". As the first dot of the "S" word is shifted into the output stage the next character to be displayed is latched in the holding register J3.

The output of the shift register is then "AND"ed with an signal that is true for scan lines 1 through 7 and false for 0 and 8. For a black-on-white presentation the jumper JP1 is installed which enables AND gate E5,5 when the CURSOR signal is low. The character bits are passed by E5 to C1 which inverts the level. B5,1 then inverts again and drives the base of Q4. For a "one" B5,3 is true which turns Q4 on. This causes a low level (0.7V) at the collector and drives the emitter of Q5 to 0 volts which is black on the CRT. Α zero bit level causes a +4.3V level at the emitter of Q5 which is white on the CRT. The capacitor C13 is to shape the signal suitably for the monitor's input amplifier. At the same time the internal monitor is receiving a 0 or +4.3 volt signal, the external monitor receives a 0.3V to 1V signal through the resistor network R34, R35, and R36. (CMBSN\* is normally high.)

### 2.3.2.4.4 Blank Mixing

In section F-5 the Vertical Blank, VBLNK, and the Horizontal Blank, HBLNK, are applied

through the NOR gate C1,11 and C1,13 to one input of the NAND gate B5,2. When either level is high, B5,2 is blocked causing B5,3 to be high which in turn causes black on the CRT screen regardless of the state of the data signal on B5,1.

### 2.3.2.4.5 Combined Sync Mixing

The signal CMBSN\* in Section E-2 is normally high. At the end of each scan line it pulses low for 5 microseconds to provide a OV level signal at the external video output (.3V sync, .7V video). At the bottom of the screen, CMBSN\* goes low for 9 scan lines to generate the vertical interval step for vertical flyback. The diodes D9 and D10 are to protect the external output from a monitor failure.

### 2.3.2.4.6 <u>Miscellaneous</u>

The discrete components around the ROM are needed to supply the proper levels to the device. Input levels must be between ground and +13V. The output drives must be sinked to a negative voltage and caught at +5V by diodes D2-D6 to operate properly with TTL circuits.

In the Video amplifier circuit, the Zener Diode D7 is used to establish a stable +5V switching level independent of TTL switching noise.

The signal CURSOR is generated by the Memory and Control P.C. card. It goes true for 639 nanoseconds in Scan Line 8 under the character whose address is held by the Memory Address Register. This causes an inversion in the background which results in a black underline of white underline depending on the screen background presentation.

### 2.3.2.5 Address and Tracking Register

The address of the next Display Memory location to be accessed is held by the Memory Address Register consisting of L3, K3, D5 and C6. L3 is an SN74192N, a synchronous up/down decimal counter. This drives K3, an SN74193N, which is a four-stage synchronous up/down binary counter. The two in tandem count from 0 to 79 (only the first 3 stages of K3 are used) or one 80-character line. This portion indicates the horizontal position of the character. The next counter is another SN74193N and is used to indicate which of the eight lines in one memory module contains the character of interest. Finally the two D-type flip-flops of C6 are wired as a synchronous up/down tertiary counter (count of three). This last counter is used to indicate in which of the three memory modules the character location of interest lies.

The Tracking Register is counted by the shift pulse (2) of the Display Memory and indicates which location in any given module is available for access. Its output is stable for one character time and increments at a 1.566 MHZ rate. This register is constructed in the same way as the Address Register in that the first stage is a decade counter, followed by a binary counter. F3 is the decade counter and E3 is a binary counter. Since the three memory modules are shifting together in parallel, only eight lines of 80 characters (one memory module) need be tracked. The last stage of E3 and the two stages of D3 make up the 0-7 counter for the line portion. F3 and the first three stages of E3 made up the character portion.

The three chips F4, E4, and D4 are dual four-bit comparators. These three chips are used to generate a signal that indicates when the memories are at the location held by the Address Counter. This is done be comparing the contents of the character and line portion of the Address Register with the Tracking Register. F4 and E4 compare the character portions and generate a signal named CHCOM, Character Comparison. The output of E4 is gated by COMENB (Comparison Enable) which is true when the memories are not pausing for line end or memory synchronization.

CHCOM is then used with the output of D4 to generate ADDCOM (Address Comparison), the combination of CHCOM and the Line Counter comparison. ADDCOM lasts for 639 nanoseconds and occurs every 510 microseconds except during the memory synchronization time, during which it occurs every 574 microseconds.

The Address Counter is controlled in two basic ways, incremental control and direct addressing. The incremental control is by use of the cursor position keys. The signals generated by the control keys are CURFR\* (Cursor Forward Not), CURBK\* (Cursor Back Not), CURUP\* (Cursor Up Not), ADV\* (Advance Not, which is cursor down) and HOME. CURFR\* is also automatically pulsed when a memory location is accessed. The signal ADV\* is generated from the Cursor Down key or the Line Feed key. It is also automatically generated when the last character in a line is accessed if the terminal is in the Auto Line Feed mode.

The circuitry around L3 is used to insure that an illegal address (greater than 9) can't be stable in the decade register. If stages 2 or 3 are true when stage 4 is true, indicating a number greater than 9, H3,1 will go true. After a delay of 300 nanoseconds (R37 and C19) the reset input L3,14 goes true and resets the counter to all zeroes. The reset level lasts for 300 nanoseconds because of the delay.

The circuitry below K3 is used to generate the line up or down signals necessary when the cursor is made to move from one line to another by forward or backward motion. ADV1, H4,8 pulses low when the first three stages of K3 are true (7) and the up count signal, L3,12 pulses low setting the first three stages back to zero (the fourth stage isn't used). The two nor-gates H3,10 and H3,13 decode the zero state of the counter and the down count pulse to cause the Line Counter D5 to count down one count. In a like manner, the up and down counts for the tertiary counter, C6, are generated at B2,10 and B2,4.

For the count of three function, the flip-flops of C6 are wired in toggle mode. The input clocks are pulsed only when that given stage should change state. For example if C6,9 is true and C6,5 is false then both should change for a down count. The gating structure of D6 with its inputs implements the proper pulses to make C6 operate as an up/ down synchronous, tertiary counter. Using the previous example, an up count could cause a positive pulse at B2,10. Since B\* is true there will be a clock via D6,1 and 13 to C6,11 which changes C6,9 from a one to a zero. At the same time, since C6,9 was true, A\* (C6,8) was false causing B5,6 to be true. This enables the other half of D6 (pins 4 and 5) and causes a clock at C6,3 changing C6,5 from a zero to a one. Note that if a down count occurred, B2,4 would pulse true and only D6,10 is enabled therefore affecting only C6,5.

The nand gate C4,11 is used to insure that the illegal state of A = B = 1 is not stable. If A and B were both true, C4,11 would go low causing a reset at C6,1 lasting for 300 nanoseconds. The second control mode for the Address Register is by direct addressing. For a horizontal address input XLOAD\* pulses low and the registers L3 and K3 are loaded with an address determined by the levels of B1 through B7. The three most significant bits B5-B7 select which group of 10 locations (0-9, 10-19----70-79) will be addressed. Bits 1 - 4 select which one of the locations within a group is addressed (0 - 9). The vertical address is input when YLOAD\* pulses low. B1 - B3 then indicate which line in a group of 8 is addressed. B4 and B5 indicate which group of 8 or which memory module is addressed.

The signal LSTLNE (Last Line) is true when C6,5 (B) is high, indicating the third memory module, and B1,12 is false indicating a count of 7 in D5. This signal, when true, is used to determine that the memories should scroll data up for a line advance in the scroll mode.

### 2.3.2.6 Memory to Video Synchronization

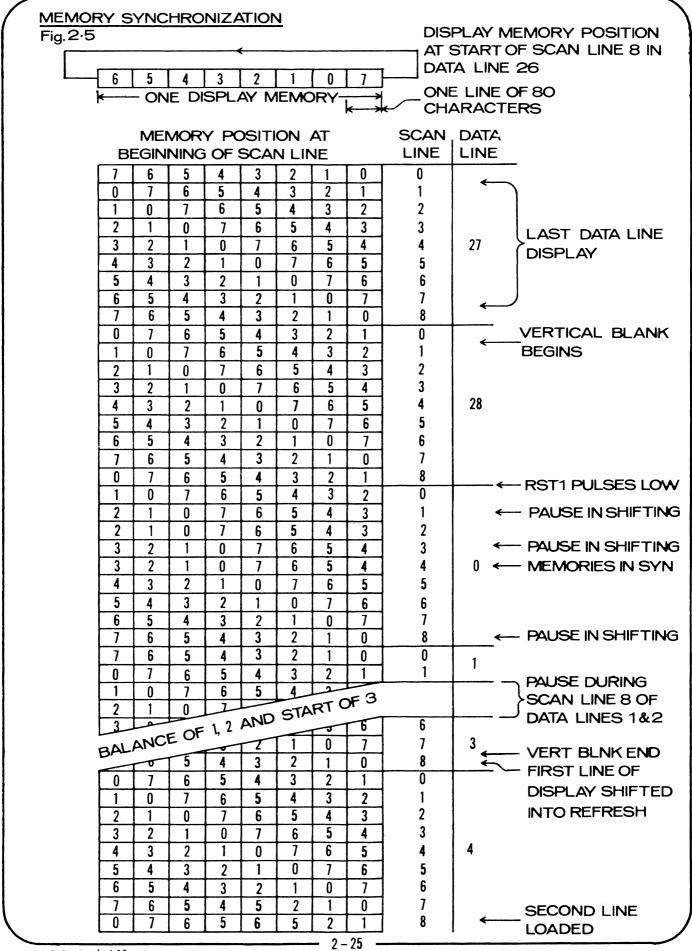

In order to explain why synchronization is necessary a discussion of the method used to transfer data from the Display Memory to the one-line Refresh Memory will be given.

As mentioned before, the Display Buffer Memory is divided into three modules of 640 characters each These modules are shifting to-(8 lines of 80). gether with their inputs and outputs multiplexed for access and display. At the top of the white page the first memory module must be ready to transfer the first line of 80 characters to the one line Refresh Memory. This indexes the memory by one line of eighty characters. During the next 8 scan lines the Display Memory shifts for 8 more lines. It is then back to the same relative position as when it completed the transfer of the first line (line 0) to the Refresh. The first line was transferred when the Scan Line Counter F7 was at a count of 8. (The characters are generated in lines one through seven.) After the bottom scan of the characters the Display Memory is ready to shift the next line of characters (line 1) to the Refresh Memory. This process continues until all eight lines have been Now the Display switches to the second transferred. memory for 8 more lines of characters and then to the third module for the bottom eight lines.

Referring to Figure 2.5, the last line transfers to the Refresh Memory during scan line 8 of data line #26. The memories continue to shift as if they were loading data for two more data lines. At the end of these two data lines the video begins the vertical flyback (RST1 pulses at the end of Data Line 28). When the Video Generator is ready to display the first line on the screen, line 0 of memory module 1 must be ready to transfer to the Refresh Memory. In order to achieve this the Display memories must be in synchronism with the Scan Line Counter. That is. line 0 in the Display Memory must shift through the output during scan line 0, memory line 1 with scan line 1, etc., in order for memory line 0 to be ready to shift into the Refresh Memory during scan line 8.

When RST1 pulses, the synchronization circuit in sections D1,2 and 3 begins to lock the memory to the Video Generator. This is done by causing the memories to pause every other scan line until memory line 0 is shifting during scan line zero. The memories are always shifting in groups of 80 shifts in sync with the Video scan line so only the line portion must be brought back into lock.

When the Scan Line Counter outputs S1, S2 and S4 and the Tracking Register outputs TR1, TR2 and TR4 are the same, the memory is in sync with the video. By not allowing the memories to shift during scan line 8, the memories will remain in sync until the first line is needed, at which time the memories will shift during scan line 8 again.

Referring to the schematic drawing, the signal RST1\* pulses low at the vertical flyback time setting the flip-flop B4,9 true. One effect of this is to enable NAND gate A2,2 allowing S8 when true to go high; which on the Memory and Control board blocks the clocks that cause the Display memories to shift. Data Gate, DATAGT, goes true at the start of the 80 character shift group and sets B4,5 true allowing A2,6 to go low. During synchronization NAND gate B1,3 is enabled because B4,9 is true. The comparator F6 causes inverter C3,12 to be true when S1, S2 and S4 are not the same as TR1, TR2 and TR4. This causes B1,6 to go

low when S1 is true. The result is that the memory clocks are disabled during the time S1 is true unit1 a true comparison is achieved. It takes two pauses to reach sync because the memories were out of sync by 2 lines when RST1\* pulsed low. When synchronization occurs, F6 causes C3,12 to be low which disables B1,6 allowing A2,5 to go true every scan line for 80 shifts. From this point on the memories pause only during scan line 8 to maintain sync. Vertical Blank goes true at the start of scan line 8 in Data Line 3. This transition is used to set B4,9 back to zero allowing the Display memories to shift during scan line 8.

### 2.4 Detailed Description - Memory and Control

# 2.4.1 <u>Memory and Control Block Diagram Description</u> (Figure 2.6, pages 2-31/32)

### 2.4.1.1 Display Memory and Refresh Memory

The Display Memory stores the 1920 characters displayed on the CRT screen. Each character position requires 6 bits because the displayable character set consists of 64 different characters. The memory is a mix of MOS static shift registers and MOS dynamic shift registers. These registers are arranged in three modules of 640 characters each, with 6 bits for each character. The memories shift at the Video character rate of 1.6 MHZ. One module has six 640-bit shift registers running in parallel such that a new 6-bit character appears at the module output every 639 nanoseconds. The outputs from each module are returned to the inputs so that the data renews itself in the memory constantly.

In the block diagram, Data 1 is the 6-bit output of memory module 1 and is returned to the input via the input multiplexer. In order to enter data, the recirculation path of Data 1 is broken for one shift period and new data (INPUT DATA) is gated to the memory input by the input multiplexer and shifted into the memory instead. After the new data has been shifted in, the recirculation path is again closed and the new data remains in memory.

The three memory modules also shift together such that three characters are shifted at a time, one in each module. When data is entered, the input multiplexer breaks the proper recirculation path. The Display Memory clocks are gated in 80-pulse bursts and stopped for 20 character times every scan line such that it takes 8 scan lines to shift 640 times, a complete cycle.

In order for the Video Generator to display a line of characters it needs the 80 character codes for that line at least 7 times for 7 sequential scan lines. The Refresh memory is used to store the one line of 80 characters for 9 scan lines (7 of which are actually used to generate characters). The Refresh memory consists of six 100-bit shift registers in parallel which shift at the Video character rate of 1.6 MHZ. The display select and recirculation control logic transfers one line of 80 characters from the proper Display Memory module to the Refresh memory once every nine scan lines. It does this by breaking the recirculation path of the Refresh memory for one scan line and allowing the data from one of the Display memories to be shifted in. Only the 80 positions filled by the one line of characters are used by the Video Generator. The clocks to the Refresh memory are not gated since the memory is the same length as one scan line (100 characters).

### 2.4.1.2 Access Logic

The access logic controls the input of a character to the Display Memory. The inputs A and B select which module is to be accessed. When the memories are in such a position that the character to be replaced is ready to be shifted from the output back to the input (Address Comparison true), the proper load pulse (LOAD 1, 2 or 3) pulses true. The load pulse causes the recirculation path to break for the one character time necessary to shift in the new data. The signal CLRG is used to force space code into the inputs of the memory modules for an Erase function.

[For units delivered before January 15, 1974, note that the force signals are CLEAR 1, 2, and 3. Also note that space code was forced for Carriage Return as well as for the Erase function.]

### 2.4.1.3 Scroll Logic

This section controls the scrolling of data up the screen. When the Memory Address register indicates the cursor is in the the last line (LSTNE true) and the Video Generator indicates that the Address has just gone through the last position on a line (ADV1\* pulses low), the circuit causes a scroll. At the same time the signal normally causing the Memory Address to change by a line (ADV\*) is not allowed to pulse. Scrolling is accomplished by making the three memories into one memory of 1920 characters for 80 shifts. This is done by gating the output of memory #2 to the input of memory #1, and memory #3 to memory Space code is input to memory #3. Thus all #2. data is shifted up by 80 characters, or one line.

This circuit also blocks the ADV\* signal normally generated by a Carriage Return when the terminal

is not in Auto Line Feed mode. The ADV\* then pulses for only cursor down or Line Feed (same code).

### 2.4.1.4 Cursor Generation

The cursor is generated as follows: When Address Comparison is true during Scan Line 8 it means that the character of interest is being loaded into the Refresh memory. The next time Scan Line 8 goes true the cursor must be generated in order to place it under this character. When the signal Character Comparison goes true during the next Scan Line 8 the cursor signal is generated after being delayed by one character time. The delay is necessary because of the one character delay through the ROM character generator. On the Video Generator card the CURSOR pulse inverts the background level causing the underline mark. (Intentionally left blank)

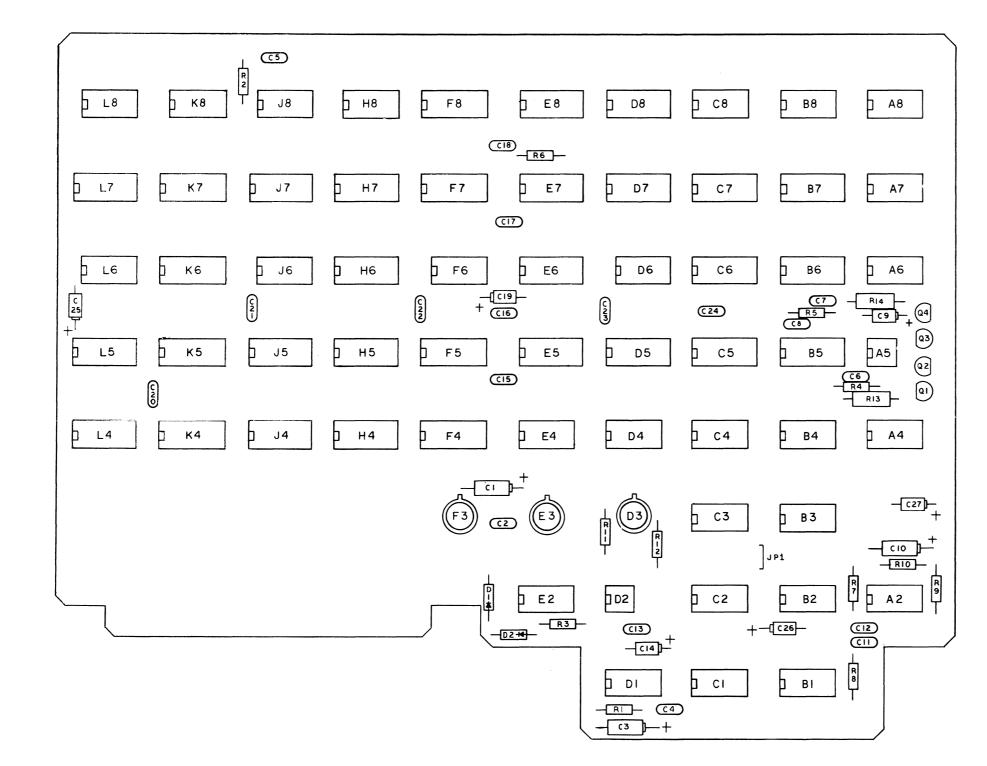

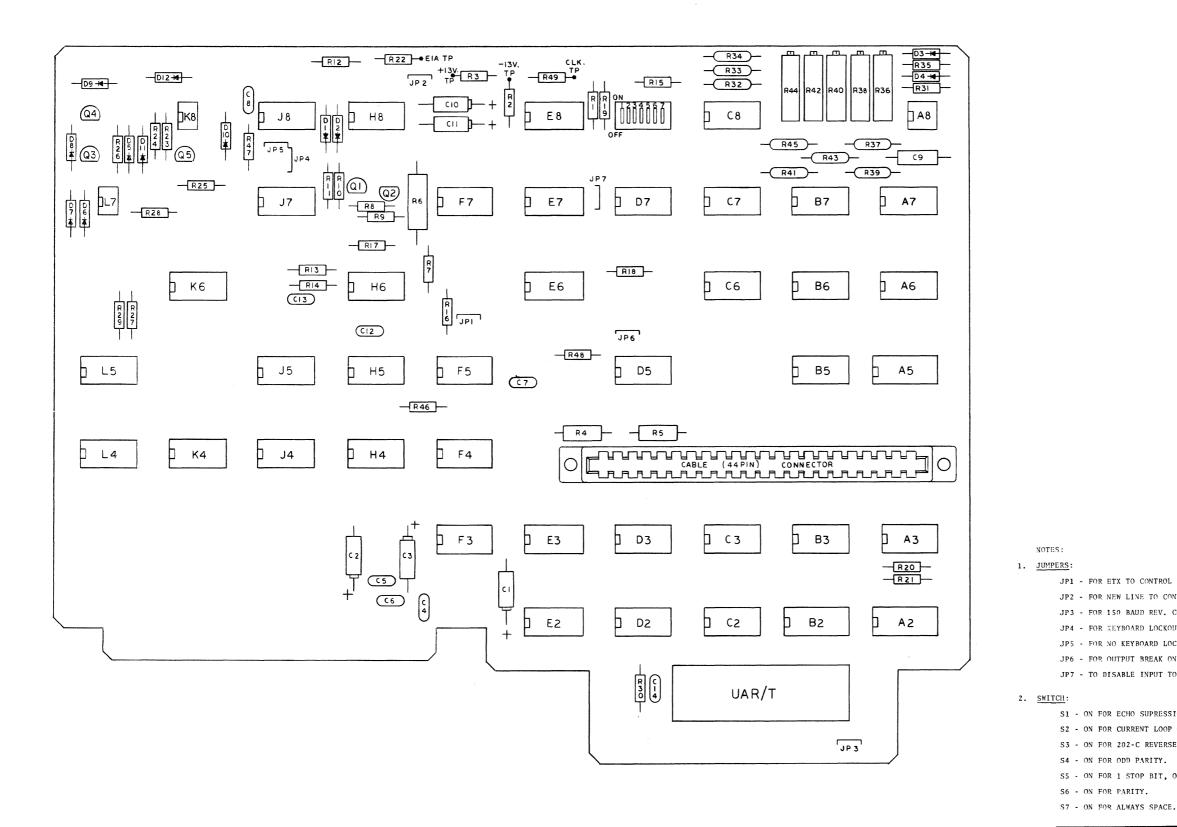

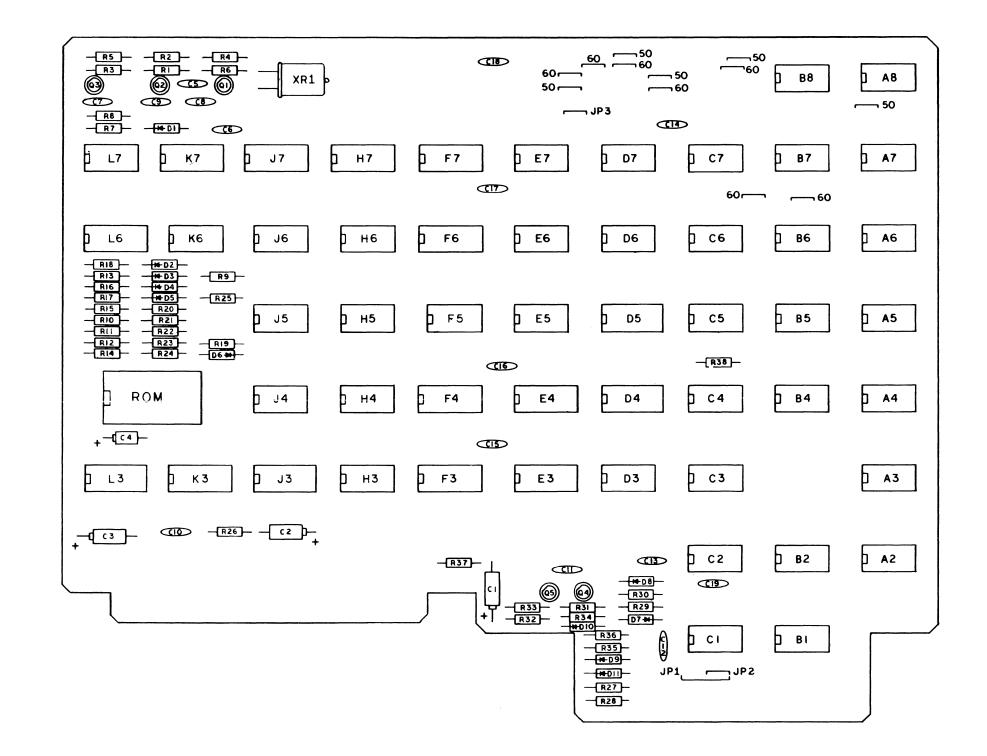

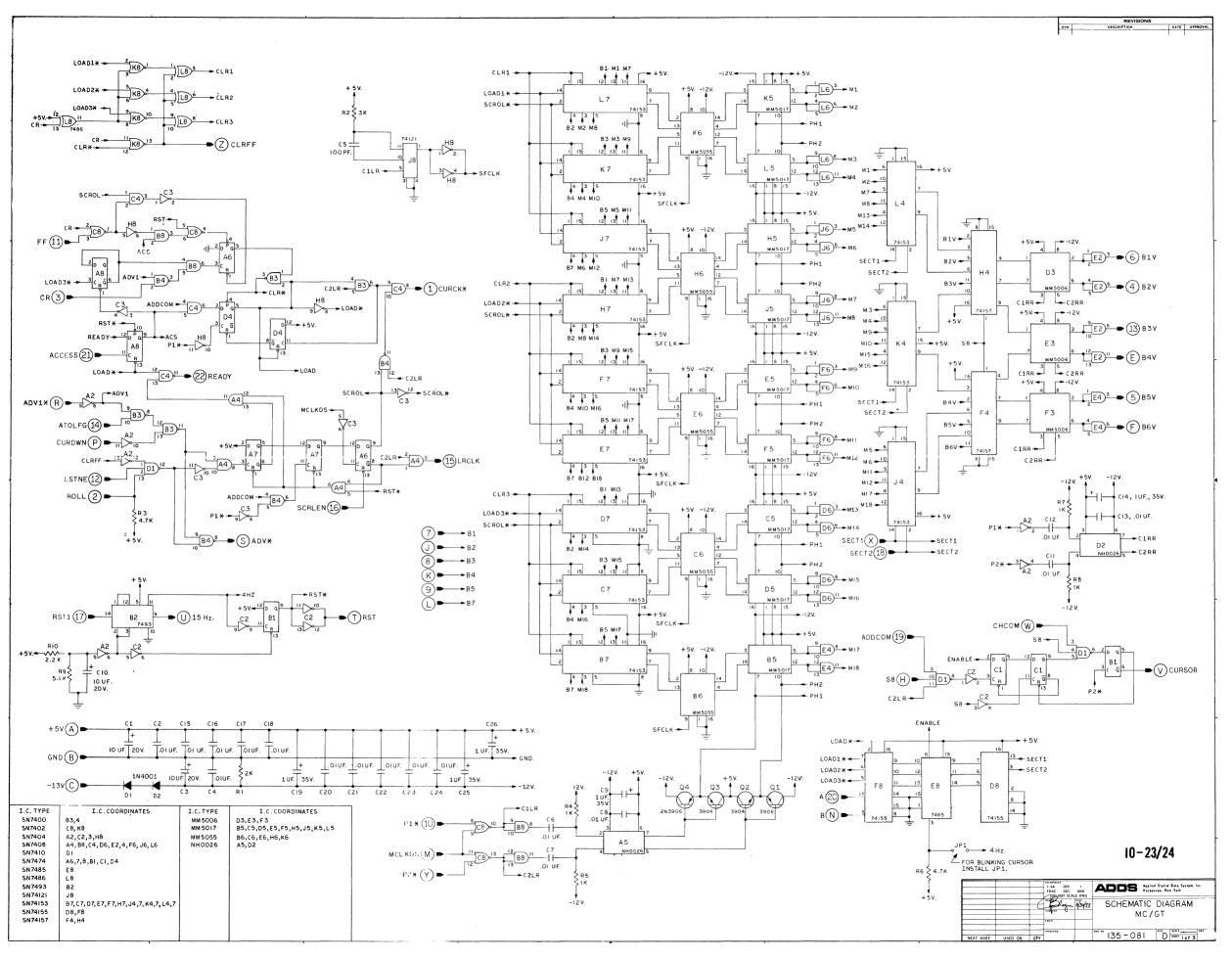

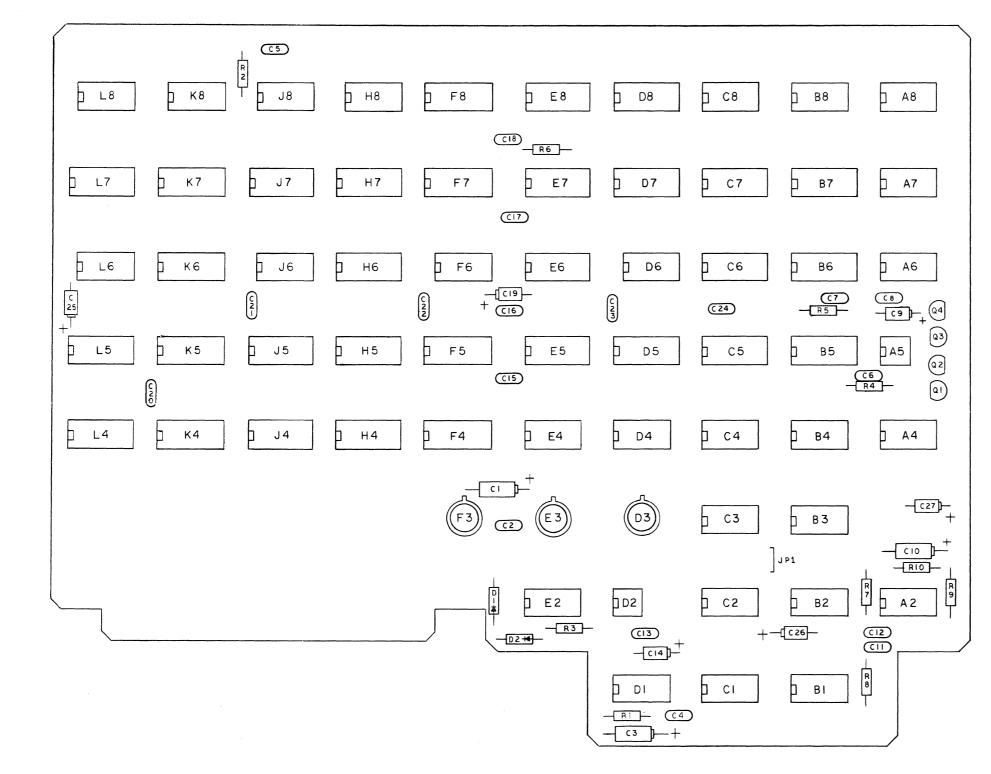

#### 2.4.2 Circuit Description - Refer to Schematic #135-081

#### 2.4.2.1 Display and Refresh Memory

The Display Memory is a group of shift registers running in parallel and recirculating their contents from output back to input. A single bit is composed of a 128-bit static register in series with a 512-bit dynamic register to make a single shift register 640 bits long. Six such register combinations make up one 6 x 640 bit memory module. Three memory modules make up the entire Display Memory of 1920 6-bit characters.

The static registers are quad 128-bit devices, MM5055. The dynamic registers are dual 512-bit devices, MM5017. Memory module #1 consists of K6, 1/2 of H6, K5, L5, and H5. In order to show the recirculation path, Bit 1 of module #1 will be used. The data path around the memory is as follows:

The output is K5 pin 5 buffered by the AND gate L6,3 and is named M1. M1 is positive for 1 and zero for a 0. M1 is applied to the input of the dual four-bit multiplexer L7,13. Normally this input is passed on to the output L7,9. L7,9 is tied to the input of the static register K6,2 whose output K6,14 drives the input of the dynamic register K5,3 completing the recirculation path.

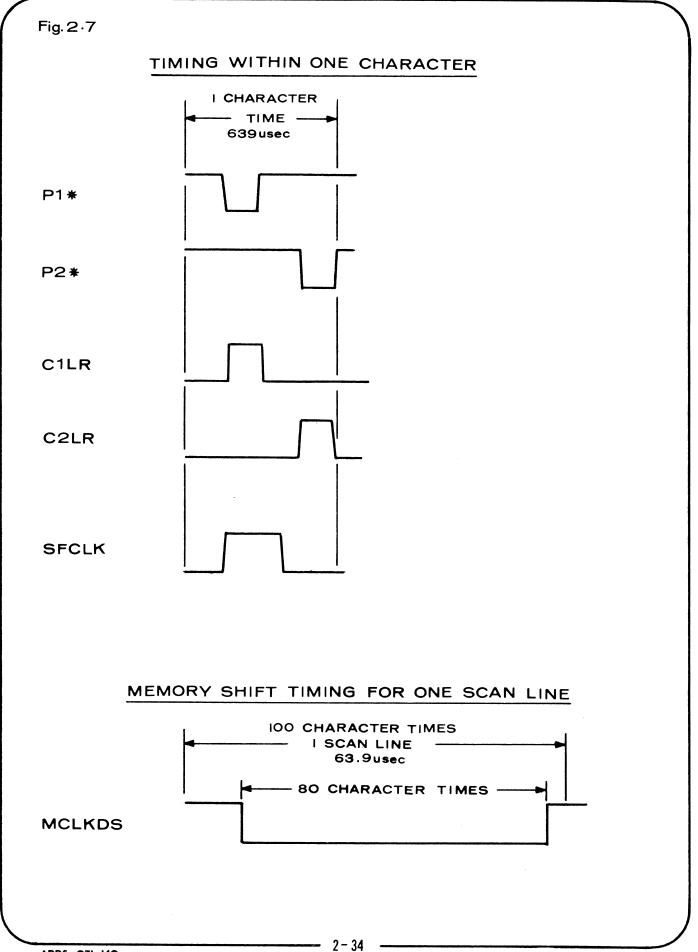

The Refresh memory is made up from three dual 100bit dynamic shift registers D3, E3, and F3. Referring to Figure 2.7 on the next page, note P1\* and P2\*. These two pulses occurring during one character period are used to generate the clocks to shift the Refresh register C1RR and C2RR. D2 is a dual MOS clock driver which outputs the +5 volt to -12 volt clocks ClRR and C2RR. These clocks are not gated because the length of the register equals the number of character positions in a scan line. The data in the Refresh memory is recirculated by the two quad 2-input multiplexers H4 and F4 which normally pass the buffered outputs B1V-B6V to the inputs of the registers. S8 is true during the ninth scan line and gates the data from the Display Memory to the input of the Refresh memory to update its contents for the generation of the next character line.

The three dual four-line-to-one-line multiplexers L4, K4 and J4 are used to select which Display Memory module will load the Refresh memory; Module 1 when SECT1 and SECT2 are low, Module 2 for SECT1

= 1 and SECT2 = 0, Module 3 when SECT1 = 0 and SECT2 = 1.

The clocks for the dynamic portion of the memory are PH1 and PH2. These are generated from P1\* and P2\* gated with Memory Clock Disable, MCLKDS, which is low for 80 character times. The transistors are necessary to supply the current for changing the memory clock inputs. The static memory clock is generated from C1LR, (C8,10) by the one-shot J8 is approximately 200 nanoseconds long, SFCLK.

# 2.4.2.2 Access Logic

#### 2.4.2.2.1 Access For Standard Displayable Characters

When an input to the Display Memory is to be made the signal ACCESS in section F8 pulses true. This sets the flip-flop A8,9 true enabling AND gate C4,5 and resetting flip-flop A8,6 true. When ADDCOM is true, indicating that the Display Memory is in the correct position for input, the D input of flip-flop D4,2 is enabled. The clock input to D4 is the inverse of P1\* and sets the flip-flop true at the leading edge of the memory clock C1LR (same time). This releases the clamp on the reset input to D4,13 and causes LOAD\* to go low. LOAD\* strobes the Dual 1-lineto-4-line data selector (F8), causing LOAD1\* LOAD2\* or LOAD3\* to go low depending on which memory module is selected by A and B. This load pulse, assume LOAD1\*, breaks the recirculation path for the memory module and allows the data B1-B7 (B6 not used) to be entered on the trailing edge of C1LR (Memory Input Clock).

Back in the access logic, note that D4,5 also enables NAND gate B3,4. When C2LR pulses (Memory Output Clock) the signal CURCK\* pulses, advancing the cursor one position. At the same time D4,11 is clocked on the trailing edge of C2LR and sets D4,8 false which resets D4,5 low completing the input of one character. As soon as D4,5 returns false it resets D4,8 removing the reset signal on D4,1. When LOAD\* pulsed low the input flip-flop A8,9 returned low blocking the next P1\* from setting D4,5 true again.

2.4.2.2.2 <u>Access For CR or FF (for units delivered after</u> January 15, 1974)

For a Carriage Return or Erase function the

access is handled somewhat differently. For Carriage Return the signal CR will be true. This causes NOR gate C8,1 to be low enabling AND gate B8,1. When ACS goes true (flip-flop A8,9 goes true upon the ACCESS signal generated by the CR input code) the Q output of flip-flop A6,5 goes true. When D4,5 goes true for the first ADDCOM, NAND gate B3,3 goes low clamping D4,5 in the set state. After the first access D4,8 goes low holding the Reset input D4,1 low but since the Preset, pin 4 is also low, output pin 5 of D4 remains high.

If the input code is FF (Erase), the signal CLRG from K8,10 and 13, section G7 is true since CR and CLR\* are both low. This breaks the recirculation path of all three memory modules, and zeroes, representing space code, are loaded as long as CLR\* is held low. The flip-flop A8,6 goes false when LOAD3\* returns true after the third memory module is cleared and then goes true again when LOAD3\* goes low and high a second time which clocks the flip-flop A6,5 back false. The reason for two passes through the memory is to insure the entire screen is erased because the cursor is not returned home by the FF operation before it starts.

If the input code is CR (Carriage Return), CLRG is held low preventing any memory module from erasing any data. The LOAD 1, 2, 3\* signals are inhibited by CLRFF, F8,1 section B3. CLRFF is the inverse of CR. The Preset clamp on D4,4 is released when A6,5 is returned false. The clock input to A6,3 is driven by ADV1, the inverse of ASV1; which pulses when the cursor has crossed a line boundary. Since the D input is grounded, the trailing edge of ADV will clock the output back to zero completing the CR function. Keep in mind that the flip-flop A8,6 is true because it was reset with first access and doesn't interfere with the ADV pulse clock.

The signal READY is not used elsewhere in the 580. It is included for possible future use. The READY input to A8,12 is to insure that a second input can't be initiated if the ACCESS logic is busy.

# 2.4.2.2.3 <u>Access For CR or FF (for units delivered before</u> January 15, 1974)

On earlier units the CR and FF functions were

handled as described below.

Consider the Carriage Return function. For Carriage Return the signal CR will be true. This causes NOR gate C8,1 to be low enabling AND gate B8,1. When ACS goes true (flip-flop A8,9 goes true upon the ACCESS signal generated by the CR input code) the Q output of flip-flop A6,5 goes true. When D4,5 goes true for the first ADDCOM, NAND gate B3,3 goes low clamping D4,5 in the set state. After the first access, D4,8 goes low holding the Reset input D4,1 low but since the Preset, pin 4 is also low, output pin 5 of D4 remains high. In the upper left corner, note that if one of the LOAD\* signals is low and CR is high, one of the CLR1, 2 or 3 signals will go true. This happens because the output of the EXC-OR gate L8,11 is false when CR is true enabling the NOR gates. When for instance LOAD1\* goes low the output of NOR gate K8,1 goes true. Since K8,13 is low (CR is true) CLR1 goes true. This breaks the recirculation path of memory module 1 and instead of loading B1-B7, zeroes are loaded, resulting from the clear input on L7, K7 and J7 (representing space code), as long as the load pulse LOAD1\* stays low. The load will continue until the flip-flop A6,5 is returned false releasing the Preset clamp on D4,4. The clock input to A6,3 is driven by ADV1 the inverse of ADV1\* which pulses when the cursor has crossed a line boundary. Since the D input is grounded, the trailing edge of ADV will clock the output back to zero completing the CR function. Keep in mind that the flipflop A8,6 is true because it was reset with first access and doesn't interfere with the ADV pulse clock.

If the input code is FF (Erase) the same thing happens as with a CR but the flip-flop A6,5 doesn't get clocked off by ADV because CR is low. Instead, the flip-flop A8,6 goes false when LOAD3\* goes low and high a second time which clocks the flip-flop A6,5 back false. The reason for two passes through the memory is to insure the entire screen is erased because the cursor is not returned home by the FF operation before it starts.

[The signal READY is not used elsewhere in the 580. It is included for possible future use.

The READY input to A8,12 is to insure a second input can't be initiated if the ACCESS logic is busy.]

The signals CLR1, 2 and 3 are all forced true when a FF is done because CR is low disabling NOR gates K8, 1, 4 and 10. When CLR\* goes low K8,13 goes true and all the clears go true.

# 2.4.2.3 Scroll Logic

The Scroll circuitry handles two functions, the scrolling of data up the screen and the gating of ADV\* which is the signal from the character portion of the Memory Address register which indicates that the cursor has gone from character position 79 to 0 (crossed the end of a line.) If the terminal is in Auto Line Feed, then B3,10 is true which allows ADV1\* to pass on through inverted to the input of NAND gate B4,9. If the terminal is in non-ROLL mode or the cursor is not in the bottom line the other input B4,10 will be enabled allowing ADV1\* to pass as ADV\*. However, if the terminal is not in Auto Line Feed, then ATOLFG is low blocking ADV1\* at B3,10. Now, in order for ADV\* to pulse, a Line Feed code or Cursor Down (same code) must be entered which causes a positive pulse at inverter A2,11 which generates an ADV\* pulse advancing the cursor down one line.

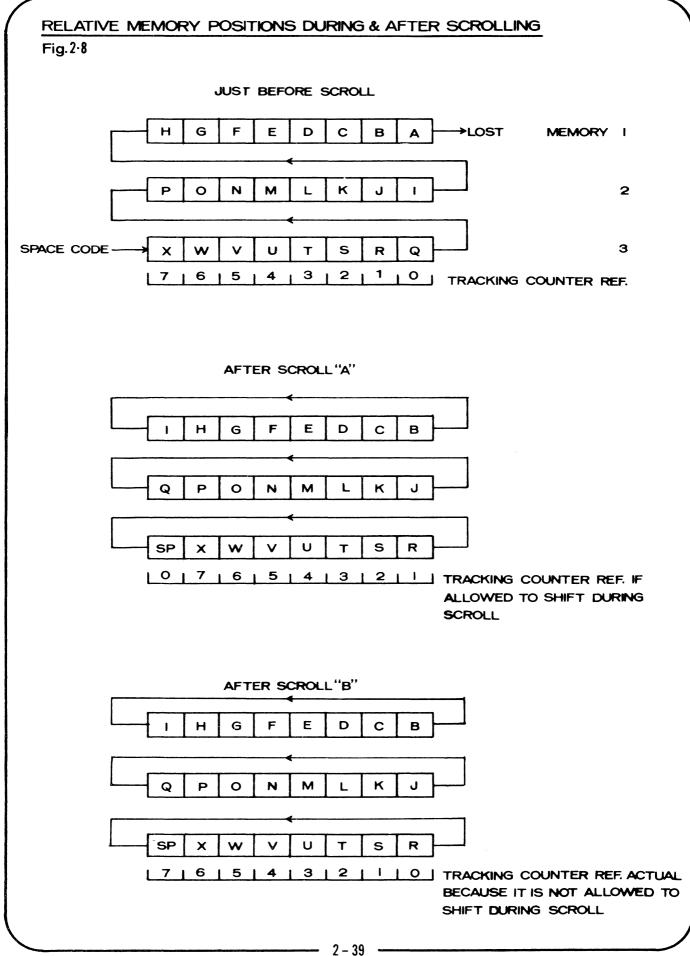

In order to understand what occurs when the Memories scroll refer to Figure 2.8. At the top the three memory modules are shown with the output of #3 attached to the input of #2, and the output of #2 attached to the input of #1. The input of #3 is forced to space code while the output of #1 is lost. This occurs when SCROL\* into the dual 4 line-to-1 line multiplexers B7, C7, D7, E7, F7, H7, J7, and K7 goes low. When SCROL\* is low the memories are attached together as one 1920 character shift register.

Returning to Figure 2.8, the registers are shifted for 80 counts in the long configuration. After 80 shifts the signal SCROL\* returns true and the memories are returned to the normal configuration as shown in the middle of Figure 2.8. Note that after the scroll, the 80 spaces in memory #3 are in what would be the position of line 0 or the top line of the group of 8 instead of the bottom

line where they should be. The same is true of memories #1 and #2. In order to correct this situation, the Tracking Counter must be allowed to go out of sync for the 80 shifts. This is done by not allowing it to count during the time the memories scroll. This reassigns the lines such that the spaces are in line 7. The bottom of Figure 2.8 shows the actual relationship between the data and the Tracking Counter. Note the Tracking Counter hasn't changed from the top reference.

Referring to the schematic, a scroll operation is initiated by ADV1\* pulsing when the cursor is in the last line (LSTNE true), and ROLL is true. ADV\* is blocked and flip-flop A7,5 is set true. This enables the D input of flip-flop A7,12. When ADDCOM is true, P1\* strobes it and clocks flip-flop A7,9 true. This means that the character over the cursor is now at the output of memory #3. When this line (line seven) finishes shifting, the memories are in the position shown in Figure 2.8 at the top. That is, line 0 is ready to shift out. The end of shifting of line 7 is indicated when MCLKDS goes true. Since MCLKDS is inverted it has no effect on the state of flip-flop A6,9 until it goes negative again indicating the start of the next shift period. At this time A6,9 is inverted by C3,12 to become SCROL\*, which sets up the memories as one shift registor when low. A6,8 being low clamps A7,5 and A7,9 low via AND gate A4,6. The signal READY is also held low which blocks any further inputs until the Scroll is completed. The reset input of flip-flop A6,13 is SCRLEN (Scroll Enable). This signal is generated on the VG/GT and is always a logical "1". The flip-flop A6,9 resets low ending the Scroll function when MCLKDS goes negative a second time at the start of another shift period.

#### 2.4.2.4 Cursor Logic

The Cursor circuitry is in section C-2 of the schematic. Below this circuitry is a dual 4 line-to-1 line data selector, D8, with its inputs tied to GND. The two inputs SECT1 and SECT2

indicate which third of memory is being displayed. Pin 7 will be low for memory 1 display pin 6 and 5 low for memory 2 and 3 display. The 74155, F8, has its inputs for the half not used for LOAD\* tied to GND also. The outputs are selected by A and B. E8 is a comparator which has an output, ENABLE, true when A and B equal SECT1 and SECT2. This indicates that the Video Generator is displaying the memory module that is selected by the Memory Address register which is the third of memory in which the cursor should be displayed. ENABLE enables the D input of flip-flop C1,2. When an ADDCOM (Address Comparison) is true during Scan Line 9 (S8 true) the character under which the cursor should be shown is being loaded into the Refresh. This sets flip-flop C1,5 true indicating that the cursor mark should be generated the next time S8 is true. C1,5 enables the D input C1,12. When S8 goes false C1,9 goes true enabling NAND gate D1,5. The next time S8 is true the second input of NAND gate D1,4 is enabled. Then when CHCOM (Character Comparison) goes true (after the trailing edge of P2\*) B1,2 is enabled. The next P2\* (one character delay later) sets B1,5 true making the cursor mark. Meanwhile, on the trailing edge of P2\*, CHCOM went false allowing the flip-flop to reset on the third P2\*. The cursor mark lasts for 639 nanoseconds or one character time.

#### 2.4.2.5 Reset and Repeat Rate

In the lower left corner of the schematic, a 4 stage binary counter is driven by the Video Generator reset signal RST1 (60 HZ). This is divided by 4 to produce the 15HZ signal used for the repeat function on the keyboard. For the blinking cursor option the 4HZ output is used to clamp off the ENABLE signal at E8,3 (if jumper JP1 is installed).

When power comes on, the capacitor C10 charges more slowly than the power comes up causing A2,6 to be high and C2,6 to be low for a few milliseconds. This clamps the counter and the flipflop B1 in the reset state. When C10 charges up, the inverters switch and release the resets. The buffered output of the flip-flop RST is used to cause a power clear of the memories by forcing the access circuitry to the clear function by setting A8,9 and A6,5 true as long as RST remains true. The Front End card also uses RST to condition the UAR/T and all flip-flops to the proper state. B1,9 goes true when the signal 4HZ goes true and returns false (250 milliseconds later) completing the reset function.

# 2.5 Detailed Description - Front End

# 2.5.1 Front End Block Diagram Description (Figure 2.9, page 2-45/46)

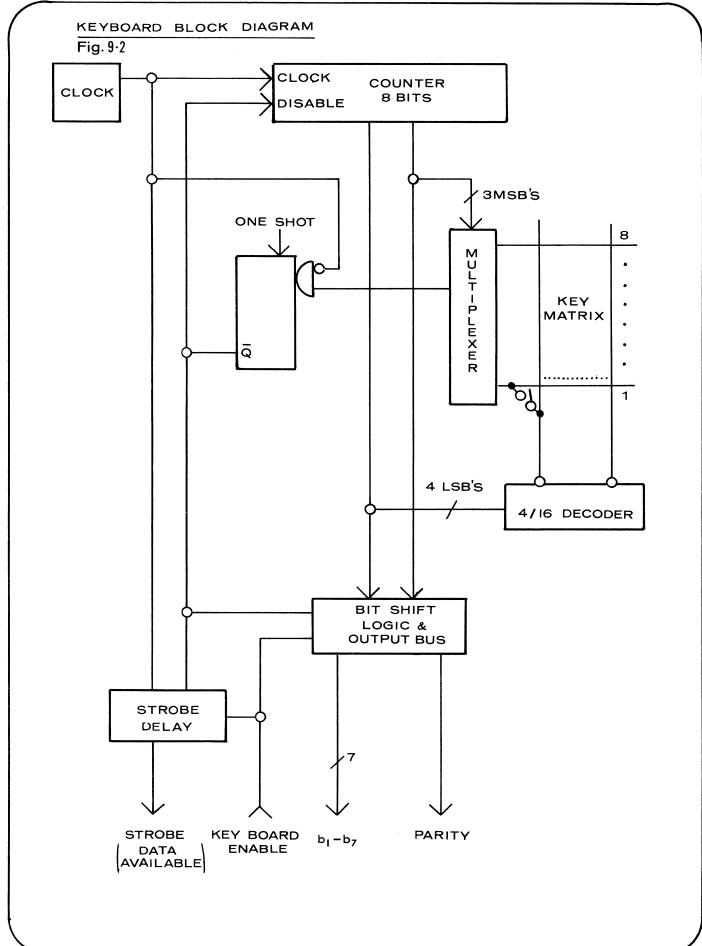

#### 2.5.1.1 Serial to Parallel Converter

The converter is an MOS device called a UAR/T (Universal Asynchronous Receiver/Transmitter). It accepts parallel data and converts it to 10 or 11 bit serial data. It also accepts 10 or 11 bit serial data and converts it to parallel data. A clock is used to drive the chip and determines at what rate the device will operate. The clock has five switchable rates. The serial input and output is converted from TTL levels to either EIA (±13V) or current loop (20 ma) for operation with standard communication equipment.

# 2.5.1.2 Decode and Control Logic

Parallel data into the terminal (from the UAR/T) is checked for validity by the Decode logic. Characters from ASCII columns 2, 3, 4 and 5 are allowed into the memory. Characters from columns 6 and 7 (lower case) with the exception of Rubout are converted to columns 4 and 5 for input to memory. Control characters from columns 0 and 1 are ignored unless they indicate a terminal control function such as CR, LF, cursor controls, etc.

This logic generates the Access strobe and the cursor address control signals.

# 2.5.1.3 Keyboard Input

The keyboard supplies the only parallel input to the UAR/T. When a key is struck, the code along with a strobe is applied to the UAR/T for serialization. When the UAR/T has output the character another key may be struck. The only two keys on the keyboard not coded are BREAK and REPEAT. BREAK causes a 500 millisecond SPACE on the EIA output and is also used to control the Secondary Channel Request to Send, SCA. REPEAT is used to repetitively output the same code - 15 times per second (10 times per second for 110 baud).

#### 2.5.1.4 RS232C Control Logic

The terminal is capable of operating on any 103 type Modem or 202 type Modem. For primary chan-

nel control the logic raises Request to Send (RQSEND) when the first character of a message is keyed and holds it true until an ETX (End of Text) character is output or a New Line function is performed (CR output in AUTOLF or LF in non-AUTOLF) at which time RQSEND is dropped. The terminal will wait until the Modem raises Clear to Send before actually outputting the first character.

The Secondary Channel may also be controlled by the terminal. As a switchable option the keyboard will be locked until the computer allows the terminal to enter the send mode by use of the signals SCA and SCF. If the terminal is in the send mode the computer may interrupt and force it to the receive mode, locking the keyboard and resetting RQSEND.

# 2.5.1.5 Printer Output

There is a serial EIA output port for driving a serial printer. The output is enabled when a Printer-On code is received by the control logic. It is disabled with a Printer-Off code. When on, the printer output copies any serial data that the UAR/T would convert to parallel code. In Half-Duplex therefore the printer copies the keyboard data as well as data from the computer. In Full-Duplex only data from the computer is copied.

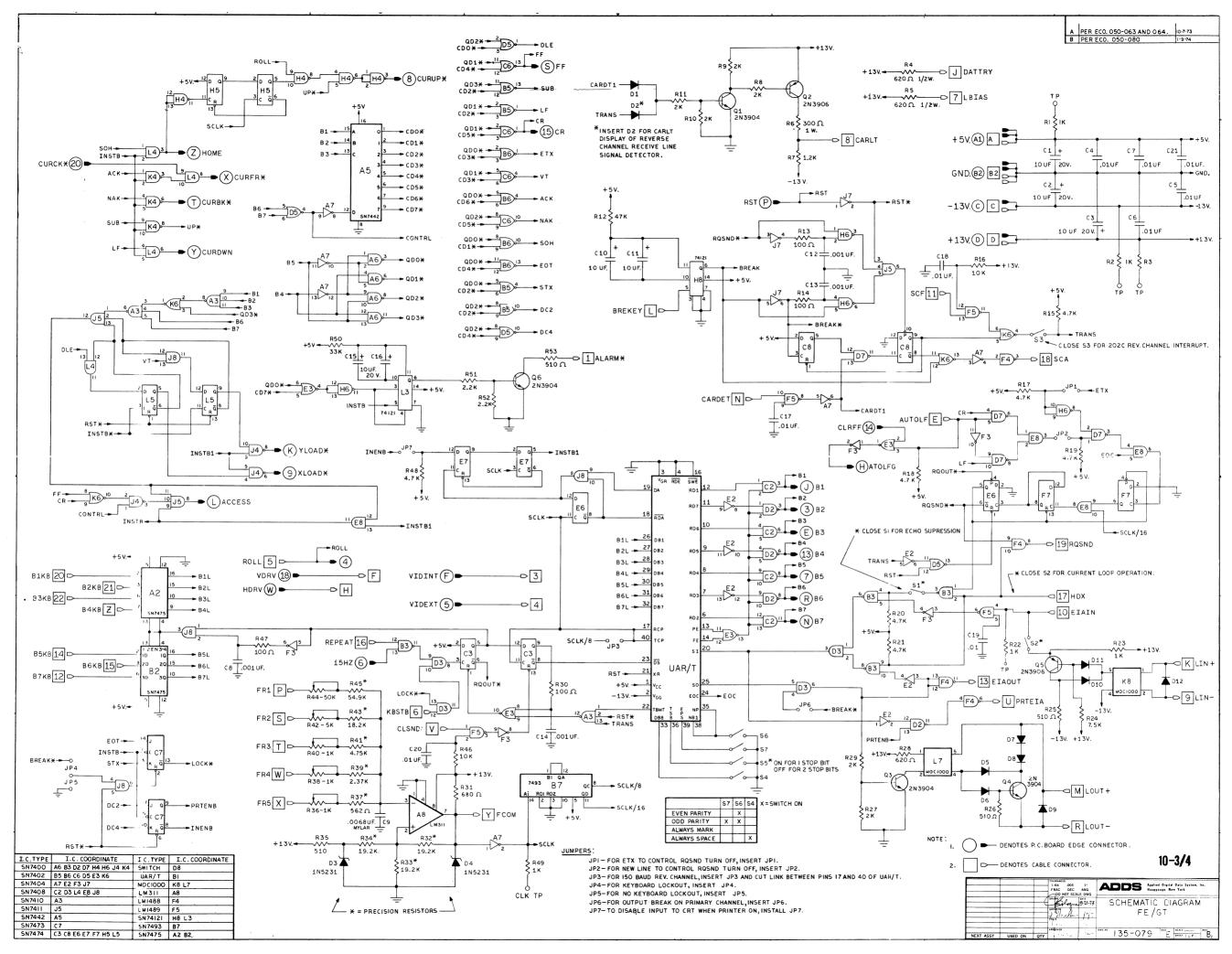

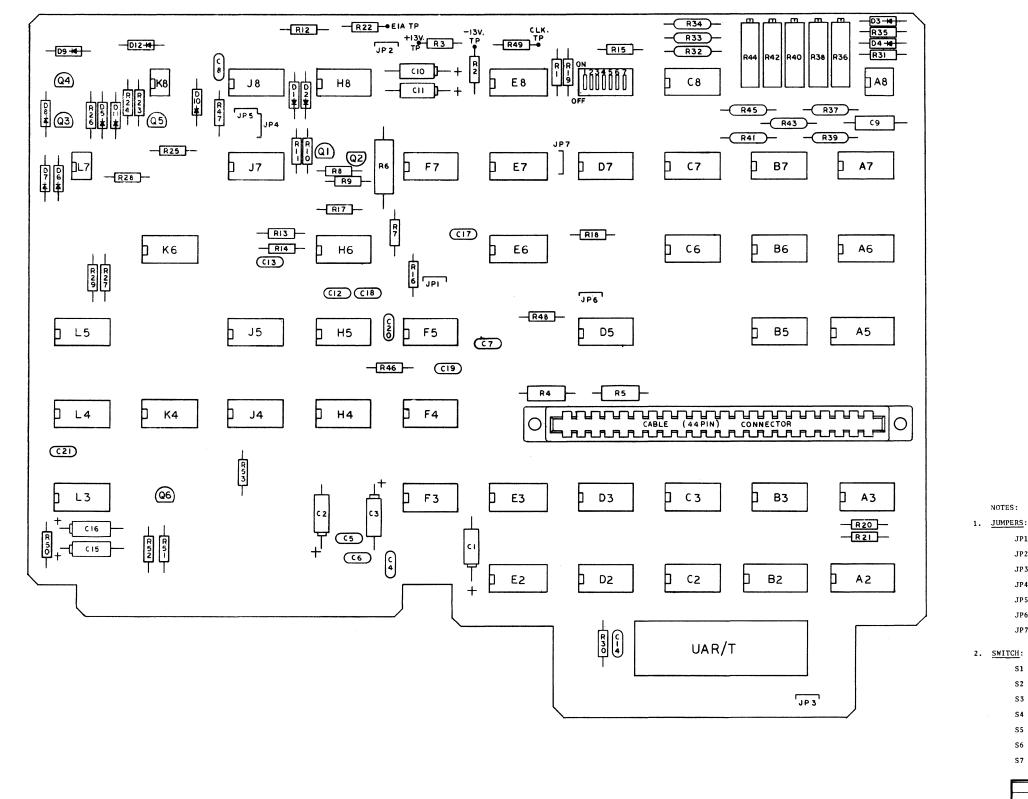

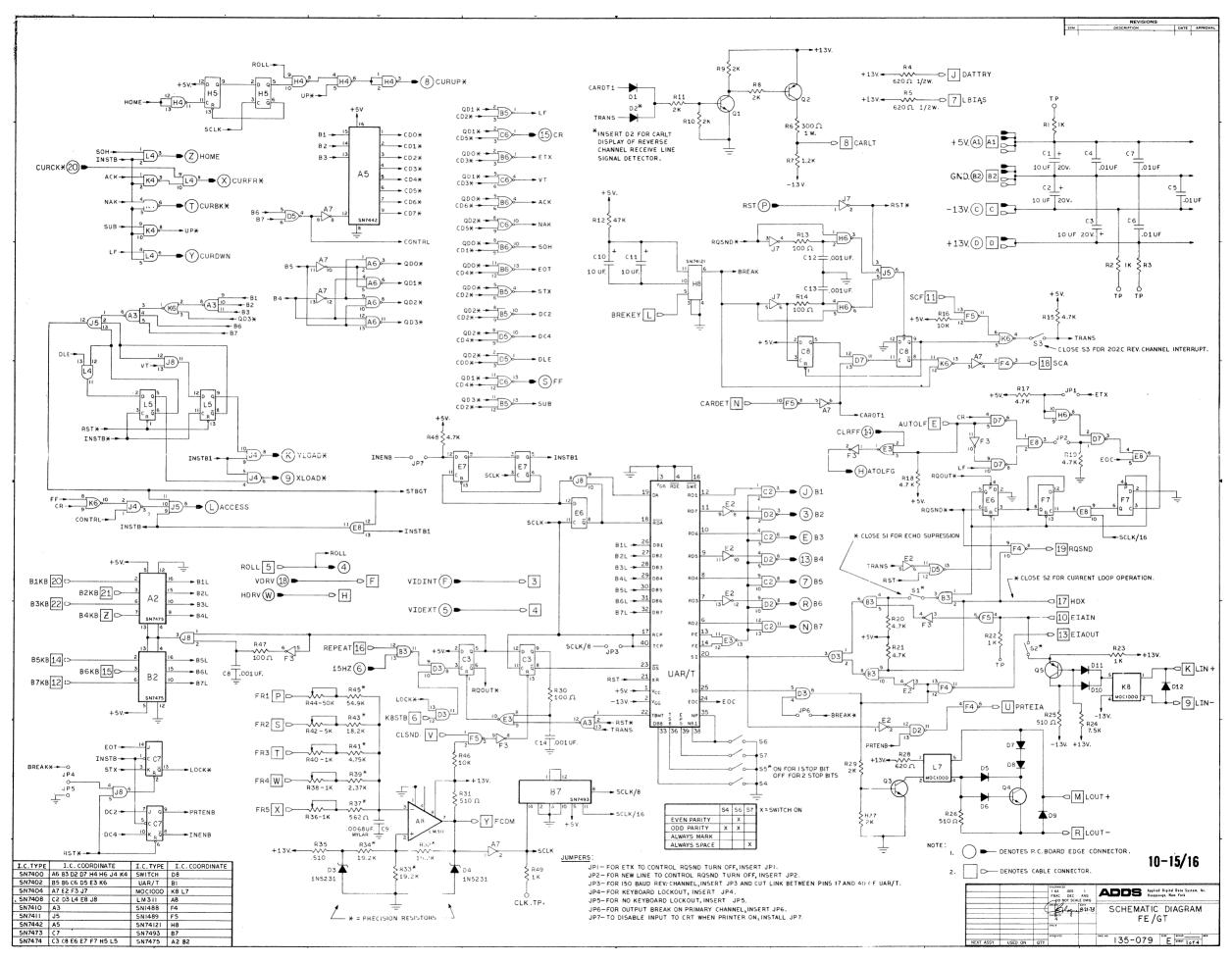

#### 2.5.2 Circuit Description - Schematic #135-079

#### 2.5.2.1 Serial to Parallel Conversion

The UAR/T does the conversion from serial to parallel and parallel to serial at TTL levels. The serial data is asynchronous 10 or 11 bit. Normally the data line is at a true or 1 level until a character is sent. The start bit, always a zero, begins the character. The next seven bits are the data bits 1 through 7. The ninth bit is parity and the tenth or both the tenth and eleventh are stop bits, always 1's.

The UAR/T is driven by a clock that is 16 times the bit rate. The input is sampled by the clock for the first zero level. If a sample taken 8 clock periods later (center of start bit) is also low the rest of the bits are detected by center sampling and are stored in a latch. The stop bit (or bits) are checked as well as parity, if set. If all checks good the UAR/T raises Data Available, DA. If an error were detected, DA is still raised but either Parity Error, PE, or Framing Error, FE, are raised which results in NOR gate E3,13 being The Data out is on pins 6 through 11 of the 1ow. UAR/T and is buffered for input to the terminal. If an error is detected E3,13 being low will force an asterisk code on B1 through B7. When DA goes true, AND gate output J8,8 goes true (E6,8 normally true) setting flip-flop E7,9 true. At the same time E6,12 is enabled so that the next positive edge of SCLK will set E6,8 false, which resets DA. The output data B1-B7 remains stable until just prior to the next DA true level. The edge of SCLK that set E6,8 true also clocked E7,5 true generating INSTB1 which generates ACCESS. E7,6 going false resets E7,9 so that the next SCLK pulse resets E7,5 low again completing one input cycle. This same SCLK pulse also sets E6,8 true again because DA has returned false.

In order to output a character the UAR/T must be presented a character in parallel and be given a strobe. When a key is depressed on the keyboard a 7-bit code is generated and applied to the inputs of the two quad latches A2 and B2. At the same time a strobe is generated called Keyboard Strobe, KBSTB. KBSTB when it goes true sets flip-flop C3,5 true (LOCK\* is normally high and REPEAT is normally low). This enables the D input of flip-flop C3,12 and also strobes the

latches to obtain BlL-B7L. When SCLK goes true C3,9 goes true which after a delay of 100 nanoseconds (R30, C14) resets C3,5 and removes the strobe from the latches. C3,8 has gone false and returns true on the next SCLK which strobes the UAR/T causing it to begin the serialization of the character. Ιt is assumed that Clear to Send, CLSND, is true. Ιf CLSND is false, DS is delayed until it goes true. The input REPEAT goes true when the Repeat key is held down causing a 15HZ signal at D3,9. If a character key is also held down D3,10 will be enabled and that character will be output at a 15HZ If the character rate is too fast (15HZ at rate. 110 baud for instance) the signal, Transmitter Buffer Empty (TBMT), will be low when the UAR/T is busy which forces C3,5 to be missed. The same will happen if characters are keyed too fast. The signal EOC, End of Character, indicates when the last stop bit for a character has been output.

There are several options concerning the UAR/T which are switch selectable. The Parity may be selected to be even or odd or always 1 or 0. When S6 is closed, the number of data bits is 7, plus one parity bit. The type of parity (odd/even) is selected by S7 which is on for odd and off for even. For no parity; S6 is left off which also selects 8 data bits. The state of the eighth bit is selected by S4; on for a zero, off for a one. The number of stop bits is selected by S5; on for one, off for two.

The clock is a differential comparator operating as a dual ramp integrator. The comparator is A8. The output (bare collector) is pulled up to +13V through 510 $\Omega$ . When on, the output is near zero volts; when off the output is at the reference voltage of Zener diode D4 (5.1V). Assume A8 has switched from zero to +5.1V. This places the positive input pin 2 at +3.3V (note that the positive feedback network is biased at the other side by another Zener diode D3, also The output FCOM (Frequency Common) 5.1 volts). is returned to one of the five inputs FR1-FR5 through the baud rate switch on the rear panel. The capacitor C9 charges towards +5V. When +3.3 volts is reached the comparator switches low, changing the positive input to +1.65V. Now the capacitor discharges towards ground and again switches high when +1.65 Volts is reached. The inverter A7,2 inverts FCOM to generate SCLK which

is the clock used by the UAR/T. The frequency is set by the five Cermet potentiometers R36, R38, R40, R42 and R44. The Baud Rate switch ties FCOM to FR1 for 110 Baud. The other points FR2-FR5, are 300, 1200, 2400 and 9600 baud. The frequencies are 1.76 KHZ, 4.8 KHZ, 19.2 KHZ, 38.4 KHZ and 153.6 KHZ respectively.

## 2.5.2.2 Decode and Control Logic

Input characters are screened by the decode logic to determine whether they are displayable, non-displayable or control functions. Bits four and five (B4 and B5) are decoded into four signals QDØ\*, QD1\*, QD2\* and QD3\*. These levels when low indicate in which quadrant of any pair of ASCII columns the character lies. If the character is a control character then CONTRL is true which when inverted by A7,8 enables the first 8 outputs of the BCD decoder, A5. Its outputs CDØ\* through CD7\* each go low for one of the possible combinations of B1, B2 and B3. Thus a combination of  $QD\emptyset^*-QD3^*$  and  $CD \emptyset^*-CD7^*$  can select any control character. This is done by use of NOR gates such as B5. For example, B5,1 is the Line Feed code (LF). The ASCII code for LF is 0001010. The first two zeroes are decoded by the NOR Gate D5,4 to enable A5. CD2\* goes low because B3, B2 and B1 equal 010, or 2. QD1\* goes low because bits 5 and 4 are 0 and 1 respectively. Therefore NOR gate inputs B5,2 and B5,3 are both low causing LF to be high. The other control codes used are generated in a similar manner.

The only exception to the decode method is RUBOUT which isn't in columns 0 or 1 and so must be handled differently. In section F-7, the output of NAND gate A3,8 is false when B1, B2 and B3 are true enabling NOR gate K6,2. For a RUBOUT QD3\* is low which causes NOR gate K6,1 to be high enabling A3,3. When B6 and B7 are true then A3,6 is low causing J5,12 to be low blocking ACCESS and INSTB.

For cursor address two codes are used, VT and DLE. VT is used for Vertical positioning and DLE for Horizontal. The two flip-flops (L5) in section E7 and E8 control the addressing. For vertical address VT is true which enables the D input of L5,12 (L5,8 is true allowing AND gate J8,11 to go true with VT). The trailing edge of INSTB\* sets L5,9 true and L5,8 false. L5,8 being false blocks the ACCESS signal by forcing J5,12 low. This also blocks INSTB at E8,12. The AND gate J4,10 is enabled such that when the next input is made (flipflop E7,5 pulses true) the signal YLOAD\* pulses low. This in turn loads the least significant five bits of the character following VT into the line portion of the Address Register. The trailing edge of INSTB\* resets L5,9 to false (pin 12 is low because L5,8 blocks AND gate J8,12) completing the function.

The Horizontal Address is done in the same way when DLE is input to the terminal. L5,5 now sets true generating XLOAD\* causing the character following DLE to be loaded in the character portion of the Address Register.

The signals INSTB and ACCESS are blocked during the X and Y load periods because the address characters may be recognizable control or displayable characters.

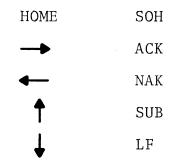

The cursors are controlled by 5 codes from the ASCII control columns (0 and 1). The codes are:

These are generated by the decode logic mentioned above. In section G-7 the logic array shown generates the pulses that are used by the Memory and Control board to move the cursor. Note that all five codes are strobed by INSTB to produce a clean signal. The Cursor Forward signal CURFR\* is a combination of the forward code (ACK) and CURCK\*, a signal from the access logic causing a cursor forward when an access to memory is made. The Cursor Up signal, UP\*, is used in a special way. The logic in section H-7 is used to cause the cursor to go home to the bottom left in Roll mode by generating a cursor up after the home code is acted upon. When the code for cursor up is

input, UP\* pulses low causing CURUP\* to pulse low via the AND gate H4,5. When a cursor home is done in Roll mode the trailing edge of the pulse HOME sets H5,9 true. The next SCLK pulse sets H5,5 true and H5,6 goes low resetting H5,9 again. H5,5 is combined with ROLL to produce a negative pulse at H5,8 causing CURUP\* to pulse low. This causes the cursor to move from the HOME position (top left) up one line which causes a wraparound to the bottom left. If ROLL is false H4,9 is blocked and the cursor remains in the top left corner.

In the lower left corner of the schematic are two more control functions, Printer Enable and Keyboard Lockout. The signal RST\* resets both J-K flip-flops (C7) upon power up. The Keyboard Lock flip-flop C7,13 (LOCK\*) is optionally reset by the BREAK\* signal or disabled by jumping J8,4 to ground. When enabled the code EOT causes LOCK\* to go false blocking the Keyboard Strobe KBSTB at D3,13. STX sets LOCK\* back true allowing the keyboard to operate again. When JP4 is inserted, the Break key may be used to unlock a locked keyboard. The other half of C7 controls the EIA Printer output. DC2 causes C7,9 to be high which enables AND gate D2,13 in section B-3. Any characters following will be output by the EIA driver F4,6. Note the input to D2,12 is the same as the serial input (inverted) to the UAR/T which means that the printer will copy whatever goes to the CRT screen in Full or Half-duplex.

# 2.5.2.3 RS232C Interface

The voltage range for the EIA standard RS232C interface is +3V to +15V for a Data zero level and -3V to -15V for a Data 1 level. Control signals such as Request to Send and Clear to Send have the same voltage swing but positive is true and negative is false.

Integrated circuits are available to translate these levels to TTL levels. The driver is a 1488 and the receiver is a 1489.

The EIA output signal, EIAOUT, is generated by F4,11 (1488). The UAR/T output is "ANDED" with BREAK\* via D3,6 to drive F4,12 and 13. BREAK\* goes false for about 1/2 second when the Break key is pressed causing a positive

level (space) on the EIA output. The output of the UAR/T is normally high and goes low for space bits causing positive levels on EIAOUT. Another section of F4 (pins 4 and 6) is used for the serial EIA printer output described before.

The receiver F5 (pins 4 and 6) is a section of a 1489 and has a TTL level output. EIAIN is converted to TTL and applied to NAND gate B3.5 for input "or-ing" to the UAR/T. If the signal (Half Duplex) is false B3,9 is blocked and HDX output data D3,6 is not gated into the UAR/T. If HDX is true then serial TTL output data is mixed with the input data to provide a local echo path. Either data from the CPU or the keyboard will be input to memory. Switch S1 connecting the output of NAND gate B3,3 to the input of B3,4 blocks the input when Request to Send is high in Half-Duplex mode to supress any echo from the external device (202C modem for instance).

The Request to Send circuitry is just above. When a key is struck, the RQOUT\* goes low (C3,6 in section C-5) which sets E6,5 true and RQSND\* false which via F4 drives RQSND true. The modem raises CLSND which when converted by F5,3 (Section C-5) allows the character to be output. RQSND remains true until an ETX, CR (AUTO LF) or LF (non-AUTO LF) is output. The flip-flop (section D-1) is set when E8,4 is true and EOC (End of Character) returns true. E8,4 is true for three conditions. Assuming JP1 and JP2 are installed, one condition is the output of ETX which when true drives H6,8 false and E8,4 true via D7. When F7,6 goes true (pin 2 grounded, F7 was preset by E6,5 being low before the process began) the signal SCLK/16 (SCLK divided by 16) clocks the flip-flop F7,8 false and then true which clocks E6,5 back low completing a Request to Send sequence. If the terminal is in AUTO LF then the CR code enables E8,4. In non-AUTO LF the LF code enables E8,4.

The NOR gate E3, 1, 2 and 3 is used to generate ATOLFG used by the Memory and Control for Erasing in non-AUTO LF mode. This is done by forcing AUTO LF true when CLRFF goes true during an Erase function.

# 2.5.2.4 Reverse Channel Control

The Reverse Channel (202C) control circuitry is in section F-3. If the reverse channel is to be used for circuit assurance and interrupt, Switch S3 should be closed. Upon power up or after a transmission, flip-flop C8,9 will be true forcing TRANS low blocking any keyboard input by clamping flip-flop C3.5 reset (Section C-5). At the same time since BREAK is false and C8,8 is false, SCA is true. SCA is the signal that causes a 202C modem to turn on the reverse channel carrier. The CPU monitors SCA for a negative condition and holds SCF normally false. SCF is the received signal detector for the reverse channel. When the user presses the Break key the signal BREAK goes true for approximately 500 milliseconds driving SCA false. The CPU detects the negative level on the reverse channel and responds by raising and dropping carrier or just dropping carrier if already raised. The trailing edge of BREAK sets flip-flop C8,5 true, conditioning the clock input of C8,11 to follow the Carrier Detect signal CARDT1. When the carrier goes false flip-flop C8,9 goes false which enables NOR gate K6,5. When SCF goes true (CPU raises SCA at its end which is SCF at the terminal) K6,6 goes false causing TRANS to go true enabling the keyboard strobe. (Note that the break signal when going true causes a negative pulse of approximately 100 nanoseconds at J5,5 presetting C8,9 true. This allows the transmit mode to be aborted with a Break.) When the transmission is complete Request to Send returns false causing RQSND\* to go true which places a 100 nanosecond negative pulse at J5,4 which presets C8,9 forcing TRANS back false. (H8 is a 74121 one-shot. The time constant is determined by R12 and C10, C11).

# 2.5.2.5 Current Loop

The Current Loop portion is in the lower right hand section. L7 and K8 are opto-isolators (MOC1000). The input stage is K8. When current is present K8,4 and 5 present a low impedance to -13V. Q5 is turned on holding the EIA input to approximately -11V (S2 is closed for current loop operation). When the loop opens (space) K8,4 and 5 present a high impedance and Q5 turns off allowing the EIA input to go to +13V. The diodes D11 and D10 are used to keep Q5 from saturating insuring that the output stage of K8 is not in an overdrive condition which would reduce the speed because of excess minority carrier storage.