# USER'S

# GUIDE

Document Revision 3 September 12, 1995

# AIC-8375

# Fast IDE Disk Controller IC

Adaptec Confidential

# **dadaptec**

# ATA Interface Block

- ▼ ATA Multiword DMA modes 0-2

- ▼ Fast IDE PIO modes 0-4

- ▼ IORDY for PIO flow control

- ▼ Automatic AT R/W command execution

- ▼ Automatic AT Task File updates

- ▼ 32-byte host FIFO

- ▼ LBA or CHS TASK File Modes

- Programmable IRQ automation to comply with different BIOS implementations

- ▼ Provides logic for daisy chaining two embedded disk drive controllers

- ▼ Hardware selectable PCMCIA 2.0

- ▼ Full BIOS compatibility

- ▼ On-Chip12 mA Host Drivers

- PCMCIA Attribute Memory stored in buffer memory

#### **Buffer Controller Block**

- ▼ 8 bit wide or 16 bit wide buffer data bus with parity

- DRAM support with up to 4 Mbyte addressing capability; up to 36 Mbyte/s (18 Mbyte/s PCMCIA) buffer bandwidth using page mode DRAM access

- SRAM support for up to 256 Kbyte direct addressing; up to 50 Mbyte/s (25 Mbyte/s PCMCIA) buffer bandwidth

- Automated Data Flow Management (ADFM) automates disk/host transfers.

- ▼ 2K page direct microprocessor access

- ▼ Variable Segmentation

- ▼ Write Cache Support

- ▼ Servo Split count out of buffer

#### **Other Features**

- ▼ 128-pin QFP and TQFP packages

- ▼ Automatic power-down modes

- ▼ High-speed, low-power CMOS

#### **EDAC Block**

- ▼ Optimized 168 bit ECC with Triple Burst on-the-fly (OTF) correction

- ▼ 65 bit single burst OTF correction in <1 sector time or 17 bit Double or Triple Burst OTF correction in <1 sector time</p>

- ▼ SW correction up to three 17-bit bursts

- ▼ Error detection of one 89-bit error, two 41-bit errors, or three 17-bit errors

- ECC seeding validating servo and head track position

- ▼ Fault tolerant sync mark detection with 2 byte sync

## **Disk Controller Block**

- ▼ Enhanced Headerless Architecture (EDSA)

- ▼ 50 Mbits/sec, 100 Mbits/sec and 120 Mbits/ sec disk rate in single, dual, and byte-wide NRZ modes respectively

- ▼ 31 x 3 byte flexible high-speed RAMbased sequencer

- ▼ Defect skipping and/or embedded servo capabilities with Constant Density Recording (CDR)

- ▼ 32-byte disk FIFO for speed matching with the buffer manager

- ▼ Two-index timer

- ▼ Supports (1,7) and (2,7) RLL interfaces

- ▼ MR and PRML channel support

#### **Microcontroller Interface Block**

- Direct support for Intel or Motorola multiplexed or non-multiplexed interfaces

- Ready line for interfacing to faster microprocessors and for direct microprocessor access to the Buffer

- ▼ Programmable open drain interrupt output for host, disk, and buffer

- ▼ Address latch outputs for multiplexed microprocessor interface

- Direct buffer addressing in programmable 2K windows with 1K resolution on base address

Copyright© 1995 Adaptec, Inc. All rights reserved. The information contained in this document (including all revisions) is the confidential, trade secret and proprietary property of Adaptec, Inc. It may not be used, copied, distributed, or disclosed without the express written permission of Adaptec, Inc. Adaptec and the Adaptec logo are registered trademarks of Adaptec, Inc. All other trademarks used are owned by their respective owners. The information contained in this document is subject to change without notice.

# Table of Contents

| REVISION | EVISION NOTESX |                                                        |      |  |

|----------|----------------|--------------------------------------------------------|------|--|

| SECTION  | 1 - OVE        | ERVIEW                                                 | 1    |  |

| 1.1      | Introdu        | ction                                                  | 1    |  |

| 1.2      | General        | Description and Features                               | 1    |  |

|          | 1.2.1          | The Local Microprocessor Interface Block               |      |  |

|          | 1.2.2          | The Host Interface Block                               |      |  |

|          | 1.2.3          | The Buffer Control Block                               |      |  |

|          | 1.2.4          | The Disk Control Block                                 |      |  |

|          | 1.2.5          | Power Management                                       | 8    |  |

| SECTION  | 2 - HAF        | RDWARE DESIGN INFORMATION                              | 9    |  |

| 2.1      | Interfac       | ing to the Local Microprocessor                        | 9    |  |

|          | 2.1.1          | Selecting the Microprocessor Bus Mode                  | 9    |  |

|          | 2.1.2          | Selecting Multiplexed or Non-Multiplexed Address Mode  | . 10 |  |

|          | 2.1.3          | Enabling the Internal Address Latch                    | 10   |  |

|          | 2.1.4          | Chip Select Generation and Memory Mapping              |      |  |

|          | 2.1.5          | Using the Ready Signal                                 | .11  |  |

|          | 2.1.6          | Interrupt Sources to the Microprocessor                | .11  |  |

| 2.2      | Buffer H       | RAM Device Selection                                   | .12  |  |

|          | 2.2.1          | Static RAM                                             | .12  |  |

|          | 2.2.2          | Dynamic RAM                                            | .15  |  |

| 2.3      | Interfac       | ing to the Host                                        | .18  |  |

|          | 2.3.1          | Selecting ATA or PCMCIA Mode                           | .18  |  |

|          |                | 2.3.1.1 Automatic Detection                            | .18  |  |

|          |                | 2.3.1.2 Programmed Selection                           | .18  |  |

|          |                | 2.3.1.3 Initializing the AIC-8375 for PCMCIA Operation | .18  |  |

|          |                | 2.3.1.4 Initializing the AIC-8375 for ATA Operation    | .18  |  |

|          | 2.3.2          | ATA/IDE Interface Support                              | .19  |  |

|          | 2.3.3          | AT Register Mapping                                    | .19  |  |

|          | 2.3.4          | ATA Interface Signal Requirements                      | .20  |  |

|          |                | 2.3.4.1 Bus Drivers and Receivers                      | .20  |  |

|          |                | 2.3.4.2 Specific ATA Signal Requirements               | .20  |  |

|          | 2.3.5          | Master/Slave Support                                   | .20  |  |

|          | 2.3.6          | PCMCIA Interface Support                               | .21  |  |

|          |                | 2.3.6.1 Primary/Secondary I/O Mode Addressing          | .22  |  |

|          |                | 2.3.6.2 Block I/O (Independent) Mode Addressing        | .23  |  |

|        | 2.3.6.3 Memory Mode Addressing                                                                                     |  |

|--------|--------------------------------------------------------------------------------------------------------------------|--|

|        | 2.3.7 Attribute Memory                                                                                             |  |

|        | 2.3.7.1 Card Information Structure (CIS)                                                                           |  |

|        | 2.3.7.2 Card Configuration Registers (CCR)                                                                         |  |

| 2.4    | Interfacing to the Drive Electronics                                                                               |  |

|        | 2.4.1 NRZ Data Configuration                                                                                       |  |

|        | 2.4.2 Control/Status Signals                                                                                       |  |

| 2.5    | Read Reference and Buffer Clock                                                                                    |  |

| 2.6    | Power-On Reset (*POR) Condition                                                                                    |  |

| 2.7    | Configuration/Option Switch Interface                                                                              |  |

| 2.8    | Miscellaneous Design Information                                                                                   |  |

|        | 2.8.1 Power/Temperature Requirements                                                                               |  |

|        | 2.8.2 Unconnected Pins                                                                                             |  |

|        |                                                                                                                    |  |

| SECTIO | N 3 - FUNCTIONAL DESCRIPTION                                                                                       |  |

| 3.1    | Microprocessor Interface and Control                                                                               |  |

|        | 3.1.1 Microprocessor Interface Block Architecture                                                                  |  |

|        | 3.1.2 Interrupt Generation                                                                                         |  |

|        | 3.1.2.1 Host Block Interrupts                                                                                      |  |

|        | 3.1.2.2 Buffer Block Interrupts                                                                                    |  |

|        | 3.1.2.3 Disk Block Interrupts                                                                                      |  |

|        | 3.1.3 Intel and Motorola Mode Memory Mapping                                                                       |  |

|        | 3.1.4 Microprocessor Access of the Internal Device Registers                                                       |  |

|        | 3.1.5 Microprocessor Access of the Buffer RAM                                                                      |  |

|        | 3.1.5.1 Buffer RAM Read                                                                                            |  |

|        | 3.1.5.2 Buffer RAM Write                                                                                           |  |

|        | 3.1.6 Microprocessor Access of the Disk Sequencer RAM                                                              |  |

|        | 3.1.7 Microprocessor Access of the Configuration/Option Switches                                                   |  |

|        | 3.1.8 Microprocessor Block Initialization                                                                          |  |

| 3.2    | AT Host Interface and Control                                                                                      |  |

|        | <ul> <li>3.2.1 AT Host Interface Block Architecture</li> <li>3.2.2 AT Software Reset and Hardware Reset</li> </ul> |  |

|        | 3.2.2 AT Software Reset and Hardware Reset                                                                         |  |

|        | 3.2.3 Master/Slave Drive Option                                                                                    |  |

|        | 3.2.3.2 Logical Implementation                                                                                     |  |

|        | 3.2.4 Transfer Modes                                                                                               |  |

|        | 3.2.4.1 PIO Transfer Mode                                                                                          |  |

|        | 3.2.4.2 Single-Word DMA Transfer Mode                                                                              |  |

|        | 3.2.4.3 Multi-Word DMA Transfer Mode                                                                               |  |

|        |                                                                                                                    |  |

| 3.2.5  | AT Host Automation                                          | 54 |

|--------|-------------------------------------------------------------|----|

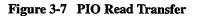

|        | 3.2.5.1 PIO Transfer Mode Automation                        | 54 |

|        | 3.2.5.2 Task File Update Control                            | 58 |

|        | 3.2.5.3 IRQ Mode / Interblock Gap Automation                | 59 |

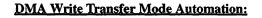

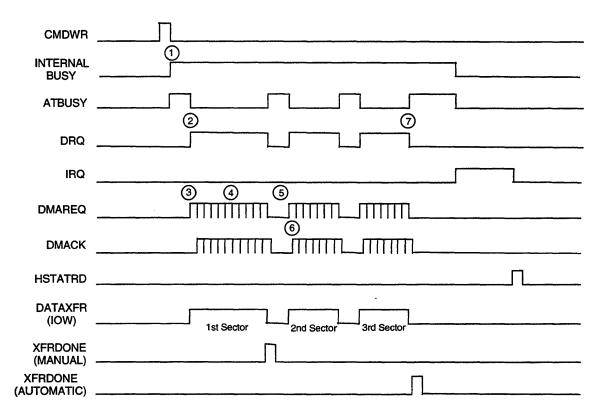

|        | 3.2.5.4 DMA Transfer Mode Automation                        | 61 |

|        | 3.2.5.5 Auto-Write Command Execution                        | 65 |

|        | 3.2.5.6 Auto-Read Command Execution                         | 65 |

|        | 3.2.5.7 Automatic Multi-Sector Write Transfers              | 66 |

|        | 3.2.5.8 Automatic Multi-Sector Read Transfers               | 67 |

| 3.2.6  | AT Host Manual Operation                                    | 67 |

| 3.2.7  | Starting and Stopping Transfers Between the Host and Buffer | 67 |

| 3.2.8  | PCMCIA Interface Functionality                              | 69 |

|        | 3.2.8.1 Addressing Modes                                    | 69 |

|        | 3.2.8.2 Primary/Secondary I/O Mode Addressing               | 69 |

|        | 3.2.8.3 Block I/O (Independent) Mode Addressing             | 69 |

|        | 3.2.8.4 Memory Mode Addressing                              | 69 |

| 3.2.9  | Host / Buffer ECC Transfers                                 | 70 |

|        | 3.2.9.1 Write Long Transfers                                | 70 |

|        | 3.2.9.2 Read Long Transfers                                 |    |

| 3.2.10 | Host FIFO Operation                                         | 73 |

| 3.2.11 | Host Logical Block Addressing                               | 75 |

| 3.2.12 | Host Block Initialization                                   | 76 |

| 3.2.13 | ATA Write Command Execution                                 | 77 |

|        | 3.2.13.1 Auto-Write Sector(s)                               | 77 |

|        | 3.2.13.2 Manual Write Sector(s)                             | 78 |

|        | 3.2.13.3 Auto-Write Long                                    | 79 |

|        | 3.2.13.4 Manual Write Long                                  | 79 |

|        | 3.2.13.5 Auto-Write Multiple                                |    |

|        | 3.2.13.6 Manual Write Multiple                              |    |

|        | 3.2.13.7 Auto-Write DMA                                     | 81 |

|        | 3.2.13.8 Manual Write DMA                                   |    |

| 3.2.14 | ATA Read Command Execution                                  | 83 |

|        | 3.2.14.1 Auto-Read Sector(s)                                | 83 |

|        | 3.2.14.2 Automated Read Sector(s)                           | 84 |

|        | 3.2.14.3 Manual Read Sector(s)                              | 84 |

|        | 3.2.14.4 Manual Read Long                                   |    |

|        | 3.2.14.5 Auto-Read Multiple                                 | 85 |

|        | 3.2.14.6 Manual Read Multiple                               |    |

|        | 3.2.14.7 Auto-Read DMA                                      |    |

|        | 3.2.14.8 Manual Read DMA                                    | 88 |

|        |                                                             |    |

|     |         | 3.2.14.9 Read Verify                                       | 88          |

|-----|---------|------------------------------------------------------------|-------------|

| 3.3 | Data B  | Iffer Interface and Control                                | 89          |

|     | 3.3.1   | Buffer Block Architecture                                  | 89          |

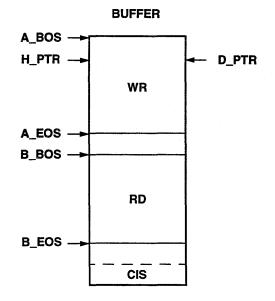

|     | 3.3.2   | Buffer Segmentation                                        | <b> 9</b> 1 |

|     | 3.3.3   | Host Port Transfers                                        | 94          |

|     | 3.3.4   | Disk Port Transfer                                         | 97          |

|     | 3.3.5   | Correction Port Transfers                                  | 100         |

|     | 3.3.6   | Servo Port Transfers                                       | 101         |

|     | 3.3.7   | Host CIS Port Transfers                                    | 101         |

|     | 3.3.8   | Buffer Access Priority                                     | 101         |

|     | 3.3.9   | Buffer Automation                                          | 102         |

|     | 3.3.10  | Manual Buffer Operation                                    | 1 <b>07</b> |

|     | 3.3.11  | Buffer Block Initialization                                | 108         |

| 3.4 | Disk In | erface and Control                                         | 110         |

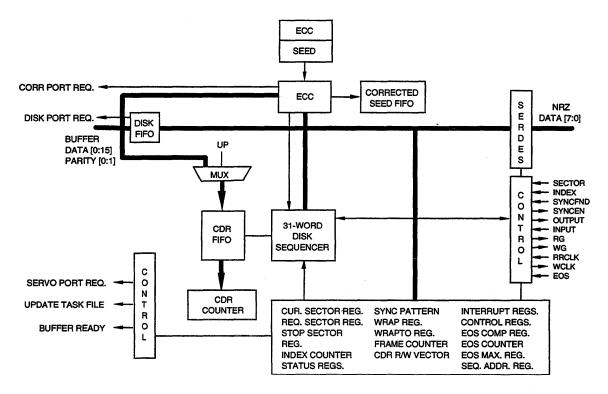

|     | 3.4.1   | Disk Block Architecture                                    | 110         |

|     | 3.4.2   | Disk Sequencer Operation                                   | 110         |

|     |         | 3.4.2.1 Time-Out Functions                                 | 111         |

|     |         | 3.4.2.2 Decision / Branching Functions                     | 111         |

|     |         | 3.4.2.3 Counting Functions                                 | 111         |

|     |         | 3.4.2.4 Compare Functions                                  | 112         |

|     |         | 3.4.2.5 Input / Output Functions                           | 112         |

|     |         | 3.4.2.6 Control Functions                                  | 112         |

|     |         | 3.4.2.7 Frame Counter                                      | 112         |

|     |         | 3.4.2.8 Starting and Stopping the Disk Sequencer           | 113         |

|     | 3.4.3   | Automatic Frame and Sector Management (EDSA Mode)          | 114         |

|     |         | 3.4.3.1 Two-Byte Sector Number                             | 115         |

|     | 3.4.4   | Data Sync Generation and Detection                         | 115         |

|     |         | 3.4.4.1 Single-Byte Internal Sync Generation and Detection | 115         |

|     |         | 3.4.4.2 Fault Tolerant Sync Generation and Detection       | 116         |

|     |         | 3.4.4.3 External Sync Byte Generation and Detection        | 116         |

|     | 3.4.5   | Disk NRZ Data Operating Modes                              | 117         |

|     |         | 3.4.5.1 Single-Bit NRZ Operation                           | 117         |

|     |         | 3.4.5.2 Dual-Bit NRZ Operation                             | 117         |

|     |         | 3.4.5.3 Eight-Bit NRZ Operation                            | 118         |

|     | 3.4.6   | Disk FIFO Operation                                        | 118         |

|     | 3.4.7   | Disk Block Automation                                      | 119         |

|     | 3.4.8   | Disk Block Initialization                                  | 120         |

|     | 3.4.9   | Disk Operation Execution                                   | 121         |

|     |         | 3.4.9.1 Format Operation                                   | 121         |

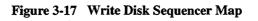

|     |         | 3.4.9.2 Write Operation                                    | 124         |

iv

|     |         | 3.4.9.3 Write Long Operation                                                | 127   |

|-----|---------|-----------------------------------------------------------------------------|-------|

|     |         | 3.4.9.4 Read Operation                                                      | 130   |

|     |         | 3.4.9.5 Read Long Operation                                                 | 133   |

|     |         | 3.4.9.6 Read Verify Operation                                               | 136   |

| 3.5 | Split D | Data Field/Constant Density Recording (CDR) Support                         | 138   |

|     | 3.5.1   | Generating the CDR Interrupt                                                | 139   |

|     | 3.5.2   | Loading Servo Split Locations From the Microprocessor                       | 140   |

|     | 3.5.3   | Loading Servo Split Locations From the Buffer                               | 140   |

|     | 3.5.4   | Skipping the Servo Burst During Read/Write Operations                       | 141   |

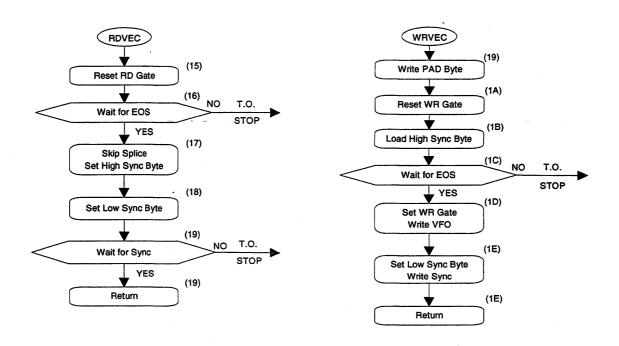

|     |         | 3.5.4.1 CDR Read Vector                                                     | 141   |

|     |         | 3.5.4.2 CDR Write Vector                                                    | 141   |

|     |         | 3.5.4.3 End Of Servo Input                                                  | 141   |

|     | 3.5.5   | Skipping the Servo Burst During Format Operations                           | 142   |

|     | 3.5.6   | External CDR Interrupt                                                      | 142   |

| 3.6 | Error I | Detection and Correction                                                    | 143   |

|     | 3.6.1   | Data Field EDAC                                                             | 143   |

|     |         | 3.6.1.1 Data Field EDAC Specification and Capabilities                      | 144   |

|     |         | 3.6.1.2 ECC seed injection theory of operation                              | 147   |

|     |         | 3.6.1.3 Using Interleaves When Analyzing Or Testing ECC                     | 149   |

|     |         | 3.6.1.4 Read and Write Operation Using Data Field Hardware EDAC             |       |

|     |         | 3.6.1.5 Verify Operation                                                    | 152   |

|     |         | 3.6.1.6 Read Long Operation                                                 |       |

|     | 3.6.2   | Probabilities of Uncorrectable Errors and Miscorrection                     |       |

| 3.7 | EDSA    | Headerless Format Support                                                   |       |

|     | 3.7.1   | Details of EDSA Implementation                                              |       |

|     |         | 3.7.1.1 The EOS Counter Function                                            |       |

|     |         | 3.7.1.2 The Current Sector Register (Reg. 5Ah, 5Bh)                         |       |

|     |         | 3.7.1.3 The Requested Sector Register (Reg. 6Ch, 6Dh)                       |       |

|     |         | 3.7.1.4 The EOS Signal                                                      |       |

|     |         | 3.7.1.5 Sector Mark                                                         |       |

|     |         | 3.7.1.6 Index Mark                                                          |       |

|     |         | 3.7.1.7 Servo Segment                                                       |       |

|     |         | 3.7.1.8 Servo Page Pointer                                                  |       |

|     | 3.7.2   | Servo Pointer                                                               |       |

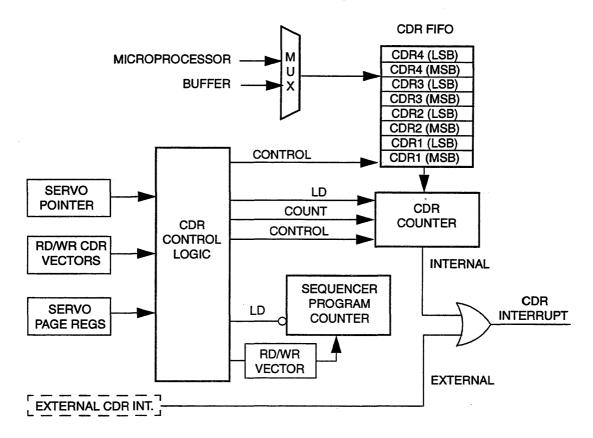

|     |         | 3.7.2.1 Data Split Table                                                    |       |

|     |         | 3.7.2.2 Data Split Word                                                     |       |

|     |         | 3.7.2.3 Defect Table                                                        |       |

|     |         | 3.7.2.4 The Enable Reading Servo Counts From Buffer Bit (Reg. 63h, R/W, bit | 1)158 |

|     |         | 3.7.2.5 The Wait for EOS Compare Equal Decode (Alternate, BRSEL = '100')    |       |

|     |         | 3.7.2.6 The Wait for Sector Valid Decode (Alternate, BRSEL = '111')         |       |

|     |       |         | 3.7.2.7 The LOAD CDR FIFO Decode (Primary, SEQCTLC = '001')               |     |

|-----|-------|---------|---------------------------------------------------------------------------|-----|

|     |       |         | 3.7.2.8 The Wait for Defect Flag Decode (Alternate, BRSEL = '000')        | 159 |

|     |       |         | 3.7.2.9 The CDR Parity Error Bit (Reg. 64h, R, bit 6)                     |     |

|     |       |         | 3.7.2.10 The Wait for EOS Decode (Alternate, BRSEL = '001')               | 159 |

|     |       |         | 3.7.2.11 The Increment Current Sector Decode (Primary, SEQCTLB = '01')    |     |

|     |       |         | 3.7.2.12 The Increment Requested Sector Decode (Primary, SEQCTLC = '010') |     |

|     |       | 3.7.3   | Example EDSA Headerless Implementation                                    |     |

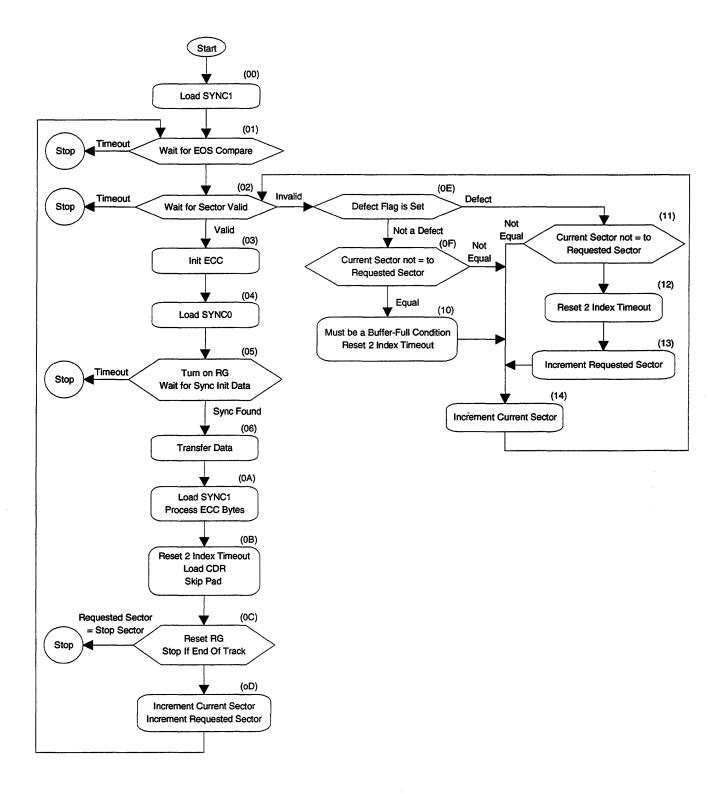

|     |       |         | 3.7.3.1 Example - Simple Five-Sector Read                                 | 160 |

|     | 3.8   | Automa  | atic Data Flow Management                                                 | 165 |

|     |       | 3.8.1   | All the Blocks Work Together                                              | 166 |

|     |       | 3.8.2   | Boundary Conditions                                                       | 166 |

|     |       | 3.8.3   | Write Command Flow Example                                                |     |

|     |       | 3.8.4   | Read Command Flow Example                                                 | 174 |

|     | 3.9   | Power 3 | Management                                                                | 181 |

|     |       | 3.9.1   | Power Down Modes                                                          | 181 |

|     |       |         | 3.9.1.1 Disk Block Power Management                                       | 181 |

|     |       |         | 3.9.1.2 Buffer Block Power Management                                     | 182 |

|     |       |         | 3.9.1.3 Host Block Power Management                                       | 183 |

|     |       |         |                                                                           |     |

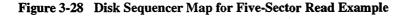

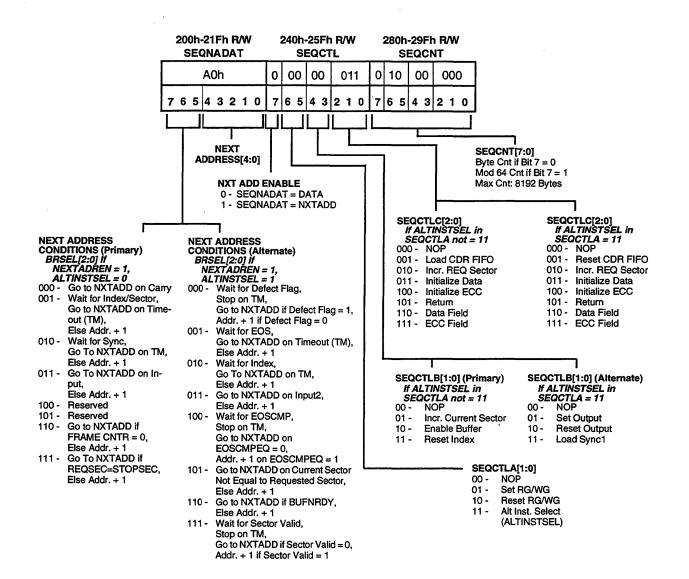

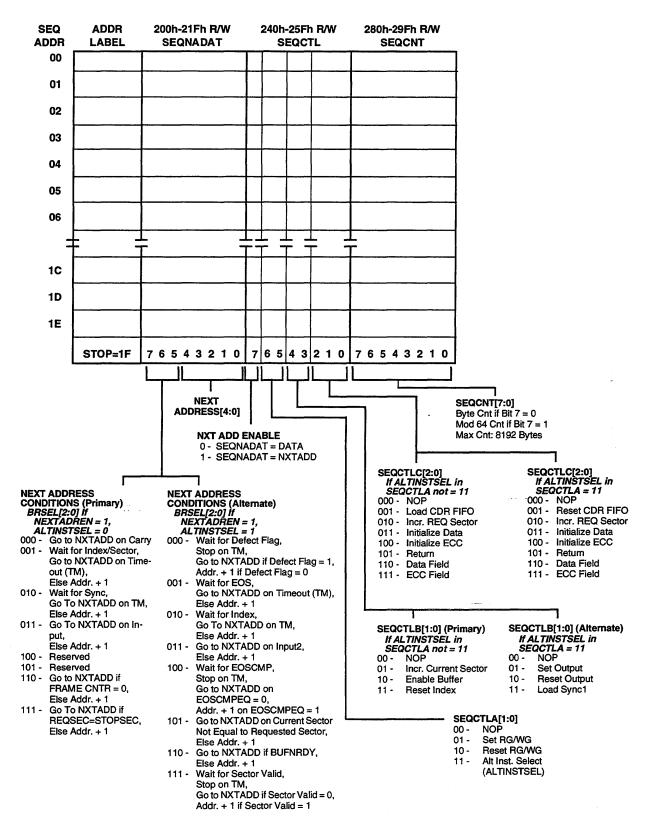

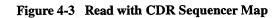

| SEC | CTION | 4 - THE | E DISK SEQUENCER MAP                                                      | 185 |

|     | 4.1   | Overvie | ew Of The Disk Sequencer Map                                              | 185 |

|     | 4.2   | Sequen  | cer Data/Next Address Byte (200h-21Fh, R/W, SEQNADAT)                     | 186 |

|     |       | 4.2.1   | Data Field                                                                | 187 |

|     |       | 4.2.2   | Next Address Field                                                        | 187 |

|     | 4.3   | Sequen  | cer Control Byte (240h-25Fh, R/W, SEQCTL)                                 | 191 |

|     | 4.4   |         | cer Count Byte (280h-29Fh, R/W, SEQCNT)                                   |     |

|     | 4.5   | -       | equencer Examples                                                         |     |

|     |       | 4.5.1   | EDSA Read/Write/Format With CDR Example                                   |     |

|     |       | 4.5.2   | Write Sequencer Modification                                              |     |

|     |       | 4.5.3   | Format Sequencer Modification                                             |     |

|     |       |         |                                                                           |     |

| ADI | DEND  | UM - OI | PERATIONAL CHARACTERISTICS - (8/28/95)                                    | 199 |

|     | A1.1  |         | lock - No operational characteristics noted.                              |     |

|     | A1.2  |         | Block - No operational characteristics noted.                             |     |

|     |       |         |                                                                           |     |

|     | A1.3  |         | lock<br>Reset 2 Index Timeout Operational Characteristic                  |     |

|     |       |         |                                                                           |     |

|     | A1.4  | -       | rocessor Block - No operational characteristics noted.                    |     |

|     | A1.5  | ECC B   | lock - No operational characteristics noted.                              | 199 |

# List of Tables

| Table 1-1  | Compatible Microprocessors                                                  | 2   |

|------------|-----------------------------------------------------------------------------|-----|

| Table 2-1  | Microprocessor Class PSEL[1:0] Values                                       | 9   |

| Table 2-2  | 8-bit SRAM Buffer Configuration                                             | 12  |

| Table 2-3  | 16-bit SRAM Buffer Configurations                                           |     |

| Table 2-4  | DRAM Address Bit Specification (8-bit Mode)                                 | 15  |

| Table 2-5  | DRAM Address Bit Specification (16-bit Mode)                                | 15  |

| Table 2-6  | AT Register Mapping                                                         | 19  |

| Table 2-7  | AIC-8375 Addressing Modes for Host Access                                   | 22  |

| Table 2-8  | Primary/Secondary I/O Mode Addresses                                        | 22  |

| Table 2-9  | Block I/O Mode Addresses                                                    | 23  |

| Table 2-10 | Task File ATA Register Accesses in Block I/O and Memory Addressing Modes    | 24  |

| Table 2-11 | 16-Bit Task File Register Accesses in Block I/O and Memory Addressing Modes | 24  |

| Table 2-12 | Memory Address Block 1                                                      | 26  |

| Table 2-13 | Memory Address Block 2                                                      | 26  |

| Table 2-14 | Task File Register Access in Memory Addressing Mode                         | 27  |

| Table 3-1  | Registers and Bits Used With Host Block Interrupts                          | 35  |

| Table 3-2  | Registers and Bits Used With Buffer Block Interrupts                        | 36  |

| Table 3-3  | Registers and Bits Used With Disk Block Interrupts                          | 37  |

| Table 3-4  | Synchronous Registers                                                       |     |

| Table 3-5  | Registers and Bits Used During Microprocessor Accesses Of Buffer RAM        | 39  |

| Table 3-6  | Registers and Bits Associated With Host Resets                              | 47  |

| Table 3-7  | Registers, Bits, and Pins Used For the AT Master/Slave Environment          | 48  |

| Table 3-8  | Registers and Bits Associated With Transfer Modes                           | 50  |

| Table 3-9  | Control and Status Bits Available For Use In PIO Transfer Mode              | 57  |

| Table 3-10 | Task File Register Update Conditions                                        | 58  |

| Table 3-11 | Additional Control and Status Bits For Use In DMA Transfer Mode             | 64  |

| Table 3-12 | CHS and LBA Mode Details                                                    | 75  |

| Table 3-13 | Host Block Initialization                                                   | 77  |

| Table 3-14 | Registers Used To Configure Segments                                        | 91  |

| Table 3-15 | HBC Wrap Value Selection                                                    | 95  |

| Table 3-16 | Key Registers and Bits used to Manage Host/Buffer Transfers                 | 96  |

| Table 3-17 | DBC Wrap Value Selection                                                    | 98  |

| Table 3-18 | Key Registers and Bits used to Manage Disk/Buffer Transfers                 | 99  |

| Table 3-19 | Buffer RAM Access Priorities                                                |     |

| Table 3-20 | Buffer Block Initialization                                                 |     |

| Table 3-21 | Disk Block General Initialization                                           | 120 |

| Table 3-22 | Disk Block Specific Initialization                                |     |

|------------|-------------------------------------------------------------------|-----|

| Table 3-23 | Format Operation Flow                                             |     |

| Table 3-24 | Write Operation Flow                                              |     |

| Table 3-25 | Write Long Operation Flow                                         |     |

| Table 3-26 | Read Operation Flow                                               |     |

| Table 3-27 | Read Long Operation Flow                                          |     |

| Table 3-28 | Read Verify Operation Flow                                        |     |

| Table 3-29 | Guaranteed Correctable and Detectable Error Burst Spans (#bits)   |     |

| Table 3-30 | Interleave Locations for 512-Byte Sector                          |     |

| Table 3-31 | Triple Error Correction Probability (3 Interleaves)               |     |

| Table 3-32 | Double Error Correction Probability (3 Interleaves)               |     |

| Table 3-33 | Triple Error Correction Probability (1 Interleave)                |     |

| Table 3-34 | Double Error Correction Probability (1 Interleave)                |     |

| Table 3-35 | The Data Split Word Format                                        |     |

| Table 3-36 | Data Split Table for the Example                                  |     |

| Table 3-37 | Summary of Events for Example                                     |     |

| Table 3-38 | Buffer Management Configurations for Host/Buffer Write Operations |     |

| Table 3-39 | Buffer Management Configurations for Host/Buffer Read Operations  |     |

| Table 3-40 | Write Command Host Block Setup                                    |     |

| Table 3-41 | Write Command Buffer Block Setup                                  |     |

| Table 3-42 | Disk Block Specific Initialization                                |     |

| Table 3-43 | Write Command Flow                                                | 170 |

| Table 3-44 | Read Command Host Block Setup                                     |     |

| Table 3-45 | Read Command Buffer Block Setup                                   | 175 |

| Table 3-46 | Read Command Disk Block Setup                                     |     |

| Table 3-47 | Read Command Flow                                                 | 177 |

| Table 3-48 | Summary of Available Power Management Control Bits                |     |

| Table 4-1  | Relationship Between Byte Time and Read Reference Clock (RRCLK)   |     |

| Table 4-2  | Disk Sequencer Data Sources                                       |     |

| Table 4-3  | Sequencer Program Flow Instructions                               |     |

# List of Figures

| Figure 1-1  | AIC-8375 Block Diagram                                    | 2   |

|-------------|-----------------------------------------------------------|-----|

| Figure 2-1  | SRAM Performance Relationships                            | 14  |

| Figure 2-2  | DRAM Performance Relationships                            |     |

| Figure 2-3  | Switch Placement on the Buffer Data Bus                   | 32  |

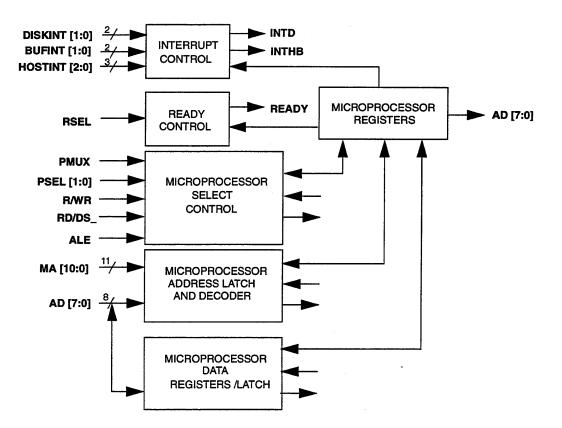

| Figure 3-1  | Microprocessor Interface Block                            | 34  |

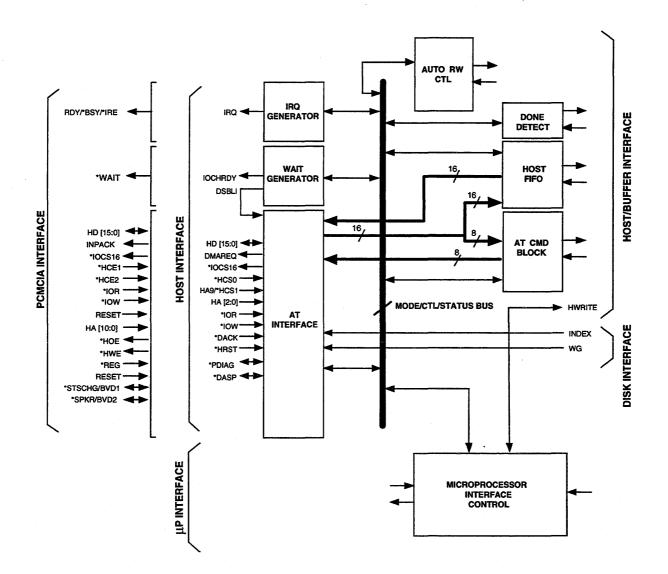

| Figure 3-2  | AT Host Block Architecture                                | 46  |

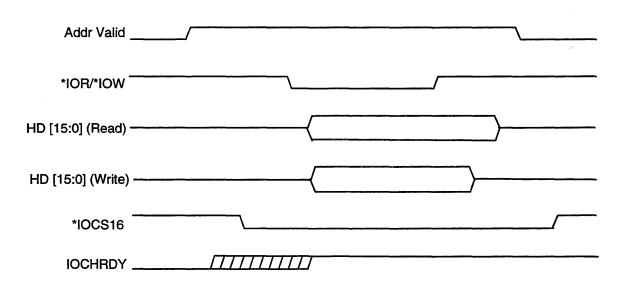

| Figure 3-3  | Typical PIO Mode Transfer                                 | 51  |

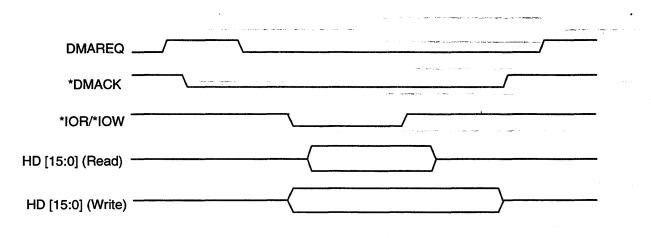

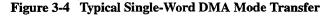

| Figure 3-4  | Typical Single-Word DMA Mode Transfer                     | 52  |

| Figure 3-5  | Typical Multi-Word DMA Mode Transfer                      | 53  |

| Figure 3-6  | PIO Write Transfer                                        | 54  |

| Figure 3-7  | PIO Read Transfer                                         | 56  |

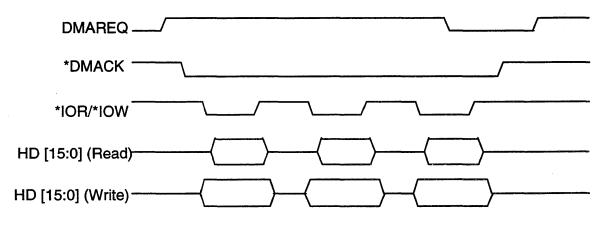

| Figure 3-8  | DMA Write Transfer                                        | 61  |

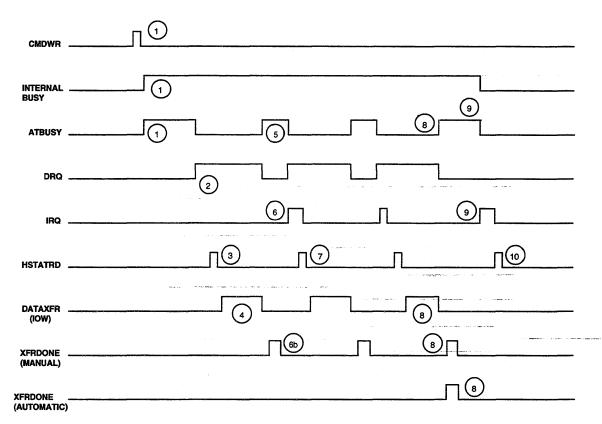

| Figure 3-9  | DMA Read Transfer                                         | 63  |

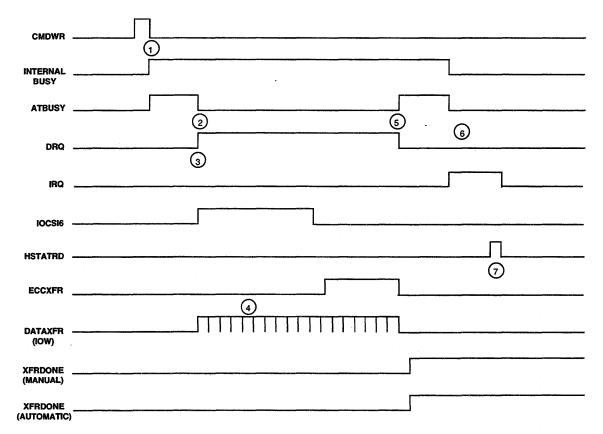

| Figure 3-10 | Write Long Transfers                                      | 70  |

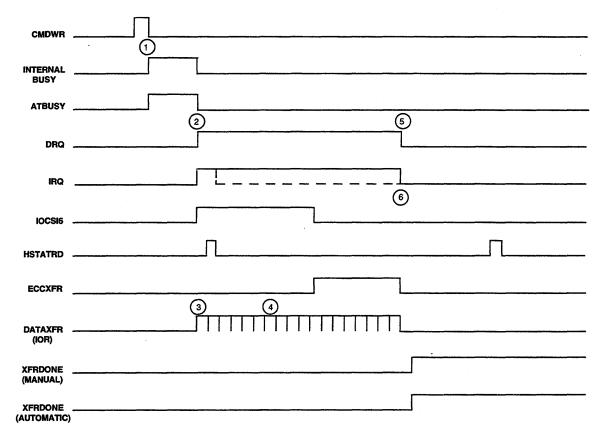

| Figure 3-11 | Read Long Transfers                                       | 72  |

| Figure 3-12 | Buffer Block Architecture                                 | 90  |

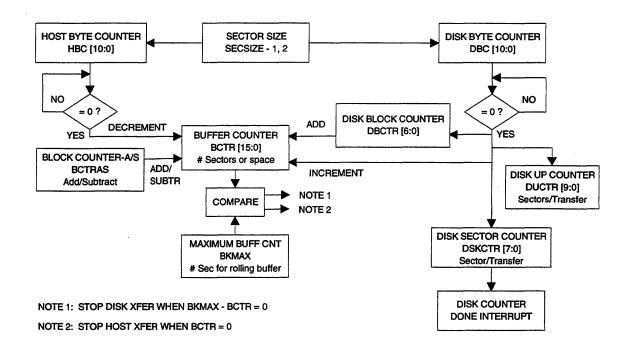

| Figure 3-13 | Buffer Empty/Full (BCTR) Automation Control Block Diagram |     |

| Figure 3-14 | A Typical Buffer Segmentation Scheme                      |     |

| Figure 3-15 | Disk Block Architecture                                   |     |

| Figure 3-16 | Format Disk Sequencer Map                                 |     |

| Figure 3-17 | Write Disk Sequencer Map                                  |     |

| Figure 3-18 | Write Long Disk Sequencer Map                             |     |

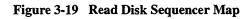

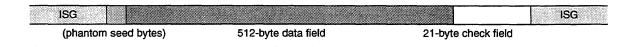

| Figure 3-19 | Read Disk Sequencer Map                                   |     |

| Figure 3-20 | Read Long Disk Sequencer Map                              |     |

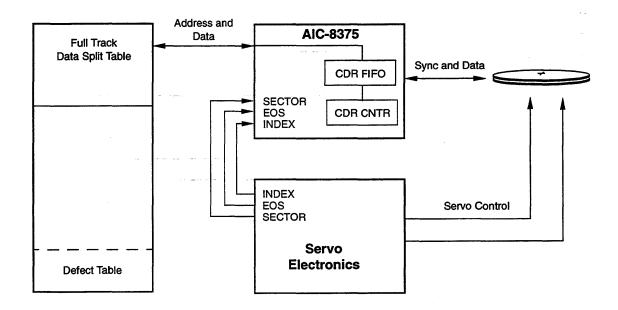

| Figure 3-21 | CDR Circuitry                                             |     |

| Figure 3-22 | Data Split Word Format                                    |     |

| Figure 3-23 | Sector Interleave Organization                            | 145 |

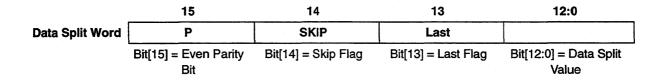

| Figure 3-24 | Sector Layout                                             | 145 |

| Figure 3-25 | Major Blocks and Signals for EDSA Headerless              |     |

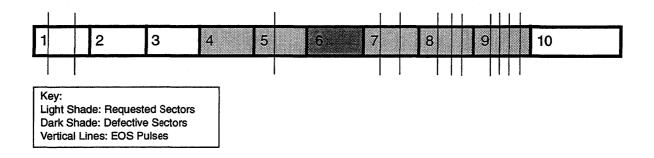

| Figure 3-26 | Track Layout for the Example                              |     |

| Figure 3-27 | Read Operation Flow for Five-Sector Read Example          |     |

| Figure 3-28 | Disk Sequencer Map for Five-Sector Read Example           |     |

| Figure 4-1  | Sequencer Map Format                                      |     |

| Figure 4-2  | Blank Sequencer Map                                       |     |

| Figure 4-3  | Read with CDR Sequencer Map                               |     |

# **REVISION NOTES** for AIC-8375 User's Guide (PN 700191-011A Rev 3) - September 1995

In this document, **all** changes to technical information incorporated by *Rev 3* are indicated by a change bar in the left-hand margin. (Superficial or non-technical edits are not indicated.)

This page contains a list of pages having technical information that has changed from Rev 2 to Rev 3.

#### **Changes Incorporated Into Rev 3**

| Section         Pages         Change Description           Updated         Affected         Change Description |                                                                                                                                                                                | Change Description                                                                                                    |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Front Cover                                                                                                    | -                                                                                                                                                                              | Chip revision level removed from title.                                                                               |

| 2.3.1.3                                                                                                        | 18                                                                                                                                                                             | Two bulleted items added regarding the CIS.                                                                           |

| 3.6                                                                                                            | 3.6       143       Removed sentence - "Software correction is optionally available etc."         Removed bullet - "Handles user data block sizea from 360 to 744 bytes. etc." |                                                                                                                       |

| 3.6.1.1                                                                                                        | 3.6.1.1144Changed second bullet to "A maximum of 744 data bytes can be handled<br>the ECC (the max under ATA spec is currently 512 bytes)."                                    |                                                                                                                       |

| 3.6.1.1                                                                                                        | 3.6.1.1 146 Changed 219 NRZ byte times to 320 - changed Table 3-29.                                                                                                            |                                                                                                                       |

| 3.6.1.3                                                                                                        | 3.6.1.3 149 Added note to Table 3-30.                                                                                                                                          |                                                                                                                       |

| 3.6.1.4                                                                                                        | 3.6.1.4 152 Added reference to ECC Correction Threshold to first bulleted item.                                                                                                |                                                                                                                       |

| 3.6.2                                                                                                          | 3.6.2 153-154 Changed text. Changed Tables 3-31 & 3-32 to 3-31 - 3-34.                                                                                                         |                                                                                                                       |

| 4.2.2                                                                                                          | 188                                                                                                                                                                            | Deleted "pointed to by the 'Next Address' instruction etc." from "Note."<br>Add SYNCEN pin statement to decode '010'. |

# **1.1 Introduction**

The Adaptec AIC-8375 is an automated single-chip disk controller designed for high performance embedded ISA/EISA/ATA and PCMCIA drive applications. The AIC-8375 has evolved from the AIC-8371 and is targeted for low cost, high performance headerless drive designs. It incorporates significant new advances over the AIC-8265 series of controller devices in the areas of AT automation, disk format, buffer management, and increased data rate. These advances provide the designer with methods for bridging the increasing gap between host processor performance (MIPS) and disk drive performance (I/Os per second).

The AIC-8375 is capable of executing full track read/write operations, at a maximum disk rate of up to 50 Mbits/sec in single NRZ mode, 100 Mbits/sec in dual NRZ mode, and 120 Mbits/sec in byte wide NRZ mode, with complete automation including full automation of the various sub-functions such as error detection and correction, buffer data flow management, embedded servo or defect algorithms, and AT interface management. The various functional blocks within the device work together automatically to ensure proper data flow management and data integrity. This automation provides the local microprocessor with more bandwidth to apply to other tasks such as servo control functions. Alternately, the improved bandwidth may be applied towards the use of a lower performance microprocessor to further increase the performance/price ratio.

Designed using high speed CMOS technology, the AIC-8375 provides a hierarchy of power down and automatic wake up modes for power sensitive applications.

# **1.2 General Description and Features**

The AIC-8375 works in conjunction with a local microprocessor to perform the ISA/EISA/ATA and PCMCIA interface control, buffer data flow management, disk format/read/write control, and error correction functions of an embedded disk drive controller. The microprocessor communicates with the AIC-8375 by reading from and writing to its various internal registers.

To the microprocessor, the registers of the AIC-8375 appear as unique memory or I/O locations that are randomly accessed and operated upon. By reading from and writing to the registers, the local microprocessor initiates operations and examines the status of the different functional blocks. Once an operation is started, successful completion or an error condition may cause the AIC-8375 to interrupt the local microprocessor, which then examines the status registers of the AIC-8375 and determines an appropriate course of action. The local microprocessor may also poll the device to ascertain successful completion or error conditions.

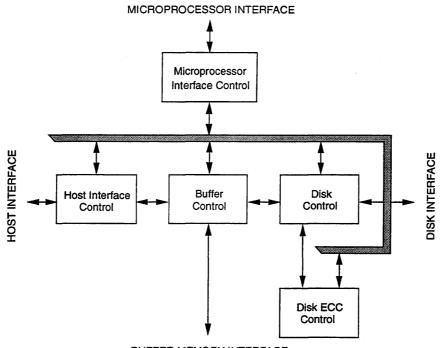

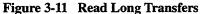

Figure 1-1 reveals the various blocks within the AIC-8375 along with their generalized interconnection. The blocks described in this figure will be referred to throughout this document.

BUFFER MEMORY INTERFACE

Figure 1-1 AIC-8375 Block Diagram

#### **1.2.1 The Local Microprocessor Interface Block**

It is through the Local Microprocessor Interface Block that the local microprocessor communicates to the other control blocks within the device or to the buffer. The AIC-8375 supports Intel and Motorola type 8-bit multiplexed address/data busses. Non-multiplexed Intel and Motorola type interfaces are also supported. This enables the AIC-8375 to interface directly to a variety of microprocessors including, but not limited to, those listed below.

| Table 1-1 | Compatible | <b>Microprocessors</b> |  |

|-----------|------------|------------------------|--|

|-----------|------------|------------------------|--|

| Microprocessor       | Mode                        |

|----------------------|-----------------------------|

| Intel 8051/31        | multiplexed                 |

| Intel 80C196KD20     | multiplexed                 |

| Intel 80C188         | multiplexed                 |

| Motorola 68HC11F1    | multiplexed/non-multiplexed |

| Motorola 68HC16      | multiplexed/non-multiplexed |

| Hitachi H8/532       | non-multiplexed             |

| National HPC         | multiplexed/non-multiplexed |

| Siemens 88C165, 6, 7 | multiplexed/non-multiplexed |

| TI TMS320C25 (DSP)   | non-multiplexed             |

| Adaptec AIC-4420     | non-multiplexed             |

There are other families of microprocessors which can be easily interfaced to the AIC-8375 using minimal external logic. Information provided in the Timing Specifications section of the AIC-8375 Data Sheet can be used to design any required external glue logic which may be required to interface to other types of microprocessors.

To accommodate a variety of microprocessors and embedded applications, the Local Microprocessor Interface Block provides the following features:

- Optional address latch for multiplexed busses.

- Programmable byte order for accesses of multi-byte registers.

- Ready signal for interfacing to various high end microprocessors.

- A Host/Buffer/ Disk Interrupt signal for use by the microprocessor with all interrupts maskable.

- Direct read/write access to any 2 Kbyte window in the buffer.

#### **1.2.2 The Host Interface Block**

The Host Interface Block provides the necessary functions for interfacing the AIC-8375 to the ATA (IDE) interface or the PCMCIA interface. Emulation of the IBM PC ISA/EISA Task File is accomplished via a set of registers and logic which is accessible by the local microprocessor. The Task File contains eleven I/O registers that enable the host PC to set drive configurations, execute commands, and check their status.

Both the ATA and PCMCIA interfaces provide a means for the host to access the Task File registers. The PCMCIA communication modes available are:

- Attribute Memory: This is read by the host to determine information about the PCMCIA card and to change the card's configuration. It is not available in ATA mode. The Attribute Memory can be read by the host at any time the AIC-8375 is not in the busy state. The AIC-8375 Attribute Memory consists of two parts:

- Card Information Structure: This data structure contains readable tuple configuration data. This is a user-defined interface that supports up to 256 bytes of information. The CIS is implemented as the first 256 bytes of buffer memory and is not writable by the host.

- Configuration Registers: These registers return information about the current configuration. The host can write to these registers to change the current configuration (e.g., change from Memory to a Block I/O addressing mode).

- Primary/Secondary I/O Addressing Mode: This mode is compatiable with existing IDE drives and ATA BIOSes. The primary addresses are 1F0h 1F7h and 3F6h 3F7h. The secondary addresses are 170h 177h and 376h 377h.

- Block I/O Mode: This mode allows the host to locate the Task File Registers on a 16-byte boundary in the host's I/O memory space. This allows multiple cards to co-exist without I/O conflicts.

- Memory Mode: The Task File Registers are mapped into memory along with a 1KByte block of memory for data transfers. The PCMCIA specification refers to this memory as Common Memory.

The Host Interface Block can be programmed to execute various host read/write commands either completely automatically without any microprocessor intervention, semi-automatically with minimal microprocessor intervention, or manually with the aid of the microprocessor.

Of particular interest to most designers, are the significant advances in AT automation which have been incorporated into the AIC-8375. The highlights of AT automation are:

- Automatic data transfer management for multi-sector Read/Write commands without microprocessor intervention.

- Automatic data transfer management for Read/Write Multiple commands without microprocessor intervention.

- Automatic execution of read commands. (Auto-Read command execution) for cached data in the buffer by matching the first sector.

- "Auto-Write" command execution (First sector of a multiple sector write operation is automated or the transfer of one sector of the selected single sector write operation is automated.)

- Automatic Task File register updates during automatic multi-sector transfers.

- Programmable methods of IRQ assertion to allow automation to work with different BIOS implementations and different device drivers.

- Capability to execute multiple consecutive "Auto-Write" commands without loss of data in the buffer.

- 32-byte host FIFO to allow automation to occur smoothly during discontinuities in transfers on the AT interface.

- Ability to pause the AT automatic transfers between the host and buffer on sector and block boundaries.

- Automation of an extensive portion of the ATA command set.

- Auto-Read Command Interlock to facilitate cache support.

The AIC-8375 supports both PIO and DMA type transfers. The supported DMA type transfers includes ISA and EISA Type A/B DMA modes. DMA transfers and PIO transfers utilize the bus in 8- or 16-bit mode depending upon the command being executed. The bus is automatically switched between 16- and 8-bit mode while performing Read Long and Write Long commands at the time of ECC byte transfers.

Additional functionality is provided in the Host Interface Block by the following features:

- Programmable transfer length for automatic ECC byte transfer on the AT bus.

- Automatically inserted wait states are provided to support the IOCHRDY signal pin functions at any AT interface speed.

- Support for Master/Slave configuration of two embedded disk controller drives.

- Automatic detection of Host status reads.

- Support of both LBA and CHS Task File register formats.

- Automatic detection of both the software AT reset and hardware AT reset.

- 12-mA drivers are provided for direct connection to the ISA/EISA bus. Some AT inputs are Schmitt trigger inputs.

- Support for PIO modes 0 through 4.

When the AIC-8375 is configured for PCMCIA mode the chip is restricted to using a byte wide buffer. The upper byte of the buffer bus is reconfigured as the additional host address signals required by the PCMCIA interface. Additionally the upper two bits of the NRZ are reconfigured as HOE and HWE.

#### **1.2.3 The Buffer Control Block**

The Buffer Control block manages the flow of data into and out of the buffer. Significant automation is incorporated which allows buffer activity to take place automatically during read/write operations between the host and the disk. This automation works together with automation within the Host Control and Disk Control blocks to provide more bandwidth for the local microprocessor to perform non-data flow functions.

The buffer control circuitry keeps track of buffer full and empty conditions and automatically works with the Disk Control block to stop transfers to or from the disk when necessary. In addition, transfers to or from the host are automatically stopped or started based on buffer full or empty status.

A prioritized seven port architecture is implemented. All ports, except the refresh port, utilize 22bit buffer address pointers.

The data path to the buffer RAM can be configured as an 8- or 16-bit path in ATA mode and 8-bit only in PCMCIA mode. A parity bit is available for each of the low and high order eight bits.

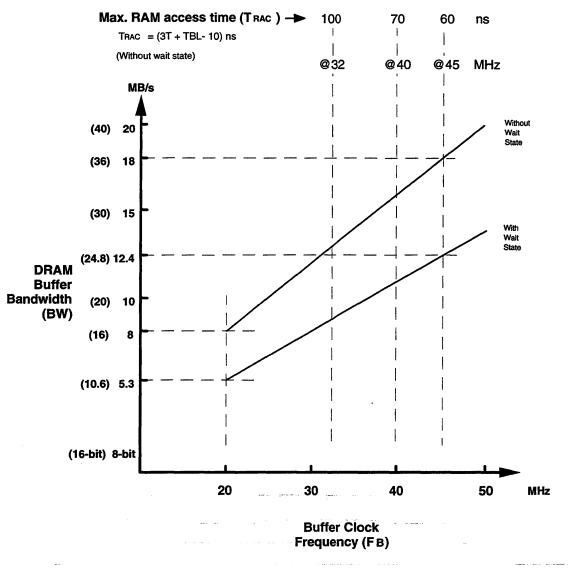

DRAM configurations from 64 KBytes to 4 MBytes are supported. Eight-byte Page Mode access along with CAS before RAS type refresh is implemented. In 8-bit mode, the sustained DRAM buffer bandwidth, during concurrent host and disk transfers, is 18 MBytes/sec utilizing a 45 MHz BUFCLK. In 16-bit mode, the sustained DRAM buffer bandwidth, during concurrent host and disk transfers is 36 MBytes/sec while using a 45 MHz BUFCLK.

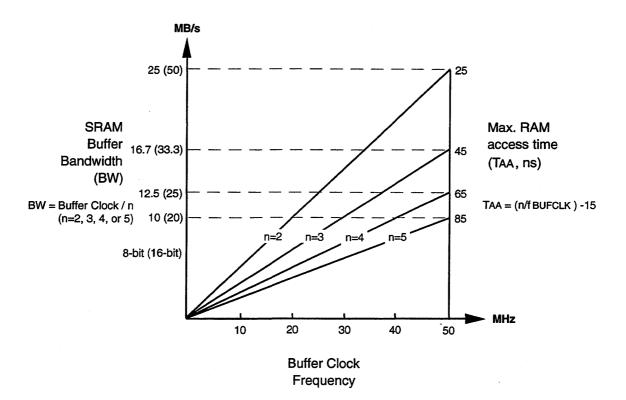

SRAM configurations of up to 256 KBytes are supported. Two independent RAM chip selects allow the option for two separate SRAMs (up to 128K Bytes each) to be addressed and accessed. In 8-bit mode, the sustained SRAM bandwidth, during concurrent host and disk transfers, is 25 MBytes/sec utilizing a 50 MHz BUFCLK. In 16-bit mode, the sustained SRAM bandwidth, during concurrent host and disk transfers, is 50 MBytes/sec utilizing a 50 MHz BUFCLK. Flexible control options allow various speed SRAMs to be matched with available BUFCLK frequencies to support the desired throughput.

The Buffer Control block incorporates very flexible segmentation support. Two operational segments can be set up to support general read/write, auto write, and read caching (auto read) algorithms. The segment size is programmable to any value up to 4 MBytes with 1-byte resolution (2byte resolution in 16-bit mode). In addition, there is special segment support for storing disk servo split pointers. The various pointers are designed to automatically wrap at segment boundaries to ensure data integrity without microprocessor intervention. Additional functionality is provided in the Buffer Control block through the following features:

- Increased automation to support zero latency read operations with minimal latency and true buffer alignment.

- Support for sector sizes up to 1500 bytes in length.

- Capability to support the execution of multiple consecutive Auto-Write commands without loss of data due to overwriting of data.

- 8/16-bit buffer data bus with optional parity feature for DRAM.

- Support for delayed block release.

- Write cache pointer.

- A disk sector counter that can monitor the transfers between the disk and buffer.

- Servo Pointer wrap capability.

- Two independent BCTR registers for use with any two selectable buffer segments.

#### **1.2.4 The Disk Control Block**

The AIC-8375 Disk Control block manages the flow of data between the disk and the buffer. It is capable of performing completely automated track read and write operations at a maximum data rate of 50 Mbits/sec in single NRZ mode, 100 Mbits/sec in dual NRZ mode, or 120 Mbits/sec in byte-wide NRZ mode. The AIC-8375 Disk Control block has been redesigned to allow for EDSA headerless support. This design is the first headerless only design in that ID fields or headers are no longer supported. Many flexible features and elements of automation have been incorporated to complement the automation contributed by the host and buffer blocks.

The Disk Control block consists of the programmable sequencer, EDAC circuitry, CDR/data split logic, disk FIFO, and other support logic.

The programmable sequencer contains a 31 by 3 byte programmable SRAM and associated control logic, which is programmed by the user, to automatically control all single track format, read, and write operations. From within the sequencer micro program, the Disk Control block can automatically deal with such real time functions as defect skipping, servo burst data splitting, branching on critical buffer status, address verification, and data compare operations. Each sequencer instruction is capable of an execution count of 8 KBytes. Once the sequencer is started, it executes each word in logical order. At the completion of the current instruction word, it either continues to the next instruction, continues to execute some other instruction based upon an internal or external condition having been met, or stops. During instruction execution or while stopped, registers can be accessed by the local microprocessor to obtain status information reflecting the sequencer operations taking place. In addition to the flexible sequencer, the Disk Control block contains many other features which are available to satisfy diverse requirements. These include:

- Support for optimized zero latency read operations, with minimal microprocessor intervention.

- Programmable "Wrap To" register.

- Ability to specify at which sector to wrap "wrap to" register, independent of the stopping sector.

- Index counter for power management command support.

- Missing RRCLK detector.

- Time-out support when waiting for Sync, Index, Sector, and End of Servo Burst to relieve microprocessor of overhead associated with managing time outs.

- Optional 2-byte fault tolerant Byte Sync.

- Configurable logic to deal with CDR and embedded servos to allow adaptation to diverse disk formats.

- Ability to automatically stop the sequencer on receipt of an Auto-Write command.

- Split data support from microprocessor or buffer. Buffer split data support utilizes indexing into the buffer servo segment.

- A 32-byte FIFO between the buffer and the Disk Control block smoothes out data flow attributed to discontinuities in data or differences in speed.

- Read Gate and Write Gate are directly controlled from the disk sequencer micro program.

Features that have been added to support EDSA headerless formats include:

- End of Servo (EOS) counter.

- EOS MAX register which allows the EOS counter to wrap at a specified value.

- Ability to clear the EOS counter by Index.

- EOS compare instruction (EOSCMP) in the disk sequencer.

- Current Sector counter (Disk Sequencer Physical Position Counter).

- Ability to reset current CDR instruction

Error detection and correction is handled in the Disk Control block. The AIC-8375 provides a fixed, 3-way interleaved, 168-bit Reed-Solomon code. Automatic on-the-fly hardware correction will take place for up to three symbols in error per interleave. Correction is guaranteed to complete before the ECC Field of the sector following the sector where the error occurred. Optional burst limiting can be used to decrease the probability on misdetection and miscorrection. The ECC can be seeded with a four byte value that consists of the requested sector value plus three bytes specified by the user. An added feature of the AIC-8375 ECC block is the ability to log corrected ECC errors.

#### **1.2.5 Power Management**

Power management features are incorporated into each block of the AIC-8375. This allows the designer to tailor the amount of power management to the specific design as required. Other power management features include:

- Independent power management control for each block.

- ECC logic automatically powered down when not in use and powered up when needed.

- Disk sequencer and associated disk logic powered up when the sequencer is started.

- Weak pull-up structure on input pins to prevent undesirable power consumption due to floating CMOS inputs.

## 2.1 Interfacing to the Local Microprocessor

#### 2.1.1 Selecting the Microprocessor Bus Mode

The AIC-8375 is programmable to be compatible with several different microprocessor interfaces. The AIC-8375 is autoconfigured at power-on time to the specific microprocessor to which it is interfaced. Immediately after \*POR is negated, the AIC-8375 samples the voltage on the BD14/PSEL0 and BD15/ PSEL1 pins. At this time these two pins function as the PSEL[1:0] signals. If the AIC-8375 is configured for PCMCIA Mode (see Section 2.3.1), PSEL[1:0] maps to BA[6:5]. The value of PSEL[1:0] for each of the microprocessor classes are shown in the table below.

| •••                  | Mi              | croproce | ssor Sig | nal Usage | Configuration Control Signal Pins |                                                                                                                |           |        |  |

|----------------------|-----------------|----------|----------|-----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-----------|--------|--|

| Microprocessor Type  | DSTB            | DIR      | CS       | CSLAT     | INT                               | RSEL                                                                                                           | PSEL[1:0] | PMUX   |  |

| Intel 80C196KB20     | *RD/*WR         |          |          | 1         | 0                                 | · 1 = READY                                                                                                    | 11        | 1      |  |

| Siemens 88C165, 6, 7 | *RD/*WR         |          |          | 1         | 0                                 | 0 = *READY                                                                                                     |           | 1 or 0 |  |

| Motorola 68HC11      | E               | R/*W     | *CS      | 1         | 0,↓                               | And a second | 10        | 1 or 0 |  |

| Motorola 68HC11F1    | *CS             | R/*W     |          | 0         | 0,↓                               |                                                                                                                | 01        | 1 or 0 |  |

| Motorola 68HC16      | *DS             | R/*W     | *CS      | 0         | 0                                 | 0 = *DSACK0                                                                                                    | 0 1       | 0      |  |

| TI TMS320C25 (DSP)   | *DS             | R/*W     |          | 1         | 0                                 | 1 = READY                                                                                                      | 0.0       | 0      |  |

| Adaptec AIC-4420     | *************** | '        |          | 1         | 0                                 | · · · ·                                                                                                        | 11        | 0      |  |

#### Table 2-1 Microprocessor Class PSEL[1:0] Values

- DSTB = Type of data strobe: \*RD/\*WR for active low read and write strobes, E for active high read/write strobe, \*CS for active low read/write strobe gated with Chip Select and driving the CS or BS input (68HC11F1), and \*DS for active low read/write strobe.

- DIR = Direction Control: --- for none due to separate \*RD and \*WR strobes, and R/\*W for direction.

- CS = Type of Chip Select: \*CS for active low, CS for active high, and --- for none supplied by processor.

- CSLAT = Chip Select Latch Control: When a "1" the chip selects are latched, otherwise they are not latched. The 68HC11F1 when run in ECLK Chip select mode, cannot latch CS. The 68HC16 cannot latch CS because there is not guaranteed positive setup time to DSTB.

- INT = Type of Interrupt: 0 for low level, 1 for high level, ↑ for rising edge detect, ↓ for falling edge detect, --- for none supplied by the processor.

- RSEL = Type of Wait State Control: 1 for active high READY, 0 for active low \*READY (\*DSACK for 68HC16), --- for none supported by the processor so RSEL is don't care.

- PSEL = Processor Select Control, PSEL[1:0] inputs driven to this value to select the processor shown.

- **PMUX** = Type of Processor Bus: 0 for non-multiplexed, 1 for multiplexed (0 or 1 if can support both).

These pins are internally pulled high so that external resistors tied to Vdd are not required. However, to operate in Motorola or TI modes, a high value resistor must be connected between the PSEL0 and/or PSEL1 pins and Vss. The value chosen must be high enough so as not to interfere with the operation of the buffer parity function during buffer transfers.

The functionality of the E/\*RD/\*DS pin and the R/\*WR pin is dependent upon which mode is selected. In mode 3 (PSEL[1:0] = '11'), the E/\*RD/\*DS and R/\*WR input pins function as \*RD and \*WR respectively. In mode 2 (PSEL[1:0] = '10'), they function as E and R/\*W inputs respectively. In modes 1 and 0, they function as \*DS and R/\*W inputs respectively with latched CS for mode 0 and no latched CS for mode 1.

#### 2.1.2 Selecting Multiplexed or Non-Multiplexed Address Mode

Immediately after \*POR is negated, the AIC-8375 samples the voltage on the BD13/PMUX pin (BA4/ PMUX in PCMCIA mode). If it is found to be low, the device is configured for non-multiplexed operation. If high, the device is configured for multiplexed bus operation. This pin is pulled high by an internal high resistance. Therefore, if it is desired to operate the AIC-8375 in the multiplexed bus mode, an external resistor tied to Vdd is not required. However, to operate in non-multiplexed mode, a high resistance resistor must be connected between the PMUX pin and Vss. The value chosen must be high enough so as not to interfere with the operation of the PMUX pin during buffer transfers.

#### 2.1.3 Enabling the Internal Address Latch

The AIC-8375 has an internal 8-bit latch that latches the low-order byte of the address during a multiplexed mode microprocessor memory access cycle. This latched value is then presented on the eight MA[7:0] outputs and can be used by the rest of the system. This eliminates the need for an external "373" latch for address/data multiplexing. In non-multiplexed mode, the MA[7:0] pins become microprocessor address inputs.

The internal address latch is enabled when the multiplexed address mode is selected. On the falling edge of ALE, the value on the AD[7:0] pins is latched in the internal transparent latch and held on the MA[7:0] outputs.

#### 2.1.4 Chip Select Generation and Memory Mapping

The AIC-8375 utilizes two separate chip selects to access the various areas associated with the device. These chip selects are CS (pin 100) and BS (pin 101). The designer is required to provide address decoding for these two chip selects. The registers and Sequencer RAM within the AIC-8375 are accessed by the microprocessor using the CS input along with the appropriate address. The Buffer RAM is accessed by using the BS input. Refer to Section 3 for more functional details on how the microprocessor accesses the device registers, the Sequencer RAM, and the Buffer RAM.

The polarity of the CS and BS signals is determined when \*POR is negated at power-up. At this time, the BD12/CSP pin (BA3/CSP in PCMCIA mode) is sampled. If it is found to be low, the polarity of the CS pin will be active low. If high, CS will be active high. Likewise, the BD11/BSP pin (BA2/BSP in PCMCIA mode) is sampled when \*POR is negated at power-up. If this pin is found to be low, BS will be active low, and if high, BS will be active high. These pins incorporate an internal pullup resistor to bias them high. An external pulldown resistor is required if a low sample level is desired.

Refer to Section 4 of this document for more detailed information on the sequencer RAM address mapping. Section 5 of the AIC-8375 Data Sheet contains further details on the AIC-8375 register mapping while using CS.

## 2.1.5 Using the Ready Signal

The Ready function provides the AIC-8375 with the capability of requesting the microprocessor to insert wait states during the current microprocessor read or write access. The AIC-8375 will drive the Ready pin low to notify the microprocessor that it is "not ready" for it to end the current access. When the microprocessor detects that the AIC-8375 is not ready, it will extend the current read or write access until the AIC-8375 drives the Ready pin high, indicating that it is now ready.

The Ready function is obviously useful when interfacing to very fast microprocessors. However, even if a slower microprocessor is used, there are times when the Ready line is required. This is true when the buffer RAM or sequencer RAM are being accessed. Because access to the buffer is shared between the host, disk, ECC correction logic, and refresh, the Ready line is necessary to hold off the microprocessor when a microprocessor access is attempted while the buffer is being accessed by another source. The Sequencer RAM has internal restrictions as to when it can be accessed during instruction cycles. As a result, the Ready line is asserted to handle these situations.

The READY function polarity is chosen based on the value found on the BD10/RSEL pin (BA1/RSEL in PCMCIA mode) after power-on-reset is negated as shown in Table 2-1.

The Enable Push-Pull READY bit (reg. 51h, R/W, bit 3) is used to configure the READY line for either push-pull or open drain configurations. This is useful for connecting to dedicated or shared interrupt lines.

The Ready line timing that is implemented when accessing the buffer RAM or sequencer RAM (using the BS chip select) is slightly different from that used for the CS chip select. Refer to the appropriate timing diagrams in the *Timing Specifications* section of the AIC-8375 Data Sheet for details on these differences.

#### **2.1.6 Interrupt Sources to the Microprocessor**

Two interrupt signal pins are available for sending interrupts to the microprocessor; INTD is the source for disk block related interrupts and INTHB is the source for host block or buffer block related interrupts (the logical 'OR' of all interrupts from these two blocks). All of the device interrupts from the host, disk, and buffer blocks can be output on the INTHB signal pin if the COMBINT bit (reg. 51h, R/W, bit 2) is set.

The polarity of both the INTD and INTHB signal pins is determined by the ACTHIINT bit (reg. 51h, R/W, bit 0).

At power up, these pins default to an active low/open drain state. In open drain mode, an external 1-10K Ohm pullup resistor is required on this pin. These pins can be configured as push-pull if the ENPPINT bit (reg. 51h, R/W, bit 1) is set.

## 2.2 Buffer RAM Device Selection

The choice of which buffer RAM device to use in a particular design will depend on several factors. These factors include speed, real estate, cost, available system clocks, the need for buffer parity support, and required buffer bandwidth. The following two sections provide technical information on how to interface static RAMs and dynamic RAMs to the AIC-8375. This information will provide a base from which the user can establish buffer memory requirements for a particular application.

#### 2.2.1 Static RAM

A maximum of 256 KBytes of SRAM may be addressed using the available eighteen buffer address lines (BA[17:0]). The implementation of this address space will be determined by the users choice of the following variables:

- One, two, or multi-RAM device implementation

- 8-bit- or 16-bit-wide buffer data path

- SRAM cycle time (2T, 3T, 4T, or 5T)

- Type of SRAM (with or without an \*OE pin)

The RAMSEL[2:0] bits (reg. 100h, R/W, bits 5:3) together with the BEN16BIT bit (reg. 100h, R/W, bit 2) establish the physical SRAM configuration. The BEN16BIT control bit establishes an 8- or 16-bit buffer data path. The types of configurations available are summarized in Tables 2-2 and 2-3.

| Table 2-2 | 8-bit SRAM Buffer | Configuration        |

|-----------|-------------------|----------------------|

|           |                   | COMPANY OF THE OWNER |

| RAMSEL[2:0] | SRAM Types                           | SRAM Control                                | BEN16BIT   | BA0/*WE1    | *WE0/*CAS0   |

|-------------|--------------------------------------|---------------------------------------------|------------|-------------|--------------|

| 000         | Single X 8 SRAM<br>(with *OE pin)    | *MOE controls<br>SRAM *OE pin               | 0 (8-bit)  | used as BA0 | used as *WE0 |

| 001         | Single X 8 SRAM<br>(without *OE pin) | *MCE controls<br>SRAM *CE pin               | 0 (8-bit)  | used as BA0 | used as *WE0 |

| 010         | (Reserved)                           | (Reserved)                                  | (Reserved) |             |              |

| 011         | (Reserved)                           | (Reserved)                                  | (Reserved) |             |              |

| 100         | Dual 32Kx8 SRAMs                     | *MCE1 and *MCE2<br>control<br>SRAM *CE pins | 0 (8-bit)  | used as BA0 | used as *WE0 |

| 101         | Dual 64Kx8 SRAMs                     | *MCE1 and *MCE2<br>control<br>SRAM *CE pins | 0 (8-bit)  | used as BA0 | used as *WE0 |

| 110         | Dual 128Kx8<br>SRAMs                 | *MCE1 and *MCE2<br>control<br>SRAM *CE pins | 0 (8-bit)  | used as BA0 | used as *WE0 |

| 111         |                                      | (DF                                         | RAM)       |             |              |

Confidential

| RAMSEL[2:0] | SRAM Types                                                                   | SRAM Control                                | BEN16BIT   | BA0/*WE1     | *WE0/*CAS0   |

|-------------|------------------------------------------------------------------------------|---------------------------------------------|------------|--------------|--------------|

| 000         | Single X 16 SRAM<br>(with *OE pin)<br>Two X 8 SRAMs<br>(with *OE pins)       | *MOE controls<br>SRAM *OE pin               | 1 (16-bit) | used as *WE1 | used as *WE0 |

| 001         | Single X 16 SRAM<br>(without *OE pin)<br>Two X 8 SRAMs<br>(without *OE pins) | *MCE controls<br>SRAM *CE pin               | 1 (16-bit) | used as *WE1 | used as *WE0 |

| 010         | (Reserved)                                                                   | (Reserved)                                  | (Reserved) |              |              |

| 011         | (Reserved)                                                                   | (Reserved)                                  | (Reserved) |              |              |

| 100         | Dual 32Kx16 SRAMs                                                            | *MCE1 and *MCE2<br>control<br>SRAM *CE pins | 1 (16-bit) | used as *WE1 | used as *WE0 |

| 101         | Dual 64Kx16 SRAMs                                                            | *MCE1 and *MCE2<br>control<br>SRAM *CE pins | 1 (16-bit) | used as *WE1 | used as *WE0 |

| 110         | Dual 128Kx16 SRAMs                                                           | *MCE1 and *MCE2<br>control<br>SRAM *CE pins | 1 (16-bit) | used as *WE1 | used as *WE0 |

| 111         |                                                                              | (DF                                         | RAM)       |              |              |

| Table 2-3 | 16-bit SRAM Buffer | <b>Configurations</b> |

|-----------|--------------------|-----------------------|

|-----------|--------------------|-----------------------|

The AIC-8375 can be interfaced to SRAMs which have an \*OE (output enable) and \*CS (chip select) control input as well as SRAMs which do not have an \*OE control input. The \*MOE/\*RAS/\*MCE1 pin is typically connected to the \*OE pin of those SRAMS which have this control input. If the SRAM does not have an \*OE control input, the \*MOE/\*RAS/\*MCE1 pin is connected to the \*CS or \*CE pins of the SRAM.

Note that the functions of the \*MOE/\*RAS/\*MCE1 signal pin and the \*WE0/\*CAS0 signal pin are different in SRAM and DRAM modes.