AIC-7770 EISA/ISA Bus Master Single-Chip SCSI Host Adapter

Data Book

# Preliminary

# AIC-7770 EISA/ISA Bus Master Single-Chip SCSI Host Adapter

Data Book

# PRELIMINARY

#

#### Copyright

Copyright 1992 Adaptec, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means; electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of Adaptec, Inc., 691 South Milpitas Blvd., Milpitas, CA 95035

#### **Trademarks**

AT is a registered trademark of International Business Machines Corporation.

386 is a trademark of Intel Corporation

Microsoft is a registered trademark of Microsoft Corporation.

All other product names are trademarks and registered trademarks of their respective owners.

#### Changes

The material in this manual is for information only and is subject to change without notice.

Adaptec reserves the right to make changes in the product design without reservation and without notification to its users.

#### Literature

ii

Additional information may be obtained from:

Adaptec, Inc. Literature Department - MS/40 691 South Milpitas Blvd. Milpitas, CA 95035 1-800-634-2766

# **Table of Contents**

# 1

### Introduction

| Dverview                 | -1 |

|--------------------------|----|

| Feature Summary 1-       | -1 |

| ISA Interface            | -1 |

| EISA Interface 1-        | -2 |

| Host Adapter Features 1- | -2 |

| SCSI Features            | -2 |

| Block Diagram            | -3 |

# 2

### **Pin Description**

| Pin Summary              |

|--------------------------|

| Host Interface           |

| SCSI Interface           |

| Other Pins               |

| Pin Description          |

| ISA/AT Signal Definition |

| ISA Interface            |

| EISA Interface           |

| SCSI Interface           |

| Other Pins               |

# 3

### **Register Description**

| ISA I/O Map 3-                               | -1 |

|----------------------------------------------|----|

| EISA and Chip I/O Map 3-                     |    |

| Register Summary                             |    |

| SCSI Registers                               |    |

| Scratch                                      |    |

| Sequencer Registers                          |    |

| Host Registers                               |    |

| SCB Array                                    |    |

| Bit Definition Summary                       |    |

| SCSI Registers                               |    |

| Scratch RAM Area                             |    |

| Sequencer Registers                          |    |

| Host Registers                               |    |

| SCB Array                                    |    |

| Register Definition                          |    |

|                                              |    |

| SCSI Sequence Control (SCSISEQ)              |    |

| SCSI Transfer Control 0 (SXFRCTL0)           | 13 |

| SCSI Transfer Control 1 (SXFRCTL1)           | 4  |

| SCSI Control Signal Read Register (SCSISIGI) |    |

|                                              |    |

|                                               | 0.10   |

|-----------------------------------------------|--------|

| SCSI Control Signal Write Register (SCSISIGO) | 3-16   |

| SCSI Rate Control (SCSIRATE)                  |        |

| SCSI ID (SCSIID).                             |        |

| SCSI Latched Data (SCSIDATL,[H])              |        |

| SCSI Transfer Count (STCNT[n])                | 3-19   |

| Clear SCSI Interrupt Register 0 (CLRSINT0)    | 3 - 20 |

| SCSI Status Register 0 (SSTAT0)               | 3-21   |

| Clear SCSI Interrupt 1 (CLRSINT1)             |        |

| SCSI Status 1 (SSTAT1)                        |        |

| SCSI Status 2 (SSTAT2)                        |        |

| SCSI Status 3 (SSTAT3)                        |        |

| SCSI Test Control (SCSITEST).                 |        |

| SCSI Interrupt Mode 0 (SIMODE0)               |        |

| SCSI Interrupt Mode 1 (SIMODE1)               | 3-28   |

| SCSI Data Bus (SCSIBUSL, [H])                 | 3-29   |

| SCSI/Host Address (SHADDR[0:3])               | 3-30   |

| Selection Timeout Timer (SELTIMER)            |        |

| Selection/Reselection ID (SELID)              |        |

| SCSI Block Control (SBLKCTL)                  |        |

| Sequencer Control (SEQCTL)                    |        |

| Sequencer RAM Data (SEQRAM).                  |        |

| Sequencer Address (SEQADDR(1:0))              |        |

| Accumulator (ACCUM)                           | 3-35   |

| Source Index (SINDEX).                        |        |

| Destination Index (DINDEX)                    |        |

| Break Address Low (BRKADDR0)                  |        |

| Break Address High (BRKADDR1).                |        |

| All Ones (ALLONES).                           |        |

| All Zeros (ALLZEROS).                         |        |

| No Destination (NONE).                        |        |

| Flags (FLAGS)                                 |        |

| Source Index Indirect (SINDIR)                |        |

| Destination Index Indirect (DINDIR)           |        |

|                                               |        |

| Function1 (FUNCTION1)                         |        |

| Stack (STACK).                                |        |

| Board ID 0 (BID0)                             |        |

| Board ID 1 (BID1)                             |        |

| Board ID 2 (BID2)                             |        |

| Board ID 3 (BID3)                             |        |

| Board Control (BCTL)                          |        |

| Bus On/Off Time (BUSTIME)                     |        |

| Bus Speed (BUSSPD).                           | 3-45   |

| Host Control (HCNTRL)                         | 3-47   |

| Host Address (HADDR[3:0])                     | 3-48   |

| Host Count (HCNT[n])                          | 3-49   |

| SCB Pointer (SCBPTR)                          | 3-49   |

| Interrupt Status (INTSTAT)                    | 3-50   |

| Clear Interrupt Status (CLRINT)               | 3-52   |

| Hard Error (ERROR)                            | 3-53   |

| Data FIFO Control Register (DFCNTRL)          | 3-54   |

| Data FIFO Status (DFSTATUS)                   |        |

| Data FIFO Write Address 0 (DFWADDR0)          |        |

| Data FIFO Read Address 0 (DFRADDR0) | 01 |

|-------------------------------------|----|

| Data FIFO Data Register (DFDAT)     | 58 |

| SCB Auto Increment (SCBCNT)         | 59 |

| Queue In FIFO (QINFIFO)             | 60 |

| Queue In Count (QINCNT)             | 60 |

| Queue Out FIFO (QOUTFIFO)           | 61 |

| Queue Out Count (QOUTCNT)           | 61 |

| Test Chip (TESTCHIP)                | 62 |

### **Functional Description**

| SCSI                                   |

|----------------------------------------|

| Wide/Dual Busses                       |

| Initializing the SCSI Section          |

| Manual Mode Data Transfer              |

| Automatic Mode Data Transfer           |

| Normal (DMA) Mode Data Transfer        |

| Differential                           |

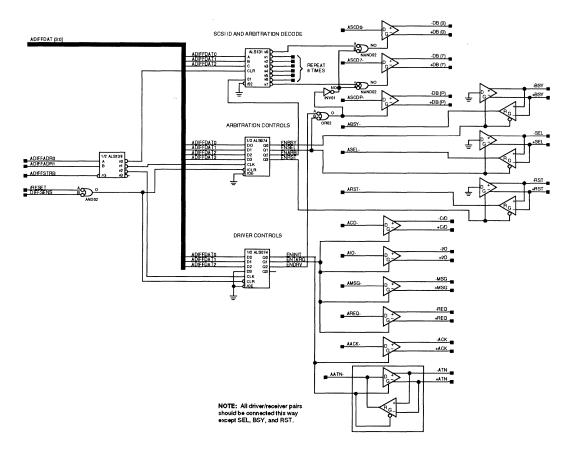

| Differential Schematics. 4-5           |

| SCSI Interrupts                        |

| Counters                               |

| SCSI FIFO                              |

| SCSI Reset                             |

| SHADDR Address Pointer 4-7             |

| Sequencer                              |

| Loading                                |

| Pause                                  |

| Breakpoint                             |

| Single Step                            |

| Reset                                  |

| Restart                                |

| Indirect Jump                          |

| Hardware Failure Detect 4-8            |

| Writing Hardware Control Bits 4-9      |

| Host in ISA Mode                       |

| Device Identification                  |

| Bus Time                               |

| Bus Speed 4-10                         |

| Data Transfer                          |

| MEM16 Control                          |

| Host in EISA Mode                      |

| Configuration                          |

| Data Transfer                          |

| Bus Master Modes 4-11                  |

| Reading and Writing the Data FIFO 4-12 |

| Writing to the SCB Array 4-13          |

| Executing a Command 4-14               |

| -14 |

|-----|

| 15  |

| 15  |

| 15  |

| 15  |

| 16  |

| 16  |

| 17  |

|     |

### **Application Notes**

| Chip Initialization                                                          | -1 |

|------------------------------------------------------------------------------|----|

| SCSI Phases 5-                                                               | -1 |

| Arbitration/Selection                                                        | -1 |

| ID Message                                                                   | -1 |

| Command 5-                                                                   | -2 |

| Data Phase                                                                   | -2 |

| Disconnection                                                                | -2 |

| Reconnection                                                                 | -2 |

| Modify Data Pointers 5                                                       |    |

| Status                                                                       |    |

| Command Complete Message 5-                                                  |    |

| SCB Definition                                                               |    |

| Scratch RAM Definition                                                       |    |

| Multi-threaded Operation 5-                                                  |    |

| Scatter/Gather                                                               |    |

| Tagged Queuing                                                               |    |

| Using the FIFO Threshold Control 5-                                          |    |

| Contingent Allegiance 5-                                                     |    |

| Abort                                                                        |    |

| Retry on Busy                                                                |    |

| Command Linking 5-                                                           |    |

| Target Mode                                                                  |    |

| Programming the Sequencer 5-                                                 |    |

| Instruction Set Definition                                                   |    |

| Command Line Format                                                          |    |

| Command Line Field Definitions                                               |    |

|                                                                              |    |

|                                                                              |    |

| Command Line Functions       5-2         Command Line Applications       5-2 |    |

# 6

### Design Notes

|  | I/O Decodes | 6-1 |

|--|-------------|-----|

|--|-------------|-----|

**Test Features**

| Overview                           |

|------------------------------------|

| Test Register Description          |

| SCSI Test Control (SCSITEST)       |

| Selection Timeout Timer (SELTIMER) |

| Test Chip (TESTCHIP)               |

| Test Group Description             |

| Input Pad Testing                  |

| Output Pad Testing                 |

| Process Check Oscillator           |

| Monitor Illegal Address            |

| Host Tests                         |

| Sequencer Tests                    |

| SCSI Tests                         |

| FIFO Test                          |

| RAM Tests                          |

# 8

### **Electrical Information**

| Absolute Maximum Ratings  |     |

|---------------------------|-----|

| Operating/Test Conditions | 8-1 |

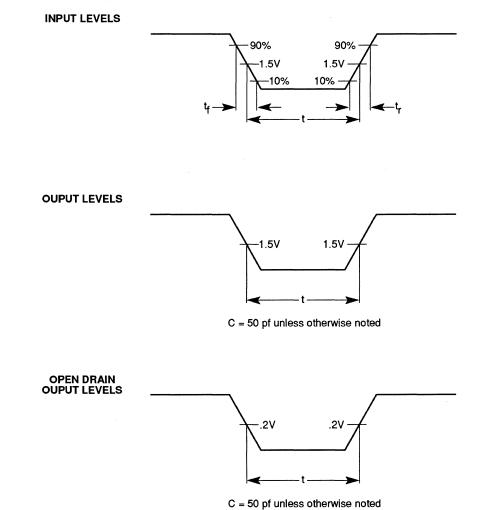

| Switching Waveforms       |     |

| DC Parameters             | 8-3 |

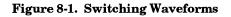

| Signal Test Loads         | 8-4 |

# 9

### System Timing

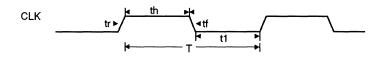

| Clock Timing                                            | -1 |

|---------------------------------------------------------|----|

| SCSI Bus Timing                                         |    |

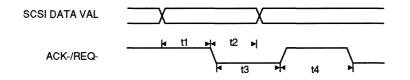

| SCSI Data Transfers                                     |    |

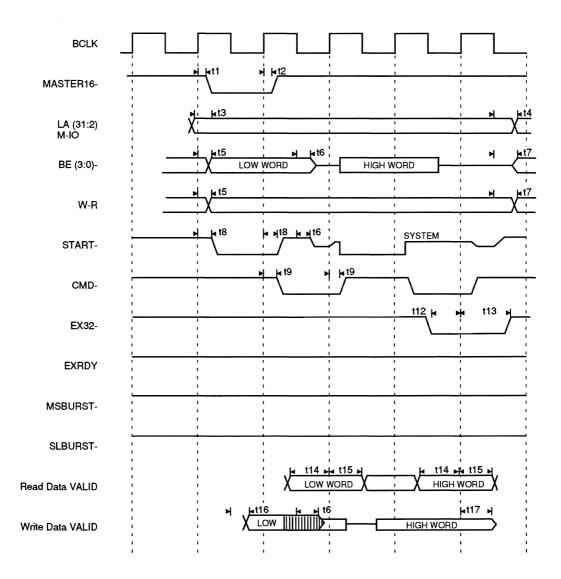

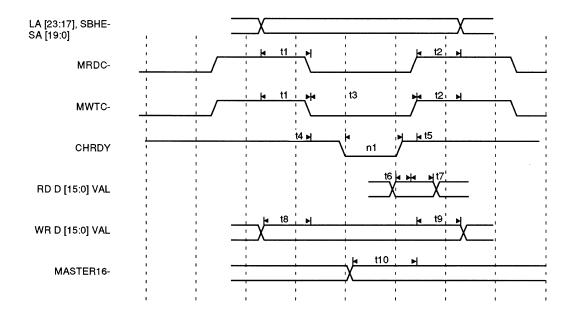

| EISA Master Bus Timing                                  |    |

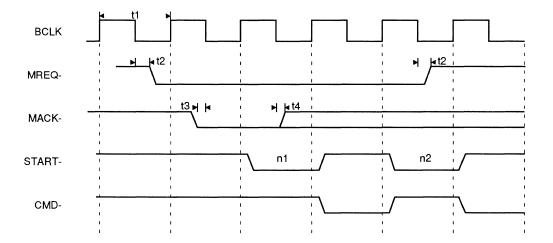

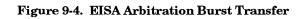

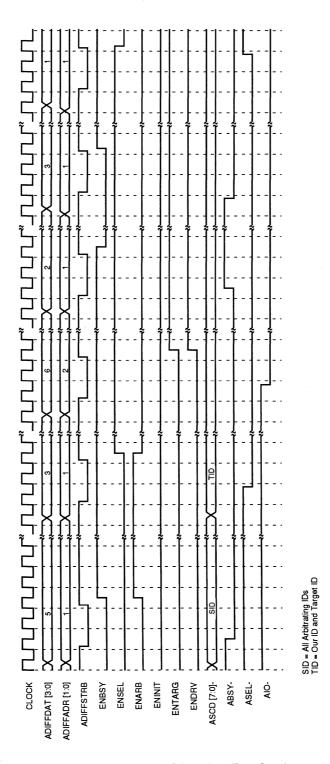

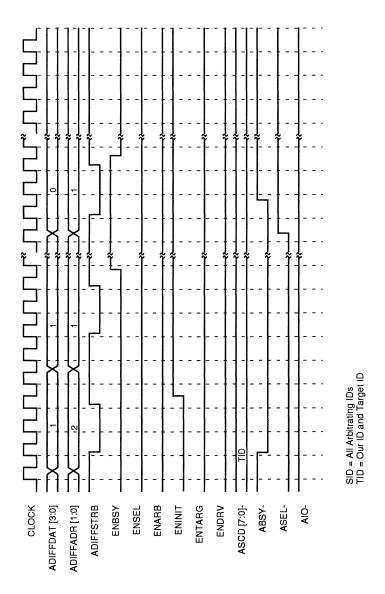

| EISA Arbitration                                        |    |

|                                                         |    |

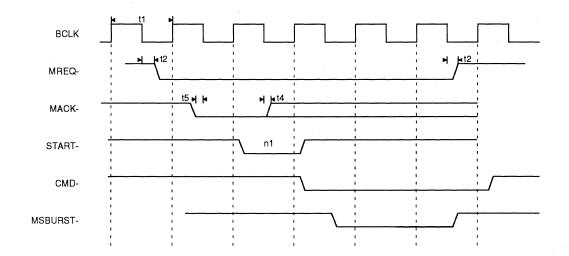

| EISA Arbitration Burst Transfer                         |    |

| EISA Arbitration Downshift Burst                        | .5 |

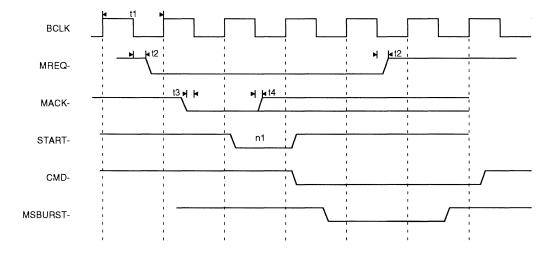

| EISA Two Cycle Transfer – 32-bit                        | -6 |

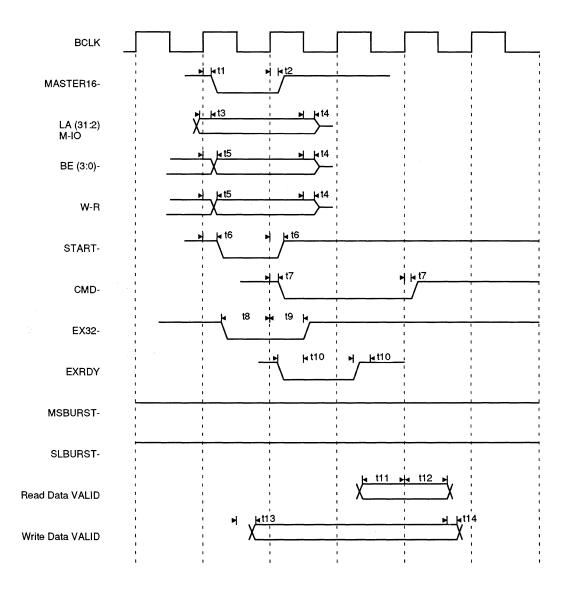

| EISA Burst Transfer – 32-bit Burst                      |    |

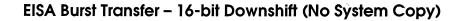

| EISA Burst Transfer – 16-bit Downshift (No System Copy) | 0. |

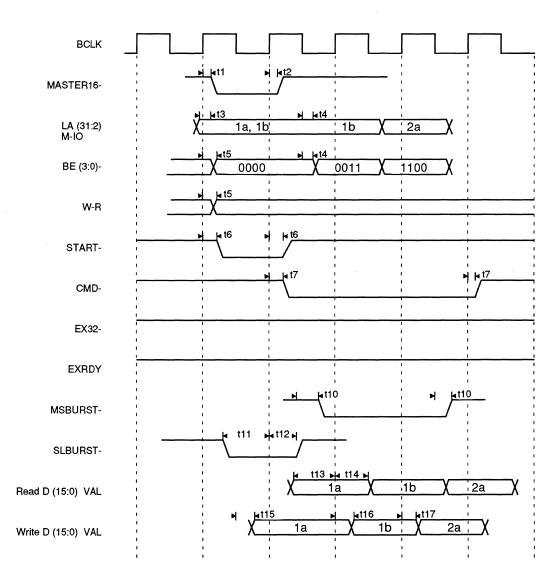

| EISA Burst Transfer – 16-bit Downshift (System Copy)    |    |

| EISA Two Cycle Transfer – 16-bit Translate              |    |

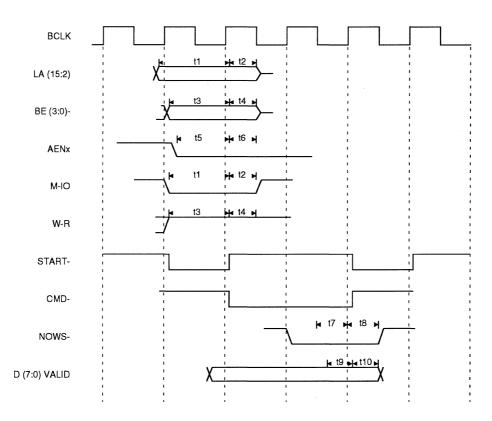

| EISA Slave Bus Timing                                   |    |

| EISA I/O Slave – 8-bit Write 9-1                        |    |

| EISA I/O Slave – 8-bit Read                             | .7 |

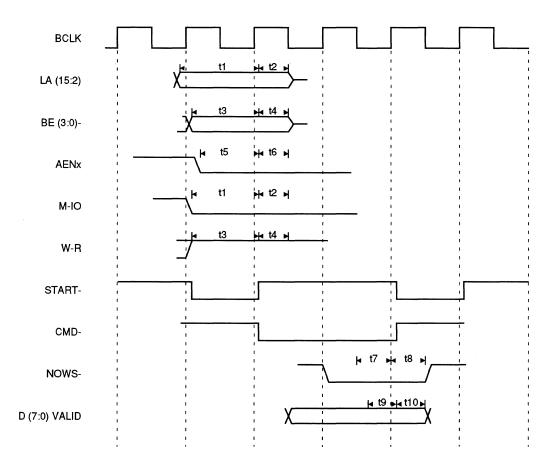

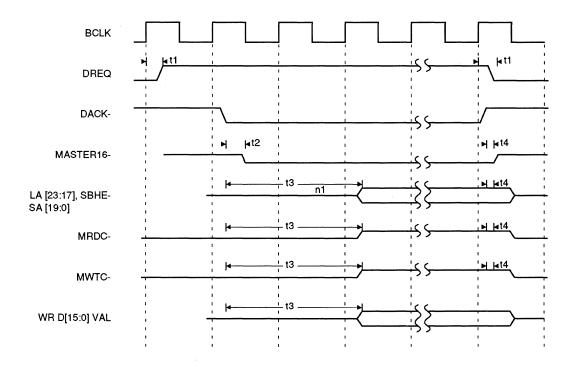

| ISA Master Bus Timing                                   | 8  |

| ISA Master Arbitration                                  |    |

| ISA Master – 16-bit Transfers                           | 9  |

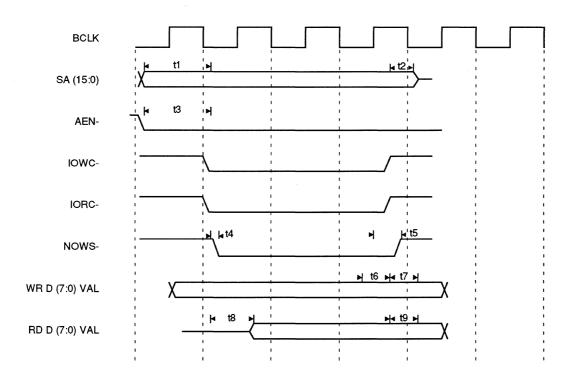

| ISA Slave Bus Timing                                    |    |

| ISA I/O Slave – 8-bit Write/Read                        |    |

| Differential Timing   |               | <br> | <br> |       | <br> | <br> |  | <br>    | <br>. 9 |

|-----------------------|---------------|------|------|-------|------|------|--|---------|---------|

| Initiator Arbitration | n Selection   | <br> | <br> | • • • | <br> | <br> |  | <br>    | <br>. 9 |

| Target Arbitration    | Reselection . | <br> | <br> |       | <br> | <br> |  | <br>    | <br>. 9 |

| Initiator Reselection | n             | <br> | <br> | • • • | <br> | <br> |  | <br>    | <br>. 9 |

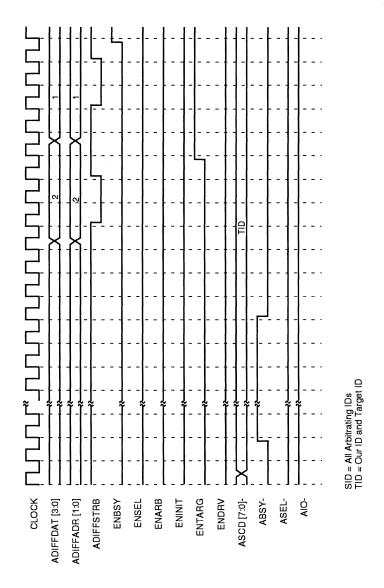

| Target Selection      |               | <br> | <br> | • • • | <br> | <br> |  | <br>••• | <br>. 9 |

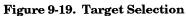

### EISA Package Outline

10

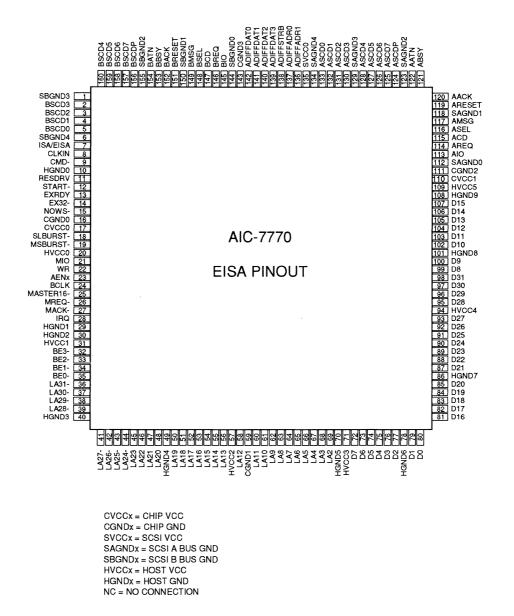

## ISA Package Outline

| <br>11-1 |

|----------|

| 1104 | $\sim$ |          |   | ~ ~ |

|------|--------|----------|---|-----|

| List |        | E III. J |   |     |

|      | •••    |          | • | ~~  |

|      |        |          |   |     |

| Figure 1-1. Block Diagram 1-3                                                    |

|----------------------------------------------------------------------------------|

| Figure 4-1. Differential Controls 4-5                                            |

| Figure 8-1. Switching Waveforms    8-2      Figure 8-2. Signal Test Loads    8-4 |

| Figure 9-1. Clock Parameters                                                     |

|                                                                                  |

| Figure 9-2. SCSI Data Transfers                                                  |

| Figure 9-3. EISA Arbitration9-3Figure 9-4. EISA Arbitration Burst Transfer9-4    |

| Figure 9-5. EISA Arbitration Downshift Burst                                     |

| Figure 9-6. EISA Two Cycle Transfer – 32-bit                                     |

| Figure 9-7. EISA Burst Transfer – 32-bit Burst                                   |

| Figure 9-9. EISA Burst Transfer – 16-bit Downshift                               |

| Figure 9-9. EISA Burst Transfer – 16-bit Downshift                               |

| Figure 9-10. EISA Two Cycle Transfer–16-bit Translate                            |

| Figure 9-11. EISA I/O Slave – 8-bit Write                                        |

| Figure 9-12. EISA I/O Slave – 8-bit Read                                         |

| Figure 9-13. ISA Master Arbitration                                              |

| Figure 9-14. ISA Master – 16-bit Transfers                                       |

| Figure 9-15. ISA I/O Slave – 8-bit Write/Read 9-20                               |

| Figure 9-16. Initiator Arbitration Selection                                     |

| Figure 9-17. Target Arbitration Reselection                                      |

| Figure 9-18. Initiator Reselection                                               |

| Figure 9-19. Target Selection                                                    |

| Figure 10-1. EISA Package Outline                                                |

| Figure 11-1. ISA Package Outline 11-1                                            |

# 1 Introduction

### Overview

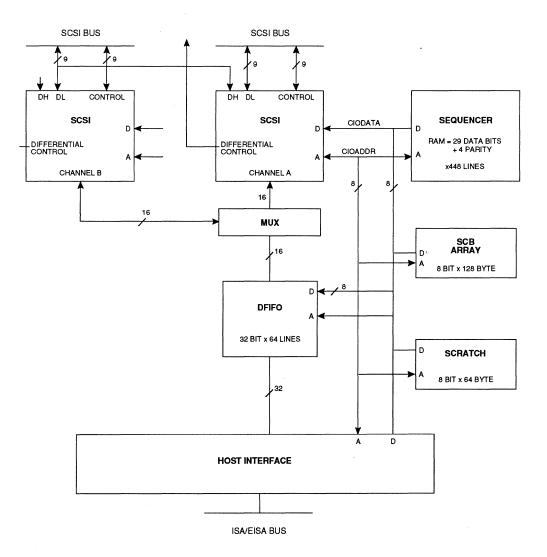

The AIC-7770 is a single chip, dual SCSI channel host adapter with Bus Master transfer capability which will attach to the ISA or EISA interface with no additional logic required. The AIC-7770 contains an advanced Sequencer which will execute a SCSI command described by a Sequencer Control Block (SCB). The AIC-7770 has within it an SCB Array which will hold up to four SCBs loaded by a driver. These SCBs will be executed independently of the SCSI Target ID or SCSI Channel in the order that they are received. The SCB is a data structure which contains all information necessary for the execution of the command. The on board SCSI Sequencer will handle all phases of the SCSI bus, including the Disconnect/Reconnect and Command Complete message. On the host side, transfers will be made at the maximum rate available for the particular host. ISA mode will provide several transfer rates, and EISA will transfer up to the maximum burst rate of 33 MBytes/sec.

The device will also support new SCSI features and emerging host adapter features such as Fast/Wide/Differential SCSI data transfers, Tagged Queuing and Scatter/Gather.

### **Feature Summary**

#### **ISA Interface**

- Direct connect to bus

- Eight I/O address ranges, 32 ISA locations each

- 16-bit Bus Master data transfer

- Video memory 8 or 16-bit transfers

- 24-bit address range

- Programmable data transfer rates 1 to 5 Megatransfers/second (2 to 10 Megabytes)

- Programmable bus on/bus off times for system performance tuning

#### **EISA Interface**

- Direct connect to bus

- 8-bit I/O transfers in 3 BCLKS vs. 6 when system responds to NOWS

- 32-bit burst transfers at 33 MBytes/sec

- 16-bit Downshift mode supported

- System translate cycles supported

- 1K address boundary detection in Burst mode

- 32-bit address range

- Programmable rising edge or negative level interrupts

- Programmable bus release times when preempted

#### Host Adapter Features

- Automatic data FIFO threshold selection

- Power-down mode

- Scatter/Gather supported

- Extremely low overhead

- Data residue reported on underruns

- One interrupt per command

- Queued commands per Target/LUN, overlapped execution

- Modify data pointers message handled

- Tagged Queuing supported

#### **SCSI Features**

- 2 SCSI busses

- Fast data transfers

- Wide data transfers, 1 SCSI bus

- Differential Controls for 1 SCSI bus

- Flexible configuration

- Two 8-bit single ended, both Fast

- One 8-bit single ended, and one 8-bit differential, both Fast

- One 16-bit single ended or differential, Fast

## **Block Diagram**

Figure 1-1. Block Diagram

ø

# 2 Pin Description

## **Pin Summary**

The pins are summarized here, listing the name, pin number, if the pin is an input, and the type and drive of the outputs. The type definitions are listed in the table below. The ISA and EISA pin definitions are mutually exclusive, only one group will be active at a time. A more complete description follows the summary.

| Type Definition | Description                                   |

|-----------------|-----------------------------------------------|

| I               | Input                                         |

| 3ST/#           | Tristate output/Min drive current in mA       |

| OC/#            | Open collector output/Min drive current in mA |

| 2ST/#           | Two state output/Min drive current in mA      |

#### Host Interface

Common pin names are listed singly and shared pins are listed side by side. Pins with no counterpart on the other bus are listed in only one column.

| Signa<br>ISA/EISA=1<br>ISA | l Name<br>ISA/EISA=0<br>EISA | Pin<br>Number                                                                     | I/O<br>Driver<br>ISA<br>Master | I/O<br>Driver<br>ISA<br>Slave | I/O<br>Driver<br>EISA<br>Master | I/O<br>Driver<br>EISA<br>Slave |

|----------------------------|------------------------------|-----------------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------------------------|--------------------------------|

|                            | EN                           | 23                                                                                | NA                             | I                             | NA                              | I                              |

|                            | CLK                          | 24                                                                                | I                              | I                             | I                               | I                              |

|                            | /EISA                        | 7                                                                                 | I                              |                               | T                               | I                              |

|                            | 15:0)                        | 107, 106, 105,<br>104, 103, 102,<br>100, 99, 72,<br>73, 74, 75, 76,<br>77, 79, 80 | I, 3ST/24                      | I, 3ST/24                     | I, 3ST/24                       | I, 3ST/24                      |

| Ι                          | RQ                           | 28                                                                                | 3ST/5                          | 3ST/5                         | 3ST/5                           | 3ST/5                          |

| LA(                        | 23:17)                       | 45, 46, 47, 48,<br>50, 51, 52                                                     | 3ST/24                         | NA                            | 3ST/24                          | NA                             |

| MAS'                       | FER16-                       | 25                                                                                | OC/24                          | NA                            | OC/24                           | NA                             |

| NC                         | WS-                          | 15                                                                                | NA                             | OC/24                         | NA                              | OC/24                          |

| RES                        | SDRV                         | 11                                                                                | I                              | Ι                             | Ι                               | I                              |

|                            | D(31:16)                     | 98, 97, 96, 95,<br>93, 92, 91, 90,<br>89, 88, 87, 85,<br>84, 83, 82, 81           | NA                             | NA                            | I, 3ST/24                       | NA                             |

|                            | LA(31:27)-                   | 36, 37, 38, 39,<br>41                                                             | NA                             | NA                            | 3ST/24                          | NA                             |

| CHRDY                      | EXRDY                        | 13                                                                                | I                              | NA                            | I                               | NA                             |

| DACK-                      | MAK-                         | 27                                                                                | I                              | NA                            | I                               | NA                             |

| DRQ                        | MREQ-                        | 26                                                                                | 3ST/5                          | NA                            | 3ST/5                           | NA                             |

| IORC-                      | START-                       | 12                                                                                | NA                             | I                             | 3ST/24                          | I                              |

| IOWC-                      | CMD-                         | 9                                                                                 | NA                             | I                             | Ι                               | Ι                              |

| M16-                       | BE(2)-                       | 33                                                                                | I                              | NA                            | 3ST/24                          | I                              |

| MRDC-                      | MIO                          | 21                                                                                | 3ST/24                         | NA                            | 3ST/24                          | I                              |

| MWTC-                      | WR                           | 22                                                                                | 3ST/24                         | NA                            | 3ST/24                          | I                              |

| IOSEL1                     | EX32-                        | 14                                                                                | I                              | I                             | Ι                               | NA                             |

| IOSEL2                     | MSBURST-                     | 19                                                                                | I <sup>†</sup>                 | I <sup>†</sup>                | $3ST/24^{\dagger}$              | NA <sup>†</sup>                |

| SBHE-                      | BE(3)-                       | 32                                                                                | 3ST/24                         | NA                            | 3ST/24                          | NA                             |

| SA(1:0)                    | BE(1:0)-                     | 34, 35                                                                            | 3ST/24                         | I                             | 3ST/24                          | I                              |

| SA(9:2)                    | LA(9:2)                      | 62, 63, 64, 65,<br>66, 67, 68, 69                                                 | 3ST/24                         | I                             | 3ST/24                          | I                              |

| SA(15:10)                  | LA(15:10)                    | 54, 55, 56, 58,<br>60, 61                                                         | 3ST/24                         | I                             | 3ST/24                          | NA*                            |

| SA(16)                     | LA(16)                       | 53                                                                                | 3ST/24                         | NA                            | 3ST/24                          | NA                             |

| SA(19:17)                  | LA(26:24)-                   | 42, 43, 44                                                                        | 3ST/24                         | NA                            | 3ST/24                          | NA                             |

| IOSEL0                     | SLBURST-                     | 18                                                                                | I                              | I                             | I                               | NA                             |

### SCSI Interface

| Signal Name   | Pin Number                                | I/O Driver |

|---------------|-------------------------------------------|------------|

| ASCD7-ASCD0   | 125, 126, 127, 128, 130, 131,<br>132, 133 | I, OC/48   |

| ASCDP         | 124                                       | I, OC/48   |

| ACD           | 115                                       | I, OC/48   |

| AIO           | 113                                       | I, OC/48   |

| AMSG          | 117                                       | I, OC/48   |

| AREQ          | 114                                       | I, OC/48   |

| AACK          | 120                                       | I, OC/48   |

| ARESET        | 119                                       | I, OC/48   |

| ASEL          | 116                                       | I, OC/48   |

| ABSY          | 121                                       | I, OC/48   |

| AATN          | 122                                       | I, OC/48   |

| ADIFFDAT(3:0) | 139, 140, 141, 142                        | 2ST/4      |

| ADIFFADR(1:0) | 136, 137                                  | 2ST/4      |

| ADIFFSTRB     | 138                                       | 2ST/4      |

| BSCD7-BSCD0   | 157, 158, 159, 160, 2, 3, 4, 5            | I, OC/48   |

| BSCDP         | 156                                       | I, OC/48   |

| BCD           | 147                                       | I, OC/48   |

| BIO           | 145                                       | I, OC/48   |

| BMSG          | 149                                       | I, OC/48   |

| BREQ          | 146                                       | I, OC/48   |

| BACK          | 152                                       | I, OC/48   |

| BRESET        | 151                                       | I, OC/48   |

| BSEL          | 148                                       | I, OC/48   |

| BBSY          | 153                                       | I, OC/48   |

| BATN          | 154                                       | I, OC/48   |

### **Other Pins**

| Signal Name | Pin Number                                  | I/O Driver |

|-------------|---------------------------------------------|------------|

| CLK         | 8                                           | I          |

| CVCC(1:0)   | 110, 17                                     | NA         |

| CGND(3:0)   | 143, 111, 59, 16                            | NA         |

| SVCC0       | 135                                         | NA         |

| SAGND(4:0)  | 134, 129, 123, 118, 112                     | NA         |

| SBGND(4:0)  | 6, 1, 155, 150, 144                         | NA         |

| HVCC(5:0)   | 109, 94, 71, 57, 31, 20                     | NA         |

| HGND(9:0)   | 108, 101, 86, 78, 70, 49, 40,<br>30, 29, 10 | NA         |

# **Pin Description**

### **ISA/AT Signal Definition**

The signal names used in this specification correspond to the names in the EISA standard. A cross reference to original  $AT^{$ <sup>®</sup> bus signal names which differ is given here for convenience.

| AT Names   | ISA Names |

|------------|-----------|

| RESET DRV  | RESDRV    |

| SD(15:0)   | D(15:0)   |

| I/O CH RDY | CHRDY     |

| -IOR       | IORC-     |

| -IOW       | IOWC-     |

| -MEMR      | MRDC-     |

| -MEMW      | MWRC-     |

| SBHE       | SBHE-     |

| -MASTER    | MASTER16- |

| -MEM CS16  | M16-      |

| ows        | NOWS-     |

### ISA Interface

| Signal Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN         | Address Enable – AEN is driven by the system board and when de-asserted<br>the device will respond as a slave to specific I/O addresses on the ISA bus.<br>AEN will be de-asserted before, during and after IORC- or IOWC- is asserted<br>for ISA. AEN is ignored when in Master mode.                                                                                                                                                                                                                                                                                                  |

| BCLK        | Bus Clock – BCLK provides the capability to synchronize device bus activities<br>to the main system clock. The BCLK frequency operates between 8.333 MHz<br>and 6MHz, with a normal duty cycle of 50 percent. BCLK is driven only by<br>the system board. The BCLK period may be extended for synchronization to<br>the system CPU or other system board devices with no adverse effect since<br>events are synchronized to BCLK edges without regard to frequency or duty<br>cycle. BCLK is driven by the system board. NOWS-, and DRQ are<br>synchronized to the rising edge of BCLK. |

| ISA/EISA    | ISA/EISA Select – ISA/EISA defines the pinout of the host interface section to<br>be either ISA or EISA. When ISA/EISA is high the ISA interface is selected<br>and when low the EISA interface is selected. This pin should be hard wired to<br>VDD or GND.                                                                                                                                                                                                                                                                                                                            |

| CHRDY       | Channel Ready – When operating as a Bus Master, this line is sampled two T cycles before the programmed rising edge of MWTC or MRDC. When CHRDY is detected de-asserted, the device will extend its assertion of MRDC- or MWTC- for as long as CHRDY is de-asserted plus three or less T cycles after sensing CHRDY asserted. CHRDY is also used as an input to enable writing to TESTCHIP.                                                                                                                                                                                             |

| DACK-       | DMA Acknowledge – DACK- is asserted by the system board to acknowledge<br>the grant of the ISA response to DRQ- asserted. The device asserts<br>MASTER16- after detecting DACK- asserted to complete the ISA bus<br>arbitration.                                                                                                                                                                                                                                                                                                                                                        |

| DRQ         | DMA Request – DRQ is asserted by the device as an ISA Bus Master to arbitrate for the system bus. DRQ is deasserted/asserted synchronously with the rising edge of BCLK.                                                                                                                                                                                                                                                                                                                                                                                                                |

| D(15:0)     | Data – D15 is the most significant data bit of the data bus. All I/O commands<br>are transferred on D(7:0). All data transferred as a Bus Master will be on<br>D(15:0), except for leading and trailing byte offsets and when the address is<br>between A0000 and BFFFF. When the address is between A0000 and<br>BFFFF, if M16- is asserted, the transfer will be 16-bits wide and if de-<br>asserted will be 8-bits wide.                                                                                                                                                             |

| IORC-       | I/O Read Control – SA(15:0), AEN, and IOSEL(2:0) are decoded and if a valid address is detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IOSEL(2:0)  | I/O Address Select – The IOSEL(2:0) inputs provide a means to select the primary I/O address range that will respond to IORC- and IOWC                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IOWC-       | I/O Write Control – SA(15:0), AEN, and IOSEL(2:0) are decoded and if a valid address is detected, data from $D(7:0)$ will be written into the selected register on the trailing edge.                                                                                                                                                                                                                                                                                                                                                                                                   |

| IRQ         | Interrupt Request – This is a high true signal which will become true when<br>an interrupt event happens and that event has been enabled by the driver.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LA(23:17)   | Latched Address – These high true signals are driven at the same time as the SA address lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | Continue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Signal Name | Description                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER16-   | Bus Master – This signal is asserted as part of the normal protocol when<br>arbitrating for the ISA bus. It is asserted after the system board asserts<br>DACK- to indicate a Bus Master now controls the ISA Bus. It will be<br>de-asserted immediately after DACK- is de-asserted.           |

| MRDC-       | Memory Read Control – This signal is asserted as a Bus Master during<br>memory reads. Data is latched on the trailing edge of the pulse, and the<br>width and rate are programmable.                                                                                                           |

| MWTC-       | Memory Write Control – This signal is asserted as a Bus Master during<br>memory writes. Data is valid before the leading edge of the pulse, and the<br>width and rate are programmable.                                                                                                        |

| M16-        | Memory width 16-bit – This signal is asserted by a memory slave when the data is 16-bits wide. It is only considered valid for video RAM transfers and will take effect only when the address is between A0000 and BFFFF.                                                                      |

| NOWS-       | No Wait State – The device asserts NOWS- when responding as an I/O slave<br>synchronous to the rising edge of BCLK. This action requests that the I/O<br>cycle be shortened. The device may be programmed to shorten the cycle by 3<br>or 4 BCLKs by setting or clearing ENABLE (bit 0, BCTL). |

| RESDRV      | Reset – Assertion of RESDRV causes a hardware reset to the AIC-7770. All<br>bus drivers will be disabled until RESDRV is de-asserted. The AIC-7770<br>registers will be put in the initialized state, RAM is indeterminate. RESDRV<br>is usually asserted at power up time.                    |

| SA(19:0)    | System Address – As a Bus Master, the system address lines are driven with<br>the appropriate address during memory reads and writes. SA (19:0) and<br>LA(23:17) are driven with the total 24-bit address.                                                                                     |

|             | As a slave, SA (15:0) are decoded to detect a valid I/O address.                                                                                                                                                                                                                               |

| SBHE-       | System Byte High Enable – As a Bus Master, SBHE- is asserted to indicate that a 16-bit data transfer, or an 8-bit data transfer to an odd address is about to occur.                                                                                                                           |

### **EISA Interface**

| Signal Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN         | Address Enable – AEN is driven by the system and used by the I/O decode logic to validate the address on the LA lines. AEN will be de-asserted when START- is asserted for I/O accesses until after CMD- is asserted. AEN is ignored when in Master mode.                                                                                                                                                                                                                                                                                                                                                                                                 |

| BCLK        | Bus Clock – BCLK is used to synchronize the device bus activities to the<br>main system clock. The BCLK frequency operates between 8.333 MHz and<br>8 MHz, with a normal duty cycle of 50 percent. BCLK is driven only by the<br>system board. Events are synchronized to BCLK edges without regard to<br>frequency or duty cycle. BCLK is always synchronous with the trailing<br>edge of START- and the leading edge of CMD BCLK may not be<br>synchronous with the leading edge of START- or the trailing edge of CMD-                                                                                                                                 |

| BE(3:0)-    | Byte Enable – $BE(3:0)$ - are the byte enable signals that identify the specific bytes addressed in a double word space. $BE(3:0)$ - are pipelined from one cycle to the next and are inputs latched as an I/O slave and are outputs when a Bus Master. The timing of these signals varies depending on the cycle type. During normal cycles they are presented in reference to the rising edge of BCLK and for burst cycles they are presented in reference to the falling edge of BCLK and remain valid as long as LA(31:2) remain valid.                                                                                                               |

| ISA/EISA    | ISA/EISA Select – ISA/EISA selects either the ISA or EISA interface to be<br>the active host interface. When ISA/EISA is asserted the ISA interface is<br>selected and when de-asserted the EISA interface is selected. Changing<br>this pin will redefine the I/O pins of the device. This pin should be hard<br>wired to VDD or GND.                                                                                                                                                                                                                                                                                                                    |

| CMD-        | Command – CMD- is driven by the system board and provides timing<br>control within the EISA bus cycle. The system board asserts CMD- on the<br>rising edge of BCLK, simultaneously with de-assertion of START The<br>system board holds CMD- asserted until the end of a normal cycle (2<br>BCLKs) which may be extended by the system board when performing<br>data size translations. When burst cycles are being performed the system<br>board holds CMD- asserted until MSBURST- is de-asserted. The end of<br>the cycle may be extended by EXRDY and is normally synchronized with<br>the rising edge of BCLK, but in certain cases is asynchronous. |

| D(31:0)     | Data – Data is 32-bits wide for normal or burst transfers. The Data bus is<br>divided up into 4 byte lanes of 8-bits each. Valid data in a particular byte<br>lane is indicated by one of the BE- lines being asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | When responding as an I/O Slave, data is transferred on $D(7:0)$ only.<br>When transferring as a Bus Master, data will be transferred 32-bits at a time, or less if the transfer is less than 4 bytes long such as during leading or trailing partial double-word transfers. Data may be transferred with normal cycles or with burst cycles. If a 16-bit system memory is installed with the ability to transfer with burst cycles, the device will go into Downshift mode and transfer data on $D(15:0)$ .                                                                                                                                              |

| EXRDY       | EISA Transfer Ready – This signal is sampled when in Master mode to determine if wait-states should be added to the current cycle. It is sampled with BCLK and the cycle will be extended for as long as EXRDY is de-<br>asserted. EXRDY is not driven as a slave.                                                                                                                                                                                                                                                                                                                                                                                        |

|             | Continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Signal Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| EX32-       | EISA Transfer 32-bit – EX32- is asserted by a 32-bit EISA memory after decoding a valid address on signals LA(31:2) and MIO. EX32- is also asserted by the system board when it is performing data size translation to indicate the completion of the translation. EX32- is sampled by the device when transferring data as a Bus Master.                                                                                                                                                                                                                                                       |  |  |  |  |

| IRQ         | Interrupt Request – IRQ may be selected to operate in either the edge triggered or level sensitive interrupt mode. IRQ is asserted when the INTEN bit is active and one of the interrupt conditions is true with its corresponding interrupt enabled. In the edge triggered mode, IRQ will drive high when active and drive low when inactive. In the level sensitive mode, IRQ will drive low when active and will remain turned off when inactive.                                                                                                                                            |  |  |  |  |

| LA(23:2)    | Latchable Address – These lines are driven along with LA(31:24)- and BE(3:0)- when in Bus Master mode.<br>When responding as an I/O Slave, address lines LA(9:2) and BE(3:0)- are                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| LA(31:24)-  | decoded with AEN and MIO for a valid address.<br>Latchable Address – These lines have the same characteristics as LA(23:2)<br>except they are active low.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| MAK-        | Master Acknowledge – MAK- asserted indicates to the device that it has<br>been granted bus access as an EISA Bus Master. MAK- is driven by the<br>system board in response to MREQ- asserted by the device.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| MASTER16-   | Master, 16-bit – MASTER16- is asserted as a Bus Master to indicate that<br>it is able to enter the Downshift mode while transferring to or from a 16-<br>bit EISA memory which has burst ability.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| MIO         | Memory, I/O – MIO is asserted by a EISA Bus Master or the system board to indicate a memory cycle is in progress. MIO de-asserted indicates that the cycle in progress is an I/O cycle.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| MREQ-       | Master Request – MREQ- is asserted by the device to request access to the<br>bus as an Bus Master. The device will hold MREQ- asserted until the<br>system board grants access by asserting MAK The system board samples<br>MREQ- on the rising edge of BCLK. When the device has completed a<br>transfer it can release the bus by de-asserting MREQ- on the falling edge<br>of BCLK. The device will wait a minimum of two BCLK cycles between de-<br>asserting MREQ- before again asserting MREQ Once MREQ- is asserted,<br>it will not be released until at least one transfer takes place. |  |  |  |  |

| MSBURST-    | Master Burst – MSBURST- is asserted by the device in Bus Master mode<br>to indicate that burst cycles will be performed to the addressed memory<br>slave if SLBURST- is asserted. The device begins a data transfer to or<br>from memory with normal cycles (2 BCLKs/cycle) and will shift to burst<br>cycles (1 BCLK/cycle) when it samples SLBURST- asserted with the rising<br>edge of BCLK at the end of START-, as long as EXRDY is sampled<br>asserted on the next falling edge of BCLK.                                                                                                  |  |  |  |  |

|             | 1K page boundary detection during a burst sequence will cause the burst<br>to be interrupted with an normal cycle being performed when passing over<br>the bounds, then the burst will be resumed until one of the following<br>occurs (the Host byte count is zero, a Bus Master preemption occurred and<br>the number of BCLKs determined by the BOFF value have passed or<br>HDMAEN is set inactive).                                                                                                                                                                                        |  |  |  |  |

| NOWS-       | No Wait State – The device asserts NOWS- when responding as a slave to shorten the standard 6 BCLK I/O cycle to 3 BCLKs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Signal Name | Description                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESDRV      | Reset – Assertion of RESDRV causes a hardware reset to the AIC-7770.<br>All bus drivers will be disabled until RESDRV is de-asserted. The AIC-<br>7770 registers will be put in the initialized state, RAM is indeterminate.<br>RESDRV is usually asserted at power up time.               |

|             | In EISA mode, after RESDRV is de-asserted all bus drivers will remain<br>inhibited until the ENABLE bit is set active (=1) in the BCTL register by<br>an IO write cycle from the system board, except that data will be driven as<br>requested by I/O Read cycles from the system board.   |

| SLBURST-    | Slave Burst – SLBURST- is driven by a memory slave to indicate it is able<br>to perform burst transfers. SLBURST- is sampled by the device when<br>transferring as a Bus Master. If it is asserted, the device will go into Burst<br>mode.                                                 |

| START-      | Start – START- is asserted by the device at the beginning of a cycle after LA(31:2) and MIO become valid. START- is de-asserted on the rising edge of BCLK after 1 BCLK time.                                                                                                              |

| WR          | Write/Read – The device asserts WR when in Master mode to indicate a memory Write. WR remains valid as long as LA(31:2) are valid. WR is driven from the same edge of BCLK that activates START. As an I/O Slave, WR is sampled as an input and determines the direction of data transfer. |

### **SCSI Interface**

| Signal Name | Description                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASCD(7:0)-  | SCSI Data, port A – The SCSI data lines drive the ID during arbitration and selection, and command and data information as well as status and messages.                                                                                                                |

| ASCDP -     | SCSI Parity, port A – This bit provides odd parity for $ASCD(7:0)$ .                                                                                                                                                                                                   |

| ACD-        | Command/Data, port A – This control line is received when in Initiator mode or driven when in Target mode. It indicates Command or Message phase when asserted, and Data phase when de-asserted. This control signal is also used for 16-bit transfers.                |

| AIO-        | In/Out, port A – This control line is received when in Initiator mode or<br>driven when in Target mode. It indicates the In direction when asserted,<br>and the Out direction when de-asserted. This control signal is also used<br>for 16-bit transfers.              |

| AMSG-       | Message, port A – This control line is received when in Initiator mode or driven when in Target mode. It indicates a Message phase when asserted, and a Command or Data phase when de-asserted. This control signal is also used for 16-bit transfers.                 |

| AREQ-       | Request, port A – This control line is received by the device when in<br>Initiator mode and driven when in Target mode. A Target will assert REQ-<br>to indicate a byte is ready or is needed by the Target. This control signal is<br>also used for 16-bit transfers. |

|             | Continued                                                                                                                                                                                                                                                              |

| Signal Name    | Description                                                                                                                                                                                                                                                                                                |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AACK-          | Acknowledge, port A – This control line is received by the device when in Target mode and driven when in Initiator mode. An Initiator will assert ACK - to indicate a byte is ready or is needed by the Target. This control signal is also used for 16-bit transfers.                                     |  |  |

| ARESET-        | Reset, port A – This line is received and driven. It is interpreted as a Hard Reset and will clear all commands pending on the SCSI bus. This control signal is also used for 16-bit transfers.                                                                                                            |  |  |

| ASEL-          | Select, port A – This line is driven after a successful arbitration to Select<br>as an Initiator or Reselect as a Target, and otherwise it is received. This<br>control signal is also used for 16-bit transfers.                                                                                          |  |  |

| ABSY-          | Busy, port A – This line is driven by the Initiator as a handshake during arbitration, and received for the rest of the transfer. As a Target it is driven also as a handshake during arbitration, and then is driven for the rest of the transfer. This control signal is also used for 16-bit transfers. |  |  |

| AATN-          | Attention, port $A$ – This line is driven as an Initiator when a special condition occurs. It is received by the Target. This control signal is also used for 16-bit transfers.                                                                                                                            |  |  |

| ADIFFDAT(3:0)- | Differential Data – These lines contain information which is latched by outside circuitry to provide control of differential drivers. The definition of these bits depends on the value of DIFFADR(1:0).                                                                                                   |  |  |

| ADIFFADR(1:0)- | Differential Address – These lines determine the meaning of DIFFDAT(3:0).                                                                                                                                                                                                                                  |  |  |

| ADIFFSTRB-     | Differential Strobe – This signal clocks the data from DIFFDAT into the addressed latch specified by DIFFADR. Both DIFFDAT and DIFFADR are stable for the duration of DIFFSTRB.                                                                                                                            |  |  |

| BSCD0-SCD7-    | SCSI Data, port B – The SCSI data lines drive the ID during arbitration and selection, and command and data information as well as status and messages.                                                                                                                                                    |  |  |

| BSCDP-         | SCSI Parity, port B – This bit provides odd parity for $ASCD(7:0)$ .                                                                                                                                                                                                                                       |  |  |

| BCD-           | Command/Data, port B – This control line is received when in Initiator<br>mode or driven when in Target mode. It indicates Command or Message<br>phase when asserted, and Data phase when de-asserted. BCD- is<br>grounded to indicate a 16-bit transfer hardware connection.                              |  |  |

| BIO-           | In/Out, port $B$ – This control line is received when in Initiator mode or driven when in Target mode. It indicates the In direction when asserted, and the Out direction when de-asserted.                                                                                                                |  |  |

| BMSG-          | Message, port $B$ – This control line is received when in Initiator mode or driven when in Target mode. It indicates a Message phase when asserted, and a Command or Data phase when de-asserted. BMSG- is grounded to indicate that no hardware connection has been made to Channel B.                    |  |  |

| BREQ-          | Request, port $B$ – This control line is received by the device when in Initiator mode and driven when in Target mode. A Target will assert REQ-to indicate a byte is ready or is needed by the Target.                                                                                                    |  |  |

| BACK-          | Acknowledge, port B – This control line is received by the device when in<br>Target mode and driven when in Initiator mode. An Initiator will assert<br>ACK - to indicate a byte is ready or is needed by the Target.                                                                                      |  |  |

| BRESET-        | Reset, port $B$ – This line is received and driven. It is interpreted as a Hard Reset and will clear all commands pending on the SCSI bus.                                                                                                                                                                 |  |  |

| Signal Name Description |                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BSEL-                   | Select, port $B$ – This line is driven after a successful arbitration to Select as an Initiator or Reselect as a Target, and otherwise it is received.                                                                                                                                                                                                               |  |  |  |

| BBSY-                   | Busy, port $B$ – This line is driven by the Initiator as a handshake during arbitration, and received for the rest of the transfer. As a Target it is driven also as a handshake during arbitration, and then is driven for the rest of the transfer. BBSY- is tied to VDD when indicating a 16-bit hardware connection or no hardware connection. See BMSG- and BCD |  |  |  |

| BATN-                   | Attention, port $B-$ This line is driven as an Initiator when a special condition occurs. It is received by the Target.                                                                                                                                                                                                                                              |  |  |  |

### **Other Pins**

| Signal Name | Description                                  |  |  |  |

|-------------|----------------------------------------------|--|--|--|

| CLK         | Clock input. 40 MHz nominal input frequency. |  |  |  |

| CVCCx       | Chip +Voltage supply                         |  |  |  |

| CGNDx       | Chip Ground                                  |  |  |  |

| SVCCx       | CSI A and B bus Driver +Voltage supply       |  |  |  |

| SAGNDx      | SCSI A bus Driver Ground                     |  |  |  |

| SBGNDx      | SCSI B bus Driver Ground                     |  |  |  |

| HVCCx       | Host bus Driver +Voltage supply              |  |  |  |

| HGNDx       | Host bus Driver Ground                       |  |  |  |

Notes:

- Unused pins should not be connected

- The device should be decoupled using standard practice of locating capacitors as close as possible to the device. As the host and chip power connections are separated internal to the chip, care should be taken not to couple noise from HVCC pins to CVCC pins

# 3 Register Description

# ISA I/O Map

All I/O registers are decoded in groups of 32 registers so as not to use excessive ISA I/O space. The registers are decoded within 32 address spaces and the aliases of that space. The 32 address group may be moved to other locations, to provide flexibility for the system integrator. The register groups and the possible locations are summarized below.

| IOSELn 210 | SCSI<br>Primary | Scratch<br>Alias 1 and 2 | Sequencer<br>Alias 3 | Host<br>Alias 4 | SCB Array<br>Alias 5 |

|------------|-----------------|--------------------------|----------------------|-----------------|----------------------|

| 000        | 0120-013F       | 0520-053F<br>0920-093F   | 0D20-0D3F            | 1120-123F       | 1520-153F            |

| 001        | 0140-015F       | 0540-055F<br>0940-095F   | 0D40-0D5F            | 1140-115F       | 1540-155F            |

| 010        | 0220-023F       | 0620-063F<br>0A20-0A3F   | 0E20-0E3F            | 1220-123F       | 1620-163F            |

| 011        | 0240-025F       | 0640-065F<br>0A40-0A5F   | 0E40-0E5F            | 1240-125F       | 1640-165F            |

| 100        | 0280-029F       | 0680-069F<br>0A80-0A9F   | 0E80-0E9F            | 1280-129F       | 1680-169F            |

| 101        | 02A0-02BF       | 06A0-06BF<br>0AA0-0ABF   | 0EA0-0EBF            | 12A0-12BF       | 16A0-16BF            |

| 110        | 0320-033F       | 0720-073F<br>0B20-0B3F   | 0F20-0F3F            | 1320-133F       | 1720-173F            |

| 111        | 0340-035F       | 0740-075F<br>0B40-0B5F   | 0F40-0F5F            | 1340-135F       | 1740-175F            |

### EISA and Chip I/O Map

The EISA I/O map is contained entirely within the slot specific address range of zC00zCFF where z is the slot number. The on-chip address may be obtained from the EISA address by using the lower eight bits of the EISA address. Address bits LA10 and LA11 are not decoded so that the chip will respond to addresses 000-0BF, 400-4BF, 800-8BF, and C00-CBF. This is to allow for multiple chips attached to a single EISA slot with some additional external decoding logic. The EISA ranges are summarized below.

| Register Group | Address Range |

|----------------|---------------|

| SCSI           | C00-C1F       |

| SCRATCH        | C20-C5F       |

| SEQUENCER      | C60-C7F       |

| HOST           | C80-C9F       |

| SCB Array      | CA0-CBF       |

### **Register Summary**

The summary below lists the complete name and mnemonic of each register in the chip. The list is divided into groups with a common address range. The ISA range given is an example of one of the ranges offered for this group. The EISA and chip addresses uniquely specify the address. When the host must access these registers the Sequencer must be paused, except when noted otherwise.

#### **SCSI Registers**

ISA 0340-035F, EISA zC00-zC1F, CHIP 00-1F

| Register Name             | Mnemonic | Read/Write | Comments                           |

|---------------------------|----------|------------|------------------------------------|

| SCSI Sequence control     | SCSISEQ  | R/W        |                                    |

| SCSI Transfer Control 0   | SXFRCTL0 | R/W        |                                    |

| SCSI Transfer Control 1   | SXFRCTL1 | R/W        |                                    |

| SCSI Signal Out           | SCSISIGO | w          |                                    |

| SCSI Signal In            | SCSISIGI | R          |                                    |

| SCSI Rate                 | SCSIRATE | R/W        |                                    |

| SCSI ID                   | SCSIID   | R/W        |                                    |

| SCSI Latched Data Low     | SCSIDATL | R/W        |                                    |

| SCSI Latched Data High    | SCSIDATH | R/W        |                                    |

| SCSI Transfer Count 0     | STCNT0   | R/W        |                                    |