# AIC-6260

# Single-Chip PC AT-to-SCSI I/O Processor

Data Sheet Rev. 3 May, 1991

#### **FEATURES**

- Single-chip PC AT-to-SCSI host adapter

- Low-cost connectivity to multiple SCSI peripherals

- 8-bit DMA or 16-bit PIO transfers supported

- Average data transfer rates up to 4 megabytes/second

- 128-byte FIFO for data buffering

- Synchronous and asynchronous SCSI devices supported

- Multitasking driver software available now

- Up to eight simultaneous I/O tasks supported

- BIOS available now

- 68-pin PLCC or 80-pin QFP packages

- CCS and SCSI-2 supported

© Copyright 1990 Adaptec, Inc. All rights reserved. The information contained in this data sheet is subject to change without notice. No part of this document may be copied or reproduced in any form without prior written consent from Adaptec, Inc.

# Table of Contents

| Sec | ction Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>'</b> age                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1.0 | Overview1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -1                                                                                             |

| 2.0 | Pin Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                |

| 3.0 | 3.1       SCSI Sequence Control (SCSISEQ)       3-         3.2       SCSI Transfer Control 0 (SXFRCTL0)       3-         3.3       SCSI Transfer Control 1 (SXFRCTL1)       3-         3.4       SCSI Signal In (SCSISIGI)       3-         3.5       SCSI Signal Out (SCSISIGO)       3-         3.6       SCSI Rate Control (SCSIRATE)       3-         3.6       SCSI Rate Control (SCSIRATE)       3-         3.7       Selection/Reselection ID (SELID)       3-         3.8       SCSI ID (SCSID)       3-         3.9       SCSI Latched Data (SCSIDAT)       3-1         3.10       SCSI Transfer Count 2–0 (STCNT0, STCNT1, STCNT2)       3-1         3.11       SCSI Interrupt Status 0 (STAT0)       3-1         3.12       SCSI Interrupts 0 (CLRINT0)       3-1         3.13       Clear SCSI Interrupts 1 (CLRINT1)       3-1         3.14       SCSI Status 2 (SSTAT2)       3-1         3.15       Clear SCSI Interrupts 1 (CLRINT1)       3-1         3.16       SCSI Status 2 (SSTAT3)       3-1         3.17       SCSI Status 2 (SSTAT3)       3-1         3.18       SCSI Status 4 (SSTAT4)       3-2         3.20       Clear SCSI Errors (CLRSERR)       3-2 <t< td=""><td>-3 -4 -5 -7 -7 -8 -9 -9 10 11 12 14 15 17 18 19 20 12 22 32 42 56 7 78 99 00 30 30 30 30 30 31</td></t<> | -3 -4 -5 -7 -7 -8 -9 -9 10 11 12 14 15 17 18 19 20 12 22 32 42 56 7 78 99 00 30 30 30 30 30 31 |

|     | 3.33 Test Register (TEST)3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                             |

| 4.0 | Fun               | ctional Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-1                                                                                                                                                  |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 4.1               | General Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      |

|     | · ·               | 4.1.1 SCSI Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2                                                                                                                                                  |

|     |                   | 4.1.2 SCSI Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |

|     |                   | 4.1.3 SCSI Selection/Reselection Autoconnect Sequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-2                                                                                                                                                  |

|     |                   | 4.1.4 SCSI FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

|     |                   | 4.1.5 Address Mapping and External Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

|     |                   | 4.1.6 Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                      |

|     |                   | 4.1.7 Host Interface,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |

|     |                   | 4.1.8 Host FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

|     | 4.2               | SCSI Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |

|     |                   | 4.2.1 SCSI Manual PIO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                      |

|     |                   | 4.2.2 SCSI Automatic PIO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      |

|     |                   | 4.2.3 SCSI Normal Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                      |

|     | 4.3               | Host Processor Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      |

|     |                   | 4.3.1 Host PIO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |

|     |                   | 4.3.2 Host DMA Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |

|     | 4.4               | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                      |

|     | 4.5               | External PortsDecode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

|     | 4.6               | Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                      |

|     | 4.7               | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                      |

|     |                   | 4.7.1 Powerdown-Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                      |

|     | 4.8               | Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                      |

|     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

|     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

| 5.0 | Ap                | olication Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

| 5.0 | Арј<br>5.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

| 5.0 |                   | olication Notes<br>Selection/Reselection Sequences<br>5.1.1 Selection Out Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-1                                                                                                                                                  |

| 5.0 |                   | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1                                                                                                                                           |

| 5.0 |                   | Selection/Reselection Sequences<br>5.1.1 Selection Out Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1<br>5-2                                                                                                                                    |

| 5.0 |                   | Selection/Reselection Sequences<br>5.1.1 Selection Out Sequence<br>5.1.2 Selection In Sequence<br>5.1.3 Reselection In Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1<br>5-2<br>5-2                                                                                                                             |

| 5.0 |                   | Selection/Reselection Sequences<br>5.1.1 Selection Out Sequence<br>5.1.2 Selection In Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1<br>5-2<br>5-2<br>5-3<br>5-3                                                                                                               |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3<br>5-4<br>5-4                                                                                                 |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-4                                                                                          |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-4<br>5-5                                                                                   |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-5<br>5-5<br>5-5                                                                     |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-4<br>5-5<br>5-5<br>5-5<br>5-6                                                       |

| 5.0 | 5.1               | Selection/Reselection Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-3\\5-3\\5-3\\5-3\\5-4\\5-4\\5-5\\5-5\\5-5\\5-5\\5-6\\5-7\end{array}$                                          |

| 5.0 | 5.1               | <ul> <li>Selection/Reselection Sequences.</li> <li>5.1.1 Selection Out Sequence.</li> <li>5.1.2 Selection In Sequence.</li> <li>5.1.3 Reselection In Sequence.</li> <li>5.1.4 Reselection Out Sequence.</li> <li>SCSI PIO Data Transfers.</li> <li>5.2.1 Initiator Data Transfer: Host to SCSI.</li> <li>5.2.2 Initiator Data Transfer: SCSI to Host.</li> <li>5.2.3 Target Data Transfer: Host to SCSI.</li> <li>5.2.4 Target Data Transfer: SCSI to Host.</li> <li>Normal Mode Data Transfer: Host to SCSI in Host PIO Mode.</li> <li>5.3.1 Initiator Data Transfer: SCSI to Host in Host PIO Mode.</li> <li>5.3.2 Initiator Data Transfer: SCSI to Host in Host PIO Mode.</li> <li>5.3.3 Initiator Data Transfer: SCSI to Host in Host PIO Mode.</li> <li>5.3.4 Initiator Data Transfer: SCSI to Host in Host DMA Mode</li> </ul>                                                                                                                                         | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-2\\5-2\\5-3\\5-3\\5-4\\5-4\\5-5\\5-5\\5-5\\5-5\\5-6\\5-7\\5-7\end{array}$                                     |

| 5.0 | 5.1               | <ul> <li>Selection/Reselection Sequences.</li> <li>5.1.1 Selection Out Sequence.</li> <li>5.1.2 Selection In Sequence.</li> <li>5.1.3 Reselection Out Sequence.</li> <li>5.1.4 Reselection Out Sequence.</li> <li>SCSI PIO Data Transfers.</li> <li>5.2.1 Initiator Data Transfer: Host to SCSI.</li> <li>5.2.2 Initiator Data Transfer: SCSI to Host.</li> <li>5.2.3 Target Data Transfer: Host to SCSI.</li> <li>5.2.4 Target Data Transfer: SCSI to Host.</li> <li>Normal Mode Data Transfer: Host to SCSI in Host PIO Mode</li> <li>5.3.1 Initiator Data Transfer: SCSI to Host in Host PIO Mode</li> <li>5.3.2 Initiator Data Transfer: SCSI to Host in Host PIO Mode</li> <li>5.3.3 Initiator Data Transfer: SCSI to Host in Host PIO Mode</li> <li>5.3.4 Initiator Data Transfer: Host to SCSI in Host DMA Mode</li> <li>5.3.5 Target Data Transfer: Host to SCSI in Host PIO Mode</li></ul>                                                                          | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-2\\5-3\\5-3\\5-3\\5-4\\5-4\\5-5\\5-5\\5-5\\5-5\\5-6\\5-7\\5-7\\5-7\\5-7\\5-7\end{array}$                      |

| 5.0 | 5.1               | <ul> <li>Selection/Reselection Sequences.</li> <li>5.1.1 Selection Out Sequence.</li> <li>5.1.2 Selection In Sequence.</li> <li>5.1.3 Reselection Out Sequence.</li> <li>5.1.4 Reselection Out Sequence.</li> <li>SCSI PIO Data Transfers</li> <li>S.2.1 Initiator Data Transfer: Host to SCSI.</li> <li>5.2.2 Initiator Data Transfer: SCSI to Host.</li> <li>5.2.3 Target Data Transfer: Host to SCSI.</li> <li>5.2.4 Target Data Transfer: SCSI to Host.</li> <li>Normal Mode Data Transfer: Host to SCSI in Host PIO Mode.</li> <li>5.3.1 Initiator Data Transfer: SCSI to Host in Host PIO Mode.</li> <li>5.3.2 Initiator Data Transfer: Host to SCSI in Host PIO Mode.</li> <li>5.3.3 Initiator Data Transfer: SCSI to Host in Host PIO Mode.</li> <li>5.3.4 Initiator Data Transfer: Host to SCSI in Host DMA Mode</li> <li>5.3.5 Target Data Transfer: SCSI to Host in Host PIO Mode.</li> <li>5.3.6 Target Data Transfer: SCSI to Host in Host PIO Mode.</li> </ul> | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-2\\5-3\\5-3\\5-3\\5-4\\5-4\\5-5\\5-5\\5-5\\5-5\\5-6\\5-7\\5-7\\5-7\\5-7\\5-8\end{array}$                      |

| 5.0 | 5.1               | <ul> <li>Selection/Reselection Sequences</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-2\\5-2\\5-3\\5-3\\5-3\\5-4\\5-5\\5-5\\5-5\\5-5\\5-6\\5-7\\5-7\\5-7\\5-7\\5-8\\5-9\end{array}$                 |

| 5.0 | 5.1               | Selection/Reselection Sequences.5.1.1 Selection Out Sequence5.1.2 Selection In Sequence.5.1.3 Reselection In Sequence.5.1.4 Reselection Out Sequence.SCSI PIO Data TransfersScSI PIO Data Transfers5.2.1 Initiator Data Transfer: Host to SCSI.5.2.2 Initiator Data Transfer: SCSI to Host.5.2.3 Target Data Transfer: Host to SCSI.5.2.4 Target Data Transfer: SCSI to Host.Normal Mode Data Transfer: SCSI to Host.S.3.1 Initiator Data Transfer: Host to SCSI in Host PIO Mode.5.3.2 Initiator Data Transfer: SCSI to Host in Host PIO Mode.5.3.3 Initiator Data Transfer: Host to SCSI in Host PIO Mode.5.3.4 Initiator Data Transfer: SCSI to Host in Host DMA Mode .5.3.5 Target Data Transfer: Host to SCSI in Host PIO Mode.5.3.6 Target Data Transfer: SCSI to Host in Host PIO Mode.5.3.7 Target Data Transfer: Host to SCSI to Host in DMA Mode .5.3.8 Target Data Transfer: SCSI to Host in Host DMA Mode.                                                       | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-2\\5-2\\5-2\\5-2\\5-3\\5-3\\5-4\\5-5\\5-5\\5-5\\5-5\\5-5\\5-6\\5-7\\5-7\\5-7\\5-8\\5-9\\5-9\\5-9\end{array}$  |

| 5.0 | 5.1<br>5.2<br>5.3 | <ul> <li>Selection/Reselection Sequences</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\begin{array}{c}5-1\\5-2\\5-2\\5-2\\5-2\\5-2\\5-2\\5-3\\5-3\\5-4\\5-4\\5-5\\5-5\\5-5\\5-5\\5-7\\5-7\\5-7\\5-7\\5-7\\5-7\\5-9\\5-9\\5-10\end{array}$ |

÷

| 6.0 | Elect | rical Information6-1                                 |

|-----|-------|------------------------------------------------------|

|     | 6.1   | Absolute Maximum Ratings                             |

|     | 6.2   | Operating Conditions                                 |

|     | 6.3   | DC Electrical Characteristics                        |

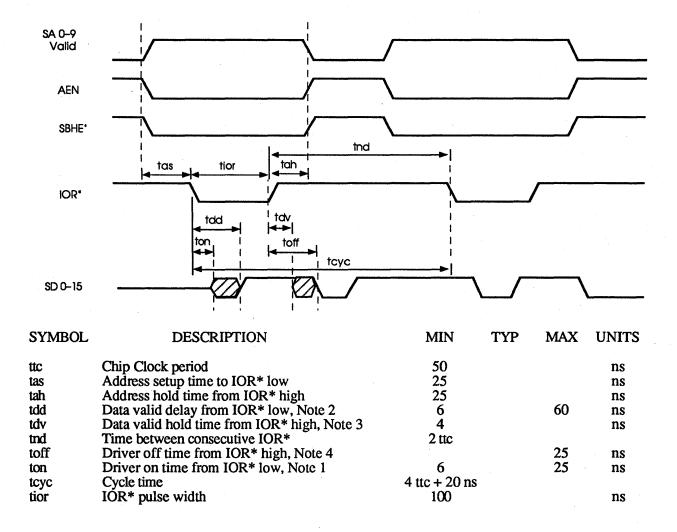

|     | 6.4   | System Timing                                        |

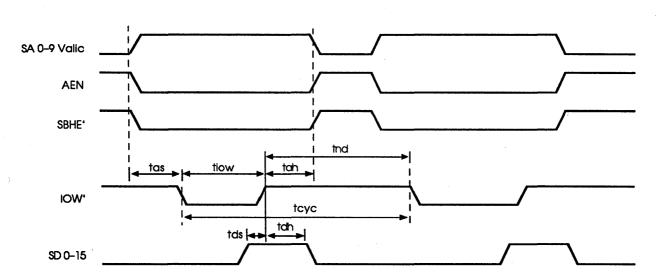

|     |       | 6.4.1 Host Processor PIO Data Read Operation         |

|     |       | 6.4.2 Host Processor PIO Data Write Operation        |

|     |       | 6.4.3 Host Processor I/O Read Operation              |

|     |       | 6.4.4 Host Processor I/O Write Operation             |

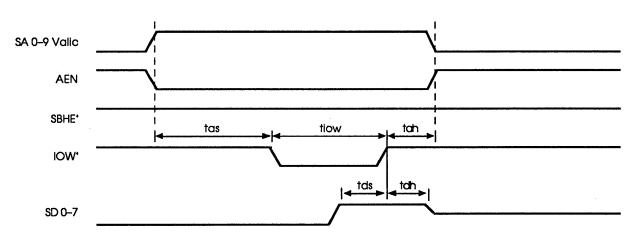

|     |       | 6.4.5 Host Processor DMA Read Operation6-6           |

|     |       | 6.4.6 Host Processor DMA Write Operation             |

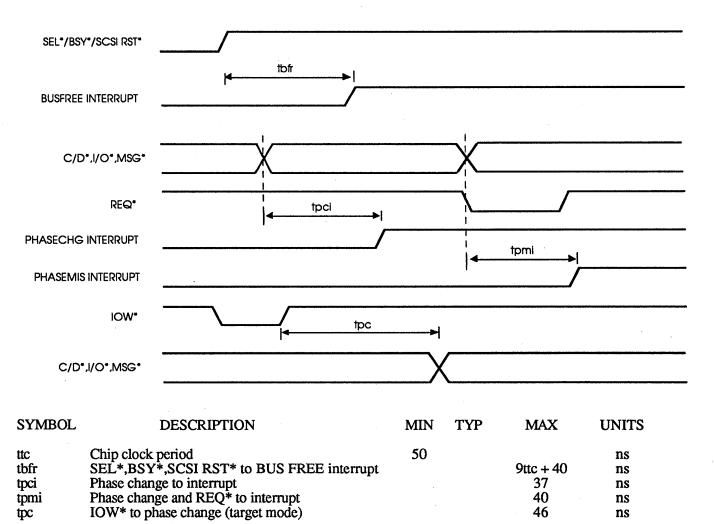

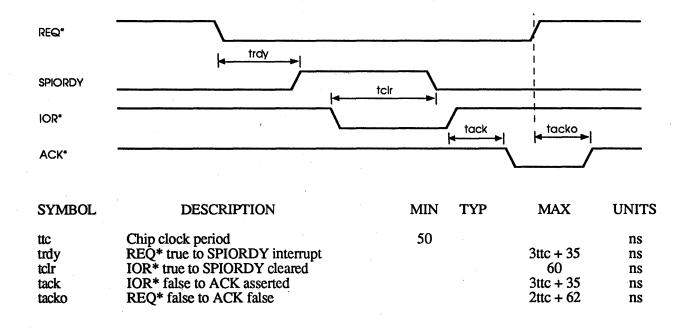

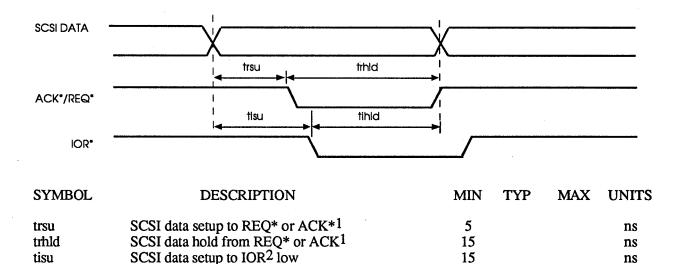

|     | 6.5   | SCSI Bus Timing                                      |

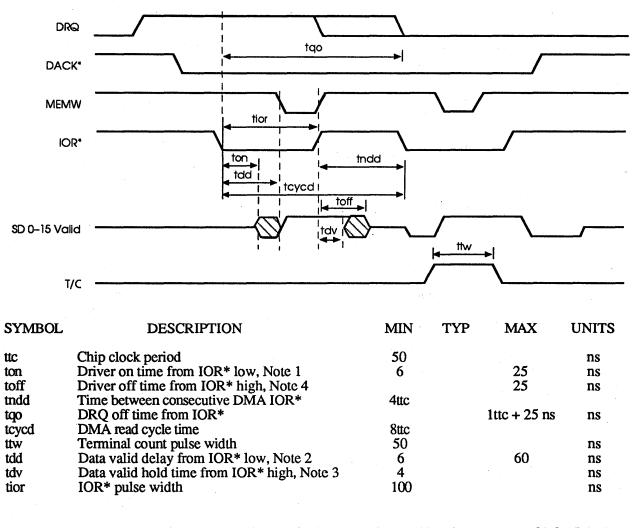

|     |       | 6.5.1 Arbitration/Selection                          |

|     |       | 6.5.2 SCSI Bus Free Detection                        |

|     |       | 6.5.3 SCSI PIO                                       |

|     |       | 6.5.4 SCSI Data Setup and Hold. Latched Data and PIO |

|     |       |                                                      |

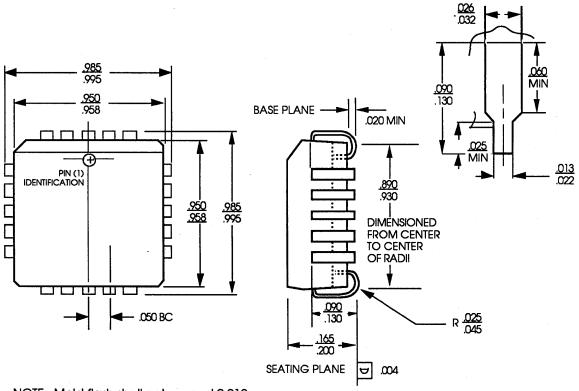

| 7.0 | Pack  | cage Outlines                                        |

|     | 7.1   | 68-Pin PLCC                                          |

|     | 7.2   | 80-Pin Quad Flatpack                                 |

| Ap  | pendi | ix A: Data Transfer Rate Calculations                |

| T   |       | Burst Rate A-1                                       |

|     | A.2   | PIO Transfer Rate Calculation A-2                    |

|     | A.3   | PIO Transfer Rate Examples                           |

|     |       | 1                                                    |

| Ap  | pend  | ix B: Example PIO Transfer Loop                      |

| Ap  | pendi | x C: PC AT DMA Setup C-1                             |

| Ap  | pendi | x D: PC AT InterruptD-1                              |

| -   |       | Interrupt InitializationD-1                          |

|     | D.2   | Interrupt Response                                   |

# **Table of Contents**

# List of Figures

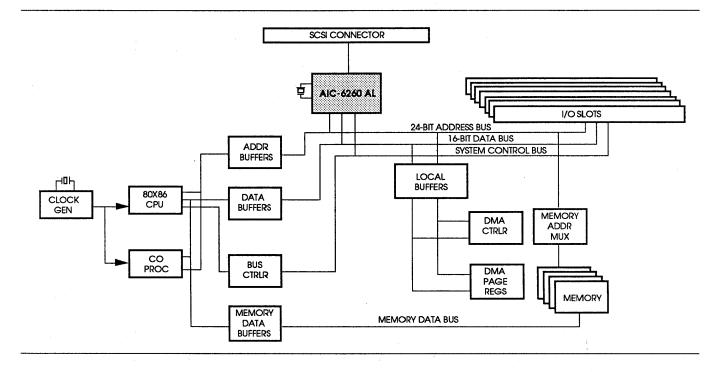

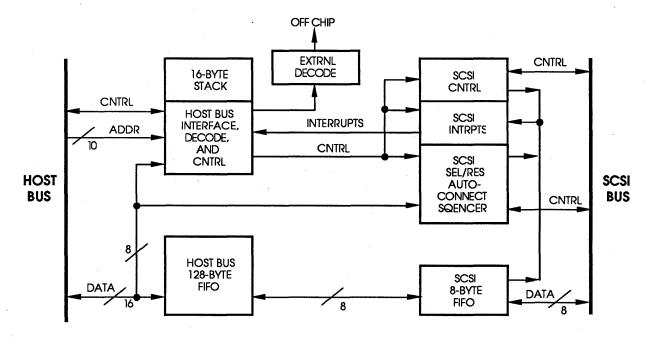

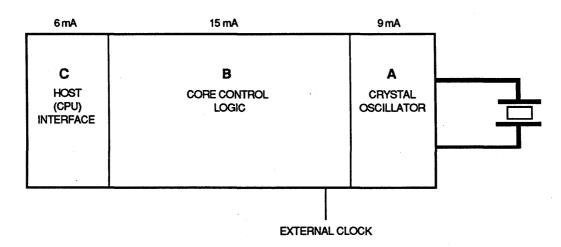

| 1-1 | AIC-6260 Functional Block Diagram   |  |

|-----|-------------------------------------|--|

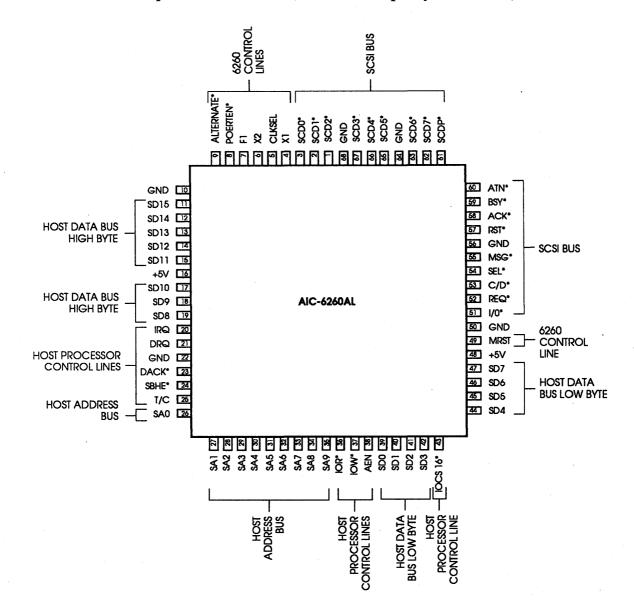

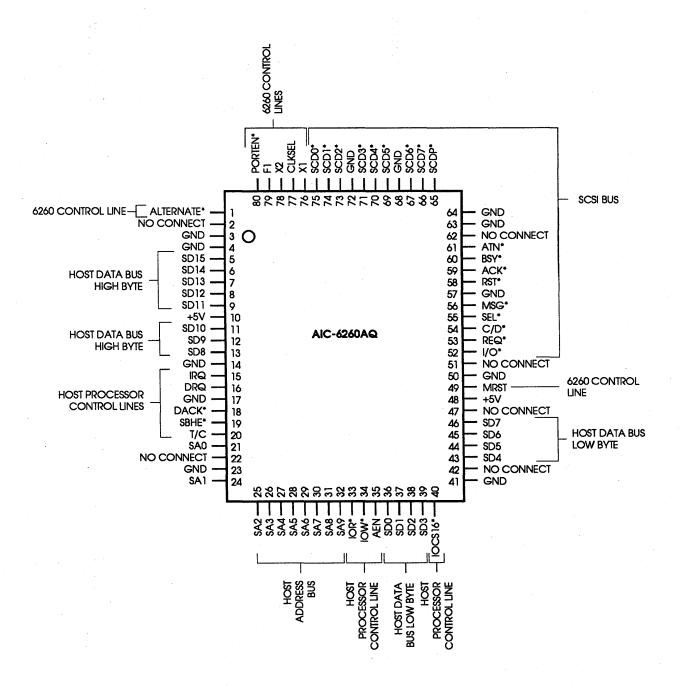

| 2-1 | AIC-6260 Pin Locations              |  |

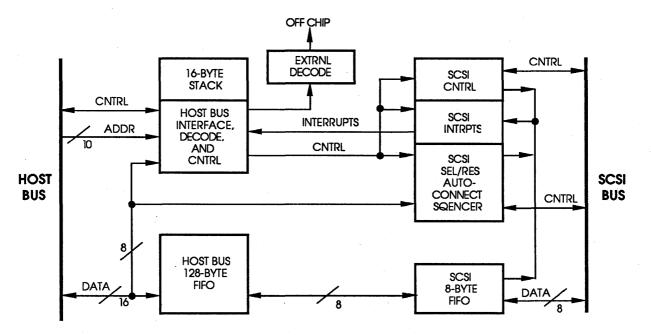

| 4-1 | AIC-6260 Simplified Block Diagram   |  |

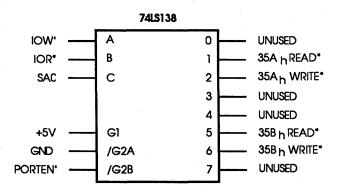

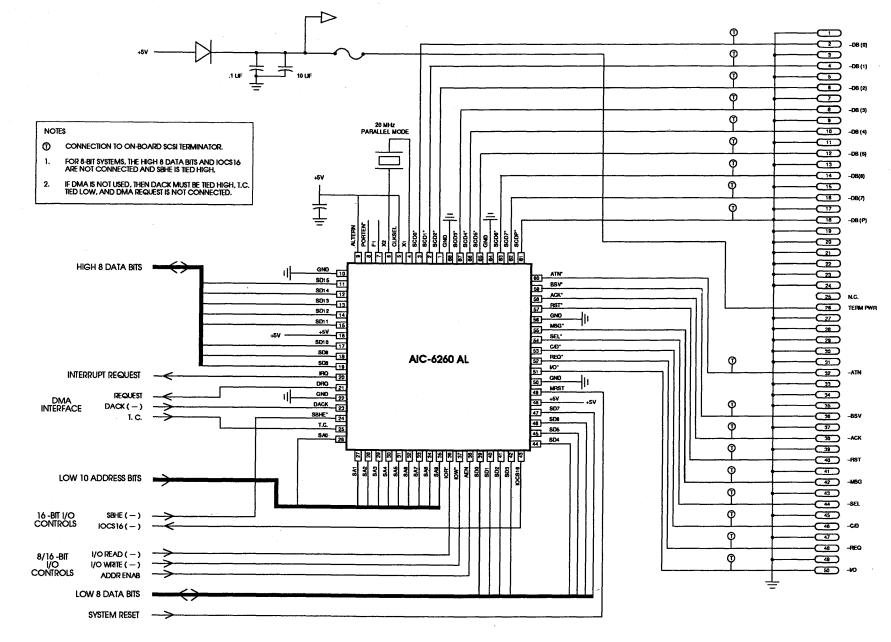

| 4-2 | Typical External Logic Circuit      |  |

| 5-1 | Sample AIC-6260 Application Drawing |  |

# List of Tables

| 2-1 | AIC-6260 Pin Descriptions                                        | 2-2  |

|-----|------------------------------------------------------------------|------|

| 3-1 | AIC-6260 Register Address Map                                    |      |

| 3-2 | STIMESEL Values                                                  |      |

| 3-3 | SXFR Codes                                                       |      |

| 3-4 | STCTEST Transfer Count Read Register (bits 0-5). To Select Abort |      |

|     | Counter Reassignments                                            | 3-23 |

| 3-5 | SCSIBLK TESTR Pin Redefinitions                                  |      |

| 3-6 | DMABLK TESTR Pin Redefinitions                                   | 3-39 |

| 4-1 | Interrupts                                                       |      |

# Section One

The AIC-6260 is a single-chip SCSI solution for PC AT and microprocessor-controlled peripherals applications. The AIC-6260 provides all of the functionality necessary to implement a multiple-unit SCSI in one 68-pin PLCC or 80-pin QFP package. Typical applications include laptops, portables, and low-end desktop computers.

The AIC-6260 is a single-chip PC AT bus to SCSI bus controller, designed to bring the power and connectivity of SCSI to the computer system motherboard.

The power of SCSI is demonstrated by a sustained data transfer capability of up to 4 megabytes per second. SCSI bus connectivity gives the system the ability to hook up to any of the growing number of SCSI compatible peripherals available, from hard drives to high–capacity floppy drives, tape drives, CD-ROM, DAT and removable drives.

Embedding the AIC-6260 increases reliability, reduces cost and eliminates the need for a traditional host adapter card. This makes the chip an ideal I/O solution for both desktop and laptop systems.

The AIC-6260 supports second party DMA transfers or programmed I/O. The chip contains a 128byte data buffer to increase PIO performance. Synchronous or Asynchronous SCSI transfer is supported. A built-in "sleep" mode saves power.

Adaptec cuts the system designer's job in half by supporting the AIC-6260 with a full complement of SCSI driver software.

The ASW-1210 is a multitasking ASPI (Advanced SCSI Programming Interface) manager for DOS, and contains features such as Disconnect/Reconnect on the SCSI bus. This frees the host CPU while peripherals execute time-consuming functions such as Seeks. Up to eight simultaneous I/O tasks can be run in the background, and the driver also allows interrupts from the host CPU. Automatic Request Sense can be done in the event of a "Check Condition" status from a SCSI target LUN. This ensures that valuable status data is not lost.

Configuration Options are programmable and can be set by software during system power up. No need for jumpers!

Configurable options are:

- Enable/Disable Disconnect

- AT Bus ON/OFF Time

- Selection Time Out

- Parity Checking Disable

- DMÅ/PIO

- SCSI ID

- Synchronous Negotiation

BIOS code is available to allow booting from the SCSI hard drive and to emulate DOS hard disk calls.

Compatibility is assured by support of the ANSI Common Command Set and SCSI-2.

FIGURE 1-1. AIC-6260 FUNCTIONAL BLOCK DIAGRAM

#### 2.1 PIN DESCRIPTIONS

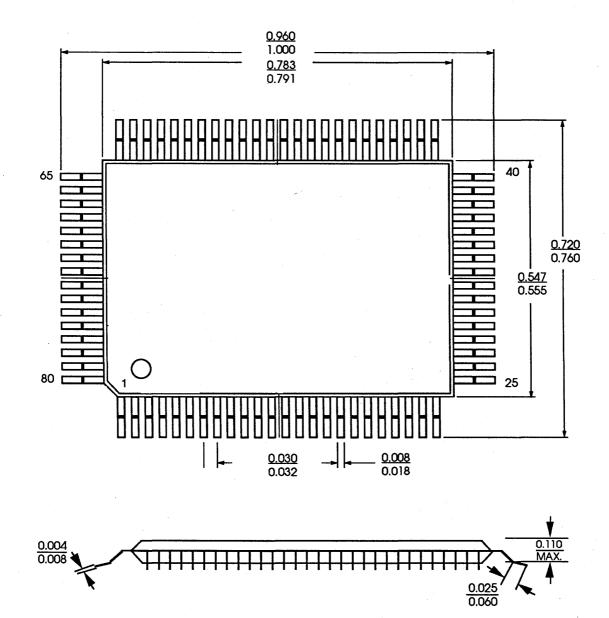

The AIC-6260 is available in a 68-pin PLCC or 80-pin Quad Flat Pack. Figure 2-1 shows the 68-pin PLCC pinout while Figure 2-2 shows the 80-pin QFP. Table 2-1 defines the pin assignments for the AIC-6260.

All SCSI lines utilize open collector drivers (IOL=48mA, input hysteresis=.2V).

FIGURE 2-1. AIC-6260AL 68-PIN PLCC LOCATIONS

# Section Two

FIGURE 2-2. AIC-6260AQ 80-PIN QUAD FLAT PACK LOCATIONS

AIC-6260

# TABLE 2-1.AIC-6260 PIN DESCRIPTIONS

| SYMBOL     | 6260AL<br>PIN NO. | 6260AQ<br>PIN NÕ. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                              |

|------------|-------------------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAO-SA9    | 26-35             | 21,<br>24-32      | I    | System Address Lines. A 10-bit bus used to load addresses into the AIC-6260 from the host. Chip addresses are decoded at $340_h$ with ALTERNATE* tied high, and at $140_h$ with ALTERNATE* tied low.                                                                                                     |

| AEN        | 38                | 35                | Ι    | Address Enable. A control signal used to indicate the type of transfer taking place across the Host bus. This signal is low for I/O access and high for DMA transfers.                                                                                                                                   |

| ALTERNATE* | 9                 | 1                 | I    | Alternate I/O Address Decode. When tied high, chip addresses are decoded from $340_h$ . When tied low, chip addresses are decoded from $140_h$ .                                                                                                                                                         |

| SD0–SD7    | 39–42<br>44–47    | 36-39<br>43-46    | I/O  | System Data Lines, Low-Order Byte. An 8-bit data bus used to transfer data between the host and the AIC-6260. Data transfers include register values and data. The host data bus utilizes tri-state drivers (IOH = $-8mA$ , IOL= 24mA).                                                                  |

| SD8–SD15   | 17–19<br>11–15    | 5-9,<br>11-13     | I/O  | System Data Lines, High-Order Byte. An 8-bit data bus used to transfer data between the host and the AIC-6260 in 16-bit mode. The host data bus utilizes tri-state drivers (IOH = $-8mA$ , IOL= 24mA).                                                                                                   |

| DRQ        | 21                | 16                | Ο    | DMA Request. A data transfer control signal used to indicate that the AIC-6260 has data to send or is ready to receive data. This signal forms half of the DMA handshake. It is valid for DMA mode transfers only. DRQ utilizes a two-state driver (IOH = $-8mA$ , IOL= 24mA).                           |

| DACK*      | 23                | 18                | Ī    | DMA Acknowledge. A data transfer control signal used to indicate<br>that the host is ready for a DMA transfer. This signal forms half of<br>the DMA handshake. It is valid for DMA mode transfers only.                                                                                                  |

| IRQ        | 20                | 15                | 0    | Interrupt Request. A control signal used to indicate the occurrence<br>of a condition requiring host intervention. This is the signal used<br>for all SCSI interrupts. Only interrupts which have been enabled<br>can assert this signal. IRQ utilizes a two-state driver (IOH = $-8mA$ ,<br>IOL= 24mA). |

| IOR*       | 36                | 33                | I    | I/O Read. A control signal used to indicate direction of data transfer across the Host bus. When asserted (active low), indicates data is being read out of the AIC-6260.                                                                                                                                |

| IOW*       | 37                | 34                | I    | I/O Write. A control signal used to indicate direction of data transfer across the Host bus. When asserted (active low), indicates data is being written into the AIC-6260.                                                                                                                              |

| Section 7 | Гwo                        | •                        |     | Pin Information                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------|--------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T/C       | 25                         | 20                       | I   | Terminal Count. A control signal used to indicate the completion<br>of a DMA transfer. This signal is driven by the host DMA<br>controller.                                                                                                                                                                                                                  |

| SBHE*     | 24                         | 19                       | I   | System Bus High Enable. This signal indicates that data on the SD8–SD15 lines is valid.                                                                                                                                                                                                                                                                      |

| IOCS16*   | 43                         | 40                       | 0   | I/O Chip Select 16. This signal is driven low when the current I/O data transfer is 16 bits (one word) wide. Open collector driver, IOL = $24 \text{ mA}$ .                                                                                                                                                                                                  |

| MRST      | 49                         | 49                       | I   | Master Reset. A control signal is used to restore the AIC-6260 to its start-up condition. This signal is active high at power up or hard reset. This signal has hysteresis for noise immunity. $(1.5V < Vth + <2.0V; .6V < Vth - <1.1V; Vth + - Vth - = .4V)$                                                                                                |

| SCD0-7*   | 1–3<br>62,<br>63,<br>65–67 | 66,67<br>69-71,<br>73-75 | I/O | SCSI Data Bus. An 8-bit data bus used to transfer data between the AIC-6260 and devices on the SCSI Bus. Data transfers include SCSI commands, Status, Messages and user data. Open collector driver, $IOL = 48mA$ , input hysteresis .2V.                                                                                                                   |

| SCDP*     | 61                         | 65                       | I/O | SCSI Data Parity. A control signal used to check for data transfer<br>errors on the SCSI bus. This signal with SCSI data always<br>generates odd parity when the AIC-6260 is driving the SCSI Bus.<br>This signal is tested when the AIC-6260 is receiving and parity<br>checking is enabled. Open collector driver, $IOL = 48mA$ , input<br>hysteresis .2V. |

| RST*      | 57                         | 58                       | I/O | SCSI Reset. A control signal used to restore devices attached to the SCSI bus to their start-up condition. This signal is driven under programmed control. When detected, RST* may cause the assertion of IRQ. Open collector driver, IOL = $48$ mA, input hysteresis .2V.                                                                                   |

| ATN*      | 60                         | 61                       | I/O | SCSI Attention. A control signal used to indicate that an initiator wishes to send a Message out to a Target. ATN* is driven when the AIC-6260 is in initiator mode and detected when the AIC-6260 is in target mode. Open collector driver, $IOL = 48mA$ , input hysteresis .2V.                                                                            |

| BSY*      | 59                         | 60                       | I/O | SCSI Busy. A control signal used for bus arbitration and device selection on the SCSI bus. Open collector driver, $IOL = 48 \text{ mA}$ , input hysteresis .2V.                                                                                                                                                                                              |

| SEL*      | 54                         | 55                       | I/O | SCSI Select. A control signal used for device selection on the SCSI Bus. Open collector driver, $IOL = 48mA$ , input hysteresis .2V.                                                                                                                                                                                                                         |

| C/D*      | 53                         | 54                       | I/O | SCSI Command/Data. A control signal driven by the target to indicate the type of transfer taking place across the SCSI bus (SCD0-7). C/D* is driven when the AIC-6260 is in target mode and detected when it is in initiator mode. Open collector driver, IOL = $48$ mA, input hysteresis .2V.                                                               |

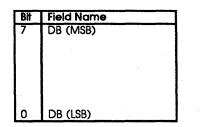

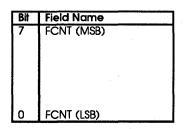

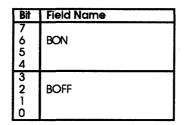

# Section Two