# 2,7 RLL Encoder/Decoder

- Supports 2,7 RLLencoding which provides up to 50% increased bit density

- Full NRZ to/from 2,7 RLL encode and decode

- 2.5 MHz To 10 MHz bit rates

- address mark detection

- Supports soft-sectored drives without special address mark logic

- Minimum passive support components

- Minimum board space requirements

- Two selectable VFO sync patterns

- Two selectable address mark options

- Single +5V power supply

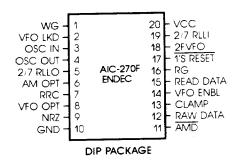

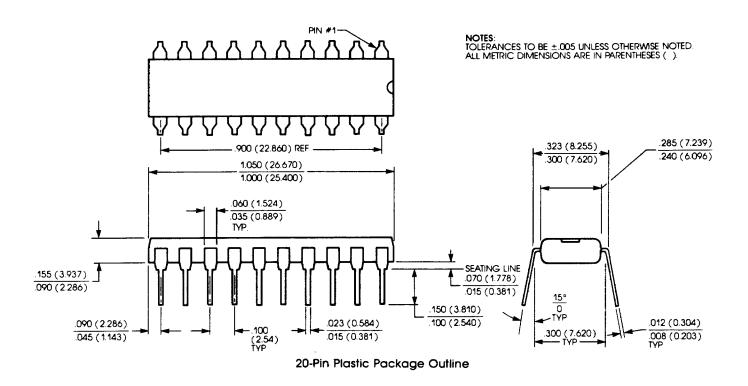

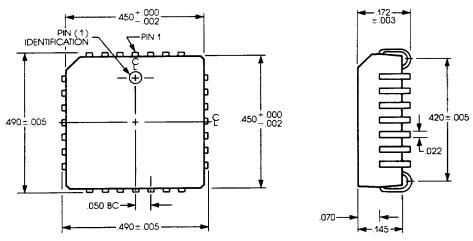

- 20-pin dual-in-line or 28-pin surface mount package

<sup>©</sup> Copyright 1982, 1987 Adaptec, Inc. All rights reserved. The information contained in this data sheet is subject to change without notice. No part of this document may be copied or reproduced in any form without prior written consent from Adaptec, Inc.

Section One Overview

The Adaptec AIC-270F Encode/Decode Chip is a 20-pin custom CMOS LSI device which provides an efficient data interface between NRZ data and 2,7 Run-Length Limited (RLL) recorded disk drives with a minimum of external support. The AIC-270F can be used as part of Adaptec's Winchester controller chip set, or can reside on the disk drive and provide increased capacity with an NRZ output to a controller as in ESDI.

This chip performs all of the functions necessary to convert NRZ data to and from 2,7 RLL data. An external variable frequency oscillator (VFO) is also necessary to provide synchronous clock and data. The AIC-270F also incorporates address mark generation and detection logic. This feature includes VFO sync field circuitry which enables the VFO data lock-on and performs address mark search and detection.

This ENDEC (Encode/Decode) device also includes the ability to generate selectable VFO sync field patterns and address marks ahead of the outgoing 2,7 RLL data stream.

The AIC-270F is designed to operate at bit rates from 2.5 MHz to 10MHz.

TABLE 1. PIN DESCRIPTION

| Symbol   | Pin   | Туре   | Name and Function                                                                                                                                                                                                                 |  |

|----------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WG       | 1-2   | IN     | WRITE GATE: An input which is used to gate the write data stream to the drive interface.                                                                                                                                          |  |

| VFO LKD  | 2-3   | OUT    | VFO LOCKED: An output generated by the preamble detect section after a count of 64 2,7 RLLI (pin 19) pulses have been reached since the last 1's RESET (pin 17).                                                                  |  |

| -OSC IN  | 3-6   | IN     | OSCILLATOR INPUT.                                                                                                                                                                                                                 |  |

| +OSC OUT | 4-7   | OUT    | OSCILLATOR OUTPUT.                                                                                                                                                                                                                |  |

| 2,7 RLLO | 5-8   | OUT    | 2,7 RLL OUT: This is 2,7 output data generated by the chip.                                                                                                                                                                       |  |

| AM OPT   | 6-9   | IN     | AM OPTION: A control input that selects one of two different address mark patterns used by both the encoder and the decoder.                                                                                                      |  |

| RCC      | 7-10  | OUT    | READ REFERENCE CLOCK: An output to the Winchester controller which is sourced from the VFO oscillator during Read Gate active; otherwise sourced from the write oscillator. RRC frequency is one-half that of OSC IN or 2FVFO IN. |  |

| VFO OPT  | 8-13  | IN     | VFO SYNC OPTION: A control signal that selects one of two different VFO sync field patterns used during encoding.                                                                                                                 |  |

| NRZ      | 9-14  | IN/OUT | NRZ READ/WRITE DATA: Non-return to zero data input to, or output from, the AIC-270F. This pin is an output when RG is active, and an input at all other times.                                                                    |  |

| GND      | 10-15 |        | GROUND.                                                                                                                                                                                                                           |  |

| AMD      | 11-16 | OUT    | ADDRESS MARK DETECT: When read gate is active, a latch is set when an address mark has been detected. An external 2K pull-up resistor must be used to pull this signal high when RG is false.                                     |  |

| RAW DATA | 12-17 | OUT    | RAW DATA: The raw data stream to be output to the external VFO. Source for this output is OSC IN if VFO ENABLED is low. When VFO ENABLED is high, the source is READ DATA.                                                        |  |

| CLAMP    | 13-20 | OUT    | CLAMP: An output generated by the preamble detect section whenever the state of VFO ENABLED changes.                                                                                                                              |  |

| VFO ENBL | 14-21 | OUT    | VFO ENABLED: An output generated by the preamble detect section after a count of 16 2,7 RLLI pulses have been reached without a 1's RESET occurring.                                                                              |  |

| Symbol           | Pin   | Туре | Name and Function                                                                                              |  |

|------------------|-------|------|----------------------------------------------------------------------------------------------------------------|--|

| READ DATA        | 15-22 | IN   | READ DATA: An input which signals the phase-lock-loop to lock onto the read data stream coming from the drive. |  |

| RG               | 16-23 | IN   | READ GATE: An input which signals the phase-lock-loop to lock onto the read data stream coming from the drive. |  |

| 1'S RESET        | 17-24 | IN   | 1'S RESET: A pulse input to the preamble detect section that resets the counter.                               |  |

| 2FVFO            | 18-27 | IN   | 2FVFO: This is a fundamental VFO input from the external data/clock standardizer.                              |  |

| 2,7 RLLI         | 19-28 | IN   | 2,7 RLL IN: This provides the 2,7 code to be converted to NRZ data.                                            |  |

| V <sub>C</sub> C | 20-1  |      | +5 Volts                                                                                                       |  |

AIC-270F

adaptec

#### 3.1 Functional Description

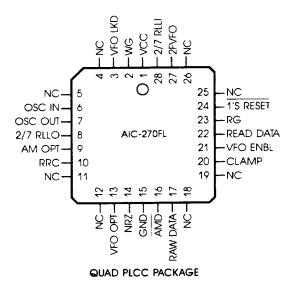

The AIC-270F Encode/Decode Chip has three major areas of logic:

Data Encode Circuitry

Sync Field Search Circuitry and Counter

Address Mark Detect and Data Decode Circuitry

The functional block diagram is shown in Figure 1. The data encode circuitry is used during a disk write operation (NRZ to 2,7 RLL conversion) and the sync field search circuitry, address mark detect, and data decode circuitry are used during a disk read operation (2,7 RLL to NRZ conversion).

#### 3.2 Figure 1 - Functional Block Diagram

#### 3.3 Write Operation

During a write operation, the AIC-270F chip converts NRZ format data to 2,7 RLL format. In addition to this, during a format operation, the chip also automatically generates one of two possible VFO sync fields (preamble patterns). The VFO sync field is generated between the time write gate goes high and the first low-to-high transition on the NRZ line. The two possible patterns are:

1. 100100100...(VFO sync = 0), or 2. 100010001000...(VFO sync = 1),

selectable by the VFO sync option pin. On the first low-to-high NRZ transition, the device stops sending the preamble pattern and then generates an address mark.

There are two possible address marks used which are selectable by an external pin (AM option). The first option (AM option = 1), uses a 5EA x H pattern that satisfies the 2,7 constraints, but never occurs during a normal encoding sequence. Use of this feature provides zero probability of erroneous syncing, say, in the middle of a data field. The second option (AM option = 0), uses a FFH pattern for syncing. This option requires some additional external mechanism to prevent false syncing, such as a D.C. erased area on the disk.

#### 3.4 Read Disk Operation

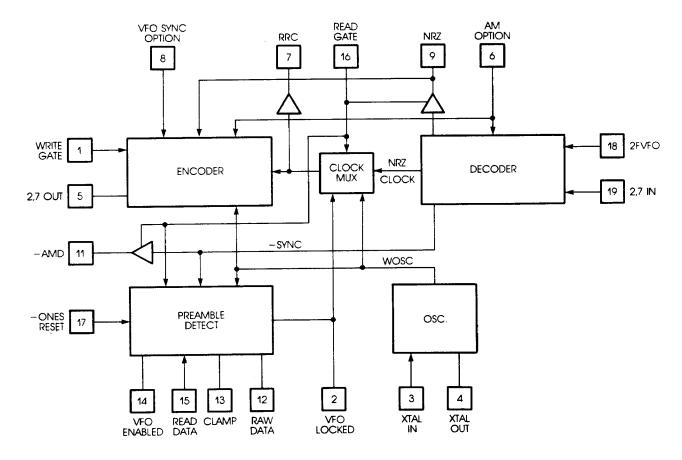

During a read operation, the AIC-270F chip works in conjunction with external VFO circuitry, such as the AIC-6225, to convert 2,7 RLL data to NRZ data. The VFO circuitry can also be referred to as a data standardizer. A block overview of the data standardizer is shown in Figure 2.

The two signals that interface to the VFO are "RAW DATA" and "CLAMP." The raw data input to the VFO is the signal that the VFO is required to track. When "READ GATE" is off, the raw data output of the AIC-270F is "2FOSC." The purpose is simply to provide an input to the VFO that will keep the VFO pumped to nominal disk data rates.

When "READ GATE" is turned on, a sequence of events must occur for a successful transition from "2FOSC" feeding the VFO to "READ DATA" feeding the VFO. The sequence is as follows:

- 1. After RG is turned on, the counter must count 16 2,7 RLLI transitions in a row. Any time a greater than expected space between bit transitions is detected externally, a "ONE'S RESET" input will occur to restart the counter. The "ONE'S RESET" input will be a minimum of 40ns in width and is typically implemented with a retriggerable one shot of 2.5 x bit cell duration for the 100100100...preamble and a 3.5 x bit cell duration for the 10001000100...preamble. This is done to ensure that the VFO is enabled only when reading the VFO sync field. A "ONE'S RESET" implies that the pattern being observed on the drive is not the VFO sync field.

- 2. When count 16 is reached, a latch is set that will switch the "RAW DATA" source from "2FOSC" to "READ DATA" and generate a "CLAMP" output. The "CLAMP" signal is guaranteed to be at least two data periods in length and its trailing edge will follow the "RAW DATA" output by not more than 20ns or precede it by no more than 10ns. The "CLAMP" signal is used by the VFO circuit to minimize the phase error between "READ DATA" and "2FVFO." The "VFO ENABLE" signal is asserted at this time.

- 3. With "READ DATA" feeding the VFO, the counter will continue for 48 more 2,7 RLLI counts to a maximum of 64. During this period, if a "ONE'S RESET" occurs, the counter will be reset, a "CLAMP" signal will occur, and the "RAW DATA" source will be switched back to "2FOSC." If "ONE'S RESET" does not occur, a latch will be set that allows for the detection of an address mark and disallows any further "ONE'S RESET" from affecting the counter. This latch will also switch the "RD/REF CLOCK" output source from the divided "2FOSC" to "1FVFO." There are no timing constraints for this switch to occur and a glitch will be output on the RD/REF clock at this point. The "VFO LOCKED" signal is asserted at this time.

- 4. The counter continues to run while the AM detector is looking for an address mark. If the counter reaches count 128 without an AM detected, the count 16 latch will be reset, causing a "CLAMP" signal to be generated and a "2FOSC" to be output to the VFO. Also, the search AM latch will be reset, disabling the AM detector and switching the source for the "RD/REF CLOCK" output. The VFO will be input with "2FOSC" for four byte times and the sequence will begin again at Step 1. If an address mark is found, the "AMD" latch will be set and its output will appear on the "AMD" pin. The "AMD" latch being set will disable any further contributions to the sequence by the counter, allowing the data field to be read.

- 5. "RG" may be turned off at any time, resetting the counter and causing a "CLAMP" signal to be generated and the "RAW DATA" source changed to "2FOSC."

NOTE: The device has additional outputs, such as VFO ENABLE (count 16) and VFO LOCKED.

Figure 2 - VFO Block Overview

adaptec

### 4.1 Absolute Maximum Ratings

| Ambient Temperature Under Bias            | 0°C to 70°C              |

|-------------------------------------------|--------------------------|

| Storage Temperature                       | 65°C to 150°C            |

| Voltage on Any Pin with Respect to Ground | $-0.3$ to $V_{cc} + 0.3$ |

| Power Dissipation.                        | 0.25 watt                |

| Power Supply Voltage                      | 4.75 to 5.25 volts       |

Note: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 4.2 D.C. Characteristics

| Symbol          | Parameter                                                                           | Min                   | Мах                   | Units | Conditions             |

|-----------------|-------------------------------------------------------------------------------------|-----------------------|-----------------------|-------|------------------------|

| V <sub>IL</sub> | Input Low Voltage (NRZ,RG,<br>WG,2FVFO,-1'S RESET,READ<br>DATA,AM OPT and VFO OPT)  | -0.3                  | 0.8                   | V     |                        |

| $v_{IL}$        | Input Low Voltage (OSC)                                                             |                       | 0.2 x V <sub>CC</sub> | V     |                        |

| $V_{IL}$        | Input High Voltage (NRZ,RG,<br>WG,2FVFO,-1'S RESET,READ<br>DATA,AM OPT and VFO OPT) | 2.0                   | V <sub>CC</sub> + 0.3 | V     |                        |

| $v_{IH}$        | Input High Voltage (OSC)                                                            | 0.8 x V <sub>CC</sub> |                       | V     |                        |

| VOL             | Output Low Voltage (NRZ,RRC, 2,7 OUT,RAW DATA,CLAMP, AMD,VFO LKD,VFO ENBL)          |                       | 0.4                   | V     | $I_{OL} = 4mA*$        |

| V <sub>OH</sub> | Output High Voltage (NRZ,RRC, 2,7 OUT,RAW DATA,CLAMP AMD,VFO LKD,VFO ENBL)          | 4.0                   |                       |       | $I_{OH} = -400  \mu A$ |

| $I_{CC}$        | Supply Current                                                                      |                       | 50                    | mA    |                        |

| $C_{IN}$        | Input Capacitance                                                                   | 10                    |                       | pF    |                        |

| COUT            | Output Capacitance                                                                  | 50                    |                       | pF    |                        |

AIC-270F

## 4.3 A.C. Timing Characteristics.

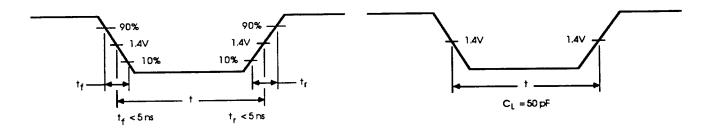

## 4.3.1 AIC-270F Output Timing

| Symbol | Parameter             | Min | Мах | Units |

|--------|-----------------------|-----|-----|-------|

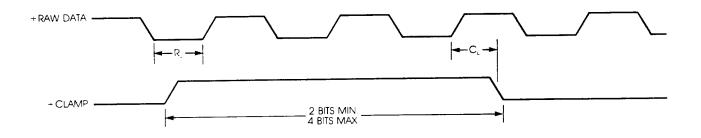

| $R_L$  | Raw Data Active Low   | 20  |     | ns    |

| $C_L$  | Raw Data ↑ to Clamp ↓ |     | 20  | ns    |

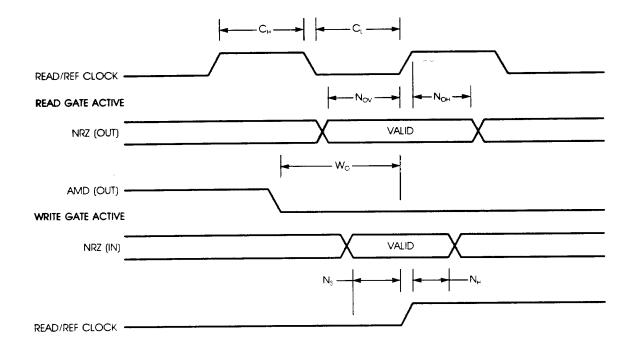

## 4.3.2AIC-270F Bi-Directional Timing

| Symbol          | Parameter                   | Min | Мах | Units |

|-----------------|-----------------------------|-----|-----|-------|

| C <sub>H</sub>  | Read/Ref Clock High         | 40  |     | ns    |

| $C_L$           | Read/Ref Clock Low          | 40  |     | ns    |

| Ns              | NRZ in Setup to Read/Ref ↑  | 25  |     | ns    |

| N <sub>H</sub>  | Read/Ref ↑ to NRZ in Hold   | 15  |     | ns    |

| Nov             | NRZ Out Valid to Read/Ref ↑ | 30  |     | ns    |

| $W_{O}$         | Read/Ref ↑ to WAM Out Valid | 30  |     | ns    |

| N <sub>OH</sub> | NRZ Out Hold                | 20  |     | ns    |

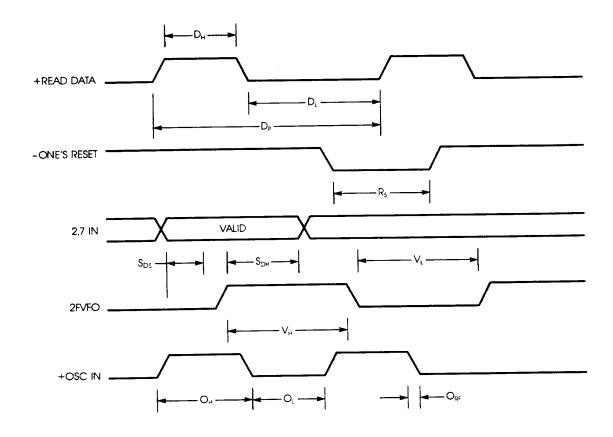

## 4.3.3 AIC-270F Input Timing

| Symbol                     | Parameter                 | Min | Max  | Units |

|----------------------------|---------------------------|-----|------|-------|

| $\mathcal{O}_{\mathrm{H}}$ | Read Data High            | 20  |      | ns    |

|                            | Read Data Low             | 100 |      | ns    |

| ) <u>L</u><br>) p          | Read Data Period          | 140 | 4000 | ns    |

| S                          | One's Reset Low           | 20  |      | ns    |

| 'H                         | 2FVFO High                | 16  |      | ns    |

| n<br>'t                    | 2FVFO Low                 | 16  |      | ns    |

| L<br>DS                    | Std Data Setup to 2FVFO ↑ | 15  |      | ns    |

| DS<br>DH                   | Std Data Hold             | 10  |      | ns    |

| рн<br>Н                    | OSC in High               | 16  |      | ns    |

| 'H<br>h                    | OSC in Low                | 16  |      | ns    |

| L<br>PRF                   | OSC in Rise or Fall       |     | 5    | ns    |

28-Lead Plastic Surface Mount Package