# Data Book

AIC-7890A/7891, Rev. C PCI Bus Master Ultra2 SCSI Host Adapter Chip Stock Number: 511683-00, Rev B. 8/98

Adaptec, Inc. 691 South Milpitas Boulevard Milpitas, CA 95035

© 1998, Adaptec, Inc. All rights reserved. Adaptec and the Adaptec logo are registered trademarks of Adaptec, Inc.

Printed in Singapore STOCK NO: 511683-00, Rev B. SG 8/98

# ••••• Adaptec AIC-7890A/7891 PCI Bus Master Ultra2 SCSI Host Adapter Chip

**Data Book**

Stock Number: 511683-00, Rev. B 8/98

# **Gadaptec**

#### Copyright

© 1998 Adaptec, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of Adaptec, Inc., 691 South Milpitas Blvd., Milpitas, CA 95035.

#### Trademarks

Adaptec, the Adaptec logo, AIC, ARO, FLEXPort, RAID Option, and SCSISelect are trademarks of Adaptec, Inc. which may be registered in some jurisdictions.

Windows and Windows 95 are registered trademarks and Windows NT is a trademark of Microsoft Corporation in the U.S. and other countries used under license.

All other trademarks are owned by their respective owners.

#### Changes

The material in this document is for information only and is subject to change without notice. While reasonable efforts have been made in the preparation of this document to assure its accuracy, Adaptec, Inc. assumes no liability resulting from errors or omissions in this document, or from the use of the information contained herein.

Adaptec reserves the right to make changes in the product design without reservation and without notification to its users

# •••• Contents

# 1 Introduction

Feature Summary 1-2 PCI Interface 1-2 SCSI Interface 1-3 Sequencer 1-4 Command Channel 1-4 Data FIFO 1-4 Sequencer Control Block / FlexPort 1-4 AIC-7890A/7891 Block Diagram 1-5

# 2 Pin Description

Pin Signal Summary 2-1 PCI Host Interface Pins 2-2 SCSI Interface Pins 2-3 FlexPort (Memory) Interface Pins 2-4 Clock and Miscellaneous Pins 2-4 Test Pins 2-5 Power and Ground Pins 2-5 Spare Pins 2-6 Pin Signal Description 2-7 PCI Host Interface Pins 2-7 SCSI Interface Pins 2-20 FlexPort (Memory) Interface Pins 2-23 Clock and Miscellaneous Pins 2-30 Test Pins 2-32 Power and Ground Pins 2-33 Spare Pins 2-33

## **3** Functional Description

PCI Interface 3-2 PCI Signals 3-2 PCI Protocol 3-3 Configuration 3-3 Data Transfer 3-3 PCI Bus Commands 3-3 Scatter/Gather Operation with / without Preload 3-8

Queue Offset Registers for SCB Delivery and Done SCB Queue Management 3-9 PCI Big Endian Support 3-9 PCI Power Management 3-11 Error Reporting and Interrupt Handling 3-12 SCSI Interrupts 3-12 Command Complete Interrupts 3-12 Breakpoint Interrupts 3-12 Software Interrupt 3-12 Interrupt Summary 3-13 SCSI Interface 3-13 Manual Mode Data Transfer 3-13 Automatic Mode Data Transfer 3-13 Normal (DMA) Mode Data Transfer 3-14 Differential/Single Ended Support 3-14 SCSI Interrupts 3-15 SCSI Reset 3-18 SCAM Support 3-18 SCSI Performance Monitor Register Set 3-18 Writing to the Scatter/Gather SRAM via Command Channel DMA Operation 3-18 Writing to the SCB Array via Command Channel DMA Operation 3-19 Reading from the SCB Array via Command Channel DMA **Operation 3-20** FLEXPort Interface 3-20 FLEXPort Not Used 3-21 FLEXPort Stand-alone Operation 3-21 FLEXPort Shared Operation 3-21 SEEPROM/Board Control Logic Operation 3-22 **FLEXPort External Arbitration 3-23** SCB Array 3-23 Arbitration Protocol 3-24 Sequencer 3-24 Loading 3-24 Pause 3-25 Breakpoint 3-25 Single Step 3-25 Reset 3-25 Restart 3-25 Indirect Jump 3-25 Hardware Failure Detect 3-26

511683-00, Rev. B 8/17/98

# 4 Register Description

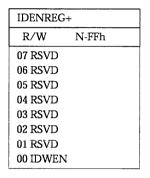

**Register Summary 4-1** PCI Configuration Registers 4-1 Device Registers in the Functional Mode (ALT\_MODE = 0) 4-6Device Registers in the Alternate Mode (ALT\_MODE = 1) 4-15**Register Definitions 4-19** PCI Configuration Registers 4-20 Vendor Identification (VENDOR ID) 4-20 Device Identification (DEVICE ID) 4-21 Command (COMMAND) 4-22 Status (STATUS) 4-24 Device Revision ID (DEVREV\_ID) 4-27 Programming Interface (PROGINFC) 4-27 Sub Class (SUBCLASS) 4-28 Base Class (BASECLASS) 4-28 Cache Line Size (CACHESIZE) 4-29 Latency Timer (LAT TIME) 4-30 Header Type (HDRTYPE) 4-31 Built-In-Self-Test (BIST) 4-32 Base Address 0 (BASEADR0) 4-33 Base Address 1 (BASEADR1) 4-34 Subsystem Vendor ID, Subsystem ID (SUBVENDOR\_ID, SUBSYSTEM\_ID) 4-36 Expansion ROM Base Address (EXROMBADR) 4-38 Capability Pointer (CAP\_PTR) 4-40 Interrupt Line Select (INTLINSEL) 4-41 Interrupt Pin Select (INTPINSEL) 4-42 Min\_Gnt Status (MINGNT) 4-43 Max\_Lat Status (MAXLAT) 4-44 Device Configuration (DEVCONFIG) 4-45 Device Status 0 (DEVSTATUS0) 4-47 Device Status 1 (DEVSTATUS1) 4-49 PCI Error Generation (PCIERRGEN) 4-50 Capability Identifier (CAPABILITY\_ID) 4-51 Next Item Pointer (NEXT\_ITEM\_PTR) 4-52 Power Management Capabilities (PM\_CAPABILITY) 4-53 Power Management Control Status Register (PM\_CSR) 4-54 PMCSR Bridge Support Extension (PMCSR\_BSE) 4-55 PM Data Register (PM\_DATA) 4-56 ID Enable Register (IDENREG) 4-57 Device Registers in the Functional Mode (ALT\_MODE = 0) 4-58

SCSI Sequence Control (SCSISEO) 4-58 SCSI Transfer Control 0 (SXFRCTL0) 4-60 SCSI Transfer Control 1 (SXFRCTL1) 4-62 SCSI Control Signal In (SCSISIGI) 4-64 SCSI Control Signal Out (SCSISIGO) 4-65 SCSI Rate (SCSIRATE) 4-66 SCSI Maximum Offset (SCSIOFFSET) 4-68 SCSI Latched Data (SCSIDATH, SCSIDATL) 4-69 SCSI Transfer Count (STCNT[2:0]) 4-70 Clear SCSI Interrupt 0 (CLRSINT0) 4-71 SCSI Status 0 (SSTAT0) 4-72 Clear SCSI Interrupt 1 (CLRSINT1) 4-74 SCSI Status 1 (SSTAT1) 4-75 SCSI Status 2 (SSTAT2) 4-77 SCSI Status 3 (SSTAT3) 4-78 SCSI ID (SCSIID) 4-79 SCSI Interrupt Mode 0 (SIMODE0) 4-80 SCSI Interrupt Mode 1 (SIMODE1) 4-81 SCSI Data Bus (SCSIBUSH, SCSIBUSL) 4-82 Shadow Host Address (SHADDR[7:0]) 4-83 Target ID In (TARGIDIN) 4-84 Selection/Reselection ID (SELID) 4-85 SCAM Control (SCAMCTL) 4-86 SCAM Status (SCAMSTAT) 4-88 Target ID High/Low (TARGIDH, TARGIDL) 4-89 Board Control (BRDCTL) 4-90 Serial EEPROM Control (SEECTL) 4-91 SCSI Block Control (SBLKCTL) 4-94 Sequencer Control (SEQCTL) 4-97 Sequencer RAM Data (SEQRAM) 4-99 Sequencer RAM Address (SEQADDR[1:0]) 4-100 Accumulator (ACCUM) 4-101 Source Index Register (SINDEX) 4-102 Destination Index Register (DINDEX) 4-103 Break Address 0 (BRKADDR0) 4-104 Break Address 1 (BRKADDR1) 4-105 All Ones (ALLONES) 4-105 All Zeros (ALLZEROS) 4-106 No Destination (NONE) 4-106 Flags (FLAGS) 4-106 Source Index Indirect (SINDIR) 4-107

Destination Index Indirect (DINDIR) 4-107 Function One (FUNCTIONONE) 4-108 Stack (STACK) 4-109 Device Space Command 0 (DSCOMMAND0) 4-110 Device Space Command 1 (DSCOMMAND1) 4-112 Host/Sequencer Mailbox (HS MAILBOX) 4-113 Host Control (HCNTRL) 4-114 Data Channel Low Host Address (HADDR[3:0]) 4-116 Data Channel High Host Address (HADDR[7:4]) 4-117 Data Channel Host Count (HCNT[2:0]) 4-118 SCB Pointer (SCBPTR) 4-119 Interrupt Status (INTSTAT) 4-120 Clear Interrupt (CLRINT) 4-123 Error (ERROR) 4-124 Data FIFO Control (DFCNTRL) 4-126 Data FIFO Status (DFSTATUS) 4-128 Data FIFO Write Address (DFWADDR) 4-130 Data FIFO Read Address (DFRADDR) 4-131 Data FIFO Data (DFDAT) 4-132 SCB Counter (SCBCNT) 4-133 Special Function (SFUNCT) 4-134 Command Channel Low Host Address (CCHADDR[3:0]) 4-135 Command Channel High Host Address (CCHADDR[7:4]) 4-136 Command Channel Host Count (CCHCNT) 4-137 Command Channel S/G RAM Data Port (CCSGRAM) 4-138 Command Channel S/G RAM Address Pointer (CCSGADR) 4-139 Command Channel S/G Control (CCSGCTL) 4-140 Command Channel SCB RAM Data Port (CCSCBRAM) 4-142 Command Channel SCB RAM Address Pointer (CCSCBADR) 4-143 Command Channel SCB Control (CCSCBCTL) 4-144 Command Channel SCB Count (CCSCBCNT) 4-146 Command Channel SCB Base Address (SCBBADDR) 4-147 Command Channel SCB Pointer (CCSCBPTR) 4-147 Host New SCB Queue Offset (HNSCB QOFF) 4-148 Sequencer New SCB Queue Offset (SNSCB QOFF) 4-148 Sequencer Done SCB Queue Offset (SDSCB QOFF) 4-149 Queue Offset Control & Status (QOFF\_CTLSTA) 4-150 Data FIFO Threshold (DFF\_THRSH) 4-151 SG Cache Pointer (SG\_CACHEPTR) 4-154 Device Registers in the Alternate Mode (ALT\_MODE = 1) 4-155Bus Free Counter (BUSFREE[3:0]) 4-155

Bus BSY Counter (BUSBSY[3:0]) 4-155 Frequency Synthesizer Control 0 (FROSYNCTL0) 4-156 Frequency Synthesizer Control 1 (FROSYNCTL1) 4-157 SCSI Test Control (SCSITEST) 4-158 SCSI Transfer Control 2 (SXFRCTL2) 4-160 SCSI IOCell Powerdown Control (IOPDNCTL) 4-161 Sequencer Debug Control Register (SEQDBCTL) 4-162 Special Function (SFUNCT) 4-163 PCI DMA Read/Write REO# GNT# Cvcle Count (PF\_REQGNTCYCCNT[3:0]) 4-164 PCI DMA-Read Burst Count (PFRD BURSTCNT[3:0]) 4-165 PCI DMA-Read Double Word Transfer Count (PFRD\_DWXFRCNT[3:0]) 4-166 PCI DMA Read REQ# Count (PFRD PREQCNT[3:0]) 4-167 PCI DMA-Read Maximum Burst Length (PFRD MAXBURSTLEN[1:0]) 4-168 PPCI DMA-Write Burst Count (PFWR\_BURSTCNT[3:0]) 4-169 PCI DMA-Write Double Word Transfer Count (PFWR\_DWXFRCNT[3:0]) 4-170 PCI DMA Write REQ# Count (PFWR\_PREQCNT[3:0]) 4-171 PCI DMA-Write Maximum Burst Length (PFWR MAXBURSTLEN[1:0]) 4-172 Performance Register Monitoring Control (PF\_CNTRL) 4-173 Data FIFO Pointer (DFPTRS) 4-174 Data FIFO Backup Pointer (DFBKPTR0) 4-175 Data FIFO Backup Read Pointer (DFBKPTR) 4-175 Data FIFO Debug Control (DFDBCTL) 4-176 Data FIFO Space Count (DFSCNT0) 4-177 Data FIFO Space Count (DFSCNT1) 4-177 Data FIFO Byte Count (DFBCNT0) 4-178 Data FIFO Byte Count (DFBCNT1) 4-178 Command Channel SCB RAM Back-Up Address Pointer (CCSCBADR\_BK) 4-179

# 5 Pin Assignment

AIC-7890A Pinouts 5-2 AIC-7891 Pinouts 5-13

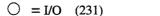

# 6 Electrical Information

Absolute Maximum Ratings 6-1 Operating/Test Conditions 6-1 DC Parameters 6-2 PCI 6-2 SCSI (Single Ended) 6-3 SCSI Support Pins 6-4 Memory Port 6-4 Other Pins 6-5 Signal Test Loads 6-5 AC Parameters 6-6 PCI Pin V/I Curves 6-6 Clock Timing 6-13 PCI Bus Timing 6-14 Memory Port Timing 6-18

# 7 System Cycles

PCI Master Bus Cycles 7-1 PCI Slave Bus Cycles 7-6

# •••• Figures

## Figure

| 1-1         | AIC-7890A/7891 Chip Package 1-1                          |

|-------------|----------------------------------------------------------|

| 1 <b>-2</b> | AIC-7890A/7891 Block Diagram 1-5                         |

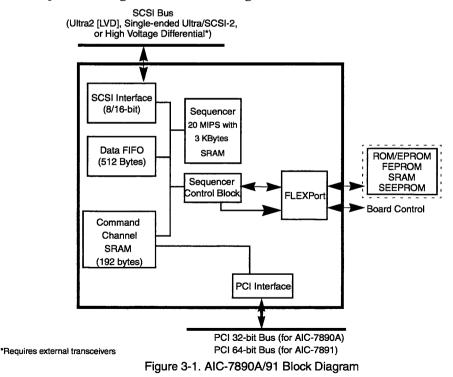

| 3-1         | AIC-7890A/91 Block Diagram 3-1                           |

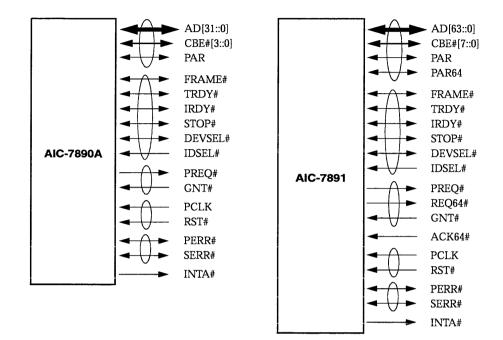

| 3-2         | PCI Interface 3-3                                        |

| 3-3         | Arbitration Protocol 3-24                                |

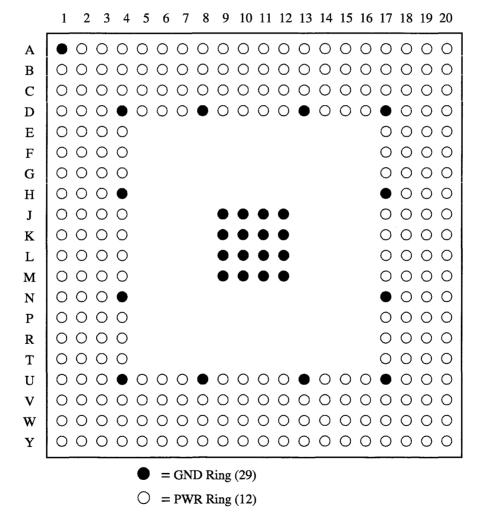

| 5-1         | Top View of 272-PIN BGA (Ball Grid Array) 5-1            |

| 6-1         | A.C. Input Conditions 6-1                                |

| 6-2         | A.C. Output Conditions 6-1                               |

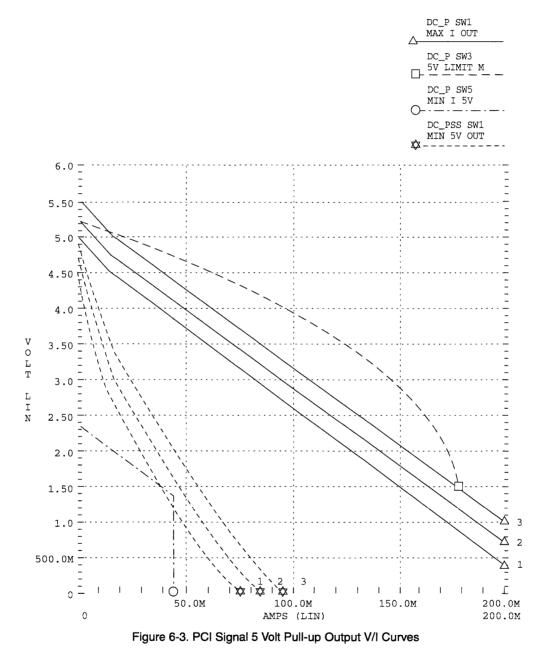

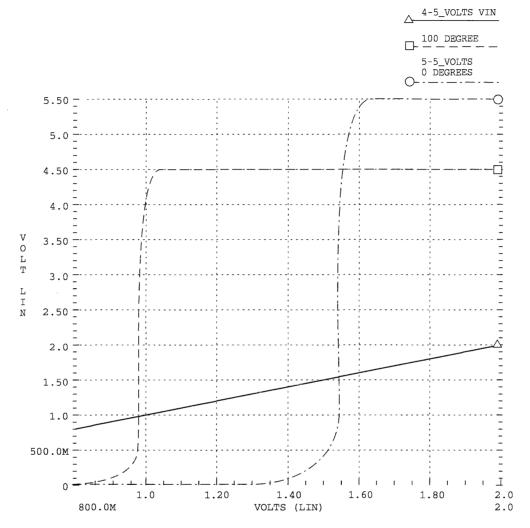

| 6-3         | PCI Signal 5 Volt Pull-up Output V/I Curves 6-6          |

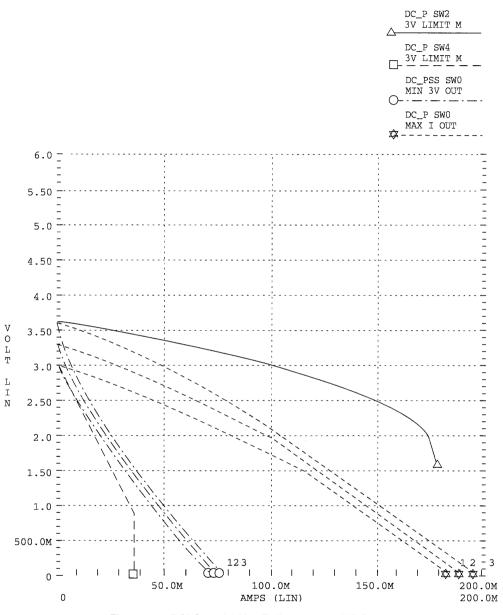

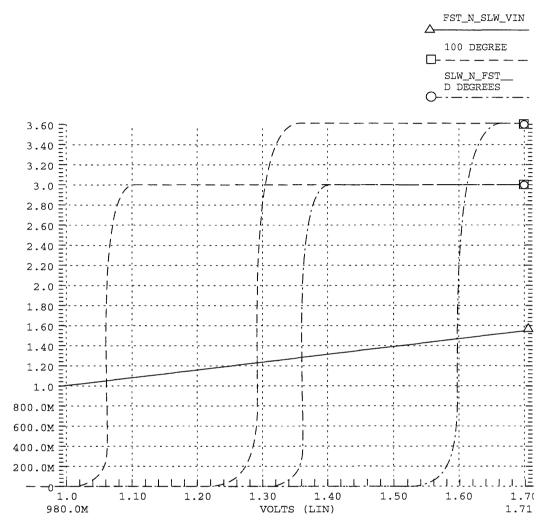

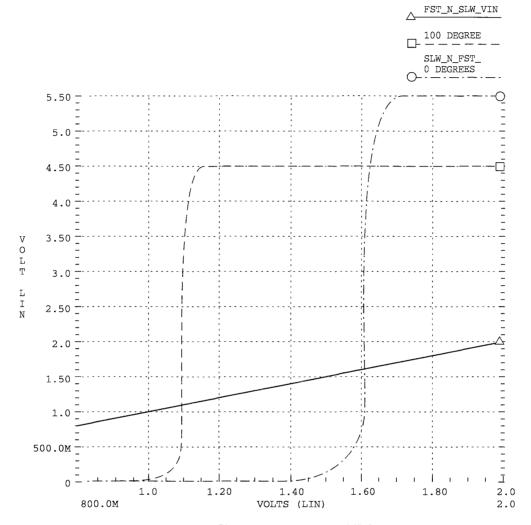

| 6-4         | PCI Signal 3 Volt Pull-up Output V/I Curves 6-7          |

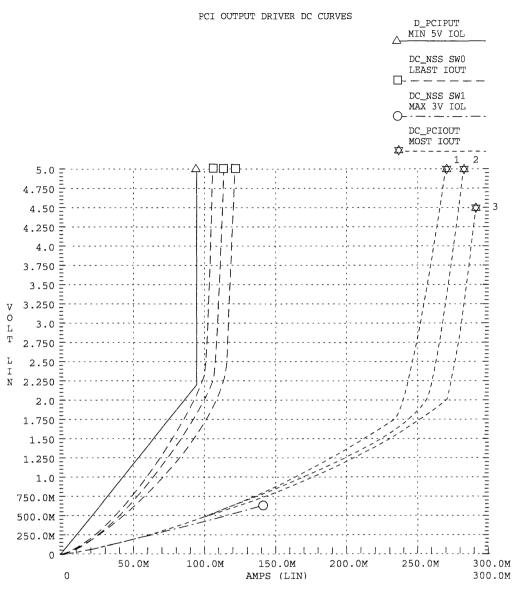

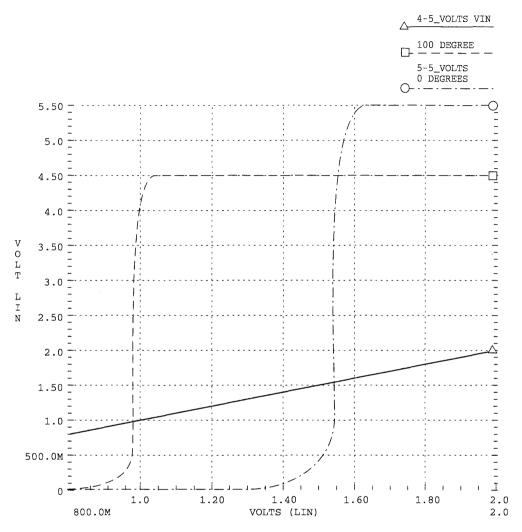

| <b>6-</b> 5 | PCI Signal 3 Volt/5 Volt Pull-down Output V/I Curves 6-8 |

| 6-6         | PCI Signal 5 Volt Input V/I Curves 6-9                   |

| 6-7         | PCI Signal 3 Volt Input V/I Curves 6-10                  |

| 6-8         | PCI Signal 3 Volt/5 Volt Input V/I Curves 6-11           |

| 6-9         | PCI Signal PCI Clock 5 Volt Input V/I Curves 6-12        |

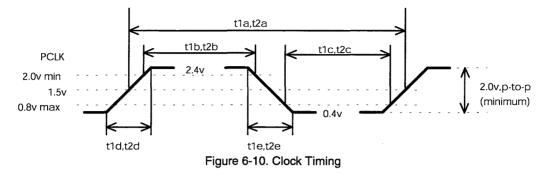

| 6-10        | Clock Timing 6-13                                        |

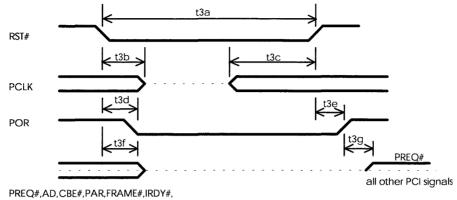

| 6-11        | Reset Timing 6-14                                        |

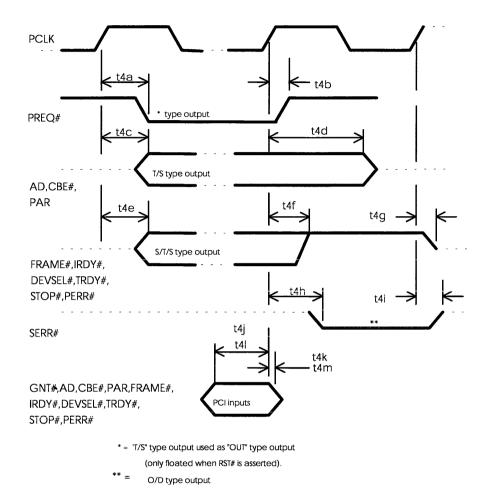

| 6-12        | PCI Signal Input Output Timing 6-15                      |

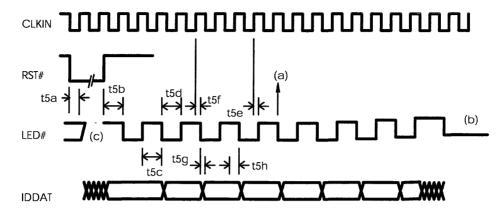

| 6-13        | PCI Device Identification Value Replacement Timing 6-17  |

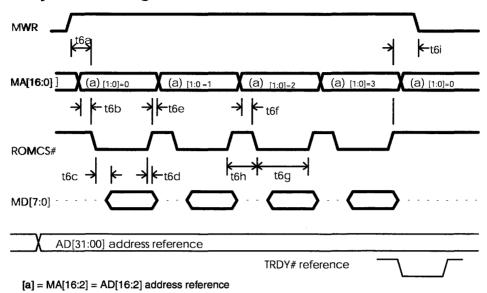

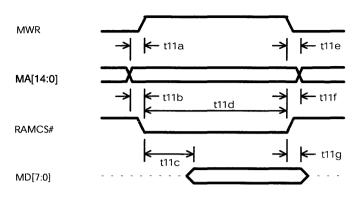

| 6-14        | PCI ROM/EEPROM Read Memory Port Timing 6-18              |

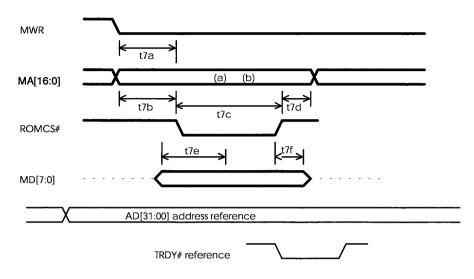

| 6-15        | PCI EEPROM Write Memory Port Timing 6-19                 |

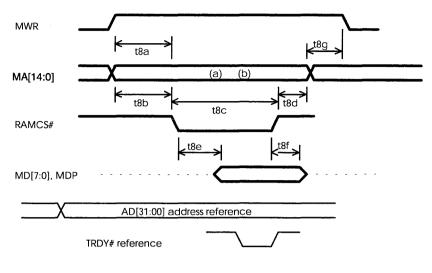

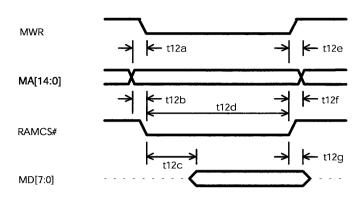

| 6-16        | PCI SRAM Read Memory Port Timing 6-20                    |

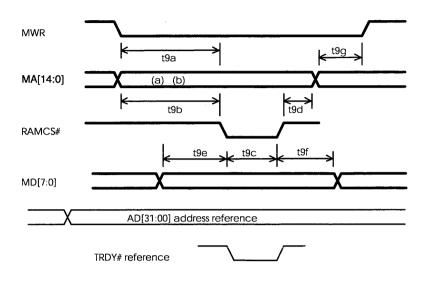

| 6-17        | PCI SRAM Write Memory Port Timing 6-21                   |

| 6-18        | Sequencer Read Memory Port Timing 6-22                   |

| 6-19        | Sequencer Write Memory Port Timing 6-23                  |

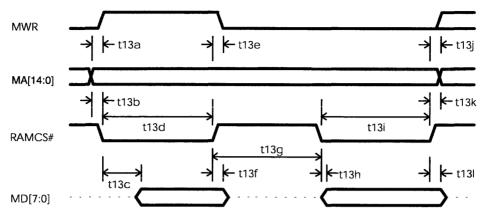

| 6-20        | Sequencer Read-Modify-Write Memory Port Timing 6-24      |

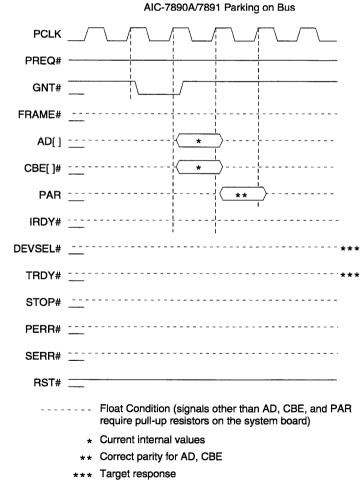

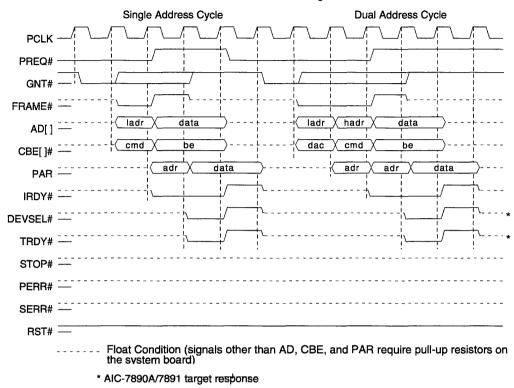

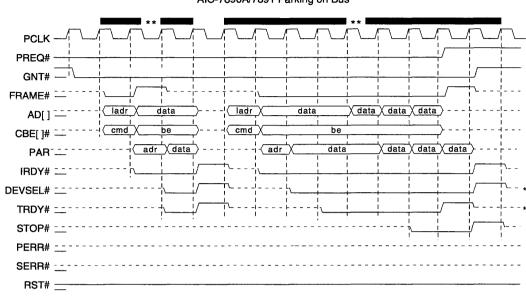

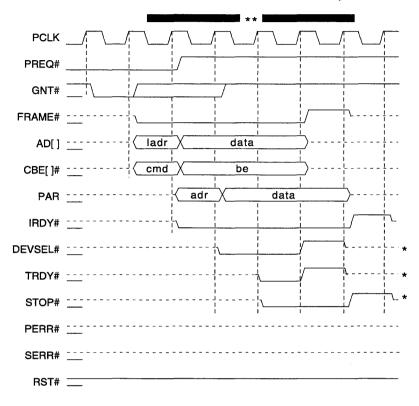

| 7-1         | Master Parking on Bus 7-1                                |

| 7-2         | Master Single Transfer Write 7-2                         |

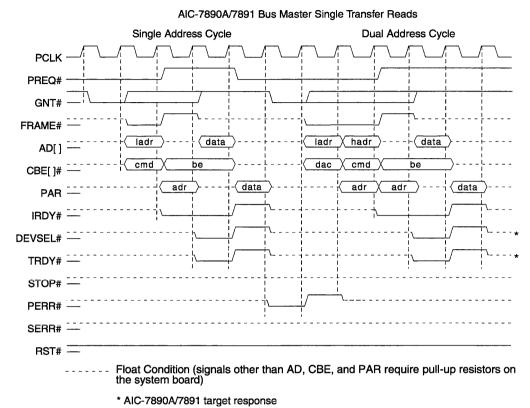

| 7-3         | Master Single Transfer Read 7-3                          |

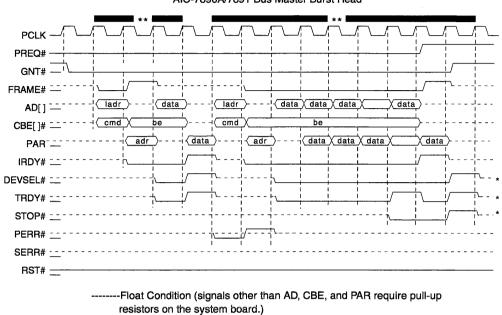

| 7-4         | Master Burst Transfer Write 7-4                          |

#### Figure

- 7-5 Master Burst Transfer Read 7-5

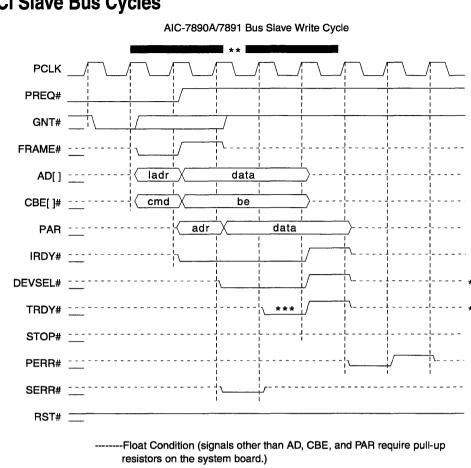

- **7-6** Slave Single Transfer Write 7-6

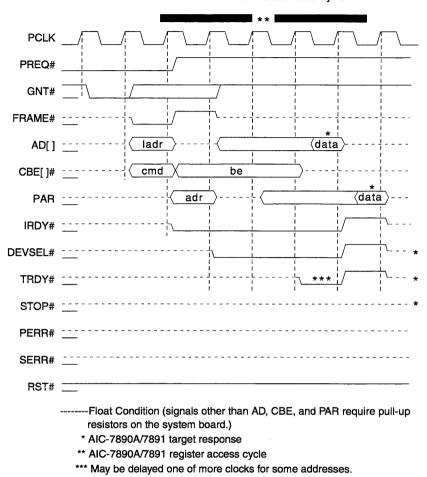

- **7-7** Slave Single Transfer Read 7-7

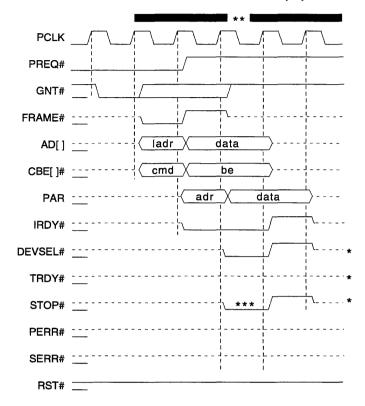

- **7-8** Slave Retry 7-8

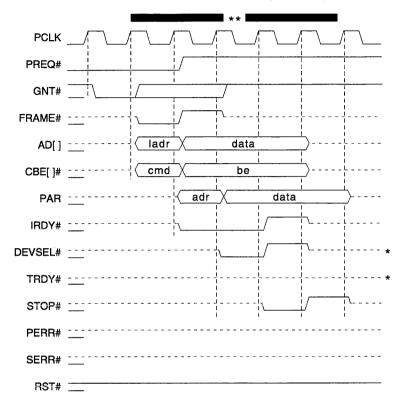

- 7-9 Slave Target Abort (width error) 7-9

- 7-10 Slave Burst Disconnect 7-10

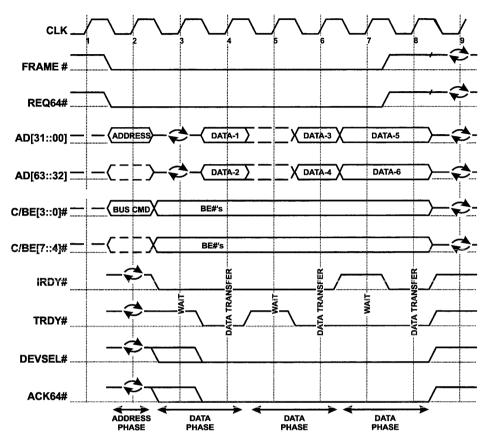

- 7-11 64-Bit Read Request with 64-Bit Transfer (AIC-7891 only) 7-11

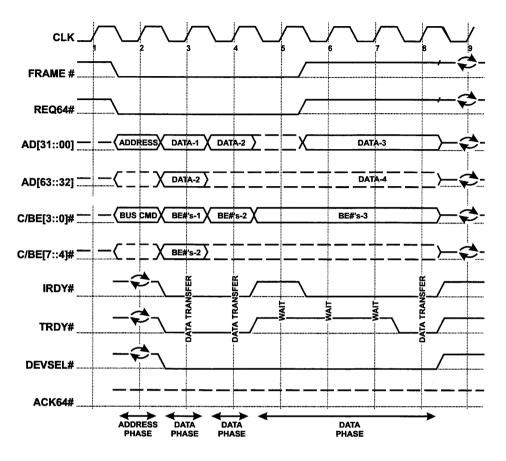

- 7-12 64-Bit Write Request with 32-Bit Transfer (AIC-7891 only) 7-12

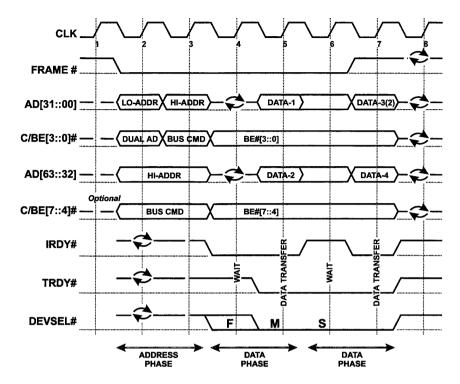

- 7-13 64-Bit Dual Address Read Cycle (AIC-7891 only) 7-13

# •••• Tables

## Table

| • •                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-1                                                                              | Pin Type Definitions 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2-2                                                                              | PCI Host Interface Pins 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2-3                                                                              | SCSI Interface Pins 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2-4                                                                              | FlexPort (Memory) Interface Pins 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2-5                                                                              | Clock and Miscellaneous Pins 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2-6                                                                              | Test Pins 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2-7                                                                              | Power and Ground Pins 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2-8                                                                              | Spare Pins 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2-9                                                                              | PCI Host interface Pins 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2-10                                                                             | SCSI Interface Pins 2-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2-11                                                                             | FlexPort (Memory) Interface Pins 2-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2-12                                                                             | Clock and Miscellaneous Pins 2-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2-13                                                                             | Test Pins 2-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2-14                                                                             | Power and Ground Pins 2-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2-15                                                                             | Spare Pins 2-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3-1                                                                              | Effects of D0 to D3hot Transition 3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3-1<br>3-2                                                                       | Effects of D0 to D3hot Transition 3-11<br>Effects of D3hot to D0 Transition 3-11                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3-2                                                                              | Effects of D3hot to D0 Transition 3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3-2<br>3-3                                                                       | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3-2<br>3-3<br>3-4                                                                | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3-2<br>3-3<br>3-4<br>3-5                                                         | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6                                                  | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22                                                                                                                                                                                                                                                                                                                                                                   |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7                                           | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22                                                                                                                                                                                                                                                                                                                                 |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8                                    | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22<br>SEECTL Support Functions 3-23                                                                                                                                                                                                                                                                                                |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>4-1                             | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22<br>SEECTL Support Functions 3-23<br>CACHETHEN = 0, Transfer from Data FIFO to System Memory 4-152<br>CACHETHEN = 0, Transfer from System Memory to Data FIFO 4-152                                                                                                                                                              |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>4-1<br>4-2                      | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22<br>SEECTL Support Functions 3-23<br>CACHETHEN = 0, Transfer from Data FIFO to System Memory 4-152                                                                                                                                                                                                                               |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>4-1<br>4-2<br>4-3               | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22<br>SEECTL Support Functions 3-23<br>CACHETHEN = 0, Transfer from Data FIFO to System Memory 4-152<br>CACHETHEN = 1, Transfer from Data FIFO to System Memory 4-153                                                                                                                                                              |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>4-1<br>4-2<br>4-3<br>4-4        | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22<br>SEECTL Support Functions 3-23<br>CACHETHEN = 0, Transfer from Data FIFO to System Memory 4-152<br>CACHETHEN = 0, Transfer from Data FIFO to System Memory 4-152<br>CACHETHEN = 1, Transfer from Data FIFO to System Memory 4-153<br>CACHETHEN = 1, Transfer from Data FIFO to System Memory 4-153                            |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1 | Effects of D3hot to D0 Transition 3-11<br>Interrupt Summary 3-13<br>SCSI Interrupts 3-16<br>FLEXPort Interface 3-21<br>BRDCTL Signal Correlation 3-22<br>SEECTL Signal Correlation 3-22<br>SEECTL Support Functions 3-23<br>CACHETHEN = 0, Transfer from Data FIFO to System Memory 4-152<br>CACHETHEN = 0, Transfer from System Memory to Data FIFO 4-152<br>CACHETHEN = 1, Transfer from Data FIFO to System Memory 4-153<br>CACHETHEN = 1, Transfer from System Memory to Data FIFO 4-153<br>AIC-7890A Left Side 5-2 |

| Table |                                                                  |

|-------|------------------------------------------------------------------|

| 5-4   | AIC-7890A Top Side 5-8                                           |

| 5-5   | I/O Ball Location Grids A1-7 through Y1-7 for AIC-7890A 5-10     |

| 5-6   | I/O Ball Location Grids A8-14 through Y8-14 for AIC-7890A 5-11   |

| 5-7   | I/O Ball Location Grids A15-20 through Y15-20 for AIC-7890A 5-12 |

|       |                                                                  |

- **5-8** AIC-7891 Left Side 5-13

- **5-9** AIC-7891 Bottom Side 5-15

- **5-10** AIC-7891 Right Side 5-17

- 5-11 AIC-7891 Top Side 5-19

- **5-12** I/O Ball Location Grids A1-7 through Y1-7 for AIC-7891 5-21

- 5-13 I/O Ball Location Grids A8-14 through Y8-14 for AIC-7891 5-22

- 5-14 I/O Ball Location Grids A15-20 through Y15-20 for AIC-7891 5-23

# ....1

# Introduction

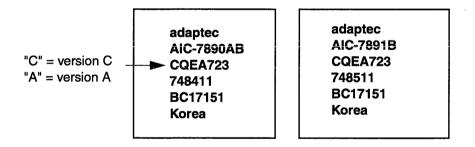

This *Data Book* documents the "C" version of the AIC-7890A and AIC-7891 single-chip host adapters. The AIC-7890A/7891 "C" version introduces several features and functions that were not available in earlier "A" version of the chip. The version level of the chip is indicated by the first character in the third line of the text on the chip package as shown in Figure 1-1.

Figure 1-1. AIC-7890A/7891 Chip Package

The new features of version "C" of the AIC-7890A/7891 chip are:

- Enhanced Microsoft PC98 compliance

- Support for changeable PCI IDs through software and hardware

The AIC-7890A and AIC-7891 provide advanced host adapter features in a single 272-pin Ball Grid Array (BGA) chip. The AIC-7890A provides an Ultra2 SCSI bus controller combined with a full-featured PCI 2.1-compliant 32-bit bus master capable of supporting zero wait state 32-bit memory data transfers at 133 MBytes/sec data burst rate. The AIC-7891 provides an Ultra2 SCSI bus controller combined with a full-featured PCI 2.1compliant 64-bit bus master capable of supporting zero wait state 64-bit at 267 MBytes/sec data burst rate. The PCI interface of the AIC-7891 can also function as a PCI 2.1-compliant 32-bit bus master with zero wait state 32-bit memory transfers at 133 MBytes/sec data burst rate. The AIC-7890A and AIC-7891 are identical devices with the exception of the 64-bit capability of the AIC-7891. Hereinafter they are referenced as the AIC-7890A/7891. The AIC-7890A/7891 Ultra2 SCSI controllers comply with SCSI-3 standard and are compatible with single ended (SE) or dual mode Low Voltage Differential (LVD) SCSI I/O. Support for external High Voltage Differential (HVD) transceivers is provided.

**Note:** This document describes the functionality and features of the "C" revision of the AIC-7890A and AIC-7891 chips.

The data channel DMA engine in the AIC-7890A/7891 supports data transfer rates up to 80 MBytes/sec on a wide (16-bit) SCSI bus using LVD SCSI I/Os. The AIC-7891's 64-bit PCI interface supports up to 267 MBytes/sec transfer rates. A 512-byte data FIFO is embedded in the AIC-7890A/7891 to buffer data between the PCI bus and Ultra2 SCSI bus. The 512 byte data FIFO allows more efficient utilization of both the PCI and SCSI bus by reducing the number of unnecessary wait states on the PCI bus or disconnects on the SCSI bus. The data FIFO can serve as a temporary storage for the sequencer.

Beside the data channel DMA engine, a dedicated command channel DMA engine in the AIC-7890A/7891 can be used to bring in SCSI commands described by Sequencer Control Blocks (SCBs) and the scatter/gather lists associated with each SCB. The SCB data structure and scatter/gather lists contain all the information needed for the execution of the command. This command channel can allow new commands to be brought into the chips while the data channel is executing the existing commands. The command channel provide a 128-byte buffer for the scatter/gather lists and a 64-byte buffer as a temporary SCB storage which allows more efficient utilization of the PCI bus.

The AIC-7890A/7891 provide an improved version of the internal RISC-based sequencer, which is capable of executing instructions at 20 MIPS. The sequencer executes SCBs to initiate data transfers between the PCI and SCSI interfaces. The AIC-7890A/7891 sequencer supports variable execution speeds of 10/20 MIPS and provides 768x32 bits of SRAM microcode storage.

In addition to the 64/32-bit PCI interface, Ultra 2 SCSI interface, 512-byte Data FIFO, command channel, and RISC based sequencer, the AIC-7890A/7891 provide 80 bytes of scratch SRAM, embedded storage for 16 SCBs, and a FLEX Port. The FLEX Port can be used to access external SRAM/ROM/FLASH EPROM/SEEPROM/external logic. The SCB array containing the 16 SCBs can be expanded to 256 SCBs with external SRAM accessed through the FLEX Port.

The components of the AIC-7890A/7891 combines to provide a full feature Ultra 2 SCSI host adapter with a 64-bit PCI interface on the AIC-7891 and a 32-bit on the AIC-7890A in a single 272-pin BGA chip which is compatible to current generation 32-bit PCI architecture and existing SCSI-2 and Ultra SCSI peripherals.

# **Feature Summary**

#### **PCI Interface**

- Supports programmable PCI configuration registers, Subsystem ID and Subvendor ID, through external pinor software (BIOS or BDK)

- Direct pin out connection to PCI 64/32-bit bus interfaces

- PCI 64-bit bus master with zero wait state 64-bit memory data transfers up to 267 MBytes/sec for AIC-7891

- PCI 32-bit bus master with zero wait state 32-bit memory data transfers up to 133 MBytes/sec for AIC-7890A

- PCI down-shift 64 to 32-bit bus master with zero wait state 32-bit memory data transfers up to 133 MBytes/sec for AIC-7891

- Supports both single and dual address cycle

- Supports PCLK frequencies from 0 to 33.3 MHz

- Supports programmable Latency Timer, Cache Size, and Interrupt Line Select registers

- Supports PCI Power Management

- PCI bus access of AIC-7891 or AIC-7890A device registers from both PCI I/O address space and PCI Memory address space

- Medium PCI target device-select response time, DAC cycles support for target

- Capable of streaming PCI enhanced memory data Read and Write commands as PCI bus master

- PCI bus address and data parity generation and checking

- Supports PCI PERR# and SERR# requirements

- Master data transfers are initiated by selected cacheline size and Data FIFO threshold

- PCI bus address phase and data phase error generation for checking system and device error support

- PCI configuration space register accessible through PCI I/O or Memory address space

- PCI target latency of 16 clocks maximum for first target access cycle (revision 2.1 support)

- Hardware PCI bus utilization monitor

- Supports external ROM system byte/word/dword read access and byte write access

#### SCSI Interface

- SCSI data transfers up to 40 Mega-transfers/sec.

- 8- or 16-bit SCSI data path

- SCAM level 2 support

- SCSI Offsets to 127 transfers

- Compatible with single ended or dual mode Low Voltage DIfferential (LVD) SCSI I/O

- Supports for external High Voltage Differential (HVD) transceivers

- Extensive hardware support for disconnect/reconnect and scatter/gather

- Full support for both initiator and target operations

- Multi target I.D. lets chip respond to multiple I.Ds as a SCSI target

- Hardware SCSI bus utilization monitor

#### Sequencer

- Variable execution speed of 10/20 MIPS RISC design

- Internal 3 KByte SRAM for microcode storage with parity protection and RAM Built-In-Self-Test (BIST) function

- Fifteen instruction group types

- Operation can be paused by the software driver

- Diagnostic instruction single-step and hardware address breakpoint

#### **Command Channel**

- Dedicate DMA engine to fetch SCBs from system memory and to post command done status to the system memory

- 128 bytes of internal RAM with parity protection for holding scatter/gather list elements for current command execution

- 64 bytes of internal RAM with parity protection for holding SCBs temporarily before moving to on or off chip SCB array SRAM

#### **Data FIFO**

- 512-byte data FIFO with BIST function

- Parity protection for each byte transferred

#### **Sequencer Control Block / FlexPort**

- 80 bytes of dual-ported scratch RAM with parity protection and BIST function

- Internal 1-KByte SCB array with parity protection and BIST function for storage of sixteen SCBs

- SCB array expandable to 256 SCBs with external 16-KByte SRAM

- Single ported 8- or 9-bit SRAM (20 ns access) with direct connection for 16 KBytes

- Single ported 8-bit ROM/EEPROM (150 ns access) with direct connection for 128 KBytes

- Serial SEEPROM with register based access with hardware timer support

- Multi-device arbitration (two wire) for sharing FLEXPort connected devices

- SRAM, ROM, EEPROM three line interface for read/write control

- SEEPROM four line interface

- External eight line interface for general read/write purpose

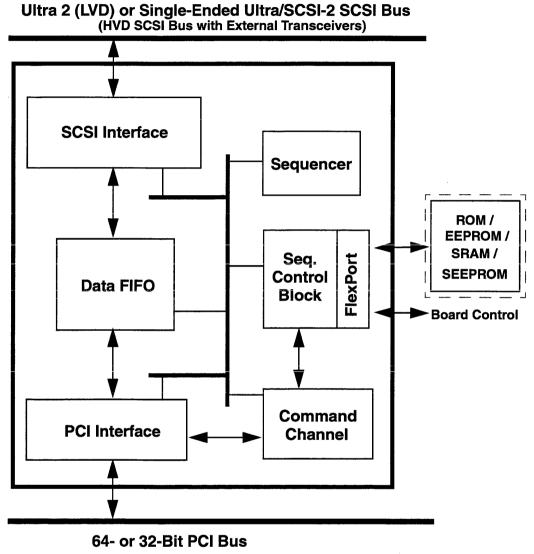

# AIC-7890A/7891 Block Diagram

Figure 1-2. AIC-7890A/7891 Block Diagram

.

.

# ....2

# Pin Description

# **Pin Signal Summary**

The pins are summarized here, listing the name, pin number, if the pin is an input, and the type and drive of the outputs. The type definitions are listed in Table 2-1.

| Туре             | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| analog-in        | Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| analog-out       | Analog output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Dual Mode<br>I/O | <b>Dual Mode LVD SCSI I/O Pins</b> . They are organized in pairs, two pins per SCSI signal. This pins act as either Low-Voltage-Differential (LVD) SCSI or Single Ended (SE) SCSI depending on the voltage on the DIFFSENSE input.                                                                                                                                                                                                                                                                                           |

| gnd              | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| in               | Input indicates that this pin has a standard input receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ts/#             | Three-state is an output signal with control enabled output driver. # is the min drive current in mA.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| sts/#            | <b>Sustained Three-state</b> is a bidirectional signal, active low three-state signal and driven by one, and only one agent at a time. The agent that drives an in-sts signal low must drive it high for at least one PCLK before letting it float. A new agent cannot start driving an in-s/t/s signal any sooner than one clock after the previous owner floats it. A pull-up sustains the inactive state until another agent drives it and is provided by the PCI bus central resource. # is the min drive current in mA. |

| od/#             | <b>Open Drain</b> is an open drain output. The system board provides a light pull-up for o/d signals. Multiple devices share the signal as a wire-OR. The signal is asserted synchronous with PCLK for one PCLK period. The signal deassertion period is determined by the RC time period provided by the pull-up. # is the min drive current in mA.                                                                                                                                                                         |

| pu               | <b>Pull-up</b> indicates that this pin has an internal pull-up resistor. The resistor is approximately 50 Kohms.                                                                                                                                                                                                                                                                                                                                                                                                             |

| pwr              | Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 2-1. Pin Type Definitions

#### PCI Host Interface Pins

| Signal Name        | Pin Number                                                                                                                                                    | PCI Master<br>I/O Driver Type | PCI Target<br>I/O Driver Type | Notes |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-------|

| ACK64#             | M1                                                                                                                                                            | in                            | in                            | 2     |

| AD[31 <b>:00</b> ] | T1, V2, U1, W2, V1, W3, W1, W4, Y2,<br>W6, Y3, W7, Y4, W8, Y6, W9, W14,<br>Y15, W15, Y16, W16, Y18, W17, Y19,<br>W20, W19, V20, V19, U20, U19, T20,<br>T19    | in-ts/6                       | in-ts/6                       |       |

| AD[ <b>63:32</b> ] | N3, V6, P4, V7, P3, V8, R3, V9, T4,<br>V10, T3, V11, U5, V12, U7, V13, U9,<br>V14, U11, V15, U12, V16, U14, V17,<br>U16, V18, T17, U18, R18, T18, P17,<br>R19 | in-ts/6                       | in-ts/6                       | 2     |

| CBE <b>[3:0]</b> # | Y1, Y8, Y14, W18                                                                                                                                              | in-ts/6                       | in-ts/6                       |       |

| CBE[ <b>7:4</b> ]# | V3, M4, V4, M3                                                                                                                                                | in-ts/6                       | in-ts/6                       | 2     |

| DEVSEL#            | Y10                                                                                                                                                           | in                            | sts/6                         | 1     |

| FRA <b>ME</b> #    | W10                                                                                                                                                           | sts/6                         | in                            | 1     |

| GNT#               | U2                                                                                                                                                            | in                            | NA                            |       |

| IDSEL              | W5                                                                                                                                                            | NA                            | in                            |       |

| IRDY#              | Y9                                                                                                                                                            | in-sts/6                      | in                            | 1     |

| PAR                | W13                                                                                                                                                           | in-ts/6                       | in-ts/6                       |       |

| PAR64              | V5                                                                                                                                                            | in-ts/6                       | in-ts/6                       | 2     |

| PCLK               | L3                                                                                                                                                            | in                            | in                            |       |

| PERR#              | Y12                                                                                                                                                           | in-sts/6                      | in-sts/6                      | 1     |

| PREQ#              | R1                                                                                                                                                            | ts/6                          | NA                            |       |

| REQ64#             | U3                                                                                                                                                            | ts/6                          | NA                            | 2     |

| PCIRST#            | T2                                                                                                                                                            | in                            | in                            |       |

| SERR#              | Y13                                                                                                                                                           | in                            | od/6                          | 1     |

| STOP#              | W12                                                                                                                                                           | in                            | sts/6                         | 1     |

| TRDY#              | W11                                                                                                                                                           | in                            | sts/6                         | 1     |

| IRQA#              | R2                                                                                                                                                            | od/6                          | ts/6                          | 1     |

Table 2-2. PCI Host Interface Pins

<sup>1</sup> Signal requires external pull-up resistors.

<sup>2</sup> Those signals are for AIC-7891 only, and are not required to be connected for 32-bit PCI systems. Those pins do not exist for AIC-7890A, and are defined as N/C.

## **SCSI Interface Pins**

| Signal Name    | Pin Number                         | I/O Driver Type | Notes |

|----------------|------------------------------------|-----------------|-------|

| SCDP15-SCDP8   | J4, J2, K3, L1, C12, B11, A11, B10 | Dual Mode I/O   |       |

| SCDM15-SCDM8   | J3, J1, K1, L2, B12, C11, A10, C10 | Dual Mode I/O   |       |

| SCDP7-SCDP0    | B2, B1, D3, C1, E3, F3, F2, G2     | Dual Mode I/O   |       |

| SCDM7-SCDM0    | A2, C2, E4, D1, E2, G4, F1, G1     | Dual Mode I/O   |       |

| SCDPHP, SCDPHM | H2, H1                             | Dual Mode I/O   |       |

| SCDPLP, SCDPLM | C4, B3                             | Dual Mode I/O   |       |

| CDP, CDM       | A8, B8                             | Dual Mode I/O   |       |

| IOP, IOM       | A9,B9                              | Dual Mode I/O   |       |

| MSGP, MSGM     | A6,C7                              | Dual Mode I/O   |       |

| REQP, REQM     | C9, D9                             | Dual Mode I/O   |       |

| ACKP, ACKM     | C6, B5                             | Dual Mode I/O   |       |

| RESETP, RESETM | B6, A5                             | Dual Mode I/O   |       |

| SELP, SELM     | A7, B7                             | Dual Mode I/O   |       |

| BSYP, BSYM     | A4, C5                             | Dual Mode I/O   |       |

| ATNP, ATNM     | B4, A3                             | Dual Mode I/O   |       |

| DIFFSENSE      | A15                                | analog-in       |       |

| EXTXCVR#       | C16                                | in-pu           |       |

| LED#           | A19                                | ts/24           |       |

| LVREXT         | C13                                | analog-out      | 1     |

| SEREXT         | A14                                | analog-out      | 2     |

| STPWCTL        | C15                                | ts/4            |       |

| WIDEPS#        | B16                                | in-pu           |       |

| EXPACT         | A16                                | in              | 3     |

Table 2-3. SCSI Interface Pins

<sup>1</sup> A 10K +/- 1% ohms resistor should be connected between pins C13 and D12.

<sup>2</sup> A 11.8K +/- 1% ohms resistor should be connected between pin A14 and the analog ground.

<sup>3</sup> This signal must be pulled low by an external resistor or by tying to ground when this signal is not connected to AIC-3860.

| Signal Name | Pin Number                                                                           | I/O Driver | Notes |

|-------------|--------------------------------------------------------------------------------------|------------|-------|

| BRDOE#      | B17                                                                                  | ts/4-pu    |       |

| BRDWE       | B18                                                                                  | out/4      |       |

| EXTARBACK#  | E18                                                                                  | in-pu      |       |

| EXTARBREQ#  | E17                                                                                  | ts/4-pu    |       |

| EXTPAUSE#   | A17                                                                                  | in-pu      |       |

| MA[15:0]    | B20, C19, C20, D19, D20, E19,<br>E20, F19, F20, G19, H19, H20, J19,<br>K19, K20, L20 | ts/8-pu    |       |

| MD[7:0]     | G17, G18, H18, J17, J18, K17, K18,                                                   | in-ts/8-pu |       |

| MDP         | C18                                                                                  | in-ts/8-pu |       |

| MRW         | M20                                                                                  | ts/8-pu    |       |

| RAMCS#      | M19                                                                                  | ts/24-pu   |       |

| RAMPS#      | N20                                                                                  | in-ts/4-pu |       |

| ROMCS#      | M18                                                                                  | ts/8-pu    |       |

| SEECS       | M17                                                                                  | ts/4       | 1     |

## FlexPort (Memory) Interface Pins

Table 2-4. FlexPort (Memory) Interface Pins

<sup>1</sup> This signal requires an external pull-down resistor.

## **Clock and Miscellaneous Pins**

| Signal Name | Pin Number | I/O Driver | Notes |

|-------------|------------|------------|-------|

| CLKIN       | D16        | in         |       |

| SCLKIN      | D14        | in         | 1     |

| IDDAT       | N19        | in-pu      |       |

| EXTPAUSE#   | A17        | in-pu      |       |

| PULLUP1     | M1         | in         | Z     |

| PULLUP2     | U3         | in         | 2     |

$^1$  This signal must be tied high or low if not used.  $^2$  AIC-7890A only. This signal must be pulled up to PVCC with a 10 Kohm resistor.

## **Test Pins**

| Signal Name | Pin Number | VO Driver | Notes |

|-------------|------------|-----------|-------|

| TCK         | N1         | in        | 1     |

| TDI         | P2         | in        | 1     |

| TDO         | P1         | ts/6      |       |

| TMS         | N2         | in        | 1     |

| TRST#       | M2         | in        | 2     |

| PDPUDIS#    | R20        | in        | 3     |

| TESTMODE#   | P19        | in        | 4     |

Table 2-6. Test Pins

<sup>1</sup> This signal must be tied high or low if not used.

<sup>2</sup> This signal must be tied low if not used.

<sup>3</sup> This signal must be tied to a known state. See *Pin Signal Description* for more details.

<sup>4</sup> This signal must be tied high during normal operation.

#### **Power and Ground Pins**

#### Table 2-7. Power and Ground Pins

| Signal Name | Pin Number                                                                                                                                    | I/O Driver | Notes |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| AVCC1-AVCC0 | B14, C14                                                                                                                                      |            |       |

| CVCC7-CVCC0 | B19, C3, B15, A18, P20, Y7, L4, G3                                                                                                            |            |       |

| MVCC6-MVCC0 | C17, D18, F18, G20, J20, L19, N18                                                                                                             |            |       |

| PVCC        | D6, D11, D15, F4, F17, K4, L17, R4,<br>R17, U6, U10, U15                                                                                      |            | 1     |

| SVCC8-SVCC0 | D5, D7, C8, D10, A12, K2, H3, E1,<br>D2                                                                                                       |            |       |

| AGND2-AGND0 | D12, A13, B13                                                                                                                                 |            | 2     |

| GND         | A1, D4, D8, D13, D17, H4, H17, J9,<br>J10, J11, J12, K9, K10, K11, K12, L9,<br>L10, L11, L12, M9, M10, M11, M12,<br>N4, N17, U4, U8, U13, U17 |            | 3     |

<sup>1</sup> These BGA ball pads are connected to the power potential ring in the package.

<sup>2</sup> A 10K +/- 1% ohms resistor should be connected between pins C13 and D12. D12 should not be connected to pins A13 and B13 on the board.

<sup>3</sup> These BGA ball pads are connected to the die pad and the ground potential ring in the package.

# Spare Pins

| Signal Name | Pin Number                                                                                                                                                                        | Notes                  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| N/C         | Y5, Y11, Y17, Y20, A20, P18                                                                                                                                                       | AIC-7890A and AIC-7891 |

| N/C         | M3, M4, N3, P3, P4, R3, T3, T4, V3,<br>V4, U5, V5, V6, U7, V7, V8, U9, V9,<br>V10, V11, U11, V12, U12, V13, V14,<br>U14, V15, V16, U16, V17, V18, U18,<br>T17, T18, R18, P17, R19 | AIC-7890A only         |

#### Table 2-8. Spare Pins

# **Pin Signal Description**

The logical state of a signal name that does not end in a # symbol is asserted or active when high and is deasserted or inactive when low. The logical state of a signal name that ends in a # symbol is asserted or active when low and is deasserted or inactive when high.

## **PCI Host Interface Pins**

| Symbol                       | Туре    | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK64#<br>(AIC-7891<br>only) | in      | <b>PCI Acknowledge 64-bit Transfer Input</b> is an active low signal that indicates the target is willing to transfer data using 64-bit. As a target, AIC-7891 doesn't transfer data in 64-bit; therefore, ACK64# is never driven by the AIC-7891.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AD[31:0]<br>(AIC-7890A)      | in-ts/6 | PCI Address and data are multiplexed on the same PCI bus pin. During the first clock of a transaction, AD[31:00] contain a physical byte address of (32 bits) called low address 31:00 for Single Address Cycles (SAC). During subsequent clocks, AD[31:00] contain data of (32-bits) called low data 31:00 except for Dual Address Cycles (DAC) where both the first (low address 31:00) and second (high address 63:32) clocks of a transaction contain address and the remaining clocks contain data (low data 31:00). The turnaround PCLK period for AD[31:00] is the idle cycle between transactions. A PCI read or write bus transaction consist of one Address phase (SAC) or two Address phases (DAC) followed by one or more Data phases. Each PC Data phase may consist of one or more PCLK periods. Little-endian byte ordering is used. AD[07:00] define the least significant byte and AD[31:24]                                                                                                                                                                                                                                                                                                                                            |

|                              |         | the most significant byte. All 32 AD[31:00] bits must be driven to stable values (excluding turn around PCLK periods) during every Address and Data phase, to enable even-parity checking. All AD[31:00] bits must be decoded for memory and I/O phases to allow for future address expansion The use of AD[01:00] varies in the Address phase of the three different PCI address spaces:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              |         | In the PCI Configuration address space, AD[01:00] identify the type of configuration space the access is intended for. A value of 0h identifies th configuration space as type 0; a value of 1h identifies it as type 1. Values of 2h and 3h are reserved. Type 0 configuration accesses are not propagated beyond the local PCI bus and must be claimed by a local device or terminated with master-abort. Type 1 configuration accesses are for targets that do not reside on the local PCI bus. For type 0, AD[07:02] define a 32-bit register address within the configuration address space. Thus, configuration address space defaults to Double Word (DWD) addressing aligned to the DWD boundary. Targets with multiple functions must contain a configuration space for each function. The value supplied on AD[10:08] is used to point to each space. The AIC-7890A, as a single function target supporting type 0 address space, accesses with a single configuration space. As a target, the AIC-7890A uses positive address decoding over AD[10:02], along with CBE[3:0]# (command is CRDC or CWRC), IDSEL, AD[01:00] = 0h and FRAME# to validate the configuration register address decode, then asserts DEVSEL# to claim the transaction. |

|                              |         | ter address decode, then asserts DEVSEL# to claim the transaction.<br>AD[10:08] must be "000" to enable configuration access of the AIC-7890A<br>IDSEL is normally connected to an ADn signal in the range of AD[31:11]<br>of the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Symbol | Туре | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |      | <ul> <li>In the IO address space, all 32 AD lines are used to provide for direct byt address decoding. The AIC-7890A as a target uses positive address decoding over BASEADR0 register (stored value), AD[31:08] (for mapping), CBE[3:0]# (for command), AD[07:00] (for register address) and FRAME# to validate the Device Space register 256 decodes. When the AIC-7890A as a target is enabled to allow access to its Device Space regist ters from the PCI I/O address space, the use of AD[01:00] during the Address phase allows the AIC-7890A to validate the register address decode and claim the transaction (assert DEVSEL# = medium speed). TRDY# is deasserted for the first Data phase to allow the Data phase CBI value to become valid for byte steering to the internal 8-bit register path for a three PCLK data transfer cycle for register write. For register read, TRDY# is deasserted for the required AD[31:00] turn-around cycle, plus an additional PCLK for H/W registers, plus one or more to enable internal or external RAM data to become valid. Note, additional PCLKs are required for some addresses by the internal RISC PhaseEngine (sequencer)</li> <li>In the PCI memory address space, AD[01:00] are excluded from the address decode and as such, the address defaults to Double Word (DWD addressing aligned to the DWD boundary. The value AD[01:00] are used in the memory address space to indicate different Memory Address Transfer modes. A value of 0h indicates linear address increment mode, 1h is reserved (disconnect after first data phase), 2h indicates Cache Line Wrap mode, and 3h is reserved. The AIC-7890A as a amaster or target on the address of the address cache Line Wrap mode, and 3h is reserved. The AIC-7890A as a master or target on the address of the cache of the target of t</li></ul> |