15 cummings park, woburn, ma. 01801

telephone (617) 935-6668

telex 949329

INSTRUCTION MANUAL

FOR

ADAC CORPORATION

MODEL 1030

DATA ACQUISITION

AND

CONTROL SYSTEM

IM-678 A2-10019, Rev. 6

5.3

\$

The second second

Contraction of the other

## PREFACE

## ORDERING CODE

The ordering code for the Model 1030 is as follows:

|      | 5   |                      |                  |        |                          |                                       |

|------|-----|----------------------|------------------|--------|--------------------------|---------------------------------------|

| 10   | 30- | ] - 🔲 - 🗍            | - 🖸 - 📮 - 🖸      |        |                          |                                       |

|      |     |                      |                  |        |                          | ж.                                    |

|      |     |                      |                  | No. of | DAC                      | DC/DC                                 |

| Mux  | A/D | Range                | A/D Type & Speed | DACs   | Range                    | Converter                             |

| 8DI  | A:  | +10V                 | l: 100KHz        | 0.     | 0: None                  | O: Omit                               |

| 16SE | в:  | $\overline{0} - 10V$ | 3: 35KHz         | 1      | A: +10V                  | P: Include                            |

| 16PD | C:  | +5V                  | 1PGA: 100KHz     | 2      | B: $\overline{0}$ to 10V |                                       |

| 16DI | *D: | <u>0</u> – 5V        | PG=1,2,5,10      |        | C: +5V                   |                                       |

| 32SE |     | e e                  | 1PGB: 100KHz     |        | D: 0 to 5V               |                                       |

| 32PD | . ē |                      | PG=1,2,4,8       |        | 4                        |                                       |

| 32DI |     |                      | 3PGA: 35KHz      | -      |                          | 10)<br>                               |

| 64SE |     |                      | PG=1,2,5,10      |        |                          | · · · · · · · · · · · · · · · · · · · |

| 64PD |     |                      | 3PGB: 35KHz      |        |                          |                                       |

|      |     |                      | PG=1,2,4,8       |        |                          |                                       |

\* Not available with 100 KHz module.

ADAM 12 module used for 35 KHz option. ADAM 100 module used for 100 KHz option.

# TABLE OF CONTENTS

~ 3

\*

L. H. L.

IJ

ŋ

| Ϊ.                                              | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1                                                                          |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------|

| II.                                             | HANDLING PRECAUTIONS                                                                                                                                                                                                                                                                                                                                                                                                     | <br>  | 2                                                                          |

| III.                                            | INSTALLATION INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                |       |                                                                            |

|                                                 | <ul> <li>A. General</li> <li>B. Mounting</li> <li>C. Bus Grant Capacity</li> <li>D. Cabling</li> <li>E. Grounding Considerations</li> <li>F. Case and Power Grounds</li> <li>G. DAC Returns</li> </ul>                                                                                                                                                                                                                   |       | 2<br>2<br>3<br>4<br>5<br>5                                                 |

| IV.                                             | CONNECTOR TERMINATIONS                                                                                                                                                                                                                                                                                                                                                                                                   |       |                                                                            |

| 1. 6. 2. 6. 6. 6. 6. 6. 6. 6. 6. 6. 6. 6. 6. 6. | <ul> <li>A. Connector J1 (End of Cable)</li> <li>B. Connector J2 (End of Cable)</li> <li>C. Connector C1 (On PC Board)</li> <li>D. Connector C2 (On PC Board)</li> </ul>                                                                                                                                                                                                                                                 |       | 6<br>7<br>8<br>9                                                           |

| v.                                              | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                           |       | ÷                                                                          |

|                                                 | <ul><li>A. Analog Inputs</li><li>B. Analog Outputs</li><li>C. Environmental and Physical</li></ul>                                                                                                                                                                                                                                                                                                                       | 4<br> | 10<br>11<br>11                                                             |

| VI.                                             | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                      |       |                                                                            |

|                                                 | A. General                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                                            |

|                                                 | <ol> <li>Multiplexer</li> <li>Programmable Gain Amplifier</li> <li>Sample and Hold</li> <li>Analog to Digital Converter</li> <li>Converter Timing</li> <li>ADC Triggering</li> <li>Digital to Analog Converters</li> <li>Address Selection</li> <li>Status Register</li> <li>Data Transfer Bus Transactions</li> <li>Priority Transfer Transactions</li> <li>Interrupt Transaction</li> <li>Priority Chaining</li> </ol> |       | 12<br>13<br>14<br>15<br>15<br>16<br>16<br>17<br>18<br>20<br>21<br>21<br>21 |

i

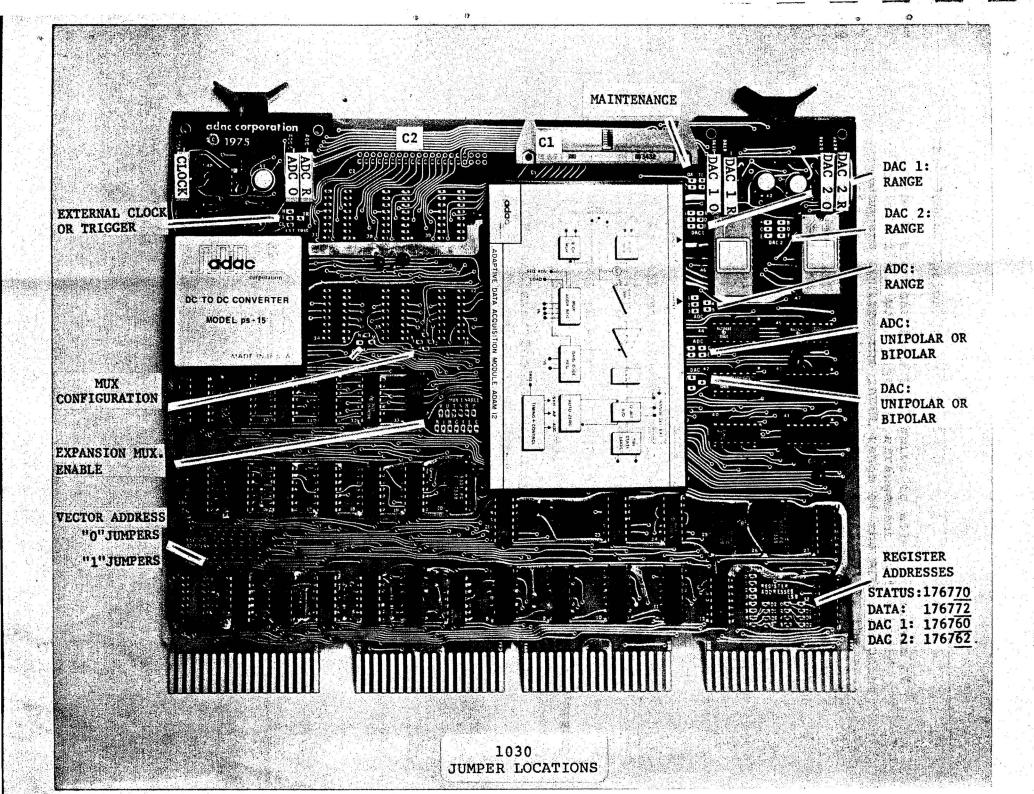

# B. Jumper Options

c.

D.

-

The second s

a sold the second

A COLORADOR

-

6,

North and

Sec. 1

ALC: NO.

Chestan State

Md Street

A CONTRACTOR

Sector.

| 1.       | ADC Input Range                                                 | 22<br>22 |

|----------|-----------------------------------------------------------------|----------|

| 2.<br>3. | Multiplexer Channel Capacity<br>Multiplexer Input Configuration | 23       |

| 4.<br>5. | DAC Full Scale Range<br>External Clock and Trigger Option       | 23<br>23 |

| Cal      | ibration Procedure                                              |          |

| 1.<br>2. | ADC Adjustments<br>DAC Adjustments                              | 24<br>25 |

| Dia      | gnostic Program                                                 | 27-31    |

## 1. GENERAL DESCRIPTION

R.

The ADAC Model 1030 is a series of data acquisition systems that are designed to fit directly into the backplane of a Digital Equipment Corporation LSI-11 or LSI-11/03 microcomputer. The system is built on an 8 1/2" x 10" printed circuit board and occupies but one slot in any of the chassis.

It uses the +5 volts from the backplane to power its logic as well as to power a self-contained DC to DC converter which supplies +15 volts and -15 volts to the analog circuitry mounted on the board.

A flat shielded ribbon cable assembly is attached to the end of the board opposite the I/O bus connector to bring the analog signals into and out of the computer. Mating connectors and cable clamps are supplied to allow reliable cable to cable connections.

Contained on the board is a multiplexer of up to 64 analog input channels, a programmable gain amplifier with automatic zeroing, a differential input amplifier, a high speed sample and hold amplifier, and a high speed 12 bit analog to digital converter. A program interrupt scheme is included to connect the output of the analog to digital converter to the computer bus.

In addition, provision is made for up to two digital to analog converters with interface to the bus.

#### II. HANDLING PRECAUTIONS

The system, protected with bubble pack and styrofoam, is shipped in a 15  $3/4 \ge 9 1/2" \ge 3"$  cardboard container. Should the system have to be sent back to the factory for any reason, wrap the board in bubble pack, taking care to separately wrap the connector so that it is cushioned on all sides. Pack the unit in its original shipping container.

#### III. INSTALLATION INSTRUCTIONS

#### A. General

The critical analog circuitry of the Model 1030 is encased in grounded steel modules to minimize both EMI and RFI pickup. The analog inputs and outputs are connected via shielded ribbon cable and are not run through the I/O connector because of the high frequency digital signals that exist there.

However, care should be taken both in the choice of slot to be used in the computer as well as how the source returns are connected to the system, in order to prevent degradation of system performance.

#### B. Mounting

The ADAC Model 1030 is designed to work with the DEC LSI-11 or PDP-11/03 series of microcomputers. The board measures 10.4" x 8.5" x .75" and plugs directly into the DEC H9270 backplane or any other backplane designed to the LSI-11 I/O bus pinning. The H9270 backplane consists of a group of connectors four slots wide (A, B, C, & D) and four slots deep (1, 2, 3 & 4). Each slot contains 36 lines (18 each on component and solder side of the circuit board). The LSI I/O bus is contained within two slots (A & B or C & D). The Model 1030 occupies four slots (A, B, C, & D) of one row and can be used in any of the four slots. The "A" connector is the one furthest to the right when viewing the board from the component side, fingers down.

CAUTION:

The board should be inserted or withdrawn only with power off. Damage can result if the board is plugged in backwards.

## C. Bus Grant Capacity

Control signals provided by the LSI-11 CPU card include two daisy-chained grant signals which provide a priority structured I/O system. These signals are BIAKO/BIAKI (for interrupts) and BDMGO/ BDMGI (for DMA grant). These signals, generated on the CPU board, normally propagate through the H9270 backplane until they reach the requesting device. Generally, the CPU is mounted in slot 1. The grant signals are first passed to slots 2-CD, and then to slots 2-AB, 3-AB, 3-CD, 4-CD and then to 4-AB. Any cards mounted between the CPU and the Model 1030 must pass the grant signals along, If any of the intervening double slots are not used, then the grant signals must be jumpered on the H9270 backplane in order to maintain the daisy-chained signal continuity.

For each unused slot, AN2 must be jumpered to AM2, and CN2 must be jumpered to CM2 for interrupt continuity. For DMA grant continuity, AS2 must be jumpered to AR2 and CS2 jumpered to CR2.

On the Model 1030, the interrupt acknowledge circuitry inputs on Pin CM2 and exits on Pin CN2.

The following internal jumpers are supplied to provice continuity: AM2 to AN2, AR2 to AS2 and CR2 to CS2.

#### D. Cabling

A shielded flexible ribbon cable assembly is supplied to carry the analog input and output signals to the Model 1030. In a fully loaded system, two cables are used. The first cable contains the first 32 analog input channels as well as the two DAC outputs. The second cable contains the second group of 32 analog input channels. The cables plug into right angle headers mounted on the board opposite to the bus.

The cable is supplied with a dual cable clamp assembly to allow a reliable cable to cable connection to be made. The shield of the cable is connected to Pin 49 of each connector.

## E. Grounding Considerations

To maintain good 12 bit performance, proper grounding of the sources to the data acquisition system is required.

Several different ground points are brought out to the connector. On the board, the analog and digital grounds are run separately, and are tied together at one point only to eliminate possible ground loops. The common point is physically close to the analog return of the analog to digital converter. This point is brought out to Jl connector Pin 48 and should be used as the source return in single-ended systems.

In fully differential systems, both sides of each source are switched in the multiplexer and no direct connection is made to analog return. However, there is a system constraint that the signal plus common mode voltage cannot exceed 10.24 volts. If the source is truly floating (e.g. a non-grounded battery) then a resistor must be connected from the low side of the source to analog return. This is necessary, since, although the multiplexer presents a very high input impedance (over 100 megohms) there is still some finite leakage current that flows (1 nanoampere @ 25°C, 20 nanoamperes @ 60°C). Since two input switches are connected to the source a resistive path must be supplied to analog return for 40 nanoamperes of current.

If the source voltage is a maximum of 10 volts, then a maximum of 6.2 megohm resistor must be connected between the source low terminal and analog return to stay within the system constraint of 10.24 volts maximum of signal plus common mode. If a maximum full scale of 5 volts is used, then the resistor can be about twenty times larger and still maintain proper operation.

A pseudo-differential mode is provided as standard on all models. A fully differential amplifier is included between the multiplexer and the sample and hold amplifier. The output of the multiplexer is internally connected to the high side of the differential amplifier. The low side of the differential amplifier is brought out to connector J1 Pin 50. For single-ended operation, Pin 50 must be jumpered to J1 Pin 48 (analog return). However, if all the sources connected to the multiplexer have a common return, then the common return can be connected to the differential amplifier low terminal (Pin 50) rather than to analog return (Pin 48). In this mode, there is excellent high impedance isolation between the source return and the data acquisition ground, eliminating potential ground loops and noise problems without sacrificing the number of multiplexer channels that can be fully employed. (Sixteen multiplexer switches can scan 16 sources rather than 8 as in fully differential mode). The same constraints on keeping the common mode as exists for the fully differential mode.

F. Case and Power Grounds

In order to minimize the amount of 60 Hz signal that flows in the input return (Pin 48), the case or power ground for the sources (or the shield of the input cable) must not be connected to analog ground (Pin 48) since this would allow power currents to flow through the input return lead and cause a 60 Hz normal mode signal to be in series with actual signal to be measured.

The input shield should be connected to the source case (or power) ground, and be left unconnected at the data acquisition end. A separate wire should be run to connect the source case (or power) ground to a terminal provided on connector J1 Pin 49.

## G. DAC Returns

Although all the grounds for each digital to analog converter are connected together on the board, two wires are brought out from each DAC to connector J1, the DAC output and the DAC return. In this fashion, crosstalk between DACs is minimized since the output currents for each DAC are separately returned to the appropriate points in the system. It is good practice to follow through with the separation of returns external to the Model 1030 to the DAC loads.

CONNECTOR TERMINA IV. 1030 for LSI-11 w. dist 11-8-78 ADAC - model DACL-RET () DACL-RET () DACL-OUT () '0' ?ir or 10 33> Q 10A 16 # | # (13) > (P) AL JB 9 DAC 2-OUT 1 1A Ð X-TAL elock ExT. TRIST #2#  $(\dot{r})$ (I) >== -( 9 EXT. TRIG 27 (17) ble ine 2S: \* 3\* SHA SSIS ig) OGRND 38 30> ıpı 0 3-1 34 to pin 50 for averator-differential 3C. Ì )-1 P :s

•3

10

. (\*

a

()

IV. of sacket view rear 9 10 LI A 12 0 15 OA 16 OA 0 073 <sup>0</sup>1B 0 313 0 330B O O Q EXT TRIG An? Lo IN GND PAC2 Dee-1 SIGANL RETURN for Single enter For pseudo-didlerencial disconnest QR, 18, 28, 33 and tie then to più 50

CONNECTOR TERMI

()

## IV. CONNECTOR TERMINATIONS

## CONNECTOR J1

(At End of Cable)

|   | Pin<br>No. | 2   |                  | Pin<br>No. |      | в ,              | Pin<br>No. |                              |

|---|------------|-----|------------------|------------|------|------------------|------------|------------------------------|

| - | 1          | сн. | 16-8A IN         | 18         | CH.  | 24-8B IN         | 34         | ×                            |

|   | 2          | 0   | 17-9A            | 19         | CII. | 25-9B            | 35         |                              |

|   | 3          |     | 18-10A           | 20         |      | 26-10B           | 36         |                              |

|   | 4          |     | 19-11A           | 21         |      | 27-11B           | 37         |                              |

|   | 5          |     | 20-12A           | 22         |      | 28-12B           | 38         | 34<br>40                     |

|   | 6<br>7     |     | 21-13A<br>22-14A | 23         |      | 29-13B           | 39         |                              |

|   | 8          |     | 22-14A<br>23-15A | 24<br>25   |      | 30-14B<br>31-15B | 40<br>41   |                              |

|   | 9          |     | 7-7A             | 26         |      | 15-7B            | 42         |                              |

|   | 10         |     | 6-6A             | 27         |      | 14-6B            | 43         | DAC 2 RETURN                 |

|   | 11         |     | 5 <b>-</b> 5A    | 28         |      | 13-5B            | 44         | DAC 2 OUTPUT                 |

|   | 12         |     | 4 - 4 A          | 29         |      | 12-4B            | 45         | DAC 1 RETURN                 |

|   | 13         |     | 3-3A             | 30         |      | 11-3B            | 46         | DAC 1 OUTPUT                 |

|   | 14         |     | 2-2A             | 31         |      | 10-2B            | 47         | EXTERNAL TRIGGER             |

|   | 15<br>16   |     | 1-1A             | 32         |      | 9-1B             | 48         | SIGNAL RETURN                |

|   | 17         |     | 0-0A             | 33         |      | 8-0B             | 49<br>50   | POWER RETURN<br>AMP LO INPUT |

|   | т,         |     |                  |            |      | 1                | 50         | AMP LO INPUT                 |

NOTES:

Ē

- Ribbon cable mounted connector: Cannon DD50S Mating connector: Cannon DD50P

- A and B designations for differential inputs. Connect high side of inputs to A pins and low side of inputs to B pins.

- 3. For single-ended operation, connect Pin 50 to Pin 48. Also connect source return to Pin 48.

- For pseudo-differential operation, connect source return to Pin 50. Refer to Section III F for constraints.

- 5. Connect earth or case ground of sources to Pin 49.

- 6. Run DAC returns separately to their respective loads.

#### CONNECTOR TERMINATIONS IV.

CONNECTOR J2

(At End of Cable)

| Pin<br><u>No.</u>                                                                         | · .                                                                                                                                                                 | Pin<br>No.                                                                                       | · · · ·                                                                                                                                                         | Pin<br><u>No.</u>                                                                                                                       |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | CH. 48-24A IN<br>49-25A<br>50-26A<br>51-27A<br>52-28A<br>53-29A<br>54-30A<br>55-31A<br>32-16A<br>33-17A<br>34-18A<br>35-19A<br>36-20A<br>37-21A<br>38-22A<br>39-23A | 18 CH.<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33 | 56-24B IN<br>57-25B<br>58-26B<br>59-27B<br>60-28B<br>61-29B<br>62-30B<br>63-31B<br>40-16B<br>41-17B<br>42-18B<br>43-19B<br>44-20B<br>45-21B<br>46-22B<br>47-23B | 34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48 SIGNAL RETURN<br>49 POWER RETURN<br>50 AMP LO IN |

|                                                                                           |                                                                                                                                                                     |                                                                                                  |                                                                                                                                                                 |                                                                                                                                         |

7

NOTE:

1.

Ribbon cable mounted connector: Cannon DD50S Mating connector: Cannon DD50P

## IV. CONNECTOR TERMINATIONS

#### CONNECTOR C1

(Connector on PC Board)

| 1  | CH | 16-8A    | IN  |        | 2  | CH      | 24-8B   | IN    |   |

|----|----|----------|-----|--------|----|---------|---------|-------|---|

| 3  | CH | 17-9A    | IN  |        | 4  | CH      | 25-9B   | IN    |   |

| 5  | CH | 18-10A   | IN  |        | 6  | CH      | 26-10B  | IN    |   |

| 7  | CH | 19-11A   | IN  |        | 8  | CH      | 27-11B  | IN    |   |

| 9  | CH | 20-12A   | IN  |        | 10 | CH      | 28-12B  | IN    |   |

| 11 | CH | 21-13A   | IN  |        | 12 | CH      | 29-13B  | IN    |   |

| 13 | CH | 22-14A   | IN  |        | 14 | CH      | 30-14B  | IN    |   |

| 15 | CH | 23-15A   | IN  |        | 16 | CH      | 31-15B  | IN    |   |

| 17 | CH | 7-7A     | IN  |        | 18 | CH      | 15-7B   | IN    |   |

| 19 | CH | 6-6A     | IN  |        | 20 | CH      | 14-6B   | IN    |   |

| 21 | CH | 5-5A     | IN  |        | 22 | CH      | 13-5B   | IN    |   |

| 23 | CH | 4-4A     | IN  | 2<br>2 | 24 | CH      | 12-4B   | IN    |   |

| 25 | CH | 3-3A     | IN  |        | 26 | CH      | 11-3B   | IN    |   |

| 27 | CH | 2-2A     | IN  | 1      | 28 | CH      | 10-2B   | IN    |   |

| 29 | CH | 1-1A     | IN  | P      | 30 | CH      | 9-1B    | IN    |   |

| 31 | CH | 0-0A     | IN  |        | 32 | CH      | 8-0B    | IN    |   |

| 33 | AM | P IN LO  |     |        | 34 | POW     | ER RETU | JRN   |   |

| 35 | SI | GNAL RET | URN | 1      | 36 | <br>EXI | ERNAL 7 | RIGGE | R |

| 37 | DA | C 1 OUT  |     | ° (    | 38 | DAC     |         | JRN   |   |

| 39 | DA | C 2 OUT  |     |        | 40 | DAC     | 2 RETU  | JRN   |   |

|    |    | · ·      |     |        |    |         |         |       |   |

NOTES:

1. Connector 1 is a 40 pin header, 3M-3432/1002 mating connector: 3417/3000.

- A and B are designations for differential inputs. Connect high side of inputs to A pins and low side of inputs to B pins.

- For single-ended operation, connect Pin 33 to Pin 35. Also connect source return to Pin 35.

- 4. For pseudo-differential operation, connect source return to Pin 33. Refer to Section III F for constraints.

- 5. Connect earth or case ground of sources to Pin 34.

6. Connect input shield to Pin 34.

7. Run DAC returns separately to their respective loads.

## CONNECTOR TERMINATIONS

## CONNECTOR C2

(Connector on PC Board)

| 1  | 2        | CH 48-24A  | IN   |                                                                                                                                                                                                                                    | 2  |     | CH  | 56-24B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

|----|----------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3  |          | CH 49-25A  | IN   |                                                                                                                                                                                                                                    | 4  |     | CH  | 57-25B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 5  |          | CH 50-26A  | IN   |                                                                                                                                                                                                                                    | 6  |     | CH  | 58-26B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 7  |          | CH 51-27A  | IN   |                                                                                                                                                                                                                                    | 8  |     | CH  | 59-27B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 9  |          | CH 52-28A  | IN   | Â.                                                                                                                                                                                                                                 | 10 |     | CH  | 60-28B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 11 |          | CH 53-29A  | IN   |                                                                                                                                                                                                                                    | 12 | · * | CH  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IN |

| 13 |          | CH 54-30A  | IN   |                                                                                                                                                                                                                                    | 14 |     | CH  | 62-30B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 15 |          | CH 55-31A  | IN   |                                                                                                                                                                                                                                    | 16 |     | CH  | 63-31B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 17 |          | CH 32-16A  | IN   | 240 <sup>140</sup><br>N                                                                                                                                                                                                            | 18 |     | CH  | 40-16B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 19 |          | CH 33-17A  | IN   |                                                                                                                                                                                                                                    | 20 |     | СН  | 41-17B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 21 | 5.<br>5. | CH 34-18A  | IN   | 1.1                                                                                                                                                                                                                                | 22 |     | CH  | 42-18B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 23 |          | CH 35-19A  | IN   |                                                                                                                                                                                                                                    | 24 |     | CH  | 43-19B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 25 |          | CH 36-20A  | IN   |                                                                                                                                                                                                                                    | 26 |     | CH  | 44-20B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 27 |          | CH 37-21A  | IN   |                                                                                                                                                                                                                                    | 28 |     | CH  | 45-21B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 29 |          | CH 38-22A  | IN   |                                                                                                                                                                                                                                    | 30 |     | CH  | 46-22B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IN |

| 31 |          | CH 39-23A  | IN   |                                                                                                                                                                                                                                    | 32 |     | CH  | 40-22B<br>47-23B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 33 |          | AMP IN LO  |      |                                                                                                                                                                                                                                    | 34 |     |     | 100 C | IN |

| 35 | 5        | SIGNAL RET | IIRN | and god                                                                                                                                                                                                                            | 36 |     | POW | IER RETU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RN |

| 37 |          |            | on   | 1. 150 j. n.                                                                                                                                                                                                                       | 38 |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 39 |          |            |      |                                                                                                                                                                                                                                    | 40 |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |          |            |      | a de la compañía de l<br>Transmiser de la compañía de la comp | 40 |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

NOTE:

Connector C2 is a 40 pin header, 3M-3432/1002. Mating connector: 3M-3417/3000.

9

IV.

## V. SPECIFICATIONS

## A. ANALOG INPUTS

Number of inputs to multiplexer

64 single ended

32 true differential

64 pseudo-differential

Input Voltage Range (full scale range)

1030-X-X-3-X-X-X (35 KHz)

1030-X-X-1-X-X-X (100 KHz)

With Programmable Gain

Maximum Input Voltage for Proper Operation (signal plus common mode)

Maximum Input Voltage (no damage)

Input Resistance

Resolution

Relative Accuracy

Inherent Quantizing Error

Tempco of Linearity

Tempco of Range

Tempco of Offset

Maximum Throughput Rate (12 bits)

1030-X-X-3-X-X-X 1030-X-X-1-X-X-X

Sample & Hold Aperture Uncertainty

Crosstalk

-10V to +10V, 0 to +10V - 5V to + 5V, 0 to + 5V

-10V to +10V, 0 to +10V- 5V to + 5V

Standard ranges, preceded by Gains of 1, 2, 5 & 10 or 1, 2, 4, & 8

-10.24V to +10.24V

-15V to +15V

Greater than 100 megohms

12 bits

+0.025% of FSR w/o prog. amp. +0.035% of FSR, + 100 uV with respect to input, w/prog. gain

+ 1/2 LSB

Less than 3 ppm FSR/<sup>O</sup>C

Less than 30 ppm FSR/OC

0.001% FSR/<sup>O</sup>C

35,000 channels/sec. 100,000 channels/sec.

20 nanoseconds

80dB down at 1 KHz, "off" channels to "on" channels

|    | Differential Amp CMRR                                                                             | 70 dB (DC to 1 kHz)                                  |

|----|---------------------------------------------------------------------------------------------------|------------------------------------------------------|

|    | Sample & Hold Feedthrough                                                                         | 80 dB down at 1 kHz                                  |

| a  | Maximum Error for FS to FS<br>Transition Between Channels                                         | l LSB                                                |