## CONFERENCE PROCEEDINGS

# The 2nd Annual Symposium on COMPUTER ARCHITECTURE

Sponsored by the IEEE Computer Society and the Association for Computing Machinery

in cooperation with the University of Houston

JANUARY 20-22, 1975

Additional copies may be ordered from: IEEE Computer Society Publications Office 5855 Naples Plaza, Suite 301, Long Beach, CA 90803

Association for Computing Machinery 1133 Avenue of the Americas, New York, N.Y. 10036

75CHO916-7 C

Copyright © 1975 by the Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, New York 10017

SYMPOSIUM CHAIRMAN

WILLIS K. KING

PROGRAM CHAIRMAN OSCAR GARCIA

PROGRAM COMMITTEE

HARVEY G. CRAGON TSE-YUN FENG REINER W. HARTENSTEIN E. DOUGLAS JENSEN TED A LALIOTIS HAROLD LORIN ELLIOTT I. ORGANICK

STEVE SHERMAN DANIEL P. SIEWIOREK HAROLD S. STONE STEPHEN Y. SU BRUCE WALD RODNAY ZAKS

## SYMPOSIUM COMMITTEE

JAMES BARGAINER OSCAR GARCIA JUNG-CHANG HUANG OLIN JOHNSON

JACK LIPOVSKI DUANE PYLE HUGH WALKER

**CO-SPONSORS:**

ACM SIGARCH COMPUTER SCIENCE DEPARTMENT, UNIVERSITY OF HOUSTON COMPUTER SOCIETY OF THE IEEE

## CHAIRMAN'S REMARKS

A professional symposium should provide the attendees with the opportunities, 1) to gain new knowledge and keep abreast of new developments in the field and 2) to express and exchange ideas with other attendees. We believe the Second Annual Symposium on Computer Architecture will achieve these goals.

First of all we trust that anyone who reads this volume would agree with us that we have an abundance of high quality papers assembled here. As a matter of fact, it was most gratifying to us in organizing the symposium to find the tremendous enthusiastic response from the practitioners of the field in the form of the large number and high quality of papers submitted. The program committee, especially its chairman, of course, had to be faced with the difficult task of deciding how to limit the size of the technical program without leaving out any topic of importance. We are, however, pleased to say that every paper submitted was reviewed by no less than three referees and all papers accepted were rated as top quality by at least two of the referees. The result is a technical program consisting of twelve sessions with topics ranging from the architecture of computer networks to computer architecture education. Within this broad spectrum, most every computer architect will find some novel and exciting topic that will benefit him professionally.

No less encouraging and significant than the large number of papers being submitted, is the fact that over one third of them come from foreign countries. We are well aware of the fundamental contributions in computer architecture made by many European countries in the past. The full participation by those countries and others assure us that the state of art of research in computer architecture in the world will be reflected in the conference.

Furthermore, we were able to organize in conjunction with the symposium a one day tutorial on microcomputers --a subject that really attracts the interest and fancy of many of us. So, for those who come here with the intention of keeping themselves abreast in the field, they will not be disappointed.

As far as facilitating the exchange of ideas among the attendees is concerned, we provide the following: We have scheduled an evening of panel discussion with a list of distinguished speakers leading the discussion. We hope and expect to have some exciting and perhaps even heated debates on the current issues of computer architecture not only among the panelists but also with active participation from the floor. We have arranged a coffee break of half an hour after every one and a half hours of technical session so that the audience can have an additional chance to question the speakers closely while the subject is still fresh in everybody's mind. We provide a cocktail hour so that people can talk in a relaxed and informal atmosphere. We hold our meetings on the campus of the University of Houston away from the big hotels downtown so that attendees can seek one another out easily.

Beginning this year, we established a best paper award for the symposium. Steve Szygenda, as program chairman of the previous symposium, assumes the chairmanship of the award committee. The committee will not only examine the papers but also evaluate the oral presentation of the candidates. The award will be presented to the winner in the next symposium.

We are indebted to a great many people, too numerous, in fact to mention them all individually. However, we do want to acknowledge our appreciation to the following in particular. We would like to thank the chairmen of our sponsoring organizations, Jack Lipovski of TCCA and Chuck Casale of SIGARCH, for their continuous support. Mike Flynn, in spite of his busy schedule, never failed to provide his valuable advise and guidance when asked. Harry Haymann of IEEE, with his vast experience and contact, not only helped us in publicizing the symposium, but also in publishing the proceedings. The members of the symposium provide us with indispensable help, particularly, J. C. Huang who serves as treasurer and registration chairman, and Olin Johnson who serves not only as our publication chairman but also as the acting chairman of the Department of Computer Science, provided the extensive use of its facilities. To each of them, we would like to express our thanks. However, most of all we would like to send our gratitude to our program chairman, Oscar Garcia, and his program committee. Due to the extraordinarily large number of papers submitted and the strict standard of review we adhere to, it would have been impossible to get the job done were it not for the tireless effort and boundless resourcefulness of oscar. We understand that before the technical program was finally hammered out, over forty people got themselves involved in the process of reviewing papers for the symposium.

Finally, we wish to acknowledge the assistance of the secretaries, particularly, I want to thank Alice Sand for her infinite patience and didication and help in answering all the correspondence and putting this proceedings in its final shape.

> Willis K. King Symposium Chairman

## TABLE OF CONTENTS

PAGE

| "Decentralized Priority Control in Data Communication,"<br>L. Nisnevich and E. Strasbourger, Technion                                                                       | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| "A Loop Network for Simultaneous Transmission of Variable-Length Messages,"<br>Cecil C. Reames and Ming T. Liu, Ohio State University                                       | 7   |

| "The Architecture of THE PICTURE SYSTEM,"<br>James F. Callan, Evans and Sutherland Computer Corp                                                                            | 13  |

| "A Fast Display-Oriented Processor,"<br>John Staudhammer, Jeffrey F. Eastman and James N. England, N.C. State University                                                    | 17  |

| "Computer Display of Colored Three-Dimensional Objects,"<br>Jeffrey F. Eastman and John Staudhammer, N.C. State University                                                  | 23  |

| "A Microprogrammed Processor for Interactive Computer Graphics,"<br>Henry D. Kerr, Adage, Inc                                                                               | 28  |

| "Functional Memory Techniques Applied to the Microprogrammed Control of an Associative Processor,"<br>C.V.W. Armstrong, University of Edinburgh                             | 34  |

| "Instruction Design to Minimize Program Size,"<br>James F. Wade and Paul D. Stigall, University of Missouri                                                                 | 41  |

| "HMO, A Hardware Microcode Optimizer,"<br>James O. Bondi and Paul D. Stigall, University of Missouri                                                                        | 45  |

| "The Computer Aided Design of Processor Architectures,"<br>A.M. Peskin, Brookhaven National Laboratory                                                                      | 51  |

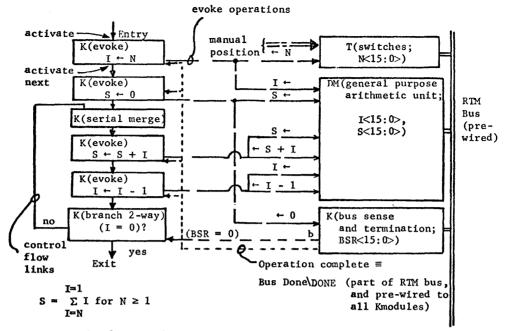

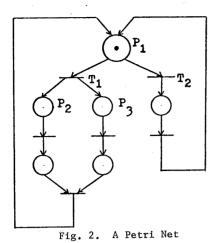

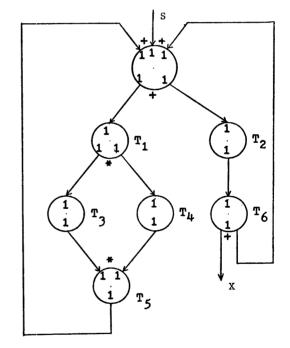

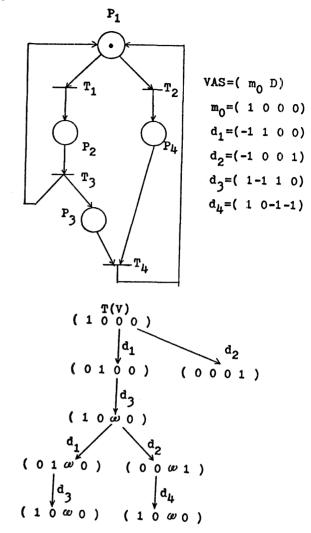

| "Intermodule Protocol for Register Transfer Level Modules: Representation and Analytic Tools,"<br>W.H. Huen and D.P. Siewiorek, Carnegie-Mellon University                  | 56  |

| "Picture Systems, PS, and the Design of a Channel-to-Channel Computer Interface,"<br>Portia Isaacson, Xerox Corp                                                            | 63  |

| "Reference Concepts in a Tree Structured Address Space,"<br>Lennart Löfgren, Saab-Scania                                                                                    | 71  |

| "A Virtual Memory for Microprocessors,"<br>Judith A. Anderson, NASA Kennedy Space Center and G.J.Lipovski, University of Florida                                            | 80  |

| "The Performance Enhancement of Descriptor-Based Virtual Memory Systems Through the Use of Associative Registers,"<br>R.E. Brundage and A.F. Batson, University of Virginia | 0.  |

| "SPEAC_Special Purpose Electronic Area Correlator,"                                                                                                                         | 85  |

| Orin E. Marvel, Honeywell Government and Aerospace Products                                                                                                                 | 91  |

| "Architecture Advances of the Space Shuttle Orbiter Avionics Computer System,"<br>James M. Satterfield, NASA Lyndon B. Johnson Space Center                                 | 95  |

| "Design Study of an Avionics Navigation Microcomputer,"<br>Uno R. Kodres and William McCracken, Naval Postgraduate School                                                   | 99  |

| "An Iteratively Structured Information Processor,"<br>Gerald R. Kane, University of Tulsa                                                                                   | 106 |

| "Hardware-Software Interactions in SYMBOS-2R's Operating System,"<br>Hamilton Richards, Jr. and A.E. Oldehoeft, Iowa State University                                       | 113 |

| "The Design and Evaluation of the Array Machine: A High-Level Language Processor,"<br>Pierre Sylvain and Maniel Vineberg, U.C.L.A                                           | 119 |

| "A Preliminary Architecture for a Basic Data-Flow Processor,"<br>Jack B. Dennis and David P. Misunas, M.I.T.                                                                | 126 |

| "Reduction Languages for Reduction Machines,"<br>K.J. Berkling, Gessellschaft für Mathematik und Datenverarbeitung, Bonn                                                    | 133 |

| "Output Devices Sharing by Minicomputers,"<br>Willis K. King and Fulvio Carbonaro, University of Houston                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "On Relating Small Computer Performance to Design Parameters,"<br>S. Rannem, V.C. Hamacher, S.G. Zaky, P. Connolly, University of Toronto                         |

| "Advantages of Structured Hardware,"<br>Harold W. Lawson, Jr., Linköping Högskola and Bengt Magnhagen, Datasaab                                                   |

| "Concepts of the MATHILDA System,"<br>Peter Kornerup, University of Aarhus                                                                                        |

| "SOCRATES,"<br>Caxton C. Foster, University of Massachusetts                                                                                                      |

| "Conjoined Computer Systems: An Architecture for Laboratory Data Processing and Instrument Control,"<br>Donald F. Wann and Robert A. Ellis, Washington University |

| "A Distributed Function Computer for Real-Time Control,"<br>E. Douglas Jensen, Honeywell, Inc. Systems and Research Center                                        |

| "Switched Multiple Instruction, Multiple Data Stream Processing,"<br>C.H. Radoy and G.J. Lipovski, University of Florida                                          |

| "Sequentially Encoded Data Structures that Support Bidirectional Scanning,"<br>Robert J. Lechner, Honeywell Information Systems                                   |

| "An Instruction Class for an Extensible Interpreter,"<br>Martin Freeman, American University                                                                      |

| "STARLET — A Computer Concept Based on Ordered Sets as Primitive Data Types,"<br>W.K. Giloi and H. Berg, University of Minnesota                                  |

| "A Cellular General Purpose Computer,"<br>R.G. Cornell, Bell Laboratories and H.C. Torng, Cornell University                                                      |

| "A Machine-Oriented Resource Management Architecture,"<br>Barry C. Goldstein and Thomas W. Scrutchin, IBM                                                         |

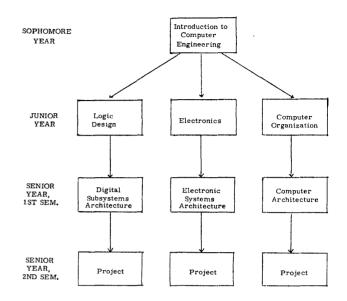

| "A Design-Oriented Computer Engineering Program,"<br>M.E. Sloan, Michigan Technological University                                                                |

| "An Educational Laboratory in Contemporary Digital Design,"<br>Janis B. Baron and D.E. Atkins, University of Michigan                                             |

PAGE

## REFEREES

The persons listed below have contributed their time and efforts to the reviewing process for this symposium, and their invaluable assistance is gratefully acknowledged.

| M. D. Abrams                                                                                                                                      | S. Kamal                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| D. E. Atkins                                                                                                                                      | H. D. Kerr                                                                                                                                           |

| J. F. Callan                                                                                                                                      | W. K. King                                                                                                                                           |

| K. M. Chandy                                                                                                                                      | T. A. Laliotis                                                                                                                                       |

| H. G. Cragon                                                                                                                                      | G. J. Lipovski                                                                                                                                       |

| D. C. Davis                                                                                                                                       | H. Lorin                                                                                                                                             |

| J. B. Dennis                                                                                                                                      | A. B. Marcovitz                                                                                                                                      |

| M. P. deRegt                                                                                                                                      | P. N. Marinos                                                                                                                                        |

| R. A. Ellis                                                                                                                                       | 0. E. Marvel                                                                                                                                         |

| T. Y. Feng                                                                                                                                        | E. I. Organick                                                                                                                                       |

|                                                                                                                                                   |                                                                                                                                                      |

| E. A. Feustel                                                                                                                                     | L. Presser                                                                                                                                           |

| E. A. Feustel<br>C. C. Foster                                                                                                                     | L. Presser<br>D. M. Robinson                                                                                                                         |

|                                                                                                                                                   |                                                                                                                                                      |

| C. C. Foster                                                                                                                                      | D. M. Robinson                                                                                                                                       |

| C. C. Foster<br>S. J. Garrett                                                                                                                     | D. M. Robinson<br>S. W. Sherman                                                                                                                      |

| C. C. Foster<br>S. J. Garrett<br>H. Glass                                                                                                         | D. M. Robinson<br>S. W. Sherman<br>D. P. Siewiorek                                                                                                   |

| C. C. Foster<br>S. J. Garrett<br>H. Glass<br>M. J. Gonzalez                                                                                       | D. M. Robinson<br>S. W. Sherman<br>D. P. Siewiorek<br>M. E. Sloan                                                                                    |

| C. C. Foster<br>S. J. Garrett<br>H. Glass<br>M. J. Gonzalez<br>T. G. Hagan                                                                        | D. M. Robinson<br>S. W. Sherman<br>D. P. Siewiorek<br>M. E. Sloan<br>J. Staudhammer                                                                  |

| <ul> <li>C. C. Foster</li> <li>S. J. Garrett</li> <li>H. Glass</li> <li>M. J. Gonzalez</li> <li>T. G. Hagan</li> <li>R. W. Hartenstein</li> </ul> | <ul> <li>D. M. Robinson</li> <li>S. W. Sherman</li> <li>D. P. Siewiorek</li> <li>M. E. Sloan</li> <li>J. Staudhammer</li> <li>H. S. Stone</li> </ul> |

L. Nisnevich & E. Strasbourger

Computer Science Department Technion, Haifa, Israel

of data transmission within real time parallel systems. Control is effected by a number of identical units which are uniformly distributed among sender-receivers. When senders desire a transmission channel, their units try to capture the channel. The unit having the highest priority captures the channel. We describe a procedure for assigning and changing unit priorities under the constraint that customer service indices remain above given levels. The suggested procedure can be used to assign priorities in real time systems.

Index Terms. real time, parallel processing, decentralized control, priority control, data communication, channel control, priority assigning.

#### Introduction

In this paper, we are concerned with real time parallel systems and in particular with their data communication subsystems. In parallel systems decentralized control increases flexibility and reliabil-ity. The following comment deals with this important feature of parallel system organization:

"While graceful degradation is desirable in many commercial applications, it is essential in any military system where the results of complete system failure for even a short period of time could be catastrophic. The importance of this aspect of parallel processor techniques is further enhanced in military systems, since they face the loss of part of the system hardware not only from normal equipment and hardware failures, but also from the results of enemy action such as shell or bomb damage. In the latter case, however, it is important to note that this advantage of a parallel organization may be largely nullified unless the components of the parallel system are distributed physically as well as conceptually."

Recently, some publications have appeared 2,3,4 related to a data communication system with decentralized control proposal by Pierce<sup>5</sup>. Control is effected by distributing control units throughout the system. Pierce system has many advantages, but data communication control in a real time system may require interrupts and priority servicing. It is difficult to include such features in a Pierce system. Other proposals<sup>6,7,8</sup> for decentralized data communication priority control in real time parallel computers have been based on the ideas of associative memory. Using these ideas, it is possible rq achieve complete decentralization of priority control . For such systems it is interesting to investigate the possibility of controlling priority parameter values in decentralized ways. This paper contains the outline of some results relating to decentralized priority control. First we shall consider schemes for the realization of dispersed control and then consider a scheme for changing priority values. We shall limit our discussion and consider only those systems in which the order of servicing is defined by absolute static priorities. The suggested methods may be extended to other systems.

Changing the order of servicing involves a reassignment of customer priorities. The purpose of such changes in this context is to find permissible priorities, i.e. to generate permissible values for multiple service

This paper describes a new principle for the control indices. Such indices describe the level of customer ata transmission within real time parallel systems. service. Their values should not exceed the limits specified by the conditions under which customers operate. Examples of service indices are: average time between arrival and fulfillment of customer requirements for service, average number of customer requirements awaiting service more than a fixed limit. Such problems are important in real time computer systems. Their solution can have a strong influence on the structure of those hardware and software components which interact among the subsystems.

#### Channel Capturing Units (CCU)

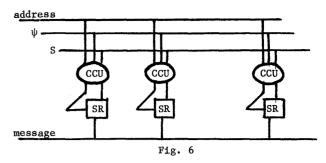

Consider a channel connecting some sender-receivers (SR). We shall describe the decentralized control of the transmission time distribution to sender-receivers where the addresses of the SR's are fixed. This method was suggested in  $1970^{13}$ . The address of all

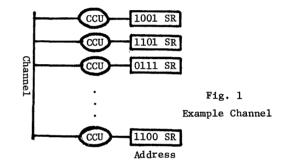

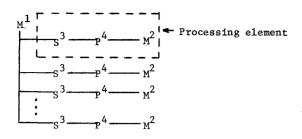

SR's are binary numbers having an identical number of bits which determine the priority assigned to the SR. Each SR is provided with a channel capturing unit (CCU) (Fig. 1). If it is necessary to transmit a message, SR, switches CCU, into the active state. While in this state, CCU, is watching the state of the channel.

The channel may be in three states: "transmit 1", "transmit 0", or "no transmission". The "no transmission" signal causes all of the active CCU's to transmit the highest bit (left most) of their addresses into the channel. In other words, after a message has been transmitted and the channel turns into the "no transmission" state, the active CCU's start transmitting their addresses into the channel. If at least one of the transmitted bits is one then the channel is in the state "transmit 1", while if all the transmitted bits are zero, the channel is in the state "transmit 0". CCU, of SR, compares the state of the channel with its own<sup>1</sup> highest bit. If the channel is in the state "transmit 1" and CCU, has transmitted a "O", then it switches itself off and awaits the next "no transmission" state. Otherwise, CCU, remains connected to the channel.

Each CCU which remains connected to the channel transmits into the channel its second address bit and the channel turns into state of either "transmit 1" or "transmit 0". All of the CCU's which have sent their second bit behave as they did following the transmission of their first bit. In other words, if the channel is in the state "transmit 1" then all the CCU's which have sent the signal "O" are switched off and await the next "no transmission" state. This process

is repeated until all the address bits have been transmitted.

After the last bit is transmitted, only one SR remains connected to the channel (its CCU having captured the channel). The address of this SR is greater than the addresses of all of the other SR's that have been trying to occupy the channel during this period.

#### Example

Let the senders that require transmission time have the addresses 1001, 1101, 0111, and 1100 (as shown in Fig. 1). During the transmission of the highest bit the SR having the address 0111 will stop transmitting its address. The rest will start transmitting the second bit of their addresses. At this moment the SR having the address 1001 will stop its transmission. The remaining two SR's will transmit the third bits of their addresses which are 0. Therefore, they will continue to transmit their addresses. While the fourth bit is being transmitted, the SR having the address 1100 will stop transmitting. Thus, the channel will be occupied by the SR with address 1101.

After all the bits of the address have been transmitted, the CCU of the sender occupying the channel transmits the destination address and having received an answer as to whether it is free either starts sending a message for its SR or switches off and after some time repeats its attempt to establish communication with the same receiver.

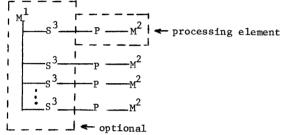

#### Parallel Channel Capturing Units

Now consider a parallel scheme realizing decentralized control of the channel (Fig. 1). This scheme incorporates priority interrupt, whereby a higher priority CCU can preempt the channel from a lower priority CCU that is currently using the channel. For this approach the channel must have a line for each address bit plus a line for the message. Each line may be in one of two states: "transmit 0" if the line is dormant, or "transmit 1" if the line is set by one or more CCU's. Each active CCU continually attempts to capture the channel as follows: (see Fig. 2).

If the most significant address bit of an active CCU is a 1, then the CCU sets the most significant address line to "transmit 1" and activates the next most significant bit capture logic. Also, if the most significant bit is a 0 and the most significant address line is "transmit 0", the CCU activates the next most significant bit capture logic. However, if the most significant bit is a 0 and the corresponding address line is a"transmit 1", then the CCU simply waits for either a change in state of the address line (indicating that a higher priority CCU has relinquished the channel) or a change of state of the address bit (indicating a raise in priority of the CCU).

Thus, if the most significant address bit of an active CCU matches the corresponding address line of the channel, then the next most significant address line is set or compared and so on throughout the address lines or until a mismatch occurs. Only the address of the highest priority SR will completely match the channel address and force channel capture by its CCU. However, there is a transient time when two or more SR's might think they match the channel address (i.e. a logical 1 occurring at point "address match" in Fig. 2). This is because of transmission time lag from the time a higher priority CCU sets an address line to "transmit 1" and the time that the same address line at a lower priority SR switches from "transmit O" to "transmit 1". This transient effect is eliminated by the settle detect, which has an output of 1 if and only if the "address

match" stays at 1 for a sufficient period of time T as explained below.

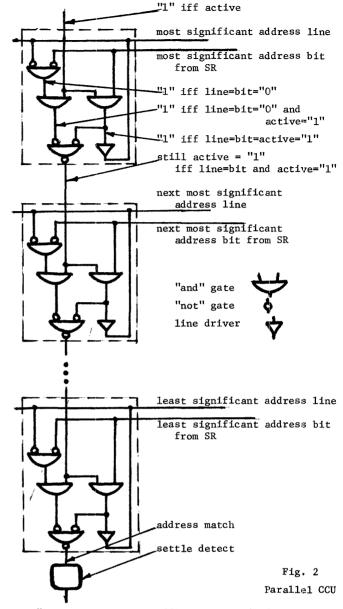

For example consider the channel in Fig. 1 with the number n of bits per address equals 4, with maximum channel transmission time  $t_{\rm T}$ , and with maximal gate delay time  $\tau$ . Let the SR with address Oll1 have control of the channel and let an SR with address 1111 become active which is t < t<sub>r</sub> time along the channel away from the Oll1 SR. The Oll1 SR will not release the channel until the following chain of events occurs: (see Fig. 3)

1. The "transmit 1" on the most significant address line propagates from the 1111 SR to the Oll1 SR (time t  $< t_{T}$ )

2. The most significant address bit mismatch propagates through the 3 gates of the capture logic at each of the n = 4 address bit positions (time <  $3n\tau$ ).

Therefore the 1111 SR has to wait a maximum time of  $t_{\perp}$  + 3nT before the 0111 SR (or any other SR) releases control of the channel. A settle detect element of time delay T =  $t_{\perp}$  + 3nT is thus needed after detection of a complete address match before a CCU can capture channel control for its SR. The CCU settle detect (Fig. 2)

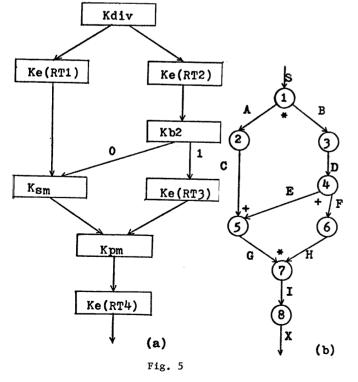

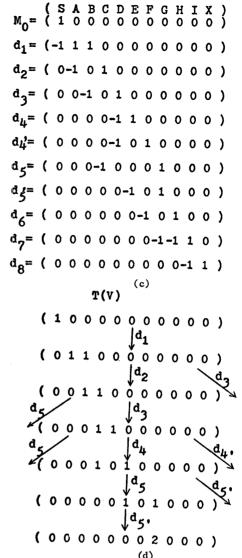

Fig. 5

Worst Case Active CCU Active Pulse Propagation Of Star Configuration (Shown Linearly For Clarity)

provides this delay in a decentralized manner and assures that the channel is controlled by at most one SR.

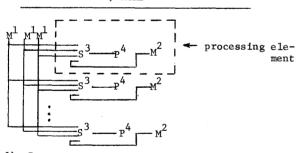

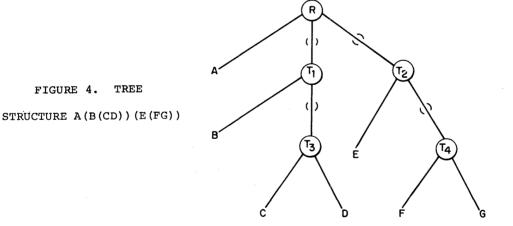

It is also interesting to examine the maximum time that an active SR with the highest priority must wait while its active pulse propagates through its CCU until it reaches its settle detect element. Consider the following worst case as illustrated in Fig. 4 and Fig.5.

Let a channel address contain n address bits and let the SR's be arranged in a star such that each SR is t\_ distant along the channel from all others. Furthermore, let an SR with address 101010...10 become active while an SR with address 0101...01 is in control. Also assume that SR's with addresses 1001..., 101001..., etc., become active at their critical worst effect times. Then the active signal propagation of the CCU with address 1010...10 can at worst follow the path as shown in Fig. 4 and Fig. 5, taking  $\Delta t = nt_{\perp} + 3nt$  time. This sequence of events is unlikely but possible. Adding this active propagation time nt\_ + 3nt to the settle detect time of t\_ + 3nt yields a time of (n+1)t\_ + 6nt as a maximum bound **G**n waiting before the highest priority active SR obtains control of the channel. Notice that the higher the SR priority with the most consecutive address bits set to 1, then the less the waiting time for active pulse propagation. In particular, an SR with address containing all 1 bits waits only 2nt time until its delay element is activated.

Two advantages of the parallel scheme are:

1. Channel capture is much faster (at least an order of magnitude).

2. Priority interrupt is built in to the scheme alleviating the need to incorporate separate protocol and logic.

A disadvantage of the parallel scheme is the additional address lines (or higher bandwidth) needed in the channel.

#### Changing Priority Parameters

The general approach to the problem of selecting priority parameters is as follows. Assume that a system serves some fixed number N of customers denoted by i; i = 1, 2, ..., N. On the basis of some a priori considerations all the customers are divided into several groups which are assigned different priorities. Quantitative characteristics of system behavior are then specified only for the whole system and for the selected groups. These characteristics determine the sort of necessary priorities. Since each group is generally considered to have a unique priority the search routines which select adequate priority sets must use priority permutations.

A system in which customers are separated into L groups where each group has a different priority can be described as follows. Let us assign each customer i (i = 1, 2, ..., N) a priority parameter  $P_i$  and let the value of  $P_i$  be equal to the priority of the group to which the customer belongs. Therefore, all customers belonging to the same group will have identical parameter values, while the total number of different values will be L. The queue discipline is determined by priority parameter  $P_i$  in the following manner. Customer i has a higher priority with regard to customer j if  $P_i > P_i$ . Requirements of customers having identical values of priority parameters are serviced in the order "first come, first serve". Using this approach the value of each priority parameter  $P_i$  can be changed independent of the other priority parameters.

To illustrate, consider a given number L of priority groups dividing all the customers. Pick any customer i and let his priority parameter value change continuously from  $-\infty$  to  $+\infty$ . Observe the changes taking place in the system. At the outset i will represent a separate group having the lowest priority. Then as the value of P<sub>1</sub> becomes equal to the parameter value of the lowest priority group this customer will be included in it. Subsequently he will constitute a separate group again having a higher priority than this first group but a lower priority than the rest. This process will continue until customer i forms a separate group with the highest priority.

#### Priority Parameter Value Changing To Get Adequate Service

The possibility of changing priorities independently allows a system to respond in a very simple way to customer dissatisfaction when the level of service falls below a permissible value. Under such conditions the values of priority parameters for dissatisfied customers should be increased while leaving the rest unchanged.

In order to appreciate the need for demonstrating the validity of this simple procedure, consider another simple process of selecting priority parameters. Choose the group of customers with the highest priority among all the groups whose level of service is inadequate. Interchange the priority of this group with that of the group having the next higher priority. Then continue this process of interchanging group priorities until the level of service is adequate for all groups in the system.

queueing discipline even when there is such a discipline. By way of illustration, select three groups of customers whose assigned priorities correspond with their numbers (1, 2, 3). Assume that under such a queueing discipline the level of service is inadequate only for the first group. Also assume that if we interchange priorities of the first and second groups then the level of service will be inadequate only for the second group. Continuing in this manner, we will return to the initial state and the process will cycle. If assigning the third group the lowest priority would in fact solve the problem, then this process will not find the solution.

Let us now return to the process of independent parameter change. This process ensures a solution of the problem whenever service indices possess certain properties described below. This method also permits the assignment of customers to a specified number of priority levels within the constraint of adequate service, providing such an assignment is possible at all.

For a fixed arrival and service pattern, the values of service indices depend only on the vector  $P = (P_1, P_2, ..., P_N)$ . Denote the total set of service indices which have the property that each index is associated with exactly one customer by  $\phi_1(\overline{P}), \phi_2(\overline{P}), \ldots, \phi_r(\overline{P})$ . Some subset of these indices indicate the service level of the first customer, another subset that of the second, etc. Denote the permissible level of the  $\phi_k(\overline{P})$  index by C<sub>k</sub>. Let the components of vector  $\overline{P}*$  be a permissible set of priority values for which the following system of inequalities holds:

$$\phi_{L}(\bar{P}^{*}) \geq C_{L}$$

(k = 1, 2, ..., K)

If we want to find a permissible set of parameters for a system in which the number of priority levels does not exceed L then we have to introduce an additional constraint that the components of the vector  $\overline{P}*$  take no more than L different values.

Note that any vector  $\overline{P}$  whose components differ from the corresponding components of a vector  $\overline{P}$  by the same value defines the same queueing discipline. Therefore, the service indices  $\phi_1(\vec{P})$  do not change along the straight line defined by:

$$P_{1} = P_{1}^{(0)} + t$$

$$P_{2} = P_{2}^{(0)} + t$$

$$P_{N} = P_{N}^{(0)} + t$$

where  $\overline{P}^{(0)}$  is any fixed vector and  $-\infty < t < +\infty$ .

Many service indices used in practice such as the examples cited earlier for the case of service by a single machine or a single channel have a so called monotonicity property which is explained as follows. Let  $\phi(\overline{P})$  be a service index of customer 1. If the vector  $\overline{P}^{(1)}$  is generated from the vector  $\overline{P}^{(2)}$  by decreasing the value of any priority parameter excluding the i-th, then  $\phi(\overline{P}^{(1)}) \geq \phi(\overline{P}^{(2)})$ .

For monotonic systems in which all service indices  $\phi_1(\overline{P}), \phi_2(\overline{P}), \ldots, \phi_k(\overline{P})$  possess the monotonicity property, the problem of finding a permissible set  $\overline{P}*$  of priority values is solved by the process which we will call "simple descent" and denote by II. The initial set of

parameter values may be represented by any integer component vector  $\overline{P}^{(0)}$ . If at some stage of the\_process If we have determined a set of parameter values  $\overline{P}$  then the next stage will involve the following procedure. process of interchanging group priorities until the Choose a service index  $\phi_{L}(\overline{P})$  for which the inequality of service is adequate for all groups in the system.  $\phi_{L}(\overline{P}) \geq C_{L}$  does not hold for the vector found at the previous stage. Let  $\phi_{L}(\overline{P})$  be the service index of cus-Such a process does not always lead to a satisfactory tomer 1 which means that this customer receives inadequate service for this index  $\phi_k$ . We will assume that inadequate service for one index means inadequate service in general. The value of parameter P. in the vector  $\vec{P}$  is replaced by (P<sub>1</sub>+1) while the rest of the components do not change. It has been shown<sup>9</sup> that the process  $\Pi$ terminates in a finite number of stages not exceeding N(N-1) and results in a permissible set of priority parameter values provided such a set actually exists.

> If we initially adopt the queueing discipline "first come, first serve" for all the requirements of all customers (this discipline is specified by a vector  $\overline{P}(0)$ with equal components) then the process  $\Pi$  will result in a set of priority parameter values in a number of stages less than N(N-1)/2. This set of values determines an adequate service level for all the customers with a minimum possible number of priority levels. In case an adequate set of parameter values does not exist, the process will result in a situation demonstrating this fact during the same number of stages. Therefore, the process having an initial vector with equal components solves the problem of assigning customers to priority levels when the number of levels must be limited.

At any stage of the process II the values of service indices of several customers might lie below corresponding permissible values. In such a case one can choose one of these indices and raise the value of the priority parameter associated with the corresponding customer. It is possible to raise the values of several priority parameters simultaneously. The set of parameter values generated by the process I does not depend on this choice, but is determined by the initial vector  $\overline{P}(0)$ .

It is important to stress that in order to realize the search process one does not need to know the values of the functions  $\phi_k(\overline{P})$  (k = 1,2,...,K). The only essential information is whether these values lie below specified levels. In other words it is only necessary to know if each customer is getting adequate service when the set of priority values is given.

#### Example

There are four customers in the system. Their requests arrive independently in conformity with a Poisson distribution. The customers are serviced by a single channel with exponential service times. The parameters of the corresponding distributions for each customer are:

$$\lambda_1 = 1/5$$

$\lambda_2 = 1/20$   $\lambda_3 = 1/10$   $\lambda_4 = 1/20$

$\mu_1 = 1$   $\mu_2 = 1/4$   $\mu_3 = 1/2$   $\mu_4 = 1/4$

The average total time (ATT) any requirement is in the system should not exceed 4 units for the first customer, 5 for the second, 16 for the third, and 30 for the fourth.

To find the values of the priority parameters satisfying these constraints, consider the operations of process  $\Pi$ . At the outset assign priorities in the order of decreasing the values of the given constraints (ATT), i.e. the initial vector  $\overline{P}^{(0)}$  will be equal to (4,3,2,1). Under this queueing discipline the average total times are 1.25 for the first customer, 8.75 for the second, 9.17 for the third, and 37.50 for the fourth. As we can observe, this apparently natural set of priorities does not satisfy customers 2 and 4.

At the first stage of process  $\Pi$  raise the priority parameter values of customers 2 and 4. Then we obtain

priority vector  $\overline{P}^{(1)} = (4,4,2,2)$ . Under this queueing discipline, the average total times are 2.07, 5.07, 14.33, and 16.33. Now only the second customer is not satisfied. By raising his priority parameter value, we obtain the vector  $\overline{P}^{(2)} = (4,5,2,2)$ , which gives times of 3.33, 5, 14.33, and 16.33, thereby satisfying all of the customers. In this case partitioning the customers into three priority levels is sufficient and in addition is the only possible solution.

This method of changing parameter values in order to determine an adequate queueing discipline can be applied when the order of servicing depends on priority in other ways, i.e. in other classes of priority systems<sup>10</sup>. To ensure efficiency of the process  $\Pi$ , it is sufficient that service indices remain monotonic functions of priority parameters. Other papers<sup>11</sup> are devoted to the study of such systems and contain proofs of the efficiency of the simple descent procedure.

For real time systems the process  $\Pi$  may serve as a means to introduce dynamic priorities. Specifically, such priority will adapt to changes in the system and modify priority parameters when the values of service indices approach their limits provided external conditions change sufficiently slowly<sup>9</sup>,<sup>10</sup>.

#### Distributed Control of a Multiplex Channel For Real Time Systems

Consider now the channel capture units as described earlier. Let the address of each SR consist of three parts:  $A = p \ s \ a$ .

Part p is the binary value of the customer priority parameter. This part changes independently as determined in the simple descent mode II as just described. A modification of II is required however, because of the upper limit of priority values, to prevent all customer priorities settling at the highest level. When an SR attains the highest priority level and is still not receiving adequate service, then its CCU will send the pulse "1" into the auxiliary channel  $\psi$  (Fig. 6). Each other CCU will respond by lowering its priority parameter p.

Part s is employed to provide the order of servicing "first come, first serve" among the SR's having equal priority values. This part of A is formed in the following manner. The value of s is 0 for all inactive SR's. When a requirement arrives and the CCU becomes active, it sends the signal "1" into the auxiliary channel S (Fig. 6). From this moment each "1" which is entered into the auxiliary channel S due to the activation of a channel capture unit is added to the value of s for each CCU awaiting transmission time. Among the senders belonging to the same priority group, the one whose waiting time for message transmission is the longest has the greatest value of s. After a message is transmitted and its SR becomes passive, its s returns to 0.

Address part a is the number (personal address) of an SR. This part is necessary only because address part p s may have the same value for two SR's. The auxiliary channels  $\psi$  and S can be combined into one line by special coding of the limit and the longevity pulses.

Thus in such a data communications system with decentralized control, transmission time is granted to an SR with the highest priority parameter value. In case of ties, an SR with the longest waiting time is chosen. If ties still remain, the SR having the greatest personal address is serviced.

Priority interrupt is built in to the parallel CCU scheme. For the serial CCU scheme a multiplex channel with interrupt capabilities may be organized by dividing the channel into two channels: one to transmit the

Priority Interrupt Channel With Distributed Control

addresses of the SR's and the other to transmit the regular messages (see Fig. 6). In this case the SR's try to capture the message channel by sending their addresses along the address channel after a "no transmission" state has appeared in the address channel. The CCU occupying the address channel transmits into this channel the address of the required receiver and connects its sender to the message channel. After this it creates a "no transmission" state in the address channel (i.e. switches off this channel) but remains active. When the "no transmission" state appears, the CCU's start to fight for the channel by trying to transmit addresses into the address channel. A CCU only disconnects its sender from the message channel when it has completed sending the message or when it has been preempted by another CCU. In the latter case its transmission time is interrupted and another SR with higher priority connects to the message channel and transmits its message. When a sender has completed its message it causes its CCU to enter the passive state and the CCU does not make any attempt to reference the address channel until it again becomes active.

Papers<sup>14,15</sup> are devoted to the problems of broadening the functional possibilities of multichannel and multiloop data communication systems based on the principles discussed above. These papers also consider design methods for such systems.

The decentralized distributed control systems des-Part s is employed to provide the order of servicing cribed above have a great deal of flexibility. In case st come, first serve" among the SR's having equal such a system connects highly organized devices such as rity values. This part of A is formed in the follownanner. The value of s is 0 for all inactive SR's. a requirement arrives and the CCU becomes active.

#### Conclusions

Parallel computers inherently have a communication control problem. Schemes have been presented in this paper to realize the following control capabilities:

- 1. decentralized priority control

- 2. decentralized priority changing

- 3. priority interrupt handling

Decentralized priority control using small channel capturing units enables efficient communication path utilization between parallel processors. Decentralized priority changing using independent priority determining automata alleviates unacceptable service conditions and lockouts. Priority interrupt handling allows minimal response time for most critical tasks. The implications of these capabilities upon parallel architecture should be investigated.

#### References

L.C. Hobbs and D.J. Theis. "Survey of Parallel Processor sor Approaches and Techniques". Parallel Processor Systems, Technologies and Applications, Ed. Hobbs, New York - Washington, 1970.

- W.J. Kropfl. "An Experimental Data Block Switching System". The Bell System Technical Journal, Vol.51, No.6, 1972.

- 3. C.H.Coker. "An Experimental Interconnection of Computers through a Loop Transmission System". The Bell System Technical Journal, Vol.51, No.6, 1972.

- E.E. Newhall, A.N. Venetsanopoulos. "Computer Communications-Representative Systems". Proc. of the IFIP Congress 71, Vol.1, Amsterdam-London, 1972.

- 5. J.R. Pierce. "Network for Block Switching of Data". The Bell System Technical Journal, Vol.51, No.6,1972.

- R.J. Gountanis, N.L. Viss. "A Method of Processor Selection for Interrupt Handling in a Multiprocessor System". Proc. of the IEEE, Vol.54, No.12, 1966.

- 7. M. Lehman. "A Survey of Problems and Preliminary Results Concerning Parallel Processing and Parallel Processors". Proc. IEEE, Vol.54, No.12, 1966.

- J.A. Githens. "An Associative, Highly-Parallel Computer for Radar Data Processing". Parallel Processor Systems, Technologies, and Applications, Ed. Hobbs, Spartan Books, New York - Washington, 1970.

- L.B. Nisnevich, G.G. Stetsyura. "Organization of Choice of Static Priorities in Systems with Decentralized Control". I. II. Automation and Remote Control, No. 6,7, 1971.

- 10. L.B. Nisnevich. "Organization of Service in Class of  $\theta\text{-Priorities"}.$  Automation and Remote Control, No. 8, 1969.

- L.B. Nisnevich, G.G. Stetsyura. "Decentralized Control of Customers Interaction in Single-Step Systems of Resource Flow Allocation I,II". Automation and Remote Control, No. 5,6, 1972.

- 12. L.B. Nisnevich, G.G. Stetsyura. "Decentralized Control by the Simplest Descent Method Using Inaccurate Information". Automation and Remote Control, No.29, 1972.

- 13. G.A. Kotyujanski, L.B. Nisnevich, G.G. Stetsyura. "Decentralizovanoye prioritetnoye upravleniye v odnokanalnoy systeme obmena danimi". Izv. ANSSSR, Technitcheskaya Kibernetika, No.6, 1970.

- 14. L.B. Nisnevich, G.G. Stetsyura. "Mnogokanalnaya decentralizovanaya prioritetnaya sistema". Izv.ANSSSR, Technitcheskaya Kibernetika, No.2, 1971.

- L.B. Nisnevich, G.G. Stetsyura. "Application of Principles of Decentralized Priority Control in Integral Systems of Data Transmission". Automation and Remote Control, No.5, 1971.

#### A LOOP NETWORK FOR SIMULTANEOUS TRANSMISSION OF VARIABLE-LENGTH MESSAGES

Cecil C. Reames and Ming T. Liu Department of Computer and Information Science, and Mechanized Information Center The Ohio State University Columbus, Ohio 43210

#### Abstract

A loop (ring) system is proposed for distributed computer networks which: 1) allows simultaneous transmission of variable-length message frames, 2) minimizes loop access and transmission times, and 3) provides a form of automatic traffic regulation. The ring interface transmitter which performs these three functions is described, and a conceptual model of its operation is developed. The model illustrates a technique by which the ring interface transmitter can delay incoming messages by hardware buffering just long enough for a variable-length output message to be placed on the loop. It is shown how advantage can be taken of gaps between incoming messages to clear out the delay buffer and to make room for future outgoing messages. It is further demonstrated that an interesting form of automatic message traffic regulation results from use of the proposed technique. Possible hardware implementations of the model are also considered, using a variable-length shift register for the incoming message delay buffer. The probable effects of the proposed technique on message transmission are discussed, and ongoing analytic and simulation studies are described.

#### I. Introduction

The loop topology is becoming increasingly popular today for the design of distributed computer networks [3,4,5,6,7,8,13,14,17,18]. A loop network consists of a high-speed digital communication channel, arranged as a closed loop (ring), to which the nodes (which may be processors, peripherals or terminals) are attached through simple ring interfaces. Messages are sent from a source node as addressed blocks of data which travel around the loop from interface to interface until picked off by the destination node. Some of the major advantages of a loop network are: 1) the ease of controlling information, 2) the simplicity of message routing, 3) the high rate of data transmission, 4) the facility to attach dissimilar nodes through a standard ring interface, and 5) the low costs of construction and incremental expansion.

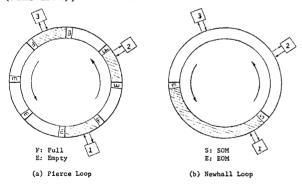

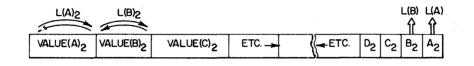

With only a few exceptions, most loop systems studied or constructed have employed the concept of fixed-size frames (slots) for message transmission [3, 4,5,8,9,13,17]. Such systems, as illustrated by Fig.la, are sometimes called Pierce loops. The reason for using a fixed-size frame is that message transmission protocol and ring interface hardware are thereby greatly simplified. The loop is initially filled with an integral number of empty frames, where a bit in the control field of each frame specifies if that frame is empty (not in use) or full (in use). If a node has a message it wishes to output which is shorter than the frame size, it simply waits for an empty frame to appear and then inserts its message into that frame; the unused frame space is wasted. On the other hand, should the output message be longer than the frame size, it must be broken down into frame-size packets and transmitted one packet at a time. The disadvantages of this approach are obvious: message space on the loop is wasted for short messages, while longer messages require elaborate buffering and disassembly/assembly techniques. Clearly, it would be more efficient if variable-length messages could be transmitted directly as variablelength frames.

A few attempts have been made to provide loop systems for transmission of variable-length message frames, but such systems, using Newhall loops as shown in Fig. 1b, have been severely handicapped by their inability to allow simultaneous message transmission [6,14]. Newhall loops operate under a round-robin control-passing mechanism which permits only one node at a time to transmit an arbitrary length message onto the loop. This restriction, although highly inefficient as far as loop utilization and message transmission is concerned, is absolutely necessary. Otherwise, two or more messages transmitted onto the loop during overlapping time periods could completely destroy each other.

It is primarily for this reason that most loop designs have favored fixed-size frames for message transmission. It seems entirely reasonable to suppose, however, that if variable-length frames could be transmitted as easily as fixed-size frames, it would be advantageous to do so. A loop system constructed for variable-length message transmission should result in faster message transmissions and better loop utilization, since no frame space (and thus time) would ever be unnecessarily wasted.

In this paper, a new ring interface design is proposed which does allow simultaneous transmission of variable-length message frames in a loop system. It will be argued that the proposed system does have the desirable properties mentioned above. It will also be asserted that the proposed scheme provides a bonus in the form of automatic traffic regulation, in the sense that access to the loop is controlled by the ring interface hardware based on the current system load and previous individual accesses. Preliminary investigation by the authors has already established the feasibility of the proposed scheme; analytic and simulation studies are now underway to verify the claims made for improved performance [18].

#### II. Design Considerations

Rather than immediately launch into a description of the proposal, it would be instructive to consider first a few of the motivating factors which led to the particular design chosen. The desired goal was a variable-length message transmission technique which would not restrict use of the loop to a single node at a time. Any such scheme must ensure that two or more messages, transmitted from different nodes during the same time period, never meet and interfere with each other. But if a completely distributed loop network is assumed, with each node acting independently and without knowledge of other nodes' actions, then it is impossible to guarantee that simultaneous transmissions will not cause messages to overlap and destroy

This research was supported in part by the National Science Foundation under grants GN-534.1 and GN-27458 and in part by the Office of Naval Research under contract N00014-67-A-0232-0022.

each other.

The obvious means of overcoming this problem is to buffer any incoming messages received at a node while an output message is being transmitted. The loop network then takes on some characteristics of a message store-and-forward network. While such a solution is obvious, it is not so easy to apply to a distributed loop network, for the nodes in such a network may well be unintelligent peripheral devices that are incapable of buffering messages.

In fact, in a loop network the node itself never sees messages not addressed to it; only the ring interface sees all messages that pass by on the loop. So if any buffering of incoming messages is to occur, it must be done entirely by the ring interface. But this requirement poses a new problem: the ring interface is a relatively simple, inexpensive (\$200-\$600) hardware device with little data buffering capability. It was deliberately designed that way to be cheap and reliable. Replacing it by a much more expensive minicomputer is not a feasible alternative, although in the future a microprocessor system might be economical. For the present time, however, it seems that the function of the ring interface must be expanded by giving it some hardware buffering capability.

Before describing how the ring interface is to accomplish this buffering of incoming messages while output is in progress, some other desirable characteristics for such a loop system will be listed for inclusion in the new design:

1) Incoming messages should experience the minimum delay possible in passing through the ring interface, the amount depending solely on the quantity of previously buffered data.

2) Outgoing message transmission should be possible at the completion of any incoming message, even if another message is incoming and must be delayed.

3) The quantity of data buffered by a ring interface should be reduced whenever possible and should be strictly limited so as to avoid unreasonable transmission delays.

4) All nodes should be allowed access to the loop as much and as often as the system can handle, but no node should be permitted to dominate the loop to the exclusion of other nodes.

## III. Proposal for New Ring Interface

With these thoughts in mind, the major functions of the ring interface proposed in this paper will now be described. The scheme chosen allows the ring interface to delay an incoming message by hardware buffering just long enough for a variable-length message to be output onto the loop. The maximum length of an output message which can be transmitted at any moment is determined by the available space in this hardware delay buffer. More space is made available by taking advantage of gaps between messages to reduce the amount of data buffered, gaps appearing either from a lack of message transmission or due to removal of a message from the loop by its receiving node. Since an output message cannot be transmitted until sufficient buffer space is available to delay possible incoming messages, and since space is made available by the accumulation of intermessage gaps whose arrival rate depends on the total system traffic, it can be seen that output message transmission is automatically regulated as a function of traffic load.

A conceptual model of the proposed ring interface transmitter will be developed in the next section, so that its operation can be explained and understood without worrying about hardware details. Following the model presentation, Section V will consider hardware implementations of the model, with several approaches being suggested. A discussion of the effects the proposed scheme might have on message transmission in a loop system will be taken up in

#### Section VI.

#### IV. Conceptual Model Development

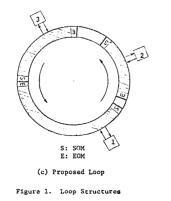

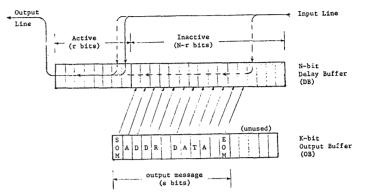

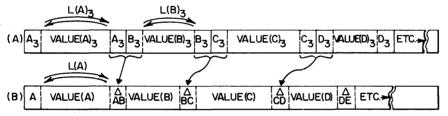

The operation of the proposed ring interface transmitter will be explained through the development of a hardware-independent conceptual model; the design of the interface receiver is not considered in this paper. Fig. 2 is an illustration of the data buffers and paths for the model. It shows an Output Buffer and a multifunctioned Delay Buffer as the two data storage devices in the transmitter. Incoming messages enter this part of the ring interface from the loop communication channel bit-serially over the Input Line. The same incoming messages (perhaps after some delay) and outgoing messages from the attached node exit the transmitter onto the loop bit-serially on the Output Line. The Input and Output Lines are synchronized at the same data rate, so that for each bit input, another is output.

The function of the Output Buffer is simply to hold the output message as it is being assembled by the attached node and while it is waiting for its transmission onto the loop to begin. When transmission actually is to start, the output message will be parallel-transferred into a portion of the Delay Buffer, freeing the Output Buffer so that it can again be filled by the attached node. Since messages are of variable length in this system, only a portion of the Output Buffer may actually be used for a particular message transmission. The attached node is allowed to output a message of any length that does not exceed the capacity of its Output Buffer.

The Delay Buffer is slightly more complicated, for it has several functions to accomplish. It is physically one storage device, but logically it can be thought of as partitioned into two distinct storage devices, the boundary of this partition being changed from time to time. In the illustration of Fig. 2, this partitioning is shown as active and inactive portions of the Delay Buffer. Consider for the moment just the active portion.

The active portion of the Delay Buffer acts as a FIFO queue that delays the retransmission of incoming messages for a specified time period. Assume the entire Delay Buffer to have a capacity for storing N bits of data, and assume that r bits are presently allocated to the active portion,  $1 \le r \le N$ , leaving N-r bits for the inactive portion. Let the bit positions in the Delay Buffer be labeled DB<sub>0</sub>, DB<sub>1</sub>,  $\dots$ DB<sub>r-1</sub>, DB<sub>r</sub>,  $\dots$ DB<sub>N-1</sub>. Choose a time scale for the rate of data transmission on the loop so that message bits arrive every one time unit. Then if the next message bit is to arrive at time t+r, the active portion of the Delay Buffer (DB<sub>0</sub>, DB<sub>1</sub>,  $\dots$ DB<sub>r-1</sub>) represents a FIFO delay queue which contains the message bits that arrived at times t, t+1,

Since the capacity of this FIFO delay queue is

bits, at time t+r the longest delayed message bit (contained in DB<sub>0</sub>) is removed from the queue and is output to the loop on the Output Line. Simultaneously, the incoming message bit from the Input Line is added to the queue (stored in DB<sub>r-1</sub>) so that the length of

the delay queue remains constant at r bits. Thus at the completion of these activities at time t+r, the new contents of  $\text{DB}_0$ ,  $\text{DB}_1$ ,  $\dots$   $\text{DB}_{r-1}$  will be the message bits received at times t+1, t+2,  $\dots$  t+r. Stated in hardware terms, the contents of  $\text{DB}_0$ ,  $\text{DB}_1$ ,  $\dots$   $\text{DB}_{r-1}$ , Input have been shifted into Output,  $\text{DB}_0$ ,  $\text{DB}_1$ ,  $\dots$   $\text{DB}_{r-1}$ .

The size of this FIFO delay queue is adjustable at each time period (if r>1), the object being to reduce r to 1 as quickly as possible. A reduction can take place only between incoming messages, when the data being received is not part of any message and thus does not need to be saved for later transmission. Thus, the preceeding explanation of the FIFO delay queue operation should be modified to state that if r>l and the bit input on the Input Line is not part of any incoming message, then the input is discarded (not stored in DB<sub>r-1</sub>) and r is reduced to r' = r-l. In effect, the logical boundary of the partition of the Delay Buffer is changed one position, so that the active portion is smaller and the inactive portion larger. When r reaches 1, no further reduction is possible, and the input is always stored in DB<sub>0</sub>

The space in the inactive portion of the Delay Buffer,  $DB_r$ ,  $DB_{r+1}$ ,  $\dots DB_{N-1}$ , is not just wasted, but also plays a very important role in the ring interface transmitter operation. It is here that output messages are transferred from the Output Buffer when they are to be transmitted onto the loop. Assume an s-bit output message has been prepared by the attached node and is in the Output Buffer awaiting transmission, Assume also that at least s+1 bits of space are available in the inactive portion of the Delay Buffer (which is of size N-r bits). That being the case, the s bits of the Output Buffer are parallel-transferred into the inactive portion of the Delay Buffer at  $DB_r$ ,  $DB_{r+1}$ ,  $\dots DB_{r+(s-1)}$ , directly adjacent to the active portion. Then if no incoming message is being received over the Input Line, r is immediately changed to r' = r+s+1; otherwise, the change is made at the end of the current incoming message.

This sudden change in r means that now the active portion of the Delay Buffer includes its previous contents  $(DB_0, \ldots DB_{r-1})$ , the message to be output  $(DB_r, \ldots DB_{r+(s-1)})$  and an extra position for delaying new input  $(DB_{r+s})$ . In effect this means that the FIFO delay queue has been expanded by s+1 positions and has had an s-bit message pushed into it. New incoming messages will enter the delay queue through  $DB_{r+s}$  and will thus be transmitted onto the loop followings the output message. Thus an output message has been inserted onto the loop between two incoming messages.

It may be the case, however, that when the output message in the Output Buffer is ready to be transferred into the Delay Buffer, insufficient space is available in the inactive portion of the Delay Buffer (N-r < s+1) for the transfer to take place. If that is true, then no output message can be transmitted by the ring interface until sufficient space becomes available in the Delay Buffer. Space is made available, however, only between incoming messages when the size of the FIFO delay queue can be reduced. Furthermore, the size of the delay queue is increased only when transmitting an output message onto the loop. Thus insufficient space for output message transmission can only happen when a node tries to output too many messages, of too long a length, over too short a time for the loop to handle. Under those circumstances, it seems entirely justifiable to force the offending node to wait for the system load to decrease before transmitting any more messages, especially since other nodes with shorter delay queues are still allowed to transmit their messages.

It should be apparent from the above discussion that the capacity of the Delay Buffer must be at least as large as that of the Output Buffer. Furthermore, it should be obvious that the greater the Delay Buffer capacity, the less likely is the chance that output message transmission will be blocked because of insufficient space being available. Thus, certain nodes can in effect have higher output priority than others, simply by increasing the sizes of their Delay Buffers. The size of the Delay Buffer is thus a design parameter which can be adjusted differently for each node to suit individual output requirements. However, it should also be observed that for messages already on the loop, transmission time is minimized by having the sum of all possible delays be as small as possible. Thus, optimization of overall system performance requires that Delay Buffer sizes be neither too excessive nor too small.

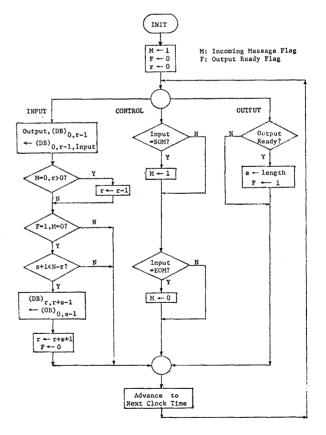

The complete operation of the model just developed is summarized in the flowchart of Fig. 3. Hopefully, the model has demonstrated (at least in concept) a plausible method by which variable-length message frames can be transmitted in a distributed loop system. In any case, it is now time to consider possible hardware implementations of the model.

## V. Hardware Implementations

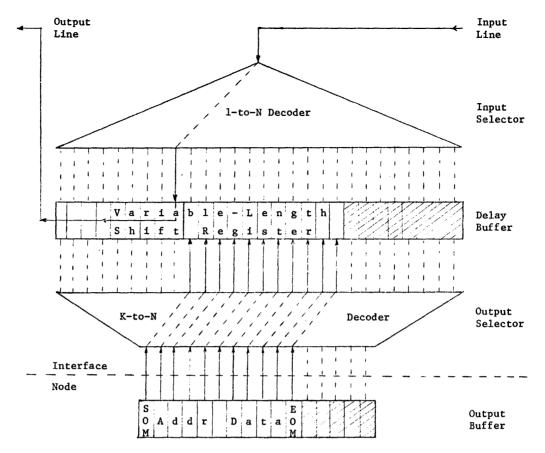

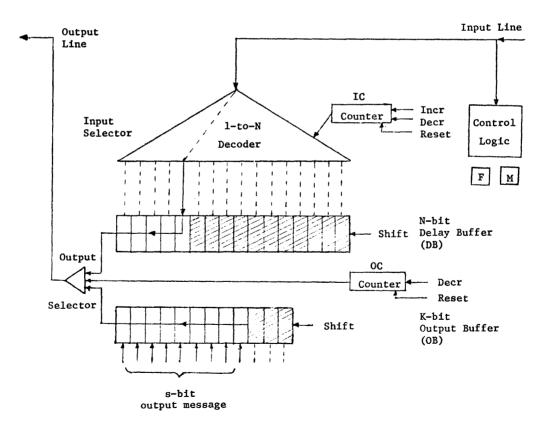

A direct translation of the model into hardware might look something like the device depicted by Fig.4. The essential feature of this implementation is a variable-length shift register which serves as the model's Delay Buffer. Only the left-most r bits of this shift register are activated (shifted), corresponding to the r-bit FIFO delay queue of the model. A 1-to-N decoder (Input Selector) is provided to gate the incoming message bits from the Input Line into the right-most active position of the shift register. The Input Selector thus defines the logical partition of the shift register into active and inactive portions. A similar K-to-N decoder (Output Selector) performs the more complicated operation of parallel-transferring s bits of an output message from the Output Buffer into the inactive portion of the shift register.

While the hardware illustrated by Fig. 4 could certainly be constructed, it would likely prove to be too expensive for a ring interface transmitter. The variable-length shift register is essential in any implementation for a Delay Buffer and thus cannot be eliminated. The same is true for some kind of Input Selector to direct incoming data into the shift register. The most expensive hardware component, however, seems to be the Output Selector, since its function is so complicated.

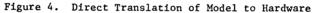

The Output Selector can be totally eliminated by separating the Delay Buffer into two distinct registers. The variable-length shift register will then be used exclusively as a FIFO message delay queue, while a second shift register will function for the inactive portion of the Delay Buffer. A further saving of hardware is possible by letting this second shift register also serve as the Output Buffer. If that is done, output messages can be assembled in the Output Buffer as before and then directly shifted out onto the loop.

This latter, more economical hardware implementation of the model is shown in Fig. 5. Now there are two shift registers which may be connected to the Output Line, the Delay Buffer and the Output Buffer, but only one or the other may be activated (shifted) at a time. If no output transmission is in progress, the Delay Buffer will be shifted out onto the loop. During receipt of incoming messages, the length of this shift register will remain constant; between messages when no valid information is being received, the length of the Delay Buffer will be decreased by one at each time period (until it is completely empty or a new incoming message arrives).

When an output message is assembled in the Output Buffer and is ready for transmission onto the loop, the control circuitry of the ring interface scans the Output Line, watching for the end of the current incoming message (if any is being received). When the end is detected and if sufficient space is available in the Delay Buffer (equal to the output message length), then the Delay Buffer is deactivated and the Output Buffer is activated, thus shifting the output message onto the loop. While its transmission is in progress, incoming message bits are saved in the Delay Buffer by increasing its length by one at each time period; between incoming messages the length of the Delay Buffer remains constant. When the last bit of the output message has been shifted onto the loop, the Output Buffer is deactivated and the Delay Buffer is reactivated to operate again as previously described.

By restricting or imposing certain limitations on the conceptual model developed in Section IV, further hardware savings are possible. It is likely that some of these limited implementations might be much more economical and just as useful for certain applications. There is no reason that several implementations of varying degrees of sophistication could not be used in the same loop network. For further information in this regard, the reader is referred to the authors' previous work [18].

#### VI. Effects on Message Transmission

Since analytic and simulation studies of this proposed loop system are still in progress, no precise statements can be made at this time concerning performance. On the other hand, a number of performance factors can be evaluated, and certain improvements can be plausibly argued. Consider the following factors concerning message transmission in the proposed system:

1) The queueing delay a ready message in the Output Buffer may experience before being transmitted onto the loop depends on its length and the amount of data already stored in the Delay Buffer. If sufficient delay space is available, transmission can begin at the end of the current incoming message. Otherwise, the queueing delay will be extended for whatever time is required to make space in the Delay Buffer. This time obviously depends in a complicated manner on total system traffic and loop utilization.

2) The transmission delay a message will experience in getting from its source to its destination node once it is on the loop is simply the sum of the delays imposed by each intermediate node. Each of these delays depends solely on the amount of data already in each Delay Buffer when the message arrives there. The transmission delay will obviously increase rapidly with increasing system load but for a worst-case upper limit can be no greater than the total capacity of all Delay Buffers.

3) For moderate to heavy traffic loads, nodes that transmit messages only infrequently should experience little queueing delay, while nodes that desire to transmit almost constantly will undoubtedly be slowed down because of limited Delay Buffer space. Thus heavy, frequent users of the loop are restricted while less frequent users still receive reasonably prompt service. Of course, the transmission delays will be about the same for all nodes.

In comparing the proposed loop system with previous fixed-size and/or variable-length loop systems, certain performance improvements and advantages can be recognized:

Variable-length message frames can be transmitted directly.

2) Simultaneous message transmission is allowed by independently acting nodes.

3) Nearly immediate access to the loop is given to any node with sufficient space in its Delay Buffer, regardless of the traffic on the loop.

4) Subsequent loop access is granted by the hardware in a manner determined by individual past accesses and current traffic.

5) Automatic access regulation tends to favor infrequent or light users and to prevent domination of the loop by one or several nodes.

6) Loop utilization and message transmission are improved due to less wasted frame space and simultaneous message transmissions.

#### VII. Conclusion

As previously mentioned, verification of these

performance claims is now underway. Research is proceeding in the areas of analytic modeling and simulation. An analytic model of the queueing and transmission delays in the proposed system is being sought as one goal. In conjunction with that work, a simulation study of loop networks is being performed. These studies are expected to yield considerable insight as to the actual operation and performance of the proposed system. The results of this research will be made available in a subsequent report [18].

It is felt that distributed loop systems with variable-length message transmission facilities could play an important role in areas as diverse as creditcard verification systems, mini-computer networks, and telephone switching systems. It is hoped that the ideas presented here may be of some interest in the future development of these and other application areas.

#### Acknowledgements

The authors wish to thank Drs. Marshall C. Yovits, Gerald J. Lazorick, and David K. Hsiao for their support and constant encouragement during the period of this research.

#### References

1. Anderson, Richard R., Jeremiah F. Hayes and David N. Sherman. "Simulated Performance of a Ring-Switched Computer Network," <u>IEEE Trans. on Comm.</u>, COM-20, 3 (June 1972), 576-591.

2. Chu, Wesley W. "Some Recent Advances in Computer Communications," Proc. First USA-JAPAN Computer Conference, Tokyo, Japan, October 1972, pp. 514-519.

3. Coker, C.H. "An Experimental Interconnection of Computers through a Loop Transmission System," <u>Bell</u> Syst. Tech. Jour., LI (Jul./Aug. 1972), 1167-1175.

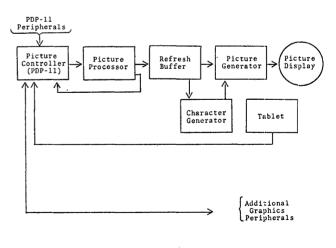

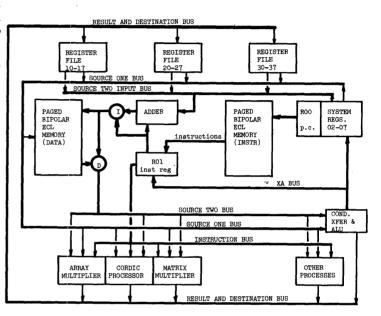

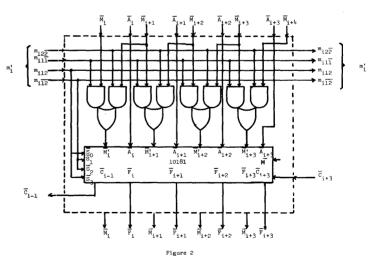

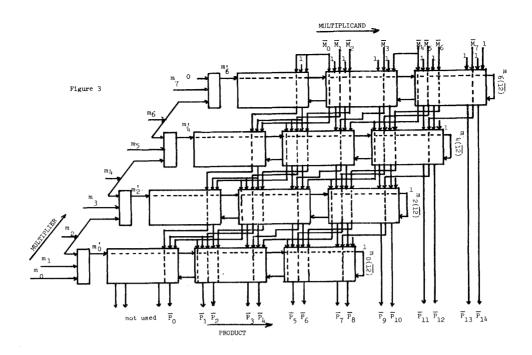

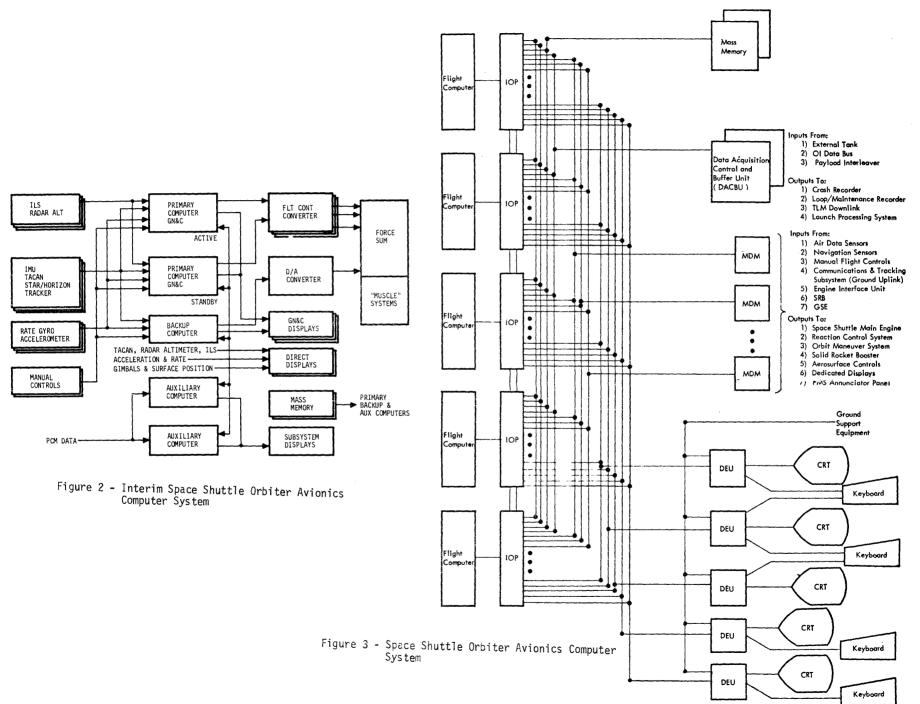

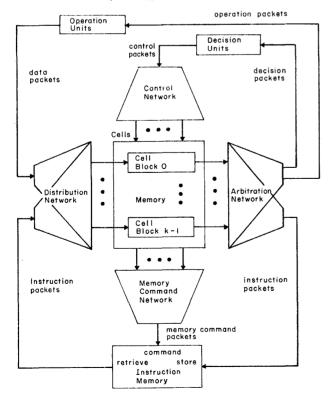

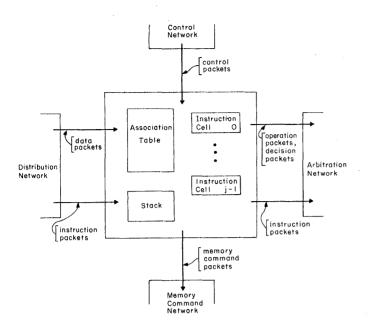

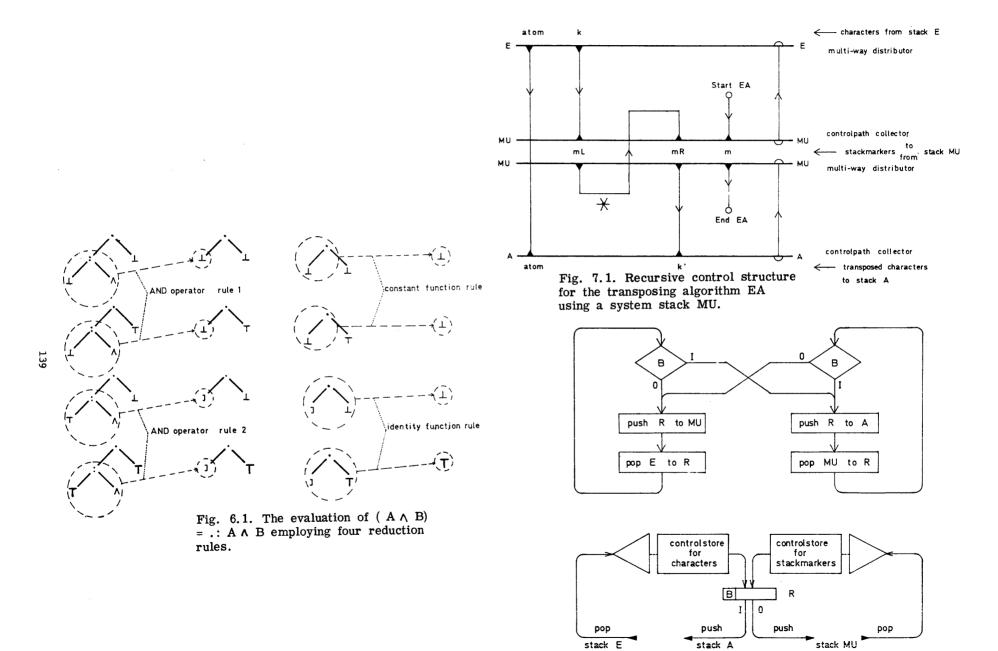

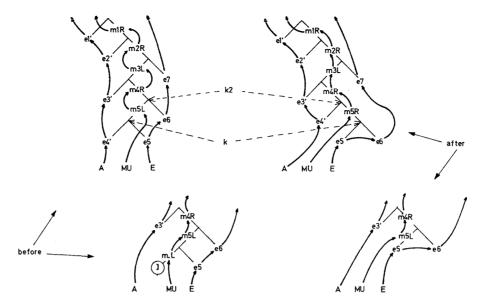

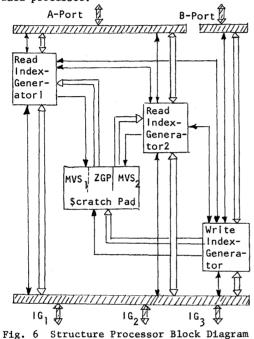

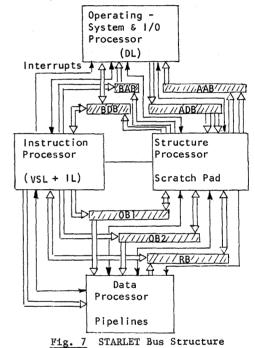

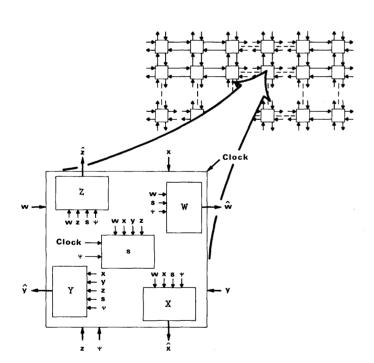

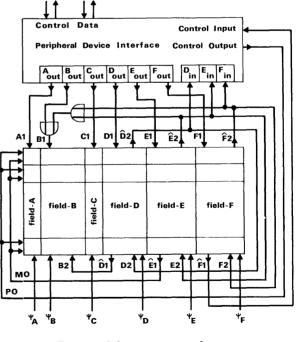

4. Farber, David J., et al. "The Distributed Computer System," Proc. COMPCON 73, Feb. 1973, pp. 31-34.