SOME RISC CHIPS ARE BORN PERFORMERS

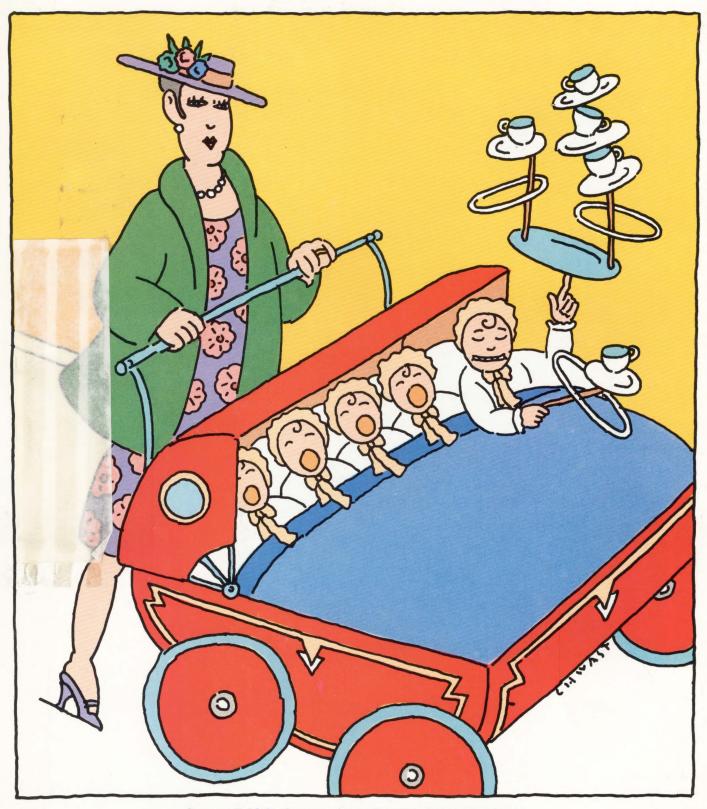

### THE POINT **OF NO RETURN.**

When you put a Fujitsu ASIC to work, you can rest assured it will work the way it should. And keep on doing its job for a very long time to come. In fact, when you look at our performance record over the years, you'll be hard pressed to find any field failures at all. This is no empty promise. Product reliability has been a way of life for us for more than 15 years

years.

That's why we always take a conservative approach to the design process. Giving you realistic worst case specs that no production device will exceed.

Guaranteeing a minimum 90% utilization of all gates. And giving you a simulation-to-production correlation of 99%.

It's also why we control every step of the production process. From design to wafer fab to assembly and final test, including 100% AC testing at frequency. So nothing is left to chance.

To us, reliability in the field is everything. And when you remember we've taken over 8,000 ASIC devices from design through mass production, you can see that we'll give you a level of confidence no one else can offer.

So count on parts that have longer life expectancies.

Call our Hot Line today at (800) 556-1234, Ext. 82; in California (800) 441-2345. Look into ASICs you can send out the door. Never to return again.

#### **CIRCLE NUMBER 1**

Technology That Works.

# Contents

#### RTICLES

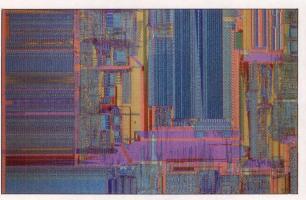

#### C HIPS

The right balance of RISC vs. CISC features can breed higher-performance RISC chips

#### 18 80960's RISC-LIKE ARCHITECTURE

PHILIP BRIDE AND TONY BAKER, Intel Corp. Embedded controller architecture uses RISC concepts and a modular design.

#### TOOLS

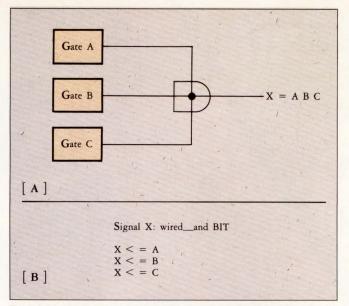

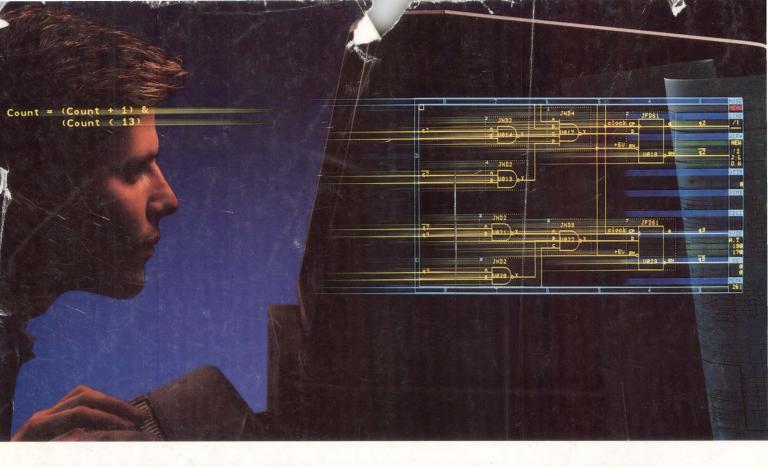

#### **28** BEHAVIORAL DESCRIPTIONS IN VHDL

#### DAVID L. BARTON, Intermetrics Inc. Users can create complex, detailed algorithmic descriptions of behavior.

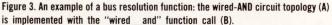

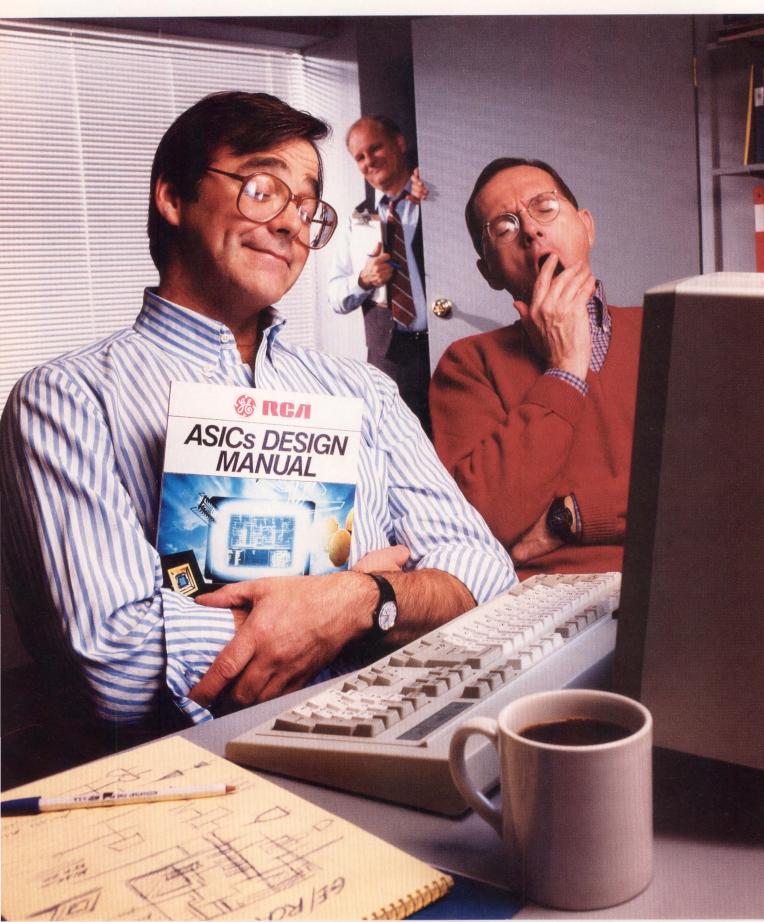

#### **36** BOOSTING ASIC VERIFICATION CAPABILITIES

NORBERT R. LAENGRICH, Hilevel Technology Inc. Virtual memory scheme handles extended vector sets.

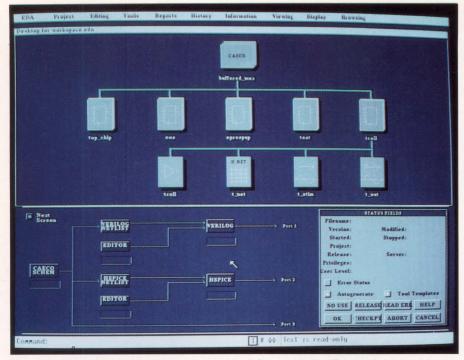

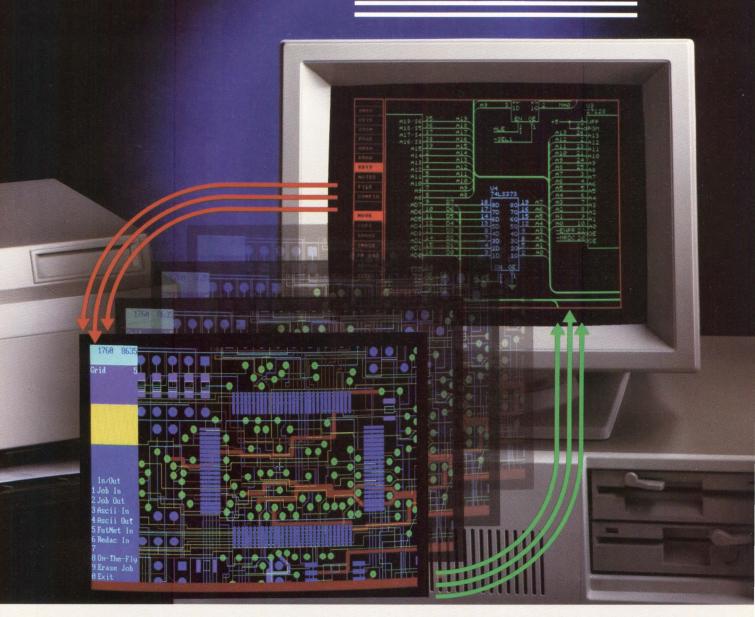

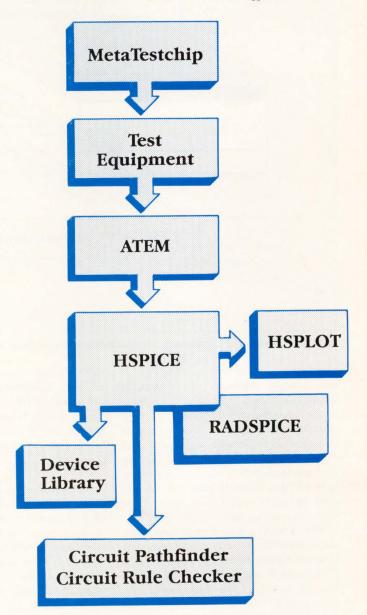

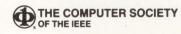

#### **46** A DESIGN AUTOMATION ENVIRONMENT

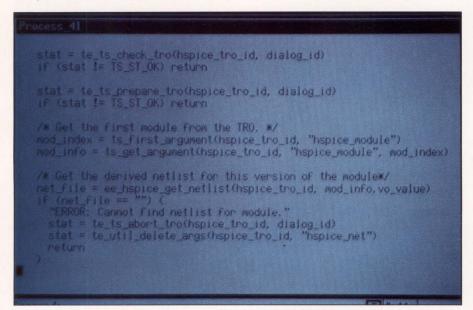

KYLE GOLDMAN AND TED STOUT, EDA Systems Inc. One solution to integrating heterogeneous design tools.

#### **52** ENTRY SYSTEMS FOR ANALOG DESIGNS

VLSI SYSTEMS DESIGN STAFF Our directory of analog CAE entry systems summarizes what they offer.

#### S TRUCTURES

#### **64** RISC CHANGES THE BALANCE

BOB CUSHMAN, Senior Editor The start of a series on RISC and its recent IC incarnations.

#### METHODS

#### **72** WRITING YOUR OWN CAE TOOLS

MARTY DENHAM, Textronix Inc., Lab Instruments Division Creating a tool makes sense when commercial software isn't available.

#### C ODE

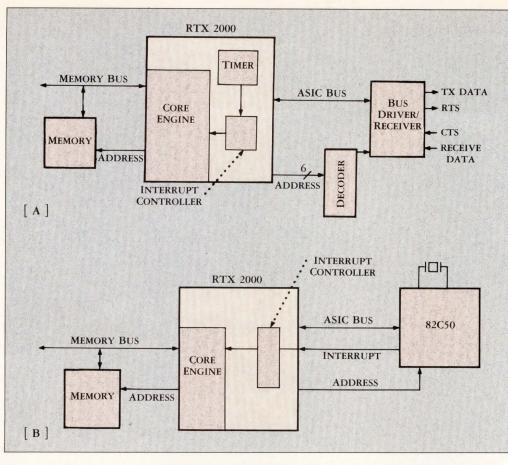

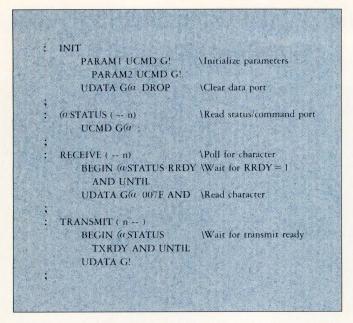

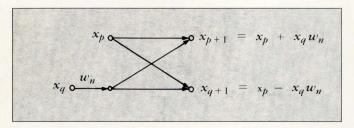

#### 80 HARDWARE-SOFTWARE TRADE-OFFS IN REAL-TIME SYSTEMS

CHRIS W. MALINOWSKI AND PETER S. DANILE, Harris Corp., Semiconductor Sector A core microprocessor simplifies partitioning.

#### **P**ERFORMANCE FRONTIERS

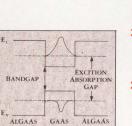

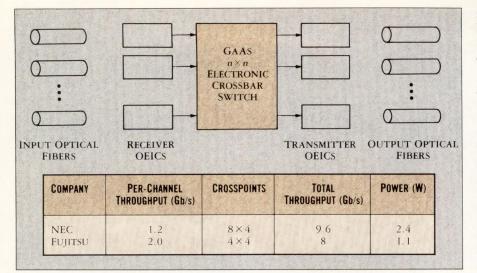

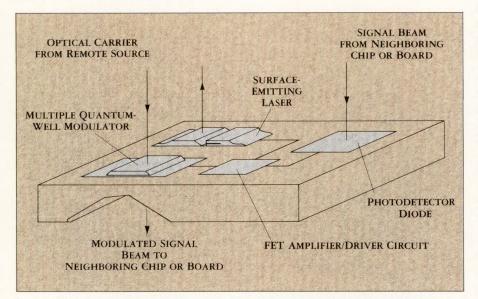

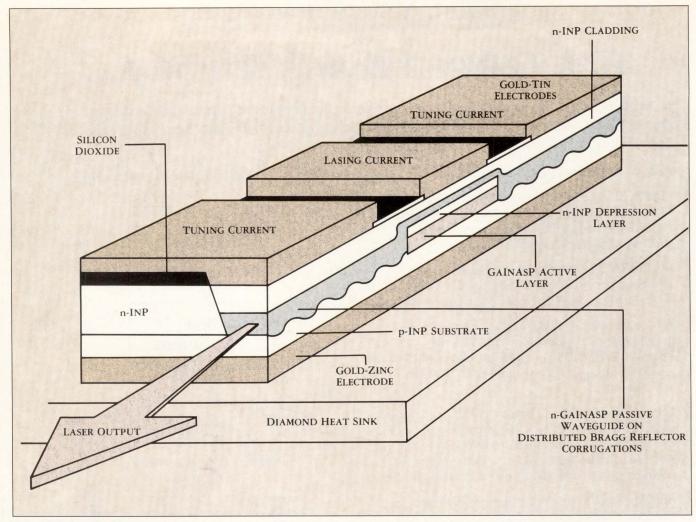

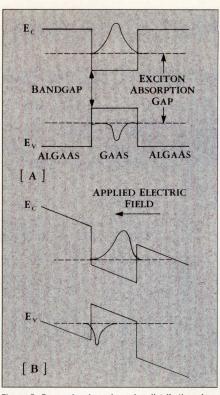

#### **90** OPTOELECTRONIC ICs

**RODERIC BERESFORD**, *Editor Emeritus* The coming world of integrated electronics and photonics.

#### **P**ERFORMANCE PROJECTS

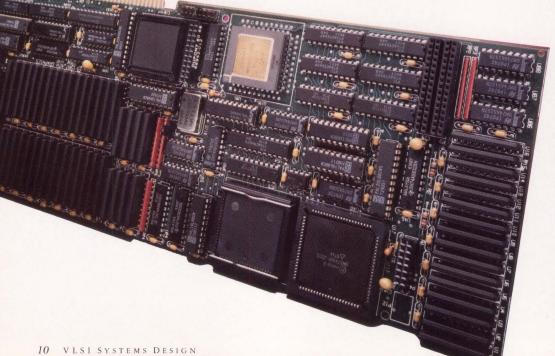

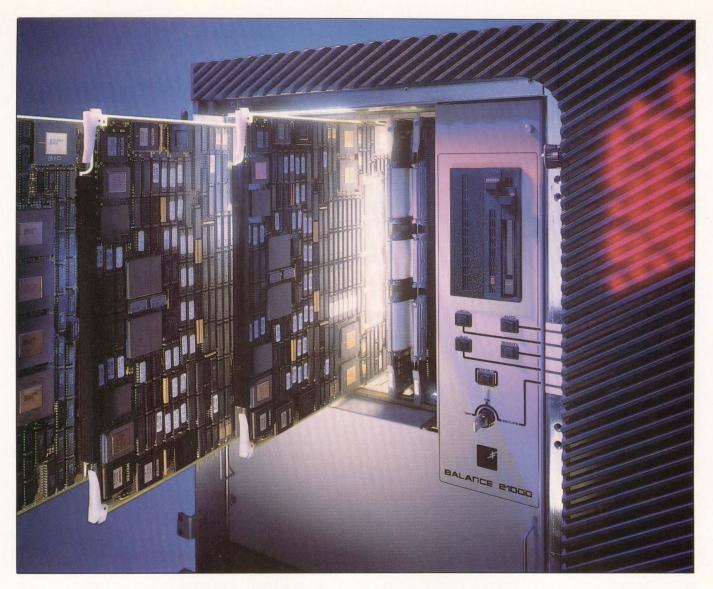

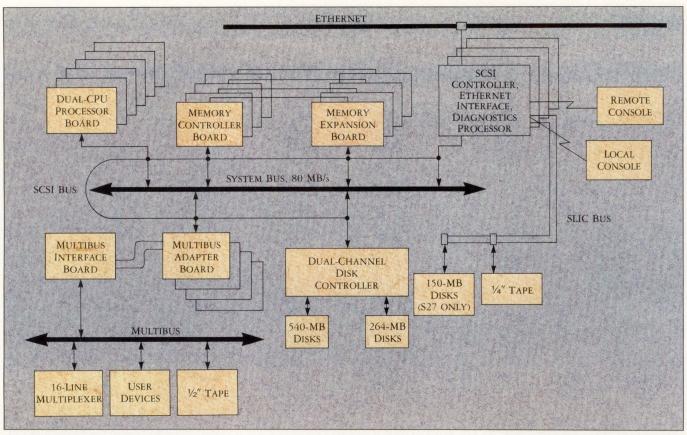

#### **98** SEQUENT'S SYMMETRY SERIES

PAUL GIFFORD, Sequent Computer Systems Inc. Extensive board and ASIC simulation sliced a third off the development time.

#### 80

Real-time system development calls for a fine balance between hardware and software

VHDL shows its real worth in behavioral descriptions of hardware

#### **11** Two electrostatic

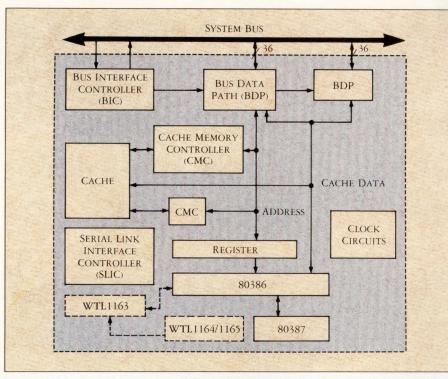

plotters deliver the quality of pen plotters

#### Quantum wells hold the key to optoelectronic ICs

90

#### DEPARTMENTS

#### **6** FROM THE EDITOR

It Was the Best of Times, It Was the Worst of Times

#### 8 CALENDAR

#### **10** BIT STREAM

Calma Unbundles IC CAD for a Valid Deal

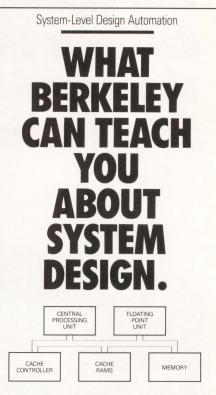

State Machine EPLD Clocks at 50 MHz Major Computer Companies Fight for Open Unix

Super-3D on a PC HP Plotters Target CAE/CAD Applications Altera PLDs Evolve to the Max AMD Increases RISC VLSI Technology and Hitachi Make a Swap

#### **12** NEWS ANALYSIS

The Dual Nature of Logic Synthesis

#### **14 PEOPLE**

A Darwinian Approach to Microprocessor Design

#### **16** INDUSTRY INSIGHTS

How Accurate Must Behavioral Models Be?

#### **104 PRODUCT SHOWCASE**

The Integration of the Design Process

#### 120 AD INDEX

COVER ILLUSTRATION BY SEYMOUR CHWAST

EDITOR/EDITORIAL DIRECTOR Girish Mhatre

> **EXECUTIVE EDITOR** Roland C. Wittenberg

MANAGING EDITOR Mike Robinson

> SENIOR EDITOR Bob Cushman

EDITOR EMERITUS Roderic Beresford

EDITOR-AT-LARGE Stan Baker

WESTERN REGIONAL EDITOR David Smith

> DIRECTORIES EDITOR Michelle A. Losquadro

TECHNICAL ADVISERS John A. Darringer Jeffrey T. Deutsch Edward J. McCluskey Alan F. Podell Daniel G. Schweikert Susan L. Taylor

EDITORIAL PRODUCTION Patricia L. Gaynor, Sr. Production Editor Deborah Porretto, Ass't Production Editor

> EDITORIAL ART Terry Koppel, Art Director Rosemary Intrieri, Designer Marie D'Ippolito, Design Director

MANUFACTURING David Getlen, Dir. of Manufacturing Marie Myers, Production Manager James Pizzo, Production Supervisor Jane Mahoney, Asst. Production Supervisor Vance Hicks, Coordinator

#### PUBLISHER Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in May by CMP Publications, Inc., 600 Community Drive, Manhaset, NY 11030. (516) 562-5000. VLSI SYSTEMS DESIGN is free to qualified subscribers. Subscriptions to others in the US: one year \$60.00, two years \$95.00; Canada and Mexico: one year \$90.00, two years \$155.00; Europe, Central and South America: one year \$120.00, two years \$225.00. Asia, Australia, Israel and Africa: one year \$150.00, two years \$285.00. Second-class postage paid at Manhaset, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN, 600 Community Drive, Manhaset, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

> CMP ELECTRONICS GROUP Kenneth D. Cron Vice President/Group Publisher Electronic Buyers' News Electronic Engineering Times VLSI Systems Design

**CMP PUBLICATIONS, INC.**

Michael S. Leeds, President Pearl Turner, Vice President/Treasurer Daniel H. Leeds, Vice President

> Lilo J. Leeds, Gerard G. Leeds Co-Chairpersons of the Board

# DO YOU HAVE WHAT IT TAKES TO MAKE IT BIG IN ASICS?

Not long ago, designing accelerator is seamlessly intewith more than 170 design ASICs wasn't even grated with the schekits supplied by 70 different ACCELERATED part of your job. vendors. So you can build promatic, so you can locate DESIG ASIC Now it's the and correct design ductivity instead of libraries. problems interactively. Which may explain why part everyone's more MegaLOGICIANs are counting on. That means faster That's where in use today than all other debugging and more Daisy comes in. time to improve accelerators combined. Cadnetix Daisy CAE tools the quality of your Speaking of combining, you are used by more design. Plus ASIC designers than no other accelerator any other CAE workstations. is as well supported, Because from schematic creation through post-layout Daisv 53% 5.000 7vcad 110 Simulation accelerator market share. Source: Prime Data, 1985 and 1986 unit shipments. simulation, Daisy has what it takes to keep ASICs on time and on budget. For example, our MegaLOGICIAN<sup>™</sup> simulation

© 1988, Daisy Systems Corporation. MegaLOGICIAN is a trademark of Daisy Systems Corporation.

Based on minimum 10x performance improvement compared to 32-bit workstations. Source for design kit estimates: VLSI Systems Design Semicustom Design Guide, 1987.

can share a MegaLOGICIAN with a network of our 386based desktop workstations. for a high-powered low cost ASIC design environment.

And that's just the beginning.

With our library of more than 4,500 system-

level components,

you can include your ASIC in complete "real world" system simulations to ensure that your designs will be ready for production, instead of revision.

All of which makes Daisy today's choice for no-sweat ASIC success.

But what about tomorrow?

Gate counts are on the rise. If your tools run out of steam at 5,000 gates, so could your future.

No problem. Our ASIC design tools glide through 20,000DEAD gate designs END

breathing hard. In fact, new design kits already support arrays of over 100,000 gates.

without even

So you'll never have to worry about hitting a dead-end.

But don't take our word for it, listen to what Rockwell and other industry leaders have to say. For a free copy of "Making It Big In ASICs" call Daisy at 1 (800) 556-1234, Ext. 32. In California, 1(800) 441-2345, Ext. 32.

**European Headquarters:** Paris, France (1) 45 37 00 12. **Regional Offices:** England (256) 464061; West Germany (89) 92-69060; Italy (39) 637251

ROM THE EDITOR

### It Was the Best of Times, It Was the Worst of Times

Universal standards

are a must for the design automation industry

Ithough it was over 100 years ago when Charles Dickens began A Tale of Two Cities with "It was the best of times, it was the worst of times " to describe the conditions in London and Paris just before the French Revolution, the same statement describes the financial and mental state of today's electronic design automation industry.

This month the Design Automation Conference will celebrate its 25th anniversary. The design automation industry grew rapidly during these years, with the electronics segment blossoming at the start of this decade. Unfortunately, not all the players fared well. The losers included not only small vendors, but also industry giants that stumbled badly and whose efforts were eventually acquired whole, carved up into small pieces, or simply abandoned. But all is not lost: some vendors showed a remarkable ability to avoid the potholes on the road to success; some finally got their act together; and some were revived after successful mergers.

What caused the problems? Perhaps some industry leaders were like the royalty of Dickens's novel; they were too busy enjoying the best of times to realize their customers' needs and moods were changing. When many of the original CAE/CAD products were introduced, the IC designers—overwhelmed by the exploding complexity of ICs—were desperate for help, even from high-priced, user-unfriendly tools that were often late and didn't perform as promised. They did, however, help designers in their time of need.

But the tides changed; the early successes of the CAE/CAD tool vendors brought out new ventures in droves; every company went its own way, with different interfaces, operating systems, and computing platforms; and the growth of the IC design automation market faltered. The anticipated large-scale move of design automation tools into the much bigger system engineering market didn't materialize.

Nevertheless, it can be the best of times again if industry leaders look beyond their own palaces and make a serious effort to provide systems engineers with the universal standards they desparately need.

Colar All the

ROLAND WITTENBERG EXECUTIVE EDITOR

# There Will Still Be a Few Uses for Conventional ECL ASICs.

### Cold facts: now the highest-density ECL logic array runs at a cool 1/10 the gate power of competing devices.

Raytheon's ASIC design expertise and proprietary technology make conventional ECL arrays too hot to handle. The superior performance of the new CGA70E18 and CGA40E12: the ECL logic array family with the highest density and the lowest power requirement now available.

□ Superior performance: 300 pS delay and 300  $\mu$ W (typical gate) power dissipation deliver the industry's lowest speed-power product: <0.1 pJ. Toggle frequency 1.2 GHz (typical).

#### □ Highest density:

CGA70E18 — 12540 equivalent gates CGA40E12 — 8001 equivalent gates

□ Lowest power: Industry's smallest bipolar transistors result in power dissipation that is a fraction of conventional ECL at comparable propagation delays. Typical chip power dissipation of 3W to 5W.

□ Et cetera: Interface TTL, ECL (10K, 10KH, 100K), ETL. Customer access to proven, fully integrated CAD system. Commercial and military operating ranges.

**CIRCLE NUMBER 2**

Call Raytheon for access to the right ECL technology. We're not blowing any smoke, and neither should your system's performance.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

Access to the right technology

## alendar

June 12–16 Anaheim Convention Center Anaheim, Calif.

AC '88, sponsored by the IEEE Computer Society and the Association for Computing Machinery, is devoted solely to the field of design. automation. This year's conference will offer tutorials, panel discussions, and technical presentations. General session topics will include design for testability, VHDL in use, timing verification, parallel simulation, high-level synthesis, placement algorithms, layout compaction, logic synthesis and optimization, physical design verification, fault simulation, and micro-architecture synthesis. For more information, contact Pat Pistilli, MP Associates Inc., 7490 Clubhouse Road, Suite 102, Boulder, Colo. 80301. (303) 530-4333.

#### INTERNATIONAL WORKSHOP ON VLSI FOR ARTIFICIAL INTELLIGENCE

July 20–22 University of Oxford Oxford, England

T his workshop will provide a forum where AI experts and VLSI system designers can come to discuss trends in AI applications and their computational requirements, VLSI implementations, and computer architectures. Topics to be discussed will include alter-

native technologies, functional-language architectures, knowledge-oriented machines, rule-based engines, Prolog and Lisp machines, and fifth-generation computers. Further information may be obtained by contacting, Dr. Jose G. Delgado-Frias or Dr. Will R. Moore, Dept. of Engineering Science, University of Oxford, Parks Road, Oxford OX1 3PJ, England, U.K. Phone: (0865) 273188.

#### SIGGRAPH '88

August 1–5 Atlanta, Ga.

This 15th annual confer-ence on computer graphics and interactive techniques is sponsored by the Association for Computing Machinery's Special Interest Group on Computer Graphics in cooperation with the IEEE Technical Committee on Computer Graphics. It will feature panel sessions, courses, and exhibitions, as well as a film and video show and an art show. Technical presentation topics will include algorithms, animation, CAD/CIM, applications, color, computational geometry, geometric modeling, graphics hardware, and graphics systems. Additional information may be obtained by contacting SIGGRAPH '88 Conference Management, Smith, Bucklin, and Associates Inc., 111 E. Wacker Dr., Suite 600, Chicago, III. 60601. (312) 644-6610.

#### **OIS '88**

September 7–9 Washington Sheraton Washington, D.C.

The eighth annual Optical Information Systems Conference and Exhibition, sponsored by Meckler Corp., will focus on write-once and erasable optical storage systems and digital document-image automation. Sessions are planned in areas such as electronic image and document storage systems, erasable optical disk media developments, erasable optical disk drives and systems, evaluating and selecting a WORM subsystem, future trends and new developments, converging optical information technologies, and integrated systems development. Additional information about the conference may be obtained by contacting Marilyn Reed, OIS '88 Conference Manager, Meckler Corp., 11 Ferry Lane West, Westport, Conn. 06880. (800) 635-5537.

#### 7th VLSI and GaAs Packaging Workshop

September 12–14 San Jose, Calif.

T his workshop is being sponsored by the IEEE's Components, Hybrids, and Manufacturing Technology Society and the National Bureau of Standards. Topics that will be addressed include package interconnection options, GaAs IC packaging, dieattachment solutions for large chips, VLSI and wafer-scale package design, and VLSI package materials advancements. For additional information about the workshop, contact Paul Wesling, IEEE Council Office, 701 Welch Road, Suite 2205, Palo Alto, Calif. 94304. (415) 327-6622.

#### INTERNATIONAL TEST Conference 1988

September 12–14 Sheraton Washington Hotel Washington, D.C.

The ITC provides a major forum for an exchange of information about the testing of electronic devices, assemblies and systems. This year the conference focuses on the test techniques and equipment needed to meet the challenges of new technologies. Technical papers will be presented on such topics as analog devices, yield modeling and process diagnosis, testability analysis, education and training, application-specific devices, micro-

Continued on page 113

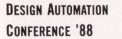

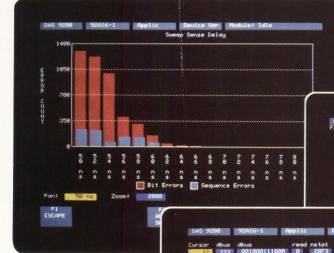

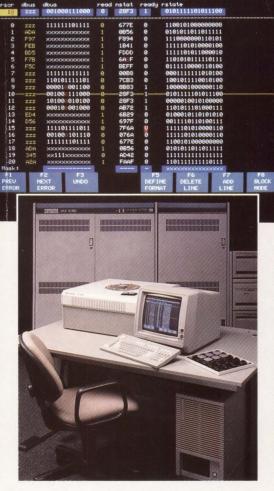

### At 100 MHz, the IMS Logic Master XL creates a new world standard for ASIC verification.

### But speed isn't everything.

You might think it sufficient that we're introducing the highest performance ASIC verification system available anywhere.

And that our new Logic Master XL is the first system with data rates of 100 MHz.

But we didn't think that was enough.

Instead, we concentrated on the kind of features that turn superior performance into superb productivity.

Like advanced driver electronics which produce symmetrical waveform edges for measurement accuracy.

And complete per-pin control. So you can handle complex timing configurations with ease. And mixed technology devices.

Plus automatic wiring for rapid, error-free setup, and superb system skew for greater measurement confidence.

Best of all, the Logic Master XL comes from Integrated Measurement Systems, the international leader in ASIC verification.

Contact us for more information.

Integrated Measurement Systems, Inc. Corporate Headquarters 9525 S.W. Gemini Drive Beaverton, Oregon 97005 TEL 503 626-7117

**CIRCLE NUMBER 3**

Photo courtesy of NASA

U.S. Regional Offices: Boston, MA 617-366-3676; Irvine, CA 714-768-5808; Portland, OR 503-626-7117. International Offices: Belgium 02-219-2453; Canada 416-890-2010; France 01-4534-7535; Hong Kong 5-701181; Japan 0423-33-8111; Sweden 753-38465; Switzerland 830-5040; Taiwan 02-501-0055; The Netherlands 01-40-582911; United Kingdom 06-284-76741; West Germany 5722-2030.

# Stream

#### **Calma Unbundles IC CAD for a Valid Deal**

ALID LOGIC SYSTEMS Inc. (San Jose, Calif.) has purchased Calma Co. (Milpitas, Calif.), whose GDS II design system for ICs was the granddaddy of most modern IC CAD systems, from General Electric Co. for cash and stock valued at less than \$3.5 million. Valid will consolidate its IC CAD product line and the Calma group into an IC CAD division and will assume responsibility for Calma's GDS II and newer EDS III design systems. The deal became a reality when W. Douglas Hajjar, Valid's president and CEO, convinced GE executives to unbundle the IC CAD division from the mechanical division.

#### State Machine EPLD Clocks at 50 MHz

HE FIRST of a family of 28pin EPLDs, the CY7C330 Programmable State Machine from Cypress Semiconductor Inc. (San Jose, Calif.), can implement state machines that operate with a 50-MHz clock. The new chip contains 11 dedicated inputs and 12 I/O macrocells, both with registers; four buried registers; and a logic array that provides 9 to

19 product terms for each output macrocell. Two input clock pins synchronize the arrival of input signals, and a third clock input drives the output and buried registers. The input register setup time is 5 ns, and the clock-to-output delay is 15 ns.

The new EPLD is built with Cypress's 0.8-µm dual-layermetal CMOS technology.

#### **Major Computer Companies Fight for Open Unix**

EVEN GIANTS in the computer industry put their money on the line for a "truly open Unix." The chief executives of IBM, Hewlett-Packard, Digital Equipment, Apollo Computer, Siemens, the Bull Group, and Nixdorf expressed their dissatisfaction with the AT&T-Sun Microsystems handling of the development of a unified Unix operat-

ing system by making a threeyear, \$90 million commitment to an international effort directed toward open software standards. The efforts will be channeled through the newly formed Open Software Foundation. John L. Doyle, executive vice president of HP's Systems Technology Division, will serve as the OSF's first chairman.

#### Super-3D on a PC

NEW DISPLAY controller board from Nth Graphics (Austin, Texas) delivers 3D color graphics performance at a superworkstation level when plugged into an IBM PC AT. The Nth 3D Engine, priced from \$13,000, uses Inmos Transputers, in addition to the company's proprietary graphics coprocessors, to provide the required computing power. The board, which drives color monitors with a  $1,024 \times 768$ -pixel resolution at a 60-Hz non-interlaced refresh rate, can handle a variety of complex graphics operations, such as transforming 5,000 constant-shaded, 500pixel polygons per second.

#### **HP Plotters Target CAE/CAD Applications**

WO LOW-PRICED electrostatic plotters have been introduced by Hewlett-Packard Co. The HP 7600 series, Models 240D and 240E plotters can typically produce mechanical engineering type drawings in less than one min-

ute. HP says that the Model 240D is the only electrostatic plotter priced at less than \$23,000 that features pen-plotter quality with a resolution of 406 dots per inch. The

The Model 240E, which is priced at \$27,500, has the same resolution as the 240D, but handles the larger E size

#### **Altera PLDs Evolve to the Max**

NEW PLD architecture developed by Altera Corp (Santa Clara, Calif.) combines logic array blocks (LABs) with a programmable interconnect array (PIA) that connects signals among blocks and I/O pads. The architecture takes form in the Max family of devices, ranging from the EPM5016 with 20 pins and 16 macrocells to the EPM5128 with 68 pins and 128 macrocells.

Each LAB contains macrocells (with an AND-OR logic array and flip-flops), "logic expanders" that expand the number of available product terms, and I/O functions that can drive either I/O pins or other macrocells to create buried resources. The combination of format. Both plotters includebuilt-in HP-GL, the Hewlett-Packard Graphics Language, which makes them fully compatible with hundreds of existing software packages. HP-GL/2 is also included to provide for future software per-

> formance enhancements.

The plotters can connect to a wide variety of host computers through their RS-232-C, IEEE-488, and Centronics parallel

interfaces. The host central processing unit is offloaded by the 40-megabyte storage capacity of the built-in vector-to-raster converter, which can hold up to 3 million vectors.

Max new architecture and 0.8-μm CMOS process technology (from

second-source Cypress Semi-

conductor) allows the parts to operate with 40-MHz system clock frequencies. The Max family and the Max + design system will be available in the second half of this year.

#### AMD Increases RISC

A DVANCED MICRO Devices Inc. (Sunnyvale, Calif.) is now sampling a 30-MHz, 20-MIPS version of its Am29000 RISC processor, six months ahead of schedule. It has also promised three support chips by year-end: the Am29027 floating-point processor; the Am29062 integrated cache unit, with cache memory and control logic; and the Am29041 data transfer controller, which implements DMA and I/O functions. Next year expect to see a 50-MHz, 35-MIPS version of the 29000.

#### VLSI Technology and Hitachi Make a Swap

ILLIAM GSAND, vice president and general manager of Hitachi America Ltd.'s Semiconductor and IC division, and Alfred J. Stein, chairman and CEO of VLSI Technology Inc. (San Jose, Calif.), shook hands on a deal that took 18 months to negotiate. The five-year agreement gives Hitachi rights to all of VLSI Technology's broad line of

proprietary IC physical design tools, silicon compilers, megacells, and standard-cell libraries. In return, VLSI will obtain manufacturing know-how on Hitachi's 1-µm and smallergeometry CMOS processes. Other provisions are secondsource rights to Hitachi's manufacturing technologies and the availability of VLSI's tools to Hitachi's customers.

# ews Analysis

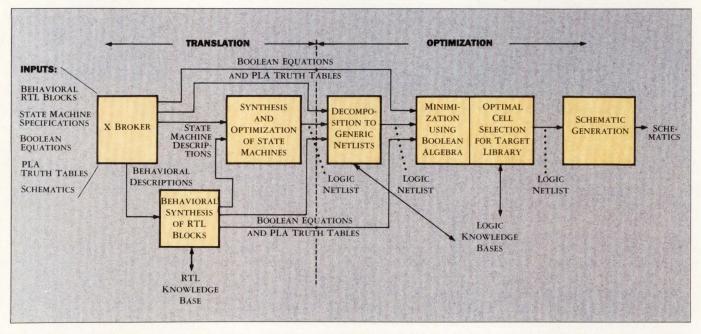

### The Dual Nature of Logic Synthesis

The term *logic synthesis* implies the creation of a circuit structure directly from a high-level description. A crop of programs to be first shown at the Design Automation Conference comes very close to satisfying that description. From a point high in the design hierarchy, they automatically translate and optimize designs that can then be implemented in semicustom ICs.

Translation: The designer creates high-level modelsregister-transer-level (RTL) blocks, behavioral descriptions, or equations to represent portions of his design. The synthesizer replaces each of those blocks with lower-level components that can be implemented in the target technology. Often the high-level description must first be translated into more malleable forms. For example, a state machine may be divided into a sequential block and a logic block, both of which can be implemented directly in lower-level components.

*Optimization:* Once the design has been translated into lower-level components, the tools try to optimize the implementation. They use signal path delay, power consumption, and silicon area (in terms of total number of gates) to judge whether a change in the design results in a better implementation.

All tools contain some optimization routines that perform minimization using. Boolean algebra. Espresso is the most

prevalent algorithm for such optimization. Minimization usually reduces silicon area and power consumption because it reduces the total number of components in the implementation. The tools can optimize across entire designs, or the designer can limit them to optimize portions of designs within specified boundaries. To minimize propagation delay, logic synthesis tools must incorporate timing analysis programs to measure the delay along signal paths. One strategy for reducing signal delays rearranges logic expressions to minimize components along a signal path.

### TIMING IN CRITICAL PATHS

Another technique replaces components in critical signal paths with higher-drive alternatives. When timing is improved through fewer components, silicon area and power consumption may improve as well. More often, though, faster designs obtain their speed through the use of higher-drive components and are therefore a little larger and consume more power than slower implementations. Logic synthesis is designed to be complementary to, instead of a replacement for, existing CAE environments. The tools create netlists or schematics (or both) in the format for Mentor Graphics workstations (and some others). Designers then verify the functionality and timing of the design, as well as the placement and routing, using existing tool sets.

#### ■ NEW TOOLS DEFINE THE ART

Three logic synthesis programs are becoming available that execute both functions of synthesis: the Design Consultant, from Trimeter Technologies Corp. (Pittsburgh, Pa.); the Design Compiler, from Synopsys Inc. (Mountain View, Calif.); and SilcSyn, from Silc Technologies Inc. (Burlington, Mass.). Another new logic synthesis tool, the DS23 design program from Xilinx Inc. (San Jose, Calif.), performs only optimization, and it produces designs solely for Xilinx's programmable gate arrays.

Trimeter's Design Consultant (Figure 1) accepts designs in five forms: register-transferlevel designs, state machines, Boolean equations, PLA truth tables, and schematic diagrams. It evaluates the design using two knowledge bases. It first performs optimization at the RTL level, making architectural and structural tradeoffs that are independent of the implementation technology. Then the company's Logic Consultant, which is embedded in the Design Consultant, makes trade-offs that are specific to the implementation technology.

To the Logic Consultant, the Design Consultant adds the additional input forms and the translation of those input forms into equations, state machines, and netlists for implementation. It produces designs for gate arrays from LSI Logic, Toshiba, and Hughes. Preliminary release is planned by the beginning of the fourth quarter of this year.

The founders of Synopsys developed the Design Compiler's progenitor, Socrates, while at General Electric's Research Triangle Park facility (for a description of Socrates, see VLSI Systems Design, January 1988, p. 40). After five years of experience with Socrates, Synopsys has begun to encode some of the knowledge base in algorithms instead of expert rules. Algorithms, which can be considered highly structured, complex rules, execute more quickly than rules.

S ome of the Design Compiler remains rules-driven, because it is easier to create and modify a knowledge base in terms of rules than it is in algorithms. Once a set of rules becomes tested and verified over time, however, the effort *Continued on page 112*

# ARRAY FOR BicNoS!

#### 180 MHz with low power.

It's cause for celebration. AMCC extends its lead as the high performance/low power semicustom leader with three exciting, new BiCMOS logic

arrays that optimize performance where today's designs need it most. In throughput (up to three times faster than  $1.5\mu$  CMOS).

Today, system designers look at speed, power and density. For

| Q14000 SERIES                  |             |             |               |  |

|--------------------------------|-------------|-------------|---------------|--|

|                                | Q2100B      | Q9100B      | Q14000B       |  |

| Equivalent Gates               | 2160        | 9072        | 13440         |  |

| Gate Delay* (ns)               | .7          | .7          | .7            |  |

| Maximum I/O<br>Frequency (MHz) | 180         | 180         | 180           |  |

| Utilization                    | 95%         | 95%         | 95%           |  |

| Power<br>Dissipation (W)       | 1.8         | 4.0         | 4.4           |  |

| I/O                            | 80          | 160         | 226           |  |

| Temperature<br>Range           | COM,<br>MIL | COM,<br>MIL | COM,<br>MIL   |  |

| *(2 loads, 2 mm of metal)      |             | †A          | vailable soor |  |

good reasons. As CMOS gate arrays become larger and faster, designers can't meet their critical paths due to fanout and interconnect delay. As Bipolar arrays become larger and faster, power consumption becomes unmanageable. So AMCC designed a BiCMOS logic array family that merges the advantages of CMOS's low power and higher densities with the high speed and drive capability of advanced Bipolar technology. Without the disadvantages of either.

Our new Q14000 BiCMOS arrays fill the speed/power/ density gap between Bipolar and CMOS arrays. With high speed. Low power dissipation. And, mixed ECL/TTL I/O compatibility, (something CMOS arrays can't offer).

For more information on our new BiCMOS logic arrays, in the U.S., call toll free (800) 262-8830. In Europe, call AMCC (U.K.) 44-256-468186. Or, contact us about obtaining one of our useful evaluation kits. Applied MicroCircuits Corporation, 6195 Lusk Blvd., San Diego,

CA 92121. (619) 450-9333.

#### EOPLE

The 29000's Architect Believes in Evolution

STAUNCH proponent of an evolutionary approach, Mike Johnson learned the hard way about how to design a microprocessor. A survivor of the RISC microprocessor program at IBM, he received a chance to create a new architecture at Advanced Micro Devices. The result, the Am29000 RISC processor, didn't pop out from a product specification; instead, it evolved.

Chance, a key factor in evolution, steered Mike into processor design to begin with. For example, as a master's candidate at Arizona State, he had specialized in digital control and signal processing. This expertise suited him well for developing magnetic-card typewriters at his new employer, IBM. However, on leaving college, his car broke down, forcing him to scrap his travel plans. Showing up early at IBM, Mike was placed in the next available slot: microprocessor design. "It was a total accident," he says.

Mike was the first of a group whose charter was to design IBM's next generation of microprocessors. The Research Office-Products Mini Processor (ROMP) project faltered because it was started too early to benefit from technology trends and too late to begin from scratch.

"ROMP suffered a lot from being the bridge between the old and the new," Mike says. For example, the designers toiled to design an interleaved memory interface that subsequent advances in DRAM technology would make not only unnecessary but also cumbersome.

Also, ROMP was originally a 24bit architecture, because, he says, IBM "didn't have the guts to go directly from 16 to 32 bits." A year after its inception, the architecture did expand to 32 bits; in addition the designers then had to retrofit virtual memory onto it. The experience in trying to tune the stubborn ROMP architecture taught him "what you don't do" in creating a microprocessor.

When Mike joined the team developing the 29000, he used a model for the project that could be pulled from the notebooks of Charles Darwin. He explains: "Biological things progress by changing randomly, with many intermediate forms dying off. Processors can change randomly too, and intermediate steps don't need to live. I can have an intermediate stage that is this long and this wide and has pink polka dots on it-it doesn't matter. But an intermediate stage gives ideas that continue the evolution.'

As a result, the 29000 started as an infinitely large chip from which the designers subtracted functions, instead of being built up piece by piece. "It's creating the chip instead of designing it," Mike says.

In addition to evolution, an-

PROCESSORS CAN CHANGE RANDOMLY TOO,

A Darwinian Approach to

**Microprocessor** Design

AND INTERMEDIATE STEPS DON'T NEED TO LIVE' other philosophy emerged from his ROMP days: Don't design all functions in hardware or the processor can get in the way of the final system design. "Saying 'let me do that in hardware' doesn't always make things faster," he says.

System-level technology, such as software design, changes faster than designers can implement functions in hardware. Processor designs should implement a set of flexible primitive functions that execute as fast as possible. The system designer then plugs them together, using the most recent ideas in system design.

As an illustration of both philosophies, Mike points to the 29000's large register set. It began as 32 registers and progressed through numerous intermediate stages, including a 64-register file with cache backup to a 256-register file. It was finally pared down to 192 registers. No restrictions are placed on the use of the registers, so the system designer can use them to best advantage in the type of system he is building.

This RISC concept of implementing only primitive functions in hardware was difficult to accomplish because of human nature. "We had to slap each other's hands to keep features out of the design," Mike explains.

His hands, as well as the rest of him, are now at Stanford University, where he's investigating parallel processing at the instruction level that will result in microprocessors that can execute more than one instruction each clock cycle. So Mike Johnson, it seems, continues to be closely tied to the evolution of microprocessors.

# Feel trapped by one ASIC supplier? Reach for the Super Foundry.

Now you can design complex ASICs to meet your needs, not to fit one supplier's limited capabilities. The Super Foundry<sup>™</sup> offers the combined resources of the world's premier CMOS manufacturers. Our process independent design tools and production services give you maximum freedom and control—from concept through delivery. FREE. ASIC Estimating Kit.

What will it take to do your ASIC? With our free ASIC Estimating Kit, you can analyze design-process trade-offs and explore the performance, cost and scheduling implications of your design in a variety of processes. Take control of your ASIC design and avoid the single-supplier prison. Call the Super Foundry for your free ASIC Estimating Kit: 1-800-FOR-VLSI ext. 200.

THE SUPER FOUNDRY SEATTLE SILICON

3075-112th Ave NE., Bellevue, WA 98004, (206) 828-4422. Copyright 1988, Seattle Silicon Corp. Super Foundry is a trademark of Seattle Silicon Corp. CIRCLE NUMBER 5 N D U S T R Y I N S I G H T S

System-level simulation hinges on accurate models

S WE approach the 1990s, many factors are driving companies to find faster, more efficient methods of design verification. Burgeoning system complexity and shrinking design cycles are the most imperative factors. In addition, more and more systems are incorporating ASICs. Although it's true that 99% of the time an engineer can make an ASIC meet its design specification on the first pass, only 50% go into production; the other 50% don't function correctly in their systems. This situation is prompting the need for logical simulation of ASICs within a complete board design, and as a result, system-level simulation-the logic simulation of board- and system-level products-is becoming very popular.

The efficacy of system-level simulation hinges on the availability and accuracy of simulation models. Understandably, users of simulators want the behavior of device models to match the behavior of the devices exactly. To realize this state, some users argue, models should be certified by the IC vendors themselves. Unfortunately, it is both a mathematical and a physical impossibility that 4,000 to 5,000 lines of code can represent a silicon device exactly, replicating its unspecified deviant behavior as well as its specified good behavior. Therefore we must ask what "accuracy" means.

Most semiconductor companies will not certify the accuracy of even their own data sheets. It isn't reasonable, then, for them to assure users that 4,000 to 5,000 lines of

### How Accurate Must Beavioral Models Be?

WILLIAM W. LATTIN, LOGIC AUTOMATION INC., BEAVERTON, ORE.

code will faithfully represent all possible responses of a quarter of a million transistors interconnected on a chip. What *is* possible is to submit the model to the same characterization and test suites that the semiconductor vendor runs on the device. This approach verifies the model's behavior for the *specified* behavior of the chip. It does not model the *unspecified* or deviant behavior of the chip.

Developers of models must work very closely with semiconductor companies and use the same test vectors on the model of the chip that are used on the device itself. At Logic Automation, for example, we have relationships with most leading semiconductor vendors to exchange proprietary test vectors and technical information. These relationships help ensure the highest possible accuracy of our behavioral models.

Most importantly, a behavioral model that is verified in the same manner as the device it models allows a designer to determine whether a device is being used correctly in a system design. The model performs to the device's specified behavior, which is what a designer needs. The system designer doesn't need the model to re-create the device's unspecified THE SYSTEM DESIGNER DOESN'T NEED THE MODEL

TO RE-CREATE THE DEVICE'S UNSPECIFIED BEHAVIOR' behavior—he doesn't use that behavior when he defines the functionality of his system. So the model, despite not matching 100% of the device's behavior, should meet the designer's needs completely.

We are often asked, "Do these 4,000 to 5,000 lines of code exactly represent the chip?" My response is, "No, they don't; in fact, the software model does more than the chip does." The reason is that our software models actually issue an error message when it is being used improperly-a feat that no chip can do. Therefore, I think this issue is similar to an argument that arose in the old days regarding the accuracy of testing the chips themselves. If you think of a complex microprocessor with 300,000 transistors, a complete test would contain 2300,000 vectors that set each transistor into an on and off state. We all know that that is not only impractical but impossible. The argument about the accuracy of software models for simulation is analogous.

The real value of behavioral models does not arise from having them represent every transistor in the chip with 100% accuracy. Their value stems from the fact that behavioral models allow designers to use system simulation to control the complexity and reduce the time of their design projects.

WILLIAM W. LATTIN is the president and chief executive officer of Logic Automation. He has been involved with simulation and modeling for over 20 years, playing a key role in the introduction of design automation at both Motorola and Intel. Prior to Logic Automation, he was the vice president and general manager of Intel's Systems Group.

### PCB LAYOUT ON YOUR PC. FOR ONLY \$1495. OrCAD PCB COMES TO LIFE.

ith nearly 10,000 systems already in use, electrical engineers like the no-nonsense capability of OrCAD/SDT schematic capture. Well, now there's even more to like. Introducing OrCAD/PCB. A fast, easy-touse PCB layout package that runs on your PC. And costs only \$1,495.

-CAD/PCB

ting

#### A NO-NONSENSE DESIGN TOOL FOR NO-WAIT DESIGNERS.

OrCAD/PCB pumps up your productivity. Pop-up menus appear in a flash. Macros speed repetitive operations.

OrCAD sales and support representatives.

- 1. WA, OR, MT, ID, AK Seltech, Inc. 206-746-7970

- 2. N. CA, Reno NV Elcor Associates, Inc. 408-980-8868

- 3. S. CA Advanced Digital Group 714-897-0319

- 4. Las Vegas NV, UT, AZ, NM, CO Tusar Corporation 602-998-3688

OR8801

Bit-mapped graphics make redraws, zooms and pans instantaneous. And, since you know SDT, you have no new commands to learn; PCB's interface is exactly the same.

51

#### POWER AND FLEXIBILITY MINUS CLUTTER.

OrCAD/PCB produces structured, elegant PCB layouts. It auto-routes boards up to 32"x32" with up to 8,000 track segments and 16 layers, taking into account manually routed connections. And, it adapts to your design with features like:

0.00

00

Find your OrCAD region number on this map; then locate your sales and support representative on the list below.

- Selectable track and via widths from 0.001" to 0.255."

- Square, rectangular, round,

- elliptical, and SMD pads.

Grid bases of 100, 50, 25, 10 and 5 mils. Or, go off grid to 1 mil.

- FL High Tech Support 813-920-7564

DE, VA, MC, DC

- MGM Visuals 703-352-3919 13. MS, AL, GA

- Electro-Cadd 404-446-7523 14. E. PA, NJ, NY Beta Lambda, Inc. 201-446-1100

- 15. CT, RI, MA, VT, NH, ME DGA Associates, Inc. 617-935-3001

- Support for digital and analog components and surface-mount devices.

- Ratsnest and force vector placement.

- Definition of board edge, forbidden zones, and copper zones.

#### GIVE OUR DEMO DISK A SPIN.

If you need affordable, nononsense PCB layout, call for a free OrCAD/PCB demo disk. Not an OrCAD user? Call for the SDT demo disk while you're at it (OrCAD/SDT costs only \$495). Then, watch your PCB layouts take shape.

- BC, AB, SK, MB Interworld Electronics & Computer Industries, Ltd. 604-984-4171

- 17. ON, PQ Electralert, Ltd. 416-475-6730

1049 S.W. Baseline St., Suite 500 Hillsboro, OR 97123 USA 503-640-5007

#### 6. NE, KS, IA, MO Walker Engineering, Inc. 913-888-0089

7. TX, OK, AR, LA Abcor, Inc. 713-486-9251

5. ND, SD, MN, W. WI

Comstrand, Inc

612-788-9234

- MI, E. WI, IL Cad Design Systems, Inc. 312-882-0114

- 9. IN, OH, KY, WV, W. PA Frank J. Campisano, Inc. 513-574-7111

- 10. TN, NC, SC Tingen Technical Sales 919-878-4440

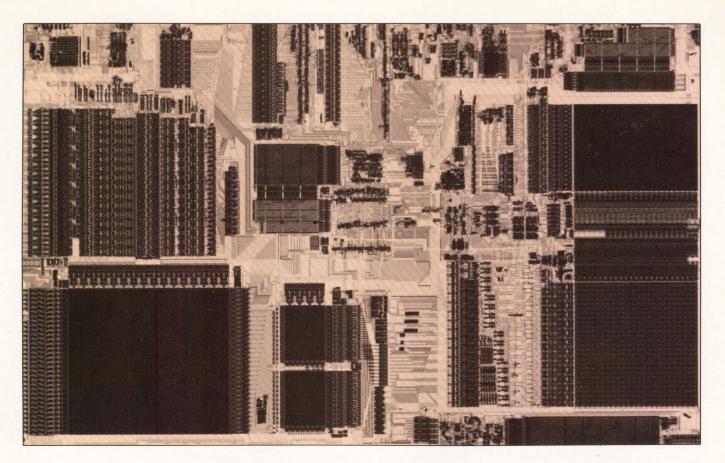

# **BOBBOORS** RISC-Like Architecture

PHILIP BRIDE AND TONY BAKER, INTEL CORP., HILLSBORO, ORE.

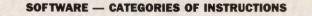

Designers of microprocessor-based system perform a balancing act, juggling performance, cost, power consumption, and size. Because the priorities of embedded systems differ significantly from those of reprogrammable systems, achieving this balance in an embedded application requires different microprocessor capabilities.

The classic requirements for embedded systems are low cost, small size, low power consumption, and predictable

performance. In contrast, reprogrammable systems balance these same concerns but generally put performance in first place.

To illustrate the difference, compare the design considerations for an engineering workstation and a desktop laser printer. The primary competitive advantage for the workstation is high performance. The printer must achieve high performance as well, but price, size, and power consumption are equally important. In other words, embedded systems have all the problems of reprogrammable systems, plus a few more.

In simpler designs, embedded controllers can balance cost and size with lower performance. That compromise is not applicable, however, to more complex products that require significant processing power. Advanced embedded designs in machine control, robotics, process control, and avionics need lots of processing horsepower to handle complex, real-time interrupts and highspeed floating-point calculations.

To achieve these higher performance levels, some embedded system designers have turned to 32bit architectures, but available general-purpose processors were not designed to meet embedded controller needs. Recognizing this need for a high-performance embedded processor, Intel has developed the 80960 processor family, based on a high-performance core architecture that limits system size and cost, integrates a wide variety of special capabilities, and provides an upward growth path for future development.

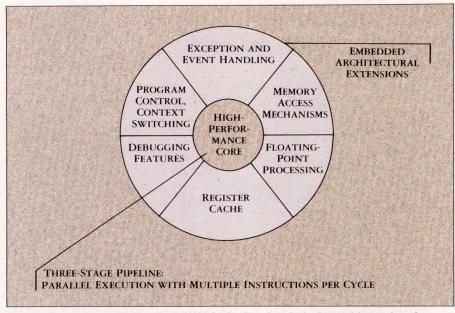

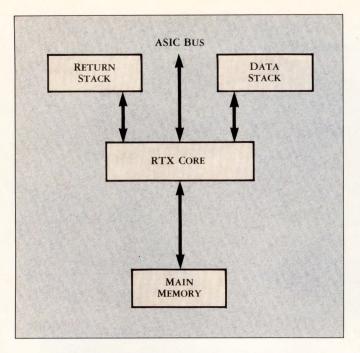

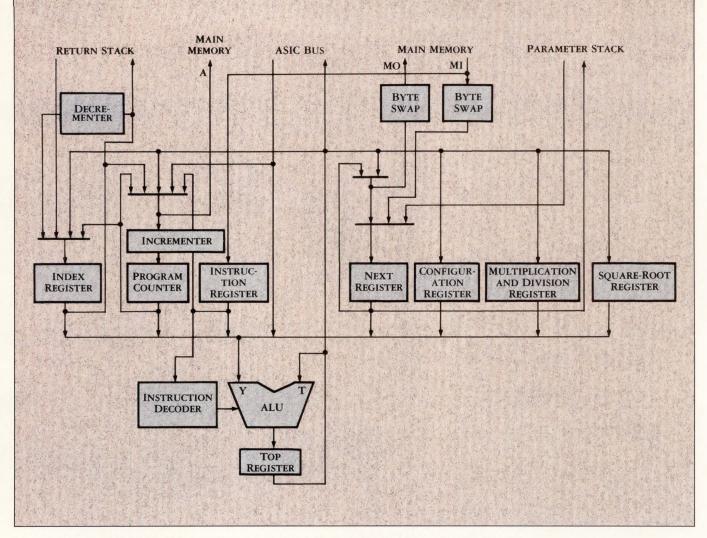

#### RISC-LIKE

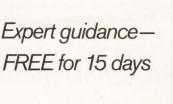

The architecture of any processor is an abstract definition of the computer, its instruction set, its register model, and the functions needed for control. In developing the 80960 architecture, the designers viewed RISC as a set of design techniques available to architects, instead of as predefined architectural constructs. We took a pragmatic approach, selectively applying RISC techniques when they were appropriate and modifying them when necessary to improve functionality or ease of use. The resulting architecture uses pipelined structures and highly parallel instruction execution in the engine that form the core of its computation and data processing capabilities. Around the engine are modular features that extend the functionality of the core in embedded systems (Figure 1).

Because the 80960 was built from the ground up specifically for embedded applications, each architectural decision was subjected to very specific design tests. For

MODULAR APPROACH PRODUCES Embedded Controllers For specific Applications

example, many RISC theorists assume that systems will be programmed only in a high-level language (HLL). Because of this assumption, designers may omit safety mechanisms such as silicon interlocks within pipelines and depend on the software compiler to manage pipeline execution. As a consequence, the RISC processor may be difficult to program in assembly language.

Designers of embedded systems, however, require assemblylanguage programming capabilities for certain time-critical operations. The 80960 solves these problems with a careful balance of hardware and software functions. It includes silicon interlocks to managing its pipeline invisibly to the programmer. This capability makes it practical to program the processor in assembly language essential for such tasks as building I/O control routines.

The processor includes other features, like the register cache, that are effective without compilation. On the other hand, it contains some functions, such as register scoreboarding, which operate more efficiently with software from an optimizing compiler.

The 80960 architecture ad-

dresses the special needs of embedded systems by controlling system costs, size, and power consumption at every stage of the development process. For example, operations for bit-field manipulation, debugging, and self-testing simplify system development and add functionality without forcing the designer to compromise performance. Integration of special features like floating-point processing and interrupt control directly onto the processor eliminates the cost and board space of additional peripheral devices and coprocessors. In this way the architecture minimizes overall chip count and simplifies system design to decrease space and power needs.

The 80960 uses many RISC design techniques: a simple load and store design; large, general-purpose register sets; a small set of instructions that are aligned by the word—32 bits wide—and that execute in one cycle; optimizing compilers that operate on complex HLL code; and simple hardware that makes efficient use of silicon. These characteristics have been modified to meet the practical requirements of embedded computing, and the modular structure of the architecture allows different versions of the architecture to be produced quickly.

In the 80960 family architecture, operations work on data in on-chip registers, with only load and store instructions accessing memory. This attribute simplifies both the instruction set and the decoding process. A load/store architecture is well suited to embedded applications, because simple instruction decoding lets the compiler optimize source code more effectively. In addition, the decoupling of external memory operations from internal processing aids performance. The 80960KB implementation (see "80960 Implementations," p. 24, and the table) further reduces the number of memory accesses by providing a 512-byte, direct-mapped instruction cache.

All instructions are 32 bits long and aligned on 32-bit boundaries, a detail that eliminates the need for an instruction alignment stage. The instruction set has a three-operand format with space for two source operands and one destination operand. That means it is possible to do an operation without writing over the source operand in the course of executing the instruction. Extensible architecture uses pipelines and paralell instruction execution

Figure 1. The modular architecture of the 80960 family allows it to be implemented in a variety of ways.

The 80960 instruction set provides an extensive set of operations to the programmer. It supports logical operations in addition to integer operations such as add, subtract, multiply, and divide. It also provides a broad range of data instructions to deal with individual bits within fields and within registers and with Boolean operations. More than 50 of these instructions can be executed in a single clock cycle. Multicycle instructions, such as sine or cosine, are also available to make programming more practical. The instruction set supports the ability of future 80960 family members to add functional blocks like DMA controllers, timers, and interrupt controllers.

The 80960 architecture includes large register files that serve to simplify task switching and execution. In this architecture, local registers are unique to each procedure, whereas global registers retain their values across procedure boundaries. Global registers serve as a common block for passing information from one procedure to another, so that procedure calls using this mechanism do not need to access external memory. For example, more than 90% of all C routines pass fewer than six parameters, but the 80960KB has 16 global 32-bit registers that can be used to pass as many as 12 words of parameters. Most HLL routines can execute wholly out of the 'KB's 16 local registers, with 13 words of local variables available per procedure and excess global registers available for scratchpad use. The other local registers are reserved for such chores as task linkage and tracing return instructions.

Although the architecture specifies 16 local and 16 global registers, it does not define how many local register sets its "register cache" will hold. That characteristic is defined within each implementation. All parts will have these 32 registers, but an implementation may extend this number to add features such as the 80960KB's 64-register cache and four 80bit floating-point registers.

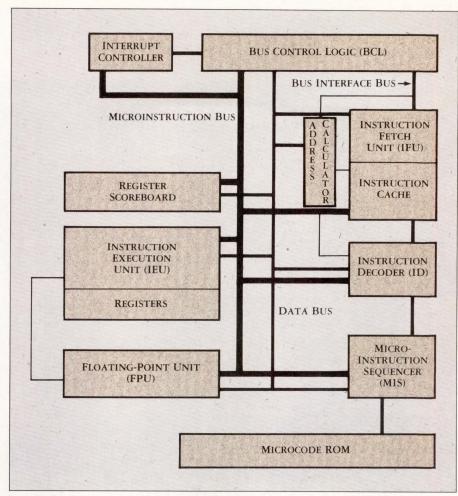

The pipeline structure of current 80960 implementations (Figure 2) is organized in three functional stages: fetching, decoding, and execution. The fetch stage includes bus control logic (BCL) and an instruction fetch unit (IFU). The decoding stage corresponds with the instruction decoder (ID) and the micro-instruction sequencer (MIS). The execution stage consists of the integer execution unit (IEU) and, in the 'KB and 'MC versions, a floating-point unit. An autonomous interrupt controller operates next to the pipeline. Future implementations of the 80960 will be similar to, but more elaborate than, the version described here.

#### ■ THE FETCH STAGE

In the fetch stage, the bus control logic is the interface between the 80960 and the external 32-bit L-bus that connects it to the system memory and I/O modules. This multiplexed bus can transfer data at a maximum sustained rate of 53 MB/s when the processor is operating at 20 MHz with no wait states. The BCL accepts memory requests from other units within the 80960 on a first-come, first-served basis and executes them. It attempts to maximize bus access efficiency through buffering and burst accesses.

The BCL buffers memory references in a three-deep FIFO. Once a memory access is initiated, it will be completed before any other access in the FIFO is initiated. The BCL queuing mechanism, coupled with other 80960 features such as scoreboarding, enables other modules in the 80960 pipeline to continue operation without waiting for memory bus requests to be completed. Most memory reference instructions are executed with little or no delay in the instruction pipeline.

Bus throughput is improved by the use of burst memory access, which allows a multiword access to and from the L-bus with only one address cycle. Any address cycle can be followed by as many as four data words and a recovery cycle. The BCL controls the burst access, automatically maintaining 16-byte boundaries within memory accesses.

Burst memory access improves memory bandwidth substantially. For example, if this bus were limited to single-word access, it would be capable of only 27 MB/s, one half the burst bandwidth of 53 MB/s. Burst access also allows the 80960-based system to utilize the nibble and staticcolumn modes in DRAMs. By limiting bursts to four words, under control of the BCL, the bus also simplifies external memory-control logic.

The hardware portion of the interrupt controller is located within the BCL, although interrupt control logic is located in a separate module. When an external source requests the 80960 to handle another chore, it causes an implicit procedure call to the interrupt controller. Each of the four interrupt pins has an associated 8-bit interrupt vector. Programmable registers allow the designer to multiplex two or more interrupt pins to service a larger number of interrupts. Using the interrupt vector, the interrupt controller signals the micro-instruction sequencer that an interrupt has occurred and the MIS starts a microprogram to service the interrupt. The current state of the machine is saved on an interrupt stack in main memory. If the interrupt occurs during an instruction that requires many machine cycles, the instruction state is also saved in the interrupt stack and the execution of the instruction is suspended.

A 4-bit register records and prioritizes further interrupts that occur after the initial interrupt and before the interrupt controller's microprogram can finish its task and return to the interrupted task. Upon returning, the interrupt controller examines the 4-bit register and if need be begins executing the next-highest priority interrupt.

The last function of the BCL is arbitration of control of the three major internal buses in the 80960: the bus interface (BI) bus, the data bus, and the microinstruction ( $\mu$ I) bus. The BI and data buses are each 32 bits wide, and the  $\mu$ I bus is 42 bits wide. The 80960 also employs a series of other, smaller buses, including the X bus, the microinstruction address ( $\mu$ ADDR) bus, and an internal bus within the microinstruction sequencer. The BI, X, and  $\mu$ ADDR buses all are within the same data path. The BI bus connects the BCL and the instruction fetch unit. The X bus extends from the IFU to the instruction decoder, and the  $\mu$ ADDR bus continues from the instruction decoder to the microinstruction sequencer.

The next module in the fetch stage is the instruction fetch unit, which acts as an intelligent buffer for the instruction decoder. It includes the 512-byte, directmapped instruction cache, which holds instructions from the bus control logic. If an instruction in a new block of instructions must be initiated immediately, it is put into the cache and sent immediately to the instruction decoder for decoding instead of being put into the cache and then read back out and decoded.

The effective-address ALU within the instruction fetch unit performs address calculations under the control of the instruction decoder. Address calculation is executed during decoding (as opposed to during the execution phase), saving two to three clock cycles when instruction execution occurs in parallel with address calculations. The address calculation can be done in parallel with an integer execution or a floating-point operation.

#### DECODING STAGE

The instruction decoder decodes the instructions it receives from the instruction fetch unit and routes them to the appropriate execution units. It manages all tracing mechanisms and illegal op-code faults. Upon detection of a trace event or an illegal op-code, it issues a command to the microinstruction sequencer to start a flow for that fault. Instructions are decoded based on how they are to be executed: simple instructions; floating-point and branch instructions; complex instructions; and load and store instructions.

Simple instructions—logical, compare, shift, integer add, integer subtract, and ordinal add and subtract—require little decoding. The ID decodes these instructions and passes them to the instruction execution unit, where they are executed, usually in a single clock cycle.

Floating-point and branch instructions do not execute in one cycle. Floatingpoint instructions are executed by the floating-point unit and may require interaction among the FPU, the instruction decoder, and the microinstruction sequencer. The instruction decoder executes

Figure 2. The multiple autonomous units and bus structure of the 80960KB implement the part's three-stage pipeline operation.

| ld | xyz, r6          | # r6 < load data from address xyz |

|----|------------------|-----------------------------------|

| ad | di g4, g6, g7    | # add: g7 < g4 + g6               |

| ad | di g9, g10, g11  | <b>#</b> g11 < g9 + g10           |

| ld | abc, r8          | #r8 < load data from address abc  |

| an | d g0, 0xffff, gl | # g1 < g0 AND 0xffff              |

| ad | di r6, r8, r7    | # r7 < r6 + r8                    |

Figure 3. Register scoreboarding permits parallel execution of load and register-driven instructions. Here, four additional instructions can be executed during the load operation, because they don't make use of register 6.

branch instructions directly. If the branches are unconditional, no interaction with the processor's other execution units is required. On conditional branch instructions, the ID uses a condition code scoreboard (described later) to streamline the branching process.

Pipelined operation can make the branching appear to occur in zero clock cycles. For example, the branch instruction ("b") shown below will execute in zero cycles, because the branch time is overlapped completely by the execution time of the floating-point instruction ("sinr"):

sint g0, g1 b some—location some—location:

mov g1, g2 Complex instruction execution requires the use of microcode within the microinstruction sequencer. The instruction decoder decodes complex instructions and forwards them to the sequencer, which then sends the equivalent microcode to the appropriate execution units.

Load and store instructions request data to be read from or written into memory.

This is the stuff reputations are built on.

A cell design with 100,000 gates. More than 1000 library elements. 2MB of memory. And sub-micron

HCMOS technology.

You can search high and low, but there's only one place in the world you can find a chip of such staggering complexity.

LSI Logic.

Designs like this are precisely why we're the #1 domestic ASIC supplier with more than

4,000 working cell and array-based designs in the field.

And why our Modular Design Environment (MDE)<sup>™</sup> software is the best foundation for building killer cells.

MDE is the industry's most advanced design software for ASICs. It arms you with the capability to build today's most sophisticated cellbased designs. Easily. And with the smallest possible die size.

Besides MDE, LSI Logic delivers more than 400 LSI and VLSI building

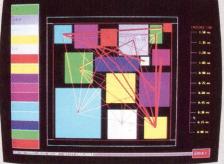

High complexity Cell-Based ASICs require advanced tools like the MDE chip floorplanner to optimize delays and verify performance prior to layout.

blocks, including 16 and 32-bit microprocessor cells and industry-standard processor and peripheral functions; the longest list of SSI and MSI functions; and memory compilers to

> develop exactly the RAM or ROM your chip requires.

> And if your application calls for lower densities, that's covered, too. Because LSI Logic has more cost-effective cell-based solutions than you can imagine.

> No matter what kind of Cell-Based ASIC you

build, LSI Logic will deliver a fullytested prototype in as little as 4 weeks.

All in the production quantities you want, thanks to our advanced worldwide wafer fabrication, assembly, and test facilities.

So find out more about LSI Logic's Cell-Based ASICs by calling the sales office nearest you.

After all, we can help you make a killing.

LSI Logic Sales Offices and Design Resource Centers: Scottsdale, AZ 602-951-4560, Milpitas, CA 408-433-8000, San Jose, CA 408-248-5100, Irvine, CA 714-553-5600, Sherman Oaks, CA 818-906-0333, Denver, CO 303-756-8800, Altamonte Springs, FL 305-339-2242, Boca Raton, FL 305-395-6200, Norcross, GA 404-448-4898, Chicago, IL 312-773-0111, Bethesda, MD 301-897-5800, Waltham, MA 617-890-0161, Ann Arbor, MI 313-769-0175, Minneapolis, MN 612-921-8300, Bridgewater, NJ 201-722-7522, Poughkeepsie, NY 914-454-6593, Raleigh, NC 919-783-8833, Worthington, OH 614-438-2644, Beaverton, OR 503-644-6697, Trevose, PA 215-638-3010, Austin, TX 512-338-2140, Dallas, TX 214-778-2966, Bellevue, WA 206-822-4384, Calgary, Alta 403-262-2922, Paris, France 33-1-46212525, Israel 972-3-403741/6, Milan, Italy 39-39-651575, Tokyo, Japan 81-3-589-2711, Seoul, Korea 82-2-785-1693, Nidau/Biel, Switzerland 032-515441, Bracknell, United Kingdom 44-344-426544, Munich, West Germany 49-89-926903-0. © 1988 LSI Logic Corporation. Modular Design Environment and MDE are trademarks of LSI Logic Corporation.

#### **CIRCLE NUMBER 7**

#### 80960 Implementations

The 80960 architecture provides the framework for a complete family of products. It is currently implemented in three versions: the 80960KB, which integrates a floating-point unit and an interrupt controller (see Figure 2 and the table, main text); the 80960KA, which is socket-compatible with the 'KB but does not include the floating-point unit; and the 80960MC, a military-qualified version of the 'KB with memory management and instructions that simplify the use of Ada multitasking capabilities. All three are built using 1.5- $\mu$ m two-layer-metal CHMOSIII technology. The silicon technology produces chips with low power requirements—less than 2 w in the 80960KB. The 80960KB is housed in a 132-pin PGA, although the processor actually requires only 78 pins. The 132-pin PGA was chosen because its cavity size accommodates the current die size of 390 × 390 mils.

The low pin count of the 80960KB is made possible by the use of a multiplexed bus, which reduces the number of pads necessary on the die. The lower bus pin count translates into easier signal routing, and the reduced number of drivers means higher reliability and lower power consumption. The lower bus pin count, coupled with a high ratio of power pins to bus pins, results in lower levels of switching noise, higher reliability, and superior performance in noisy environments.

The 80960MC adds multiprocessing and fault-tolerant computing to its basic embedded capabilities. The chip works with the 82965 bus extension unit (BXU) to support error detection, reporting, and automatic system reconfiguration. The BXU connects the processor with Intel's proprietary Advanced Processor (AP) silicon bus, allowing designers to replicate subsystems and achieve any desired level of multiprocessing or fault tolerance.

Fault-tolerant systems based on the 80960MC use functional redundancy checking (FRC) processor pairs that run simultaneously in lockstep. The processors can be started and stopped synchronously using an interagent communication (IAC) message. In a quad modular redundancy (QMR) system, two FRC pairs are joined to form a QMR. One pair (the primary) is actively issuing and responding to AP bus accesses, while the other (the shadow) is in lockstep with the primary but not active on the bus. This system can toggle between the primary and shadow pair and can run nonstop when a single fault occurs. The hardware can reconfigure itself, with the shadow assuming the bus activity of the primary, in real time. Because configuration control resides entirely in BXU programmable registers, the same processor pairs can also be configured for multiprocessing.

We expect the next standard version to be tailored specifically for data control. Its capabilities would be optimized for applications such as protocol handling and telecommunications. This data controller will operate at three to four times the performance level of the current 80960KB and is expected to be announced in early 1989.

The instruction decoder sends these instructions directly to the bus control logic, which executes them. The instruction decoder is responsible for converting addressing information encoded in load, store, branch, and call instructions into effective memory addresses. If during decoding an operand reduction (address calculation) is required, the instruction decoder issues all the commands for the calculation to the instruction fetch unit.

#### EXECUTION STAGE

The instruction execution unit contains the ALU, register sets, and the mechanisms for register and condition-code scoreboarding. In a single clock cycle, it can perform addition and subtraction of integers and ordinals, moves between registers, logical operations, bit operations, shifts, rotations, or a comparison. It can also work with integer literals in the range of 0 to  $\pm 31$ , which are encoded in the instruction format. The IEU receives its control either from the microinstruction sequencer or the instruction decoder via the  $\mu$ I bus.

Operands for these operations are fetched from internal registers or from external memory, or they are literals. The instruction execution unit contains a simple sequencer used for aligning and accessing multiple-word operands. For floatingpoint operations, the IEU passes data to and from the floating-point unit across the data bus. Any register can be used for a floating-point operation.

Whenever two operands go through the ALU and their result or a constant is used in the next operation, the IEU saves that operand internally, so it need not be fetched again from the register. Most integer operations are two cycles long without the bypass. With the bypass, an operation for which the compiler is optimized, they require one cycle.

The instruction execution unit contains 16 global registers and 16 local registers, plus 32 scratchpad registers used for internal microprograms. It is responsible for maintaining the local register cache and the associated allocation logic.

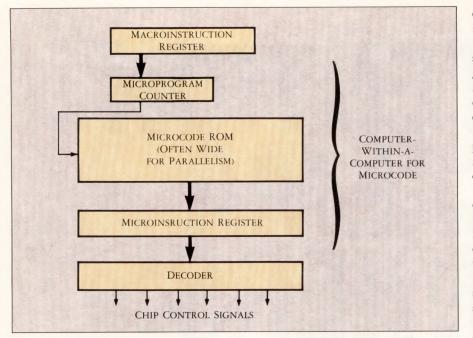

In parallel with the instruction execution unit, the microinstruction sequencer executes instructions that require microcode. Processor microcode is stored in a  $3\kappa \times 42$ -bit microcode ROM, which is accessed through the MIS. When the instruction decoder receives a complex instruction that requires microcode to be executed, it sends the starting microaddress of the flow to the MIS, which steps through the microprogram.

Microcode is used for complex instruction execution, exceptions such as interrupt and fault handling, local register cache manipulations, and the power-up and self-testing performed during processor initialization. The microinstruction sequencer also initializes the FPU for floating-point instructions.

#### REGISTER SCOREBOARDING

The register scoreboarding mechanism keeps track of outstanding memory accesses and enables subsequent instructions to execute while outstanding accesses are being completed. The resulting concurrent instruction execution improves performance by 20% to 50% in tight software loops and by 10% in large C programs.

When a LOAD instruction begins, the 80960 sets a scoreboard bit on the target register to indicate that a particular register or group of registers is being used in a load operation. If the instructions that follow do not use registers in that group, the processor is able to execute those instructions before execution of the prior instruction is complete. The 80960 ensures that these additional instructions do not make reference to the target register by transparently checking the scoreboard bit. After the target register is loaded with data, the processor resets the bit.

A common application of this feature is to execute one or more fast instructions taking one to three clock cycles—concurrently with load instructions. A load instruction typically takes three to nine clock cycles, depending on the use of burst access. For example, the instructions in Figure 3 load a group of local registers while performing some other operations on data in global registers. The two "addi" instructions following the first load, as well as the instruction following the second load, are executed in parallel with the load instructions.

Another situation where scoreboarding can be useful for procedure optimization is when floating-point instructions are being executed. Floating-point operations are executed by a separate unit from the IEU. As a result, non-floating-point instructions can often be executed concurrently with floating-point instructions, providing that they do not use the same registers and do not use the ALU.

#### ■ FLOATING-POINT UNIT

The floating-point unit performs all the floating-point computations for the processor, as well as the integer multiplication and division operations. It manages the four 80-bit floating-point registers (mentioned earlier) used for extended-precision floating-point calculations. It is fully compatible with IEEE-754 Rev. 10, including all extensions for transcendental, exponential, and logarithmic operations.

Capable of 32-bit (single), 64-bit (double), and 80-bit (extended) precision, the FPU passes data to and from the rest of the chip via the data bus. It shares the resources of the processor, using the global and local registers (in addition to its own registers) as operands for floating-point operations and the microinstruction sequencer for initialization. All floating-point operations are initiated by microinstruction bus.

There are three main logical blocks within the floating-point unit: the mantissa block, the exponent block, and the control block. The mantissa block consists of a shifter, an adder, three working registers (two operand and one accumulator), and a 44-word ROM that is 68 bits wide. The exponent block comprises two temporary registers, an adder, and a four-word, 16-bit-wide ROM. The control block directs the FPU, receiving instructions from the instruction decoder or the microinstruction sequencer, as well as control signals. It controls sequencing, data

|                         | THE 80960KB AT A GLANCE                                                                                                                                            |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERFORMANCE             | 20 MIPS BURST EXECUTION AT 20 MHz                                                                                                                                  |

| REGISTERS               | 7.5 MIPS SUSTAINED EXECUTION AT 20 MHz<br>16 32-BIT GLOBAL<br>16 32-BIT LOCAL<br>4 80-BIT FLOATING-POINT<br>REGISTER SCOREBOARDING<br>CONDITION CODE SCOREBOARDING |

| CLOCK SPEEDS            | 16, 20, 25 MHz                                                                                                                                                     |

| INSTRUCTION CACHE       | 512 BYTES, DIRECT-MAPPED                                                                                                                                           |

| REGISTER CACHE          | 4 SETS OF LOCAL REGISTERS                                                                                                                                          |

| ADDRESS SPACE           | 4 GB, LINEAR                                                                                                                                                       |

| BUS                     | 32-BIT MULTIPLEXED<br>UP TO 16 BYTES PER BURST<br>53.3 MB/s IN THE BURST MODE                                                                                      |

| FPU                     | IEEE-754–Compatible<br>4 Million Whetstones/s at 20 MHz                                                                                                            |

| INTERRUPT<br>Controller | 32 PRIORITY LEVELS<br>248 VECTORS<br>SUPPORTS 8259A                                                                                                                |

movement from registers, and bus usage internal to the FPU.

To perform integer multiplications and several floating-point calculations, the FPU contains a 32-bit integer Booth multiplier. This multiplier performs integer multiplication operation in a variable amount of time, depending on the number of significant bits.

#### ■ THE PROGRAMMING ENVIRONMENT

The 80960 architecture defines a completely flat address space: no translations are necessary to calculate addresses. Direct one-for-one address mapping, without segmentation, provides a straightforward programming environment and eliminates the need for special address control registers.

The 80960 architecture provides the multiple addressing modes typical of embedded applications, plus, as noted, a separate ALU for address calculation. Addressing modes are built into the instruction stream and managed by the part itself to make programming easier.

The 80960's procedure call mechanism uses a register cache to reduce memory accesses. At every procedure call, the processor caches the contents of the previous procedure's registers on chip and allocates a new set of registers, often eliminating the need for stack accesses. The 80960KB has a four-deep cache that can make up to four procedure calls before it has to do a stack access, and the processor automatically handles stack accesses.

Embedded applications frequently involve the development of custom hardware in parallel with custom software. The debugging facilities built into the 80960 are designed to make system integration easier. The processor offers two different break instructions—conditional and unconditional. In addition, the design includes a breakpoint register that stores two addresses for designated breaks.

The 80960's tracing facility looks for specific classes of instructions like subroutines, branch conditions, supervisor calls, and single-stepping operation. When any of those user-specified events occurs, it transfers control of the processor to a user-specified subroutine, and the processor provides information on the exact nature of the event to the subroutine.

#### ABOUT THE AUTHORS

PHILIP BRIDE is a hardware applications engineer in the 80960 applications group. He joined Intel in 1984 as a member of the VLSI design group that developed the 80960 and was a circuit design engineer for the architecture's instruction decoder. He graduated from the University of Portland with a BSEE in 1984. TONY BAKER is an applications engineer for the 80960 project. He has been at Intel for seven years, serving also as a software engineer and as a field applications engineer. He received his BSEE in 1981 from the University of Portland.

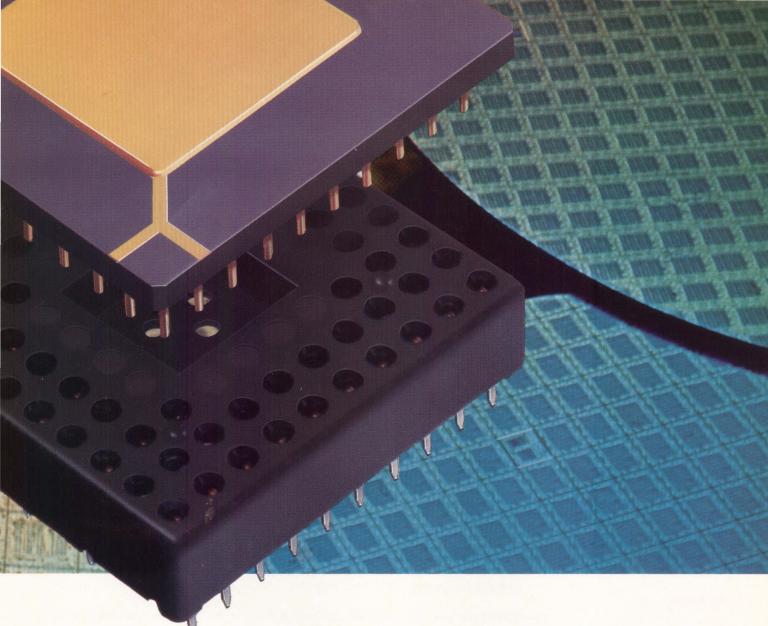

# How we've made sure the chip's locked in, but you're not.

TETETTT TO A CONTRACT OF THE TETETT

ZIF and LIF PGA sockets, plus our minimal profile spring sockets in PGA footprint.

AMP is a trademark of AMP Incorporated.

Whichever direction you take in microprocessor technology, AMP makes sure you have the socketing options you need to make it pay off.

Our high pressure tin sockets for plastic leaded packages come with an exclusive Positive Lock retention system that keeps chips secure during handling and shipping. Ceramic chip carrier sockets feature duplex plated contacts and snap-on covers that accommodate heat sinks. Both are available in standard and surfacemount versions.

AMP offers you more: high-speed, surface-mount sockets on .020" centers. Gold-plated plastic carriers and sockets. For pin grid arrays, sockets in ZIF and LIF styles, plus custom VHSIC capability.

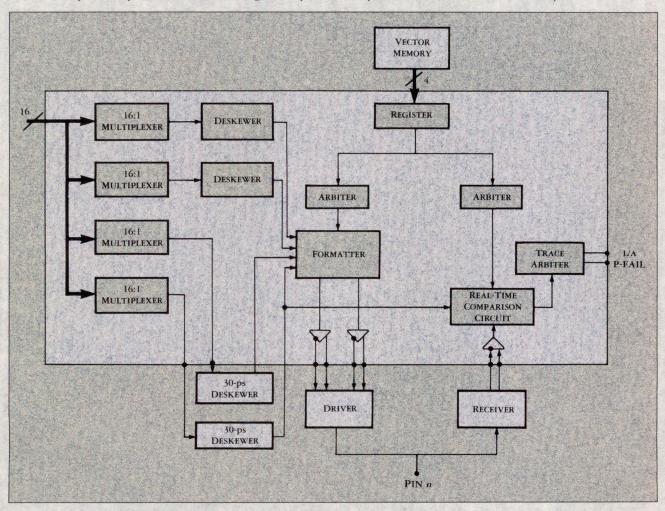

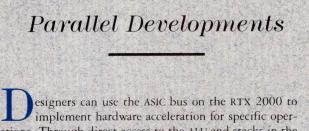

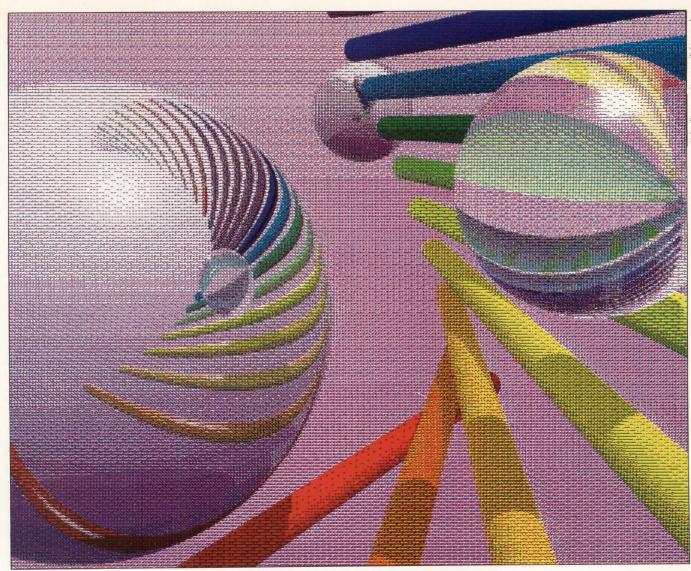

Choose your technology. AMP makes it easy to implement, with full socketing support.