# ONE-STOP ARCnet<sup>™</sup> LAN SOLUTIONS

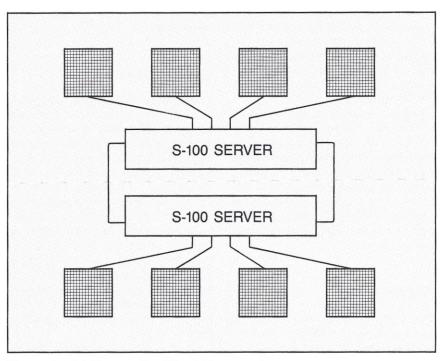

Now you can get all the tools you need to build industry standard **TOKEN-PASSING** networks from one source.

InterContinental Micro.

Our networking packages let you configure any combination of nodes (PC s and compatibles, ATs, XTs, Jrs., Z-100 s) to a common Fileserver in just a few minutes with our menu-driven installation program.

Active and passive hubs allow you to integrate up to 255 users on a single network with *increased* efficiency as the network grows.

In addition, our stand-alone ARCnet™ Workstation/Fileserver and complete line of S-100 Bus products (single board computers, slaves and controllers) give you and your customers even more options.

ARCnet is a trademark of Datapoint Corporation.

We're also compatible with other industry-leading ARCnet PC<sup>™</sup> and S-100 products, and our PC networking boards include an optional 256K of system RAM.

All with InterContinental Micro's reputation for outstanding reliability, exceptional service, and highly competitive pricing.

Call InterContinental Micro today, or circle the bingo number below for ARCnet<sup>™</sup> LAN solutions.

4015 Leaverton Court, Anaheim, CA 92807; Phone: (714) 630-0964 Telex: 821375 SUPPORT UD: Easylink: 62562040.

Call for GSA pricing.

Editor and Designer Jay Vilhena

Associate Editor Robert Petersen

Technical Editor Don Pannell

Circulation Linda Vilhena

Advertising Jay Vilhena

Software Consultant Steve Renshaw

**Contributing Artists** Joslyn L. Johanna G. N. Pereira

**S-100 Journal** is published quarterly by Octoplus Corporation, 1275 N. University Ave., Unit 7, Provo, UT 84604. Telephone (801) 373-0696. Copyright©1986 by Octoplus Corporation. All rights reserved

All rights reserved. **Subscriptions:** U.S.A.: \$14.00 for 1 year, \$25.00 for 2 years. Canada and Mexico: add \$3.00 per year. Other countries: add \$6.00 per year. All foreign payments must be in U.S. currency. Send orders and payments to S-100 Journal, P.O. Box 1914, Orem, UT 84057. **Advertising:** Contact Jay Vilhena at one of above addresses or call (801) 373-0696. **Postmaster:** Send address changes to S-100 Journal, P.O. Box 1914, Orem, UT 84057.

## goutlin

LOCAL AREA NETWORKS UNDER TurboDOS

#### BUILD A 4-PORT SERIAL S-100 BOARD

2 32 BITS ON THE S-100 BUS

THE CROMEMCO XXU A 32-BIT S-100 BOARD

- **4** EDITORIAL

- 7 EDITOR INTERFACE

- 8 696 BUS

- **13** MULTIUSER OS

- 59 BITS

- 72 NEWS AND NEW PRODUCTS

- 75 S-100 SOFTWARE

- 76 S-100 DIRECTORY

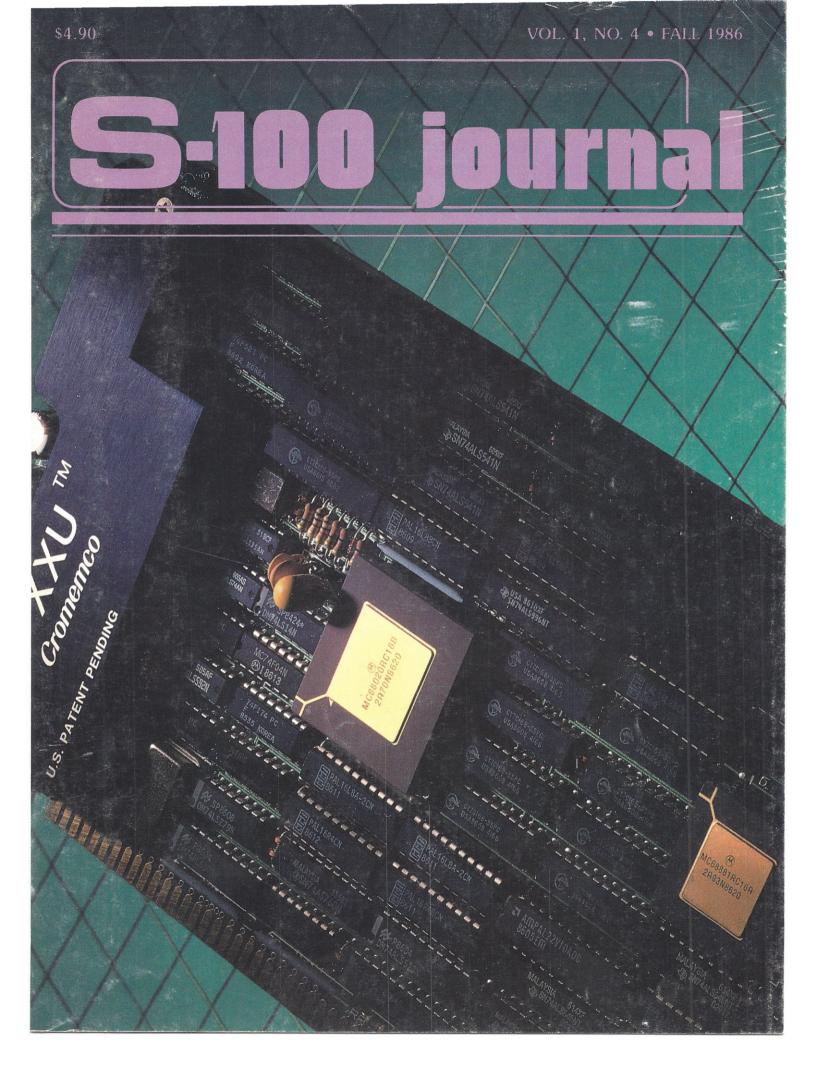

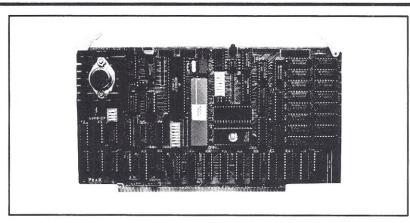

#### OUR COVER

The new XXU, a 68020/68881 CPU card from Cromemco, delivers true 32-bit processing for the S-100 bus. See page 69.

Cover photograph by Mark Gottlieb. Photograph production courtesy of Cromemco, Inc.

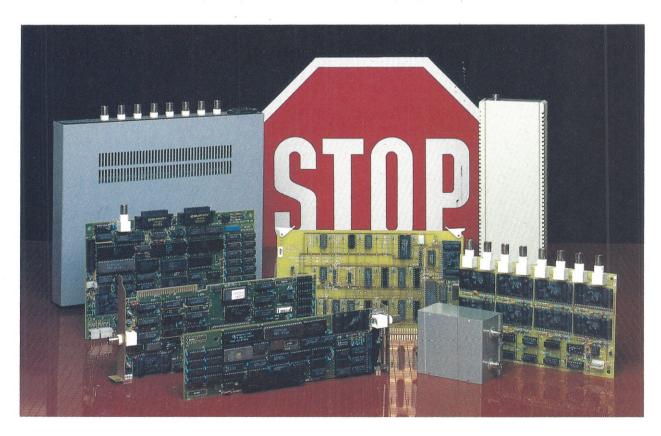

# What you should know about the S-100 market & Advanced Digital... BEFORE you buy;

"With the new wave of outstanding S-100 products hitting the market, S-100 manufacturers continue to assert their dedication to superior quality and innovative design. For many years ahead, they will equip thousands of small businesses and professionals with the most versatile and upgradable microsystems in existence."

> – Jay Vilhena, Editor S-100 Journal

## Attractive Features. Attractive Prices.

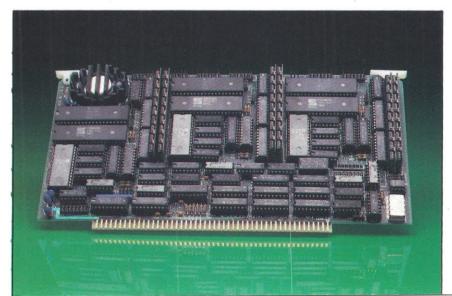

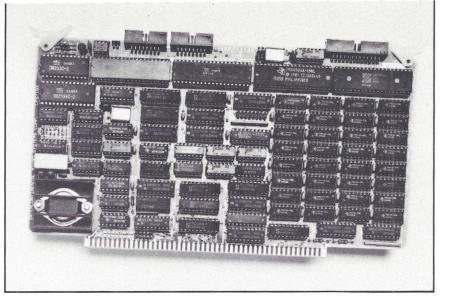

Advanced Digital Corporation offers the most complete line of S-100 products with the latest in the state-of-the-art microcomputer technology. All of ADC's S-100 products are powerful high speed 8-bit and 16-bit single board computers. Your S-100 system can grow from ordinary to awesome with ADC's superb family of S-100 boards quickly, easily and cost-effectively.

## 2. Financial Stability

Founded in 1980, Advanced Digital Corporation is one of the most financially sound, privately held computer manufacturers. The company has consistently shown a profit in every quarter since 1980. It is the intention of ADC to continue as the industry leader and remain in the forefront of technology assuring you of the finest product and service for years to come.

## **Ouality** Assurance

Rigorous testing of each and every product by ADC's highly skilled technicians assures customers of trouble-free products. ADC prides itself with the strictest quality control in the industry. No company has higher quality control standards, or a better success rate than ADC's. Every product is backed by a one year warranty. "At Advanced Digital Corporation our business philosophy can be stated in one word - "Pride." Pride in the quality and performance of the products we design and manufacture...Pride in the dedication, experience and performance of our employees...and Pride in our achievements and contributions to the S-100 marketplace."

Hossein Asadi, President Advanced Digital Corporation

## Customer Service; 1 24 Hour Repair.

Highly-skilled technicians are assigned to customer support full time. In most cases, a problem can be solved over the phone in a few minutes. If not, repairs can be completed within 24 hours from receipt of product. Centralized repair service is available through ADC's Service Center.

# Market Penetration; Over 12,000 units installed.

With an installed base of over 12,000 units worldwide, ADC provides service to thousands of businesses and individual owners. By developing a superior line of S-100 products, ADC has become a major force in the industry. Customers include: US Navy, NASA, Harris Systems, Aerospace Corp.

## Resources... Technical Expertise, Advanced Engineering.

ADC has assembled a team of highly experienced, industry renown specialists in engineering, manufacturing, marketing, sales and administration. ADC is a company of pioneers and innovators that have led the way and set the S-100 standards.

#

Founded in 1980, by a team of highly skilled and experienced engineers, Advanced Digital Corporation has grown to become a leading supplier of Single-Board Computers, Multi-User, Multi-Processor computer systems and memory subsystems for the S-100 Bus and PC

Compatible Product's marketplace. We're a company that has made tremendous growth without sacrificing the major factor that led to it. Quality...quality in our product, in our people, and in the way we do business.

Leading our success in the S-100 market, is a legacy of products that represent the needs of the S-100 market. Products such as Super System II, Super 16, Super 186 and Multi-Slave have made ADC the success it is today.

#### SUCCESS STORIES:

• SUPER SYSTEM II...A fully integrated system that runs under CP/M 2.2® for single-user applications or TurboDOS® for multi-user installations for both 8 and or 16-Bit including networking to PC's.

ADVANCED DIGITAL CORPORATION 5432 Production Drive • Huntington Beach, CA 92649 (714) 891-4004 • (800) 251-1801 • Telex 183210 ADVANCED HTBH • SUPER 16...The cost effective 16-Bit 8 MHz Multi-User Single Board Slave processor.

SUPER 186... The first high speed 8 MHz 16-Bit S-100 Single Board Computer.

MULTI-SLAVE...A three user board contains three independent computers at 8 MHz and runs the TurboDOS operating system.

The success of ADC in the S-100 market is also due to the following line of quality products: • Super Star • Super Quad • Super Six • Super Slave • Master 9.

At ADC we're an aggressive company, a progressive company, an innovative company. To be successful, we know that each product we develop must be totally unique to the market.

Our progress and success is with products that have gained the highest ratings and the respect of the entire S-100 industry. Our success is based on superior technology, unique features, and the most cost competitive prices in the market. When you're looking for progress, look to ADC, because it's the story of our company.

ADVANCED DIGITAL CORPORATION

ADVANCED DIGITAL U.K. LTD. eet. Hanover Square • London W1R8NQ-Unite

Huntington Beach, CA 92649

27 Princes Street, Hanover Square

London W1R8NQ-United Kingdom

(01) 409-0077

(01) 409-3351

TLX 265840 FINEST

" TurbosDOS is a trademark of Software 2000.

\* CP/M 2.2 is a trademark of Digital Research Corporation.

SEE US AT FALL/COMDEX 86 • BOOTH 1480

#### BYPASSING THE OBSOLESCENCE GAME

editorial

The September 1 issue of *Info-World* announces on its first page: 'IBM Planning to Replace PC Line, Analyst Predicts.' The September 8 issue of *Newsweek* carries a 16-page full-color ad from IBM promoting the PC line and accessories.

We know that it will happen again because it always has. Computers arrive and they soon depart. And companies will advertise their obsolete micros until the eve of the day they announce a new replacement (sometimes the replacement is not even obsolete!). And, until the eve of that day, there is no lack of takers who wake up the next morning to find that their \$2495 system is now advertised in *The Morning News* for \$995.

For the nontakers there are alternatives. S-100 systems continue to succeed as the never-obsolete micro. Consider that the S-100 bus was first introduced more than 11 years ago. Probably 90% of all the types of other computers that were born since are now long dead, never to be spoken of again. With them died most publications that over the years have emerged to support specific machines. *S-100 Journal* was introduced only 1 year ago. That's more than 10 years after the S-100 bus came on the scene. Yet, our magazine is flourishing and still steady on its course to support only S-100 computers.

During this past year, more than 30 new S-100 boards have been introduced. These are performance products that continue to expand the versatility and capabilities of the bus. Onemegabyte S-100 static RAM boards are now available from CompuPro, Lomas Data Products, and other companies. A twomegabyte static RAM board is available from MACROTECH International. From Intelligent Computer Designs comes the HD64180-based single board computer that carries on-board everything from memory to LAN controller. InterContinental

Microsystems places four HD64180 chips on a single board allowing four users on a single card. Inner Access is shipping SCSI interface boards that allow S-100 systems to run optical disk drives. Z80 slave boards have allowed running 8-bit software on 16-bit systems. Now Advanced Digital lets you have three Z80H CPUs running at 8 MHz on one slave board and throws in six serial ports. Teletek, Earth, ICM, and other S-100 companies are implementing sophisticated LANs that connect S-100's to many other computers and allow as many as 4,000 workstations. Finally, to top a successful year, we now have 32-bit S-100 boards from Cromemco.

The list goes on. It will continue growing in the future. In the most fluid industry of the century, only the S-100 bus is permanent this side of the VAX. If you own an S-100 system, keep it. If you don't, go out and buy one.

Jay Vilhena

#### S-100 JOURNAL ADVERTISEMENT POLICY

S-100 Journal is fully dedicated to the support of the S-100 bus. This editorial policy extends to the advertisements that are accepted for publication.

We welcome advertisers of S-100 systems, S-100 boards and other components, and most products or services adequate for the typical S-100 environment or which we judge to be of interest to the S-100 community in general. This includes terminals, printers, modems, software, accessories, supplies, and other products or services. Advertisements of nonS-100 systems and their accessories are not published. Advertisements of MS/PC-DOS software are usually not accepted. However, they can be accepted if the software is specially configured or produced for an S-100 system, or if it is also available, and is being advertised, for other operating systems.

Ads that are primarily S-100 and which include some nonS-100 material are usually accepted but are subject to our final approval.

We reserve the right not to publish any advertisement and to decide whether or not a product or service meets our S-100 criteria.

# The Peak of Performance

#### SCALE THE HEIGHTS OF PRODUCTIVITY

Sure, you've proven that in your hands a computer is a productive tool. But if you haven't teamed up with a SemiDisk you have heights yet to climb!

#### IT'S NO MERE RAMDISK

SemiDisk has been leading the way for Disk Emulators since their inception. If you've seen RAMdisks you know what it's like to load programs in an

## SEMIDISK

SemiDisk Systems, Inc. P.O. Box GG, Beaverton, Oregon 97075 503-626-3104

instant, and read or write files without delay. Unlike alternatives, the SemiDisk offers up to 8 megabytes of instant-access storage while leaving your computer's main memory free for what it does best - computing! KEEP A GRIP ON DATA

Go ahead, turn off your computer. Take a vacation. With the battery backup option, your valuable data will be there in the morning even if you aren't. You'll sleep better knowing not even a 5 hour blackout will sabotage your files.

#### NEW LOWER SEMIDISK PRICES THAT WON'T SNOW YOU UNDER

| •                  | 512K  | 2Mbyte |

|--------------------|-------|--------|

| IBM PC, XT, AT     | \$495 | \$995  |

| Epson QX-10        | \$595 | \$995  |

| S-100, SemiDisk II | \$799 | \$1295 |

| S-100, SemiDisk I  | \$595 |        |

| TRS-80 II, 12, 16  | \$695 | \$1295 |

| Battery            |       |        |

| Backup Unit        | \$130 | \$130  |

| Battery            |       |        |

Software drivers available for CP/M 80, MS-DOS, ZDOS, TurboDOS, and VALDOCS 2.

Call 503:646-5510 for CBBS/NW, and 503:649-8327 for CBBS/Aloha, all SemiDisk equipped computer bulletin boards, (300/1200/2400 baud) SemiDisk, SemiSpool trademarks of SemiDisk System

## **MACROTECH-STILL THE S-100** PERFORMANCE PACESETTER

MI-286. Our 80286/Z80H Dual CPU Board is at least twice as fast as Compupro's 8085/88 and it's a direct replacement. The MI-286 has already become the standard by which other 80286 based systems are measured. Ask us for a complimentary Benchmark Report.

ADIT. There's nothing else like it on the market. It's an Intelligent I/O Board with its own real time firmware that lets you control up to 16 different terminals, modems or printers all from a single slot. ADIT is the performance standard in environments such as Alpha Micro where I/O speed is critical.

> V-RAM. High performance Static CMOS system memory/virtual disk in either quarter or half megabyte configurations. With its onboard battery and power-fail logic, the V- RAM sets a new performance standard at conventional static memory prices. When accessed through I/O port channels, the half megabyte V-RAM becomes M Drive compatible with true non-volatile solidstate disk capability.

MSR. High performance and reliability in a memory so fast you won't believe it's a dynamic ram product. Compatible with all popular S-100 environments, the MSR's low power consumption and 120 nanosecond ram devices set a new standard for dynamic memory products. The MSR is available in guarter, half, one and two megabyte configurations at the lowest prices in the industry.

MACROTECH

ADIT

#### Dealers:

(415) 895-0798 (800) 222-8686 Gifford Computer Systems Custom Computer Technology (800) 423-5922 S-100 (212)448-6298 John D. Owens & Associates In England; Fulcrum (Europe) Ltd. (0621) 828763 Macrotech dealers also include most Compupro Systems Centers, Heathkit Electronic Centers and Alpha Micro Dealers.

MSR

MI-286

MACROTECH International Corp. 21018 Osborne Street, Unit #5 Canoga Park, CA 91304 (800) 824-3181 • in Calif. (818) 700-1501 elex: 9109970653

V-RAM

## editor interface

Welcome to our biggest and best issue so far. We'll stabilize at this size now for a few issues just to catch our breath. Whenever we think that production is under control, we decide to increase the number of pages and off schedule we go again. No more! Expect the next issue exactly 3 months from now like a well-behaved quarterly must do.

I want to once more thank all our subscribers for the support you continue to give us. It is your enthusiasm about the S-100 bus that runs this magazine. The S-100 bus belongs to all of us, not to any particular company, and I hope you feel the same about S-100 Journal. To that end, I'll incorporate into the magazine as many of your ideas and suggestions as possible within our S-100 editorial direction.

Whenever you have questions, comments, suggestions, or complaints about the magazine, any of our articles, or any of the subjects discussed in this column, please write to Editor Interface, S-100 Journal, PO Box 1914, Orem, UT 84057. We prefer to receive your letters typewritten (dot matrixed?).

Let's read some of the mail since the last issue:

#### **More PC Feelings**

I recently received my first copy of S-100 Journal and was very pleasantly surprised by the content and editorial quality. I am extremely pleased to **at last** find a strictly S-100 oriented magazine.

It is certainly 'hiding your head in the sand' to ignore IBM. On the other hand, I don't own an IBM, I don't want one, and I am frankly tired of IBM. Congratulations on publishing **S-100 Journal**!

Mark Pickerill Salinas, California I just read the Editor Interface section in issue number 3 and I'd like to address a few of the points raised.

It seems there are lots of people out there who, for one reason or another, would have the major manufacturers of S-100 boards and systems refocus their attention to the task of building S-100 versions of the IBM PC. While I can certainly sympathize with the frustrations of those who wish they could run all those 'Gee Whiz!' PC graphics programs on their S-100 computers, I don't expect to see the S-100 market go in that direction.

My advice to those who would like to run all those great programs written for the PC is to go straight out and buy a PC. The little devils are so cheap now that they can be bought for very little more than the price of a standard computer terminal. They can also be networked to S-100 systems, thus providing the best of both worlds. And they are so universally supported by peripheral vendors and software developers that the IBMoriented computer hobbyist can stay busy for years just finding out about all the stuff.

Now, before you jump to the conclusion that I have somehow lost all of my marbles and am advocating the abandonment of the S-100 bus (which for an owner of a CompuPro System Center would seem a silly thing to do), let me point out a few areas in which the venerable IEEE-696 standard is, in my opinion, years ahead of the PC.

**Modularity** — the ability to upgrade to later technology as it becomes available. (Let's just wait and see how impressed the owners of all those 8088/8086 PC compatibles will be with the next generation of 'IBM-compatible' software products which will **only** run on 80286/80386 processors with multimegabyte directly-addressable RAM areas. Just smile as you tell them how you swapped-in that new CPU board and installed that new operating system.)

**Multiuser Effectiveness** — As the PC crowd continues to wait for a clear winner to emerge in the multiuser arena, and quick-fix approaches continue to proliferate as inexperienced PC dealers grapple with this 'new' technology, we S-100 users can enjoy the benefits of mature, multiuser/multitasking systems which have been working effectively for years.

Long-term Flexibility — To a growing business, in these times of rapid technological change, the ability to reconfigure, expand and enhance the central computer system can have a significant, positive effect on the bottom line. The modularity of an S-100 system can allow its owner to adapt the existing computer to fit changing requirements in cases where a less flexible system would have to be discarded and replaced.

**Reliability** — Most PC compatibles are designed by people who expect their machines to compete largely on the basis of price. The obvious consequence of that circumstance is that, during the design process, these products must often sacrifice a certain amount of 'reliability margin' in exchange for a higher return of performance for the consumer's dollar. This translates to a higher incidence of component failure than would be the case otherwise. S-100 systems, on the other hand, are for the most part being marketed to more sophisticated and demanding buyers who may place a higher value on system reliability. To many businesses, a loss of data or a few days of down time would represent a much greater expense (in terms of dollars) than the extra cost for a more reliable system.

For these and many other reasons, I am confident that the S-100 bus will continue to flourish in the (continued on page 55)

## A FAST WAIT STATE GENERATOR

BAB hus

696 Bus is a regular column that concentrates on the hardware aspects of the IEEE-696 bus (i.e., the S-100 bus) and answers questions that readers might have about the IEEE standard.

Don Pannell, our 696 bus columnist, is an S-100 hardware enthusiast and is coauthor of the IEEE-696 standard. He bought his first S-100 system (an Altair 8800b kit) in January 1978 and has since designed and built most of his present components. These include a terminal, EPROM programmer, serial/parallel I/O cards, two designs of DMA floppy-disk controller, and a 68000 coprocessor card. Don is president of Peak Electronics and is technical editor for S-100 Journal.

If you have questions about the S-100 bus and IEEE standard, write to Don Pannell, PO Box 700112, San Jose, CA 95170-0112. Your questions can range from architectural concerns to how to interface a specific device or function with the bus. In future issues, Don will incorporate answers to the most common questions. major advantage of the S-100 bus is its ability to accept various speeds of devices on the same bus at the same time. This feature allows a system to be upgraded one card at a time and has helped prolong the life of many systems. To make this possible, a slow device must be able to place the bus master into wait states. This is done with a wait-state-generator circuit.

At first glance, the need for a fast wait state generator is not apparent. In fact, it seems to be a contradiction of terms. Why worry about speed when the reason for a wait state generator is to slow accesses down? Simply put, the faster the processor the less time there is for the wait state circuit to do its job. If a board is expected to work with an 8 or 10-MHz bus clock, and it needs to insert wait states as well, its wait state generator must be fast.

#### WHAT ARE WAIT STATES?

Wait states are used to stretch the bus read strobe (pDBIN) or the bus write strobe (pWR\*) to allow slow devices to communicate with a fast processor.

When wait states are not used, read and write strobes can be as small as 0.9 tCY (tCY is the bus-cycle time tCY values for common clock speeds are shown in Table 1). This implies strobes of 90ns for a 10MHz processor. But many I/O devices, like serial chips and floppy-disk controllers, require more than 90ns, and often more than 150ns, for their read and write strobes. The only way to interface these chips to a fast bus is to use wait states.

Don Pannell

Each wait state will increase the width of the strobes by 1 tCY.

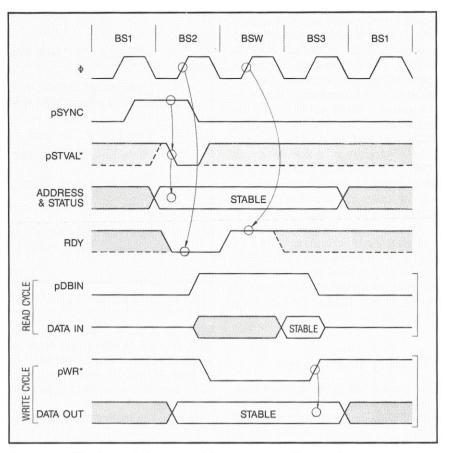

Figure 1 shows the fundamental timing relationships that occur during a bus cycle. It depicts a bus access with one wait state (BSW) inserted between bus states 2 (BS2) and 3 (BS3). This wait state was inserted because the bus ready line (RDY) was low during the rising edge of  $\Phi$  (Phi) in bus state 2 (BS2). If RDY were low again during the rising edge of  $\Phi$  in BSW, another wait state would have been inserted. This method allows for any number of wait states to be generated for any access.

#### FUNCTIONS OF A WAIT STATE GENERATOR

The job of a wait state generator is to perform the functions outlined in Table 2, page 10. This does not sound difficult until you try to make the circuit work at 10 MHz while keeping the bus loading within specifications.

There is another problem: the IEEE-696 standard is not complete in this area. No specifications are given for the maximum amount of time allowed between the address or status lines becoming stable and the wait state circuit asserting RDY. Calculating these values from the existing timing specifications results in numbers that are impossible to use.

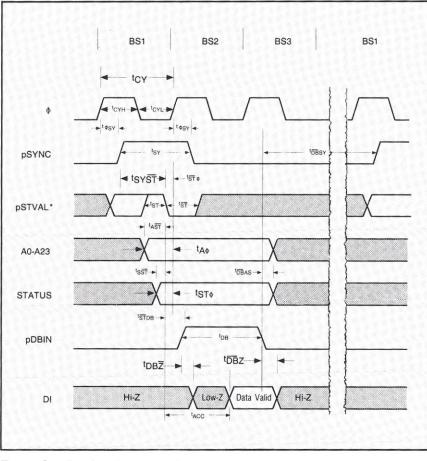

It is very useful for a designer to know how much time is allowed for the wait state generator to determine if the addresses are within the desired range so that RDY can be pulled low. This specification, if it were present, would be called tARDY for 'delay Addresses stable to RDY stable.' To calculate tARDY from the documented IEEE-696 specifications, one proceeds as follows (please refer to Figure 2 for the read-cycle timing diagram):

$tARDY = tAST^* + tST^*\Phi - tRDY\Phi$  where

$tAST^* = Address stable prior to pSTVAL^* low during pSYNC high. IEEE specification is 70ns.$

$tST^{*}\Phi = pSTVAL^{*}$  low prior to  $\Phi$  high during pSYNC. IEEE specification is 0ns.

$tRDY\Phi = Setup time RDY to \Phi$  rising. IEEE specification is 70ns.

Therefore,

tARDY = 70ns + 0ns - 70ns = 0ns!This means that the wait state generator must pull RDY low 0ns after the addresses are stable. Obviously, this is an impossible circuit to build.

The other missing specification should define how much time the wait-state circuit has to pull RDY low, counted from the time the status lines become stable. This would be called tSRDY, 'delay status stable to RDY stable.' Its equation is:

$tSRDY = tSST^* + tST^*\Phi - tRDY\Phi$  where

$tSST^* = Status$  stable prior to pSTVAL\* low during pSYNC high. IEEE specification is 40ns.

$tST^*\Phi = pSTVAL^*$  low prior to  $\Phi$  high during pSYNC. IEEE specification is Ons.

$tRDY\!\Phi$  = Setup time RDY to  $\Phi$  rising. IEEE specification is 70ns.

With these values, tSRDY = 40ns + 0ns - 70ns = -30ns!This part of the circuit has an impossi-

ble job: it has to know what is going to happen before it does. In the real world, tARDY and tSRDY must both be positive

numbers. It is the responsibility of the CPU vendors to insure that adequate time is allotted for wait state generators to perform their function. And it is the job of the wait state generator designers to make the circuit as fast as possible.

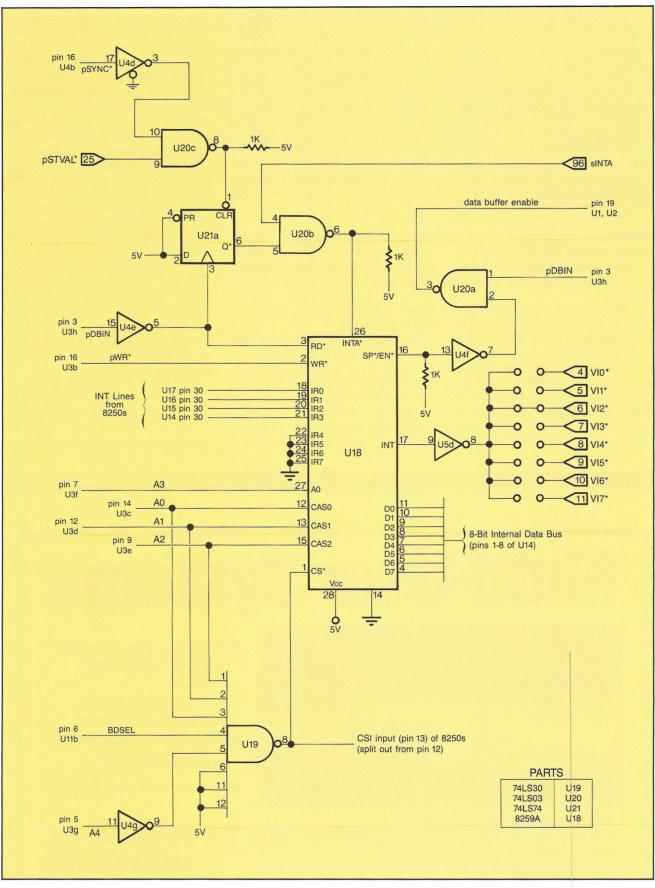

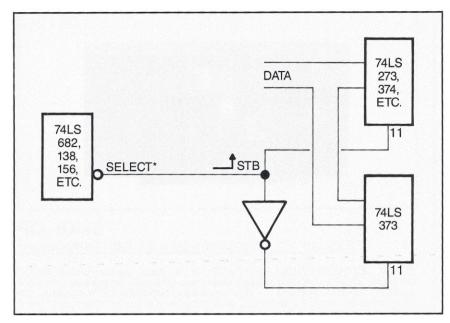

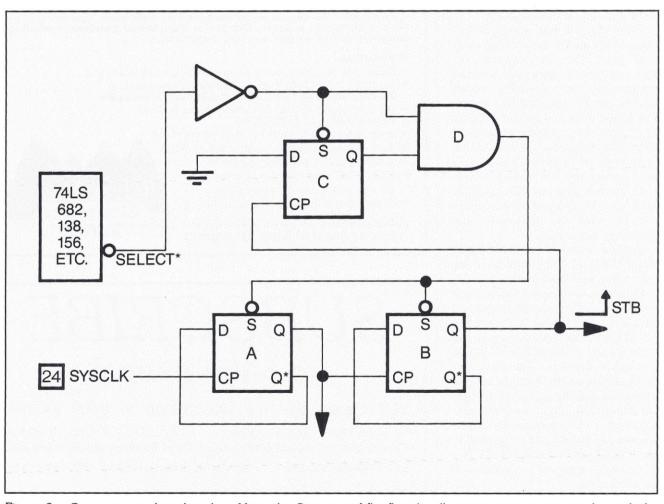

## THE FAST WAIT-STATE CIRCUIT

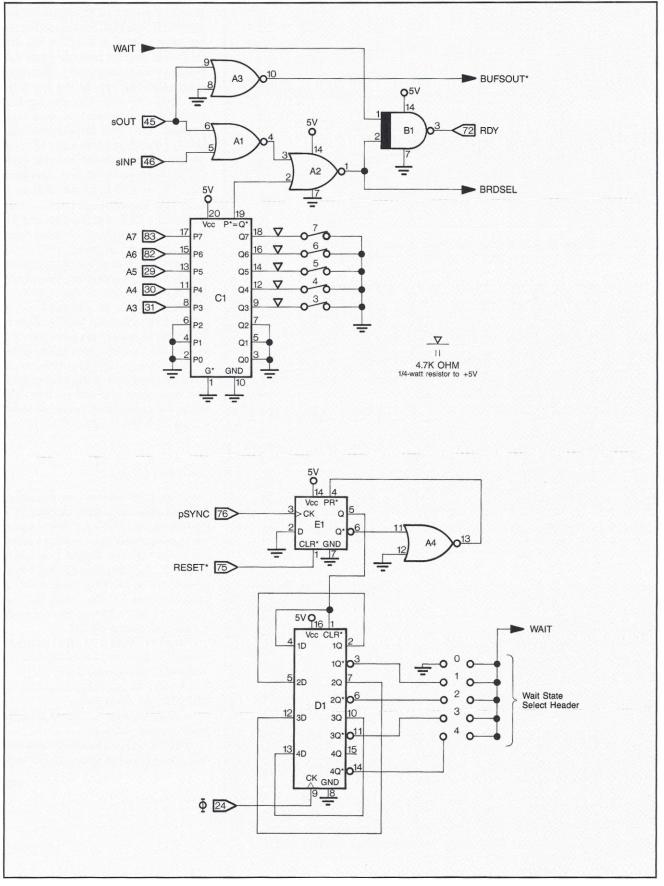

The top of Figure 3 (page 11) shows the first half of a very fast wait state generator for I/O devices. It performs functions 1, 2, and 3 (as listed in Table 2). An I/O-device wait state generator

Figure 1. Fundamental timing relationships of a bus cycle.

is shown for two reasons. First, it is the type of wait state generator most likely to be used. Second, it is the worstcase circuit due to the values that must be decoded from the status bus during I/O operations.

This part of the circuit (Figure 3 – top) works as follows:

Chip C1 compares the bus address to that preset on the I/O board's dip switch. The output of C1 (pin 19) will go low whenever a match exists.

| CLOCK  | tCY    | 0.9 tCY |

|--------|--------|---------|

| 2 MHz  | 500 ns | 450 ns  |

| 4 MHz  | 250 ns | 225 ns  |

| 6 MHz  | 166 ns | 150 ns  |

| 8 MHz  | 125 ns | 112 ns  |

| 10 MHz | 100 ns | 90 ns   |

|        |        |         |

Table 1. Bus clock speeds and corresponding tCY values.

Gate A1 decides if the bus cycle is an I/O cycle by looking at the bus status lines. The output of A1 will go low whenever an I/O bus cycle is in progress.

Gate A2 combines the outputs of the above two functions. Its output will go high whenever the address and bus cycle are directed to this I/O card. Hence, this output is called BRDSEL for *board select*.

Gate B1 is used to pull RDY low if wait states are needed. This will happen whenever the board is selected (BRDSEL is high) and WAIT is high. WAIT comes from the second half of the wait state generator, and it will be discussed later.

Gate A3 is not part of the wait state generator. It is shown, however, because most designs need to know as soon as possible if a read or write operation is going to take place. An area where this may be important is in enabling the I/O board's internal data bus drivers. The only signals that can perform this function are the sOUT and sINP status lines. One or both could be buffered and then sent to gate A1. However, this would slow down the wait state circuit. The only way to solve the timing problem is to double-load one of the bus nets (as shown). This is allowed as long as the bus-loading specifications are not violated. Unfortunately, two LSdevice input loads would violate the specification. But ALS works. (One ALS input load = 1/4 of an LS input load). Therefore, chip A in the circuit must be a 74ALS02. The same chip should be used for both gates A1 and A3 to reduce the length and capacitance of the input net.

Table 3 lists the amount of time this wait state circuit takes depending on the types of chips used for B1 and C1 (again, chip A must be a 74ALS02). All listed combinations will work and meet the IEEE bus-loading specifications.

#### **Counting Wait States**

The second half of the fast wait state generator is shown in Figure 3, bottom. This logic performs function 4

#### ROLES OF THE WAIT STATE GENERATOR

1. Determines if the address on the bus matches the address of the device that needs longer read or write strobes.

2. Decides if the bus cycle is of the proper type (for example, I/O or memory).

**3.** Pulls RDY low 70ns before the rising edge of  $\Phi$  in Bus State 2.

4. Keeps RDY low for as many bus states as needed, and raises it 70ns before the next rising edge of  $\Phi$ .

Table 2. The functions of a Wait State Generator.

(as listed in Table 2) which is to keep RDY low for as many bus states as needed. When it does allow RDY to go high, it must do so (according to IEEE specifications) 70ns before the rising edge of  $\Phi$ .

At slow bus speeds, these goals are

Figure 2. Read-cycle timing diagram.

easily met. But, if the bus clock is 10MHz (tCY=100ns), some design options are lost. At 2 or 4 MHz, the wait state counter (chip D1) can be reset by an inverted copy of pSYNC and clocked by an inverted copy of  $\Phi$  (see Figure 2 for timing relationships). But, at 6 to 10 MHz, an inverted copy of  $\Phi$  cannot be used. The rising edge of  $\Phi$  must clock the wait state counter so that there is the maximum amount of time for the counter's outputs and RDY to change before the next rising edge of  $\Phi$ . Table 4 lists the possible delays (from a rising edge of  $\Phi$  until RDY is high) for the bottom circuit in Figure 3.

For any system, the maximum delay allowed from  $\Phi$  to RDY is tCY-70ns. Table 5 lists this value for common  $\Phi$  values.

Tables 4 and 5 show that it is possible to meet the IEEE specification for the RDY setup time of 70ns, but, for a fast clock, it is difficult.

Since the number of wait states must be counted by the rising edge of  $\Phi$  (as opposed to the falling edge of  $\Phi$ ), an inverted copy of pSYNC cannot be used to reset the counter. If it were used, it would be impossible to insert only one wait state. This is because the first rising edge of  $\Phi$ that should clock the wait state counter would fail to do so. The counter would fail to do so. The counter would be held in reset mode by pSYNC still being high (pSYNC must be high on the rising edge of  $\Phi$ in bus state 2 — refer to Figure 2).

To solve this problem, the wait state

Figure 3. Circuits of the Fast Wait State Generator.

|          | tARD  |          | RDY       |

|----------|-------|----------|-----------|

| CHIP B   | tSRDY | C1=LS688 | C1=ALS688 |

| B1=LS38  | 50ns  | 63ns     | 60ns      |

| B1=ALS38 | 40ns  | 53ns     | 50ns      |

| B1=S38   | 32ns  | 45ns     | 42ns      |

Table 3. Worst-case timing delays from addresses stable to RDY stable.

| D1=LS175 | D1=ALS175                       | D1=S175                                                                            |  |

|----------|---------------------------------|------------------------------------------------------------------------------------|--|

| 57ns     | 36ns                            | 49ns                                                                               |  |

| 58ns     | 37ns                            | 50ns                                                                               |  |

| 35ns     | 14ns                            | 27ns                                                                               |  |

|          | <b>D1=LS175</b><br>57ns<br>58ns | D1=LS175         D1=ALS175           57ns         36ns           58ns         37ns |  |

Table 4. Worst-case timing delays from the rising edge of the clock cycle to RDY high.

| CLOCK (Φ) | tCY    | MAXIMUM $\Phi$ to RDY |

|-----------|--------|-----------------------|

| 2 MHz     | 500 ns | 430 ns                |

| 4 MHz     | 250 ns | 180 ns                |

| 6 MHz     | 166 ns | 96 ns                 |

| 8 MHz     | 125 ns | 55 ns                 |

| 10 MHz    | 100 ns | 30 ns                 |

|           |        |                       |

Table 5. Maximum  $\Phi$ -to-RDY delays for various bus clock speeds.

counter is reset by a 'chopped' version of pSYNC. pSYNC is chopped by using one half of a 74LS74 flip-flop (chip E1) and an inverter (gate A4, but any inverter will work). The rising edge of pSYNC clocks the low D input to the Q output of the flip-flop which in turn resets the wait state counter (D1). The Q output is held low for the time it takes the Q\* output to go through the inverter (gate A4) and preset the flip-flop. This takes about 25ns and is plenty of time to fully reset the wait state counter (chip D1). Note: Both the flip-flop and the counter are reset by the bus reset line (RESET\*, pin 75) going low.

The desired number of wait states is selected by connecting (usually by jumper plugs) one of the outputs of the wait state counter to the input of gate B1 (signal name WAIT). Zero to four wait states are possible with this circuit. If zero wait states are needed, WAIT is always held low. Otherwise, WAIT will go high at the start of each bus operation and will go low only after the selected number of rising edges of  $\Phi$  have occurred.

#### CONCLUSION

Wait state generators are necessary when connecting slow devices to a fast processor. While the devices may be slow, the wait state generator must be as fast as the fastest bus speed allowed. Unfortunately, the IEEE-696 standard is lacking some timing specifications in this area, so the design of the high-speed wait state generator is very critical.

Future revisions of the standard should specify the following new or revised timing parameters:

tARDY, Delay Address Stable to RDY Stable, 65ns (new).

**tSRDY**, Delay Status Stable to RDY Stable, 55ns (new).

**tRDY** $\Phi$ , Setup Time RDY to  $\Phi$  Rising, 20ns (current standard is 70ns).

multiuser os

ast time we compared three similar operating systems available for the Motorola 68000: d/OS, AMOS/L, and Mirage. Among them, d/OS is emerging very strongly due to the tireless work of Mike Lewis and his associates at d/Soft. We will now take a closer look at this operating system.

#### SCREEN FEATURES

Several aspects of d/OS set it apart from other multiuser operating systems on microcomputers. Most apparent is the 'look' of the operating system. Both d/OS and its utilities make extensive use of CRT features such as cursor positioning, reverse video, intensity control, etc. Many commands and utilities have status displays or are menu-driven with block cursors. This is not just for aesthetics but to provide information and easy-to-use options not normally available in system utilities.

Most second-party operating

systems assume a teletype-like terminal since they cannot count on any particular terminal being attached to a given port. In d/OS all commands that control terminal functions are generic. The terminal driver then translates the generic commands into those required by the terminal in use. And d/OS allows a given terminal driver to be loaded at any time. If a user logs in with a terminal that is not setup for that port, then a simple command (e.g., DRIVER WYSE50) loads a new terminal driver for that port.

#### MODULARITY AND SYSTEM GENERATION

Device independence and modularity have been carried to a near limit and include terminal, character I/O, disk, tape, and CPU (clock and timer) drivers. Making new drivers is not terribly difficult, and source code for a number of sample drivers is provided.

This modularity makes it easy to

#### WANTED OPERATING SYSTEMS EXPERTS

We are expanding the *Multiuser OS* column to include several authors. Each columnist will need to be expert in only one operating system. Gary Feierbach will continue to write about d/OS, Mirage, and AMOS/L, and we are looking for other columnists to write about TurboDOS, Concurrent DOS, THEOS, Unix, OS-9, S1, and other multiuser operating systems currently running on S-100 micros. Each columnist will also be expected to read mail and answer questions from readers.

Columnists must have a solid knowledge of the OS they write about and must be currently running or implementing it on S-100 systems. A columnist may be a vendor of the operating system but cannot be part of the software company that produces the operating system. If you are interested in becoming a columnist for *Multiuser OS*, please write to S-100 Journal, PO Box 1914, Orem, UT 84057, or call Jay Vilhena (801-373-0696).

#### Gary Feierbach

configure the operating system for new combinations of disk and tape drives, terminals, and jobs. A menudriven program is provided, making system generation even easier. This program allows the user to completely and accurately reconfigure the system and the job environment in as little as 30 seconds, assuming that the drivers already exist on the system. This feature is of particular importance to VARs who have to support many system configurations and have to generate new ones with relative ease. With other systems, many dealers try to limit the number of configurations they sell since system generation is typically difficult. With d/OS, Henry Ford's quote 'You can have any color you want as long as it is black' need not be a computer vendor's motto.

#### MULTITASKING

A user can initiate any number of tasks with the LAUNCH command. Each task launched takes space from the system memory heap with its terminal output directed to an associated file. These tasks are spun off as temporary jobs that release the acquired heap space after completion. Utilities are available to examine the status of the jobs as they progress and to view the terminal output. A super programmer will never again have to hog three terminals to maintain high productivity. Programs can assemble and compile while the programmer edits or debugs other modules using only one terminal. Perhaps the programmer will loose some much-needed exercise by not jumping from one terminal to another.

#### THE SCHEDULER

The heart of any time-sharing system is the job (task) scheduler. Most microcomputer-based systems use a simple round-robin scheduler with fixed maximum time for each job. But d/OS sports a full-blown, dynamicpriority scheduler with enormous flexibility. Jobs can be assigned priority ranges within which the scheduler can operate. The scheduler promotes jobs that have been bypassed by higherpriority jobs until they finally get a piece of the pie. Some low-priority jobs may not get to run at all until very high-priority jobs are completed. This has a strong effect on the user's perception of the system response time, and it can dramatically change the number of users a given system can comfortably support.

#### WILDCARDS AND WILDFILES

All operating systems have wildcards like \* (asterisk) that can be used in filenames, allowing a group of files to be dealt with collectively. Many commands (e.g., DIR, COPY, ERASE, PRINT, and BACKUP) use this facility. In d/OS, this concept is applied to an extreme that some would consider bizarre. Consider the following example:

#### \*LS\*,-\*AB\*,-\*.LIT

This would specify the set of all files with LS in the filename, excluding all those with AB or with the extension LIT.

The next example, although more complex, also has a straightforward interpretation:

{A−F}@@#\*.BAS,TEST.BAS, TRIAL#.BAS,-C\*.BAS,-TRIAL3.BAS This represents the set of all files beginning with a letter from A through F, followed by two more letters, then a number, then any other characters, and the extension BAS. Also included are the files TEST.BAS and TRIAL0.BAS through TRIAL9.BAS. From this set we exclude any file that begins with C and has the extension BAS, and we also exclude the file TRIAL3.BAS.

These specifications can easily become unwieldy, but we can place them in a file and make them multiline for readability, editability, and future use. Assuming the wildcard specifications are put into the

file SPEC1.WLD, then preceeding the filename with an apostrophe ('SPEC1.WLD) indicates a wildcard-specification file to the using program. These in turn may be part of a specification list as in:

'SPECX.WLD,'OTHER.SPC,-WS#.BAS This would specify the set of files resulting from merging the files SPECX.WLD and OTHER.SPC, but excluding the files defined in WS0.BAS through WS9.BAS.

At this point, one is moved to ask why such a capability is necessary. A simple example will help. Suppose a user wants to dump a directory onto floppy disk, but the floppy disk capacity is less than the contents of the directory. The following copy commands could be used to place the file in two disks:

#### COPY FLP0: = $\{A - M\}^{**}$

(for first floppy) COPY FLP0: =\*,- {A-M}\*\* (for second floppy)

The user may utilize this wildcard capability in a program that he or she generates (e.g., PROG1) by using wildcard system calls or simply by typing:

#### X PROG1 wildspec

Here, X is a utility that will keep recalling the program PROG1 until all the files defined by 'wildspec' are used up. PROG1 will think it is called each time followed by a specification for a single file. With the X utility, the user can thus avoid the complexity of the wildcard system.

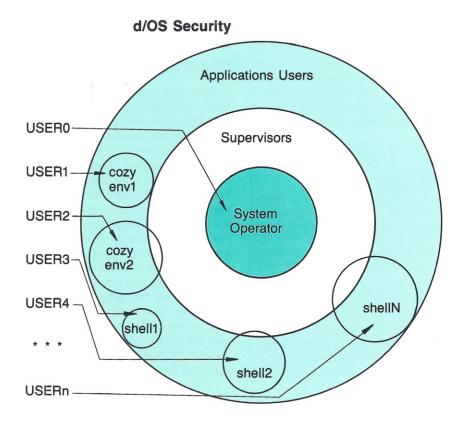

#### SECURITY

When a user logs onto the system, he (or she) provides his initials, password, and company or department name or initials. At this point, he is granted access privileges that depend on his security level and the account, program, or shell he may be autologged into.

There are two programs, d/SHELL and COZY, that can keep users in a restricted enviroment. d/SHELL is a sophisticated menu-generating program that uses a block-structured script to generate a hierarchy of menus. COZY allows a user to talk to the system in the normal fashion, but under the control of a file that contains the names of the programs he is allowed to run.

#### TIMING AND BILLING

Each user is assigned an account number (typically associated with a company or department name) and a subaccount number (usually associated with the individual). Each time a user logs onto and off the system, the elapsed time is recorded for that account. Charges can be levied for three levels of CPU and three levels of disk-block usage. Charges are setup by account number, so rates can be different for different accounts. A billing program is provided, complete with source, so that it may be modified to handle a particular customer's requirements.

#### UTILITIES, UTILITIES

The operating system comes with a number of quality utilities, and each deserves some mention. Included is a macroassembler, Extended BASIC compiler, BASIC debugger, editor (for both program writing and word processing), text formatter for laser printer, disk caching, printer spooling, electronic mail, bulletin board, communications package, and of course all the usual utilities for disk maintenance, copying, and for poking around in the system.

#### Extended BASIC

The Extended BASIC compiler is AMOS/L-compatible at both the source and object level. It is also compatible with Softworks' BASIC compilers for the Macintosh, Atari ST, and Amiga computers. The compiler features implicit data-type conversion, allowing strings and numeric quantities to be freely mixed in expressions. Routines like FIX and VAL are still provided for compatibility and type forcing.

The most powerful feature of this BASIC is the MAP feature (borrowed from Alpha Micro). It permits the construction of very complex data structures that can involve arrays of strings, floating-point numbers, and integers from one to five bytes long. MAP statements may share the same area of memory. This last feature makes them particularly suitable for constructing record formats.

The BASIC debugger features a single-step capability that allows statement-by-statement execution, under cursor control, through source code. Break points can be set at particular statements or when variables meet a certain condition or change in value. Variables can be displayed at any time. BASIC programs can be checked quickly and thoroughly using this software. It makes the debugging technique of sprinkling PRINT statements throughout a program appear primitive and laborious.

#### Editor

The d/VUE editor, included with d/OS, was originally intended as a source code editor, but, over time, capabilities have been added that make it a reasonable word processor for letters and manuals. Editor functions include the ability to move blocks of text, set margins and tabs, and all the usual cursor controls to move quickly through text. For programmers, some useful features are auto-capitalization, command macros and macro-learning mode. Also included are searchand-replace (with or without query) and word-wrap functions. The commands are fairly intuitive, making it easy to learn.

#### Electronic Mail and Bulletin Board

Electronic mail is borrowed from large time-sharing systems and in d/OS it offers a few small refinements. Each user has a mail box, and mail can be sent from user to user, to groups of users, or to everyone on the system. In addition, general purpose mailboxes can be defined that are treated as bulletin boards by groups of users or by the system at large. Commands are available to sort, select, and read only messages on topics of interest.

In 'chat' mode, users logged on simultaneously can exchange messages in real time. With 'certified' mail, reply messages are automatically transmitted when the original message is read. A d/VUE-like editor

TurboDOS is a trademark of Software 2000 IBM-PC is a trademark of IBM within the mail subsystem facilitates message composition. It even includes the macro-learning capability.

#### **Communications**

Two d/OS systems can talk to one another via telephone (or direct wire for that matter) using the communications software provided with the system. This software allows a user at one terminal to converse, through another port, with another system and to send files back and forth. In the 'transparent' or terminal mode, it appears as though one is sitting at a terminal on the remote system. In file transfer mode, two programs FSEND and FRCV are started at each end. These programs check each block transmitted, correcting errors when possible, or retransmitting the block if necessary. The size of the block transmitted is adaptive and dependent on line conditions.

#### APPLICATIONS SOFTWARE

Applications for d/OS include the large body of software already developed for the AMOS/L operating system. These include accounting, inventory control, database management, professional (medical, dental, legal, and CPA), restaurant and hotel management, finance, wholesale distribution, education, construction, and engineering packages. A number of database application generators are also available, including Andi (from d/Soft) and SUMUS (from CShare).

#### **NEGATIVE ASPECTS**

In d/OS there are a few shortcomings that hopefully will disappear soon. The most glaring is its adherence to the Intel (and DEC) bute order within a word. This stems from Alpha Micro's use of the Western Digital chip set before going to the 68000 processor. To be compatible, d/OS followed suit. On a system without DMA, one can simply reverse UDS and LDS on the 68K processor. DMA requires a more extensive modification. Currently, d/OS runs on S-100 systems from Inner Access Corporation (Intel or Motorola order) and Alpha Microsystems (Intel order). However, d/Soft plans to make a piggyback board that will plug into a 68000 socket and perform the byte swap for other manufacturers. At some point, a version of d/OS which will adhere to the Motorola byte order is likely. Mike Lewis, of d/Soft, indicated that such a version might be a year away (sooner if a manufacturer is interested in underwriting the changes.)

Another shortcoming is the use of 16-bit file pointers. This limits logical drive and therefore file size to 32

megabytes. A 90Mb drive is necessarily subdivided in smaller 30Mb logical drives. This has not been a serious problem, but now, with the advent of gigabyte CD-ROMs, it is beginning to look more limiting. Plans for changing this are in the works and are likely to be accomplished within the next six to nine months.

#### CONCLUSION

Presently, d/OS is going through a rapid evolution with a number of very dramatic improvements in just the last few months. If this pace continues unabated, d/OS could become the most outstanding operating system for microcomputers whether single or multiuser. It's a sound operating system with a good set of development tools. It makes efficient use of the 68000, leaving over 98% of the processor's computational power for jobs. The next d/OS revision level will take advantage of the performance improvements offered by the Motorola 68010 and 68020 processors. The current price of d/OS is \$1250.

The production of good operatingsystem software requires clear, elegant thinking and accurate programming; d/Soft seems to have this talent.

d/OS is a product of d/Soft. For more information on d/OS contact d/Soft, 310 Cedar Lane, Teaneck, NJ 07666.

S-100 JOURNAL, VOL. 1 NO. 4

DON'T HIDE

FROM

YOUR MARKET

IF YOU SELL S-100 OR RELATED PRODUCTS, S-100 JOURNAL IS THE NATURAL ENVIRONMENT TO ADVERTISE THEM

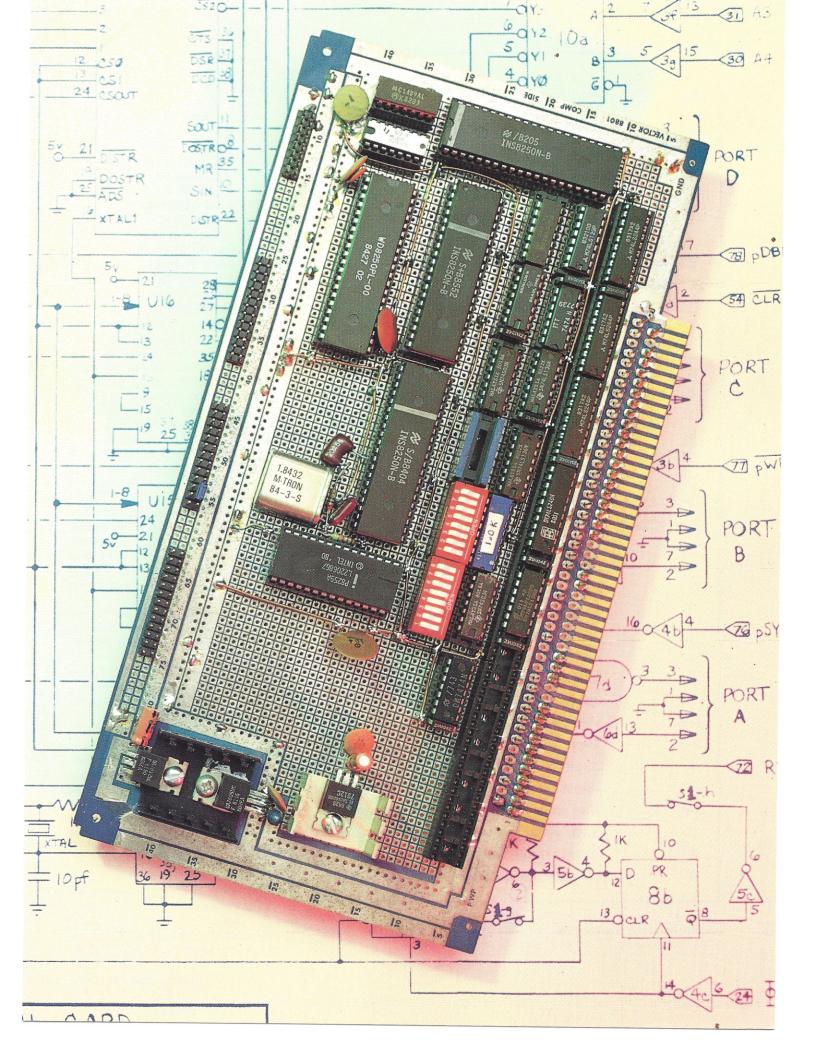

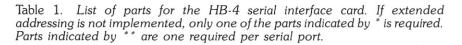

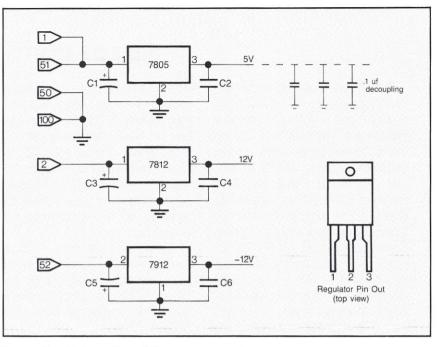

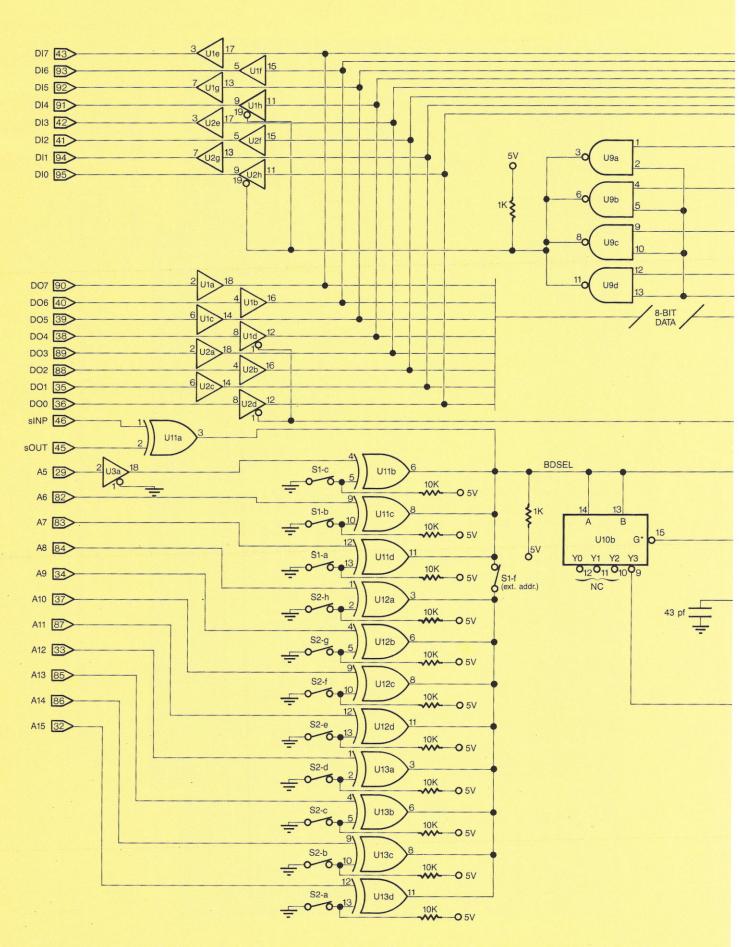

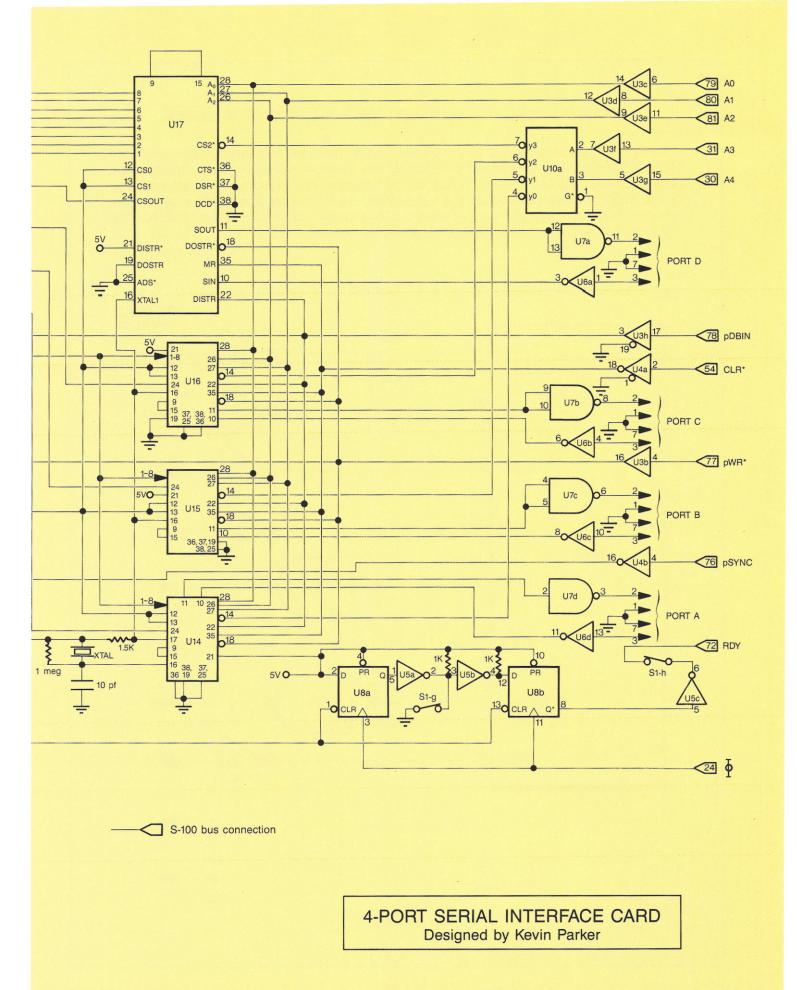

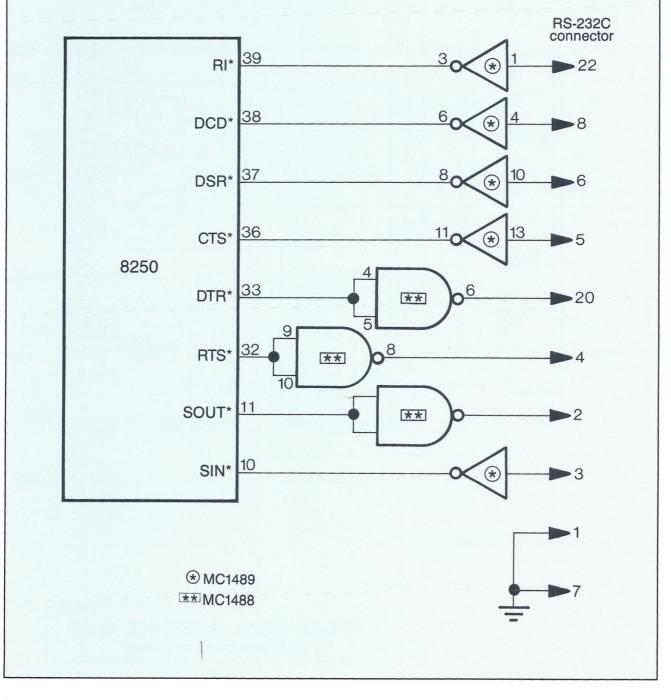

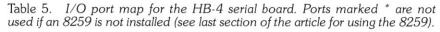

| MS-DOS 2.0 DEVICE DRIVER FOR<br>THE HB-4 SERIAL INTERFACE S-100 BOARD<br>Text starts on page 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| THIS SOFTWARE WAS WRITTEN BY KEVIN PARKER. COPYRIGHT © 1986 BY KEVIN PARKER.<br>PERMISSION GRANTED TO REPRODUCE THESE PROGRAMS FOR INDIVIDUAL OR IN-HOUSE USE ONLY. THE SALE OF<br>THESE PROGRAMS IN WHOLE OR IN PART WITHOUT WRITTEN PERMISSION FROM THE AUTHOR IS PROHIBITED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| <pre>This device driver is written for an HB-4 Serial Port card that has all four 8250 UARTs installed. Code is provided for polled driven and interrupt driven I/O. Each UART's serial line characteristics can be read and manipulated through MS-DOS using Function 44h (I/O Control for Devices). Interrupt driven I/O buffer status can also be controlled and read with this operating system call. The format of the control strings that will perform these functions is as follows: For IOCTL Input (to get device information) - Up to 7 bytes are returned that contain the following information:     Ist word - Number of bytes waiting in the input buffer.     Znd word - Number of bytes in the output buffer.     Srd word - Baud rate in bits/sec (binary number). The baud     rate must be between 4 and 56K baud.     The byte - Configuration information as follows:     </pre> |  |  |

| Stop bits       Parity       Data length (in bits)         00 - 1 bit       00 - none       0101 - 5 data bits         01 - 1 1/2       01 - even       0110 - 6 data bits         10 - 2 bits       10 - none       0111 - 7 data bits         11 - odd       1000 - 8 data bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| ; For IOCTL Output (to set device characteristics) - A string (maximum<br>length <65536) that is composed of the following commands may be<br>sent to the device (parameters inside < > are ASCII characters<br>except for 'word' which is a binary number):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| <ul> <li>Set the base address of the board here. Also select interrupt driven</li> <li>I/O if you have the 8259 controller installed on the HB-4 board and</li> <li>a master 8259 on another board (such as the SCP CPU Support Card).</li> </ul> BASE EQU 0000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| INTERRUPT_IO EQU 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

This device driver provides an interrupt-driven input and output buffer for each serial port if selected. If you set INTERRUPT IO to 1, select ; the size of the input and output buffers below: . ;Interrupt driven input buffer size (bytes). INO SIZE EOU 100 ;Interrupt driven output buffer size (bytes). OUTQ SIZE EQU 200 -----; For an 8250 clock frequency of 1.8432 Mhz: CLOCK EQU 11520 ;UPPER WORD = CLOCK FREQ / (16 \* 65536) UPPER WORD = 1 49664 LOWER WORD ;LOWER WORD = (CLOCK FREQ / 16) MOD 65536 = DATA AVAIL EQU 1 EQU 20H XMIT RDY IF INTERRUPT IO MASTER 59 0 EQU ;Base port address of system master 8259 OFOH MASTER 59 1 EQU OF1H SLAVE 59 0 EQU BASE + 07H SLAVE 59 1 EQU BASE + OFH ENDIF ; ;----> Device driver headers <-----SEGMENT WORD PUBLIC 'CODE' DEV CODE ASSUME CS:DEV CODE,DS:DEV CODE ORG 0 ;Device headers (1 for each serial port) PRN DEV: ;Header for the Printer EPROM DEV, DEV CODE DW ;Next device header DW 0C000H ;Normal character device with IOCTL ;Routine to pass Command Header pointer DW STRATEGY DW PRN INT ;Device driver entry point "PRN ... DB ;Name of this device EPROM DEV: ;Header for the serial EPROM programmer DW MODEM DEV, DEV CODE DW 0C000H DW STRATEGY DW EPROM INT "EPROMPRG" DB MODEM DEV: ;Header for the MODEM AUX1 DEV, DEV CODE DW DW 0C000H DW STRATEGY DW MODEM INT "MODEM DB AUX1 DEV: ;Header for the remaining port (currently not dedicated) DW -1,-1 ;Last device driver in this file DW 0C000H DW STRATEGY AUX1 INT DW DB "AUX1

-----> Device interrupt service routines <-----This section of code may only be used if the 8259 Priority Interrupt ; Controller is installed. ; The following routines require a valid stack that has at least 4 words. IF INTERRUPT IO Return sequence used by all service routines. **ŘETURN** MACRO IN ;Are there any more interrupts pending AL,DX CMP ; from this serial port? AL,1 SEL INT JNE ;Send End of Interrupt command to the MOV AL, 20H ; slave 8259 (Auto-EOI mode doesn't MOV DX,SLAVE 59 0 ; work for a slave 8259). OUT DX,AL POP SI POP DX POP AX POP BX IRET ENDM 'Transmitter Holding register empty' interrupt **TRANS PROC:** MOV SI,CS:[BX].OQ FRONT CMP SI,CS:[BX].OQ BACK JE DISABLE CLD LODS BYTE PTR CS:[SI] ;Output the next byte at the ; front of the output buffer. OUT DX,AL MOV AX,BX ADD AX,0Q END :Let pointer wrap around to CMP SI,AX ; front of input buffer if JNE NO WRAP1 it falls outside the area. SUB SI, OUTQ SIZE NO WRAP1: MOV CS:[BX].OQ FRONT,SI INC ;Point to the Interrupt DX ; Identification Register. INC DX RETURN ;Disable transmitter interrupts if there INC DISABLE: DX IN AL,DX ; is no more data in the output buffer. AND AL,1101B OUT DX,AL ;Point to the Interrupt Identification Reg INC DX RETURN :---> Interrupt service routine entry points: PUSH EPROM INT RTN: BX MOV BX. OFFSET EPB JMP SHORT INT DISPATCH MODEM INT RTN: PUSH BX BX, OFFSET MODB MOV SHORT INT DISPATCH JMP PUSH BX AUX1 INT RTN: MOV BX, OFFSET AUXB JMP SHORT INT DISPATCH PRN INT RTN: PUSH BX MOV BX, OFFSET PRNB

All interrupts use the following code to determine what type of interrupt occurred. BX is used to point to the appropriate serial port's I/O buffer block. INT DISPATCH: PUSH AX PUSH DX PUSH SI MOV DX,CS:[BX + BLEN].PORT BASE INC DX :Point to the Interrupt Identification reg. INC DX ;Poll the 8250 to determine what caused IN AL,DX SEL INT: CBW ; the interrupt. MOV SI,AX DX ;Point to UART data register. DEC DEC DX CS: INT TYPE TABLE[SI] JMP 4 different interrupts from each UART TABLE DW MODEM INT\_PROC INT TYPE TABLE TRANS PROC DW RCVD DATA PROC DW RCV ERROR PROC DW MODEM status interrupt ;Read the MODEM Status Register to clear MODEM INT PROC: ADD DX,6 ; the interrupt. IN AL,DX Point to the Interrupt Identification Reg SUB DX,4 RETURN 'Received data error' interrupt ;Throw away the received data and read RCV ERROR PROC: IN AL,DX ; the Line Status Register in order to ; clear the 'received data' and 'receiver ; error' interrupts, point to the ; Interrupt Identification Register. DX,5 ADD IN AL,DX SUB DX,3 RETURN 'Received data available' interrupt RCVD DATA PROC: MOV SI,CS:[BX].IQ BACK IN AL,DX ;Get the data. :Store at the back of the input MOV CS:[SI],AL INC ; buffer. SI MOV AX,BX AX, IQ END ADD ;Make the 'Buffer-back' pointer wrap CMP SI,AX ; around to the front of the buffer JB NO WRAP3 SUB SI, INQ SIZE ; if beyond the allotted area. NO WRAP3: MOV CS:[BX].IQ\_BACK,SI CMP CS:[BX].IQ FRONT,SI ;Update buffer starting point if JNE NO OVERRUN buffer overrun occurs. INC SI CMP SI,AX JB NO WRAP4 ;Don't let buffer 'front' pointer go beyond the allotted area. SUB SI, INQ SIZE NO WRAP4: MOV CS:[BX].IQ FRONT,SI ;Point to the Interrupt NO OVERRUN: INC DX ; Identification Register. INC DX RETURN ENDIF ;

S-100 JOURNAL, VOL. 1 NO. 4

| ;                | >            | Strategy Routine entry      | point <                                                        |

|------------------|--------------|-----------------------------|----------------------------------------------------------------|

| STRATEGY         | PROC         | FAR                         |                                                                |

|                  | MOV          | WORD PTR CS:REQ HDR PTR, B  | X ;Pointer to the function                                     |

|                  | MOV          | WORD PTR CS:REQ HDR PTR[2   | ],ES ; request header passed here                              |

|                  | RET          |                             |                                                                |

| STRATEGY         | ENDP         |                             |                                                                |

| ·                | -> De        | vice driver function reque  | st dispatcher <                                                |

|                  |              |                             |                                                                |

| COMMAND DISPATCH |              | PROC FAR                    | ;Use BX to point to the driver's                               |

| AUX1_INT:        | PUSH<br>MOV  | BX<br>BX,OFFSET AUXB        | ; command/data table.                                          |

|                  | JMP          | SHORT SAVE ALL              | , communar du              |

| EPROM INT:       | PUSH         | BX                          |                                                                |

|                  | MOV          | BX, OFFSET EPB              |                                                                |

|                  | JMP          | SHORT SAVE ALL              |                                                                |

| MODEM INT:       | PUSH         | BX –                        |                                                                |

|                  | MOV          | BX, OFFSET MODB             |                                                                |

|                  | JMP          | SHORT SAVE_ALL              |                                                                |

| PRN_INT:         | PUSH         | BX DEESET DDND              |                                                                |

|                  | MOV          | BX,OFFSET PRNB              |                                                                |

| SAVE ALL:        | PUSH         | AX                          |                                                                |

|                  | PUSH         | SI                          |                                                                |

|                  | PUSH         | CX                          |                                                                |

|                  | PUSH         | DX                          |                                                                |

|                  | PUSH         | DI                          |                                                                |

|                  | PUSH<br>PUSH | DS<br>ES                    |                                                                |

|                  | CLD          | L3                          |                                                                |

|                  | LDS          | SI,CS:REQ HDR PTR ;         | DS:SI points to the request header.                            |

|                  | MOV          | CX, [SI]. BYTE COUNT        | ;Amount of data passed in CX.                                  |

|                  | LES          | DI, DWORD PTR [SI]. XFER AD | DR ; ES:DI holds transfer address                              |

|                  | MOV          | SI, WORD PTR [SI].COM_CODE  |                                                                |

|                  | AND          | SI,OFFH                     | In this a logal command?                                       |

|                  | CMP          |                             | Is this a legal command?                                       |

|                  | JBE<br>MOV   | VALID_COM<br>AX,8103H ;     | Return 'Unknown command' error.                                |

|                  | XOR          | CX,CX ,                     |                                                                |

|                  | JMP          | SHORT FILL_HDR              |                                                                |

| VALID COM:       | SHI          | SI,1                        |                                                                |

|                  | MOV          | AX,CS                       |                                                                |

|                  | MOV          | DS,AX                       |                                                                |

|                  | MOV          | DX,[BX + BLEN].PORT_BASE    | ;Base address of I/O port in DX                                |

|                  | CALL         | [SI + BX + BLEN]            | ;Perform the requested function.                               |

| FILL_HDR:        |              | BX,CS:REQ HDR PTR           | Chatter and in AV                                              |

|                  | MOV          |                             | Status returned in AX.<br>Return actual number of bytes xferre |

|                  | SUB<br>POP   | [BX].BYTE_COUNT,CX ;<br>ES  | Recurn actual number of bytes xierre                           |

|                  | POP          | DS                          |                                                                |

|                  | POP          | DI                          |                                                                |

|                  | POP          | DX                          |                                                                |

|                  | POP          | CX                          |                                                                |

|                  | POP          | SI                          |                                                                |

|                  | POP          | AX                          |                                                                |

|                  | POP          | BX                          |                                                                |

| COMMAND DISPATCH | RET          | ENDP                        |                                                                |

| DISTRICI         |              | LIDI                        |                                                                |

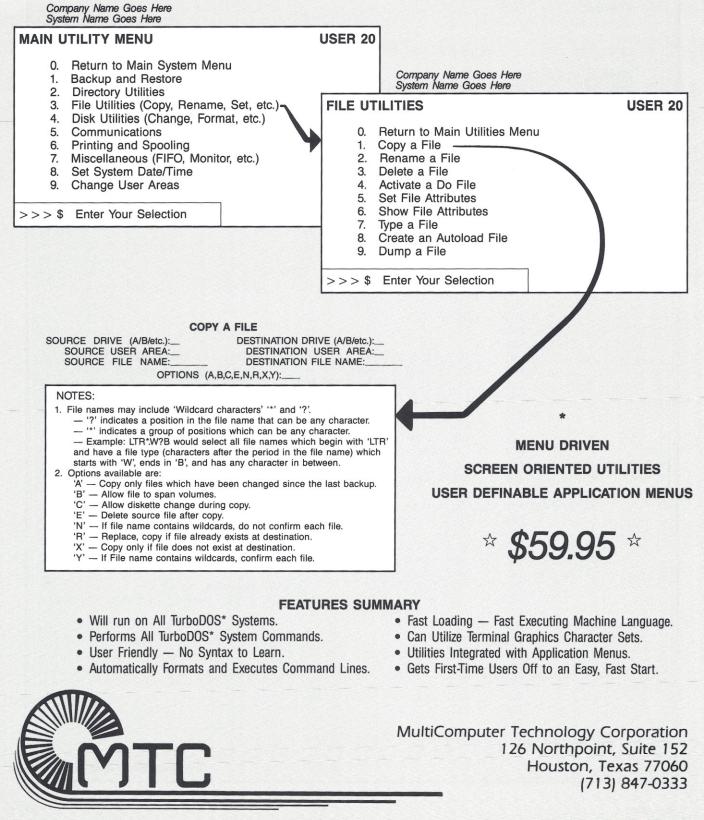

# THE COMPLETE TurboDOS MENU SYSTEM

\*TurboDOS is a trademark of Software 2000.

# LOCAL AREA NETWORKS UNDER TurboDOS

local area network is a communications system, much like a telephone system, where any connected device can use it to send and receive information. The networks discussed here are used exclusively for data transfer, although the technology is now also available for carrying voice and video signals.

As the name implies, a local area network (LAN) is used to cover a relatively short distance. Usually, a local area network will be limited to a department, a single building, or a group of buildings within close proximity. However, if used properly with a multiuser operating system such as TurboDOS, a local area network can have a large number of user stations.

An important characteristic of local area networks is speed; they deliver data fast. A person passing and receiving data over a local area network ideally experiences the same kind of response time as if data were coming from a local machine. To get this kind of response time, most local area networks operate at 1 to 10 megabits per second.

A LAN is a system made from building blocks which can be added

and shaped as needed. The basic components are:

A **Cable** that transmits messages from one device to another.

Network Interface Cards that go between each computer and the cable.

A Central Mass Storage device, or devices, where network-shared data exists.

One or more **System Servers** which make network data available to the requesting party or parties.

A Network Operating System that makes provisions for using the network. The operating system discussed in this article is **TurboDOS**.

#### ADVANTAGES AND DISADVANTAGES OF LANS

Main advantages of local area networks are their flexible architecture, sharing of system resources (mass storage, printers, etc.), common access to data and program files over the network, and reliability against total system failure. The main arguments in favor of LANs are:

1. The sharing of peripherals reduces the per-user cost. Sharing in

a properly designed network improves the reliability of an entire system.

Akin Orhun

2. Better response time can be achieved through networking. Coupled with the distributed-processing approach of TurboDOS, properly designed and operated LANs are serious competitors to much more expensive mainframe approaches.

3. The peripherals attached to a network tend to be faster than those dedicated to stand-alone PCs. The cable speed (bandwidth) of all networks currently available far exceeds the speed capability of most PCs. However, a LAN between two or more S-100 TurboDOS systems operates at much higher efficiency due to the distributed master-server/slave-receiver philosophy of TurboDOS.

4. Networking promotes organizational efficiency, interaction and teamwork. Individual, nonintegrated workstations may create serious threats of data loss.

Dr. Akin Orhun is the president of TurboComp Computer Consultants and he is a research scientist at the University of California, Davis. In addition, Akin is a consultant for Teletek Enterprises, Inc. The NIB100/01 S-100 Network Interface Board. Interface boards provide the vital link between a computer and the LAN.

> The NIB100 is produced by Destek and is available from Teletek

The ever-changing marketplace for microcomputers as well as advances in technology have made the local area network between multiuser, multiprocessor systems a strong alternative to timesharing on minicomputers or mainframes.

LANs, despite the many benefits they can bring to an office, can also be the source of certain problems. Even though LANs are logical extensions to personal computers, their operations are not similar. Software written for a single-user environment. although working in a LAN, may wreck data files if sharing files has not been resolved properly. Security problems exist because the cable, or one of the many workstations, may be easily available to outsiders. Or. a more common threat, authorized users may use their workstations to rummage through the files in the mass storage location. However, as it will be discussed, various safeguards exist in an operating system like TurboDOS.

#### STANDARDS

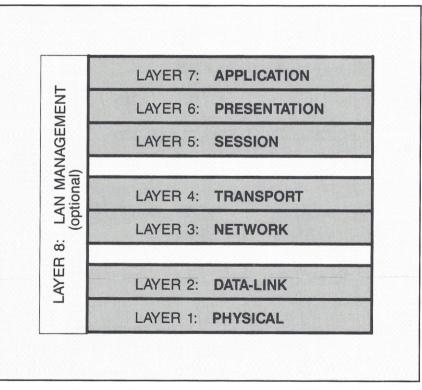

The computer industry cannot decide on the best, single solution for LANs. However, it can agree on one basic structure. Most LAN manufacturers have accepted the importance of an established structure and follow the scheme of the International Standards Organization (ISO), referred to as the Open System Interconnection or **OSI model**.

The OSI model does not establish any particular standard. It is broad enough to include many standards, yet it provides a structure which requires enough similarities, so that network-to-network interfaces, called **gateways**, can be built and will enable the networks to communicate.

The OSI model defines the components and functions of a LAN in 7 layers, and sometimes an 8th layer, as shown in Figure 1. These layers are interdependent and the model is hierarchical. Each layer can only communicate with the layer below or above it.

Layer 1 defines the physical connection and is partly mechanical (connectors, cables) and partly electrical, specifying modulation techniques and voltages. Layer 2 defines the formats used in the message units as well as the means of controlling access to the network. LANs break up messages into packets, or message units. Each packet carries with it its source, destination, and some type of error detection mechanism.

Layer 3 defines the switching and routing of information between network nodes. Network management, which includes the relay of status information and regulation of packet flow, is established in this layer.

Layer 4 defines the distribution of addresses on the network. If necessary, the procedure to divide the messages into smaller units is determined in this layer. Error detection and recovery are also handled here.

The layers 1, 2, 3, and 4 define the network and how it functions. The top three layers define how the network is used.

Layer 5, the session layer, defines the binding and unbinding of communication links, as well as the passage of data.

Layer 6 defines the translation of formats and syntax from an application to the network.

Layer 7 defines the support for applications run on the individual node

points and specifies the manner in which applications can enter the network.

Some versions of the OSI model contain Layer 8 to cover the network management features. While the traditional 7 layers are stacked in their hierarchical configuration, the 8th layer runs vertically, interfacing with all 7 layers.

In a typical configuration of TurboDOS with Desnet (a networking system by Destek), the first two layers are handled by Desnet and the remainder layers by TurboDOS.

#### NETWORK TOPOLOGY

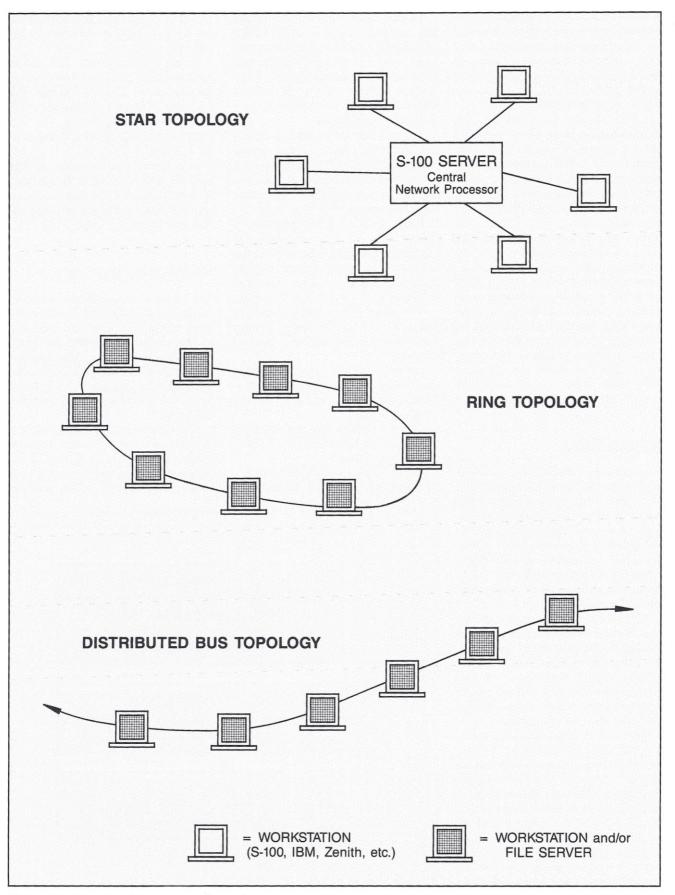

The physical layout of the network, its topology, is defined in the hardware layers. The cost and flexibility of the network installation are partly affected by topology, as is the system's reliability. There are four basic configurations for topology: the Star, the *Ring*, the *Distributed Bus*, and the *Token Bus*.

The **Star** topology (Figure 2) has a separate cable for each personal computer on the network. Each cable attaches to a central network processor. The Star is widely used in

Figure 1. Profile of the Open System Interconnection (OSI) model for LANs.

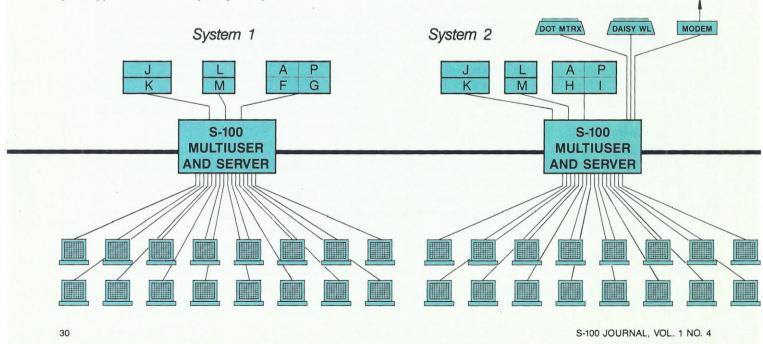

host-to-terminal networks, PBX networks, and in a few LANs. The only advantages of the Star are the simplicity of its hardware and the possible use of existing phone lines as transmission media. On the other hand, it uses more cable than any other topology. It is also more cumbersome to install additional computers to the network since it requires a new cable each time. Another cause of concern is its vulnerability to the failure of the central processor.