B

**JANUARY 9, 1992**

QUICHLOOK

FOR ENGINEERS AND ENGINEERING MANAGERS -- WORLDWID

A PENTON PUBLICATION U.S. \$10.00

FPGAs OFFER GATE-ARRAY SPEED

AN EARLY LOOK AT THE ISSCC

TWELVE INVITED EXPERTS PREVIEW THE FUTURE

## WHO NEEDS THE SIGNAL PROCESSING WORKSYSTEM?

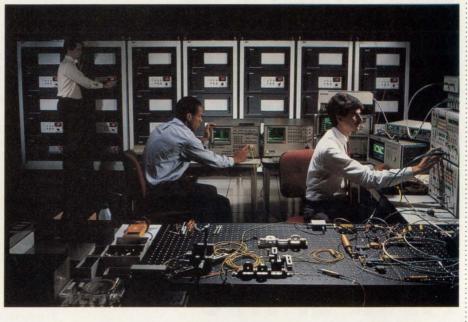

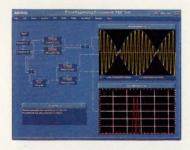

Anyone involved in DSP and communications design can benefit from the Signal Processing WorkSystem.<sup>®</sup> Because SPW<sup>™</sup> is the only complete, integrated CAE software tool for signal processing design, simulation, analysis and implementation.

Satellite communications. Modems. Mobile radios. Cellular phones. Radar. Sonar. Speech encoding. Voice processing. Image processing. Digital audio. Multimedia. Automotive electronics. Robotics. Neural nets and pattern recognition. Data compression. HDTV. Biomedical instrumentation. All these and much more can be designed using SPW on industry-standard platforms from Sun, DEC and HP/Apollo.

That's why over 200 of the world's leading telecommunications, aerospace and electronics companies around the world now use SPW.

With SPW you first create a high-level, hierarchical design using its extensive libraries of DSP and communications function blocks, as well as your own custom blocks. SPW then automatically converts your design into an error-free simulation program that can accept real-world signals and parameters for accurate design analysis.

SPW also provides several optional paths to implementation, including bit-accurate fixed-point simulation, VHDL generation, logic synthesis and other ASIC/PCB support. A code generation system produces generic-C for fast prototyping on any DSP platform, links SPW to DSP chips from AT&T, Motorola and TI, and supports boards from leading vendors.

To preview the Signal Processing WorkSystem, call (415) 574-5800 for a free video demonstration tape. In fifteen minutes, you'll see how SPW can save hundreds of hours and thousands of dollars in DSP design.

919 East Hillsdale Blvd., Foster City, CA 94404 (415) 574-5800 CIRCLE 190 FOR U.S. RESPONSE CIRCLE 191 FOR RESPONSE OUTSIDE THE U.S.

## **Control Tower**

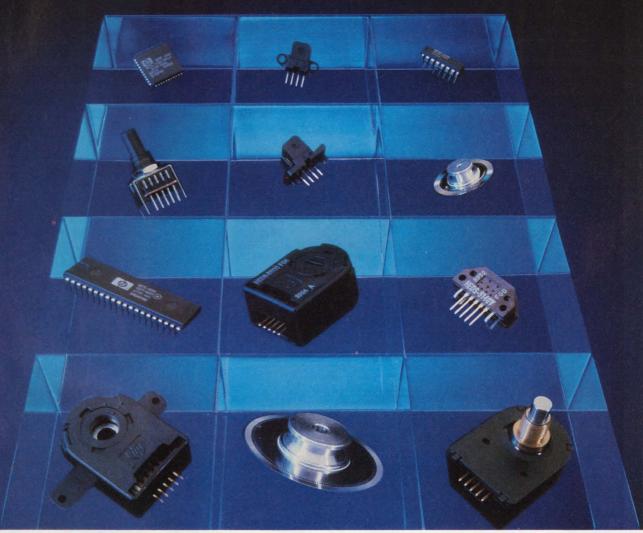

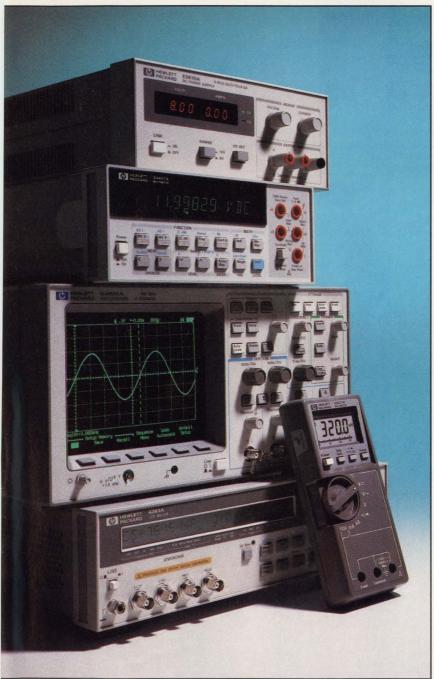

When it comes to motion control products, Hewlett-Packard towers over the rest with a more diversified and innovative line of solutions. Giving you one source to meet all your design needs.

Just look at our award-winning HEDS 9000 series of encoder modules. Using HP's unique optical technology, these modules are the ideal building blocks for creating precision high-speed linear or rotary applications.

Your choices include everything from a 3-channel module for industrial applications to the small footprint of our 9700 collection for business equipment.

## Control panel: the HRPG series.

For front panel applications, turn to our RPG series of potentiometers. Offering you full configuration flexibility, improved rotational feel, and small footprint, HP delivers the perfect line of data entry devices for your test, medical, analytical, and computer equipment.

### Controlled performance: the HCTL series.

Our new line of high-speed HCTL ICs give you high performance servo control in low-power CMOS. The result: superior performance and more microprocessing power left over for your laboratory, medical, and industrial automation designs.

And because these motion control solutions come from HP, you're assured of our on-going commitment to excellence in service, support, and reliability.

So why take a chance, when you can take control. With motion control products from HP. Call for our free brochure: **1-800-752-0900, ext. 1497**.

There is a better way.

The Incredible Hulk and The Silver Surfer are registered trademarks of Marvel Comics Group

# Very Special Be #1 In EPROMs.

AMD EPROMs today are what other mere mortal EPROMs can only aspire to be: high density, of course. But also high speed. Able to store massive amounts of information, with lightning fast access times. All in our superior CMOS technology.

EPROMs have always been our strength—thanks to our unparalleled performance, selection, reliability, and quality.

That's why we sell more EPROMs than any other vendor.\* Period. And we're ready to do the same for years to come. While other vendors have abandoned EPROMs, we're still committed to making the fastest, highest density EPROMs.

In fact, we've got the most advanced EPROM wafer fab, assembly and test facilities in the world. Which produce the most reliable, highest quality EPROMs available. In everything from surface mount plastic to mil spec compliant packages.

So make yourself a hero. The instant you know your EPROM requirements, get them fast. Get them dense. Get them in volume. And get them right away.

Call AMD at **1-800-222-9323** for more information. Or call your local sales office to place an order.

901 Thompson Place, PO. Box 3435, Sunnyvale, CA 94088 © 1991 Advanced Micro Devices, Inc. All brand or product names mentioned are trademarks or registered trademarks of their respective holders. \*Dataouest, March 1991, based on 1990 data.

CIRCLE 161 FOR U.S. RESPONSE

# JANUARY 9, 1992 VOL. 40, NO. 1

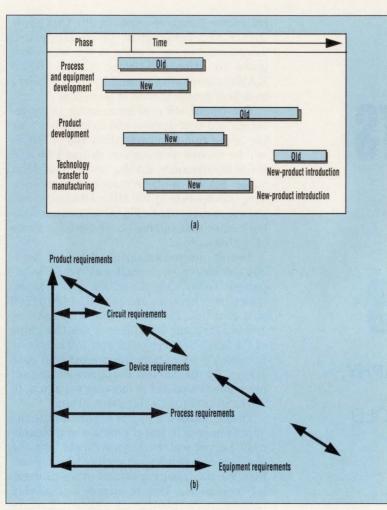

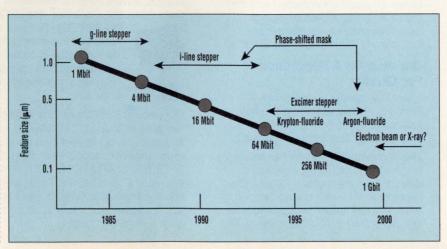

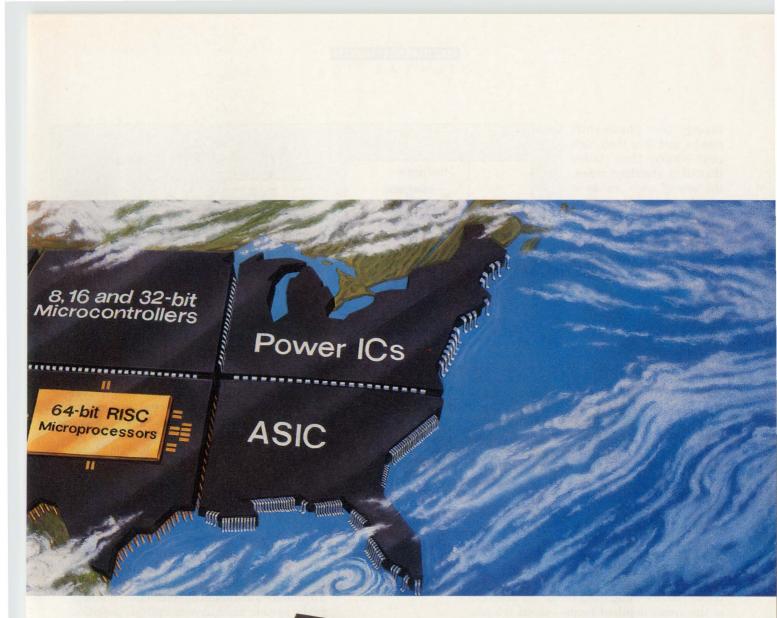

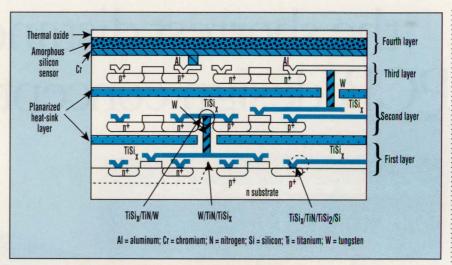

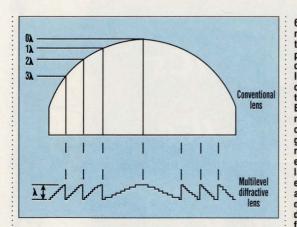

32 TECHNOLOGY 37 PROCESS ADVANCEMENTS FUEL IC DEVELOPMENTS FORECAST Improvements in lithography, etching, and deposition hold the key to digital chip enhancements.

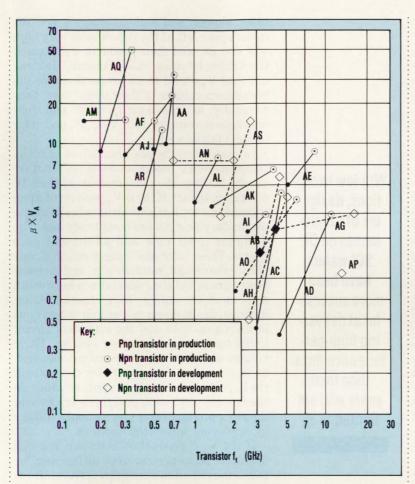

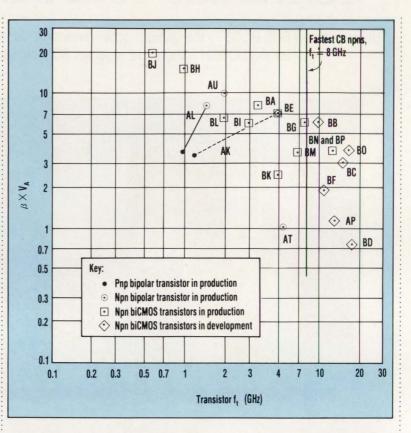

> 59 NEW PROCESSES TO SPAWN ANALOG, MIXED-SIGNAL, POWER ICS Future submicron processes on SOI wafers to boast  $f_t$ s beyond 25 GHz.

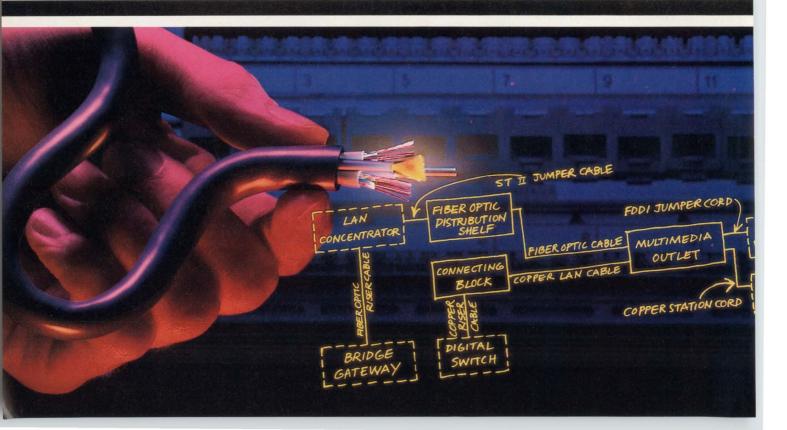

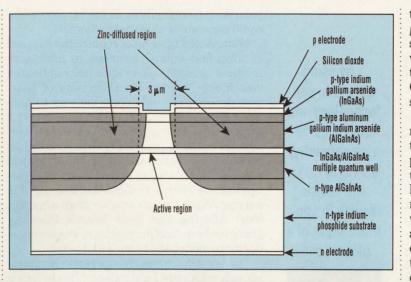

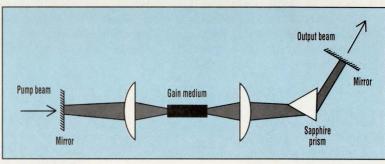

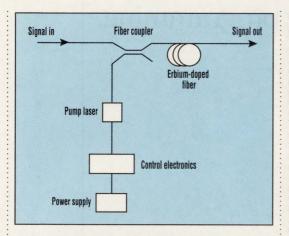

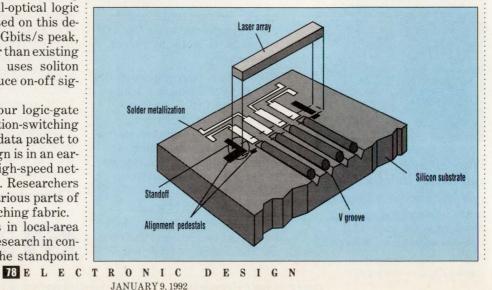

73 THE WORLD OF COMMUNICATIONS IS MOVING TO FIBER OPTICS Electrons teamed with photons produce stunning throughputs.

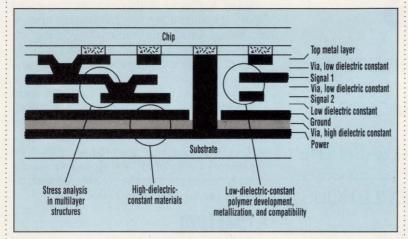

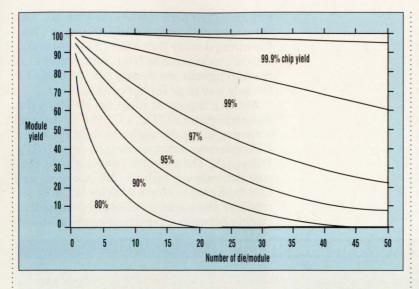

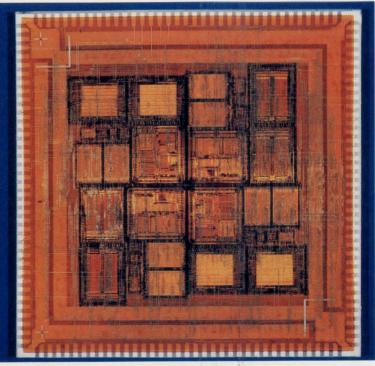

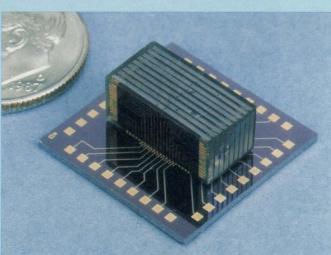

83 FUTURE PACKAGING DEPENDS HEAVILY ON MATERIALS Packaging design must rise to a system level for tomorrow's multichip modules to unleash the power of the silicon they will house.

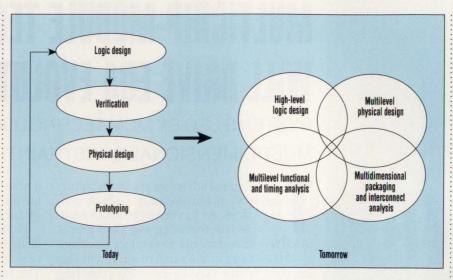

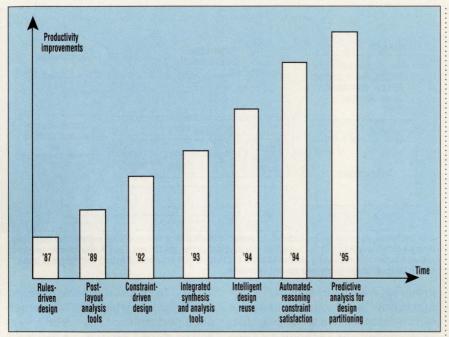

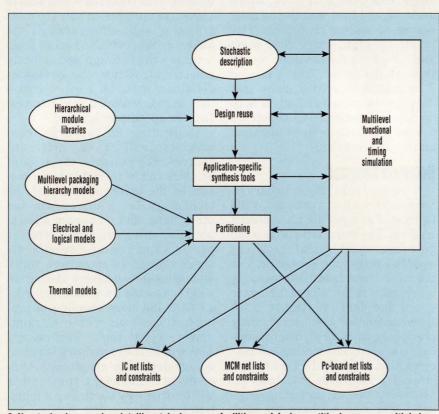

99 MULTICHIP-MODULE TECHNOLOGY WILL DRIVE EDA EVOLUTION Systems led by MCM technology will need multidimensional constraintdriven design.

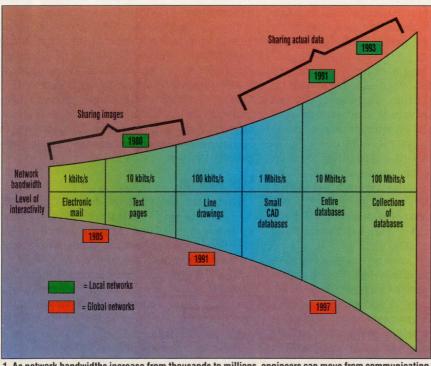

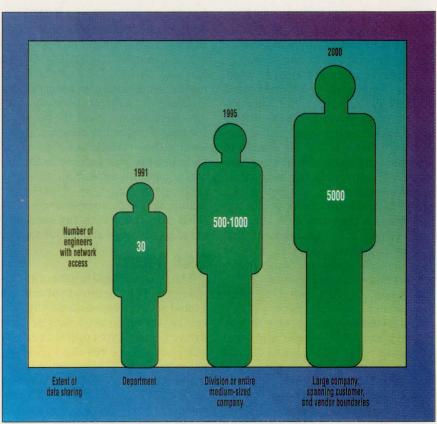

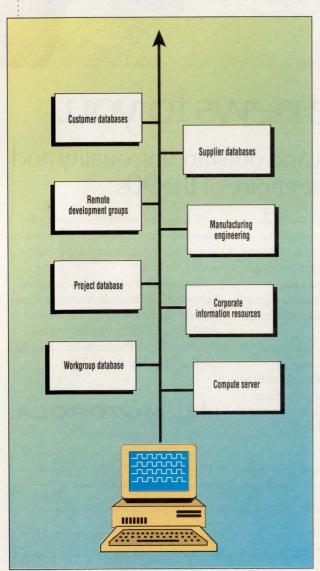

**107 NETWORKING ADVANCES TO ANCHOR CONCURRENT ENGINEERING** To keep pace in the 1990s, networks will need to be faster and more economical.

## **115 INTERVIEW SECTION**

Experts offer their views on what's in store for the coming years.

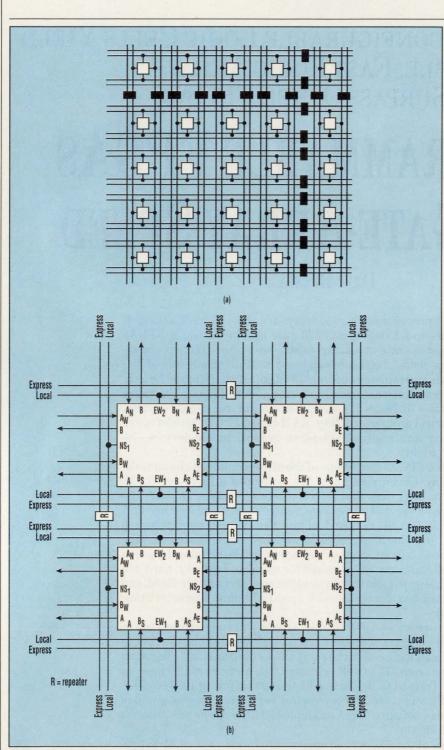

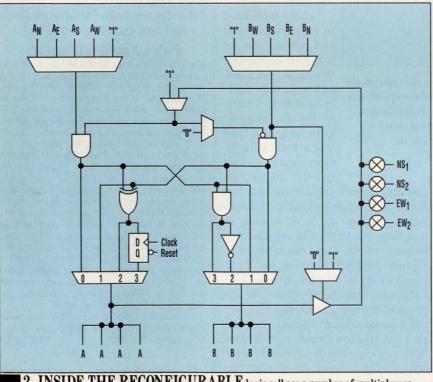

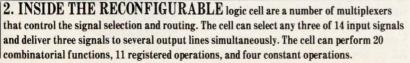

PRODUCT 143 REPROGRAMMABLE FPGAS OFFER GATE-ARRAY SPEED INNOVATION SRAM-based reconfigurable logic cells yield flexible, fast logic arrays that surpass other FPGAs.

> 4 E L E C T R O N I C DESIGN **JANUARY 9, 1992**

#### **14 EDITORIAL**

### **18 TECHNOLOGY BRIEFING**

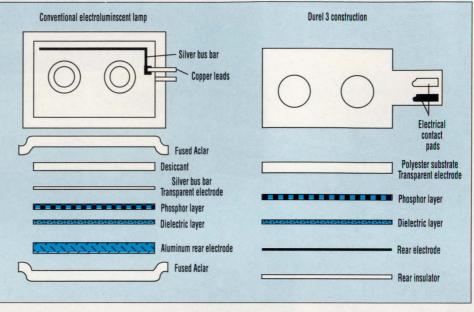

Reducing flat-panel display costs

#### **23 TECHNOLOGY NEWSLETTER**

• Superconductors implement logic gates

• Polymers improve electro-optic devices

CFI set to release standards commercially

• Multiple-gate FET aimed at neural nets

• Sensors use thin film with shape memory

• Improved state averaging aids power-supply design

• Design process shrinks SBC development time

• Port eases building real-time control jobs

• FPGA alliance program ups membership to 19

#### **29 TECHNOLOGY ADVANCES**

• RISC processors, multimegabit RAMs, and mixed-signal developments highlight ISSCC

• Phosphor encapsulation lets ultrathin EL lamp shrug off moisture

• Waferscale integration addresses reconfigurability, interconnects testing, and applications

Jesse H. Neal Editorial Achievement Awards: 1967 First Place Award 1968 First Place Award 1972 Certificate of Merit 1975 Two Certificates of Merit 1976 Certificate of Merit 1978 Certificate of Merit 1980 Certificate of Merit 1986 First Place Award 1989 Certificate of Merit

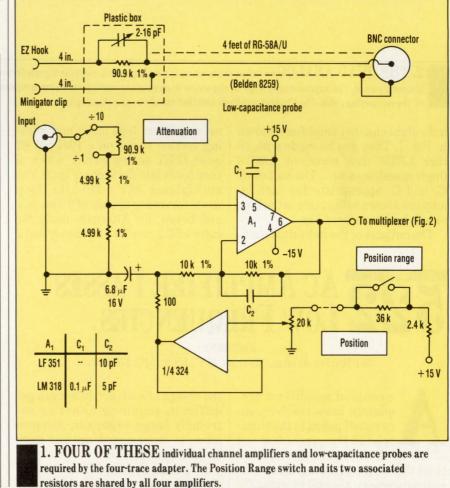

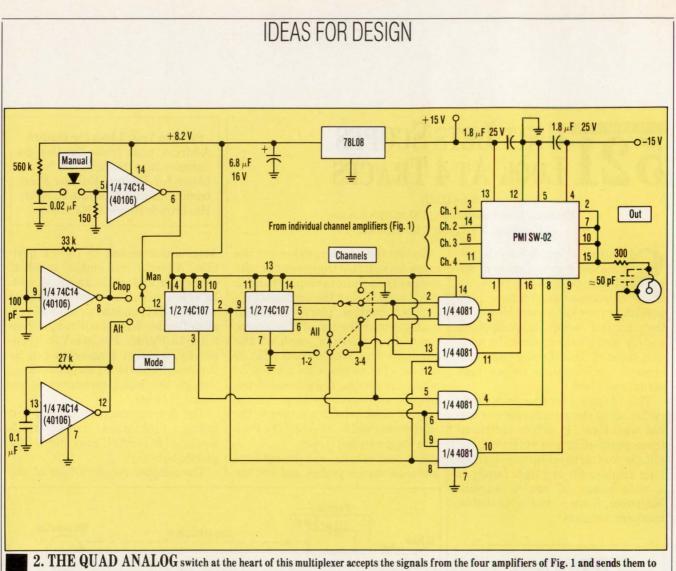

## **129 IDEAS FOR DESIGN**

- Unit lets scopes look at four traces

- AC amplifier passes low

frequencies

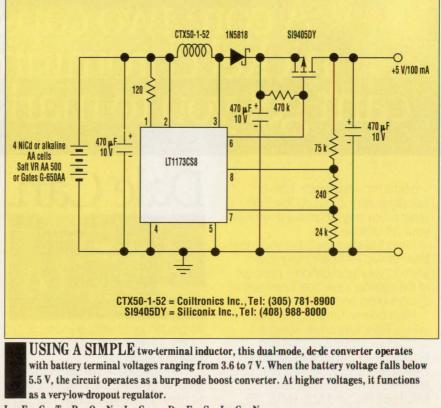

• Get +5 V/100 mA from four cells

#### **135 QUICK LOOK**

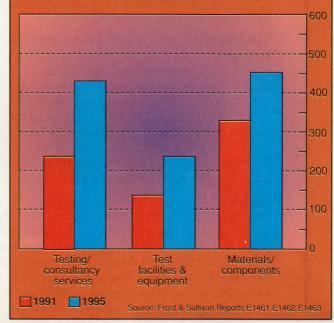

• EMC ruling spurs European market

- Skunk works encounter opposition

- Shaving years off time to market

- Income-tax planning for engineers

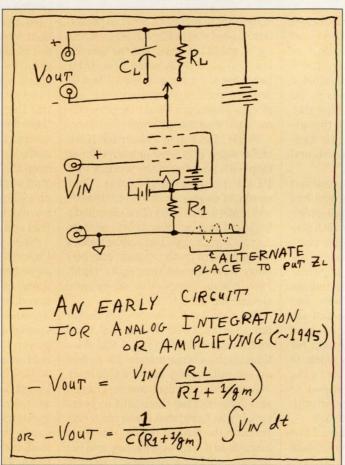

#### **141 PEASE PORRIDGE**

What's all this negative feedback stuff, anyhow?

#### **NEW PRODUCTS**

**147 Instruments 149 Computer Boards 152 Communications 158 Computers & Peripherals 163 Digital ICs** 165 Analog

#### **168 INDEX OF ADVERTISERS**

#### **169 READER SERVICE CARD**

#### **COMING NEXT ISSUE**

• Special Report: Memory-card technology opens up new schemes for I/O connections

• PIPS Special Section: Power, Interconnections, Passive components, Switches and Relays

• Designing for electrical-transient immunity

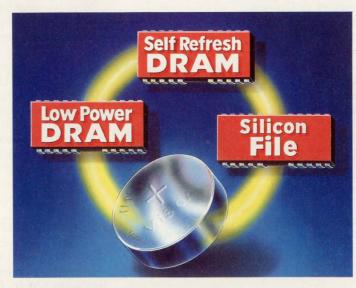

• First details on new special-purpose DRAMs

• Using single-slope a-d conversion for low-cost solutions

• Enhanced EPLDs tackle high-frequency systems

• New microcontrollers span the 8-and 16-bit worlds

• PLUS: Ideas for Design Pease Porridge Technology Advances QuickLook

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: \$85 U.S., \$160 Canada, \$230 International. Second-class postage paid at Cleveland, OH, and additional multime officion Editorial and advortion additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright©1992 by Penton Publishing Inc. All rights reserved. The contents of this publica-

All rights reserved. The contents of this publica-tion may not be reproduced in whole or in part without the consent of the copyright owner. Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to pho-tocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$1 per copy of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/91 \$1.00 + .50). (Can. GST # R126431964) Copying done for other than personal or internal reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor. For subscriber change of address and subscrip-

For subscriber change of address and subscription inquiries, call (216) 696-7000.

POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

Correction: On page 26 in our November 21.

1991 issue, the telephone number for CMX

Systems was listed as (203) 238-2622. It

should be (203) 238-3622. Also, the position-

ing system was correctly cited as the CMX

3030 in the initial part of the story, later it

was incorrectly called the CMS 3030. ED

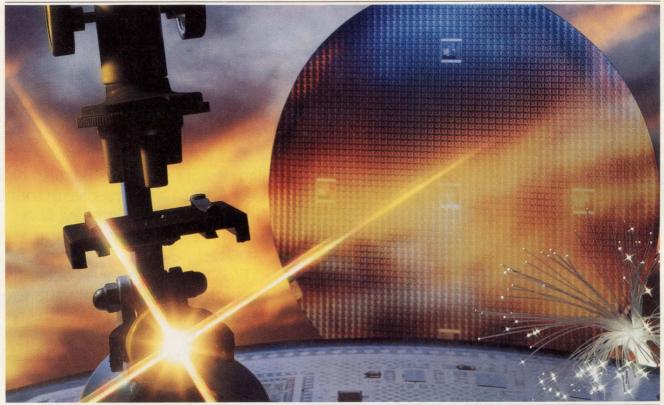

# IN THE TIME IT TAKES COULD ROUTE THE WO

Believe it or not, it only takes about 150 seconds to place and route a Xilinx FPGA.

Chances are: it'll take you longer to read this ad.

### THE FIRST AND STILL THE FASTEST.

At Xilinx we invented the FPGA. And we've led the industry ever since.

With the fastest, highest performance FPGAs available anywhere.

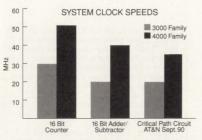

Today, we offer system clock speeds of 60 MHz.

We're also the first programmable logic company to offer you on-board RAM.

Making our newest FPGAs ideal for everything from FIFOs to register stacks.

What's more, we're the only programmable logic company that provides you with on-chip wide decode.

And that's just the beginning. Because as formidable as our hardware may seem, it's only half the story.

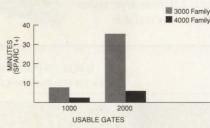

As measured by typical design benchmarks, the XC3000 family is the industry's fastest FPGA. Or at least it was until we introduced the 4000 family.

#### NEW ENHANCED SOFTWARE PROVIDES PUSH BUTTON SOLUTION.

Device speed alone doesn't determine the fastest, highestperformance logic device.

When you're designing, the clock on the wall is every bit as

Our new push-button software makes programming other logic devices seem positively tedious.

important as the clock speed of the chip.

So to make Xilinx FPGAs even faster and easier to program, we've redesigned our software.

This is no mere upgrade. It's a major rewrite.

Our new version of XACT now comes with 200 soft macros. And fifty hard macros.

Providing automatic placing and routing for virtually all designs.

With greater than 90% gate utilization.

If you've worked with Xilinx FPGAs before, you'll see improvements even before you start to place and route your design.

If you've never worked with Xilinx FPGAs before, you'll find every other logic device to be positively tedious by comparison.

### WHEN IT COMES TO SYSTEM TESTING, WE PASS WITH FLYING COLORS.

Our newest FPGAs offer you yet another competitive advantage that's exclusive to Xilinx.

© 1991 Xilinx, Inc. 2100 Logic Drive, San Jose, CA 95124. Europe, 44 (932) 349401. Japan, 81 (3) 297-9191. Asia, 852 (3) 721-0900. Xilinx is a trademark and The

# TO READ THIS AD, YOU RLD'S FASTEST FPGA.

The industry's first on-chip JTAG boundary scan for easy testing of PC boards and device I/Os.

This unique Xilinx offering improves overall system testability

and dramatically reduces board test costs. It's a major boost for those designing highdensity, surface mount systems or complex, multilayer PC boards. We told you we'd save you time and money.

## IF AT FIRST YOU DON'T SUCCEED, IT'S EASY TO TRY AGAIN.

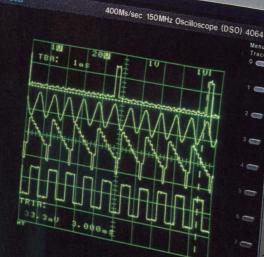

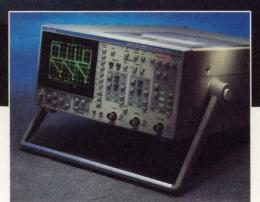

As you well know, when you're designing a system, changes keep coming fast and furious. Which is why Xilinx FPGAs are designed to be reprogrammed quickly an unlimited number of times.

And not only do our FPGAs save you an enormous amount of time early on, they also save you time later when you need to make those "last minute" enhancements.

It's one more way we make it easier for you to get your product to market as fast as possible. First time. Every time.

ELAPSED TIME FOR 100% ROUTING

New algorithms have reduced place and route times by a factor of four.

#### GETTING AN EDGE OVER YOUR COMPETITORS IS JUST A PHONE CALL AWAY.

If you've read this far, you could have already placed and routed one of our FPGAs.

So don't delay. No other programmable logic company can offer you the many exclusive features of Xilinx FPGAs.

Call 1-800-255-7778. Or in California, 408-559-7778. And we'll send you more information on how our FPGAs can give you the competitive edge.

But you'd better hurry. Some of your competitors have already finished reading this ad.

Programmable Gate Array Company is a service mark of Xilinx, Inc. All other trademarks or registered trademarks are the property of their respective holders.

CIRCLE 244 FOR U.S. RESPONSE

**CIRCLE 245 FOR RESPONSE OUTSIDE THE U.S.**

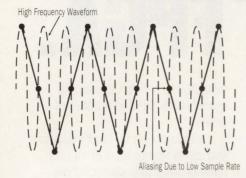

## Correct A/D Errors With Anti-Aliasing Filters

- 8-pole Cauer elliptical, Bessel, & Butterworth filters

- Frequency range 1 Hz to 100 KHz

- Frequency step resolution .001 Hz to 10 Hz

- Roll-off >82 dB / octave

- Stopband attenuation >94 dB

- Pre-amplifier gain to 100

- 16 channels per card

- Up to 128 channels per system

- OEM pricing available

How to Avoid an A/D Sampling Disaster!

Anti-aliasing filters are the only protection to prevent unwanted highfrequency waveforms from appearing as low frequency signals. Give yourself the best protection with R.C. Electronics' instrumentation quality **RC-AAF programmable low pass filters** for 12 and 16 bit data acquisition systems. Compatible with any data acquisition or PC-based system.

#### CIRCLE 153 FOR U.S. RESPONSE CIRCLE 154 FOR RESPONSE OUTSIDE THE U.S.

ELECTRONIC DESIGN

Editor-in-Chief: Stephen E. Scrupski

Executive Editor: Roger Allan

Managing Editor: Bob Milne

Senior Editors: Frank Goodenough, Milt Leonard, John Novellino

**Technology Editors:**

Analog & Power: Frank Goodenough Communications & Industrial: Milt Leonard (San Jose) Components & Packaging: David Maliniak Computer-Aided Engineering: Lisa Maliniak Computer Systems: Richard Nass Semiconductors: Dave Bursky (San Jose) Software: Sherrie Van Tyle Test & Measurement: John Novellino

#### **Field Bureaus:**

West Coast Executive Editor: Dave Bursky (San Jose) Communications & Industrial: Milt Leonard (San Jose) Dallas: Jon Campbell Frankfurt: John Gosch London: Peter Fletcher

Chief Copy Editor: Roger Engelke, Jr.

Contributing Editors: Ron Kmetovicz, Robert A. Pease

Editorial Production Manager: Lisa Iarkowski

Production Coordinator: Pat A. Boselli

Associate Art Director: Tony Vitolo

Staff Artist/Designer: Tom Pennella

Editorial Support Supervisor: Mary James

Editorial Assistant: Ann Kunzweiler

Editorial Secretary: Bradie Guerrero

#### Editorial Offices: (201) 393-6262

Advertising Production: (201) 393-6093 or FAX (201) 393-0410

**Production Manager:** Michael McCabe *Production Assistants:* Donna Marie Bright, Lucrezia Hlavaty, Eileen Slavinsky

Circulation Manager: Robert Clark

Promotion Manager: Clifford Meth

Reprints: Helen Ryan 1-800-835-7746

Group Art Director: Peter K. Jeziorski

Published by Penton Publishing Vice President-Editorial: Perry Pascarella

Publisher: Paul C. Mazzacano

CIRCLE 232 FOR U.S. RESPONSE CIRCLE 233 FOR RESPONSE OUTSIDE THE U.S.

# Afford. Ability.

### With HP basic instruments, performance costs less than you expect.

Now you don't have to accept trade-offs in a basic test instrument. Because HP offers the performance you want at prices you can afford.

Need a dual-range output power supply? The HP E3610 Series makes choosing a 30-watt dc power supply easy—especially when you consider the low noise and **\$300**\* price.

What about a digital multimeter for bench or system use? The rugged 6 ½ digit HP 34401A does both with uncompromised performance for **\$995**\*.

You won't find a better 100 MHz digitizing scope than the HP 54600 Series. It combines analog look and feel with digital troubleshooting power for only **\$2,395** (2-channel) or **\$2,895** (4-channel)\*.

At **\$3,800**\*, the HP 4263A LCR Meter lowers the cost of high-precision 100 Hz to 100 kHz benchtop and system component measurements.

And the 8-function HP E2377A is just one of the HP E2300 Series 3 <sup>1</sup>/<sub>2</sub> digit handhelds priced from **\$99** to **\$189**\*.

**C** For more information or sameday shipment from HP DIRECT, call 1-800-452-4844\*\*. Ask for Ext. T514 and we'll send you a data sheet that shows how affordable performance can be. \* U.S. list price \*\* In Canada call 1-800-387-3867, Dept. 433

In Canada can 1-000-001-0001, Dept. 400

There is a better way.

© 1991 Hewlett-Packard Co. TMINI112/ED

# Our new ops

Introducing the op amps that are more than twice as fast as any others. The new Harris HFA-1100 family. 870 MHz of blinding op amp speed. A shocking 2500 volt/µsec slew rate. A low low low 11 ns settling time. Harris' unique UHF1 process technology makes all this possible. It all means these new ops are the top. The top of

HFA-1110. It's a buffer amplifier, featuring ultra high speed 700 MHz unity gain bandwidth, 2500 V/µsec slew rate and 7 ns settling time.

HFA-0005. High speed in a monolithic design. 420 V/µsec slew rate. 300 MHz bandwidth.

HA-5033. Buffering video has never been easier. Thanks to a 1300 V/µsec slew rate, excellent differential phase and gain.

HA-2444. A mux and 4 video op amps in a single chip. Ideal for digitally selectable 4-channel video.

CA-3246. This NPN transistor array covers a wide array of applications — all the way from DC to 1.5 GHz.

# really hop.

the broadest line of op amps in the world: the Harris line. So for ops that really hop, to ops at low cost, remember.

Nobody gives you more to choose from than Harris. Call 1-800-4-HARRIS, extension 1110.

| World's Fastest Op Amps |         |             |  |  |  |  |

|-------------------------|---------|-------------|--|--|--|--|

| HFA1100                 | 870 MHz | 2500 V/µsec |  |  |  |  |

| HFA1110                 | 700 MHz | 2500 V/µsec |  |  |  |  |

HFA-1100. This op is tops. It's the world's fastest

monolithic

op amp at

870 MHz.

HFA-1130. The same 870 MHz speed as our industry-leading HFA-1100. Plus a 1 ns output clamp.

HFA-0001. With a 1000 V/µsec slew rate, and 350 MHz bandwidth, this op really hops.

HA-2841. A 40 MHz, low-power version of our industrystandard HA-2541. HA-5020. Our low-cost version of the EL2020, but enhanced to give you a full 100 MHz

bandwidth.

## OUR ADVER RECOMMENDED AGA

Since we're one of the largest memory suppliers in the world and the Samsung SRAM program is one of the best, our advertising agency thought we should find a more dignified way to get our new fast 1-megs into your hands. But we know that once you try them you'll buy them. And we believe these guys are, once again, overthinking. So: free SRAM it is.

Our fast 1-megs run at 20 ns and are in full production in large quantities now.

| 20 ns I-ME | 20 ns I-MEG SRAMs FROM SAMSUNG |          |  |  |  |  |

|------------|--------------------------------|----------|--|--|--|--|

| Part       | Organization                   | Features |  |  |  |  |

| KM641005°  | 256K x 4                       | Separate |  |  |  |  |

| KM641001°  | 256K x 4                       |          |  |  |  |  |

| KM681001°  | 128K x 8                       |          |  |  |  |  |

| KM611001°  | 1M x 1                         |          |  |  |  |  |

|            |                                |          |  |  |  |  |

Like our 256K and 64K parts, which we're sampling now and will have in full production Q1 1992, they're part of our major SRAM

© Samsung Semiconductor, Inc., 1991. 3725 No. First St., San Jose, CA 95134.

## TISING AGENCY INST THIS APPROACH.

commitment. We use our formidable DRAM capacity to make them.

All parts are in DIP and SOJ. Our new 256K and 64K chips run at 15 ns.

So if speed, technology, superb breadth of line, and state-of-the-art parts aren't

| Part      | Organization | Features         |

|-----------|--------------|------------------|

| KM64258B  | 64K x 4      | Output Enable    |

| KM64259B  | 64K x 4      | Sep. I/O, High 2 |

| KM64260B  | 64K x 4      | Sep. I/O, Low Z  |

| KM68257B  | 32K x 8      |                  |

| KM61257A° | 256K x 1     |                  |

| KM64257A° | 64K x 4      |                  |

| KM6466B°  | 16K x 4      | Output Enable    |

| KM6465B°  | 16K x 4      |                  |

| KM6865B   | 8K x 8       |                  |

JULIO D

enough for you—maybe our free chip offer will be.

CIRCLE 198 FOR U.S. RESPONSE

ONE MEGIII FASTI

Technology that works for life.

CIRCLE 199 FOR RESPONSE OUTSIDE THE U.S.

## Accelerate your Stepper Motor to 27,000 Steps/second! Travel 16 Million Steps and back!

Is your motor earthbound by sluggish

controllers that can't give you the performance you need? Look at

what you get with the new CY545 single chip stepper motor controller:

- 40-pin, CMOS, + 5v chip

- Speeds up to 27K Steps/sec

- 16 Million steps per motion

- Programmable start rate, accel/decel, slew rate

- Pulse and Direction Output

- Separate Limit Switches

- Jog operation

- Home seek command

- ASCII or binary commands

- Parallel or Serial interface

- 8 General Purpose I/O lines

- External memory control

- LCD & LED Display interface

- Thumbwheel Switch interface

Break the single chip *speed* barrier and the high performance *price* barrier. You can't afford to pass up this latest innovation from the company that, ten years ago, brought you the first stepper motor controller on a

single chip! Order by Fax or phone or call today for free info.

Cybernetic Micro Systems PO Box 3000 • San Gregorio CA 94074

Ph: (415) 726-3000 • Fax: (415) 726-3003

CIRCLE 226 FOR U.S. RESPONSE CIRCLE 227 FOR RESPONSE OUTSIDE THE U.S.

## More Than Just Another Year

appy new year! 1992 is a landmark year for us at Electronic Design because it marks our 40th anniversary, and, to highlight this event, we've planned a Special Issue in November. Throughout the coming months, we'll give you more details on the Anniversary Issue. We'll also offer you an opportunity to participate by asking for your inputs on the contents of certain special sections that we're considering.

FDITORIAL

Despite the urge to wax nostalgic at such times, the basic thrust of the issue will be the future. Electronic Design is built on the foundation of giving its readers a look ahead at the technologies and products that will help them attain a competitive edge in their next product. Thus, we plan to devote most of that blockbuster issue to articles that focus on the future, rather than on the past: a look ahead at possible technology breakthroughs and their impact on system performance.

As for this issue, those of you who are longtime readers of Electronic Design know that the first issue of each year features our Technology Forecast Special Report. This year, we return to fundamentals with a report on the enabling technologies that will lead to future advances in product performance. The Technology Forecast, which begins on p. 37, features four staff-written pieces that focus on digital semiconductors, linear and mixed-signal semiconductors, optoelectronics, and packaging. Two further articles look at networking for the global design environment and techniques for designing with multichip modules. The report closes with ten one-page articles that assess the trends in ten specific technologies: microprocessors, displays, EMI, micromachining, instrument accuracy, test probes, capacitors, power supplies, magneto-optical memories, and computer boards.

We have, in fact, a full slate of technology special reports and design applications on tap for our 26 issues this year. Also returning are such popular sections as Pease Porridge, QuickLook, Ideas for Design, our technical conference previews, and our Salary and Career Surveys. In addition to the regular features, you can look forward to the PC Design and PIPS (power, interconnections, passive components, and switches and relays) special sections six times during the year, and our Test & Measurement Update four times.

We know that the coming year will unleash a host of interesting technology advances that will be covered in Electronic Design. Beyond that, here's hoping that 1992 not only advances technologically, but also politically and economically worldwide, where we can finally put

those problems behind us and once again prosper, in peace.

Stephen & Scrupski

Editor-in-Chief

**14** E L E C T R O N I C D E S I G N JANUARY 9, 1992

## PRECISION **TTL- CONTROLLED** ATTENUATORS

## up to 35dB 10 to 1000MHz FROM \$5995

2 CONTROLS CON

9129 05

GND

+51

| ZFAT-I<br>Accura | DAT-R512<br>FAT-R512<br>couracy |            | TOAT-124<br>ZFAT-124<br>Accuracy |             | -3610<br>-3610<br>acy |             | -51020<br>51020<br>acy |

|------------------|---------------------------------|------------|----------------------------------|-------------|-----------------------|-------------|------------------------|

| (dB)             | (+/-dB)                         | (dB)       | (+/-dB)                          | (dB)        | (+/-dB)               | (dB)        | (+/-dB)                |

| 0.5              | 0.12                            | 1.0        | 0.2                              | <b>3.0</b>  | 0.3                   | <b>5.0</b>  | 0.3                    |

| 1.0              | 0.2                             | 2.0        | 0.2                              | <b>6.0</b>  | 0.3                   | <b>10.0</b> | 0.3                    |

| 1.5              | 0.32                            | 3.0        | 0.4                              | 9.0         | 0.6                   | 15.0        | 0.6                    |

| <b>2.0</b>       | 0.2                             | <b>4.0</b> | 0.3                              | <b>10.0</b> | <b>0.3</b>            | <b>20.0</b> | <b>0.4</b>             |

| 2.5              | 0.32                            | 5.0        | 0.5                              | 13.0        | 0.6                   | 25.0        | 0.7                    |

| 3.0              | 0.4                             | 6.0        | 0.5                              | 16.0        | 0.6                   | 30.0        | 0.7                    |

| 3.5              | 0.52                            | 7.0        | 0.7                              | 19.0        | 0.9                   | 35.0        | 1.0                    |

Price \$ (1-9 qty) TOAT \$59.95/ZFAT \$89.95 bold faced values are individual elements in the units

Finally... precision attenuation accurate over 10 to 1000MHz and -55°C to +100°C. Standard and custom models are available in the TOAT(pin)- and ZFAT(SMA)-series, each with 3 discrete attenuators switchable to provide 7 discrete and accurate attenuation levels.

The 50-ohm components perform with 6µsec switching speed and can handle power levels typically to +10dBm. Rugged hermeticallysealed TO-8 units and SMA connector versions can withstand the strenuous shock, vibration, and temperature stresses of MIL requirements. TOAT pin models are priced at only \$59.95 (1-9 qty); ZFAT SMA versions are \$89.95 (1-9 qty).

Take advantage of this striking price/performance breakthrough to stimulate new applications as you implement present designs and plan future systems. All units are available for immediate delivery, with a one-yr. guarantee, and three-sigma unit-to-unit repeatability.

P.O. Box 350166. Brooklyn, New 11235-0003 (718) 934-4500 Fax (718) 332-4661 Telexes: 6852844 or 620156

**CIRCLE 206 FOR U.S. RESPONSE**

**CIRCLE 207 FOR RESPONSE OUTSIDE THE U.S.**

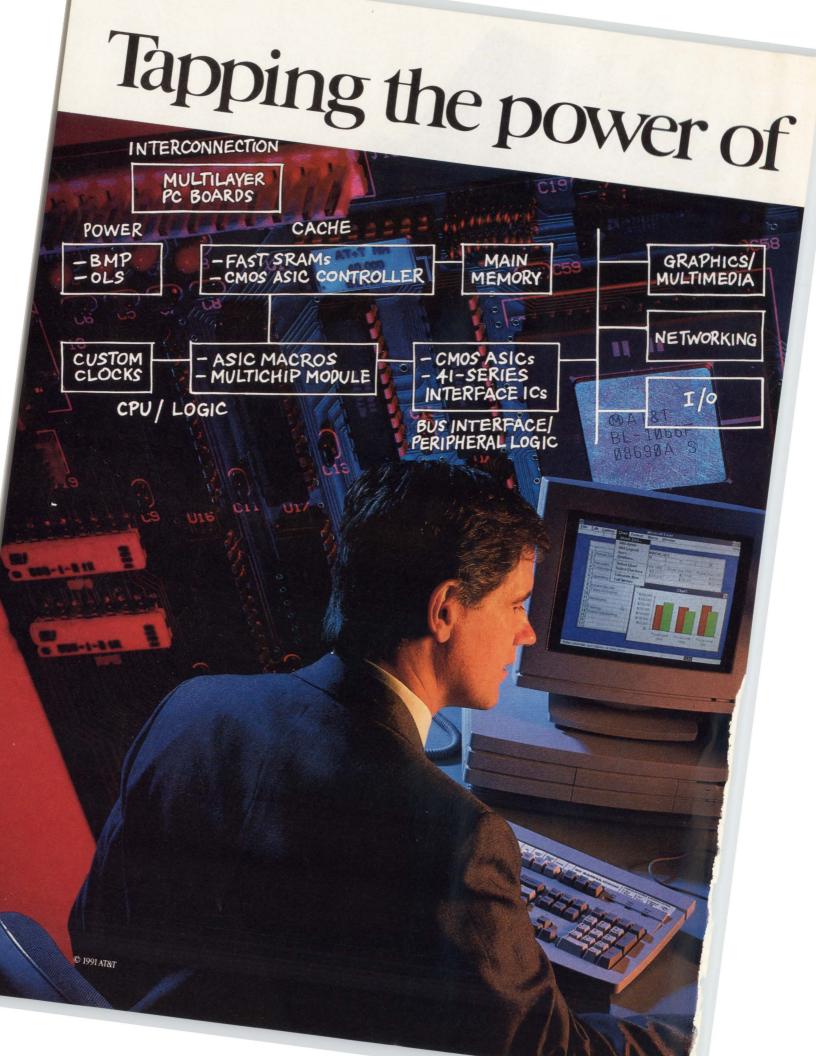

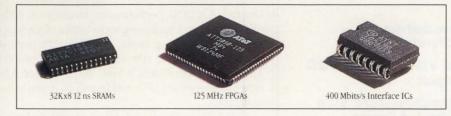

## today's fastest CPUs.

## That's AT&T "Customerizing."

"Customerizing" means providing the component solutions and support technology your systems need to help keep pace with CPU speeds up to 50 MHz and beyond.

Faster CPUs demand higher-

## **Cache Solutions**

Microprocessor-specific, fast SRAMs for 10 to 15 ns cache tag and data.

And a proven ASIC capability for differentiated Cache Controllers.

performance cache, I/O bus, peripheral logic and interconnect: bigger, faster, denser, smarter. We have what it takes to close this CPU I/O gap, while reducing chip count and development costs.

**CPU/Logic and Bus Solutions** Industry-pacing submicron Standard Cell CMOS ASICs for high speed, highly integrated core logic.

ECL ASICs with up to 2.2 GHz I/O buffer speeds and delays under 140 ps.

High speed bus interfacing with 200-400 Mbits/s 41-Series Interface ICs.

And custom clocks to meet the tight timing specs of today's fastest CPUs.

**Interconnection Solutions** Up to 22-layer PC Boards with 5 mil line density.

And Multichip Modules that can reduce interchip delays to under 1 ns.

AT&T also provides Application Teams to work with your team, along with the expertise of AT&T Bell Laboratories.

For more about AT&T's "One-Stop-Shop Solutions," get our PC/Workstation Solutions brochure.

Just give AT&T Microelectronics a call at 1 800 372-2447, ext. 636. In Canada, call: 1 800 553-2448, ext. 636.

CIRCLE 84 FOR U.S. RESPONSE CIRCLE 85 FOR RESPONSE OUTSIDE THE U.S.

## High Voltage DC-DC Converters

ACTUAL

## .5"×.5"×.4" Ht. 1000 VDC Output

- New Series AV— 56 Standard Models

- 100 VDC to 1000 VDC Output

- Ultra-miniature Size Weight: 4 Grams 0.1 Cubic Inch Volume

- Standard Input Voltages 5, 12, 24 and 28 Volts DC

- Operating Temperature Standard: -25°C to +70C Optional: -55°C to +85°C

- MIL-STD-883 Screening Available

- Isolated: Input to Output up to 1500 VDC

PICO also manufactures over 800 regulated and isolated DC-DC Converters and AC-DC Power Supplies and over 2500 standard ultra-miniature Transformers and Inductors.

CIRCLE 168 FOR U.S. RESPONSE CIRCLE 169 FOR RESPONSE OUTSIDE THE U.S.

## **TECHNOLOGY BRIEFING**

## **REDUCING FLAT-PANEL DISPLAY COSTS**

ttempts to replace the cathode-ray-tube (CRT) monitor with more manageable flatpanel display devices have met with little success. Even though they're bulky and generate lots of heat, the venerable CRT still sets the price and performance standards against which competing display technologies are compared. However, the surging demand for "thinness" in desktop and portable computers is accelerating the development of flat-panel displays with dramatically improved viewing quality, power consumption, and cost.

MILT LEONARD SENIOR EDITOR

Of the three existing forms of flat-panel displays – liquid crystal (LCD), plasma, and electroluminescent

(EL) – industry observers think active-matrix LCDs (AMLCDs) have the most potential to dominate the flat-panel market. AMLCDs use amorphous or silicon thin-film transistors (TFTs) to control individual pixels on the display panel. Overall AMLCD performance already exceeds or compares favorably with other flat-panel technologies in terms of viewing criteria. On the negative side are limited viewing angle, operating temperature range, and panel size; vulnerability to shock, vibration, and high humidity; and high power dissipation. The biggest drawback is cost. Today's color AMLCDs can cost up to 12 times as much as a color CRT, and from 5 to 10 times as much as other flat-panel technologies.

AMLCDs can now be fabricated with feature sizes under 5.0  $\mu$ m. But unlike IC processing, where the probability of a defect landing on a die decreases as the number of chips on a wafer increases, AMLCDs are made with one "chip" per wafer. Therefore, further feature-size shrinks to get smaller "die" dimensions doesn't necessarily mean higher yields, which presently range from 10 to 40%. And to decrease cost, most industry efforts focus on minimizing process-related defects.

The industry's concern over AMLCD yield was apparent in new equipment rollouts at SEMICON/Japan last month. Various American, European, and Japanese firms introduced integrated processing systems that control contamination by using robotics and automated substrate transport between processing chambers under vacuum. But according to Francois J. Henley, president of Photon Dynamics Inc., San Jose, Calif., a yield loss of up to 40% can occur during electrical testing of a panel alone. This is because the testing technologies are adaptations of systems designed for IC testing.

What's also needed are non-intrusive in-process inspection and repair strategies that depart significantly from methods developed for the semiconductor industry. It's now understood that inspection and repair equipment for activematrix LCDs should be designed around the requirements of AMLCD technology – namely automation, high throughput, in-process operation, noncontact and nondestructive inspection, and networked inspection and repair systems. This way, yield is boosted by detecting and repairing defective pixels prior to final panel assembly.

To obtain maximum AMLCD yield, the ultimate approach may be integrating such a system with automated processing schemes. Last year, Photon Dynamics introduced an inspection and repair system based on a patented noncontact pixel-sensing technique. The system uses several advanced technologies, including laser optics; laser-controlled physical optics; electro-optics; image processing; and electronics test, measurement, and inspection. A report from Stanford Resources Inc., SanJose, Calif., says this type of in-process testing can reduce manufacturing costs by about 50%, even with testing-equipment costs factored in. Integrated inspection and repair could further reduce manufacturing cost by another factor of three, the report states.

**18** E L E C T R O N I C D E S I G N JANUARY 9, 1992

## **ULTIMATE CONTROL**

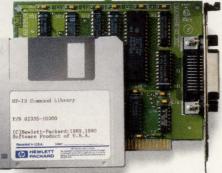

## No one can give you control of your GPIB test system like National Instruments can.

## PERFORMANCE

The NAT4882<sup>™</sup> chip makes our GPIB controller boards completely IEEE-488.2 compatible. When the NAT4882 is teamed with the Turbo488<sup>®</sup> performance chip, you get the

maximum IEEE-488 transfer rate of 1 Mbytes/sec for both read and write operations.

Use our industry-standard NI-488® software to control your GPIB instruments and give your test programs maximum throughput, regardless of your choice of personal computers or workstations.

## COMPATIBILITY

The NAT4882 controller chip is also compatible with the controller chips of the past, so you get the best of both worlds – complete compatibility with your existing applications and the ability to meet your future requirements.

And when your controller needs change, NI-488 programs are compatible across many different platforms and operating systems – without modification.

### **UPGRADE PROGRAM**

Existing PC, PS/2, and Macintosh customers can upgrade to the benefits of IEEE-488.2 and increased performance through a special upgrade program.

## TRAINING

Learn even more ways to improve your test system by taking our hands-on, IEEE-488 training course.

For more information on how you can have the ultimate GPIB control, call: (512) 794-0100 or (800) IEEE 488 (Toll-free U.S. and Canada) NATIONAL INSTRUMENTS The software is the Instrument

6504 Bridge Point Parkway Austin, TX 78730-5039

See Us At ATE And Instrumentation Booth #108

AUSTRALIA (03) 879 9422 • DENMARK (45) 76 73 22 • FRANCE (1) 48 65 33 70 • GERMANY (089) 714 5093 • ITALY (02) 4830 1892

JAPAN (03) 3788 1921 + NETHERLANDS (01720) 45761 + NORWAY (03) 846 866 + SPAIR (908) 604 304 + SWITZERLAND (056) 45 58 00 + U.K. (0635) 523 545

Product names listed are trademarks of their respective manufacturers. Company names listed are trademarks or trade names of their respective companies. © Copyright 1991 National Instruments Corporation. All rights reserved.

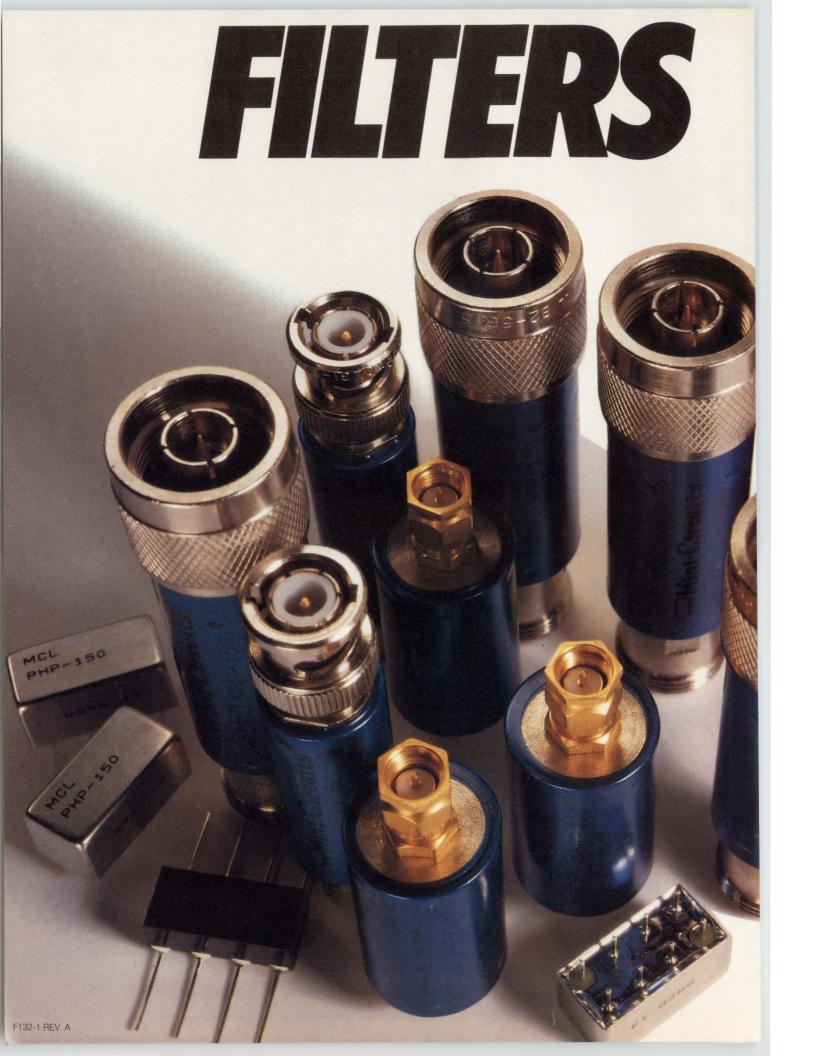

lowpass, highpass, bandpass • less than 1dB insertion loss • greater than 40dB stopband rejection • surface-mount • BNC, Type N, SMA available

dc to 3GHz from \$1145

•5-section, 30dB/octave rolloff •VSWR less than 1.7 (typ) •rugged hermetically-sealed pin models •constant phase • meets MIL-STD-202 tests • over 100 off-the-shelf models • immediate delivery

HIGH PASS

frequency

frequency

BANDPASS

Bb untion

#### IOW DASS, Plug-in, dc to 1200MHz

| Model<br>No.                                                                                           | Passband<br>MHz<br>loss < 1dB                                                                    | Stopbar<br>loss<br>> 20dB                                                                      | nd, MHz<br>loss<br>> 40dB                                                                             | Model<br>No.                                                                                                 | Passband<br>MHz<br>loss < 1dB                                                                                         | Stopba<br>loss<br>> 20dB                                                                                   | nd, MHz<br>loss<br>> 40dB                                                                                     |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| PLP-5<br>PLP-10.7<br>PLP-21.4<br>PLP-30<br>PLP-50<br>PLP-70<br>PLP-90<br>PLP-100<br>PLP-150<br>PLP-200 | DC-5<br>DC-11<br>DC-22<br>DC-32<br>DC-48<br>DC-60<br>DC-81<br>DC-81<br>DC-98<br>DC-140<br>DC-190 | 8-10<br>19-24<br>32-41<br>47-61<br>70-90<br>90-117<br>121-137<br>146-189<br>210-300<br>290-390 | 10-200<br>24-200<br>41-200<br>61-200<br>90-200<br>117-300<br>167-400<br>189-400<br>300-600<br>390-800 | PLP-250<br>PLP-300<br>PLP-450<br>PLP-550<br>PLP-600<br>PLP-750<br>PLP-800<br>PLP-800<br>PLP-1000<br>PLP-1200 | DC-225<br>DC-270<br>DC-400<br>DC-520<br>DC-520<br>DC-700<br>DC-700<br>DC-720<br>DC-760<br>DC-760<br>DC-900<br>DC-1000 | 320-400<br>410-550<br>580-750<br>840-1120<br>1000-1300<br>1080-1400<br>1100-1400<br>1340-1750<br>1620-2100 | 400-1200<br>550-1200<br>750-1800<br>920-2000<br>1120-2000<br>1400-2000<br>1400-2000<br>1750-2000<br>2100-2500 |

| Price, (1-9 qty                                                                                        |                                                                                                  |                                                                                                | NC \$32.95, SMA                                                                                       | \$34.95. Type N \$3<br>570 MHz                                                                               | 5.95                                                                                                                  |                                                                                                            |                                                                                                               |

| SCLF-21.4<br>SCLF-30<br>SCLF-45<br>SCLF-135                                                            | DC-22<br>DC-30<br>DC-45<br>DC-135                                                                | 32-41<br>47-61<br>70-90<br>210-300                                                             | 41-200<br>61-200<br>90-200<br>300-600                                                                 | SCLF-190<br>SCLF-380<br>SCLF-420                                                                             | DC-190<br>DC-380<br>DC-420                                                                                            | 290-390<br>580-750<br>750-920                                                                              | 390-800<br>750-1800<br>920-2000                                                                               |

Price, (1-9 qty), all models: \$11.45

#### Flat Time Delay, dc to 1870 MHz

|                                                                                              | Passband<br>MHz                                                                     | Stopband<br>MHz                                                                          |                                                         |                                                                                  | WR<br>ge, DC thru                                                    |                                                          | Delay Variat<br>, Range, DC                          |                                                         |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|

| Model<br>No.                                                                                 | loss < 1.2dB                                                                        | loss<br>>10dB                                                                            | loss<br>> 20dB                                          | 0.2fco<br>X                                                                      | 0.6fco<br>X                                                          | fco<br>X                                                 | 2fco<br>X                                            | 2.67fc                                                  |

| PBLP-39<br>PBLP-117<br>PBLP-156<br>PBLP-200<br>PBLP-300<br>PBLP-467<br>▲BLP-933<br>▲BLP-1870 | DC-23<br>DC-65<br>DC-94<br>DC-120<br>DC-180<br>DC-280<br>DC-280<br>DC-560<br>DC-850 | 78-117<br>234-312<br>312-416<br>400-534<br>600-801<br>934-1246<br>1866-2490<br>3740-6000 | 117<br>312<br>416<br>534<br>801<br>1246<br>2490<br>5000 | 1.3:1<br>1.3:1<br>0.3:1<br>1.6:1<br>1.25:1<br>1.25:1<br>1.3:1<br>1.3:1<br>1.45:1 | 2.3:1<br>2.4:1<br>1.1:1<br>2.2:1<br>2.2:1<br>2.2:1<br>2.2:1<br>2.9:1 | 0.7<br>0.35<br>0.3<br>0.4<br>0.2<br>0.15<br>0.09<br>0.05 | 4.0<br>1.4<br>1.1<br>1.3<br>0.6<br>0.4<br>0.2<br>0.1 | 5.0<br>1.9<br>1.5<br>1.6<br>0.8<br>0.55<br>0.28<br>0.15 |

Price, (1-9 qty), all models: plug-in \$19.95, BNC \$36.95, SMA \$38.95, Type N \$39.95 NOTE: ▲: -933 and -1870 only with connectors, at additional \$2 above other connector m

## high pass, Plug-in, 27.5 to 2200 MHz

|                                                                                    |                                                                                 | band<br>Hz                                                                 | Passband<br>MHz                                                                       | VSWR<br>Pass-                                                        |                                                                            |                                                                    | band<br>Hz                                                                | Passband<br>MHz                                                                   | VSWF<br>Pass-                                               |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|

| Model<br>No.                                                                       | loss<br>< 40dB                                                                  | loss<br>< 20dB                                                             | loss<br><1dB                                                                          | band<br>Typ.                                                         | Model<br>No.                                                               | loss<br>< 40dB                                                     | loss<br>< 20dB                                                            | loss<br><1dB                                                                      | band<br>Typ.                                                |

| PHP-25<br>PHP-50<br>PHP-100<br>PHP-150<br>PHP-175<br>PHP-200<br>PHP-250<br>PHP-300 | DC-13<br>DC-20<br>DC-40<br>DC-70<br>DC-70<br>DC-70<br>DC-90<br>DC-100<br>DC-145 | 13-19<br>20-26<br>40-55<br>70-95<br>70-105<br>90-116<br>100-150<br>145-170 | 27.5-200<br>41-200<br>90-400<br>133-600<br>160-800<br>185-800<br>225-1200<br>290-1200 | 1.8:1<br>1.5:1<br>1.8:1<br>1.8:1<br>1.5:1<br>1.6:1<br>1.3:1<br>1.7:1 | PHP-400<br>PHP-500<br>PHP-600<br>PHP-700<br>PHP-800<br>PHP-900<br>PHP-1000 | DC-210<br>DC-280<br>DC-350<br>DC-400<br>DC-445<br>DC-520<br>DC-550 | 210-290<br>280-365<br>350-440<br>400-520<br>445-570<br>520-660<br>550-720 | 395-1600<br>500-1600<br>600-1600<br>700-1800<br>780-2000<br>910-2100<br>1000-2200 | 1.7:1<br>1.8:1<br>2.0:1<br>1.6:1<br>2.1:1<br>1.8:1<br>1.9:1 |

Price, (1-9 qty), all models: plug-in \$14.95, BNC \$36.95, SMA \$38.95, Type N \$39.95

#### bandpass, Elliptic Response, 10.7 to 70 MHz

Price, (1-9 qty), all models: plug-in \$18.95, BNC \$40.95, SMA \$42.95, Type N \$43.95

| Model<br>No.                                       | Center<br>Freq.<br>(MHz)             | Passband<br>I.L. 1.5 dB<br>Max.<br>(MHz)                     | 3 dB<br>Bandwidth<br>Typ.<br>(MHz)                       | I.L.<br>> 20dB<br>at MHz                               | Dipbands<br>I.L.<br>> 35dB<br>at MHz                                                | Model<br>No.                                     |  |

|----------------------------------------------------|--------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------|--|

| PBP-10.7<br>PBP-21.4<br>PBP-30<br>PBP-60<br>PBP-70 | 10.7<br>21.4<br>30.0<br>60.0<br>70.0 | 9.6-11.5<br>19.2-23.6<br>27.0-33.0<br>55.0-67.0<br>63.0-77.0 | 8.9-12.7<br>17.9-25.3<br>25-35<br>49.5-70.5<br>68.0-82.0 | 7.5 & 15<br>15.5 & 29<br>22 & 40<br>44 & 79<br>51 & 94 | 0.6 & 50-1000<br>3.0 & 80-1000<br>3.2 & 99-1000<br>4.6 & 190-1000<br>6.0 & 193-1000 | PIF-21.4<br>PIF-30<br>PIF-40<br>PIF-50<br>PIF-60 |  |

#### Constant Impedance, 21.4 to 70 MHz Center | Passband | Stopband | VSWR

| Model<br>No.                                               | Freq.<br>MHz                       | MHz<br>loss<br><1dB                                | > 20dB<br>at MHz                                                           | Total Ban<br>MHz                                         |

|------------------------------------------------------------|------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------|

| PIF-21.4<br>PIF-30<br>PIF-40<br>PIF-50<br>PIF-60<br>PIF-70 | 21.4<br>30<br>42<br>50<br>60<br>70 | 18-25<br>25-35<br>35-49<br>41-58<br>50-70<br>58-82 | 1.3 & 150<br>1.9 & 210<br>2.6 & 300<br>3.1 & 350<br>3.8 & 400<br>4.4 & 490 | DC-220<br>DC-330<br>DC-400<br>DC-440<br>DC-500<br>DC-550 |

| Price, (1-3<br>BNIC \$36                                   |                                    |                                                    | g-in \$14.95,<br>Type N \$39                                               | 95                                                       |

finding new ways. setting higher standards WE ACCEPT AMERICAN EXPRESS AND VISA P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661

Distribution Centers/NORTH AMERICA 800-654-7949 • 417-335-5935 Fax 417-335-5945 **CIRCLE 204 FOR U.S. RESPONSE**

EUROPE 44-252-835094 Fax 44-252-837010 **CIRCLE 205 FOR RESPONSE OUTSIDE THE U.S.**

F132-2 REV A

FLOATING HIGH SIDE

1221

ROUND REFERENCE LOW SIDE

Now you can replace a fistful of components, and drive power FETs and IGBTs with one costeffective part: The IR2110 monolithic dual channel 2A gate driver with floating high side and ground reference low side.

Count your design time in hours instead of days. And cut assembly time to a fraction.

The IR2110 runs as fast as it designs. With operation above

1 MHz. On-chip bootstrap. Plus matched channel delay within 10 ns. That's right. 10 ns.

It takes good care of your circuit too, with gate undervoltage protection.

And latched shutdown makes current mode control both simple and easy. Is it rugged? 50 V/ns dv/dt at –55 to 150°C in plastic. Versatile? Operates off 12 to 500 V rails with 5 to 20 V input, in any circuit topology. Reliable? The IR2110 meets the same high standards as IR's incomparable HEXFET<sup>®</sup> power MOSFETs.

+500v

MOSFET

IGBT

Call (800) 245-5549 for more information. We'll get it off the ground and on your desk in no time.

## WORLD HEADQUARTERS: 233 KANSAS ST. ELSEGUNDO. CA 90245. U.S.A. (213) 772-2000. TWX 910 348-6291. TELEX 472-0403. EUROPEAN HEADQUARTERS: HURST GREEN. OXTED. SURREY RH8 9BB. ENGLAND TELEPHONE (0883) 713215. TELEX 95219

CIRCLE 192 FOR U.S. RESPONSE

CIRCLE 193 FOR RESPONSE OUTSIDE THE U.S.

## TECHNOLOGY NEWSLETTER

**SUPERCONDUCTORS IMPLEMENT LOGIC GATES** The world's first digital-logic gates using high-temperature superconductors have reportedly been built. Researchers at the Applied Technology Div. of TRW Inc., Redondo Beach, Calif., have simulated 4-ps rise times for the devices, which translates to 250 billion switching operations per second. TRW says the architecture can be used for all Boolean functions. Functions already demonstrated include AND, EXOR, EXNOR, inversion, and buffer. Each logic gate is formed by a string of dc superconducting quantum-interference devices (SQUIDs), which are thin films made from the ceramic compound yttrium-barium-copper oxide. The gates were originally operated at temperatures from 4.2 to 36K. But recently developed grain-boundary-junction technology will enable the logic gates to work at 65K. Power dissipation of each gate is about 2 nW. High-speed circuitry will dissipate a projected 100 nW, and 10-GHz operation will dissipate 1 W of power. TRW's high-temperature circuits resemble CMOS designs and are amenable to gate-array and ASIC approaches. For more information, call Susan Brough, (310) 812-5227. ML

**POLYMERS IMPROVE ELECTRO-OPTIC DEVICES** Avionics, and photonics applications. Currently used nonlinear optical crystals for use in fiber optics, avionics, and photonics applications. Currently used nonlinear optical crystals (such as lithium niobate) are brittle, not easily integrated with silicon or gallium-arsenide structures, and are costly to produce. In contrast, the new NLOPs have a lower dielectric constant, as well as higher electro-optic coefficients, mechanical toughness, stability, and design and manufacturing flexibility. In addition, the new materials are compatible with silicon processing. Wave-guides produced with NLOPs can be spin-coated, patterned, etched, and cladded with existing IC manufacturing processes. Other applications include high-speed fiber-optic devices, such as optical interconnects in high-speed optical computers. NWC is developing NLOPs for Langmuir-Blodgett processing, which has excellent film-thickness control. The Center is offering six classes of NLOP compositions for licensing. For more information, call Martha Harring-ton, (619) 939-1698/1215. *ML*

**CFI SET TO RELEASE STANDARDS COMMERCIALLY** Interveloped by EDA tool suppliers, and the needs of the EDA users and tool integrators. Also, CFI's standards-release process now has a Pilot Implementation Program step to bring EDA-tool suppliers, tool integrators, and tool users deeper into the standards-release version of the standards, and will then help determine how well the final standards address complex tool-integration tasks. All sponsor and corporate CFI members are eligible to participate in pilot projects, which will begin this month. Details on the program are available from CFI at (512) 338-3739. LM

MULTIPLE-GATE FET AIMED AT NEURAL NETS With the addition of multiple, independent gate electrodes to a single MOS transistor, the transistor can calculate the weighted sum of every input and control its "on" or "off" state based on the result of the weighted-sum calculation. Consequently, the neuron MOSFET (neuMOS) exhibits a function similar to that of a biological neuron cell, such as found in the brain. Developed by Dr. Tadahiro Ohmi and Tadashi Shibata at the department of electrical engineering of Tohoku University, Sendai, Japan, the neuMOS element could form a variable-threshold transistor, a neuron in a neural network, a single-gate digital-to-analog converter, and even "soft" logic (logic that can be configured to any of 16 logic functions just by changing the control signals). Unveiled at last month's International Electron Devices Meeting in Washington, D.C., the experimental device was fabricated with a standard double-polysilicon n-channel MOS process. The structure consists of a floating gate and multiple input gates that are capacitively coupled with the floating gate. And because the summing operation occurs in a voltage mode via the capacitive coupling effect, the device essentially consumes no power. That makes it an ideal candidate for use in high-integration ICs. *DB*

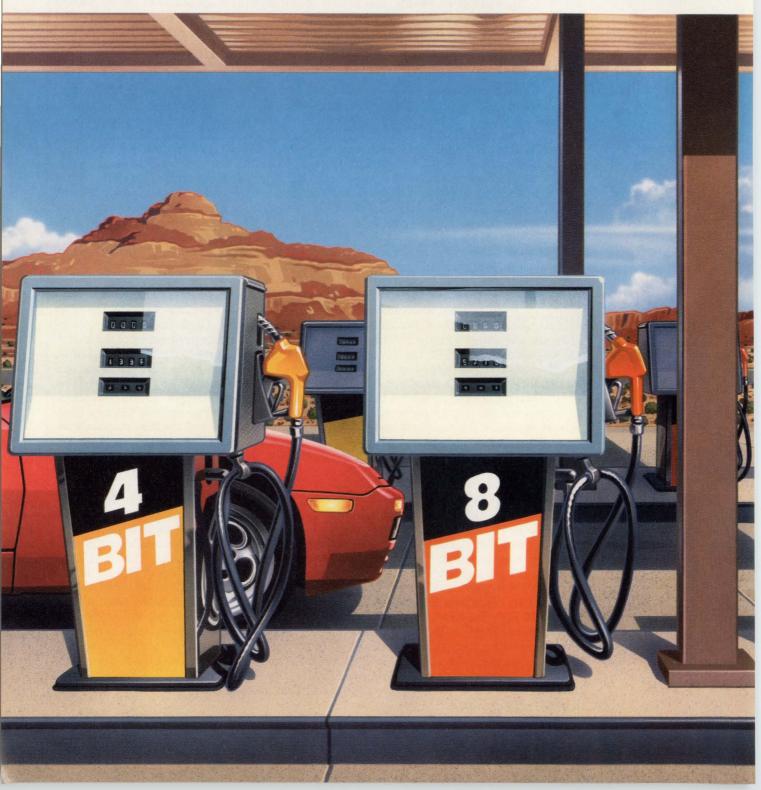

# Toshiba Micros. Accelerate Time

# 298 Ways To To-Market.

Pull into Toshiba for unmatched product selection, service and support. After you've conceptualized your latest design and you're ready to begin the long

| 4-Bit  | 139 |

|--------|-----|

| 8-Bit  | 139 |

| 16-Bit | 20  |

With Toshiba's unmatched selection of 298 micros, you're never far from market. trip to market, be sure to fuel your silicon needs with Toshiba's line of 298 varieties of 4-, 8- and 16-bit microprocessors, microcontrollers, as well as development tools.

Toshiba has over 100 4-bit microcontrollers to drive hundreds of consumer and industrial applications with high speed CMOS performance and on-chip ROM/ RAM capability. We're your sec-

ond source for Zilog Z80 and Intel 8048/8085, as well as Motorola 68HC000, 68HC11 and 68HC05. And our advanced technology lets us offer you Z80- and 68HC000-based ASSPs, too.

Since Toshiba is one of the world's largest CMOS micro manufacturers, you can count on our production and delivery to make your design/production cycle run smoothly. Our 20 years of experience in fueling fast production starts yields to none. We're capitalizing on our landmark semiconductor process to propel our diverse 4-bit, 8-bit, 16-bit and future 32-bit micros.

Whenever you're driving a new design, you can expect a smooth ride on the CMOST Expressway.

Call Toshiba today.

For technical literature, call 1-800-321-1718.

The CMOST Expressway. Paved in silicon with the world's leading CMOS technology.

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

© 1991 Toshiba America Electronic Components, Inc. Product names and company names mentioned herein may be trademarks or registered trademarks of their respective companies.

CSM-90-054

CIRCLE 131 FOR U.S. RESPONSE

CIRCLE 132 FOR RESPONSE OUTSIDE THE U.S.

## TECHNOLOGY NEWSLETTER

SENSORS USE THIN FILM A proprietary sputtering technique developed by the TiNi Alloy Co., Oakland, Calif., deposits films of nickel-titanium alloy with shape memory onto WITH SHAPE MEMORY various substrates. Films have been produced on both glass and silicon, in thicknesses ranging from 2000 Å to 50  $\mu$ m. The alloy has the unique property of assuming its original shape upon application of electrical power after it's deformed by an external force. The principle behind the shape-memory effect is the temperature-dependent change in the material's crystal structure. In a pneumatic-valve application, for example, the shape-memory film is deformed by a constant air pressure to seat against a valve orifice. When electrical current is passed through the film, the generated heat transforms the membrane to its hightemperature phase, thereby lifting the film off the inlet orifice. Valve opening and closure occurs in 15 ms. Other applications under development are Schottky-junction sensors and twostate microscopic elements for optical storage. For more information, call John Busch, (415) 658-3172. ML

IMPROVED STATE AVERAGING Simulating switched-mode power supplies with a mathematical-behavioral approach called state averaging can increase simulation speed by as much as AIDS POWER-SUPPLY DESIGN 1000 times over standard Spice techniques. State averaging isn't a new idea; many EDA vendors sell state-averaged models of a power supply's pulse-width-modulator chip. However, Dazix, Huntsville, Ala., is working with U.K.-based ERA Technology Ltd. to develop a unique switched-mode power-supply design aid based on the state-average technique. ERA has an implementation that differs from the existing models for three reasons: the complete circuit, not just the pulse-width-modulation controller, can be modeled with state averaging; the circuit's frequency response (Bode plot), and consequently its stability, can be analyzed; and current-mode controllers can be modeled. The ERA technology will be incorporated into the Dazix Analog Design Engineer product. Call (205) 730-2000. LM

DESIGN PROCESS SHRINKS System designers can create semicustom single-board computers (SBCs) in just twelve weeks using the Application Specific Automation Processor SBC DEVELOPMENT TIME (ASAP) from Ziatech Corp., San Luis Obispo, Calif. With the help of ASAP, designers can achieve the right mix of processor, I/O, and peripheral functionality by using predesigned and tested I/O circuit modules that have a proven core-processor module. Because the boards are constructed with pretested parts, the bugs should be minimal. The ASAP approach bridges the gap between off-the-shelf products and proprietary solutions. Typical ASAP boards are designed to the STDbus standard form factor (4.5 by 6.5 in.) using the STDbus edge connector. An STD 32 backplane connector or an SBX expansion interface for daughterboard modules offers added flexibility. For more information, contact Ziatech at (805) 541-0488. RN

**PORT EASES BUILDING REAL-TIME CONTROL JOBS** Developers working with embedded real-time applications may have an easi-er time of it in the wake of an agreement between Talerian Corp. and Wind River Systems. Under the pact, Talerian, Mountain View, Calif., will port its RTworks real-time development tools to the VxWorks real-time operating system and development environment from Wind River Systems, Alameda, Calif. As a result, developers will have the means to build workstation-based or embedded real-time applications that require intelligent control. They'll also be able to distribute real-time applications across multiple hosts in a client-server architecture. By including sophisticated graphics, knowledge-based systems, and interprocess communications, RTworks enables developers to build intelligent real-time monitoring and control systems for Unix and VMS workstations. VxWorks expands the RTworks realm to applications requiring a real-time operating system. SVT

FPGA ALLIANCE PROGRAM Inc. MEMORPHILLE TO 10 Three more companies have joined Actel Corp.'s Industry Alliance Program, a program that enables companies to have technical and cooperative market-UPS MEMBERSHIP TO 19 ing relationships with the Sunnyvale, Calif.-based FPGA supplier. The addition of GenRad Design Automation, Isdata, and Logic Automation brings the total membership number to 19 EDA and gate-array companies. GenRad and Isdata represent the first companies from the U.K. and Germany, respectively, to join the program. The program's goal is to provide Actel customers with links to third-party tools and ASIC-migration paths. Actel supplies Alliance members with its software and technical assistance for Actel-product-support development. For more information, call Actel at (408) 739-1010. LM

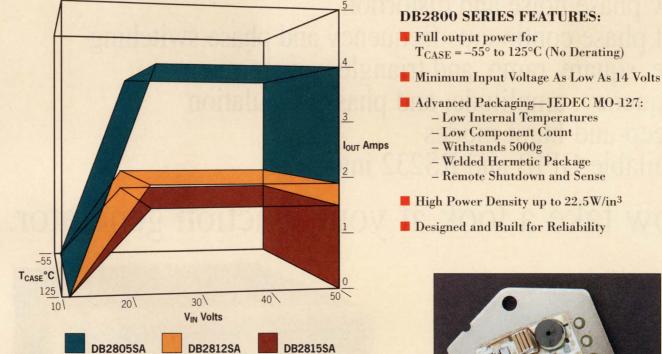

POWER AT TEMPERATURE 🗖 LOWEST MINIMUM INPUT VOLTAGE 📮 LOW THERMAL RESISTANCE

### **MODEL/VOLTAGE CHART:**

| Model               | Full Output Power<br>Input Voltage Range | Output Voltage/<br>Current |

|---------------------|------------------------------------------|----------------------------|

| DB2805S<br>DB2805SA | 16–50 Volts                              | 5 Volts/4.00 Amps          |

| DB2812S<br>DB2812SA | 14–50 Volts                              | 12 Volts/1.88 Amps         |

| DB2815S<br>DB2815SA | 15–50 Volts                              | 15 Volts/1.50 Amps         |

JEDEC MO-127 Packaging (Actual Size)

For Immediate **Product Information** Call 1-800-448-1025 or FAX (602) 888-3329

ICATED TO EXCELLENC

**APEX MICROTECHNOLOGY CORPORATION**

5980 N. SHANNON ROAD, TUCSON, ARIZONA 85741

**For Applications** and Product Selection **Assistance Call Newly Expanded Hotline** 1-800-421-1865

CANADA (416) 821-7800 DENMARK (42) 24 48 88 GERMANY (6152) 61081 SPAIN (1) 4094725 FINLAND (0) 8041-041 FRANCE (1) 69 07 08 24 HONG KONG 8339013 ISRAEL (3) 9345171 INDIA (212) 339836 ITALY (2) 99041977 JAPAN (3) 3244-3787 NETHERLANDS (10) 4519533 NORWAY (2) 50 06 50 KOREA (2) 745-2761 AUSTRIA (1) 505 15220 SWITZERLAND (56) 26 54 86 SINGAPORE 284-8537 SWEDEN (8) 795 9650 TAIWAN (02) 721-9533 UK (0844) 278781 BELGIUM/LUXEMBOURG (3) 828-3880 AUSTRALIA (08) 277-3288 "APEX HYBRID & IC HANDBOOK" — Order Your Free Copy Of The New 5th Edition Today!

**CIRCLE 174 FOR U.S. RESPONSE**

**CIRCLE 175 FOR RESPONSE OUTSIDE THE U.S.**

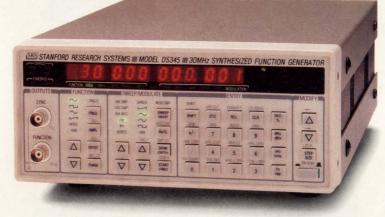

# Take a look at what the DS345 Synthesized Function Generator offers for only \$1895.

30 MHz direct digitally synthesized source 1 µHz resolution 12 bit, 40 Msample/sec arbitrary waveform generation Low phase noise and distortion Fast phase continuous frequency and phase switching Sine, square, ramp, and triangle waveforms Frequency, amplitude, and phase modulation Sweep and burst modes Available GPIB and RS232 interfaces

Now take a look at your function generator.

The DS345 from SRS. At \$1895, it's the only function generator you need.

1290 D Reamwood Avenue, Sunnyvale, CA 94089 TEL (408)744-9040 FAX 4087449049 TLX 706891 SRS UD

CIRCLE 155 FOR U.S. RESPONSE CIRCLE 156 FOR RESPONSE OUTSIDE THE U.S.

## TECHNOLOGY ADVANCES

## RISC PROCESSORS, MULTIMEGABIT RAMS, AND MIXED-SIGNAL DEVELOPMENTS HIGHLIGHT ISSCC

TTigh-performance microprocessors, dense memories, and precision analog and mixed-signal circuits will be showcased at next month's International Solid-State Circuits Conference. The conference's 80 technical papers will detail such innovations as a 1000-MIPS processor implemented with 0.3-um features, sub-15-ns 16-Mbit SRAMs, 8-bit 650-MHz analog-to-digital converters, and a 10-Gbit/s silicon-bipolar chip set for optical communications. Other developments covered include active-matrix thinfilm transistor technology. and image sensing and processing.

To achieve a throughput of 1000 MIPS, researchers at the Central Research Laboratory of Hitachi Ltd., Tokyo, Japan, integrated two superscalar processors, each with a two-level cache memory, onto a biCMOS chip by employing 0.3-µm design features-a technological first. The chip can operate at 250 MHz, with each processor executing two instructions per clock, for a total throughput of 1000 MIPS. About 1.02 million transistors are employed by the processors, each of which has a 1.2-ns 32-bit adder, a 1.3-ns eight-port register file, and a 2.8-ns translation-lookaside buffer and cache memory.

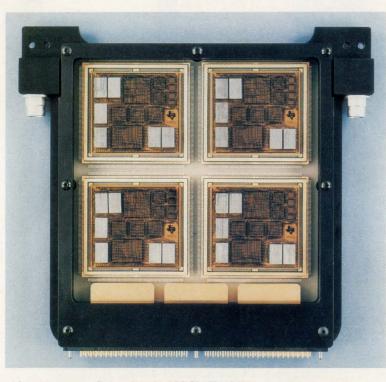

A pair of biCMOS chips—a 3-million-transistor Sparc-compatible superscalar RISC processor and a companion 2.2-million-transistor cache-controller chip—both capable of operating at 50 MHz. will be described by Sun Microsystems Inc., Mountain View, Calif., and Texas Instruments Inc., Dallas. The SuperSparc CPU chip packs 36 kbytes of first-level cache, a complete memory-management unit, and a full double-precision floatingpoint unit. It can execute up to three instructions per clock, vielding a throughput of up to 150 MIPS. The cache-control chip provides 264 kbits of tag RAM power dissipation goes up to 30 W.

The CISC processor is also implemented with the same 3.3-V submicron technology. It employs a macropipelined architecture and dissipates about 18 W when running at 100 MHz. The chip's clocksper-instruction ratio is 2.4 times better than for the company's micropipelined implementation of the same instruction set. Consequently, a performance benchmark of 50 Spec-

#### ing 8 kbytes each.

To support such highperformance processors, dense and fast static RAMs as well as new-architecture dynamic RAMs are being developed to fill the system designer's wish list. A pair of 16-Mbit SRAMs, one from NEC Corp., Sagamihara, Japan, and the other from Fujitsu's Kawasaki research center, achieve access times of 12 and 15 ns, respectively. Both are based on 0.4-um design rules and CMOS processes. The NEC device is made from a quadruple-polysilicon, doublemetal process with thinfilm-transistor (TFT) active loads. It operates from a 3.3-V supply and dissipates just under 300 mW when running at 30 MHz. Fujitsu's chip operates from a 3-V supply, and dissipates only 60% of the power of NEC's chip-165 mWat30MHz.

Experimenting with 1-V process technology, Hitachi's researchers will detail the fabrication of a small 4-kbit test chip. The memory cells employ TFT loads and are fabricated with 0.4- $\mu$ m design rules. When scaled to a 4-Mbit RAM, the larger chip would occupy about 75 mm<sup>2</sup> and draw just 0.7  $\mu$ A of standby current.

Pushing biCMOS for high-speed memory, Toshiba Corp., Kawasaki, and NEC have crafted 3.3-V, 4-Mbit SRAMs that access in just 9 and 6 ns, respectively. The Toshiba memory is organized as 256 kwords by 16 bits and consumes just 430 mW when operating at 50 MHz with TTL I/O levels. NEC's part employs ECL I/O or 3.3-V TTL I/O (with TTL I/O, access time slows

## ISSCC - WANT TO GO?

he International Solid State Circuits Conference will be held at the San Francisco Hilton Hotel, Feb. 19-21. For registration details and the

that supports up to 2 Mbytes of external cache memory. Two different multiprocessor-system bus interfaces and two different I/O electrical interfaces are supported by the controller.

Both a CISC and a RISC processor will be detailed in a pair of papers from Digital Equipment Corp., Hudson, Mass. The RISC device has a 64-bit architecture and runs at 200 MHz to deliver a peak throughput of 400 MIPS. The CMOS circuit includes 8-kbyte instruction and data caches, and can execute two instructions per clock to achieve its 400-MIPS peak performance. Fabricated with 0.75-µm design rules in a 3.3-V process, the CPU is a power-hungry device due to its high clock rate—

contact Diane Suiters at Courtesy Associates, 665 15th St. NW, Suite 300, Washington D.C. 20005; (202) 639-4255, or by fax at (202) 347-6109.

full advance program,

marks is attained when running at a frequency of 100 MHz.

Another high-performance CPU to be disclosed in the same session is a 289-MFLOPS supercomputer on a chip developed by Fujitsu Ltd., Atsugi, Japan. Also fabricated in CMOS, the processor operates at 70 MHz and achieves a 289-MFLOPS throughput for single-precision computations and 149 MFLOPS for double-precision operations. To move data on and off the chip quickly, designers implemented a bus that can transfer 560 Mbytes/s. To perform the computations, the processor contains six vector pipelines, four of which operate simultaneously with four-way bank-structured vector registers contain-

DESIGN29

E L E C T R O N I C I JANUARY 9, 1992

## TECHNOLOGY ADVANCES

to 8 ns) and is organized as either 4 Mwords by 1 bit or 1 M by 4. It dissipates 750 mW with the ECL I/O and just 230 mW with the TTL option.

Suprisingly, there are only two DRAM papers at this year's conference venue-in past years it seemed that high-density DRAM papers dominated the spotlight. The first describes a novel combination DRAM and SRAM circuit developed by Mitsubishi Electric Corp., Itami, Japan. The IC combines 16 kbits of SRAM cache memory along with 4 Mbits of DRAM. The cache-DRAM can transfer data at 100 MHz over its cache port, and includes a copy-back scheme that keeps the copy-back time equal to the DRAM access time, and a flexible DRAM-to-cache mapping scheme.

The other DRAM paper is from NEC and details a 64-Mbit device that can be accessed in just 30 ns. The chip includes a built-in testand-repair capability to reduce test cost and increase reliability. Additional memory papers include a 16-Mbit flash device from NEC and a 4-Mbit flash EEPROM developed by Toshiba. Both can be read or programmed from a lone 5-V supply. NEC's chip also has a selective sector-erase capability that allows any 512-word sector to be erased and reprogrammed, minimizing the memory update time.

Data conversion is also a hot topic at the upcoming conference, with over a half-dozen papers focused on ADCs. The fastest of the lot is an 8-bit, 650-MHz folded-architecture ADC developed at the Philips Research Labs, Eindhoven, the Netherlands. Implemented in a silicon bipolar process, the chip takes advantage of folding interpolation and comparator error averaging in the analog domain to achieve 7.8 effective bits at a 150-MHz input and a 650-MHz conversion rate. The chip dissipates a mere 850 mW from a - 4.5-V supply.

Slowing the conversion rate to 50 MHz, a second bipolar device from Philips ups the resolution to 10 bits by employing a fully-differential pipelined architecture. An on-chip sample-and-hold amplifier and digital error correction give the chip 66 dB of signal-to-(noise + distortion) ratio at the 50-MHz conversion rate. The chip consumes about 750 mW from a-5-V supply.

A trio of 12-bit devices from Hewlett-Packard Co., Palo Alto, Calif.; Stanford University, Stanford, Calif.; and a joint development by Analog Devices Inc., Wilmington, Del., and the University of Illinois at Urbana will also be described. The H-P chip runs at 20 MHz and employs a 10-stage ripple-through architecture with on-chip track-and-hold and digital error correction. Able to maintain the signal-tonoise ratio over the full Nyquist bandwidth, the converter can limit the harmonic distortion to -72 dB with some external adjustment. This chip, though, is rather power-hungry, consuming 3.5 W when powered by +5- and -5.2-V power supplies.

The converter from Stanford runs at only 5 MHz but employs a fullydifferential two-step architecture with analog and digital error correction.

30 E L E C T R O N I C JANUARY 9, 1992

The third 12-bit converter, a CMOS device developed by Analog Devices, employs an all-digital linearity improvement scheme to reduce feedthrough, offset, and digital-to-analogconverter errors, and to simultaneously improve the total harmonic distortion from -64 to -77 dB. Another paper by Analog Devices will describe a 17-bit algorithmic high-resolution converter implemented in biCMOS. The chip exhibits 15 bits of resolution with a 500-µs conversion time. On-chip auto-gainranging with offset cancellation lets the chip achieve the 17-bit dynamic range with only 20 µV of dc offset voltage.

Circuits for communications applications are scattered throughout various sessions at the upcoming conference. For instance, a frequency divider that can operate at up to 18.26 GHz will be described by researchers at Varian Corp.'s Research Center, Palo Alto, Calif. Implemented in gallium-arsenide two-dimensional electron-gas structures, the divide-by-N prescaler can be extended to eventually allow input frequencies up to 80 GHz. The 18.26-GHz input speed, though, is beaten by a 28-GHz silicon-bipolar dynamic frequency divider that NEC will describe in another session. The 1.5-mm<sup>2</sup> NEC circuit includes spiral inductive loads, polysilicon resistors, and aluminum-silicon-dioxide-aluminum capacitors and can divide the input signal by a 1:16 ratio.

In the same session as its divider paper, NEC will deliver details of a 10-GHz chip set for coherent optical communication sys-I C D E S I G N tems. The amplifier chip provides 20 dB of gain when running at 10 GHz, while the mixer chip keeps the conversion loss to just 10 dB.

Researchers from the University of California at Los Angeles will detail simple NMOS circuits that can operate at 1.8 Gbits/s with jitter of just 13 ps rms. Part of the circuit includes a phase-locked loop (PLL) that extracts the clock from a 223-bit pseudorandom sequence that comes in at 1.8 Gbits/s. A 6-GHz PLL was also developed by the University of California with support from TRW Inc., Redondo Beach, Calif. The PLL employs Al-GaAs/GaAs heterojunction bipolar devices and includes a frequency quadrupling voltage-controlled oscillator, a full balanced mixer, a lag-lead loop filter, and an output buffer.

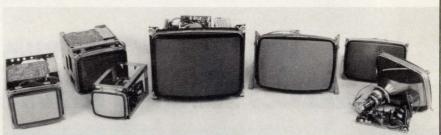

In other sessions, image sensing and processing will be spotlighted with several papers detailing 2-Mpixel imaging chips targeted at the high-definition TV market. Sony Corp., Atsugi, Japan, Toshiba, and NEC will describe image sensors in 1- and 2/3-in. formats. The Toshiba and NEC CCD sensors are set up on the 1-in. format. Overlaid with an amorphous silicon photo-conversion layer, the Toshiba chip achieves a dynamic range of 108 dB. The NEC device is a little more limited, with a 75-dB dynamic range. Sony squeezes the same number of pixels into a 2/3-in. format chip, employing a lenticular microlens array and a scaled output structure to achieve a 70-dB dynamic range.

DAVE BURSKY

## Our Model 91 will make your pulse race and help you function better.

Introducing the latest member of the 90 Series family: Model 91 Synthesized Pulse Function Generator. It delivers functions and pulses to 20 MHz with five digit frequency accuracy and has even faster pulse rates out the rear: 50 MHz, plus a 100 MHz clock rate. Choose ECL, CMOS or TTL levels, or set your own.

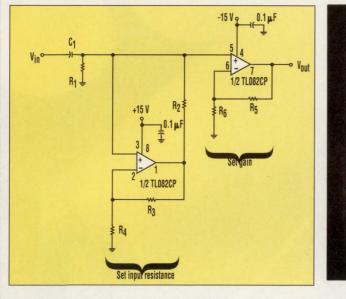

The functions and pulses can be swept or modulated,