AMORGAN-GRAMPIAN PUBLICATION DIGITAL DESIGN SYSTEMS ARCHITECTURE, INTEGRATION AND APPLICATIONS JANUARY 1985

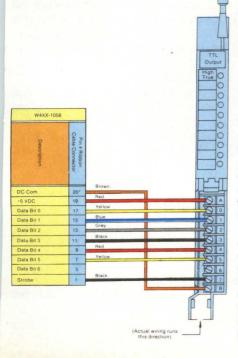

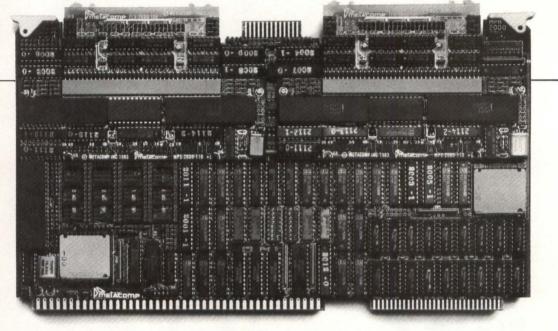

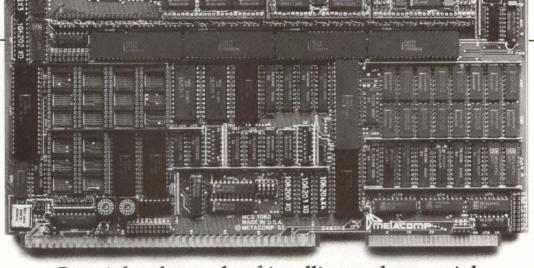

PLETHORA OF BOARDS OFFERS FLEXIBILITY IN MULTIBUS DESIGNS

INITIAL

Antimum minimum

In the second second second

The second s

## Bit Pad Two

## Feast your I/Os on this.

Unplug the old. Plug in the new. Bit Pad Two. The newest addition to Summagraphics' MM Series Data Tablets is format, function and plug compatible with Bit Pad One and Ten, and our other RS-232 UIO tablets. Summagrid, Supergrid and Microgrid.

Bit Pad Two offers the high reliability and low cost you'd expect of a product called Bit Pad. Plus electromagnetic technology to eliminate periodic biasing. And contemporary styling for today's ergonomic workstations.

Bit Pad Two is slim. Handsome. With a flat work surface for cursor steering or menu picking. And no metal edges or restrainers to scratch desks, catch spills, or collect dust. You have a choice of a 3 or 4 button cursor or one button stylus, which are interchangeable. Resolution (up to 1000 lines/inch), baud rate and sampling rate are switch selectable or programmable via the keyboard, along with remote request, software reset and self diagnostics.

Now you can move up to the latest in digitizer technology without special drivers or software rewrites. With Bit Pad Two. It's versatile. Programmable. Friendly. Built and backed by the company that knows how to deliver high quality. Summagraphics.

For information contact Summagraphics Corporation, 777 State Street Extension, P.O. Box 781, Fairfield, CT 06430. Telephone: (203) 384-1344. Telex 96-43-48. European Sales Office, Geneva, Switzerland. Telephone: 022-31-39-40.

Summaglaphic

Draw on our experience.

**Circle 30 on Reader Inquiry Card**

# Now your IBM PC can see like a hawk!

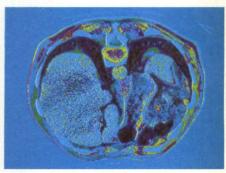

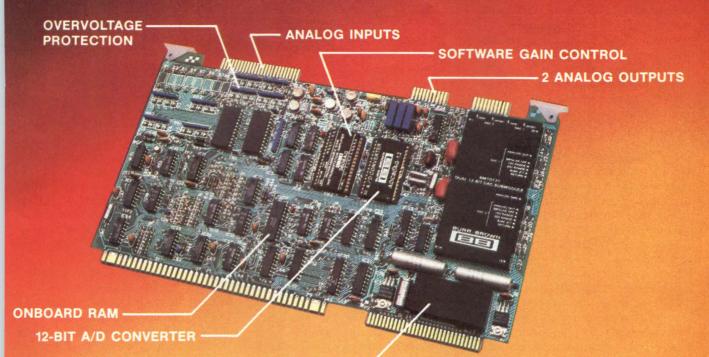

# Datacube's real-time frame grabber matched for CCD cameras.

Datacube's new IVG-128 is the perfect match for QC inspection and medical imaging applications on the IBM PC.

- Real-time video acquisition with 384H × 512V resolution and 256 grey levels or pseudo-color output (256 colors out of 16 million configurable palette).

- CCD & CID cameras map directly and efficiently in the memory space. These cameras include Sony, Fairchild, Panasonic, Hitachi, NEC and GE.

- Single, low-power board is cascadable for 24-bit true color processing.

- Dual phase-locked loop for excellent display stability and locking to external video tape input.

- Language-independent image processing and pattern recognition software routines.

See how easy it is to make your computer see like a hawk. Call or write Datacube Incorporated, 4 Dearborn Road, Peabody, MA 01960, Telephone: (617) 535-6644.

Circle 56 on Reader Inquiry Card

# **DIGITAL'S NETWORKING. AN OPEN WINDOW TO** DYNAMIC MARKET GROWTH.

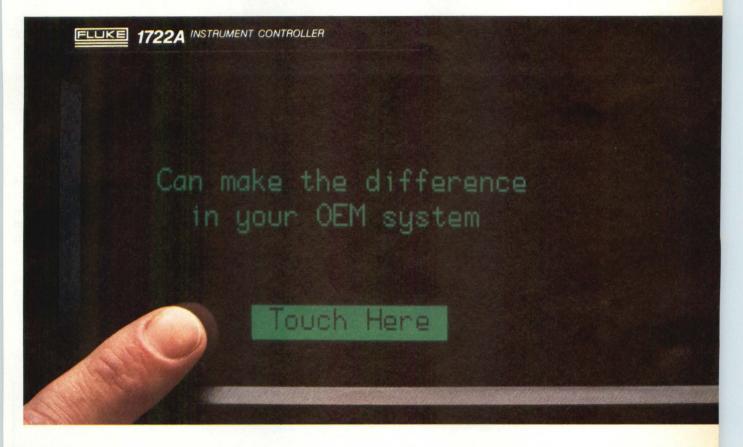

If you want to significantly enhance your OEM product offerings and enable your products to fit in easily with your customers' distributed computing environments, consider the advantages of Digital Network Architecture.

No other company offers a wider range of efficient networking options tailored to OEM reguirements. And no other company does so much to help you and your customers achieve the full benefits that networking can provide.

With Digital as your OEM supplier, you'll have the products you need to make local and wide nect model. area networking an essential part of your marketing plan. And that opens up an endless growth

## DIGITAL NETWORK ARCHITECTURE, YOUR WINDOW TO THE WORLD.

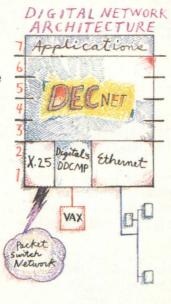

**Digital Network Architecture** (DNA) is the most comprehensive communications strategy yet developed, and currently implemented in proven, deliverable products. It supports several communications technologies. And it can accommodate future standards as they emerge because DNA is implemented in a layered structure consistent with the ISO Open Systems Intercon-

As an OEM, DNA gives you tremendous marketing and product opportunities. You can incor-

path for you and your customers. porate the best price performance You can communicate with maincomponents in your systems.

frame systems. You can match the technology to the job. And, most importantly, you can keep pace with your customers' distributed processing needs as they develop.

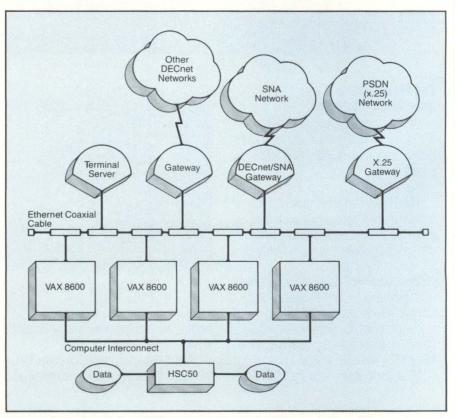

DECnet<sup>™</sup> software lets you link Digital's systems in both local and wide area configurations. It supports high-speed local area network communications using Ethernet. And it provides gateways to allow Digital's computers to communicate with other vendors' systems over private lines or packet switched X.25 networks. This means you can tailor your products to fit in with your customers' current and future networks.

© Digital Equipment Corporation, 1984. Digital, the Digital logo, DECnet, Professional 300 Series, MicroVAX I and VAX are trademarks of Digital Equipment Corporation

#### BENEFITS FOR YOUR USERS. BENEFITS FOR YOU.

The benefits you and your customers get by incorporating Digital's networking capabilities are virtually unlimited.

First of all, your systems can incorporate recognized industry standards. Such as Ethernet (IEEE 802.3 specification), X.25, and others.

In addition, our growing set of network-based products, including a distributed database system, allow your single systems to easily grow into networks. Your applications can access remote data and other resources transparently, with no extra development required.

This means that, with Digital, your systems are in an excellent position to be widely used in your customers' computing environments.

Your products need to communicate with equipment from different vendors. Ethernet was designed with this fact in mind. Today, Ethernet-based networks are proliferating across all application segments – such as CAD/ CAM, ATE, factory automation and medical applications.

Digital's networking systems allow Ethernet to be part of a single-source solution for your OEM installations. And DECnet gateways provide highly functional links to other non-Digital communications environments.

In short, DNA and Digital's products do the most to ensure that your systems will fit in with both new and existing networks.

#### WE'LL BACK YOU WITH TRAINING AND SUPPORT.

If you're already a Digital OEM, you know the advantages of Digital training and support. It's second to none in the industry.

We can give you the skills to configure, market, install and service local and wide area networks effectively. We'll help you make the most of our networking products in your systems.

Digital representatives are

available for pre-sales consultation and installation assistance. And our world-wide service organization can provide all the on-site network maintenance your customers require.

#### BEST ENGINEERED MEANS ENGINEERED TO A PLAN.

The communications systems implemented as part of Digital Network Architecture, like all Digital hardware and software products, are engineered to conform to an overall computing strategy. This means our systems are engineered to work together easily and expand economically.

Every system we make – from the Professional<sup>™</sup> 300 Series workstations, to our MicroVAX I<sup>™</sup> supermicro, to our high-end VAX<sup>™</sup> computing systems – can cooperate using DECnet software. Only Digital provides you with a single, integrated computing strategy, from chips to 32-bit systems, and direct from desktop to data center.

For more information about how you can make networking

from Digital part of your product line, send in the coupon below or contact your Digital Sales Representative or a Digital Authorized Industrial Distributor. Or call 1-800-848-4400, ext. 139.

- Please send more information about

Digital Network Architecture and

DECnet

- I'd like the whole story about OEM networking opportunities with Digital. Please have your representative call today.

| Name      |     |        |

|-----------|-----|--------|

| Title     |     |        |

| Company   |     |        |

| Address   |     |        |

| City      |     |        |

| State     | Zip |        |

| Telephone | Ext | - This |

Send to: Digital Equipment Corporation, 77 Reed Road, HL02-1/E10, Hudson, MA 01749.

#### THE BEST ENGINEERED COMPUTERS IN THE WORLD.

## **DIGITAL DESIGN**

JANUARY 1985 VOL. 15 NO. 1

**High-end Minis**

## DEPARTMENTS

- Peripherals / Electroluminescent Development Pays Off In Thinner Commercial Flat Panel Display

- CAD / Test Equipment Manufacturers Unite With Workstation Vendors

- 4 **Communications** / Options For Implementing LAN Protocols Before Standards Gel

- Graphics / A Graphics Architecture For Apollo's Workstations • Dedicated Image Processing Chip Provides Low Parts Count And Greater Functionality

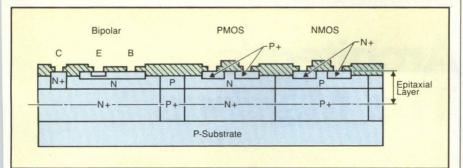

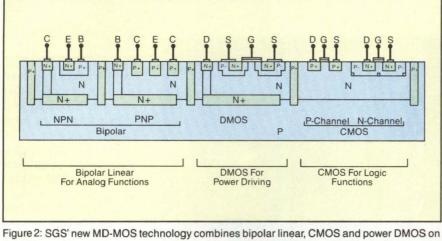

- ICs / Multiple Technologies Merge Onto One IC

- Market Trends / The Rise Of Korean Semiconductor Imports

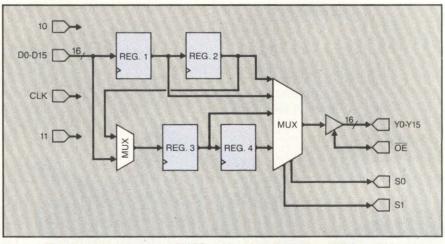

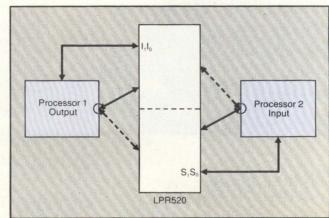

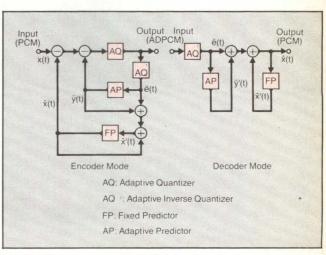

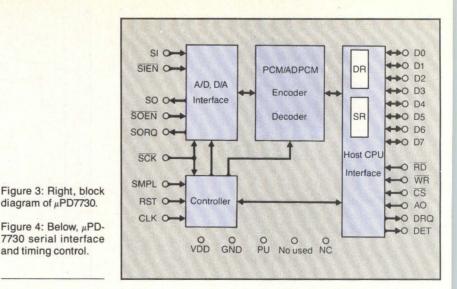

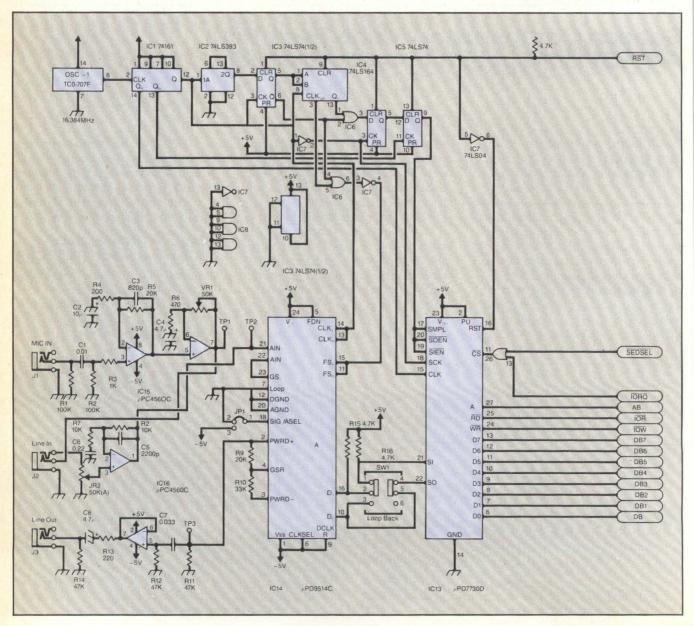

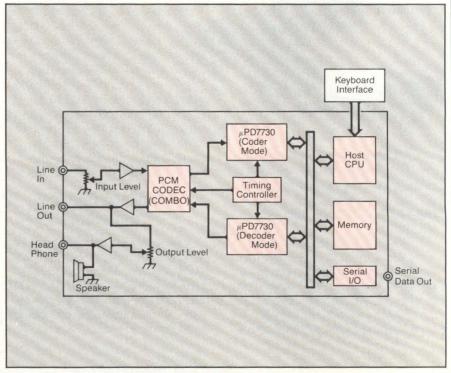

- Applications Notebook / 16-Bit CMOS Pipeline Register Replaces Multiple Circuits In DSP Delay Functions • Speech Compression Made Easy With An ADPCM Speech Encoder/Decoder

- **Reader Service Publisher's Comment** 81 8 **Editor's Comment New Products** 14 98 **New Literature** Update 105 16 Washington Report 108 Calendar 18 **Product Index Advertiser Index** 108 80

Published monthly thirteen times a year with two issues in November. Copyright 1985 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215, Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, Berkshire Common, Pittsfield, MA 01201 ISSN 0147-9245.

68

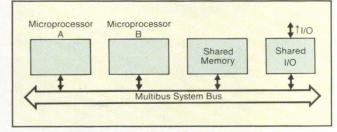

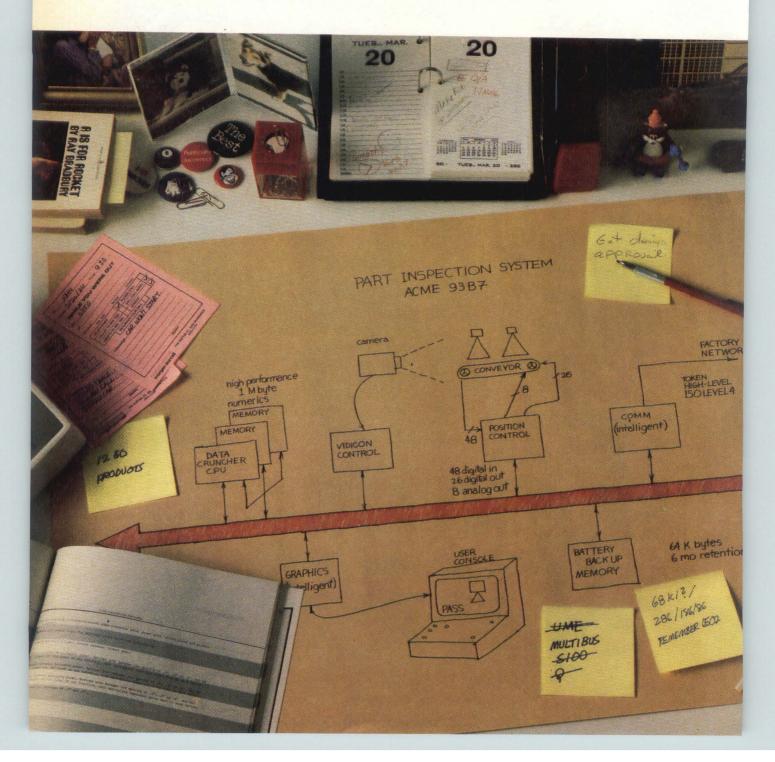

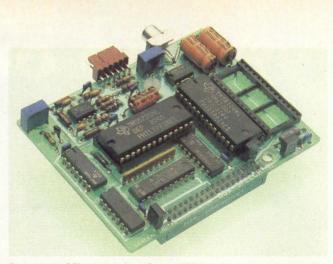

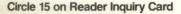

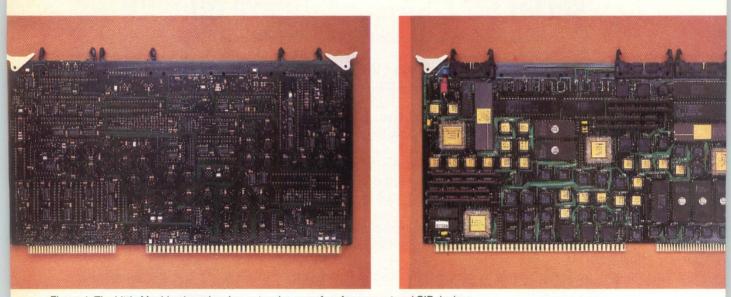

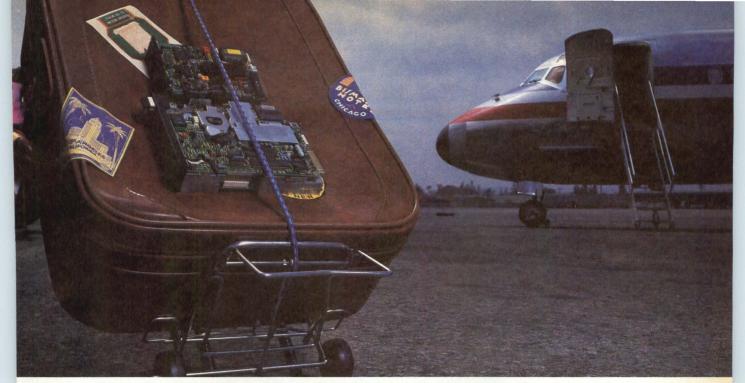

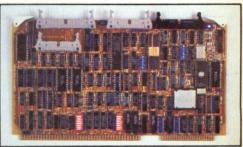

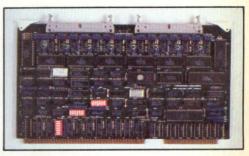

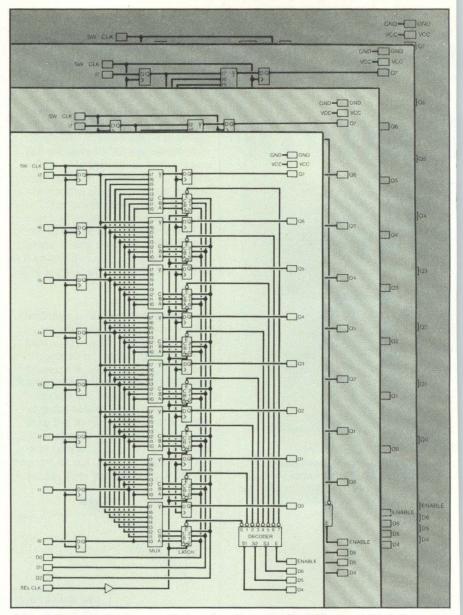

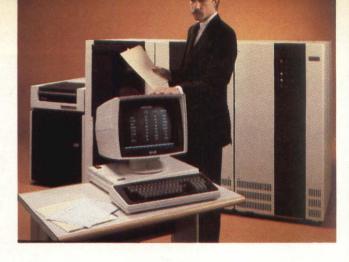

32 Systems Architect's Guide The Multibus retains its lead in the OEM board business.

## TABLE OF CONTENTS

### FEATURES

COURTESY ZENDEX CORP

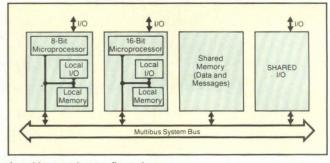

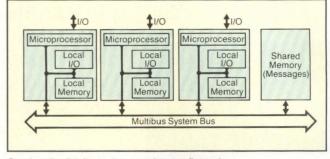

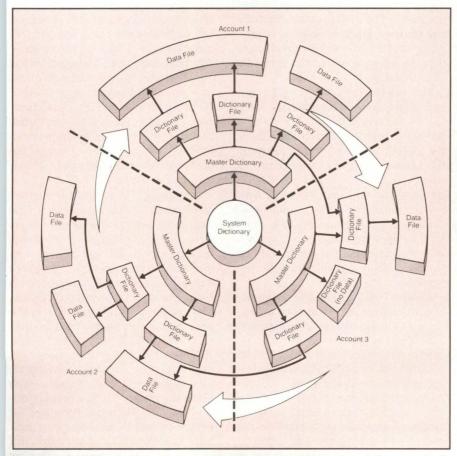

#### Systems Architect's Guide To The Multibus

by Dave Wilson

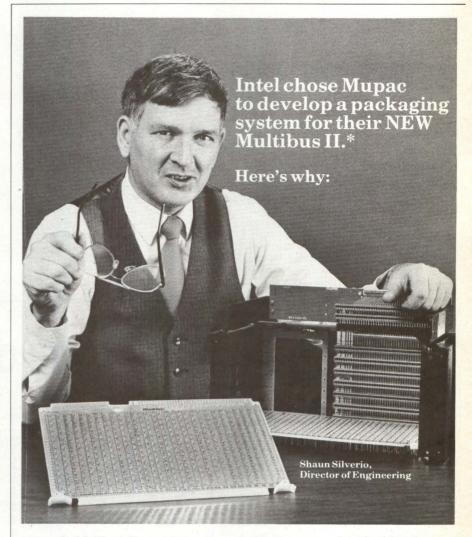

The Multibus marketplace continues to grow rapidly with currently over 200 vendors of products available to the systems integrator. This growth helps the Multibus retain its lead as the most popular bus in the OEM market today.

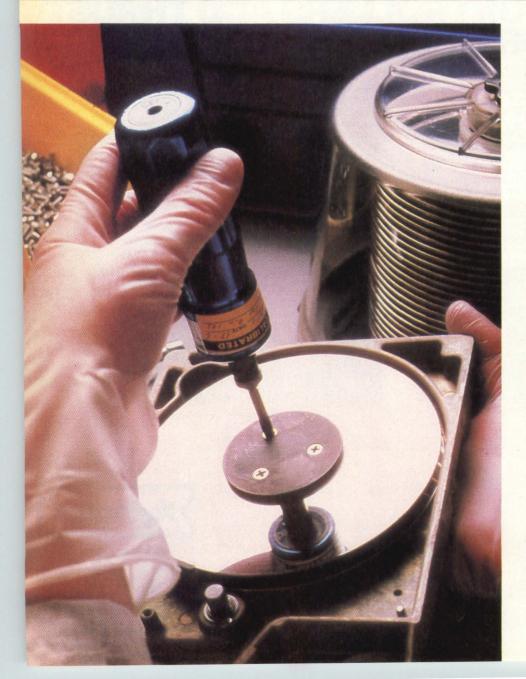

Making The Most Of 51/4" Winchester Drives For Improving System Performance by Julie Pingry

In choosing a disk drive, cost, reliability, quantity availability, technological merit and supplier reliability must be balanced and traded off against each other.

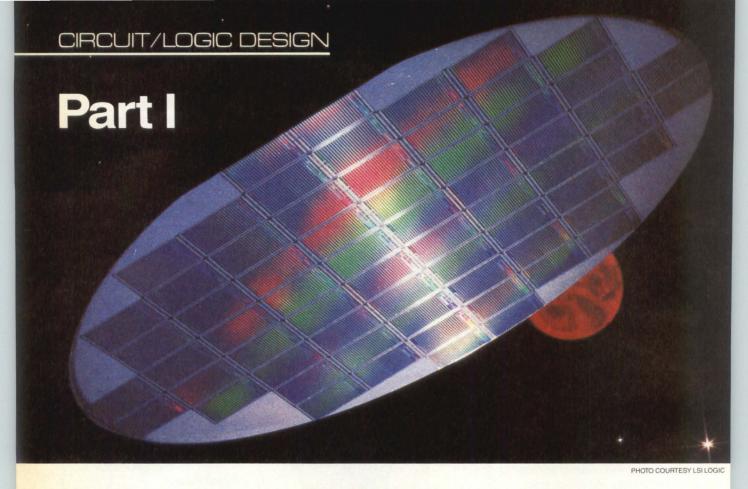

#### Unlocking The Mysteries Of Gate Array Design, Part I

by Ronald Collett

In this three part series, *Digital Design* moves into the design lab to uncover the issues behind workstations and gate array design.

#### Design Options Increase For Users Of 256K Dynamic RAMs

by Brita Meng

The new generation of 256K DRAMs is not only ideal for mainframe applications, but also for applications such as graphics systems, workstations, portable computers and microcomputers.

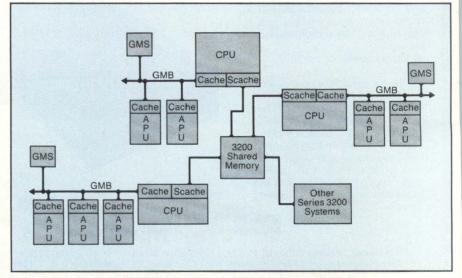

#### **High-End Minis Forge New Application Areas**

#### by Mary Rose Hanrahan

The advent of semiconductor memory and LSI circuitry has added to the minicomputer boom by allowing faster manipulation, greater accuracy, smaller size and reduced cost.

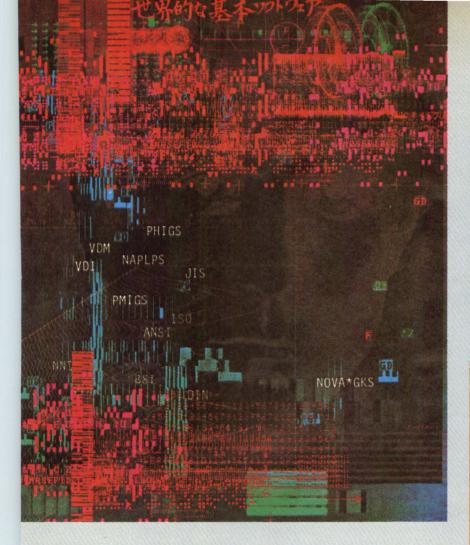

#### **Operating Systems For Micros – Too Much For Too Little?**

#### by Gregory MacNicol

Today's operating systems require application programs to interact with graphics, light pens, touch screens, mice, communications protocols, multiple file systems and graphics standards. The problem quickly becomes an issue of compromise.

#### ON THE COVER

The options available to the systems architect when implementing a Multibus system are now even greater. As newer technologies, such as surface mount devices and SIPs find their way onto boards, the Multibus will meet market demands for greater functionality at lower cost. Photo courtesy Intel Corp.

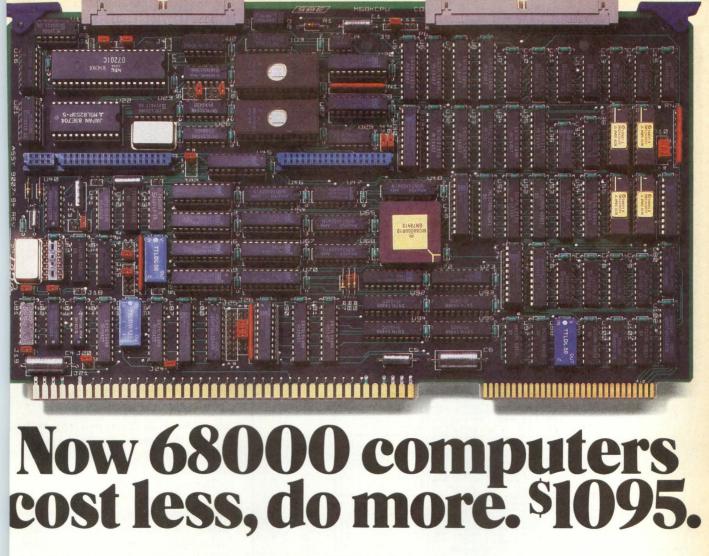

# FORCE COMPUTERS System 68000 VMEbus

## Single board solutions for 16/32 bit "open systems" in industrial, business, and scientific environments

If your application requires advanced technology available in production quantities if quality, reliability, and price/performance ratio are the major criteria for supplier selection – then compare our product portfolio with other alternatives.

- Three CPU's for most applications from intelligent I/O controllers to multiuser/ multitasking environments with powerful UNIX\* or real time operating software PDOS\* and up to 1M byte of on-board memory: CPU-1B, CPU-2, CPU-3.

- Two DRAM Boards: 512KB and 2MB; two SRAM Boards: 128KB and 512KB. RAM/ROM Board: 512KB (max.); DRAM-1, DRAM-2, SRAM-1/2, RR-1/S/E

- Mass memory interface boards with either direct control of up to seven drives (WFC-1) or intelligent VMEbus interface to SASIbus with DMAC (SASI-1).

- Six-channel serial I/O board with Multi-Protocol-Communications-Controller (SIO-1).

- 32-channel parallel I/O boards either optically isolated (1000V) with DMAC (OPIO-1) or TTL-level with 64 mA drive capability signals (PIO-1).

- Intelligent high resolution graphics subsystem (master/slave) with resolution of 1024 x 1024 pixels and up to 12 bits of pixel depth. Powerful graphics operation through local 68000 MPU in parallel with 7220 graphics controller(s) GDC-1M/1S.

- Winchester/Floppy drive modules with up to 80M bytes: WFMOD-20/80.

- Auxiliaries: Backplanes, chassis, power supplies.

- A variety of Software Products, e.g.:

PDOS\* Real-Time, Multi-Tasking, with Basic interpreter, Pascal, Fortran 77, and C Compilers.

- COHERENT\* UNIX\* V.7 compatible with C Compiler, Pascal and Fortran 77 in preparation.

- UNIX\* System V, Multi-User, Multi-Tasking.

- In development: memory boards with byte parity and 32 bit addressing; dedicated LAN-Controller; high performance communication I/O.

Supported by a worldwide network of distributors and representatives, FORCE Computers is recognized by its customers (and competitors) as the leading supplier of 68000/VMEbus board products.

\*PDOS is a trademark of Eyring Research, COHERENT is a trademark of Mark Williams Co., UNIX is a trademark of AT&T.

Consider, compare, and contact: FORCE COMPUTERS, INC.

# READER INVOLVEMENT

A recent issue of *Business Marketing* featured an editorial entitled "Journalism Close To Your Wallets." The question was asked, "Can business/industrial advertisers simply sit back, offering nothing more than good wishes to the foundation, and enjoy its long-term benefits?"

The author answered his own question by saying: "We think not. Advertisers should support vigorous, high-quality trade journalism by limiting buys to

Jim DiFilippo, Publisher of *Digital Design* (second from left) presents a Sony Watchman to Bill Schilp, Sr. Member of Technical Staff, RCA Corp. (Somerville, NJ). Mr. Schilp was the winner, randomly selected from those responding to a recent *Digital Design* Benchmark Study. Also pictured are (far left) David Wilson, Executive Editor, *Digital Design* and (far right) Dale Ludlum, Public Relations Director, RCA Corp.

publications that really earn reader involvement. Buying the best editorial vehicles serving a market is, clearly and simply, good business sense.

"Instead, however, advertisers buy publications in the same cavalier way they buy direct mail lists and postcard decks. Or they make a snap buy of the top-selling book in the field, or the one that the media rep claims has the most circulation among potential buyers. But all this ignores readership."

Reader involvement is a vital ingredient for the success and value of any publication. You, the readers of *Digital Design*, have shown a great deal of involvement. This is evidenced by the tremendous response we receive from our bound-in studies, our editorial benchmark study and other research surveys that we've conducted during the past year.

Surveys and studies can be a detriment rather than a help if they're used simply to guide action. Reliance upon them is a sure-fire way to become followers rather than leaders. The editors of *Digital Design* agressively research a range of topics. On the basis of information gathered from competing manfacturers, they objectively analyze technologies and products. There are no followers here.

At *Digital Design*, we realize that each of you are faced with a number of design choices in your day-to-day activities. The appreciation that these design choices exist is what makes *Digital Design* unique to the marketplace. We feel that to serve our readership, the editorial content should focus on addressing the design issues of the present and future.

Your input in all areas of research has provided the editorial staff with vital information and direction in addressing your needs. In addition to written research, we recently assembled several of you at a round table and conducted a reader focus group. We will continue to enlist your support and involvement in every way possible. Without it, we have no purpose to serve.

The new year is upon us. What we will offer you in 1985 is the most comprehensive editorial package of any magazine in the marketplace. Our focus will continue to address the issues of systems architecture, integration and applications. Our scope will discuss these issues at the IC, board and systems level. Within each of these categories – chip, board and box – you are faced with options. We will help you explore these options.

Publishing today demands flexibility. But flexibility and adaptability must not be achieved at the cost of personality. A publication must attain and project a consistent personality or each issue becomes a disparate miscellany within covers bearing the same title. *Digital Design*'s personality stems from a consistent, readily recognized editorial approach. Without it, continuity of attention and interest – and reader loyalty – are lost because the competition for attention from trade publications has never been greater.

I look for your continued involvement with *Digital Design*. Your involvement and our commitment will allow us to provide you with the most complete magazine in the industry—one that you cannot wait to get your hands on month after month.

Best personal regards, James R. DiFilippo, Publisher

## DIGITAL DESIGN

| SYSTEMS ARCHITECTURE, INTE                        | GRATION AND APPLICATIONS                                                                           |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Publisher                                         | James R. DiFilippo                                                                                 |

| Editor-in-Chief                                   | John Bond                                                                                          |

| Executive Editor                                  | Dave Wilson                                                                                        |

| Managing Editor                                   | Debra A. Lambert                                                                                   |

| Senior Editor/Directory E                         | ditor Julie Pingry                                                                                 |

| Senior Technical Editor                           | Ronald E. Collett                                                                                  |

| West Coast Technical<br>Editor (408) 356-0405     | Gregory MacNicol                                                                                   |

| West Coast Technical<br>Editor (408) 356-0405     | Joe Aseo                                                                                           |

| Associate Editor                                  | Mary Rose Hanrahan                                                                                 |

| Technical Editor                                  | Brita Meng                                                                                         |

| Copy Editors                                      | Sherri Mack<br>Winnie Jenkins Rubino                                                               |

| Editorial Assistant/<br>Associate Directory Edito | or Terri Lamneck                                                                                   |

| International<br>Electronics Editor               | Ron Neale                                                                                          |

| Contributing Editor<br>Peripherals                | Bob Hirshon                                                                                        |

| Washington Corresponde                            | ent Anne Armstrong                                                                                 |

| Production Manager                                | Paul Dadarria                                                                                      |

| Art Director                                      | Maureen Bernardini                                                                                 |

| Advertising Production M                          | lanager Martha Watjen                                                                              |

| Graphics Supervisor                               | William Manning Jr.                                                                                |

| Production/Graphics                               | Don Schaaf<br>Paul Christo                                                                         |

| Marketing Director                                | Charlotte King                                                                                     |

| Promotion Manager                                 | Elaine Bull                                                                                        |

| Marketing Assistant                               | Jamie Rose                                                                                         |

| Research Carolyn V                                | Nulfsberg, Peter Micheli                                                                           |

| <b>Circulation Director</b>                       | Hugh J. Dowling                                                                                    |

| <b>Circulation Supervisor</b>                     | Maggie Hayes-Miville                                                                               |

| Circulation Staff M                               | iriam Hlister, Betty Papa                                                                          |

| Reader Service (413) 499                          | -2550 Rose Wetherell                                                                               |

| Direct Mail                                       | Deborah Goldstein                                                                                  |

| Executive Administrator                           | Suzanne Levecque                                                                                   |

| General Administration                            | Karen Melanson<br>Nancy Deveau<br>Deanna Richardson<br>Debra James<br>Karen Bowman<br>Sharon Lembo |

President Ronald W. Evans

#### **Advertising Sales**

Northeast: Terry L. Willins (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic/Southeast: Sharon Greenberg (In PA) (215) 592-1895, (Outside PA) 800-223-7110, 703A South Street, Philadelphia, PA 19147

Midwest, South Central: Hank Bean, Rob Robinson (312) 794-1515, Edens East Office Center, 6200 N. Hiawatha, Suite 215, Chicago, IL 60646

Western Regional Sales Manager: Ralph Petersen Northwest: Ralph Petersen, Carole Sacino, (408) 356-0405, 15951 Los Gatos Blvd., Suite 7, Los Gatos, CA 95030

Southwest: Mike Prewitt, Joanne Gillis (714) 851-8550, 2041 Business Center Dr., Suite 206, Irvine, CA 92715

National Postcard Sales: Jon Binder (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

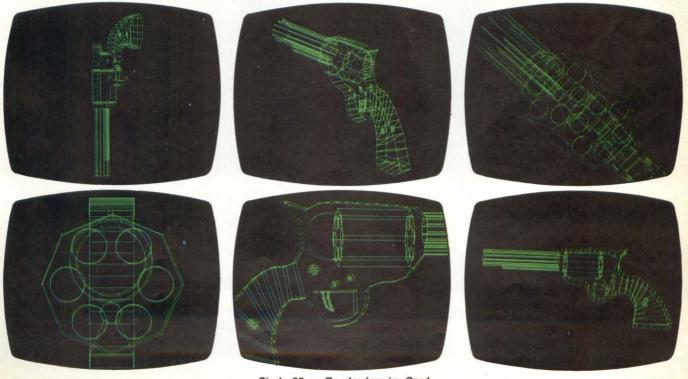

## The Lundy UltraGraf<sup>®</sup> is absolutely the fastest draw in the West or anywhere else.

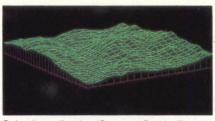

This is the fastest, most intelligent 3-D computer graphics workstation available. The superlatives would seem to indicate a high price, too. But the Lundy UltraGraf workstation is surprisingly low cost considering its unmatched performance features.

At Lundy we don't develop technology for its own sake; we develop it to meet your needs. In the case of 3-D computer graphics workstations, you needed more speed, higher IQ, larger display and easier operation. UltraGraf delivers all four.

## The Lundy UltraGraf is first when it comes to speed and IQ.

Keys to UltraGraf's instant response are a high speed microcomputer and a high resolution vector display, both developed by Lundy.

Besides these features, we've designed more intelligence into the workstation, so UltraGraf places fewer demands on your host computer.

The result is unmatched interaction while freeing up your host computer to concentrate on other operations.

## $19 \times 15$ inches sets a new screen standard.

UltraGrafs 21-inch CRT has the largest viewing area— $19 \times 15$  inches—in the industry. Fast vector drawing and mini-

Lundy UltraGraf sets 3-dimensional standards.

mum operator time produce easy-toread, flicker-free images. Spot size is only one ten thousandths of an inch, which produces remarkable crispness and clarity.

Furthermore, UltraGraf is easier to use. You send a picture only once, instead of resending over and over as with many other systems. And you have local storage of all control functions for the interactive input devices. This provides maximum input flexibility, with minimum keyboarding.

## Lundy helps you see more in graphics.

When you take a close look at our graphics terminals, service, support, software, systems capability, enhancements—and our company—you'll understand why Lundy can help you see more in graphics now and in the long term.

For more information about our 3-D UltraGraf, or other CAD/CAM products, write Lundy Electronics & Systems, Inc., Glen Head, New York 11545, or call: (516) 671-9000.

Get the draw on sluggish productivity with Lundy's UltraGraf. Shown here are six views of a six shooter generated in just a matter of seconds.

Circle 55 on Reader Inquiry Card

#### EDITORIAL AND SALES OFFICES Digital Design, 1050 Commonwealth Avenue, Boston, MA 02215, Telephone: (617) 232-5470

#### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215, (617) 232-5470. Brian Rowbotham, Chairman; Ronald W. Evans, President; Charles Benz, Vice President.

#### **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 2 Park Avenue, New York, NY 10016 (212) 340-9700. The following is a list of conferences produced by the Expositions Group:

ATE West CADCON West ATE Northwest ATE East CADCON East ATE Central CADCON Central

In addition to Digital Design, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronic Imaging • Electronics Test • Computer & Electronics Marketing

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronics Times • What's New in Electronics • What's New in Computing • Business Computing and Communications • Communications Systems Worldwide.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral manufacturers, integrating OEM's and commercial end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

### ₩авр ВРА

#### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

Circulation Department, DIGITAL DESIGN, Berkshire Common, Pittsfield, MA 01201

Subscription rates: non-qualified subscribers (US and Canada) – \$35/yr; foreign – surface mail – \$45; air mail – \$70. Single copies – \$4.

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by Morgan-Grampian Publishing Co. for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$2.00 per copy, plus \$.25 per page is paid directly to CCC, 21 Congress St., Salem, MA 01970. 0147-9245/84 \$2.00 + \$.25.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

JANUARY 1985 I DIGITAL DESIGN

**MALHEURIKON**

Minibox-

C) 1984

Heurikon's new multiuser, multitasking work-

station—puts the power of the MC 68000/68010 microprocessor (8 or 10 Mhz) and the flexibility of UNIX all in 1.5 square feet of desk space. Designed with the OEM in mind, Minibox gives you these features and capabilities you've been searching for: Electronic mail • Interprocess communications (IPC) • Fully integrated streaming tape drive, up to 280 MB of Winchester storage • 1 MB floppy drive • UNIX System V or III • Ethernet (TCP/IP) for fast expansion and networking • Floating Point Processor • CPM Shell for CP/M-to-UNIX link • Hotline customer support.

UNIX is a trademark of Bell Telephone. Unity is a trademark of Unity. Ethernet is a trademark of Xerox Corp. Minibox is a trademark of Heurikon Corp.

**Circle 11 on Reader Inquiry Card**

REPRINTS

**DIGITAL DESIGN** will reprint any article from past or present issues. Reprints are custom printed. Minimum order: 1,000 copies. Purchase order or letter of authorization required.

Allow one month from receipt of order for delivery, unless previously arranged and confirmed.

Advertisements alone can also be reprinted. Call (617) 232-5470, and ask for reprints.

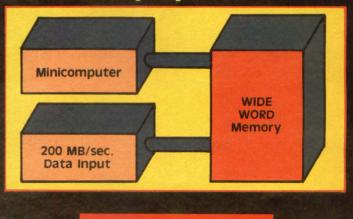

200 MB/second!

## World's Fastest Bulk Memory System

It's true. Dataram's WIDE WORD memory system delivers an incredible data rate of 200 MB/sec! Achieved by utilizing 80 or 160 bits per word and four-way interleaving.

Much faster than even the fastest minicomputers can handle...but not too fast for your real-time applications, image processing, array processing or data acquisition needs.

Multi-port capability enables you to bring WIDE WORD speed to your host minicomputer. Simply connect one port to your high-speed input; the other to your mini.

Our library of dedicated interfaces allows you to run with Digital Equipment, Data General, Ampex, Control Data, CSPI, Honeywell, Intel (MULTIBUS), MODCOMP, Motorola (VERSAbus), Perkin-Elmer, ROLM, and SEL. And, possibly even more importantly, we can work with you to develop a custom WIDE WORD interface.

WIDE WORD, 128 MB of high-performance memory in a compact 15%4" system. Word lengths up to 160 bits. And, of course, a data rate of 200 MB/second.

Our new WIDE WORD brochure will tell you more. And you can have it at no charge by circling the Reader Response Number or calling us at (609) 799-0071.

WIDE WORD is a trademark of Dataram Corporation. MULTIBUS is a registered trademark of Intel Corporation. VERSAbus is a trademark of Motorola, Inc

TM

Princeton Road 🗆 Cranbury, NJ 08512 🗆 (609) 799-0071 🗆 TWX: 510-685-2542

DATARAM

# **MEET THE STRONGEST**

here's a lot more to a Fujitsu gate array than glass, gold, and

aluminum; it's the human element that really sets our product apart.

When you order a Fujitsu gate array, you become part of a team. You work through your objectives with a highly-skilled design engineer who knows silicon the way you know logic.

That way, you combine your expertise with ours to shape the subtleties of silicon into product advantages. Instead of glitches.

This approach is a good part of the reason that since 1974, Fujitsu has produced more than 3,000 gate array designs – and every one of them has worked according to plan.

Our engineers can help you execute designs in a complete range of technologies – CMOS, TTL, ECL – you name it. Because the Fujitsu team's incredible versatility comes from a solid background within each of those technologies.

That's how you get numbers like these:

|              | CM             | 10S                 |           |

|--------------|----------------|---------------------|-----------|

| TECHNOLOGY   | GATE<br>LENGTH | PROP DELAY<br>TIME* | GATE      |

| STD CMOS     | 3.6 µ          | 7.0 ns              | 700-3900  |

| H CMOS       | 2.8 µ          | 5.0 ns              | 440-3900  |

| VH CMOS      | 2.3 μ          | 2.5 ns              | 2600-8000 |

| *2-Input NAN | D Gate, F      | /O = 2              |           |

|             | BIPO       | LAR      |                                  |

|-------------|------------|----------|----------------------------------|

| TECHNOLOGY  | PROP DELAY | GATE     | POWER<br>DISSIPATION<br>PER GATE |

| LSTTL       | 1.8 ns     | 500      | 2.3 mW                           |

| LSTTL       | 1.9 ns     | 240-1100 | 0.8 mW                           |

| LSTTL       | 0.95 ns    | 2000     | 0.65 mW                          |

| *3.Input NA | ND Gate E  | 0 = 1    |                                  |

\*3-Input NAND Gate, F/O = 1

# TEAM ON THE CIRCUIT.

equipped Fujitsu Gate Array Design Centers in the U.S.; in Boston, Dallas, and Santa Clara. There's a sophisticated telecommunications network between centers, and high-speed leased-line and satellite communications with FMI host computers in Japan. All that. and a firstclass gate array design team, too. With you as star player.

There are now three fully

Call the FMI Design Center nearest you. We'll show you how to get our team on your circuit.

Boston Design Center 57 Wells Avenue Newton Centre Massachusetts 02159 (617) 964-7080

> Santa Clara Design Center 3320 Scott Boulevard Santa Clara, CA 95051 (408) 727-1700

> > Dallas Design Center 1101 East Arapaho Road Suite 225 Richardson, TX 75081 (214) 669-1616

Literature request line: 800-556-1234 (ext. 82) In California, 800-441-2345

FUJITSU MICROELECTRONICS, INC. Technology that works 3320 Scott Boulevard, Santa Clara, CA 95051 · (408) 727:1700

Circle 14 on Reader Inquiry Card

Three additions to the editorial staff of *Digital Design* have recently been made with the intent of providing our readers with an even greater perspective on the industry.

#### EDITOR'S COMMENT

eeping track of developments in the computer industry is no easy task for the systems architect or for an editor. Often a number of interrelated issues must be considered when conceiving and implementing a product. Most times, developments in one field cannot be viewed in isolation because they impact other areas of technology.

It was with this rationale in mind that the editors of *Digital Design* developed this year's editorial calendar. Five main subject areas will be covered in each issue; they relate to overall systems architecture, integration of peripheral devices into systems and applications of ICs, board level products and systems. In addition, our advanced technology series will examine those developments just starting to emerge from the laboratories in order to give our readers a feeling for what the future may hold.

To execute this task and still remain objective, *Digital Design* has been assembling a team of editors over the past two years who will be contributing heavily to this calendar. Today, we are the most comprehensive group of writers in the technical publishing field.

Over the past two years we have been given a charter to expose not only the options available to you but the problems you may encounter in your day-to-day work designing OEM equipment. Recently, three additions to the editorial staff have been made with the sole intent of providing even greater in-depth industry coverage. They bring to the magazine an experience that goes beyond that of simply reporting upon issues that affect the industry. In some cases, our editors are evaluating products and using and testing some of the same equipment that you are.

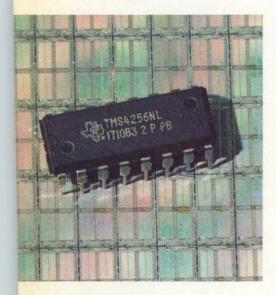

In November of last year, Brita Meng, our East Coast Technical Editor, joined *Digital Design* after completing a BSEE at Princeton University. This issue marks her first contribution to the magazine. In her article, "Design Options Increase For Users Of 256K DRAMs," Brita examines the latest parts on the market, their organization and addressing modes – important considerations in choosing the right devices for a particular application.

With the continuing development in Silicon Valley, the recent addition of our second West Coast Technical Editor, Joe Aseo, will prove invaluable. Over the past year, Joe has been working at a leading IC house. Prior to that he was based in Los Angeles as the West Coast Editor for *Computer Design* where he specialized in the area of disk drive and related interfacing issues. Joe brings to the magazine a BS in communications and is currently working on a BSEE in Computer Science. He will be working out of our Los Gatos office in Northern California

and can be reached at (408)356-0405. He will join our other West Coast Technical Editor, Gregory MacNicol.

For his part, Gregory has set up a lab where he plans to evaluate many new product introductions in order to bring a greater level of objectivity to his writing. Gregory's involvement with the industry does not stop there. His enthusiasm for the graphics business has led to his election to a chair for SIG-GRAPH and the SIGGRAPH conference in 1985. His position there will be to accept and choose the material for the art, technical and industry slide sets.

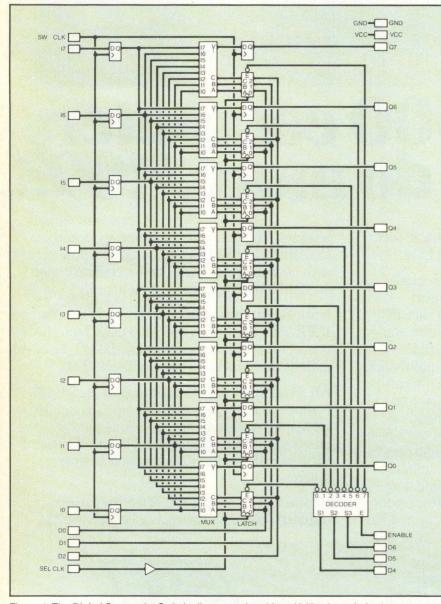

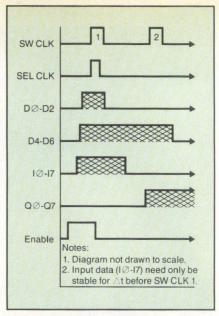

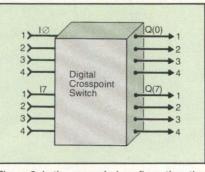

Closer to home, Ron Collett, our Senior Technical Editor, has started his work on the design of a gate array. In this issue, he begins the first of a three part series that will trace the design from start to finish. Ron will be using a Valid Logic workstation and the part (a cross point switch designed by Datacube) will be produced by LSI Logic. Those readers considering gate array design will gain considerable insight by reading a series that unveils the pros and cons of the semi-custom approach. Others who have already gone through the process using different vendor equipment may like to discuss their experience with Ron.

One important comment that we consistently hear from our readers relates to the objectivity of contributed articles to the magazine. Realizing that fact, Senior Editor Julie Pingry, in charge of the Applications Notebook, is making a push to solicit features from users, not just manufacturers of the latest ICs. Those readers who would like to contribute to that section of the magazine should call Julie in the Boston office to discuss their ideas.

Finally, it is my pleasure to announce that John Bond has been appointed to the position of Editor-in-Chief of *Digital Design*. For the past two years, John has been Senior Editor at *Computer Design*. John brings to his position extensive industry experience. He has held positions at General Dynamics, Texas Instruments and Digital Equipment Corp. as well as several leading trade journals. On behalf of the editors of *Digital Design*, I welcome John in heading up a team of individuals whose output is second to none.

David Wilson, Executive Editor

## D.A.T.A. BOOKS<sup>®</sup> are like having 18 researchers at your fingertips...

## but much easier to manage.

If you're an electronics engineer, chances are you've already heard about D.A.T.A.BOOKS. You may even be among the thousands of engineers who use one or more of our 25-plus publications daily.

Whatever information you need for your projects, D.A.T.A.BOOKS have it. Electrical specs...logic drawings... package design...device replacement...manufacturing sources... and more. D.A.T.A.BOOKS reference over 852,000 types of products from nearly 1,000 major manufacturers worldwide.

Our information is complete, accurate and up to date because we contact these manufacturers continually to get the technical data you need to complete your project faster and more efficiently. We know the information you require because we've been in the business since 1956.

Inside D.A.T.A.BOOKS, you'll find easy to use standardized performance specifications, block drawings, alternate sources of supply, functional equivalence data, manufacturer locations and more.

You'll save time and money by contacting *only* those manufacturers you really need to for the best price and availability.

Your time is much too valuable to waste calling manufacturers and paging through out-of-date catalogs when you can have D.A.T.A.BOOKS do it for you!

Publications include – Integrated Circuits: Digital ICs, Linear ICs, Interface ICs, Memory ICs, IC Functional Equivalence Guide, Microprocessor ICs, Microcomputer Systems, Modules/Hybrids and Audio/Video

#### Circle 70 on Reader Inquiry Card

ICs. **Discrete Devices:** Transistors, Diodes and Thyristors. **Special Devices and Directories:** Optoelectronics, Power Semiconductors, Power Supplies, Microwave, Master Type Locator, Microprocessor Software and Applications Notes. **Discontinued Devices:** Digital and Audio/Video, Interface and Memory, Linear, Transistors, Diodes, Thyristors, Optoelectronics, Microwave and Type Locator.

Call or write us today. Or contact the D.A.T.A. BOOKS representative nearest you.

Toll-Free (800) 854-7030 Inside CA, call (800) 421-0159

A., I

P.O. Box 26875 9889 Willow Creek Road San Diego, CA 92126

D.A.T.A. BOOKS Representative Listings: **EAST**: Motion Engineering, MA (617) 485-2144; Astrorep, NY (516) 422-2500, NJ (201) 826-8050; Motion Technology, DE/MD/DC/VA (800) 482-6318; Stegman Blaine, PA/WVA (513) 729-1969. **SOUTH:** Motion Technology, NC (800) 532-6849, TN/SC/GA/AL/FL (800) 482-6318; Blackburn Associates, TX/LA/AR/OK (214) 692-8885, TX (713) 463-1354. **MIDWEST**: Stegman Blaine, OH/KY (513) 890-7975, (216) 871-0520, (513) 729-1969; Enco Marketing, MI (313) 642-0203; JHS Associates, IL/IN/WI (312) 741-9070; J.F. Gleeson & Associates, IA/KS/MO/NE (913) 362-4422. **WEST**: System Sales of Arizona, Inc., AZ (602) 829-9338; SSA Inc. of New Mexico, NM (505) 881-8877; Dynatech, CO/UT (303) 773-2830; Applied Controls Northwest, WA (206) 775-2999, (509) 922-1762, OR (503) 257-7408; Leddy Associates, No. CA/NV/HI (415) 969-6313; Varigon Associates, So. CA (213) 322-1120, (714) 855-0233, (619) 576-0100. **CANADA**: Tech-Trek, (416) 674-1717, (604) 273-1800. **INTERNATIONAL**: (619) 578-7600 or TLX: 910530606.

## UPDATE

#### Qume, AT&T Printer Contract

AT&T Information Systems has selected daisywheel printers from Qume Corp. to be integrated with their new business computers. The contract calls for deliveries of Qume's Sprint 11/55 Plus letter-quality business printers and accessories for AT&T's 3B Series of business computers and PC6300 Personal Computer.

#### VTI, Lattice Cross License

VLSI Technology, Inc. (VTI) and Lattice Semiconductor Corp. signed a technology and product cross licensing agreement, under which VTI will receive alternate sourcing rights for very high performance EEPROMs, static RAMs and programmable logic devices currently in development by Lattice. In exchange, VTI will provide Lattice with wafer fabrication, assembly and test capacity, product engineering and equipment leasing support.

#### RCA Kicks Off JAN Gualification

A program to qualify 23 logic device types of the CD4000 "B" series for high reliability applications is underway at RCA Solid State. The JAN program will qualify the standard-product "B" series ICs to MIL-M-38510 Class B and Class S for inclusion on the Qualified Products List (QPL). It is expected that the logic devices will be on the QPL by 1985.

#### FutureNet, Augat Link

FutureNet DASH

workstations can be used to directly link the electronic design engineer to the board level design and manufacturing services of Augat's Interconnection Systems Div. Information created on the workstation can be transmitted electronically to Augat's VAX computer systems for quick turnaround prototype fabrication of Wire-Wrap board. When additional production is required, the design engineer may choose to stay with Wire-Wrap, or to use the same FutureNet database to have Augat design, route, and fabricate boards.

#### DEC, Cullinet Development

Digital Equipment Corp. plans to integrate Cullinet Software Inc.'s Information Database (IDB) with its VAX family of computer systems. Under a development agreement, both companies will cooperate to enhance their respective information center and distributed database products in settings where Digital Equipment and IBM systems coexist. They also will cooperate to market existing products and develop new ones to improve communications and database interfaces between DEC's VAX/VMS-based family of management information products and those on IBM-based systems.

#### CD ROM Mastering System

**3M** Purchases

3M has purchased from North American Philips Corp. its Compact Disk Mastering facility for mastering of Compact Disk Read Only Memory (CD ROM) disks. Both companies will jointly support CD ROM as an industry standard for optical Read Only Memory disks. The purchase coincides with a 100,000square-foot expansion of 3M's optical media production facility in Wisconsin.

#### ITT Forms Multicomponents Division

ITT Components plans to expand into boardline electronic component distribution with the formation of a new division called ITT Multicomponents. The division will stock passive electromechanical and active components at the recently relocated and expanded headquarters in California.

#### Carnegie Selects Symbolics<sup>1</sup> Computing Systems

Symbolics, Inc., has sold 50 computing systems to Carnegie Group Inc. for use in artificial intelligence and other symbolic computing applications. Carnegie will use the systems for software development in two areas, PLUME and SRL+.

#### Intel Supplies Board-Level System

Intel Corp. will supply NetExpress Inc. with \$10 million in single-board computers and memory boards for a worldwide image-transfer service, providing its iSBC 286/10 single-board computer and its iSBC 010 CX memory board. The 286/10 computer is based on the Intel 80286, a high-performance 16-bit microprocessor. The service will allow worldwide distribution of text and images to be distributed through digital signals via satellite or land lines.

#### Motorola Acquires CTX International

Motorola, Inc. has acquired CTX International to become part of its New Enterprises organization. CTX develops and markets information systems and software for semiconductor manufacturing and related industries. The goal of New Enterprises is to build new businesses in emerging high-growth, high-technology industries.

#### Mostek offers IPI Operating Systems

Industrial Programming, Inc. will integrate Mostek Corp.'s 16-bit MK68000 and 8-bit MK3880 microcomputer systems with several versions of its realtime, multi-tasking MTOS operating system. Both companies will cooperate to offer design and development support so computer system integrators and designers, software developers, and end-users may use a single source for 16- and 8-bit microcomputer hardware and real-time software.

#### Remote LANs Interconnection

Vitalink Communications Corp. and Digital Equipment Corp. will cooperatively market TransLANs, a hardware/ software product that transparently connects LANs via satellites and/or terrestrial lines. TransLAN is designed to connect several Ethernet or IEEE 802.3 LANs so they appear as one large network. LAN information sent to remote sites is automatically forwarded across the digital transmission network in a datalink-layer relay that screens and forwards information to protect the LAN and transmission system from unnecessary traffic.

CHUMs solve shortages by replacing LSTTL, HC, HCT and other scarce parts.

Parameter

Gates

Bonding Pads

Output Drive

Frequency

Voltage Range

Suffering from acid indigestion

manufacturing problems?

caused by tough engineering or

Take CHUNS" for your tummy!

REGULAR AND EXTRA STRENGTH!

- CHUMs save money and power by replacing MMI PALS® and MMI HALS®.

- CHUMs save space on your PCB by consolidating "glue" logic onto a single chip

- CHUMs save time—prototype in 4 weeks—full production in 8 weeks.

CHUM stands for CMOS High-speed Universal Microarray. There are two products available: the CHUM-99 (22 pads), and the CHUM-180 (40 pads). Both have high-frequency performance, low power dissipa-CHUM SPECIFICATIONS tion, and a wide power-supply range (3-8 volts). CHUMs can help you in many ways. If you're hav-

ing trouble getting a standard CMOS or TTL part, we'll integrate it on a CHUM and deliver pin-compatible samples in four weeks. If you're facing production with expensive and power-consuming bipolar programmable logic arrays, send us your equations and we'll put them on a CHUM. If you've run out of PCB and still have some random logic left over, send us your schematic and we'll send you back a CHUM. And that's just a few ways CHUMs can help your indigestion.

So, if you're facing a problem that's standing between you and shipping product, give us a call at 408-279-2830. Chances are your friend in need will be a CHUM CHUM-180 indeed!

"The Fastest CMOS in the West"

MMI PALS® and MMI HALS® are registered trademarks of Monolithic Memories Inc.

TUMS® (which you will probably need if you don't use CHUMs) is a registered trademark of Norcliff Thayer Inc.

CHUMs<sup>™</sup> is a trademark of Universal Semiconductor Inc.

UNIVERSAL SEMICONDUCTOR INC.

CHUM-99

22

99

9 ma 25 MHz

3-8 Vdc

04 180

1925 Zanker Road, San Jose, CA 95112. 408-279-2830

Circle 17 on Reader Inquiry Card

# WASHINGTON

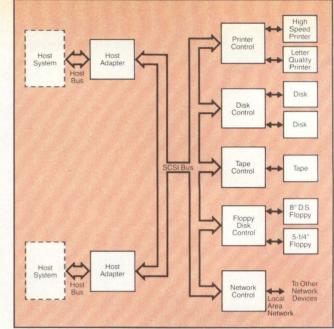

#### SCSI Standard Nearing End Of ANSI Approval Process

Racing to complete a new standard for hooking up intelligent peripherals to small computers before the industry bypasses the process and adopts one of its own, the American National Standards Institute's subcommittee, X3T9.2, has finished the second version of the 14th draft of the Small Computer Systems Interface standard and sent it out for the 4-month publication and public comment period.

An arduous task of reconciling many different ideas and needs, standards drafting frequently takes years to do properly—years in an industry that has become so fluid that a whole generation of equipment may last only two or three years.

"The market will not wait for the AN-SI standard," said William Burr, chairman of the subcommittee that has been working on the SCSI standard. Manufacturers will go ahead with products even without the standard, but it is better for customer confidence if the public knows that there are not going to be 10 different versions of products that will not work together, he told us. The proposed SCSI standard is based on a Shugart Corp. interface that was used in 1982 as a starting point for writing a standard to connect intelligent peripherals to small computers. but with the power and flexibility of the input/output channels found in large mainframe computers.

Since the interface can handle large amounts of data very quickly, the adoption of the standard is also expected to prompt greater use of VLSI chips in future computers and peripherals. Interface chips and disk controller chip sets that support the proposed SCSI standard have already hit the market, even though formal approval of the standard is six months to a year away.

"You can always tell when a standard is catching on," said Burr," "because the connector firms start showing up at meetings. At the last SCSI meeting, the connector houses were out in force."

Burr believes that most problems with the SCSI standard have been ironed out in committee and he does not foresee any serious opposition during the public comment period. One possible exception would be formulating standards for cache disk controllers, although Burr said that is likely to be handled in a supplementary document, rather than holding up the primary standard while it is written.

The SCSI is only one of 22 standards that are in the works at X3, which is the information processing committee of ANSI. Coordination and support for the work is handled by the Computer and Business Equipment Manufacturers Association, which acts as secretariat for the X3 committee. Other X3 subcommittees are working on a whole stream of intelligent peripheral interface standards that cover specific and generic command sets for a variety of storage devices, including optical and magnetic disks.

#### Signetics Chips Also Found With Testing Irregularities

Just as many contractors were beginning to finish the paperwork necessary to have shipments containing suspect TI chips resumed, the industry learned that similar source control drawing chips from Signetics also had testing irregularities. Signetics was reportedly a second source for TI chips and so many companies with systems that had just been cleared of problems with TI chips, found they were on hold again until the second problem could be resolved.

The Defense Logistics Agency outlined in its alert to prime government contractors that some 2,300 different Signetics semiconductor devices dated from January 1981 to the present could have been improperly tested. More than 250 contractors are said to be involved.

The embargoes of many weapons systems have created chaos in the industry and have prompted several trade associations, including the Aerospace Industries Association and the Electronics Industry Association, to look for solutions other than the stop shipment approach now employed by Defense.

An EIA spokesman told us it is the association's policy not to get involved in questions between buyer and supplier; however, the stopping of whole shipments in which there are suspect parts has become a big problem plaguing OEMs currently. "DOD is penalizing a lot of innocent people," he said. "We are trying to find a way to cope with the problem and avoid the disadvantages of stop shipments." Charged with the job of finding other solutions is a task force of industry experts, headed by Mike Michaelis of General Dynamics. At press time, no specific suggestions had been made public; however, the group has been meeting with Defense officials to discuss ways of handling suspect parts.

While negotiations are going on, most contractors have been working with Defense officials to get waivers for specific systems. Although the procedures being followed are up to each government agency, several contractors report that they have been able to get waivers on retesting TI chips if they can show that they performed 100% inspection tests on components before they were included in a larger system. Others have offered to warrant the system regardless of the chips in question.

It is too early to tell how great a financial impact the systems embargoes will have on the prime contractors. Sperry Corp., however, did cite the delay of defense shipments as one reason for a decline in profits in its quarterly statement. Texas Instruments-whose chip testing failures started the whole mess-reported a profit of almost \$86 million in the third quarter, ending Sept. 30. However, even the \$13 million loss in this quarter's figures that TI attributes to the chip testing problem looks good compared to the \$110 million loss in the third quarter a year ago as the company was getting out of the home computer business.

#### Defense Restricts Publication Of Technical Data

In a follow-up to a decision made more than a year ago, Secretary of Defense Caspar W. Weinberger has signed a directive (#5230.25) that restricts the publication of certain technical information and establishes a tiered system of data classification ranging from no release to full disclosure.

Exempted from the new regulations would be most academic and research centers conducting "fundamental research"; defense contractors, on the other hand, would be required to become certified to receive the unclassified, but "sensitive" data. Contractors would have to agree to protect the information and see that it is not released to anyone without DOD permission.

JANUARY 1985 DIGITAL DESIGN

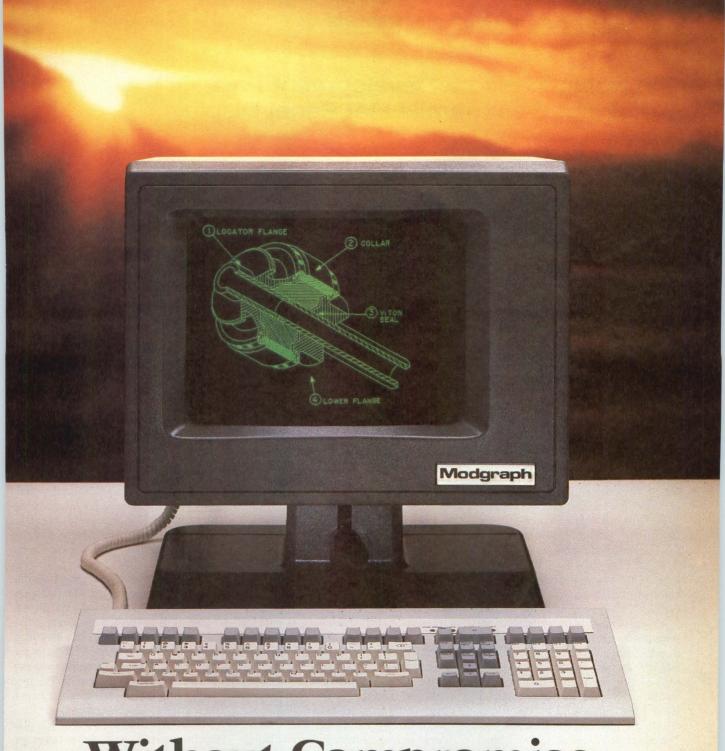

## Without Compromise. The Modgraph GX-1000.

1024 X 780 Resolution

4010/4014 Emulation

15 inch CRT

Write 74 on Reader Inquiry Card

☐ 132 Column Text Display

□ VT100/VT52 Emulation

□ \$2795

Modgraph, Inc., 1393 Main Street, Waltham, MA 02154 (617) 890-5764

4010/4014 are trademarks of Tektronix, Inc. + VT100/VT52 are trademarks of Digital Equipment Corporation + The Screen image is courtesy of Computervision Corporation

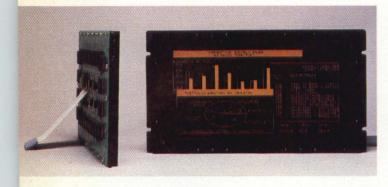

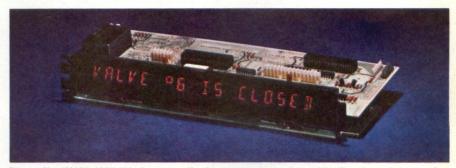

## Electroluminescent Development Pays Off In Thinner Commercial Flat Panel Display

The Planar EL6648 MX can display  $256 \times 512$ , though a total system is only 34'' thick and weighs 16 ounces.

lat panel displays have long been an area of great interest, particularly with the trends toward shrinking footprints and portable computers. But the expense of driver electronics and problems of resolution and viewability have largely prevented flat displays from penetrating the commercial market. The use of custom ICs and surface mount devices (SMD) has allowed Planar Systems (Beaverton, OR) to reduce the size of their electroluminescent (EL) display by 50%; the EL6648 MX is .75" deep  $\times$  5.7" high  $\times$  10.3" wide, including the driver and control electronics, bezel, frame and panel.

Though Planar is only one year old, their product is based on development begun in 1976. The firm was founded in 1983 by former Tektronix (Beverton, OR) employees when Tek decided it would not set up facilities to manufacture EL displays. Like their EL6648 M introduced last year, the EL6648 MX has a  $256 \times 512$  pixel matrix, for 80 columns and 25 rows using a 5  $\times$  7 matrix for characters. New drivers and insulators have improved reliability. Meanwhile, automation and increased quantity runs are improving the manufacturing process. The price of the new EL panel is \$775 in quantities of 1000, and it is available this month.

Other firms working on this resolution EL display are Sharp (Tokyo, Japan, with US offices in Paramus, NJ) and Lohja (Finland). Lohja has not yet shipped. Sharp's product is used in Grid System's portable computer, but the Japanese system uses five boards compared to the one board in Planar's new product.

Electroluminescence is only one technology for making flat panel displays. Efforts to make thinner CRTs cannot solve the problem of curvature. Liquid crystal (commonly used in watches and small clocks) and plasma displays make thin, flat displays. Plasma displays are high quality, but heavy; they require more power than is desirable for portable or smaller systems. Liquid crystal panels are non-emissive, so legibility depends on ambient light. In addition, they are relatively difficult to address. An advantage EL has over the other two is that it is solid state, ideal for harsh environments.

Liquid crystal technology is popular for small screens needed to relay only a few characters due to its extremely low power consumption and relatively low cost. Plasma displays are more easily enlarged than the others, so their cost may not prevent them from finding applications in large mainframe-level systems. An intermediate marketplace including mobile and harsh environments appears open for EL panels as they develop.

One aid to acceptance of the EL6648 MX may be that it is designed to work with CRT controllers. The board in the system converts a standard CRT controller's signals to signals needed by the flat display. For graphics, each pixel is individually addressable. The device requires 768 drivers (512  $\times$  256) which, until recently, was an expensive proposition. Planar uses Texas Instruments (Dallas, TX) drivers that now cost \$0.11 per line, compared to \$1.25 18 months ago.

In addition to the cost of drivers, EL

panels have suffered reliability problems due to a lack of uniformity in the glass insulator layer. A proprietary process for depositing the insulator has improved the efficiency and reliability of that layer greatly.

Since flat panel technology is often chosen to reduce size, the fact that the volume of this display is 5% that of a standard CRT with the same usable display size may prove critical. Fitting all of the electronics onto a single circuit board has allowed that size, a reduction in volume by half over the model they introduced last year. Surface mount devices and custom ICs are used extensively in the EL6648 MX.

Another important factor in the thinness of the Planar display is the interconnect system. The driver board and panel both have gold contact patterns that are interconnected by a gold-plated, metalon-elastomer connector. Clamped pressure contacts have proven not only resistant to environmental effects, but also easy to assemble and dissassemble for on-site repair.

Planar is devoted exclusively to EL display manufacture and plans for future developments include a full page display (scheduled for before mid-year), capabilities for two colors, and in several years, full color. Improvements in brightness, lower power consumption and lower costs are also in the works. The firm claims to be the only EL manufacturer offering custom configurations.

If all continues to develop well, hostile environments as well as mid-range systems in which a flat, thin display is desirable may be well served by EL displays. Planar has been shipping some of the older model panel already and with the product improvements, more may follow.

Price has been a major barrier for EL displays. Because the panel technology, SMDs, drivers and interconnect scheme are new, the downward curve for costs must take place. But as a solid-state product, the ongoing developments in electronic components will likely continue to help prices and availability of EL technology-based products. *— Pingry*

# ONLY EKONIX®

## DOES SO MUCH IN HIGH PERFORMANCE DIGITAL IMAGING CAMERAS.

EIKONIX

EIKONIX\*high-performance digital imaging cameras offer unique capabilities that clearly distinguish them from all others.

CCD or Photodiode Technology

Only EIKONIX offers a choice of high-resolution cameras employing either linear CCD (charge-coupled device) or photodiode technology. In fact, EIKONIX offers the highest-resolution CCD camera available anywhere, with up to 20 million pixels per image (4096 x 5200).

You can choose the economy and low-light capabilities of a CCD camera, or the greater dynamic range of a photodiode camera, *without sacrificing high resolution*.

#### Color or Monochrome

Only EIKONIX has a family of high-resolution cameras available for either monochrome (256 gray-scale levels) or color (a palette of 16 million colors) applications.

#### More User Control

Only EIKONIX cameras use a precision stepping-motor/lead-screw/ ball-slide stage mechanism, which provides precise positioning of the array and eliminates one-dimensional

smearing. In addition, this mechanism allows asynchronous operation, so the user can control both scan speed and data collection rate. This eliminates the need for a separate "frame grabber" or dedicated processor, and frees the host computer for multi-tasking.

#### Buy Just What You Need

Only EIKONIX' broad product line lets OEMs and end users match needs precisely. Configurations range from bare-bones digital camera heads through complete image acquisition subsystems, including cameras, light sources, control electronics, imaging software, and interfaces for many widely used computers (including most DEC and Multibus-based systems).

#### **More Applications**

Only EIKONIX offers the performance and flexibility to handle the broadest range of the most demanding applications, including mapping, engineering drawing digitizing, graphic arts, CAD/ CAM input, office automation, X-ray storage and analysis, textile pattern design,

geological imaging, communications, animation and microscopy.

#### **EIKONIX Know-How**

Only EIKONIX digital imaging products are backed by our 17 years of experience in matching advanced electro-optical technology to a widening world of applications.

To find out what we can do to support your digital imaging applications, contact EIKONIX, 23 Crosby Drive, Bedford, MA 01730, (617) 275-5070.

Circle 72 on Reader Inquiry Card

© Copyright 1985 EIKONIX® Corporation. DEC is a trademark of Digital Equipment Corporation. Multibus is a trademark of Intel Corporation.

#### DEPARTMENTS/CAD

### Test Equipment Manufacturers Unite With Workstation Vendors

Since the introduction of the first workstations in the early part of the decade, workstation vendors have sought to provide the systems architect with the complete design solution. Taking an objective view of these systems, most users agree that they do an adequate job at facilitating the front end of the design cycle (i.e. schematic capture, simulation, verification) as well as presenting a hierarchical partitioning of the design. However, the integration of test capabilities into the workstation seems to have been put on the back burner.

As a result, a new breed of agreements between test system manufacturers and workstation vendors has emerged. New hardware and software which links existing workstations to test equipment is surfacing. For instance, Integrated Measurement Systems (Beaverton, OR) recently unveiled the Logic Master I & II which provides 40 MHz functional test capability to workstations such as those from Valid Logic (San Jose, CA), Daisy (Mountain View, CA), and Apollo (Chelmsford, MA). (For a more complete description of the Logic Master I & II, see *Digital Design*, November, 1984, p. 30).

Unlike IMS, whose systems are targeted for functional testing of prototype chips, Dolch Logic Instruments (San Jose, CA) announced Caesar (Computer Aided Engineering System Analyzing Resource) which is an upgraded version of their Atlas 9600 and focuses on test analysis via test instrumentation. At the hardware interface level, Caesar has a GPIB interface, an RS-232 port and an Ethernet interface. (The software supporting the Ethernet will not be available until mid 1985.) The basic difference between Atlas and Caesar is the number of instrumentation slots in each system; Atlas has two slots, while Caesar offers four. Plug-in instrument modules are available for word generation, data acquisition, logic analysis, signature analysis, waveform analysis and emulation for microprocessor development. In essence, Caesar provides the user with an integrated test and measurement cluster which can be tied to CAE Systems' workstations.

Other differences between the two systems are the user interfaces, the optional imbedded CP/M-based computer and the Caesar, from Dolch Logic Instruments, is an upgraded version of the firm's Atlas 9600 which can be linked to a workstation or function as a standalone system.

physical packaging. Atlas is built around a CRT display but since Caesar works in conjunction with a workstation, the user interface is the workstation's display. Atlas also comes equipped with an imbedded CP/M-based computer system. With Caesar, however, users have the option of purchasing the system with, or without the computer. As far as the physical package is concerned, Atlas is a benchtop system whereas Caesar is a floor unit.

In conjunction with the unveiling of Caesar, Dolch also announced a joint technology agreement with CAE Systems (Sunnyvale, CA). CAE Systems, a workstation manufacturer, offers Apollo-based systems which focus on the needs of the electrical engineer. According to Dolch, Caesar can be directly interfaced to CAE's model 2000 workstation. CAE Systems' President, Phillips Smith, commented that "the intent of the agreement with Dolch is to develop a fully integrated system for design automation and test."

Another joint development agreement recently announced comes from Daisy Systems and Factron (Billerica, MA). (Factron was formerly known as Fairchild Test Systems). The first product from the Daisy-Factron venture is a software interface package that provides a link between Daisy's workstations and Factron's test

systems. The new package allows system engineers to capture simulation data that, is generated in the design phase to be translated into a test program to be used in the debugging or production stage. Dave Stamm, Executive VP of Daisy noted, "the link between Daisy and Factron is a significant event for the design and test engineering communities since it will provide a sizeable reduction in the total design-to-manufacturing cycle."

Judging from the recent introductions from the various test and workstation manufacturers, it appears that the long awaited interface between the two disciplines has arrived. The result of the merging fields will undoubtedly bring about a significant improvement of efficiency. Finally, these first introductions are likely to be just the tip of the iceburg, a host of other workstation and test vendors will surely aim to secure a piece of this huge market. -Collett

#### Integrated Measurement

|   | Syste   | n  | 2.5 | 5  |   |   |  |   |   |  |  |  | Circle 231 |

|---|---------|----|-----|----|---|---|--|---|---|--|--|--|------------|

| 1 | /alid L | 0  | g   | ic | ~ |   |  |   |   |  |  |  | Circle 232 |

| 1 | Daisy   |    |     |    |   |   |  |   |   |  |  |  | Circle 233 |

| 1 | Apollo  |    |     |    |   |   |  |   | • |  |  |  | Circle 234 |

| 1 | Dolch   |    |     |    |   |   |  |   |   |  |  |  | Circle 235 |

| ( | CAE Sy  | vs | te  | 21 | n | s |  | * |   |  |  |  | Circle 236 |

| 1 | Factron | 1  |     |    |   |   |  |   |   |  |  |  | Circle 237 |

|   |         |    |     |    |   |   |  |   |   |  |  |  |            |

JANUARY 1985 DIGITAL DESIGN

# Leading the way in touch technology

Touch technology is leading the way for more people to use computers in more ways than ever before...and Carroll Touch has been leading the way in touch technology for over a decade.

By using touch, you interact with your computer by simply touching the screen. With touch input systems, there are no command languages to learn and no typing skills to master.

When touch makes sense — with casual users, or in a harsh environment — we've got the touch. We're putting people in touch with these remarkable systems in applications ranging from industry, education and the military to public information and office automation.

Carroll Touch can lead you to the touch system that's right for your product. We design and manufacture hardware for a variety of standard monitors and terminals as well as custom designs. Get in touch with us to find out more.

PRODUCT TOUCH THE "C" AND " INITIALS ARE A PERFECT COMPILATION FOR THE FORM

HAND JOING WITH KHICKLES

Circle 71 on Reader Inquiry Card

P.O. Box 1309 Round Rock, Texas 78680 512 244-3500 Telex 881906

follow hatibal gives of hand and glant of knickles

LENGTHEN "T" TO CORREGIOND WITH IDEA OF AN EXTENDED -PINGER

#### Carroll Touch a subsidiary of AMP Incorporated

In Touch With Technology

**DEPARTMENTS**/Communications

## Options For Implementing LAN Protocols Before Standards Gel

Thanks to the IEEE 802 committees, most of us now understand what a local area network (LAN) is and the standard hardware implementations available. Unfortunately, the difficult part of LAN standardization is still underway. The question of what software protocols to use has several answers with strong arguments for each.

The main options for LAN communication software are: to implement custom protocols optimized for the specific equipment offered and provide bridges and gateways to other networks; to offer Xerox XNS protocols, which are relatively well defined and available; to use TCP/IP, developed by the DOD for AR-PA, also well documented and available; and to implement ISO (NBS supported) standard protocols, still being defined, but available in subsets adequate for basic LAN communication. If the network is specifically for MS DOS PCs, Microsoft's (Bellevue, WA) Networks is the emerging standard. Further possibilities are X.25 and IBM's SNA, but they are not designed specifically for peer-to-peer communications in a local area.

There are examples of success with all of these options. Implementing any set of network protocols takes a good bit of work. Standards do not specify exact implementations, leaving the designer both the task of implementation and the possibility of incompatibility even with others using the 'same' protocols.

There is general agreement that a layered approach, as in the ISO's seven-layer OSI (Open Systems Interconnect) model, is desirable. One advantage is that each level is directly dependent on only the next lower layer; this allows various low layer (physical, access and link) network types to use common software. It also means that changes or variations in implementation at one level may require only localized system revision.

A brief description of the functions of the ISO network layers, and how different protocols currently address them is shown in **Table 1**. Note that there are several gaps in the ISO network at present; within a few years, most of these will no doubt be specified. XNS has no defined Session level, and DOD has specified only one set of protocols for layers 5-7. The NBS demonstration at NCC this summer similarly used a null implementation of level 6.

Other important facts are that TCP/IP is designed as part of UNIX 4.2 BSD, but was originally conceived as a wide area network protocol set (for ARPA in the Defense Department). XNS has very well defined and developed internetwork-

| ISO OSI Model Protocol Level<br>Number: Name: Description                                                              |                                                                                             | al Standards<br>n (ISO)/ANSI                                                                  | National Bureau<br>of Standards (NBS)                     | DOD ARPAnet<br>(TCP/IP)                                              | XEROX XNS                                                                | IBM                               |  |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|--|

| 1: Physical: Electrical,<br>mechanical, functional<br>control; topology of net                                         | IEEE 802 Stds (802.3, 802.4, 802.5)                                                         |                                                                                               | NBSNet/IEEE 802                                           |                                                                      | Ethernet<br>(IEEE 802.3)                                                 | Token ring<br>(no spec published) |  |

| 2: Data Link: Medium access,<br>logical link control, some<br>error and flow control                                   | al link control, some                                                                       |                                                                                               |                                                           |                                                                      | Ethernet<br>(IEEE 802.3 & .2)                                            | ?                                 |  |

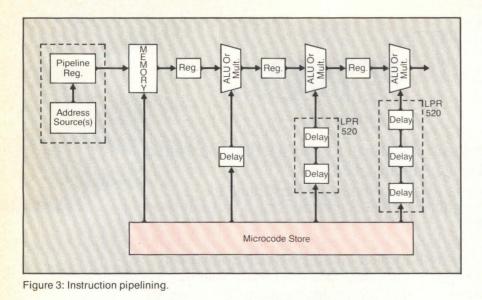

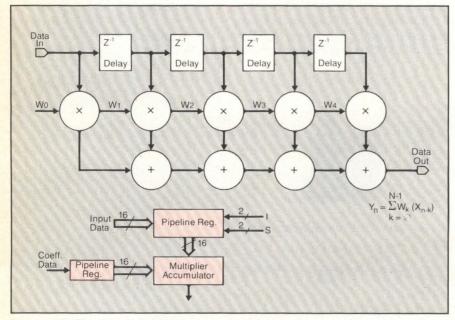

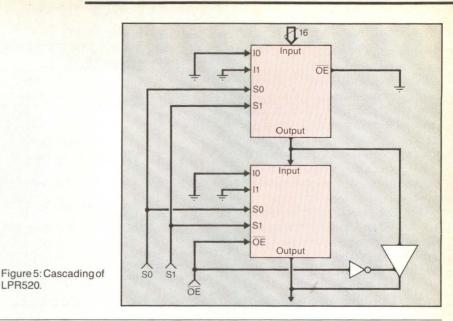

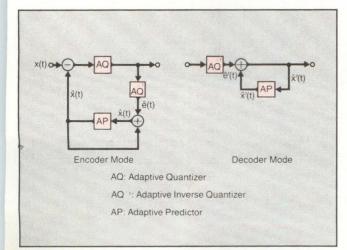

| 3: Network: Routing, switching,<br>internetworking, error<br>recovery, flow control                                    | Connectionless<br>Protocol (CLNS)<br>Internet                                               | CCITT X.25<br>Connection-<br>Oriented (CONS)                                                  | ISO connectionless protocols                              | Internet Protocol<br>(IP)<br>(ARP for address<br>resolution)         | Internet<br>Datagram<br>Protocol                                         | ?                                 |  |