# INTRODUCING THE EXTRAORDINARY EPSON OEM FAMILY OF FLOPPY DRIVES

| SERIES                                                    | SMD 100            |         | SD 500               |         |         | SD 300                 |  |

|-----------------------------------------------------------|--------------------|---------|----------------------|---------|---------|------------------------|--|

| MEDIA<br>SIZE<br>Max. Capacity (2 Sides)<br>(Unformatted) | 31⁄2″              |         | 5¼″<br>(1/2 High)    |         |         | 5¼"<br>(1/3 High)      |  |

|                                                           | 4" x 1.57" x 5.98" |         | 5.75" x 1.6" x 7.68" |         |         | 5.75" x<br>11" x 9.27" |  |

|                                                           | 500 KB             | 1000 KB | 500 KB               | 1000 KB | 1604 KB | 500 KB                 |  |

| Drive Motor Speed                                         | 300 RPM            | 300 RPM | 300 RPM              | 300 RPM | 360 RPM | 300 RPM                |  |

| Track Density                                             | 67.5 TPI           | 135 TPI | 48 TPI               | 96 TPI  | 96 TPI  | 48 TPI                 |  |

| Access Time                                               | 6 msec             | 3 msec  | 6 msec               | 3 msec  | 3 msec  | 15 msec                |  |

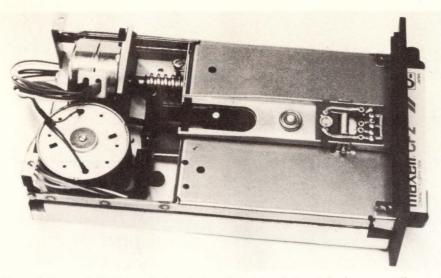

Extraordinary is the best word we could find to describe the new Epson family of  $3\frac{1}{2}$  and  $5\frac{1}{4}$  floppy disk drives. Because there is nothing ordinary about them.

The  $3\frac{1}{2}''$  drives, for instance, feature two-sided capacities up to 1MB. And some draw so little power they can operate on batteries.

500KB to 1.6MB and access times down to 3 msec. And the one-third height 5¼" drive is the industry's slimmest. But that's only part of the story. What really makes them extraordinary is the fact that they're Epson drives. Designed and built by the people who have made "quality in quantity" their trademark around the world.

That means they're designed and engineered with such state-of-the-art features as noise and RF shielding, ultra-high precision head positioning and loading, perfect disk centering, reduced power consumption and heat generation. But, even more importantly, it means they're manufactured by the people who have established the lowest rejection rate in the industry. When you buy Epson, you buy confidence.

If you'd like more information about the extraordinary Epson family of floppy drives and how they can solve your storage problems, write or call us today.

**SW Region** (714) 751-1919 • **NW Region** (408) 985-8828 • **SE Region** (404) 458-9666 **NE Region** (617) 245-8007 • **CENTRAL Region** - (815) 338-5810 EPSON AMERICA, INC.

**OEM Products Division Peripherals Group** 3415 Kashiwa Street, Torrance, CA 90505 (213) 533-8277 Telex: 182412

# EPSON INTELLIGENT LCD MODULES BETTER VISIBILITY NO MATTER HOW YOU LOOK AT THEM.

That's the first thing you notice about Epson LCD displays: they're so easy to read. One reason is the unusually wide viewing angle. Another is the high contrast. It's hard to quantify, but you can see it at a glance. Your customers can see it too.

What you may not notice offhand is how easy they are to use: the easy microprocessor interface, the CMOS TTL compatibility (and low power consumption), the compact size and ease of installation.

Epson Intelligent LCD Modules are available in a range of sizes and formats, including both alpha numeric and graphic formats. Features include a built-in 96-character

ASCII character generator and data RAM. Plus Epson's state-of-the-art technology and unrivalled experience in meeting user needs.

But the best way to judge Epson LCD superiority is to take a look for yourself. Call or write us today, tell us your application, and we'll provide the visibility.

# **CENTERS OF**

lot of gate array manufacturers are talking about their new design centers. The

ones they're planning, or just starting to build. Not Fujitsu.

We're not building any right now. We think the three we have already will do quite nicely.

That's right. We have three design centers now.

Fully built. Fully equipped. Fully staffed.

As a matter of fact, Fujitsu is the only company to make such a large commitment to the gate array marketplace.

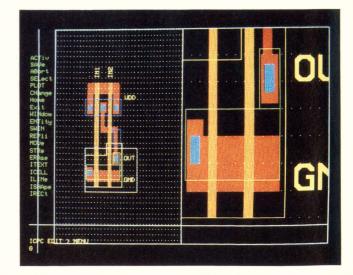

Boston Design Center 57 Wells Avenue Newton Centre Massachusetts 02159 (617) 964-7080 The FMI Design Centers are located in Boston, Santa Clara and Dallas. Each has a multiple station CAD system. High-speed job entry terminals. Time-share terminals. Dual-terminal engineering work stations. And a sophisticated telecommunications network for an added measure of support.

With high-speed leased-line and satellite communications, information can be transferred almost instantly. Not only between the three Design Centers in the U.S., but also to and from FMI host computers in Japan.

Santa Clara Design Center 3320 Scott Boulevard Santa Clara California 95051 (408) 727-1700

It amounts to some pretty exceptional resources. And the best way to eliminate a lot of risks.

You'll also get all the help you need at every stage of design.

From experienced gate array specialists. And the company that's brought more than 3,000 successful designs to light.

# ATTENTION.

You'll be able to make the most of various technologies – CMOS, TTL and ECL. And you'll work with one of the broadest selections of packaging types and styles in the world.

So call the FMI Design Center nearest you. We'll be very happy to make you our center of attention.

Literature request line: 800-556-1234 (ext. 82). In California, 800-441-2345.

# FUJITSU MICROELECTRONICS, INC. Technology that works.

3320 Scott Boulevard, Santa Clara, CA 95051 · 408/727-1700

Write 4 on Reader Inquiry Card

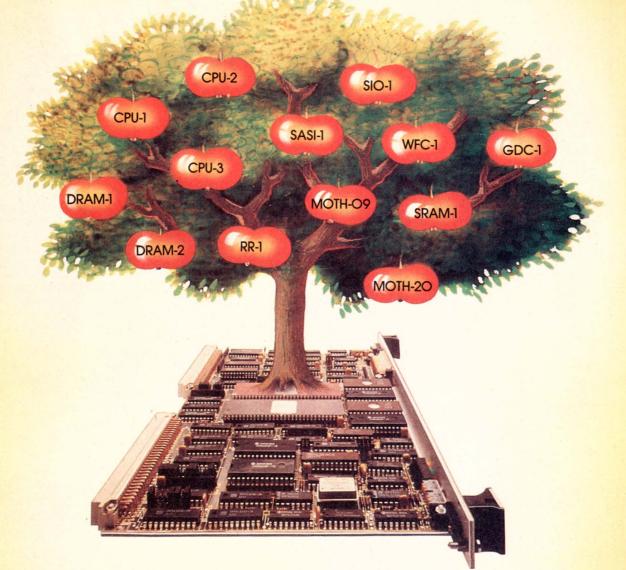

# You've asked for a

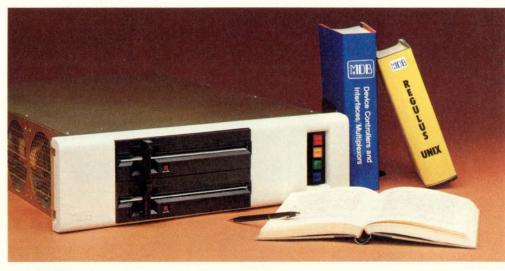

32-bit computer system with \* unlimited expansion capabilities...one that is low-cost and compact vet powerful enough for multi-user, multi-tasking requirements.

So we created the MDB Micro/32! an MC68000 based system with 512KB memory (expandable to 4MB). This powerful system combines MDB's REGULUS with the incredible expansion capability of our in place Q-Bus repertoire of peripheral controllers... as well as our interfaces/multiplexors for all communication modes, protocols and disciplines.

The result: speed, power and versatility of systems design you can't get anywhere else!

REGULUS is MDB's UNIX...the

most advanced and powerful version in the world. Featuring user source compatibility with UNIX V6, 7, and System III, REGULUS offers complete support of all UNIX kernel features, multi-key B-tree ISAM and VAX/ PDP-11<sup>2</sup> cross support, and a host of operating systems and command functions not available in any other UNIX.

We speak your language too. Under REGULUS you can also have BASIC, FORTRAN, COBOL. PASCAL and DIBOL, in addition to most other pop-SZ ular compilers, utilities and special software packages.

Best of all, you don't have to wait. It's all available now. Call us today for complete information.

\*UNIX is a Trademark of Bell Laboratories. 1MC68000 is a registered Trademark of Motorola, Inc. 20-BUS, VAX/PDP-11 are Trademarks of Digital Equipment Corporation

TEMS INC

THE WORLD'S LARGEST INDEPENDENT MANUFACTURER OF COMPUTER INTERFACES.

See us at Mini/Micro Southeast!

**Corporate Headquarters** 1995 N. Batavia Street, Box 5508 Orange, California 92667-0508 714-998-6900 TWX: 910-593-1339 FAX: 714-637-4060

# MDB Systems, U.K., Ltd.

**Everitts House** 426 Bath Road Slough, Berkshire (England) SL1 6BB Tel. (06286) (67377) Telex (847185) WWTSLO FAX (41) (2812) (3507)

### MDB Systems Europe, Inc.

9, route des Jeunes Geneva (Switzerland) CH-1227 Tel. (41) (22) (367697) Telex (289787) fnb FAX (41) (22) (861336)

Write 19 for Micro/32

Write 22 for REGULUS

# **Digital Design**

p. 39 (Photo courtesy Force Computer)

p. 87 (Photo courtesy Aydin Corp.)

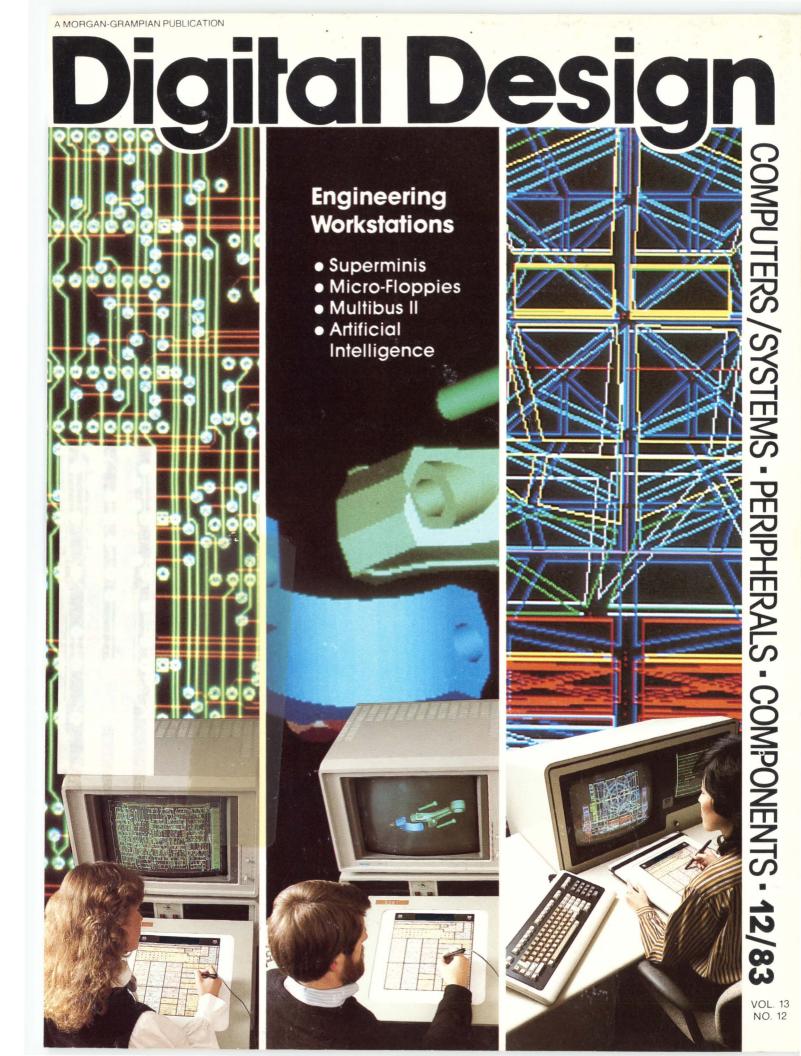

### Cover

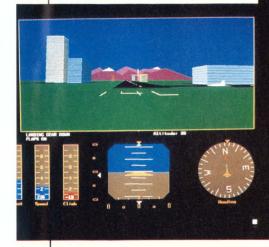

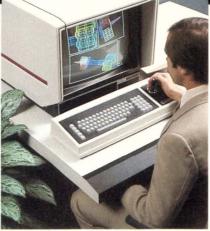

Photos of high performance workstations courtesy of Control Data Corporation, Minneapolis, MN. The new ICEM Ergonomic Workstation (right) is shown displaying a color wire frame of a radar screen. Tektronix 4115 workstations (center and left) display Control Data's ICEM (Integrated Computer-aided Engineering and Manufacturing) applications. An exploded view of an automotive connecting rod (center) uses ICEM Solid Modeling and the complex printed circuit board layout (left) is designed with ICEM Schematics.

Published monthly thirteen times a year with two issues in November. Copyright © 1983 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. ISSN 0147-9245

# COMPUTERS/SYSTEMS

| Industry Spotlight<br>Looking Ahead: A Forecast For The '80s                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The predominant trend in computer systems in 1983 and continuing into 1984 is for an increase of performance at lower levels of cost.                                      |

| 1983 Salary Survey And Employment Trends                                                                                                                                   |

| An increasing hope for the industrial sector resides not only in the continual moderniza-<br>tion of plants and equipment, but in a new emphasis on employee satisfaction. |

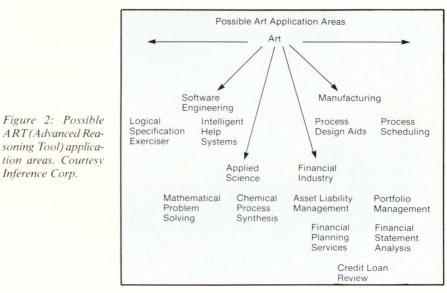

| The Debut Of Second Generation Artificial Intelligence                                                                                                                     |

| Artificial Intelligence is that part of computer science that is concerned with the symbol-<br>manipulation processes that produce intelligent action.                     |

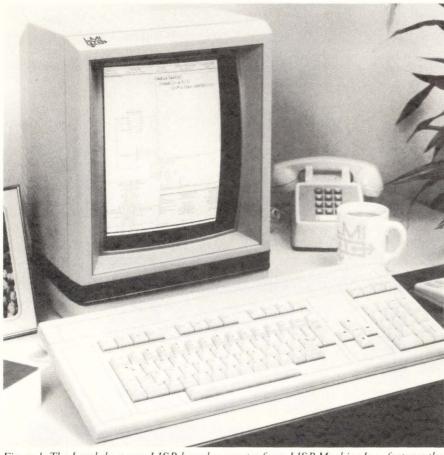

| Engineering Workstations Meet Demands For Individual                                                                                                                       |

| Design Needs                                                                                                                                                               |

| While there has been new development of workstations, it is the performance not the applications that are radically changing.                                              |

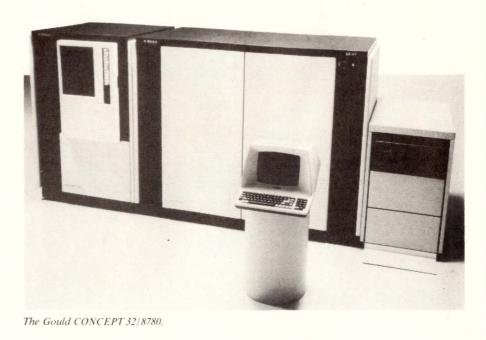

| Superminis Offer A Cost-Effective Solution For                                                                                                                             |

| High Throughput                                                                                                                                                            |

| Superminis have been preferred to mainframes for a variety of applications, primarily due to their lower cost.                                                             |

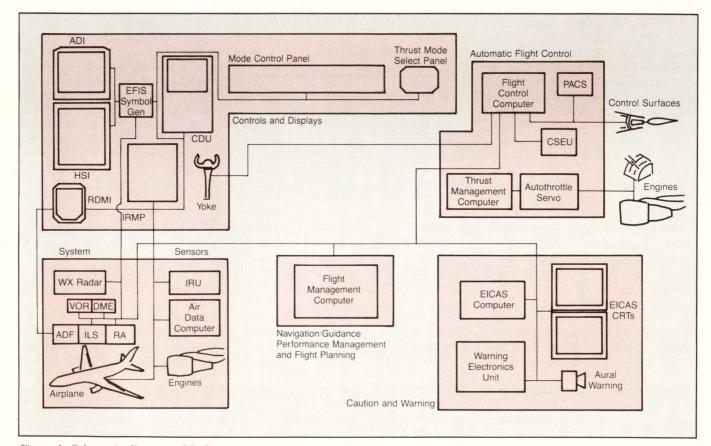

| Integration Issues For The First All Digital Commercial Aircraft 101                                                                                                       |

| The ability to quickly and accurately diagnose conditions and potential problems prompted the move to digital systems.                                                     |

| PERIPHERALS                                                                                                                                                                |

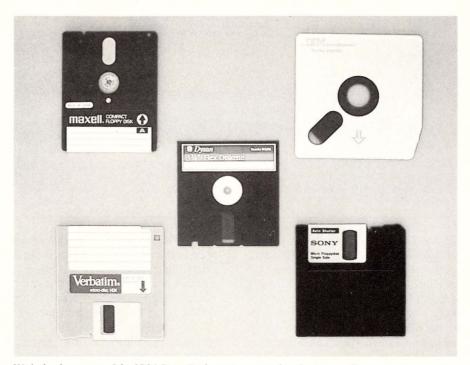

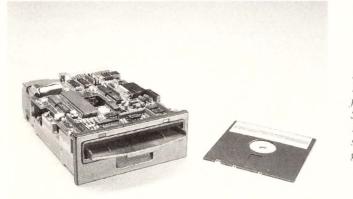

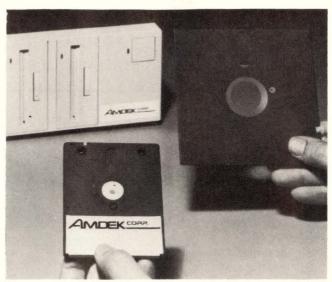

| The Micro-Floppy Race Tightens                                                                                                                                             |

| With the demise of IBM's Demi Diskette, three micro-floppy media contenders remain in the running.                                                                         |

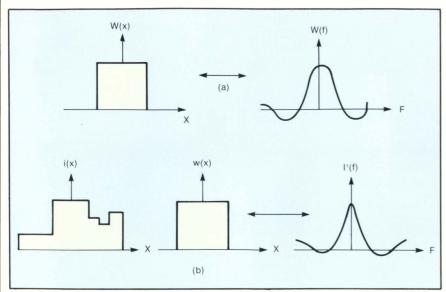

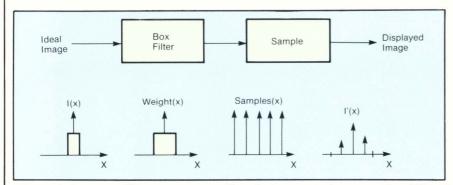

| Graphics System Design                                                                                                                                                     |

| Filtering Improves Effective Resolution                                                                                                                                    |

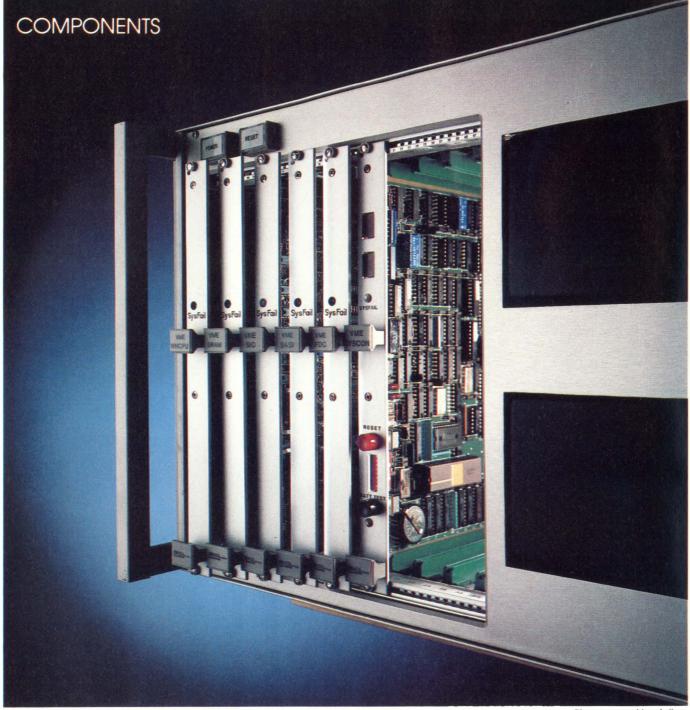

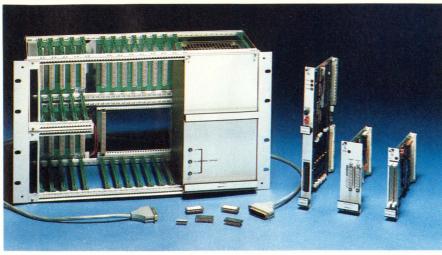

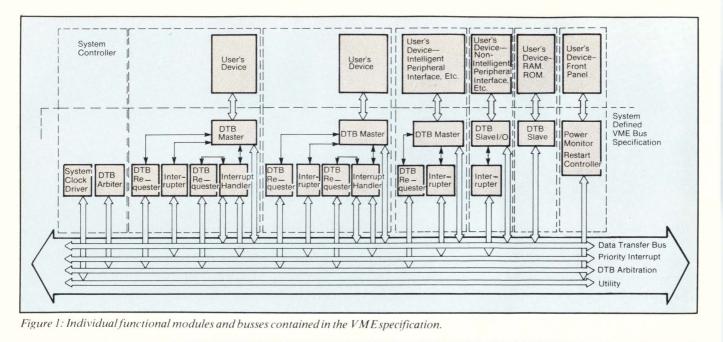

| COMPONENTS                                                                                                                                                                 |

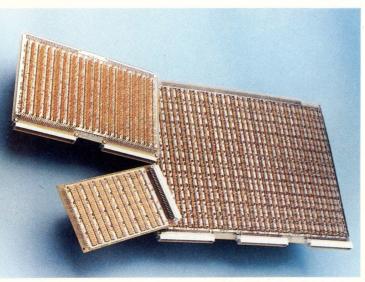

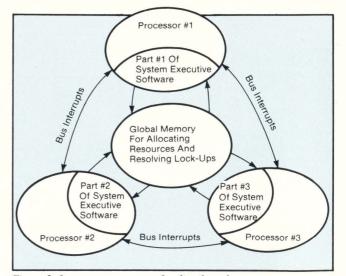

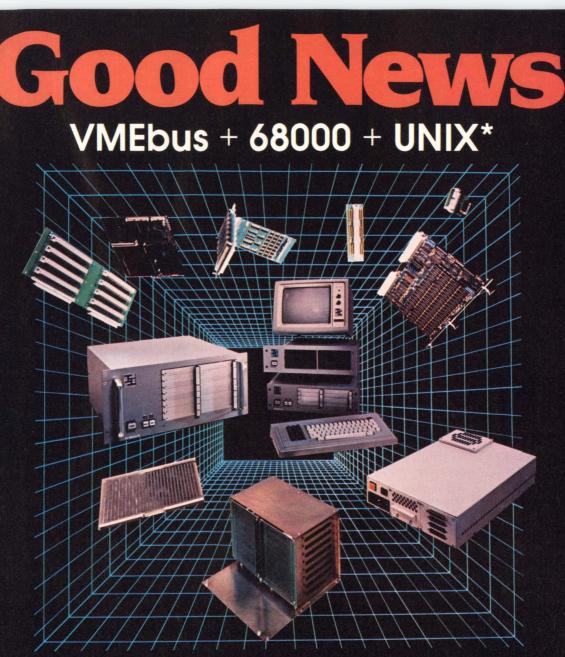

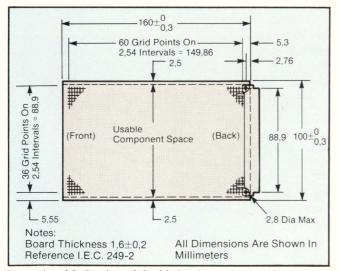

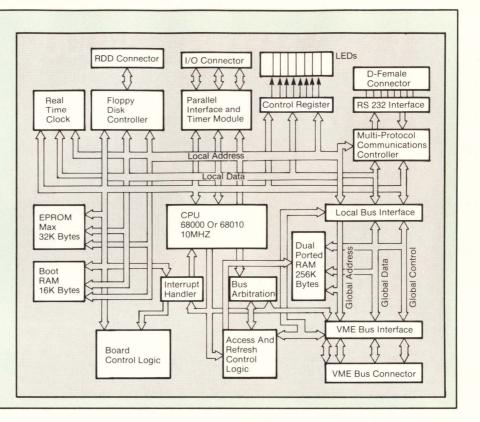

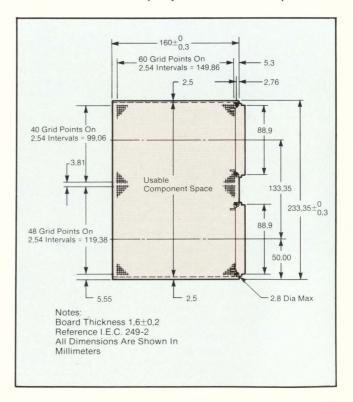

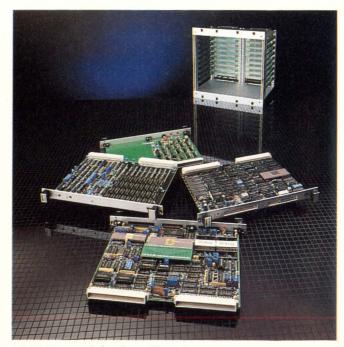

| The Designer's Guide To The VME Bus — Silicon Simplifies Building<br>Block Approach                                                                                        |

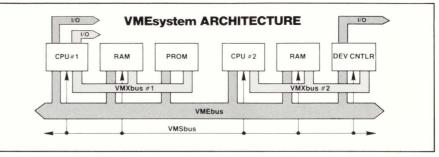

The definition of the VME bus is a departure from previous architectures that may have grown haphazardly around the support of one particular processor.

|                                                                         | <b>h</b>                                                                                       |  |  |  |  |  |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| oards are available for the designer to choose from.                    |                                                                                                |  |  |  |  |  |  |

|                                                                         | ics System Design       32         ne-Board Solution • Custom Chip Boosts Speed Of Workstation |  |  |  |  |  |  |

| Application Notebook            Expanding The Bandwidth Of Optical Fibe | er Systems                                                                                     |  |  |  |  |  |  |

| Editor's Comment14News Update20Washington Report24Technology Trends26   | Innovative Design 110<br>Letters                                                               |  |  |  |  |  |  |

Market Trends ..... 28

Product Index ..... 102

Reader Service ..... 103

Calendar ..... 122

Advertiser Index ..... 122

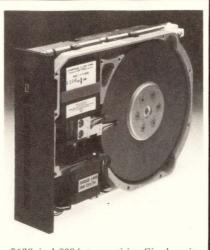

# The design solution: Winchester

Save your customers time, space, and money with  $\frac{1}{4}$ " data cartridges.

When 3M invented the ¼" data cartridge, they designed it to be fast, dependable, small in size, and big in capacity — up to 67 megabytes today, with more in store for the future. No wonder more and more systems designers are finding it the perfect choice for backing up Winchester drives. 45 megabytes of data can be transferred from disk to tape in under nine minutes — with no time lost for media changes. One cartridge does it all! It would take a stack of 38 eight-inch floppies\* to hold the same amount of data. The cartridge is small enough to fit in a coat pocket — and rugged enough to be transported that way, too.

**New rules of standardization.** Industry standards are now being formulated which will improve interchangeability of ¼" recorded data cartridges across most major manufacturers' ¼" drive systems.

# back-up that eliminates stack-up.

This means concerns about compatibility are diminishing.

# The logical choice.

The ¼" data cartridge is the logical choice for designers specifying back-up systems for Winchester drives. It's small, reliable, easy to handle and transport, and has a very low cost per megabyte. These high capacity cartridges are useful for archival storage and program loading, too. So don't wait, give your customers the future. Put this innovative technology to work in the next computer system you design. Data cartridge drives are available from over 30 manufacturers throughout the world.

# For more information:

For more information on how 3M ¼" data cartridges can save your customers time, space, and money, write to Chris Binner, National Sales Manager – OEM Market, Data Recording Products Division, Building 223-5N, 3M Center, St. Paul, MN 55144.

\*Double sided/double density 1024 format 8" diskettes.

3M hears you...

# **GRAPHIC CONTROLLER MLZ-VDC**

Heurikon unveils a graphic solution for your microcomputer application. **On-Card Feature Summary CPU Section:** Z80A CPU Z80A DMA Up to 32K bytes of EPROM/ROM Up to 16K bytes of RAM One iSBX module module 132 byte bi-directional FIFO Buffer Multibus<sup>™</sup> Multimaster or Slave mode 24 bit address bus Memory mapping RAM Hardware and software selectable bus maps

Video Section: NEC 7220 graphics controller chip 512K bytes of video memory. arranged as 4 overlapping planes. 1024 by 1024 pixels 640x480 display format standard 16 Color programmable look-up table 4096 color palette Light Pen I/F Interlaced video Non-interlaced video Composite SYNC Separate SYNC BNC or MOLEX connectors on card for the video

Call Heurikon Direct 1 800 356-9602 In Wisconsin 1 608 271-8700

Write 7 on Reader Inquiry Card

Please use the enclosed qualification form to notify us of your address change. A change of address requires that you fill out the entire form. Please allow 6 - 8 weeks for your change to take effect.

# **Digital Design**

|                                              | 3                                                                                    |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Publisher                                    | Jeffrey C. Hoopes                                                                    |  |  |

| Editor-in-Chief                              | Jerry Borrell                                                                        |  |  |

| Production Editor                            | Debra A. Lambert                                                                     |  |  |

| Senior Technical Editor                      | Dave Wilson                                                                          |  |  |

| West Coast (213) 981-33<br>Technical Editor  | 00<br>Mike Cashman                                                                   |  |  |

| West Coast (408) 371-962<br>Technical Editor | Tom Inglesby                                                                         |  |  |

| Associate Editor/<br>Directory Editor        | Julie Pingry                                                                         |  |  |

| Departments Editor                           | Mary Rose Hanrahan                                                                   |  |  |

| New Products Editor                          | Andrea Coville                                                                       |  |  |

| International<br>Electronics Editor          | Ron Neale                                                                            |  |  |

| International<br>Computers Editor            | Eric Wignall                                                                         |  |  |

| Contributing Editor<br>Data Communications   | Walter Bolter, Ph.D.                                                                 |  |  |

| Contributing Editor<br>Graphics Systems      | Thomas DeFanti, Ph.D.                                                                |  |  |

| Contributing Editor<br>Peripherals           | Bob Hirshon                                                                          |  |  |

| Washington Correspond                        | ent Anne Armstrong                                                                   |  |  |

| Publication Services Ma                      | nager Charlotte King                                                                 |  |  |

| Production Manager                           | Jon Buchbinder                                                                       |  |  |

| Art Director                                 | Maureen Bernardini                                                                   |  |  |

|                                              | Martha Watjen<br>Judy Osburn,<br>cheffler, Vete Saulenas,<br>aul Christo, Gary Byrne |  |  |

| Promotion Manager                            | Elaine Bull                                                                          |  |  |

| Research Helen Obermayer, Peter Mich         |                                                                                      |  |  |

| <b>Circulation Director</b>                  | Hugh J. Dowling                                                                      |  |  |

| Circulation Maggi Haye                       | s-Milville, Miriam Hlister                                                           |  |  |

| Direct Mail                                  | Deborah Goldstein                                                                    |  |  |

| General Administration                       | Karen Melanson<br>Nancy Deveau<br>Dianna Lynn Reed<br>Wynne Shieh<br>Debra Sturm     |  |  |

President Ronald W. Evans

# **Advertising Sales**

Northeast: John C. Moon (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic: Barbara L. Smith (212) 340-9700, Morgan-Grampian Publishing, 2 Park Avenue, New York, NY 10016

Southeast: Rich Santos (404) 393-2505, 1224 Mt. Vernon Road, Dunwoody, GA 30338

Midwest, South Central: Hank Bean, Rob Robinson (312) 346-4611, Morgan-Grampian Publishing, 2 North Riverside Plaza, Chicago, IL 60606

Northwest: Ralph Petersen (408) 371-9620, 1901 S. Bascom, Suite 1005, Campbell, CA 95008

Southwest: Pam Rock (213) 981-3300, 15910 Ventura Boulevard, Suite 1215, Encino, CA 91436 Telemarketing/Northwest: (408) 371-9620, 1901 S. Bascom, Suite 1005, Campbell, CA 95008

Telemarketing/Southwest: (213) 981-3300, 15910 Ventura Boulevard, Suite 1215, Encino, CA 91436

# Lundy graphics terminals are setting standards because we set high standards for Lundy.

Standards: no other 3D graphics vector work-station delivers more speed or a higher IQ than the UltraGraf;<sup>™</sup>only our color raster scan display products offer resolution as high as 1,536 × 1,024 pixels. But there's still another standard you should investigate—the one we set for our company.

Be careful. The fast-paced world of high tech breeds a lot of companies that don't survive; five years from now, many graphic terminal manufacturers won't be around anymore. Which means you could be left without service, support or enhancements.

# Lundy: a company as good as its products.

That's why we think it's important you know as much about our company as our products. We're a high tech company that's been able to balance standard-setting technology with solid business sense—no small achievement.

Now, don't take our word for that, take *Forbes* magazine's instead. Lundy was on *Forbes*' Up&Coming List for 1982, a select roster of companies that look good for the long term because they've paid attention to basics: low debt load, consistently good profit picture, sound management, investment in service, support and R&D.

T5680 color raster, 3D UltraGraf ™and T5470.

Lundy maintains the largest service infrastructure—52 locations.

Our graphics terminals feature the best price/performance ratios available today.

We have developed a new software subroutine package with exceptional compatibility. Its 300 functions deliver a new high in high powered productivity.

Lundy continues to invest in expanded R&D each and every year. Because R&D is the name of this highly competitive game—and we intend to *keep* setting standards.

# We'll help you see more in graphics.

When you take a close look at our graphics terminals, service, support, software, systems capability, enhancements—and our company—you'll understand why Lundy can help you see more in graphics now and in the long term.

For more information, write: Lundy Electronics & Systems, Inc., Glen Head, New York 11545, or call: (516) 671-9000.

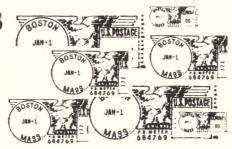

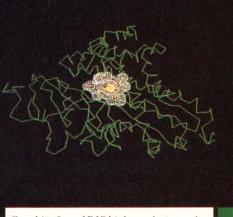

Mt. Everest, symbolic of aiming high, was generated on the Lundy T5680 raster. It offers 16 colors and 136 shades from a palette of 4,096 colors.

Write 10 on Reader Inquiry Card

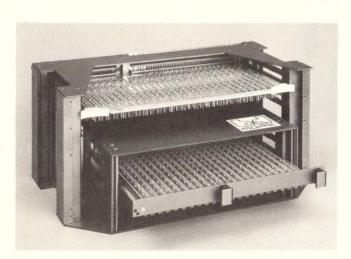

Low noise backplanes, local distributor stock and a wide selection of 4 through 26-slot versions make Scanbe's MICRO-FILE<sup>™</sup> family the better choice for MULTIBUS<sup>®</sup> card cages. And only MICRO-FILES offer Deep-Track<sup>™</sup> card guides. There are other features too: rugged, lightweight aluminum construction; attractive black anodized finish; compact size; unparalleled quality; and Scanbe's unsurpassed experience in card cage design and manufacture. Available with or without backplanes, optional Parallel Priority Resolution Circuitry, and custom design capability all make Scanbe...the better choice for MULTIBUS<sup>®</sup> card cages.

**Scanbe,** Division of Zero Corporation, 3445 Fletcher Avenue, P.O. Box 4159, El Monte, CA 91731, Phone: **(213) 579-2300**, TWX: (910) 587-3437

LEADERS IN PACKAGING TECHNOLOGY

### Write 6 on Reader Inquiry Card

ell us your thoughts

*Digital Design* is your forum — your inputs help keep the magazine interesting and vital to

the design community. So let us know how we're doing and how we can serve you better in the future. We want to know what you like or dislike about *Digital Design*, the subjects you'd like to see us address, how you feel about the problems you face every day as design professionals.

If you have thoughts your peers should know about, put them in a letter in *Digital Design*. Have your say in *your* magazine! Send letters and comments to: Editor, *Digital Design*, 1050 Commonwealth Ave., Boston, MA 02215.

# **Digital Design**

EDITORIAL AND SALES OFFICES Digital Design 1050 Commonwealth Avenue Boston, MA 02215 Telephone: (617) 232-5470

Z

MORGAN-GRAMPIAN

### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215, (617) 232-5470. Brian Rowbotham, Chairman; Ronald W. Evans, President; Charles Benz, H. G. Buchbinder, Robert Poggi, Vice Presidents.

### **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 2 Park Avenue, New York, NY 10016 (212) 340-9700.

The following is a list of conferences sponsored by the Expositions Group:

ATE West CADCON West ATE Northwest ATE East

CADCON East ATE Central CADCON Central

In addition to Digital Design, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronic Imaging • Electronics Test • Computer & Electronics Marketing

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation

● Electronics Times ● What's New in Electronics ● What's New in Computing ● Business Computing and Communications.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

# Кавр ♥ВРА

### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

> Circulation Department DIGITAL DESIGN Berkshire Common Pittsfield, MA 01201

Subscription rates: non-qualified subscribers (US and Canada) — \$35/yr; foreign — surface mail — \$45; air mail — \$70. Single copies — \$4.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicted manuscripts.

# NEED A HIGH PERFORMANCE CMOS GATE ARRAY IN A HURRY? HOW ABOUT 6 WEEKS\* FROM TODAY!

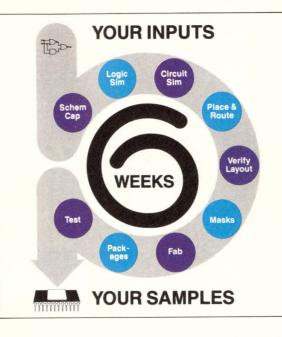

We specialize in fast turnaround. We have to. Most of our customers are in computers or peripherals. Fastbreaking markets with narrow windows. Our 6-week design cycle helps them hit these windows. Here's how we do it.

Weeks 1 and 2—We computer-capture your schematic and create a net list. Next, we run complete logic and circuit simulations. Any problems are noted, discussed with you, and fixed. Then, we start developing the test program.

Week 3—Using computer assistance, we place and route your circuit. All functions are implemented with standard precharacterized macrocells.

Week 4—We verify the circuit design. Engineering and design rules are checked. Any violations are repaired. Then, the IC layout is verified against the net list. This guarantees the actual silicon will be error free.

Week 5—We generate PG tapes and convert them to masks. Test program development is completed.

Week 6—Your wafers are personalized and die sorted. Good dice are packaged in our prototype shop and retested. Then, 10 functional engineering samples That's the kind of service that can help you beat your

press, if necessary.

toughest competition into the marketplace. It's the difference between winning

are shipped to you-air ex-

ings to silicon in 6 weeks.

From engineering draw-

and losing. First prize versus the booby prize.

The Products—At Universal, you have a choice of two technologies. Choose our fast ISO-5 process for toggle rates to 25MHz. If you need more speed, our ultrafast ISO-3 process can take you to 40 MHz. Eighteen different arrays, ranging in size from 180 to 2400 gates, are available. Chances are, there's an array to fit your circuit perfectly. Also, we offer a complete assortment of packages including leaded plastic chip carriers.

Our Philosophy—Service is our business. Your problems are our problems. You're more than a customer to us—you're a partner. Your success will be our success and we know it.

Give Universal a try! Call us at (408) 279-2830 today. Or contact us at Universal Semiconductor Inc., 1925 Zanker Road, San Jose, California 95112. TWX 910 338 7617.

UNIVERSAL SEMICONDUCTOR INC.

# The Fastest CMOS in the West!™

\*500 gate complexity

1925 Zanker Road, San Jose, CA 95112 (408) 279-2830

© 1983 Universal Semiconductor Inc

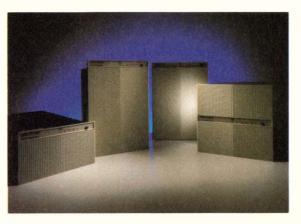

# Floating Point Systems array processor to break

# The FPS-5000 Series from Floating Point Systems

Now, a new family of products from Floating Point Systems brings increased computing power and unmatched price/performance to the signal/image processing world.

With 3 to 6 times the speed and 4 times the memory capacity of previous FPS products, the FPS-5000 Series provides computing for applications that exceed their present system's capability.

The FPS-5000 Series offers fast, accurate, flexible computing for the most demanding real-time, user-interactive, and productionoriented applications.

Four basic product groups make up the new FPS-5000 Series: the 5100, 5200, 5300 and 5400. Peak performances range from 26 million floating-point operations per second (MFLOP), to 62 MFLOP. Data memory of 0.5M to 1M words is available along with program memory to 32K words.

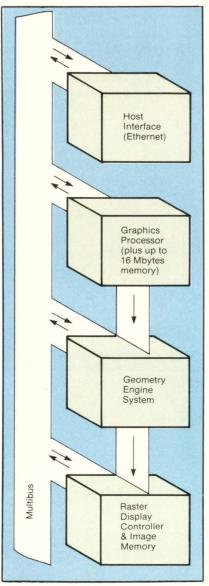

By combining a distributed architecture concept with the latest VLSI technology, the Typical performance examples of geophysical, medical imaging and signal/image processing applications.

| Application Example                                                            | AP-120B    | FPS-5410  | 5420      | 5430      |

|--------------------------------------------------------------------------------|------------|-----------|-----------|-----------|

| 1. Demodulation/Signal<br>Analysis                                             | 13.8 msec. | 6.5 msec. | N/A       | N/A       |

| 2. Tomography Preprocessing                                                    | 60 sec.    | 25 sec.   | 16 sec.   | 12 sec.   |

| 3. Multispectral Image Classification<br>(512 x 512 pixels 8 Bands, 4 classes) | 49 sec.    | 25 sec.   | 13.3 sec. | 10.5 sec. |

| 4. 2D FFT<br>(512 x 512 complex)                                               | 3.4 sec.   | 1.4 sec.  | .7 sec.   | .5 sec.   |

| 5. Matrix Multiply<br>(100 x 100)                                              | 439 msec.  | 177 msec. | 96 msec.  | 71 msec.  |

Based upon specifications subject to change.

FPS-5000 Series sets a new standard for cost-effective computing, breaking the \$2,000 per MFLOP\* barrier—the first time this has been achieved in any floatingpoint computing system.

\*Based on U.S. Domestic Prices

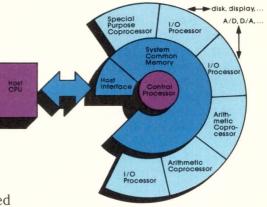

# Distributed processing architecture

The FPS-5000 Series is a distributed processing system that maximizes throughput by allocating the computational load to a set of high-performance, independent, floatingpoint processing elements called Arithmetic Coprocessors. Data flow is simultaneously managed

# FPS-5000 Series Architecture

# introduces the first the \$2,000/MFLOP barrier.

by a combination of independent I/O Processors and the central Control Processor.

Each Arithmetic Coprocessor, with synchronous architecture to allow simple application debugging, functions as a selfcontained unit.

The new Multiple Array Processor Execution Language (MAXL), based upon

FORTRAN 77, allows the user to construct an integrated system environment which can be tuned to application requirements.

Increased performance can be achieved by adding Arithmetic Coprocessors as a field-installable upgrade as the user's requirements evolve.

# Compatibility

11171

The FPS-5000 Series maintains software compatibility with previous FPS 38-bit processors and is supported on a range of host computers. Thus, the extensive

$\mathsf{FFT}[\mathsf{H}_{\mathsf{H}}\mathsf{NN}(\mathsf{X}(\mathsf{T}))]$

software support developed for FPS-100 and AP-120B products is maintained and users are able to move existing applications onto the FPS-5000 Series with minimal effort.

# **Quality and Reliability**

The FPS-5000 Series was designed and built with the same quality standards inherent in all of the previous Floating Point Systems products—standards that have earned those products a reputation for unprecedented reliability and one of the best meantime between failure (MTBF) rates in the industry.

The Series is backed by the same outstanding worldwide support services that distinguish Floating Point Systems from other manufacturers.

For more information about how the FPS-5000 can be used in your specific application, call (800) 547-1445 or your local sales office.

The world leader in array processors.

P.O. Box 23489 Portland, OR 97223 (503) 641-3151 TLX: 360470 FLOATPOIN BEAV

FPS Sales and Service Worldwide.

rrs suies and service wondwae. U.S.: CA Laguna Hills, Los Angeles, Mountain View, CO Lakewood, CT Simsbury, FL Winter Park, GA Attanta, IL Schaumburg, LA New Orleans, MD Rockville, MA Dedham, NJ Red Bank, NM Corrales, PA Devon, TX Grand Prairle, Houston, WA Bellevue.

INTERNATIONAL: Canada, Calgary, Montreal, Ottawa; England, Bracknell, Berkshire; France, Rungis; Japan, Tokyo; Netherlands, Gouda; West Germany, Haar.

Could, west Cermany, Hadi. DISTRIBUTORS: Argentina, Buenos Aires (Coasin Computacion, S.A.): Australia and New Zealand, Milsons Point-N.S.W., Melbourne-Victoria, Canberra-ACT (Techway Phy. Ltd.): Austria, Vienna (Othmar Lackner Elektronische Bauelemente Und Gerötte): Denmark, Copenhagen (BLT Agenturer A/S): Finland, Helsinki (OY Emmett AB): India, Bombay (Hinditron Computers PVT, Ltd.): Israel, Tel Avv (Eastronics, Ltd.): Korea, Seoul (World Business Machine, Inc.): Singapore (Hong Kong, Brunel, Indonesia and Malaysia), Singapore (Scientek Engineering Co.): Southern Africa, Johannesburg (Anker Data Systems): Sweden and Norway, Vaxholm (Tre Konsulter AB): Taiwan, Taipei (Scientek Corporation): United Arab Emirates, Rashidya, Dubai (Albwardy IAL), Abu Dhabi (ADIAL).

©Floating Point Systems, Inc. 1983

Write 60 on Reader Inquiry Card

# EDITOR'S COMMENT

The articles in this issue reflect several subtle changes taking place in engineering and design. During the last few months, the editors of *Digital Design* have observed an increase in the number of production tools which support engineers. A great deal of this activity is due to the designing of new 16/32 and 32 bit microprocessors. Much of the trade press has been actively reporting on the new announcements; however, we hope to examine some of the implications, both for the designers of workstations and the designers using them.

In working with manufacturers across the country, several issues relating to the design process were apparent. One group of topics dealt with the enhancement of drafting efficiency, storage and transmission, editing, design capture, and so on. Many of these aspects are quantifiable or easily demonstrated. There is, however, a second group of issues about the changing nature of the design process itself.

Some engineers believe that while computers will assist the engineer, the activity will remain organized much as it is to date with drafting, analysis, design, and the interface to manufacture as separate disciplines within the overall work environment. Others perceive a coalescence of both organizational job descriptions and actual job skills. That is, just as the computer-based workstation will provide more functional tools to the engineer, the individual who will operate the system will begin to take on a multidisciplinary role.

Given the increasing sophistication of today's workstations this is an obvious oversimplification. Some of today's systems not only require months to learn to use efficiently, but may also be best used by someone with experience in a specific field—either drafting, engineering, or design.

There are several implications here, such as a greater need to train engineers in multiple disciplines, or to lose jobs through automation. Displacement in the marketplace seems almost implausible given the demand for engineers, but the publishing industry has certain similar analogies where electronics has both increased the demand for technical editors and displaced other workers in the printing process.

In this analogy it is the operators of systems which use older technology that are initially made redundant. As the integration of electronics gradually becomes more complex, the nature of organizations changes more dramatically. It is not necessary to ask whether the nature of design will change but when and in what form the changes will occur.

Many users of engineering workstations raise questions about possible homogenization or uniformity brought about through the use of popular software packages. Finite Element Modeling or analysis is a pertinent example where packages such as Nastran or Ansys have become de facto standards. While the code for these packages is complex and the ways in which they are applied are sophisticated, their increasingly wide use makes a good case for a uniform design approach. The general response to them is positive (because they represent excellent pro-

E. L. Busick, President, Spectragraphics Corp. and Jerry Borrell

ducts and promote sound design).

On the negative side, these tools could promote uniformity, or worse, limit the creative process. It may be fair to say that the powerful software packages being developed for today's systems will make the work of the less competent designer/engineer better, and provide possible detraction from the more competent designers.

To date, the emphasis on fifth-generation computers in the US has been primarily on how to bring companies together and coordinate resources, and in planning an agenda. Over three years ago in Tokyo, Chairman Moto-Oka of the Japanese Fifth Generation Project outlined the four goals of their decade-long project. One of these is to develop "intelligent" CAD tools. Combined with another goal: the compilation of "knowledge databases," the project was to bring about the third stage of fifth generation computer architectures.

Can it be that within the next two years engineers in the Japanese project will be working in research centers with intelligent CAD systems which will not only span applications such as electrical and mechanical design, but whose programming will allow their users to work with a new approach to design? One of the key concepts in combining CAD with a knowledge data base is in providing a system with the ability to query the designer not only on what the intent of the work is, but about possible design solutions given certain performance criteria.

Our December issue reflects the vigorous activity in the US market for systems, devices and design tools that may change the way designers work. The effort that we must make over the next year, then, is not only to continually improve the quality of our reportage, but to look critically towards the future. We have developed a series for 1984, the Advanced Technology Series, that addresses future trends and their implications.

> Jerry Borrell Editor-in-Chief

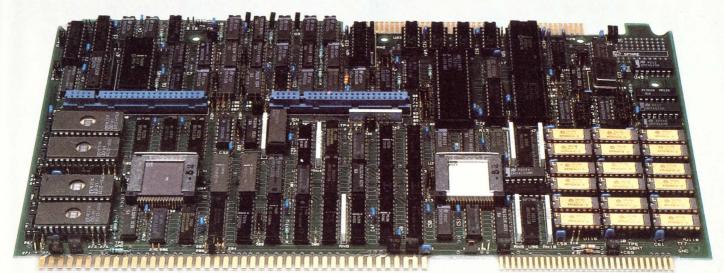

# **MULTIBUS PLUS PERFORMANCE DEPENDABILITY** FLEXIBILITY

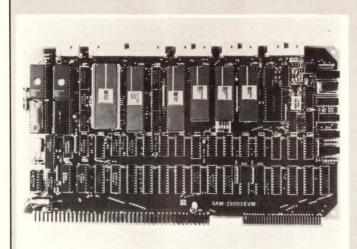

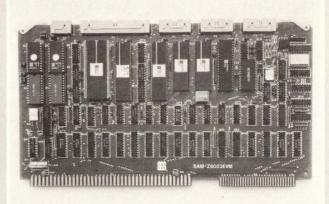

Monolithic Systems Corporation has always been synonymous with Multibus technology. In fact, MSC has the distinction of having designed the first patented single board computer. Other firsts include: the first use of 64K RAM elements, on-board EPROMS, floppy disk controllers, APU's, user selectable addressing and multimaster CPU configurations. These board level accomplishments have benefited OEM's for over 12 years and have culminated into a powerful line of systems, the MSC 8800 series. As the leading innovator in Multibus products, Monolithic Systems offers a family of systems intended to do things never done before. Systems to assist and create test programs for the scientific and industrial markets, to be multi-user and multi-tasking, to be expandable, rugged and reliable beyond anyone's expectations. Available with operating systems by Digital Research, the MSC 8800 series and board level products will be prominent factors in Multibus applications now and in the future.

For more information about Monolithic Systems Corporation and its Multibus product line call Toll Free 1-800-525-7661.

USA

84 INVERNESS CIRCLE EAST ENGLEWOOD COLORADO 80112 303-770-7400 TELEX: 45-4498

## EUROPE

JUSTINIANSTRASSE 22 6000 FRANKFURT aM MAIN 1 WEST GERMANY 611590061 TELEX: 41-4561

### CANADA

6503 NORTHAM DRIVE MISSISSAUGA ONTARIO, CANADA L4V IJ2 416-678-1500 TELEX: 96-8769

# **16 BIT PROCESSING**

- iAPX 186 8 Mhz. CPU

- 128 OR 512 KBYTE PARITY RAM

- UP TO 128 KBYTES EPROM

- FOUR 16 BIT COUNTER TIMERS

\*Multibus is a registered trademark of Intel Corporation.

- TWO iSBX CONNECTORS

- ONE RS232C PORT

- 24 LINES PARALLEL I/O

- 1 YEAR WARRANTY

Write 11 on Reader Inquiry Card

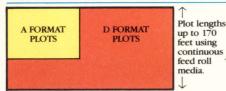

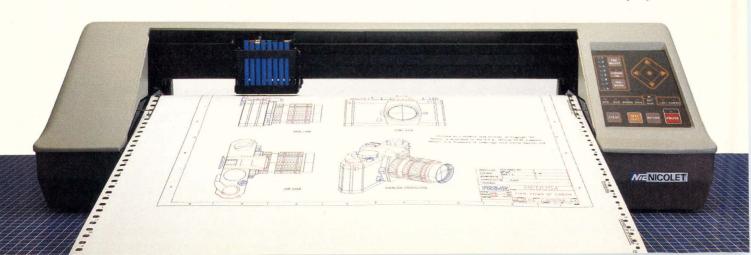

# At last. A plotter designed to run both cut sheet and roll media.

*The most flexible 'D'' format* 8-pen plotter ever.

$\leftarrow$  (Plots up to 24.5" or 594 mm)  $\rightarrow$

Now you can create virtually any size plots you want up to 24.5" wide, including ANSI sizes A-D and ISO sizes A4-A1, on cut sheet or roll media. Use standard bond paper, glossy bond, vellum, clear film or mylar.

Run dozens of entirely different plots automatically thanks to a builtin microcomputer that can be preprogrammed to plot on roll media up to 170 feet. Then quickly switch to cut sheet plotting – great for your preprinted forms. The ZETA 822 is the only plotter that can do both.

Best of all, we've got line quality and throughput at a price that makes us the cost-effective choice for just about anybody's plotter applications. You'll get vector independent speed of 25 ips. And 2 g acceleration insures the plotter reaches top speed fast. With resolution of one-one thousandth's of an inch.

Change character sets just by plugging-in a ROM chip.

Our firmware character generator produces typeset quality lettering similar to the popular Helvetica font with user-controlled proportional spacing. Now you can add special character symbol sets for both engineering and architecture simply by plugging in a new ROM chip.

*Eight color, carriage-mounted pens eliminate time-consuming pen changes.*

Incredibly, some plotters still grind to a dead stop to change pens. Not ours. We put all eight pens on the carriage. You'll be amazed at what that does for plot throughput. And when you want to use our liquid ink option, just snap in our four-pen cartridge.

You have total user control over such variables as speed, pen pressure, acceleration and pen up/down delay times. Touch controls automatically adjust the ZETA 822 for perfect liquid ink plots.

Naturally, we support most computer protocols. And you can use the ZETA 822 on-line, off-line or remotely via RS 232C or IEEE 488 interfaces.

Call (415) 671-0600. Or write: Nicolet Zeta Corporation, 2300 Stanwell Drive, Concord, CA 94520 TWX 910-481-5951

Write 16 on Reader Inquiry Card

Micolet

mmm

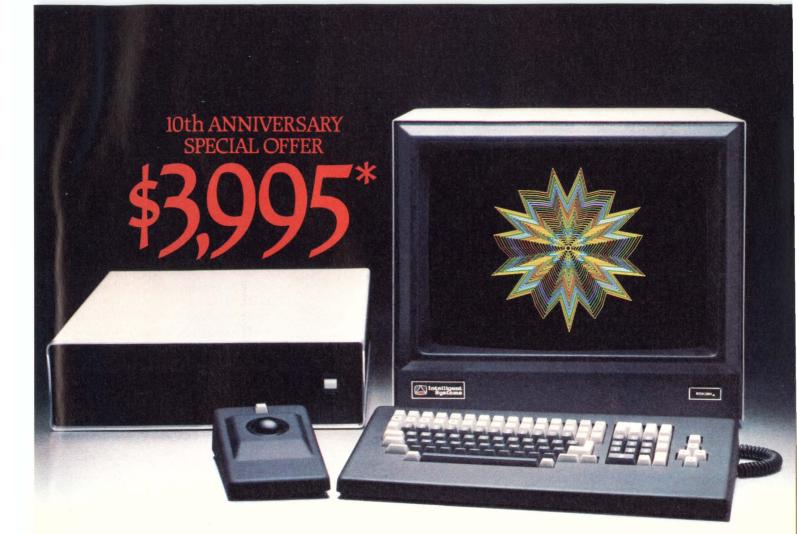

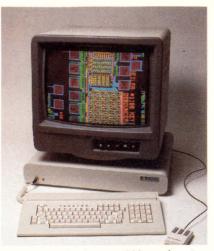

# Intecolor VHR-19 challenges Tektronix with 1024 x 1024 resolution, PLUS COLOR, and at less than half the price!

Comprehensive Graphics Capabilities: 1024 x 1024 workspace; 1024 x 768 displayable; 4096 x 4096 virtual addressing for extended Tektronix 4014 compatibility. High-level graphics primitives, including polygon fill. Bit-mapped 19" screen. Three dot-addressable bit planes. Separate alphanumeric plane. Hardware pan and zoom. Expanded peripheral support. Simple menu set-up. Host programmable function keys. Fast Response: 2.5 million pixels/sec. direct screen memory access port.

Fast Response: 2.5 million pixels/sec. direct screen memory access port Industry Standard Protocol: ANSI X3.64/VT100 command protocol. Compatibility: VT100, TEK 4010/4014/4014-1 and enhanced Intecolor 8001R.

Raster Color: Palette of 4,096 colors, 8 concurrently displayable. Advanced Processor Design: Three graphics processors (7220D-1); separate alphanumeric processor; plus terminal processor (Z80) and keyboard processor.

\*100-piece OEM price and single-unit introductory price through 12-31-83; includes color monitor, graphics display processor and keyboard. Trackball is optional at \$330. U.S. Domestic prices.

From the same company that pioneered the world's first microprocessor-based color terminal (Intecolor 8000) way back in 1973. And the same company that continually leads the color graphics industry with new product innovations. NOW, a bold, new addition to the fastest growing area of the industry: Intecolor VHR-19 high resolution graphics workstation.

If you need more than a graphics preview terminal, but less than a turnkey CAD system, the VHR-19 delivers an unprecedented price/performance ratio. With an advanced design graphics display processor. With fine image detail and high-

level resolution. And, with an introductory, single package price of \$3,995. Unbeatable.

AN INTELLIGENT SYSTEMS COMPANY Intecolor Drive, 225 Technology Park/Atlanta, Norcross, GA 30092, 404/449-5961, TWX 810-766-1581

# NEWS UPDATE

# **EEPROM Joint Effort**

INMOS Corporation and General Instrument announce a joint effort involving 64K EEPROM technology. Specifically, INMOS is naming General Instrument as second source for its IMS3630 8K x 8 EEPROM, a high performance +5V only non-volatile memory device. The joint effort involves a complete technology transfer, including masks and processing information.

# **China Trade**

Digital Sound Corporation, developer and manufacturer of the DSC-200 audio digitizing peripheral unit, has received an order for the system from the Institute of Acoustics in the People's Republic of China. This underscores a current softening in the United States position regarding trade of high technology equipment with the People's Republic of China. The DSC-200 provides a complete interface between conventional audio equipment and computer disk storage and has broad applications in speech research, music synthesis and speech product development.

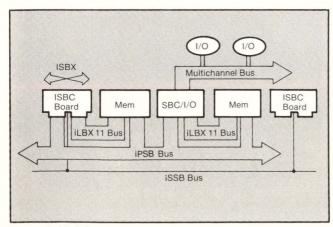

# **Multibus II Specs Gain Support**

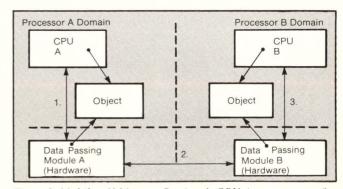

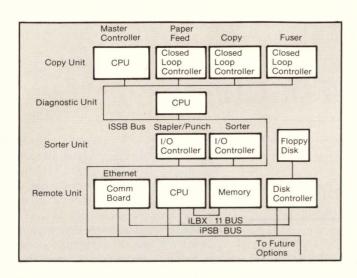

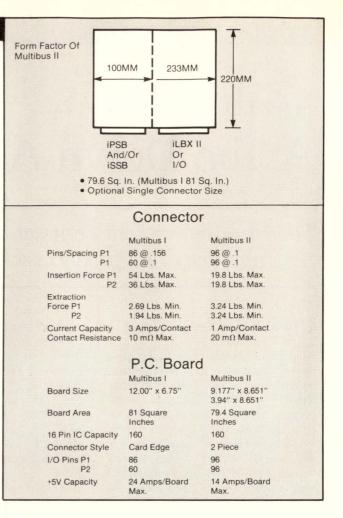

Intel Corp. announced that 68 companies support specifications for a new microprocessor data bus — the path over which information moves from the central processor to memory and peripheral devices in a microprocessorbased system. Called Multibus® II, the new architecture meets the needs of advanced 8-, 16- and 32-bit highperformance, microprocessor-based systems. The Multibus Manufacturers Groups (MMG) was recently formed to preview the new bus specifications.

# **Designs For Porsche**

Intergraph Corporation will supply Porsche AG, a West German car maker, with interactive computer graphics systems for research and development. The company expects to use the system for car body and engine design, as well as other general mechanical and electrical applications. The Intergraph computer-aided engineering system purchased by Porsche includes a VAX-11/780-based Intergraph computer equipped with the company's Graphics Processor and three of its latest dualscreen engineering workstations.

# **GTE Telenet Approval**

Bridge Communications, Inc., received certification from GTE Telenet Communications Corporation to operate its Ethernet local area network gateway products over GTE Telenet's public and private data networks. The certification will allow Bridge's Gateway Server/1 (GS/1) units to connect Xerox Network System (XNS) Ethernet networks to host computers or other XNS Ethernets via GTE Telenet's packet-switching network, using the CCITT X.25 protocol for the LAN-to-Telenet interface.

# **One-Stop Design Center**

Control Data Corporation and NCR Corporation's Microelectronics Division announced the opening of an electronic computer-aided design (ECAD) services center that is believed to be the first of its kind in the nation. Control Data, NCR, and Array Technology, NCR's Bay area sales representative and design group, have combined their expertise in systems, semiconductors and computer-aided design to offer a combination of consulting, training and computing resources at the center. The center is designed to assist integrated circuit manufacturers and systems houses apply state-of-theart ECAD technology from initial design concept to the production stage.

# First Flexible Disk Cartridge

A major breakthrough in magnetic media storage technology has brought Verbatim Corporation and Iomega Corporation together in a licensing agreement to produce the computer industry's first flexible disk cartridge. Under the terms of the agreement, Verbatim, manufacturer of magnetic media products, will supply the media for Iomega's flexible disk cartridge. Iomega, based in Ogden, Utah, is the first disk drive manufactureer to successfully employ Bernoulli technology in the development of magnetic media storage products.

The new cartridges are considered

significant because they are the first magnetic media storage products to combine flexible media with the density and access speed characteristics of more costly rigid media. As a result, the cartridges are expected to sell for half to one-third less than other commercially available removable cartridges using rigid media.

Bernoulli technology dates back to the 18th century when Swiss mathematician Daniel Bernoulli developed his theory of fluid mechanics. Bernoulli's work has played a major role in aircraft wing design and, most recently, in flexible disk cartridge technology.

### **Transmission Security**

A new data encryptor designed to prevent unauthorized access to computer information during transmission has been added by Racal-Milgo to its family of link encryption devices. The new product, Datacryptor III, secures data over point-to-point wideband circuits at data rates up to 112 Kbits per second. It operates synchronously on full duplex, leased line facilities and is equipped with both V.35 and RS 232 interfaces wired in parallel. Either interface may be used depending upon network data rate requirements, V.35 for higher rates and RS 232 for lower ones. No configuring or strapping is required.

# G.E. Sells Printer Dept.

General Electric Company and the Genicom Corporation announced a definitive agreement whereby Genicom will purchase General Electric's Data Communication Products Business Department, including all operations in Waynesboro, Virginia and Reynosa, Mexico.

Genicom, a new company, which was formed to operate this business in the future, will purchase the Data Communication Products Business Department assets from General Electric. The Waynesboro plant manufactures and markets teleprinters, line printers and serial printers, which are used in a wide range of data processing and telecommunications applications and electromechanical relays, which are sold primarily to the aerospace/ defense industry.

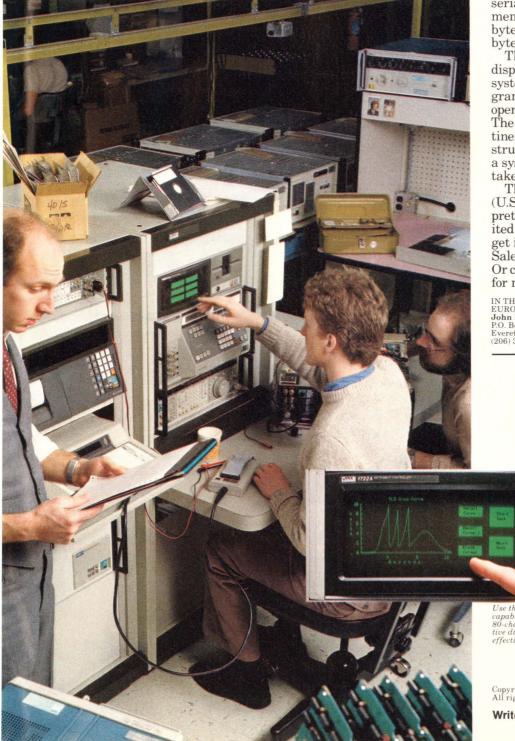

# Put powerful instrument control

The new Fluke 1722A Instrument Controller combines the computational ability and interfacing flexibility you need with the rugged packaging and easyto-use human interface your factory demands. All at a new, low price. Now you can integrate your next factory test, process control or OEM system faster and put your people to work sooner.

The power of the 1722A is a 16-

bit single-board computer with 136K bytes of main memory. Its 12 MHz speed puts it in the same class as many minicomputers. Four programming languages are available to simplify programming, including Interpreted and Compiled BASIC, FORTRAN and Assembly. Each includes special adaptations for controlling IEEE-488-compatible programmable instrumentation. And if you

already own a 1720A Instrument Controller, you can run existing software on the 1722A-without modification.

The modular mainframe easily mounts in a standard 19 inch rack and allows you to configure the interfaces and memory to your exact needs. The IEEE-488 (1980) and RS-232-C interfaces can be expanded with an optional IEEE-488 and RS-232-C interface card, parallel interface card or dual serial interface card. Onboard memory is expandable to 2.6M bytes with RAM cards or 1.4M bytes with bubble memory.

The 1722A's touch-sensitive display dramatically simplifies system operation. Once programmed, your system can be operated entirely from the CRT. The 1722A displays only the pertinent options, allowing you to structure the user's response to a system. This helps reduce mistakes and increase throughput.

The 1722A is priced at \$7450 (U.S. list), including BASIC Interpreter, documentation and a limited one-year factory warranty. So get in touch with your local Fluke Sales Engineer or Representative. Or call us toll free at 800-426-0361 for more information.

IN THE U.S. AND NON-EUROPEAN COUNTRIES: IN EUROPE: John Fluke Mfg. Co., Inc. Fluke (Holland) B.V. P.O. Box C9090, M/S 250C P.O. Box 5053, 5004 EB Everett, WA 98206 Tilburg, The Netherlands (206) 356-5400, Tlx: 152662 (013) 673973, Tlx: 52237

Use the new graphics capability of our 16-line, 80-character touch-sensi-tive display to create more effective operator prompts.

Copyright © 1983, John Fluke Mfg. Co., Inc. All rights reserved.

Write 12 on Reader Inquiry Card

# NEWS UPDATE.

# **Computer Controlled Systems Include Robotic Vehicles**

Veeco Instruments Inc. announced the formation of a previously announced joint venture (August 22, 1983) to design and manufacture automated systems for companies that fabricate semiconductor wafers. Automated wafer fabrication will extend the Veeco product line of semiconductor processing equipment. The company plans to develop a state-of-the-art computer controlled system that will be housed in clean rooms with robotic vehicles controlling all movement involved in the operation.

Allen E. Busching, President, said that the elimination of workers from the actual fabrication area will improve productivity substantially. "There are more than 200 semiconductor wafer fabrication factories worldwide and their yields on new VLSI products generally are below 50% due primarily to the contamination of the sensitive silicon wafers that results from workers

involvement in the facility."

The company plans to open a customer demonstration laboratory in Dallas during 1984, and expects to begin delivery of systems in 1985.

# Full CAD/CAM for ASEA

ASEA, a world industrial group, has turned to Racal-Redac to help complete a major computerized manufacturing program at its Electronics Division in Vasteras, Sweden. ASEA currently has four Redac Maxi systems for PCB design, as well as a DSM 6 host computer. Two newer Maxi systems are expected to be linked this year to the DSM 6 VAX 11/780 computer, which will be at the hub of the new computerized production system.

# **Timplex Contract**

Timeplex, Inc. signed an agreement with GTE to supply data multiplexers to their Business Communication Systems division. Three lines of Timeplex products offered by GTE are statistical multiplexers, data concentrators for smaller installations, and standalone modems that operate synchronously.

# **Quantum Pacts**

Quantum Corporation signed three new agreements for the distribution and purchase of the company's 8- and 5-1/4-inch Winchester disk drives. Future Electronics, Montreal, Quebec, Canada, signed a distribution agreement for Quantum's Q2000 and Q2080 8-inch disk drives. A two-year contract, valued at \$4.5 million, was signed by Pixel Computer Inc., Wilmington, Mass., for Quantum's Q2000 and O2080 8-inch drives and O500 5-1/4inch products. A second OEM agreement was signed by Telesis Systems Corporation of Chelmsford, Mass. The \$3 million contract calls for Quantum's Q2000, Q2080 and Q500 disk drives.

### The DS120 Terminal Controller makes your LA36 perform like a DECwriter® III.

The Datasouth DS120 gives your DECwriter® II the high speed printing and versatile performance features of the DECwriter® III at only a fraction of the cost. The DS120 is a plug compatible replacement for your LA36 logic board which can be installed in minutes. Standard features include:

- 165 cps bidirectional printing Horizontal & Vertical Tabs

- Page Length Selection

110-4800 baud operation

- 1000 character print buffer

- •X-on, X-off protocol •Self Test

- Double wide characters Parity selection

Optional APL character set

RS232 interface

20 mA Current Loop interface

Top of Form

Adjustable Margins

Over 9,000 DS120 units are now being used by customers ranging from the Fortune 500 to personal computing enthusiasts. In numerous installations, entire networks of terminals have been upgraded to take advantage of today's higher speed data communications services. LSI microprocessor electronics and strict quality control ensure dependable performance for years to come. When service is required, we will respond promptly and effectively. Best of all, we can deliver immediately through our nationwide network of distributors. Just give us a call for all the details.

Write 5 on Reader Inquiry Card

Digital Design ■ December 1983

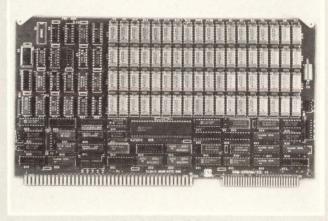

# Four Answers To Your S-100, Multi-User Problems.

Intercontinental Micro Systems makes everything you need for S-100 bus multi-user systems, networks or single user systems.

At a price that won't break your budget. Quite simply, our single board computers, slaves, 256K memories and personality boards let you build a system *now*, not later. The hardware works, the software works, and the prices are what you'd expect from a company that uses the most advanced design, software and production techniques to keep costs down.

What you won't expect is the almost awesome sophistication of Intercontinental Micro System's products.

So stop messing around with multiple sourc-

ing, hardware integration problems and software nightmares. Come to Intercontinental Micro and get it all — price, performance and delivery.

Read the specs, then call, write or circle the bingo number below. We'd be glad to send more information and help solve your S-100, multi-user system problems.

# CPX-MX SLAVES.

□ IEEE 696.1/D2 S-100 compliance. □ Compatible with CPZ-48000 SBCP. any Z-80A based CPU with extended address capability or 16 bit based CPUs complying with IEEE 696.1/D2 bus specification. □ Z-80B" 6MHz (CPS-6X) or Z80A4MHz (CPS-4X) operation. □ Two synchronous (CPS-MS) or asynchronous (CPS-MA) serial I/O ports. □ TurboD0S" & CP/NET" compatible. □ Master confiscation of slave memory for diagnostic purposes. □ Two parallel I/O ports; eight data bits + 2 handshake lines per port. □ 64 Kbytes of onboard dynamic RAM.

bits + 2 handshake lines per port. □ 64 Kbytes of onboard dynamic RAM □ Master/slave memory-to-memory transfers under DMA control @ 571 Kbyte/sec transfer rate when used with CPZ-48000 SBCP. □ Software selectable baud rates. □ Usable as an intelligent I/O processor in single user system.

# PERSONALITY BOARDS.

□ Centronics printer. □ 8 inch floppy disk. □ 5¼ inch floppy disk. □ RS232 serial communications. □ Synchronous/ asynchronous modem. □ Priam smart/smart E hard disk. □ Long distance serial communication (2000 ft @ 9600 baud). □ Shugart Associates Systems Interface (SASI). □ Clock / calendar. □ Konan David,Jr.™ hard disk. □ Archive tape drive.

### Write 25 on Reader Inquiry Card

1733 South Douglass Road,Ste.E Anaheim, California 92806 (714) 978-9758 Telex: 678401-TAB-IRIN

# CPZ-48000 SINGLE BOARD COMPUTER.

□ IEEE 696.1/D2 S-100 compliance. □ Z80A," 4MHz Operation. □ Floppy disk controller (FDC). Single or double sided. Single or double density. 8" or 5¼." □ Two synchronous or asynchronous serial I/O channels (SIO). □ Two parallel I/O channels (PIO). □ Four channel DMA controller. □ 64K on board RAM. □ Memory management unit (MMU). Addresses up to 16 megabytes of system memory. □ Eight Vectored priority to □ Provisions for 2K or 4K onboard EPBOM. □ Software select

Integrables of system memory. □ Light vectored profile vectored provisions for 2K or 4K onboard EPROM. □ Software selectable baud rates. □ IBM Bisync, HDLC, SDLC and other protocols. □ CP/M," MP/M," and TurboDOS'" operating systems available. □ Turbo-Disk\* implementation included.

# 256KMB-100 256K MEMORY.

□ IEEE S-100 bus, spec 696.1/D2 compliance. The 256KMB-100 is compatible with most IEEE S-100 board products now on the market. □ Linear addressable to 2 megabytes. □ 225 nanosecond access time, maximum, 160 nano-seconds, typical. □ 295 nano- second read-write time, minimum. □ Bank selectable 16K increments. □ //0 port address bank selection. □ Configures for phantom deselection. □ Parity error detection,

Z80A & Z80B are trademarks of ZILOG Corp. • CP/M. MP/M & CP/NET are trademarks of Digital Research Corp. • TubroDOS is a trademark of Software 2000 Inc. CROMIX is a trademark of CROMEMCO Corp. • DAVID JR. is a trademark of KONAN Corp.

# WASHINGTON REPORT

### by Anne A. Armstrong

The debates over policy which seem to drag on endlessly in Washington usually have little effect on the bottom line for business, but a campaign now shaping up over "industrial policy" could significantly change the financial climate and the tax situation for many computer manufacturers.

Begun as a call for increased growth and support of high-tech industries by a group dubbed the "Atari Democrats," the idea of a "new industrial policy" has caught the imagination of a widening group that now includes Republicans and even the executive council of the AFL-CIO.

Like most catch phrases, the notion of a new industrial policy means different things to different people. In common, however, is the belief that it is in the interest of the nation's economy for government to support the growth of high-technology by creating a favorable business climate. One way to do that is to provide tax incentives.

The 1981 Economic Recovery Act was a big help to traditional industries such as steel and oil, but did very little for high technology companies because the short life of most high tech equipment precludes taking advantage of the ERA's long-term equipment depreciation. A whole host of legislative solutions is currently under consideration on Capital Hill.

Lobbying efforts have increased and a new group, the Ad Hoc Electronics Tax Group, has been formed to concentrate pressure for new legislation. Directing the group is Robert Kirkwood from Hewlett-Packard's governmental affairs office. Another entry is the Computer and Business Equipment Manufacturer's Association (CBEMA), which recently adopted a position on industrial policy and has begun to lobby the Hill for support.

Not everyone sees tax cuts as a solution. Rep. Richard A. Gephardt. (D-Mo.), suggests an Economic Cooperation Council, which would be a forum for discussion about economic issues and a place where information could be exchanged. He is not in favor of continued tax changes.

"We are destroying our tax system. We have made the tax code our direct spending program. The 1981 tax bill made the significant decision to allocate capital to older industries to the detriment of other industries. We no longer stop to see if it works, we just do a new tax bill every year. Twothirds of the bills introduced each session include tax preferences for someone," Gephardt told executives at a recent CBEMA meeting on industrial policy.

Also cautious about government involvement and aid to high technology companies is Rep. Ed Zschau, (R-Calif.), who founded a high tech firm — System Industries — before he was elected to Congress from the district which includes Silicon Valley.

"The proper role of government is to create an environment in which risk taking and innovation flourish," he said. Japanese style agencies — such as MITI — which provide centralized planning and targeting for industry would probably not work in this country, Zschau believes. "Government is not known here to be the servant of business."

"The legislative agenda should focus on making sure that bottlenecks for business are removed. The four main points of industrial policy should include 1) a commitment to basic research 2) incentives for investors. 3) educational opportunities to provide an adequate supply of trained engineers, and 4) expanding market opportunities brought about by reducing trade barriers," Zschau said.

Since no one bill has emerged as a consensus solution to the industrial policy problem. Congress is faced with more than 100 bills purporting to help high technology companies in one fashion or another. Industry efforts are concentrated on tax relief. but most observers see a long battle ahead. CBEMA's president Vico Henriques says. "Industrial policy promises to be a key point in the debates surrounding the coming 1984 elections."

# ARPANET Split Into Two Networks

The Department of Defense's pioneering packet-switching network. ARPANET, has been divided into two systems to insure greater security for military information. Originally designed as an experiment into advanced networking techniques and as a way for researchers working for the government to communicate and trade information. ARPANET has evolved into an operational electronic mail and messaging system used by more than 10,000 people.

The civilian system will continue to be called AR PANET and will remain the link between universities and laboratories doing government research and the government. MILNET, the new defense system, will be used for military communications only and will be part of what DOD expects by 1985 to be a secure, top-secret communications system. There will be gateways or mail bridges between the two networks, but the systems are designed to be completely independent.

### FCC Delays Access Charges

In a move that surprised many and angered AT&T, the FCC delayed implementation of the access charge plan and AT&T's related long-distance rate reduction proposal. The Commission says it needs a 3-month delay (until April 3, 1984) in order to adequately review voluminous new tariffs filed earlier this month by local phone companies for their planned new system of payments by users and intercity carriers for access to the long-distance network. AT&T's plan was to reduce long-distance rates \$1.75 billion overall. Both plans were tentatively scheduled to take effect January 1, 1984, the same date as AT&T's divestiture.

For the equipment industry, a key change in a bill passed by the House Telecommunications Subcommittee last month is the Bliley (R-VA) amendment that called on the FCC to review access charges for existing non-profit users of Centrex service.

# The fastest...the largest memories... the easiest to program...

### MARS-432 Array Processor Speed

A high-speed programmable arithmetic processor used as a peripheral to a general purpose computer.

The state of the art in 32-bit floating point array processors. Direct addressability of up to 16 million words (64 megabytes) of data memory and direct access to the highspeed internal data bus assure the user of highest throughput rates.

# MARS-432 Array Processor Features Include:

- Add and multiply times of 100ns

- Computational power of 30 megaflops

- Computes a 1024-point complex FFT in 1.7ms

- DMA transfers at I/O bus rates of 20 megabytes/sec

- Data memory read or write in 100 ns

- Memory paging for uninterrupted processing during I/O transactions.

### MARS-432 Array Processor Memories

Program and data memories compatible with programs written for today's array processor applications.

# **Program Memory**

Virtual and physical address space of 4K words – standard. Expanded configuration uses a 4K cache memory to extend total memory to 64K words.

# **Data Memory**

Data I/O is supported by DMA transfers into data memory with a physical address space of 16 million words. A data memory page-loading feature provides the option of zero overhead background loading of data during time critical program execution. No DMA cycle stealing overhead is incurred. Uninterrupted processing can occur simultaneously with high-speed I/O transfers.

### MARS-432 Array Processor Software

An architecture specifically designed to support a FORTRAN compiler and other software development tools.

# FORTRAN Development System (FDS)

FORTRAN compiler, linker, and trace/monitor provide high-level language access to the MARS-432.

### Microcode Development System

Off-line development package includes macro-assembler, microcode diagnostics, and a unique utility for automatic microcode optimization.

### AP Run Time Executive Support Package (AREX)

As the interface to the MARS-432 at run time, AREX provides processor initialization, I/O operations, and array function execution.

# **Applications** Libraries

Extensive applications libraries include math, signal processing, and image processing.

For additional information on the MARS family of high-speed Array Processors, write or call: Numerix Corp., 320 Needham Street, Newton, MA 02161 Tel. 617-964-2500 TELEX 948032

Write 81 on Reader Inquiry Card

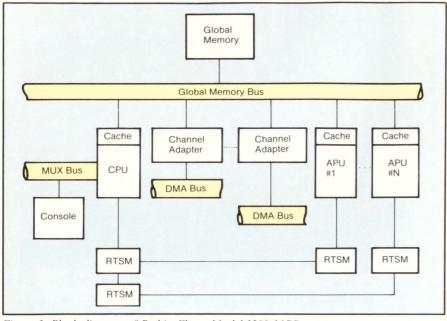

# Expandable Supercomputer Uses Semi-Custom ECL Gate Arrays

Available in configurations capable of processing from 4 to 40 million instructions per second, the ELXSI 6400 is a multi-purpose system that can be used in time-sharing, real-time or batch environments from large number crunching tasks to highvolume tranaction processing.

The system consists of a modular multiprocessor computer, a proprietary operating system called EMBOS (Elxsi message-based operating system), peripherals configured to customer specifications and data management tools. Each basic system includes a Gigabus high-speed central bus, CPU units, memory system, input/ output processors (IOPs) and service processor. A variety of programming languages are available, including Pascal, C, Cobol-74 and Fortran-77. In the past the limiting factor in multiple computer architectures has been the central system bus. Elxsi's solution is to provide a 64-bit wide synchronous bus with an effective bandwidth of 320 Mbytes/sec. Taking into account all bus overheads for memory access, usable data rates range from 160 to 213 Mbytes/sec. The Gigabus allows for the attachment of up to 32 identical modules, which can be configured as the user requires.

At the heart of the 6400's I/O subsystem are dedicated I/O Processors (IOPs), up to four of which can be configured in a single system. All physical I/O is handled by the IOP, freeing the CPU's for computational tasks rather than array processing. Key performance features of the IOP include a 50ns processor cycle time, microcoded control of all I/O and virtual-to-physical memory address translation for data transfers between memory and devices. Each IOP can have two sub-busses, each of which can operate at 8Mbytes/ sec, giving a total bandwidth of 16M Bytes/sec per IOP. Each sub-bus can support up to 16 device controllers which may be dual-ported across two sub-busses belonging to the same or different IOPs.

The controller types that are currently supported include a disk controller, a combined tape/printer controller, a communications controller and a DEC DR11-compatible interface. An IOP can function with any mix of controller types. All con-

Above: The ELXSI 6400 multi-purpose system.

# Technology Trends

trollers are self-identifying, allowing dynamic configuration of the I/O subsystem.

The operating system (written almost entirely in Pascal) is implemented as a collection of independent processes which communicate with each other and with user processes via an inner kernal that provides a microcoded message system. The interactive interface to EMBOS is a user-friendly command language interpreter, or shell. The system 6400, typically priced from \$600,000 to \$4,000,000, is available now with a 60 to 90 day delivery time. *Elxsi Corp.*,

Write 233

# Data Storage Breakthrough

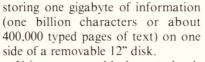

By offering a combination of very high capacity and media removability at a significantly lower cost than current random access storage devices, the pending generation of optical disk drives will be well suited for a wide range of traditional computer applications as well as new market opportunities. In addition, the optical disk drive's low power consumption and small footprint will be advantageous in the large office automation market projected to mature in the second half of the 1980s.

Based on laser rather than magnetic technology, optical disk drives are significant primarily because they will help satisfy the world's exploding demand for data storage capacity. With early products expected to offer 1,000 Mbytes on a 12" disk, they will offer a solution to the challenge of satisfying tomorrow's data storage requirements in local area networks, small business computers, minicomputers, mainframes and imaginal storage applications.

Imaginal storage, or the ability to store the representations of documents or graphics, is an area not adequately addressed by current storage products, but is an application for which high-capacity optical disk drives are well-suited.

Despite offering many advantages, optical disk drives will not render floppy or Winchester disk drives obsolete. Magnetic technology-based products will remain the correct choice for many system applications; the two technologies will complement each other within the same system and can co-exist for at least a decade.

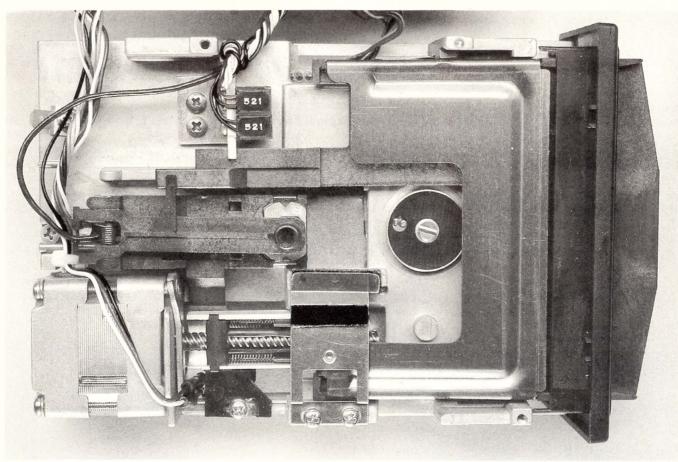

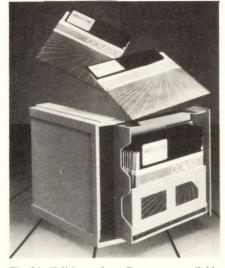

Shugart Corporation became the first American OEM company to announce a laser-based optical disk drive with the introduction of the Optimem 1000, a device capable of *Cartridge being inserted into the Optimem* 1000.

Using non-erasable laser technology, the Optimem 1000 provides up to 10 times more on-line storage capacity than comparably priced magnetic disk drives, greatly reducing the cost-per-byte for stored information.

Developed by Shugart's Optimem division, the new drive writes and reads information on the disk using non-erasable, laser technology (write once, read many times). Unlike magnetic recording technology, which uses a mechanical read/write head to record data, the Optimem product uses a laser beam to perform this function. Information is recorded and played back on a removable 12" disk which is protected during operator handling, transport and storage by a hard shell cartridge. The cartridge also accommodates labeling information and incorporates write protect and operator interlock features. The Optimem media is pregrooved for servo-tracking and preformatted with sector address information.

The Optimem 1001 cartridge contains a single-sided optical disk. This disk features a sandwich construction consisting\_of\_two\_1.2mm-thick PMMA (polymethylmethacrylate)

layers permanently bonded together with the recording layer on the inside surfaces. The 1.2mm of PMMA functions as protection for the disk as well as serving as a substrate material. The Optimem 1002 cartridge contains a double-sided disk; the second surface is accessed by flipping the cartridge over.

System integration is simplified through the industry standard controller-to-host Small Computer System Interface (SCSI). Each SCSI controller can operate up to eight peripheral devices.

Key specifications of the new Optimem 1000 include a five megabitper-second transfer rate and an average access time of 100 milliseconds. The Optimem drive is only 7" high, 19" wide, and 24" deep. It requires less than 230 watts to operate, greatly reducing power and cooling requirements. Built-in microprocessorcontrolled electronics and modular design simplify field maintenance and repair.