A PENNWELL PUBLICATION

AUGUST 1, 1988 DESCRIPTION THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

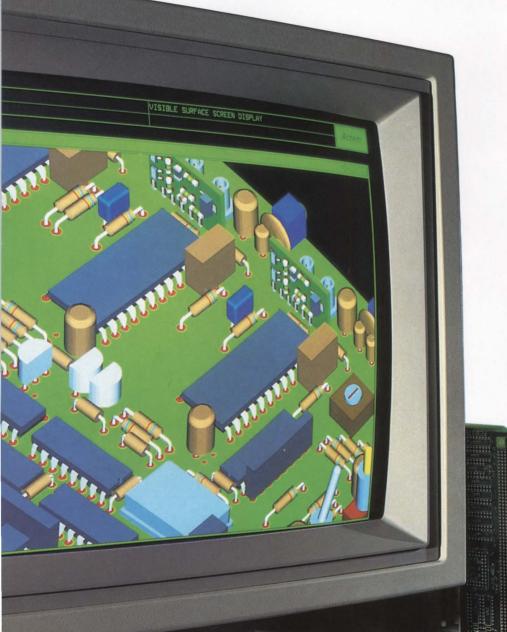

raphics system esigners strive r photorealism

High-density gate arrays tax utility, packaging and testing Mixed-mode simulator accurately models real-world designs Denser devices, flash designs spawn new applications for EEPROMs

# Shake. Rattle. Ready to roll...

# Canon races away from the competition by offering the next step in portability design.

The MD3611 is a 2.0/1.0MB 3.5" Floppy Disk Drive designed to be driven:

- +5V only, 1" high Light weight...430g

- Unequalled Shock Resistance... 60G @ 11 milliseconds

- Oil Dampened Head Loading

- Selectable Trigger on Dual Color L.E.D.

- Flush Bezel...No more broken buttons

- Low Power...20 milliwatts on standby, 1 watt operating

- Dust Shutter

The Canon MD3611 is no ordinary microfloppy. Besides meeting industry standards for performance and reliability we went a step further and designed a drive to meet the harsh environment and physical demands of portability.

> When you're ready to test drive the Canon MD3611 please call or write: Canon U.S.A., Inc.,

Flexible Disk Drive Division, One Canon Plaza, Lake Success, NY 11042 (516) 488-6700.

West Coast: Canon U.S.A., Inc., 4000 Burton Drive, Santa Clara, CA 95054, (408) 986-8780.

CIRCLE NO. 1

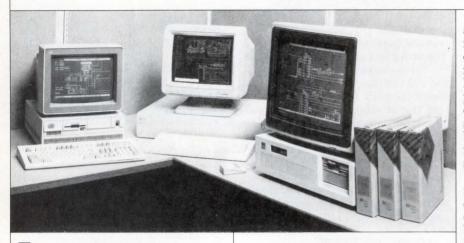

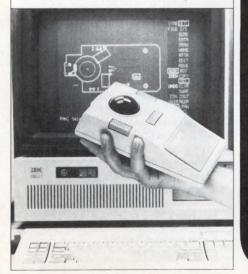

# The "Look and Feel" CAE Users Have Been Looking For

On-Screen Prompt line makes it easy to find the feature you're looking for. Hierarchical Menus eliminate keyboard commands.

Action Button selects functions.

Menu Button toggles between menu and graphics.

> Pan Button Redraws screen around cursor location.

Use Visionics' Super Hi-Res graphics board for workstation (1284 x 960) graphics on a PC platform, or use standard CGA or EGA graphics. EE Designer III takes advantage of all 3 mouse buttons for maximum operating speed and throughput.

# Introducing EE Designer III<sup>™</sup> The first ergonomic PC-based CAE software system

The fact is that today's CAE software systems have a lot of features. The problem is that you have to read a huge manual or go to a HELP screen to find the feature you need.

Finally, an integrated desktop CAE software system with all the features you need plus an ergonomic user interface that lets you easily find and access them.

EE Designer III combines on-screen function prompts with a graphicbased hierarchical menu structure. So whether you're capturing a schematic or Auto-Routing your printed circuit board you can always find the function you need.

You'll be hearing a lot about Visionics' EE Designer III in the next few At only \$3995, no other CAE tool can match the features of EE Designer III:

- Supports 2 mb of L/I/M EMS memory

- On-line Netlist Capture

- Forward and Back-Annotation of Multipage Schematics

- Analog and Digital Circuit Simulation

- Full SMT Support

- 1 mil Grid Resolution

- 45° Memory Auto-Routing

- Fabrication/Assembly Drawing Support

months. Everyone knows that our EE Designer was the first end-to-end CAE tool for under \$1000; now the new EE Designer III continues setting the price-performance standard. Isn't it time you found out what over 5000 worldwide users already know — that the EE Designer family of products get the job done. The best way to see for yourself just how good it feels to make the right choice in CAE software is to call Visionics today.

343 Gibraltar Drive Sunnyvale, CA 94089 (408) 745-1551 **1-800-553-117**7 Telex: 346352 Fax: (408) 734-9012 **CIRCLE NO. 2**

# Peter picked a plain paper plotter.

# Paul picked a pack of pictures.

Paul has a problem. Poor Paul. He's out of pictures...again. Pity.

Peter is more productive because he prefers the powerful GOULD 4070

Series digital storage oscilloscope. Peter's probes stay put, because with 4-channel capability Peter can simultaneously view the relationship between signals. Also, Peter's 400 MS/sec sample rate can capture a single event with 2.5 ns between samples. And, of course, Peter's primary reason for picking GOULD— Peter's plain paper plotter produces plotted waveforms...immediately, perfectly. Peter couldn't be more proud. Pick the plain paper plotter. Contact GOULD today for a **free evaluation**. We'll leave a GOULD DSO for you to try. No salesperson. No pressure. Call **1-800-GOULD-10** or write GOULD Inc., Test and Measurement, 19050 Pruneridge Ave., Cupertino, CA 95014.

Vol. 27, No. 14

Page 21

# DEVELOPMENT AND INTEGRATION TECHNOLOGY UPDATES Computers and Subsystems Application tuning: a key to RISC

| system development2                                        | 1 |

|------------------------------------------------------------|---|

| PS/2 boards equipped for speed in data-acquisition tasks2  | 2 |

| SCSI adapter ties computers and peripherals into Ethernet2 | 5 |

THE FIRST MAGAZINE OF SYSTEM DESIGN

# Integrated Circuits

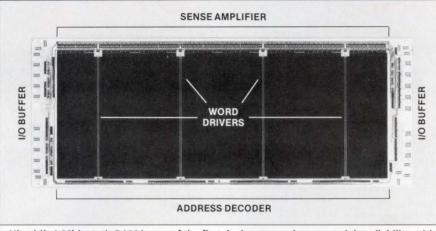

| First 1-Mbit SRAMs foreshadow changes for users and vendors      | .28 |

|------------------------------------------------------------------|-----|

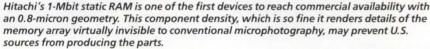

| Self-clocking PLD implements asynchronous interfaces             | .30 |

| User-configurable arrays bridge gap between gate arrays and PLDs | .32 |

## **Design and Development Tools**

AUGUST 1, 1988

Page 43

# TECHNOLOGY AND DESIGN FEATURES

# High-density gate arrays tax utility, packaging and testing

As gate array densities continue to escalate, designers combat the side effects .......43

# Mixed-mode simulator accurately models real-world designs

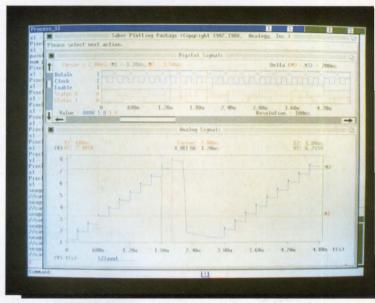

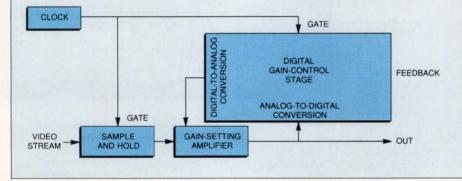

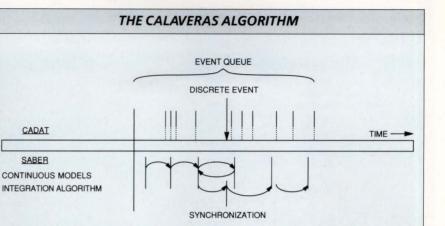

Integrated simulation lets designers monitor the interaction of digital and analog events to verify mixed-mode ASICs, systems and boards.......65

# COVER STORY

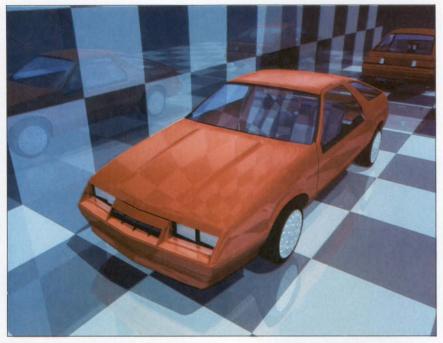

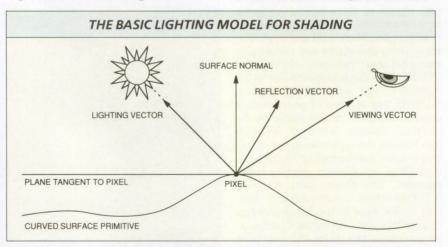

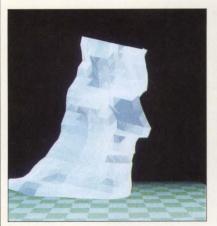

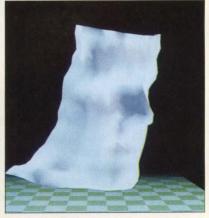

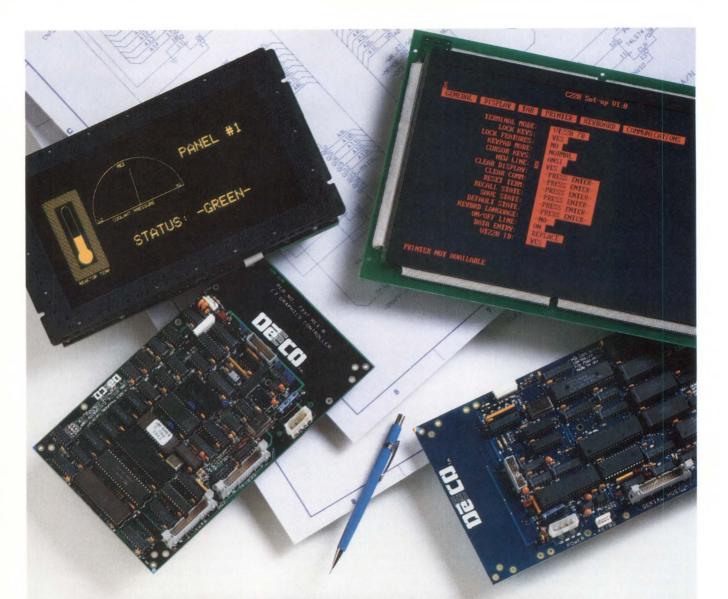

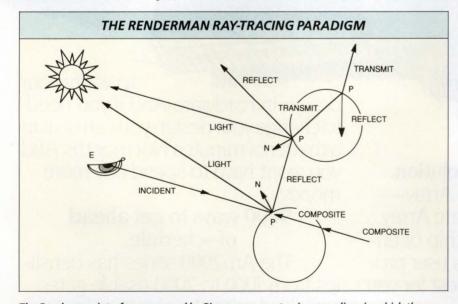

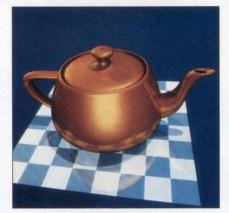

# Graphics system designers strive for photorealism

# ■ NEW PRODUCT HIGHLIGHTS

# **PRODUCT FOCUS**

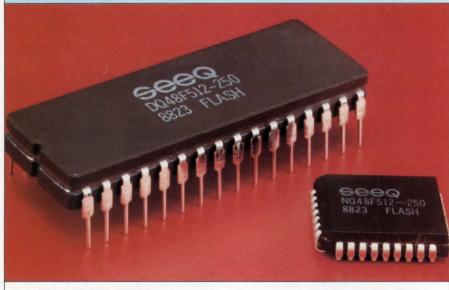

Denser devices, flash designs spawn new applications for EEPROMs......70

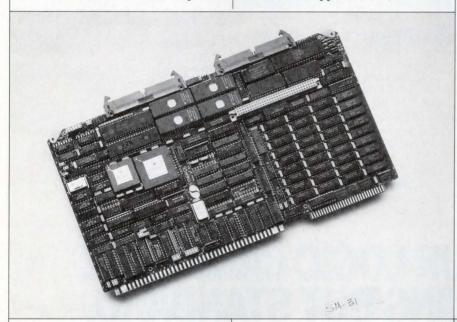

Computers and Subsystems 68030 CPU board delivers 32-Mbyte/s Multibus I throughput ......75

Integrated Circuits Chip set allows 10-Mbit Ethernet transmission over twisted-pair wiring ...77

# Major System Components

| Four-layer wire-wrap panels boost component density |  |

|-----------------------------------------------------|--|

| Data Communications                                 |  |

| VMEbus Ethernet processor transfers                 |  |

| files at 3 Mbits/s88                                |  |

| Product Briefs                                      |  |

# DEPARTMENTS/COLUMNS

| News Briefs                       | 3 |

|-----------------------------------|---|

| ditorial14                        |   |

| .etters                           | 5 |

| Calendar91                        | 1 |

| Design for Testability92          | 2 |

| Advertisers'/New Products Index96 | 5 |

Page 70

# SWIFT<sup>\*\*</sup> 3<sup>1</sup>/2" HIGH-CAPACITY, HIGH-PERFORMANCE DISK DRIVES NOW AVAILABLE FOR EVALUATION.

Get the  $3\frac{1}{2}$ " disk drive that sets the standard for capacity and performance. We combined the two most important things everyone wants in a storage device—capacity and speed. And packed it into the size everyone would like... $3\frac{1}{2}$ ".

CAPACITY PLUS PERFORMANCE Swift disk drives feature a

blistering 15 ms average seek time. The top model offers 200 Mbytes of unformatted storage with high-performance device level or intelligent interfaces. Swift drives feature 1-to-1 interleave, synchronous or asynchonous operation and a 32k cache buffer with read ahead capability to optimize performance.

# **DESIGNED FOR RELIABILITY**

A rotary voice coil actuator, advanced surface mount electronics and a unique high torque, phaselocked in-hub spindle motor are just a few of the advanced features that make Swift the industry's leader.

# SWIFT IS A FAMILY

Production shipments of 100 and 150 Mbyte models are already

underway. Now you no longer have to limit the capacity or performance of your system just because you need a  $3\frac{1}{2}$ " drive.

If you're a qualified OEM, you can get an evaluation unit now.

CIRCLE NO. 4

| Model<br>9435X | Capacity<br>(Mbytes) | Avg. Seek<br>(ms) | Interfaces      | Transfer Rate<br>(MHz) |

|----------------|----------------------|-------------------|-----------------|------------------------|

|                | 200                  | 15                | SCSI, ESDI, AT  | 10                     |

| 1.00           | 150                  | 15                | SCSI, ESDI, AT  | 10                     |

|                | 150                  | 15                | ST506/412 (RLL) | 7.5                    |

|                | 100                  | 15                | ST506/412 (MFM) | 5                      |

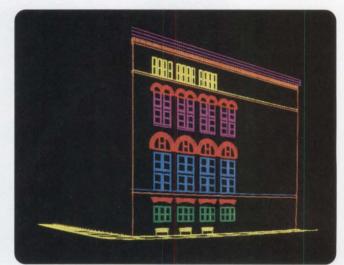

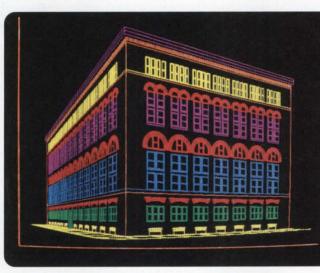

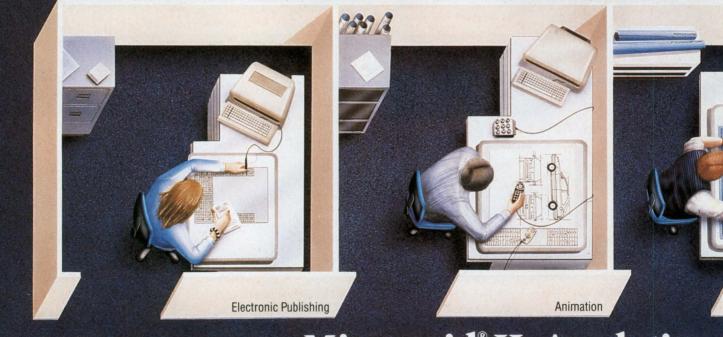

# In the time it takes other graphics engines to draw a few lines...

Texas Instruments TMS 34010 (2%)

AMD Am95C60 (17%)

Hitachi HD63484 (20%)

Intel 82786 (25%)

GeoCad perspective drawing courtesy of Rudolph Horowitz and Associates, Architects. Simulated performance based on maximum patterned line-drawing rates in an eight-bit color system with a resolution of 1024 by 768. Of course, performance ultimately depends on system elements like memory speed.

# ours gives you the whole picture.

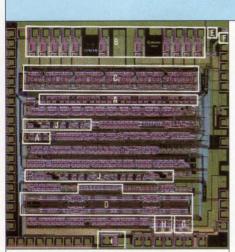

# THE FIRST FULLY PROGRAMMABLE GRAPHICS PROCESSOR WITH ON-CHIP ACCELERATION

You can have the fastest calculations in the world but if your system's graphics are slow, your system is slow. National's latest addition to its Advanced Graphics Chip Set—the DP8500 Raster Graphics Processor (RGP) —is the fastest graphics engine on the market.

This 20-Mhz CMOS chip features a bus cycle time of 100 nanoseconds on back-to-back vector and block operations.

It gives you blazing speed in line drawing, BitBLT, fills, polygons, character drawing, and windowing – regardless of the number of bit planes. It also controls screen refresh.

# COMPLETE FLEXIBILITY

The RGP gives you the programmability of a general-purpose processor, so you can optimize your system for specific applications. Or differentiate it from your competitors through proprietary algorithms.

The RGP, with our DP8511 BitBLT processing unit, is also the only

©1988 National Semiconductor Corporation

National DP8500 Raster Graphics Processor

graphics solution that effectively allows you to select either planaror pixel-oriented operation onthe-fly. So you no longer have to lock yourself into one architecture or the other.

The RGP handles the very highest-resolution CRTs and printers, including laser printers. And it supports any type of memory.

It also gives you the right "hooks" and the right architecture for moving into 3D and solids modeling applications.

# A COMPLETE SET OF CHIPS

Our Advanced Graphics Chip Set also includes

- two BitBLT processing units

- four video clock generators

- four video shift registers

- three video RAM controllers

- a growing list of video DACs

They're all part of National's unique modular approach — the only approach that addresses the complete graphics pipeline. And the only one with the performance and flexibility you need to carry you into the 1990s.

# COMPLETE SUPPORT

We offer a wide range of software tools — including assembler, debugger, librarian, linker, software

utilities, graphics kernel packages, and a C compiler package.

Nova Graphics International is providing full support for graphics software standards, including GKS and CGI.

Check it all out for yourself with the DP850EB demo/evaluation board for only \$1495. Buy the board and we'll include a coupon good for ten free RGPs on your first order of 100 or more.

To order today, call National Semiconductor at (408) 721-5404. Or for a copy of our system-level comparison brochure, circle the reader service number.

CIRCLE NO. 5

# EFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEW

# Graphics processor to team with dedicated floating-point chip

A full 32-bit version of the 34010 graphics processor from Texas Instruments (Dallas, TX), the 34020, will be teamed with the 34082, a specially designed 40-MFlops floating-point coprocessor. The math chip connects directly to the 34020's data and address lines without glue logic.

In addition to supporting the IEEE floating-point standard, the 34082 contains microcoded functions to support three-dimensional graphics. These include matrix operations for clipping, scaling and rotation; vector operations for lighting calculations; and splines for curved surfaces.

In addition, the floating-point chip boasts 100-ns cycle times and addresses up to 64k 32-bit words of external microcode for user-written algorithms.—Tom Williams

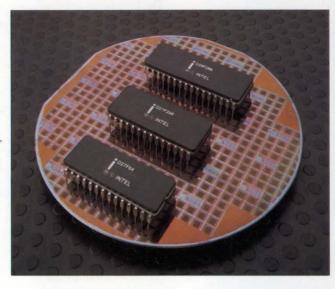

# Intel reorganizes ASIC effort, drops gate array services

Citing a mismatch between market needs and the company's high-performance—and high-priced—gate array operation, Intel (Santa Clara, CA) has withdrawn from the merchant gate array business and reorganized its application-specific IC products group.

Cell-based ASIC operations and programmable logic products will be unaffected by the move, except for a change in reporting structure. The gate array product team will essentially become a captive supplier to Intel's other product divisions, providing tools and processes for development of application-specific standard products.—*Ron Wilson*

# Sun OEMs and VARs rethink the future

Sun Microsystems (Mountain View, CA) has opted not to support equal access to its disk controller aftermarket. This decision, plus Sun's prominent position in the ongoing hullabaloo over the next version of Unix, has some Sun VARs and OEMs rethinking their long-term strategy.

Those who have become successful by building systems on a Sun platform will have to reevaluate both their commitment to opensystems architecture and their feelings about the relative safety and inflexibility of accepting dictated solutions. They will also have to decide whether it's in their long-term interests to move to a new workstation platform, instead of, or in addition to, Sun.—David Lieberman

# FDDI chip set due in final form

Just 13 months after sending the Supernet Fiber Distributed Data Interface (FDDI) chip set to beta sites for evaluation, testing and debugging, Advanced Micro Devices (Sunnyvale, CA) will release a final revision to all customers.

The revised silicon, which will start volume shipment in December, will contain only three sublayers of the four-layer standard expected to be released by Accredited Standards Committee X3T9.5 and accepted by the International Standards Organization, according to Patrick Green, AMD strategic development manager for FDDI products. These three will be the physical media dependent layer, the physical layer and the media access controller layer.

Since the still-unapproved fourth layer—station management—can be handled by software workarounds, AMD won't wait for that layer's definition and acceptance and will leave it out of the revised chip set. —Sydney Shapiro

# VME II—the bus that never was

The VMEbus community reports that the rumor of an impending "VME II" was a temporary, and regrettable, glitch. The bus expected to become the high-end, 32-bit asynchronous bus-of-choice already has a name—Futurebus—and most agree that calling it VME II would suggest relationships and compatibilities that don't exist.

"It would be a mistake to do what Intel did with Multibus and Multibus II, whose only relationship is that Intel developed them both. All that did was confuse the customer," says one industry observer. —David Lieberman

# Toolset provides foundry-independent ASIC development

A new toolset from Mentor Graphics (Beaverton, OR) may help change the way application-specific ICs are designed. While designers today must select an ASIC foundry before beginning schematic capture, Mentor's ASIC Vendor-Independent Designer (Avid) software lets that decision be put off until later in the design cycle.

Avid provides a library of generic schematic symbols that can be mapped into a selected vendor's component models following schematic entry and functional simulation.

ASIC vendors formally committed to supporting Avid include Fujitsu, GE Solid State, Gould, Intel and Toshiba.—*Richard Goering*

# **Could Unix be replaced?**

That heretical thought has come up amid rumors that a workstation from Next (Palo Alto, CA), whose announcement is also rumored to be imminent, will use the Mach operating system developed at Carnegie-Mellon University. While not Unix, Mach is said to offer binary compatibility with BSD 4.3 Unix and have virtually all functions of Unix and then some.

The system, which features interprocess communication, is based on an object-oriented model similar to Smalltalk developed by Xerox (Rochester, NY).

There's no word yet as to what kind of user interface the Next machine may use, but Mach is said to be able to easily run one of many known visual interfaces such as Sun's NeWS, IBM's Presentation Manager or the Macintosh Finder. Bets are that the system won't run the latter.—Tom Williams

# Interface to link logic synthesis with VHDL

Two of the hottest trends in the electronic design automation indus-

**COMPUTER DESIGN**

**COMPUTER DESIGN**

A CONTRACTOR DANGE MAX AND ADA MOTO DE ALTIME (CENTE S

ASIC BUYERS GUIDE: ASIC BUYERS GUIDE: FINDING YOUR WAY FINDING YOUR AND PARTS TO THE BEST TOOLS AND PARTS

THE FIRST MAGAZINE OF SYSTEM DESIGN, DEVELOPMENT AND INTEGRATION

- There are publications that focus exclusively on ASICs.

- There are publications that talk about board-level computers.

- SUB OU THE There are publications that cover software only.

- There are publications that inundate you with news about people and business.

**COMPUTER DESIGN** is the ONLY publication that's devoted exclusively to all of the things you do-design and integrate systems that incorporate microprocessors, ASICs, single-board computers, OEM computers and software. And COMPUTER DESIGN is particularly useful if you supervise or manage system design and integration projects because it goes beyond the "how-to".

COMPUTER DESIGN zeros in on the "why-to" of design: on the suitability of a technology or design strategy; on alternative solutions; on build-or-buy trade-offs, and on cost/performance trade-offs.

# IN EVERY ISSUE OF COMPUTER DESIGN, YOU'LL FIND:

# **TECHNOLOGY FOCUS REPORTS**

These in-depth articles highlight a technology area of importance to COMPUTER DESIGN readers. Tech Focus Reports provide timely analysis of technology news and market-related factors which may affect design choices and decisions. These articles include snapshots highlighting "real-life" applications, which delve into the problems, trade-offs, solutions and experiences of a typical user, and offer insight into the way the technology discussed is actually applied.

# SPECIAL REPORTS

These comprehensive features explore the technology and design issues that are of major importance to COMPUTER DESIGN readers. They provide in-depth analyses that examine the directions in which key technologies are driving microprocessor- and computer-based product design and development. The emphasis in these reports is on design trade-offs and the build-or-buy decisions senior engineers and engineering managers must always make when choosing a technology approach or implementing an overall design strategy. These reports highlight the most important or controversial issues, assess the impact of technological developments, and offer insights on how real-life design decisions are made.

# PRODUCT FOCUS REPORTS

Included in every issue, Product Focus Reports complement the coverage provided in other reports and the Buying Guides by stressing product features, specifications, availability and price for products such as standard ICs, disk drives, power supplies, and oscilloscopes.

## **REGULAR MONTHLY COLUMNS**

Design for Testability ASICs in Systems Technology Market Forecasts

# PLUS, COMPREHENSIVE BUYING GUIDES SIX TIMES A YEAR....

The Buying Guides are targeted at the special needs of engineering teams that design board-level products using microprocessors, peripheral ICs and ASICs, and build systems around single-board computers and peripheral boards. These Buying Guides are especially useful to senior engineers and engineering managers because they present key specifications, performance characteristics and prices in a concise, organized fashion, which makes product comparisons quick and easy.

# HERE'S HOW TO GET YOUR FREE SUBSCRIPTION

Just complete the enclosed subscription form today (please be sure you answer all questions). Then sign, date and drop it in the mail.

If you are already a subscriber, please pass the subscription form on to anyone else in your organization who needs up-to-date information on ICs, ASICs, single-board computers, OEM computers or software.

# EFS NEWS BRIEFS NEWS BRIEFS NEWS BRIEFS NEI

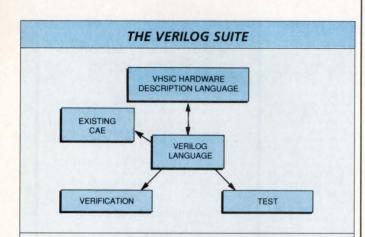

try—logic synthesis and the VHSIC Hardware Description Language (VHDL)—will be brought together as the result of an agreement between Silc Technologies (Burlington, MA) and Vantage Analysis Systems (Fremont, CA).

The two companies will build an interface between Silc's Silcsyn product, which can synthesize gatelevel logic from behavioral descriptions, and the Vantage Spreadsheet, a VHDL simulation environment. This interface will eventually let users describe designs using VHDL and have Silcsyn automatically generate the gate-level logic.

Both toolsets run on workstations from Mentor Graphics (Beaverton, OR).—*Richard Goering*

# New platform may be antidote for workstation vendors' woes

Competition is intensifying in the workstation market, and nobody knows this better than Apollo Computer (Chelmsford, MA). After unexpectedly low second-quarter earnings, Apollo unveiled two new product families that it expects will be price/performance leaders for the near term.

Built around a 33-MHz MC68030 CPU and a 33-MHz MC68882 floating-point coprocessor, the Series 4500 delivers up to 7-Mips performance. Prices for the series start at about \$19,000.

A lower-cost series features a 25-MHz MC68030, a 25-MHz 68882 and 4 to 32 Mbytes of main memory. The 4-Mips Series 3500 sells for under \$8,000.—John Mayer

# Math software wins flurry of big-name approval

Heavy hitters from seven major computer firms turned out at the recent introduction of a new math software package to announce their support. Mathematica from Wolfram Research (Cupertino, CA) can function both as an application program and as a programming language to form the basis of more specialized applications. It can do numerical calculations at arbitrary precision, perform symbolic math on algebraic formulae and graph functions interchangeably.

Steve Jobs, president of Next (Palo Alto, CA), announced his company will be bundling the package with the long-awaited Next workstation. Jobs stressed Mathematica's importance as the basis for a new generation of applications that will use intense mathematics.

Addison-Wesley (Redwood City, CA) will be publishing a new calculus that will use the interactive features of the package. Other companies supporting Mathematica include IBM, Silicon Graphics, Ardent Computer, Apple Computer and Sun Microsystems.—*Tom Williams*

# Program established for application-specific memory design

Standard-memory IC vendors will have to alter their approach to vendor-customer relationships if the promising application-specific memories market takes off. That at least seems to be the assumption underlying a new program developed by NEC Electronics (Mountain View, CA).

Under the program, a team of the company's design managers will work with customers to identify and design products to specific system memory needs. One example would be to embed processing elements right in a memory array. The application-specific memory designs will then draw on NEC's dynamic RAM and static RAM expertise at company facilities in Japan and Roseville, CA.—John Mayer

# Altera allies with TI on erasable PLDs

Altera (Santa Clara, CA), which is just beginning to branch out from relatively conservative architectures into larger-scale PALs and application-specific programmable logic devices, must face challenges both from standard-parts vendors that are beginning to add programmable logic to their devices and from radical new, gate-array-like PLD architectures. In an apparent effort to recruit additional allies in this growing war over programmable logic architectures, Altera has formed a strategic alliance with Texas Instruments (Dallas, TX).

Under the agreement, TI will manufacture and distribute certain of Altera's high-density PLDs. Adding the TI alliance to a similar existing relationship with Intel (Folsom, CA) may give Altera marketing and distribution strength to supplement its architectural moves.—*Ron Wilson*

# DEC ponders purchase of RISC chip

Rumors persist that Digital Equipment Corp (Maynard, MA) may finally move away from its proprietary microprocessor and build products around a reduced-instruction-set computer chip. The likely candidate appears to be the R3000 CPU from Mips Computer (Sunnyvale, CA), allegedly capable of yielding 20 VAX Mips, or 20 times the integer performance of a DEC VAX-11/780.

Feeding the rumors was DEC's recent cancellation of two development projects, one to develop a faster VAX and a second to build an in-house RISC CPU. If DEC does decide to go the RISC route, questions about compatibility will be the first to surface. The company has made dramatic inroads on competitors in recent years on the strength of its product lines' uniquely compatible VAX design.—John Mayer

# Desktop parallel machine supports portable software

Cogent Research (Beaverton, OR) is trying to bring software portability into the parallel market by combining a parallel-processing software, called Linda, with its XTM workstations. Other parallel processors use proprietary software to take advantage of a system's unique architecture, but that approach produces software that's incompatible with all other parallel machines.

Linda isolates the peculiarity of particular parallel architectures from applications software, letting the same programs run on any Linda-based processor. Though this concept has been adopted by others, Cogent is the first to implement the methodology in a desktop machine.—*Michael Donlin*

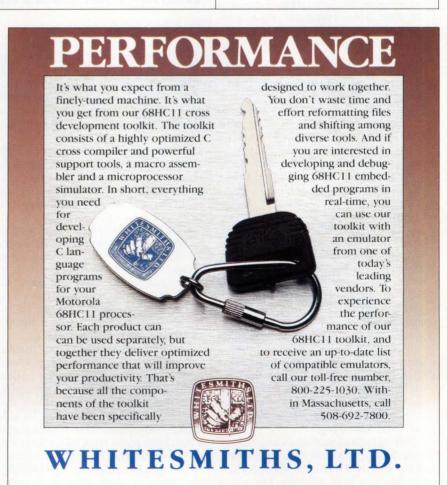

# Object-Oriented Engineering Not all object-oriented pro-gramming environments are created equal. Especially when it comes

Without Objective-C, you could be missing something important.

to features and support.

Unfortunately, many software engineers find this out too late.

Avoid missing out by using Objective-C. It's the most advanced object-oriented environment for C programmers available today.

And it will be tomorrow.

Our business is object-oriented technology, so we have the know-how and desire to keep you at the leading edge.

Objective-C is 100% compatible with the new ANSI C standard. So you can freely intermix objectoriented code with "straight C." And combine new object-oriented programs with existing C code.

Objective-C provides powerful type checking and compile-time error detection independent of your C compiler. Plus, you can choose between static and dynamic binding.

Even better, you get powerful memory management features ranging from a memory leakage detector to a set of state-of-the-art garbage collectors.

There's also built-in support to automate the complexities of releasing multiply-owned objects. And built-in support for your own runtime memory manager.

Objective-C puts you in control. You determine just how much of the power of object-oriented engineering you want to use for each application.

So if you want your software to turn out as efficient and safe as you planned, get Objective-C.

You'll never know what you've been missing till vou do.

The Stepstone Corporation Objective-C is a registered trademark of The Stepstone Corporation. Stepstone is a trademark of The Stepstone Corporation.

75 Glen Road

Sandy Hook, CT 06482

203 426 1875

1800 BUY OBJECT

(1800 289 6253)

**CIRCLE NO. 7**

# "A CLEVER TOY, BUT WE EXPECTED SOMETHING THAT WOULD BE MUCH MORE USEFUL". AMERICAN JOURNALIST, 1879

# "IT'S A GREAT PRODUCT, BUT I DON'T WANT TO LEARN A WHOLE NEW LANGUAGE JUST TO USE IT." DESIGN ENGINEER, 1988

For years, people have been intrigued with the latest in technology. But, they've been less than enthusiastic about learning how to put it to good use. The Transputer from INMOS is no exception.

System designers agree that Transputer's are revolutionary, but the prospect of learning a new programming language has made some of them a little uneasy.

The truth is, Transputers can actually be easily programmed in most high level languages developed for standard microprocessors including C, Fortran and Pascal. And, since Transputers are so much more than standard microprocessors, we've also developed OCCAM.

But don't let that scare you. OCCAM actually eases the system designer's task by simplifying the representation and control of parallel systems. It's easy to learn and can be intermixed with the languages you already know. And OCCAM creates a whole new programming dimension. Because a program running in a Transputer is formally equivalent to an OCCAM process, a network of Transputers can be described directly as an OCCAM program.

Together with just one or more Transputers, the formal rules of OCCAM provide the design methodology for true concurrency and unlimited system extendability. And OCCAM programs do not have to be rewritten as Transputer-based systems grow to utilize future levels of integration.

So take another look at the Transputer with OCCAM. It's a revolutionary way of processing information. And it's easy to speak the language.

INMOS, Colorado Springs, Colorado 80935. Tel. 719-630-4000, Orange County 714-957-6018, Santa Clara 408-727-7771, Denver 303-368-0561, Minneapolis 612-932-7121, Dallas 214-490-9522, Boston 617-229-2550, Baltimore 301-995-6952, Atlanta 404-242-7444.

INMOS Transputer Cand IMS are trademarks of the INMOS Group of Companies.

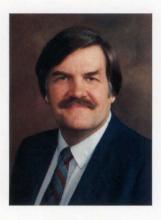

"Just because we have to be serious doesn't mean we have to be stodgy."

John C. Miklosz Associate Publisher/ Editor-in-Chief

# A change in style but not in substance

We've talked about it for a long time and now we've done it. *It* is *Computer Design*'s new look. It's a look that's contemporary and makes for easier reading, but isn't flamboyant or too flashy. After all, *Computer Design* is targeted at senior design engineers and design engineering managers like yourself. You're serious about the technical decisions you have to make, and *Computer Design* is serious about bringing you the kind of information that will help you in making those decisions. The look and the content of *Computer Design* have to work together, but just because we have to be serious doesn't mean we have to be stodgy. We think we've achieved the right balance and the right look. We hope you agree.

It took some doing, and some key people working together: Bruce Sanders, the publication designer who turned verbal expressions of abstract descriptions into type and layouts; Jan Horner, our art director, and Jan Lopez, our production director, the two people who kept everything moving through design, typesetting and layout; Jan Kasiecki, our expert in composition who formatted the new pages on our page-makeup equipment; and Mari Rodriguez, our production manager, who saw to it that every detail of editorial, art, photography and type came together correctly at just the right time for this first issue—and who'll be doing the same for future issues. And finally, Susan Nykamp, our managing editor, and our indefatigable copy editors: Richard Dagley, Kerstin Rosenquist and Barbara-Ann Scofidio, all of whom had to struggle with unfamiliar type specs, new layouts and different ideas about graphics without missing a beat in the regular schedule.

But a word of reassurance among all of this hoopla about redesign. We've made some major alterations in our appearance, but we haven't changed our editorial charter. That charter, summed up in the subtly different tag line that you'll find right under the *Computer Design* logo, is to be "the first magazine of system design, development and integration." Since our first issue, published in 1962, *Computer Design* has taken the "systems" view. It's a view that treats hardware design, software development and hardware/software integration—at all levels, whether chip, board or box—as inseparable aspects of the product creation and development cycle. Some other publications have apparently heard our message because they now include the word "systems" in their names. But *Computer Design* was the first—and will remain the first. The first magazine of system design, development and integration.

John Mikling

# The Complete UNIX/Real-Time Connection.

# **OS-9 UniBridge**

Integrating UNIX and C applications into VMEbus systems has just been made easier with Microware's introduction of UniBridge. UniBridge is a complete development and communications package that allows you to connect your SUN 3, DEC VAX, HP 9000 or Motorola Delta workstation, to the world's premier real-time operating system: OS-9.

UniBridge provides a gateway so you can utilize UNIX in every phase of VMEbus

system integration. From hosting C application development to monitoring large real-time networks, UniBridge connects UNIX to your OS-9 target system; whether it's ROM-based, disk-based, networked or stand alone.

UniBridge contains three high performance software modules that link UNIX and OS-9:

- OS-9/XCC Cross C Compiler allows you to produce compact, re-entrant and position independent C applications on your workstation for high speed execution on your OS-9 target.

- OS-9/ESP Ethernet Support Package provides industry standard BSD 4.2 sockets for TCP/IP communications with full FTP and Telnet support. UniBridge lets your workstation become a real-time server.

- OS-9/SRCDBG debugs resident VMEbus applications at the C source level, all interactively, across the Ethernet network from your UNIX terminal. And UniBridge makes all file access and transfer transparent from system to system while you debug.

OS-9 and UniBridge are trademarks of Microware Systems Corporation. VAX and VMS are trademarks of Digital Equipment Corporation. UNIX is a trademark of Bell Laboratories. Sun is a trademark of Sun Microsystems, Inc

**Microware Systems Corporation** 1900 N.W. 114th Street Des Moines, IA 50322 Phone: 515-224-1929

Microware Western Regional Office — Santa Clara, CA 408/980-0201; Microware Japan 0474 (22) 1747

Distributors: West Germany 06221-862091; France (1) 43-33-96-38; Italy (6) 762221; Switzerland (056) 83-3377; Sweden (018) 138595; Australia (02) 919-4917 **CIRCLE NO. 10**

- **OS-9 utilizes common UNIX features:**  Multi-user, Multi-tasking Pipes and Signals UNIX I/O model Shell User Interface • UNIX task model: Hierarchical Disk File System (fork, set priority,...) ... and more to connect you to Real-Time: Fast task switching Fast interrupt servicing

- Data modules

- Easy system generation and reconfiguration

- Events and semaphores

- Resident OS-9 compilers, assemblers and debuggers

And no other operating system complements UNIX with real-time functionality better than OS-9. OS-9, like UNIX, is a complete operating system to provide extensive C and math libraries, independent file managers, inter-process communications, debuggers and resident compilers. Yet OS-9 is 100% ROMable and executes in real-time to host thousands of imaging, process control, data acquisition, communications and robotics projects worldwide.

Best of all, every module of UniBridge and OS-9 is written entirely by Microware to provide you one source for technical support and service.

From UNIX and C, to OS-9 and VME, contact Microware today and let your next real-time application shine with UniBridge: The Complete UNIX/Real-Time Connection.

# LETTERS

#### Accuracy and ease-of-use

We are writing to you concerning Richard Goering's article entitled "Behavioral simulation speeds pathdelay modeling," (*Computer Design*, April 1, p 33). Although it was generally a fair and unbiased report, a single sentence in the article incorrectly implied that the Cadnetix method for behavioral model development might result in inaccurate models. We would like to set the record straight.

During the process of design tool development, Cadnetix' focus has traditionally been twofold: to produce a technologically advanced application tool that is also easy to use. For this reason, Cadnetix developed a heuristic method for creating behavioral models. This approach allows Cadnetix users to automatically model most parts to 100 percent accuracy, at a very rapid rate. As cited in your article, this is the case because the system heuristics do not automatically address certain situations (e.g., transmitting from floating to unknown states). In these instances, the user can add his or her own rules, with a minimum of effort, to complete the model(s) in question. Cadnetix has chosen this approach in order to offer customers both ease of use-the hallmark of all Cadnetix tools-and 100 percent model accuracy. **David Niehaus**

CAE Product Marketing Manager Chuck Robertson CAE Product Development Cadnetix Boulder, CO

# **Recognizing two misconceptions**

I enjoyed the Special Report on Object Recognition (*Computer Design*, May 1, p 69). The article does, however, reinforce two common misconceptions about object recognition. Both of these are exemplified by the statement in the second paragraph: "All practical image processing works with grayscale images."

First, image processing and object recognition aren't synonymous. Image processing customarily implies modification of one image to produce a new image. It is used to enhance certain diagnostic features relative to other features. Image processing is often, but not always, used as part of traditional object recognition procedures.

Second, it is no longer true that all

practical object recognition works with gray-scale images. Use of color often facilitates recognition of objects and, in many cases, can entirely eliminate the need for image processing in the recognition process. Color frame grabbers for PCs have been available for several years from such manufacturers as Truevision (Indianapolis, IN). Recently, Data Translation (Marlboro, MA) and Coreco (Longueuil, Quebec) have added color frame grabbers to their product lines. *Robert K. McConnell Arlington, MA*

# Congratulations

You've done a lot with *Computer Design* in the last several years and are to be congratulated for not only the technical quality of the magazine but for your willingness to speak out on issues of conscience. It seems that technology is ever in danger of becoming its own god. If we are to be masters of technology, rather than be mastered by it, we must always be mindful of the consequences.

**David Barnes**

Manager, Marketing Communications Advanced Processor Division, Intergraph Palo Alto, CA

#### Sign me up

I have been using copies of your magazine at other institutions very productively for about a year, and I would like to compliment you on a fine publication. *Computer Design* has been so useful, in fact, that I wonder if you would consider adding me to your "qualified subscriber" list.

I am an investigator on NIH-funded research in lung physiology, and the work involves acquiring, setting up, and running a digital image-processing workstation in my lab, with a couple of different image sources. The system will probably be a Sun-3/150 with Vicom image-processing board set and software, a Sky array processor, and an Interphase H-SMD interface, with a 330-Mbyte hard disk, 4-Mbyte system memory and 8-Mbyte image memory to start with. I do much of the programming and have done the investigations and winnowing out that led to these choices, so your magazine could be quite a help. Eben H. Oldmixon

Memorial Hospital of Rhode Island Pawtucket, RI

PUBLISHER David L. Allen

ASSOCIATE PUBLISHER/EDITOR-IN-CHIEF: John C. Miklosz

#### TECHNOLOGY EDITORS:

Ron Wilson, Integrated Circuits (Portland) Richard Goering, Design & Development (Santa Clara) David Lieberman, Computers & Subsystems Tom Williams, Graphics & Imaging (Santa Clara) John H. Mayer, Computers & Subsystems Sydney F. Shapiro, Data Acquisition & Control

#### CONTRIBUTING EDITORS:

Warren Andrews, Integrated Circuits S. Louis Martin, Integrated Circuits William Harding, Design & Development Howard Falk, Software Art DeSena, Testing & Manufacturing

RESEARCH/SPECIAL PROJECTS MANAGER: Sydney F. Shapiro

SECTION/SPECIAL PROJECT EDITORS: Ron Wilson, Technology Updates

David Lieberman, Contributed Articles Michael G. Donlin, New Products Patti Villandry, Directories

MANAGING EDITOR: Susan R. Nykamp

COPY EDITORS: Richard Dagley, Kerstin L. Rosenquist, Barbara-Ann Scofidio

EDITORIAL ASSISTANTS: Claire Coupal, Claire Ellis

#### WEST COAST OFFICES MANAGING EDITOR: Tom Williams

3333 Bowers Ave, Suite 100 Santa Clara, CA 95054, Tel: (408) 982-0288

1111 S.W. Gaines, No. 8 Portland, OR 97201, Tel: (503) 224-9396

> ART DIRECTOR: Jan Horner ILLUSTRATOR: Christopher Hipp

PRODUCTION DIRECTOR: Jan M. Lopez PRODUCTION MANAGER: Mari Rodriguez ADVERTISING COORDINATOR: Shari L. Hasche COMPOSITION MANAGER: Holly Kersey COMPOSITION/REDESIGN: Jan Kasiecki COVER ART: John Bonner

CIRCULATION DIRECTOR: Robert P. Dromgoole Postmaster: Send change of address form 3579 to COMPUTER DESIGN, Circulation Department, Box 3466, Tulsa, OK 74101

Advanced Technology Group L. John Ford, Senior Vice-President Leslie P. Cypret, Vice-President, Administration P.O. Box 417 119 Russell St, Littleton, MA 01460 Tel: (508) 486-9501 Fax: (508) 486-9397

# This powerful new graphics processor comes with one very important attachment.

# Your LAN.

Introducing the Vexcel GT — the most versatile graphics and data communications

system ever developed — from KMW Systems.

The Vexcel GT vector-to-raster converter provides an optional Ethernet LAN connection, which allows multiple users to share hardcopy output devices such as electrostatic plotters more productively than ever before.

The Vexcel GT is ideal for highdensity mapping and other complex electrical and mechanical CAD applications. Features of the Vexcel GT include:

- file transfer through standard Ethernet TCP/IP protocols

- support for both HPGL 7585/7586 and CGM

- multiple input and output capabilities

- optional external spooler with a capacity of up to 140 megabytes

- support for virtually all electrostatic plotters

- unattended overnight plotting abilities

- raster buffer storage for up to 200-dpi E-size plots or 400-dpi C-size plots

- internal disk subsystem for extremely dense plots

- full color support, with user-selectable opaque or transparent modes

# The latest solution from KMW.

The Vexcel GT is the newest graphics processor from KMW. If you don't require the extensive capabilities of the Vexcel GT, you'll find all the processing power you need with KMW's costeffective VP-10.

The VP-10 is perfect for less demanding applications, with the capability of driving color or monochrome printers or plotters up to 24" wide.

# Unmatched service and support.

You can count on KMW's dedicated field service team for support after the sale. We also offer a technical support hotline for immediate answers to your questions. KMW has been helping companies make the right connections for more than ten years, with graphic element processors, protocol converters, and channel interfaces. We have sales representatives across the nation, as well as in London. Call (800) 531-5167 for the sales office nearest you.

(800) 531-5167 In Texas, (512) 338-3000 CIRCLE NO. 11

# See us at SIGGRAPH, Booth #1418

Hewlett-Packard Graphics Language is a registered trademark of Hewlett-Packard. Plot data courtesy of Versacad. ©1988 KMW Systems Corporation

# FDDI. From deskwork to network.

Good news for networks!

The X3T9.5 Task Group, under the procedures of ANSI Accredited Standards Committee X3, has reaffirmed approval of the Media Interface Connector (MIC) for the proposed FDDI (Fiber Distributed Data Interface) Physical Layer Medium Dependent (PMD) document. More good news! AMP has the complete fiber optic interconnection system—the AMP OPTIMATE Fixed Shroud Duplex System—that meets all FDDI PMD requirements. And includes all the physical components you need to make your fiber optic network a reality.

Of special note: the transceiver —the first of its kind—is capable of operating at data rates up to 125 Mb/s. Available in standard or raised (+5v) ECL logic, it gives you a compact, board-mount data link in a single 24pin module. Reliable duplex mating and electro-optic conversion are now easier than ever.

You can also order complete, custom-built cable assemblies from us. Either way, you'll have the assured compatibility that comes from dealing with only one supplier for all your FDDI interconnection components. A supplier whose capability in fiber optic technology is everything you'd expect from the world's largest connector company.

For technical literature and more information, call 1-800-522-6752. AMP Incorporated, Harrisburg, PA 17105-3608.

# Interconnecting ideas

# For Long Life. In the Fast Lane.

Rev-up your system with Hitachi's durable new 382MB driving machine

> Hitacbi DK514-38 382MB 5.25" Wincbester 16ms seek 1.8MB/sec. transfer ESDI, E-SMD, SCSI interface 30,000 MTBF

> > **Fast Action:**

To get product literature immediately, CALL TOLL FREE 1-800-538-8157, Ext. 877. *In California*, 1-800-672-3470, Ext. 877. Ask for literature number PB-514.

Regional Sales Offices: Natick, MA 617/655-5501 • Dallas, TX 214/991-7983 • Brea, CA 714/993-1610 • San Bruno, CA 415/872-1902

Hitachi America, Ltd. Computer Division 950 Elm Avenue, Suite 100 San Bruno, CA 94066

Who says fast can't last? Not Hitachi. Our new DK514-38 382MB 5.25-inch drive brings you lightningfast performance with unbeatable reliability.

Sophisticated technology has cut average seek time to a scorching 16ms, and increased the data transfer rate to 1.8MB/sec. Normally, you'd expect such speed to cost endurance. Not with Hitachi. In-house design and production of all major components and the most stringent quality assurance program in the industry give the DK514-38 30,000-hour MTBF.

If your super-micro, mini or workstation demands a drive that can keep up with your processor, and do it over the long haul, our DK514-38 is one machine you can't afford to pass up.

To learn more about this powerful, dependable performer, contact your best partner for mass-storage solutions...Hitachi. We'll show you the right way to drive. Fast.

# COMPUTERS AND SUBSYSTEMS

# Application tuning: a key to RISC system development

Ron Wilson, Senior Editor

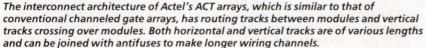

he fundamental principles of reduced-instruction-set computer design assume a smooth flow of instructions through the CPU. To achieve this flow at high CPU speeds, RISC designers rely on extensive instruction and data caches. But for this strategy to be effective, every part of the system, from instruction set to operating software to applications code, must work to minimize flushing and reloading of the caches. Designers at Pyramid Technology (Mountain View, CA) and Hewlett-Packard (Palo Alto, CA) have used system-level simulations with actual application-code samples to choose their cache-management strategies.

Pyramid has used actual application data extensively in the design of its new 9000TA processor family. The approach lets Pyramid's designers increase throughput substantially by tuning the instruction set, Unix-derived operating system and cache organization without major changes to the CPU execution unit. "We have performance gains of 30 to 100 percent on data base and network-serving applications, even though the underlying Mips figure has increased by only 5 percent," says Stephen Tolchin, vice-president of software development at Pyramid.

#### Tailoring cache to application

The performance enhancements in the 9000TA family were born during architectural research for an entirely different family of Pyramid products. "In the course of developing our next-generation product, we took instruction streams from Pyramid machines in production environments and ran the streams through four levels of simulation. We found that for many applications, we could make substantial improvements in throughput without an entirely new architecture," says William Gimple, vice-president of systems technology and product marketing.

"First, we made important changes in the way Unix schedules jobs for the CPUs in a system. Then we made hardware changes focusing on the organization of the instruction cache," he continues. Pyramid's investigation of the instruction streams showed that, while its two-way set-

"We have performance gains of 30 to 100 percent on data base and network-serving applications, even though the underlying Mips figure has increased by only 5 percent."

-Stephen Tolchin, Pyramid Technology

associative data cache was working well, its similar instruction cache wasn't suited for some applications. In data base applications in particular, Gimple's team discovered that the working set, which is the portion of an active program that is most frequently executed, was much larger than had been the case for more traditional Unix-based applications. This larger working set didn't fit in the instruction cache, resulting in a loss of efficiency.

# Eight-bank organization

The design team began trying various instruction cache designs with their simulation. They found that no matter how large they made a twoway set-associative cache, it still had problems with the large working sets. When a process became inactive, at least half of the instruction cache had to be invalidated.

The designers' novel solution was a 256-kbyte cache, organized into eight banks. Rather than being strictly set-associative, the banks are associated with a process identification code assigned by the operating system. Each active process in a CPU, therefore, can have its own

William Gimple, vice-president of systems technology and product marketing for Pyramid Technology, discusses performance evaluation results of the new caching subsystem Pyramid developed for its 9000TA processor family. By using application data extensively in designing the family, according to Gimple, Pyramid's designers increased throughput by tuning the instruction set, Unix-derived operating system and cache organization without major changes to the CPU extension unit.

# COMPUTERS AND SUBSYSTEMS

bank of instruction cache, even if many processes share the same virtual address range. The result is that when a process becomes inactive, only a small portion of the instruction cache has to be invalidated.

Another application-tailored design

The developers of the Precision Architecture at Hewlett-Packard were among the first to use comprehensive application-code samples to tune their system design. "The starting point for design of the Precision Architecture was an extensive set of code samples from actual applications running on existing HP systems. The data covered interactive and batch environments and contained code generated in all of the popular languages," says Michael McMahon, district manager for HP's information technology group.

The HP designers fed their code samples into an iterative process. "We would postulate an architecture from observations of the actual workload and then validate it with feedback from the software and hardware implementation groups," explains McMahon. This approach led to many of the key characteristics of the HP RISC CPU, including the design of the instruction set and the organization of the register file. In addition, the application data influenced certain system software decisions, such as the way registers are managed during a context switch.

#### Embedded-system implications

The experiences of HP and Pyramid designers indicate the value of tuning a RISC system with real application code samples rather than benchmarks. Both companies found that non-CPU issues such as contextswitching strategies and cache-management techniques have an impact on real system throughput in the commercial environment.

As RISC machines move into embedded applications, the same conclusions may remain valid. Like large data base and transactionprocessing installations, embedded computers tend to have a small set of tasks that must be performed within a fixed response time. Like commercial systems, embedded computer behavior has been notoriously hard to predict from benchmarks. And like the larger systems, embedded computers are known to be sensitive to such issues as context switching time and cache hit rates.

It may well be that system modeling and tuning using actual code samples will be a key tool in RISC embedded system development. This technique may offer designers a way to choose between on-chip and external caches, to select caching strategies, and to plan real-time kernel designs. Certainly if the technique can yield the kind of performance improvements reported by Pyramid, it's worth a try.

# PS/2 boards equipped for speed in data-acquisition tasks

Sydney F. Shapiro, Research/Special Projects Manager

Ithough the IBM PC is still by far the dominant controller for laboratory and small-tomedium factory data-acquisition systems, there's little question that system designers will eventually replace the PC with a faster, more versatile small computer. As would be expected, one contender—the Micro Channel-based IBM Personal System/2—has a major advantage over

Designers of dataacquisition systems will likely opt for boards that meet the PS/2 specifications because the Micro Channel bus can handle much higher throughputs than can the 16-bit AT bus.

#

any other computer competitor. Simply because it's an IBM product, the PS/2 is most likely to be the eventual successor to its elder sibling.

A main concern of users of dataacquisition systems is how quickly they can input and access data. One reason that designers of data-acquisition systems will likely opt for boards that meet the PS/2 specifications is the capability of the Micro Channel bus architecture to handle higher throughputs than can the 16-bit AT bus. That's particularly true with the 32-bit 80386-driven PS/2 Model 80 and the Model 70 386. While direct memory access on PCbased products is limited to about 400 kbytes/s (unless special, costly measures are taken), it's possible to routinely obtain throughputs of up to 1 Mbyte/s on the Micro Channel.

Multiple DMA channel capability of the Micro Channel bus architecture lends another advantage to the PS/2. The IBM PC AT provides only two DMA channels; the PS/2 has eight. A designer of a data-acquisition system, therefore, can provide multiple boards without worrying about one going fast because it's under DMA and another going slow because its I/O operations are limited by the CPU.

## PS/2 board threesome

National Instruments (Austin, TX) announced its first PS/2 data-acquisition board—the MC-GPIB IEEE-488 interface—last July, only a few months after IBM introduced the PS/2. Now, a year later, National has announced three very high speed data-acquisition boards that let IBM PS/2 Models 50 through 80—including Models 70 386 and 50 Z, which were introduced in June—handle time-critical laboratory and factory applications.

National Instruments' efforts haven't been limited to the PS/2. In fact, one-quarter of National's business has focused on boards for the Apple Computer Macintosh II and its Nubus, according to James Truchard, president. The company's expertise in designing data-acquisition boards for other buses, however, has aided in

# SPIE ANNOUNCES

# An International Symposium and Exhibition on Fiber Optics, Optoelectronics, and Laser Applications in Science and Engineering

6-10 September 1988 • Boston Marriott Copley Place Hotel • Boston, Massachusetts USA

Cooperating Organizations: Applied Optics Laboratory/New Mexico State University

Center for Applied Optics Studies/Rose-Hulman Institute of Technology

Center for Applied Optics/University of Alabama in Huntsville • Center for Electro-Optics/University of Dayton Center for Optical Data Processing/Carnegie Mellon University • Electro-Optics Technology Center/Tufts University Georgia Institute of Technology • The Institute of Optics/University of Rochester • Massachusetts Fiberoptic Council Optical Sciences Center/University of Arizona

## Two-Conference Program on Lasers and Applications

- Excimer Beam Applications Conference Chairs: Anthony Pirri, Physical Sciences, Inc.; Bernhard P. Piwczyk, Leitz-Image Micro Systems Co.

- Advances in Photochemotherapy *Conference Chair:* Tayyaba Hasan, Wellman Labs., Harvard Medical School and Massachusetts General Hospital

# Two-Conference Program on Laser Radar and Wavefront Control

- Laser Radar III

Conference Chair: Richard J. Becherer, Science Applications

International Corporation

- Laser Wavefront Control: Critical Reviews of Optical Science and Technology Conference Chair: John F. Reintjes, Naval Research Laboratory

# Four-Conference Program on Fiber and Laser Sensors

- High Bandwidth Analog Applications of Photonics II Conference Chair: Barry T. Neyer, Monsanto Research Corporation/Mound

- Fiber Optic and Laser Sensors VI Conference Chairs: Eric Udd, McDonnell Douglas Astronautics Company; Ramon DePaula, Optical Technologies, Inc.

- Fiber Optic Smart Structures and Skins Conference Chair: Eric Udd, McDonnell Douglas Astronautics Company

- Chemical, Biochemical, and Environmental Applications of Fibers

Conference Chair: R. A. Lieberman, AT&T Bell Laboratories; M. T. Wlodarczyk, General Motors Research Laboratories

# **Boston '88 Exhibition**

The O-E/FIBER LASE Exhibition, located in the hub of the Northeast fiber, laser, computer, and communications industries, will present a major exhibition of related products and services, while emphasizing device and equipment demonstrations and use.

Exhibit Coordination and Promotion by

"FIBERLASE" is a registered trademark of Pilkington Medical Systems.

FOR COMPLETE PROGRAM AND EXHIBIT INFORMATION contact SPIE, PO Box 10, Bellingham, WA 98227-0010, 206/676-3290, Telex 46-7053. In Europe contact SPIE, Koblenzer Strasse 34, D-5300 Bonn 2, FRG; Telephone (49) 228/36.15.46. Telex 172 283 747.

## Two-Conference Program on High Data Rate Atmospheric, Space, and Analog Communications

- High Data Rate Atmospheric and Space Communications Conference Chair: Robert Hauptman, Ford Aerospace and Communications Corporation

- High Frequency Analog Communications Conference Chair: Paul Sierak, Rome Air Development Center

# Four-Conference Program on Fiber Optic Communications

- Fiber Optic Datacom and Computer Networks Conference Chairs: J. E. Hayes, Fotec Inc.; J. Pazaris, Digital Equipment Corporation

- Components for Fiber Optic Applications and Coherent Lightwave Communications *Conference Chairs:* Paul M. Kopera, Amphenol Fiber Optic Products; Harish R. D. Sunak, University of Rhode Island

- Fiber Optic Systems for Mobile Platforms II Conference Chairs: Norris Lewis, Litton Poly-Scientific Division/Engineering and Research; Emery L. Moore, Litton Systems, Inc./Guidance and Control Systems Division

- Fiber Optics Reliability: Benign and Adverse Environments II Conference Chairs: Dilip K. Paul, COMSAT Laboratories; Roger A. Greenwell, Science & Engineering Associates, Inc.; Shekhar Wadekar, University of Delaware

#### Two-Conference Program on Integrated Optoelectronics

- Optoelectronic Materials and Devices, Packaging, and Interconnects II Conference Chairs: Glen McWright, Lawrence Livermore National Laboratory; Henry Wojtunik, Microwave Semiconductor Corporation

- Integrated Optical Circuit Engineering VI Conference Chair: Mark A. Mentzer, Sechan Electronics, Inc.

# COMPUTERS AND SUBSYSTEMS

the design of its new PS/2 boards. Designers used the knowledge gained from their development of Nubus boards to fit all the components required for high-speed data acquisition on the small-format boards used in the PS/2, Truchard says.

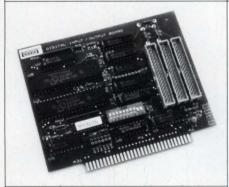

One of the three PS/2 boards introduced by National Instruments is the MC-MIO-16, a high-performance, multifunction analog, digital and timing I/O board with a Micro Channel DMA interface. Even though the Micro Channel card size is 29 percent smaller than that of the Macintosh II. all of the functions on the Nubus board have been included in this PS/2 board, according to Audrey Harvey. engineering group leader for data acquisitions. National accomplished this, she says, by reducing component counts on the MC-MIO-16 through the use of a commercially available PS/2 Micro Channel interface gate array.

■ Features lend speed and accuracy Two features of the MC-MIO-16 PS/2 board are software-programmable gain and analog-to-digital (A-D) firstin, first-out (FIFO) timing. With the PC versions, data-acquisition boards either had fixed gains determined by the values of resistors on the boards or hardware jumpers that had to be moved to change the gain. The latter solution meant that the boards had to be removed for every gain change, which endangered the accuracy of the gain setting unless the board was handled very carefully. With software-programmable gain, however, several gain settings can be set in advance, and there's no need to access the boards physically.

An A-D FIFO gives the PS/2 boards higher throughput speeds. With PC boards, data-acquisition and throughput speeds were limited by on-board counters that had to count down before a data conversion could be initiated. The converted data was then stored until the system was interrupted by a DMA request. If the computer could respond within one sample interval, there would be no need for a FIFO because the last value stored would then be read out before the next value arrived. But latency can be highly variable, and the timing sequence can't be assured. The A-D FIFO memory buffers the inputs and allows storage of up to 16 values before the memory has to be serviced by the computer. This increases by an order of 16 the time that can be

Although much of the expertise for development of National Instruments' line of dataacquisition boards for the IBM Personal System/2 Micro Channel bus architecture resulted from the company's experiences in designing similar boards for Apple Computer's Macintosh II, comparable functions could be included on the PS/2 boards only through use of Micro Channel interface gate arrays.

tolerated before data is lost.

The MC-MIO-16 also provides onboard timing, a flexible automatic channel-scanning system, doublebuffered D-A converters and timergenerated interrupts. It has a 12-bit A-D converter with 16 single-ended analog inputs, two 12-bit D-A converters, eight lines of TTL-compatible digital I/O and three 16-bit counter/timer channels.

Conversion times for three available versions of this board differ according to the speed of the on-board A-D converter. A 9- $\mu$ s board samples data acquired at a typical rate of 100 ksamples/s, a 15- $\mu$ s board samples at 71 ksamples/s, and a 25- $\mu$ s board samples at 45 ksamples/s.

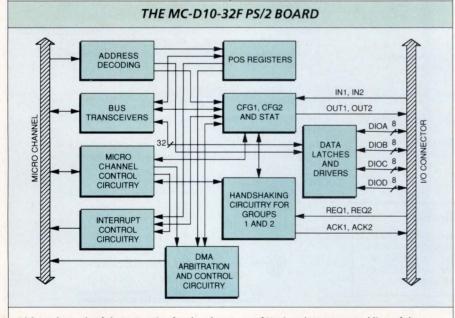

#### Completing the set

A second PS/2 board, the MC-DIO-32F, is a high-speed 32-bit parallel digital I/O interface that features a maximum DMA transfer rate of 400,000 16-bit words/s. Its 32 lines of digital I/O are divided into 4 bytes, with each byte programmable as input or output. Compatibility to a wide range of peripheral devices and other computers is attained through several digital I/O handshaking options. Two DMA channels can receive 16-bit transfers simultaneously.

Completing the picture is the MC-DIO-24, a 24-bit parallel digital I/O interface for applications that don't require more than a maximum transfer rate of 300 kbytes/s. A programmable peripheral interface controls 24 bits of digital I/O. This board can operate in either unidirectional or bidirectional mode and can generate interrupt requests.

A salient feature of these new boards, according to National Instruments' Harvey, is a timing bus that the company had first developed for Nubus data-acquisition boards. Conventional computer buses don't provide high-speed timing signals because they're more concerned with data transfers, addressing and interrupts. But data acquisition requires timing signals between boards, and timing buses provide the necessary paths for these signals. This feature, plus the inherent speed of the PS/2 Micro Channel, provide a solid platform for the PS/2 as the eventual successor to the PC and the PC AT for data-acquisition applications.

COMPUTERS AND SUBSYSTEMS

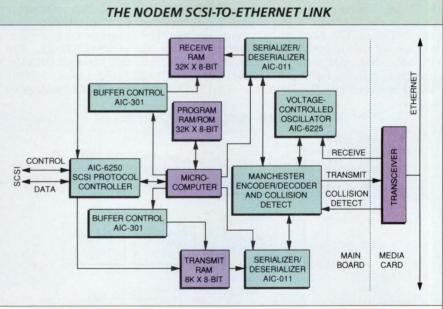

# SCSI adapter ties computers and peripherals into Ethernet

Tom Williams, Western Managing Editor

new, flexible LAN interface unit lets any device using the small computer system interface (SCSI) connect to any Ethernet network. The SCSI-based Nodem from Adaptec (Milpitas, CA) acts as an Ethernet interface for systems that already have SCSI. The connecting device can be a peripheral-such as a disk drive or a printer-or a computer system. When the device is a computer, network-based applications can be easily ported to Ethernet or written specifically for Ethernet by using protocols to Ethernet's datalink layer of the Open Systems Interconnection model.

Since SCSI supports eight devices per controller, a Nodem link to Ethernet can be daisy-chained with other SCSI devices such as disk or tape drives. The SCSI sees the Nodem as just another device on the SCSI bus.

# Low-cost interface to Ethernet

Adaptec developed the unit because the company saw a need for a lowcost interface to Ethernet from IBM PC XTs and PC ATs, Apple Macintoshes, minicomputers and so forth, according to Joe Carballosa, Adaptec's LAN product manager. Adaptec has initially targeted its hardware and software product for the Macintosh because it has a built-in SCSI port. The software lets applications written for the Appletalk protocols run unmodified on Ethernet.

Adaptec will also soon offer similar protocols for IBM PCs and compatibles running DOS, as well as for OS/2 and its LAN manager. Any computer with a SCSI adapter and software to access Ethernet will be able to use the Nodem. Initially, Adaptec will adapt popular network software to the Nodem, but third parties can also easily write or adapt applications to the Ethernet protocols.

Adaptec designed the Nodem interface without using any specialized Ethernet silicon. In addition to a microprocessor and memory, the Nodem uses Adaptec's AIC-6250 SCSI controller and AIC-011 serializer/deserializer (Serdes). The Serdes, which is used in SCSI disk controllers to encode sector formats, is flexible enough to encode the data packets Ethernet uses.

# A speed advantage

Connecting to Ethernet via the SCSI port gives microcomputers like the Macintosh a definite speed advantage. Because SCSI runs at about 8 Mbits/s (1 Mbyte/s) in its asyn-

In addition, the intelligent nature of SCSI fits well with a network such as Ethernet, which uses CSMA/CD (carrier sense multiple access/collision detect) protocols. Such networks are fairly unpredictable in terms of exactly when a request for access or data will be granted. SCSI's disconnect/reconnect ability lets an interface accept a request and data from the host, then free the host until, for example, the interface has obtained access to the network, has transmitted the packet, and needs more data. The interface then can "reconnect" with the host by issuing an interrupt without the host having to poll it. By the same token, the host doesn't need to get involved with trying to gain ac-

chronous mode, it's on a fair speed parity with Ethernet and lets systems take nearly full advantage of Ethernet's 10-Mbit/s bandwidth. SCSI II, expected to run at around 4 Mbytes/s in synchronous mode, will have speed to spare. Applications that use Appletalk can run at only 230 kbits/s using Localtalk, Apple's physical and data-link architecture. This difference in speed means that 254 Appletalk nodes can be connected via Ethernet, compared to only 32 connected via Localtalk. cess. SCSI also has a target/initiator mode that allows easy peer-topeer communication: any SCSI device can either initiate a connection or be the target of a communication.

Adaptec plans to expand the SCSIto-Ethernet link to include other LAN standards such as IEEE 802.5 token ring, according to Carballosa. Since a single SCSI host adapter can accept up to eight devices, multiple Nodems could be placed on a single host to act as gateways between different network architectures.

# INTEGRATED CIRCUITS

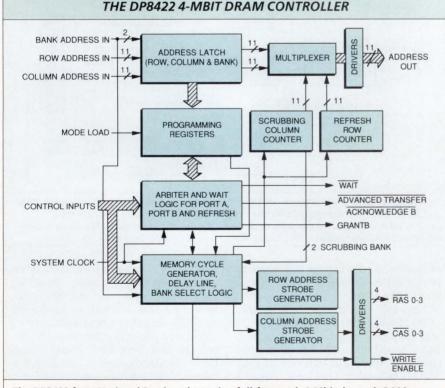

# Fast, full-featured 4-Mbit DRAM controllers begin to surface

S. Louis Martin, Contributing Editor

he first 1-Mbit dynamic RAM controller appeared just two years ago, with the inconspicuous introduction of the huge, complex WE32103 chip from AT&T (Berkeley Heights, NJ). Designers generally felt, however, that the AT&T part was overkill for their needs. National Semiconductor (Santa Clara, CA) and Monolithic Memories (Santa Clara, CA) were the next vendors to introduce competitive 1-Mbit DRAM controllers, followed about a year later by Advanced Micro Devices (Sunnyvale, CA) and Texas Instruments (Dallas, TX). Now, with the approaching availability of 4-Mbit DRAMs, National is first to introduce a controller for those devices, and a newcomer to the DRAM controller market—Korean Samsung Semiconductor (San Jose, CA)—is in hot pursuit.

Considering the huge consumption of DRAMs as opposed to static RAMs and other types of memories, it's surprising that there are relatively few vendors offering controllers for DRAMs. Clearly, Samsung and National Semiconductor have recognized the importance of the DRAM controller at an opportune time.

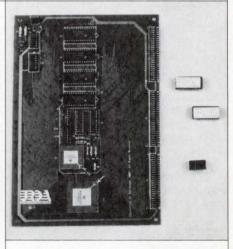

For each new generation of DRAMs, National Semiconductor has consistently produced controllers. The company's latest offerings are the DP8420/21/22. The DP8420 addresses 256-kbit DRAMs; the DP8421 addresses 1-Mbit DRAMs; and the DP8422 addresses

the upcoming 4-Mbit devices. The devices are functionally identical, except for the DP8422's provision for dual-accessing.

#### New features lend flexibility

The previous generation of controllers from National (the DP8428 and DP8429) offered the basics of DRAM support, such as DRAM drivers, refresh counters, row/column multiplexing and multiple rowaddress strobe (RAS) lines for activating multiple banks of DRAMs. The new generation offers important additional features, many of which National and Monolithic Memories criticized as overkill in the AT&T chip two years ago. However, the new design keeps the pin count down to 84 pins on the DP8422, compared to the AT&T part's 132 pins.

Probably the most striking new feature of the National part is its programmability. "It allows the controller to be interfaced to all the major processors," says Timothy Garverick, design engineering manager at National. This is accomplished by loading a 22-bit register at power-up.

Another new feature of the DP8422 is dual-port access, which is particularly useful in cases where two independent processors need to access the same bank of DRAM. This isn't an uncommon situation, according to Garverick. "Laser printer applications in particular benefit from dualport access," he says. For instance, when National's 32CG16, which is a special processor for graphics, is used in conjunction with another generalpurpose processor, dual-port access lets both processors access memory through a single DRAM controller.

The National device features access/refresh arbitration, a process that's new to industry, according to Michael Sodergren, National's manager of interface product marketing. Access/refresh arbitration is accomplished by providing a wait signal to the processor during refresh operation to hold off access. Providing the arbitration signal from the DRAM controller saves at least one chip in the memory-system design.

The DP8420/21/22 also provide four column-address strobe (CAS) outputs, CAS0-3, which can be asserted independently. Each CAS output can be used to select 1 byte from a 32-bit-wide memory, letting the memory system respond with any combination of the 4 bytes in a word. The CAS outputs were a feature of the previous-generation Monolithic Memories part that National chose to add to its latest controller.

#### Determining in-circuit speed

National rates the latest version of the controllers, due for availability sometime soon, at 25 MHz. While this is a succint way to state the speed of the parts, it doesn't tell the designer much about how fast the controller will work in-circuit. For that information, designers have relied on other figures entirely.

In the older generation of controllers, the favorite basis of comparison was the delay time between the RAS input and the assertion of CAS low, often referred to as tRICL. But in the new-generation chips that include their own microprocessor interface, the most appropriate measure is the delay between address strobe low and CAS low, known as tPADSCL.

Because National's parts are programmable, the picture is more complicated. The RAS address hold time (tRAH) and the address setup to CAS time (tASC), programmable in the new devices to accommodate different types of DRAMs, both affect tPADSCL. So the speed of the part has to be stated with reference to its programming. For instance, when tRAH is programmed to be 15 ns and tASC is programmed to be 0 ns—a fairly typical setting for conventional DRAMs—tPADSCL is 79 ns for the 25-MHz National part.

An even more meaningful measure of performance can be obtained by calculating the required number of wait states for a particular processor that's operating at a specified frequency and working with DRAMs with a specified access time, according to Garverick. For instance, an 80386 processor operating at 20 MHz and using 100-ns DRAMs will need one wait state in pipelined access mode and two wait states in nonpipelined mode.

The DP8420/21/22 are CMOS devices. The price for the DP8422 is \$25.30 in quantities of 1,000 for the 25-MHz part.

Samsung Semiconductor sees its

# INTEGRATED CIRCUITS

"We expect that once we go through the normal cycle of process optimization, we should be up around 40 MHz."

-Mike Levis, Samsung Semiconductor

#

entry into the DRAM controller market as an important step. "Samsung is a very large supplier of memory products, and our intent here is to position ourselves as the leading supplier of memory-system components," says Mike Levis, product marketing manager.

Samsung is about to introduce 1and 4-Mbit DRAM controllers, the KS84C21 and the KS84C22, respectively. The Samsung devices are quite similar to the National devices, according to Levis. "Our parts are a superset of National's implementation, and we have a lot of added features," he says. While the word "superset" may overstate Samsung's case, the parts do combine many of National's features with some exclusive to the Korean vendor.

Multiple RAS and CAS (RAS0-4 and CAS0-4) will be available on the new parts, just like on the National parts, allowing for multiple bank selection (up to four banks) and for byte access as well as word access. Any combination of bytes within a 32-bit word, as well as the entire 32-bit word, may be selected.

The first product to be available will be a 25-MHz device, like the upcoming revision of the National part, but Samsung also expects to introduce a 40-MHz version soon. Current silicon tests at just under 40 MHz, claims Levis. "We expect that

CIRCLE NO. 15

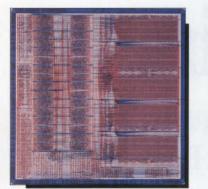

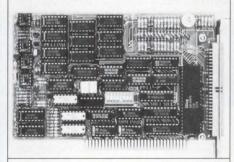

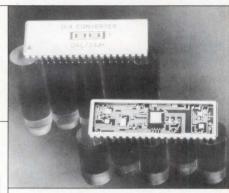

The KS84C22 dynamic RAM controller from Samsung Semiconductor is functionally very similar to National Semiconductor's DP8422. Multiple column-address strobe (G) and row-address strobe (RAS) (H) allow for multiple bank selection (up to four banks) and for byte access and word access. Software programming and mask programming (A) are available. The device also features 11 address outputs (B); a row/ column multiplexer (C); RAS bank decoding (D); WAIT, RFIP and WE drivers, (E), (F) and (I), respectively; and a precision delay (J).

once we go through the normal cycle of process optimization, we should be up around 40 MHz," he says. For the 25-MHz Samsung part, when programmed for tRAH=15 ns and tASC=0 ns, tPADSCL is 85 ns-6 nsslower than for the similarly programmed National part. But Samsung's 40-MHz device should bring that value down considerably.

The Samsung devices will also be register-programmable, with two varieties available. A softwareprogrammable version is intended for small-volume applications for which it's anticipated that the access mode could change. For higher volume applications, there will be a mask-programmable version. "Once the application development is completed, the customer can then give us the register profile and we can program it via mask programming. You then have a much more reliable implementation," explains Levis. Access/refresh arbitration will be available on the Samsung part, but not dual accessing.

Initial beta sampling is now in process. The target date for introduction of the KS84C21/22 is September. The devices are both CMOS. The price

# INTEGRATED CIRCUITS

will be \$24.70 in quantities of 1,000 for the 4-Mbit version.

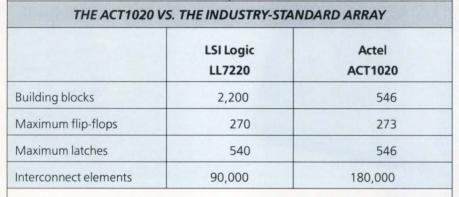

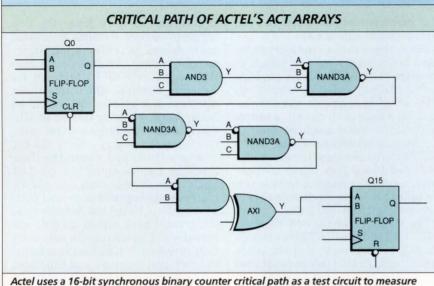

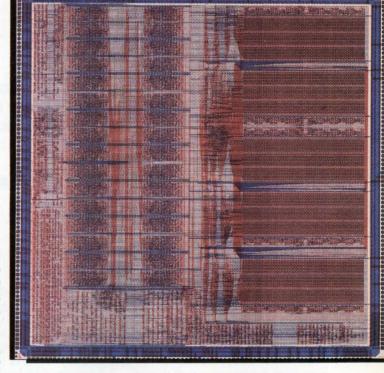

## Followers and dropouts