A PennWell Publication **GOUNDATER DESIGN** THE MAGAZINE OF SYSTEM DESIGN AND INTEGRATION

### AUTOMATING DESIGN: A BUYERS' GUIDE TO CAE/CAD TOOLS

JUNE 1, 1988

# You've just assembled the "perfect" EDA system. Now it's boxing you in.

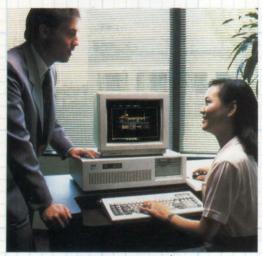

Mentor Graphics delivers the only Electronic Design Automation system that grows in size and power at the same time.

### **Engineer or referee?**

The time has come. You're about to take on a major design project, so you assemble a little of this and a little of that to construct the "perfect" EDA system. And quickly discover it's too little too late.

Why? Because unless all your tools are on speaking terms, you spend more time patching up arguments than you do designing. And the further you expand your system, the more boxed in you become.

Fortunately, there's a single, simple solution. Mentor Graphics' EDA tools.

### The sum of the parts.

No other EDA vendors provide the rich inter-tool communications paths found within our IDEA Series<sup>™</sup> EDA system. From schematic capture to output for manufacturing, your design data flows freely from one tool to the next. Nor do they offer the broad array of tools you need to actually get your design out the door. Whether you're designing ICs, ASICs, PCBs, systems or embedded software, Mentor Graphics' tools cover the entire design cycle.

Nor can other vendors claim the experience we've accumulated. Cur-

rently, there are over 12,000 Mentor Graphics workstations producing everything from 32-bit VLSI microprocessors to 108 MIPS parallel computers. And our continuous dialogue with these customers gives us invaluable feedback in designing subsequent generations of EDA tools.

Mentor Graphics also provides a single source of service and support for your entire EDA tool set. No more finger pointing. No more delays. Our support organization takes care of all your hardware and software needs.

### To be continued.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us show you where this vision can take you.

Before you open all those strange boxes, call us toll-free for an

overview brochure and the number of your nearest sales office. **Phone 1-800-547-7390 (in Oregon call 284-7357).**

Yourideas. Our experience.

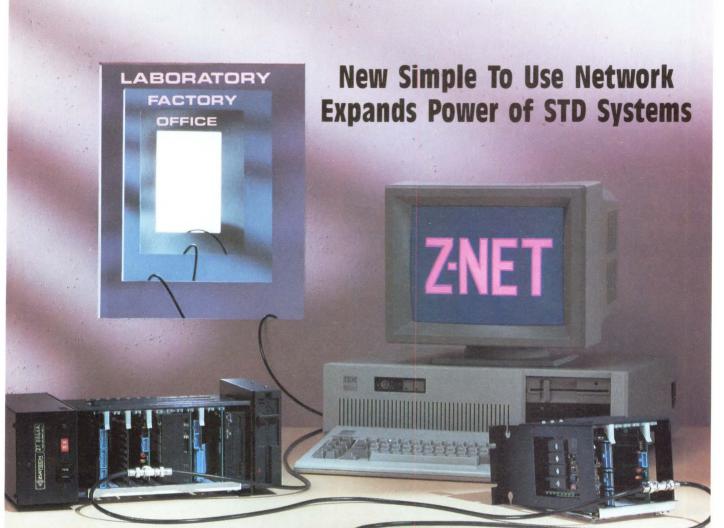

### Turnkey industrial networking for STD Bus and personal computers

Z-NET is a complete, simple to use network for industrial applications. Z-NET extends the capabilities of Ziatech's PC DOS-based STD Bus systems by allowing them to share information and resources with other STD systems and IBM-compatible personal computers.

### **ARCNET hardware protocol**, ViaNet software

Ziatech's STD and PC network controllers are based on the well-established ARCNET protocol, and are supported by ViaNet, a software package from Western Digital that makes using the network as easy as making simple DOS calls.

### **Remote control for embedded systems**

Z-NET was designed to meet the specific network needs of industrial STD Bus computers, which are typically unattended or embedded in equipment. Z-NET makes an ideal sub-network in a large factory or a total solution for smaller applications.

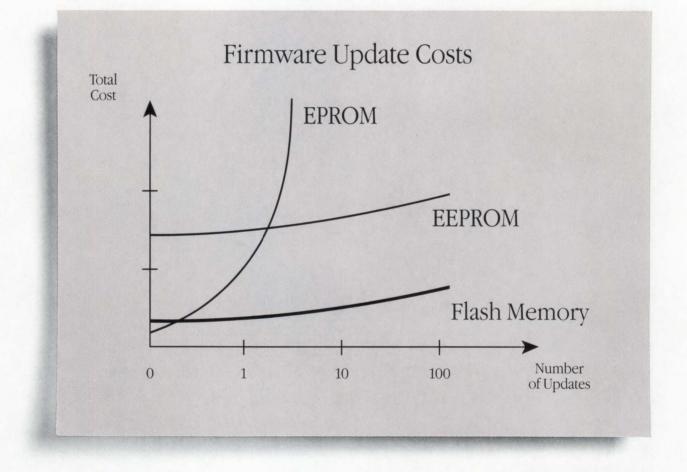

Ziatech's exclusive Virtual Network Console (VNC) lets a network manager control a remote node from his local STD or PC console. VNC capabilities let operators remotely reboot a node and remotely execute or download programs, eliminating the need for PROM installation or replacement.

### A single network source

Z-NET is a complete network solution for industrial STD and personal computers, available now from an established source. The necessary hardware, software, cables, documentation, and applications support are all available from Ziatech, a leading manufacturer of STD Bus and IEEE 488 products.

### Free industrial networking guide

For a complete technical brochure and configuration guide to a complete STD and PC network, call Ziatech today. (805) 541-0488

#

3433 Roberto Court San Luis Obispo, CA 93401 USA ITT Telex 4992316 FAX (805) 541-5088 Telephone (805) 541-0488

ARCNET is a registered trademark of Datapoint Corporation. ViaNet is a registered trademark of Western Digital Corporation. PC DOS and IBM are registered trademarks of International Business Machines, Incorporated.

# The best of both worlds.

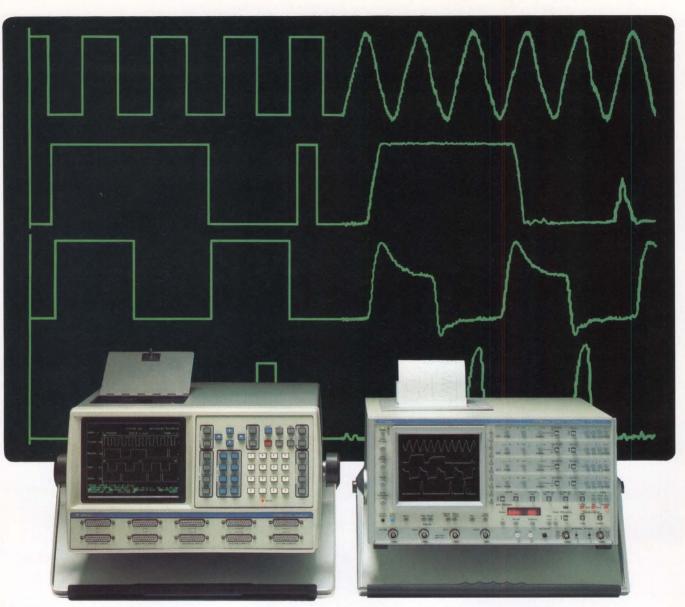

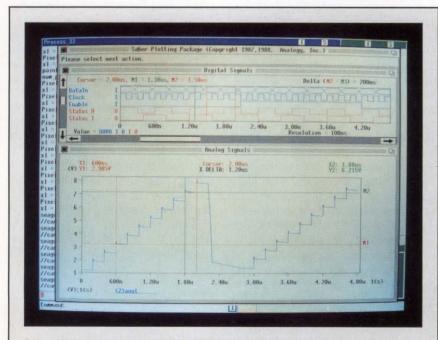

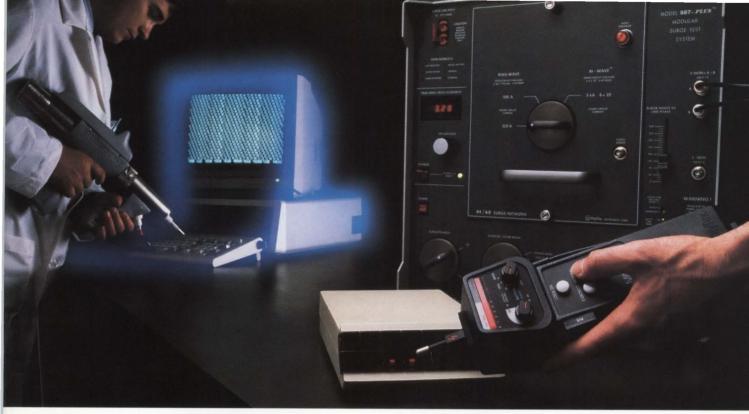

### The K450B Logic Analyzer and the 4074 Digital Storage Oscilloscope from Gould...

State-of-the-art test instruments for designers of today's superfast digital and data communications systems.

### Powerful measurement capabilities...

The K450B Logic Analyzer, with up to 80 channels at 100 MHz or 40 channels at 200 MHz and glitch capture across all channels, provides top performance. AND the 4074 DSO—the only 4 channel instrument with 400 MSample/Sec 8 bit converters on every channel—is the most sophisticated oscilloscope available for the high speed pulse measurements required by electronics designers and test engineers. TOGETHER—they work as an integrated system without any of the compromises of hybrid systems; APART—two high performance instruments available for separate test applications.

### ease of use ....

We provide that on both the K450B and the 4074 with our AUTO SETUP facility.

### and fail-safe performance!

Gould Electronics created the timing analyzer market in 1978 with the introduction of the first logic analyzer; and we were pioneers in DSO technology. Today we supply leading computer and telecommunications equipment makers with logic analyzers and DSOs for digital design verification, hardware and software integration, component and subsystem test, hardware debug and digital remote diagnostics.

Wherever high performance test and analysis is required in digital electronics design, Gould is at the leading edge with a price/performance record second to none.

For further details, contact: Gould, Inc. Test & Measurement 19050 Pruneridge Avenue Cupertino, CA 95014 **1-800-GOULD 10**

CIRCLE NO. 2 FOR INFORMATION ON PRODUCT 4074 CIRCLE NO. 3 FOR INFORMATION ON PRODUCT K450B

June 1, 1988

This issue's cover was designed by John Bonner.

### DEPARTMENTS

9 Up Front 14 Editorial 174 System Showcase 176 Advertisers' Index 176 System Products Index

### **DAC Special Product Preview**

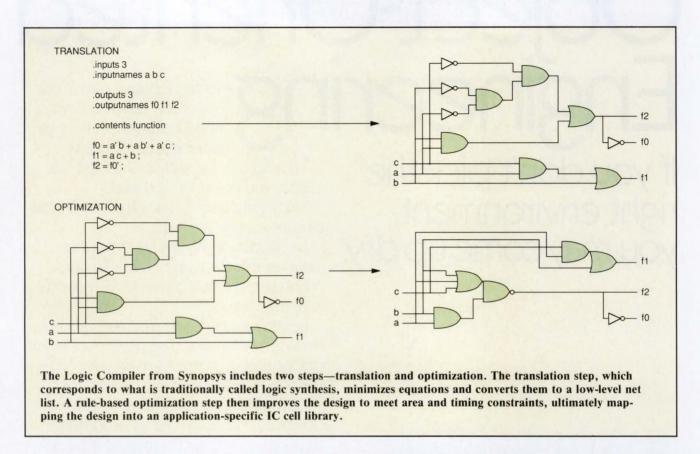

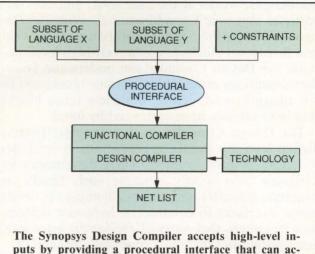

This month's Design Automation Conference will spotlight the major technologies and products of the ever-growing electronic design automation industry. Our special four-page section highlights some of the industry's hotter areaslogic synthesis, simulation, CASE tools and products that support the VHSIC Hardware Description Language. We also preview some of the more outstanding product introductions. Page 160.

### **MPUTER DESIGN** THE MAGAZINE OF SYSTEM DESIGN AND INTEGRATION

### **DESIGNERS' BUYING GUIDE TO CAE/CAD TOOLS**

### **Special Report**

65 Logic-synthesis tools forge link between behavior and structure A new generation of electronic design automation tools can automatically generate structural descriptions from high-level inputs.

### 87 Designers' Buying Guide

- 88 Schematic capture systems

- 100 PCB CAD systems

- 112 Simulation systems

- 134 ASIC layout systems

### SYSTEM TECHNOLOGY

### **Integrated Circuits**

- 19 DRAM shortage holds computer makers hostage

- 22 New PLD architectures deliver needed flexibility

- **28** Intelligent memory architectures attack real-world computation

### **Peripherals and Memory Systems**

**35** Erasable optical media promises data-storage breakthroughs

### **Design and Development Tools**

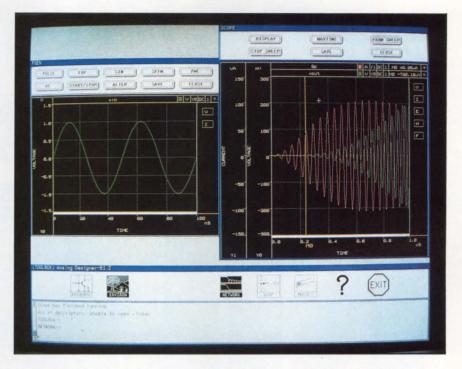

36 Analog/digital simulator tackles board-level designs

### **Technology Focus on Graphics Subsystems**

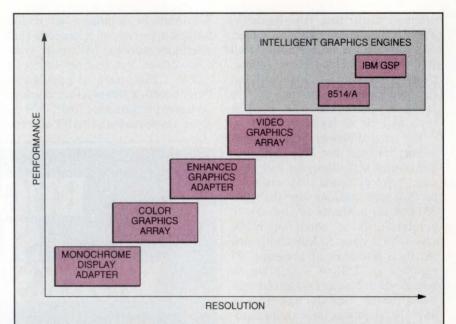

41 PCs crack the barrier to high-powered graphics

### **Technology Focus on 8-bit Microprocessors**

49 8-bit processors demand attention as integration, speed evolve to new levels

### SYSTEM PRODUCTS

### **Design and Development Tools**

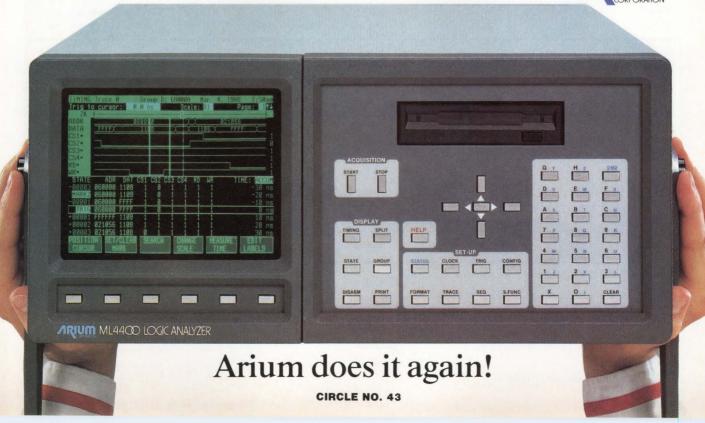

146 Logic analyzers preserve user investment with expandability, higher performance

### **Computers and Computer Subsystems**

168 Single-board computer uses Motorola RISC processor

### **Data Acquisition and Control**

170 HP networking products meet MAP 3.0 specs

### Peripherals

171 Electrostatic plotter offers high throughput

### Integrated Circuits

172 Programmable array logic family features 10 dedicated inputs

COMPUTER DESIGN© 1988 (ISSN-0010-4566) is published twice monthly, except one issue in July and December, by the Advanced Technology Group of PennWell Publishing Company, PO Box 417, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Tulsa, OK 74112. Rates for non-qualified subscribers: \$70 in U.S.A. and \$95 elsewhere. Single-copy price is \$6.00 in U.S.A. and \$8.50 elsewhere. SUBSCRIPTION INQUIRIES: (918) 831-9401, 8 am-5 pm E.S.T. © COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

POSTMASTER: Send change of address form 3579 to COMPUTER DESIGN, Circulation Department, Box 3466, Tulsa, OK 74101 (USPS 127-340)

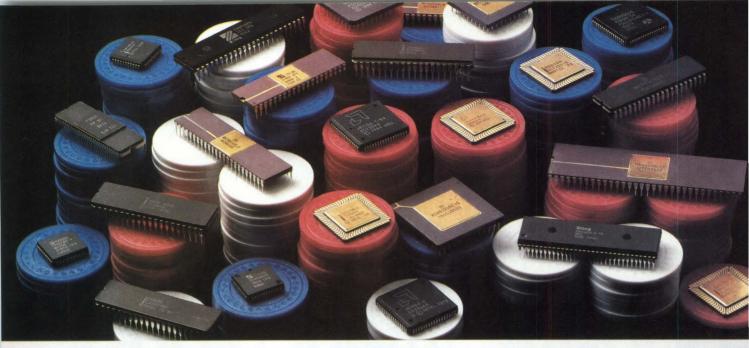

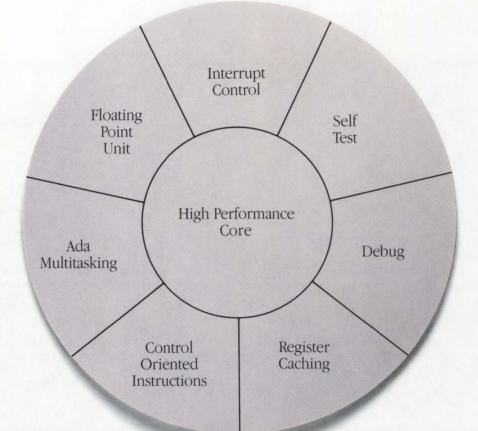

Seventeen MIPS with a single 32-bit RISC chip. Sustained. 42,000 dhrystones. In CMOS. Complete hardware and software development support. Optimizing compilers. Assemblers. Debuggers. Industry standard operating systems. Hardware development tools. Documentation, training

> and customer support. Now.

### Advanced Micro Devices' 29K. The next platform.

Call toll-free (800) 222-9323. Advanced Micro Devices, Inc., 901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088. 29K logo is a trademark of Advanced Micro Devices, Inc. © Advanced Micro Devices, Inc. 1988.

CIRCLE NO. 4

# for VMEbus, Multibus II, and Multibus Interconnect Packaging.

The breadth of our interconnect packaging product line is as great or greater than anyone else's in the industry. It includes everything you need for VMEbus, Multibus II, and Multibus packaging from racks and backplanes to complete systems enclosures with all interconnects, power supplies, and cooling. But, we have even more to offer....

When you come to MUPAC, you'll find a willingness and a capability to

design interconnect packaging that precisely meets your system requirements. We'll never try to force you into the trade-offs of a preengineered solution that isn't exactly right for you.

Find out how much more Mupac has to offer for interconnect packaging. Circle the readers' service number, call toll free (800) 225-0398, inside Massachusetts (617) 588-6110, or write today. Mupac Corporation, 10 Mupac Drive, Brockton, Massachusetts 02401.

The Adaptable Leader in Interconnect Packaging. CIRCLE NO. 5

### New dimensions in memory.

It's ITT Cannon's new Star Card, an IC memory device no larger than a credit card.

Yet Cannon's Star Card will have a tremendous impact on the way you think about and use memory.

Here, in a mere 2%" x 3%" space, is a powerful device for high speed data storage and retrieval. In an era where environmental requirements and reduced space demand increasingly sophisticated electronic technology, the card's compact size and powerful features offer the designer enormous potential.

Unlike a floppy disk, Star Card's compact, durable package protects it from data loss due to dirt, dust or handling. And its connection system is rated for a minimum of 10,000 mating and unmating cycles.

How and where can you put Star Card to

work? Anywhere space, speed, versatility and reliability are important. From the high performance world of electronic printers and word processing

to the rugged demands of process control. To see how the Star Card IC Memory System can bring an extra dimension to your data storage capabilities, talk to us.

Contact ITT Cannon's Components Division, Star Card Products Group, 10550 Talbert Ave., Fountain Valley, CA 92708. Or call (714) 964-7400, ext. 8337.

**TT CANNON** We're making progress. Not excuses

# **UP FRONT**

### **IBM-led consortium challenges AT&T domination of Unix**

Seven top U.S. and European computer manufacturers have formed the international Open Software Foundation (OSF) as a direct challenge to the AT&T-Sun Unix alliance. Initial members of OSF are Apollo, Digital Equipment Corp, Groupe Bull, Hewlett-Packard, IBM, Nixdorf and Siemens, but membership is open to all organizations around the world. Starting with a new version of IBM's AIX Unix operating system, the foundation will build application interface, user interface, networking, data base and other standards to let applications move freely among the hardware and software environments of the member companies. Such existing specifications as X/Open and Posix will be incorporated in the new standard. In addition, each OSF member will contribute its own software expertise. Apollo's Network Computing System, Groupe Bull's Open System Interconnection (OSI) support, DEC's X-Window-based user interface toolkit, HP's NewWave graphics interface and Nixdorf's distributed SQL data base technology are among the items cited as specific contributions to the foundation. Given the scope of its charter and the technological strength of its participants, establishment of the foundation may have permanently deprived AT&T of the power to dictate the future of Unix.-Sydney Shapiro

### 1-Mbit static RAMs hit market

One-Mbit static RAMs, long the stuff of conference papers and market research reports, are finally being announced as real products. Among the first is a  $128k \times 8$ -bit configuration introduced at Electro '88 by Toshiba America (Irvine, CA). With an operating power consumption of 350 mW and a not-exactly-blazing access time of 70 to 100 ns (depending on the version), the new part seems typical of the introductions expected from active high-density SRAM vendors in coming months. Dense enough for main memory applications, these new SRAMs may help take the pressure off some customers suffering in the continuing dynamic RAM squeeze.—*Ron Wilson*

### Electroluminescent prototype first to display full color

No flat-panel display technology will replace CRTs until it can deliver inexpensive, comparable, full color. Developments at this year's Society of Information Display conference, held in Anaheim last week, brought flat-panel displays closer to that goal. General Electric (Schenectady, NY) exhibited the highest resolution color LCD to date, a thin-film transistor-driven panel with a  $1,024 - \times 1,024$ -pixel matrix. The show also featured the first full three-color electroluminescent display. The prototype, from Planar Systems (Beaverton, OR), has a 320-( $\times 3$  phosphors)  $\times$  240-pixel matrix over a  $4.8 - \times 3.6$ -in. active display area. The company developed two-color (red and green) prototypes last year but had difficulty developing a blue phosphor that's bright enough.—John Mayer

### Logic checker brings artificial intelligence to CAE tools

A rule-based design checker running on workstations from Sun Microsystems (Mountain View, CA) offers one of the strongest applications to date of artificial intelligence in electronic design automation. The

(continued on page 10)

**UP FRONT**

#### (continued from page 9)

Yoda product from start-up Orcas Systems (San Jose, CA) is a batch program that checks logic entered with various schematic-capture programs. Users can add their own rules for detecting structural errors, finding timing problems and enforcing testability. A similar product is available from NCR Microelectronics (Fort Collins, CO) for its standard-cell customers, but Yoda appears to be the first such tool that's foundry-independent.—*Richard Goering*

### Hewlett-Packard makes 100 percent commitment to MAP

Although in the past each division of Hewlett-Packard (Palo Alto, CA) used its own proprietary network in its systems, all HP divisions are now committed to the Manufacturing Automation Protocol interpretation of the Open System Interconnection model. The only exception will be for some instrumentation. The announcement was part of the company's unveiling of plans for several MAP and OSI products to be introduced over the next three years. HP OSI Express, a new technology that implements Layers 1 through 7 of the OSI model, will be implemented first on a board called MAP 3.0 MMS (Manufacturing Message Specification). Software and a device-interface system toolset will be available by the end of the year. A MAP 3.0 protocol analyzer and MAP 3.0 file-transfer, -access and -management (FTAM) software will be available by mid-1989.—*Sydney Shapiro*

### Sony makes serious play in high-speed logic

Sony's recent foray into the bipolar market is only a hint of things to come, according to J.P. Laussade, director/general manager of the company's Component Products Division (Cypress, CA). The company's new logic family achieves speeds of up to 4 GHz while keeping power consumption well under 1 W. That performance comes from Sony's ECL III technology, a 1-micron process with a 10-GHz transition frequency and an 80-ps gate delay at 300  $\mu$ A. "Transmit time from pin-to-pin is faster than gallium arsenide," says Laussade. And that's only the beginning. ECL IV, a submicron process twice as fast as ECL III, lurks just around the corner, according to Laussade. —John Mayer

### Daisy ports CAE tools to Sun 80386-based workstations

After years of offering its proprietary workstations, Daisy Systems (Mountain View, CA) will announce this month that it plans to port its CAE/CAD software to 80386-based workstations from Sun Microsystems (Mountain View, CA). The move should considerably strengthen Daisy, which recently experienced two bad years largely because of its exclusive reliance on proprietary hardware. By this fall, Daisy will port its schematic-entry and simulation tools to the Sun 386i family and will later offer printed circuit board and IC layout tools. Daisy has already begun porting its tools to the SunOS Unix environment. For the foreseeable future, Daisy will continue to offer its proprietary Personal Logician and Logician workstations, and its proprietary Dnix operating system.—*Richard Goering*

Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Rd., Ann Arbor, MI 48106. Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101; Philip C. Lauinger, Jr., Chairman and Chief Executive; Joseph A. Wolking, President; L. John Ford, Senior Vice President; Carl J. Lawrence, Senior Vice President; V. John Maney, Vice President/Finance.

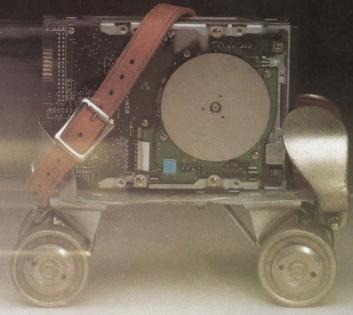

# Shake. Rattle. Ready to roll...

### Canon races away from the competition by offering the next step in portability design.

The MD3611 is a 2.0/1.0MB 3.5" Floppy Disk Drive designed to be driven:

- +5V only, 1" high Light weight...430g

- Unequalled Shock Resistance... 60G @ 11 milliseconds

- Oil Dampened Head Loading

- Selectable Trigger on Dual Color L.E.D.

- Flush Bezel...No more broken buttons

- Low Power...20 milliwatts on standby, 1 watt operating

- Dust Shutter

The Canon MD3611 is no ordinary microfloppy. Besides meeting industry standards for performance and reliability we went a step further and designed a drive to meet the harsh environment and physical demands of portability.

> When you're ready to test drive the Canon MD3611 please call or write: Canon U.S.A., Inc.,

Flexible Disk Drive Division, One Canon Plaza, Lake Success, NY 11042 (516) 488-6700.

West Coast: Canon U.S.A., Inc., 4000 Burton Drive, Santa Clara, CA 95054, (408) 986-8780.

# Mitsubishi Means Monitors.

Mitsubishi Sales Offices: Carrollton, TX (214) 241-5300 • Piscataway, NJ (201) 981-1001 • Mt. Prospect, IL (312) 298-9223 • Minnetonka, MN (612) 938-7779 • Norcross, GA (404) 662-0758 • Sunnyvale, CA (408) 730-5900 • Torrance, CA (213) 515-3993 • Woburn, MA (617) 938-1220

Mitsubishi's extensive line of high resolution graphics monitors offers a solution for virtually every application.

And when you buy a Mitsubishi monitor, you're buying from a company positioned to offer the industry's broadest range of service, products and resources. For years, Mitsubishi has led the industry in supplying graphics monitors.

Whether your application is CAD/CAM, image processing or basic business text and graphics, Mitsubishi has the perfect monitor. Choose from our comprehensive line including 11," 13," 14," 15," 19," 25," 31" and 35" models. Each screen size is available in a variety of performance ranges to meet your application needs.

And no matter which model you select, you can count on Mitsubishi to see to all the details. Details like improved viewability and chassis design that's easy to integrate into any workstation. New ergonomic features such as tilt and swivel bases, non-glare screens and plastic cabinets make Mitsubishi monitors better than ever. Our team of application experts will assist and support you every step of the way to ensure you have the best cost/ performance monitor for your requirements.

You get all these advantages from only one company. Mitsubishi.

So now you don't have to deal with a lot of different companies with a lot of different ideas about monitor design and quality, applications assistance, warranty responsibilities and service.

See for yourself why so many customers have continuously relied on Mitsubishi for design innovations and product reliability.

> To get all the details, call or write Mitsubishi today. Mitsubishi Electronics America, Inc., Computer Peripherals Division, 991 Knox Street, Torrance, CA 90502. Telephone: (213) 515-3993, Peripherals Sales Department.

| Screen Size<br>(V/in.) | Mitsubishi<br>Model                                                                                   | Horizontal<br>Scan Freq.<br>(kHz)                                                    | Screen Size<br>(V/in.)               | Mitsubishi<br>Model                                                | Horizontal<br>Scan Freq.<br>(kHz)                     |

|------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------|

| 11" Graphics           | HF1200/50<br>HF2200/50<br>HF3200/50                                                                   | 15.5–20<br>20–25<br>30–35                                                            | 14" Flat Sq.                         | FHF3500                                                            | 30-35                                                 |

|                        |                                                                                                       |                                                                                      | 15" PC CAD/<br>Eng. Work-<br>station | C8652<br>FG6600<br>HL/FL6605                                       | 47–52<br>60–65<br>30 ~ 64*                            |

| 13" PC<br>Graphics     | XC1409C<br>XC1410C/30C<br>XC1429C<br>AUM1371A/81A<br>FA3415/25<br>HF1400/50<br>HF2400/50<br>HF3400/50 | 15.75<br>22.4 & 15.75<br>31.5<br>4 15 ~ 35*<br>15 ~ 35*<br>15.5-20<br>20-25<br>30-35 |                                      |                                                                    |                                                       |

|                        |                                                                                                       |                                                                                      | 19" CAD/PC<br>CAD                    | C3920/21/22<br>C6920/21/22<br>HA3905<br>HL6905<br>HG6905<br>HJ6905 | 15-24<br>28-35<br>15~35*<br>30~64*<br>40-67<br>40~70* |

|                        |                                                                                                       |                                                                                      | 25" Graphics                         | C3510<br>C6512                                                     | 15–18<br>28–34                                        |

|                        |                                                                                                       |                                                                                      | 31" Graphics                         | XC3310                                                             | 15~35*                                                |

| *Auto-tracking         |                                                                                                       |                                                                                      | 35" Graphics                         | XC3710                                                             | 15~35*                                                |

New Models Now Available

Graphic images courtesy of Autodesk, Inc., Computervision Corp., Megatek Corp., and Environ, Inc.

### EDITORIAL

### Chips vs. chips

t wasn't a world-shaking international incident. It only warranted a 30-second spot on the nightly news. The Associated Press wire service picked it up, so it made its way into a few

newspapers. What was the incident? You might call it the second battle of Midway. But this time around, it was fought by Japan, some sailors aboard the USS Midway anchored at the Navy Air Station in Atsugi, Japan, and the Girl Scouts of America. It was all about 400 boxes of cookies.

As the story goes, these young men, doing what a lot of good young American men have been doing now for nearly 75 years—namely helping to defend the world against tyranny—also tried to help the Girl Scouts by buying some cookies. The news stories didn't mention whether the cookies were peanut butter or shortbread or chocolate chip. But no matter. Whatever they were, they cost only \$2 a box. The Japanese, true to form in their dedication to protect their markets and their culture from intrusion by everything from beef and oranges to microprocessors, cellular telephones and American construction workers, classified the cookies as an agricultural product and slapped on a tariff of \$5 a box. Not 5 cents, or 50 cents, but \$5. The sailors finally got their cookies, but only after surrendering to this extortion.

What happens to \$400 worth of Girl Scout cookies is infinitesimally inconsequential in comparison to the multibillion-dollar U.S.-Japanese trade imbalance. The significance of the incident is far from inconsequential, however. It underscores, once again, the myth of free or even fair trade as far as the Japanese are concerned, as well as their gross insensitivity to their trading partners. More than that, it once again focuses the spotlight on the true protectionists.

The time has come for us to wake up to the realities that few, if any, of our trading partners believe in free trade, that fair trade is open to as many interpretations as there are trading partners, and that protectionism, in one form or another, is the rule. The game of international trade isn't being played for the fun of playing; the game is being played to be won. Our trading partners, and the Japanese perhaps more than anyone else today, want to go to the Super Bowl, and they want to win. As noted in Warren Andrews' article on the current dynamic RAM shortage (see page 19), we should take whatever measures are needed to reestablish our position in the semiconductor industry, and the same holds true for a host of other industries.

I'm not big on sports analogies, but if you have to beat the Green Bay Packers to make it to the Super Bowl, you don't cry about the subzero weather, the raging snow or the muddy field. You strap on your padding, go into the mud and do whatever it takes to win. Winning in domestic and international markets requires the same grit and strategy.

John C. Miklosz Associate Publisher/Editor-in-Chief

# How To Wring Workstation-Level PCB Designs Out Of Your PC.

### P-CAD's new Master Designer turns an ordinary PC into a full-fledged PCB workstation.

WORK-

MASTER

When you need to wring every drop of performance out of your next PCB design, you need Master Designer<sup>™</sup> software.

Master Designer provides all the horsepower you'd expect only from workstations priced from \$50K up to as much as \$200K.

With Master Designer you can tackle the really big jobs. Board designs with 500 EICs, 32,000 pins and 2,500 nets are just the beginning.

P-CAD's Master Designer routes multiple layers simultaneously cutting the number of vias and unrouted subnets in half. So, you'll wring out cleaner designs and higher completion rates (up to 100%).

\*\*\*\*\*\*\*\*\*\*\*

For forward annotation of logic changes and "history independent" back annotation, Master Designer also has an ECO processing option.

If you're interested in wringing every penny out of your PCB design station instead of wringing your hands, ring P-CAD. Let P-CAD show you how to turn a PC into a high-powered workstation.

290 Parkmoor Ave., San Jose, CA 95126 USA Telex: 371-7199 FAX: 408-279-3752

800-628-8748 CA 800-523-5207 U.S. See us at DAC, Booth #1350

P-CAD is a registered trademark and Master Designer is a trademark of Personal CAD Systems, Inc.

TYPICAL PC SOFTWARE

NUMBER OF USERS

The AP Labs IOS is a programmable I/O Subsystem enabling many general purpose and scientific host computers to perform data acquisition, storage and data routing tasks in real time environments. The IOS interfaces with Gould, DEC-VAX, Sun Microsystems, UNIX and NTDS Host computers, VMEbus computers, and Aptec and FPS Processors.

The AP Labs IOS provides: LOW COST INTERFACE

LARGE SELECTION OF PE-RIPHERALS—with drivers

PHERALS—with drivers CA 92117 ( CIRCLE NO. 11

OFF LOADING OF THE HOST COMPUTER

HIGH LEVEL SOFTWARE CONTROL

TEST AND DEBUG PROGRAMS AP Labs IOS supports Real Time Data Routing, Hardware In-The-Loop Simulation, Signal/Image Processing, Process Control, Data Acquisition, Data Switching and Real Time Graphics. Call today.

### **AP Labs**

ADVANCED PROCESSING LABORATORIES, INC. 4411 Morena Blvd. Ste. 150, SanDiego, CA 92117 (619) 272-8890 COMPUTER DESIGN

PUBLISHER

David L. Allen

ASSOCIATE PUBLISHER/EDITOR-IN-CHIEF: John C. Miklosz

#### **TECHNOLOGY EDITORS:**

Ron Wilson, Integrated Circuits (Portland) Richard Goering, Design & Development Tools (Santa Clara) David Lieberman, Computers & Computer Subsystems Tom Williams, Graphics & Imaging (Santa Clara) John H. Mayer, Computers & Computer Subsystems Sydney F. Shapiro, Data Acquisition & Control

#### **CONTRIBUTING EDITORS:**

David Gabel, Computers & Computer Subsystems Warren Andrews, Integrated Circuits Steven L. Martin, Integrated Circuits Howard Falk, Software Art DeSena, Testing & Manufacturing

RESEARCH/SPECIAL PROJECTS MANAGER:

Sydney F. Shapiro

### SECTION/SPECIAL PROJECT EDITORS:

Ron Wilson, *System Technology* David Lieberman, *System Design* John H. Mayer, *System Products* Patti Villandry, *Directories*

#### MANAGING EDITOR: Susan R. Nykamp

COPY EDITORS: Richard Dagley, Kerstin L. Rosenquist, Barbara-Ann Scofidio

EDITORIAL ASSISTANTS: Martha Ewing, Claire Ellis

#### WEST COAST OFFICES MANAGING EDITOR: Tom Williams EDITORIAL ASSISTANT: Deborah Reinke

3333 Bowers Ave, Suite 100 Santa Clara, CA 95054, Tel: (408) 982-0288

1111 S.W. Gaines, No. 8 Portland, OR 97201, Tel: (503) 224-9396

MARKETING SERVICES MANAGER: Mary M. Gregory CIRCULATION DIRECTOR: Robert P. Dromgoole

**ART DIRECTOR:** Jan Horner **ILLUSTRATOR:** Christopher Hipp

PRODUCTION DIRECTOR: Jan M. Lopez PRODUCTION MANAGER: Mari Rodriguez ADVERTISING COORDINATOR: Shari L. Hasche COMPOSITION: Holly Kersey COVER ART: John Bonner

L. John Ford, Senior Vice-President Advanced Technology Group P.O. Box 417 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

# How KMW meets graphics processing needs from A to E.

### As much graphics processing power as you need.

Look to KMW for the right connections to fit your needs. Our high performance graphic element processors – the VP-10 and the VP-30 – can handle everything from simple A-size plots to high density E-size plots. Both processors are designed to help you produce graphics output as efficiently as possible.

Our VP-10 is perfect for plots up to 24". Buffered input allows the VP-10 to store 2Mb of graphics data.

The high speed VP-30 has a disk storage capacity expandable to 40Mb and can handle plots up to 44".

### Better productivity through decreased downtime.

If you're letting your host computer rasterize your data, it ties up the whole system, keeping you and your co-workers from getting any work done while the plot's

in progress. But the VP-10 and VP-30 rasterize data independently of the host computer, so you can stay productive while your plots are being produced. And both processors can receive input while they're outputting a plot.

# Compatible with a variety of software packages and output devices.

The VP-10's pen plotter emulation feature allows compatibility with hundreds of graphics software packages, including VersaCAD, AutoCAD, and SAS. The VP-30 can be used with such popular packages as CADAM, CADS4X and Scicards/Quickplot.

The VP-10 supports electrostatic plotters from Benson, CalComp and Versatec, as well as small color raster devices from Seiko and Mitsubishi. Input data formats include KMW.PLT, HPGL (HP pen plotters), and CalComp 906/907. The VP-30 supports Versatec, Benson and CalComp electrostatic plotters – including color – and drives them at full speed. It accepts CalComp 906/907, 925, 960 and KMW.PLT data formats.

This wide range of compatibility allows you to use different plotters without having to replace your processor.

### Designed for better quality – in black and white or color.

Both the VP-10 and VP-30 produce monochrome and color raster page

composition for

applications such as architectural, mechanical or electrical CAD and business graphics. In conjunction with an electrostatic plotter or thermal printer, both processors let you produce plots of the highest quality – in a fraction of the time it would take to produce a pen plot.

### Expert answers from KMW.

KMW has been helping companies make the right connections for more than ten years, with graphics processors, channel interfaces, and protocol converters. For complete information, call the toll-free number below. Or write KMW Systems Corporation, 6034 W. Courtyard Drive, Austin, Texas, 78730.

**(800) 531-5167** In Texas, (512) 338-3000

Trademarks: Versatec – Versatec, Inc., a Xerox Company; Benson – Benson Corporation; CalComp – California Computer Products, Inc.; Seiko – Seiko Instruments USA; HPGL – Hewlett-Packard; Scicards/Quickplot – Scientific Calculations. Registered trademarks: Mitsubishi – Mitsubishi Electric Corp.; AutoCAD – Autodesk; VersaCAD – Versacad Corp.; CADAM – CADAM, Inc.; CADS4X – Computervision; SAS – SAS Institute Inc. ©1987 KMW Systems Corporation

# For Long Life. In the Fast Lane.

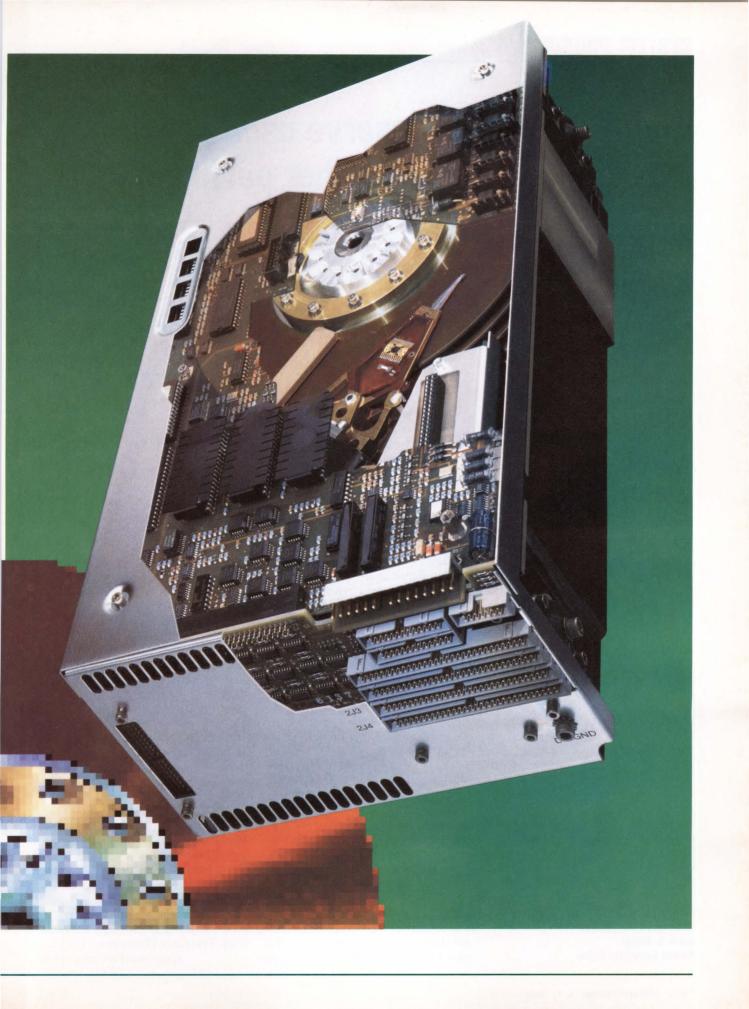

Rev-up your system with Hitachi's durable new 382MB driving machine

> Hitacbi DK514-38 382MB 5.25" Wincbester 16ms seek 1.8MB/sec. transfer ESDI, E-SMD, SCSI interface 30,000 MTBF

> > Fast Action:

To get product literature immediately, CALL TOLL FREE 1-800-538-8157, Ext. 877. *In California*, 1-800-672-3470, Ext. 877. Ask for literature number PB-514.

Regional Sales Offices: Natick, MA 617/655-5501 • Dallas, TX 214/991-7983 • Brea, CA 714/993-1610 • San Bruno, CA 415/872-1902

Hitachi America, Ltd. Computer Division 950 Elm Avenue, Suite 100 San Bruno, CA 94066

Who says fast can't last? Not Hitachi. Our new DK514-38 382MB 5.25-inch drive brings you lightningfast performance with unbeatable reliability.

Sophisticated technology has cut average seek time to a scorching 16ms, and increased the data transfer rate to 1.8MB/sec. Normally, you'd expect such speed to cost endurance. Not with Hitachi. In-house design and production of all major components and the most stringent quality assurance program in the industry give the DK514-38 30,000-hour MTBF.

If your super-micro, mini or workstation demands a drive that can keep up with your processor, and do it over the long haul, our DK514-38 is one machine you can't afford to pass up.

To learn more about this powerful, dependable performer, contact your best partner for mass-storage solutions...Hitachi. We'll show you the right way to drive. Fast.

### **DRAM** shortage holds computer makers hostage

**D**ynamic RAMs are the oxygen of the computer business, and the industry is experiencing some breathing problems because of the recent shortages. The DRAM shortage that began late last year is beginning to cast a pall over the nearterm-and perhaps long-term-future of the computer business. Initially, the scarcity of parts was attributed to four factors: a glitch in a large Japanese fab line, a delay in coming up to speed on 1-Mbit parts, unprecedented demand, and restrictions imposed by the Semiconductor Trade Agreement that the U.S. signed with Japan.

"All of these factors may have contributed to the disaster in the memory market," comments one major DRAM buyer, "but there seems to be something more organized about it. The disaster is turning into a pogrom." This same sentiment has been echoed by numerous vendors (who don't wish to be identified) in the board-level business, as well as elsewhere. "We're facing a major problem, and a lot of people believe that it's just going to go away," comments a prime semiconductor maker.

"The large horizontally aligned Japanese companies don't want to buy just the chip business or, for that matter, the semiconductor business. They want the whole thing—chips, boards and computers," emphasizes another industry executive. "And they're going to get it," he adds, "unless U.S. companies, the government and industry trade associations cooperate to stave off this disaster."

By constricting the supply of memory chips, offshore vendors not only drive prices up, but get their foot in the door as suppliers of other semiconductors, such as application-specific ICs, by leveraging their "allotment" of memory chips. In addition, they bite off chunks of the board, subsystem and system business by being able to provide timely

Warren Andrews Contributing Editor delivery of completed assemblies.

Forecasts for the next few years don't look bright. Japanese vendors say they'll increase production (and exports), but even the figures they quote won't fill the shortfall (see table below). U.S. vendors (the two still in the business) can't make up the difference, and even with an allout effort and an investment estimated at close to \$2 billion, other U.S. semiconductor manufacturers could only meet about 40 percent of the estimated demand by 1991.

### How it happened

How the U.S. semiconductor industry got to this point is an oft-repeated story. In the late 1970s and early 1980s, there were almost a dozen U.S. DRAM vendors. Lowpriced Japanese imports drove all but two—Texas Instruments (Dallas, TX) and Micron Technology (Boise, ID)—out of the business. TI, for its part, has retained its DRAM facility, but primarily as a proving ground for new technology. Micron has had to struggle to stay above water in the price wars.

In their aggressiveness to capture the DRAM market, Japanese vendors flooded the U.S. market with cheap chips, driving out U.S. competitors. Semiconductor industry experts estimate that the chief Japanese DRAM vendors lost about \$4 billion on sales of DRAMs to the United States. Charges of dumping were levied against the Japanese manufacturers, and were upheld, resulting in the 1986 Semiconductor Trade Agreement. This agreement amounted to locking the barn door after the horse has escaped. In addition, the agreement invited the offshore DRAM manufacturers to reduce exports to force prices up.

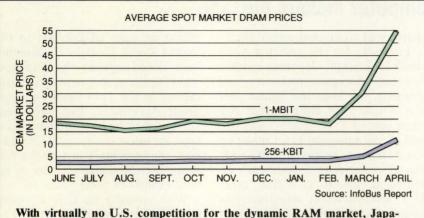

With virtually no U.S. competition, Japanese vendors are free to charge whatever price they want. The trade agreement seems to assure a shortage, and vendors are free to allocate relatively scarce parts.

As DRAMs started becoming scarce, computer makers were quick to blame the trade agreement and vented much of their anger at semiconductor manufacturers for initiating the agreement. This resulted in antagonism between the American Electronics Association-largely composed of system manufacturers-and U.S. chip makers. Though that squabble isn't vet over, most of the systems houses agree that the real problem isn't the trade agreementrather, it's the fact that U.S. vendors were driven out of the market by the price wars with Japan.

"The real problem has its roots in the U.S. semiconductor sector's almost nonexistent capacity to turn out DRAMs," system makers claim.

| Japanese Production Forecast |          |                   |                                    |                                |  |  |

|------------------------------|----------|-------------------|------------------------------------|--------------------------------|--|--|

|                              | Density  | Quarter<br>(1988) | Production<br>(units in thousands) | Export<br>(units in thousands) |  |  |

| DRAMs                        | 64-kbit  | 2<br>3            | 21,200<br>18,900                   | 12,900<br>11,900               |  |  |

|                              | 256-kbit | 2<br>3            | 159,300<br>155,100                 | 90,500<br>88,600               |  |  |

|                              | 1-Mbit   | 2<br>3            | 43,600<br>56,000                   | 28,300<br>35,000               |  |  |

| SRAMs                        | 16-kbit  | 2<br>3            | 40,800<br>42,200                   | 16,200<br>16,500               |  |  |

|                              | 64-kbit  | 2<br>3            | 46,800<br>50,600                   | 21,000<br>22,200               |  |  |

|                              | 256-kbit | 2 3               | 22,500<br>26,000                   | 10,000<br>11,800               |  |  |

Source: Ministry of International Trade and Industry

### **SYSTEM TECHNOLOGY**/Integrated Circuits

With virtually no U.S. competition for the dynamic RAM market, Japanese vendors were free to reduce exports to force prices up. When the supply of memory chips was constricted, spot market prices rose sharply, resulting in steep increases in board-level and system prices.

As mentioned, only Micron Technology and Texas Instruments survived to have any capacity to produce DRAMs. And though Micron is doubling its present capacity, it represents only a very small drop in the bucket. TI is reportedly beefing up its U.S. capability—even to the extent of bringing key personnel back from its Japanese facility.

It's also reported that other U.S. semiconductor vendors may be reentering the DRAM business. Motorola will be setting up a fab line for memory, but it isn't yet clear how committed the company is the task of taking on the offshore competition. National Semiconductor, too, is reported to be investigating prospects of surfacing with memory products. But such moves are at best risky ventures. The large Japanese chip makers could easily open the flood gates and release large volumes of parts just as U.S. semiconductor vendors have made a significant investment in tooling up and are getting up to speed.

"Without some kind of protection, either in the form of meaningful trade agreements or a managed trade policy," says a major chip maker, "such a major investment could backfire." System makers and chip builders are attempting to come up with some reasonable formula. Suggestions include long-term purchase contracts and even a co-op of system makers building their own DRAM factory.

### **Rough times ahead**

Even if U.S. manufacturers find some potentially feasible solutions, the going will be rough because the foreign chip makers are the same companies that are also in direct competition with the U.S. system makers. These include all the broadly horizontal companies making all types of computers from micros to mainframes, communications equipment from desktop consoles to central offices, and instrumentation from automatic test equipment to lab equipment. Such companies include NEC Electronics, Fujitsu, Toshiba, Hitachi, NTT, Oki Semiconductor and Mitsubishi.

In addition, many other Japanese companies such as Ricoh, Seiko-Epson and others are using DRAM availability (from internal DRAM capacity and from other Japanese sources) to leverage their market position in everything from FAX machines to personal computers.

To make matters even worse, potential problems aren't being aired. Many DRAM customers are intimidated about screaming too loud, lest suppliers freeze them out. Even in interviews with the press, buyers and users tread very gently—often even after being guaranteed anonymity. "We're being blackmailed and have no choice but to give in," says one frustrated business owner. "If, for any reason, our supply of memory is cut off, we're out of business." Even in cases where vendors blatantly sidestep the law—such as when they demand tie-in sales—customers are hesitant to complain, afraid of possible repercussions.

### What can be done?

Problems with shortages, and the movements of systems business abroad that such shortages produce, will recur as offshore vendors alternately tighten and relax their stranglehold on the market. Each time the hold tightens, a little more U.S. semiconductor, board and system business moves abroad. Aside from the loss of business, there's an even greater loss in terms of a transfer of technology to other shores. And national security becomes an issue when those shores are unfriendly.

Some industry experts believe steps can be taken to both lessen the immediate burden and plan a longterm strategy to preclude the problem from recurring. Certainly a key element in both a short- and longterm effort will include decisive government action. The following remedies have been suggested by various industry spokespeople.

• Strictly ration imports—many propose that for every bit of memory exported to this country as a system or board, some minimum number of bits must be exported as chips that are put on an open market, not just imported and sold to U.S.-based Japanese companies.

• Eliminate the bundling of other products (particularly semiconductors) as a condition of sale. (This practice was used inversely when memory prices were low, but is a violation of antitrust legislation in either event.)

• Continue (or increase) the executive order placing a 100 percent duty on any 16-bit or greater microprocessor- or processor-based imported product.

• Tighten loopholes that have traditionally let Japanese vendors sell to U.S. companies or to their own

Desktop Publishing

Drawing/ Tracing

CAM

Universal Mouse Emulator adds software compatibility with AutoSketch and hundreds of other programs.

## Hands down, the best selling most compatible graphics tablet you can buy.

SummaSketch is the world's best selling tablet because it's filled with "Plus's". Like full IBM connectivity with the PC, AT and PS/2. Plus full Microsoft® compatibility through a Universal Mouse Emulator™ Plus a separate tablet driver for Microsoft Windows. Plus a two-year warranty. Add that to our standard features-like high resolution and accuracy with the most software compatibility-and you have the tablet with all the Plus's. The 12" × 12" SummaSketch Plus.

New 18" × 12" Version. Now you can get all these great features in our larger SummaSketch® Professional tablet. All the Plus's, plus more active area to work with!

Fairfield, CT 06430 · 203-384-1344 SEND ME ALL THE PLUS'S. Send me more information on SummaSketch tablets today. Type of industry: Type of application: ( ) I'm interested in OEM information. Name: Title: Company: Address: City: State: Zip: Mail to: Summagraphics Corporation 777 State Street Ext. Fairfield, CT 06430 CD 6/1/88

CAD

### CIM

### CIRCLE NO. 14

Tablet Driver allows operation under Microsoft® Windows environment, PageMaker® and Windows Draw.

U.S. subsidiaries through other trading nations.

• Make it mandatory for any company that's dealing in interstate trade to seek a domestic supplier first or offer a reasonable excuse for purchasing foreign parts. Such legislation could be accompanied by perks for compliance, such as tax incentives—not just punishment for noncompliance.

Legislators concerned with the general economy, the total federal budget, U.S. employment and employment opportunities, and the trade balance should be studying these issues, rather than how the United States can be "nice" to its international trading partners. For the "We're being blackmailed and have no choice but to give in. If, for any reason, our supply of memory is cut off, we're out of business." —Name withheld

long term, there are other issues that must be addressed to see that the DRAM fiasco isn't repeated with other products or in other industries.

The situation demands that U.S. manufacturers be able to deal on an equal footing with their counterparts in trading nations. For them to do so, steps must be taken to manage trade policy; revise antitrust legislation; initiate tax incentives and lowinterest loans; sponsor (or at least participate in) cooperative research groups; and put a mechanism in place for rapid response to industry complaints of unfair trade practices. If these suggestions and others proposed by semiconductor leaders and system makers alike are put into action, the result might well be the beginning of a new era of prosperity for the U.S. semiconductor manufacturing sector. CD

### New PLD architectures deliver needed flexibility

New programmable logic device architectures have been coming out of the woodwork lately. First there were generic versions of standard PALs. Then there were devices that looked suspiciously like gate arrays, or like application-specific products with some programmable logic built in. Now, there are so many architectural alternatives that even vendors admit it's hard to make the right choice.

But the confused market seems to be gradually segmenting itself into three clumps. One clump focuses on the 20- to 24-pin devices used primarily in state machines. At the opposite extreme, a second group of products emphasizes high pin count and great circuit flexibility. In between these two poles, a third market segment seems to be emerging, combining some of the characteristics of both the low-pin-count and high-end devices.

Of the three areas, the 20- to 24pin device group is certainly the most

### Ron Wilson Senior Editor

traditional. These devices almost all have a PAL architecture—a programmable AND array, a fixed OR array and highly configurable output macrocells. The flexibility of the macrocells lets one part substitute for a wide variety of older parts with essentially the same AND array layout but with different buffer, register or latch configurations.

Parts with up to 24 pins seem to be used predominantly for implementing state machines. So the operating frequency of the state machine necessarily influences the way these PALs are designed. For the most speed-critical state machines, vendors have successfully assailed the 10-ns propagation delay barrier in both bipolar and CMOS technologies. But for the less speed-driven applications, virtually every vendor has moved to CMOS.

One such vendor is Signetics (Sunnyvale, CA), which announced a family of four 20V8-style CMOS parts in May. The devices are available in quarter- and half-power designs, with propagation delays ranging from 45 to 35 ns. Signetics points out that, unlike many fractional-power CMOS parts, the PLC20V8 family has 24-mA outputs.

Advanced Micro Devices (Sunnyvale, CA) recently introduced a 20pin part, the CMOS 18U8Q, that uses a similar idea. A quarter-power device, this implementation of the 18U8 offers either 25- or 35-ns propagation delays.

Pushing CMOS logic to these speeds raises a new issue for PAL designers: switching noise. "At 25 ns, a switching noise in a CMOS PAL can get pretty bad," warns Andy Robin, AMD director of marketing for programmable logic. "We control the problem in the 18U8 by limiting the output current to 8 mA. Of course, there are some backplane applications where that isn't enough current, but it's fine for the majority of uses." Robin suggests that switching noise issues could confine CMOS PALs to moderate speeds, leaving the sub-10-ns range to bipolar chips. "We believe we have the problem under control down to 7 ns, or maybe 5 ns, in TTL devices. But at these frequencies, where CMOS and

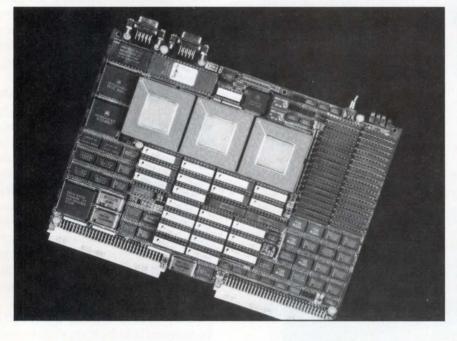

MVME141 HIGH PERFORMANCE CPL

# "The 030 running at up to 8 MIPS makes Motorola's new VME board the fastest on the market."

OEMs are finding our new MVME141 module resets the usual performance limits for CPU boards at the high end. Because it handles demanding applications like engineering simulation, computer animation and image processing at blazing speeds.

For openers, the 141 boasts a powerful MC68030 MPU and floating-point coprocessor, both running at up to 30 MHz. Then, to enhance memory and peripheral access speeds, the 141 adds three new ASICs—the VMEbus interface chip, the VME subsystem bus (VSB) chip and a custom cache controller gate array.

-----

What really boosts computing horsepower, though, is the 141's direct-mapped 6.4 Kbyte cache, which features a hit rate of greater than 90%. Implemented with 15-nsec Motorola SRAM technology, with write-posting interface, the cache allows continuous 2-cycle read access, letting the 030 operate at its maximum potential.

A companion 4/8 Mbyte memory board, the MVME224-2, has been fine tuned to work with the 141 CPU module. It features dual-ported VMEbus and VSB interfaces, and a

patented arbitration circuit that minimizes memory access times.

To move your UNIX\* and real-time applications up to the new high-performance standard in VME boards, call us today—toll free: **1-800-556-1234, Ext. 230;** in California, 1-800-441-2345, Ext. 230. Or write: Motorola Microcomputer Division, 2900 Diablo Way, Tempe, AZ 85282.

UNIX is a registered trademark of AT&T.

CIRCLE NO. 15

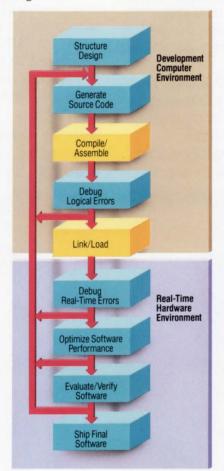

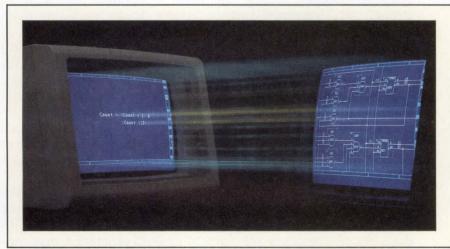

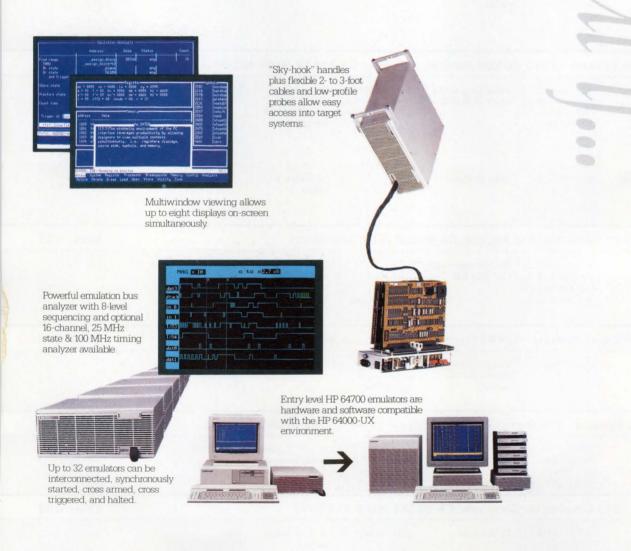

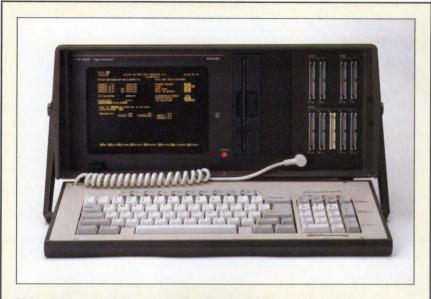

# The complex world of microprocessor development just got simpler.

EE

High-performance 8, 16 and 32-bit emulation.

Software development tools, including source and symbolic level debuggers.

Motorola, Intel, Zilog and Hitachi microprocessor support.

As the challenges of developing and debugging embedded microprocessor designs becomes more and more complex, you need the best development tools possible.

Ând nobody offers you higher reliability, better performance or a quicker way to develop and debug your 8, 16 or 32-bit systems than Applied Microsystems.

Our emulators, for example, can be controlled from the host computer you work with (VAX, Sun, Apollo, IBM PC or compatible). Your target system will run exactly as if its microprocessor were in place. And you'll get a clear picture of your design and how it interfaces with interrupts, clocks and the flow of software.

Our emulators are designed to work with easy-to-use VALIDATE software to give you powerful source level or symbolic debugging capabilities. You also get our powerful Event Monitor System, a hierarchical, real-time breakpoint and triggering system.

The list of benefits goes on and on; but the end result is a faster, easier and more accurate approach to developing, debugging and integrating your design.

To find out more, write Applied Microsystems Corporation, P.O. Box 97002, Redmond, Washington, USA 98073-9702. Or call (800) 426-3925, in WA call (206) 882-2000.

In Europe contact Applied Microsystems Corporation Ltd., Chiltern Court, High Street, Wendover, Aylesbury, Bucks, HP22 6EP, United Kingdom. Telephone 44-(0)-296-625462. AMC-230

Applied Microsystems Corporation TTL power consumptions are about the same anyway, CMOS may just not be an amenable technology."

#### Struggling for flexibility

The mass migration to CMOS has meant more than power savings for vendors. Greater CMOS densities mean the possibility of packing more complexity into the 24-pin devices. And that added complexity could serve customers building more complex state machines. But how to add flexibility, maintain a fixed I/O pin count and still make the device useful has been a puzzling problem.

One vendor, Lattice Semiconductor (Hillsboro, OR), has taken a cue from customer feedback on that quintessential PAL, the 22V10. "It's been an evolutionary development," says Lattice applications engineering manager Rodney Strange of his firm's new 24-pin chip, the 39V18. "Everyone loves the 22V10 until they try to use the top and bottom terms. Then they want more flexibility in allocating product terms."

To beat the allocation problem, Lattice took a page from the history of programmable logic: the page that describes PLAs. "We put both a programmable AND array and a programmable OR array into the 39V18," explains Strange. "That lets the designers who are working out really complex state machine designs allocate the product terms exactly as they need.

"The industry moved away from AND/OR programmability because it was too slow. But with our hot CMOS process and our inherently fast EEPROM fuses, we can make up most of the speed difference. The technology is really a key here—I don't think many vendors could build this part in an EPROM process," says Strange.

Taking additional steps to tailor the 39V18 to difficult state machines, Lattice worked out an unusual set of storage features. All 20 input pins are latchable, and all outputs are driven by sophisticated macrocells. Perhaps more important for machines in which not all state variables need to be observable, the chip provides eight buried-register macrocells.

Of course, all this capability in a 24-pin device comes at a price, and for the 39V18 that price is complexity. "This is not a part you'd give to a designer right out of college," Strange says candidly. The complexity of the chip also raises the everpopular PAL testing issue: with this

"There's no question that what this market wants is a programmable gate array." —Andy Robin Advanced Micro Devices

much going on in the chip, how do you know it's working?

The dependence Lattice has on EEPROM technology comes to the rescue here, according to Strange. Since the part can be programmed, tested, erased and reprogrammed in a matter of seconds, Lattice can feed combinations of programs and test vectors through the device to test all signal paths and all fuses before shipment. "For many of our customers, that's the biggest single point—that we guarantee 100 percent reprogrammablity so our customers can solder down the parts without testing them," Strange says.

### **Finding middle ground**

The 20-, 22- and 24-pin PALs are pursuing increasingly complex state machines with relatively conventional architectures. But at the high end, the PLD market is dominated by an entirely different idea of architecture. "There's no question that what this market wants is a programmable gate array," claims AMD's Robin. And obliging vendors, such as Xilinx (San Jose, CA), AMD and new entrant Actel (Sunnyvale, CA), are working to provide just that.

But there's still a lot of unclaimed ground left over. "There's also a need for mid-range parts, something between a 22V10 and a Logic Cell Array," observes Robin. Such a part would need the flexibility to handle

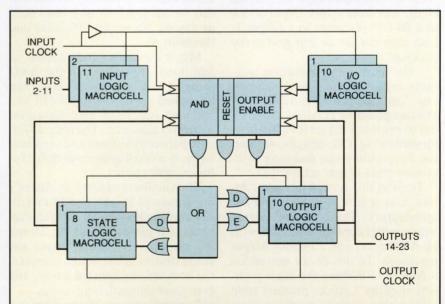

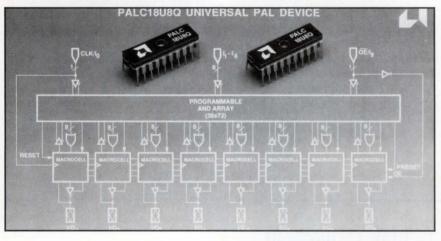

Lattice Semiconductor's 39V18 returns to a programmable-AND, programmable-OR architecture to optimize product term allocation. The 24-pin PLD's input latches, I/O macrocells and buried registers can reduce the number of packages required to implement complex state machines.

### **SYSTEM TECHNOLOGY**/Integrated Circuits

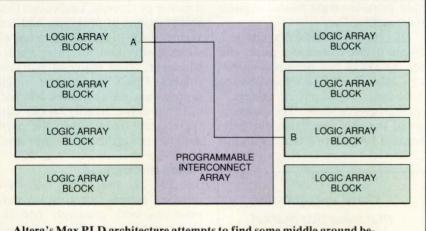

Altera's Max PLD architecture attempts to find some middle ground between conventional PALs and gate arrays. Each chip consists of a number of logic array blocks (LABs), essentially conventional PALs. The LABs are interconnected by a programmable interconnect array: a big, fixed-delay programmable version of a routing channel.

designs other than state machines, so it would need gate-array-like interconnect flexibility. But ideally it would have an understandable, predictable architecture that would look familiar to experienced PAL users.

Altera (Santa Clara, CA) thinks it has hit on this combination with its Max (Multiple Array Matrix) architecture. The architecture is provided in a family of devices, ranging all the way from a 16-I/O-pin device to a 60-I/O-pin giant in a 68-pin Jlead chip carrier or pin grid array package.

"We think our innovation warrants being called a new technology," says Stan Kopec, manager of product planning at Altera. "We set out to provide a device for efficiently implementing TTL designs, without the design hang-ups and long turnaround times of gate arrays."

To meet this formidable goal, Altera took a new approach to PLD architecture. The company started with a rather conventional PAL with an AND array and a flexible output macrocell. To this device was added a feature to address the same problem cited by Lattice: product term utilization.

"Between 70 and 80 percent of designs use only three product terms per output macrocell," explains David Laws, vice-president of marketing. "That means that more product terms permanently assigned to the cell are usually wasted. But in a fixed-allocation system, those product terms have to be there to meet worst-case needs.

"What we do in the Max," Laws continues, "is provide three product terms per macrocell. Then we have a pool of uncommitted product terms, called expander product terms, that can be assigned to any macrocell as needed. So we get efficiency and flexibility."

Max's expander terms appear as additional input lines in the AND array. From there, the terms can be picked up by the macrocell and included just as if they were permanently allocated. The only difference between the fixed and expander terms is a small additional delay for the expander terms.

The smaller members of Altera's line consist of 16-, 24- and 32-macrocell implementations of the architecture, with pin counts of 20, 24 and 28, respectively. But to make the larger devices in the family effective, the company introduced a new, and even more unusual, innovation.

Larger versions of the Max are configured not as a single big PAL with expander terms, but as a cluster of identical 16-macrocell PALs on a single chip. Chips are available with either four or eight of these logic array blocks (LABs), as they're called. To interconnect the LABs, Altera decided against the traditional gate array routing schemes used by programmable gate array vendors.

"The problems with the usual point-to-point routing," explains Kopec, "are that you can run into bottlenecks and that you can't predict what your routing delay is going to be. Some devices can have routing delays as high as 50 ns. We felt that was inappropriate."

Altera's solution is known as a Programmable Interconnect Array (PIA). Essentially, it's a set of uncommitted routing lines running down the center of the chip. From each routing line, connecting lines run through programmable fuses to each LAB. Consequently, the internal feedback signals and I/O signals from any macrocell on the chip can be connected to a PIA line and appear in the AND array of any other macrocell. The delay involved in traversing the PIA is a fixed 15 ns.

Altera's determination to make Max useful for TTL designs extends beyond the architecture to the design tools. Consequently, the design tools for the Max can work with schematic editor input as well as state machine, Boolean expression or truth table forms. Further downstream, tools extract a net list from the design data and then automatically map functions onto Max's architecture, very much in the fashion of a gate array design package.

Though Max's PIA is functionally and conceptually quite different from the variable-delay routing channels on a gate array, there's something about the analogy that sticks. In some sense, the new Altera part represents a synthesis of the well-understood but inflexible 24pin PAL and the highly flexible but more demanding gate array. Similarly, the design problems Max serves contain both elements of the state machine approach served by PALs and the random logic approach served by gate arrays. There may indeed be a fertile middle ground between the extremes. CD

# SMALL NEWS

### PC-based 8051 emulation priced to fit any engineer's desk ... MicroICE. From \$1495.\*

Need full in-circuit emulation capability for your 8051-family applications? We've got small news for you:

MicroICE<sup>™</sup> emulators from MetaLink.

MicroICE fits your budget-and fits on your desk. They're the world's smallest, full-featured 8051 ICE units.

Loaded with capability, a compact, easy-to-operate MicroICE unit takes up less of your already crowded workspace-about 1/4 the space of competitive units. And, priced from \$1495 to \$2495, our 8051-family emulators cost up to two-thirds less.

The MicroICE line offers you the same high performance (compared to

#### **Distributors:**

Distributors:

Advanced Digital Group (213) 598-9645

S.C.A

Comtel Instruments

(216) 442-8080

W.P.A, WV, OH, MI, KY

Comtel Midwest

(312) 392-4040

WT, IL, IN, MO, IA, KS, NE

Monument Technical

(215) 884-3737

E.PA, NJ, DL

our existing MetaICE specialized emulators) with even more features for about half the cost. So, you stretch your budget and give your designers more full-time emulation access-critical when you have multiple projects.

Why MetaLink? We're the 8051 experts. We understand how to maximize your design time-and get you the best performance from your 8051 application-so you can control your development deadlines.

And, you'll like the way we do business: Immediate delivery from our distributors, and comprehensive on-line technical help as close as your phonedirect from MetaLink.

Oasis Sales (602) 277-2714 AZ, NM Pen-Tech (919) 852-6000 FL, GA, MS, AL, TN, NC, SC Syntek (206) 488-0394 WA, OR Technisell (603) 893-1333 NH, VT, MA, ME, CT, RI T-Squared (315) 463-8592 NY (except NYC) **CIRCLE NO. 29**

### MicroICE features include:

- · Full symbolic debug

- High-level language support

- Menu-driven interface

- Real time and transparent emulation up to 16 MHz

- Single line assembler and disassembler

- 2-Kbyte trace buffer

- 16 break trace triggers

- Hardware supporting over 128,000 break conditions

- 16 to 64 Kbyte of program memory

- · 16 to 64 Kbyte of external data memory

- · Support of NMOS and CMOS devices

### **Special offer:**

Evaluate MicroICE with your PC. Call Meta-Link for your free demo diskette. Or, for qualified customers, we offer a free, 10-day trial. Phone 1-800-METAICE. (1-800-638-2423)

MetaLink Corporation P.O. Box 1329 Chandler, Arizona 85244-1329 (602) 926-0797 TELEX: 4998050 MTLNK FAX: (602) 926-1198

\* Price is U.S. list PC is a trademark of International Business Machines Corp.

### Intelligent memory architectures attack real-world computation

ntelligent memory systems, which integrate some specific computational function into a memory device, have for years suffered exile in the halls of academia, barred from the industry because of their heretical, non-von-Neumann approach to computing. But recent increases in VLSI densities make these unique architectures technically feasible. And the continued intractability of some computing problems is making these systems more attractive to designers.

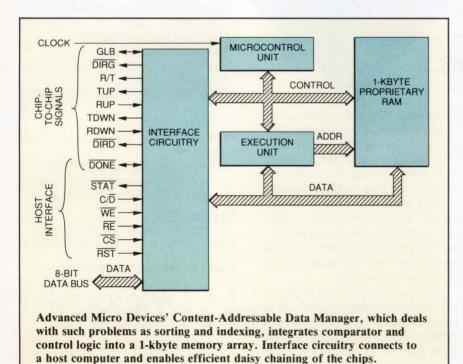

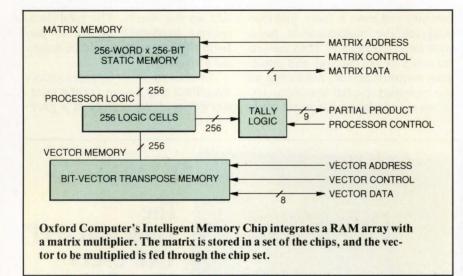

Two recent announcements illustrate the application of intelligent memory systems in real-world problems. The first, a content-addressable memory from Advanced Micro Devices (Sunnyvale, CA), deals with data-management problems such as sorting and indexing. The second example, a memory-based matrix multiplication device from Oxford Computer (Oxford, CT), finds application in areas as diverse as matrix algebra, image processing and neural network research.

#### Ron Wilson Senior Editor

AMD's 95C85 Content-Addressable Data Manager (CADM) is essentially a 1-kbyte array of static RAM with the ability to sort its contents and to match them against a key. This capability lets the CADM act as a sort coprocessor in a system, able to achieve speeds far in excess of those attainable with conventional computing equipment. "AMD has benchmarked the CADM against a Cray X-MP on a number of sorting tasks," claims Dave Horton, strategic development manager at AMD. "While the sort performance is very data-dependent, we found that at worst the CADM was more than 1.3 times faster than the Crav."

The chip has similar performance gains on content addressing. In this mode, the memory stores pairs of fields: a key field and a data field for each record. When the system sends a key to the CADM, the chip must respond with the corresponding data. The speed of this operation is also quite data-dependent, although it isn't influenced much by the total number of records in the memory. Typically, an array of CADM chips

can respond to an 8-byte key in about  $10 \ \mu$ s. AMD observes that this can be up to 500 times faster than software search algorithms.

These speeds aren't due to any breakthrough in process technology, but rather to the internal organization of the CADM chip. Inside, the CADM is essentially a very flexible 1-kbyte first-in, first-out register, surrounded by a bank of specialized comparators and controlled by a proprietary microcontroller.

The design of the FIFO permits two very special operations. First, the width of the register is programmable; hence, you can command the CADM to accept key and data fields of any length up to 255 bytes each. Second, the FIFO performs insert and delete operations very quickly. For instance, the CADM can insert a key/data record into the middle of memory, making room for it by moving all subsequent records down one space, thereby preserving the sequence of the records.

The bank of comparators is closely integrated with the memory array. Consequently, when the CADM is presented with a key, the comparator bank can establish within a matter of microseconds whether that key is present in the memory and where in the sequence of records it belongs. Meanwhile, the microcontroller is kept busy managing all of the pointers necessary for correct operation of the chip.

For cases in which the file does not fit into 1 kbyte, two alternative approaches are available. First, CADM chips can be cascaded to form one very long intelligent memory. Since all of the chips' on-board comparators and controllers will operate at once, the processing speed of the system actually increases as the number of chips increase. Thus, a file that requires a large number of chips will be handled in nearly the same amount of time as a file that fits in one chip. If the files are too big to fit into a bank of chips, search operations may be done by paging the file through the available chips.

Similarly, large files can be sorted in pages and then merged. In either case, the total time required will be considerably shorter than for a software-only approach.

"Originally, we thought of the CADM as a sort engine for data base machines," explains Horton. "But as we started taking the design out to customers for feedback, they began to find new applications. Designers suggested things such as a network bridge, where the CADM could map packet addresses from one network to another without introducing large delays. Other customers suggested hidden-surface removal in graphics systems, disk caching and patternrecognition uses.

"In one way, the part really challenges designers because it's an inexpensive hardware solution to a problem people are used to solving with software at much lower speeds. We are still finding out ourselves what you can do with a chip that can sort and search this fast."

#### **Multiplying matrices**

The integration of processing logic with memory arrays has taken quite another direction at Oxford Computer. Here, the emphasis has been on another time-consuming problem that arises frequently in computing: multiplying a vector by a matrix. "We wanted to drive the cost of a vector-times-matrix multiplication into the ground," says Steven Morton, Oxford founder and chief technical officer. "Then we could look at the applications that the low cost made possible."

Oxford's approach involved first rearranging the steps in a matrix multiplication and then designing an intelligent memory system to implement them. Morton points out that the primary problem in performing the multiply isn't the arithmetic so much as moving all the data around.

Ordinarily, each element in the vector has to be multiplied by each element in the matrix, so the whole matrix gets shuffled through a vector processor once for each vector element. Oxford's idea was elegantly simple: why not put the matrix in a memory and leave it there, and then integrate the multiplication hardware into the memory? Then the vector could be fed through this intelligent memory device, producing all the necessary partial products. External accumulating hardware could add up the results. The total datamoving bandwidth needed to perform the operation would be drastically reduced.

Another stroke of elegance greatly simplified chip design for the memory device. "We arrived at a parti-

### The "Look and Feel" CAE Users Have Been Looking For

Use Visionics' Super Hi-Res graphics board for workstation (1284 × 960) graphics on a PC platform, or use standard CGA or EGA graphics.

# Introducing EE Designer III

The fact is that today's CAE software systems have a lot of features. The problem is that you have to read a huge manual or go to a HELP screen to find the feature you need.

Finally, an integrated desktop CAE software system with all the features you need plus an ergonomic user interface that lets you easily find and access them.

EE Designer III combines onscreen function prompts with a graphic-based hierarchical menu structure. So whether you're capturing a schematic or Auto-Routing your printed circuit board you can always find the function you need. At only \$3995, no other CAE tool can match the features of EE Designer III:

- Supports 2 mb of L/I/M EMS memory

- On-line Netlist Capture

- Forward and Back— Annotation of Multipage Schematics

- Analog and Digital Circuit Simulation

- Full SMT Support

- □ 1 mil Grid Resolution

- □ 45° Memory AutoRouting

- Fabrication/Assembly Drawing Support

343 Gibraltar Drive, Sunnyvale, CA 94089 (408) 745-1551 • **1-800-553-1177** Telex: 346352 Fax: (408) 734-9012

CIRCLE NO. 17

tioning where instead of each processor handling an entire large word. each processor handled one bit of each word," explains Morton. The number of chips that are required to perform an application, therefore, is determined by both the size of the matrix—each chip can hold a  $256 \times$ 256 segment-and the precision of the numbers in the matrix, as one set of chips is required for each bit of precision. Like a conventional by-1 memory chip, the intelligent memory chips are put in an array in which each chip holds 1 bit of each number from the matrix.

Inside the chip is the 256-word  $\times$  256-bit matrix memory. There's also a memory for holding and reorganizing the vector as it's passed through the chip. "Enough vector memory is provided to double-buffer a 16-bit vector," Morton says.

Bits from the matrix memory and the vector memory come together, 256 at a time, in a bank of 256 1-bit multipliers. These 1-bit results are fed to a block of tally logic that begins the accumulation process, keeping track of which 1s go where in the resulting vector.

From the tally logic, results are clocked into a vector accumulator chip that brings the products from all the memory chips together and assigns weights to them, forming a fully significant product vector.

As in the case of the CADM, enlarging the matrix increases the number of chips and, therefore, the number of processing elements. Hence, the matrix's size and precision have only a second-order effect on the time required for an operation. In fact, a user could intentionally partition a relatively small matrix among numerous banks of intelligent memory chips just to increase throughput, Morton notes.

Applications for the part include signal processing, for which matrix multiplication is an important operation. Many similar engineering applications are not targets, however. "This is basically a fixed-point machine," explains Morton. "I'm not sure whether it makes sense in applications that are tied to IEEE floating point. Most of these applications can be done with block floating-point techniques, but right now we've decided to concentrate on fixed-point applications."

Beyond simple matrix multiplication, the flexibility with which Oxford has designed the part opens a spectrum of other alternatives. For one, the intelligent memory chips can be used in a slightly different mode to do convolution for image processing. In convolution operations, pixels get loaded into the matrix memory, and the convolution coefficients are loaded into the vector memory. If the pixels are ordered correctly in matrix memory, the chip will then proceed to convolve the pixels with the coefficients, each clock producing 1 bit's worth of a  $256 \times 256$  convolution.