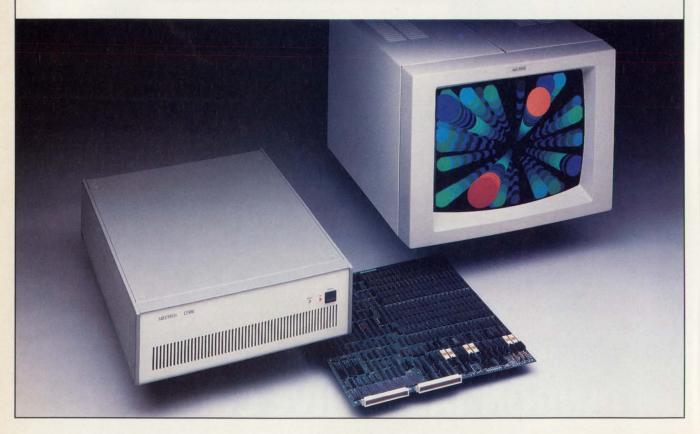

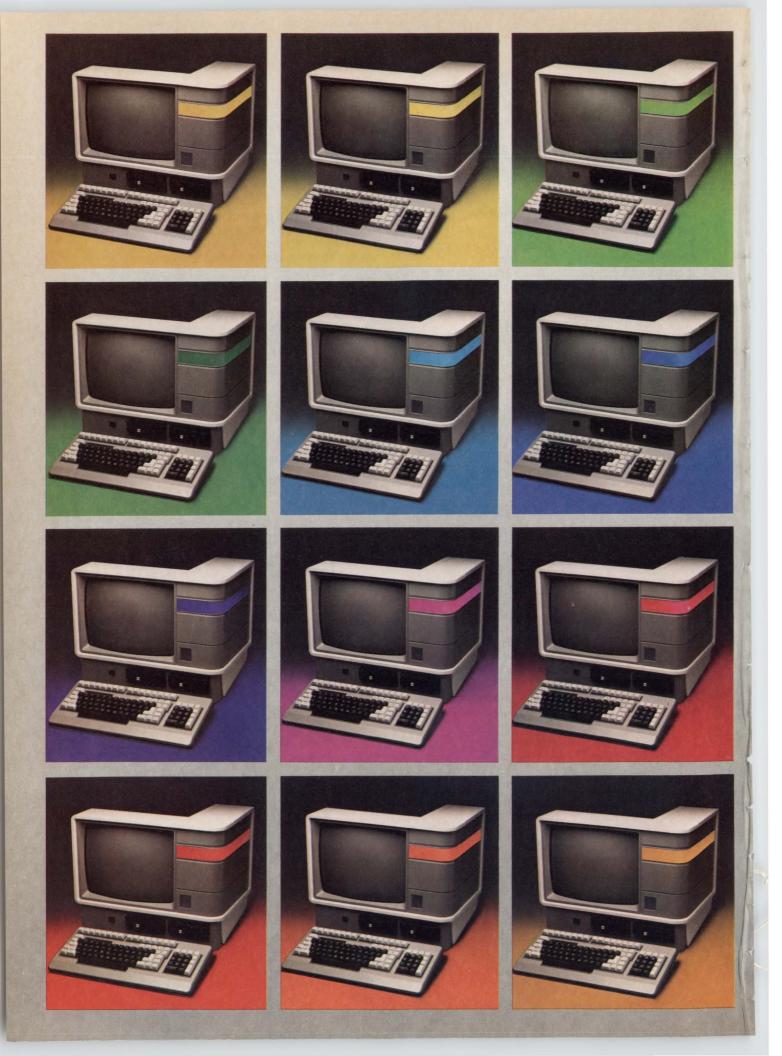

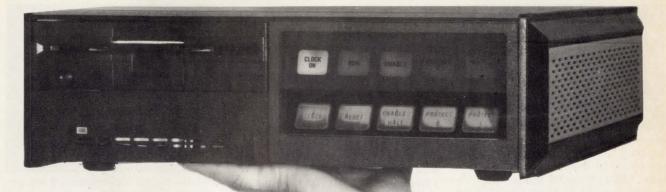

# Introducing the Whizzard 3355. Now you can break the speed limit without paying the price.

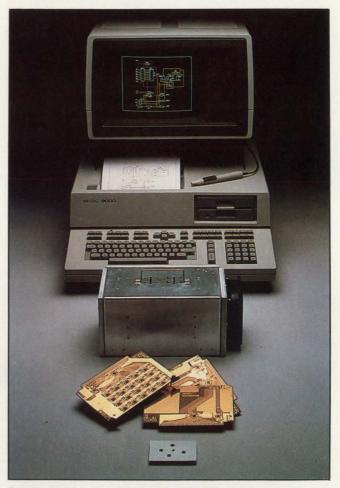

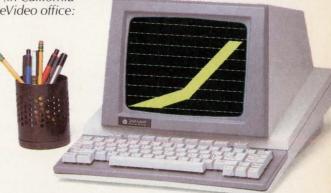

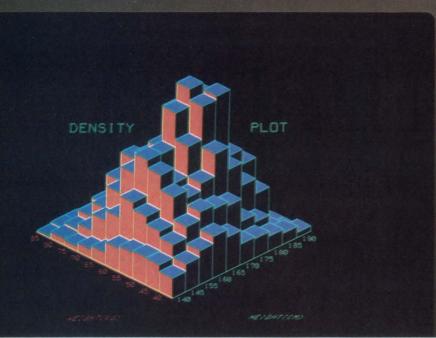

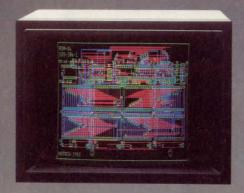

Whizzard 3355. Meet the Whizzard 3355, the newest computer graphics system from Megatek. Up to 400 thousand vectors per second. The fastest high speed performance of any system in its price range, thanks to our Graphics Engine. Upward compatibility with every Whizzard. And a high resolution color raster display with 2D real-time dynamic transformations.

Now you can have the speed you want, and pay a lot less for it in the bargain.

The Whizzard 3355 is a full-function computer graphics system that cost-effectively supports your graphics applications. Especially in the areas of mechanical or electronic CAD, simulation, or command and control. And its RS232C interface, with its own 16-bit processor and up to 500 Kbyte dedicated local RAM, offloads the host computer and allows serial communications.

The Whizzard 3355's standard features include a 19" 1024² 60 Hz non-interlaced monitor, 16 simultaneously displayable colors out of a possible 4096, complex 2D graphics transformations (rotate, translate, continuous scale, and clip), and proprietary local processor with serial interface. You also get VT-100™ emulation, an ergonomic keyboard, and a host of available options. Then there's graphics software. Megatek's WAND,™ TEMPLATE\* and a wide variety of third party application packages, too.

application packages, too.

The Whizzard 3355. High speed performance, and true cost-effectiveness.

That's Megateknology.

# World Headquarters • 3605 Scranton Road • San Diego, California 92121 • 619/455-5590 • TWX: 910-337-1270 European Headquarters • 34, avenue du Tribunal-Fédéral • CH-1005 Lausanne, Switzerland • Telephone: 41/21/20 70 55 • Telex: 25 037 mega ch

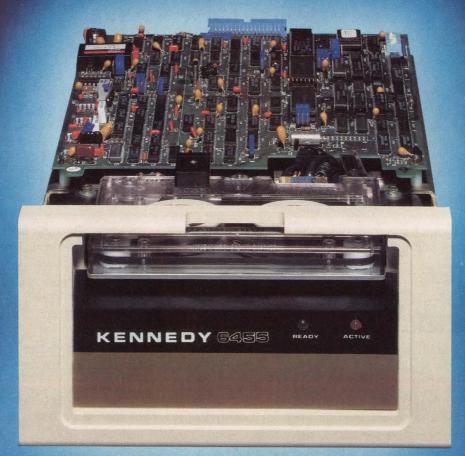

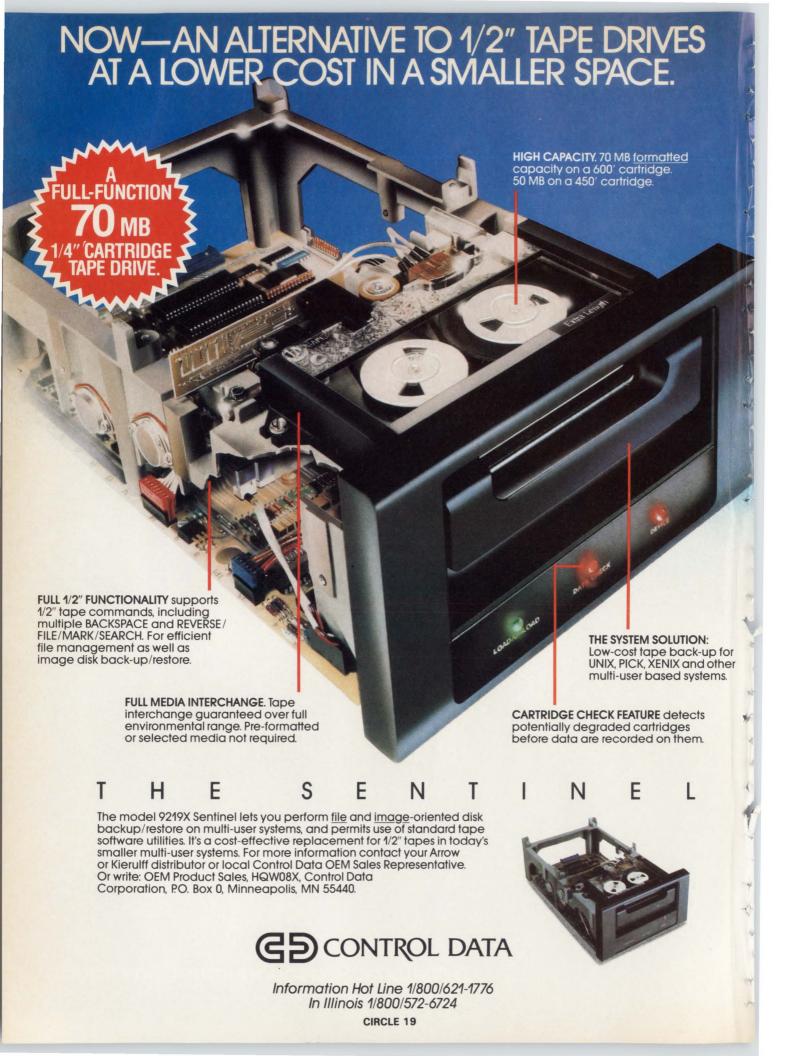

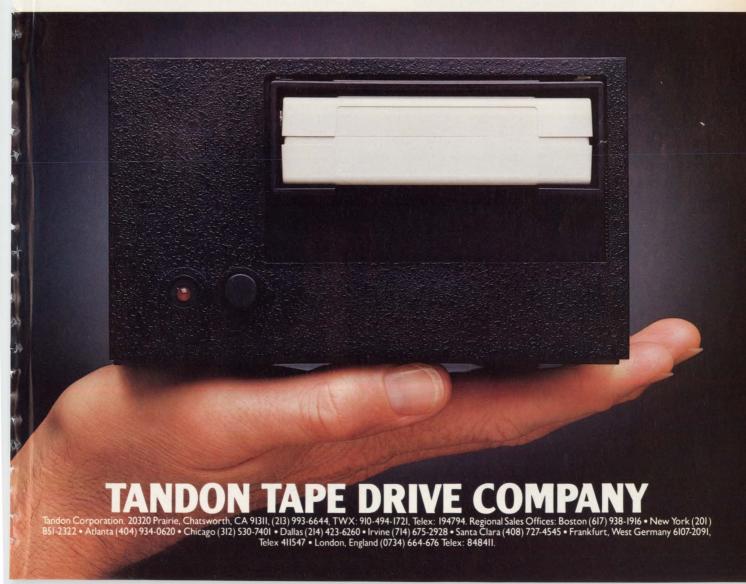

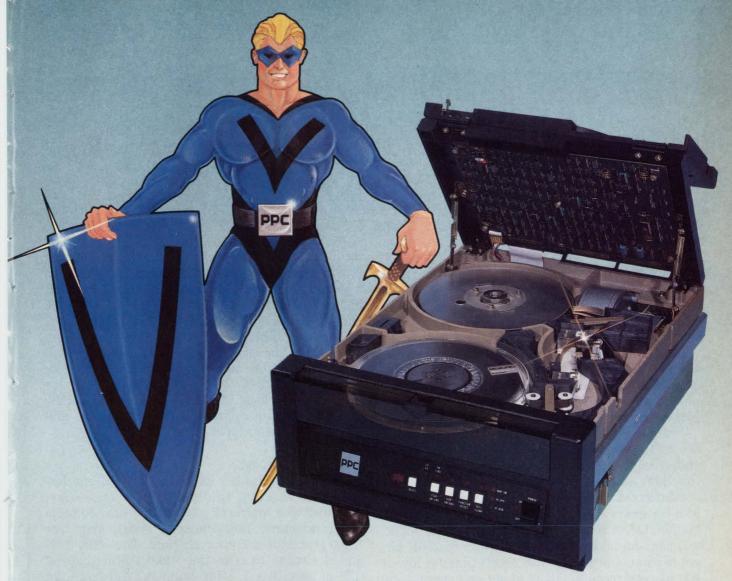

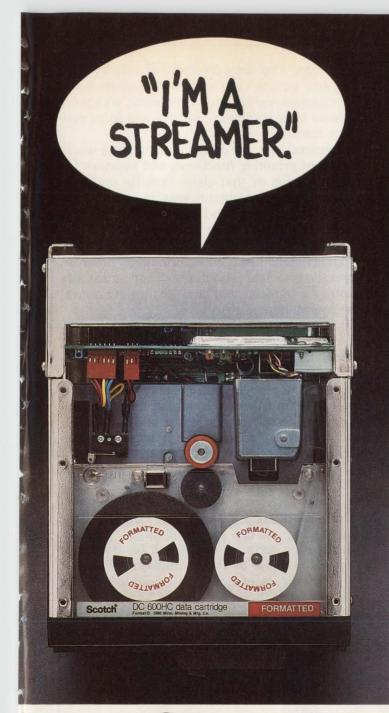

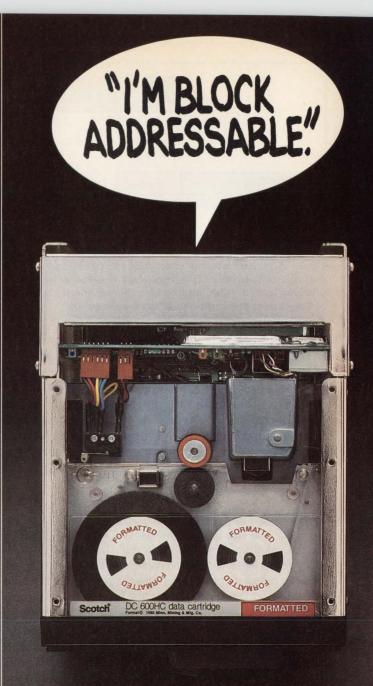

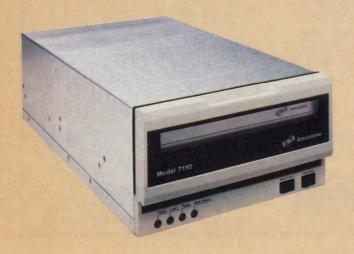

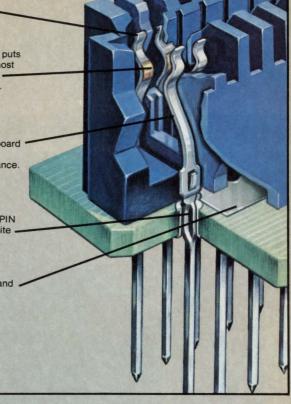

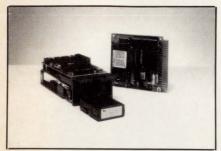

Model 6455 Cartridge Tape System

# Loaded with Features — Loaded with Benefits.

Kennedy products have always provided innovative new features. And these features have always provided added benefits and convenience for the user. For instance, our Model 6455 offers these features and benefits:

Feature: Start/Stop Operation

Benefit: Drive can emulate a 1/2" tape drive by providing

the ability to perform selective file back-ups, file-restructuring, journaling and software

updates.

The drive is effectively a 1/2" Tape Drive in a

smaller package.

Feature: Hard Read Error Spec. of 1 in 10" bits.

Benefit: Best data reliability of any tape cartridge drive.

Gives the user confidence in the integrity of the

back-up medium.

Feature: On-board Diagnostics

Benefit: Drive can be tested off-line with no test

equipment required. Use of S.A. also lowers the

MTTR.

Feature: Cartridge Jam Protection

Benefit: Protects the cartridge from damage if cartridge

jams. This is accomplished by sensing a current surge and then disabling the motor, thus

insuring that the cartridge will not be damaged.

Feature: High Density Recording

Benefit: Storage capacity of 23 MB on a single cartridge.

Feature: Optional industry standard ½" tape interface.

**Benefit:** Operates with existing tape couplers and software.

The drive operates as though it were a  $\frac{1}{2}$ " tape drive without having to modify existing

hardware or software.

By now you can see what we're driving at. Model 6455 is full of unique features and benefits for you. For the complete story, write or call us today.

# KENNEDY

An Allegheny International Company 1600 Shamrock Ave., Monrovia, CA. 91016 (213) 357-8831 TELEX 472-0116 KENNEDY TWX 910-585-3249

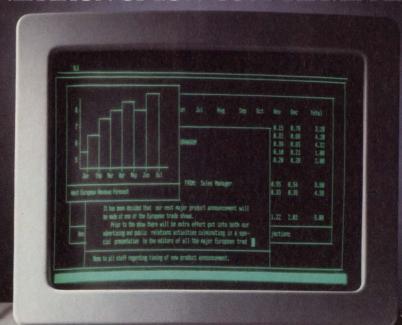

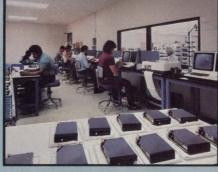

# THE 22-SECOND DEMONSTRATION OF DESKTOP PERFORMANCE

In the computerized business of the eighties, more decisions will hinge on getting the right information in the right hands at the right moment. How well you do that will ultimately depend on the performance and durability of your printer.

# SMARTER, FASTER, STRONGER.

In the Tally MT160/180 series, a powerful 16-bit microprocessor masterminds document flow. That means saving valuable seconds when seeking the shortest possible print path. And printing at top speed all day long. Some machines claim 160 cps but can't hold that speed because they're not engineered or built like a Tally.

You can quickly run down the extensive menu of print styles and word processing enhancements, making selections at a touch. On *L* models, switch from draft mode to letter quality just as easily and get results the *Creative Computing* magazine calls "superb."

All 160/180 models have adjustable tractors and friction feed paper handling. And both parallel and serial interface ports are built in. So you're ready to print right out of the box.

The spreadsheet you see above was produced in a scant 22 seconds. In an age when every moment counts, that's desktop performance at its best.

For more information and the name of your nearest dealer, call toll free: 800-447-4700.\*

\*In Illinois: 800-322-4400 In Canada: 416-661-9783

MANNESMANN TALLY

# **UP FRONT**

CALIFORNIA INSTITUTE OF

MAR 8 1984

# Realtime system integrates process control and plant information

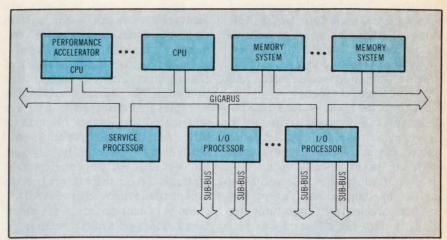

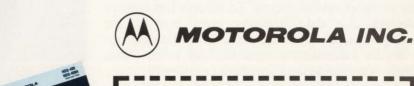

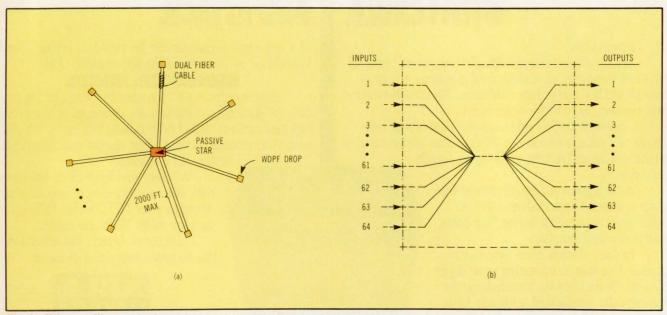

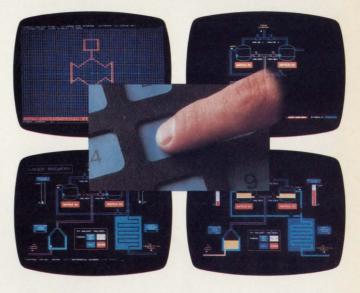

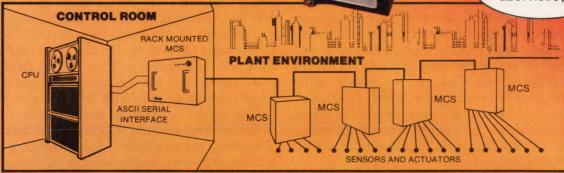

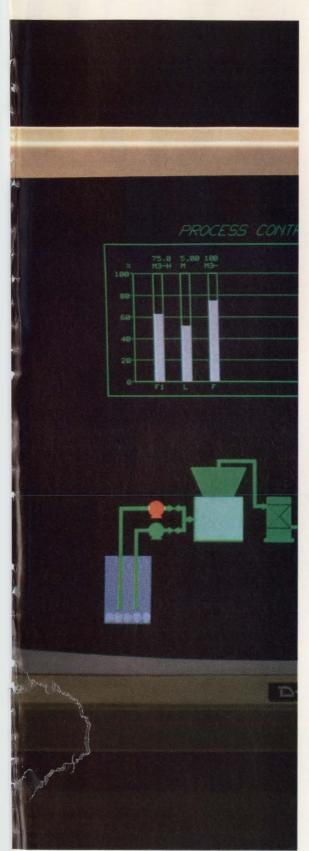

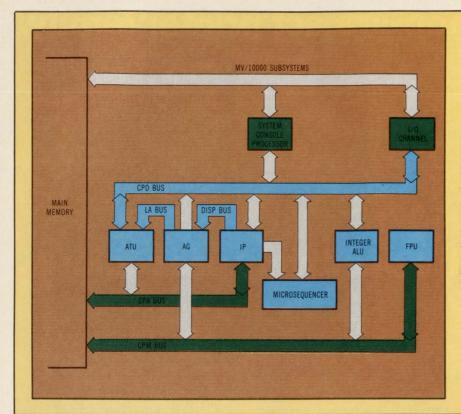

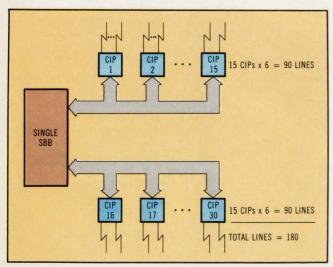

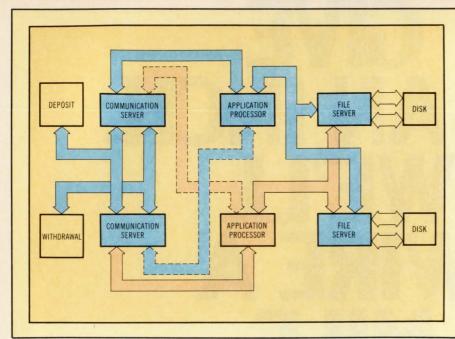

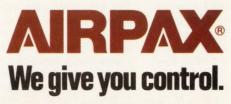

Parallel processing has brought about complete integration of process and information management in a control system announced at the October Instrument Society of America (ISA) conference in Houston. The TDC 3000, introduced by Honeywell's Process Management Systems Div of Phoenix, Ariz, functions in real time through a local control network (LCN). Data Hiways link microprocessor-based multiloop controllers, application modules, and computing modules to the 5-Mbit/s LCN via gateways that buffer and translate data. Other gateways link the system to plant computers and instrumentation subsystems.

Three levels of control are maintained: the hardware oriented single function process level, the unit control and optimization level, and the plant-wide strategy level. All levels interface through a universal station that provides a single window to all information. Plant data acquisition and control functions for both continuous and batch processes are integrated. Information access is provided at the station via keyboard and CRT or through an optional touch screen. When an alarm light flashes on the display, the operator merely touches that alarm on the screen. Detailed information to assist the operator's next action then appears.

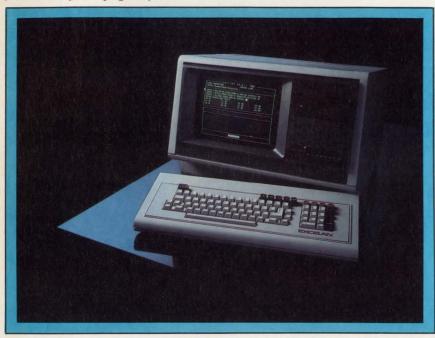

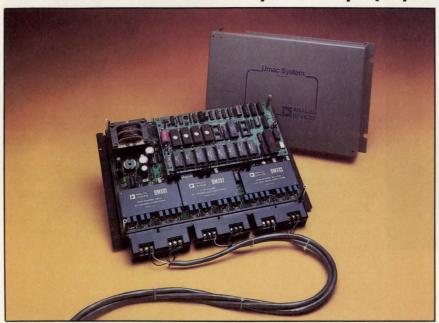

# I/O system converts Rainbow to data recognition systems

Although not yet officially announced by Data Translation (Marlboro, Mass), the Digital Equipment Corp booth at ISA contained a DT311 I/O subsystem attached to a Rainbow 100 personal computer to form a complete data acquisition and control system. A microprocessor interface to the Rainbow controls all analog and digital I/O operations and self-test functions. The subsystem, part of the manufacturer's PCDAX family, can be programmed under CP/M or MS-DOS.

# The other PCs still in evidence at ISA

Programmable controllers, which were known as PCs long before the now better known personal computers were even available, are still a major part of the plant and factory control picture. Both types of PCs could be seen at various ISA booths but it was apparent that the new PC was not likely to eliminate the longer established PC in the near future.

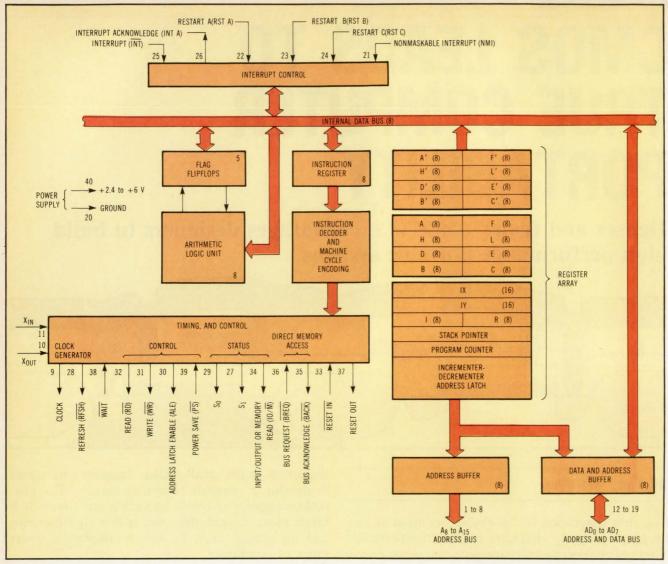

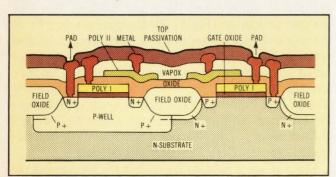

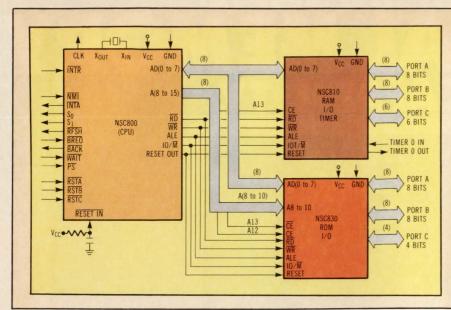

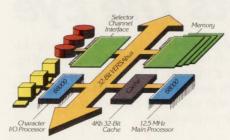

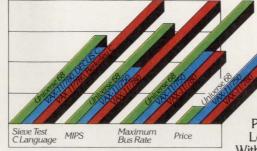

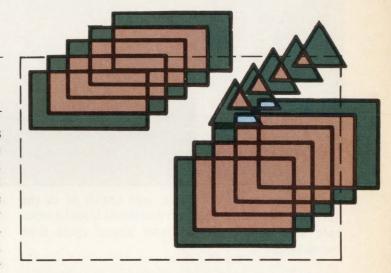

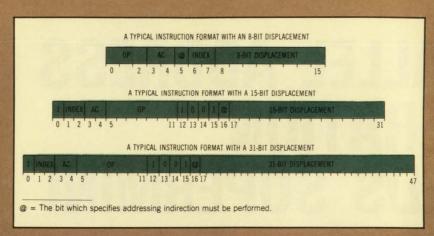

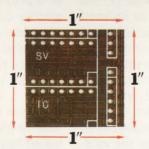

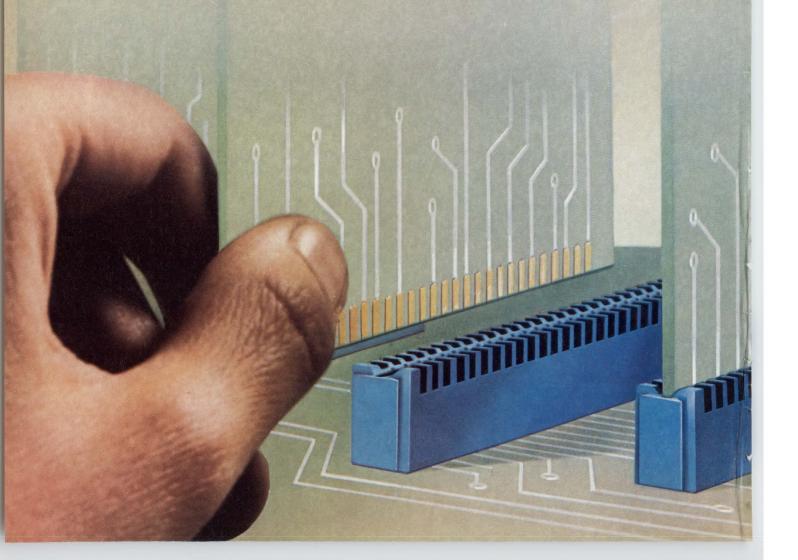

# True 32-bit micro debuts

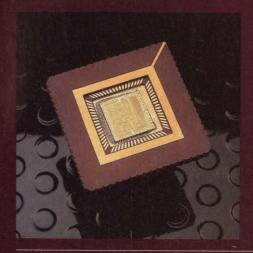

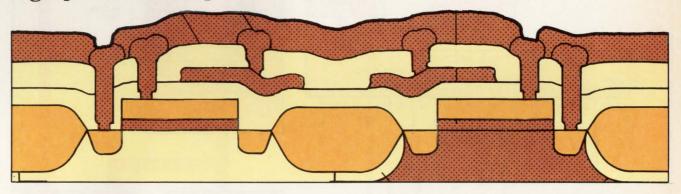

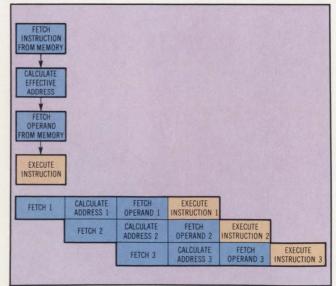

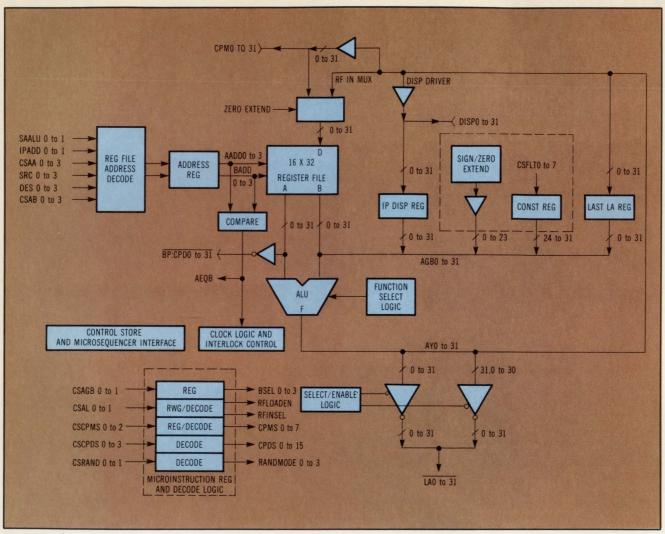

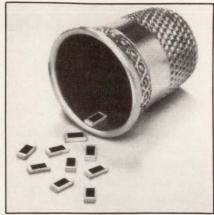

Claimed to be the first commercially available 32-bit microprocessor, the NS32032 was introduced last month by National Semiconductor of Santa Clara, Calif. The chip, a member of the company's NS16000 family, features true 32-bit internal and external architecture and supports high level languages. Unlike its competitors, the IC's internal and external buses both for addresses and data as well as the ALU and registers are all 32 bits wide. This configuration effectively speeds up computational operations, in some cases halving the time that data circulates among memory, ALU, and registers. The company anticipates that, because of the chip's features, many current mainframe and minicomputer OEM companies will find it easy to transport their 32-bit high level software onto 32032-based systems. A 6-MHz version of the chip is available immediately for \$220 in high volume quantities. A 12-MHz chip will be available in the first quarter of 1984.

# **UP FRONT**

# Word processor types as if it writes

A handheld word processor that uses only five keys to type a letter as one would write the letter by hand has been imported from England by Microwriter Ltd of New York. The unit contains an 8-Mbyte nonvolatile memory and can be attached directly to printers. It is programmed, when attached to a video screen via an RS-232 serial interface, to send out ASCII code according to the sequence of the activated five keys. The company claims that a typical user can learn the appropriate sequence of keys for the entire alphabet including punctuation marks and numerals in about an hour. Unit price is \$499.

# English is not English-like

Themis, a friendly query program, uses artificial intelligence concepts to allow users of VAX-11 machines to pose commands in English. This frees the users from learning another set of English-like instructions, which is a common chore for most query programs. The software can understand up to 900 common English words and can be expanded by the user for a specific application. The package runs in 1.5 to 2 Mbytes of main memory and requires either VAX-11 Datatrieve or the Oracle relational database management system. Themis will be available from Frey Associates of Amherst, NH in the first quarter of 1984 at a price of \$24,500. A similar program for running on IBM machines will soon follow.

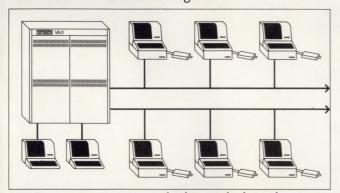

# Netting relational data bases

Ingres owners can now expand their reach by using Ingres/Net, a software package that allows distributed access to remote data bases on any VAX computer that is part of a DECNET network. Thus functions can now be distributed with applications running on the user's local system while the Ingres database management systems can run remotely. According to the company, Relational Technology Inc of Berkeley, Calif, this configuration decreases communication costs and improves response times for interactive applications. With Ingres interfaces such as queries, graphics, reports, and applications-by-form, the user can display, update, or retrieve data stored on any VAX in the network. Network access is transparent to the user. Ingres/Net will also be available on 68000-based systems that support Ingres in the Unix environment.

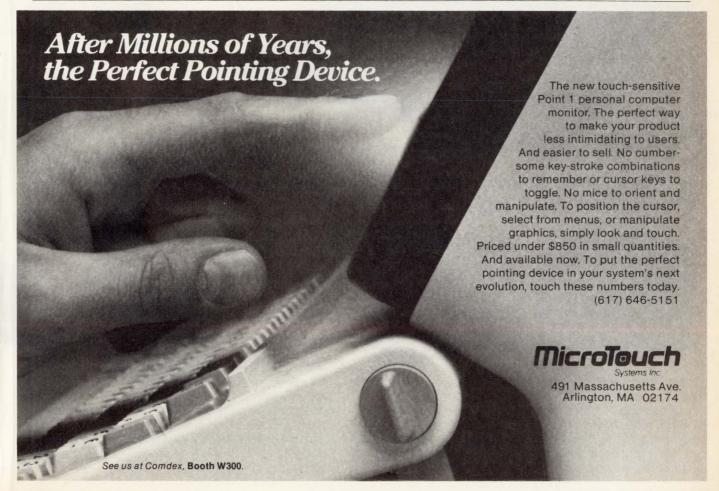

# Matrix printer prints quality letters

A letter-quality multimode matrix printer will be introduced at the Comdex Fall show later this month in Las Vegas. Designers have incorporated key features in today's office printer in a dot-matrix unit such that the output is distinctly letter quality. Letter mode runs at 45 char/s while "draft" mode prints at 250 char/s; a third mode yields a 16 x 72 matrix at a rate of 100 char/s. Multiple fonts are available. The multi-color graphics resolution is 240 x 720 dots/in. Advanced Matrix Technology, Inc (Newbury Park, Calif) plans to have full production capabilities by the first quarter of 1984. Initial OEM price will be \$2995.

COMPUTER DESIGN (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in April and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell Street, Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$50 in U.S.A. and \$75 elsewhere. Single copy price is \$5.00 in U.S.A. and \$7.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. POSTMASTER: CHANGE OF ADDRESS-FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (USPS 127-340).

**VBPA ₹ABP**

Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101: P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President/Finance; L. John Ford, Vice President.

COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

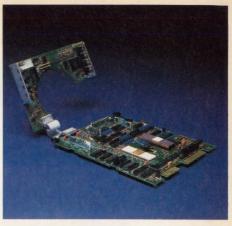

# Start with an LSI-11

Dataram's W23 starts with the LSI-11/23 (soon the LSI-11/73)

DATARAM

1.0 MB minimum... up to 4.0 MB!

27 dual-slot backplane

RM02-compatible 80 MB or 160 MB Fujitsu Winchester I/O mapping accommodates

18-bit peripherals (e.g. RX02)

and 22-bit peripherals,

while supporting 4.0 MB of memory

W23's RM02-compatible controller can support external CDC 9762 SMD drive for removable media capability or backup, in addition to controlling the integral Winchester

\$16,940 system price\*

Supports RSX-11M, RSX-11M-PLUS, RSTS, and UNIX

Cipher Microstreamer with controller available for less than \$5300

...and end up with a powerful minicomputer!

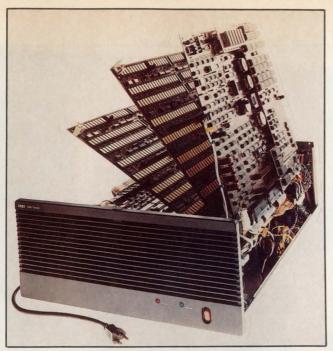

Dataram's W23 minicomputer system gives you more than an LSI-11. By packaging an LSI-11/23 (or LSI-11/73) in a compact 10½" chassis with 160 MB Winchester capacity, 27 dual slots, and a hefty 50 A power supply. And then going a step further with I/O mapping that allows up to 4.0 MB of memory while supporting both 18-bit and 22-bit controllers.

For more information, forward this coupon to us or, even better, call us today at (609) 799-0071.

☐ Send information.

☐ Contact me immediately.

Name

Company

Address

ate

Phone

Return to:

Dataram Corporation, Princeton Road, Cranbury, NJ 08512

\*\$16,940 system price is single-quantity domestic price for W23 with LSI 11/23, 1.0 MB, 80 MB Winchester, and I/O mapping.

DEC, LSI-11, RSTS, and RSX are trademarks of Digital Equipment Corporation UNIX is a trademark of Bell Laboratories.

Dataram Corporation ☐ Princeton Road ☐ Cranbury, New Jersey 08512 ☐ (609) 799-0071 ☐ TWX: 510-685-2542

# **COMPUTER DESIGN®**

# System technology

Page 36

- 33 Software: Artificial intelligence systems make their mark

- 36 Data communications: Workstation analyzes and simulates LANs

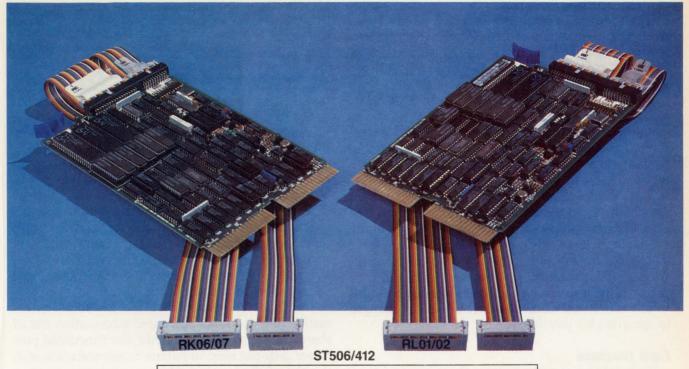

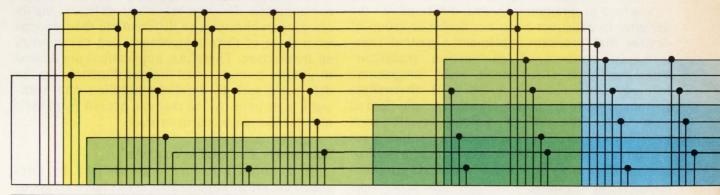

- 50 Microprocessors/microcomputers: DEC counterattacks with advanced Q-bus boards

- 54 Memory systems: Hardware disk cache boosts online performance

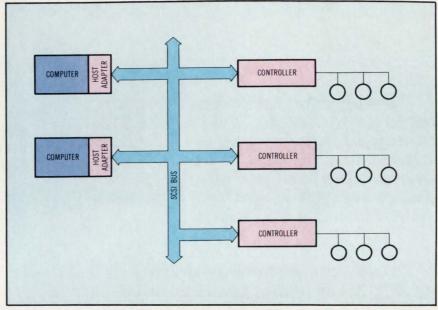

- 64 Interface: Processors divorced from peripherals with separate I/O bus

- 74 Peripherals: Color graphics system accesses images at 20M bytes/s

- 76 Computers: Message-based OS balances tasks in 64-bit multiple CPU system

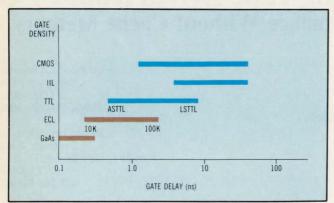

- 87 Integrated circuits: Commercial GaAs digital ICs run at 2 GHz

Page 118

- Integrated circuits: CMOS leads to true computer portability by Tony Moroyan—Denser and faster CMOS VLSI encourages designers to build high performance portable systems.

- 107 Software: Occam architecture eases system design—Part I by Pete Wilson—Software development is simplified by constructing a language—Occam—suitable for the description of multiple processor systems.

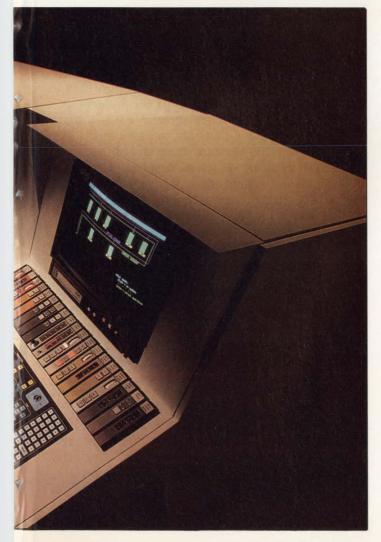

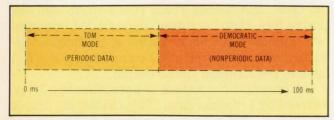

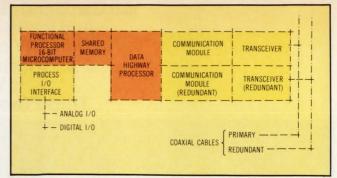

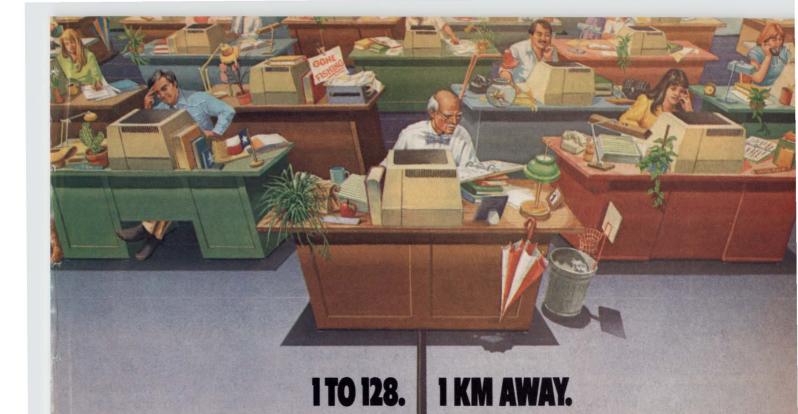

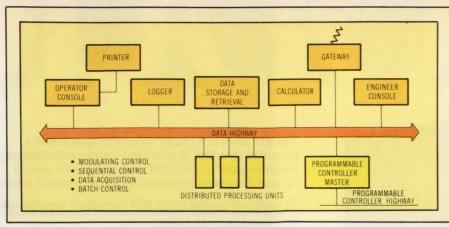

- 118 Data communications: Data highway provides database management by Kirk D. Houser—With the industrial environment, a high performance network prevents degradation of distributed control processing.

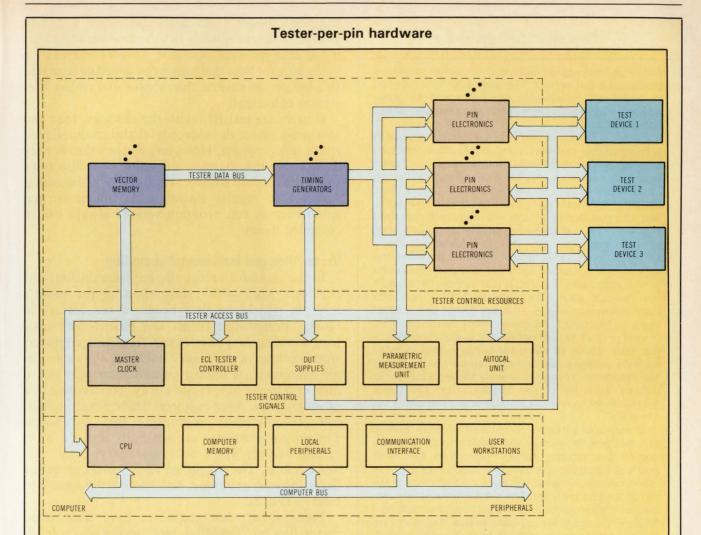

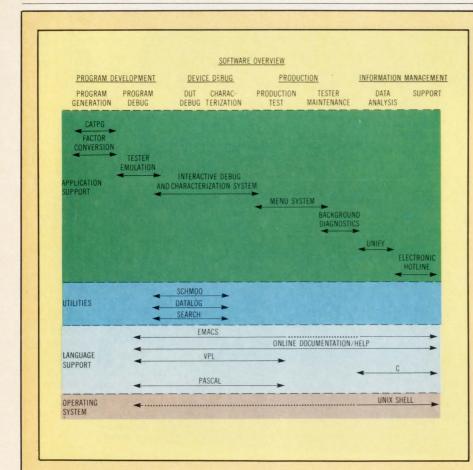

- 133 Test & measurement: Develop VLSI test software quickly by Lance Lawson—With complete test hardware devoted to each pin of a VLSI device under test, users can write test programs in Pascal for a multi-user environment.

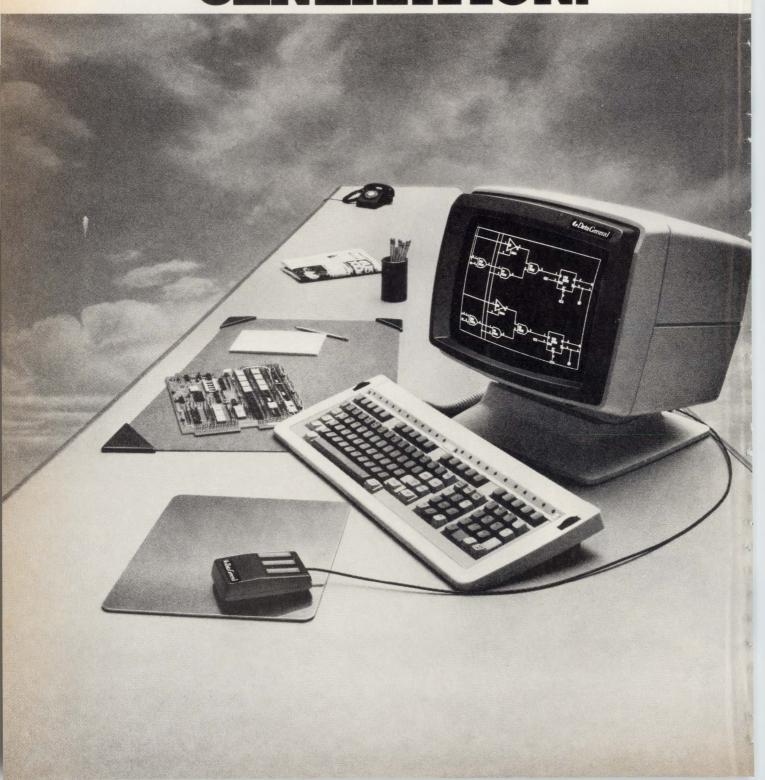

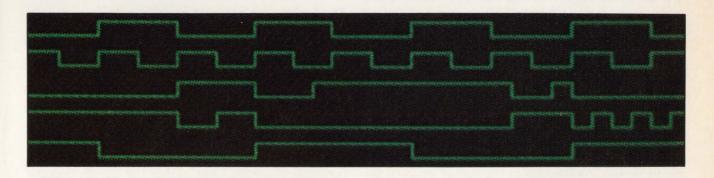

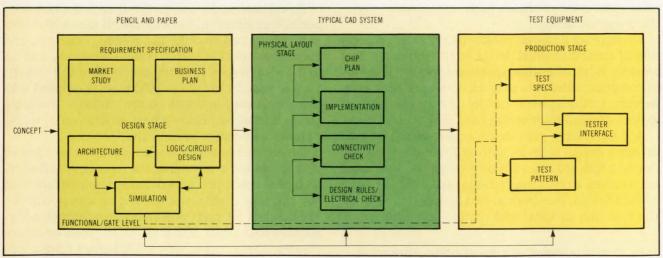

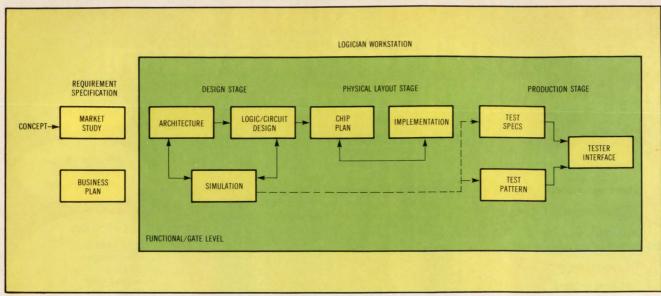

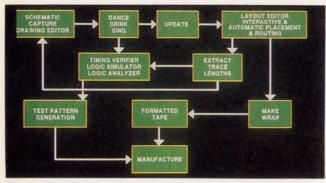

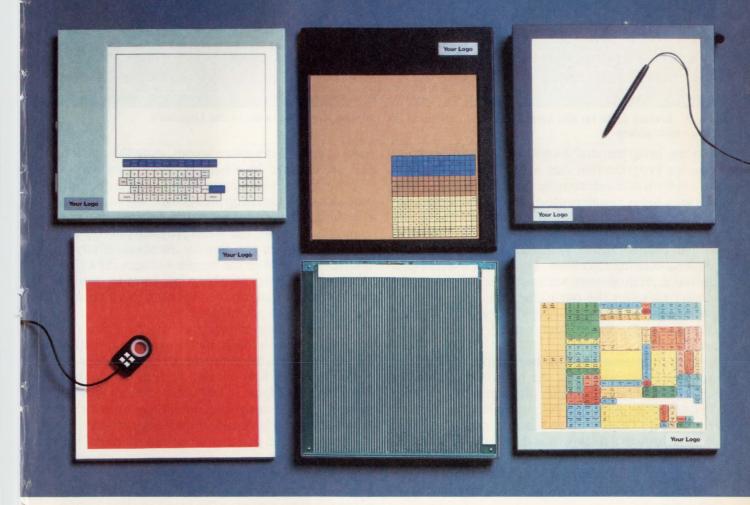

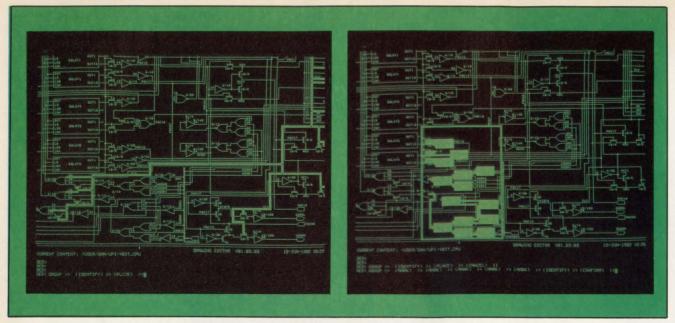

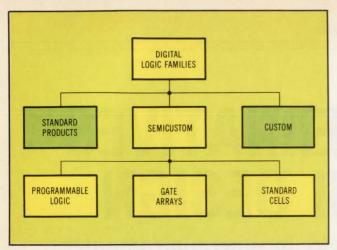

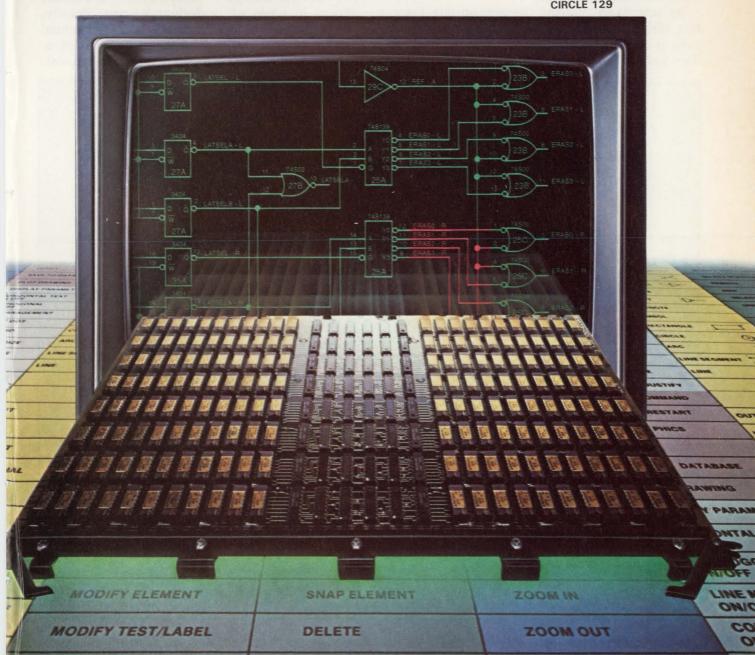

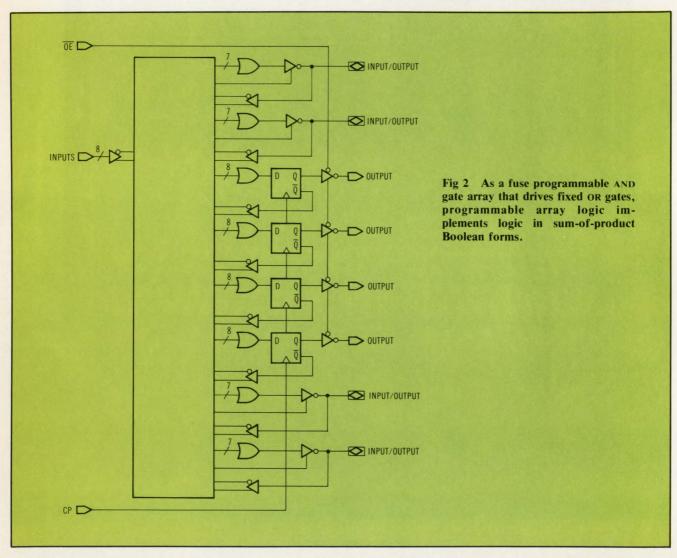

- 145 Development systems: CAE unifies logic and gate array design by John Wright—Standalone computer aided engineering systems prevent logic errors and force correct layout. Results are lower equipment cost, reduced feedback time, and computing power for designers.

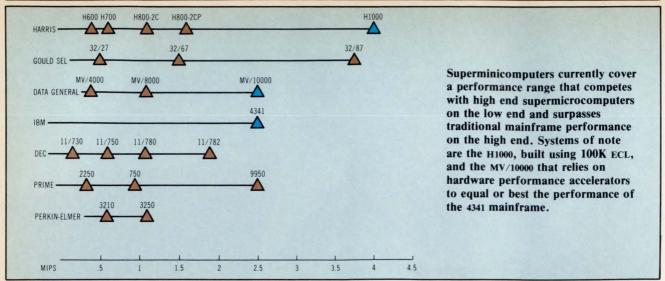

# Special report on minicomputers

163

Caught in the throes of change, minicomputers are taking on new technology and adopting new architectures in preparation for the future. These moves, necessary to fend off the sallies being made by both micros and mainframes, are both evolutionary and revolutionary. With performance levels boosted by both technology and innovation, today's systems continue to hold the price line. Newcomers entering the market bring with them nontraditional concepts. This influx of new blood virtually guarantees that minicomputers will fend off threats from 32-bit micros as they arrive on the scene.

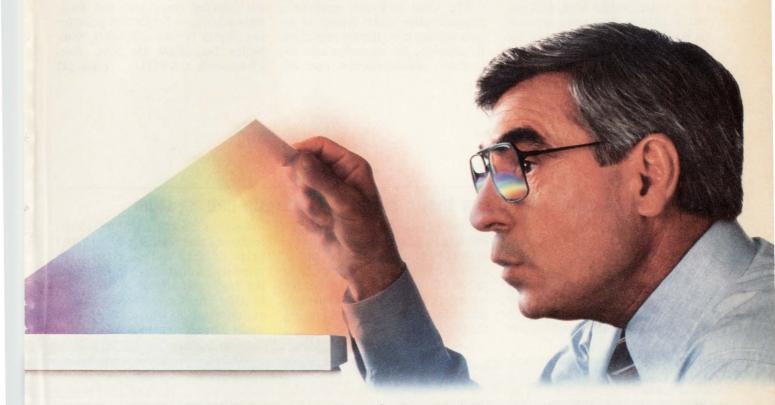

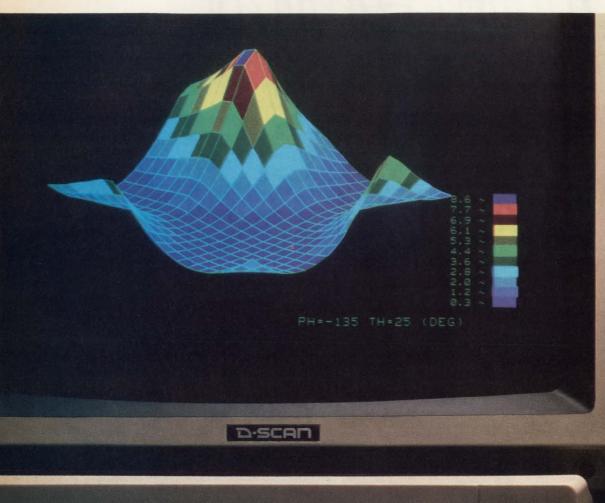

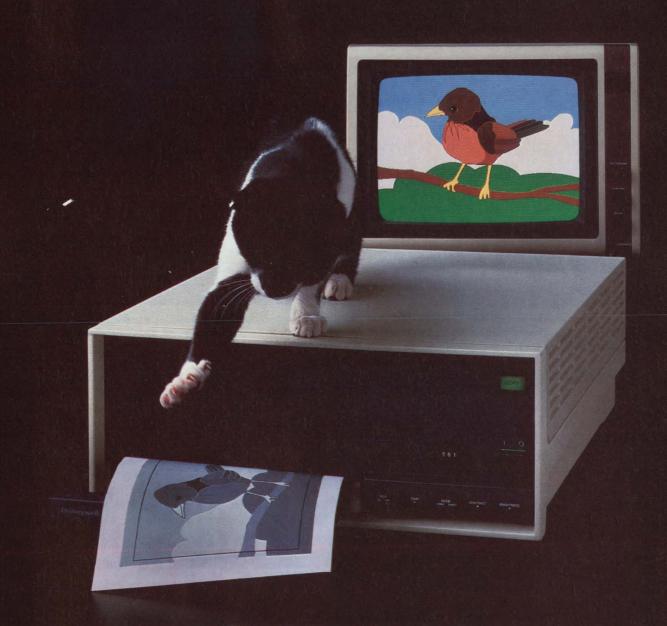

This month's cover was created and designed by Mark Lindquist and Alan Green on the Digital Effects Video Palette III and D-48 high resolution camera system.

# System components

Page 272

- 271 Measurement and control system employs powerful Basic

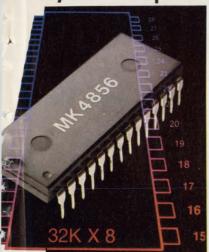

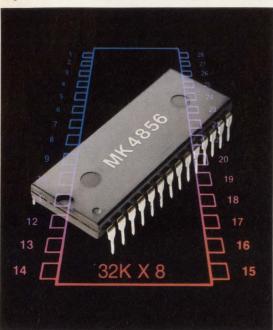

- 272 New generation, 32K x 8 DRAMs provide wide operating margins

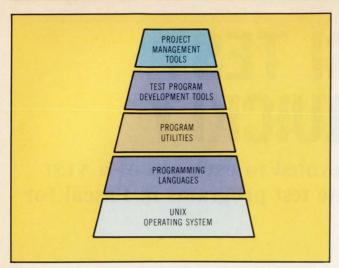

- 272 Multi-user development system runs Unix version

- 273 High performance workstation offers processor options

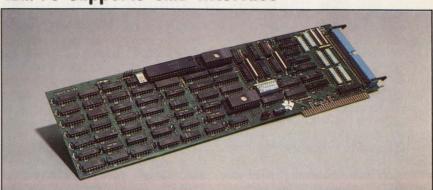

- 273 Rigid disk controller for IBM PC supports SMD interface

- 274 Superminicomputer uses 100K ECL for high speed

- 274 Modular PCU improves broadband LAN performance

- 276 Memory systems

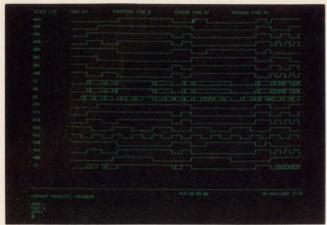

- 278 Development systems 308

- 283 Data conversion

- 203 Data Conversion

- 284 Peripherals

- 286 Data communications

- 293 Control & automation

- 299 Power sources & protection

- 300 System elements

- 307 Test & measurement

- 308 Interface

- 311 Integrated circuits

- 314 Interconnection & packaging

- 315 Software

- 316 Computers

- 316 Microprocessors/

- Microcomputers

# **Departments**

| 3   | Up front              | 323 | Designer's bookcase    |

|-----|-----------------------|-----|------------------------|

| 11  | Editorial             | 324 | System showcase        |

| 17  | Editorial rebuttal    | 326 | Advertisers' index     |

| 25  | Letters to the editor | 331 | Reader inquiry card    |

| 318 | Literature            | 331 | Change of address card |

| 321 | Calendar              |     |                        |

## Designers' preference survey\*

297 Development systems, test & measurement

For the 68000 design team manager whose job depends on the deadline.

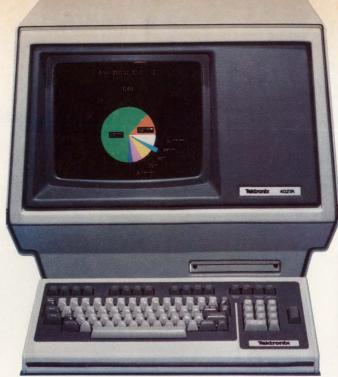

# Tektronix announces 68000, 68008 and 68010 support.

### The only productive choice for 16-bit design.

You've got deadlines to meet, and you can't afford to waste your engineers' time with desk-top development tools. So Tek brings you the power you need to get your project done, whether your team is designing with the 68000, 68008, 68010, or all three. Your design team will work faster, from software and hardware development through debugging and integration.

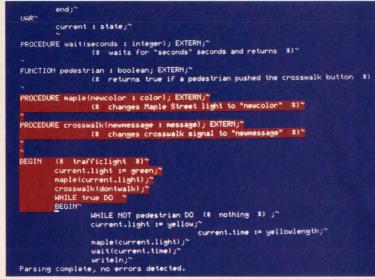

## Tek LANDS saves time with Pascal and C design support.

The LANDS languagedirected development system helps you finish your project on schedule. With the languagedirected editor, you quickly track down syntax errors before compiling. Our microcomputeroptimized Pascal and C compilers with The Integration Control System\* let you write

even device dependent code without assembly language. And then, you debug on your hardware entirely in Pascal or C.

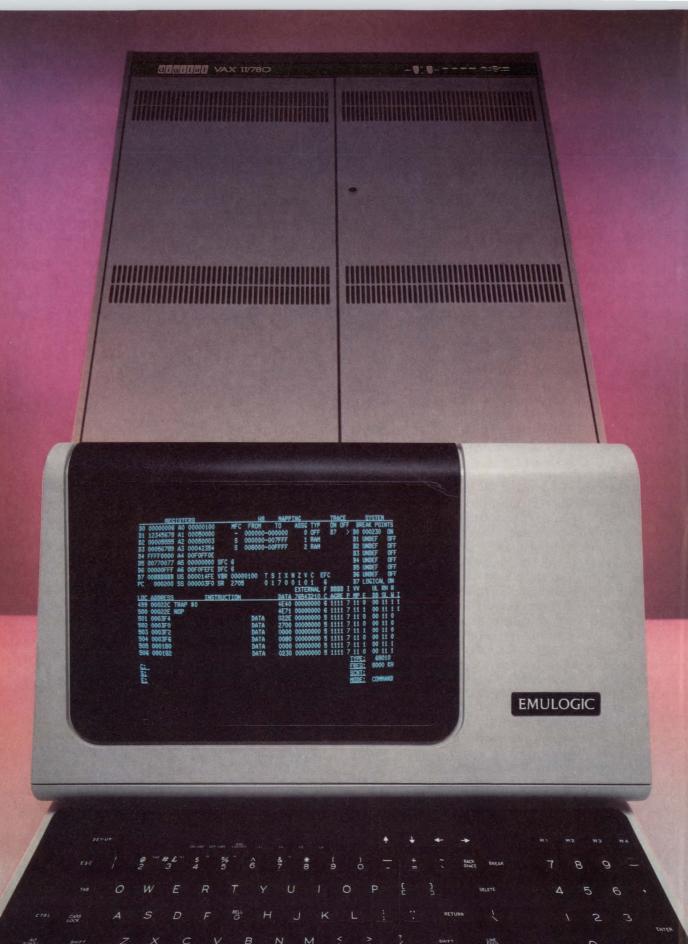

### Whether stand-alone or on your VAX™, you get the same tools.

Make sure your team's computing power is matched to the job at hand. Choose our 8560/40 stand-alone development systems with their own multiprocessing computer. Or select the 8540 integration unit and Tek's software, and turn your VAX into a powerful microcomputer design system, with all the capabilities of our proven tool set.

Either way, you can count on Tek's superior emulation to

get your products to market faster. Full speed, completely transparent emulation of the 68000, 68008, and 68010 lets you concentrate on your design,

not on the limitations of outmoded tools. And support for a wide variety of other chips with the addition of the appropriate emulator and software guarantees the return on your investment.

## Call 1-800-547-6711 for technical details.

Call us for your new brochure and for data sheets on any of our emulators. Or contact your local Tektronix Sales office.

### For further information, contact:

U.S.A., Asia, Australia, Central & South America, Japan Tektronix, Inc., P.O. Box 1700, Beaverton, OR 97075. For additional literature, or the address and phone number of the Tektronix Sales Office nearest you, contact: Phone: 800/547-1512, Oregon only 800/452-1877, TWX: 910-467-8708, TLX: 15-1754, Cable: TEKTRONIX Europe, Africa, Middle East Tektronix Europe B.V. European Headquarters, Postbox 827, 1180 AV Amstelveen, The Netherlands, Phone: (20) 471146, Telex: 18312-18328

Canada, Tektronix Canada Inc., P.O. Box 6500, Barrie, Ontario L4M 4V3, Phone: 705/737-2700

\*Patent Applied For

™VAX is a registered trademark of Digital Equipment

Language Directed Editor reduces compile time by detecting and correcting syntax errors.

# Some of our VARs' best ideas began on the backs of envelopes.

Great ideas, plus hard work, business sense and commitment to customer satisfaction. That's what it takes to be a Value Added Remarketer for IBM.

IBM is looking for business people with specialized industry experience. For companies that can successfully merge our systems with applications software. For those to whom quality is fundamental.

### Put IBM to work for your customers.

To begin with, IBM wants qualified VARs to have the broadest choice of systems and software: the IBM Personal Computer, Displaywriter, Datamaster, CS-9000, 4300 systems, System/36 and Series/1 with its new enhancements.

These products carry IBM's reputation for quality. Equally important, all have access to IBM's nationwide service.

That means VARs who work with IBM have more to offer their customers. But that's only part of what IBM can offer to its VARs.

### Put IBM to work for you.

IBM also provides VARs with tools to assist them in marketing to their customers and prospects.

For instance, IBM helps VARs with business shows and product literature. We help VARs create their own direct mail programs.

And IBM brings prospects with special needs together with VARs who have unique solutions. It's done with a special referencing system which supplies information about our VARs' offerings to IBM's salesforce

IBM's Value Added Remarketer Program: Great ideas, hard work and business ability are what's required. For more information, call 1 800 IBM-VARS or send in the coupon.

# **DEMOCRATIZING THE IEEE**

What I have to say this month is more of a personal statement than an editorial. As a long-standing and long-suffering member of the Institute of Electrical and Electronics Engineers, I believe control of that organization should be returned to its membership. To further the goal of making the IEEE a participatory democracy, I hope to cast a write-in vote for Irwin Feerst, chairperson of the Committee of Concerned EEs, as president-elect.

I say that I "hope" to cast my vote because, unlike most IEEE members, I have not yet received a ballot form. One of the many ways in which the IEEE subverts the democratic process is to mail ballot forms via third-class mail instead of first-class mail. The postal service does not forward third-class mail, therefore, those engineers like me who relocated to pursue new job opportunities are automatically disenfranchised. However, the IEEE is careful to send bills for

want your money but don't bother to vote."

membership dues via first-class mail. So, the message from the IEEE seems to be "We

Such petty harassment, however, is not a new experience for IEEE members. What does seem new is the organization's recent heavy-handed suppression of possible dissent within its ranks. In moves reminiscent of Richard Nixon's famed "Saturday Night Massacre," the IEEE fired Malcolm Drummond, head of its Pension Task Force, and precipitated the resignation of David Lewis, head of its Manpower Task Force. Both men seemed guilty of nothing more than doing their jobs: Drummond dared to write a letter to the president of RCA asking why retirement benefits of two RCA engineers had apparently been arbitrarily reduced. Lewis had testified at hearings of a Congressional subcommittee on immigration and had dared to recommend a return-home requirement for foreign engineering students after their graduation from U.S. colleges.

Drummond acted at the direct request of two IEEE members. If he had failed to act, he would have neglected an obligation of his position. As it turned out, however, he need not have bothered because his superior within the IEEE—Edward J. Doyle, vice president for Professional Activities—subsequently apologized to RCA and fired Drummond. Lewis also fell victim to the treachery of Doyle. In the July 1983 issue of The Institute, an IEEE publication, Doyle coauthored an article with Lewis in which they supported legislation requiring alien engineering students to return home upon graduation. After the article was published, and long after Lewis had gone out on a limb before the House Subcommittee on Immigration, Doyle reversed himself and voted with the rest of the U.S. Activities Board of the IEEE to permit many exceptions to the original policy.

The list of ways in which the IEEE has resisted participatory democracy seems endless. There have been a succession of proposed constitutional amendments to do such things as increase the number of signatures required on a nominating petition, move up the dates by which petitions must be filed, and delay by a year the date on which a new presidentelect assumes office. Also, overseas members have long held proportionately greater representation than U.S. members, thus violating the basic principle of "one person, one vote."

All things considered, I have the feeling that the corporate and academic hierarchy controlling the IEEE no longer gives a damn about the individual members or the unpaid volunteers who help run the organization. Though I disagree with Irwin Feerst on some issues, I think he really cares about American working engineers—who constitute the bulk of the membership of the IEEE—and he has steadfastly represented their interests for many years. Finally, I would add that it seems fitting for such an Orwellian organization as the IEEE to be celebrating its centennial in 1984.

and leght

Michael Elphick Editor in Chief

# Introducing the with more

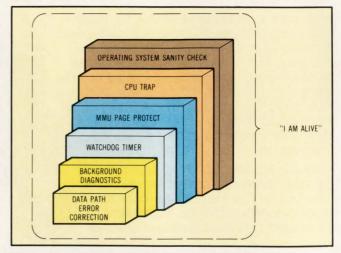

Real-time. A world where response times are measured in microseconds and performance is the only criteria.

In the hectic world of real-time, time waits for no man, woman or computer.

That's why you need a computer operating system

that takes care of business now, not later. Computer-Automation's

CARTOS is the answer. The most powerful real-time operating system ever created to meet the challenge of all your industrial and commercial real-time applications.

From oil wells to nuclear power plants, robotized assembly lines to transportation systems, CARTOS runs them all—smoothly, efficiently, quickly. And more cost-effectively than any other system available.

Here's why:

Fast task switching time.

CARTOS cuts response time dramatically with the fastest context switching time around –150 μsec.

The result? Critical events are serviced within the available time. It all adds up to peace of mind.

# Virtual machines.

CARTOS makes your computer into 64 virtual machines. That means you have the whole computer

to yourself even while sharing it with 63 other virtual environments.

So you get more capacity with less interference.

Simultaneous development and debug.

Other systems require two separate computers to develop and debug ongoing programs. CARTOS gets both jobs done all by itself. Up to ten programmers can work on-line even while CARTOS executes a large number of real-time tasks. So your program-

# real-time system real value.

mers don't waste time waiting in line.

Super sysgen speed.

CARTOS knocks off in minutes what it takes other systems hours to accomplish. Our benchmark tests prove it. Faster sysgen means your productivity goes up while your costs go down.

Compatibility.

CARTOS' impressive development capabilities are compatible with Computer Automation's entire line of minicomputers.

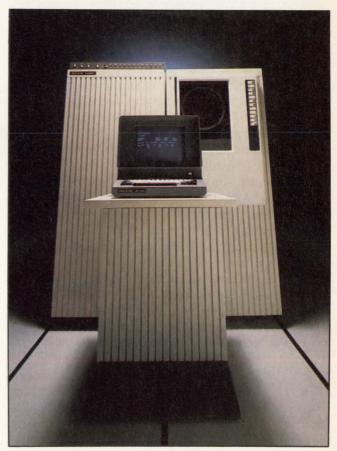

dataCASE/5.

Best of all, CARTOS runs on a family of low-cost, flexible minicomputer systems called dataCASE/5. dataCASE/5 supports a large variety of CPUs and storage media. Floppies. Winchesters. Streaming tape. Use any media you want in any combination you choose up to ½ gigabyte of capacity. With a 45 MB tape backup.

And you can put it wherever you want it.

Lightweight and compact,

dataCASE/5 sits on

your desk, on the floor

or in a rack. And when you want to expand, it's easy and fast.

When you don't have time to lose, consider the real-time system with more real value. CARTOS. dataCASE/5. From ComputerAutomation. We've been providing real-time solutions to the OEM world for 15 years. With 50,000 installations to prove it.

Why not tell us about your real-time needs by filling out and mailing the coupon today. Or give us a call.

Because time is running out.

# **ComputerAutomation**

NAKED MINI, Division

18651 Von Karman, Irvine, CA 92713. PH: (714) 833-8830, Ext. 353. TWX: 910 595 1767 It's about time.

- ☐ I want to discuss my application. Please have a sales representative call me.

- ☐ I'm interested in more information. Please send the latest brochure describing CARTOS, dataCASE/5 and other real-time offerings.

| COMPANY | TITLE |     |  |

|---------|-------|-----|--|

| ADDRESS |       |     |  |

| CITY    | STATE | ZIP |  |

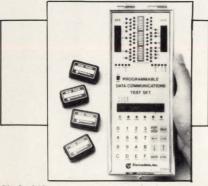

# TAKE THE GUESSWORK **OUT OF TAPE DRIVE** CALIBRATION\_ FOR LESS THAN \$1000

# Accurate digital calibrations—instantly.

Pericomp's PCM-4 Tape Drive Calibration Meter\* eliminates the need to interpret fluctuating oscilloscope readings to align and adjust tape drives. It provides instant calibrations of static skew, tracking, velocity and amplitude. And they're microprocessor-based, digital calibrations. So instead of trying to read a moving line, you immediately know exactly how far the calibration is from industry standard tolerances...exactly what kind of adjustment is required...and exactly when you have achieved the desired position.

That's speed and accuracy you could never achieve with an oscilloscope.

# Specifically designed to save you time and money.

The PCM-4 is the industry's first microprocessor-based device for tape drive calibration. It's designed and manufactured by Pericomp Corporation, an authority in magnetic media. And it's priced at under \$1000.

So take the guesswork out of your tape drive calibrations. Contact Pericomp, 14 Huron Drive, Natick, Massachusetts 01760, Telephone (617) 655-7660. And start saving time and money, today.

\*Patent Pending #450,539

The Authority in Magnetic Media

Pericomp Corporation, 14 Huron Drive, Natick, Massachusetts 01760 USA Tel. (617) 655-7660/237-4052

# **COMPUTER DESIGN**

Editor in Chief, Michael Elphick Managing Editor, Sydney F. Shapiro Senior Editors, John Bond Peg Killmon

Senior Associate Editor, Deb Highberger

Associate Editor, Malinda E. Banash

Chief Copy Editor, Leslie Ann Wheeler

Copy Editors, Helen McElwee Lauren A. Stickler Jack Vaughan

New York Field Office

Senior Editor, Nicolas Mokhoff 230 Park Ave, Suite 907, New York, NY 10169, Tel: 212/986-4310

Western Field Offices

Managing Editor, Tom Williams

Field Editor, Sam Bassett 540 Weddell Dr, Suite 8, Sunnyvale, CA 94086, Tel: 408/745-0715

Field Editor, Joseph A. Aseo 331 Freeway Center Bldg, 3605 Long Beach Blvd, Long Beach, CA 90807, Tel: 213/426-1172

Publisher, Gene Pritchard

Marketing Director, Robert A. Billhimer

Circulation Director, Robert P. Dromgoole

Production Manager, Paul Gagnon Production Assistant, Philip Korn Design Coordinator, Lou Ann Morin Technical Art, Designline

# **PennWell**

Advanced Technology Group 119 Russell Street, Littleton, MA 01460 Tel: 617/486-9501

H. Mason Fackert, Group Vice President

Saul B. Dinman, Editorial Director

David C. Ciommo, Controller

Steve Fedor, Promotion Director

Linda G. Clark,

Marketing Services/PR Manager

Linda M. Wright, Production Director

Wanda Holt, Data Services Manager

Pat Armstrong,

Administrative Services Manager

# Multifunction 16-bit personal debugger

Three instruments in one timing analyzer, state analyzer, and real-time emulator

New YEW Model 3502 Personal Debugger is actually three instruments in one—a timing analyzer, a state analyzer, and an emulator. Extensive and flexible built-in capabilities ease and speed-up testing, analysis, and total debugging of system based on the 68000 or 8086 processor families.

## **Major Capabilities**

## State analysis

Symbolic debugging Disassembly displayMulti-tracingMulti-triggering

### Timing analysis

•EXT 8 channels •Sampling clock...max. 100ns •Glitch detection...min. 15ns

### Real-time emulation

- Internal 28K bytes RAM Assembly function of single-line program

- Active tracing

### Standard Accessories

Minifloppy disk drive

RS-232C interface

Video/hard copy ports

## Microprocessor Compatibility:

Motorola 68000, Intel 8086, or equivalent

2 Dart Road, Shenandoah, Georgia 30265 Phone: 404-253-7000 TWX: 810-766-4760

See us at WESCON booths 637-639

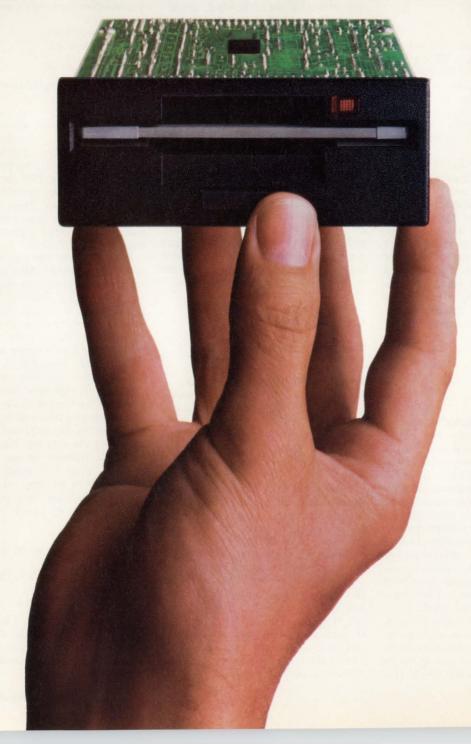

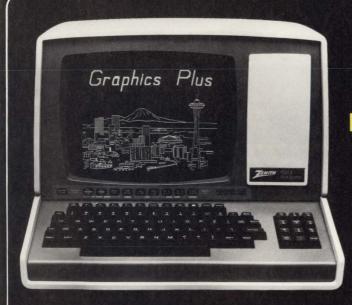

# WE'RE GOING PUBLIC WITH OUR HALF-HEIGHT FLOPPY!

See us at Booth 508, Main Hall

COMDEM/Fall '83

November 28—December 2, 1983 Las Vegas Convention Center, Las Vegas, Nevada

Don't gamble on futures!

The patent on our unique ball bearing head carriage is the *only* thing still pending with our ECHO 500 series 5½" flexible disk drive. This new system approach from Hi-Tech Peripherals achieves precise positioning accuracy and quiet stepping.

Exercise your options and take delivery now on any of six high performance

96 and 48 tpi drives with up to 1.6 megabyte capacity.

Priced from \$95.00 in OEM quantities.

For more information contact:

Hi-Tech Peripherals Corp. 15192 Triton Lane Huntington Beach, CA 92649 714 891-0027 TLX 4722123

CIRCLE 11

# ACADEMIA AND THE SHARK-PART II

This magazine, in its Sept 1983 editorial "Academia and the Shark," criticized the universities in general, and me in particular, for exaggerating the threat to the U.S. of the Japanese Fifth-Generation Computer Project. Even though the cart came before the horse, I welcome this opportunity to familiarize the editor and readers of *Computer Design* with my views on this important topic.

Many of us believe that the information revolution will affect our world more profoundly than the industrial revolution. Looking back, we find at the world's economic and geopolitical helm the countries that led that older revolution. Looking ahead, we can expect the same fate for the nations that will control the information revolution. Japan recognizes this historical

inevitability. Drawing on its superior electronic base and its technologically oriented population, and motivated by its lack of natural resources, Japan has declared its intent to achieve world supremacy in information technology within a decade. Its lead vehicle is the Fifth-Generation Computer Project, a \$1 billion government-industry effort to harness 1000-processor machines and artificial intelligence techniques into systems that understand human speech and images, translate spoken languages, and provide expert services.

This effort deserves our most serious attention for the following reasons. First, it deviates from the Japanese tradition of incrementally improving the cost-performance of existing goods, and strives instead to leapfrog the products and strategies of U.S. computer companies. Second, unlike our own corporate orientation, it focuses on potentially the most "cerebral" part of the information revolution. Finally, it will develop, within the leading Japanese companies, numerous experts in artificial intelligence, multiprocessor architectures and their applications. As a result, Japan may produce novel variations in ordinary products, like speech-driven TV sets, even if their loftier project goals are never met. An unprepared U.S., awakening to such surprises 5 or 10 years from now, will not be able to recover gracefully because it will need several years to build comparable knowledge within its own companies.

To compete with Japan in this new arena, we must strengthen our long-term orientation. One proven method is to increase government funding of basic research. The current Department of Defense initiative, which has yet to be approved by Congress, is a good start toward that end. Meanwhile, we can hear the familiar criticism that such programs need more specificity—a carry-over of our short-term bias that kills the flexibility needed for successful long-term research. The Microelectronic and Computer Technology Research Corporation is another good start, but it must prove its resilience against the short-term pressures of its corporate owners. Beyond these steps, more could, and should, be done to link longer-term thinking with the profit motive. For example, substantive tax credits could be given to companies pursuing longer-term research, and long-term financial instruments could be used to spread the associated costs and gains among willing investors. Our companies could also learn from the Japanese to carefully watch rather than ignore academia's long-term dreams and results. There are also things that we must not do. We must not, for example, restrict access to basic research, since the benefits of reduced information leakage would be overshadowed by our inability to share ideas and to utilize the brainpower of foreign scholars.

One reaction to such proposals is that competition between the U.S. and Japan is a provincial and less desirable alternative to international cooperation. Yet, we are starved for examples of technological progress without competition, so that in the long run the global welfare may be better served by competitive national tribalism.

The editorial suggests another reaction: that academics use the Japanese threat in order to increase their research budgets. Motivation notwithstanding, the fact is that industry will be the principal beneficiary of the programs under way by at least a 70 to 30 ratio. Finally, the editorial's principal contention—that the actual damage caused by sharks is considerably smaller than the accompanying Hollywood hoopla—offers little comfort to a swimmer devoured. Complacency is no substitute for vision.

Michael L. Dertouzos Professor and Director

evtor301

MIT Laboratory for Computer Science

# NO IFS. NO

© 1983 Advanced Micro Devices, Inc.

# ANDS. NO BUTS.

Some chip makers spend more time making exceptions than they do making parts. Their guarantees run on and on and on.

Ours is short and sweet, and it comes with every device AMD makes.

Next time you have to fill a tall order, look for the short guarantee.

The International Standard of Quality guarantees a 0.1% AQL on all electrical parameters over the entire operating range.

INT.STD-100

# Advanced Micro Devices 27

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 (408) 749-5000, outside California, call toll free (800) 538-8450, ext. 5000.

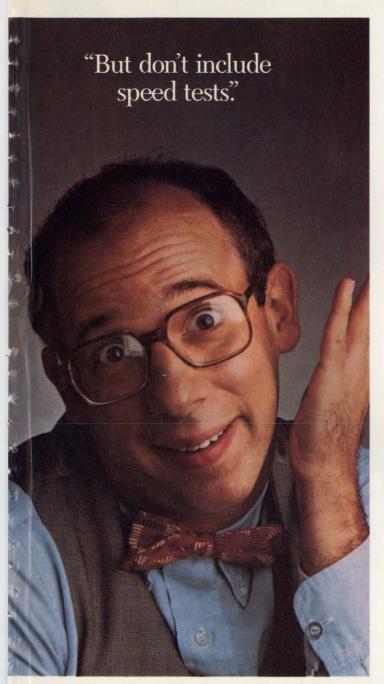

Those risky new 51/4" drives.

How much are you willing to bet on the new technologies that promise more and more megabytes in a 5¼" drive?

Your quality? Your reliability? Your reputation?

You could end up betting them all, and losing, because many of the new technologies are still unproven and could result in serious damage to your customer's data base.

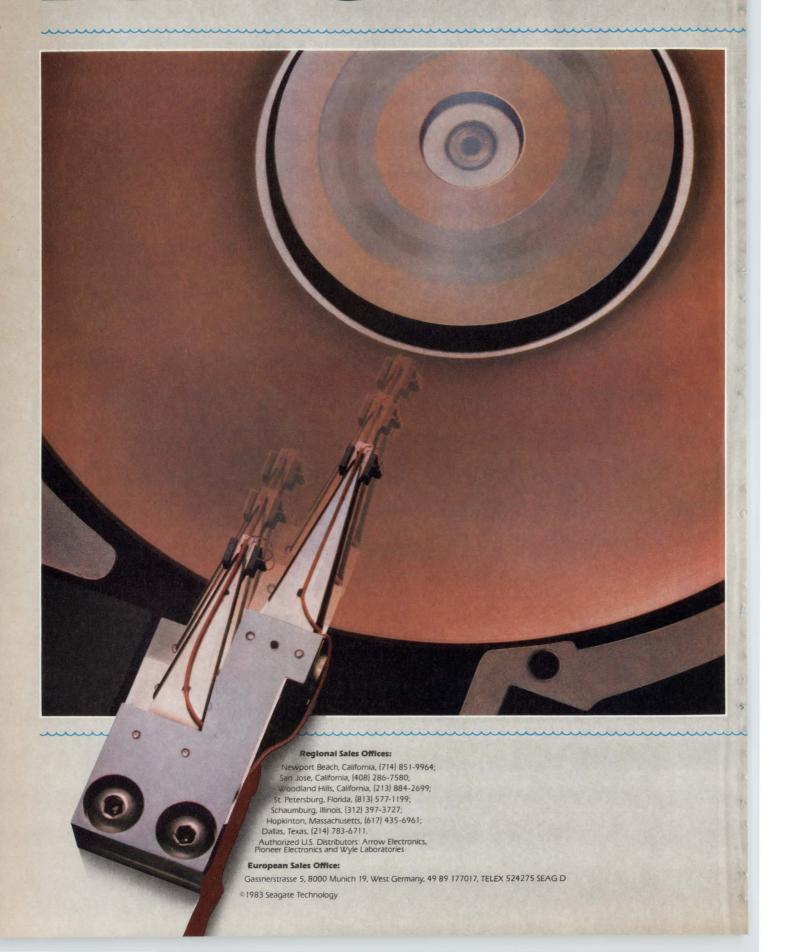

As the pioneer of high capacity 5¼" drives, we know that with leadership goes responsibility. So we spend the time it takes to develop and test exhaustively. Then only after we're convinced that the technology is reliable will we offer it to our customers.

The result of this philosophy is a remarkable plug-and-play reliability record for our complete line of 12, 19, 26 and 40-megabyte drives. And it's reliability like this that has made us the leader in volume shipments of large-capacity 5¼" Winchester disk drives.

Of course, the time is coming when the industry will demand a 60 or 80 or even a 160-

megabyte 5¼" disk drive, and you can expect Computer Memories to deliver it. Without delivering a risk.

The capacity leader.

9216 Eton Avenue, Chatsworth, CA 91311 (213) 709-6445/ Ft. Worth, TX, (817) 332-7859/Costa Mesa, CA, (714) 241-9260/Springfield, MA, (413) 783-2386/In Europe: Bray-on-Thames, Berks, UK, 06283-4281 Telex 847591. For small quantities, call Schweber Electronics, (800) 645-3040.

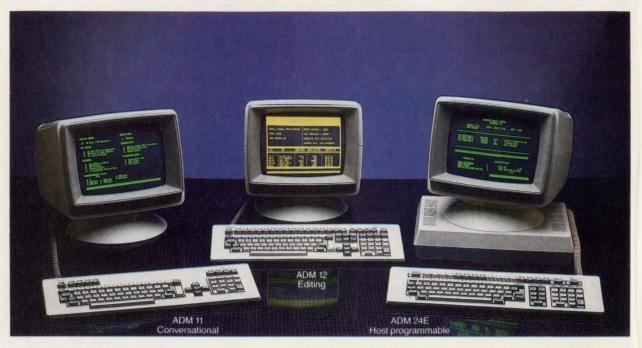

# PRESENTING LEAR SIEGLER'S AMERICAN DREAM MACHINES: THREE NEW HIGH TOUCH TERMINALS.

Have you noticed that the more high technology we put into the workplace, the more human touches the workers put in? There's a real need to soften the interface between people and high technology.

That's why we designed our new High Touch™ terminals to work together with biology, not just with technology.

Our new generation of High Touch terminals brings an elegant new touch to our American

6' coiled cable lets you put the keyboard anywhere.

Dream Machine (ADM™) tradition. The family features three new ergonomic terminals designed to meet the needs of OEMs and end users alike: The ADM 11, ADM 12 and ADM 24E.

There is more to ergonomics than simply tacking on a few faddish features as an afterthought. That's why we put our thinking in up front. And came up with a whole new way for terminals to relate to humans.

No aspect of terminal design escaped our deepest consideration. Or reconsideration. Dozens of little touches add up to the convenience and comfort of High Touch. For example, we put the power "on/off" switch and contrast control knob in front where they're easy to reach.

The monitor not only tilts and swivels, it stops positively in almost any position.

The clean, crisp display features a large character matrix on an easy-to-read green or amber non-glare screen—made even easier to read by the hooded bezel. Screens are available in 12" or 14" sizes.

Our uncluttered keyboard, with its logical separations between key groupings, improves your efficiency. The low-profile, DIN-standard keyboard is not only tapered, its angle of tilt is easily adjusted for maximum operator comfort.

Low profile DIN-standard keyboard with adjustable tilt.

The Selectric® layout with its sculptured keys makes data entry easy and efficient. And we placed the *control* and *escape* keys close to the alphanumeric keys, where people just naturally expect to find them.

The ADM 11 is a High Touch conversational terminal that accepts data continuously at 19.2 kilobauds. It features separate cursor control keys logically arranged in a cross for ease of use. Four modes are provided for the printer interface: page print,

Distributor Sales & Service: Boston (617) 456-8228 • Chicago (312) 279-7710 • Houston (713) 780-9440 • Los Angeles (714) 774-1010, Ext. 219 • Philadelphia (215) 245-4080 • San Francisco (415) 828-694 • England (04867) 80666 • From the states of CT, DE, MA, MD, NJ, NY, RI, VA and WV (800) 523-5253. **OEM Sales:** Chicago (312) 279-5250 • Houston (713) 780-2585 • Los Angeles (714) 774-1010, Ext. 582 • New York (516) 549-6941 • San Francisco (415) 828-6941 • England (04867) 80666. Selectric® is a trademark of IBM. ADM,™ High Touch™ and Express Depot™ are trademarks of Lear Siegler, Inc.

|                                                                                                                       | ADM 11                                  | ADM 12                                                     | ADM 24E                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable Function Keys                                                                                            | 4 (Shiftable to 8)                      | 16 (Shiftable to 32)                                       | 16 (Shiftable to 32)                                                                                                                                                                                 |

| Non-Volatile Function Keys                                                                                            | Optional                                | Standard                                                   | Standard                                                                                                                                                                                             |

| Function Key Legends on<br>25th Line                                                                                  | From Host                               | From Host                                                  | Standard<br>Non-Volatile                                                                                                                                                                             |

| No. of Pages of Display Memory                                                                                        | 1                                       | 2                                                          | 2 or 4                                                                                                                                                                                               |

| Display Memory<br>Configurations<br>(Plus 25th message/status line)                                                   | 24 lines by<br>80 characters            | (2) 24x80 or<br>(1) 48x80 or<br>(1) 24x158                 | User-Definable up to 96x80                                                                                                                                                                           |

| Scrolling                                                                                                             | Standard<br>Scrolling                   | Smooth, Jump<br>or Horizontal<br>Scrolling<br>Split Screen | Smooth or Jump<br>Scroll<br>Split Screen                                                                                                                                                             |

| Transmission Mode                                                                                                     | Conversation<br>Mode                    | Conversation or Block Mode                                 | Conversation or Block Mode                                                                                                                                                                           |

| Editing                                                                                                               | Limited                                 | Full Editing &<br>Protected Fields                         | Full Editing &<br>Protected Fields                                                                                                                                                                   |

| Visual Attributes:<br>Reduced Intensity, Blink<br>Blank and Reverse Video.<br>Underline also on<br>ADM 12 and ADM 24E | 3 Embedded<br>1 Non-Embedded            |                                                            | 6 Embedded or<br>Non-Embedded,<br>plus Full Screen<br>Reverse Video<br>and Highlight                                                                                                                 |

| OEM Flexibility                                                                                                       | Modifiable<br>Set-Up<br>Characteristics | Modifiable<br>Set-Up<br>Characteristics<br>& Personality   | Modifiable Set-Up<br>Characteristics.<br>Add to Program<br>in ROM or<br>Down-Line Load<br>in RAM (56K<br>ROM or RAM.<br>Plus up to 22K<br>Display Avail-<br>able) Room for<br>add'l Logic<br>Boards. |

line print, transparent print, and display and print. There are four programmable function keys (shiftable to eight). And two levels of setup mode to reduce errors while still giving the operator maximum flexibility.

For a High Touch terminal with editing and more, choose the ADM 12. It features five nonembedded attributes. Embedded mode can also be selected for existing applications. And 16 programmable non-volatile function keys (shiftable to 32). The display memory can be configured as two 24 x 80 character pages, or one 48 x 80 page, or one 24 x 158 page. The terminal runs in either conversational or block mode.

Or choose our top-of-the-line ADM 24E which features a moveable 24-line window you can use to look at 48 (or 96) lines of memory. The ADM 24E also offers plenty of additional space for OEMs, with up to 56K ROM or RAM available for add-on programs. Plus up to 22k display RAM.

more computer-based systems than any other.

When you buy Lear Siegler, you're buying proven quality and reliability, backed by the broadest network of full service centers anywhere. That means you can get walk-in Express Depot™

Monitor tilts and swivels to almost any position. Available with 12 or 14 inch screen.

service, on-site service and extended warranty service in 3,000 cities nationwide.

Lear Siegler High Touch terminals are made in America designed, engineered, manufactured and shipped from Anaheim, California to provide you with the best local support.

And that's just one more reason they're called the American Dream Machines.

Programmable Keys color-coded Separate 2- or 3-key setup sequence to reduce function keys. by function. numeric keypad. Spacious. Separate cursor control operator error. uncluttered layout. keys arranged in a cross No keys next to Dividers Selectric® layout separate keys. Control and escape keys with L-shaped return key, sculptured keys. close to alphanumeric keys.

ADM 11 keyboard.

# LEAR SIEGLER, INC. DATA PRODUCTS DIVISION

901 East Ball Road, Anaheim, CA 92805 · 714-774-1010

See Us At COMDEX Booth #3072

# EVERYBODY MAKES TERMINALS. ONLY WE MAKE LEAR SIEGLERS.

When it comes to terminal technology, we're the historic leader with the largest installed

base. Our terminals are used in

Call Lear Siegler at 800/532-7373 for an authorized distributor near you: Advanced Technology • Continental Resources • The Datastore • Data Systems Marketing • David Jamaison Carlyle, Inc. • Gentry Associates • Hall-Mark Electronics • M/A-COM Alanthus, Inc. • Marva Data Services • M.T.I. • National Computer Communications • Pioneer (Standard, Harvey, Gaithersburg) • 2M Corp. • Wyle Electronics • Kierulff Electronics • Inland Associates • Digital Source, Inc.

Designer 3

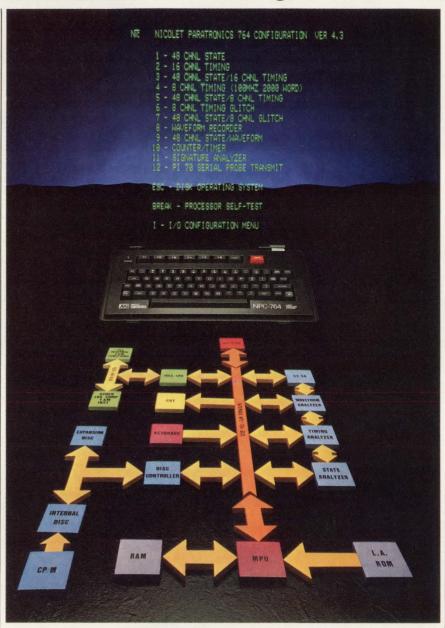

# The NPC-764: More Evolutionary than Revolutionary.

In the mid-1970's, instrument manufacturers viewed the advent of the microprocessor as an opportunity to replace hardware functions with software. Until recently, however, the external appearance and basic functionality of these instruments remained unaffected by the internal microprocessor. As far as the user was concerned, knobs still had to be rotated, switches set, and LED or similar displays interpreted.

The NPC-764 was the first instrument to give the user direct access to its internal microcomputer. This was made possible by replacing all knobs, switches, and readouts with an ASCII keyboard, a CRT, and an integral floppy disk. Since its introduction, the NPC-764's feature set and accessories have been greatly expanded. Today, because it is a proven, highly-reliable instrument, the NPC-764 is the standard by which similar analysis systems are measured.

It's understandable that other test equipment manufacturers have been reluctant to change from the old "knobs and switches" approach to instrumentation design that has prevailed ever since the first experiments with electricity. Perhaps they felt that there was a certain risk that their customers would not be ready to use an ASCII keyboard to control an instrument.

But NPC's designers realized that this traditional approach was preventing engineers from effectively performing today's complex analysis tasks. They also realized that engineers are comfortable with a computer controlling or supporting test functions.

For a complete set of Designer Notes, call **(800)-NICOLET**, *(415) 490-8300* (Calif.); In Canada: *(416) 625-8302*. TWX: *910-381-7030*, Nicolet Paratronics Corporation, 201 Fourier Avenue, Fremont, CA 94539.

Leading The Way In Analysis Technology

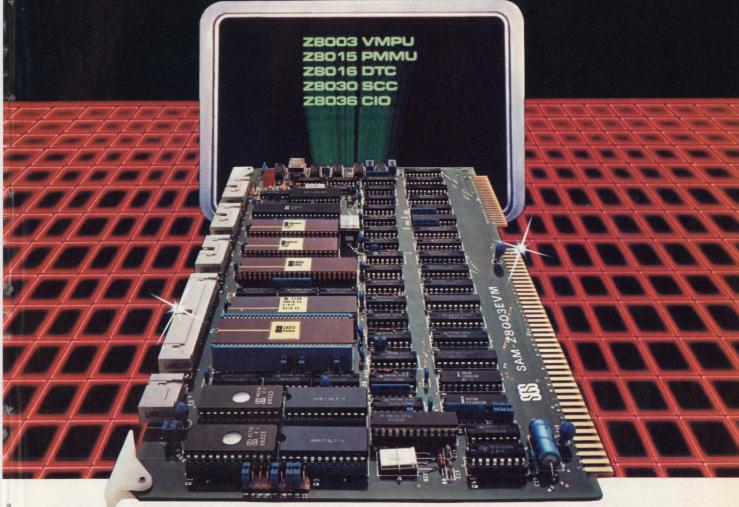

Other 16-bit options

In the article "Options Abound in 16-bit Operating Systems," (Aug 1983, p 113), there was no mention of the participation of Zilog Systems, along with the three firms, in a joint development effort with Western Electric, to produce versions of the Unix system V operating system compatible with leading 16-bit microprocessors.

The planned z8000 version of system V demonstrates Zilog Systems' continuing commitment to Unix, which began in 1979 when Zilog became the first microprocessor manufacturer to acquire a source-code license for a Unix system. Furthermore, the new operating system will also run on our system 8000 family of "supermicro" computers, which has used a licensed Unix system since its introduction in 1981, making it the leading commercially installed microcomputer running Unix or its derivatives.

Joan Marzullo Zilog 1315 Dell Ave Campbell, CA 95008

Pick system and its "Basic" language

In regard to the short review of the Pick operating system in Chris Brown's article on 16-bit operating software (Aug 1983), I have found the Pick system to be an excellent application development environment, and feel that there needs to be more media awareness of this system.

Mr Brown accurately pointed out two of the system's biggest problems, lack of visibility, and lack of communication support. I feel, however, that his discussion of the data management capabilities and language support has instilled some misconceptions in readers' minds.

Mr Brown missed the major thrust of what the Pick system is—ie, a system for data management and application development in which writing a program to do a task is viewed as the last resort. This ment where the objective is to write pro-

language is concerned, it appears in retrospect that the use of the word "Basic" to describe it was ill conceived. Although it is true that the general syntax is similar to Basic, that is where the similarity ends. The Pick programming language, which I will call "D," is a compiled language that supports the high level programming constructs expected of a language today. These include

Multi-line IF-THEN-ELSE LOOP stmt UNTIL/WHILE exp DO stmt REPEAT BEGIN CASE CASE exp [CASE exp] . . . **END CASE**

The "D" language also provides separate compilation of external subroutines, extensive character string manipulation and formatting facilities, and special constructs to operate on the variable length dynamic string arrays used in the relational file structure of the system.

Toby L. Kraft Kraft Enterprises, Inc 7822 Convoy Ct San Diego, CA 92111

Technological boycott of Soviets

In response to the Soviets' shooting down an unarmed commercial Korean airline (KAL Flight 007) on Sept 1, 1983, the Independent Computer Consultants Association is taking action to restrict future delivery of high technology to the

These capabilities have recently been used to stalk and murder 269 innocent citizens of the free world. The Soviets are continuing to insist that they have the right to utilize any power they possess in any manner they see fit, without regard to international law.

In light of this situation, we are asking all high technology professionals in the free world to join with us in a total boycott of the Soviet Union. We plan to halt all shipments of computers, computer parts and components, software, technical support, manuals and publications to the USSR and its satellites.

We request that all high technology professionals in the free world look into their own hearts and, considering their own personal values, decide whether they should be party to the delivery of any more technological capabilities to the Soviets.

This boycott will last two years, or until the Soviets demonstrate a change in policy which indicates a developing sense of responsibility.

Tom Scott Independent Computer Consultants Association 909 Mulberry Lane Bellaire, TX 77401

**Engineers and exploitation**

Finally, some editor has dared to point out that the emperor was indeed wearing no clothes. Whereas almost the entire world applauded the magical "125% solution" and salary freezes instituted by some companies, your perceptive editorial in the Aug 1983 issue correctly pointed out the very short-sighted nature of these quick fixes. There is little question that, if the opportunity presents itself, the exploited engineers will seek employment elsewhere.

Why then, did these companies elect to use these tactics? After all, it is these same employers who are moaning about an "engineering shortage." Surely, if this shortage were real, the employers would understand the great risk they run by reducing salaries while, at the same time, insisting on a longer workweek.

To me, the answer is clear. There is not now, nor has there ever been, a shortage of engineers. The companies who adopted these tactics are well aware of this (despite their public pronouncements to the contrary) and understand that there are very few places for their exploited engineers to go. One hopes, however, there is a great shortage of engineers who will long tolerate a company that reduces their wages and/or lengthens their workweek.

Irwin Feerst Committee of Concerned EEs PO Box 19 Massapequa Park, NY 11762

### **NTIS** correction

In the Sept 1983 article, "Ada Compilers -Validated and Available at Last, p 73, the NTIS order number for Ada/Ed was incorrect. The correct order number is AD-A128 707/7.

# DOYOUHAVE THE DRIVE TO SUCCEED?

You do?

Good. So do we.

Shugart's 3.5" microfloppy drive. The

SA300 by name.

And, considering where the personal/ home/portable computer market is headed (betterfastercheapersmallerwithmorestorage), it's not a moment too soon.

It's also quite an achievement. One that

allows you to engineer a wealth of advantages into smaller, more competitive systems.

Take the most obvious advantage, for instance.

Size. With the SA300 you can make your personal and home systems less imposing, more, well, personal. Our microfloppy takes up 75% less room than a standard sized Minifloppy.™

And it weighs just a tad over a pound. So your portable system can be more, you guessed it, portable, even

with two drives in it.

Yet the SA300 still delivers 500 Kbytes in the single-sided version (1 Mbyte in the double-sided version) and uses less power, worst case, than an 8-watt night-light.

It's also so quiet, you can't hear it running unless you put your ear right

down on top of it.

And with an MTBF of over 10,000 power-on hours, it should run for quite some time.

Then, of course, there's the not-sosmall matter of the industry standard 3.5" microfloppy diskette.

Which offers a few important advan-

tages of its own.

Like Minifloppy compatibility.

A track density that allows room for a generous upgrade path to more capacity.

And a hard shell plastic media cartridge for protection against the rigors of pocket and purse, with an automatic head access shutter as a last line of defense against little computer users who eat a lot of peanut butter and jelly.

Want to learn more? We'll do a private Micro-

floppy Workshop right in your office. And you'll have the chance to talk with media manufacturers and our own applications engineers about your plans for a big design win.

Call your local Shugart Sales Office to

set it up. But do it soon.

You'd be amazed at what you can do with a little drive.

**Shugart**Right from the start.

See us at Comdex Booth #3319

The 3.5" Micro-Cartridge provides maximum media protection.

# Six things you can do with your obsolete floppies.

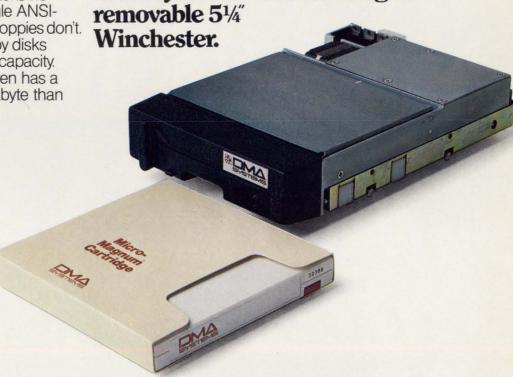

Floppies were fine in their day. But they just don't make sense with the professional desktop computers of today.

What's the answer? The DMA 360 removable 51/4" Winchester. It's exactly the same size as a 51/4" half-height floppy drive - but that's where the similarity stops.

disk reliability. Floppies don't.

The DMA 360 protects your data in a totally sealed cartridge. Floppies don't.

The DMA 360 packs 7.5 megabytes on a single ANSIstandard cartridge. Floppies don't. It takes up to 25 floppy disks to achieve an equal capacity.

The DMA 360 even has a lower cost-per-megabyte than a floppy. But it gives you so much more.

Like an average access time of 98 milliseconds. A transfer rate of 625 kilobytes per second. And an error rate that's on par with the most reliable conventional Winchester disk drives.

There's no way you'd The DMA 360 gives you hard-get that kind of performance from a floppy!

In fact, anything you can do with a floppy, you can do even better with a DMA 360. That's why we call it the floppy replacement.

For more information on what you can do with your obsolete floppies, write DMA Systems, 601 Pine Avenue, Goleta, CA 93117. Or call us at (805) 683-3811, Telex 658341.

**Introducing the floppy replacement:** DMA Systems'new half-height

See us at COMDEX Booth #166

The Removable Winchester Company.

CIRCLE 17

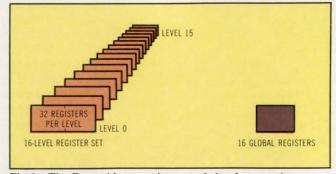

# NS32032

The First True

32-Bit Microprocessor

to Become Reality.

The first commercially available microprocessor to feature:

- 1. Full 32-bit architecture

- 2. Full 32-bit internal implementation

- 3. Full 32-bit data bus to memory

# Artificial intelligence systems make their mark

Computers of a higher order than the current generation of number manipulators are about to be unleashed on the engineering community. The machines are an outgrowth of the scientific community which has been. for the last 25 years, trying to learn how man thinks and how to duplicate the thinking process in a machine. A special breed of scientists has even proclaimed the term artificial intelligence as the goal of their pursuits. Comprising this group are not only bright computer scientists, but also specialists in such disciplines as linguistics, mathematics, psychology, and philosophy. While scientists in these respective disciplines have separately strived to understand and replicate man's thinking process for the past quarter century, recent maturation of commonly held concepts about human intelligence and the relatively cheap computing power available with today's technology have finally borne fruit to actual artificially intelligent systems.

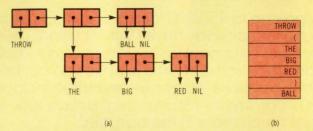

Typically referred to as "expert" systems, these machines purport to possess knowledge about a subject such as the building blocks for designing VLSI circuits, and to display this knowledge in a symbolic form. The expert system then arrives at a solution by making judgment calls that are based both on an operator's input and on the machine's embedded knowledge base. Unlike today's computers that use long and cumbersome sequential line instructions to manipulate data, expert systems use symbolic procedures to yield a fast and intelligent solution based on IF...THEN rules. In terms of current programming environments, this means that instead of writing lines of code that describe all possible characteristics about an abstract object and subsequently writing more code to describe the various possible results, the programmer can make up lists of the properties associated with the object. The bank of lists is referred to as the knowledge base. Processing the knowledge base is accomplished via a control engine.

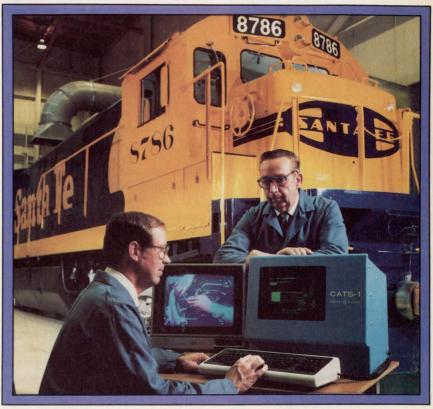

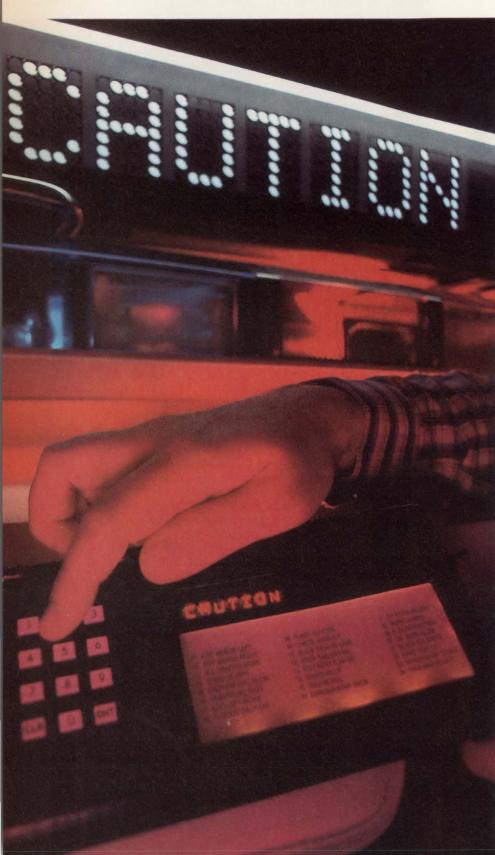

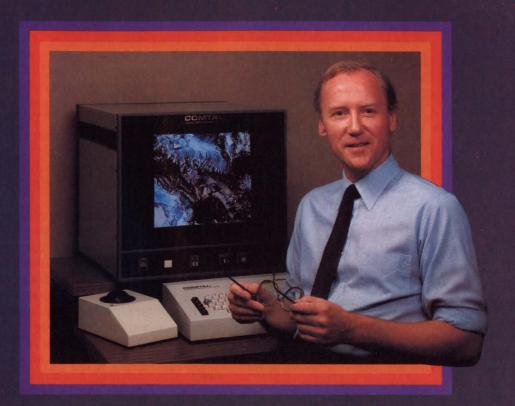

An expert system specific to train locomotive repair is embedded in CATS-1. Users type-in responses to questions concerning the malfunction displayed on the CRT. At any time, users can call up detailed drawings of the locomotive's various components. The system identifies the cause of the malfunction and also demonstrates repair procedures from a videodisk on a separate monitor.

The knowledge base and the control engine make up the expert system a close approximation of human intelligence. But a machine's intelligence is derived from inference only; the engine infers certain results based on known assumptions using a tree parsing routine based on the IF... THEN rules to reach conclusions.

The artificial intelligence (AI) language that comes closest to describing the lists and procedures has predominantly been the List Processing Language (Lisp). Developed in the late 1950s, it has only recently borne fruit in practical commercial applications. Modern Lisp is a highly interactive language that incorporates powerful editing and debugging tools. It allows a programmer to address many types of large and complex problems more efficiently, and even some problems that are impractical to solve using conventional computer languages.

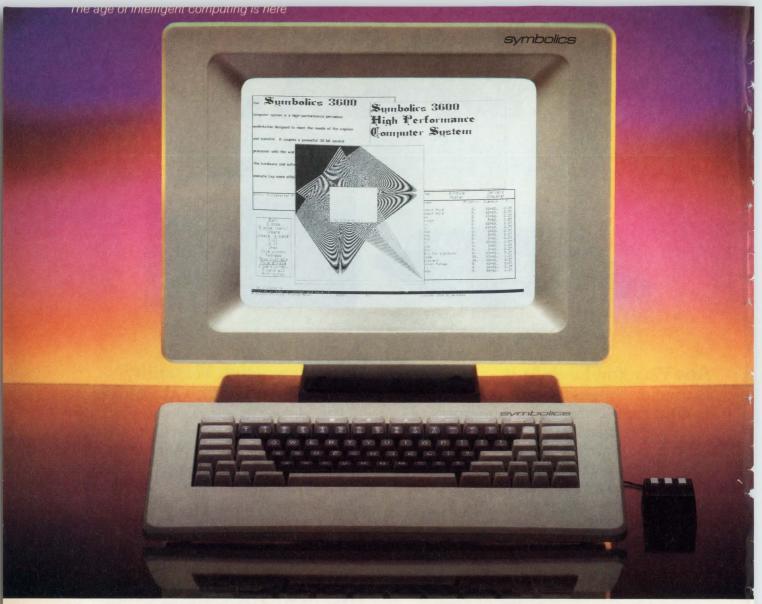

Recently, a number of companies formed by scientists who were originally doing work in theoretical AI have announced products that have Lisp as the core of their knowledgebased systems. Among these are Symbolics, Inc (Cambridge, Mass), LISP Machine Inc (Culver City, Calif), Xerox, Special Information Systems (Pasadena, Calif), General Electric Co (Schenectady, NY), Inference Corp (Culver City, Calif), Teknowledge (Palo Alto, Calif), and Intelligentics (Palo Alto, Calif). In addition to these companies, many large firms have internal programs in AI research that have resulted in expert systems for internal use. Digital Equipment Corp (Maynard, Mass) for example, has developed a

(continued on page 34)

32 Dedicated Channels

# THE **BRIGHT MULTIPLEX**

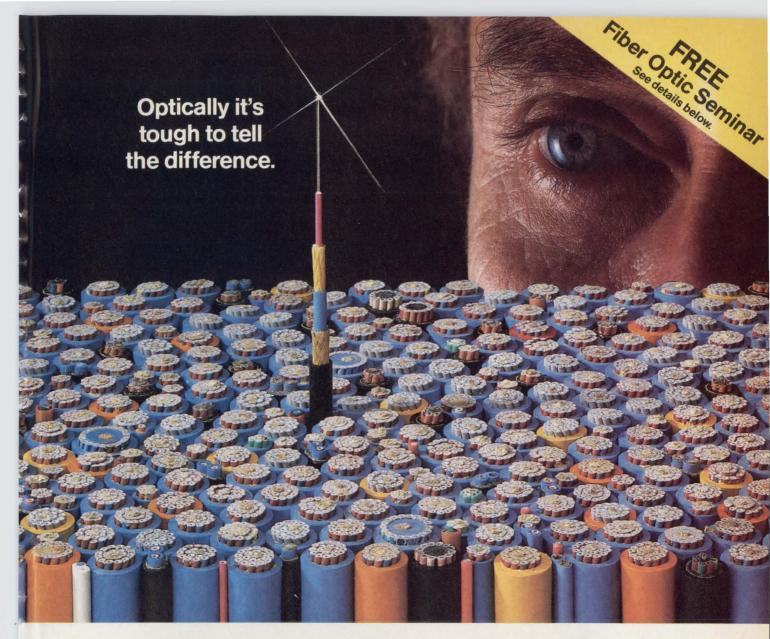

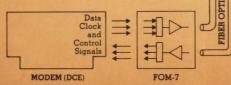

Multiplexing is more efficient with Optelecom's Model 5100 Fiber Optic Multiplexer.

The 5100 eliminates timeconsuming port contention by allowing full time division multiplexing of up to 32 data channels. You also reap all the benefits of fiber optic technology including:

- · Savings on cable installation time and space

- Immunity to electrical interference

- · Security (fiber optic cables do not radiate)

- Expansion capability

- · Lower bit error rates (no crosstalk)

- Only \$210 per port

### What Are You Waiting For?

While you're waiting for data to trickle through a conventional multiplexer, make the bright choice—call Optelecom today!

15940 Luanne Drive Gaithersburg, MD 20877 (301) 948-4232

CIRCLE 20

# SYSTEM TECHNOLOGY/ SOFTWARE

### Artificial intelligence

(continued from page 33)

number of expert systems that help configure and customize orders for a particular DEC computer system. The company expects to offer some kind of expert system on the market in the future. Schlumberger/Fairchild Mountain View, Calif has also built an expert system for internal use to analyze oil well logs-and mineral exploration. Both the DEC and Schlumberger systems are Lisp based (see special edition on Office Systems Design, Fall 1983, p 37).

### Direct programming in Lisp

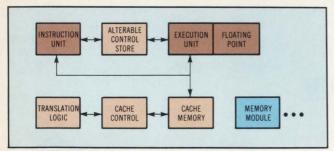

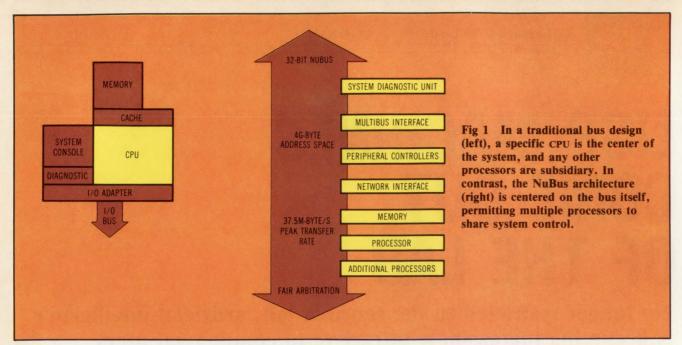

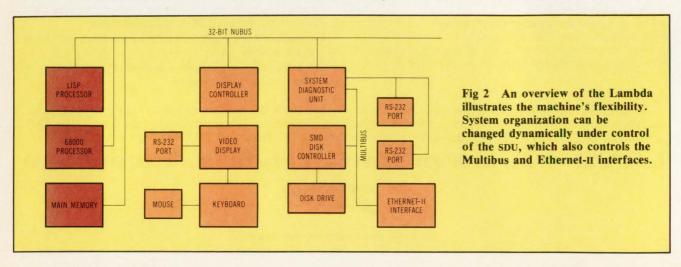

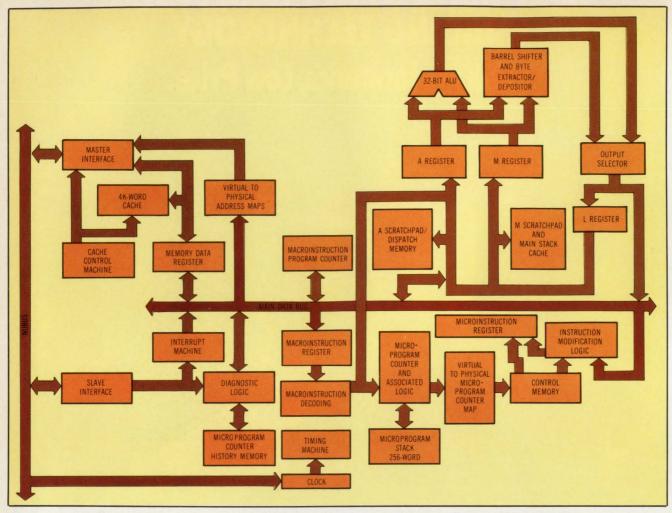

As might be expected, describing lists and procedures can be a timeconsuming chore for the programmer if done in the machine's assembly language. LISP Machine's Lambda computer has made that chore easier by having the programmer utilize the machine's microcompiler and virtual memory to microprogram directly in Lisp. The Lambda is built around a 32-bit Nubus architecture with a 37.5M-byte/s transfer rate that was developed at Massachusetts Institute of Technology's computer science laboratory. This architecture allows use of a variety of processors, memory, I/O devices, and other devices since the system diagnostic unit senses what kind of devices are installed and then conforms system operation accordingly. The machine's 4-board Lisp processor has a 24-bit virtual address space and a 4K cache.

Basic system software includes 10,000 compiled functions and over 30,000 symbols representing an initial core image of about 4 million words. Approximately 200 microcoded functions reside in 10K of user-writable control memory for output to a high resolution display (800 x 1024 pixels) that is refreshed at 60 times/s. A window capability is also built in to maintain an editing and execution environment side by side. The operator can choose from any of the standard features available within the window system or add new ones. The editing function is performed using the Zmacs editor. Zmacs accepts over 400 commands in addition to allowing users to construct their own. As an example of how easy it is to use this editor, if users choose the

APROPOS command, they have at their disposal all commands for those containing relevant key words. Thus, APROPOS FONT will generate all appropriate commands containing the work font for the user.

The Lambda also features a 16 x 16 matrix multiplier, a 256K x 32-bit error-correcting physical memory, a 470M-byte Winchester disk drive with a storage module drive controller capable of handling four drives, display, keyboard, and a 3-button mouse, all for \$72,000.

LISP Machine Inc was founded, among other entrepreneurs, by the principals of Inference Corp to allow Inference to obtain Lisp machines for its AI development projects. One of Inference's products is a symbolic manipulation program (SMP), a productivity enhancing tool used to manipulate algebraic and other symbolic mathematical expressions. SMP can perform mathematics symbolically at different levels, from high school algebra to advanced theoretical physics. The manipulation of mathematical formulations is done automatically and interactively. SMP can differentiate and integrate most mathematical expressions, solve linear and nonlinear equations, and perform matrix and tensor algebra. Mathematical expressions can be evaluated numerically, or they can be expressed graphically in two or three dimensions.

This particular program has not been written in Lisp, but rather in the C programming language. It is thereby ready for sale to the C-based end user and can be used on a variety of different computers. Currently, SMP runs on the VAX computer both under the Unix and VMS operating systems. Inference offers the program at a cost of \$36,000 for permanent license on VAX-11/780 installations.

Inference sells inference engines not complete expert systems. Its latest product is an inference engine called the advanced reasoning tool (ART). Coupled to any of a number of knowledge bases, ART becomes the engine that infers conclusions in the expert system. The system is basically

(continued on page 36)

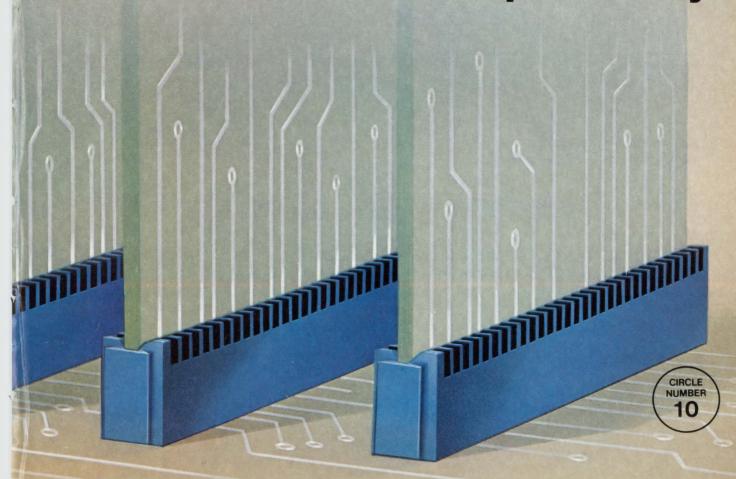

# NS16000

# The World's Most Elegant Microprocessor Family will turn "Cartwheels" on your

More and more programmers and systems designers are coming to the conclusion that the NS16000™ microprocessor family will be the foundation for the next generation of high-performance, low-cost computers. Why? Because it features a totally new, totally practical, highly symmetrical architecture; high-level language and modular-software support; a powerful instruction set; and the implementation of Demand Paged Virtual Memory.

If you're among those considering applications for the NS16000 microprocessor family, here's something else you should know: your VAX™-11 can be turned into a complete and ideal development system for less than \$18,000 - a minimal front-end

investment, considering the possibilities.

Naturally, you'll need a cross-software development package. We offer two.

The NSX-16™ cross-software development package allows > rapid, easy compiling or assembly of NS16000 programs on your VAX-11, using the VMS™ Operating System (version 3.0 or later). This package includes a Pascal compiler, and, among other utilities, an assembler, linker, librarian, and powerful symbolic debugger. (\$6,000.00)

The NSXC-16™ cross-software development package allows equally rapid, easy compiling or assembly of NS16000 programs

on your VAX-11, but using the Berkeley 4.1 bsd UNIX™ Oper-\* ating System. It includes a C compiler, and, among its utilities, an assembler, linker, librarian, and powerful symbolic debugger. (\$6,000.00) A Pascal compiler is available as an option. (An additional \$4,000.00)

Once your programs are compiled, you'll want to download them to our DB16000 evaluation board for execution and debugging.

The DB16000 is a complete microcomputer system comprising the NS16032 CPU, the NS16201 Timing Control Unit, sockets for our Memory Management Unit, Floating Point Unit, and Interrupt Control Unit, 128K bytes of on-board RAM, a wide range of both standard and optional I/O interface devices, and a monitor program in PROM. To facilitate the development of efficient software, either of our cross-software packages communicates with the monitor program (via a serial link), allowing you to down-load, execute, and debug your programs in the DB16000's native environment.

Finally, for seamless integration of your software and NS16000-based hardware application, you'll want our

ISE/16, a powerful in-system emulator.

Our easy-to-work-with ISE/16™ allows real-time emulation of the NS16000 chips, for testing and debugging hardware and software in your own hardware environment. This ISE-which includes the NS16032 CPU, the NS16082 MMU, and the NS16201 TCU, and 30K bytes of mapping RAM-plugs directly into your target system, requiring no target-system modification. (\$9,450.00)

Today, the NS16000 family—and it alone—can enable you to put large-computer-like products on the market at microprocessor prices: from elegant personal and business

computers to graphic workstations to industrial control systems.

This elegance, we believe, will breed success—which might make you want to turn one or two cartwheels yourself.

Please call the National Sales Representative nearest you for more information and the answers to your questions. Ask to meet with one of our Field Applications Engineers, too. Or circle the number below.

Here's all you need.

VAX and VMS are trademarks of Digital Equipment UNIX is a trademark of Bell Laboratories.

NS16000, NSX-16, NSXC-16, and ISE/16 are trademarks of National Semiconductor Corporation.

#### Artificial intelligence

(continued from page 34)

generic and can perform reasoning tasks that are needed for any number of applications. The company is actively pursuing joint venture partners to develop expert systems in software engineering, applied sciences, manufacturing, and the financial industry.

A very specific expert system has been developed by General Electric's Research and Development Labs. CATS-1 is a locomotive troubleshooting system whose knowledge base is embedded with the expertise of the company's top locomotive field service engineer. In operation, the user asks questions concerning the malfunction displayed onscreen (see Figure). The user can also call detailed drawings of various components at any time during the question and answer session. The expert system reaches conclusions about the malfunction by searching deeper into the layers of the locomotive's mechanism. Repair procedures for that malfunction are also displayed onscreen. The CATS-1 program evolved from the more basic GEN-X development efforts at GE. This project is an effort to develop a generic expert system that could streamline the development of specific expert systems such as CATS-1.

A similar course of action is being followed by Teknowledge Inc. The company is pursuing knowledge engineering—the engineering discipline that formalizes knowledge in expert systems. The company designs and supports commercial knowledgebased expert systems for industrial clients. Founded in 1981 by computer scientists from MIT, Stanford University, and the Rand Corp, the company will introduce its first commercial product early in 1984. It will be the first in a series of tools that will enable organizations to implement their own practical, large size, knowledge-based systems. Teknowledge's System 1 will be an integrated package of software and services for the development of such systems. It is intended for developing consultation systems that solve problems requiring complex symbolic inference or judgment. Applications include diagnosis, recommendation, classification, and global planning. An underlying rulebased structure is integrated with an Algol-like language for controlling the consultation. Using Algol will augment the need for proficiency in a symbolic programming language, says Teknowledge.

#### Bell's ACE repairs cables