# **COMPUTER DESIGN**

# THE MAGAZINE OF DIGITAL ELECTRONICS

NOVEMBER 1978

BREAKPOINT DESIGN FOR DEBUGGING MICROPROCESSOR SOFTWARE SIMPLE HARDWARE APPROACH TO ERROR DETECTION AND CORRECTION MULTIPLE PROCESSOR MINICOMPUTER SYSTEMS—PART 2: Implementation

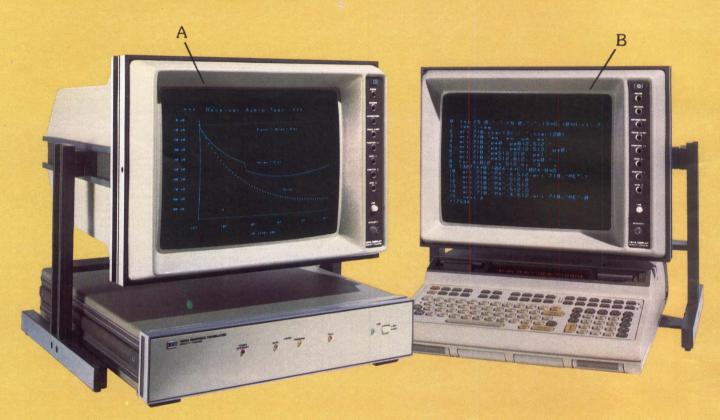

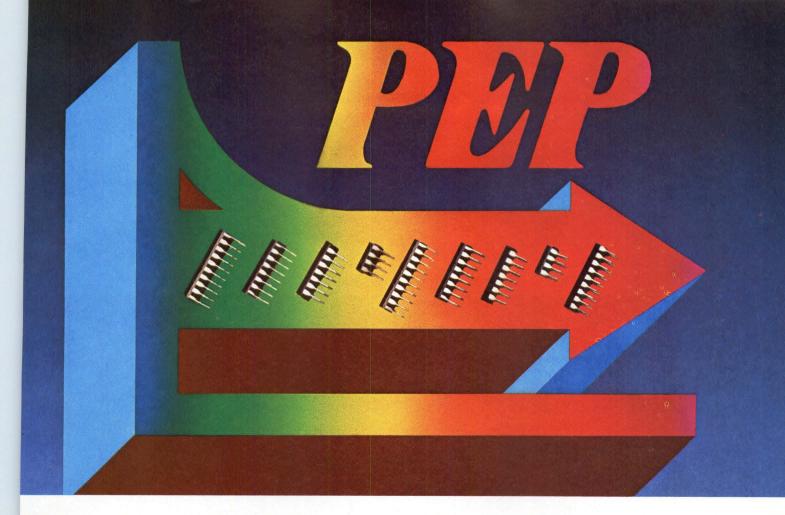

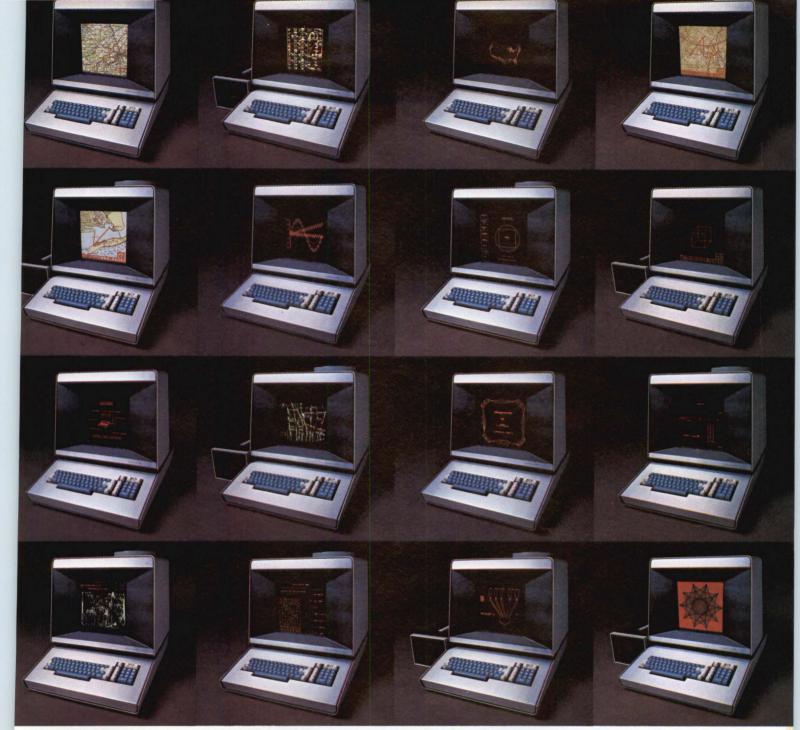

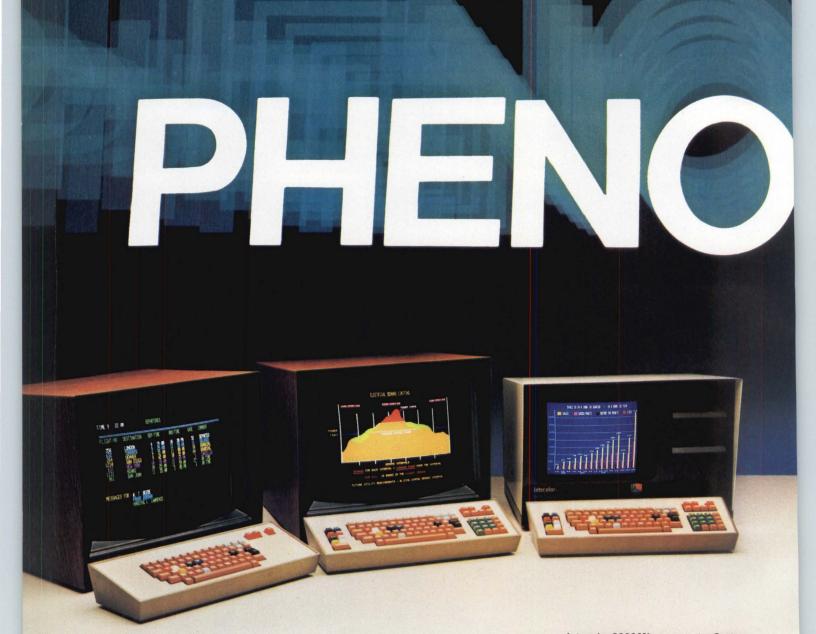

# Here's the fastest (HPHE)\* graphic peripheral available today... and it programs like a plotter.

With the HP 1350A Graphics Translator and one or more HP electrostatic CRT displays, there's no faster way of seeing your system's output. You can get a quick reading - then plot if hard copy is needed.

Because it's HP-IB\* compatible, the 1350A is easy to add to your system. It lets you present different information simultaneously on up to four CRT displays.

And, it makes writing a program for a CRT display as easy as programming a plotter. An optional binary cassette tape for the HP 9825 Desktop Computer simplifies programming and lets you use the same routines on both CRT's and plotters.

The 1350A lets you update the display selectively. For example, in an application such as sequential testing, you can view multiple data plots (A) on a CRT and update only a portion of the display for rapid comparative measurements. It also provides convenient operator interaction. You can display program listings (B), normal and expanded displays, or a cursor and its coordinates.

Ideal for use with HP Data Acquisition and Network Analysis Systems, the 1350A Graphics Translator, priced at \$3,450\*\*, is a useful tool anywhere a fast, high-resolution graphic presentation of information is needed. Write for Application Note 271-1, or call your local HP field engineer for complete details.

088/12

\*HP's implementation of IEEE Standard 488-1975 \*\*Domestic U.S.A. price only

1507 Page Mill Road, Palo Alto, California 94304

For assistance call: Washington (301) 948-6370, Chicago (312) 255-9800, Atlanta (404) 955-1500, Los Angeles (213) 877-1282

CIRCLE 1 ON INQUIRY CARD

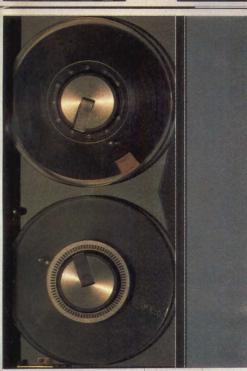

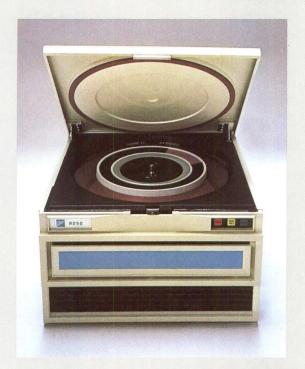

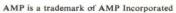

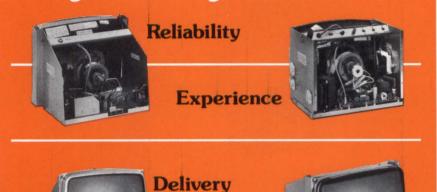

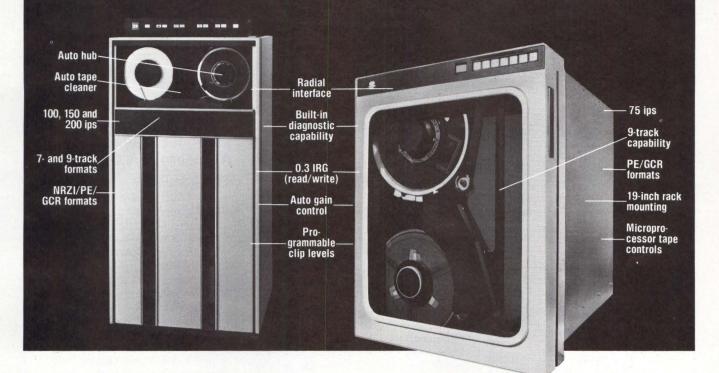

# Models 9100/9300 Vacuum Column Tape Transports ... **Proven. Period.**

Kennedy's vacuum column digital tape transports weren't designed yesterday to grab a piece of a growing market. In fact, they virtually founded the vacuum column market. They were the first to have such features as a capacitive tape-location detector for improved tape life: air bearings and hardcoated read-after-write heads to reduce tape wear and improve data integrity.

Model 9100 (75 ips) and 9300 (125 ips) offer crystal controlled timing, read-after-write shortened skew gate, front-accessible test panel, quick release hubs and simplified tape loading.

Data densities are 200/556 cpi or 556/800 on 7-track units and 800 cpi, 1600 cpi or 800/1600 cpi on 9-track transports. The format is NRZ1/PE. Models 9100/9300 offer more features, more performance, and most important, more time-in-the-field than any competitive units.

Why do we think so? Simple. Our figures show that we are about 3000 satisfied users ahead at this point.

KENNEDY CO.

540 W. WOODBURY RD., ALTADENA, CALIF. 91001 (213) 798-0953

KENNEDY MODEL 93

# THE TALLY PRINTER TERMINAL

# Control 42 functions via the keyboard or the program

The Tally T-1612 Printer Terminal is designed for the user. It's loaded with functions and features. In addition to 42 programmable functions, which are available through the keyboard or through the user program, you get features like outstanding print quality, optimized bi-directional printing at 160 cps for bonus throughput, quiet operation for office use, lots of forms control conveniences, table top or pedestal mount and outstanding reliability that translates into low cost of ownership. And plenty more. Unique features include six selectable type fonts in upper and lower case, LED column/line indicator, non-destructive memory providing pre-selected configuration on power up and 1k buffer standard (up to 4k optionally).

The Tally T-1612 is also available as a Receive Only printer. Both versions sustain a full 1200 Baud transmission rate. Or you can select 300, 600, 2400, 4800 or 9600 Baud operation.

Tally Corporation, 8301 S. 180th St. Kent, WA 98031. Phone (206) 251-5500.

# TALLY<sup>®</sup> PRINTERS WORLDWIDE

OEM SALES OFFICES Boston (617) 272-8070 New York (516) 694-8444 Chicago (312) 885-3678 Los Angeles (213) 378-0805 Miami (305) 665-5751 Philadelphia (215) 628-9998 San Jose (408) 247-0897 Seattle (206) 251-6730 San Antonio (512) 733-8153 Washington, D.C. (703) 471-1145 **BUSINESS SYSTEMS SALES** Orinda, CA (415) 254-8350

# COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS

#### **NOVEMBER 1978**

VOLUME 17, NUMBER 11

# DEPARTMENTS

#### **10 CALENDAR**

# **14 COMMUNICATION CHANNEL**

Rewrite of 1934 Communications Act has been introduced in the Congress. Column examines major features of H.R. 13015 and their potential impact on the communica-tions industry

DIGITAL TECHNOLOGY REVIEW 27

Based on a 256k-bit bubble domain memory device, family of modules and subassemblies is accompanied by a microcomputer develop-ment system which allows users to start application development

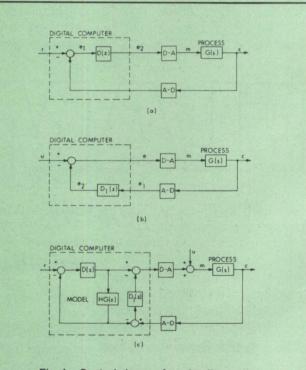

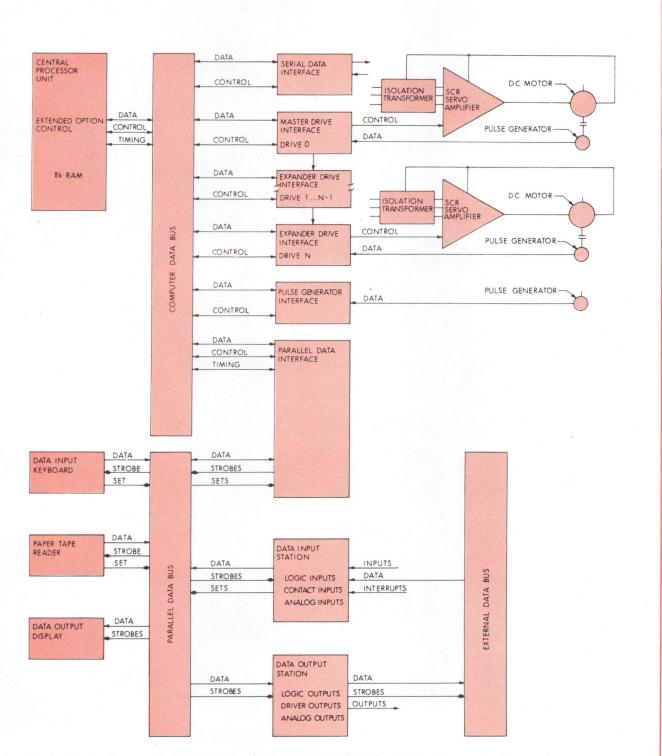

52 DIGITAL CONTROL AND AUTOMATION SYSTEMS

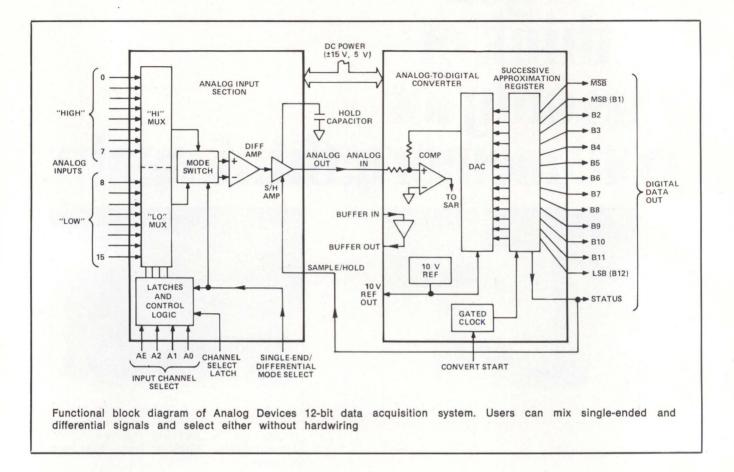

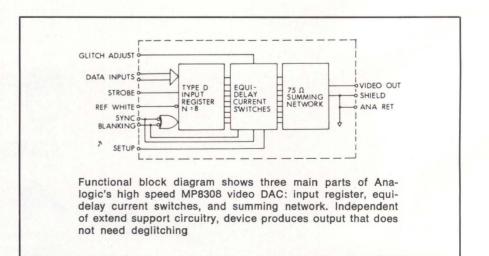

Software and hardware aspects of data ac-quisition and control are being influenced greatly by the ever present microcomputer

MICRO DATA STACK/ 158 PROCESSORS AND ELEMENTS Treatise explores comparison factors and benchmarks involved in the choice of as-sembly language or BASIC for optimum programming of microcomputers

#### MICRO DATA STACK/ 170 COMPUTERS AND SYSTEMS

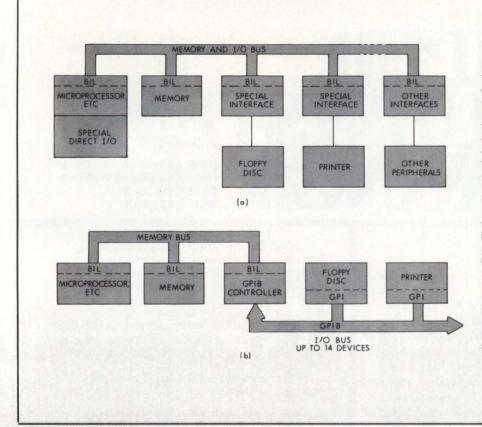

Adoption of the flexible IEEE bus as a standard for microcomputer I/O systems would result in significant savings in time and cost

#### **188 AROUND THE IC LOOP**

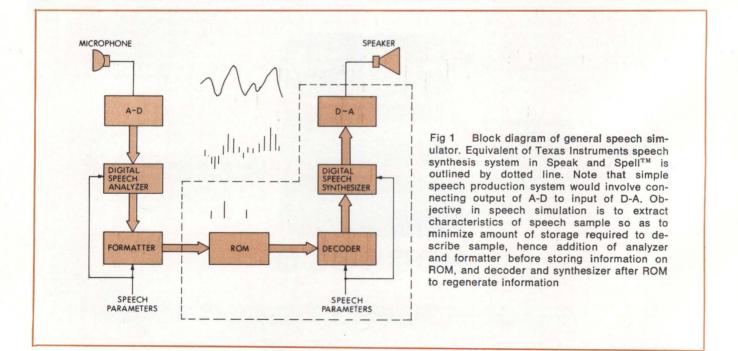

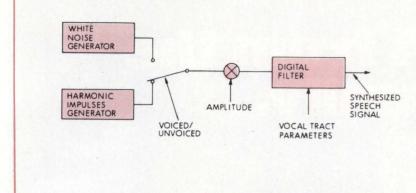

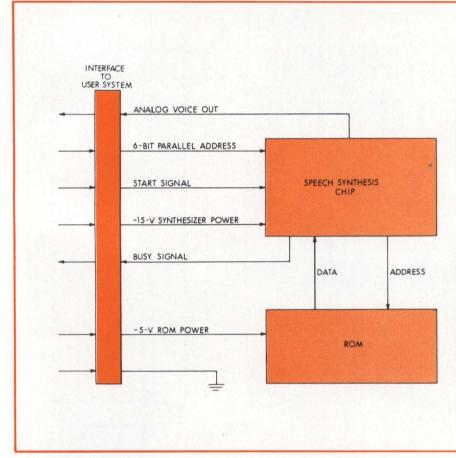

Speech synthesis logic incorporated on a single VLSI chip, when joined with a micro-computer and read-only memory, promises development of small, portable, inexpensive talking machines

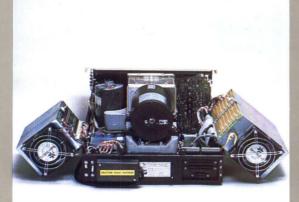

#### **210 PRODUCT FEATURE**

By incorporating fan cooling, dual output switcher gains both high power density and capability to be mounted in any plane

#### 246 LITERATURE

#### GUIDE TO PRODUCT 250 INFORMATION

#### **ADVERTISERS' INDEX** 251

Reader Service Cards pages 253-256

**CIRCULATION: 67.078** (DECEMBER 1977)

Copyright 1978, Computer Design Publishing Corp.

# **FEATURES**

#### BREAKPOINT DESIGN FOR DEBUGGING MICROPROCESSOR SOFTWARE 99 by T. P. Hughes and D. H. Sawin III

Software breakpoints, useful tools for developing microprocessor applications with debug monitors, are sufficiently powerful to debug and test sophisticated realtime software. Developing the optimum breakpoint design requires a thorough knowledge of the microprocessor's architecture

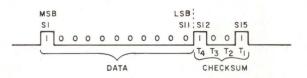

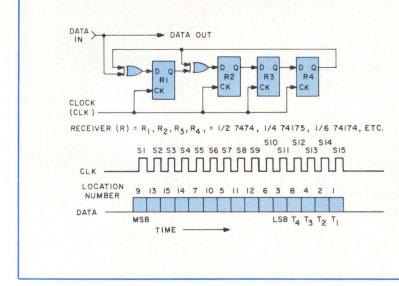

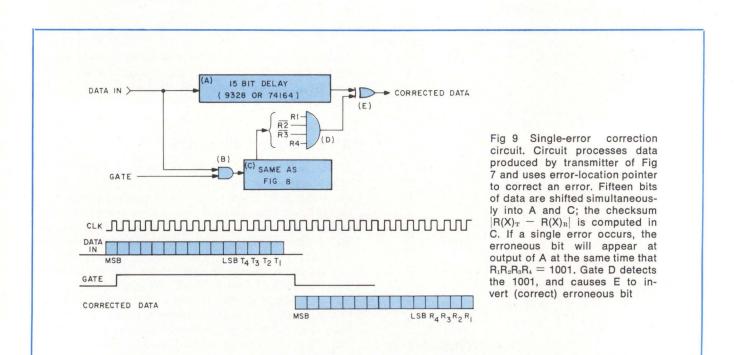

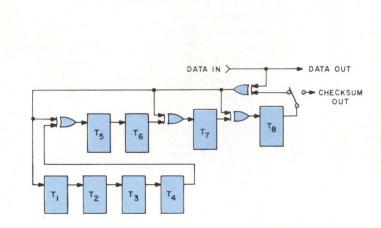

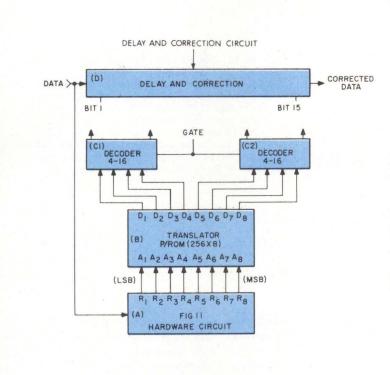

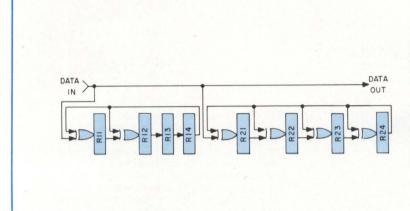

#### SIMPLE HARDWARE APPROACH TO ERROR DETECTION AND CORRECTION 109 by Richard C. Montgomery

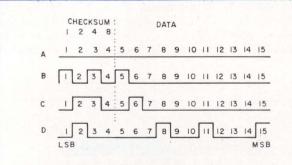

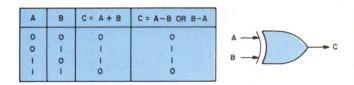

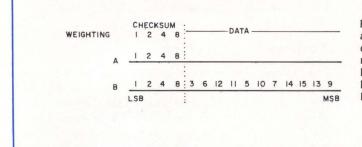

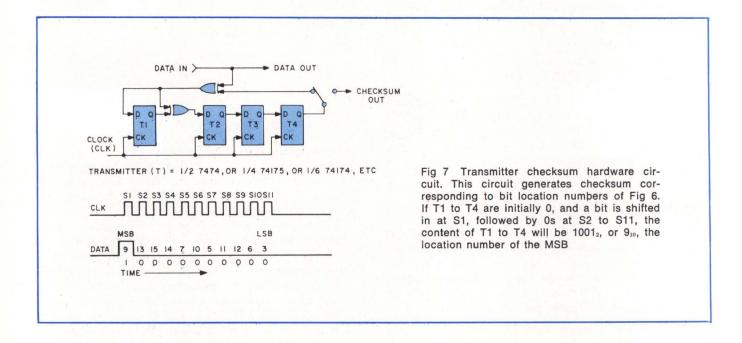

A simplified approach to the operation of single- and double-error correction codes does not require use of mathematical matrices or polynomial algebra. Specific hardware for data and checksum bit encoding and decoding is developed for both error cases

#### MULTIPLE PROCESSOR MINICOMPUTER SYSTEMS-**PART 2: IMPLEMENTATION** 121 by Burt H. Liebowitz

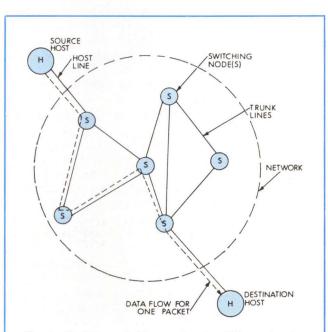

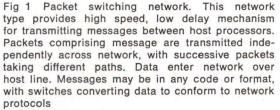

Design concepts of colocated multiple processor systems, examined in Part 1, are put to work in formulating real-world packet switch network

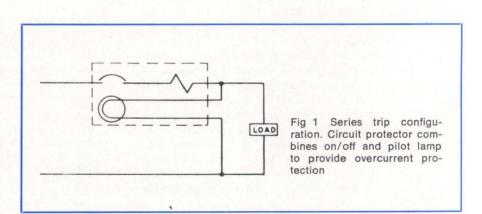

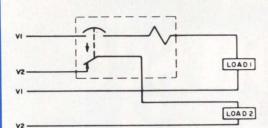

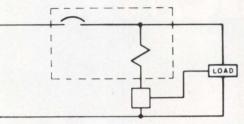

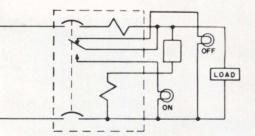

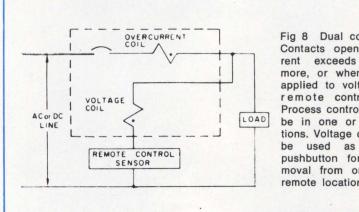

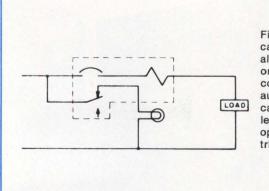

#### APPLYING MAGNETIC CIRCUIT BREAKERS IN DIGITAL CIRCUITS 132 by Donald S. Tall

Circuit breakers are available in many configurations to provide the protection necessary for a wide range of computer-related applications

#### INFORMATION PRESERVING CODES COMPRESS BINARY PICTORIAL DATA 134 by Usko Moilanen

Data compression experiments performed using variable length binary codes on redundant binary pictorial data have achieved a 76% reduction in necessary storage capacity while maintaining basic information identity

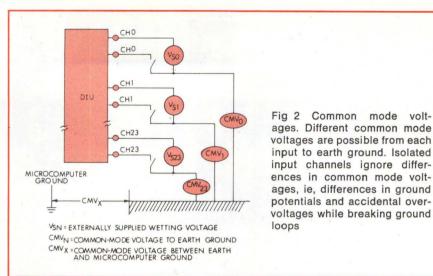

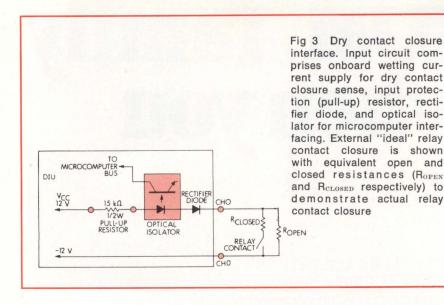

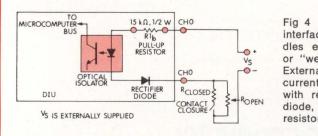

#### DIGITAL INPUT UNITS ISOLATE MICROCOMPUTER FROM INDUSTRIAL LEVEL VOLTAGES 142 by C. R. Teeple

Microcomputers can be interfaced safely to process control inputs by optical isolation from the inherent high voltages and widely varying conditions of such applications

# CONFERENCES

#### MIDCON/78 80

Program sessions, exhibits, and a seminar on the schedule for this year's Midcon provide a look at memory techniques, electro-optics, microprocessors, and telecommunications

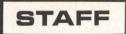

# Okidata Sells Disc Drives That Sell Minisystems

OKIDAK

Seven 3300 Series models, from 13 to 80 megabytes, fit in just 7 inches of rack space, complete with power supply and the finest air filtration system in the industry.

The 3300 combines moving head storage with over two megabytes of fixed head to satisfy the full range of business, communications and distributed processing applications—with one form factor and one set of systems programs.

Series 3300 disc drives are making hundreds of different mini- and medium-scale computer systems more reliable, with Winchester heads and discs and Okidata's unique, low mass rotary positioner.

The 3300 Series—OEM prices that create new minisystem market opportunities, a range of capacities to satisfy them and Okidata reliability—backed by a worldwide sales and service organization.

Okidata Corporation 111 Gaither Drive Mount Laurel, New Jersey 08054 Telephone: 609-235-2600

Publisher and Editorial Director Robert Brotherston

Associate Publisher Anthony Saltalamacchia

> Editor John A. Camuso

Managing Editor Sydney F. Shapiro

Technical Editor George V. Kotelly

West Coast Editor Michael Chester Arcadia, Calif. (213) 574-7447

Associate Editors Peggy Killmon James W. Hughes

Assistant Editor Joanne O'Donnell

Editorial Assistant Winifred L. Helfrich

Editorial Advisory Board Brian W. Pollard Ralph J. Preiss Rex Rice

Contributing Editors Richard Ahrons A. S. Buchman H. S. Miiller Harold H. Seward

Production Manager Judy Lober

Advertising Production Linda M. Wright

> Art Director James Flora

Technical Illustrator Charles Manchester

Circulation Manager Alma Brotherston

Marketing Manager Geoffrey Knight, Jr.

Assistant Marketing Manager Megan Kern

> Research Associate Sidney Davis

Business Manager David C. Ciommo

Vice President-Sales Lindsay H. Caldwell

Editorial & Executive Offices 11 Goldsmith St Littleton, MA 01460 Tel. (617) 486-8944 (617) 646-7872

Editorial manuscripts should be addressed to Editor, Computer Design, 11 Goldsmith St., Littleton, MA 01460. For details on the preparation and submission of manuscripts, request a copy of the "Computer Design Author's Guide."

Computer Design is published monthly. Copyright 1978 by Computer Design Publishing Corporation. Controlled circulation postage paid at Pontiac, III. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS—FORM 3579 to be sent to Computer Design, Circulation Dept., P.O. Box A, Winchester, MA 01890. Subscription rate is \$24.00 in U.S.A., Canada and Mexico, and \$40.00 elsewhere. Microfilm copies of Computer Design are available and may be purchased from University Microfilms, a Xerox Company, 300 N. Zeeb Rd, Ann Arbor, MI 48106.

# **The best** ribbon cartridges start with the best designs.

And the best designs come from experience. That's what Data Packaging offers you: Fourteen years of experience in designing and manufacturing cartridges for all kinds of requirements.

Impact printers demand a lot from a ribbon cartridge. Reliability, smooth operation, high character yield-and not just in the prototype but in volume production. We have the design experience and the manufacturing capabilities to meet all of your requirements without compromise.

(Tel. No.)

Tell us what your requirements are. Call our cartridge design team headed by Hubbard Yonkers at 617-868-6200. Or, if you prefer, send us the coupon and we'll call you.

| _ |      |    |    | 1 |

|---|------|----|----|---|

|   | Call | me | at | - |

Name, Title

Company.

Address

We deliver performance.

CIRCLE 5 ON INQUIRY CARD

# THE PARTS THAT SET US APART

Look at us part by part. There has never been a vacuum column transport like Cipher Data Product's 900X-the first vacuum column tape drive with complete microprocessor control-available in 75 ips or 125 ips.

Forget all the old problems with vacuum column tape drives-the heat, the noise, the inefficient tape control, the belts, hoses, relays, solenoids, cooling fans, incandescents, energy drain, oversize and high cost-because the Cipher Data Products 900X drives don't have any of them. The 900X Series is a completely new design concept in digital tape technology. Part 1-The Z-80 Microprocessor

The intelligence of the Z-80 microprocessor brings major performance enhancements to the 900X while increasing reliability through reduction in both the complexity and number of components. For the first time, total control of tape is a reality in a vacuum column tape drive. There is no snap, whip or loose tape during critical load and unload. There is no possibility of tape damage in the event of power failure in any mode. And, because exact tape position is sensed and con-

trolled by the microprocessor, maximum possible speed is maintained throughout the rewind operation.

Built-in diagnostics and service aids, unique to the Series 900X drives, are made possible by Z-80 intelligence. Decision making logic in ROM is automatically tested during power up and, if not successful. the drive shuts down with fault indications clearly given on the front panel. Possible damage to tape or machine is avoided and, since fault areas are readily identified, repair and maintenance time are minimized.

#### Part II - Dual Density Databoard

With the 900X Series, Cipher Data Products introduces a state-of-the-art databoard on only one card that handles dual density, NRZ or PE only and is 100% industry compatible. To the user, this multi-function board significantly reduces spares cost.

Most important, in comparison with competitive units, this new databoard provides increased reliabilitywith a 40% reduction in total parts count, improved PE resolutions, low noise generation and pickup, a 50% lower power consumption, and the elimination of troublesome write deskew alignments. In addition, self test through special diagnostic and alignment modes can be accomplished without the use of external equipment. Part III—The Beltless Direct Drive

**Compare Cipher Data** Product's 3400 rpm direct drive

motor to the belt driven 10,000 rpm motors in most competitive drives. The 900X drive operates on only 300 watts (nominal) of power in large part due both to the use of the direct drive motor and to a highly efficient, low power, multistage centrifugal pump, contrasted to the multiple pumps required by other drives. Only one blower on the 900X means quiet, whisperlike operation and no hose connections to cause maintenance problems. And, the Cipher drive can be operated on either 50 Hz or 60 Hz without frustrating belt change.

Now look at all the other parts-like the switched linear servo system, optical file protect, LED light sources, hard chromed face read/write head, sapphire tape cleaner and modulated tape sensor system. The Series 900X vacuum column tape drive is far ahead of the market in design while still fully compatible with today's industry standards.

Do your part. Call for full information and OEM quantity price competitive quotes. Cipher Data Products, Inc., 5630 Kearny Mesa Road, San Diego, California 92111. (714) 279-6550.

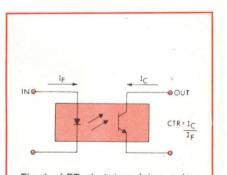

# The EMR is dead... Long live Motorola

The SPST electromechanical relay (EMR) is dead-killed by contact arcing, mechanical wearout and incompatibility with modern circuitry.

We know - and you know - where multiplepole, higher current contactor applications are required, it'll still be around.

But for the bulk of logic level designs where you need the advantages of solid-state reliability, convenience, versatility, standard packages, multiple sourcing and low cost ... solid-state relays are the only way to go!

Now Motorola presents a new, broad line of SSRs and I/O modules vastly superior to the century-old EMR and affording significant advances even over similar contemporaries. Advances that spell quality throughout.

Like better input characteristics for optimized opto coupler life. The more current, the shorter the coupler's life expectancy. Our SSRs limit coupler current and hold it to a minimum. The result is a longer-lasting SSR with constant performance over time.

· Like use of the finest, in-house manufactured semiconductors from the world's technology-involume producer. Nobody can beat that kind of QC. Like extended design goals with design performance verified by Mil-type testing. Quality and care in manufacture mean a better product from us now and a better one for you down the road. · Like complete, void-free, vibration-resistant potting that's withstood millions of hours of under-the-hood environments.

# **For Power Designs**

|   | Current | Coupler             | - |

|---|---------|---------------------|---|

| • |         |                     |   |

|   |         |                     |   |

|   |         | Motorola<br>Coupler |   |

|   |         | Current             |   |

|   |         |                     |   |

|   |         | -40° to +80°C       |   |

|   |         |                     | - |

|   |         |                     |   |

20 30 Control Voltage

### **Positive control** over temperature

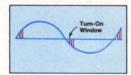

We guarantee the control points of the output switch over the full spec'd temp range. You can count on it from 3-32 V over a -40° to +80°C range. And the highest voltage doesn't shorten life of the optical isolator. Our design goal is reliable operation for 10 years.

#### zero voltage switching

Closures can occur only near the zero-crossing point of line voltage, minimizing noise generation which could inter fere with other electronics. The electrical environment therefore remains clean.

**Reverse polarity** protection

Additional features like reverse polarity protection obviate damage from error in installation and subsequent equipment malfunction.

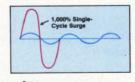

# **High peak surge** ratings

1000% single cycle surge ratings protect against current abuse. Conservativelyrated components and thermal design contribute to longer service life

## Shock & vibrationresistance

Completely potted units have shown ability to withstand MIL-spec type testing for accelerated impact, vibration, salt spray, thermal cycling life, etc. We make em rugged for rugged environments.

## Transient immunity

Motorola SSR components are 100% overrated for high voltage conditions. Each is internally protected against high line, random noise, spikes and conditions typically found in harsh industrial environments

# solid-state relays!

P120D2

Like compatibility with microprocessors, integrated circuits and other solid-state relay control circuits.

Like standardized packaging and footprints avail-

able from multiple industry sources.

• Like technical field assistance from our nationwide applications engineers and reps and stocking from authorized distributors.

That's why our relays and modules are so good. And that's why they'll last a long time.

For more information on any of these new Motorola solid-state units, contact Motorola Subsystem Products, P.O. Box 20912, Phoenix, AZ 85036 (602) 244-3103. Viva Motorola Solid-State Relays!

| Switch        | Type<br>Mounting | Output<br>Current<br>A | Line<br>Voltage<br>V | Peak<br>Surge <sup>#</sup><br>A |

|---------------|------------------|------------------------|----------------------|---------------------------------|

| M120D05A      | Chassis          | 5                      | 120                  | 50                              |

| M120D10A      | Chassis          | 10                     | 120                  | 100                             |

| M240D05A      | Chassis          | 5                      | 240                  | 50                              |

| M240D10A      | Chassis          | 10                     | 240                  | 100                             |

| P120D2*       | PC Board         | 2                      | 120                  | 20                              |

| P120D3*       | PC Board         | 3                      | 120                  | 55                              |

| P240D2*       | PC Board         | 2                      | 240                  | 20                              |

| P240D3*       | PC Board         | 3                      | 240                  | 55                              |

| IAC5 (AC in)  | PC Board         | -                      | 95-130               | -                               |

| IDC5 (DC in)  | PC Board         | -                      | 10-32                | _                               |

| OAC5 (AC out) | PC Board         | 3                      | 12-140               | 55                              |

| ODC5(DC out)  | PC Board         | 3                      | 60                   | 5†                              |

†1-second. \*Available in vertical-mount package; add "M" prefix to type number. #Single-Cycle.

# For PC Boards

Fit-anywhere, go-anywhere horizontal- or vertical-mounted convenience and economy are yours with the P/MP-series 2 & 3A, 120 & 240 V relays.

Measuring only %" thick, P-series offers the lowest profile solid-state unit of its kind for card rack mounting on ½" centers. No wire terminations. No mechanical skills. You treat system loads like any other electrical signal and avoid connector-wire, board-mounting problems and associated labor costs. 1,500 V photo isolation, zero-voltage turn on, built-in snubber network, 100% testing at rated load, I/C compatibility and a  $-40^{\circ}$  to  $+100^{\circ}$ C operating range are standard. The family's also available in a compact, vertical-mounted MP-series package for high density areas.

P120D3

In a costly electronic control system, it's easy to invest twothirds to three-fourths of total cost in just interface and wiring. We've now solved that and given you the convenience and versatility to revolutionize your I/O control system.

Because each Motorola I/O module contains signal conditioning, isolation, logic interface, power handling and status indication drive in one compact, compatible package that interfaces with all 5 V logic families and standard MPU I/O requirements. At a *fraction* of the cost of other systems.

The color-codable board's standard, too ... with or without the modules. You can interface the entire system with stan-

dard minis like PDP-11, Supernova and Motorola and Intel micros...install them in standard NEMA enclosures...and remove or replace modules without disturbing field wiring. The package is rapidly becoming the industry standard, too...and that makes it comfortable.

Motorola I/O Modules. Easy. Quick. Reliable.

CALENDAR

# CONFERENCES

DEC 4-6—Conf of the Assoc for Computing Machinery, Sheraton-Park Hotel, Washington, DC. INFORMATION: Dr Richard Austing, Dept of Computer Science, U of Maryland, College Park, MD 20742. Tel: (301) 454-2004

DEC 4-6—Internat'l Electron Devices Meeting, Washington Hilton Hotel, Washington, DC. INFORMATION: Susan Henman, Courtesy Assoc, 1629 K St NW, Washington, DC 20006. Tel: (202) 296-8100

**DEC 5-7—Design Engineering Conf/West,** Convention Ctr, Anaheim, Calif. INFORMA-TION: Clapp & Poliak, Inc, 245 Park Ave, New York, NY 10017

**DEC 12-14**—**Midcon,** Dallas Convention Ctr and Dallas Hyctt Regency, Dallas, Tex. IN-FORMATION: William C. Weber, Jr, General Mgr, Electronic Conventions, Inc, 999 N Sepulveda Blvd, El Segundo, CA 90245. Tel: (213) 772-2965

**DEC 13—Computer Networking Sym,** Nat'l Bureau of Standards, Gaithersburg, Md. IN-FORMATION: Computer Networking, PO Box 639, Silver Spring, MD 20901. Tel: (301) 439-7007

JAN 16, FEB 8—Invitational Computer Conf, Orange County, Calif; Ft Lauderdale, Fla. INFORMATION: B. J. Johnson & Associates, 2503 Eastbluff Dr, Suite 203, Newport Beach, CA 92660. Tel: (714) 644-6037

JAN 22-26—Computers and Peripheral Trade Show, London, England. INFORMATION: E. Belden, U.S. Dept of Commerce, Bureau Export Div, Washington, DC 20230

JAN 24-27—Internat'l Microcomputers/Minicomputers/Microprocessors (IMMM), Harumi Exhibition Ctr, Tokyo, Japan. INFORMA-TION: Industrial and Scientific Conf Management, Inc, 222 W Adams St, Chicago, IL 60606. Tel: (312) 263-4866

JAN 30-FEB 1—Communication Networks, Sheraton-Park Hotel, Washington, DC. IN-FORMATION: Ed Halsted, The Conference Co, 60 Austin St, Newton, MA 02160. Tel: (617) 964-4550

FEB 6-8—Sym on Modeling and Performance Evaluation of Computer Systems, Technische Universität Wien, Austria. INFORMATION: Dr A. Butrimenko, Internat'l Institute for Applied Systems Analysis, A-2361 Laxenburg, Austria FEB 12-16—Computers and Peripheral Equipment Exhibition, U.S. Trade Ctr, Sao Paulo, Brazil. INFORMATION: Industry and Trade Administration, Rm 4039, U.S. Dept of Commerce, Washington, DC 20230. Tel: (202) 377-5427

FEB 14-16—European Conf on Parallel and Distributed Processing, Toulouse, France. IN-FORMATION: C. Girault, Institut de Programmation, 4 Place Jussieu, 75230 Paris Cedex 05, France

FEB 14-16—IEEE Internat'I Solid State Circuits Conf (ISSCC), Philadelphia, Pa. IN-FORMATION: Lewis Winner, 301 Almeria Ave, PO Box 343788, Coral Gables, FL 33134. Tel: (305) 446-8193

FEB 26-MAR 1—COMPCON Spring, San Francisco, Calif. INFORMATION: COMPCON Spring 79, PO Box 639, Silver Spring, MD 20901. Tel: (301) 439-7007

FEB 26-MAR 2—INTELCOM, Dallas Convention Ctr, Dallas, Tex. INFORMATION: M. Raftery, Mgr of Promotion, Horizon House Internat'l, 610 Washington St, Dedham, MA 02026. Tel: (617) 326-8220

FEB 27-MAR 2—NEPCON WEST, Anaheim Convention Ctr, Anaheim, Calif. INFORMA-TION: Industrial and Scientific Conf Management, Inc, 222 W Adams St, Chicago, IL 60606. Tel: (312) 263-4866

FEB 28-MAR 2—Internat'I Computer Expo, Tokyo Internat'I Trade Ctr, Tokyo, Japan. INFORMATION: Golden Gate Enterprises, Inc, 1307 S Mary Ave, Suite 210, Sunnyvale, CA 94087. Tel: (408) 735-1122

MAR 4-8—Business Systems Exhibition, U.S. Trade Ctr, Tehran, Iran. INFORMATION: Susan Blackman, Project Mgr, Commerce Action Group for the Near East (CAGNE), Rm 6015B, Washington, DC 20230. Tel: (202) 377-2952

MAR 6-8—Optical Fiber Communication, Shoreham Americana Hotel, Washington, DC. INFORMATION: Optical Society of America, 2000 L St, NW, Suite 620, Washington, DC 20036. Tel: (202) 293-1420

MAR 19-21—IECI Conf and Exhibit on Industrial and Control Applications of Microprocessors, Philadelphia, Pa. INFORMATION: S. J. Vahaviolos, Physical Acoustics Corp, PO Box 3135, Princeton, NJ 08540. Tel: (609) 799-8266 SEMINARS

DEC 4-5—Microcomputers: Operating Principles, Hardware, and Software, and DEC 6-8—Microcomputer Hardware and System Design; DEC 4-8—PASCAL Programming for Mini and Microcomputers, and DEC 7-9— Bit-Slice Microcomputer and Digital System Design; and JAN 11-13—Software Engineering for Mini/Microcomputer Systems, Dallas, Tex; Woburn, Mass; and Los Angeles, Calif, INFORMATION: Prof Donald D. French, Institute for Advanced Professional Studies, One Gateway Ctr, Newton, MA 02158. Tel: (617) 964-1412

DEC 18-20—Software Testing and Test Documentation Workshop, Bahia Mar Hotel, Ft Lauderdale, Fla. INFORMATION: Dr Edward F. Miller Jr, Software Research Associates, PO Box 2432, San Francisco, CA 94126

JAN 10-11, MAR 27-28—Professional Calculator Seminar, Ambassador Motor Hotel, Minneapolis, Minn. INFORMATION: Nortronics Education Div, 8101 Tenth Ave N, Minneapolis, MN 55427. Tel: (612) 545-0401, X295

JAN 23-25—ATE Seminar/Exhibit, Los Angeles Marriott Hotel, Los Angeles, Calif. INFORMATION: ATE Seminar/Exhibit, Circuits Manufacturing Magazine, 1050 Commonwealth Ave, Boston, MA 02215. Tel: (617) 232-5470

SHORT COURSES

DEC 4-8, DEC 11-15, JAN 15-19, JAN 22-26, and JAN 29-FEB 2—Microprocessor/ Computer Short Courses, Washington, DC; Atlanta, Ga; Los Angeles, Calif; Denver, Colo; and Dallas, Tex. INFORMATION: Kim D. Sanson, Program Mgr, Integrated Computer Systems, Inc, 3304 Pico Blvd, PO Box 5339, Santa Monica, CA 90405. Tel: (213) 450-2060

DEC 11-15—Modern Digital Communications; JAN 8-12—Structured Programming and Software Engineering; JAN 22-23—Minicomputer Technology; and JAN 24-26—Design and Selection of Minicomputers, George Washington U, Washington, DC. INFORMA-TION: Martha Augustin, Continuing Engineering Education, George Washington U, Washinaton, DC 20052. Tel: (202) 676-6106

Announcements intended for publication in this department of *Computer Design* must be received at least two months prior to the date of the event. To ensure proper timely coverage of major events, material preferably should be received six months in advance.

# Head and shoulders below the competition

**DEC RX01** 10<sup>1</sup>/2<sup>"</sup> \$4300 Bootstrap \$320 extra

Data Systems' new, floppy disk system offers performance and storage equal to DEC<sup>®</sup>'s RX01, but uses half the space and costs 25% less.

Save money, save rack space and increase your system's reliability by selecting the DSD 110 for use with any DEC LSI-11 or LSI-11/2.

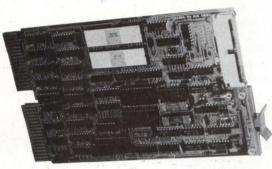

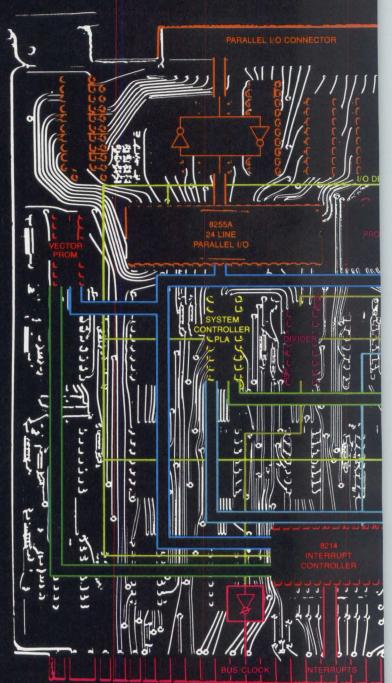

The DSD 110 provides 512K bytes of fully DEC-compatible storage in a 51/4" cabinet. While the DSD 110 saves you rack space, it also uses one less Q-bus slot than DEC's RX01. All this is possible because the interface, formatting and controller circuitry, and hardware bootstrap have been combined on a single dual-wide card. This card, which is available separately, eliminates the need for DEC's REV-11 card. To find out more about the low-cost, low-profile DSD 110, contact Data Systems today. A data sheet and price list will be forwarded to you immediately.

Registered trademark of Digital Equipment Corporation

> Data Systems Design, Inc. 3130 Coronado Drive, Santa Clara, CA 95051 (408) 249-9353 TWX 910-338-0249

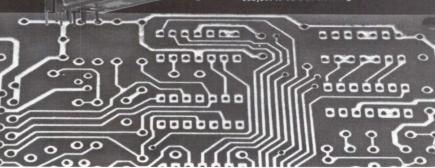

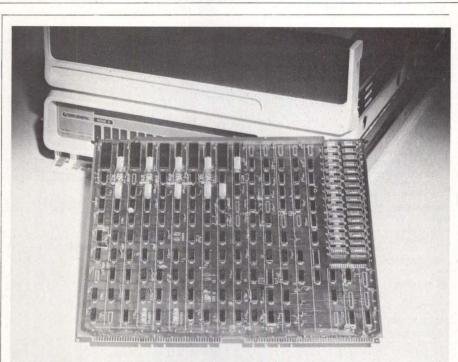

Data Systems has combined interface, formatter, controller, and hardware bootstrap on this single dual-wide card. Available separately in OEM quantities.

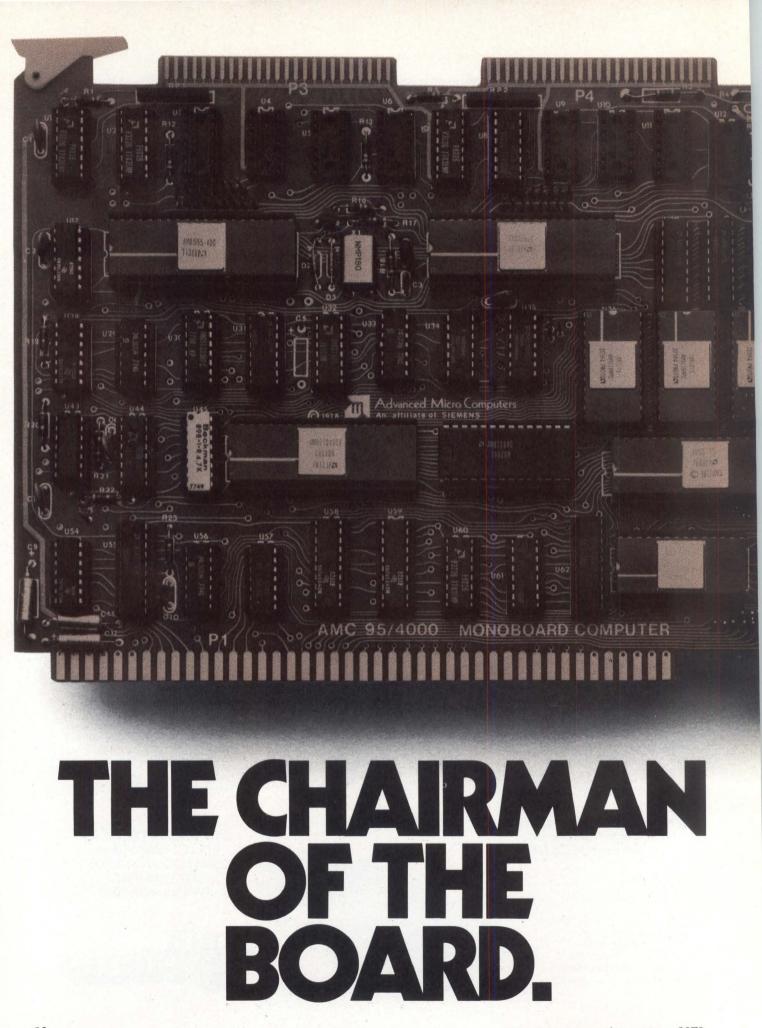

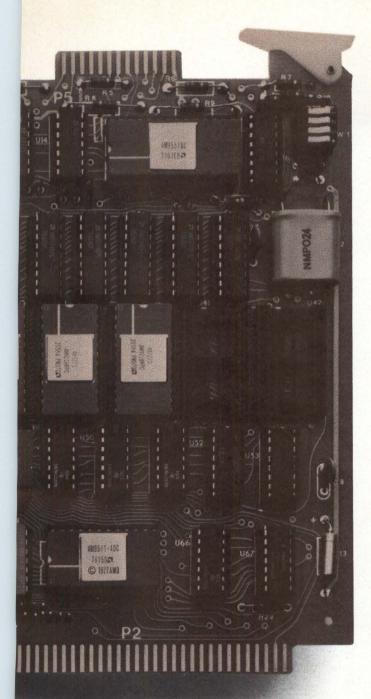

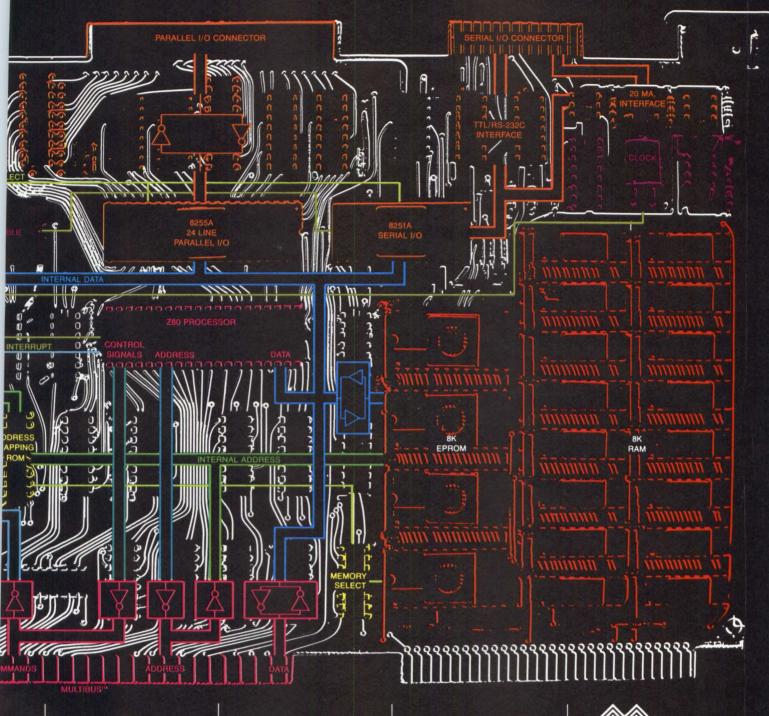

# MEET THE MONOBOARD. THE WORLD'S MOST POWERFUL SINGLE BOARD COMPUTER.

AMC's Monoboard, the AMC95/4000, is the new boss of microcomputer boards. It performs complex math at twice the speed of any other board. And it can process data at clock rates of 2MHz or more.

The Monoboard really has what it takes to be a leader. It performs both floating-point and fixed-point math operations in the blink of an LED. It can do 16- and 32-bit two's complement arithmetic (add, subtract, multiply and divide), 32-bit floating-point operations, plus transcendental and datamanipulation functions.

But those aren't the only reasons the Monoboard is taking over. It also has four independent DMA channels, 4K bytes of RAM, space for up to 12K bytes of ROM/E-PROM, a serial I/O port, and 48 programmable I/O lines.

And the Monoboard has the same physical configuration as the SBC-80 card family. So anyone now using SBC-80's can pack more power in their systems by simply plugging in the Monoboard.

If you want power, and lots of it, get the Chairman of the Board on your side. Get the Monoboard from AMC.

An Affiliate of Siemens 3340 Scott Blvd., Santa Clara, CA 95051. (408) 988-7777 Distributed nationally by Advanced Micro Devices.

# **COMMUNICATIONS ACT of 1978**

# John E. Buckley

Telecommunications Management Corporation Cornwells Heights, Pennsylvania

he year 1978 has been marked by a new attempt to replace the original Communications Act of 1934. It was under that legislation of over 40 years ago that the Federal Communications Commission (FCC) was formed, and the concept of franchised communications monopolies, ie, AT&T, was defined and implemented. Much of the confusion and turmoil characterizing today's evolving world of telecommunications regulation is the result of continuing attempts to interpret and apply the provisions of that 1934 statute to the demands and needs of the telecommunications community of 1978. It is universally agreed that there is a necessity to rewrite that Communications Act to be reflective of today's requirements, and supportive of communications developments in the foreseeable future.

During 1976 a Bell System sponsored legislation entitled the Consumer Communications Act of 1976 was introduced to the United States Congress. It was blatantly structured to prohibit competition in all aspects of communications services and equipment while at the same time granting antitrust immunity to AT&T. During an election year it was obvious that some legislators would automatically add their endorsements because of the votestimulating title of the proposed Act. It was only after a major information campaign by independent communications equipment manufacturers and by the specialized communications common carriers that the U.S. Congress acted to defeat that effort.

In June of 1978, Congressmen Van Deerlin and Frey introduced a rewrite of the 1934 Communications Act. This effort was not initiated by any special interest group. It was a genuine attempt to realign a generally outmoded legislative Act in order to meet all legitimate needs of the participants in today's communications environment.

This proposed Communications Act of 1978 would replace the present FCC with a new Communication Regulatory Commission. One of the primary tasks of this body would be to define and establish the guidelines under which services would be classified as either competitive or non-competitive. Its jurisdiction would be only over interstate telecommunications services. This classification authority would permit the allocation of competitive and monopoly markets.

As the new Act is presently drafted, the Commission is apparently provided a broad and loosely defined authority to define and classify. Many competitive communications organizations have expressed concern that, under the draft provisions, the new Commission could broaden the existence of regulation rather than encourage a growing competitive environment.

The Act specifies the objectives or guidelines for the new Commission. As with the Communications Act of 1934, the promotion and support of a nationwide telecommunication service at affordable rates is cited as a major goal. The Act also declares that the Commission is to place maximum "feasible" reliance on competitive marketplace forces. As such, it is guided to rely on the ensuing competition to bring the desired efficiencies, innovations, and economies to the consumer. These same competitive factors are to be expected to determine the variety, quality, and cost of telecommunications services. The new Commission is also instructed to establish and encourage full and fair competitive conditions, and to prevent practices that would allow or cause the limitation or exclusion of competition in the provision of telecommunications services. The only reference to the use of regulation in these guidelines is in cases where competitive marketplace forces are deficient.

The tone of the Act appears pro-competition and advocates minimal application of regulation on almost an exception basis. There appear to be concerns however, that certain oversights and omissions will encourage even greater confusion and restrictions than presently exist under the original Communications Act of 1934.

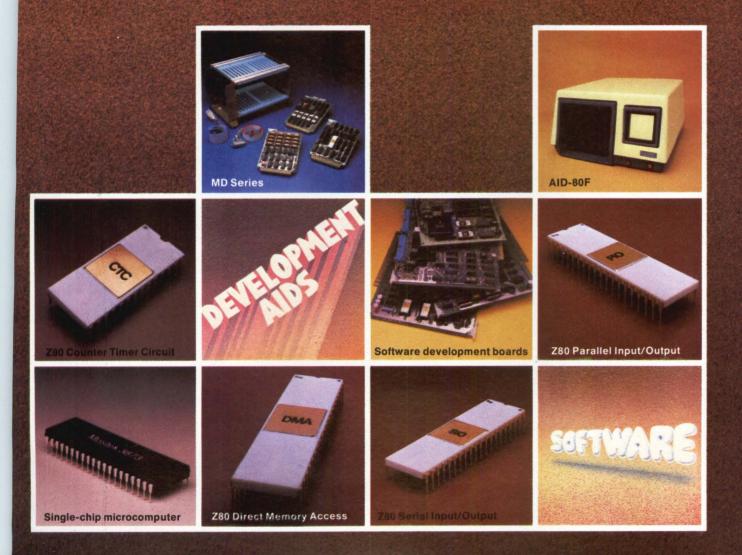

# How you can get Z80 power for \$171. Mostek's MD Series" lets you control system functions and cost.

Design Z80 systems fast and economically with Mostek's MD Series of OEM microcomputer boards. Choose either MD standalone boards or expandable MDX

| MDX      |          | <b>Design Se</b> |          |

|----------|----------|------------------|----------|

| Module   | Price*   | Module           | Price*   |

| CPU1     | \$171.00 | SIO              | \$171.00 |

| 8K DRAM  | 180.00   | PIO              | 164.00   |

| 16K DRAM | 223.00   | EPROM/UART       | 148.00   |

| 32K DRAM | 410.00   |                  |          |

|          |          | MD-SBC1          | 194.00   |

boards – both on compact 4.5" x 6.5" cards.

The MDX boards are modularized by function. This reduces system cost since you buy only the functional modules you need. And you can use any combination of MDX cards because all MDX cards are STD BUS compatible.

The STD BUS is a unique secondsourced motherboard interconnect

Manna and a state of the state

system designed to handle any MDX card in any card slot. This reduces hardware design time letting you concentrate on application software.

The MD standalone microcom-

puter boards are also Z80-based. The MD-SBC1 features 8K x 8 EPROM; 2K x 8 RAM; two 8-bit input ports; three 8-bit output ports; two interrupt inputs; and single +5 Volt power supply.

For more information, call or write Mostek, 1215 W. Crosby Rd., Carrollton, TX 75006; phone 214/242-0444. In Europe, contact Mostek Brussels; phone (32) 02/660.25.68.

CIRCLE 10 ON INQUIRY CARD

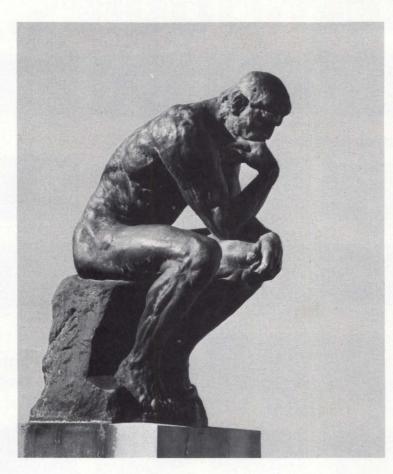

# Think fast! Which microcomputer does Mostek make?

Single-chip microcomputer

**Z80 Combo Chip**

Single-chip microcomputer

**SD** Series

Z80 Central Processing Unit

Single-chip microcomputer

AID-80F software

Mostek makes all these microcomputers. Surprised? The fact is Mostek has the capability and support to solve almost all your microcomputer design needs.

That means you can get components, microcomputer boards, and complete development systems — whatever it takes to develop your design idea.

All from Mostek. The company that's engineered some of the most exciting products around.

Like the industry-leading 3870 family of single-chip microcomputers. Or the new Combo™ Chip which gives you Z80 power with fewer components. And Mostek's latest introduction, the MD Series™, is a unique Z80-based family of modular microcomputer boards.

Plus you only need one development system, Mostek's AID-80F™, to develop and debug software for Mostek's entire product line. BASIC and FORTRAN are also available for use on the AID-80F.

Mostek's commitment to microcomputers goes far beyond products. There are also field application engineers, factory support, complete documentation, and much more.

So when you're designing with microcomputers, call or write the microcomputer company: Mostek, 1215 W. Crosby Rd., Carrollton, TX 75006; phone 214/242-0444. In Europe, contact Mostek Brussels; phone (32) 02/660.25.68.

CIRCLE IT ON INQUIRY CARD

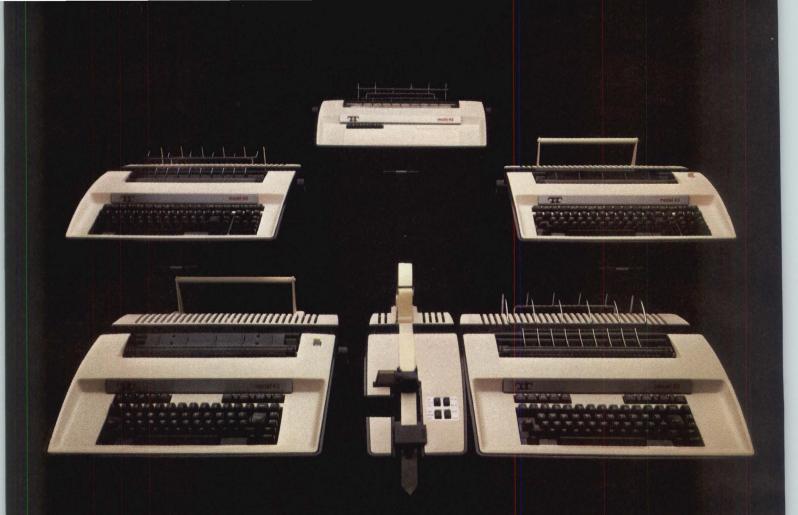

# OUR MODEL 43 TELEPRINTER FAMILY IS THE BEGINNING OF A NEW LEGEND.

When we introduced it just a year ago, the basic idea behind the Teletype\* model 43 proved so sound and flexible that today it's grown into a comprehensive terminal family with extensive capabilities for message communications.

Model 43's come in a variety of configurations with either 80 column friction-feed or 132 column pin-feed printers. Some units are designed for use on the switched network, others for pointto-point private-line systems. (There's also a new generation of 5-level buffered teleprinters for Telex applications.)

The basic model 43 series operates on-line at 10 or 30 cps in either the half- or full-duplex mode and prints multiple copies using the 96 character ASCII code set. A wide choice of interfaces, including EIA RS232C and DC 20-60ma, are available for easy system integration.

With the automatic send-receive configuration, messages can be prepared off-line via the paper tape punch, edited, combined with a master tape, then sent at maximum terminal speed—automatically and unattended—when line rates are lowest.

Buffered 43's operate on-line at speeds ranging from 10 to 180 cps and provide up to 20,000 characters of storage for sending, receiving and editing. These terminals send and receive automatically via the buffer while messages are simultaneously being prepared for future transmission. They also include full forms control, the automatic answer capability and answer back.

Just like its predecessor, the legendary model 33, our model 43 family is designed for extreme reliability. The reason is simple: simplicity. Our model 43's use only five major pluggable components (six, counting the paper tape module on the ASR), along with extensive use of LSI circuitry.

So when you think of our model 43 family, think of it as the beginning of a new legend.

# THE TELETYPE MODEL 43 FAMILY.

Teletype Corporation, 5555 Touhy Avenue, Dept. 3185, Skokie, IL 60076. Tel. (312) 982-2000. \*Teletype is a trademark and service mark of the Teletype Corporation. First of these concerns is that many of the basic legal precedents that have been achieved during the years since the Carterfone decision will be abandoned. There is no provision in the proposed legislation that assures that the principles of these past decisions, as adopted by the FCC or decreed by the courts, will continue to be recognized as being valid. There is a provision that all orders, rules, regulations, and grants of the present FCC that are not contrary to the proposed law would remain in effect until modified or repealed by the new Commission. The concern of this minimal assurance is that many settled principles could all be reopened to challenge, debate and redecision by the Commission.

A second concern is that the proposed legislation does not define clearly which telecommunications services or facilities are interstate and intrastate. The Act does state that the Commission has no authority "with respect to any intrastate telecommunications facility, or the provision of any service through the use of such facility." Without an interstate/intrastate definition, the above excerpt from the language of the proposed Act is subject to wide interpretation. The Act totally fails to address or resolve the question of predominate jurisdiction if a telecommunications facility is used for both interstate and intrastate telecommunications services. After many long judicial actions, such as in the North Carolina Utilities Commission vs FCC Decision of 1977, this jurisdictional question was finally resolved. The proposed legislation inadvertently reopens the question in an atmosphere of what appears to be more stringent language prohibiting the exercise of federal authority. While there are emphatic definitions of competitive standards, the Commission and any judicial decisions may be precluded if the telecommunications facilities or services are defined as under exclusive state authority. It is an expressed concern that customer-provided telecommunications equipment is not defined as interstate or intrastate within the language of the new bill. If it is interstate it may be classified as competitive or regulated by the Commission. If it is intrastate, each one of the 50 state public utilities commissions or equivalent agencies will decree the future viability of customerowned telecommunications equipment within that state.

A third weakness identified in the proposed legislation is the absence of any provision for the enforcement of antitrust laws. Current decisions of the u.s. Supreme Court indicate a probability that the competitive standards contained in the Act may be accepted as substitutes for the antitrust laws. As such, the communications common carriers will be provided with implied immunity from liability under the antitrust laws. It may be properly suggested that the provisions of the bill attempt to preempt the antitrust laws with the proposed regulation.

Specifically, AT&T would be released from the constraints of its 1956 Consent Decree. It would permit communications common carriers to establish separate companies to provide telecommunications services and equipment incidental to telecommunications. AT&T and its operating companies would be free to enter into the computer and data processing equipment and service industries. These events would result in new organizations that would be easily capable of overshadowing presently established entities in those industries. The actual language of the bill with respect to this capability states that 'notwithstanding any other provision of law, or any judicial determination or decree, any carrier can hold shares in, or acquire separate companies to engage in activities, provide services, or offer products which are in telecommunications or incidental to telecommunications."

It is expected that the separate corporation concept will automatically prevent cross-subsidization even though other provisions provide clear opportunities for predatory pricing. The Act appears to substitute the new Commission's authority for the Sherman and Clayton Acts as well as for federal government antitrust action as the determinant whether an activity, service or product constitutes telecommunications or is incidental to telecommunications.

It seems, therefore, that the proposed legislation is an attempt to respond to the growing competitive trend in the various telecommunications service and product industries. At present these emerging marketplaces are being constrained by traditional regulation provisions and requirements. The proposed Communications Act of 1978, however, appears to represent a swing to the other extreme of the regulation spectrum. If all participants could be expected to respond in an objective manner, with the common good as the accepted goal, such broad and almost trusting provisions would be feasible. In view of the realities, and of recent history in this arena, however, a more definitive and hence restrictive legislative posture is warranted. Existing giants in this telecommunications industry must be restrained and channeled through decreasing regulation until the many embryonic entities have been established as viable competitive factors in this marketplace.

During August and September 1978, the House of Representatives' Subcommittee on Communications held a series of hearings on the Communications Act of 1978 (H.R. 13015). A new draft of the legislation should be expected during the fourth quarter of calendar 1978. It is important that all members of the telecommunications industry take an active and visible role in the shaping of this legislation. It will determine the nature of the telecommunications industry in this country for the rest of this century and well into the next.

# Experimental Integrated Optical Device Promises Variety of Applications

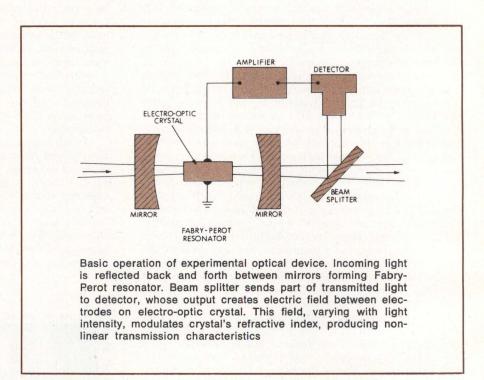

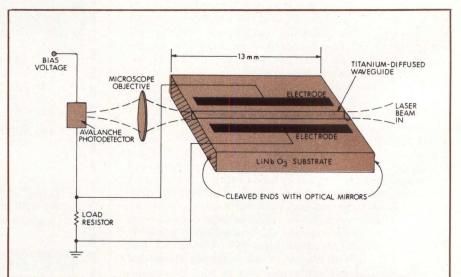

Many signal processing applications in future lightwave communications and data processing systems may be served by an integrated optical device recently devised by scientists at Bell Laboratories, Murray Hill, NJ 07974. Its properties suggest use as a logic element in optical memories, a pulse shaper and limiter, an optical switch, a differential amplifier, and an "optical triode." It operates over a broad band of wavelengths at very low optical power, requiring only 1 pJ of light energy for the switching function.

Nonlinearity is produced in the device, an optical waveguide version of a nonlinear Fabry-Perot resonator, by using the output of a photodetector, which samples the transmitted light, to drive an electro-optic lithium niobate (LiNb) element in the resonator. The unit's versatility is due to several properties: it accepts electrical or optical inputs; its nonlinearity may be modified using a nonlinear circuit; it can accept multiple inputs for optical logic operations such as AND OF OR gates; and it enables multilevel operation, allowing more complex optical logic functions and A-D conversion of optical signals. It is exexpected that in the near future the electro-optic element can be driven with as little as 0.1 V, easily obtainable from a photovoltaic device without the need for amplification or for bias voltage.

Several modes of operation are possible with the device. The resonator can be tuned to produce an "S" shaped transmission characteristic, or one exhibiting optical hysteresis. Depending on the resonator tuning and the amount of feedback, the device can then be made to function as an optical memory element, complex logic element, optical limiter or optical triode.

For complex multilevel logic operations, or A-D conversion of optical signals, high gain is required in the feedback loop. In this configuration, as many as 15 equally spaced levels of transmission are possible.

With less feedback and with the resonator tuned for transmission characterized by optical hysteresis, the device can function as a memory element. In this mode, switching between the two stable states—high transmission or low transmission—is accomplished either by an input light beam, or by applying an electrical pulse directly to the modulator electrodes.

After switching to the high transmission state, the output power remains almost constant over a wide range of input powers. In this mode, the device functions as an optical limiter. Output power rises steeply

Integrated version. Device is fabricated using standard IC processing techniques. Titanium ions are diffused into electro-optic substrate of lithium niobate material to form 4- $\mu$ m wide optical waveguide. Fabry-Perot resonator is formed with dielectric mirrors expoxied onto cleaved ends of substrate material

# Double Density Floppies for your LSI-11/2

CRDS continues its spectacular performance in the field of Peripheral Controller Design. Designing control/interface electronics onto a single Dual Height Card and with:

- Single and Double-Density Operation

- Complete Instruction Set

- Compatibility with RX02

- Integral Bootstrap Loader

- Built-In Self Diagnostic, Formatter

- Dual Height Controller for LSI-11 or LSI-11/2 Backplane

- 51/4" Low Profile Chassis

- Dual Shugart Drives

- 512K Bytes Per Drive

- Front Panel Write Protect Switches

- Photocell Write Protect

- Complete Instruction Manual

### FD-211 Dual Floppy System

# The FD-211 Dual Floppy System is the perfect plug replacement for your RX02...in half the space...and at up to 30% savings.

## MF-211 Dual Floppy/LSI-11/2 System

Our MF-211 Dual Floppy/LSI-11/2 System, using the CRDS Double-Density Controller is functionally identical to the DEC PDP-11V03-L, however using only 10½" rack space. The MF-211 is the perfect low-cost answer to your PDP-11V03-L requirement.

#### **Check These Features:**

- Single and Double-Density Operation

- Complete RX02 Instruction Set Compatibility

- Over One Megabyte Storage Per System

- Functionally identical to the DEC PDP-11V03-L

- 10½" Rack Mountable Enclosure

- Available with DEC Software and Interface Cards

- 30K Addressable Memory

- Considerable Dollar Savings

For more information on our FD-211 and/or MF-211 Double-Density Floppy Disk Systems, just get in touch. Our Data Sheet and Pricing will be on its way.

## Charles River Data Systems, Inc.,

4 Tech Circle, Natick, Massachusetts 01760 Tel. 617 655-1800

#### CIRCLE 14 ON INQUIRY CARD

COMMUNICATION CHANNEL

to a maximum point and then levels out, with little increase in output power as the input power is increased. Output power varies less than 4% for a 15:1 variation in input power.

As an optical triode, the resonator is tuned to produce the "S" type transmission characteristic, and optical power transmitted through the waveguide changes rapidly as a function of incident light. This means that a small additional light signal at the detector produces a large change in transmitted light power. In an experiment with a low level control light beam, a sevenfold gain was measured.

Researchers at the laboratories are looking to longer wavelength light to eliminate unwanted refractive index changes due to photorefractive effects in the LiNb. They expect the fully integrated version to operate with a response time of several ns, and to switch with only a few picojoules of optical energy.

# Nationwide Network Service Available for 1200-Bit/s Data Terminals

Nationwide packet network data communications service for terminals operating at 1200 bits/s is being provided by Telenet Communications Corp, 8330 Old Courthouse Rd, Vienna, vA 22180. The expanded public dial-in facilities support the new Bell 212 and Vadic 3400 fullduplex modems, and is available locally in selected major cities, as well as nationally through a central wATS number.

Cities in which public 1200-bit/s service is available include Atlanta, Boston, Chicago, Dallas, Detroit, Honolulu, Houston, Los Angeles, Newark, New York, Philadelphia, San Francisco, and Washington. According to the company, expansion of the service is due to a survey among the more than 225 organizations using the network for computer communications. Results showed a growing preference for the 1200-bit/s rate because of higher throughput and lower costs compared with lower speed terminals, both for data processing and communications.

# Laboratory Lasers/LEDs Show High Performance As Optical Transmitters

In the laboratories of Siemens AG, Postfach 103, D-8000 Munich 1, Federal Republic of Germany, both semiconductor lasers and light-emitting diodes (LEDS) have been developed for use as optical transmitters over optical fiber transmission lines. In this application adequate optical power, long service life, and only slight variation of optical parameters are essential properties.

The researchers have found that semiconductor lasers have two basic advantages: they launch a larger optical power into the fiber, and can be modulated with higher frequencies. This only holds true, however, if the lasers are designed as optical semiconductor resonators, so that only the fundamental mode is excited. Stripegeometry lasers with narrow stripe width fulfill this requirement. At stripe widths of 6  $\mu$ m, the research laboratory devices provide cw optical output powers of 6 mW.

With LEDS, an optical power of 4 mW at diode current of 100 mA has thus far been achieved. Emission wavelengths of between 800 and 900 nm can be realized by selection of a suitable crystal composition.

The stripe-geometry lasers are GaAs/GaA1As double heterostructure laser diodes with stripe widths between 6 and 13  $\mu$ m. They have alu-

See page 81

mina anti-reflection coatings that permit a high mirror load of 1-mW optical output power per  $1-\mu m$  stripe width.

On selected samples, threshold current rose by only 3% in the course of 1000 h at 80 °C amb temp. Extrapolation of these data shows that at room temp, such diodes should expect a service life of 100,000 h. This calculation is based on an activating energy of 0.7 eV and a 10% max permitted threshold current rise. How much the other operating parameters will change over such a period remains to be seen.

In early experimental applications a laboratory PCM transmission system showed a pulse amplitude variation of only  $\pm 3\%$  at a transmission rate of 560M bits/s, and at the Heinrich Herz Institute for Telecommunications in Berlin, the diodes displayed good modulation performance at 1.2G bits/s.

Circle 400 on Inquiry Card

# Modules Offer Interactive Communications for Distributed Systems

3270 display station emulator, intelligent 3270 network interface, and 3270 batch utilities package, allow users of System 21 family of distributed data processing systems choice between designing applications for interactive inquiry into a remote host system, batch transmission to the host, or a combination of local processing with interactive inquiry against local or remote files. With the new capabilities, asynchronous communications are enabled on all three series 21 models, while the 21/40 or 21/50 can also emulate terminals in the IBM 3270 family, according to Mohawk Data Sciences Corp, 1599 Littleton Rd, Parsippany, NJ 07054.

Basic asynchronous emulator, available first quarter 1979, allows operator stations to function as nonintelligent conversational terminals, transmitting data to or receiving data from a mainframe char at a time or in batch mode via diskette or disc. An enhanced version of the emulator, (initial delivery third quarter 1979) adds data formatting, operator prompting, and variety of CRT display functions, supported by MOBOL (Mohawk Business-Oriented Language) routines. MOBOL programs can interact with host processor programs for direct data input and information retrieval. Batch utilities package, also available in third guarter 1979, allows system users to transmit data to host via 3270 protocol with minimum operator intervention. Circle 401 on Inquiry Card

# **Concerto in A Flat Mini.**

Victor Borge demands the world's finest piano for his concert work. And when he performs at the computer keyboard, he naturally expects the best. The quality mini recording media. That's why he specifies Verbatim. At Information Terminals Corp. the whole message is quality. Our Verbatim brand diskettes, cartridges and cassettes capture your data and play it back bit for bit, byte for byte, verbatim.

Quality mini media is all we make. When you want to be sure *your* data will play, specify Verbatim.

Information Terminals Corp., 323 Soquel Way, Sunnyvale, CA 94086

(408) 245-4400. TWX: 910-339-9381. For the name of your nearest

Verbatim distributor, call toll free: (1) 800-821-7700, Ext. 515. (In Missouri call: 800-892-7655,Ext. 515)

CIRCLE 15 ON INQUIRY CARD

In Europe: Information Terminals S.A. Case Postale 296 1215 Genève 15 Switzerland Telephone: 41 (22) 34-90-55 Telex: 22647 ITGE CH In the Far East: ITC – Far East 404 Roppongi Skyheights 3-2-21 Roppongi, Minatoku Tokyo, Japan Telephone: (03) 583-1981 Telex: J 47879

///////

1111111

1111111

1111111

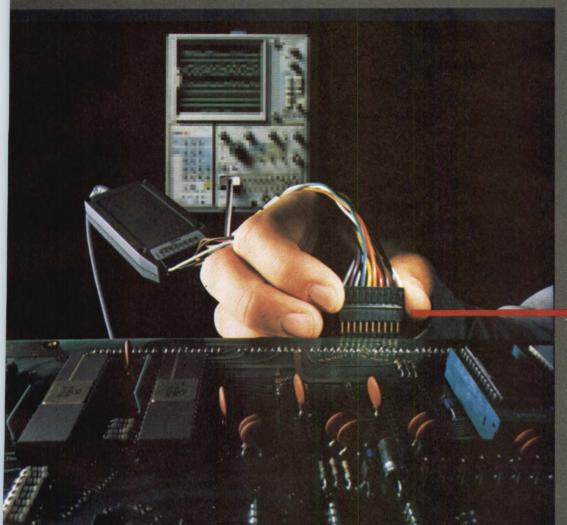

# Ever try to find a once-a-week glitch among half a million operations per second?

# We have. So our microprocessor system offers real time trace. To spot problems as they happen.

Tektronix microprocessor labs can cut your time to market by letting engineers and software designers work together throughout development.

# WE'VE GOT DEBUGGING DOWN TO A SYSTEM.

Everyone offers some kind of in-prototype testing. But our unique array of features can cut debugging time by 50 percent or more

Most significant is our lab's Real Time Prototype Analysis option: with two fully independent 48-bit breakpoint registers that let

you get software timing down to prototype clock cycle resolution. Plus pre-, post-, and center triggering. Our engineers say it saves them time in all stages of integration.

## **MORE OF THE BEST**

When you see all the debugging features available to you, you understand why our labs have been so enthusiastically adopted by engineers and software designers.

## **DISC BASED SYSTEM**

Text editor, macro relocatable assembler, file management utilities and powerful debugging software keep you moving through test and integration.

## **DUAL ARCHITECTURE**

Separate system and application memories, and processors, allow more

Tektronix microprocessor development labs. Designed by

people on your side of the bench.

program workspace and realistic emulation, while making the system virtually uncrashable. And you get versatile testing with 128byte block mapping.

# DISASSEMBLY

When the lab displays instruction data in debug mode, you receive it in easy-to-read assembler mnemonics. You never get bogged down translating machine code.

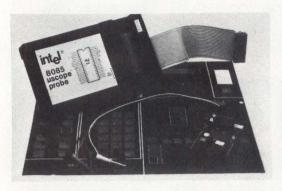

# MULTIPLE MICROPROCESSOR EMULATION

Our design aids are the first to actually emulate, not just simulate, a variety of major chips: The 8085 and 8080. The Z80. The 6800. The TMS 9900. And others to come.

Let us show you the kind of development system you'd probably engineer for yourself. Contact Tektronix Inc., P.O. Box 500, Beaverton, OR, (503) 644-0161. In Europe, Tektronix, Ltd., P.O. Box 36, St. Peter Port, Guernsey, Channel Islands.

For literature please circle # 16 For demonstration please circle # 17

For fast reply, call (800) 547-1512 (in Oregon, collect 694-9051)

# Introducing the New Billings Microsystem.

### FEATURES

MEMORY — 64K bytes RAM standard DISK — Dual mini Floppy (160 bytes, built-in) SCREEN — Twenty-five lines, 80 characters each PROTECTED Fields — Two-thirds intensity GRAPHICS — A 32-key line drawing set MICROPROCESSOR — Z-80

Including micro printer and software (Extended Basic, Fortran and Cobol Limited Time Offer

# SPECIFICATIONS

12"

CLOCK — 4 MHz POWER — 115 volts at 60 Hz CABINET — Molded structural foam CURSOR — Variable size and blink rate PORTS — Two serial RS-232 (110 to 9600 baud) Eight-bit parallel printer port KEY BOARD — 94 keys (upper and lower case), including 16 special function keys and numeric pad

Billings Computer Corporation P.O. Box 555 Provo, Utah 84601 (801) 375-0000

# Billings Microsystem Order Form

#### **Dealer Inquiries Welcome**

## **Special Introductory Offer**

Cilino) mi

Software included at no extra charge if you use this coupon in placing your order for one or more Billings Microsystem computers. Software includes Extended Basic, Fortran and Cobol.

| Name                 |           |

|----------------------|-----------|

| Title                | Phone ( ) |

| Firm                 | Dept      |

| Address              |           |

| Authorized Signature |           |

| - | croome                                                                                     | Screen           | Screen   |

|---|--------------------------------------------------------------------------------------------|------------------|----------|

|   | CPU with 64K RAM, terminal,<br>dual mini Floppy disk drives<br>(160K bytes), micro printer | (pictured above) | □ \$4095 |

|   | CPU with 64K RAM and terminal                                                              |                  | □ \$3095 |

| - | OF O WITH OAK HAW and terminal                                                             | 0.02333          | L \$2032 |

|   | CPU with 64K RAM, terminal,                                                                |                  |          |

|   | dual mini Floppy disk drives (160                                                          | K) 🗆 \$3545      | □ \$3645 |

|   | Standard Printer, \$1195                                                                   |                  |          |

|   | Payment Included D Ship C.O.I                                                              | D.               |          |

|   | Please send additional informat                                                            |                  |          |

|   | on the new Billings Microsystem                                                            |                  |          |

|   | Please send information on the                                                             |                  |          |

|   | Billings family of mini computer                                                           | systems.         |          |

|   | Please send dealer information.                                                            |                  |          |

# DIGITAL TECHNOLOGY REVIEW

# Bubble Domain Memory Devices and Subsystems Based on 256k-Bit Chip

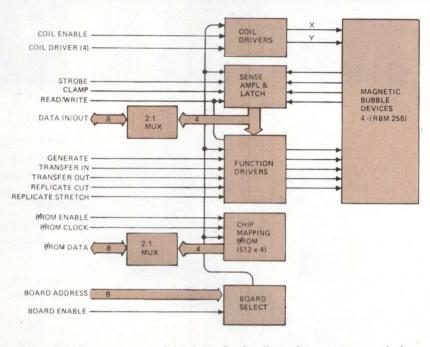

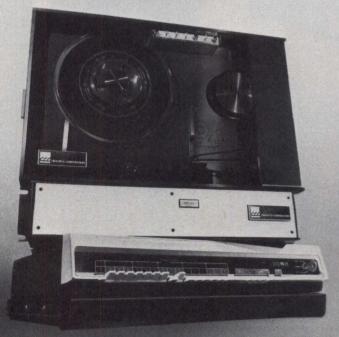

RBM256, a mass-produced binary organized device capable of storing 256k bits of data, is the basis of bubble memory devices and subsystems introduced by Rockwell International, Electronic Devices Div, 3310 Miraloma Ave, Anaheim, cA 92803. RLM658, a linear module, contains four RBM256 devices, thus forming a 1M-bit system on a board. Programmable control module RCM650 controls from 1 to 16 of the linear modules and enables storage capacities of from 128k to 2M bytes. Also available is a development system made up of two linear modules, a programmable control module, and a System 65.

Composed of 282 loops, each containing 1025 bubble positions, the RBM256 operates with a 260-bit data block, thus using only 260 of the available 282 loops. Binary data are stored in 256 loops and the remaining four hold system housekeeping bits. In a typical application where eight RBM256 devices are used in parallel, extra bits may be used to provide a 16-bit block address header and a 16-bit CRCC word suffix. The device transfers data at 150 kHz, taking less

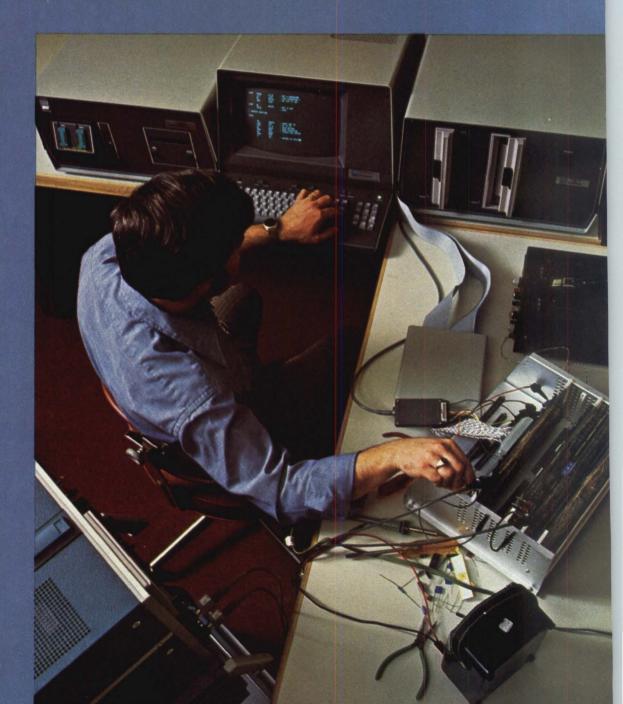

Linear bubble memory module from Rockwell packages storage devices with sense channels, coil drivers, and operator logic needed for support. Chip mapping P/ROM retains good/bad loop maps, used by system controller to skew and deskew block data streams

# Who do you think of for high-performance 16K RAMs?

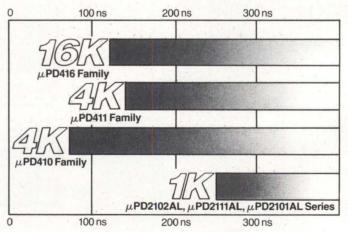

Take your pick: our  $\mu$ PD416 standard family offers a whole range of performance choices—extending to 120 ns access time and 320 ns cycle time. In either plastic or ceramic packages. Every characteristic of our  $\mu$ PD416 family meets or exceeds industry standards, which means our parts are suitable for any application

you can

name. And we've been shipping in volume since August, 1977, so you know we can deliver parts when you need them.

| P/N      | <sup>t</sup> RAC | <sup>t</sup> RC | I <sub>DD1</sub> | I <sub>DD2</sub> |

|----------|------------------|-----------------|------------------|------------------|

| μPD416-5 | 120 ns           | 320 ns          | 35 mA            | 1.5 mA           |

| µPD416-3 | 150 ns           | 375 ns          | 35 mA            | 1.5 mA           |

| µPD416-2 | 200 ns           | 375 ns          | 35 mA            | 1.5 mA           |

| µPD416-1 | 250 ns           | 430 ns          | 35 mA            | 1.5 mA           |

| μPD416   | 300 ns           | 510 ns          | 35 mA            | 1.5 mA           |

Of course, 16K RAMs are just part of our story. We also have a broad selection of other memory components, led by our industry standard

REPS: Action Unlimited, Arlington, TX; Spring, TX. Burton-Medley Associates, Grandview, MO. Cerco, San Diego, CA. Contact Sales, Inc. Burlington, MA. D/Z Associates, Inc., Denver, CO. Electronic Innovators, Inc., Minneapolis, MN. Eltron, Phoenix, AZ. HLM Assoc., Northport, NY; Parsippany, NJ. Imtech, Inc., Cleveland, OH; Dayton, OH. Kaytronics Limited, Ville St. Pierre, Quebec; Downsview, Ontario; Surrey, British Columbia. L & M Associates, Pikesville, MD; Montpelier, VA. Harry Nash Associates, Willow Grove, PA. R.C. Nordstrom & Company, Lathrup Village, MI. Perrott Associates, Inc., Fort Lauderdale, FL; Clearwater, FL; Orlando, FL. Santana Sales, Costa Mesa, CA. Stone Component Sales, Waltham, MA. Technology Sales, Inc., Palatine, IL. Trident Associates, Inc., Sunnyvale, CA. Tri-Tronix, Albuquerque, NM. Tri-Tronix, NW., Mercer Island, WA. 20th Century Marketing, Inc., Huntsville, AL; Greenville, TN. Wolff's Sales Service Company, Raleigh, NC. DISTRIBUTORS: Almo Electronics, South Euclid, OH. Diplomat/Westland, Inc., Sunnyvale, CA. Diplomat/Southland, Inc., Clearwater, FL. Diplomat/Lakeland, Inc., Elk Grove Village, IL. Diplomat/IPC of Mass., Chicopee Falls, MA. Diplomat, Holliston, MA. Diplomat/Northland, Inc., Farmington, MI. Diplomat/Electro-Com

4K Dynamic RAM ( $\mu$ PD411), with access time down to 135 ns, and our highly successful high-speed 4K Static RAM (µPD410), with access times down to 70 ns. Plus CMOS RAMs, Bipolar PROMs, 1K and 4K Static RAMs, and mask programmable ROMs up to 64K bits.

At NEC, we've built a reputation for advanced technology and volume delivery. We're also known for remarkable product reliability-thanks to experienced designers and meticulous manufacturing techniques, backed by 100% burn-in and testing with MIL-STD-883 methods. The result is an overall rejection rate of under 0.5%.

What's more, we offer thorough customer support, including documentation, testing, and special selection. And our engineers are always available to help with specific applications problems.

Our new product catalog will give you a better idea of just how much we can do for vou, not only in memories but also in 8-bit and 4-bit processors and peripherals.

To get your free copy, clip your business card or letterhead stationery to this page and send to: NEC Microcomputers, Inc., 173 Worcester Street, Wellesley, MA 02181.

If you haven't thought of NEC before, you will. Next time.

NEC **NEC Microcomputers, Inc.**

Corp., Minneapolis, MN. Diplomat/St. Louis, Inc., St. Louis, MO. Diplomat/IPC Corp., Totowa, NJ; Mt. Laurel, NJ. Diplomat Electronics Corp., Woodbury, NY. Diplomat/Alta-Land, Inc., Salt Lake City, UT. Future Electronics Corp., Montreal, Quebec; Rexdale, Ontario; Ottawa, Ontario. Hughes-Peters, Inc., Cincinnati, OH; Co-lumbus, OH. Intermark Electronics, Sunnyvale, CA; Santa Ana, CA; San Diego, CA. Kent Electronics, Houston, TX. G.S. Marshall, Sunnyvale, CA; Irvine, CA; El Monte, CA; San Diego, CA; Phoenix, AZ. Milgray Electronics, Inc., Freeport, NY; Orange, CT. Reptron Electronics, Inc., Livonia, MI. Resco/Raleigh, RO. Semiconduc-tor Specialists, Inc., Chicago, IL; Burlington, MA; Farmington, MI; Minneapolis, MN; Hazelwood, MO; Pitsburgh, PA; Dallas, TX; Milwakee, WI. Sterling Electronics, Inc., Phoenix, AZ; Sun Valley, CA; San Diego, CA; Baton Rouge, LA; Waltham, MA; Albuquerque, NM; Dallas, TX; Houston, TX; Seattle, WA. Summit Distributors, Inc., Buf-falo, NY. Summit Elec. of Roch., Inc., Rochester, NY. Technico, Inc., Columbia, MD; Roanoke, VA. Western Microtechnology Sales, Sunnyvale, CA. REGIONAL SALES OFFICES: Western Region, NEC Microcomputers, Orange, CA (714) 633-2980. Eastern Region, NEC Microcomputers, Melville, NY (516) 293-5660

CD-2-1

than 4 ms to access the first bit of a block. Throughput is preserved during read operations with the device's replicate/read block architecture in which bubbles read at the detectors are actually duplicates of the loop-resident bubbles.

Packaged in an 18-pin, molded plastic DIP, the RBM256 occupies only  $1.2 \ge 1.2"$  (3.05  $\ge 3.05$  cm). It consumes 820 mW of power, and offers -10 to 70 °C case temperature operation.

A prepackaged linear module that provides 1M bits of storage using four parallel RBM256 devices, the RLM658 operates at 100k bytes/s and, when used in conjunction with an appropriate controller, is compatible with the company's System 65 and many 6800 microcomputer development systems. The RLM658 is designed to be used in combinations of two to 16 modules in a byte oriented system environment, providing from 256k to 2M bytes of storage.

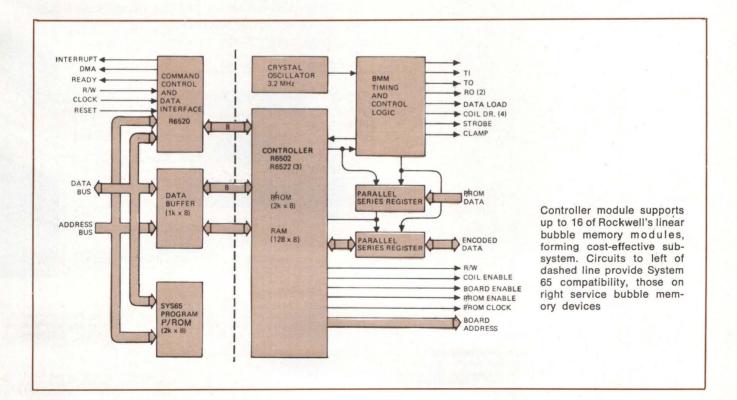

To implement a bubble memory subsystem based on linear bubble memory modules, controller circuitry is required. The RCM650 complements the 1M-byte RLM658 linear module in System 65 applications, providing byte-parallel operation in 256-byte blocks. It is totally software compatible with System 65 and the 6502 microprocessor, and can control from 1 to 16 RLM658 modules.

The RCM650 bubble memory controller and the RLM658 linear module are designed to form a cost-effective subsystem. The RCM650 controller supports up to 16 RLM658 modules, allowing system capacity to be expanded up to 2M bytes.

A 256k-byte bubble memory subsystem option (one RCM650 controller and two RLM658 linear storage modules) installed in a System 65 microcomputer development system, allows users to begin developing applications for the bubble memory devices. A powerful microcomputer development system based on the R6502 CPU, it comes standard with two minifloppy disc drives and 16k bytes of static RAM (both totally user-dedicated), plus ROM-resident debug, monitor, symbolic text editor, and 2-pass assembler programs. It includes vacant slots for adding additional memory and 1/0 modules; an auxiliary card cage permits expansion to the full 2M-byte bubble memory subsystem capability.

Low quantity price for the 256k-bit device is \$500 each; linear module is priced at \$2500; and programmable control module at \$1000. Development system cost is \$11,400. Delivery is said to be 60 to 90 days. Circle 180 on Inquiry Card

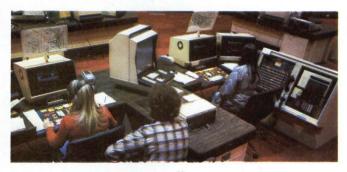

Biomation's K100-D logic analyzer provides access to its microprocessor based control subsystem through front panel keyboard and four front panel switches. Menu displayed on integral CRT eases user comprehension of unit's functional capabilities

number of functions per key and a related display menu that speeds the user's comprehension of its function capabilities, the keyboard permits the user to move rapidly into full utilization of the unit's performance characteristics.

The unit's memory is 16 bits wide by 1024 words long, and data clocking into memory can be achieved at rates up to 100 MHz (giving 10-ns time resolution) by way of the internal clock. When an external qualified clock is used, information is clocked at up to 50 MHz. These clock rates make the instrument adequate not only for TTL and ECL circuits, but also provide better timing resolution for measuring critical operating parameters of current and future microprocessors. In addition, with the appropriate accessory, the analyzer can synchronously record from 32 channels without compromising basic performance. The full 16-channel, 100-MHz capability can be used by merely interchanging the 32-channel adapter with the high performance probes.

To reduce the difficulties encountered with reflections and ringing, changing input capacitance, and crosstalk when attempting to get input signals down to 10 ns, probes for use on the K100-D combine features of active pod and individual probes rather than using active probe pods on a multiconductor cable. This approach processes signals close to the user's circuitry to preserve the signals' information content. The probe's hybrid circuit provides buffering for a 1-M $\Omega$  input impedance, and threshold detection right at the probe tip. The probe assembly is made up of groups of 10 probes each, all terminated in a common conductor. Plugging in two 10-probe connectors joins 20 probes to the instrument. With individual active probes it adds ability to probe physically distant circuit points.

High performance is augmented by a versatile control subsystem that allows the designer to easily set and access all recording and display parameters. To initiate a recording sequence, the status display is consulted on the CRT screen. Access to a particular field is gained by pressing the corresponding key, then entering the desired parameter. Various decisions can be made about clocking, delay sequence, logic polarity, 2-level trigger, threshold, input mode, arm mode, and trigger. Because there are buttons on each parameter field, parameters can be selected in any sequence desired.

All recording sequences can be monitored, and information analyzed, by way of a comprehensive set of display prompters. There are four separate display modes for data domain, and a timing domain display. All 16 channels of data can be viewed simultaneously. Data domain outputs can be presented in binary, hexadeci-

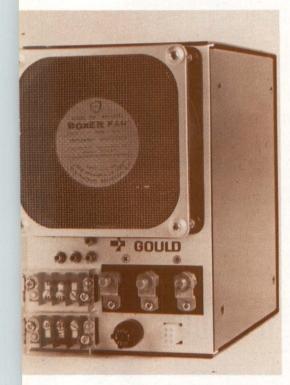

# Logic Analyzer Solves Problems of High Speed Logic Circuit Probing

Matching high performance timing mode analysis with a comprehensive set of display and decoding capabilities for data domain analysis, the K100-D is claimed to set a standard for troubleshooting at the digital design level. Integrated in the 100-MHz, 16-input channel logic analyzer developed by the Biomation Div of Gould Inc, 4600 Old Ironsides Dr, Santa Clara, cA 95050 are a microprocessor (Mc6800) controlled subsystem, CRT display, and full user oriented keyboard for specifying complicated triggering and recording sequences.

Access to the control subsystem is via the front panel keyboard and four front panel switches. Input is via probe sets that feature two 10-input connections at the instrument, and custom hybrid circuits for each active probe. Designed with a limited

# SURPRISE!

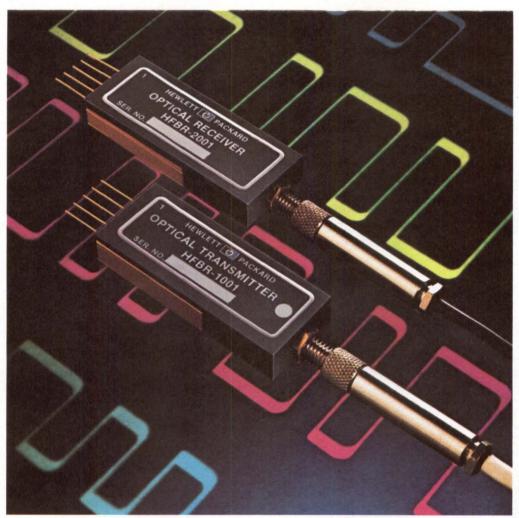

# The Data Link of the future is available from HP today.

HP's new Fiber Optic System guarantees error free ( $P_e < 10^{-9}$ ) data transmission from DC to 10Mb/s NRZ over distances up to 100 metres. This system is immune to electromagnetic interference, radiates no external signal and provides total electrical isolation between terminals.

TTL compatible, our system includes a PC board mountable transmitter and receiver which operate from a single 5V power supply. Our low loss, single fiber connector/cable assemblies are available

in five standard lengths from 10 to 100 metres.

Applications include large computer installations, distributed processing, power plants, process controls and remote instrumentation.

Prices start at \$570 for the HFBR-0010, 10 Metre System. For more information or immediate off-the-shelf delivery, call any franchised

HP distributor. In the U.S. contact Hall-Mark, Hamilton/Avnet, Pioneer Standard, Schweber, Wilshire or the Wyle Distribution Group

(Liberty/Elmar). In Canada, call Hamilton/Avnet or Zentronics, Ltd.

\*U.S. Domestic Price Only

01806

1507 Page Mill Road, Palo Alto, California 94304 For assistance call: Washington (301) 948-6370, Chicago (312) 255-9800, Atlanta (404) 955-1500, Los Angeles (213) 977-1282

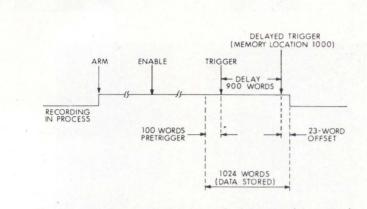

Three events in sequence are required to complete recording using K100-D logic analyzer. Arm initiates storage of data into memory; trigger controls what is stored. However, enable must be detected before trigger can be recognized. 23-word offset simplifies set up by reconciling difference between 1000 decimal and 1000 binary (1024)

mal, or octal form, as well as a special mode. In special mode, information display can be split to view, for example, 8-bit data bytes in hexadecimal, plus 8 bits in hexadecimal. Other combinations include one which decodes information in binary and ASCH code. Sequence comparison capability allows users to compare 1 word, or up to 1024 words between the two memories.

The K100-D is available on a 90day ARO schedule. Price is \$8800 including two probe sets.

Circle 181 on Inquiry Card

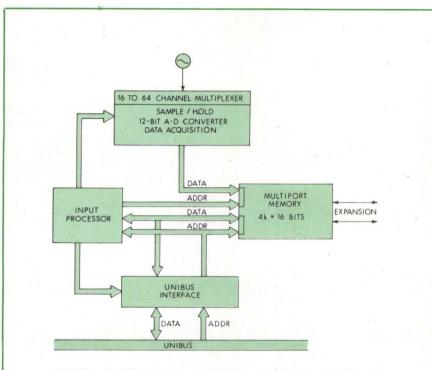

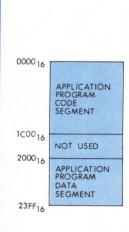

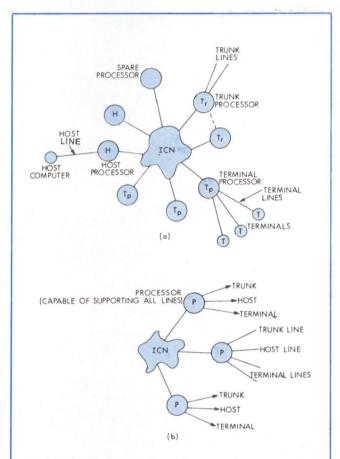

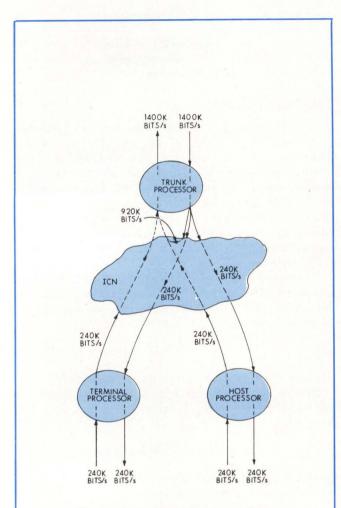

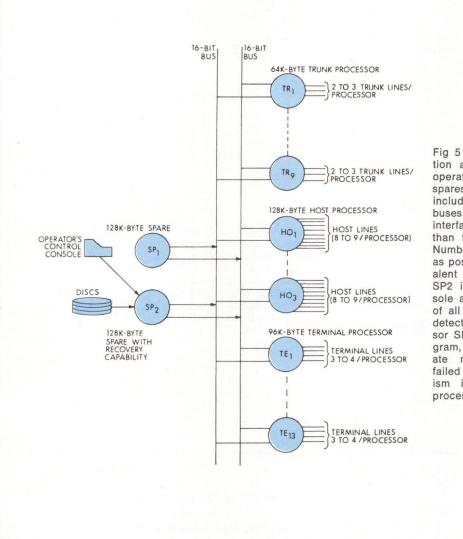

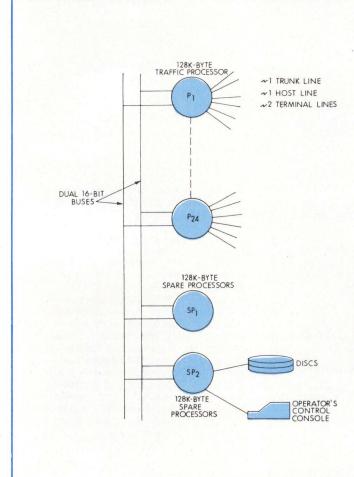

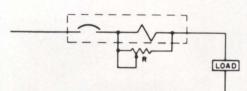

# Disc Storage System Doubles Capacity of 3350 Units