THE BELL SYSTEM echnical Journal

Volume 48

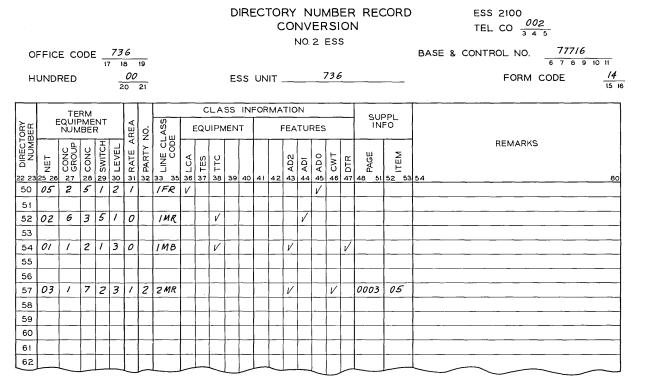

October 1969

Number 8

COPYRIGHT © 1969 AMERICAN TELEPHONE AND TELEGRAPH COMPANY

# THE BELL SYSTEM TECHNICAL JOURNAL

### ADVISORY BOARD

P. A. GORMAN, President, Western Electric Company

J. B. FISK, President, Bell Telephone Laboratories

A. S. ALSTON, Executive Vice President, American Telephone and Telegraph Company

### EDITORIAL COMMITTEE

W. E. DANIELSON, Chairman

| F. T. ANDREWS, JR. | A. E. JOEL       |

|--------------------|------------------|

| E. E. DAVID        | B. E. STRASSER   |

| W. O. FLECKENSTEIN | M. TANENBAUM     |

| W. S. HAYWARD, JR. | D.G.THOMAS       |

| C. W. HOOVER, JR.  | C. R. WILLIAMSON |

### EDITORIAL STAFF

G. E. SCHINDLER, JR., Editor

E. F. SCHWEITZER, Assistant Editor

H. M. PURVIANCE, Production and Illustrations

F. J. SCHWETJE, Circulation

THE BELL SYSTEM TECHNICAL JOURNAL is published ten times a year by the American Telephone and Telegraph Company, B. S. Gilmer, President, C. E. Wampler, Vice President and Secretary, J. J. Scanlon, Vice President and Treasurer. Checks for subscriptions should be made payable to American Telephone and Telegraph Company and should be addressed to the Treasury Department, Room 2312C, 195 Broadway, New York, N. Y. 10007. Subscriptions \$7.00 per year; single copies \$1.25 each. Foreign postage \$1.00 per year; 15 cents per copy. Printed in U.S.A.

# THE BELL SYSTEM

# TECHNICAL JOURNAL

# DEVOTED TO THE SCIENTIFIC AND ENGINEERING ASPECTS OF ELECTRICAL COMMUNICATION

| Volume 48                             | October 1969* N                                                                                   | Jumber 8                    |

|---------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------|

| Copyright                             | ©-1969, American Telephone and Telegraph Company                                                  |                             |

| System Organization                   | n and Objectives<br>A. E. Spencer and F. S. Vigilant                                              | e 2607                      |

| Control Unit System                   | n T. E. Brown<br>T. M. Quinn, W. N. Toy and J. E. Yate                                            | •                           |

| Peripheral System<br>L. I             | J. Digrindaki<br>Freimanis, H. R. Hofmann and R. G. Taylo                                         | •                           |

|                                       | d Call Processing Plan<br>R. J. Andrews, J. J. Driscol<br>Herndon, P. C. Richards and L. R. Rober | •                           |

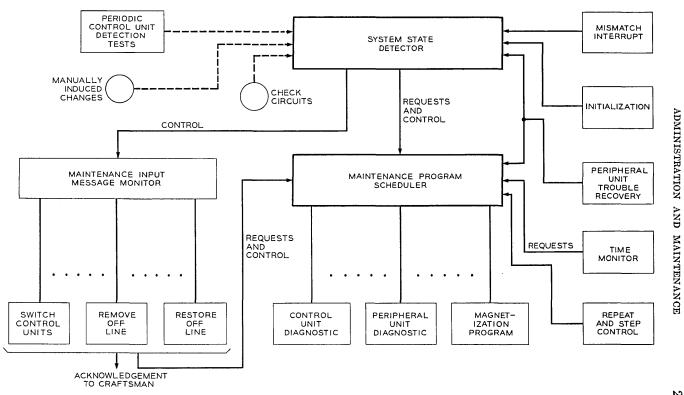

| Administration and<br>H.              | Maintenance Plan<br>J. Beuscher, G. E. Fessler, D. W. Huffman<br>P. J. Kennedy and E. Nussbau     | •                           |

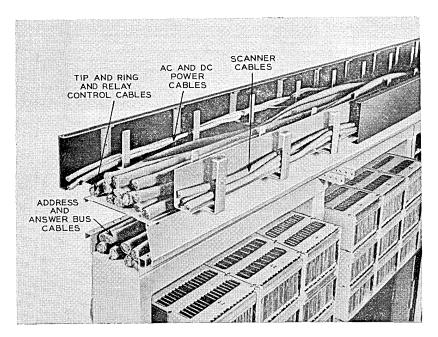

| Apparatus and Equ<br>C. W.            | ipment<br>Lonnquist, J. C. Manganello, R. S. Skinne<br>M. T. Skubiak and D. J. Wadsword           | •                           |

| Service Programs                      | M. E. Barton, N. M. Haller and G. W. Rick                                                         | er 2865                     |

| Contributors to Thi                   | is Issue                                                                                          | 2897                        |

| Index<br>* This issue of the Bell Sy. | stem Technical Journal was not published until after Octob                                        | <b>2905</b><br>er 22, 1969. |

# System Organization and Objectives

## By A. E. SPENCER and F. S. VIGILANTE

(Manuscript received February 18, 1969)

This paper describes the system organization and objectives of the No. 2 Electronic Switching System. The place of No. 2 ESS in the Bell System and the design approach used are outlined and traffic capacity estimates are discussed. This paper also serves as an introduction to the detailed set of papers which follow.

### I. INTRODUCTION

# 1.1. General

The No. 1 Electronic Switching System described by Keister, Ketchledge, and Vaughan in the September 1964 issue of the B.S.T.J. has been in commercial service since May of 1965, when the first installation was activated in Succasunna, New Jersey. Since that time, many additional installations have been made and electronic switching has been clearly established as a valuable switching medium for use in the Bell System.

The No. 1 ESS was designed for use in metropolitan areas where large numbers of lines with heavy traffic are served. Although a few installations of No. 1 ESS have been made in nonmetropolitan areas, the need within the Bell System for another system that would be economically attractive in the size range from 1000 lines to about 10,000 lines has been evident. This need will be met by the No. 2 ESS.

Broadly, then, the objectives established for the No. 2 ESS were to complement the No. 1 ESS by offering economical electronic switching service for nonmetropolitan offices in the medium size range. These broad objectives have more specific implications on customer services, maintenance and administrative features, traffic capacity, floor space, and, of course, cost.

### **II. OBJECTIVES**

### 2.1. Customer Service Feature Objectives

By and large, the service features offered on all local switching systems are and should be the same. However, there are some small differences that result from differences in the intended field of application. Just as offices for use in nonmetropolitan areas tend to be smaller than those used in metropolitan areas, the service features that are required tend to differ. For instance, four-party and eight-party lines are fast disappearing from large cities but are still required in some suburban and rural areas.

Since No. 2 ESS is intended for application in nonmetropolitan areas, the objective for the initial package of customer service features is to provide features appropriate for such areas. It is a further objective to provide the features in the form of a "basic group" that would be present in all offices plus additional groups of features that would be optional. Specific features to be provided in the initial installations of No. 2 ESS are covered in a companion paper.<sup>1</sup>

# 2.2 Maintenance and Administrative Objectives

A high degree of dependability, maintainability and operational efficiency are required in all local switching systems. Experience indicates that electronic switching systems can meet these requirements at annual costs considerably less than with conventional switching machines.

Because of its intended use in nonmetropolitan areas, the No. 2 ESS was designed to be largely unattended. That is, wherever economically practical, maintenance tests, translation changes, traffic and plant measurements, and so on, were designed to be controlled remotely. Of course, repair or replacement of circuit packs, connections to cables, and so on, all require work in the office.

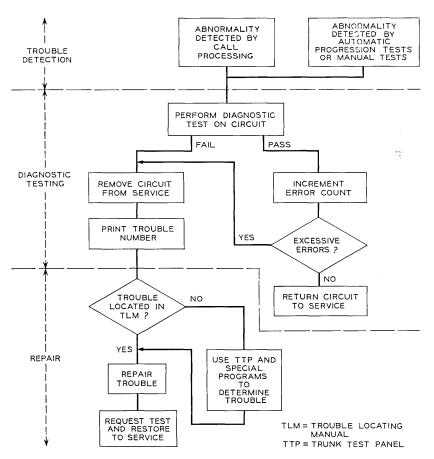

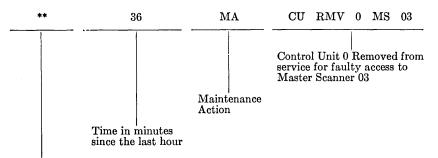

The companion article by Beuscher and others covers both hardware and software aspects of the No. 2 ESS administration and maintenance plan.<sup>2</sup> Of particular interest in this article is the system trouble example which describes the sequence of actions from a particular trouble detection through system repair.

### 2.3 Flexibility

More and more it is becoming apparent that flexibility is an extremely important objective for any new switching system. Many services being provided today had not been conceived even 20 years ago when the No. 5 crossbar system was designed, let alone at the time the step-by-step and panel switching systems were invented. Twenty to forty years from now, the electronic switching systems of today are likely to be called on to provide customer services and operating features not known today. For this reason, every attempt was made to make No. 2 ESS a flexible system.

The use of a stored program common control is, of course, a major step in providing the desired flexibility. In addition, hardware flexibility is provided by extensive use of modular equipment, connective frames and simplified peripheral communications.

### 2.4 Traffic Capacity

For an office of about 10,000 lines in a nonmetropolitan area, most Bell System requirements can be met with a minimum capacity of 16,000 busy hour calls and 40,000 ccs (hundred-call-seconds). However, it is clear that any capacity greater than these minima that can be achieved at reasonable cost would be valuable in the future for new services or increased calling rates. We discuss busy hour call capacity estimates for No. 2 ESS in Section V.

### 2.5 Economic Objectives

It is easy to say that the cost of a system to meet the preceding objectives should be as low as possible, and this, of course, is true. But what might be a realistic objective to shoot for? Since the No. 5 crossbar system is currently installed in the Bell System in this field of application, it was felt that a reasonable objective for No. 2 ESS, with its many attractive features, was to be competitive with standard No. 5 crossbar systems in terms of installed first cost. Thus the advantages of the No. 2 ESS in terms of simplified installation (relatively sophisticated factory test, shipment of several equipment frames as a factory wired unit and extensive use of plugs and jacks for interunit wiring) would be recognized in this economic comparison but other advantages, such as new service features, reduced maintenance, and administrative costs would not. This enables the using telephone company to benefit from its new equipment immediately upon installation and does not require it to anticipate future savings in order to prove in modern telephone equipment.

### 2.6 Other Objectives

Obviously many other objectives were also established for No. 2 ESS. For example, it should provide service as reliable as, or better

than, existing systems; it should occupy minimum floor space, and it should have as short an installation interval and as small an installation effort as possible.

### III. SYSTEM DESCRIPTION

## 3.1 General Design Plan

The design of No. 2 ESS was derived from experience with both the No. 1 ESS and No. 101 ESS. The system uses a ferreed network and other peripheral units similar to that of No. 1 ESS. The No. 2 ESS control is a new design based on the smaller type of control which is being used in the No. 101 Electronic Switching System.

The rationale behind these design decisions is clear. The No. 1 ESS serves large offices and creates a high production of network and peripheral apparatus. The designer of the small system gains the benefit of this large production by using the same apparatus. In the control area the small office designer has greater flexibility since he creates his own high production based on the large number of entities in the small office field. He, in addition, has the advantage of moderate traffic capacity requirements. It is, therefore, reasonable to have a specialized design for the small office control which attempts to minimize costs at some sacrifice of traffic capacity.

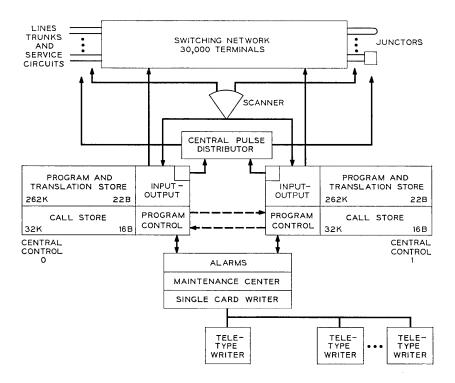

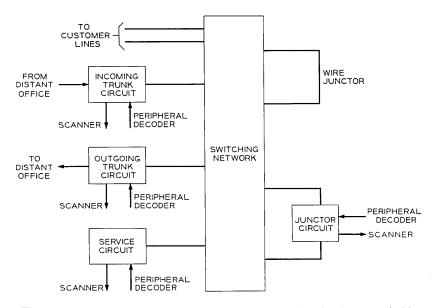

## 3.2 Control Unit

Figure 1 is a block diagram of the No. 2 Electronic Switching System. Although reminiscent of most electronic switching system block diagrams, there are several points which can be made in conjunction with this figure. The control consists of duplicated central controls, each working with a common maintenance center. Each central control has been designed as a single switchable entity. That is, the frames which contain the program and translation store, the call store, the program control and the input-output are treated as one entity rather than individually switchable units. This reduces both the quantity of equipment required and the quantity of program required for the administration of redundancy.

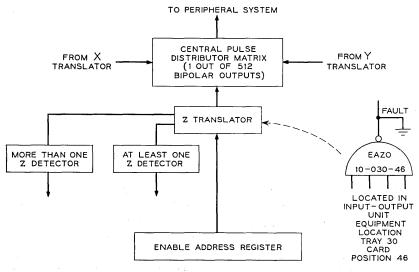

The processor frame used in No. 2 ESS contains the program control (instruction processing logic), a semiautonomous input-output section, capacity for 16,384 16-bit words of call store (temporary memory) and capacity for 512 bipolar central pulse distributor points. The call store may be equipped in steps of 4096 words while the central pulse distributor may be equipped, as required, with packages of eight central pulse distributor points. High speed transistor resistor logic is used for all logic applications in this frame. This logic uses thermocompression bonded beam leaded silicon devices with thin film resistors on an alumina substrate. Growth frames are available which allow expansion of the call store to 32,768 words and the central pulse distributor to 16,384 points.

The basic program and translation store frame for No. 2 ESS contains four permanent magnet twistor modules with a total capacity of 65,536 22-bit words. In addition to the basic frame, growth frames are available which allow this store to be expanded in steps of 16,384 words to a maximum size of 262,144 words.

The semiautonomous input-output unit which is included in each processor frame shares the call store with the program control on what is generally a lower priority. The input-output unit works together with the program to: (i) scan for line originations, (ii) collect

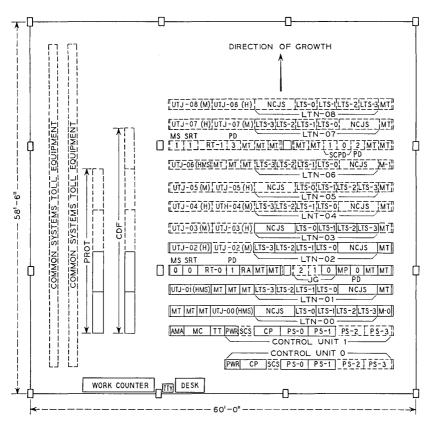

Fig. 1-No. 2 ESS Block Diagram,

dialed digits and tone signals, (iii) outpulse, and (iv) transmit data. Use of the input-output unit for digit receiving and sending functions has allowed the normal program interrupt cycle to be set at 25 milliseconds rather than the usually required 5 to 10 milliseconds. In addition, the precise timing and short scan intervals available through the input-output unit has allowed simplification in circuits such as incoming trunks from step-by-step offices. The input-output unit is fully discussed in the Control Unit paper.<sup>3</sup>

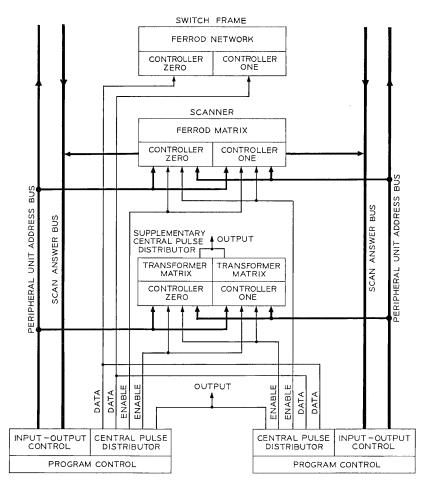

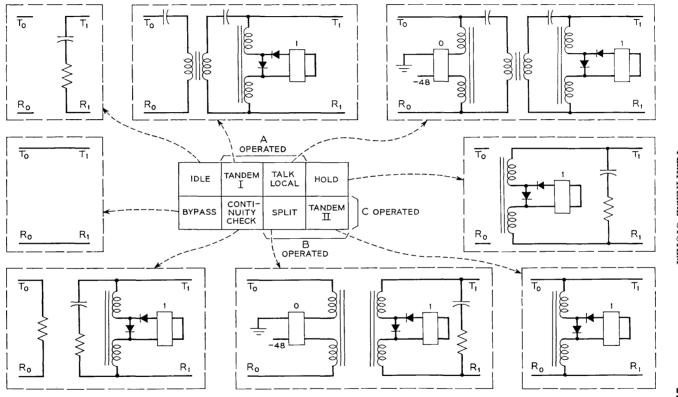

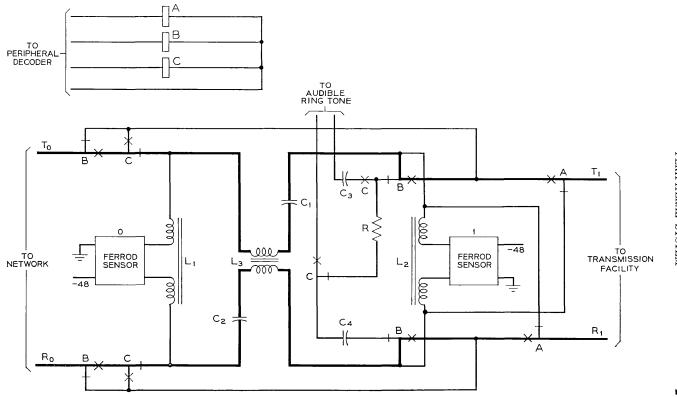

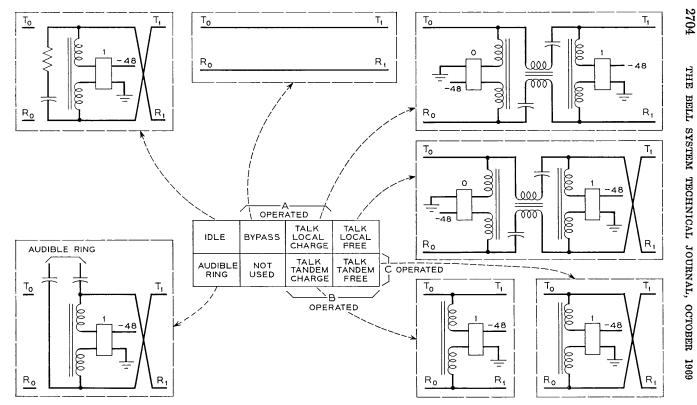

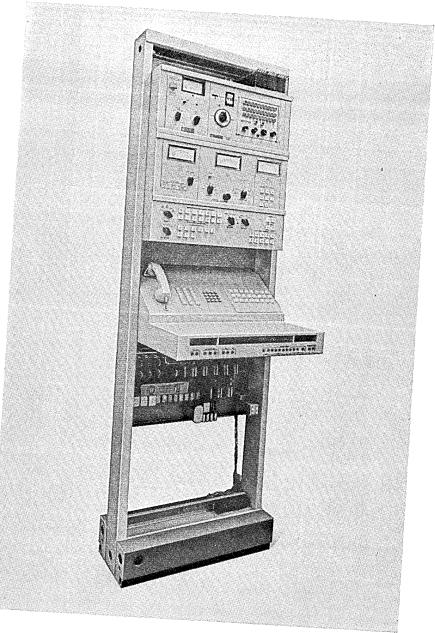

# 3.3 The Network

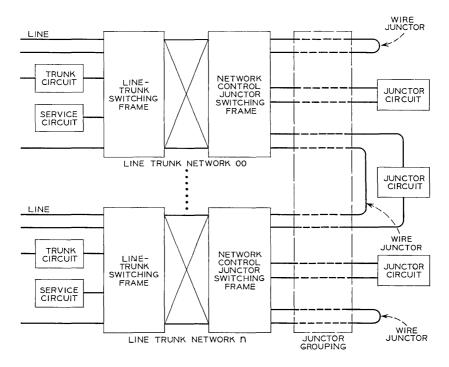

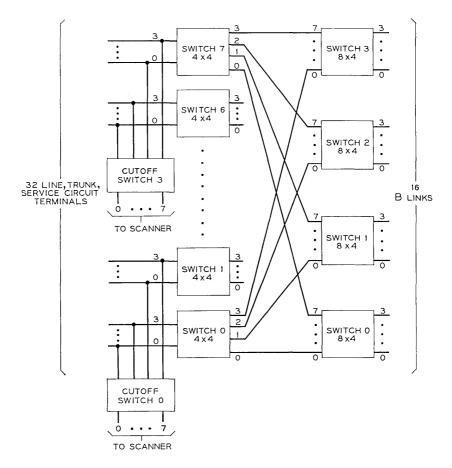

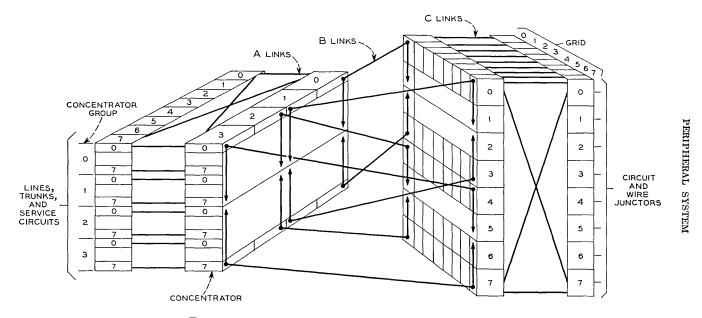

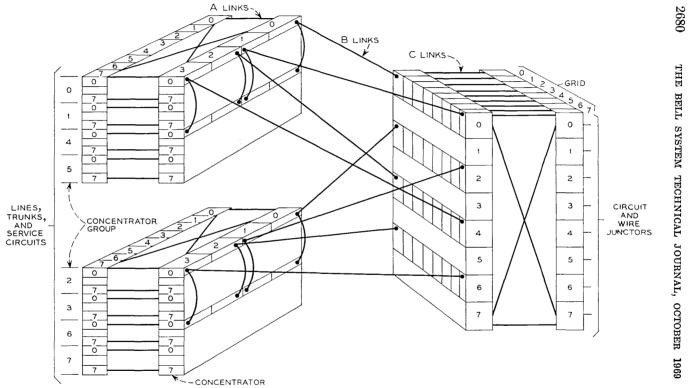

While generally using the same apparatus as No. 1 ESS, the No. 2 ESS network has been designed to minimize "getting started" costs. This was easier to achieve in No. 2 ESS since the ultimate size of the system will be considerably smaller than the ultimate size of No. 1 ESS. The system uses a two-wire folded four-stage ferreed network with lines, trunks, and service circuits all appearing on the same side. It is therefore not necessary to have a separate line and trunk link network in small offices. Only two types of frames are used to make up the No. 2 ESS network:

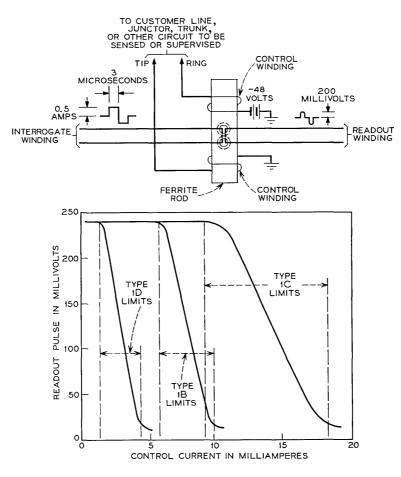

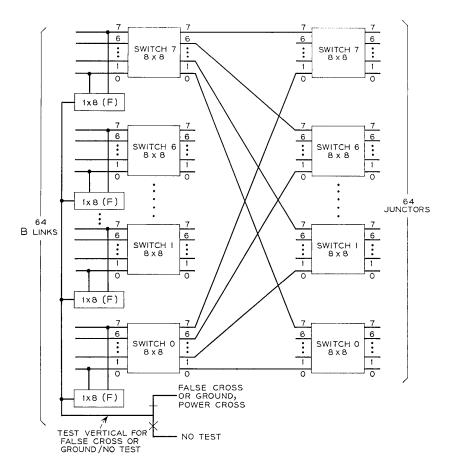

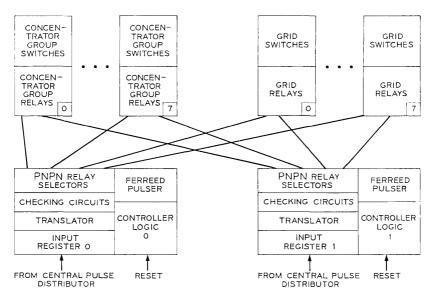

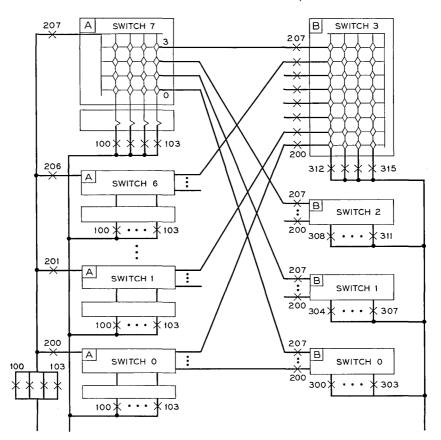

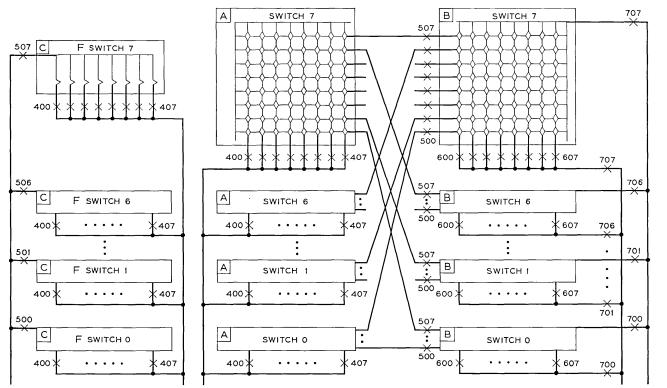

(i) The network control junctor switch frame contains eight  $64 \times 64$  octile grids which form the third and fourth stages of the network. Each grid is made up of sixteen  $8 \times 8$  ferreed switches arranged for 64 inputs and 64 outputs. This frame contains a pair of controllers which operate the junctor network and the network and scanners of the line-trunk switch frames.

(ii) The line-trunk switch frame can accommodate 512 inputs which concentrate to 256 outputs. This frame is made up of sixteen  $32 \times 16$  ferreed concentrators. These concentrators are made up of eight  $4 \times 4$  switches in the first stage and four  $8 \times 4$  switches in the second stage. This frame also contains a 512 point ferrod line scanner. One, two, three or four line-trunk switch frames can be connected through B-links to the 512 inputs of the network control junctor switch frame to form a complete line-trunk link network.

At 4:1 concentration ratio, each line-trunk link network can provide up to 2048 terminals for lines, trunks and service circuits. At 2:1 concentration ratio, 1024 terminals would be provided per line-trunk link network. Through use of circuit and wire junctors additional networks can be added with an ultimate capacity of fifteen networks which can carry over 100,000 ccs of traffic.

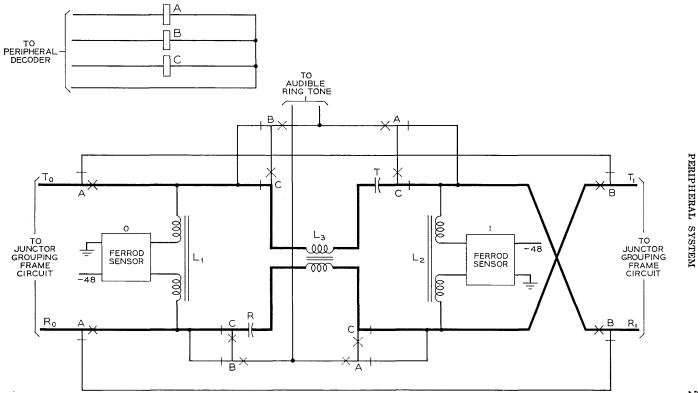

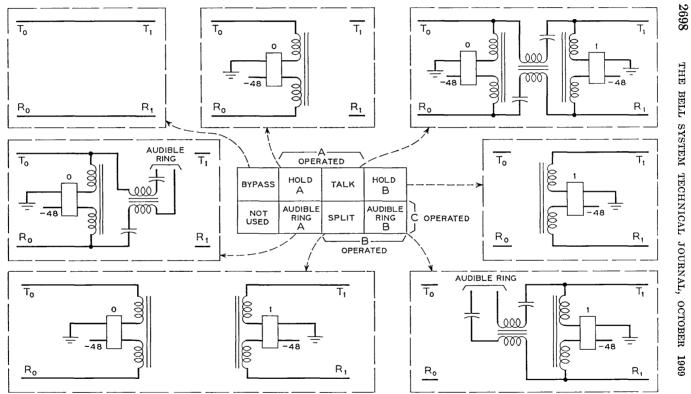

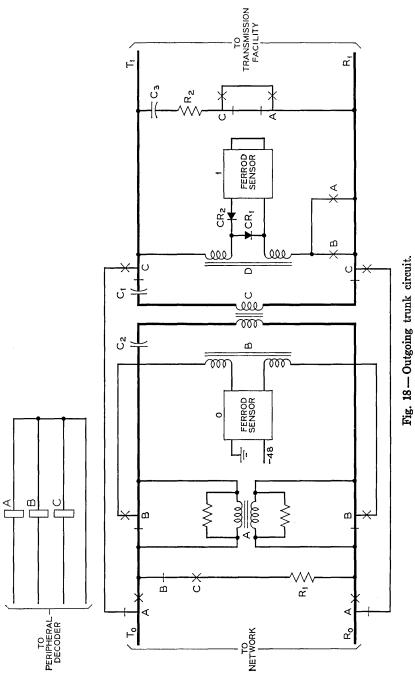

## 3.4 Trunks, Junctors and Service Circuits

The trunks, junctors, and service circuit designs of No. 2 ESS are generally the same basic types as those in No. 1 ESS. The primary difference has been in the use of a special integrated circuit package which has been designed specifically to control relays. This package, called the peripheral decoder, offers several advantages over previous trunk control schemes. Each peripheral decoder pack can operate and hold up to 12 relays and would typically be used to control four universal trunks or circuit junctors. Information is sent from a central pulse distributor point serially to the peripheral decoder where the information is stored on flip-flops and decoded to operate the desired relay. From the program point of view, the relays are thus controlled at electronic speeds. Use of the peripheral decoder also allows the trunk control to be equipped with a single pack at a time as trunks are added to the office. In addition, the peripheral decoder is a good application for integrated circuits since it will be a high production circuit package. The peripheral decoder is described in detail in the companion articles on the Peripheral System, and Apparatus and Equipment.4,5

# 3.5 Installation and Growth

A significant effort has been made in No. 2 ESS to simplify growth and change of equipment and to reduce installation intervals. Most of the connections between the central control frames and the connections to the maintenance center are through plug-in connectors. In addition, both the call store and program store growth units are equipped with plugs and jacks. It is planned that the entire control complex will be plugged together at the factory and tested as a system through X-ray programs. The same X-ray programs will be used when installing the control complex at the central office site.

Some of the maintenance center functions also include capabilities which aid in both factory test and installation of the machine. These functions provide (*i*) manual access to internal processor states, registers, and memory locations; (*ii*) control capability over execution of program segments, and (*iii*) emergency override features which put the machine under manual control.

To aid in peripheral system installation, bus communication between the control and the peripheral frames and all B-link connections within the network are on plug-in connectors. In addition, trunks and service circuits are equipped on easy-to-install mounting plates

while peripheral decoders, as already mentioned, are on plug-in packages.

### IV. PROGRAMMING

## 4.1 Program Size

Basic program and translation requirements for small (single linetrunk link network) No. 2 ESS offices are estimated at less than 65,000 22-bit words. Thus these offices may be served by a single four module program store per central control. As the offices grow in size and feature requirements, additional program modules may be added as already described.

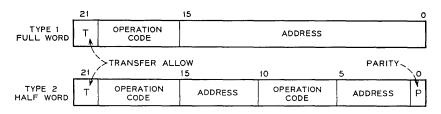

The instruction format used in No. 2 ESS is the same as that used in No. 101 ESS and consists of two types. Type 1 uses a 22-bit word which contains a 5-bit operation code and a 16-bit address plus a check bit. Type 2 contains two complete 10-bit instructions, each of which contains a 5-bit address and a 5-bit operation code. The short 5-bit address is made effective by extensive use of relative and implicit addressing of both program and call store information. Experience on No. 101 ESS and No. 2 ESS has shown that this format is highly efficient in the use of program store space thereby aiding in meeting the low cost objectives for the system.

# 4.2 Call Programs

We leave the details of the systems programming to later papers.<sup>1,2,6</sup> However, with the emphasis on low system cost, a few points are worth reviewing. We have already mentioned the highly efficient micro-type orders used for program instructions. The major feature of these kinds of instructions is that very few bits are wasted in unused options and unneeded address bits, as is often the case with larger, fixed length program instruction words.

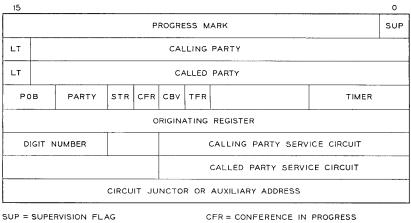

Also simplifying both program and administration is the use of general purpose registers within the temporary memory for all types of calls. These registers consist of a progress mark which defines the state of the call plus other information pertinent to the call. Call registers containing progress marks generally use the same format and the same register size, thereby allowing common programs to be used for many different call states.

The progress marks themselves define the first address of the

program required to process the particular call. The preponderance of call processing can then be described as a series of transfers to the individual progress mark programs. In addition to straightforward call processing techniques, great emphasis has been given to the use of common subroutines. Many progress mark programs consist entirely of calls to nested subroutines. In order to help in this effort some special orders and push-down list features have been included in the basic instruction repertoire to aid in the writing and to facilitate the use of subroutines. The Control Unit System article further describes the No. 2 ESS order repertoire.<sup>3</sup>

### 4.3 Maintenance and Administrative Programs

Maintenance and administrative programs constitute over half of the programming job, hence considerable effort has been extended to seek simplifications in this area. In the control system the maintenance structure is based on a single interrupt level, a single match circuit, a few internal check circuits and good program access between the on- and off-line units. These factors, in conjunction with low component counts and the single switchable entity concept, all tend to reduce and simplify the programs. In the periphery, the small number of frame types and options has reduced the adminstrative and growth program needs as well as creating some maintenance simplification.

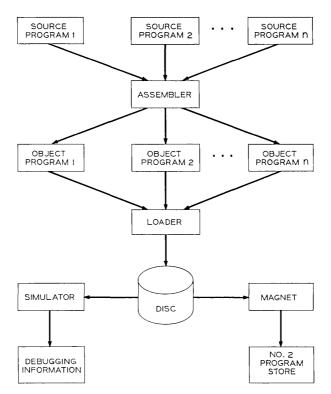

### V. TRAFFIC CAPACITY

In designing a small office, many trades are made which favor low cost over real-time traffic capacity. Care must be taken, however, to leave sufficient capacity to allow a reasonable range for newly started offices and growth. Current estimates indicate that the No. 2 ESS may be engineered for up to 19,000 busy hour calls with a traffic mix of one-third intraoffice, one-third outgoing, and one-third incoming calls. This estimate has been derived from several sources. Among these are: (i) cycle counts in the programs, (ii) simulation of the programs, (iii) laboratory measurements as the programs are being debugged, and (iv) comparisons with existing systems.

The busy hour call calculation has been made by determining the number of calls that may be carried with the processor occupied at 95 percent (peak capacity) and reducing this result by an allowance for false starts (number of false starts assumed equal to 30 percent

of originating calls). The total is further reduced to allow a 30 percent peak with the final result being 19,000 busy hour calls for engineered load. In general, all calculations have been very conservative.

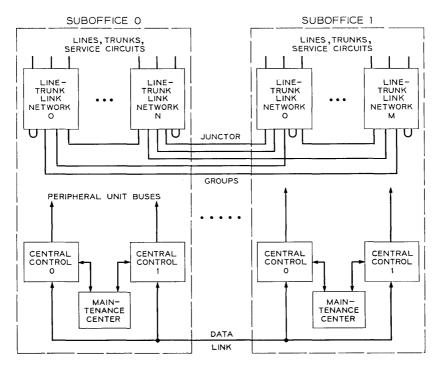

# 5.2 Dual Office

While it is generally expected that the capacity of 19,000 busy hour calls will be quite adequate for the No. 2 ESS field of application, techniques are being explored for expansion beyond this capacity. These techniques are aimed at the situation where very large unanticipated growth is necessary at a No. 2 ESS installation. Figure 2 is a block diagram for a dual No. 2 ESS office. This diagram shows a pair of No. 2 ESS offices with the networks joined by junctors. In addition, data links would be provided for communications between the controls of each suboffice. With this plan, all connections within a suboffice or between suboffices would use only eight stages of network. In addition to this, trunk groups would be distributed between the suboffices in the same way as they would be for a single office. In order to facilitate the use of common trunk groups and a common network, the data links would be used to exchange network status information, trunk status information, and supervision where necessary.

The dual office concept represents a form of multiprocessing highly suited to telephone applications. In general, each suboffice does business as usual except where a connection is to be completed between the suboffices. The number of inter suboffice connections can be minimized by not permitting service circuit connections between suboffices. For example, when a line originates, the dialing connection will always be made within the suboffice on which the line homes. When a line is called, the ringing connection will always be made within the called suboffice. By proceeding in this way the real time consumed in completing inter suboffice connections is limited primarily to the final talking path.

Except for network status information, the data communication between the offices is simple and does not add a major amount of new work to the normal single office program. Early traffic estimates on dual processing indicate that inter suboffice calls will incur an approximate 20 percent real time penalty while the penalty on intra suboffice calls appears negligible. The emphasis in the dual office is clearly to retain network and trunk efficiency since this is where, in a large telephone office, most of the expense occurs. On the control

Fig. 2-No. 2 ESS Dual Office.

side the emphasis is on relatively simple growth and retention of a large part of the single office programs. The dual office version of No. 2 ESS is not aimed at the new office field; the primary objective is to allow a greater growth range for the system while not penalizing the "get started cost" of a single office.

### VI. STATUS

The first No. 2 ESS office is scheduled to go into service during the last quarter of 1970 at Oswego, Illinois. Hardware and software are being debugged on two test models at Bell Telephone Laboratories, Indian Hill, Naperville, Illinois. The 2100-line Oswego office is expected to be followed in service by three other offices in 1971, ranging from approximately 1000 to 5000 lines, and thus representative of the typical No. 2 ESS new starts. Western Electric Company price estimates indicate that No. 2 ESS is meeting its economic objectives and wide penetration in the Bell System central office field is expected.

#### VII. ACKNOWLEDGMENTS

The design of No. 2 ESS contains the contributions of many people at the American Telephone and Telegraph Company, Western Electric Company, and Bell Telephone Laboratories. In addition, the experiences of the many Bell System operating companies using electronic switching systems has provided invaluable information for the design process.

### REFERENCES

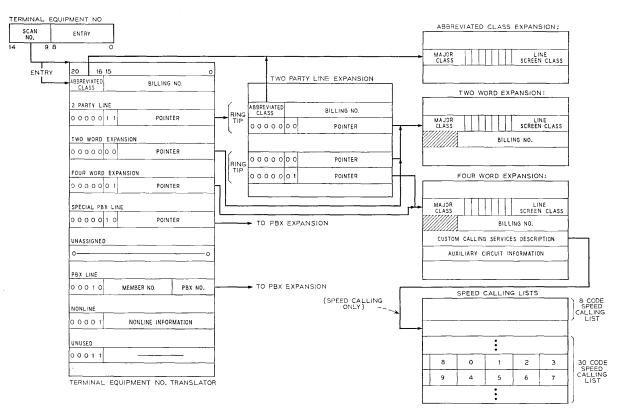

- Andrews, R. J., Driscoll, J. J., Herndon, J. A., Richards, P. C., and Roberts, L. R., "Service Features and Call Processing Plan," B.S.T.J., this issue, pp. 2713-2764.

- 2. Beuscher, H. J., Fessler, G. E., Huffman, D. W., Kennedy, P. J., and Nuss-baum, E., "Administration and Maintenance Plan," B.S.T.J., this issue, pp. 2765-2815.

- pp. 2103-2819.

Browne, T. E., Quinn, T. M., Toy, W. N., and Yates, J. E., "Control Unit System," B.S.T.J., this issue, pp. 2619-2668.

Digrindakis, J., Freimanis, L., Hofmann, H. R., and Taylor, R. G., "Peripheral System," B.S.T.J., this issue, pp. 2669-2712.

Lonnquist, C. W., Manganello, J. C., Skinner, R. S., Skubiak, M. T., and Wadsworth, D. J., "Apparatus and Equipment," B.S.T.J., this issue, pp. 2612-2662.

- 2817-2863. 6. Barton, M. E., Haller, N. M., and Ricker, G. W., "Service Programs," B.S.T.J., this issue, pp. 2865-2894.

NO. 2 ESS

# **Control Unit System**

# By THOMAS E. BROWNE, THOMAS M. QUINN, WING N. TOY and JOHN E. YATES

(Manuscript received March 7, 1969)

The control unit system consists of the combination of elements which direct and control the operation and functions of the system. It includes the stores and processing units as well as the elements of the man-machine interface. This paper describes the organization of these units, the processor order structure, and some rationale as to why certain design choices were made.

### I. INTRODUCTION

The goal of this paper is to provide a general view of the organization and structure of the No. 2 ESS control unit. An attempt is made to emphasize the background and philosophy behind some of the design choices and their relation to the broad requirements of an economical, flexible, and reliable stored program control system.

# 1.1 Definition of Control Unit System

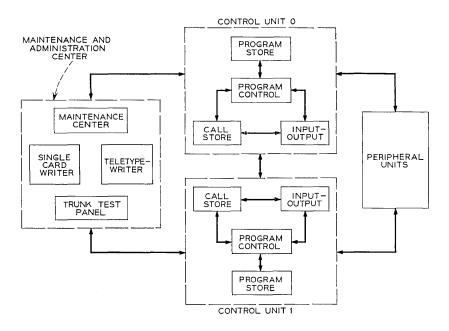

The role of the control unit is to direct the processing of calls and maintenance in the system. It is comprised of the central processing unit, the stores, and the interface to the peripheral units. Two control units and the maintenance and administration center are referred to as the No. 2 ESS control complex. The various subunits which form a control unit include the program control, the input-output control, the call store, and the program store.

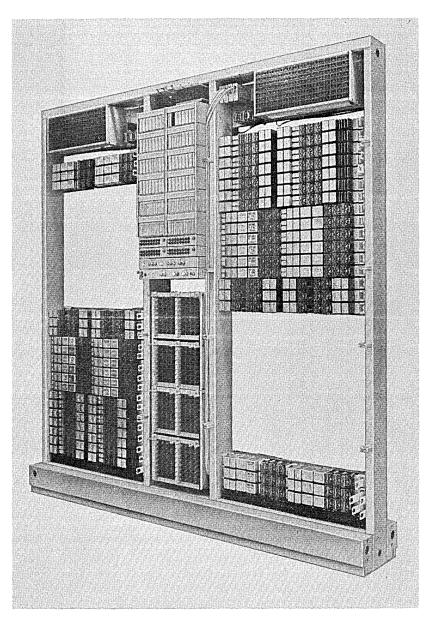

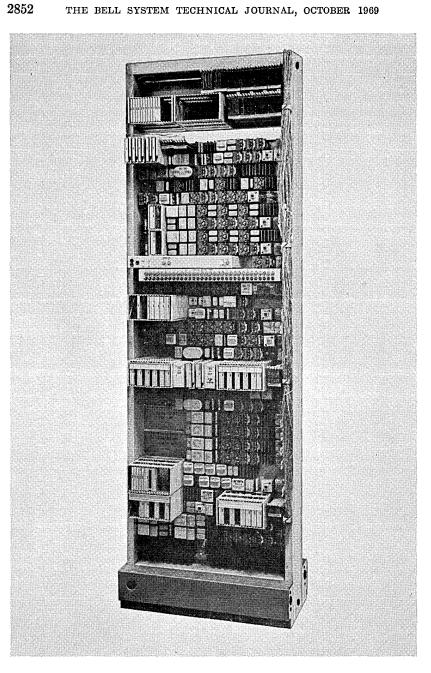

The program control is the central processing unit which executes the instructions read from the program store. The input-output control performs the function of interfacing with the peripheral units by providing circuits such as a central pulse distributor, address bus drivers, and scan answer bus receivers. In addition, the input-output control autonomously performs certain processing functions associated with high rate, time critical, peripheral communication. The call store is

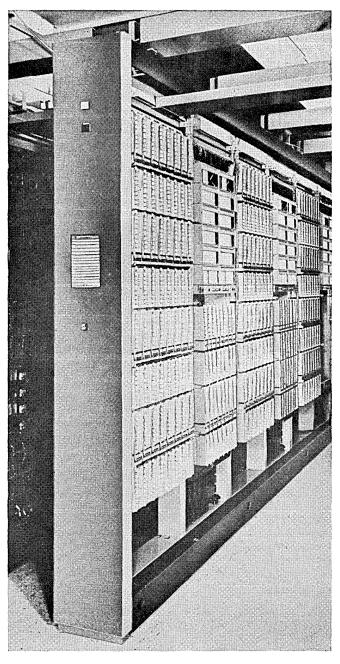

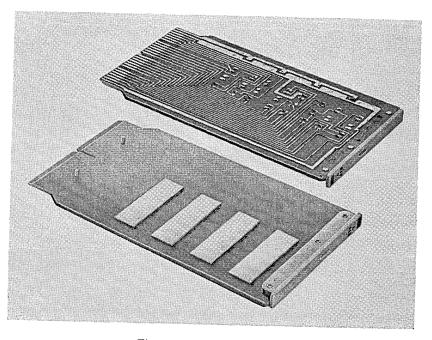

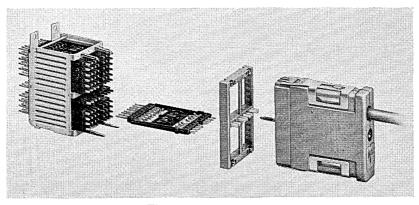

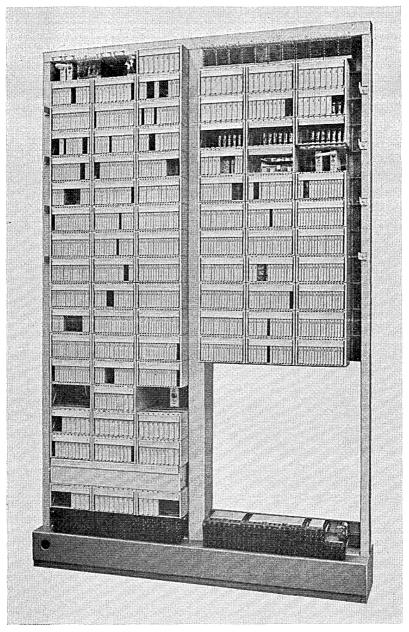

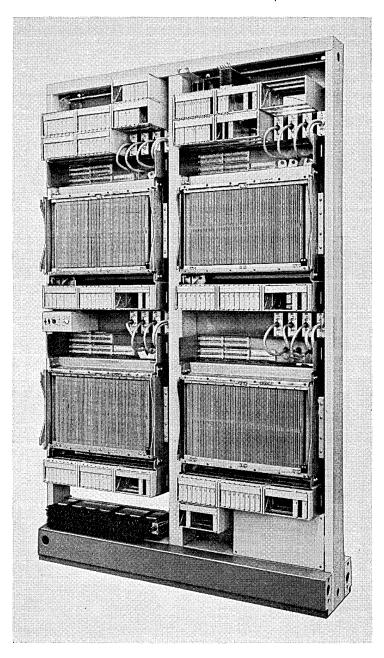

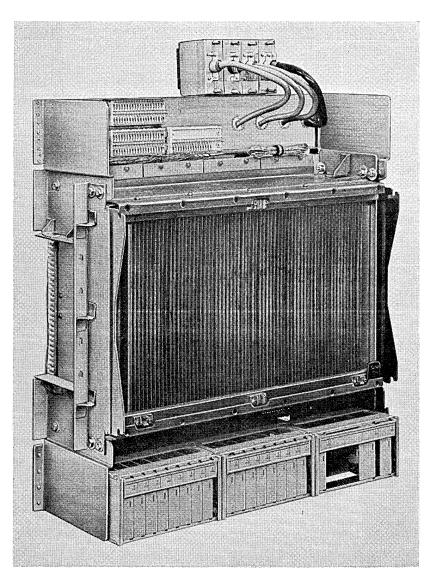

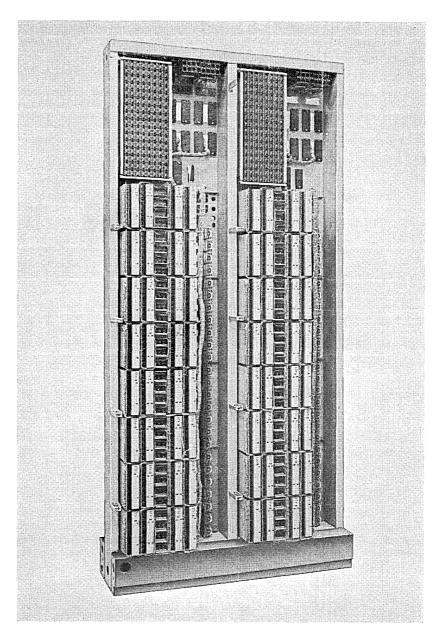

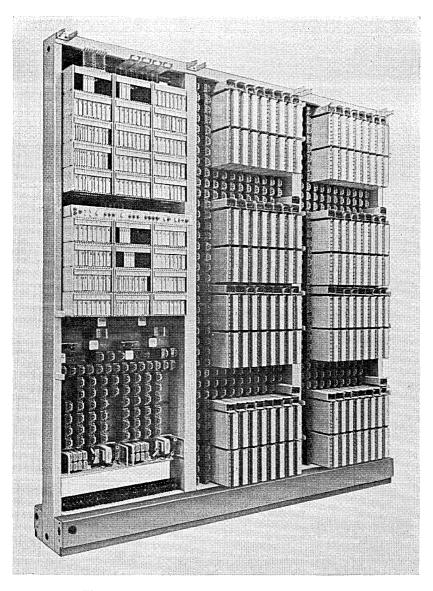

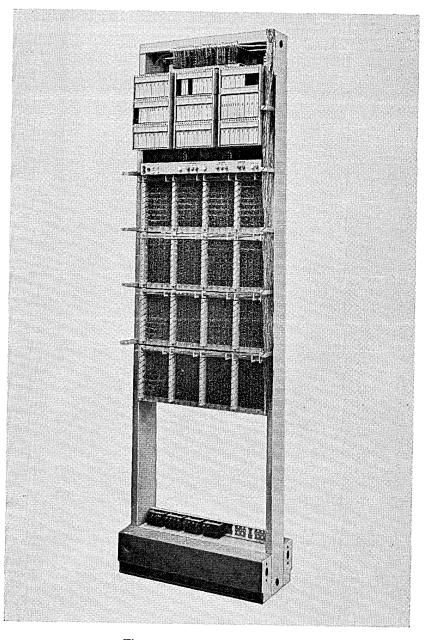

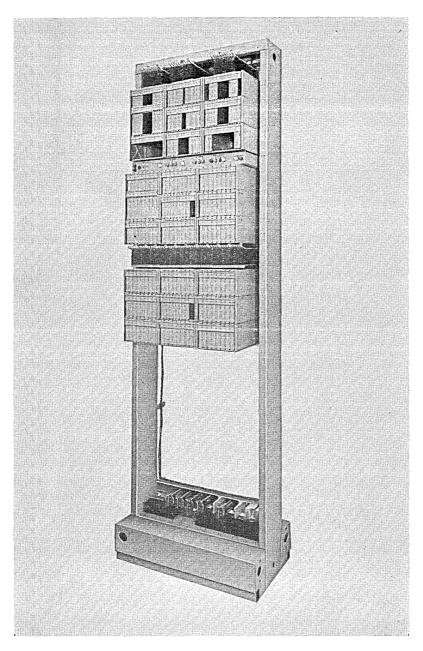

the variable memory used to hold information of a transient nature and also that which must be easily modified. The program store is a read-only memory which contains the operational programs as well as parameter and translation data. Physically, the program control, input-output control, and up to 16,384 words of call store are contained in one double bay frame called the central processor frame. Up to four 16,384-word modules are contained in a program store frame (65,536 words), four of these frames may be addressed by the system. A companion article in this issue has photographs of these frames.<sup>1</sup>

### 1.2 Design Objectives and Their Influence

The control unit was designed to control a small, low cost, electronic central office. Much of the economy was realized by the program and call store word sizes which, in turn, determine the size of various registers and gating paths in the processor. In addition, the use of a "micro" type of instruction repertoire allows the multiple use of logic elements for many of the instructions and the efficient use of the program store.

The command structure is somewhat tailored to the progress mark approach of call processing with efficient means of handling information contained in call registers or records.<sup>2</sup> However, the majority of instructions are general purpose, simple, and compact. Hardware check circuits are judiciously used in areas that are difficult if not impossible to check by program and where immediate detection is important. A high degree of internal access is provided for fault detection and diagnostic purposes. Much of this access is common to call processing as well as maintenance.

Some of these economies and the rather serial manner in which processing is performed sacrifice real-time capacity. A fairly modest investment in input-output wired logic minimizes the sacrifice by relieving the program of performing some of the highly repetitive simple functions and quite significantly avoiding the burden of a more frequent input-output interrupt with its associated overhead. This design resulted in a small enough quantity of hardware that an entire control unit forms one switchable system block, thus avoiding the expense and complexity of providing communication paths and control for switching subunits within the control unit.

### II. GENERAL ORGANIZATION

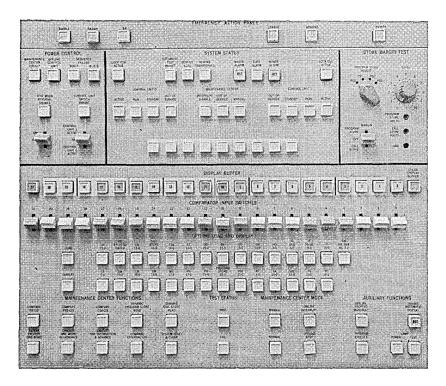

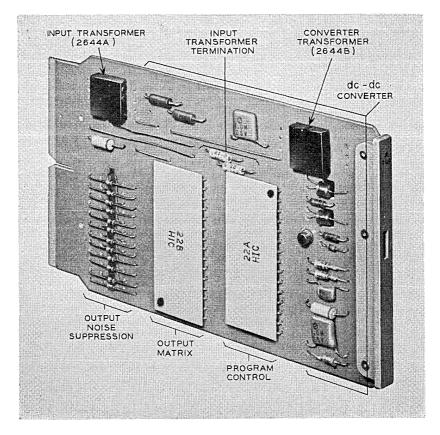

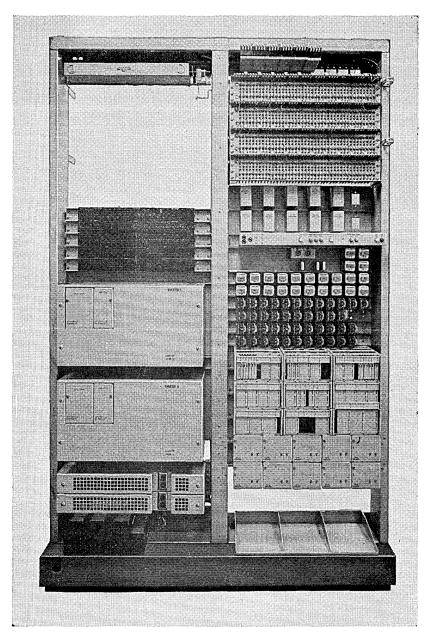

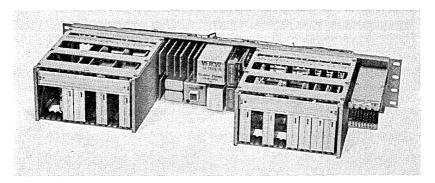

Figure 1 shows the No. 2 ESS control complex which consists of two control units and the maintenance and administration center. The CONTROL UNIT

Fig. 1-No. 2 ESS control complex.

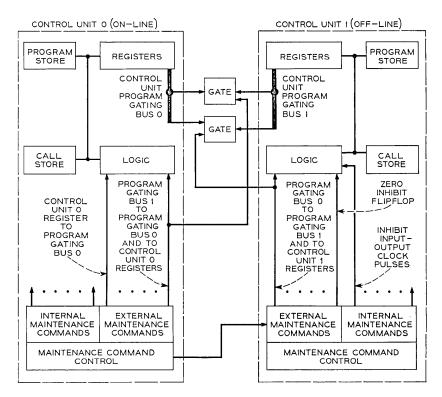

control unit is duplicated and normally running in synchronism with its mate. One control unit activates the peripheral equipment and is called the ACTIVE or more descriptively, the "on-line" control unit. The control units are matched at the maintenance center. The call store is shared by both the program control and input-output control within a control unit. Each control unit has access to only one peripheral communication link but each link provides access to the duplicated controllers of the peripheral unit frames.<sup>3</sup>

The subunits are defined in Fig. 1 and are described in detail later in this article. The bus system is considered part of the control unit and a fault in the active bus will require switching of control units. Communication between control units is for maintenance purposes as in the communication between the control units and maintenance center.

The savings involved by avoiding the interswitching of subunits within the control unit has already been mentioned. Additional savings result from the compact nature of the design in that simple direct wire (dc) communication is possible among all units in the central processor frame, between the pair of control units, and between the control units and the maintenance center. The need for

transformer-coupled (ac) drivers, receivers, and receiving registers is avoided in these instances. However, the nature of the program store signals, the store's physical size, and the growth needs, dictate the use of transformer-coupled paths for the address and read out signals between the program control and program store. This is not a severe economic penalty since there are only about 20 pairs involved in each direction. For the most part, the connections between major units are handled via plug-in cables. This connectorization of blocks leads to advantages in testing, installation, and growth and is covered in detail in a separate article in this issue.<sup>1</sup>

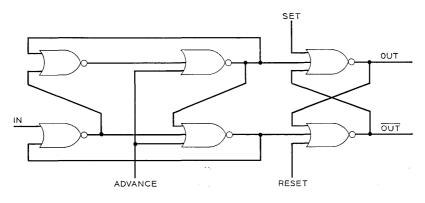

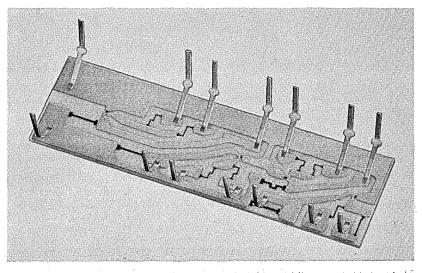

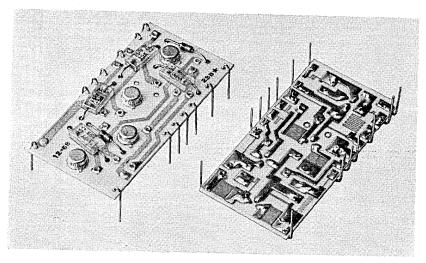

### III. LOGIC CIRCUITS AND STORES

### 3.1 Building Block Logic Circuits

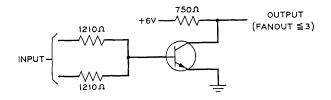

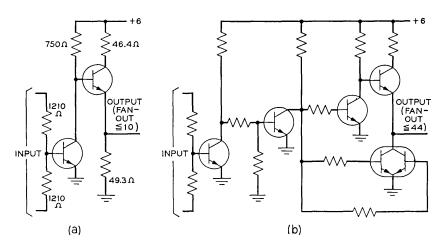

The logic circuits of the control unit are fabricated using the transistor-resistor NOR logic gate of Fig. 2 as a basic building block. Constructed with high-speed silicon transistors and tantalum-nitride thin film resistors as described in a companion article in this issue,<sup>1</sup> this gate, with a typical propagation delay of 35 nanoseconds, competes favorably with other available discrete component logic forms from an economic point of view. To provide building blocks with medium and high fanout capability, and a binary counter-shift register function, variations on the basic gate have been developed. These are shown in Fig. 3.

The fan-out of the basic gate is three and the fan-in is two. By connecting the collectors of a number of transistors to a common load resistor, a gate with greater fan-in (maximum of 40) can be formed, although not without suffering some loss of speed. The margin of this gate against false turn-on is determined primarily by the difference between the saturated collector-emitter voltage and the conduction threshold of the base-emitter junction of the transistor. In the worst case, this is only about 200 mV, and this imposes a constraint

Fig. 2 - Transistor-resistor logic gate,

CONTROL UNIT

Fig. 3 - (a) Intermediate fan-out gate, (b) high fan-out gate, and (c) binary counter-shift register.

on the backplane wiring of the machine. The wiring is also constrained by the need to avoid excessive negative noise pulses and ringing on signal leads since these may cause "on" transistors to turn off falsely. In some cases, "catching diodes" and terminating resistors have been connected on the far end of long signal leads to prevent negative undershoots from turning off gates. In the development of the No. 2 ESS, these various constraints have been evaluated and wiring rules formulated to assure reliable performance of the circuits over the range of operating voltages and environmental conditions.

2623

## 3.2 Call Store Circuit

The call store circuit provides the temporary information storage required in the control unit. It is a random-access memory of 8192 words of 16 bits each and operates with a destructive read-write cycle time of 6.0 microseconds.

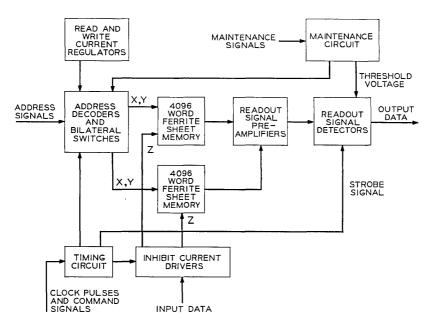

## 3.2.1 Memory Device

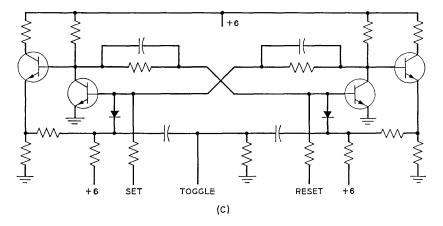

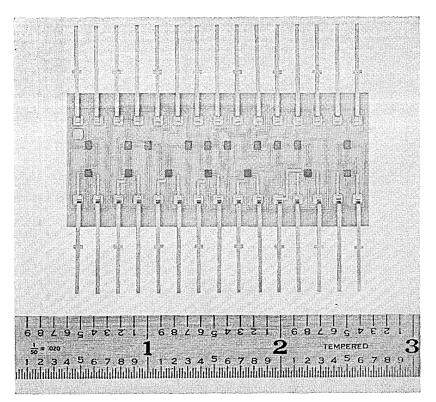

The basic memory device in the call store circuit is a 1-inch square ferrite sheet approximately 30 mils thick, having a 16-by-16 array of 25 mil diameter holes located on 50 mil centers. <sup>4,5</sup> This is the same device that is used in the No. 1 ESS call store circuit.<sup>6</sup> Two hundred fifty-six sheets are wired together to form a 4-wire coincident current memory module of 4096 sixteen-bit words. Two wires are used for access current (X and Y), a third (Z) for inhibit current, and the fourth is used for sensing the readout signal.

The wiring pattern used in this construction is designed to maximize the readout signal-to-noise ratio by minimizing the coupling of access circuit transients into the readout circuit and by canceling the delta noise along the readout signal wire. Signal-to-noise ratio is further controlled by time-staggering the application of drive currents in reading the memory. The sheet material characteristics are such as to allow a 1.90 microsecond destructive read access time and total cycle time of 6.0 microseconds with coordinate access currents of 280 mA and 0.4 microsecond rise times.

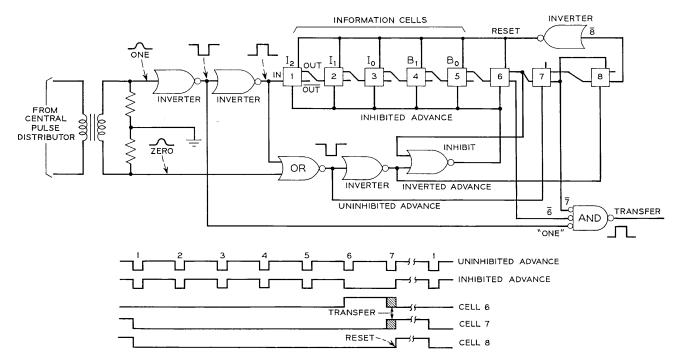

# 3.2.2 Call Store Operation

Figure 4 is a block diagram of the call store circuit. Address and input data signals are brought to the store by dc connections to the call store address and call store input registers in the program control circuit. Output data from the store is delivered by dc connections to either the general register in the program control circuit or the digitdata output register in the input-output circuit depending on which of two kinds of read command is being executed. Because of these dc connections, no registers are needed in the call store itself, and none are shown in Fig. 4.

The X and Y access windings are the crosspoints of bilateral voltage selection matrices in each of which one horizontal and one vertical coordinate is selected by the address information presented to the store at the time of a read or write command. This selection is made by the address decoders and bilateral switches under control of the CONTROL UNIT

Fig. 4 --- Call store block diagram.

timing circuit shown in Fig. 4. Access current flowing through the switches and selection matrix is controlled in both amplitude and rise and fall times by the read and write current regulators. Output signals from the ferrite sheet memories are amplified and discriminated during a specific time interval under control of a strobe signal generated by the timing circuit. This strobe signal is inhibited by the program control on "call store write" commands when the information being read is to be destroyed.

Following the read operation, the access currents reverse polarity to accomplish writing. This will switch the ferrite material at the selected holes to the "one" state except at those holes where inhibit current is applied. This is done on the inhibit windings of those bits which are to be zero, thereby cancelling the effect of half of the access current. The access currents persist long enough to switch all of the material surrounding the selected holes to the "one" state in the absence of inhibit current. Following the write operation, a postwrite disturb current is applied in the read direction on the inhibit windings in order to adjust the magnetic state of the ferrite material to achieve minimum delta noise.

2625

# 3.2.3 Maintenance

In Fig. 4, a "maintenance circuit" is shown. This circuit monitors the operation of the access circuitry to insure that on each store cycle the access currents flow in the correct direction at the correct time and that exactly two of the bilateral switches on both the X and the Y selection matrix operates. On any one cycle, if all of these conditions are not met, a "call store error" signal is sent to the program control and maintenance center circuits, indicating a fault in the access circuits of the store. In order to insure the integrity of these checking circuits, maintenance signals are brought into the store which logically simulate the access failures that should be detected by the check circuits.

Other maintenance signals which cause the store to write all 1's or all 0's at a particular address can be activated by the maintenance programs to facilitate diagnosis of faults in either the store or the circuits to which it connects. Finally, there is a third set of maintenance signals by which the threshold voltage of the sense amplifiers may be varied, either manually or by program, to evaluate the operating margins of the store.

# 3.2.4 Growth

In order to achieve minimum cost in the smaller office sizes, the call store has been designed to provide only 4096 words by eliminating one of the memory modules. Furthermore, the physical design of the call store and the program control has included connectorization to allow for growth of up to four 8192-word stores, any of which may be partially equipped so that the call store may be any size from 4096 to 32,768 words in 4096-word increments. The smallest office is expected to use 8192 words.

## 3.3 Program Store

The program store circuit provides memory for semipermanent information in the No. 2 ESS control unit. This information is the program and translation data used by the system. It is called semipermanent because it is fixed and independent of the calls being processed by the system at any given time. However, as the services provided by the system are changed, or as lines and trunks are changed, the program and translation data must change. The store is a random-access read-only memory of 65,536 words of 22 bits each and operates with a 2.5 microsecond access time and a 6.0 microsecond cycle time. Each half of the control unit may be equipped with up to four stores (in the largest office), and each store may be partially equipped to provide as few as 16,384 words.

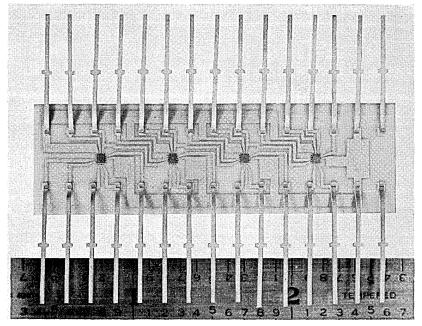

### 3.3.1 Memory Device

The program store uses the permanent magnet twistor memory for the basic storage device, in a fashion similar to the way it is used in the No. 1 ESS program store.<sup>7</sup> Information is stored in the state of small magnets affixed to aluminum cards, and the state of the magnets is sensed by the twistor wire. A detailed description of the actual readout process has been published in a number of earlier papers. The present store differs from No. 1 ESS in its organization, maintenance features, and capability for growth. These aspects of the store are described in the following paragraphs. As in the No. 1 ESS store, information is changed by withdrawing the magnet cards from the twistor module and changing the state of the magnets by means of a special writing mechanism. The operational aspects of this feature are described in some detail in Section VI.

### 3.3.2 Program Store Operation

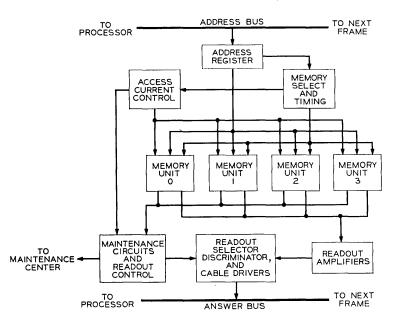

Figure 5 is a block diagram of the store. Because of its physical size and the cable lengths that would be encountered when four stores are provided in an office, the store is connected to the rest of the control unit by way of an ac bus system. Thus, within the store, there is an 18-bit address register which is cleared and filled by the signals on the address bus. All stores receive the address information and a "read" command signal from the bus and the store identified by the two most significant bits of the address responds on the answer bus. A store contains up to four connectorized memory units, each of which contains a twistor memory module and its associated address decoding and high current access circuitry. Each unit stores 16,384 22-bit words in the form of 4096 88-bit words. Readout signals from corresponding bits of the four memory units are paralleled through a resistive impedance matching network and amplified in 88 readout amplifiers.

On the basis of two of the address bits, a one-out-of-four selection is made on the 88-bit word to produce a 22-bit word which is transmitted to the program control on the answer bus. Since, on the basis of the address, only one memory unit is active at any time, the access current regulation, timing control, readout circuits, and answer cable drivers are common to the four memory units.

Fig. 5-No. 2 ESS program store.

# 3.3.3 Maintenance

In order to provide rapid detection of access circuit failures, the program store includes checking circuits to verify the correct operation of the store on every read cycle. These circuits verify the correct flow of module access currents and the correct selection of a unique current path through the selected module. In the event that these conditions are not met in a given read cycle, a "program store error" signal is sent to the program control and maintenance center circuits and certain bits of the readout information sent on the answer bus are forced to be "ones," depending on which of the check circuits detected the failure conditon. This provides for fast resolution of a failure to specific circuit packages by the diagnostic program. All that is required is that the program read a word which contains all "zeros." As in the call store, there are dc control signals brought to the program store from the maintenance center to simulate the various kinds of failures that the check circuits are designed to detect. These signals are used to verify the integrity of the check circuits and may also be used in resolving certain kinds of failures.

There is also a set of maintenance signals which provide for varying

**2**628

### CONTROL UNIT

the sense amplifier threshold voltage either manually or by program to obtain a measure of the operating margin of the store. There are two discrete amounts by which the threshold can be varied by the program from its nominal position. These are called "inner margins" (closest to nominal) and "outer margins." A store which works properly with the threshold voltage at the "outer margins" is presumed to be in good health and to contain well written magnet cards.

A store which fails to work with outer margins applied but does work with the inner margins applied is presumed to contain either an incipient hardware fault or poorly written cards. If replacing the cards with a well written set does not enable the store to operate with outer margins applied, then the existence of an incipient failure may be concluded. If a store fails to work when "inner margins" are applied, then a hard fault is presumed to exist in the store. Thus, by virtue of the access checking circuits and the program controlled maintenance signals, hardware failures and magnet card writing errors can be quickly and accurately detected and diagnosed.

## 3.3.4 Growth

To provide orderly simple growth procedures, as well as to minimize installation and repair time, the physical design of the program store uses connectors at both the frame and unit level. This means that a frame can be added to an office by simply bolting it to the floor, connecting power, and connecting it to the adjacent frame by plug-in connectors. Furthermore, a memory unit can be added to an existing frame (either as growth or replacement of a failed unit) by simply bolting it in place in the frame and plugging umbilical cables from the unit into matching connectors in the frame. As a result, a given office can have from 16,384 to 262,144 words of storage in 16,384-word increments. The estimated time to add an increment to an existing frame or to add a frame is less than one hour.

### IV. ORDER STRUCTURE

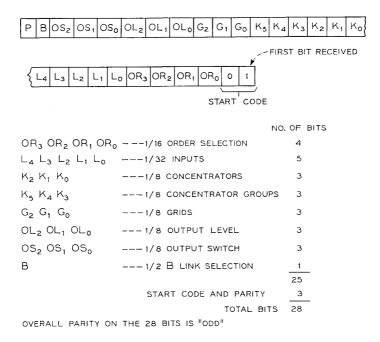

The No. 2 ESS order structure was designed with emphasis on data processing rather than arithmetic operations. The basic 22-bit instruction words, shown in Fig. 6, are divided into two types. The type 1 contains one instruction with a 5-bit operation code, 16-bit address, and a transfer check bit. This check bit is used for detecting illegal transfers and has proved to be quite useful in indicating hardware faults as well as program faults resulting from bugs or data mutilation. The instructions belonging to the type 1 class are rather few.

Fig. 6-No. 2 ESS instruction formats.

They are used primarily for absolute program transfers and for supplying constants and masks for various functions.

The type 2 word consists of two 10-bit instructions, each with a 5-bit operation code and a 5-bit address. As for the remaining two bits, one is assigned as a transfer check bit and the other as a parity check bit. The 5-bit address is used to denote a value or a modifier. For example, a value associated with a rotate instruction specifies the amount of rotation. A modifier associated with the gating operation specifies the source and destination register combination. In many cases, the combination of the two 5-bit fields can be more appropriately considered as a 10-bit operation code rather than the division just outlined. In addition, the 10-bit operation can be assigned as a full-word instruction and the second 10-bit field is available for option bits, modifiers, addresses, or other pertinent data. The majority of instructions fall into the simple type 2 category and provide for efficient program storage use.

### 4.1 Clock and Cycle Timing

The operation of logic circuitry within the central processor is generally synchronous, whereby the clock circuit provides all the basic timing signals. These signals define a machine cycle and phases within that cycle. The duration of a machine cycle is primarily determined by the rate at which the instruction can be fetched from the program store. With the type 2 order format of two instructions per program word, a machine cycle is set equal to one-half of the program store access time, or 3 microseconds. The number of clock phases is chosen to permit many of the short word instructions to be implemented in one cycle, thereby making it possible to process two short word instructions while the next word is being fetched from the program store. This maximizes the average data processing rate of the system.

A machine cycle consists of eight 750-nanosecond clock phases with

2630

### CONTROL UNIT

each pulse overlapping the preceding and succeeding pulses by onehalf their width (375 nanoseconds). This arrangement provides an adequate number of intervals to fully realize the data processing steps of the system in response to a diversity of instructions. At the same time, it is consistent with the speed of the transistor-resistor logic gate. The basic timing signal is provided by a  $2-\frac{2}{3}$  MHz crystal-controlled oscillator with the output from the on-line oscillator driving the clock in the off-line processor. In this way, synchronism between the processors is maintained.

The clock circuit provides timing signals throughout the entire system. These signals coordinate the various activities as dictated by the program sequence. Improper timing not only causes errors in the system, but causes them in such a manner that they are extremely difficult to diagnose. For this reason, error detection circuits have been incorporated into the clock. Furthermore, accessibility is provided to allow ease of program check of the clock circuitry for fault detection and diagnosis.

### 4.2 Order Decoding

The central processor decodes and executes only one instruction at any given time. Most of the orders are relatively simple, that is, setting and clearing various registers and bits, gating data from one register to another, or testing various registers and bits. The decoding of some simple instructions leads directly to the specified actions without any additional logic circuitry. In the more complex instructions, outputs from the order decoder are combined logically with the appropriate system conditions and clock signals, thus producing the necessary controls required for implementing a given order.

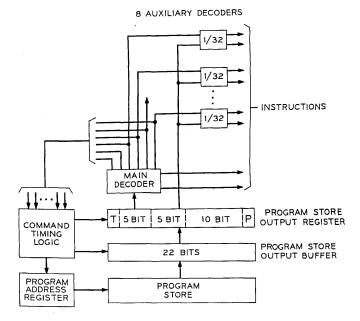

Each order, regardless of its format or complexity, has a 5-bit operation code and is decoded into one lead active out of 32. For most fullword and for some half-word orders, the address portion of the instructions (16-bit or 5-bit) is used directly as an address or a constant. These instructions are concerned mainly with providing direct addresses for program transfers and call store access, loading registers with constants, or providing data for certain logical operations. For the remaining half-word orders, the address and the operation code form a 10-bit binary combination that specifies a unique instruction. These instructions are decoded by two stages of one-out-of-32 decoders (Fig. 7). Eight outputs in the main decoder are dedicated to enabling one of eight auxiliary decoders. Each one decodes the 5-bit address to one lead active out-of-32 basis when it is

Fig. 7—Instruction order decoding arrangement.

selected by the output from the main decoder. This arrangement accommodates numerous short and simple instructions.

The decoder outputs extend throughout the system to implement the prescribed actions for each instruction. Outputs for a subset of orders extend to the maintenance center and to the duplicated central processor to permit the on-line machine to communicate with the off-line processor for maintenance purposes. The main decoder outputs also combine logically in the command timing logic to control the flow of instructions from the program store to the decoders.

### 4.3 General Description of Order Flow

The flow of program store information is normally in sequential order with the program address incremented by one each time the store is read. At times, it is necessary to branch from the regular sequences and transfer to a new one. The address will then be changed completely corresponding to a starting point for a new sequence.

The 22-bit output from the program store is first temporarily stored in a flip-flop register. It acts as a buffer for storing the information until the preceding instruction has been fully processed. The information is then gated to the program store output register for decoding and executing. Immediately thereafter, the program address counter is advanced by 1 and the program store is instructed to read the next sequential word.

The buffering action of the program store output buffer permits the next program word to be read while the instruction in the program store output register is being executed, thus reducing the overall sequencing time. If a transfer should be executed, the revised address, rather than the next sequential location, will be used in addressing the store. However, if the next location has been read, and a transfer should be executed, the contents of the program store output buffer will be discarded. The store is read at the new location.

In many cases, concurrent operation of executing the present instruction and reading the next program word requires no additional time because of transfers. If the word contains two short instructions, the decoder acts on the left one first. After the first instruction has been executed, the second instruction is then gated to the left half of the program store output register for decoding and execution. Upon completion, the new information (the next program word) in the program store output buffer is gated to the program store output register. The instructions are thus stepped along one at a time to the decoder circuit.

The program store can be read once every 6 microseconds. Consequently, most of the half-word instructions are implemented in 3 microseconds to allow the program store to operate at its maximum rate. The full-word instructions are allotted a minimum of 6 microseconds since the next word is not available for that length of time.

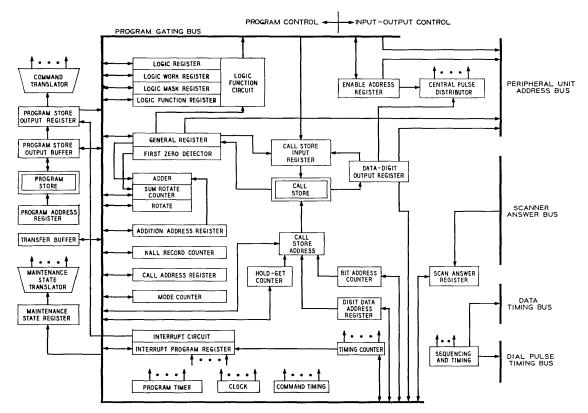

## 4.4 Data Transfer and Register Functions

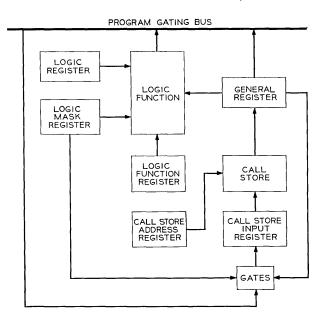

The central processor, as shown in Fig. 8, contains a large number of flip-flop registers in addition to the data processing logic. In general, the content of any one register can be gated to any other register in the system. The transfer of information is done by means of the common bus designated as the program gating bus. Most of the registers are 16 bits wide, with two sets of gates (input and output) associated with each. The corresponding bits from the output gates are oned to form the common bus outputs, fanning out to all parts of the system.

Normally, all the input and all the output gates are disabled by their respective control signals. In transferring information from one

Fig. 8 - No. 2 ESS call processor block diagram.

register to another, the output gates from the first are enabled to the gating bus and the input gates to the second are enabled from the bus. The use of a common bus is an excellent method of transmitting data signals within the processor, keeping the number of gates and the number of long leads to a minimum. The bus outputs extend to the input-output circuit, the duplicated control unit, and the maintenance center to allow data transfers via the bus among the circuits under programmed control.

There are several registers associated directly with the operation of the call store. As Section V elaborates, this store is time-shared between the processor and the input-output circuits. The outputs from the store are directed either to the general register in the processor or to the digit-data output register in the input-output depending upon which circuit is accessing the store. In addressing the addition address register or the call address register may be gated to the call store address register for use as an address in reading or writing. The data in the call store input register, normally gated from the general register, is the store input.

The registers mentioned thus far are related mainly to the operation of the call store and the program store. Other functional flip-flop registers are used either with associated logic circuits for data manipulation by the program or are dedicated to various system functions. The data modifications involve such functions as addition, rotation, identification, and marking the least significant zero in a register, and various logic functions of two variables. Some of the specific system functions are concerned with interrupt facilities, subroutine facilities, program timing, and maintenance features.

Adding to the numerous flip-flop registers in the system, is the call store, which is segmented into many registers. Much of the call processing program is concerned with call store registers. A group of eight words is assigned as a register or record for each call in progress. Several instructions are provided for quick access to these records.

## 4.5 Transfer and Decision-Making Orders

Call processing programs tend to be highly decision-oriented. In order to facilitate decision making, a multiplicity of test instructions are provided to check various data words and individual bits of certain data words. Test instructions indicate their result by the state of the condition flip-flop which is later utilized by a conditional transfer instruction. If the specified test condition is satisfied, the condition flip-flop is set to the "1" state; otherwise, it is reset to the "0"

state. Many system functions also affect the state of the condition flip-flop. For example, in adding two binary numbers, the end carry is stored in this flip-flop. Most of the decision making is based the state of the condition flip-flop.

Many conditional transfers involve short jumps, hence coding economy can be realized by the use of a 5-bit address. When a transfer is made, the low order five bits of the current address are modified. This range, however, can be extended by preloading the transfer buffer with the next five higher order bits. In this case, the five bits from the instruction and the five bits from the transfer buffer form the low ten bits of the program store address when a transfer is made. In addition to short transfers, the entire range of the 18-bit program store address is accessible by the long, or full, transfer instruction. The low 16 bits are provided by the instruction while the remaining two bits come from the transfer buffer. Indirect transfers, that is, transfers to an address contained in a system register, are also provided.

### 4.6 Data Manipulation Orders

Data manipulation orders allow the operation on data, contained in system registers, in a particular manner to implement the call processing functions. Logical rather than arithmetic needs are paramount. However, a binary ADD order is included in the instruction repertoire. This allows other arithmetical operations to be implemented rather easily by a software combination of other logical operations.

A very flexible and useful set of orders for data manipulation is the Boolean function of two variables. The "general register and the logic register are the two variables which combine logically to form the four minterms  $(\tilde{G}_n \tilde{L}_n, \tilde{G}_n L_n, G_n \tilde{L}_n, G_n L_n)$  bit by bit. The subscript n represents a unique bit of the general register (G), or logic register (L). The 4-bit logic function register (a, b, c, d) specifies the coefficients of the minterms to give the 16 possible combinations. The Boolean function of two variables represented by:

$$f(G_n, L_n) = a\bar{G}_n\bar{L}_n + b\bar{G}_nL_n + cG_n\bar{L}_n + dG_nL_n$$

generates many useful logical functions. For example, if a = d = 1and b = c = 0, the function  $(\bar{G}_n \bar{L}_n + G_n L_n)$  is used to match or compare two binary numbers. The results are placed in the logic work register and, optionally, also placed in the general register. The logic mask register controls or selects the bits in which the logic function is to be performed.

Most of the data in the call store are continuously undergoing changes. In many instances, the data read out are logically operated on with the result written back into the store. This usually involves a logical operation between two memory cycles. Since the operation of read-change-write occurs rather frequently in the system program, a considerable savings in program words and real-time can be realized by combining all three steps. This is possible within the framework of one memory cycle with no additional timing penalty. More importantly, it eliminates the possibility of having an interrupt program modifying the same word in the midst of read-write-change operation. Therefore, the store interwrite problem is avoided. Figure 9 shows that the data return to the call store input for writing may come directly from the general register or from the logic output via the gating bus or a combination of the two. The combination is a form of insertion masking which permits the bits specified by the logic mask register to be returned unchanged directly from the general register to the call store input register. The other bits are modified according to the content of the logic register and the setting of the logic function register.

Other useful data manipulation functions include rotation of a register's contents and a particular function of detecting and identifying the rightmost "0" in a register. The latter function's implementation by several conventional instructions is rather awkward and time consuming. Therefore, a special order, find low zero test, is provided to facilitate operations such as the selection of idle trunks. The status of each trunk is indicated by a binary bit, a "0" corresponds to the idle condition and a "1" to the busy condition. A word of 16 bits represents a group of 16 trunks with the bit position denoting the trunk number. In the find low zero test instruction, the logic searches for the first zero in the general register, starting with the least significant bit, and successively checks through the higher order bits in sequence until a zero is found. When a zero is detected, the logic automatically ignores the remainder of the bits, sets the selected "0" to "1," records the bit position, and marks the condition flip-flop to "1" to indicate finding an idle trunk.

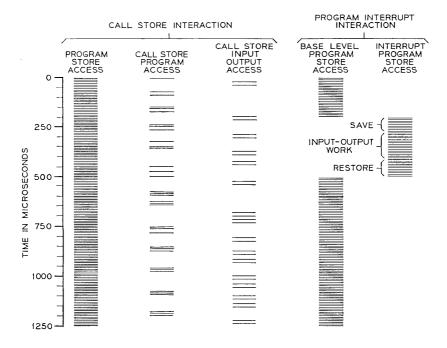

## 4.7 Interrupt Facilities

A multilevel interrupt mechanism is provided in the central processor to permit a signal to enter at any time and seize control of the system. The interrupt circuit responds to an interrupt request by injecting or replacing the next program word with a program in-

Fig. 9—Call store operation.

terrupt begin order. The order stores the program address where the program was interrupted, and then the program transfers to the entry point of the appropriate interrupt program. The first chore in the execution of the interrupt program is to store the state of the central processor in memory. At the conclusion of the required work function, the central processor is restored to its initial state. The interrupt program then ends with a program interrupt end order which transfers back to the previous interrupted program.

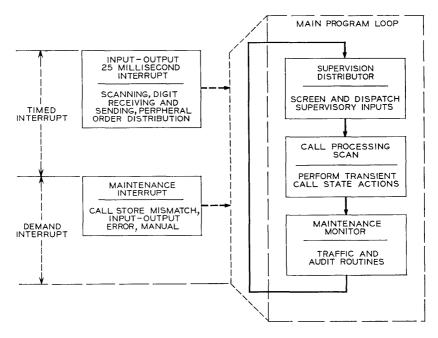

Presently, interrupts are used for two functions. One is to handle input-output data processing, that is, digit receiving, digit sending, scanning, data sending, and peripheral communication functions. These tasks are scheduled regularly in real time at 25 (or a multiple of 25) millisecond intervals.

The other function is to gain immediate access to one of several maintenance programs. The interrupt program register and logic are arranged in a hierarchy of eight levels to allow the running of the program with preference to the most urgent or highest level present at any time. Only three of the eight interrupt levels have been assigned; two for maintenance and one for input-output. The remaining five are for future growth and other applications of the No. 2 ESS control complex.

#### CONTROL UNIT

# **4.8** Subroutine Facilities

Many of the No. 2 ESS programs consist largely of a series of subroutine calls. This not only has the advantage of saving program store words, but also makes debugging simpler since a subroutine need only be debugged once. A special push-down address arrangement has been implemented and storage allocated in the call store to facilitate entry, nesting, return, and releasing of major system registers for use by subroutines. This arrangement provides 32 groups of eight words within the call store. Each time a new subroutine level is entered by means of a transfer and save address order, the pushdown level or the hold-get counter is decremented by one. In execution of the transfer and save address order, the return address is stored within the eight-word block. The remaining words are available for the major system registers. Special HOLD and GET instructions are provided to facilitate storage and retrieval of data between a selected register and the call store. When the subroutine is returned via the transfer to saved address order, the push-down level (hold-get counter) is incremented by one.

# 4.9 Orders for Repetitive Functions

Certain tasks are very repetitive and can be accomplished by a sequence of operations which is repeated a predetermined number of times forming a loop. Each time the program is repeated, different data are encountered. The transfer on index instruction in the No. 2 ESS is used primarily for program loops. An 8-bit transfer on index counter (kall record counter) is used to keep track of the number of loops. In executing the transfer on index instruction, when the kall record counter is not equal to 1, the kall record counter is decremented by 1 and a transfer is made to the beginning of the loop to repeat the given set of operations.

Many of the repetitive functions can be implemented rather easily with program loops using the transfer on index instruction. However, there are some repetitive functions that must be performed very frequently by the system. Although the program to be repeated usually contains only a few instructions (including transfer on index), the program's high usage consumes a considerable amount of system time. A real-time saving can be realized by combining these instructions into a single highly efficient macroinstruction. One order thus performs the actions of several and is repeated as many times as is specified by the contents of the kall record counter unless the data are

# 2640 THE BELL SYSTEM TECHNICAL JOURNAL, OCTOBER 1969

being tested by the program and satisfies the exit conditions prior to that. The real-time saving is obtained chiefly by: (i) not having to fetch a series of instructions from the program store, ( $\ddot{u}$ ) not having to perform a transfer at each loop back, and ( $\ddot{u}\ddot{u}$ ) concurrent operation of a set of instructions.

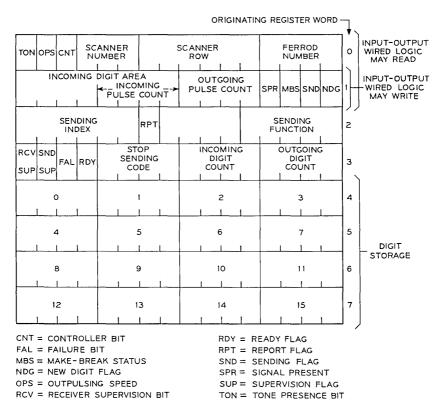

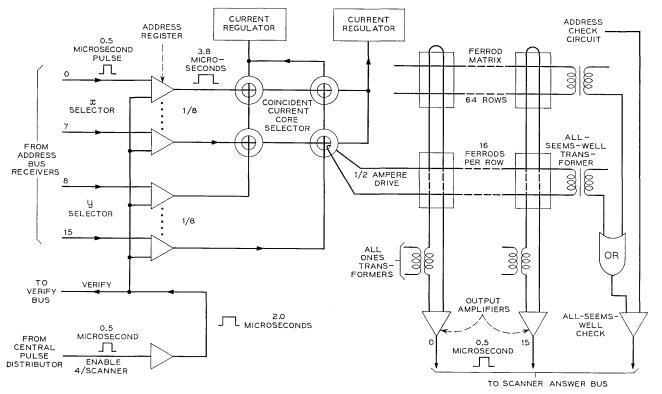

There are several repetitive or macroinstructions used in the No. 2 ESS. Among these are: (i) an instruction for performing logic on the contents of a number of words contained in call store, (ii) an instruction that scans ferrods and compares the results with call store status words, (iii) an instruction for sending serial data to peripheral units, and (iv) an instruction that scans call store records and performs indirect transfers to programs that process the records. The last instruction is the ADV (advance) command and is described in the call processing article in this issue.<sup>2</sup> The ferrod scanning instruction as well as the other peripheral unit orders are described in Section 5.4.

# 4.10 Maintenance Facilities

In the duplicated system under normal conditions both the on-line and off-line processors are run in synchronism while handling the input-output data and solving their problems independently. Only the outputs from the on-line processor are permitted to activate the external equipment, such as setting up network connections, outpulsing, and data sending. In this synchronous mode, both call stores contain identical information and both processors are in step, executing the same sequence of instructions. As a detection means, the information being written into the call stores is matched by circuitry in the maintenance center. In addition, a number of error checking circuits are strategically located throughout the system for the detection and diagnosis of faults. They provide:

(i) Parity checks of words read from the program store (odd parity for the program words, and even parity for the data words),

(ii) Transfer checks to ensure a legal program entry,

(iii) Double output checks for more than one output active from the instruction decoders,

(iv) Sequence checks of the instruction timing logic,

(v) Subroutine level checks for exceeding the number that can be nested,

(vi) System clock checks for the proper sequence and rate of the clock output signals,

(vii) Simultaneous access checks of the call store by the processor and the input-output control,

(viii) Multiple access checks in the call store and the program store,

(ix) Timing checks in the input-output control for checking dial pulse and data timing buses, and

(x) Input-output error checks involving proper access to and response from peripheral units.

Check circuits are generally provided to cope with faults which are too difficult or too time consuming to detect strictly by program. An example is the double output detector which checks for more than one output active from the instruction decoders. Within the central processor one and only one instruction is decoded and executed at any given time. Faults causing no output at all are relatively simple to detect.

If, however, the instruction decoder produces two simultaneous outputs, an additional extraneous instruction will be performed. This can seriously affect the overall operation of the system and produce obscure errors. Therefore, the double output check circuit is incorporated as part of the processor for quick detection and diagnosis. Except for input-output errors, when a check circuit in the on-line system indicates an error condition exists, the faulty processor is immediately taken off line. Input-output error signals are handled by special "working mode" programs which determine the proper actions to be taken.

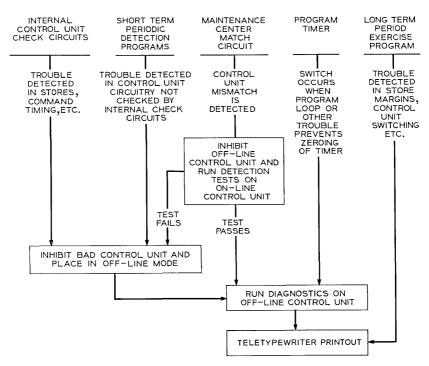

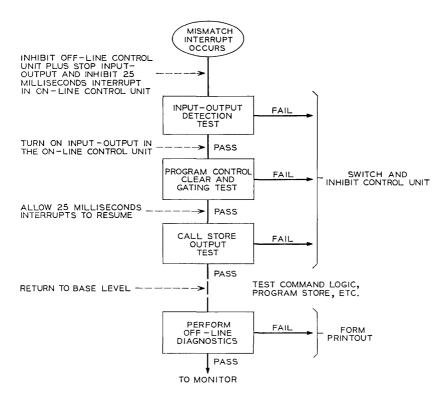

As previously indicated, a method of trouble detection available when the control units are running in synchronism is the matching of call store information by a match circuit located in the maintenance center. A mismatch causes a maintenance interrupt program to run detection tests on the on-line control unit. Upon failure, the control unit is immediately switched off-line and stopped while the other control unit is given an initialized start. In some cases, the faulty processor may be incapable of making any decision. Under this condition, the hardware emergency timer will time out and initiate the switching and initiatization functions.

In order to analyze the defective circuit, the on-line processor has direct access to the off-line machine by means of a set of external orders. Simplicity of implementation rather than coding efficiency has been the goal in the design of these orders since the total number of external orders used in the system program is relatively small. Consequently, each external order is a full word and takes two cycles to execute. The order format consists of a 5-bit operational field and two 5-bit addresses designated as the infield and the outfield. The operation code and the infield form a 10-bit binary combination which specifies the unique operation within the processor. Similarly, the operation code and the outfield specify the unique operation for the other processor. By a proper combination of the functions being performed in each of the two processors, many different operations are possible for communication and information transfer between the two processors and for direct control of the off-line processor. Some of the special orders are exceptionally useful in implementing the maintenance routines of the more difficult logic circuits, such as orders that permit the on-line machine to perform a step-by-step check of the off-line machine, or orders that start and stop the off-line clock to check timing leads.

After the fault has been diagnosed and repaired, the off-line processor must be restored to its normal working mode. In order to do this, the call store must first be updated to contain the same data as the on-line call store. If the complete transfer of the entire store is done by one continuous program, excessive time will be consumed, thereby causing errors in call processing. As a result, the data transfer from the on-line to off-line call store is interleaved with the normal program, moving a small block of words at a time until the entire store is updated. However, the data in the on-line call store is transient and the transferred portion of the store may undergo a continuous change. To ensure that the updated portion of the off-line store remains current, its address and store input data are "slaved" by hardware to the on-line store. When any read or write operation is performed, the same address and input data are used to alter the data in the off-line store. The updating of the call store is thus accomplished by the combination of software and hardware.

# 4.11 Means of Checking Error Detection Circuits

Error detection circuits are checked periodically to ensure their usefulness. When they fail in the error mode, the failures are selfdetecting and are recognized immediately. On the other hand, if the failures prevent the circuitry from giving any error indication, faults normally detected will be ignored. Consequently, a periodic program check of error detection circuitry is essential to guarantee the reliable operation of these circuits. As an aid for testing the check circuits and for testing maintenance equipment that is not easily tested by

#### CONTROL UNIT

normal program functions, a maintenance state register and an associated decoder are provided for simulating faults and test conditions. The outputs from the maintenance state decoder are used, for example, to check the instruction double output detector or to enable a programmed margin check of the call store.

### 4.12 Emergency Switching of Control Unit

In any duplicated system, the mechanism for switching controls must be highly reliable. The emergency timer and associated circuitry provide the very vital function of switching the bad control unit offline and the good control unit on-line. During the process, proper steps are taken to ensure a smooth transition in the transfer of controls.

The timer provides a further protection against faults or errors that cause programs to loop indefinitely or to bypass certain major program functions. The main call processing program is cyclic and returns to the starting point upon completion of all the tasks required by the call processing. The time required to complete one scan varies from scan to scan depending upon the amount of work required of the program. The basic timeout interval is **320** milliseconds. If the program takes longer or does not reset the timer, an equipment or program error has occurred. The timer and its associated logic then produce an output signal to switch controls to the other processor.

There are two timers, one in each processor. The off-line timer is used as "backup" and will take over the task of switching if the online timer does not work. Under most error conditions, immediate switching is performed to minimize any detrimental effect on call processing.

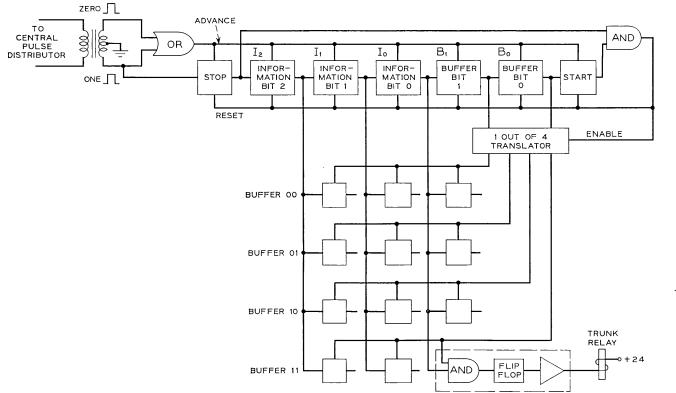

# V. INPUT-OUTPUT FACILITIES

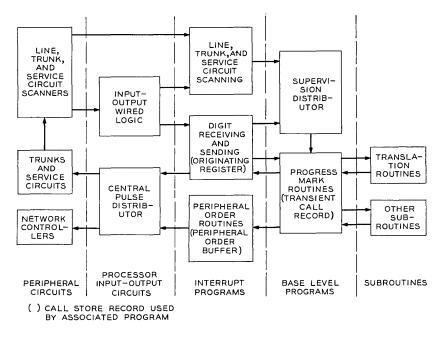

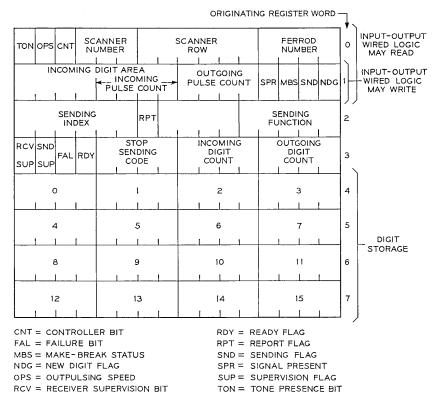

In the No. 2 ESS, all inputs and outputs between the peripheral units and the central processing unit (program control) are handled by the input-output control. Figure 1 shows the control complex block diagram. The input-output control performs the interface function both by acting as an extension of the program control in providing and controlling the special purpose circuitry required to communicate with the peripheral units under control of program instructions and also providing wired logic for autonomously performing a portion of the digit receiving, digit sending, line scanning, and data sending tasks. By assigning the repetitive high rate functions which must be performed

# 2644 THE BELL SYSTEM TECHNICAL JOURNAL, OCTOBER 1969