# Discrete Z8® Microcontrollers

For Computer Peripheral and Consumer Electronics Applications

Includes Specifications for the following parts:

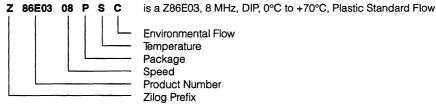

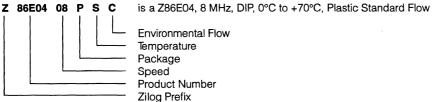

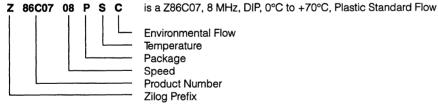

Z86C03 **Z86C08 Z86E03 Z86E08** Z86C30 Z86C04 **Z86E04** Z86E30 **Z86C06** Z86C31 **Z86E31 Z86E06** Z86C40 Z86C07 **Z86E07** Z86E40

Product Specifications Databook

# Discrete Z8® Microcontrollers

For Peripherals and Consumer Electronic Products

**Includes Specifications** for the following parts:

**Z86C03 Z86C08 Z86E03 Z86E08 Z86C04 Z86C30 Z86E30 Z86E04 Z86C06 Z86C31 Z86E06 Z86E31 Z86C07 Z86C40 Z86E07 Z86E40**

## **Databook**

## **DISCRETE Z8® MICROCONTROLLERS**

### **TABLE OF CONTENTS**

| TITLE                                                         | SECTION |

|---------------------------------------------------------------|---------|

| QUICK TAKE — A SUMMARY OF PARTS AND FEATURES                  | A       |

| Z8® PRODUCT SPECIFICATIONS                                    |         |

| Z86C03/C06 CMOS Z8® 8-BIT CONSUMER CONTROLLER PROCESSORS      | 1       |

| Z86E03/E06 CMOS Z8® 8-Bit OTP Consumer Controller Processors  | 2       |

| Z86C04/C08 CMOS Z8® 8-Bit Low Cost 1K/2K ROM Microcontrollers | 3       |

| Z86E04/E08 CMOS Z8® 8-Bit OTP Microcontrollers                | 4       |

| Z86C07 CMOS Z8® 8-Bit Microcontroller                         | 5       |

| Z86E07 CMOS Z8® 8-Bit OTP Microcontroller                     | 6       |

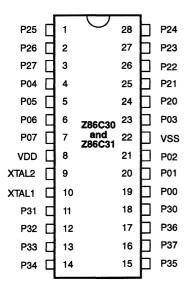

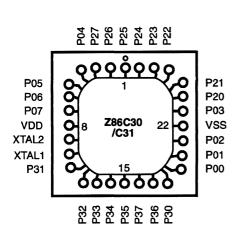

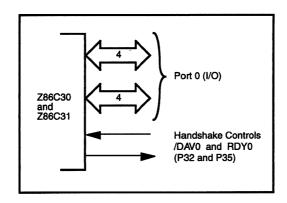

| Z86C30/C31 CMOS Z8® 8-Bit Consumer Controller Processors      | 7       |

| Z86E30/E31 CMOS Z8® 8-Bit OTP Consumer Controller Processors  | 8       |

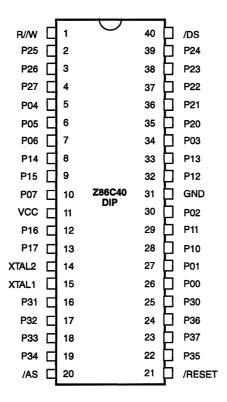

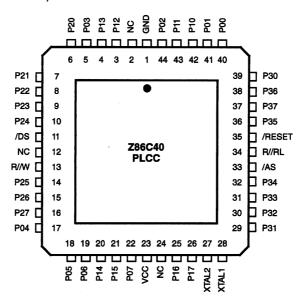

| Z86C40 CMOS Z8® 4K ROM Consumer Controller Processor          | 9       |

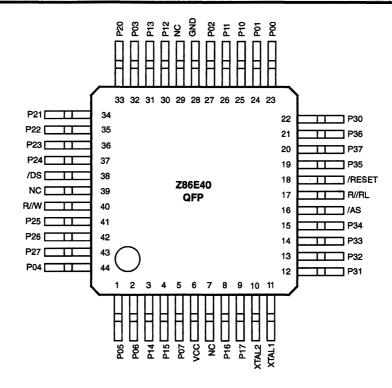

| Z86E40 CMOS Z8® 8-Bit OTP Consumer Controller Processors      | 10      |

| Z8® MICROCONTROLLERS APPLICATION NOTES                        |         |

| TIMEKEEPING WITH THE Z8®                                      | 11-1    |

| Using The Zilog Z86C06 SPI Bus                                | 11-15   |

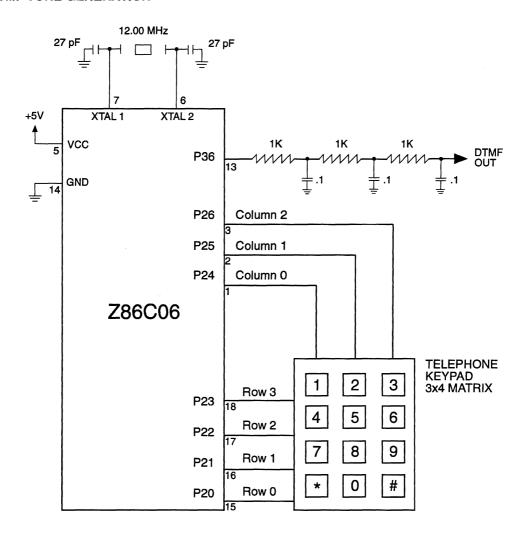

| DTMF TONE GENERATION USING THE Z8® CCP™                       | 11-37   |

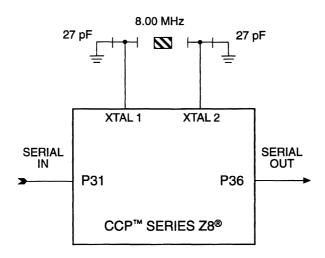

| SERIAL COMMUNICATIONS USING THE Z8® CCP™ SOFTWARE UART        | 11-45   |

| THE VERSATILE Z86C08: THREE KEY FEATURES OF THIS Z8® MCU      | 11-51   |

| THE Z86C08 CONTROLS A SCROLLING LED MESSAGE DISPLAY           | 11-59   |

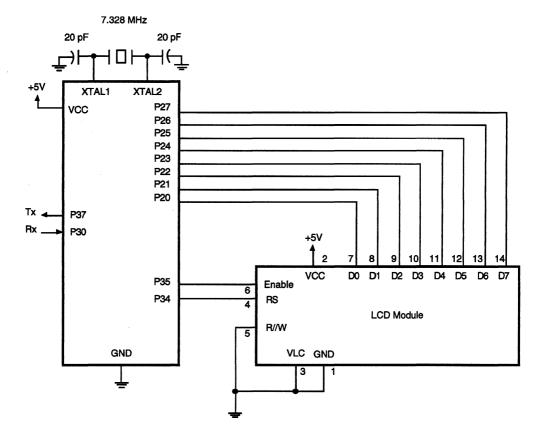

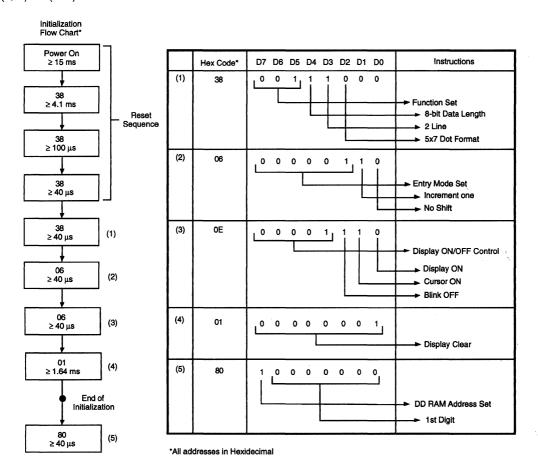

| Interfacing LCDs to the Z8® Microcontroller                   | 11-75   |

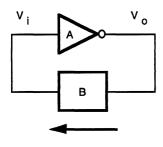

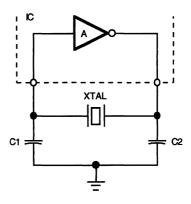

| On-Chip Oscillator Design                                     | 11-89   |

## TABLE OF CONTENTS (CONTINUED)

| TITLE                                                 | SECTION |

|-------------------------------------------------------|---------|

| SUPPORT PRODUCTS AND THIRD PARTY VENDORS              |         |

| Z86C0800ZCO EVALUATION BOARD                          | 12-1    |

| Z86C0800ZDP ADAPTOR KIT                               | 12-2    |

| Z86C1200ZEM EMULATOR                                  | 12-3    |

| Z86E0600ZDP ADAPTOR KIT                               | 12-4    |

| Z86E0700ZDP ADAPTOR KIT                               | 12-5    |

| Z86E3000ZDP ADAPTOR KIT                               | 12-6    |

| Z86E4000ZDF ADAPTOR KIT                               | 12-7    |

| Z86E4000ZDP ADAPTOR KIT                               | 12-8    |

| Z86E4000ZDV ADAPTOR KIT                               | 12-9    |

| Z86E4001ZDF ADAPTOR KIT                               | 12-10   |

| Z86E4001ZDV ADAPTOR KIT                               | 12-11   |

| Z86CCP00ZEM EMUALTOR                                  | 12-12   |

| Z86CCP00ZAC EMULATOR KIT                              | 12-13   |

| Z8®S Series Emulators                                 | 12-14   |

| THIRD PARTY VENDORS                                   | 12-15   |

| SUPERINTEGRATION™ PRODUCTS GUIDE                      | S       |

| ZILOG'S SALES OFFICES, REPRESENTATIVES & DISTRIBUTORS | Z       |

| LITERATURE GUIDE AND ORDERING INFORMATION             | L       |

## Quick Take — A Summary of Parts and Features

| Block<br>Diagram    | 512 Byte ROM  Z8® CPU  WDT 64 RAM  P2 P3                                                                                                                                                                                                                                                             | 1K ROM  Z8® CPU  WDT 128  RAM  P0 P2                                                                                                                                                             | 1K ROM  Z8® CPU  WDT 128  RAM  SPI  P2 P3                                                                                                                                                                                                | 2K ROM  Z8® CPU  WDT 124  WDT RAM  P2 P3                                                                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

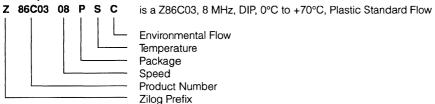

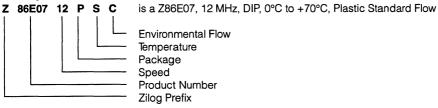

| Part Number         | Z86C03                                                                                                                                                                                                                                                                                               | Z86C04/Z86E04                                                                                                                                                                                    | Z86C06                                                                                                                                                                                                                                   | Z86C07/Z86E07                                                                                                                                                                                                                       |

| Description         | Consumer Controller Processor (CCP™)<br>with 512 Byte ROM                                                                                                                                                                                                                                            | Z86C04 = 8-Bit Low Cost 1 Kbyte ROM MCU<br>Z86E04 = OTP Version                                                                                                                                  | Consumer Controller Processor (CCP™)<br>with 1 Kbyte ROM                                                                                                                                                                                 | Z86C07 = 8-Bit 2 Kbyte ROM MCU<br>Z86E07 = OTP Version                                                                                                                                                                              |

| Process/Speed       | CMOS: 8 MHz                                                                                                                                                                                                                                                                                          | CMOS: 8 MHz                                                                                                                                                                                      | CMOS: 12 MHz                                                                                                                                                                                                                             | CMOS: 8 and 12 MHz                                                                                                                                                                                                                  |

| Features            | <ul> <li>512 Byte ROM</li> <li>64-Byte RAM</li> <li>Two Standby Modes</li> <li>One Counter/Timer</li> <li>ROM Protect</li> <li>Two Analog Comparator</li> <li>Auto Power-On Reset</li> <li>Low-Voltage Protection</li> <li>14 I/O</li> <li>RC Oscillator Option</li> <li>Low-Noise Option</li> </ul> | ■ 1 Kbyte ROM ■ 128-Byte RAM ■ Two Standby Modes ■ Two Counter/Timer ■ ROM Protect ■ Two Analog Comparator ■ Auto Power-On Reset ■ Low-Voltage Protection (ROM Only) ■ 14 I/O ■ Low-Noise Option | ■ 1 Kbyte ROM ■ 128-Byte RAM ■ Two Standby Modes ■ Two Counter/Timer ■ ROM Protect ■ Two Analog Comparator ■ Auto Power-On Reset ■ Low-Voltage Protection (ROM Only) ■ 14 I/O ■ RC Oscillator Option ■ Serial Peripheral Interface (SPI) | ■ 2 Kbytes ROM ■ 124-Byte RAM ■ Two Standby Modes ■ Two Counter/Timer ■ ROM Protect ■ Two Analog Comparator ■ Auto Power-On Reset ■ Low-Voltage Protection (ROM Only) ■ 14 I/O ■ Low Noise Option ■ Programmable Interrupt Polarity |

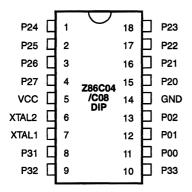

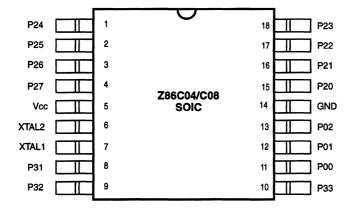

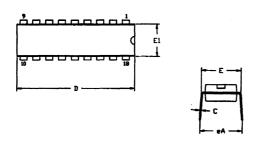

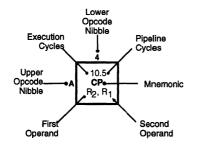

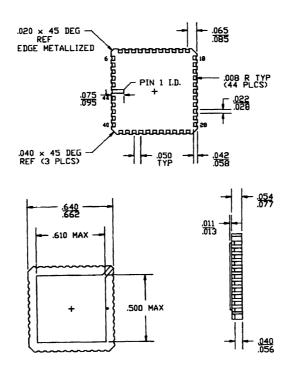

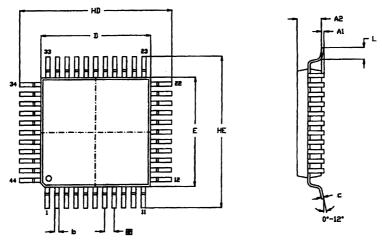

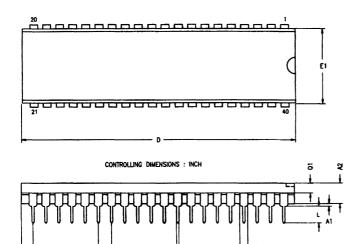

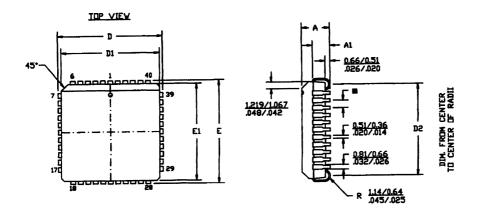

| PACKAGE             | 18-Pin DIP<br>18-Pin SOIC                                                                                                                                                                                                                                                                            | 18-Pin DIP<br>18-Pin SOIC                                                                                                                                                                        | 18-Pin DIP<br>18-Pin SOIC                                                                                                                                                                                                                | 18-Pin DIP<br>18-Pin SOIC                                                                                                                                                                                                           |

| Support<br>Products | Z86CCP00ZEM - Emulator<br>Z86CCP00ZAC - Emulator                                                                                                                                                                                                                                                     | Z86C0800ZCO - Evaluation Board<br>Z86C0800ZDP - Adaptor Kit<br>Z86C1200ZEM - Emulator<br>Z86C1200ZPD - Adaptor Kit<br>Z86CCP00ZEM - Emulator<br>Z86CCP00ZAC - Emulator                           | Z86E0600ZDP - Adaptor Kit<br>Z86C5000ZEM - Emulator<br>Z86C5000ZDP - Adaptor Kit<br>Z86CCP00ZEM - Emulator<br>Z86CCP00ZAC - Emulator                                                                                                     | Contact Your Local Zilog Sales Office                                                                                                                                                                                               |

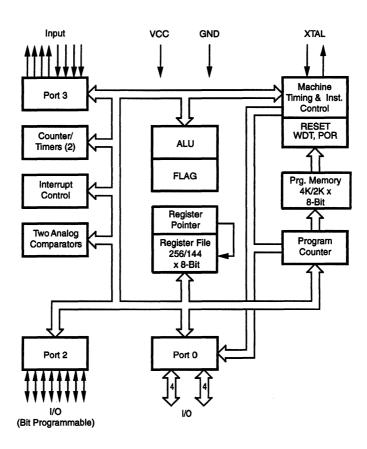

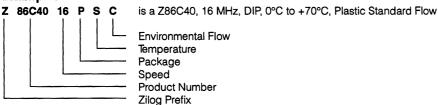

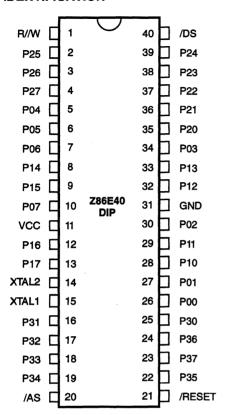

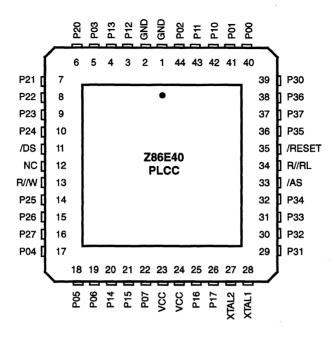

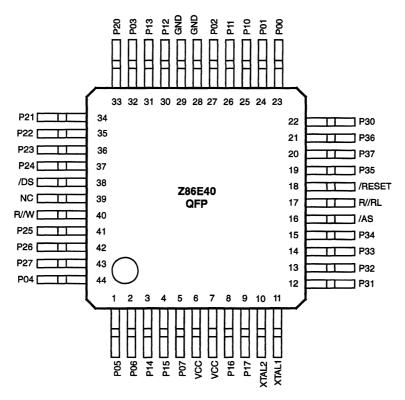

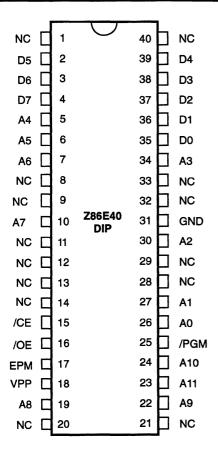

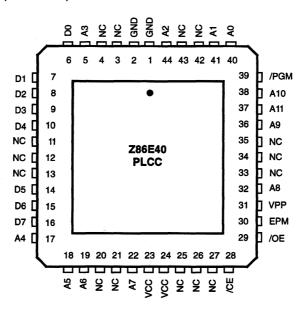

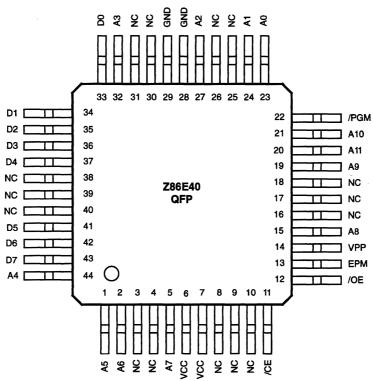

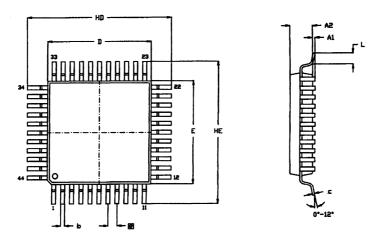

#### Silos Discrete Z8® Microcontrollers **Q**UICK TAKE — A SUMMARY OF PARTS AND FEATURES BLOCK 4K ROM 2K ROM 2K ROM 4K ROM Z8® CPU Z8® CPU Z8® CPU DIAGRAM CPU 236 RAM 128 RAM WOT WDT 128 RAM WDT WDT 236 RAM P1 P0 P3 PO Р3 P0 P2 P3 P2 P2 P2 PΩ PART NUMBER Z86C30/Z86E30 Z86C08/Z86E08 Z86C31/Z86E31 Z86C40/Z86E40 DESCRIPTION Z86C08 = Z8® MCU with 2 Kbyte ROM Z86C30 = Z8® (CCP™) with 4 Kbyte ROM Z86E30 = OTP Version Z86C31 = 8-Bit MCU with 2 Kbvte ROM **Z8®** Consumer Controller Processor (CCP\*) Z86E40 = OTP Version Z86F08 = OTP Version Z86E31 = OTP Version PROCESS/SPEED CMOS: 12 MHz CMOS: 8 MHz CMOS: 12 MHz CMOS: 12 MHz **FEATURES** 2 Kbyte ROM 4 Kbyte ROM 2 Kbvte ROM 4K ROM, 236 RAM ■ 128 Byte RAM 236 Byte RAM ■ 128 Byte RAM ■ Two Standby Modes ■ Two Standby Modes ■ Two Counter/Timers ■ Two Standby Modes Two Standby Modes ROM Protect ■ Two Counter/Timer ■ Two Counter/Timer ■ Two Counter/Timer ■ ROM Protect ROM Protect RAM Protect ROM Protect Two Analog Comparators Two Analog Comparators ■ Four Ports Two Analog Comparators Auto Power-On Reset Auto Power-On Reset ■ Low-Voltage Protection Auto Power-On Reset ■ Low-Voltage Protection (ROM Only) ■ Low-Voltage Protection (ROM Only) ■ Low-Voltage Protection (ROM Only) ■ Two Analog Comparators 24 I/O 24 I/O ■ Low-EMI Mode 14 I/O RC Oscillator Option RC Oscillator Option ■ Low-Noise Option ■ Watch-Dog Timer (WDT) ■ Low-Noise Option ■ Low-Noise Option Auto Power-On Reset ■ Low-Power Option **PACKAGE** 18-Pin DIP 28-Pin DIP 28-Pin DIP 40-Pin DIP 18-Pin SOIC 28-Pin PCB Chip Carrier 28-Pin PCB Chip Carrier 44-Pin PLCC SUPPORT Z86C0800ZCO - Evaluation Board Z86E3000ZDP - Adaptor Kit Z86E3000ZDP - Adaptor Kit Z86C5000ZEM - Emulator Z86CCP00ZEM - Emulator Z86C0800ZDP - Adaptor Kit Z86C5000ZEM - Emulator Z86C5000ZEM - Emulator PRODUCTS Z86E4000ZDP - Adaptor Kit Z86C5000ZPD - Emulator Pod Z86C5000ZPD - Emulator Pod Z86C1200ZEM - Emulator Z86E4000ZDV - Adaptor Kit Z86C1200ZDP - Adaptor Kit Z86CCP00ZEM - Emulator Z86CCP00ZFM - Emulator Z86CCP00ZEM - Emulator Z86CCP00ZAC - Emulator Z86CCP00ZAC - Emulator Z86CCP00ZAC - Emulator

## Z86C03/C06 CMOS Z8® 8-Bit CCP™ Consumer Controller Processors

1

Z86E03/E06 CMOS Z8® 8-Bit OTP CCP™ Consumer Controller Processors 2

Z86C04/C08 CMOS Z8® Low Cost 1K /2K ROM Microcontrollers

8

Z86E04/E08 CMOS Z8® 8-Bit OTP Microcontrollers  $\Lambda$

Z86C07 CMOS Z8® 8-Bit Microcontroller 5

Z86E07 CMOS Z8® 8-Bit OTP Microcontroller 6

Z86C30/C31 CMOS Z8® 8-Bit CCP™ Consumer Controller Processors 7

## Z86C03/C06

CMOS Z8® 8-BIT CCP™ CONSUMER CONTROLLER PROCESSORS

#### **FEATURES**

■ The Z86C03/C06 Devices Have the Following General Characteristics:

| Part   | ROM       | RAM | Speed  |

|--------|-----------|-----|--------|

| Z86C03 | 512 bytes | 60  | 8 MHz  |

| Z86C06 | 1 Kbyte   | 124 | 12 MHz |

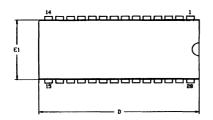

- 18-Pin Package (DIP, SOIC)

- 3.0 to 5.5 Volt Operating Range

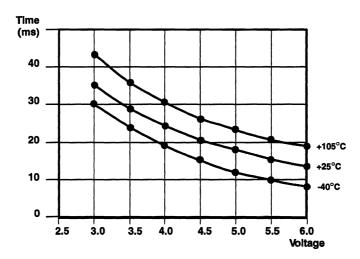

- Operating Temperature: -40°C to +105°C

- Fast Instruction Pointer: 1.5 μs @ 8 MHz (C03);

1.0 μs @ 12 MHz (C06)

- Multiple Expanded Register File Control Registers and Two SPI Registers (Z86C06 only)

- One/Two Programmable 8-Bit Counter/Timers, Each with a 6-Bit Programmable Prescaler

- Six Vectored, Priority Interrupts from Six Different Sources

- Clock Speeds up to 8 MHz (C03) and 12 MHz (C06)

- Software-Enabled Watch-Dog Timer

- Power-On Reset Timer

- Two Standby Modes: STOP and HALT

- Two Comparators with Programmable Interrupt Polarity

- 14 Input/Output Lines (Two with Comparator Inputs)

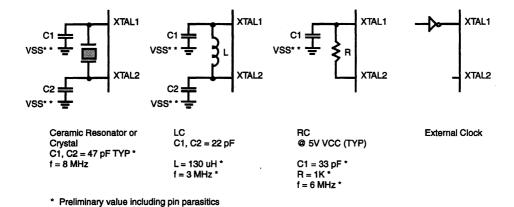

- On-Chip Oscillator that Accepts a Crystal, Ceramic Resonator, LC, RC, or External Clock Drive.

- Serial Peripheral Interface (SPI) (Z86C06 Only)

- Software Programmable Low EMI Mode

- ROM Protect Option

- Auto Latches

#### **GENERAL DESCRIPTION**

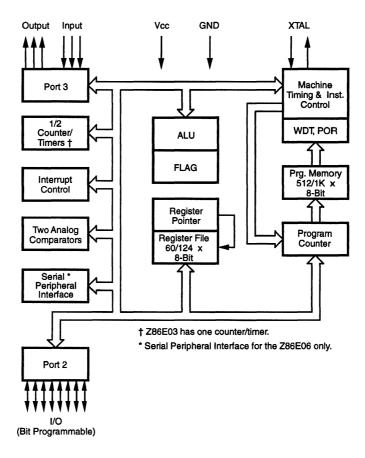

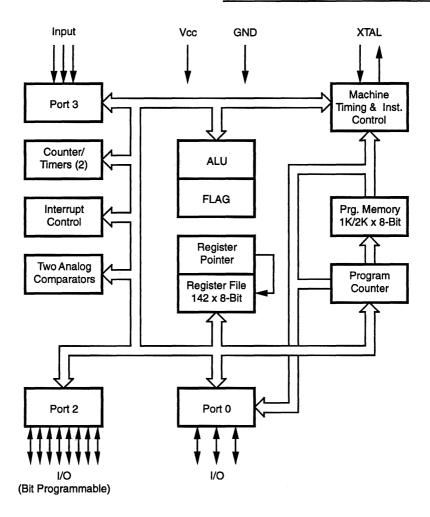

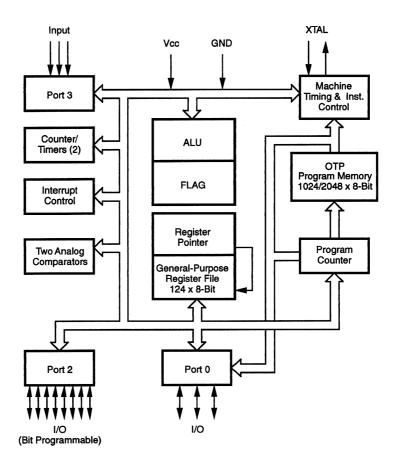

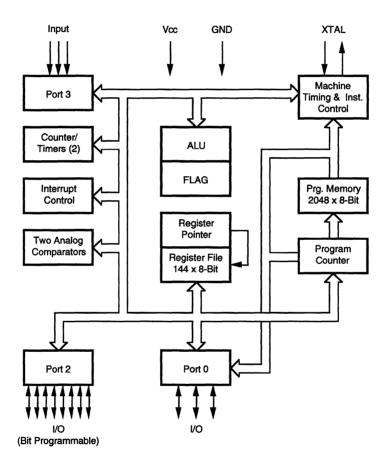

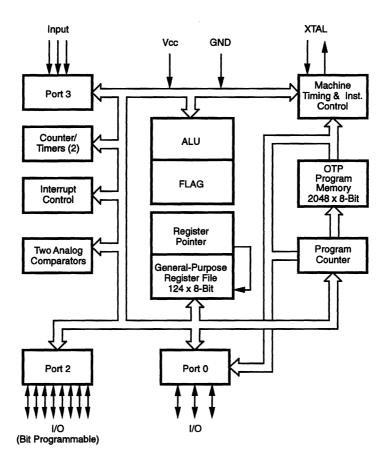

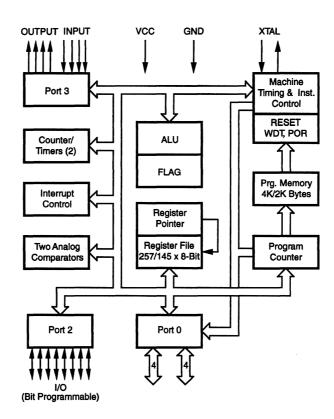

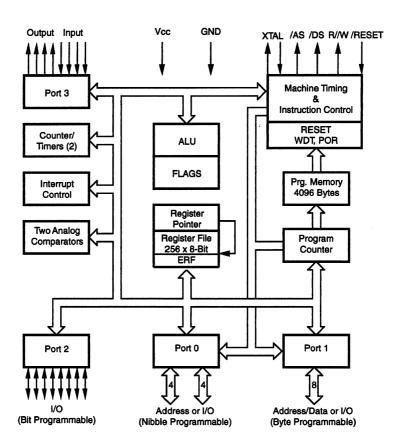

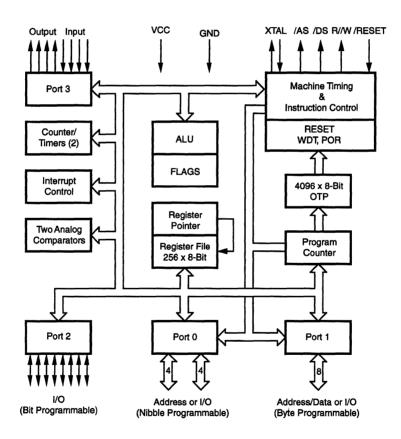

The Z86C03/C06 CCP™ (Consumer Controller Processors) are members of Zilog's the Z8® single-chip microcontroller family with enhanced wake-up circuitry, programmable watch-dog timers and low noise/EMI options. These enhancements result in a more efficient, costeffective design and provide the user with increased design flexibility over the standard Z8 microcontroller core. With 512 and 1K bytes of ROM and 60 and 124 bytes of general-purpose RAM, respectively, these low cost, low power consumption CMOS microcontrollers offer fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy hardware/software system expansion.

The Z86C03/C06 CCP architecture is characterized by Zilog's 8-bit microcontroller core with the addition of an Expanded Register File to allow easy access to register mapped peripheral and I/O circuits. The Z86C03/C06 offers a flexible I/O scheme, an efficient register and address space structure, and a number of ancillary features that are useful in many consumer, automotive, and industrial applications.

For applications demanding powerful I/O capabilities, the Z86C03/C06 provides 14 pins dedicated to input and output. These lines are grouped into two ports and are configurable under software control to provide timing, status signals, or parallel I/O.

#### **GENERAL DESCRIPTION (Continued)**

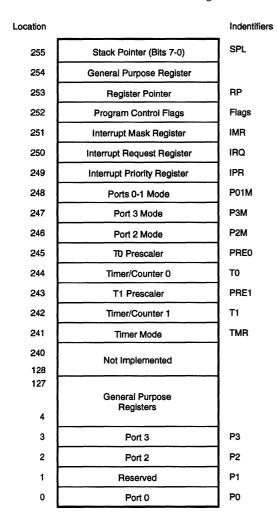

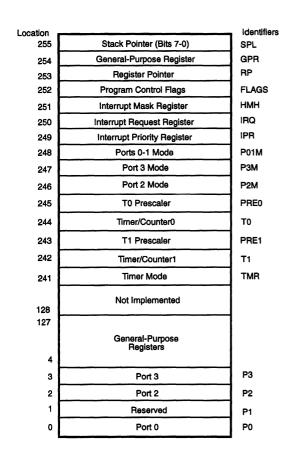

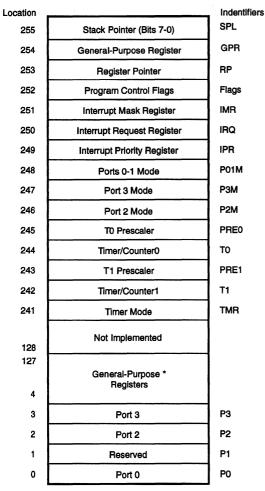

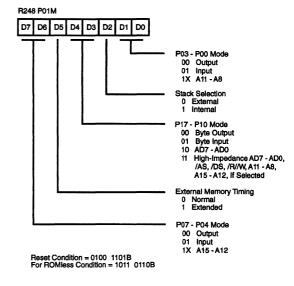

Three basic address spaces are available to support this wide range of configurations: Program Memory, Register File, and Expanded Register File. The Register File is composed of 60/124 bytes of General-Purpose Registers, two I/O Port registers, and 13/15 Control and Status registers. The Expanded Register File consists of three control registers in the Z86C03, and four control registers, a SPI Receive Buffer, and a SPI compare register in the Z86C06.

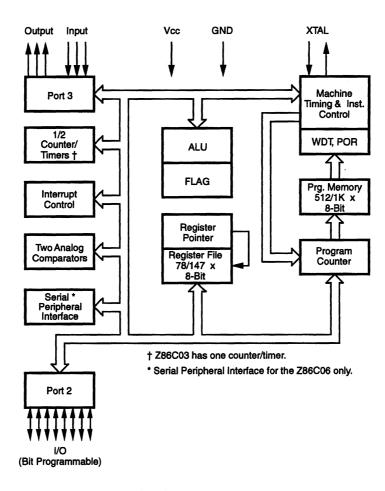

With powerful peripheral features such, as on-board comparators, counter/timer(s), Watch-Dog Timer (WDT), and Serial Peripheral Interface (SPI) (C06 only), the Z86C03/ C06 meets the needs of a variety of sophisticated controller applications (Figure 1).

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B/W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit        | Device          |

|------------|----------------|-----------------|

| Power      | V <sub>∞</sub> | V <sub>DD</sub> |

| Ground     | GND            | V <sub>ss</sub> |

Figure 1. Z86C03/C06 Functional Block Diagram

#### PIN DESCRIPTION

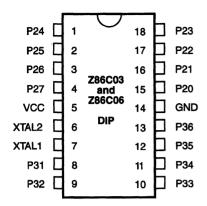

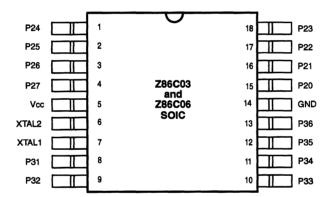

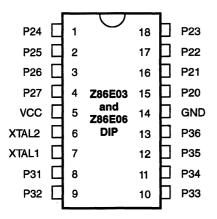

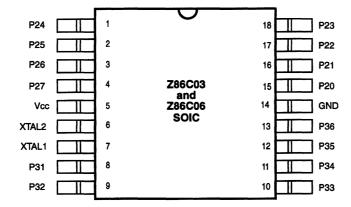

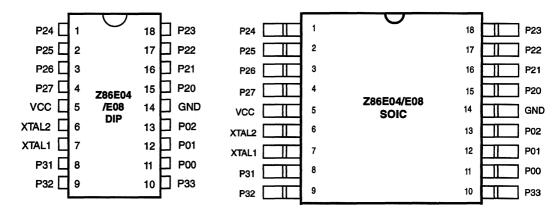

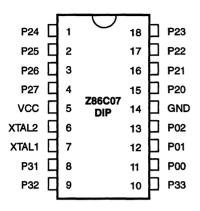

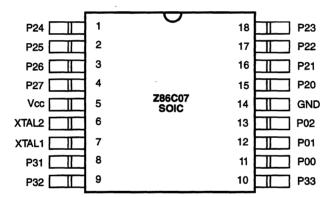

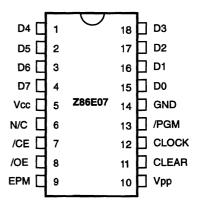

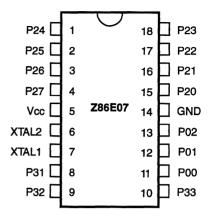

Table 1. 18-Pin DIP and SOIC Pin Identification

| No                  | Symbol                    | Function                                               | Direction                   |

|---------------------|---------------------------|--------------------------------------------------------|-----------------------------|

| 1-4<br>5            | P24-27<br>V <sub>cc</sub> | Port 2, pins 4, 5, 6, 7<br>Power Supply                | In/Output                   |

| 6<br>7              | XTAL2<br>XTAL1            | Crystal Oscillator Clock<br>Crystal Oscillator Clock   |                             |

| 8-10<br>11-13<br>14 | P31-33<br>P34-36<br>GND   | Port 3, pins 1, 2, 3<br>Port 3, pins 4, 5, 6<br>Ground | Fixed Input<br>Fixed Output |

| 15-18               | P20-23                    | Port 2, pins 0, 1, 2, 3                                | In/Output                   |

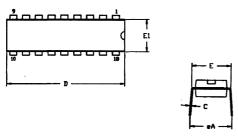

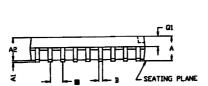

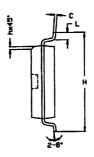

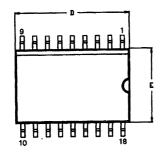

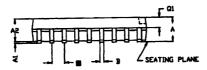

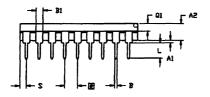

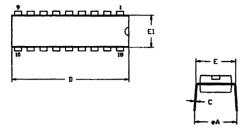

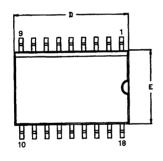

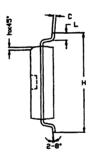

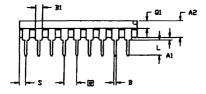

Figure 2. 18-Pin DIP Pin Configuration

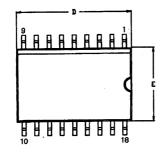

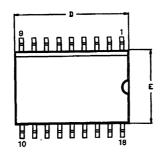

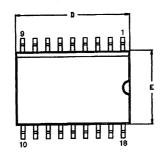

Figure 3. 18-Pin SOIC Pin Configuration

#### **PIN FUNCTIONS**

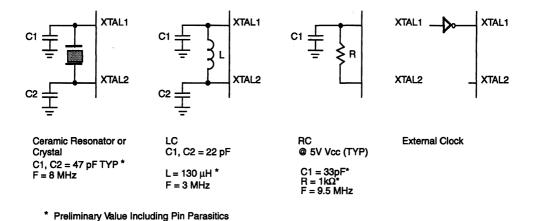

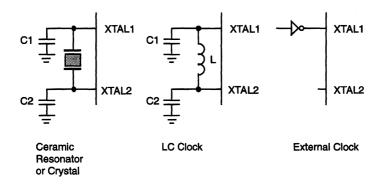

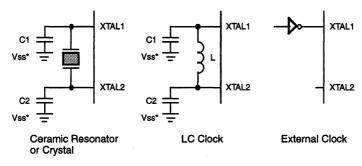

**XTAL1.** Crystal 1 (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC or RC network or an external single-phase clock to the on-chip oscillator input.

**XTAL2.** Crystal 2(time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC or RC network to the on-chip oscillator output.

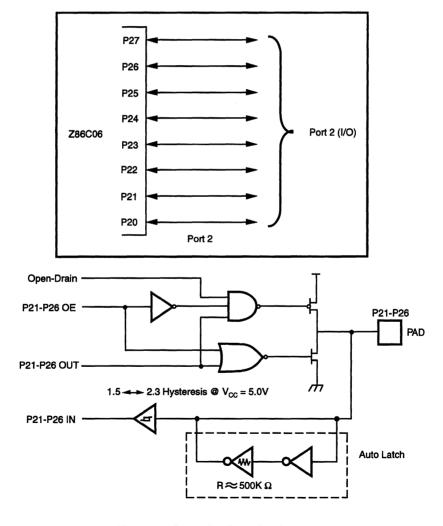

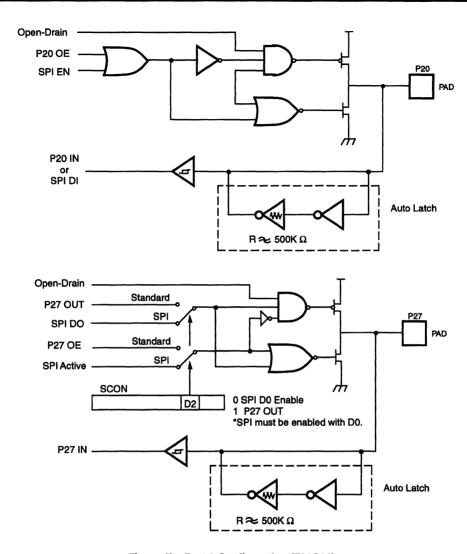

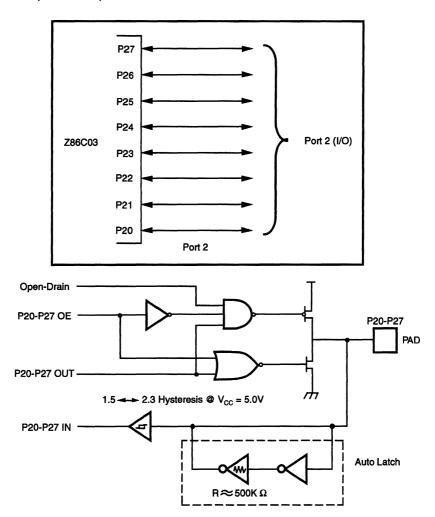

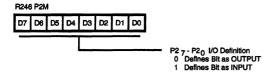

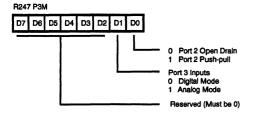

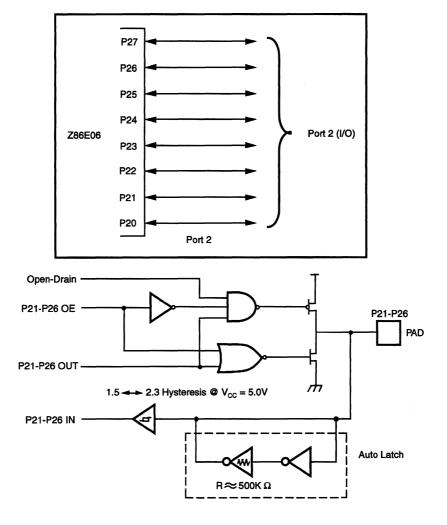

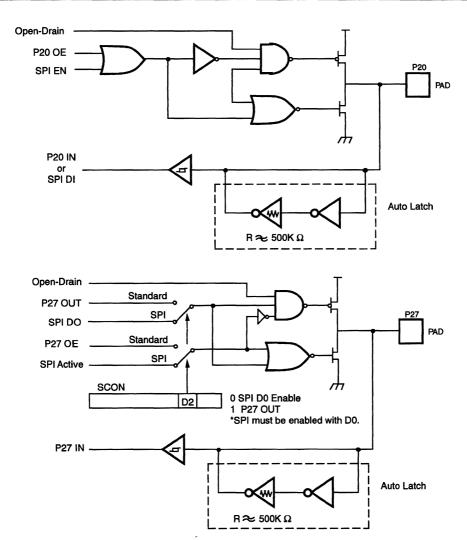

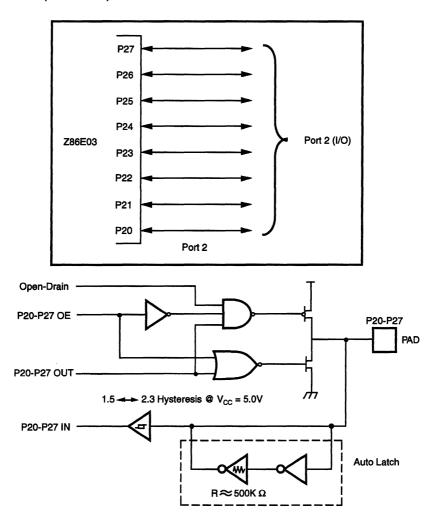

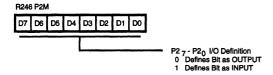

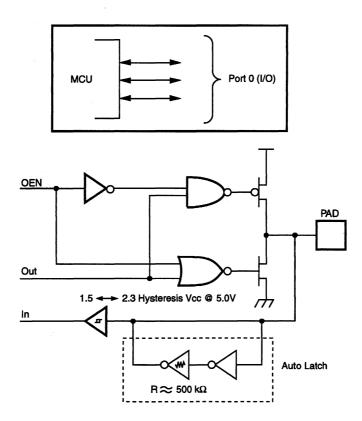

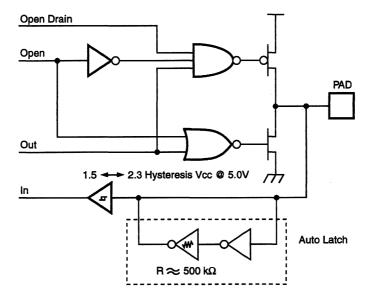

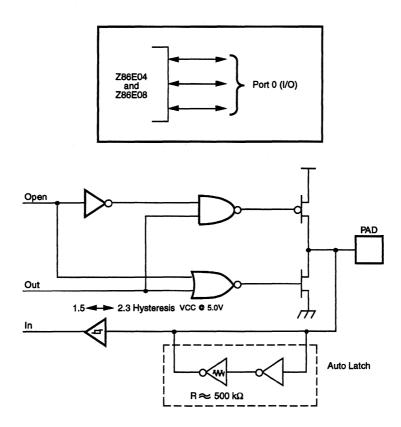

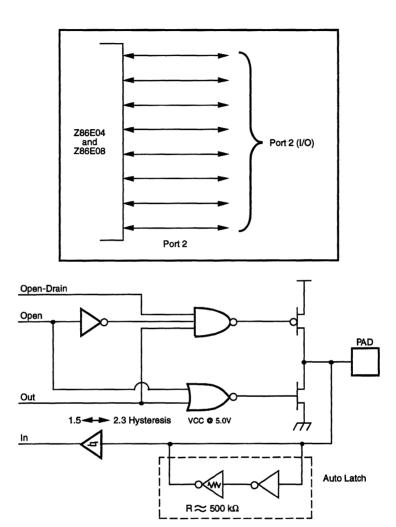

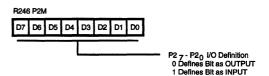

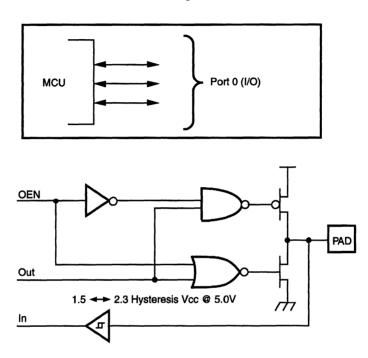

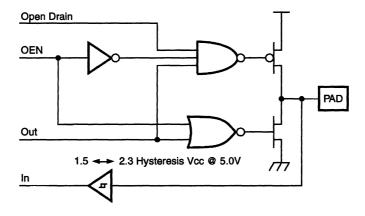

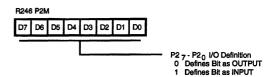

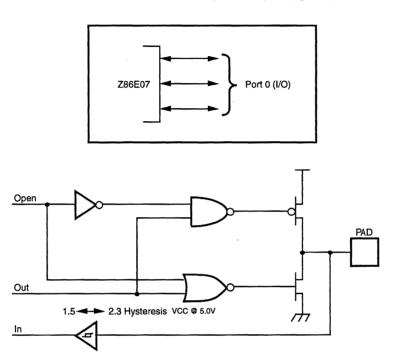

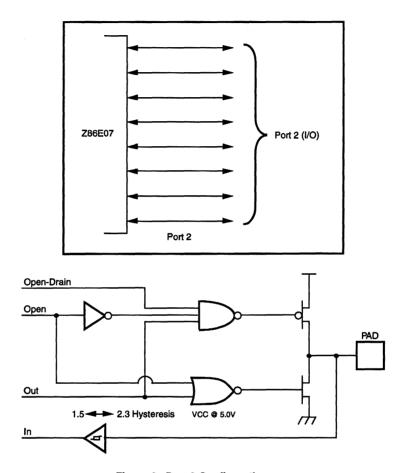

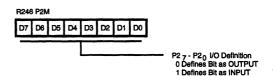

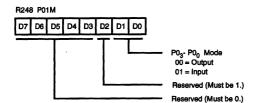

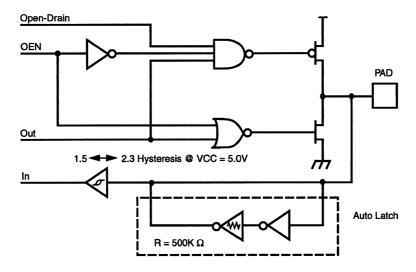

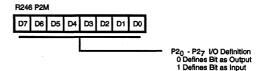

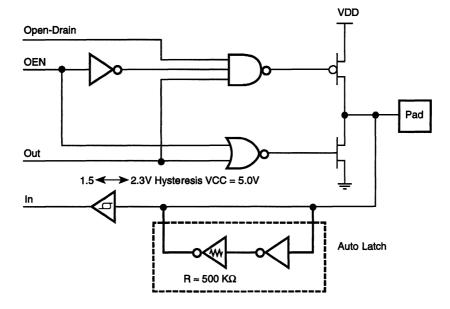

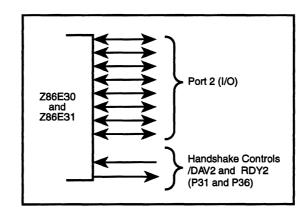

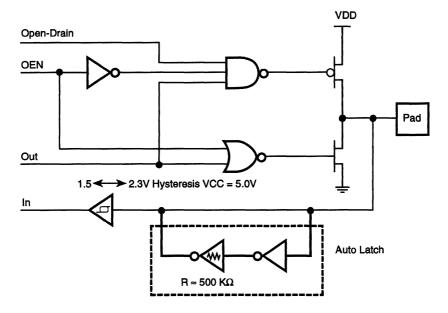

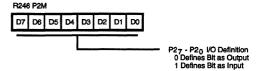

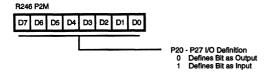

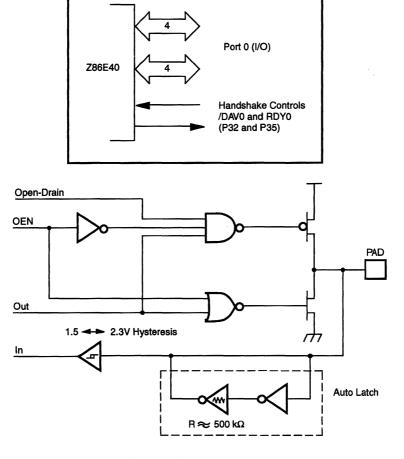

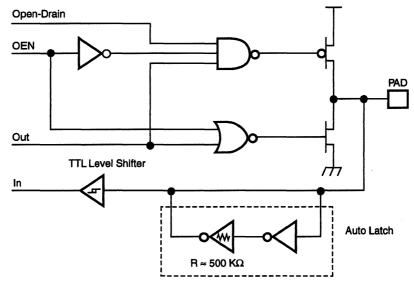

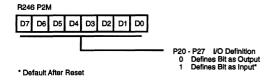

Port 2 (P27-P20). Port 2 is an 8-bit, bi-directional, CMOS compatible I/O port. These eight I/O lines can be configured under software control to be an input or output, independently. Input buffers are Schmitt-triggered and contain Auto Latches. Bits programmed as outputs may be globally programmed as either push-pull or open-drain (Figures 4a, 4b, and 4c). Low EMI output buffers can be globally programmed by the software. In addition, when the SPI is enabled, P20 functions as data-in (DI), and P27 functions as data-out (DO) for the SPI (SPI on the Z86C06 only).

Figure 4a. Port 2 Configuration (Z86C06)

Figure 4b. Port 2 Configuration (Z86C06)

### PIN FUNCTIONS (Continued)

Figure 4c. Port 2 Configuration (Z86C03)

**Auto Latch.** The Auto Latch puts valid CMOS levels on all CMOS inputs (except P33, P32, P31) that are not externally driven. Whether this level is 0 or 1 cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

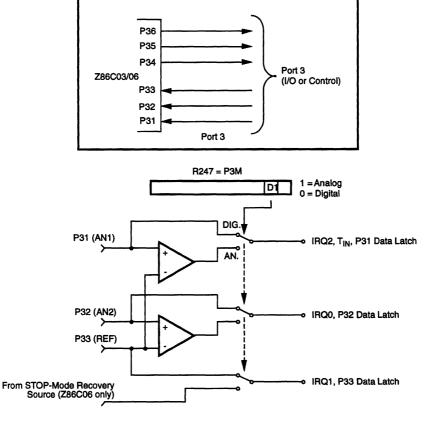

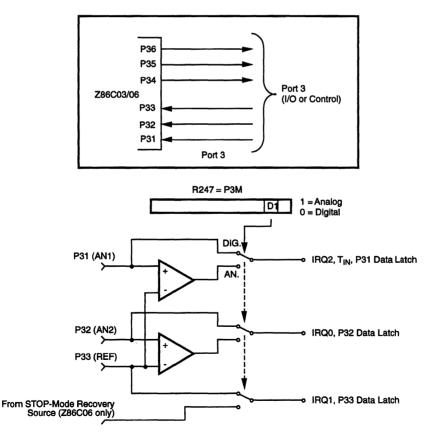

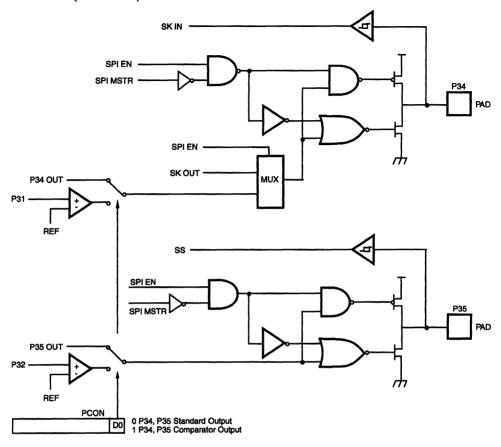

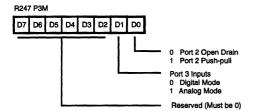

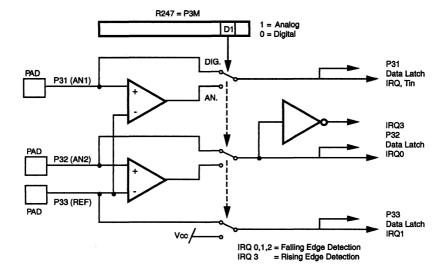

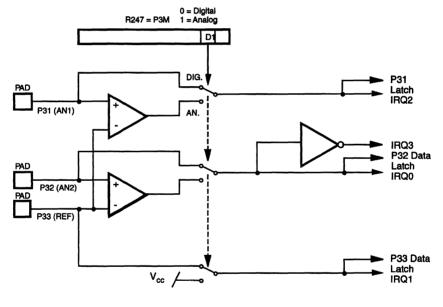

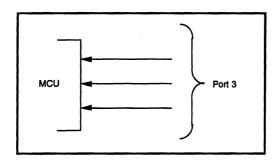

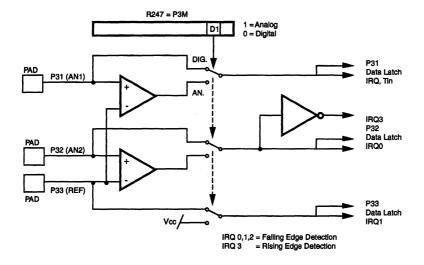

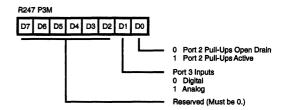

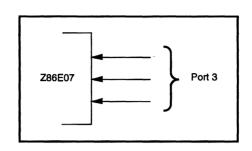

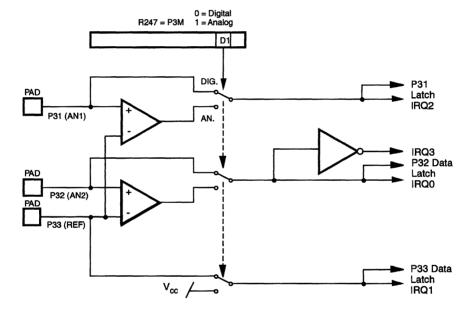

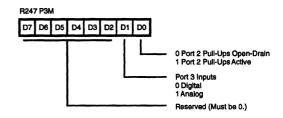

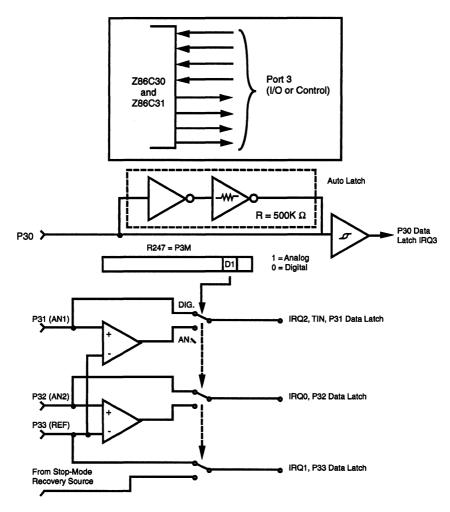

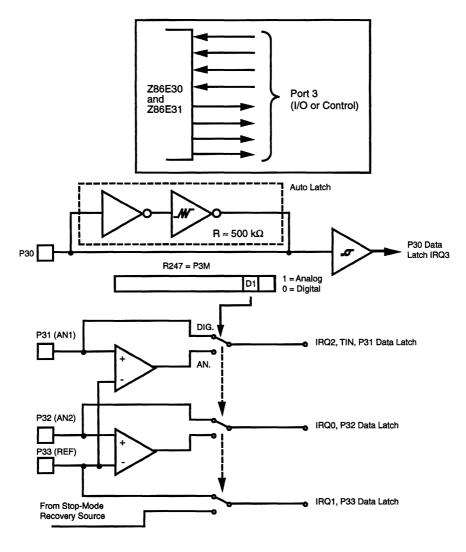

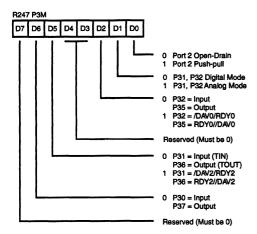

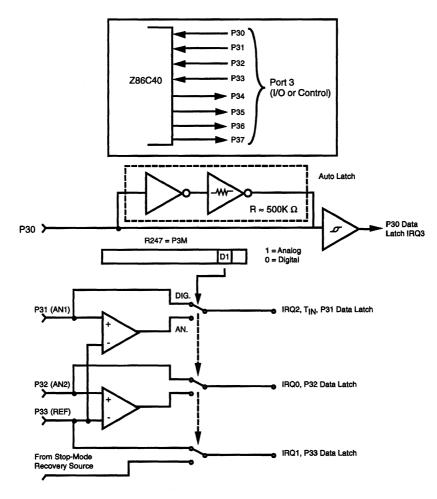

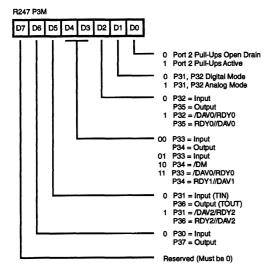

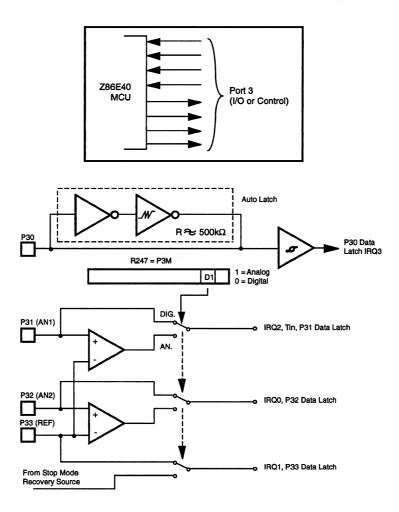

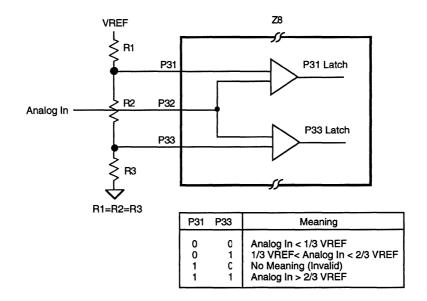

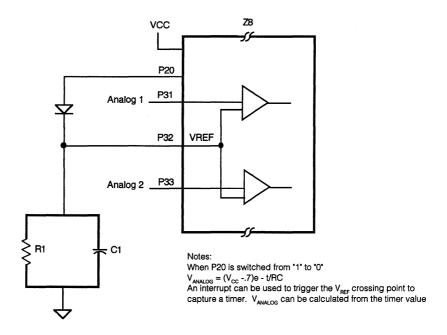

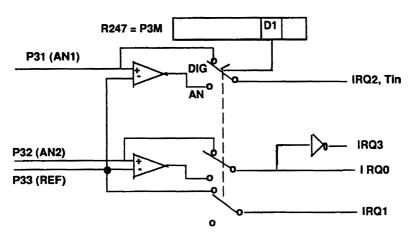

Port 3 (P36-P31). Port 3 is a 6-bit, CMOS compatible port. These six lines consist of three fixed inputs (P31-P33) and three fixed outputs (P34-P36). Pins P31, P32, and P33 are standard CMOS inputs (no auto latches) and pins P34, P35, and P36 are push-pull outputs. Low EMI output buffers can be globally programmed by the software. Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by programming Port 3 Mode Register (P3M-bit D1). Pins P31 and P32 are programmable as falling, rising, or both edge triggered interrupts (IRQ register bits 6 and 7). P33 is the comparator reference voltage input when the analog mode is selected. P33 is a falling edge interrupt input only.

**Note:** P33 is available as an interrupt input only in the digital mode. P31 and P32 are valid interrupt inputs and P31 is the T<sub>IN</sub> input when the analog or digital input mode is selected.

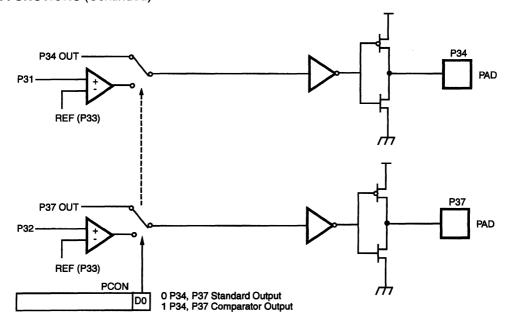

The outputs from the analog comparator can be globally programmed to output from P34 and P35 by setting PCON (F) 00 bit D0 = 1.

Access to Counter/Timer 1 is made through P31 ( $T_{\rm IN}$ ) and P36 ( $T_{\rm OUT}$ ).

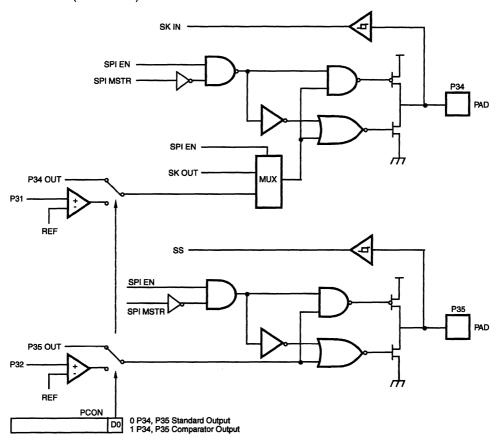

In the Z86C06, pin P34 can also be configured as SPI clock (SK), input and output, and pin P35 can be configured as Slave Select (SS) in slave mode only, when the SPI is enabled (Figures 5a and 5b).

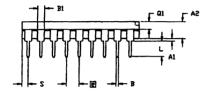

Figure 5a. Port 3 Configuration

#### PIN FUNCTIONS (Continued)

Figure 5b. Port 3 Configuration (Z86C06)

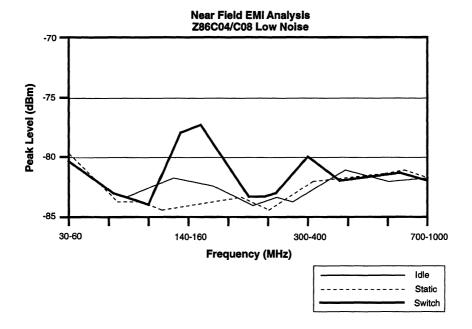

**Low EMI Emission.** The Z86C03/C06 can be programmed to operate in a low EMI emission mode in the PCON register. The oscillator and all I/O ports can be programmed as low EMI emission mode independently. Use of this feature results in:

- The pre-drivers slew rate reduced to 10 ns (typical).

- Low EMI output drivers resistance of 200 ohms (typical).

- Low EMI oscillator.

Internal SCLK/TCLK = XTAL operation limited to a maximum of 4 MHz (250 ns cycle time) when the low EMI oscillator is selected and SCLK = External (SMR Register Bit D1=1).

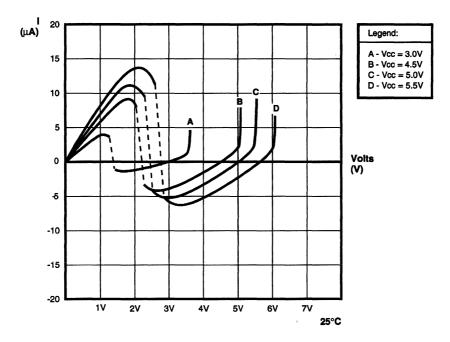

Comparator Inputs. Port 3 Pin P31 and P32 each have a comparator front end. The comparator reference voltage pin P33 is common to both comparators. In analog mode, the P31 and P32 are the positive inputs to the comparators, and P33 is the reference voltage supplied to both comparators. In digital mode, Pin P33 can be used as a P33 register input or IRQ1 source.

#### **FUNCTIONAL DESCRIPTION**

The following special functions have been added to the Z86C03/C06 CCPs to enhance the standard Z8® architecture to provide the user with increased design flexibility.

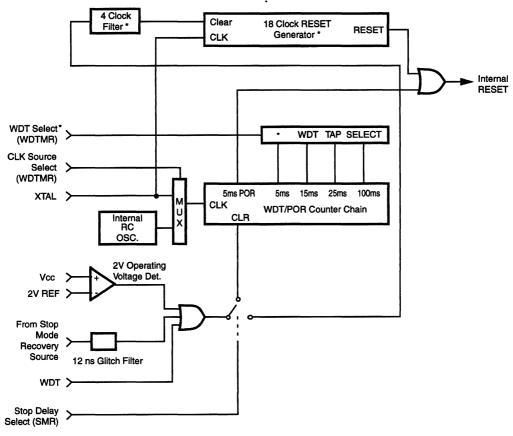

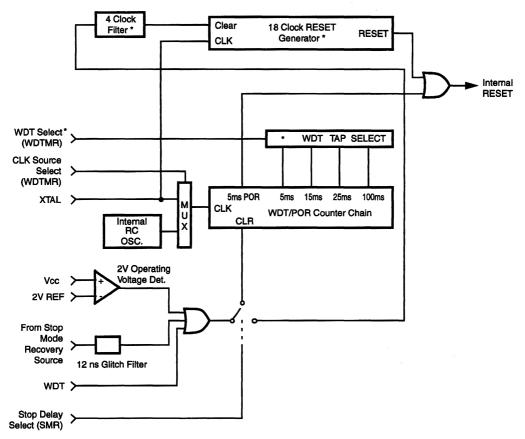

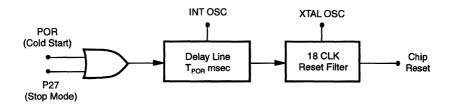

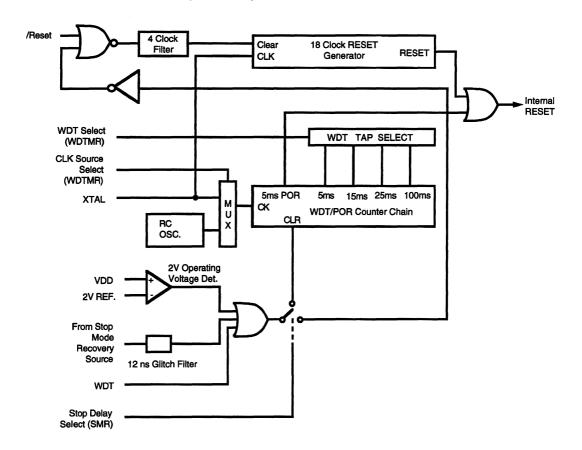

**RESET.** The device is reset in one of four ways:

- 1. Power-On Reset

- 2. Watch-Dog Timer

- 3. STOP-Mode Recovery Source

- 4. Low Voltage Protection

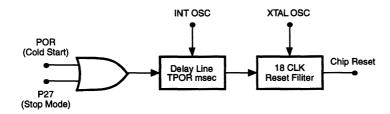

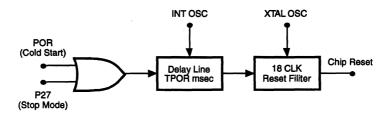

Having the Auto Power-On Reset circuitry built-in, the Z86C03/C06 does not require an external reset circuit. The reset time is 5 ms (typical) plus 18 clock cycles.

The device does not re-initialize the WDTMR, SMR, P2M, or P3M registers to their reset values on a STOP-Mode Recovery operation.

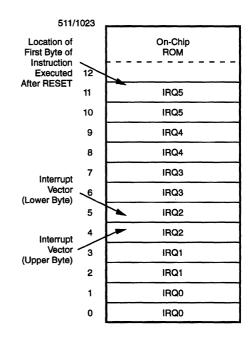

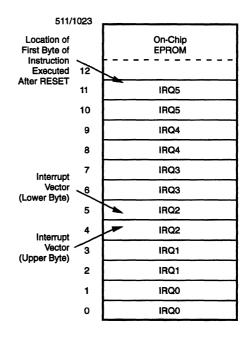

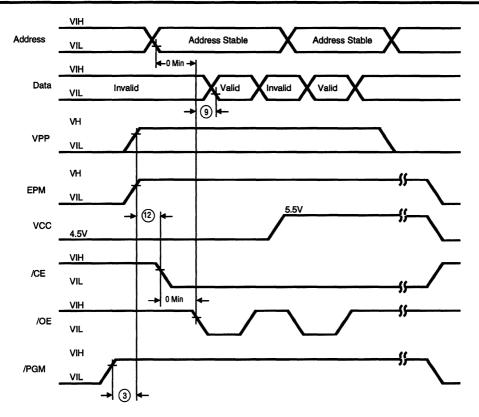

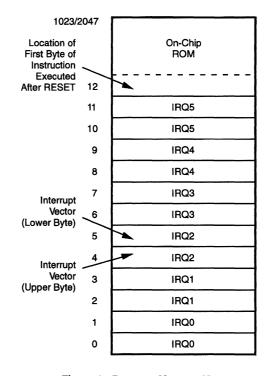

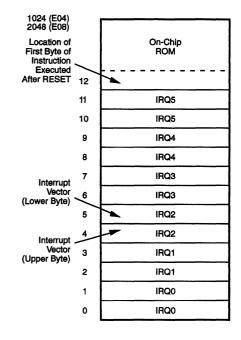

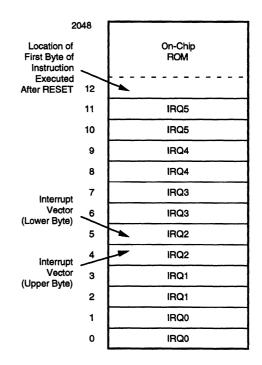

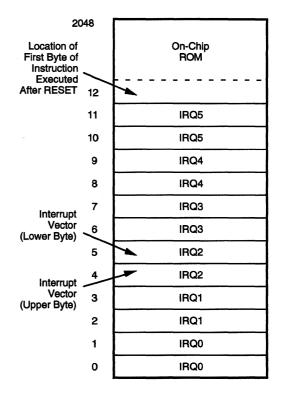

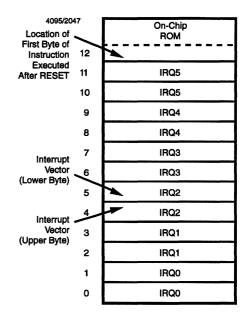

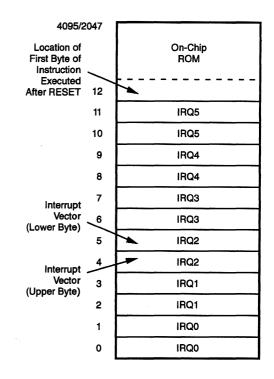

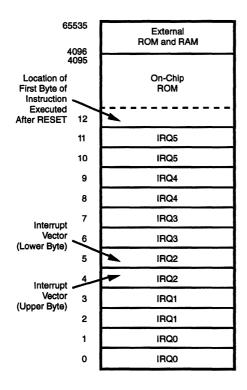

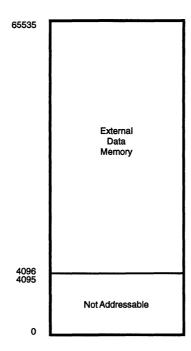

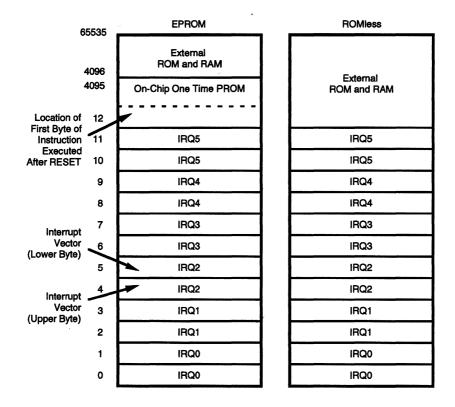

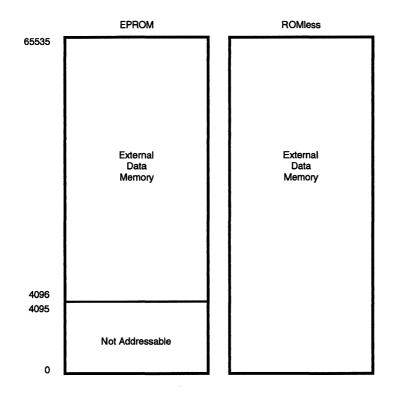

**Program Memory.** Z86C03/C06 can address up to 512/1K bytes of internal program memory (Figure 6). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. Byte 13 to byte 511/1023 consists of on-chip, user program mask ROM.

**ROM Protect.** The 512/1K bytes of Program Memory is mask programmable. A ROM protect feature will prevent "dumping" of the ROM contents by inhibiting execution of the LDC and LDCI instructions to program memory in all modes.

ROM protect is mask-programmable. It is selected by the customer when the ROM code is submitted. **Selecting ROM protect disables the LDC and LDCI instructions in all modes. ROM look-up tables are not supported in this mode.**

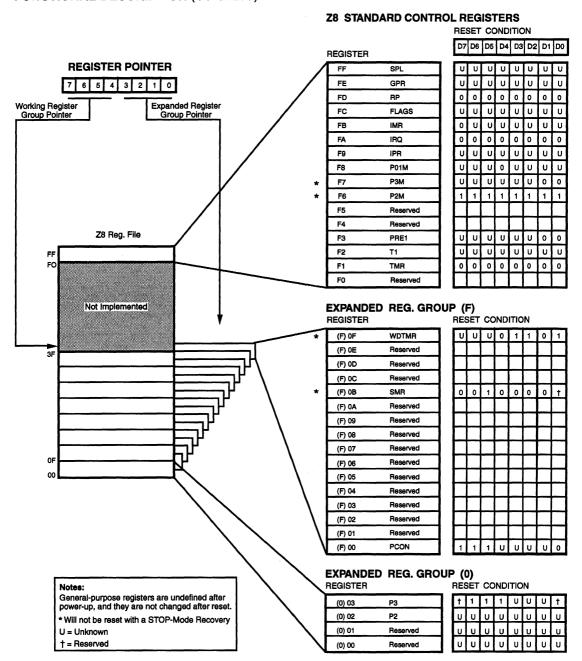

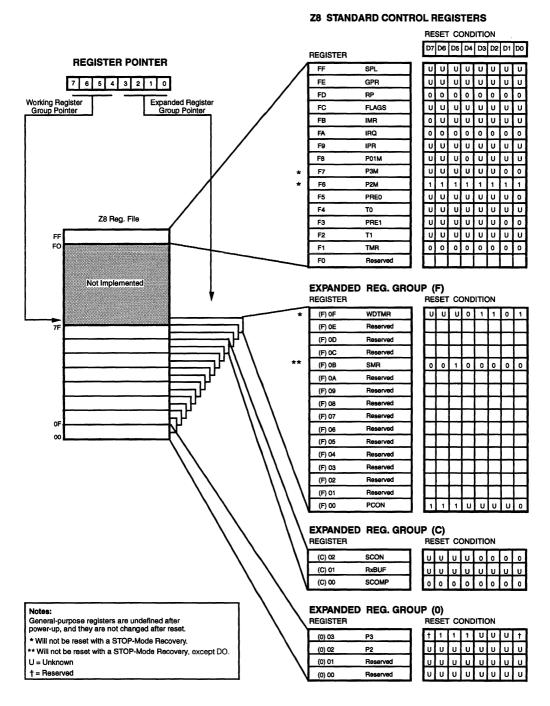

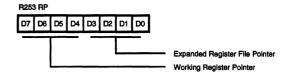

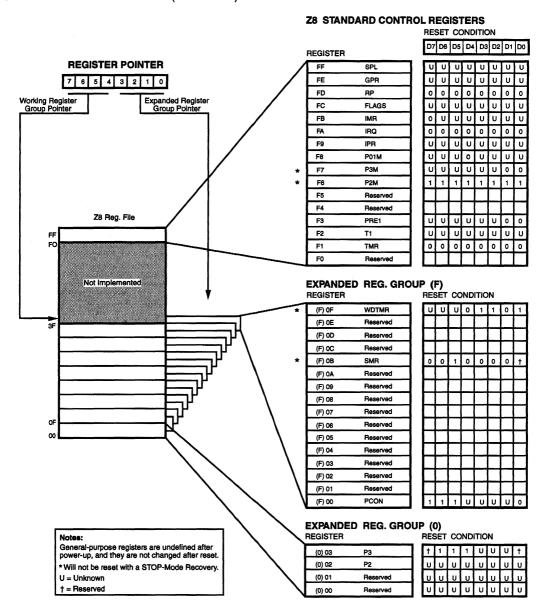

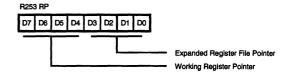

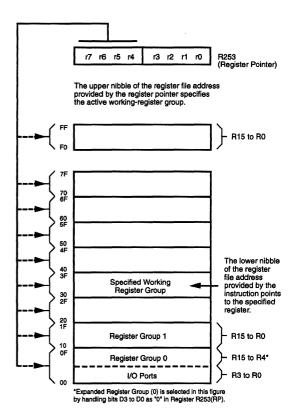

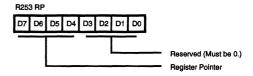

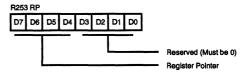

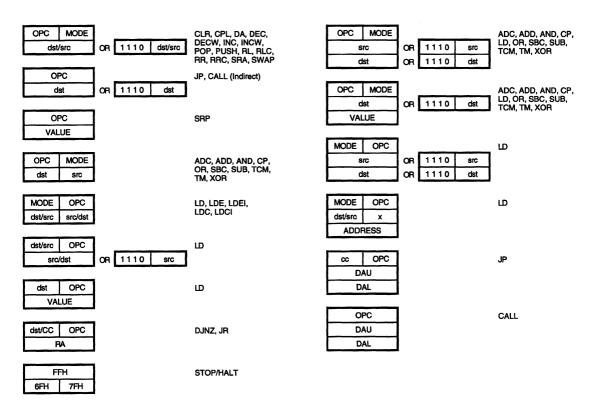

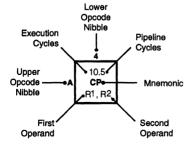

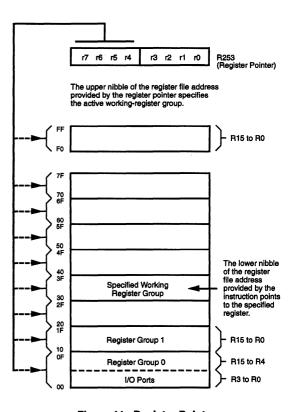

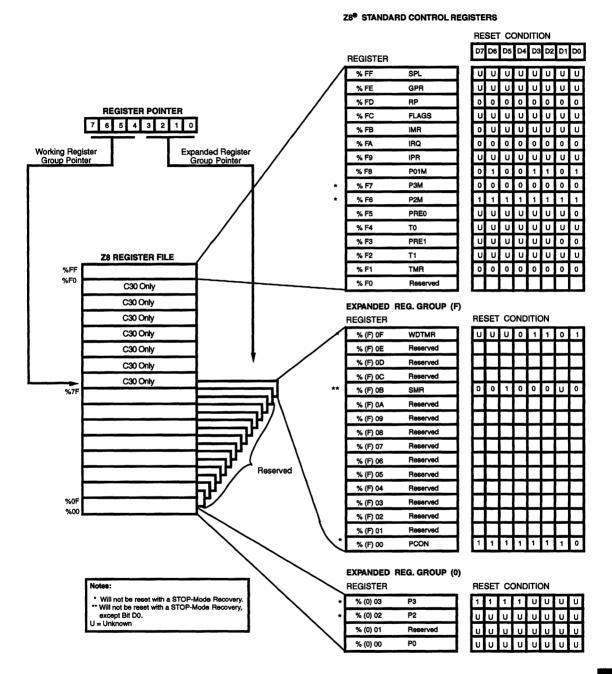

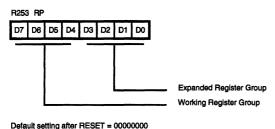

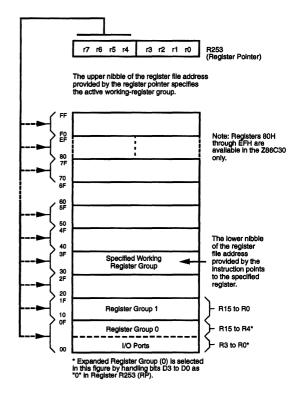

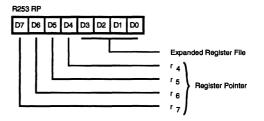

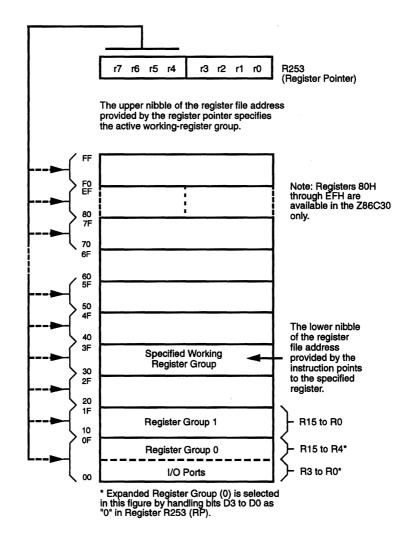

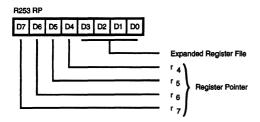

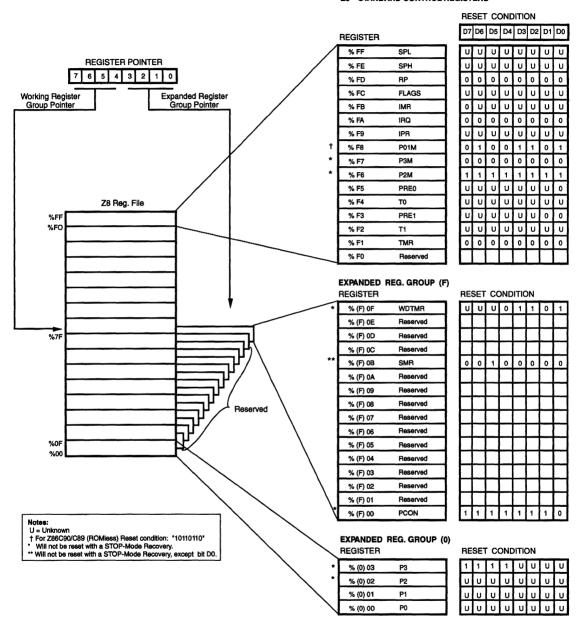

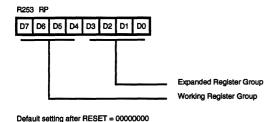

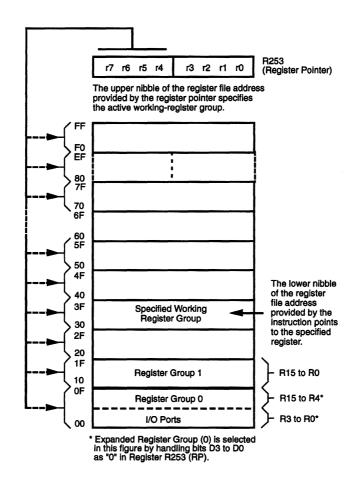

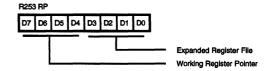

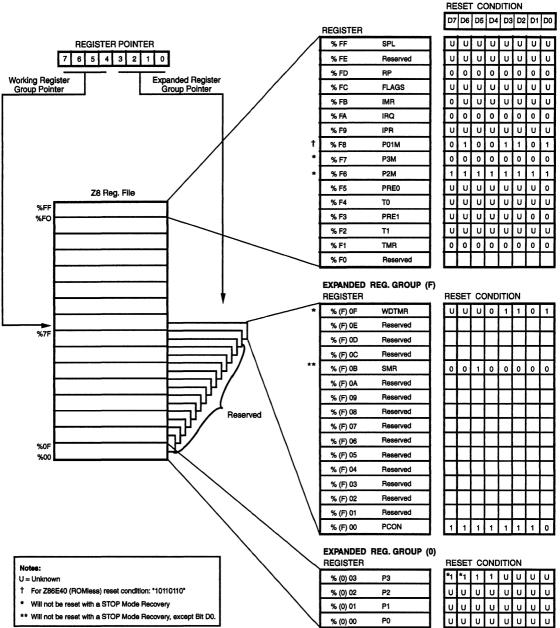

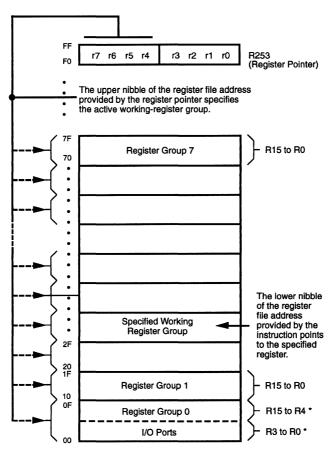

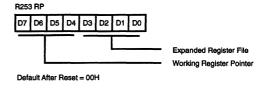

**Expanded Register File (ERF).** The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices and input/output ports into the register address area. The Z8 register address space R0 through R15 is implemented as 16 groups of 16 registers per group (Figure 7). These register groups are known as the Expanded Register File (ERF).

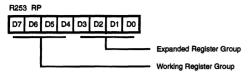

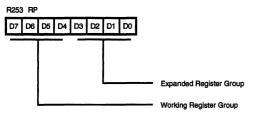

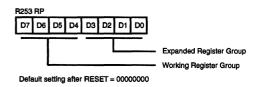

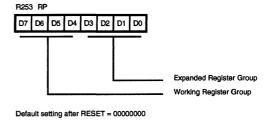

Bits 3-0 of the Register Pointer (RP) select the active ERF group. Bits 7-4 of register RP select the working register group (Figure 7). For the Z86C03, three system configuration registers reside in the ERF address space Bank F. For the Z86C06, three system configuration registers reside in the ERF address space Bank F, while three SPI registers reside in Bank C. The rest of the ERF address space is not physically implemented and is open for future expansion.

Figure 6. Program Memory Map

Figure 7a. Expanded Register File Architecture (Z86C03)

Figure 7b. Expanded Register File Architecture (Z86C06)

Note: Default Setting After Reset = 00000000

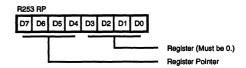

Figure 8. Register Pointer Register

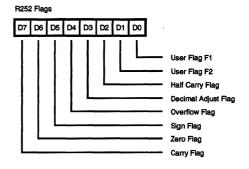

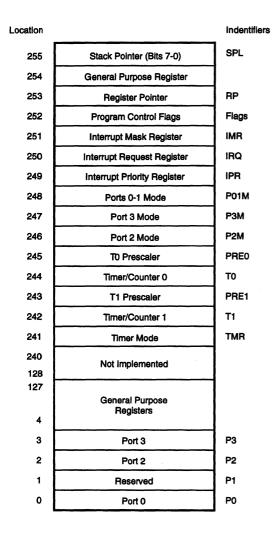

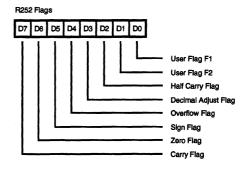

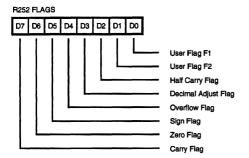

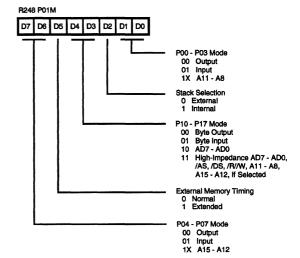

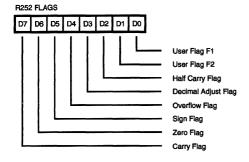

**Register File.** The Register File consists of two I/O port registers, 60/124 general-purpose registers, and 13/15 control and status registers. The Z86C03 General-Purpose Register file ranges from address 00 to 3F while the Z86C06 General-Purpose Register file ranges from address 00 to 7F (see Figure 9). The instructions can access

registers directly or indirectly via an 8-bit address field. This allows a short 4-bit register address using the Register Pointer (Figure 9). In the 4-bit mode, the Register File is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group.

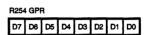

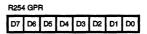

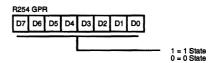

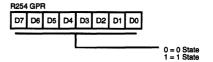

**General-Purpose Registers (GPR).** These registers are undefined after the device is powered up. The registers keep their last value after any reset, as long as the reset occurs in the V<sub>CC</sub> voltage-specified operating range. **Note:** Register R254 has been designated as a general-purpose register.

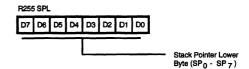

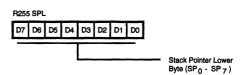

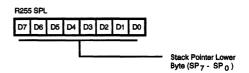

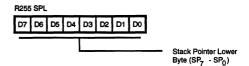

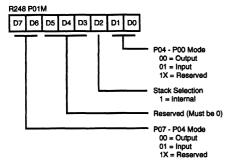

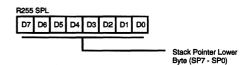

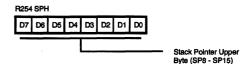

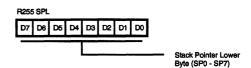

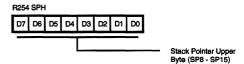

**Stack.** An 8-bit Stack Pointer (R255) used for the internal stack that resides within the 60/124 general-purpose registers.

Figure 9. Register Pointer

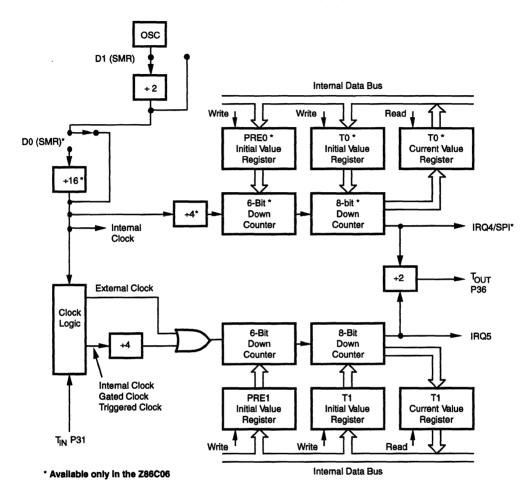

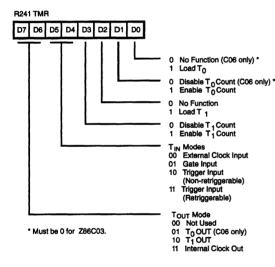

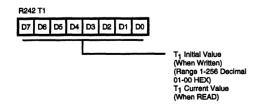

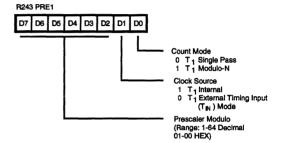

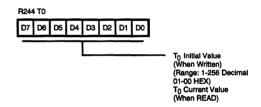

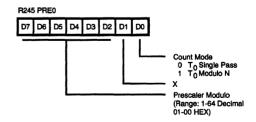

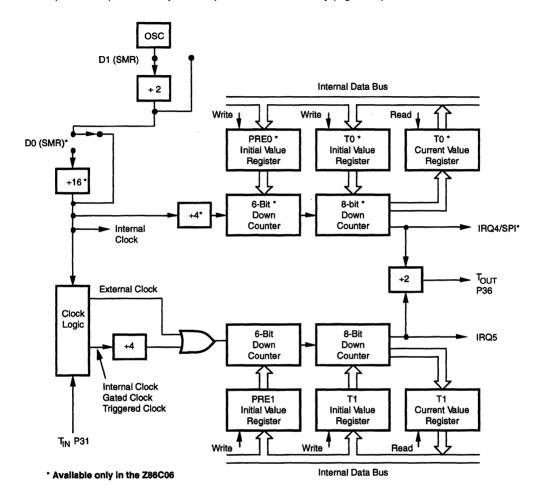

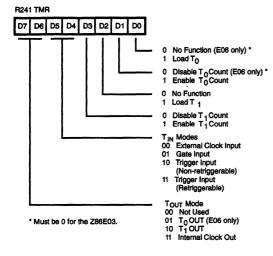

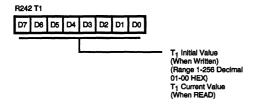

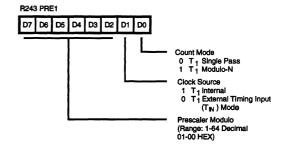

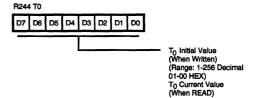

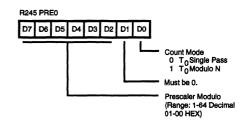

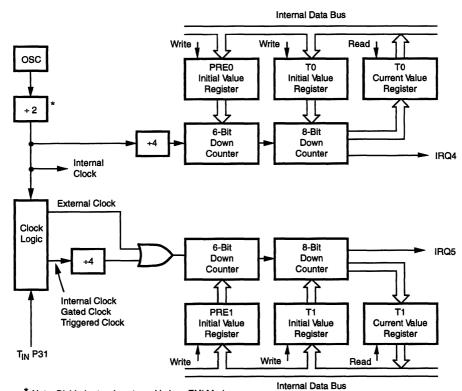

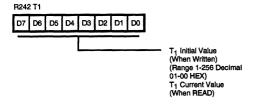

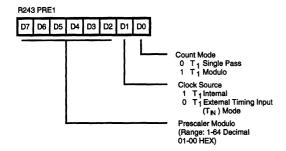

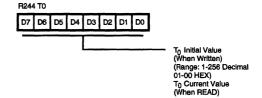

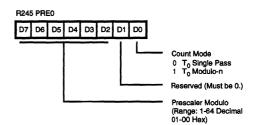

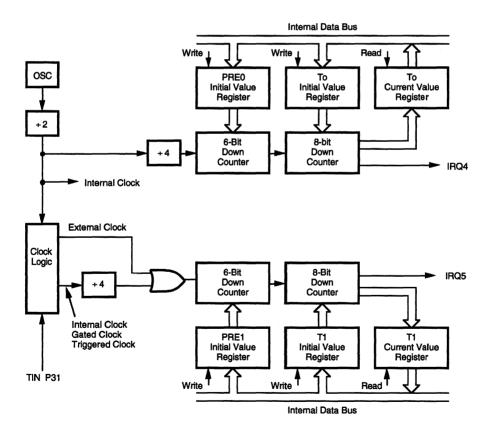

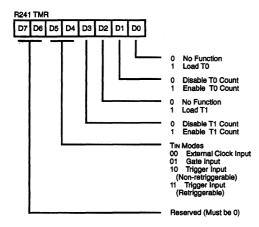

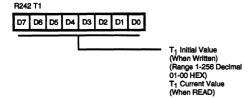

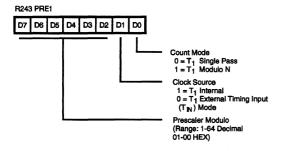

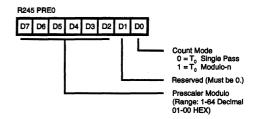

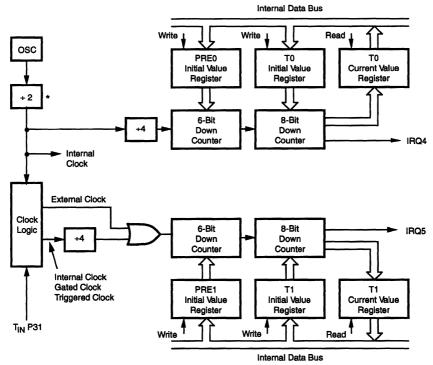

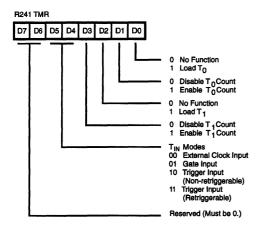

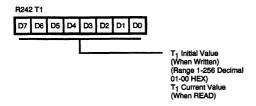

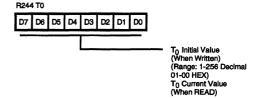

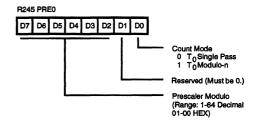

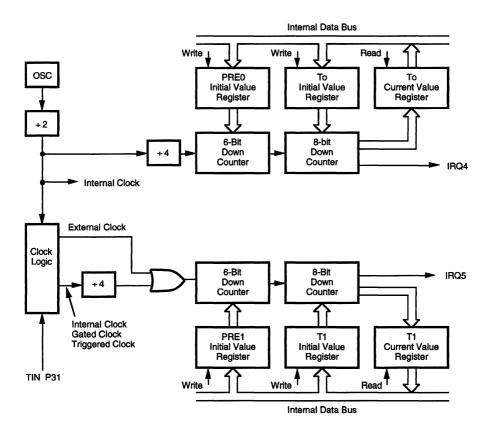

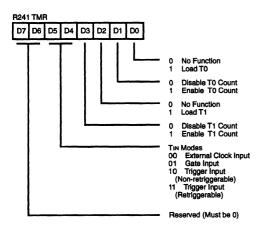

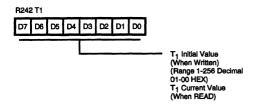

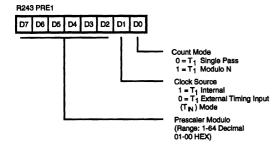

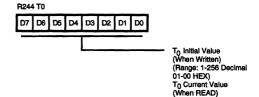

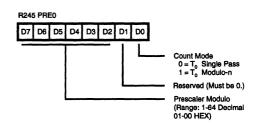

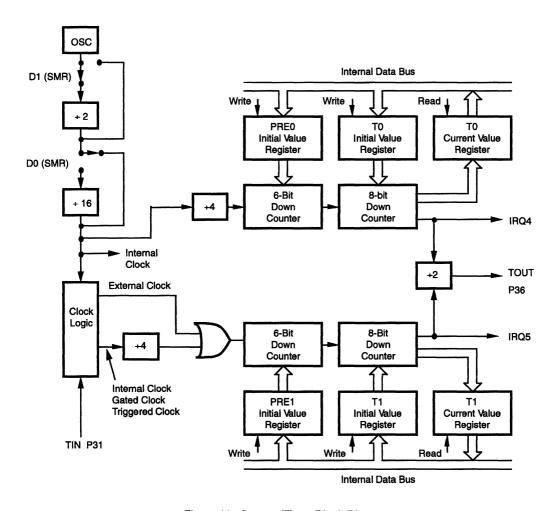

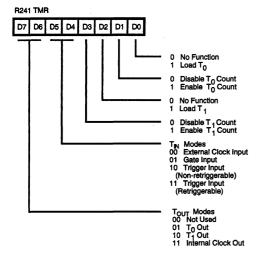

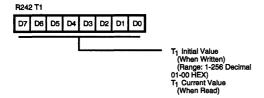

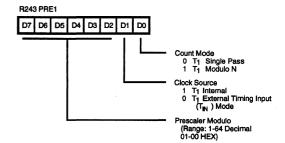

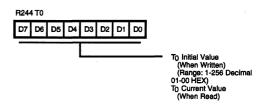

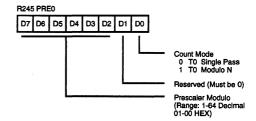

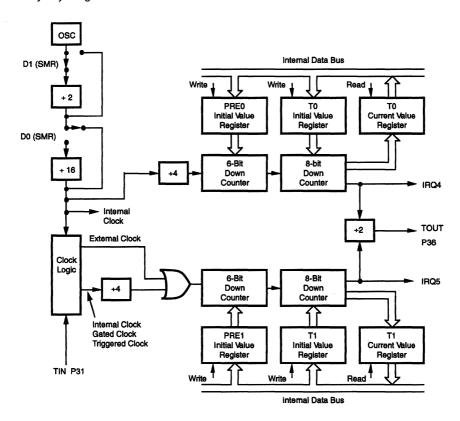

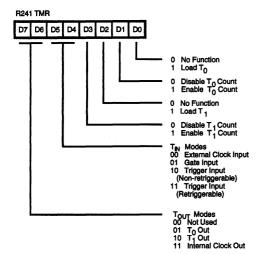

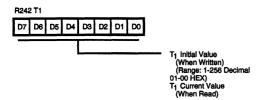

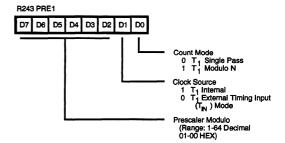

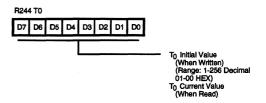

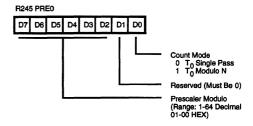

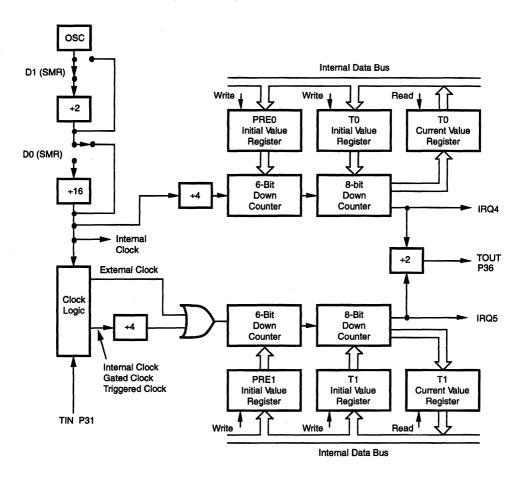

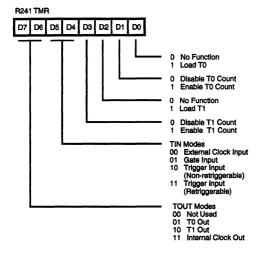

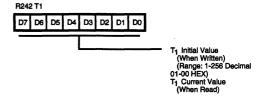

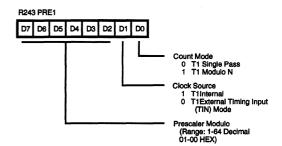

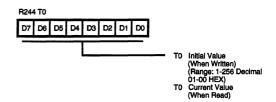

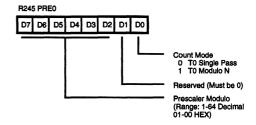

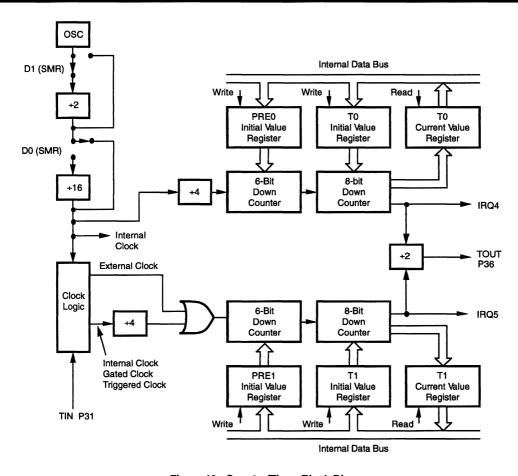

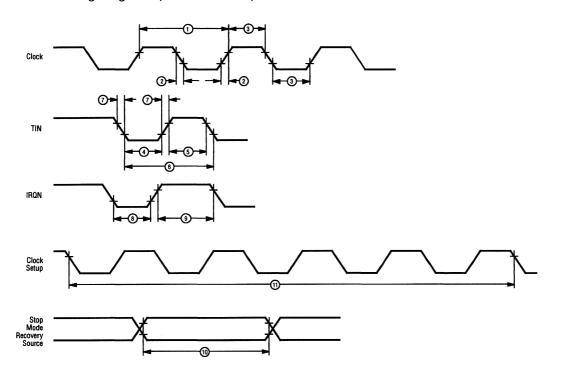

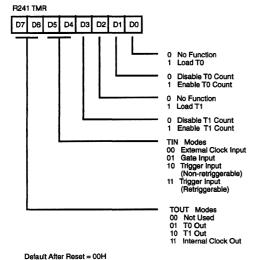

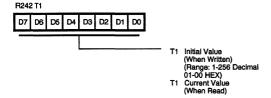

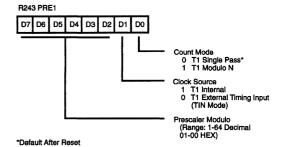

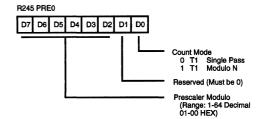

**Counter/Timers.** There are two 8-bit programmable counter/timers (T0-T1), each driven by its own 6-bit programmable prescaler (Z86C03 only has T1). The T1

prescaler can be driven by internal or external clock sources, however, the T0 prescaler is driven by the internal clock only (Figure 10).

Figure 10. Counter/Timer Block Diagram

The 6-bit prescalers divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated. Note that IRQ4 is softwaregenerated in the Z86C03.

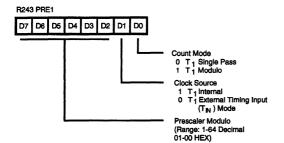

The counters are programmed to start, stop, restart to continue, or restart from the initial value. The counters can also be programmed to stop upon reaching zero (single-pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode).

The counters, but not the prescalers, are read at any time without disturbing their value or count mode. The clock source for T1 is user-definable and can be either the internal microprocessor clock divided by four, or an exter-

nal signal input via Port 3. The Timer Mode register configures the external timer input (P31) as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. Port 3, line P36 serves as a timer output ( $T_{\rm OUT}$ ) through which T0 (C06 only), T1, or the internal clock can be output. The counter/timers can be cascaded by connecting the T0 output to the input of T1 (C06 only). The  $T_{\rm IN}$  mode is enabled by setting PRE1 bit D1 (R243) to 0.

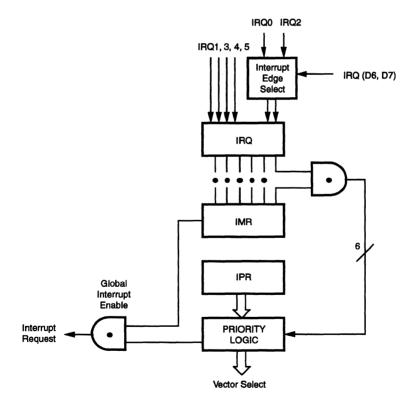

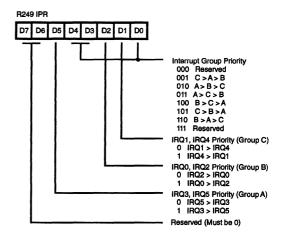

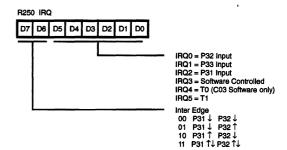

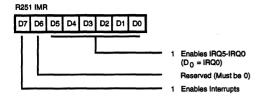

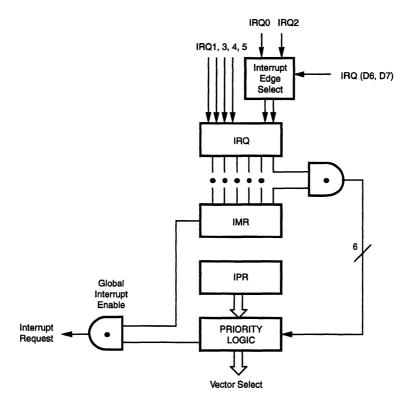

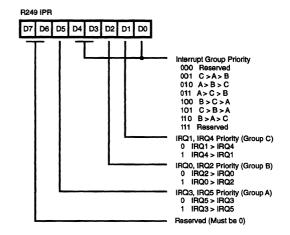

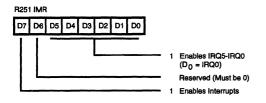

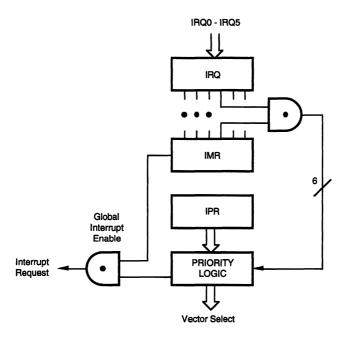

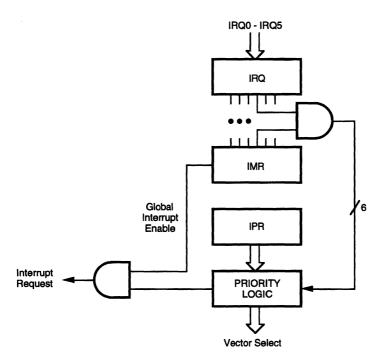

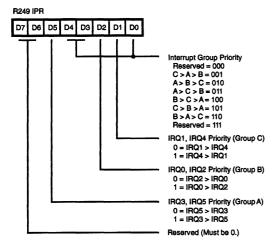

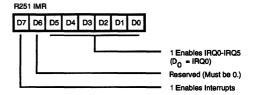

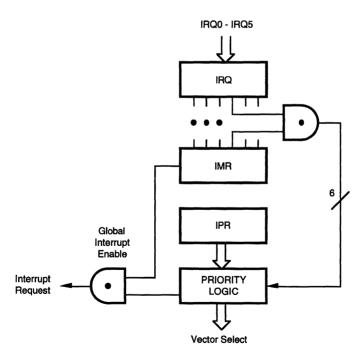

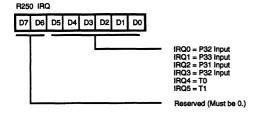

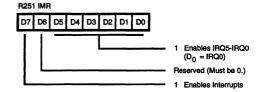

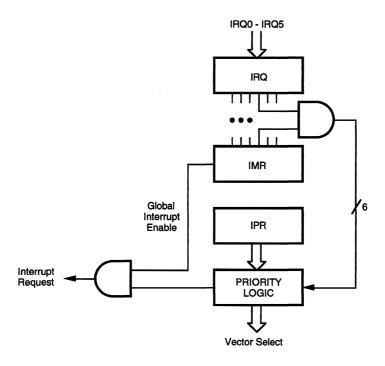

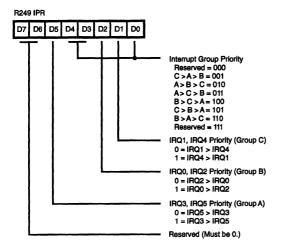

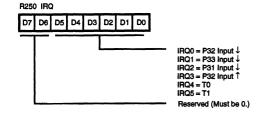

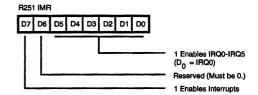

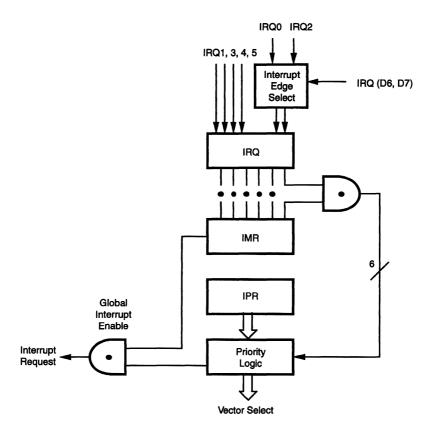

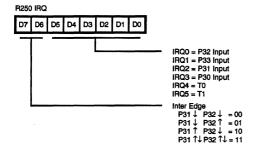

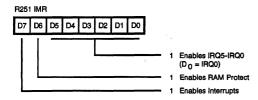

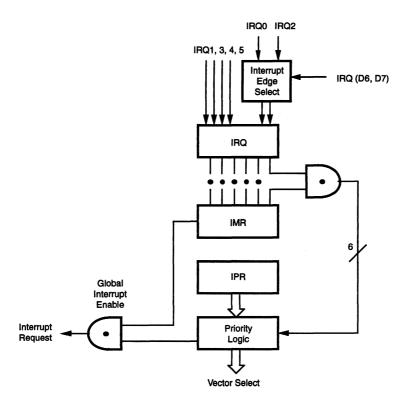

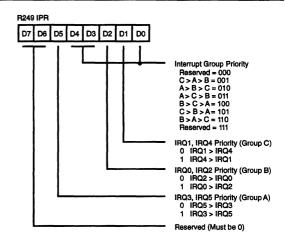

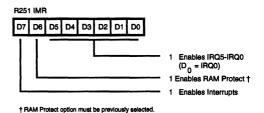

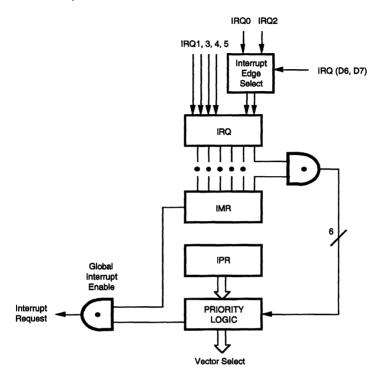

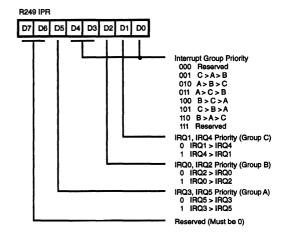

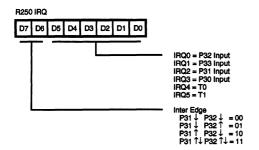

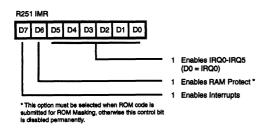

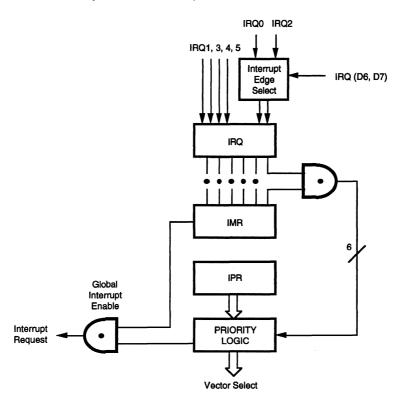

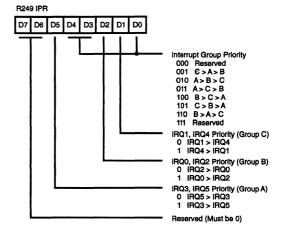

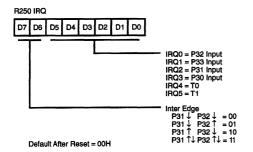

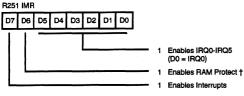

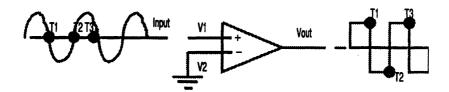

Interrupts. The Z86C03/C06 has six different interrupts from six different sources. The interrupts are maskable and prioritized (Figure 11). The six sources are divided as follows; three sources are claimed by Port 3 lines P31-P33, two sources in the counter/timers, and one source for the SPI. The Interrupt Mask Register globally or singularly enables or disables the six interrupt requests (Table 2).

Figure 11. Interrupt Block Diagram

Table 2. Interrupt Types, Sources, and Vectors

| Name   | Source                 | Vector Location | Comments                                        |

|--------|------------------------|-----------------|-------------------------------------------------|

| IRQ 0  | IRQ 0                  | 0, 1            | External (P32), Rising/Falling Edge Triggered   |

| IRQ 1  | IRQ 1                  | 2, 3            | External (P33), Falling Edge Triggered          |

| IRQ 2  | IRQ 2, T <sub>IN</sub> | 4,5             | External (P31), Rising/Falling Edge Triggered   |

| IRQ 3* | IRQ 3                  | 6, 7            | Software Generated, SPI Receive                 |

| IRQ 4  | T0/IRQ 4               | 8, 9            | Internal for C06 and Software Generated for C03 |

| IRQ 5  | TI                     | 10, 11          | Internal                                        |

#### Note:

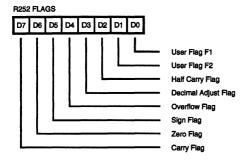

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. An interrupt machine cycle is activated when an interrupt request is granted. This disables all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. All Z86C03/C06 interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16-bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests need service. In the Z86C06, when the SPI is disabled, IRQ3 has no hardware source but can be invoked by software (write to IRQ3 Register). When the SPI is enabled, an interrupt will be mapped to IRQ3 after a byte of data has been received by the SPI Shift Register.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling, or both edge triggered, and are programmable by the user. The software can poll to identify the state of the pin.

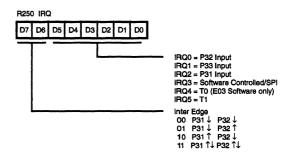

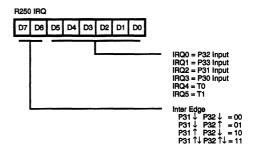

The programming bits for the INTERRUPT EDGE SELECT are located in the IRQ register (R250), bits D7 and D6. The configuration is shown in Table 3.

Table 3. IRQ Register

| IQ. | Interrupt Edge |             |

|-----|----------------|-------------|

| D6  | P31            | P32         |

| 0   | F              | F           |

| 1   | F              | R           |

| 0   | R              | F           |

| 1   | R/F            | R/F         |

|     | <b>D6</b> 0 1  | 0 F 1 F 0 R |

#### Notes:

F = Falling Edge

R = Rising Edge

<sup>\*</sup> In the Z86C06, the SPI receive interrupt is mapped to IRQ3 when enabled.

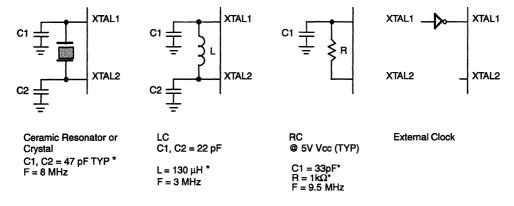

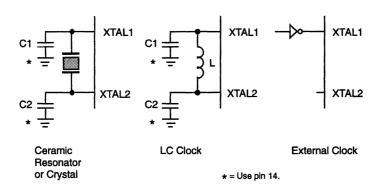

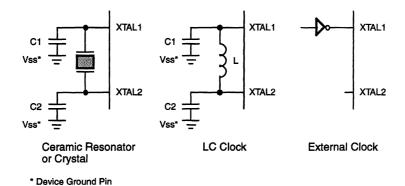

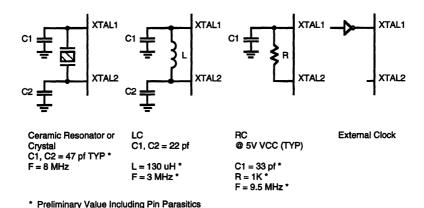

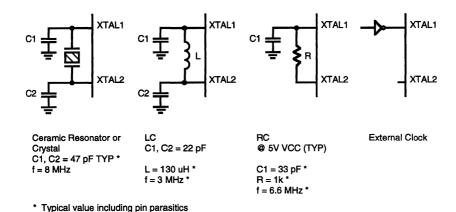

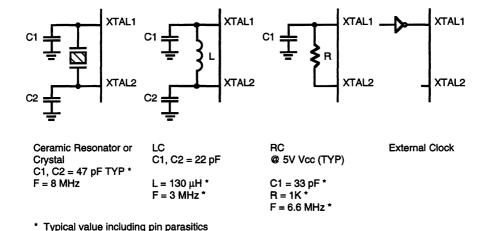

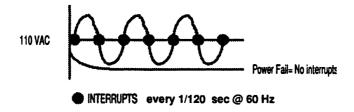

Clock. The Z86C03/C06 on-chip oscillator has a highgain, parallel-resonant amplifier for connection to a crystal, RC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 10 kHz to 8 MHz/12 MHz max, with a series resistance (RS) less than or equal to 100 Ohms.

The crystal should be connected across XTAL1 and XTAL2 using the vendor's recommended capacitor values (capacitance between 10 pF to 300 pF) from each pin directly to the device ground (pin 14). The layout is important to reduce ground noise injection.

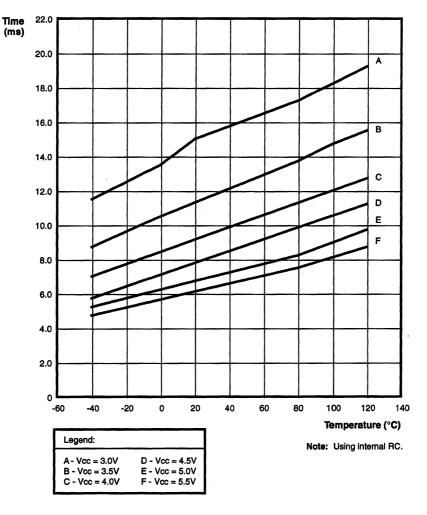

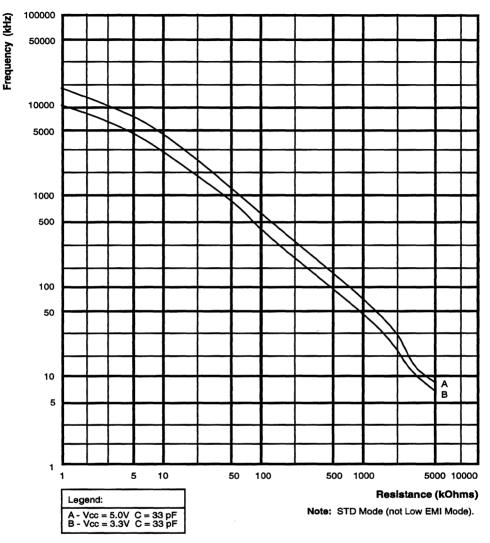

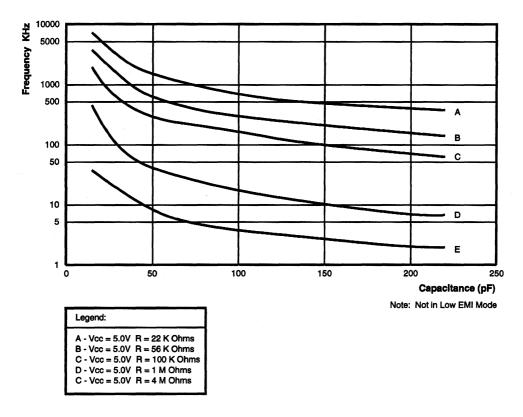

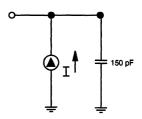

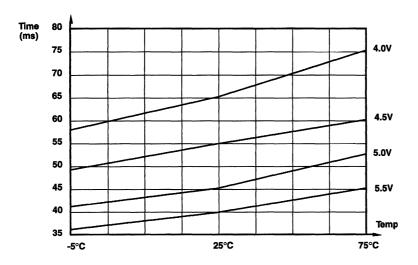

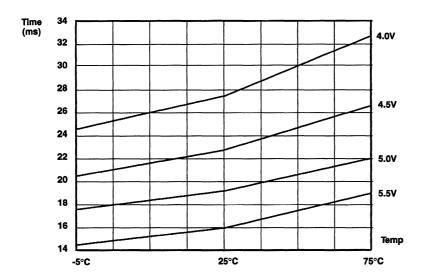

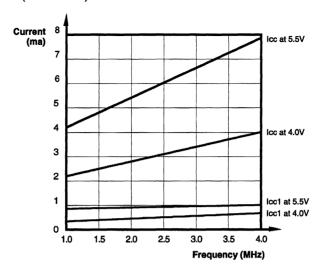

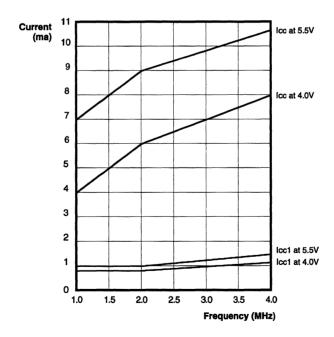

The RC oscillator option is mask-programmable, to be selected by the customer at the time ROM code is submitted. The RC oscillator configuration must be an external resistor connected from XTAL1 to XTAL2, with a frequency-setting capacitor from XTAL1 to ground (Figure 12). The RC value vs. Frequency curves are shown in Figures 57 and 58.

In addition, a special feature has been incorporated into the Z86C03/C06; in low EMI noise mode (bit 7 of PCON register=0) with the RC option selected, the oscillator is targeted to consume considerately less I<sub>cc</sub> current at frequencies of 10 kHz or less.

\* Preliminary Value Including Pin Parasitics

Figure 12. Oscillator Configuration

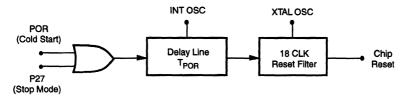

**Power-On Reset.** A timer circuit clocked by a dedicated on-board RC oscillator is used for the Power-On Reset (POR) timer function. The POR time allows  $V_{\rm CC}$  and the oscillator circuit to stabilize before instruction execution begins. The POR timer circuit is a one-shot timer triggered by one of the three conditions:

- Power-Fail to Power-OK Status

- STOP-Mode Recovery (If D5 of SMR=1)

- WDT Timeout

The POR time is a nominal 5 ms. Bit 5 of the STOP Mode Register determines whether the POR timer is bypassed after STOP-Mode Recovery (typical for external clock, and RC/LC oscillators with fast start up time).

**HALT.** A Halt instructions will turn off the internal CPU clock but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, and IRQ2 remain active. The device may be recovered by interrupts either externally or internally generated.

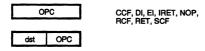

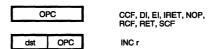

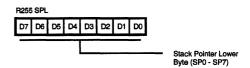

**STOP.** This instruction turns off the internal clock and external crystal oscillation and reduces the standby current. The STOP mode is terminated by a RESET only, either by WDT timeout, POR, SPI compare; or SMR recovery. This causes the processor to restart the application program at address 000C (HEX). Note, the crystal remains active in STOP mode if bits 3 and 4 of the WDTMR are enabled. In this mode, only the Watch-Dog Timer runs in STOP mode.

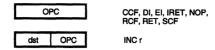

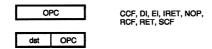

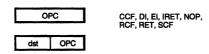

In order to enter STOP (or HALT) mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user executes a NOP (opcode=FFH) immediately before the appropriate sleep instruction, i.e.:

FF NOP ; clear the pipeline 6F STOP ; enter STOP mode or

FF NOP ; clear the pipeline 7F HALT ; enter HALT mode

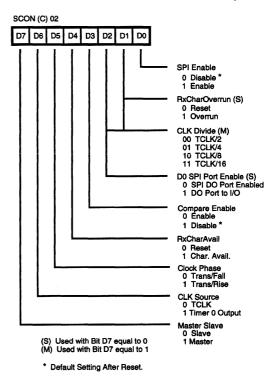

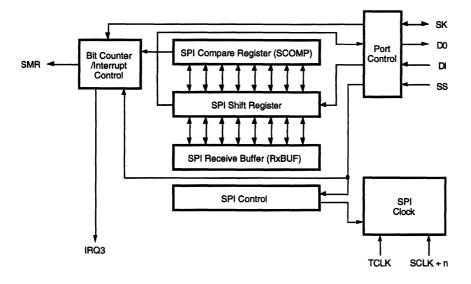

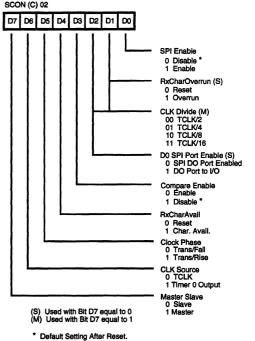

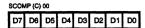

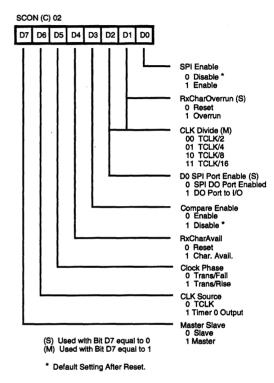

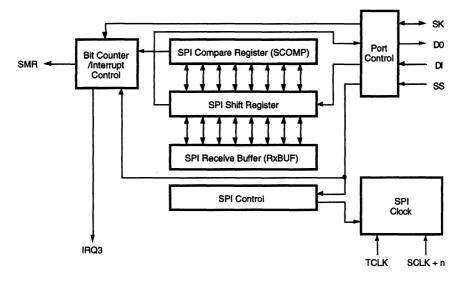

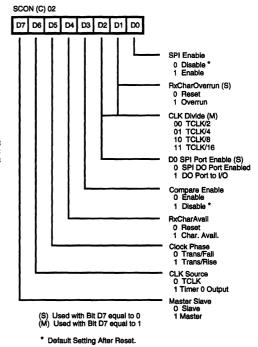

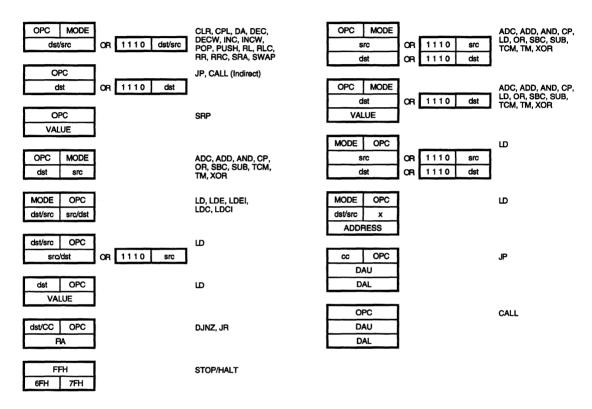

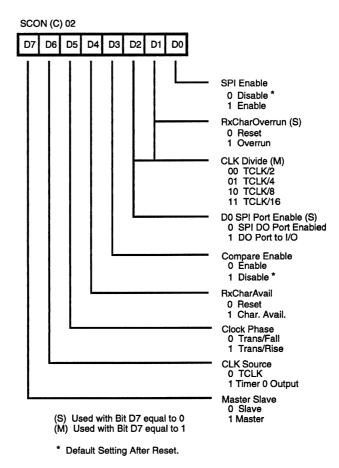

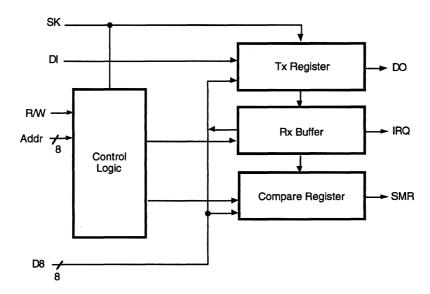

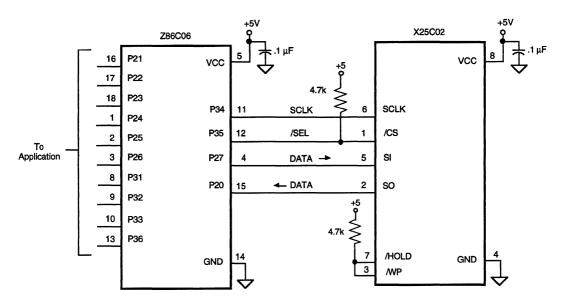

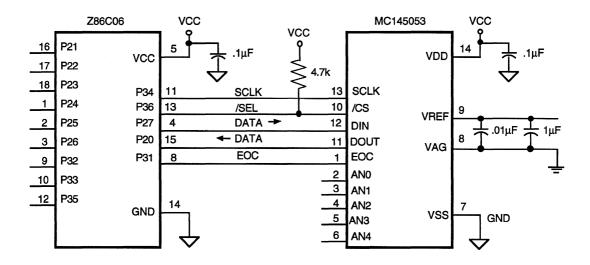

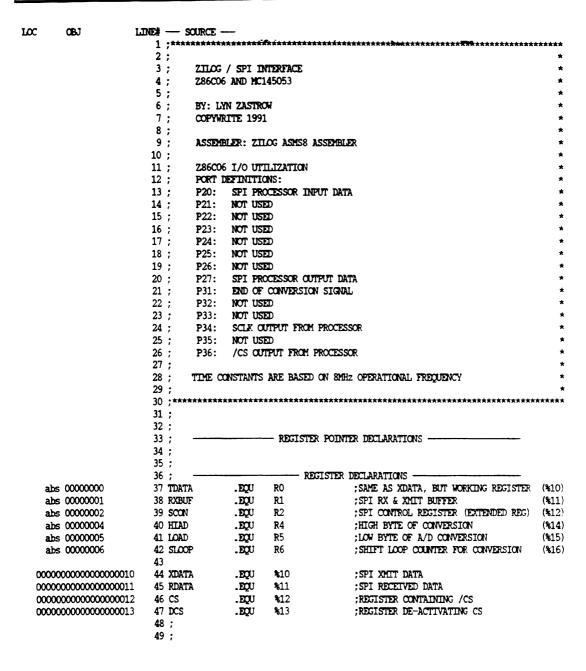

Serial Peripheral Interface (SPI)—Z86C06 Only. The Z86C06 incorporates a serial peripheral interface for communication with other microcontrollers and peripherals. The SPI does not exist on the Z86C03. The SPI includes features such as STOP-Mode Recovery, Master/Slave selection, and Compare mode. Table 4 contains the pin configuration for the SPI feature when it is enabled. The SPI consists of four registers: SPI Control Register (SCON), SPI Compare Register (SCOMP), SPI Receive/Buffer Register (RxBUF), and SPI Shift Register. SCON is located in bank (C) of the Expanded Register Group at address 02.

Table 4. Z86C06 SPI Pin Configuration

| Name | Function     | Pin Location |

|------|--------------|--------------|

| DI   | Data-In      | P20          |

| DO   | Data-Out     | P27          |

| SS   | Slave Select | P35          |

| SK   | SPI Clock    | P34          |

|      |              |              |

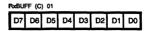

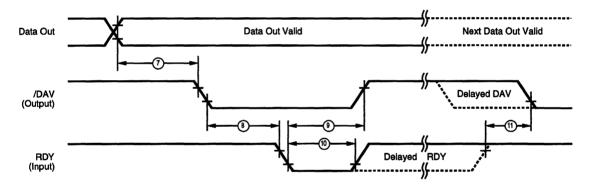

The SPI Control Register (SCON) (Figure 13) is a read/write register that controls; Master/Slave selection, interrupts, clock source and phase selection, and error flag. Bit 0 enables/disables the SPI with the default being SPI disabled. A 1 in this location will enable the SPI, and a 0 will disable the SPI. Bits 1 and 2 of the SCON register in Master mode select the clock rate. The user may choose whether internal clock is divide-by-2, -4, -8, or -16. In slave mode, Bit 1 of this register flags the user if an overrun of the RxBUF Register has occurred. The RxCharOverrun flag is only reset by writing a 0 to this bit. In slave mode, bit 2 of the Control Register disables the data-out I/O function. If a 1 is

written to this bit, the data-out pin is released to its original port configuration. If a 0 is written to this bit, the SPI shifts out one bit for each bit received. Bit 3 of the SCON Register enables the compare feature of the SPI, with the default being disabled. When the compare feature is enabled, a comparison of the value in the SCOMP Register is made with the value in the RxBUF Register. Bit 4 signals that a receive character is available in the RxBUF Register.

Figure 13. SPI Control Register (SCON) (Z86C06 Only)

If the associated IRQ3 is enabled, an interrupt is generated. Bit 5 controls the clock phase of the SPI. A 1 in Bit 5 allows for receiving data on the clock's falling edge and transmitting data on the clock's rising edge. A 0 allows receiving data on the clock's rising edge and transmitting on the clock's falling edge. The SPI clock source is defined in bit 6. A 1 uses Timer0 output for the SPI clock, and a 0 uses TCLK for clocking the SPI. Finally, bit 7 determines whether the SPI is used as a Master or a Slave. A 1 puts the SPI into Master mode and a 0 puts the SPI into Slave mode.

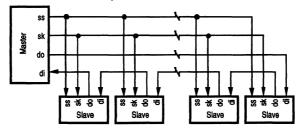

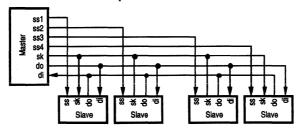

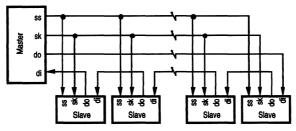

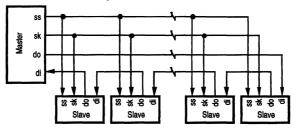

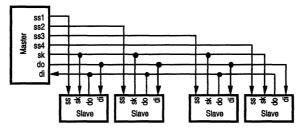

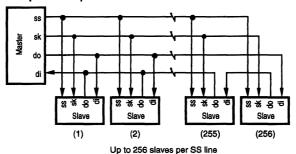

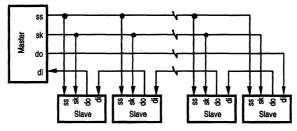

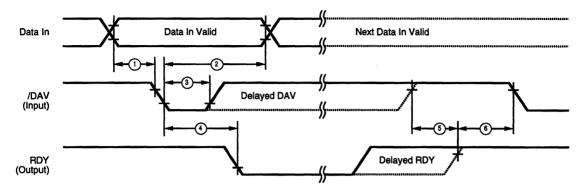

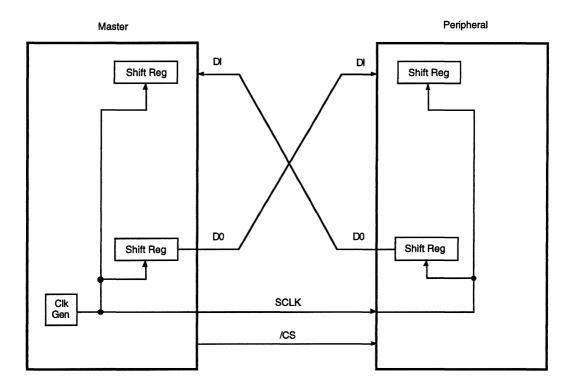

SPI Operation (Z86C06 only). The SPI is used in one of two modes: either as system slave, or as system master. Several of the possible system configurations are shown in Figure 14. In the slave mode, data transfer starts when the slave select (SS) pin goes active. Data is transferred into the slave's SPI Shift Register through the DI pin, which has the same address as the RxBUF Register. After a byte of data has been received by the SPI Shift Register, a Receive Character Available (RCA/IRQ3) flag and interrupt is generated. The next byte of data will be received at this time. The RxBUF Register must be cleared, or a Receive Character Overrun (RxCharOverrun) flag will be set in the SCON Register, and the data in the RxBUF Register will be overwritten. When the communication between the master and slave is complete, the SS goes inactive.

Unless disconnected, for every bit that is transferred into the slave through the DI pin, a bit is transferred out through the DO pin on the opposite clock edge. During slave operation, the SPI clock pin (SK) is an input. In master mode, the CPU must first activate a SS through one of it's I/O ports. Next, data is transferred through the master's DO pin one bit per master clock cycle. Loading data into the shift register initiates the transfer. In master mode, the master's clock will drive the slave's clock. At the conclusion of a transfer, a Receive Character Available (RCA/IRQ3) flag and interrupt is generated. Before data is transferred via the DO pin, the SPI Enable bit in the SCON Register must be enabled.

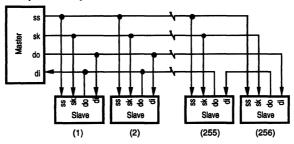

SPI Compare (Z86C06 only). When the SPI Compare Enable bit, D3 of the SCON Register is set to 1, the SPI Compare feature is enabled. The compare feature is only valid for slave mode. A compare transaction begins when the (SS) line goes active. Data is received as if it were a normal transaction, but there is no data transmitted to avoid bus contention with other slave devices. When the compare byte is received, IRQ3 is not generated. Instead, the data is compared with the contents of the SCOMP Register. If the data does not match, DO remains inactive and the slave ignores all data until the (SS) signal is reset. If the data received matches the data in the SCOMP register, then a SMR signal is generated. DO is activated if it is not tri-stated by D2 in the SCON Register, and data is received the same as any other SPI slave transaction.

When the SPI is activated as a slave, it operates in all system modes; STOP, HALT, and RUN. Slaves' not comparing remain in their current mode, whereas slaves' comparing wake from a STOP or HALT mode by means of an SMR.

SPI Clock (Z86C06 only). The SPI clock maybe driven by three sources: TimerO, a division of the internal system clock, or the external master when in slave mode. Bit D6 of the SCON Register controls what source drives the SPI clock. A 0 in bit D6 of the SCON Register determines the division of the internal system clock if this is used as the SPI clock source. Divide by 2, 4, 8, or 16 is chosen as the scaler.

#### Standard Serial Setup

#### **Standard Parallel Setup**

#### **Setup For Compare**

Up to 256 slaves per SS line

#### **Three Wire Compare Setup**

Multiple slaves may have the same address.

Figure 14. SPI System Configuration (Z86C06 Only)

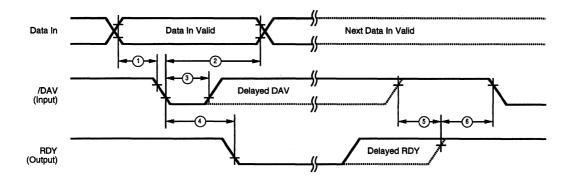

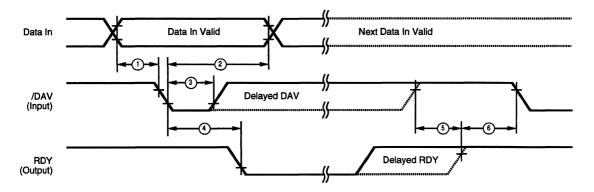

Receive Character Available and Overrun (Z86C06 Only). When a complete data stream is received, an interrupt is generated and the RxCharAvail bit in the SCON Register is set. Bit 4 in the SCON Register is for enabling or disabling the RxCharAvail interrupt. The RxCharAvail bit is available for interrupt polling purposes and is reset when the RxBUF Register is read. RxCharAvail is generated in both master and slave modes. While in slave mode, if the RxBUF is not read before the next data stream is received and loaded into the RxBUF Register, Receive Character Overrun (RxCharOverrun) occurs. Since there is no need

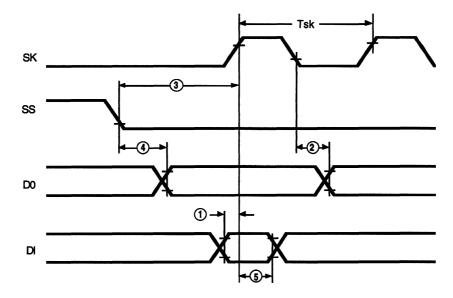

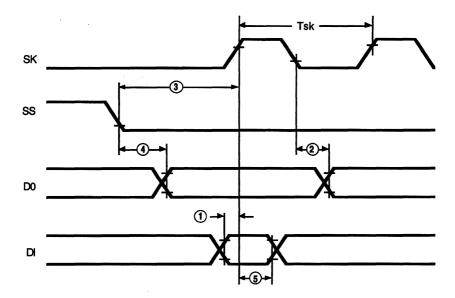

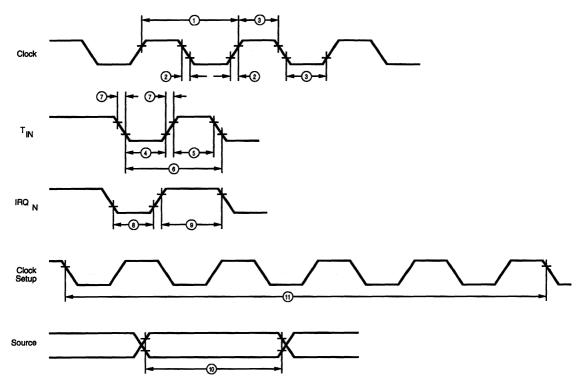

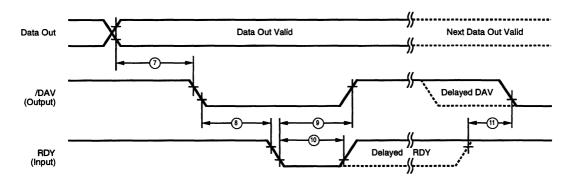

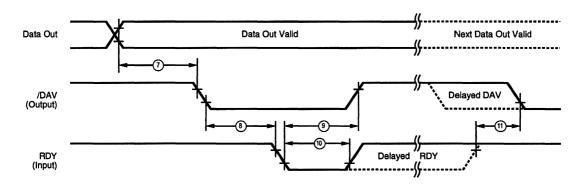

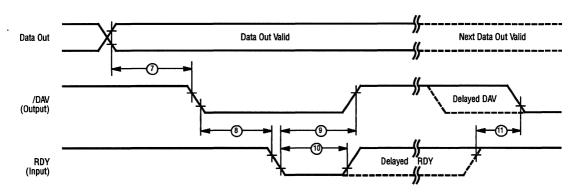

for clock control in slave mode, bit D1 in the SPI Control Register is used to log any RxCharOverrun (Figure 15 and Figure 16).

| Parameter          | Min                                                                  | Units                                                                       |

|--------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|

| DI to SK Setup     | 10                                                                   | ns                                                                          |

| SK to D0 Valid     | 15                                                                   | ns                                                                          |

| SS to SK Setup     | .5 Tsk                                                               | ns                                                                          |

| SS to D0 Valid     | 15                                                                   | ns                                                                          |

| SK to DI Hold Time | 10                                                                   | ns                                                                          |

|                    | DI to SK Setup<br>SK to D0 Valid<br>SS to SK Setup<br>SS to D0 Valid | DI to SK Setup 10 SK to D0 Valid 15 SS to SK Setup .5 Tsk SS to D0 Valid 15 |

Figure 15. SPI Timing (Z86C06 Only)

Figure 16. SPI Logic (Z86C06 Only)

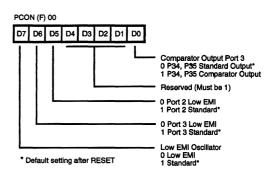

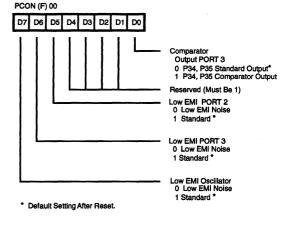

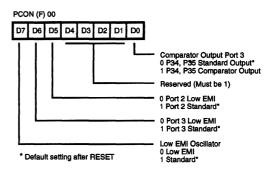

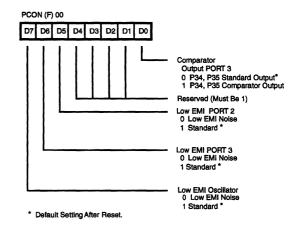

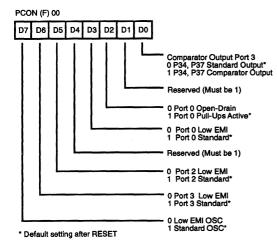

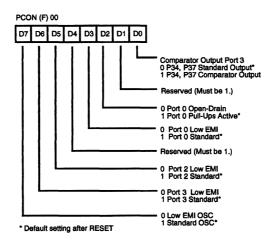

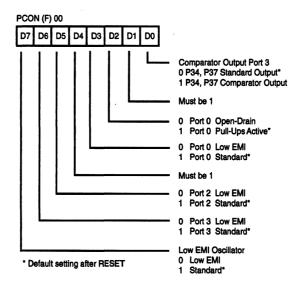

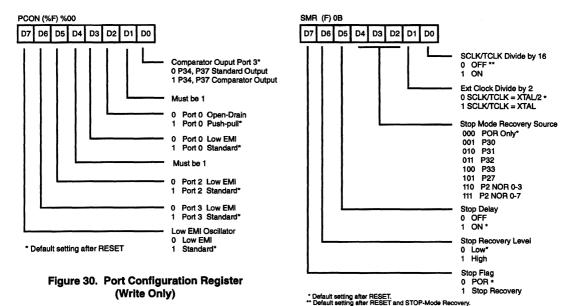

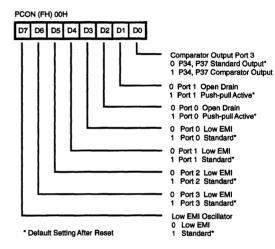

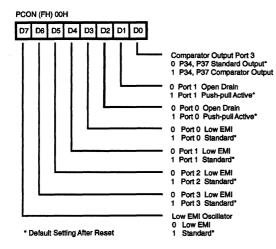

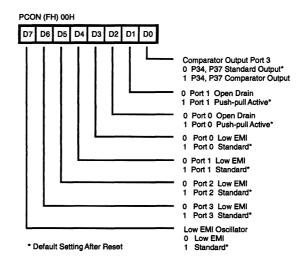

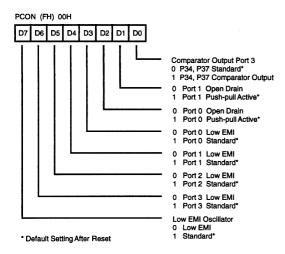

**PORT Configuration Register (PCON).** The PCON configures the ports individually for comparator output on Port 3, low EMI noise on Ports 2 and 3, and low EMI noise oscillator. The PCON Register is located in the Expanded Register File at bank F, location 00 (Figure 17).

**Comparator Output Port 3 (D0).** Bit 0 controls the comparator used in Port 3. A 1 in this location brings the comparator outputs to P34, and P35 and a 0 releases the Port to its standard I/O configuration.

Bits D4-D1. These bits are reserved and must be 1.

**Low EMI Port 2 (D5).** Port 2 is configured as a Low EMI Port by resetting this bit (D5=0) or configured as a Standard Port by setting D5=1. The default value is 1.

**Low EMI Port 3 (D6).** Port 3 is configured as a Low EMI Port by resetting this bit (D6=0) or configured as a Standard Port by setting D6=1. The default value is 1.

**Low EMI OSC (D7).** This bit of the PCON Register controls the low EMI noise oscillator. A 1 in this location configures the oscillator with standard drive. While a 0 configures the oscillator with low noise drive, it does not affect the relationship of SCLK and XTAL.

Figure 17. Port Configuration Register (PCON) (Write Only)

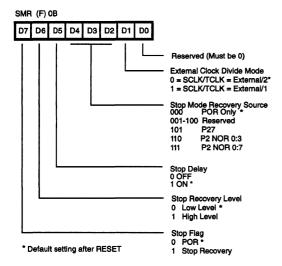

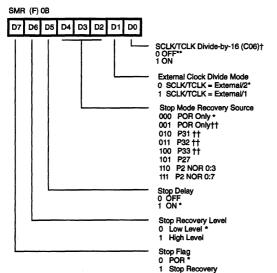

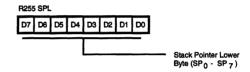

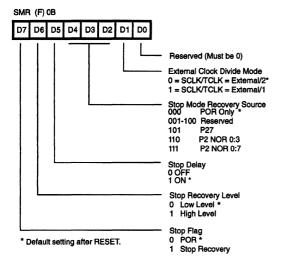

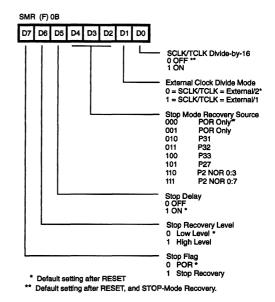

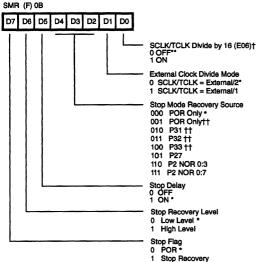

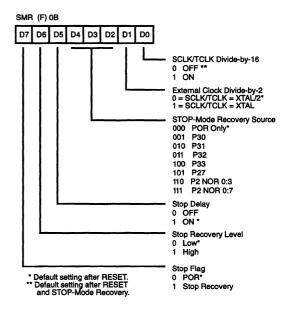

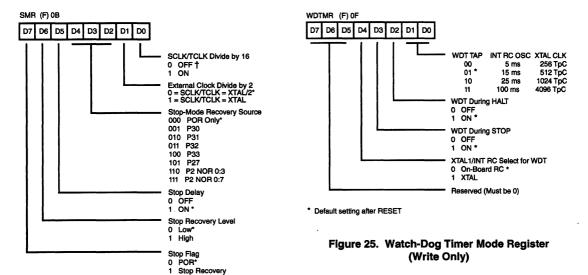

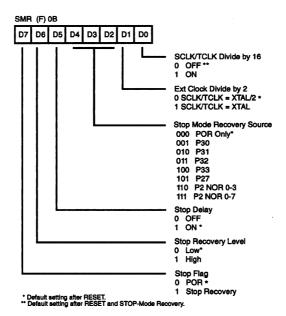

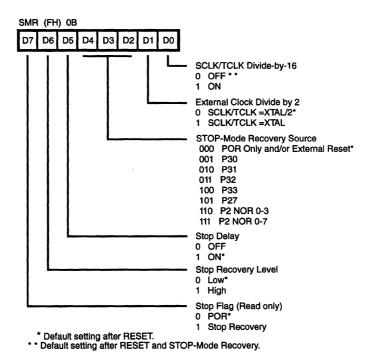

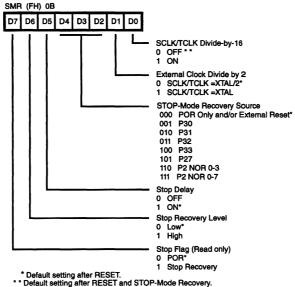

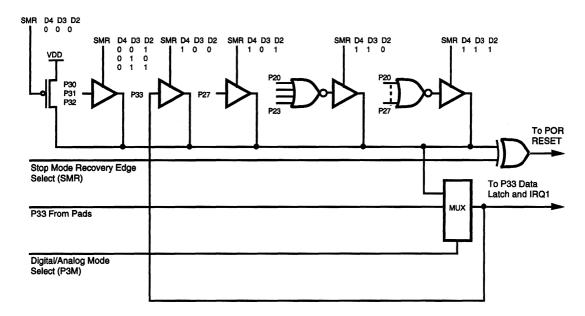

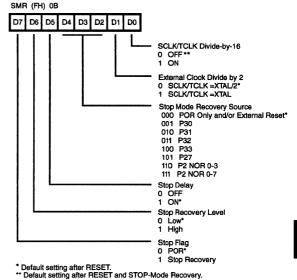

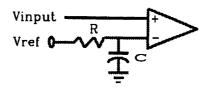

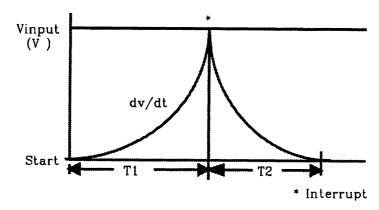

STOP-Mode Recovery Register (SMR). This register selects the clock divide value and determines the mode of STOP-Mode Recovery (Figure 18), All bits are Write Only except bit 7, which is Read Only. Bit 7 is a flag bit that is hardware set on the condition of a STOP recovery and reset on a power-on cycle. Bit 6 controls whether a low level or high level is required from the recovery source. The recovery level must be active Low to work with SPI. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4 of the SMR specify the source of the STOP-Mode Recovery signal. Bit 1 determines whether the XTAL is divided by 1 or 2. A 0 in this location uses XTAL divide-by-two, and a 1 uses XTAL. The default for this bit is XTAL divide-by-two. Bit 0 controls the divide-by-16 prescaler of SCLK/TCLK. The SMR is located in bank F of the Expanded Register Group at address 0BH.

Figure 18a. STOP-Mode Recovery Register (Write Only except bit D7, which is Read Only.) (Z86C03)

Figure 18b. STOP-Mode Recovery Register (Write Only except bit D7, which is Read Only.) (Z86C06)

SCLK/TCLK Divide-by-16 Select (D0)—Z86C06 Only. D0 of the SMR controls a divide-by-16 prescaler of SCLK/TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources the counter/timers and interrupt logic).

**External Clock Divide Mode (D1).** This bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, SCLK (System Clock) and TCLK (Timer Clock) are equal to the external clock frequency divided by two. The SCLK/TCLK is equal to the external clock frequency when this bit is set (D1=1). Using this bit, together with D7 of PCON, helps further lower EMI [i.e., D7 (PCON)=0, D1 (SMR=1]. The default setting is 0.

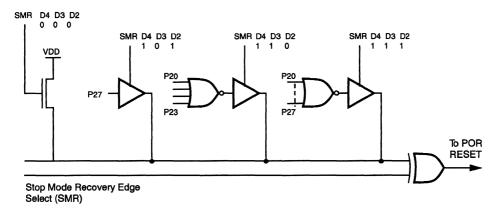

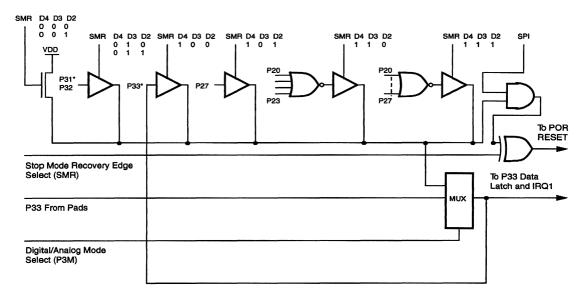

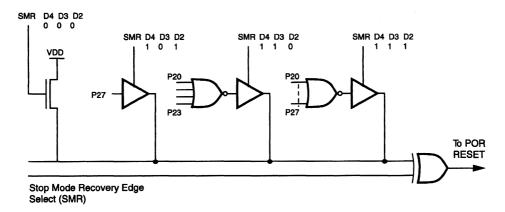

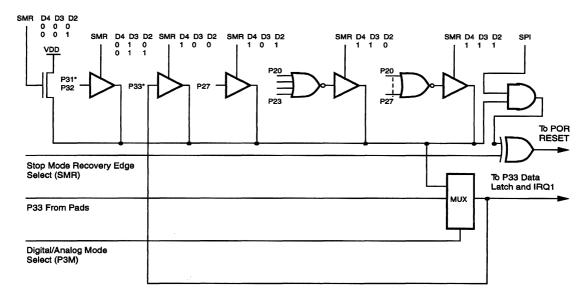

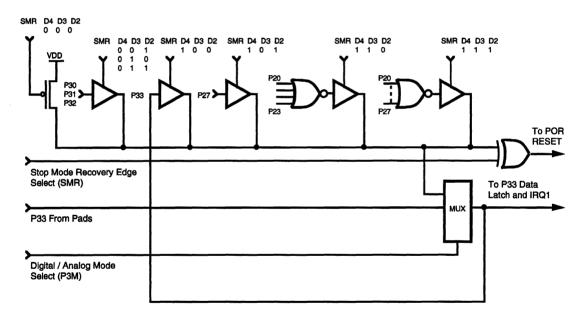

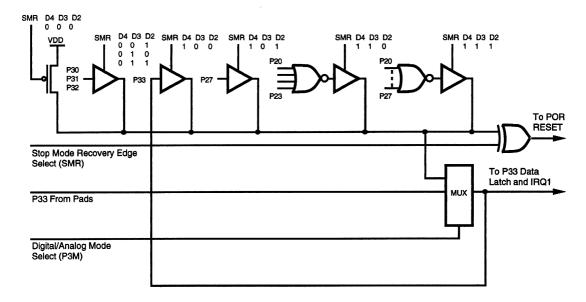

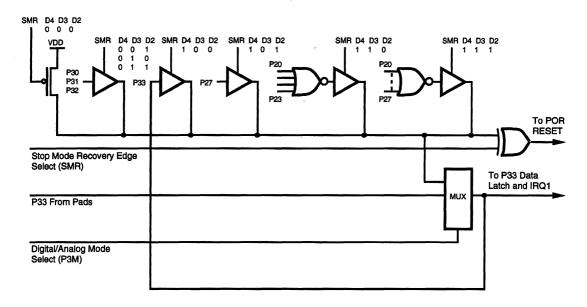

**STOP-Mode Recovery Source (D2,D3,D4).** These three bits of the SMR specify the wake-up source of the STOP-Mode Recovery (Figure 19 and Table 5).

Table 5. STOP-Mode Recovery Source

| SMR<br>D4 D3 D2 |   | D2 | Operation Description of Action    |  |

|-----------------|---|----|------------------------------------|--|

| 0               | 0 | 0  | POR recovery only                  |  |

| 0               | 0 | 1  | POR recovery only (C03 = Reserved) |  |

| 0               | 1 | 0  | P31 transition (C03 = Reserved)    |  |

| 0               | 1 | 1  | P32 transition (C03 = Reserved)    |  |

| 1               | 0 | 0  | P33 transition (C03 = Reserved)    |  |

| 1               | 0 | 1  | P27 transition                     |  |

| 1               | 1 | 0  | Logical NOR of Port 2 bits 0:3     |  |

| 1               | 1 | 1  | Logical NOR of Port 2 bits 0:7     |  |

|                 |   |    |                                    |  |

P31-P33 cannot wake up from STOP Mode if the input lines are configured as analog inputs. In the Z86C06, when the SPI is enabled and the Compare feature is active, a SMR is generated upon a comparison in the SPI Shift Register and SCOMP Register, regardless of the above SMR Reg-

ister settings. If SPI Compare is used to wake up the part from STOP Mode, it is still possible to have one of the other STOP-Mode Recovery sources active. **Note:** These other STOP-Mode Recovery sources have to be active level Low (bit D6 in SMR set to 0 if P31, P32, P33, and P27 selected, or bit D6 in SMR set to 1 if logical NOR of Port 2 is selected).

**STOP-Mode Recovery Delay Select (D5).** This bit disables the 5 ms RESET delay after STOP-Mode Recovery. The default condition of this bit is 1. If the "fast" wake up is selected, the STOP-Mode Recovery source needs to be kept active for at least 5 TpC.

**STOP-Mode Recovery Level Select (D6).** A 1 in this bit position indicates that a high level on any one of the recovery sources wakes the device from STOP Mode. A 0 indicates low level recovery. The default is 0 on POR (Figure 19).

**Cold or Warm Start (D7).** This bit is set by the device upon entering STOP Mode. It is active High, and is 0 (cold) on POR/WDT RESET. This bit is Read Only. A 1 in this bit (warm) indicates that the device awakens by a SMR source.

Figure 19a. STOP-Mode Recovery Source (Z86C03)

\*Note: P31, P32 and P33 are not in Analog Mode.

Figure 19b. STOP-Mode Recovery Source (Z86C06)

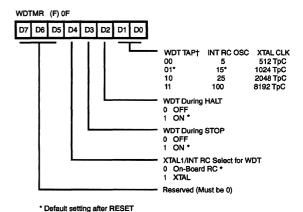

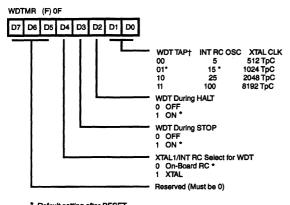

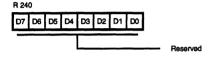

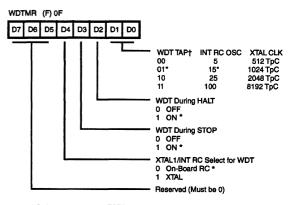

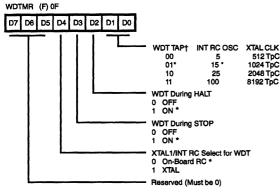

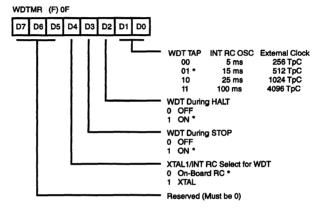

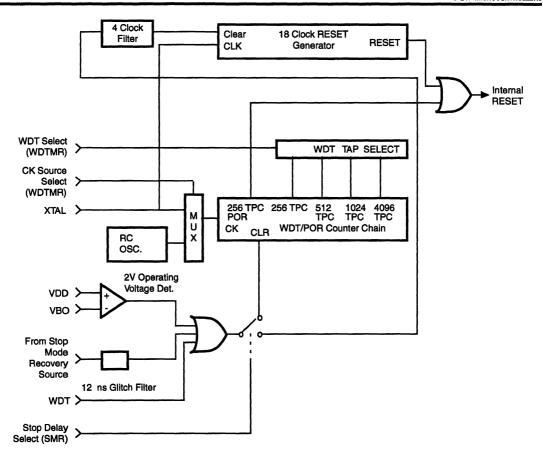

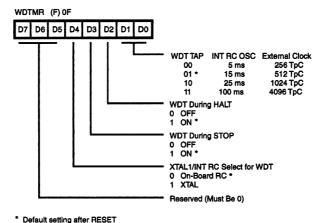

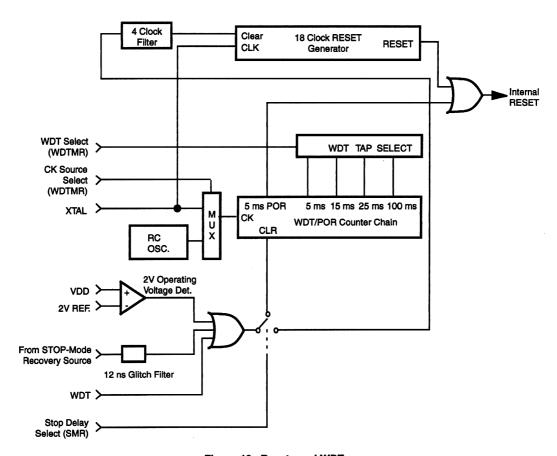

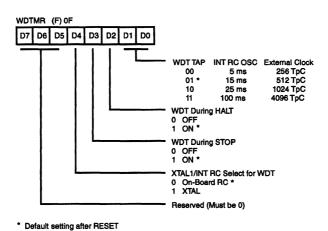

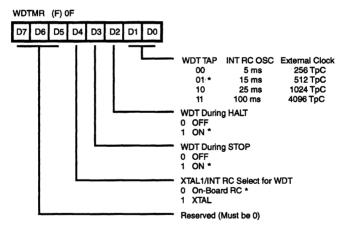

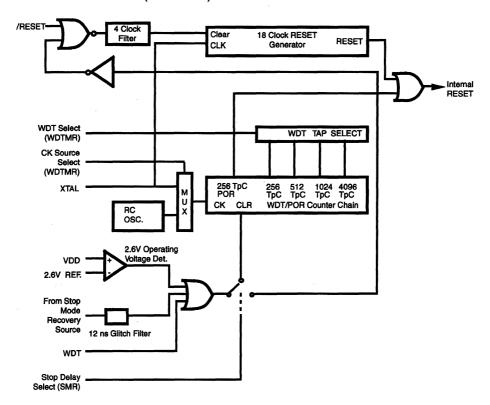

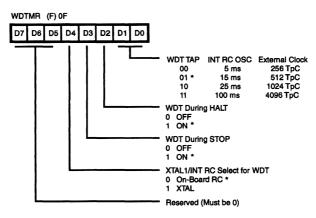

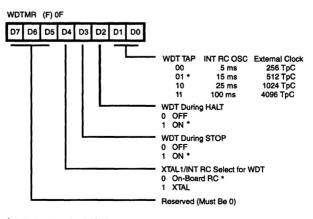

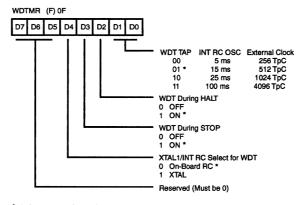

Watch-Dog Timer Mode Register (WDTMR). The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT is initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT cannot be disabled after it has been initially enabled. The WDT circuit is driven by an on-board RC oscillator or external oscillator from XTAL1 pin. The POR clock source is selected with bit 4 of the WDTMR register.

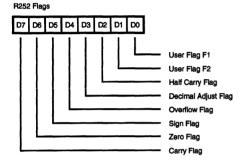

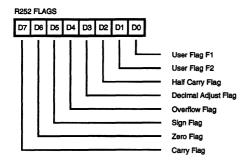

**Note:** Execution of the WDT instruction affects the Z (zero), S (sign), and V (overflow) flags.

Bits 0 and 1 control a tap circuit that determines the timeout period (on Z86C06 only). Bit 2 determines whether the WDT is active during HALT and bit 3 determines WDT activity during STOP. If bits 3 and 4 of this register are both set to 1, the WDT is only driven by the external clock during STOP mode. This feature makes it possible to wake up from STOP mode from an internal source. Bits 5 through 7 of the WDTMR are reserved (Figure 20). Note: This register is accessible only during the first 64 processor cycles (128 XTAL clocks) from the execution of the first instruction after Power-On Reset, Watch-Dog Reset or a STOP Mode Recovery (Figure 21). After this point, the

register cannot be modified by any means, intentional or otherwise. The WDTMR cannot be read and is located in bank F of the Expanded Register Group at address location 0FH.

Figure 20. Watch-Dog Timer Mode Register (Write Only)

† Must be 01 for Z86C03

<sup>\*</sup> Not available on the Z86C03, WDT fixed at 15 ms/1024TpC in the Z86C03.

Figure 21. Resets and WDT

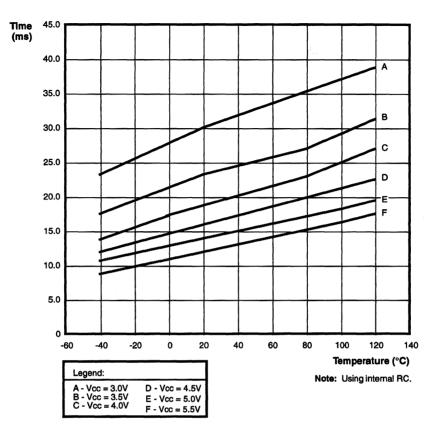

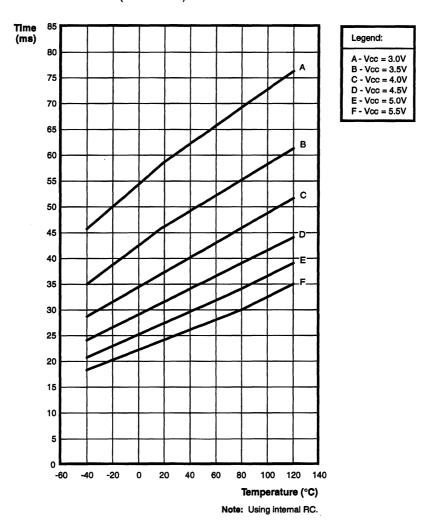

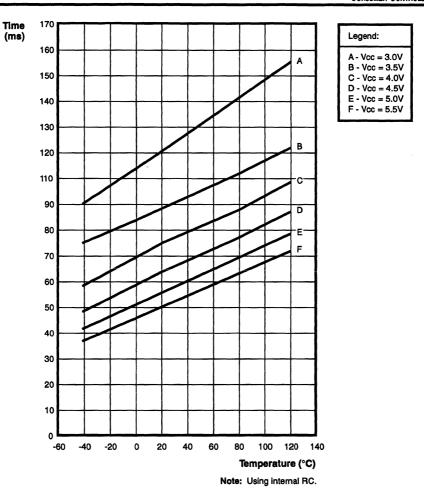

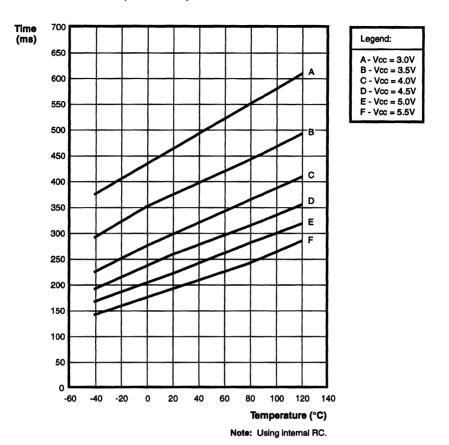

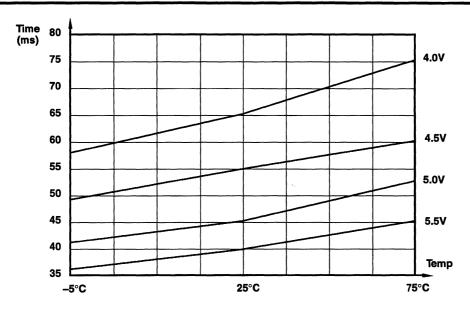

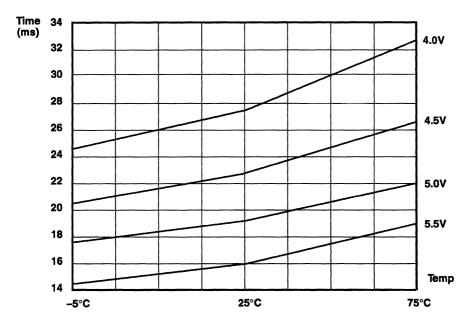

**WDT Time Select (D1, D0).** Bits 0 and 1 control a tap circuit that determines the time-out period. Table 6 shows the different values that can be obtained. The default value of D0 and D1 are 1 and 0, respectively. These select bits are present in the Z86C06 only.

Table 6. Time-Out Period of the WDT (Z86C06 Only)

| D1 | D0 | Time-Out of Internal RC OSC | Time-Out of<br>XTAL Clock |

|----|----|-----------------------------|---------------------------|

| 0  | 0  | 5 ms min                    | 256TpC                    |

| 0  | 1  | 15 ms min                   | 512TpC                    |

| 1  | 0  | 25 ms min                   | 1024TpC                   |

| 1  | 1  | 100 ms min                  | 4096TpC                   |

#### Notes:

TpC = XTAL clock cycle

The default on reset is 15 ms, D0 = 1 and D1 = 0.

See Figures 53 to 56 for details.

The values given are for  $V_{cc} = 5.0V$ .

For the Z86C03, the WDT time-out value is fixed at 1024 TpC (depending on WDTMR bit D4) period. When writing to the WDTMR in the Z86C03, bit D0 must be 1 and D1 must be 0.

**WDT During HALT (D2).** This bit determines whether or not the WDT is active during HALT mode. A 1 indicates active during HALT. The default is 1.

**WDT During STOP (D3).** This bit determines whether or not the WDT is active during STOP mode. Since XTAL clock is stopped during STOP Mode, unless as specified below, the on-board RC must be selected as the clock source to the POR counter. A 1 indicates active during STOP. The default is 1. If bits D3 and D4 are both set to 1, the WDT only, is driven by the external clock during STOP mode.

Clock Source for WDT (D4). This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a 1, the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1. The default configuration of this bit is 0, which selects the internal RC oscillator.

Bits 5, 6 and 7. These bits are reserved.

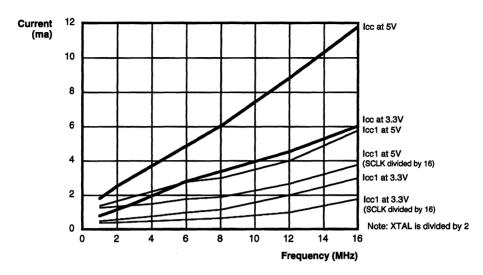

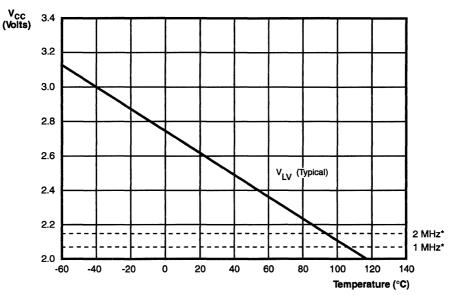

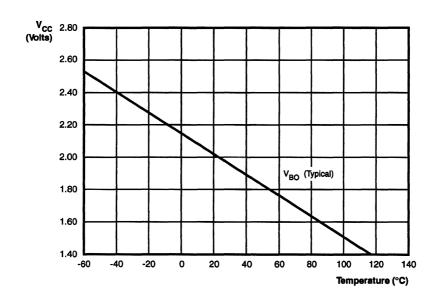

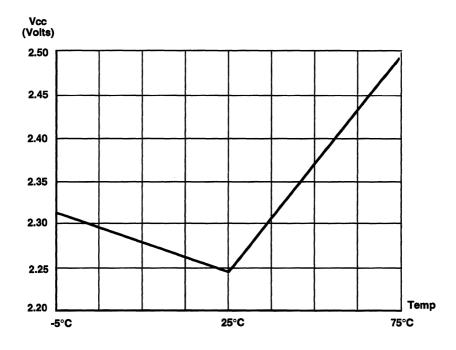

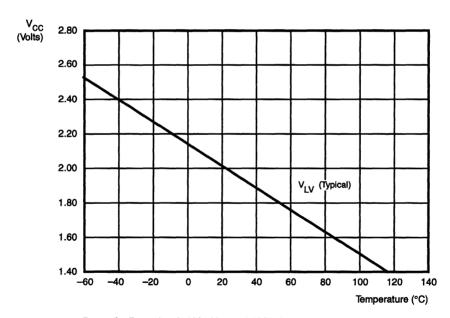

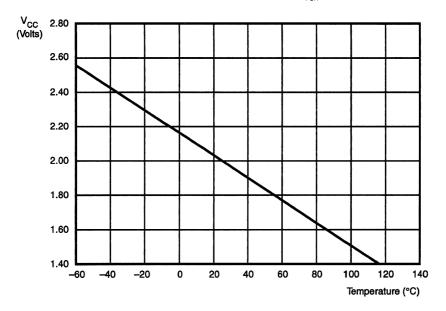

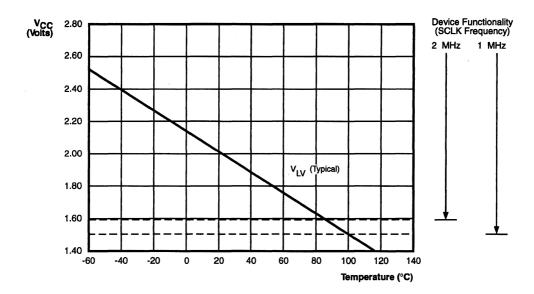

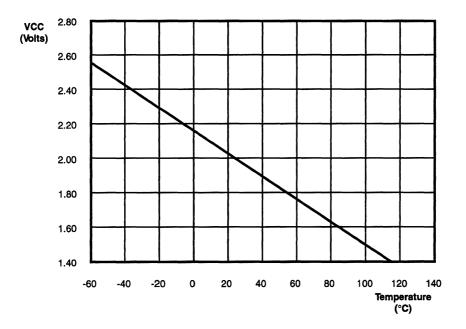

$V_{cc}$  **Voltage Comparator.** An on-board Voltage Comparator checks that  $V_{cc}$  is at the required level to ensure correct operation of the device. Reset is globally driven if  $V_{cc}$  is below the specified voltage (typically 2.1V).

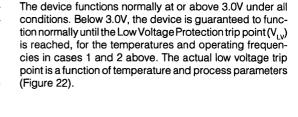

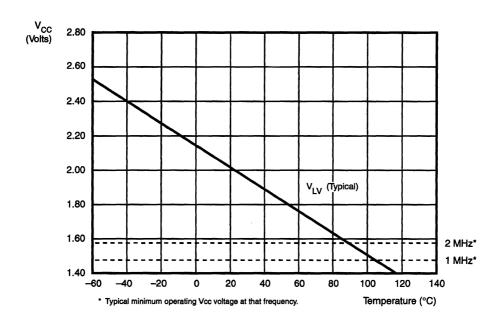

Low Voltage Protection (V<sub>LV</sub>). The Low Voltage Protection trip point  $(V_{LV})$  will be less than 3 volts and above 1.4 volts under the following conditions.

Maximum (V, v) Conditions:

Case 1:  $T_A = -40^{\circ}$  to +105°C, Internal Clock (SCLK) Frequency equal or less than 1 MHz

Case 2:  $T_A = -40^{\circ}$  to +85°C, Internal Clock (SCLK) Frequency equal or less than 2 MHz

Note: The internal clock frequency (SCLK) is determined by SMR (F)

0BH bit D1.

Figure 22. Typical Z86C03/C06 V<sub>1 v</sub> Voltage vs Temperature

#### ABSOLUTE MAXIMUM RATINGS

| Symbol                             | Description         | Min  | Max  | Units      |

|------------------------------------|---------------------|------|------|------------|

| V <sub>CC</sub>                    | Supply Voltage*     | -0.3 | +7.0 | ٧          |

| V <sub>CC</sub>                    | Max Input Voltage** |      | 12   | a <b>V</b> |

| T <sub>ere</sub>                   | Storage Temp        | -65  | +150 | °C         |

| T <sub>STG</sub><br>T <sub>A</sub> | Oper Ambient Temp   | †    |      | °C         |

#### Notes:

- \* Voltage on all pins with respect to GND.

- \*\* Applies to Port pins only and must limit current going into or out of Port pins to 250 μA maximum.

- † See Ordering Information

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

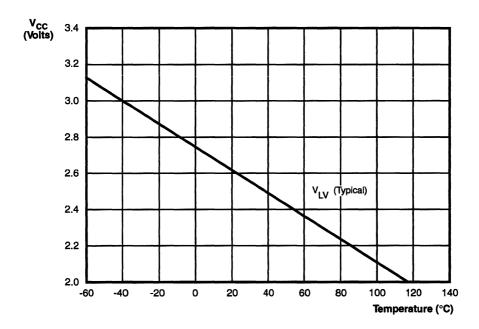

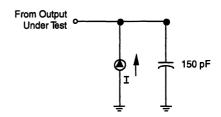

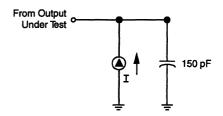

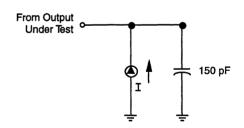

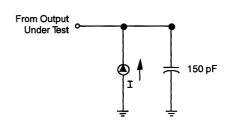

### STANDARD TEST CONDITIONS

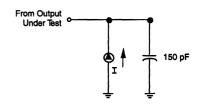

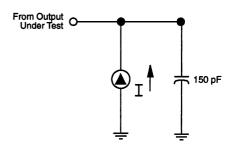

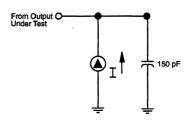

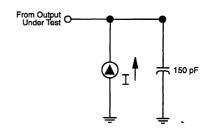

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 23).

Figure 23. Test Load Configuration

### **CAPACITANCE**

$T_A = 25^{\circ}$  C,  $V_{CC} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input Capacitance  | 0   | 12 pF |

| Output Capacitance | 0   | 20 pF |

| I/O Capacitance    | 0   | 25 pF |

### **V<sub>cc</sub> SPECIFICATION**

$V_{cc} = 3.0V \text{ to } 5.5V$

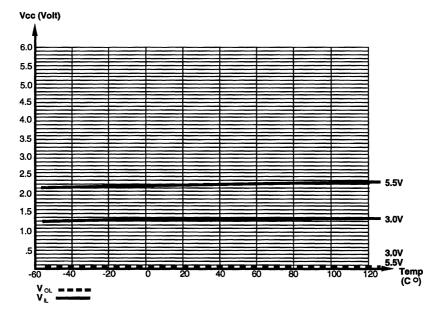

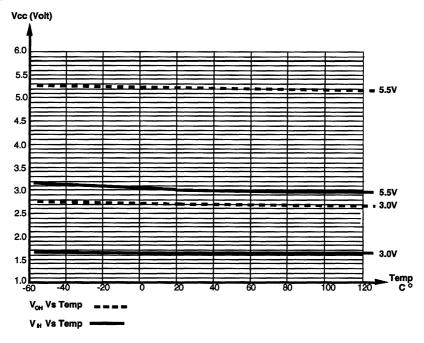

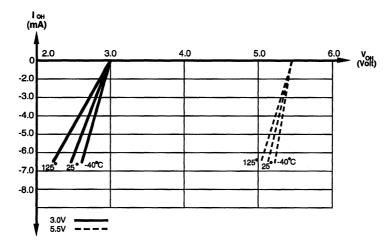

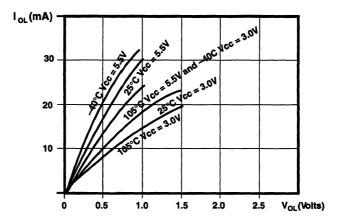

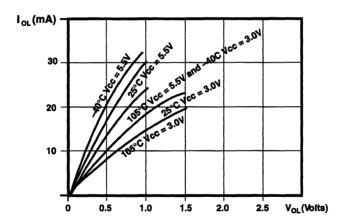

# **DC ELECTRICAL CHARACTERISTICS** Z86C03/C06

| Symbol               | Parameter                          | V <sub>cc</sub><br>Note [3] | T <sub>A</sub> = 0°C<br>to +70°C<br>Min Max                                          | T <sub>A</sub> = -40°C<br>to +105°C<br>Min Max                                       | Typical<br>@ 25°C | Units    | Conditions                             | Notes                    |

|----------------------|------------------------------------|-----------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------|----------|----------------------------------------|--------------------------|

| V <sub>CH</sub>      | Clock Input High<br>Voltage        | 3.0V                        | 0.9 V <sub>cc</sub> V <sub>cc</sub> +0.3                                             | 0.9 V <sub>cc</sub> V <sub>cc</sub> +0.3                                             | 2.4               | ٧        | Driven by External<br>Clock Generator  |                          |

|                      |                                    | 5.5V                        | $0.9V_{cc}$ $V_{cc}$ + $0.3$                                                         | 0.9 V <sub>cc</sub> V <sub>cc</sub> +0.3                                             | 3.9               | ٧        | Driven by External<br>Clock Generator  |                          |

| V <sub>CL</sub>      | Clock Input Low<br>Voltage         | 3.0V                        | V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub>                                             | V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub>                                             | 1.6               | ٧        | Driven by External<br>Clock Generator  |                          |

|                      | rollago                            | 5.5V                        | $V_{ss}$ –0.3 0.2 $V_{cc}$                                                           | V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub>                                             | 2.7               | ٧        | Driven by External<br>Clock Generator  |                          |

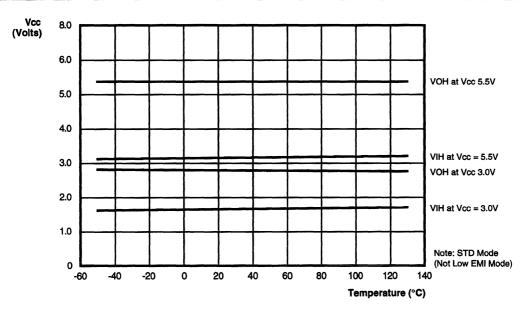

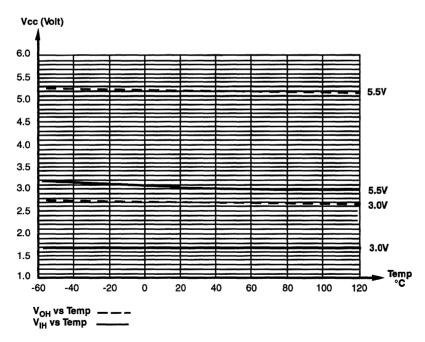

| V <sub>IH</sub>      | Input High Voltage                 | 3.0V                        | 0.7 V <sub>20</sub> V <sub>20</sub> +0.3                                             | 0.7 V <sub>cc</sub> V <sub>cc</sub> +0.3                                             | 1.8               | ٧        |                                        |                          |

| - ІН                 | parringreilage                     | 5.5V                        | 0.7 V <sub>cc</sub> V <sub>cc</sub> +0.3<br>0.7 V <sub>cc</sub> V <sub>cc</sub> +0.3 | 0.7 V <sub>cc</sub> V <sub>cc</sub> +0.3                                             | 2.8               | V        |                                        |                          |

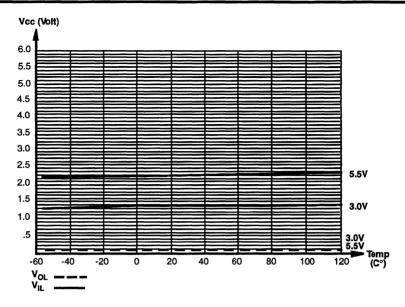

| V <sub>IL</sub>      | Input Low Voltage                  | 3.0V                        | V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub>                                             | V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub><br>V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub> | 1.0               | V        |                                        |                          |

| "-                   |                                    | 5.5V                        | V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub><br>V <sub>ss</sub> -0.3 0.2 V <sub>cc</sub> | $V_{ss}^{ss}$ -0.3 0.2 $V_{cc}^{sc}$                                                 | 1.5               | ٧        |                                        |                          |

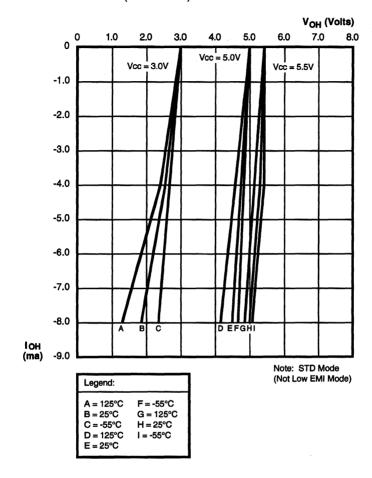

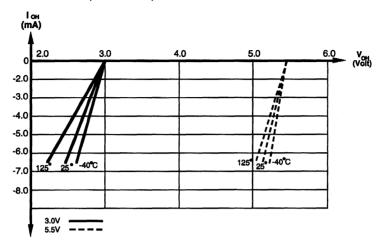

| V <sub>OH</sub>      | Output High Voltage                | 3.0V                        | V <sub>cc</sub> -0.4                                                                 | V <sub>cc</sub> -0.4                                                                 | 3.1               | ٧        | $I_{OH} = -2.0 \text{ mA}$             | [10]                     |

| OII                  |                                    | 5.5V                        | V <sub>cc</sub> -0.4                                                                 | V <sub>cc</sub> -0.4                                                                 | 4.8               | ٧        | $I_{OH} = -2.0 \text{ mA}$             | [10]                     |

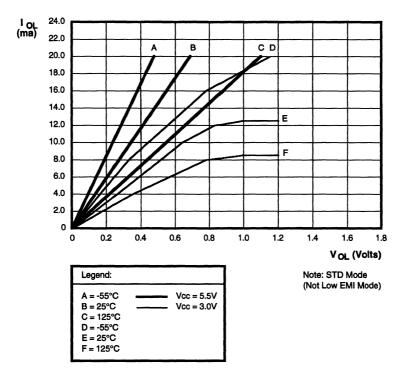

| $\overline{V_{0L1}}$ | Output Low Voltage                 | 3.0V                        | 0.8                                                                                  | 0.8                                                                                  | 0.2               | ٧        | $I_{0L} = +4.0 \text{ mA}$             | [10]                     |

| <b>01</b> .          |                                    | 5.5V                        | 0.4                                                                                  | 0.4                                                                                  | 0.1               | ٧        | $l_{0L}^{0L} = +4.0 \text{ mA}$        | [10]                     |

| V <sub>OL2</sub>     | Output Low Voltage                 | 3.0V                        | 1.0                                                                                  | 1.0                                                                                  | 0.4               | ٧        | l <sub>oL</sub> = + 6 mA,<br>3 Pin Max | [10]                     |

|                      |                                    | 5.5V                        | 1.0                                                                                  | 1.0                                                                                  | 0.5               | V        | l <sub>oL</sub> = +12 mA,<br>3 Pin Max | [10]                     |

| V <sub>OFFSET</sub>  | Comparator Input                   | 3.0V                        | 25                                                                                   | 25                                                                                   | 10                | mV       |                                        |                          |

| 552.                 | Offset Voltage                     | 5.5V                        | 25                                                                                   | 25                                                                                   | 10                | mV       |                                        |                          |

| V <sub>ICR</sub>     | Input Common<br>Mode Voltage Range | 3.0V<br>5.5V                | 0V V <sub>cc</sub> -1.0v<br>0V V <sub>cc</sub> -1.0v                                 | 0V V <sub>cc</sub> -1.5v<br>0V V <sub>cc</sub> -1.5v                                 |                   |          |                                        | [7]<br>[7]               |

| I <sub>L</sub>       | Input Leakage                      | 3.0V                        | -1.0 1.0                                                                             | -1.0 1.0                                                                             |                   | μA       | $V_{IN} = OV, V_{CC}$                  |                          |

|                      | (Input bias current of comparator) | 5.5V                        | <b>-1.0</b> 1.0                                                                      | -1.0 1.0                                                                             |                   | μА       | $V_{iN}^{iN} = OV, V_{CC}^{oc}$        |                          |

| I <sub>OL</sub>      | Output Leakage                     | 3.0V                        | -1.0 1.0                                                                             | -1.0 1.0                                                                             |                   | μA       | $V_{iN} = OV, V_{CC}$                  |                          |

|                      |                                    | 5.5V                        | -1.0 1.0                                                                             | -1.0 1.0                                                                             |                   | μA       | $V_{IN}^{IN} = OV, V_{CC}^{CC}$        |                          |

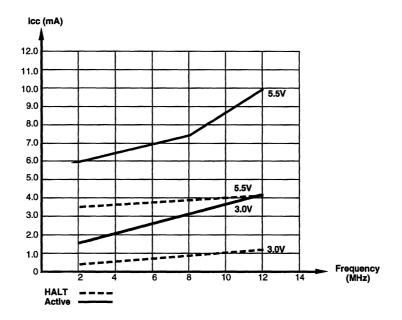

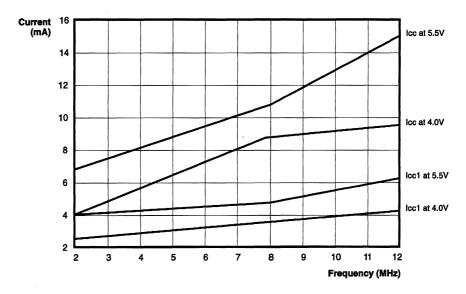

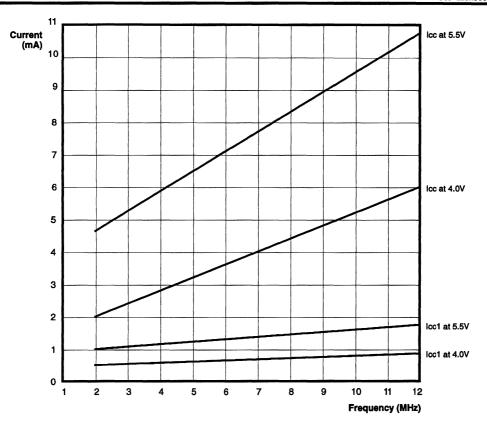

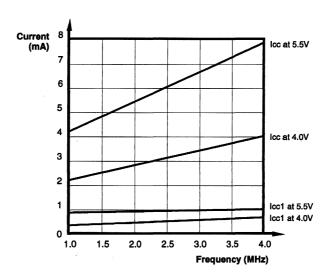

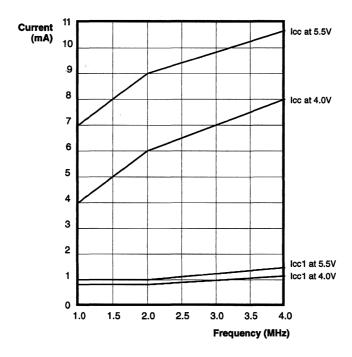

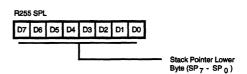

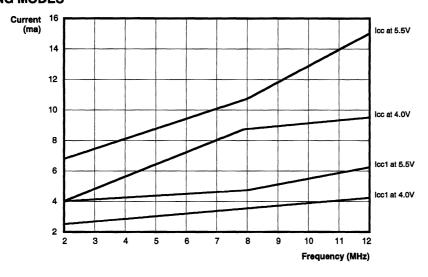

| I <sub>cc</sub>      | Supply Current                     | 3.2V                        |                                                                                      |                                                                                      | 8.0               | μA       | @32 kHz                                | [13]                     |

|                      |                                    | 3.0V                        | 6                                                                                    | 6                                                                                    | 3.0               | mA<br>m^ | @ 8 MHz                                | [4,5,10]                 |

|                      |                                    | 5.5V<br>3.0V                | 11.0<br>8.0                                                                          | 11.0<br>8.0                                                                          | 6.0<br>4.5        | mA<br>mA | @ 8 MHz<br>@ 12 MHz [                  | [4,5,10]<br>4 5 10 111   |

|                      |                                    | 5.5V                        | 6.0<br>15                                                                            | 6.0<br>15                                                                            | 4.5<br>9.0        | mA<br>mA |                                        | 4,5,10,11]<br>4,5,10,11] |

### DC ELECTRICAL CHARACTERISTICS

Z86C03/C06

| Symbol           | Parameter                                         | V <sub>cc</sub><br>Note [3] |      | = 0°C<br>+70°C<br>Max | T <sub>A</sub> =<br>to +<br>Min | -40°C<br>105°C<br>Max | Typical<br>@ 25°C | Units    | Conditions                                                                       | Notes        |

|------------------|---------------------------------------------------|-----------------------------|------|-----------------------|---------------------------------|-----------------------|-------------------|----------|----------------------------------------------------------------------------------|--------------|

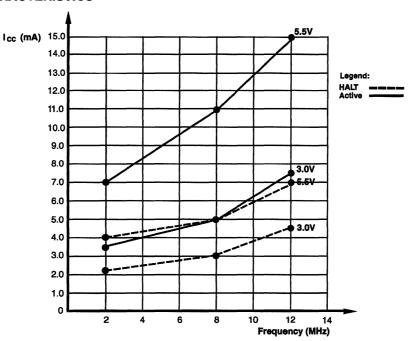

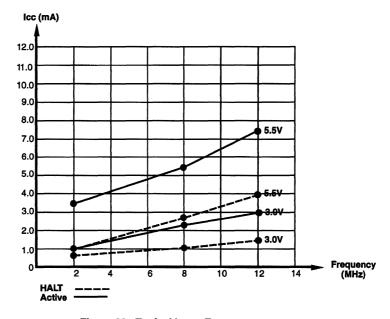

| I <sub>CC1</sub> | Standby Current                                   | 3.0V                        |      | 3.0                   |                                 | 3.0                   | 1.3               | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 8 MHz                       | [4, 5,10]    |

|                  |                                                   | 5.5V                        |      | 5                     |                                 | 5                     | 3.0               | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> 8 MHz                         | [4, 5,10]    |

|                  |                                                   | 3.0V                        |      | 4.5                   |                                 | 4.5                   | 2.0               | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 12 MHz                      | [4, 5,10,11] |

|                  |                                                   | 5.5V                        |      | 7.0                   |                                 | 7.0                   | 4.0               | mA       | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 12 MHz                      | [4, 5,10,11] |

|                  |                                                   | 3.0V                        |      | 1.4                   |                                 | 1.4                   | 0.7               | mA       | Clock Divide-by-16  @ 8 MHz                                                      | [4, 5,10]    |

|                  |                                                   | 5.5V                        |      | 3.5                   |                                 | 3.5                   | 2.0               | mA       | Clock Divide-by-16<br>@ 8 MHz                                                    | [4, 5,10]    |

|                  |                                                   | 3.0V                        |      | 2.0                   |                                 | 2.0                   | 1.0               | mA       | Clock Divide-by-16<br>@ 12 MHz                                                   | [4, 5,10,11] |

|                  |                                                   | 5.5V                        |      | 4.5                   |                                 | 4.5                   | 2.5               | mA       | Clock Divide-by-16<br>@ 12 MHz                                                   | [4, 5,10,11] |

| I <sub>CC2</sub> | Standby Current                                   | 3.0V                        |      | 10                    |                                 | 20                    | 1.0               | μA       | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>cc</sub> WDT is not Running            | [6, 9]       |

|                  |                                                   | 5.5V                        |      | 10                    |                                 | 20                    | 3.0               | μA       | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>cc</sub> WDT is not Running            | [6, 9]       |

|                  |                                                   | 3.0V                        |      | 600                   |                                 | 600                   | 400               | μA       | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>CC</sub> WDT is Running                | [6, 9,12]    |

|                  |                                                   | 5.5V                        |      | 1000                  |                                 | 1000                  | 800               | μA       | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>cc</sub> WDT is Running                | [6, 9,12]    |

| ALL              | Auto Latch Low<br>Current                         | 3.0V                        |      | 7.0                   |                                 | 14.0                  | 4.0               | μA       | OV < V <sub>IN</sub> < V <sub>CC</sub>                                           |              |

|                  | ouncil                                            | 5.5V                        |      | 20.0                  |                                 | 30.0                  | 10                | μA       | $OV < V_{IN} < V_{CC}$                                                           |              |

| I <sub>ALH</sub> | Auto Latch High<br>Current                        | 3.0V<br>5.5V                |      | -4.0<br>-9.0          |                                 | -8.0<br>-16.0         | 2.0<br>5.0        | μA<br>μA | 0V < V <sub>IN</sub> < V <sub>CC</sub><br>0V < V <sub>IN</sub> < V <sub>CC</sub> |              |

| V <sub>LV</sub>  | V <sub>cc</sub> Low Voltage<br>Protection Voltage |                             | 1.50 | 2.95                  | 1.2                             | 2.95                  | 2.1               | ٧        | 2 MHz max Ext. CLK Fro                                                           | eq. [3]      |

Notes:

[2] V<sub>ss</sub> = 0V = GND

[8] Excludes clock pins.

- [10] STD mode (not low EMI mode).

- [11] Z86C06 only

- [12] Internal RC is WDT clock source.

- [13]  $C_{L1} = 100 \text{ pF}, C_{L2} = 220 \text{ pF}$

Clock Driven on XTAL Тур Max Unit Freq [1] 8 MHz 5.0 0.3 mΑ Crystal or Ceramic Resonator 3.0 mΑ 8 MHz

<sup>[3]</sup> V<sub>cc</sub> = 3.0V to 5.5V. The V<sub>LV</sub> increases as the temperature decreases. Typical values measured at 3.3V and 5.0V.

All outputs unloaded, I/O pins floating, inputs at rail.

<sup>[5]</sup>  $C_{L1} = C_{L2} = 100 \text{ pF}$ [6] Same as note [4] except inputs at  $V_{cc}$ .

<sup>[7]</sup> For analog comparator inputs when analog comparators are enabled.

<sup>[9]</sup> Clock must be forced Low when XTAL1 is clock-driven and XTAL2 is floating.

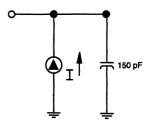

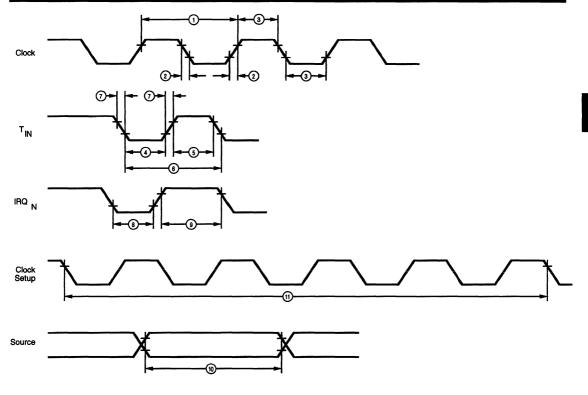

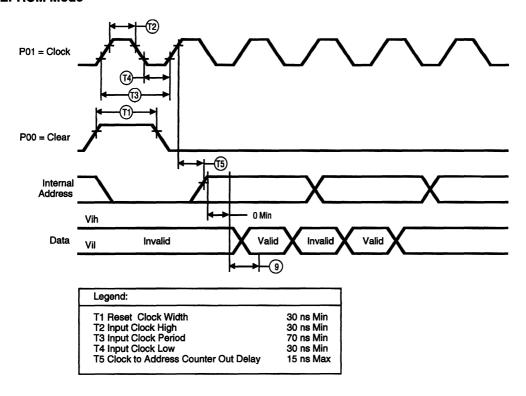

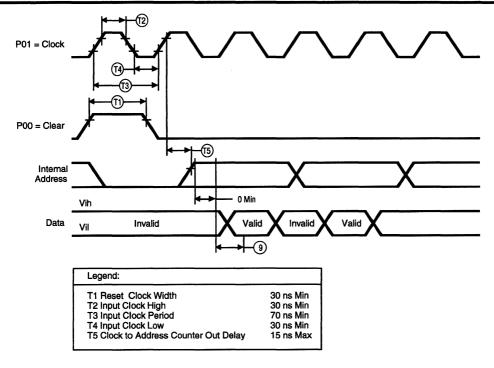

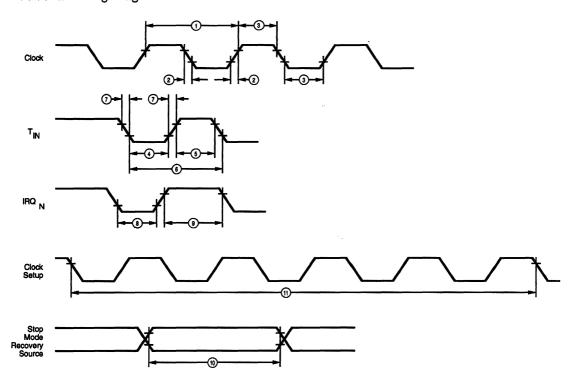

Figure 24. Additional Timing

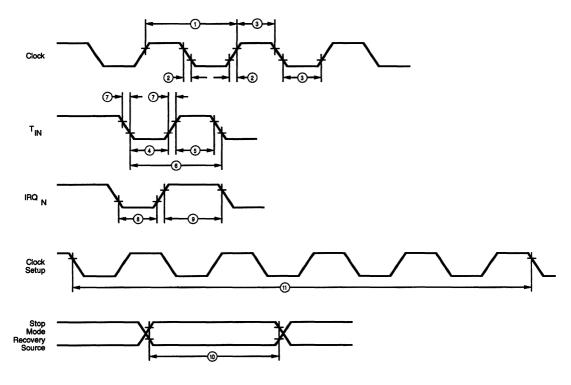

### **AC ELECTRICAL CHARACTERISTICS**

(SCLK/TCLK = EXTERNAL/2)

|    |         |                                    | V <sub>cc</sub> | T <sub>A</sub> = 0°C to +70°C<br>8 MHz <sup>[11]</sup> 12 MHz <sup>[11]</sup> |          |              | T <sub>A</sub> = -40°C to +105°C<br>8 MHz <sup>[11]</sup> 12 MHz <sup>[11]</sup> |              |          |              |          |          |                |

|----|---------|------------------------------------|-----------------|-------------------------------------------------------------------------------|----------|--------------|----------------------------------------------------------------------------------|--------------|----------|--------------|----------|----------|----------------|

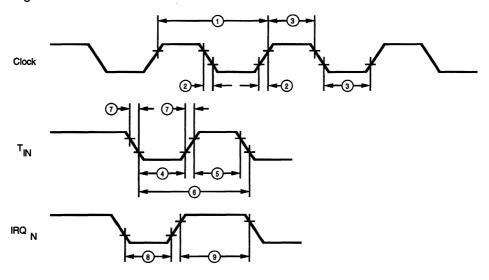

| No | Symbol  | Parameter                          | Note [3]        | Min                                                                           | Max      | Min          | Max                                                                              | Min          | Max      | Min          | Max      | Units    | Notes          |

| 1  | TpC     | Input Clock Period                 | 3.0V<br>5.5V    | 125<br>125                                                                    | DC<br>DC | 83<br>83     | DC<br>DC                                                                         | 125<br>125   | DC<br>DC | 83<br>83     | DC<br>DC | ns<br>ns | [1,7]<br>[1,7] |

| 2  | TrC,TfC | Clock Input Rise<br>and Fall Times | 3.0V<br>5.5V    |                                                                               | 25<br>25 |              | 15<br>15                                                                         |              | 25<br>25 |              | 15<br>15 | ns<br>ns | [1,7]<br>[1,7] |

| 3  | TwC     | Input Clock Width                  | 3.0V<br>5.5V    | 62<br>62                                                                      |          | 41<br>41     |                                                                                  | 62<br>62     |          | 41<br>41     |          | ns<br>ns | [1,7]<br>[1,7] |

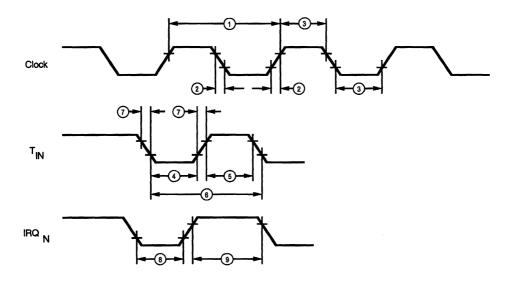

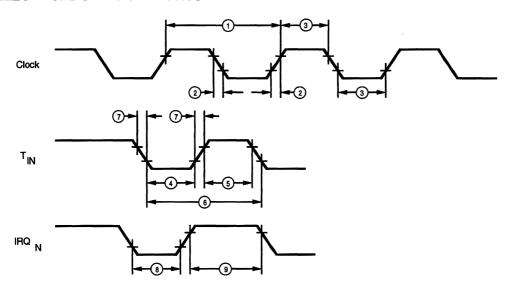

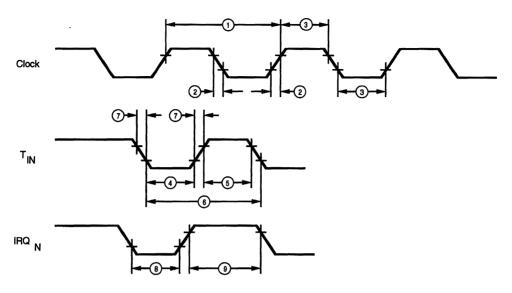

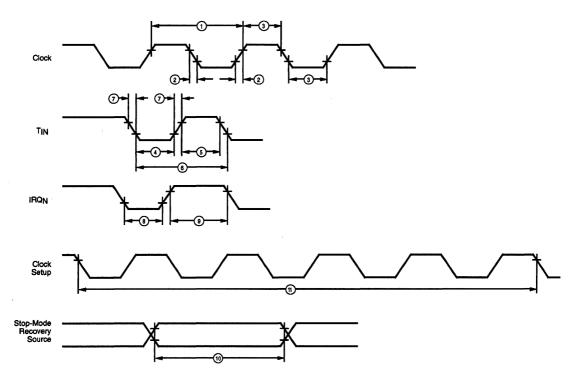

| 4  | TwTinL  | Timer Input Low Width              | 3.0V<br>5.5V    | 100<br>70                                                                     |          | 100<br>70    |                                                                                  | 100<br>70    |          | 100<br>70    |          | ns<br>ns | [1,7]<br>[1,7] |

| 5  | TwTinH  | Timer Input High Width             | 3.0V<br>5.5V    | 5TpC<br>5TpC                                                                  |          | 5TpC<br>5TpC |                                                                                  | 5TpC<br>5TpC |          | 5TpC<br>5TpC |          |          | [1,7]<br>[1,7] |

## **AC ELECTRICAL CHARACTERISTICS** (Continued) (SCLK/TCLK = EXTERNAL/2)

|    |                  |                                    | V <sub>cc</sub><br>Note [3] |              | T <sub>A</sub> = 0°C to +70°C<br>8 MHz <sup>[11]</sup> 12 MHz <sup>[11]</sup> |              | T, = | -40°C        | to +10 |              |     |       |                 |

|----|------------------|------------------------------------|-----------------------------|--------------|-------------------------------------------------------------------------------|--------------|------|--------------|--------|--------------|-----|-------|-----------------|

| No | Symbol           | Parameter                          | Note [3]                    | Min          | Max                                                                           | Min          | Max  | Min          | Max    | Min          | Max | Units | Notes           |

| 6  | TpTin            | Timer Input Period                 | 3.0V<br>5.5V                | 8TpC<br>8TpC |                                                                               | 8TpC<br>8TpC |      | 8TpC<br>8TpC |        | 8TpC<br>8TpC |     |       | [1,7]<br>[1,7]  |

| 7  | TrTin,<br>TtTin  | Timer Input Rise<br>and Fall Timer | 3.0V                        |              | 100                                                                           |              | 100  |              | 100    | -            | 100 | ns    | [1,7]           |

|    |                  |                                    | 5.5V                        |              | 100                                                                           |              | 100  |              | 100    |              | 100 | ns    | [1,7]           |

| 8  | TwlL             | Int. Request Input<br>Low Time     | 3.0V                        | 100          |                                                                               | 100          |      | 100          |        | 100          |     | ns    | [1,2]           |

|    |                  |                                    | 5.5V                        | 70           |                                                                               | 70           |      | 70           |        | 70           |     | ns    | [1,2]           |

| 9  | TwlH             | Int. Request Input<br>High Time    | 3.0V                        | 5TpC         |                                                                               | 5TpC         |      | 5TpC         |        | 5TpC         |     |       | [1,2]           |

|    |                  | · ·                                | 5.5V                        | 5TpC         |                                                                               | 5TpC         |      | 5TpC         |        | 5TpC         |     |       | [1,2]           |

| 10 | Twsm             | STOP-Mode Recovery<br>Width Spec   | 3.0V                        | 5TpC         |                                                                               | 5TpC         |      | 5TpC         |        | 5TpC         |     |       | [8,10]          |

|    |                  |                                    | 5.5V                        | 5TpC         |                                                                               | 5TpC         |      | 5TpC         |        | 5TpC         |     |       | [8,10]          |

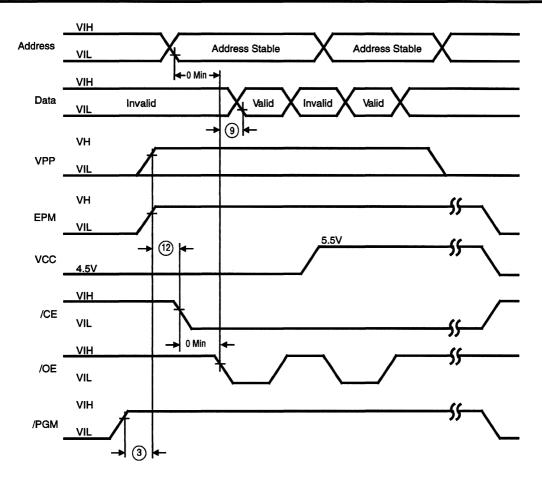

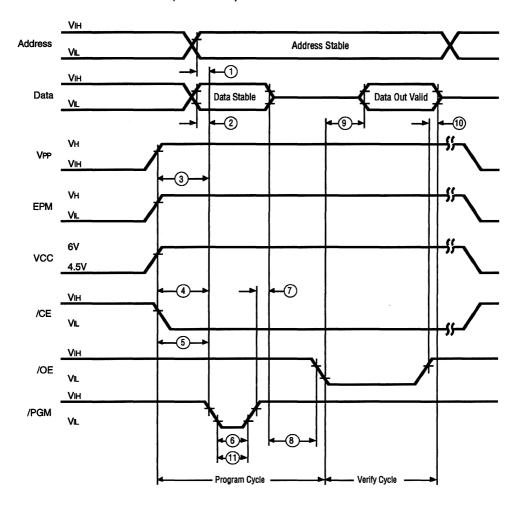

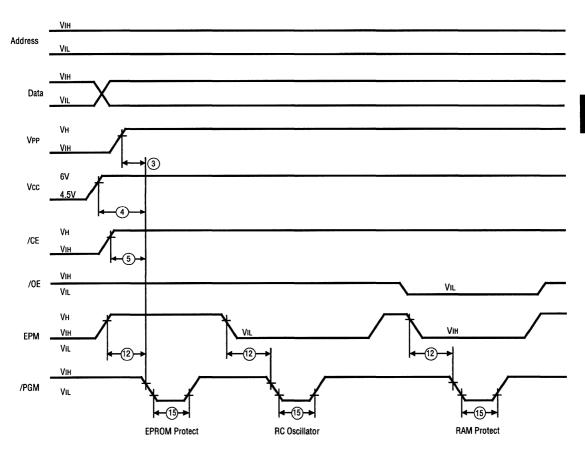

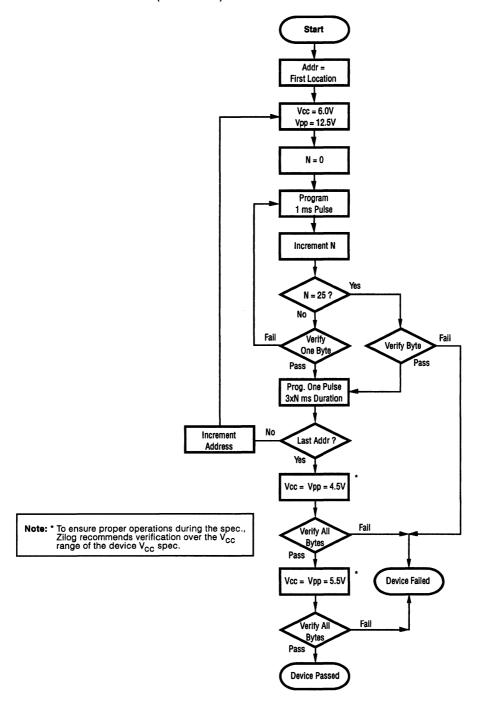

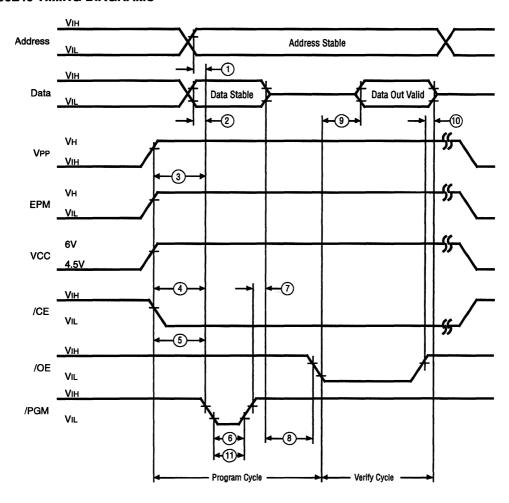

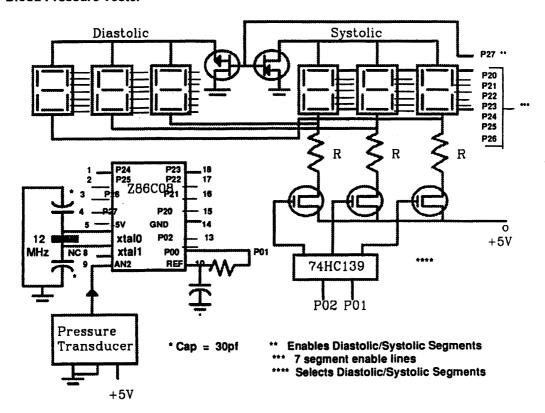

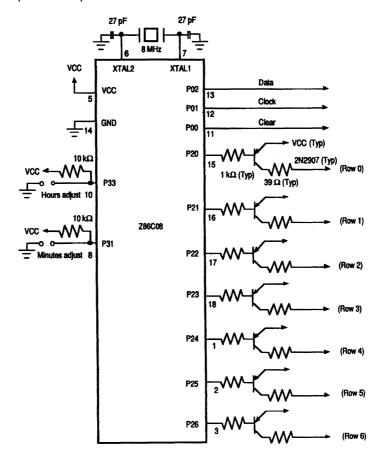

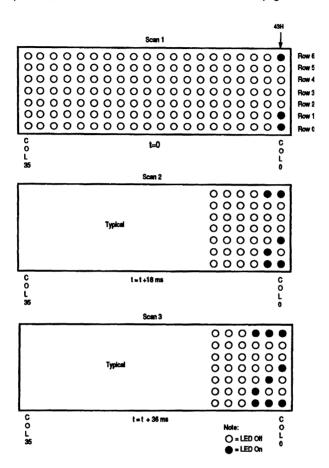

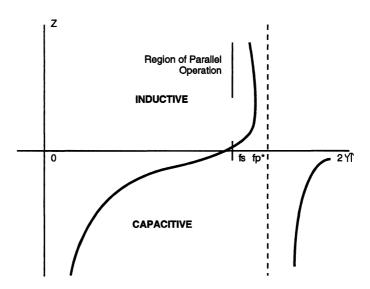

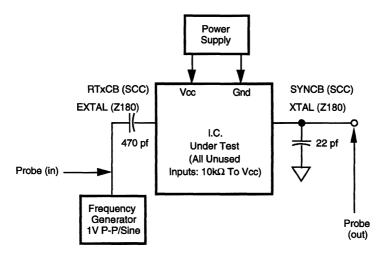

| 11 | Tost             | Oscillator Startup Time            | 3.0V                        | 12           |                                                                               | 12           |      | 12           |        | 12           |     | ns    | [4,9]           |