Issue 38 Winter 2000

Celiournal THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

#### PRODUCTS

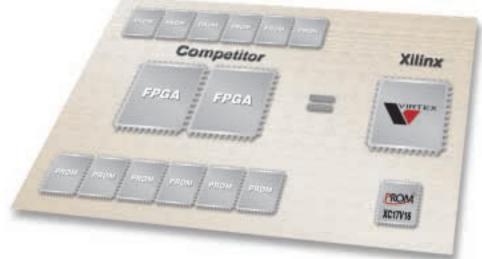

**New PROMS Simplify FPGA Designs**

#### **APPLICATIONS**

**Creating High-Performance Digital Down Converters**

#### **SOFTWARE**

**New Xilinx Foundation** Series ISE Software with **Integrated Design Flows**

#### NEW/S

Xilinx Launches **Platform-FPGA Initiative**

**XILINX**®

Synopsys Chief Technology Officer Discusses Platform-Base **FPGA Design Issues**

Cover Story

## Business is booming, and Xilinx is growing rapidly...

**P** rogrammable logic continues to grow faster than other segments of the semiconductor market, and Xilinx continues to grow along with it-there is no end in sight. To keep up with this unprecedented expansion, we are building several new facilities, acquiring new companies, and incorporating the best available complementary technologies.

We are leading the industry, not only with the most advanced device and software technologies but also with the most ambitious plans for future developments. Here are some of our most recent activities:

- Xilinx purchases two new buildings in San Jose. The buildings will provide approximately 200,000 additional square feet and are expected to house up to 700 new Xilinx employees. The purchase of the new buildings is the latest in a string of new construction projects we have undertaken in the last few years. In 1999, we completed construction of a fourth building at our San Jose headquarters, and other projects are also underway at Xilinx locations in Colorado, Ireland, and California.

- Xilinx acquires Visual Software Solutions, Inc. (VSS). Their expertise will help us further extend our software leadership and allow us to deliver a variety of customized tools that facilitate HDL-based design using our new Virtex-II FPGAs, thus improving your time-to-market. Included in the acquisition are the VSS HDL Bencher<sup>™</sup> and StateCAD<sup>™</sup> design tools.

- Xilinx acquires RocketChips, a leading developer of ultra-high-speed CMOS mixed-signal transceivers serving the networking, telecommunications, and enterprise storage markets. The RocketChips gigabit and multi-gigabit serial CMOS transceiver technologies provide solutions for a wide range of serial system architectures, and this technology will be a key feature of our nextgeneration FPGA families.

- Xilinx acquires Tornado, a full-function formal verification application deploying state-of-the-art circuit equivalence checking techniques. Based on many years of research and development efforts by Veriphia, this new software adds significant value to our advanced development tools. We plan to develop this technology even further and focus it on the Virtex FPGA architectures, in alliance with key EDA partners.

- Xilinx acquires Integral Design, a privately held design services firm headquartered in Dublin, Ireland. The acquisition enhances our professional design services capabilities in the communications and multimedia market segments. Recent advances in FPGA performance and capabilities continue to drive customer needs for additional design resources. Design services enable you to use dedicated designers with experience in Xilinx solutions to augment your own internal expertise and improve your timeto-market.

These developments continue to enhance our capability to offer you the best programmable logic devices, development tools, and services in the industry.

Our current capabilities already give you a significant ease-of-use and time-to-market advantage. As the market expands, costs decrease, and many new applications become possible, thus fueling even more growth. You can see why programmable logic is quickly becoming the technology of choice for many more applications, from low-cost consumer devices to high-performance switching systemsthere simply is no faster or easier way to create the systems of the future. And, Xilinx is well prepared to continue leading the way.

orlin Collins

Carlis Collins Editor

EDITOR

Carlis Collins editor@xilinx.com 408-879-4519

Andy Larg

Dave Stieg Mike Seither

Peter Alfke

SENIOR DESIGNER

BOARD OF ADVISORS

XCelljournal

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3450 Phone: 408-559-7778 FAX: 408-879-4780 ©2000 Xilinx Inc. All rights reserved.

Xcell is published quarterly. XILINX, the Xilinx logo, and CoolRunner are registered trademarks of Xilinx, Inc. Virtex, LogiCORE, IRL, Spartan, SpartanXL, Alliance Series, Foundation Series, CORE Generator, IP Internet Capture, IP Remote Interface, Multinx, QPRO, Select1/O, Select1/O, True Dual-Port, WebFITTER, WebPACK, ChipViewer, Select RAM, Black Ram, Xilinx Online, and all XCprefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx, Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

#### **Cover Story**

#### Page 8

#### Designing With FPGA Platforms - page 8

The Chief Technology Officer at Synopsys discusses the need for platform-based design in an era of system-on-a-chip FPGAs.

#### Perspective Page 14

#### Choosing the ARC User-Configurable Processor - page 14

ARC Cores and Xilinx provide everything you need to develop custom processor applications.

#### New Products Page 22

### New Xilinx Foundation Series ISE Software - page 22

Integrated design flows increase your productivity and accelerate your time to market.

#### New Products Page 30

### New High-Density and Cost-Effective PROMS - page 30

Xilinx announces the addition of the XC17V00 and XC17S00A families to its existing line of PROMS.

#### Page 48

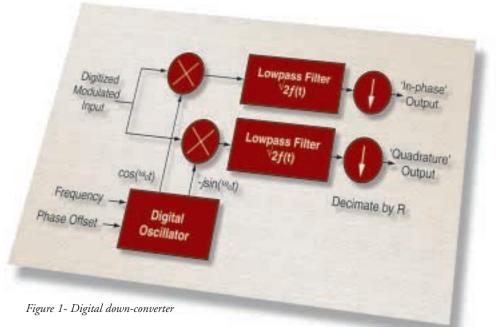

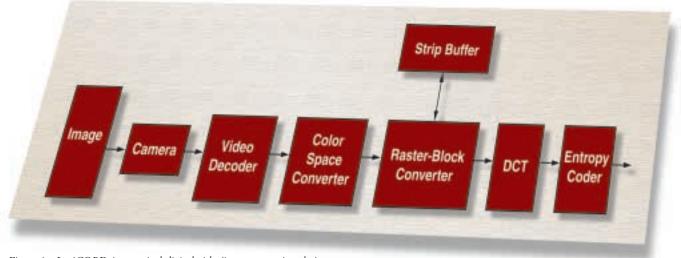

High-Performance Digital Down Converters for FPGAs - page 48

$\mathsf{Virtex}\ \mathsf{FPGAs}\ \mathsf{surpass}\ \mathsf{off}\ \mathsf{the}\ \mathsf{shelf}\ \mathsf{ASSPs}\ \mathsf{in}\ \mathsf{design}\ \mathsf{flexibility}\ \mathsf{and}\ \mathsf{system}\ \mathsf{integration}.$

#### New Products Page 54

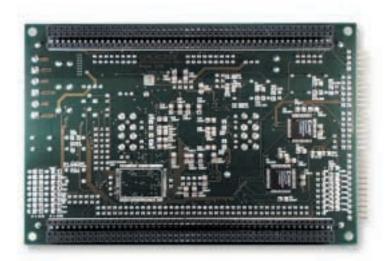

### Stackable Development Boards - page 54

A new series of prototyping boards to help you quickly test and implement your FPGA designs.

#### Contents Fall 2000 Platform FPGA-The Future of Logic Design ...... Designing with FPGA Platforms ......8 Inferring Multiplexers in FPGA Compliler II and FPGA Express ......11 Spartan-II PCI Development Kit Re-thinking Your Verification Strategies for Xilinx Foundation Series ISE Software-Delivering Guided Design Using BLIS ......28 New High-Density Virtex PROMS and Cost-Effective LogiCORE PCI Module Is a Key Element in Voice over Design a Low-Power SMBus System Using Implementing a Histogram for Image Processing Applications .....46 Stackable Development Boards for Spartan-II, Virtex, and Virtex-E FPGAs ......54 e-learning Makes the Grade ......58

### Xcelljournal

#### For a Free Subscription to the Xcell Journal E-mail your request to: literature@xilinx.com.

- Please include:

- 1. Your full name and mailing address.

- 2. Your job title.

- 3. Your e-mail address.

- 4. Your company name.

- 5. Is this a new subscription or a renewal?

# Platform FPGA-The Future of Logic Design

Xilinx and its partners are building the high-performance technology platform on which the designs of the future will emerge.

#### By: Wim Roelandts, CEO, Xilinx

The revolution in logic design continues, bringing dramatic performance improvements and new capabilities that help you create the systems of the future, and get them to market faster than ever before. FPGAs were once just interconnect routing and logic gates; then we added dedicated hard cores for memory, clock management, and I/O. Now, FPGAs are becoming the platform on which a combination of complex hard cores and flexible soft cores combine with an abundance of programmable logic gates to give you the best possible performance, along with the easeof-use and time-to-market advantages for which FPGAs are well known. Plus, we can bring you these advantages at a lower cost than ever before.

Xilinx has entered a number of strategic partnerships and has acquired key technologies for creating the new programmable logic platform. Here is an overview of our recent activities.

#### The IBM Partnership

Our recent partnership with IBM brings us two immediate and dramatic benefits: the power of the PowerPC<sup>™</sup> hard core, and the advanced CMOS manufacturing capability of IBM's state-of-the-art facilities. IBM gets intellectual property (IP) from Xilinx to help reduce defect densities and improve manufacturing productivity. This partnership has far-reaching implications, and gives both companies a significant competitive advantage.

#### The PowerPC Core

IBM's PowerPC module and CoreConnect<sup>™</sup> bus will soon be integrated into Virtex-II FPGAs. With this powerful combination, you can achieve performance that was never possible before, and you can quickly develop unique system-level applications with greater ease. We found that the PowerPC was the most-used processor in high-end designs; our communication and computing customers use the PowerPC because it has good performance, and it has a lot of peripherals and other functions that make it easy to use.

Processors like the PowerPC are often used as logic engines for low speed, very complex logic; they allow you to write detailed programs that perform intricate condition checking and control functions. However, because a processor basically executes one instruction at a time, it's slower than actual gates which can operate in parallel.

Now, in one Platform FPGA, you will have the best of both worlds; you have the dedicated PowerPC processor for complex control applications, and you have programmable logic gates for very-high-speed data paths. The big advantage of having this all on one chip is that you can very quickly move data from the PowerPC processor to on-chip peripherals or custom logic, which may be hard cores, soft cores, or unique designs created with programmable gates. This will give you much higher performance than you get using separate chips, which must pass signals through their slower I/O interfaces. We are implementing the PowerPC processor and other dedicated functions (such as memory, clock management, multipliers, and I/O interfaces) as hard cores, to give you the best possible performance. We will compliment these hard cores with over 50 soft core peripheral functions. By keeping most of the peripherals as soft cores, you can choose only those functions that you need, and create custom designs with ease.

#### Advanced CMOS Manufacturing Capability

IBM is one of the most advanced CMOS semiconductor companies in the world, with device manufacturing technologies that are typically a year ahead of most other companies. Our partnership with IBM gives Xilinx access to this manufacturing technology, and a tremendous competitive advantage. To be competitive in our marketplace we have to push manufacturing technology to the limits. By using the most advanced manufacturing processes, we can reduce the size and cost of transistors, which enables us to continue building bigger and bigger FPGAs and reduce the costs of existing devices.

For IBM, FPGAs are the ideal "process drivers" to test and refine their advanced manufacturing processes. Because FPGAs have very regular structures and they allow us to address almost every square micron of space on a chip, it makes them ideal for troubleshooting problem process areas. So, Xilinx gets advanced manufacturing technology and IBM gets devices that help them drive their manufacturing process to maturity. Thus, we can achieve better yields, faster, and that means lower costs.

Xilinx has been the leader in developing programmable logic technology, and we have expanded the market dramatically– today, the PLD business is growing 40% faster than the regular IC business. Our current technologies, bigger densities, higher speeds, and lower costs, are expanding the market much faster than in the past; with IBM, we are pushing it even further.

#### Gigabit Serial I/O Capability

Many new systems today are requiring much faster data transfer between systems, boards, and devices, due primarily to the ever increasing demand for faster networks. Very high speed (gigabit per second) serial I/O capability promises to solve this difficult problem.

Traditionally, data has been shared by using parallel busses such as PCI (Peripheral Component Interconnect). However, there are inherent limitations with shared busses. To increase the speed of a shared bus, you can either increase the speed of each wire (which is very difficult to do because there are many of them), or you can increase the number of wires (which takes more and more I/O pins). For example, PCI was once just 32 bits wide; now you also have 64-bit PCI-and that's not enough. The problem with this approach to increasing bandwidth is that at some point you reach a level of decreasing return; the extra pins and the need for shared bus protocols limits the performance and makes it prohibitively expensive.

The best solution we have for this bandwidth bottleneck is to use point-to-point connections, over a single pair of wires, operating at very high speeds. Currently, with this technology, you can achieve a data rate of two to three gigabits per second. The big advantage of this method is that you use less wires and less power, and the total amount of data you can move is in fact higher than with a typical parallel bus.

To create a gigabit serial I/O channel, a hard core is needed; you cannot achieve these speeds with soft cores in an FPGA. The hard core does several functions; it receives and transmits the data, and it also recovers the clock (because you can recover the clock from the data, a single pair of wires is all you need for data transfer). The hard core must also serialize and de-serialize the data. By de-serializing the data to a 16- or 32-bit internal bus, the data speed is then reduced by 16 or 32, which an FPGA can easily handle.

With gigabit serial I/O, all the de-serialization is done within the chip. When the work is done, you can serialize the data again and send it out to other devices, over a single pair of pins. This is a very efficient and low cost way to transfer data.

We recently made several announcements regarding our commitment to gigabit serial I/O.

#### The Conexant<sup>TM</sup> Partnership

Xilinx recently entered into a strategic development and licensing partnership with Conexant Systems, to integrate their SkyRail<sup>™</sup> 3.125 Gbps serial transceiver technology into our next generation Virtex-II FPGAs. This hard core is the fastest core available in CMOS today, and will be available in the second half of 2001 in a select offering of several different Virtex-II devices. In our Virtex-II architecture you will get more than 20 different I/O standards, plus several of these gigabit serial I/O channels.

The high-speed SkyRail transceiver is compliant with industry standards such as Gigabit Ethernet and Fibre Channel in addition to the emerging 10-Gigabit Ethernet (IEEE 802.3ae) standard. By integrating quad transceivers, which are used to create 10-gigabit attachment unit (XAUI) interfaces, a single FPGA can interface to both 10-Gigabit Ethernet and OC-192c. The high-speed transceiver is also compliant with the 2.5 Gbps InfiniBand<sup>TM</sup> architecture standard being the InfiniBand created by Trade Association.

#### The RocketChips Acquisition

High-speed serial I/O capability is so important, we decided not to stop at the 3.125 Gbps speed offered by the Conexant core–we are developing the technology further. That's why we recently acquired a company called RocketChips, which is very active in creating high speed serial I/O cores. RocketChips already has a product that is very similar to the Conexant core, and they plan to develop even higher speed cores operating at 5 to 10 Gbps.

RocketChips' gigabit and multi-gigabit serial CMOS transceiver technologies provide solutions for a wide range of serial system architectures in networking, telecommunications, and enterprise storage markets. Their products include serial backplane transceivers (Single and Quad 3.125 Gbps transceivers), telecom transceivers (SONET OC-48 and OC-192), enterprise storage transceivers (Fibre Channel, Ethernet), and nettransceivers working (Gigabit Ethernet, 10 Gbps Ethernet, and InfiniBand).

#### PMC-Sierra Partnership

Xilinx recently announced the availability of POS-PHY<sup>™</sup> Level 3 Link Layer and Physical Layer cores. These cores provide solutions for the emerging Packet Over SONET (POS-PHY) applications, and both cores are compatible with the POS-PHY Level 3 interface specified by the SATURN<sup>®</sup> Development Group. With these cores, broadband system designers can rapidly develop highly functional, scalable, and standards-based equipment to increase the speed of networks up to 2.5 Gbps, and support the exploding growth of IP traffic over SONET/SDH backbones.

Xilinx has also been active in the Optical Internetworking Forum (OIF) and the ATM Forum to drive POS-PHY Level 4 acceptance. And, we are the only FPGA company to demonstrate over 800 Mbps operation, confirming that we can provide the full speed capability to support the 10 Gbps OC-192 draft standard at the OIF (OIF2000.088.2).

#### Serial Protocol Standards

To use these high speed serial I/O channels effectively, you need well defined protocols and networking standards. Xilinx actively supports all of the emerging standards, including:

• Lightning Data Transport<sup>™</sup> (LDT) - A chip-to-chip interconnect that provides much greater bandwidth per I/O channel. It can achieve a bandwidth of 6.4

THE ROLE OF THE FPGA IS CHANGING; IT IS BECOMING A PLATFORM ON WHICH THE COMBINATION OF SOFT CORES, PROGRAMMABLE LOGIC, AND HARD CORES GIVES YOU THE BEST POSSIBLE DESIGN SOLUTION-THE SPEED OF A CUSTOM ASIC AND THE TIME-TO-MARKET ADVANTAGES OF A FLEXIBLE FPGA.

Gbps per eight-wire link width, and can support up to 32 links.

- InfiniBand<sup>™</sup> This newly designed interconnect system utilizes a 2.5 Gbps wire speed connection with one, four, or twelve wire link widths. Promoted by an association comprising industry leaders such as, Compaq, Dell, HP, IBM, Intel, Microsoft, and Sun Microsystems, InfiniBand intends to deliver a channel based, switched fabric technology.

- XAUI A quad transceiver utilizing 3.125 Gbps serial links to create a 10 gigabit attachment unit interface (XAUI). Multiple XAUI interfaces can be implemented to allow a single chip to interface to both 10 Gigabit Ethernet and OC-192c.

- Fibre Channel A high-bandwidth serial standard offering 1.06 Gbps data rates scalable to 2.12 or 4.24 Gbps. It is capable of carrying multiple existing interface command sets, including Internet Protocol (IP), SCSI, IPI, HIPPI-FP, and audio/video.

- Gigabit Ethernet + 10 Gbit Ethernet - This includes devices compliant with the IEEE 802.3 alliance.

- ATM (OC-12, OC-48, OC-192) -This includes support for OC-12 (622 Mbps), OC-48 (2.4 Gbps), and OC-192 (10 Gbps).

- RapidIO<sup>TM</sup> A next-generation switched-fabric interconnect architecture for embedded systems that is optimized for both high bandwidth and low latency. Initial implementations are expected to exceed 1.0 Gbps throughput based on clock rates of 250 MHz and higher.

These standards all use the same physical interface, so you can use our hard I/O cores for all of them. Then, we implement the level-2 protocols in programmable logic (soft cores), so you can quickly create designs using

any of these standards. This gives you a lot of flexibility and it helps you interface directly to on-site networks.

#### What Does It Mean?

An FPGA is no longer just gates and routing. Over the years we have added more and more hard cores, such as memory, clock management, and arithmetic functions. Now we are driving the technology a major step further by adding hard CPU cores and high speed serial I/O cores. Combine these dramatic technology advances with our high performance development tools, our unique Internet Reconfigurable Logic capability, our extensive training and support services, our state-of-the-art manufacturing capabilities, and our ongoing partnerships with other industry leaders, and you get a logic design solution that can breathe life into your new designs.

The role of the FPGA is changing; it is becoming a platform on which the combination of soft cores, programmable logic, and hard cores gives you the best possible design solution—the speed of a custom ASIC and the time-to-market advantages of a flexible FPGA.

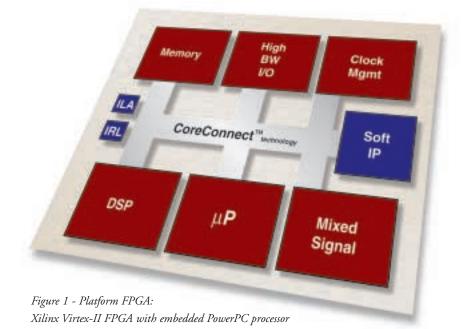

# Designing with FPGA Platforms

by Raul Camposano Chief Technology Officer, Synopsys, Inc. raul@synopsys.com

As FPGAs move into million-gate densities, a world of new possibilities and potential applications is opening up for programmable logic devices. And along with these new opportunities comes many new challenges. The pairing of a low-cost, high performance PowerPC processor (and other hard cores), along with the soft cores and programmable logic circuitry in Xilinx Virtex-II<sup>TM</sup> FPGAs means that you will now be confronting challenges similar to what ASIC designers encountered when they made the transition to system-on-achip (SoC) ASICs.

Everyone who participates in the multimillion-gate segment of the FPGA market is wrestling with the same issues: increased complexity, escalating development costs, evolving standards, too few design engineers, increasingly compressed design cycles, and so on. In addition, as complexity increases, the time it takes you to get a product to market becomes dominated more by your design time than by manufacturing considerations, compromising one of the key advantages of FPGAs.

To help address these challenges, there is increasing pressure for designs to share a common architecture or platform, especially those that are targeted to similar applications. A platform is a basic system architecture that is geared towards a specific application, such as cell phone base stations or set-top boxes, among others; it is customized through software and by adding customized logic and IP.

An FPGA platform enables you to differentiate your products by adding customized logic and IP using the tightly integrated FPGA fabric. Platforms are impor-

- Hardware design.

- Software design.

- Integration of hardware, software, and IP.

- Verification of the complete system (on a chip).

Synopsys delivers solutions in all four of these areas. The design of hardware has been our traditional domain, and we offer

tant in the era of multimillion-gate FPGAs because they enable you to focus on adding value through custom IP rather than wasting time and resources by recreating standard components.

#### **Platform-Based Design**

A central piece of any platform is the embedded processor, such as the IBM PowerPC processor core in the Xilinx Virtex-II platform. A typical platform might also include a bus, DSP, input/output channels, mixed signal functions, memory, and some configurable logic such as shown in Figure 1. FPGA design thus becomes platform design; rather than simply designing with gates, you must now focus on designing entire systems.

For you to effectively exploit a platform by designing at the system level, four primary design considerations must be addressed:

a suite of FPGA synthesis tools for this purpose. FPGA Express<sup>TM</sup> addresses the pushbutton, fast turn-around market, while FPGA Compiler II<sup>TM</sup> addresses more complex designs and compatibility with the ASIC design flow. Looking further into the future, other synthesis technologies such as Synopsys' Physical Synthesis will enable full timing closure for platform FPGAs.

#### **Open SystemC**

One of the most difficult aspects of software design involves how to interface software effectively with hardware. Open SystemC, a set of C++ class libraries that enables electronic design at the system level, provides an important tool for designing software and hardware in a common language framework. Based on C and C++ (the languages of choice for most algorithm developers, system architects, and software developers) SystemC also includes all the language elements necessary to effectively address hardware design. In this way, trade-offs between hardware and software can be addressed dynamically, even including reconfiguration in the field.

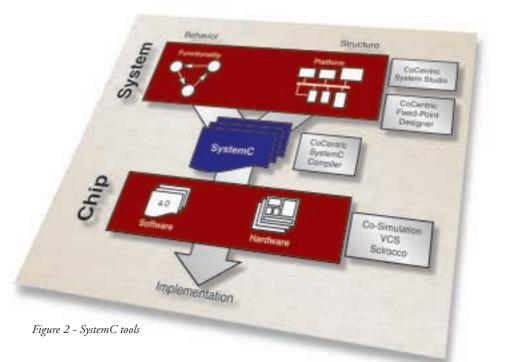

SystemC helps you create both systems and chips; the suite of tools and methodologies Synopsys has developed around SystemC significantly accelerate the design of elec-

Platform-based Design

tronic systems from concept to implementation (see Figure 2). SystemC follows the community source-licensing model and can be downloaded from the Open Initiative's SystemC website at www.SystemC.org/.

#### **IP** Integration

One of the advantages of platform-based design is that it supports the integration of other pieces of proprietary logic and thirdparty IP. In fact, it is the customized portion of any system-on-a-chip ASIC or platform FPGA that provides the competitive differentiation from one device to the next.

But with the very large number of gates that can now be implemented on a single FPGA, the challenge is to become significantly more productive when creating with these gates. One obvious solution is to leverage existing gates through design reuse. Synopsys has been leading the way in

this area and, with its DesignWare® libraries of reusable building blocks and methodology activities, offers several timesaving options for ASIC both and FPGA designers to leverage IP from a variety of

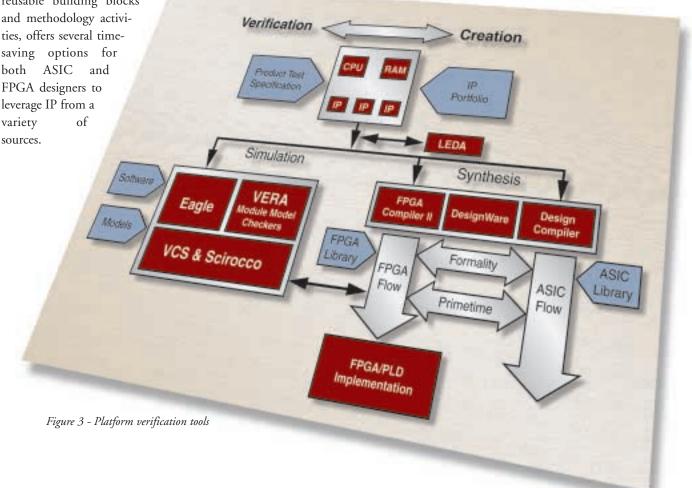

#### System Verification

The challenge for any system-on-a-chip FPGA is to verify the complete system, including the processor core, and not just the individual blocks that comprise the system. This requires not only a high-speed simulator, but also a complete array of advanced verification tools. In particular, testbench generation, coverage tools, formal verification, a simulation model of the processor and other IP, and static timing analysis tools are essential for platformbased design (see Figure 3).

Static timing analysis illustrates the verification challenges imposed by such a system. Synopsys' PrimeTime® static timing analysis tool can time and analyze a complete chip, offering the multimillion-gate capacity that is required by systems on a chip. It also offers analysis modes that handle the processor core in an effective way.

#### Conclusion

FPGAs that contain embedded processor cores and application-specific components are creating a need for platform-based design, which requires not only the suite of RTL logic design tools that are already in use today (with the right capacity), but also a comprehensive suite of system-level design tools that will be new to most FPGA designers.

FPGA design has moved beyond the era of simple logic. With the advent of FPGAs that contain an embedded processor core, such as the PowerPC, FPGA designers will soon join their peers in the ASIC world by confronting the challenges of designing entire systems. Synopsys is helping you meet these challenges through the power of its system-level EDA tools optimized for platform-based design.

For more information on all Synopsys products, see www.synopsys.com

## Inferring Multiplexers in FPGA Compiler II and FPGA Express

How to get better results by automatically inferring multiplexers that fully utilize architecture-specific FPGA resources.

by Alan Ma

Senior Corporate Applications Engineer, Synopsys, Inc. alanma@synopsys.com

In general, multiplexers can be implemented by using Look Up Tables (LUTs). To obtain the best quality of results (QoR), Synopsys FPGA Compiler II<sup>™</sup> and FPGA Express<sup>™</sup> (FCII/FE) take it one step further by utilizing the built-in multiplexer resources in high-density FPGAs, which produces significantly better results in both area and speed.

#### **The Process**

During elaboration, the process of translating the text-based description of a design to an architecture-independent gate-level representation, FCII/FE infers a generic primitive called MUX\_OP when it encounters multiplexers in the Hardware Description Language (HDL). It is during optimization where MUX\_OPs are mapped to architecturespecific multiplexer resources. The following sections describe the requirements for MUX\_OP to be inferred.

#### **General Implementation**

Our research indicates that using architecture-specific multiplexer resources is only beneficial when the number of inputs meets certain requirements. Table 1 illustrates the multiplexer sizes and the primitives FCII/FE utilizes for Xilinx Virtex-II, Virtex, and XC4000 FPGAs (and their derivatives). FCII/FE automatically maps to these hardware resources (primitives) when you follow the recommended coding guidelines.

#### **Coding Guidelines**

Synopsys recommends the use of CASE statements to describe multiplexer logic. When the requirements on the number of

inputs for the target architecture are met (as shown in Table 1), FCII/FE maps the design to architecture-specific multiplexer resources if at least 75% of all possible cases are specified.

Figure 1 shows an example of an eight-toone multiplexer in Verilog. Figure 2 illustrates its VHDL equivalent. Note that the control signal **sel** has three bits so there can be as many as eight possible cases. As a result, at least six (75% of eight) cases need to be specified for multiplexers to be inferred.

| Architecture | Min. Inputs | Max. Inputs | Primitives Used   |  |

|--------------|-------------|-------------|-------------------|--|

| Virtex-II    | 4           | 256         | LUT, MUXF5, MUXF6 |  |

| Virtex       | 4           | 256         | LUT, MUXF5, MUXF6 |  |

| XC4000       | 4           | 256         | FMAP, HMAP        |  |

Table 1 - Multiplexer size requirements for automatic inference

#### Using the infer\_mux Directive

Figure 3 shows a similar eight-to-one multiplexer with the addition of several arithmetic operators; Figure 4 shows its VHDL counterpart. To allow operator sharing, multiplexers are generally not automatically inferred for CASE statements which contain more than one operator (regardless of the number of cases specified). However, you have the option to override FCII/FE by using the infer\_mux directive.

The infer\_mux directive forces FCII/FE to infer multiplexers as long as at least 50% of all possible cases are specified. It can be used when:

- The requirements on the number of inputs (as shown in Table 1) are not met.

- The CASE statement contains more than one arithmetic operator.

It is important to understand that FCII/FE generally makes intelligent decisions on multiplexer inference based on the cost of doing so. For example, it may choose not to infer multiplexers, to allow operator sharing for better performance. As a result, QoR is likely to suffer if you override that decision by using infer\_mux. Please use this directive with caution.

#### Conclusion

FPGA Compiler II and FPGA Express take advantage of Xilinx-specific multiplexer resources to deliver the best quality of results. The tools automatically infer multiplexers if the design complies with the coding guidelines and meets the requirements for the target architecture. You also have the option to force multiplexer inference by using the infer\_mux directive.

Visit the Synopsys FPGA website at www.synopsys.com/fpga for other information on the latest FPGA synthesis technologies.

```

module mux_8to1 (

a, b, c, d, e, f, sel,

mux_out

);

input

a, b, c, d, e, f;

[2:0]

input

sel;

output

[1:0]

mux_out;

reg [1:0]

mux_out;

always @(sel or a or b or c or d or e or f)

case (sel)// synopsys infer_mux

3'b000 : mux_out = a + b;

3'b001 : mux out = a + c;

3'b010 : mux_out = d - e;

default : mux_out = d - f;

endcase

endmodule

Figure 1 - Using CASE statements for

multiplexers in Verilog

```

module mux\_8to1 ( a, b, c, d, e, f, sel, mux\_out ); input a, b, c, d, e, f; input [2:0] sel; output mux\_out;

```

reg mux_out;

```

always @(sel or a or b or c or d or e or f) case (sel) 3'b000 : mux\_out = a; 3'b001 : mux\_out = b; 3'b010 : mux\_out = c;

3'b011 : mux\_out = d; 3'b100 : mux\_out = e; default : mux\_out = f; endcase

endmodule

Figure 3 - Using infer\_mux for multiplexer inference in Verilog

library ieee; use ieee.std\_logic\_1164.all; entity mux\_8to1 is port ( a, b, c, d, e, f: in std\_logic; sel: in std\_logic\_vector(2 downto 0); mux\_out: out std\_logic ); end mux\_8to1; architecture rtl of mux\_8to1 is begin process (sel, a, b, c, d, e, f) begin case sel is when "000" => mux out <= a; when "001" = mux out  $\leq$  b: when "010"  $\Rightarrow$  mux out  $\leq$  c; => mux\_out <= d; when "011" when "100" => mux\_out <= e; when others => mux\_out <= f; end case; end process; end rtl; Figure 2 - Using CASE statements for multiplexers in VHDL library ieee; use ieee.std\_logic\_1164.all; entity mux\_8to1 is port ( a, b, c, d, e, f: in std logic; sel: in std\_logic\_vector(2 downto 0); mux\_out: out std\_logic\_vector(1 downto 0) ): end mux\_8to1; architecture rtl of mux\_8to1 is begin process (sel, a, b, c, d, e, f) begin case sel is -- synopsys infer\_mux when "000" => mux\_out <= a + b; when "001" => mux\_out <= a + c; when "010" => mux\_out <= d - e; when others => mux\_out <= d - f; end case: end process;

end rtl;

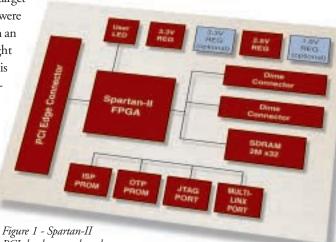

#### by Jim Beneke Technical Marketing Manager, Insight Electronics jim\_beneke@ins.memec.com

When Xilinx introduced the Spartan<sup>™</sup>-II FPGA family in January 2000, they not only offered the lowest cost FPGA devices with system-level features, they also enabled programmable logic to effectively replace off-theshelf ASSP devices for 32-bit PCI applications. Combined with the proven PCI32 LogiCORE<sup>™</sup> interface from Xilinx, the Spartan-II PCI solution was the commonsense choice for most PCI designs.

Unfortunately, designers wishing to target a Spartan-II device for a PCI project, were not able to prototype their design with an off-the-shelf PCI platform. Insight Electronics recognized the need for this type of development board, and introthe duced Spartan-II PCI Development Kit. The kit includes a Spartan-II prototype board, singleuse Spartan PCI32 LogiCORE license, Windows driver development software, one-day (eight hours) of Insight Design Services support, reference designs, Windows-based applications, example Windows 98/NT driv-

ers, source code, and hardware documentation. The demonstration board is based on the 150K-gate Spartan-II FPGA, in a 208pin plastic quad flat package (PQFP).

Implementing the full initiator/target PCI interface in the FPGA only consumes about ten percent of the logic resources, leaving approximately 135K gates for custom user back ends. Unlike other PCI prototype cards, the Spartan-II PCI board does not contain back-end application circuits to complicate your custom design. Instead, all user I/Os are brought out to expansion connectors for easy access and interfacing. This allows your designs to be quickly implemented, config-

## Spartan-II PCI Development Kit

Insight Electronics has introduced a Spartan-II PCI Development Kit to help you jumpstart your next 32-bit PCI design.

ured, and tested. Figure 1 shows a block diagram of the Spartan-II PCI card included in the kit.

#### The New Reference Design Center

In addition to the Spartan-II FPGA, the PCI board also includes the new Xilinx XC18V01 in-system programmable configuration PROM. This allows PCI application designs to be quickly downloaded multiple times to the board and saved in non-volatile memory.

PCI development board

With this re-configurable feature, Insight is including access to its new Reference Design Center. At the Reference Design Center, owners of the Spartan-II PCI kit can download pre-configured PCI application designs and run them on the demonstration board. Developed by Insight Design Services, these off-the-shelf application designs can be used as is, or can be customized to meet certain application needs. In addition to providing reference design bit streams and their associated source code files, the Reference Design Center also provides example Windows drivers and Windows-based application programs. Both drivers and application programs are provided with C++ source code so you can understand how the examples work.

To assist in the development and debugging of Windows device drivers, the Spartan-II PCI Kit includes Compuware's NuMega driver development software. The NuMega package simplifies the task of writing and configuring Windows drivers through a series of GUI windows.

#### The Xilinx Spartan 32/33 PCI Core

The Insight Spartan-II PCI Development Kit includes the new single-use version

of the Xilinx Spartan-only 32bit, 33 MHz PCI core. The single-use license allows the kit owner to support a single production PCI core implementation. If multiple PCI core solutions are required, then the core license can be upgraded to an unlimited license for a nominal fee. The 32bit Spartan PCI core is configured and downloaded through the Xilinx PCI Lounge. The downloadable core netlist is fully PCI v2.2 compliant and supports initiator and target functions with zero-waitstate burst operation.

#### Conclusion

By providing exactly what is needed to complete a PCI design, the Spartan-II PCI Kit meets the demands of both experienced and new designers of programmable logic-based PCI interfaces. Several versions of the Spartan-II PCI Development Kit are available from Insight Electronics. Prices range from \$145 for a PCI card only kit, to \$3,995 for the complete Spartan-II PCI Development Kit. For more information, go to www.insightelectronics.com/ solutions/kits/xilinx/spartan-iipci.html.

# Choosing the ARC User-Configurable Processor

ARC Cores and Xilinx provide everything you need to develop custom processor applications. by Emmanuel Benzaquen Third Party Program Manager, ARC Cores eben@arccores.com

As FPGA capacity continues to increase, especially with the new Xilinx Virtex product family, it is becoming increasingly practical to implement complete systems in a single FPGA. A soft processor core represents an attractive solution for user-configurable System-on-Chip (Soc) applications.

Hardware

Design

ynthesis

loois

Route

ools

inplement IDL/Verilo

- An ARC design can be turned from VHDL or Verilog into a configuration that runs on the Xilinx FPGA-based ARCangel prototype board in a few hours

- Both software and hardware can be tested and benchmarked at the same time

The ARC soft processor design and debug cycle

#### Processor Cores Complement Programmable Logic

Traditionally, an important motivation for adding microprocessors into a design has been that software programmable solutions are easy to change and upgrade. Since FPGAs are, by definition, programmable, you can always upgrade them. System designers know that it is much easier to design and implement certain parts of a system using software, while hardware implementations offer greater performance. For example, you may want to take advantage of a large amount of low-cost software intellectual property (IP) that is available in C or C++ code, for functions such as protocol stacks and modem algorithms. You may also want to implement high-speed co-processor functions in hardware. You can get the best of both worlds when you combine the hardware re-programmability of FPGAs with the software programmability of microprocessors.

#### The Hard Versus Soft Option

Software

Test Debug and Profile MetaWare, ARCangel

Modify

Design

Major FPGA vendors typically provide two different approaches to including processor cores in an FPGA. One approach offers a soft processor core that is provided in a synthesizable HDL format. This processor core is then included in a generic FPGA using the same design process as the rest of the logic. The second approach embeds a specific hard processor core (such as the PowerPC) into the FPGA. The most appropriate choice will depend on the application.

As a general rule, a hard processor core will offer higher clock speeds than a soft core. However, since the hard processor solution will require a specialized FPGA with dedicated processor buses and routing, it will be less flexible than incorporating a soft processor in a generic FPGA. In addition to performance and flexibility trade offs, the choice between a hard or a soft processor will also be influenced by the software applications you wish to run.

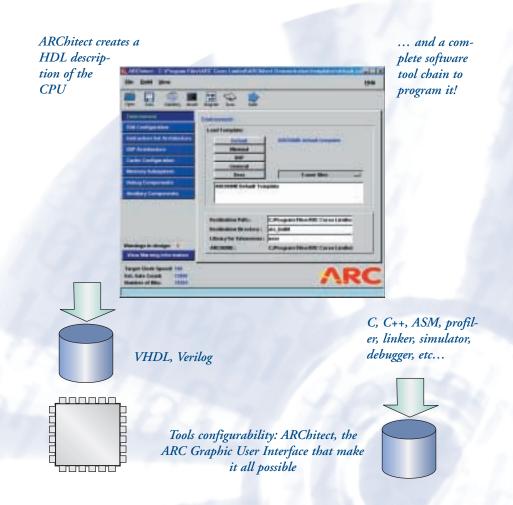

Since soft processors are available as synthesizable HDL, they inherently provide more design flexibility than hard processors because you can modify the core interface to fit better into a specific design. Some soft processors provide even greater flexibility by being configurable. A configurable processor core may include a graphical tool that enables certain functions to be included or excluded without having to manually modify HDL source code. As a result, you can create a processor core that is customized for your specific application by using the GUI.

The ARC processor is a perfect example of a soft and user-configurable core available for immediate use in Xilinx FPGAs.

#### Software Tools

The most important factor that will influence your choice of a soft processor is the software tool set that supports the code that will run on it. SoC designs can have lines of software code running anywhere from 1Kbyte to multi-megabytes. For applications that have only a few Kbytes of code, basic software tools such as an assembler may be sufficient. However once the amount of code starts increasing and becoming more complex, it becomes essential to use a high-level language like C or C++.

ARC Cores provide a complete set of high-level development tools customized for embedded applications, and offers both DSP (Digital Signal Processing) and general purpose control functions within the same processor architecture. There is no need to learn two different processor architectures and development tool environments.

#### **Integrated Software Environment**

Because of the typical complexity of the software code, ARC offers the Metaware development environment. This professional set of software development tools includes a C/C++ compiler, assembler/linker, and the SeeCode<sup>TM</sup> source-level debug-

ger. Most importantly, it offers you the ability to debug the embedded software running on the processor in the FPGA. It is critical that the core and its host interface include execution control capabilities like breakpoint checking so you can break the program execution or monitor reads and writes to program variables.

As the software content of a design increases, another important factor is the range of applications supported and the available systems software. For example, if a design requires several hundred Kbytes of

code along with standard communications software, such as TCP/IP protocols, you can save several months or more of design time by purchasing a real-time operating system (RTOS) that includes prepackaged protocols. ARC supports a large variety of commercially distributed RTOS from leading vendors and is constantly increasing their ease of integration.

In addition to the software tools and applications described above, another critical factor in choosing the ARC core is its level of flexibility. Unlike other configurable processors available today, which sometimes require you to manually "hack" the HDL code, the ARC processor core enables you to easily select special options for configuring the processor. Hacking the HDL code after configuring the processor core might break the core, or even make it incompatible with the software development tools. ARC provides the flexible ARChitect Graphic User Interface (GUI) that can be used to safely create your custom configured processor. This is very helpful when using a soft processor in an FPGA, and it allows you to experiment with different options and configurations within minutes.

Cores/IP

Generation

Processor IP

vides high performance at lower clock speeds, while still maintaining a software programmable solution.

Instruction extensions are available from ARC and some third parties. Plug-ins can be used and implemented directly in the design. For additional capability, you can

Logic

Analog

- The ARC IP is deeply embedded with the rest of the logic and interface directly with other customer logic function in the Xilinx FPGA

- "Gate-hungry" complex system buses and associated logic are no longer needed to reach high-performance because of the tight integration

"ARC, Third Generation IP"

Memory

1/Os

#### **Instruction Set Flexibility**

The instruction set is one of the most important aspects to consider when choosing a configurable processor. One potential disadvantage of soft processors is that they cannot attain the high clock speeds of a hard processor. For a conventional processor design, the clock speed is essentially the key determinant of performance. The ARC processor changes this equation by offering a configurable instruction set and the ability to add custom instructions. This enables you to accelerate an algorithm by selecting or adding a few appropriate (but powerful) instructions specifically needed for the application that is being executed. Thus, you can get the best of both RISC (Reduced Instruction Set Computer) and (Complex CISC Instruction Set Computer) processor design architectures. This approach proalso create your own specific instructions. Custom instruction extensions offer you a particularly powerful way to accelerate application performance while retaining programmability. Consider the example of a DES (Digital Encryption Standard) encryption application: by adding specialist bit-permutation, cipher instructions and additional registers to hold the keys, it is possible to greatly accelerate a range of encryption algorithms.

To provide a truly configurable instruction set, it is also important that the number of clock cycles for an instruction extension is configurable. For example, the ARC processor enables the addition of multicycle instructions to the pipeline where desired, and single-cycle operations to proceed in parallel with long latency ones. This is an advantage over architectures that enforce a strict RISC paradigm where every instruction must execute in a single cycle. Such restrictions may make it impossible to add very powerful, complex instructions that require multiple cycles to execute.

#### Interaction with Other Logic Functions

The ARC processor can further improve performance by enabling tight integration between the processor core and other logic on the FPGA. Traditional processor cores typically communicate with peripheral hardware via a system bus. To send data to the processor, the peripheral interrupts the processor, which then processes the interrupt using a software routine known as an ISR (Interrupt Service Routine). In addition to supporting this approach, ARC processor enables you to add new core extension registers. If desired, the new registers can be directly accessed by peripheral logic, enabling such devices to communicate with the processor directly. These alternative approaches can improve performance and reduce gate count by eliminating the need to duplicate a complex system bus and its arbitration logic in an FPGA.

It is no longer necessary to pass data via a bus or to interrupt the processor to have it load data from a memory-mapped register. Since the special registers are unique to a particular piece of peripheral logic, there is no need for any decoding or arbitration logic. The firmware simply selects the special purpose registers to communicate with the peripheral.

In addition to providing extension registers, configurable processors like the ARC core can also simplify integration with additional logic by providing multiple buses. This approach enables operations residing on separate buses, such as instruction fetches, load/stores, and communication with peripheral logic. As a result, the bus protocols of each bus can be relatively simple since there is no need to arbitrate between multiple devices attempting to control one bus. The ARC processor has four buses, consisting of instruction and data buses (Harvard architecture), a bus directly into the processor registers (primarily used for debugging), and an auxiliary bus (typically used to connect peripheral logic). The auxiliary bus has a very simple interface that virtually enables peripherals to be connected with just a few wires. This is well suited to FPGAs where there is no actual bus, allowing peripherals to be efficiently connected in a point-to-point manner.

#### **Tool Configurability**

Any processor that offers a high degree of configurability must also offer equally configurable software tools and a debugging environment that work in coordination. It is of no use to add new instructions to the processor if there is no way of telling the compiler and assembler about them so that actual software programs can take advantage of them. In a similar vein, the compiler must let you specify which instructions will be present in the processor, as well as be able to take advantage of features such as multipliers or barrel shifters when they are included. In fact, software tool configurability is one of the greatest challenge in providing a truly configurable processor solution.

ARC and Xilinx are responding to this challenge by offering a complete "plug and play" solution to FPGA designers. In addition, the ARC tools suite allows you to enhance the original configurations offered in a simple manner.

#### Conclusion

Soft processor cores give you the ability to include processors in standard FPGAs. Configurable cores can help you achieve higher performance at lower clock rates through instruction extension and peripheral logic integration. ARC and Xilinx offer the perfect combination of a configurable core with powerful extensions and third party "plug-ins," in addition to a complete development environment and operating system support, ready to use with Xilinx FPGA technology.

## Re-thinking Your Verification Strategies for Multimillion-gate FPGAs.

How do you alter your verification techniques to meet today's high gate count requirements? It depends on your background and experience.

by Thomas D. Tessier President, t2design Incorporated tomt@hdl-design.com

FPGA verification is essential for successful on-time product delivery, and today's million-gate FPGAs require you to rethink your old verification strategies. Many engineers continue to use simulator-specific approaches for verification; the simulation tools are primarily used for module testing, while the lab is used for system-level integration. This approach requires the engineer to manually stimulate signals and view the resulting waveform responses. Because this process is time consuming, error prone, and difficult to repeat, engineers often spend minimal time in simulation and quickly move to debugging in the lab. Multimilliongate FPGAs implement functions far too complex to rely on this ad-hoc method.

Designers are choosing million-gate FPGAs because they are fast enough and

large enough to handle the design complexity that was previously achievable only with an ASIC. When ASIC engineers begin to use high density FPGAs, they take their verification approaches with them. Those who use a validation process with robust tools and a complete selfchecking testbench environment find that continuing to use their familiar testing approaches now causes them to loose valuable design cycle time. ASIC Designers can benefit from a carefully defined and executed verification plan that takes FPGA reprogramability into consideration. Time that was once well spent in exhaustive verification at the RTL level with an ASIC, now becomes costly for a high density FPGA.

#### What is Verification?

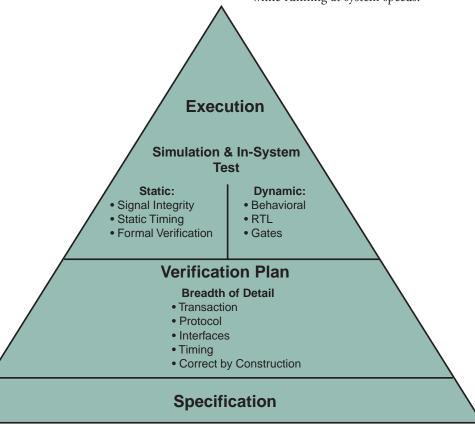

Verification is not synonymous with simulation. It is a strategy to make sure all parts of the system conform to the specification document; simulation is a tool used in the verification effort. The basic components of verification are shown in Figure 1.

#### Specification

A detailed and complete specification is essential for producing working products, on schedule. The specification document is the foundation of the verification plan, and describes the features to be implemented, under what conditions they occur, and what their expected outputs should be. This documentation should not determine implementation—that is left to the experience of the RTL designers.

#### Verification Plan

RTL engineers and verification engineers share the responsibility for implementing the test plan. The level of test granularity (or detail) is outlined at: transactions, protocol, interfaces and timing. Essential functions are identified. A determination of the number of testbenches needed, their complexity, and test module dependencies is made.

Any discrepancies in design implementation versus testbench results should be referred back to the specification for clarification. This is not a new concept but often overlooked in the rush to produce a product. When all elements described within the test plan are checked off, the verification effort has been completed to the required level of confidence. To optimize your verification effort the following list offers examples of the type of information you need to identify:

- External interfaces

- Stimulus and response

- Transaction level, such as Read vs. Write operations

- Timing requirements

- HDL models available to assist in testbench development

- Packaged with proposed Intellectual Property (IP)

- Tools available to the project

- Simulators

- Static Analysis

- Lab-based tools

- Performance Requirements, such as: need 32 block data write @ 66 MHz with a latency of less than 300 ns.

#### Execution

A verification strategy that best suits your design means breaking out those func-

tions that are essential to simulate and those that can be tested during in-system test. The execution of the Verification Plan requires simulation and in-system test on the target PC board-the final stages of the pyramid.

#### Verification Simulation

Simulation has two components:

- Dynamic simulation describes behavioral HDL, RTL, and gates.

- Static analysis encompasses Static Timing Analysis (STA), Formal Verification and Signal Integrity Analysis.

#### In-System Test

During in-system test you have a distinct advantage when using FPGAs over ASICs. An obvious benefit is the ability to reprogram the FPGA until the desired functionality is achieved. You also have an additional advantage with the Xilinx ChipScope Integrated Logic Analyzer which enables you to observe internal nodes of the chip, on your PC board, while running at system speeds.

Figure 1 - Verification pyramid

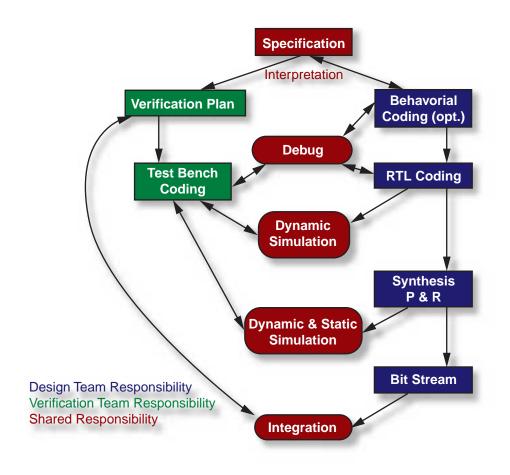

#### Interaction of Verification and Design Creation

Verification has many interactions with design creation, as shown in Figure 2. To prevent confusion and save time, the design and verification teams must work from the same thorough specification. In addition, the RTL design engineers and verification engineers must share the responsibility for implementing the test plan-testbenches are written to validate the design to the specification, not to verify the design implementation.

Once the executable specification (of the design) and testbench, both written in behavioral HDL, meet the requirements, the design is replaced with RTL code. The RTL is then verified with the system-level testbenches to make sure it meets the written specification conditions. After the RTL is validated it is synthesized and processed by the Place and Route tools. The resulting gates are plugged into the system verification testbenches or formal verification if it is available. This insures the tools have correctly implemented the design. In addition generated gates are run thorough static timing analysis. This step verifies that the system-level timing is met.

System integration is typically referred to as "power on". This is the time when project teams come up with creative answers to the question "is it working yet?" Projects are ready for in-system test when they have validated RTL code, have been successfully placed and routed, and can create a bit stream to program the FPGA on the physical PCB. At this point it is expected that module-level partitions have been tested for functionality, and that module interfaces are stable and well defined. The design has been simulated, as a chip, at both RTL and gates levels with minimum functionality necessary for power on. The simulation of the chip is often not achieved by FPGA design teams still using simulator specific approaches.

Figure 2 - Interaction of the verification components

#### Conclusion

A verification strategy combining simulation, static analysis, and in-system testing is key to success with high density FPGAs. You are bombarded with many different choices for verification of a design; to meet time-to-market pressures you need to leverage multiple approaches.

A detailed application note is available to guide you through the verification decision process, including an in-depth case study. It evaluates the design-specific trade-offs of choosing functions that are essential to simulate and those that can be tested during integration. Prepackaged IP testbenches are also evaluated for applicability in the system testbench. The full application note can be found at: www.hdl-design.com.

#### About t2design

t2design, Inc. provides HDL design and methodology process management solutions. We specialize in customizing project methodologies that create a cohesive, re-creatable design process from the architecture phase through verification. High density FPGAs, such as the Xilinx Virtex and Virtex-II families, require an "ASIC like" HDL design approach which means HDL code, simulation, and synthesis. Data flow and process management planning need to accompany the HDL design approach to create a complete project solution. Our team of designers implement this ASIC and FPGA methodology strategy while leveraging EDA tools to their fullest level of effectiveness. Contact us at 303-665-6402 regarding t2design services.

## Foundation ISE – What's In a Name?

#### Xilinx Integrated Synthesis Environment stirs Design Automation Conference debate.

by Craig N. Willert Software Marketing Manager, Xilinx cnw@xilinx.com

The new 3.1i Foundation<sup>TM</sup> ISE software from Xilinx made its debut at this year's Design Automation Conference (DAC), leaving many with the question "What should ISE stand for?" Xilinx thought the name would speak for itself–Foundation ISE is an Integrated Synthesis Environment. But designers viewing the product for the first time at the DAC show excitedly came up with other ideas of what "ISE" should mean.

- "I" is for Ingenious, Intelligent, Internet-Enabled, Incremental, Innovative, Intriguing, Inspiring, Inventive, Imaginative, Insightful, Intuitive, and Interoperable.

- "S" is for Simple, Speedy, Sensible, State-of-the-art, Smart, Savvy, and Sexy.

- "E" is for Engineered, Easy, Efficient, Empowering (EDA partners), Expedient, Easy-to-Use, Extra-Special, Essential, and Eloquent.

#### What is ISE?

To understand the basis for the differing opinions, it's necessary to look at the current state of the design process.

Integrated design, synthesis, and implementation tools automatically handle all of the file dependency issues that any designer faces, by answering questions like "What tool do I need to run next," and "Have I resynthesized all of the modified HDL blocks?" But time and time again, designers are synthesizing their designs with two or more synthesis tools-trying to create the most optimal design implementation from all of the variables.

To simplify this approach, Xilinx has builtin the HDL optimization using Xilinx Synthesis Technology and the FPGA Express HDL synthesis tools from Synopsis. This ensures that every engineer using Xilinx Foundation ISE will have access to at least two HDL synthesis tools that are highly compatible and tightly integrated.

Furthermore, a design "environment" is distinguished by its ability to address all of your needs as a designer, not just a few specific design functions. Foundation ISE provides an environment that ensures a comprehensive, integrated design flow for any programmable logic designer looking for an integrated solution that is capable of delivering world-class results with push-button flows.

#### Conclusion

The Xilinx 3.1i Foundation ISE software is already being heralded as the industry's best programmable logic design tool. By integrating the HDL design flow, synthesis, and optimization, Xilinx Foundation ISE enables you to spend more time on the creative aspects of programmable logic design. This helps you focus your resources and increase your productivity so you can get to market faster and deliver a more robust product to your customers. Xilinx 3.1i development systems deliver superior push-button, interactive, state-of-the-art design methods.

The 3.1i release will begin shipping to all registered, in-maintenance customers this Spring. To learn more, please visit the Xilinx website at: www.xilinx.com.

#### Year 2000 Worldwide Xilinx Event Schedules

Year 2000 European Event Schedule

Dec 5 Embedded Computing/Real Time

Show Tel Aviv, Isreal

#### Year 2001 Worldwide Xilinx Event Schedules

| Year 2001 No   | orth American Event Schedule                          |

|----------------|-------------------------------------------------------|

| Jan 30-31      | Portable Design 2001<br>Santa Clara, CA               |

| Feb 2001       | FPGA Conference 2001<br>Monterey, CA                  |

| Feb 13-15      | Wireless Symposium 2001<br>San Jose, CA               |

| March 5-7      | Synopsys User's Group 2001<br>San Jose, CA            |

| April 9-13     | Embedded Systems Conference 2001<br>San Francisco, CA |

| April 23-26    | NAB 2001<br>Las Vegas, NV                             |

| April 30-May 2 | FCCM 2001<br>Rohnert Park, CA                         |

| May 8-10       | ICASSP 2001<br>Salt Lake City, UT                     |

| May 15-16      | Applied Computing Conference 2001<br>Santa Clara, CA  |

| June 18-20     | 38th Design Automation Conference<br>Las Vegas, NV    |

| June 20-22     | WITI Technology Summit 2001<br>Santa Clara, CA        |

| June 24-27     | ASEE Conference and Expo 2001<br>Albuquerque, NM      |

#### Year 2001 South East Asian Event Schedule

| March 26-27 | IIC 2001<br>Shanghai, China |

|-------------|-----------------------------|

| March 29-30 | IIC 2001<br>Beijing, China  |

| April 2-3   | IIC 2001<br>Shenzhen, China |

#### Year 2001 Japanese Event Schedule

Feb 1-2 Electronic Design and Solution Fair Tokyo, Japan

For more information about Xilinx Worldwide Events, please contact one of the following Xilinx team members or see our website at: http://www.xilinx.com/company/events.htm

North American Shows: Darby Mason-Merchant at: darby@xilinx.com

or Jennifer Waibel at: jenn@xilinx.com

• European Shows: Andrea Fionda at: andrea.fionda@xilinx.com or Andrew Stock at: andrew.stock@xilinx.com

• Japanese Shows: Yumi Homura at: yumi.homura@xilinx.com

• SouthEast Asian Shows: Mary Leung at: mary.leung@xilinx.com

## Xilinx Foundation Series ISE Software-Delivering the Benefits of HDL Design

Integrated design flows increase your productivity and accelerate your time to market.

by Justine Chen Product Marketing Manager, Worldwide Software Marketing, Xilinx justine.chen@xilinx.com

Karen Fidelak Product Marketing Manager, Design Software Division,Xilinx karen.fidelak@xilinx.com

Teams of software engineers from Synopsys, Synplicity, Model Technology, Visual Software Solutions, and Xilinx, working in close collaboration, have created the ultimate design automation tools-Xilinx in Foundation Series<sup>TM</sup> ISE (Integrated Synthesis Environment). The Foundation Series ISE software gives you the most advanced design automation tools, in a fully integrated, fast-working environment that increases your productivity and accelerates your time to market.

The Foundation Series ISE software includes:

- Synopsys FPGA Express HDL synthesis software.

- Synplicity Synplify HDL synthesis software.

- Model Technology ModelSim HDL simulator.

- Visual Software Solutions HDL Bencher -Automatic testbench generation tools.

- Visual Software Solutions StateCAD-Automatic State machine generation tools.

- Xilinx XST synthesis technology For further optimization.

- Xilinx implementation tools For optimum use of device resources and the fastest place and route times in the industry.

#### The Keys to Increased Productivity

In the past, most large digital design companies relied on individual point tools, and were less concerned with managing the flow of data between the tools. Solving the problem of connecting point tools came later, and required customized design flows. This need to connect data flows between various point tools led to development of standard information exchange interfaces, such as HDL. But HDLs, including Verilog and VHDL, though useful as industry standards for hardware design, did not deliver a complete solution. For example, various simulation and synthesis tools might interpret and optimize differently, and produce undesirable results.

Today, there's a new focus. As more and more competing companies address the problem of designing a "system on a chip," they see more value in integrated tools that work together seamlessly, than in individual point tools, because tool integration is the key to increased productivity.

#### Integrated Design Flow Management

Today, you need fast, reliable flows of design information between tools. And, you want to specify common information, just once, for multiple tools; this includes the location of simulation libraries, macro libraries, and timing information. Though a homegrown, customized process for specification of common information can often be automated, updating a single point tool within a flow usually calls for a complete rewrite of setup information. And using various point tools within a design flow often requires creation of additional design data files. That additional design work and processing decreases your productivity, and slows time to market.

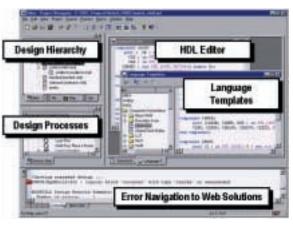

The Foundation Series ISE software automatically communicates common information to each tool and eliminates the need to create data file overhead. Unlike homegrown flow automation, an integrated design tool suite is aware of downstream tool requirements. For example, when you want to perform timing simulation after place and route, an integrated tool suite can instruct its place and route tools to produce the timing simulation netlist, so it can be read by the simulator. Today, winners in the race to market are focusing on design automation tools that are integrated (see Figure 1).

#### Integrated Project Management

Given the large number of source files, control files, and implementation files generated by today's complex, time-pressed design projects, it is not merely desirable, but necessary, to have an automated, integrated software tool that can manage project files. For example, a design project may consist of HDL files, IP cores, netlists, user constraints, or any combination of these. You know it can be difficult to manage the project when one, or more of these design modules are modified.

The Foundation Series ISE software will manage all modules in the design for you. For example, it knows about all of the HDL code in your design, and it knows when the

code has changed; therefore it will know, and can tell you, when HDL-generated netlists must be updated, and processes re-run. Then it will clearly display all design sources and implementation results, and provide easy access to the appropriate editing tool for every source file.

Many HDL compilers, as well as schematic entry tools, require that you specify a device family library up front, to provide appropriate library symbols and components for a given architecture. Additionally, if your design is retar-

geted to a new device architecture in the middle of your design project, then you must change the project libraries to match the new architecture. The Foundation Series ISE software makes the changes for you. You're left

with nothing to do but select the device family, once. Your selection will set the appropriate device libraries for design entry. And automatically pass device information forward to place and route tools.

In the course of a design cycle, it's highly likely a design will be implemented many times. For example, revisions may be made to timing constraints, target device, and place and route options, in pursuit of the best overall design implementa-

tion. The Foundation Series ISE software provides revision control by archiving each implementation, along with all design flow control files and design constraint files, for future reference or use. With this information, you can consult or deploy an archived implementation anytime, without recompiling your entire design (see Figure 2).

#### Integrated Environment for Design Optimization

You usually have some overall design strategy that you are looking to optimize in your design flow. For example, your strategy may place highest priority on fitting the design in

Figure 1 - Foundation Series ISE –well-integrated HDL solution

the smallest possible device, or on getting the fastest performance. A synthesis tool can be used to optimize the design's performance based on timing requirements, but for the best results, the place and route tools

> must then receive the same information to complete the design. This can mean setting requirements twice. However,

Figure 2 - Foundation Series ISE project snapshots for effective project management

> with the Foundation Series ISE software, you only have to define the settings once, so you can optimize your design strategy faster and more reliably.

> The Foundation Series ISE software ensures that the software tools work well together; the tools must communicate with each other

to efficiently transfer design data automatically. What's more, front to back design flow strategies are used, enabling the individual tool's features to be leveraged to their greatest benefits. In a non-integrated environment these communications tasks and decisions are left to you.

#### Integrated Environment for Collaboration

To facilitate the efficient flow of design data constraints and strategies, it is far more efficient if teams of software developers work in collaboration. An integrated environment makes possible, and enhances, collaborative work, which is critical during the project development phase. However, collaboration presents a new challenge.

Designers, working with an integrated tool, in an integrated environment, depend on software quality. When your in-house designers collaborate with third party partners for example, and use different tools, interoperability problems may occur; you can only hope solutions are available from each tool's vendor.

When you use the Foundation Series ISE software, you are assured of software quality because it has been tested thoroughly for tool interoperability, across the project creation lifecycle.

#### Conclusion

Foundation Series ISE provides you with a com-

plete HDL design environment. Now you can manage and optimize your design p

mize your design projects, and your engineers can work collaboratively, with confidence in Xilinx quality and technical support.

Learn more about how Xilinx Foundation Series ISE meets your requirements for integrated design automation. See and hear the Xilinx internet presentation, "Xilinx Foundation Series ISE: Delivering the Benefits of HDL Design to Programmable Logic Designers," by going to www.netseminar.com/tbd/tbd. Software

## StateCAD XE for Optimizing State Machine Design

Now you can implement faster, more compact state machines, with ease.

by Andy Bloom Director of Engineering, Visual Software Solutions (info@statecad.com) ambloom@testbench.com

Ricky Escoto Director of Marketing, Visual Software Solutions (info@statecad.com) rescoto@testbench.com

Control logic is usually implemented as finite state machines (FSMs), which usually require you to work through multiple levels of design and optimization, often within tight development schedules. And, as designs grow larger, the complexity of implementing control logic increases correspondingly, forcing you to migrate from schematics to hardware description languages (HDLs). StateCAD® XE automates the state machine development process, saving you a lot of time and trouble.

#### **Manual FSM Design**

Until recently, you had to specify control logic manually; you had to draw state diagrams by hand (or with a graphics package), and then manually translate them to schematics or to an HDL. Timing and logic problems identified during simulation resulted in modifications to the original design, which then needed to be reverified, step-by-step.

This approach tends to be slow, repetitive, and error-prone. Translation errors invariably creep in and require substantial effort to eliminate.

Hardware Description Languages (HDLs) allow more logic to be specified and maintained with less effort, and they can be synthesized in numerous ways. You can control how synthesis operates, allowing you to create your design in the manner best suited to your target application.

The way an HDL is structured dramatically impacts the speed, area, and power consumption of the synthesized device. When doing finite state machine design, the best results can only be achieved by careful consideration of the resources available, and by having the flexibility to experiment with different alternatives.

#### Automated FSM Design Using StateCAD XE

A quicker way to implement state machines optimized for Xilinx devices is to use the Xilinx ISE software, which includes StateCAD XE. This tool allows you to draw complex state diagrams, choose design specific optimizations, and generate synthesizable VHDL, Verilog, or Abel-HDL. StateCAD allows you to change optimizations (including state assignment mode, registering output, and signal loading), then reproduce the HDL automatically.

One advantage of automatic state machine translation is the ability to change optimizations and regenerate code in seconds. By trying different code styles, state assignment modes, and optimizations, you can find which combination yields the optimal solution for your design.

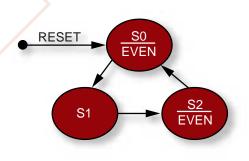

#### State Machine Example

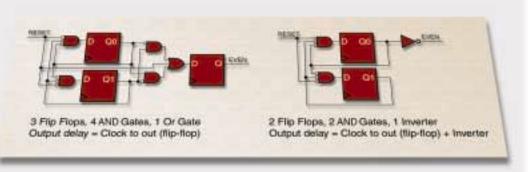

By comparing implementations of a simple state machine, we can see the impact on state machine design. The small state machine in Figure 1 will be implemented with both registered and combinatorial outputs, illustrating the impact of output optimization on implementation:

Figure 1 - Example state machine

#### **Output Optimization**

Outputs can be optimized for speed (registered) or for area (combinatorial decode). Combinatorial decoded outputs become active by decoding state registers (Moore) or by decoding state registers and inputs (Mealy). Registered outputs are calculated prior to the active edge of the clock, and typically improve speed because a level of propagation delay is removed, but usually require more area than combinatorial implementations. Registered outputs are insensitive to input glitches or to multiple state bit changes.

#### **Design Results**

In Table 1 you can see the registered design has outputs that change at the same time as the state bits, and are stable between clocks. The output delay time is the clock to output delay of the register. All decoding necessary for the output occurs before the clock, at the same time as the

decoding for the next state. The decode time is effectively "buried" in the state decode time, producing a faster design.

In comparison, the combinatorial design requires time to decode the state bits, yielding a slower implementation. The advantage for the combinatorial design is the smaller area: 5 logic elements compared to 8 for the registered design.

#### Additional StateCAD Benefits

StateCAD provides additional benefits to Xilinx customers:

- By automating the complete state machine development process, the Xilinx ISE software and StateCAD eliminate manual coding, translation errors, stale documentation, and logic bugs.

- StateCAD includes wizards tailored for designing concurrent state machines

#### REGISTERED OUTPUTS

PROCESS (sreg, RESET) BEGIN next\_EVEN <= '0'; next\_sreg<=S0; IF ( RESET='1' ) THEN next\_sreg<=S0; next\_EVEN<='1'; ELSE CASE sreg IS WHEN S0 => next\_sreg<=S1; WHEN S1 => next\_sreg<=S2; next\_EVEN<='1'; WHEN S2 => next\_sreg<=S0; next\_EVEN<='1'; END CASE; END IF; END PROCESS;

#### COMBINATORIAL OUTPUTS

```

PROCESS (sreg, RESET) BEGIN

EVEN <= '0'; next_sreg<=S0;

IF ( RESET='1' ) THEN

next_sreg<=S0; EVEN<='1';

ELSE

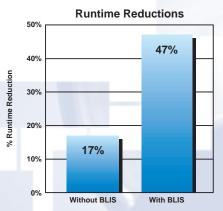

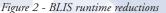

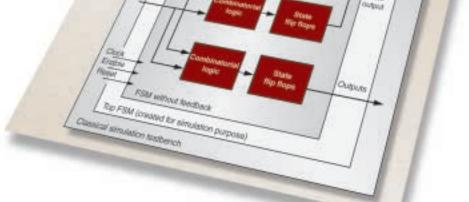

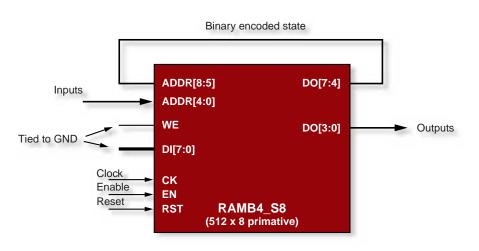

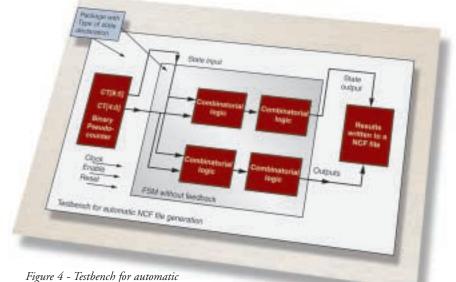

CASE sreg IS