### THE QUARTERLY JOURNAL FOR PROGRAMMABLE LOGIC USERS

DIME

5-MINT

NCV3205E

PIE

SLOT

Issue 34 **Fourth Ouarter** 1999

## **PRODUCT INFORMATION**

**QPRO** - For the Aerospace and Defense Market

Multilinx - New **High-speed Download Cable**

## APPLICATIONS

Spartan FPGAs Used in **Digital Modems**

> Simple Solutions Tricky Problems

## DEVELOPMENT SYSTEMS

Xilinx Launches Design **Reuse Initiative**

gramming a Xilinx FPGA in "C"

**Maximizing HDL** Simulation Performance

XILINX

## **COVER STORY**

New Virtex-E 3.2 million gate, high-bandwidth **FPGA** family

# FROM THE EDITOR

### EDITOR

Carlis Collins editor@xilinx.com 408-879-4519

### **SENIOR DESIGNER**

Jack Farage

#### **BOARD OF ADVISORS**

Dave Stieg Dave Galli Mike Seither Peter Alfke

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3450 Phone: 408-559-7778 FAX: 408-879-4780 ©1999 Xilinx Inc. All rights reserved.

Xcell is published quarterly. XILINX, the Xilinx logo, and CoolRunner are registered trademarks of Xilinx, Inc. Virtex, LogiCORE, IRL, Spartan, SpartanXL, Alliance Series, Foundation Series, CORE Generator, IP Internet Capture, IP Remote Interface, MultiLinx, QPRO, Selectl /O, Select I/O+, True Dual-Port, WebFITTER, WebPACK, ChipViewer, Select RAM, Block Ram, Xilinx Online, and all XC-prefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx. Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided soley for the convenience of our readers. Xilinx maes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

# What's Ahead in the Year 2000...

What do you think will be the big technology news in the year 2000?

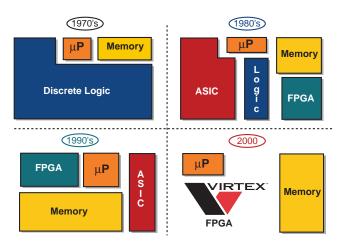

t has been a great year for the programmable logic industry. During 1999, we have seen dramatic advancements in every area: device densities have skyrocketed to two million gates, with unprecedented performance; development tools have become very fast, efficient, and easy to use; intellectual property has become plentiful and widespread; device prices have fallen; unique new applications have arisen.

So, what can you expect in the year 2000?

- Ever Denser FPGAs We already have 2-million gate Virtex<sup>™</sup>-E FPGAs available, and soon we will be shipping our 3.2-million gate, very high performance devices. This much power, in a programmable logic device, gives you unprecedented design freedom and helps you get very complex designs to market as quickly as possible.

- Very Low Cost FPGAs You will continue to get more gates for less money. Our Spartan<sup>™</sup> family of low cost FPGAs keeps getting better and less expensive. Why develop costly, time consuming, risky ASICs, when you can get the flexibility, ease of use, low risk, and low cost of FPGAs? High volume, consumer applications will take full advantage of this breakthrough.

- **Design Reuse** To reach the marketplace sooner, with robust

designs that work right the first time, companies will create libraries of inhouse and third-party intellectual property. Xilinx already provides the tools you need to create and manage intellectual property, and we will continue to lead the industry in this critical area through our Design Reuse Initiative.

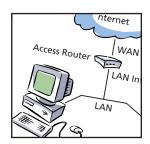

- Internet Reconfigurable Logic You will begin to see many more companies designing hardware that can be reconfigured remotely. The era of single use hardware is over, because it is so easy to build "universal" hardware systems that can change and adapt to new requirements. Using the evolving Xilinx Online™ technology, you can create field upgradable systems that last longer and provide more benefits to your customers for less cost.

- Advanced Development Tools It takes a full team to design with multimillion gate devices, and our new software tools will make it easy to collaborate on designs with engineers anywhere in the world. Look to Xilinx to lead the effort in creating the highlevel, fully-integrated, development tools you will need for both large and small designs.

In the year 2000 you will not only see bigger, better, faster, cheaper devices, you will also see the decline of single use, fixed logic hardware and the beginning of a new paradigm of field upgradable logic.  $\Sigma$

# ARTICLES

## **COVER STORY**

Now you can achieve up to 622 MHz differential I/O performance with the new Virtex-E 3.2 million gate, highbandwidth FPGA family.

## **PRODUCT INFORMATION**

### 20 Xilinx has just introduced a new bitstream download cable that reduces

5

Neticoper XILINK & GINER **IP** Center

download times by 10X over the older XChecker<sup>™</sup> solution.

New tools allow you to capture and share your own intellectual property over the Internet.

## **APPLICATIONS**

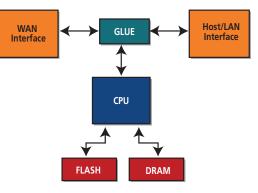

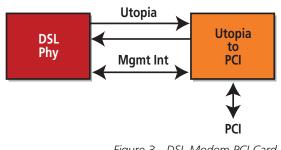

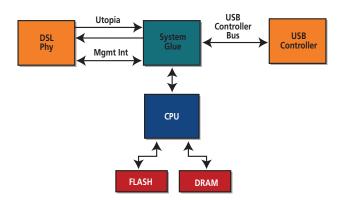

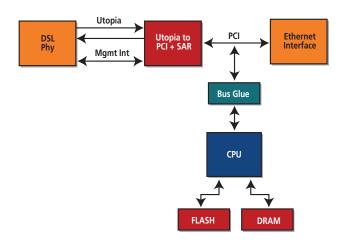

49 An overview of digital modem technologies and how Xilinx high-volume programmable devices can be used to implement complex system-level glue logic in digital modem designs.

For A FREE

**Subscription**

**To The Xcell**

## COLUMN

58

The market has shifted dramatically in the last ninety years. Today the buzzword is "mass customization"unique products at a price comparable to that of mass-produced standard goods.

## www.xilinx.com

E-mail your request to: literature@xilinx.com Please be sure to include:

- 1. Your Full Name and Mailing Address

- 2. Your Title

- Journal 3. The Name of Your Company

### **Inside This Issue:**

| Programmable Logic<br>in the Next Millenium4                    |

|-----------------------------------------------------------------|

| The New Virtex-E 2-Million Gate,<br>High-bandwidth FPGA Family5 |

| Virtex-E Package<br>Compatibility Guide10                       |

| Xilinx Receives Cisco's Highest<br>Honor for a Supplier         |

| Stackable Virtex FPGA Board for<br>General Use14                |

| QPRO - for the Aerospace and<br>Defense Market16                |

| Gamma-ray Large Area Space<br>Telescope (GLAST) Tower CPU18     |

| Xilinx introduces New<br>High-speed Download Cable 20           |

| Programmable Flash SPROMs21                                     |

| Simultaneous 4-channel, 12-bit<br>A/D Conversion22              |

| Spartan FPGAs Help Create<br>Movie-quality Video on the PC23    |

| Infrared Digital Voice Module 24                                |

| Programming a Xilinx<br>FPGA in "C"                             |

| Java Tool Increases Pipelining<br>Speed                         |

| Maximizing HDL Simulation Performance                           |

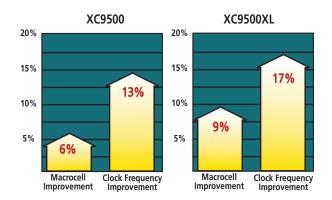

| What's New in V2.1i for XC9500 CPLDS?34                         |

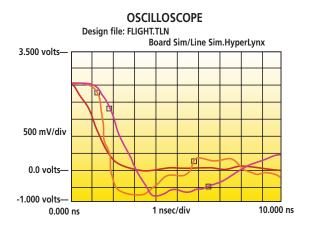

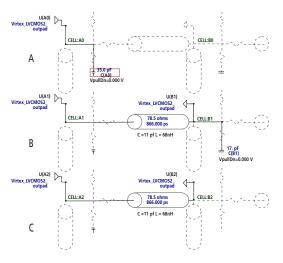

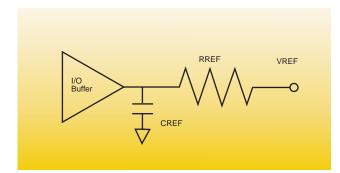

| Timing Correction for Flight<br>Time Compensation               |

| The Power of the Xilinx<br>Foundation Series Software41         |

| Xilinx Launches Design<br>Reuse Initiative                      |

| Try HDL Simulation for Free 46                                  |

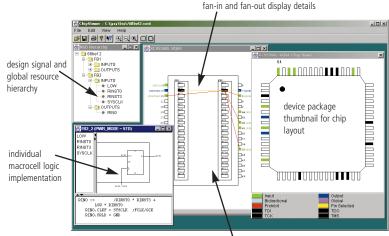

| CPLD ChipViewer -                                               |

| Graphical Design Control<br>Made Simple48                       |

| Xilinx at Work in<br>Digital Modems 49                          |

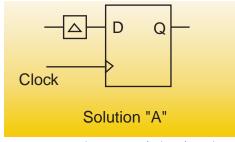

| Two Simple Solutions for<br>Tricky Problems54                   |

| Trade Show Programs56                                           |

| How Programmable Logic<br>Provides More Options                 |

| for Consumers                                                   |

| Product Selection Guide                                         |

| Competitive Overview                                            |

|                                                                 |

- 4. Your E-mail Address

- 5. Is This New Subscription or a subscription Renewal?

## **View from the Top**

# Programmable Logic in the Next Millenium

I expect that within the first ten years of the next millennium we will see programmable logic devices inside every piece of electronic equipment, because hardware will become just as programmable as software.

by Wim Roelandts, President and CEO, Xilinx

> all Street market analysts expect the programmable logic industry to grow another 25-35% in the year 2000, following a 25%

increase in 1999. This increase is being driven, in part, by a worldwide economic recovery; we are seeing dramatic increases in Southeast Asia, and Japan is also beginning to improve. However, the recovering world economy is just one of many reasons for the dramatic growth in programmable logic.

The primary reason for this phenomenal growth is the tremendous technological advances that have taken place over the last two years. In 1996, our largest FPGA contained just 50,000 gates, and no BlockRAM<sup>™</sup>. Today, the Xilinx Virtex-E family offers up to 3.2 million system gates, with 832 kbits of BlockRAM. This means that FPGAs are large enough and fast enough to interest designers who once relied on gate array or standard cell technology. Using FPGAs, designers can now get the performance and density of gate arrays, and something gate arrays never offered—fast time-to-market and affordable pricing.

Xilinx will soon introduce a new Spartan family which will offer 100,000 system gates for less than \$10.00. This downward pricing trend is expected to continue, and 500,000 system gates will be available for under \$10.00 by the year 2003. These dramatic improvements will further expand the influence of programmable logic in new, fast growing, high volume equipment such as cable and DSL modems, cell phones, handheld electronic games, and DVD players.

The total cost of ownership for an FPGA has also stayed flat, as compared to substantial increases in the cost of ownership for standard cell and gate-array technology. FPGAs eliminate the need for expensive NRE (Non Recurring Engineering), development, system integration, and field deployment costs. However, NRE charges for standard cell and gate array ASICs have risen sharply as feature sizes have dropped below 0.5 micron. In addition, for gate array and standard cell chip development, the required board debugging, system integration, and field trial costs have also gone up sharply.

Another significant attraction of programmable logic is field upgradability. Because FPGAs can be reprogrammed an infinite number of times, equipment can easily be upgraded over a network after it has been installed at a customer's premises. This allows forward-thinking manufacturers to quickly get their new products to market and then add new features, comply with evolving standards, or fix bugs, remotely, without physically replacing any hardware.

The year 2000 is clearly a turning point for the programmable logic industry, as we quickly expand into new high-volume markets with advanced high-density, low-cost technologies.  $\Sigma$

## **Cover Story**

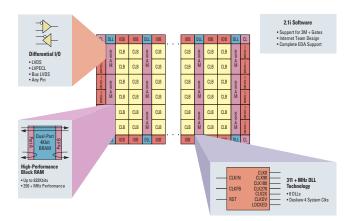

# THE NEW Virtex-E 3.2-Million Gate, High-bandwidth FPGA Family

With up to 622 MHz differential I/O performance, Virtex-E FPGAs are the high-bandwidth solution for your next generation high performance systems.

*by Bruce Jorgens, Virtex Product Marketing Manager, Xilinx, jorgens@xilinx.com*

he new Virtex-E FPGA family is built on the highly successful Virtex architecture. Leveraging our latest 0.18-micron, sixlayer metal technology, Virtex-E devices now give you up to 3.2 million system gates, 804 I/Os, and up to 622 MHz differential I/O performance. Combined with system-level features for clock management, multiple I/O standards, and embedded True Dual-Port<sup>™</sup> memory, the Virtex-E family is designed to support the high bandwidth requirements of next generation high performance DSP and communication systems.

|          |             | Dual-Port Block | Maximum  | I/O Bandwidth |

|----------|-------------|-----------------|----------|---------------|

| Device   | Logic Cells | Memory (Kbits)  | User I/O | (Gbits/sec)   |

| XCV50E   | 1728        | 56              | 176      | 44            |

| XCV100E  | 2700        | 80              | 176      | 44            |

| XCV200E  | 5292        | 112             | 284      | 71            |

| XCV300E  | 6912        | 128             | 316      | 79            |

| XCV400E  | 10800       | 160             | 404      | 100           |

| XCV600E  | 15552       | 288             | 512      | 127           |

| XCV1000E | 27648       | 384             | 660      | 164           |

| XCV1600E | 34992       | 576             | 724      | 180           |

| XCV2000E | 43200       | 640             | 804      | 200           |

| XCV2600E | 57132       | 736             | 804      | 200           |

| XCV3200E | 73008       | 832             | 804      | 200           |

1 I/O bandwidth = (80% max. user I/O) x (311 Mbps)

Table 1 - Virtex-E Features

Many designs will require multiple high bandwidth data ports with I/O bandwidth distributed across the required ports as shown in Table 1. Virtex-E devices range from 44 Gbps to 200 Gbps I/O bandwidth. For applications such as OC-192, Virtex-E devices can easily support the multiple 10-Gbps data ports that are required.

### Bandwidth-enabling Technology

The Virtex-E devices contain advanced systemlevel technology that is specifically designed to support high bandwidth applications. Figure 1 shows a block diagram of the Virtex-E bandwidth-enabling technology including digital Delay Lock Loops (DLLs), True Dual-Port embedded memory, and SelectI/O+ technology.

Figure 1 - Virtex-E Architecture Overview

### **Eight High Performance DLLs**

The Virtex-E advanced DLL technology provides the system clock management that is necessary for high bandwidth chip-to-chip or backplane applications. The DLL circuitry allows very precise synchronization of external and internal clocks. Xilinx was the first to deliver this technology by offering four 200 MHz DLLs in each Virtex device. The Virtex-E family takes this technology to the next level offering eight DLLs in each Virtex-E device.

As a fully digital implementation, the Virtex and Virtex-E DLLs do not have the typical problems encountered with analog phase locked loops (PLLs); PLLs are extremely sensitive to noise on the power and ground pins. Many systems cannot provide the isolation and decoupling required for the proper operation of a PLL, while the Virtex-E DLLs have no special requirements. Also, because the DLL is not sensitive to process variations, it is offered as a standard feature in every device, and every speed grade.

Virtex-E DLLs provide precise clock edges through phase shifting, frequency multiplication, and frequency division. Table 2 shows the basic characteristics of the Virtex-E DLLs.

| Parameter                   | Value        |

|-----------------------------|--------------|

| Maximum Output Frequency    | 320 MHz*     |

| Maximum Output Jitter       | 100 ps       |

| Output Frequency Duty Cycle | 50%+/- 100ps |

\* Based on Virtex-E -7speed grade product

Table 2 - Bandwidth-critical Specifications of the Virtex-E DLL

## Maximizing Memory Bandwidth with Virtex-E DLLs

A key technique for increasing the bandwidth of a particular data port is to have signals change on both edges of the clock, commonly referred to as the "Double Data Rate" technique. At high frequencies, signal integrity limits the clock performance, which limits the bandwidth of the data. Bandwidth for the port is immediately doubled if the architecture can change data at each edge of a system clock. Memory suppliers have already started to support this type of high performance technique to increase the memory bandwidth of their devices.

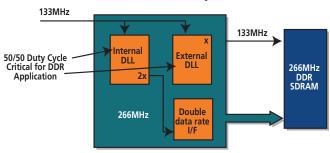

For this technique to work, it is critical that the clock duty cycle be as close to 50 percent as possible. Because Virtex-E DLLs can generate clocks with a duty cycle guaranteed to be within 100 picoseconds of 50 percent, you can achieve the maximum memory bandwidth when interfacing to the fastest DDR memories. Figure 2 demonstrates how Virtex-E DLLs, coupled with the SelectI/O+<sup>TM</sup> technology, help achieve maximum bandwidth in a 266MHz DDR application.

Figure 2 - Virtex-E Interfacing to a 266 MHz DDR SDRAM Memory

### Selectl/O+ Technology

To meet high bandwidth requirements, electrical signals must switch at over 100 MHz; standard TTL and CMOS signal technology cannot keep pace. With the original Virtex family, Xilinx pioneered the SelectI/O<sup>™</sup> technology which supports 200 MHz I/O and allows a single FPGA to interface with any other device without external converters. Virtex-E SelectI/O+ technology expands the performance and flexibility by supporting high performance I/O standards such as HSTL and SSTL at over 300 Megabits per second (Mbps) per pin. In addition, Virtex-E devices are the first programmable logic devices to directly interface with differential I/O standards including LVDS, Bus LVDS (BLVDS), and LVPECL.

| Standard                       | Typical Application                       |

|--------------------------------|-------------------------------------------|

| LVTTL                          | 3.3 V General Purpose                     |

| LVCMOS2                        | 2.5 V General Purpose                     |

| LVCMOS18                       | 1.8 V General Purpose                     |

| PCI33_3                        | 33 MHz 3.3 V PCI Backplane                |

| PCI66_3                        | 66 MHz 3.3 V PCI Backplane                |

| SSTL2 (I,II), SSTL3(I,II), CTT | SDRAM, DDR SRAM                           |

| HSTL(I,III,IV)                 | SRAM, DDR SDRAM, Backplanes               |

| GTL, GTL+, AGP                 | Backplanes, Microprocessor Interfacing    |

| LVDS                           | Point to Point and Multi-drop Backplanes  |

|                                | High Noise Immunity                       |

| BLVDS                          | Bus LVDS Backplanes, High Noise Immunity, |

|                                | Bus Architecture Backplanes               |

| LVPECL                         | High Performance Clocking, Backplanes,    |

|                                | Differential 100MHz+ Clocking, Optical    |

|                                | Transceiver, High Speed Networking, and   |

|                                | Mixed-Signal Interfacing                  |

| 5 V TTL* ( 4mA lol )           | Legacy 5V TTL Interfacing                 |

\*Requires 100 Ohms external resistor

Table 3 - I/O standards Supported by Virtex-E Family

### High-performance Differential Signaling: LVPECL, LVDS, and Bus LVDS

Increasingly, leading systems designers are turning to differential signaling as the mechanism of choice for backplane applications. Differential signaling enables high bandwidth while reducing power, increasing noise immunity, and decreasing EMI emissions. Virtex-E devices meet this emerging challenge with unprecedented capabilities and support for high-performance differential signaling.

The Virtex-E family supports a hierarchy of differential solutions including up to 36 pairs of LVDS and/or LVPECL operating at 622 MHz, and up to 344 differential pairs operating up to 311 MHz. This gives you a maximum differential I/O bandwidth of over 100 Gbps, which can be distributed over the three differential signal standards as needed. For the first time in a programmable device, you can leverage the high bandwidth and noise immunity characteristics of these standards.

LVPECL I/O is widely used in 100+ MHz inter-chip signaling in high-speed data communications and instrumentation systems. Fiber-optic network interfaces and gigahertz analog-to-digital converters, for example, rely on LVPECL I/O to achieve gigabit per second bandwidth. All Virtex-E differential I/Os support LVPECL input, output, and I/O signaling.

In addition to high-speed interfacing, LVPECL is the industry standard for transmission of precise, on-board clocks at frequencies in excess of 100 MHz. While traditional LVTTL clock sources are typically limited to 100 MHz and below (due to the fundamental signal integrity limits), LVPECL clock sources provide operation up to 400 MHz. As FPGA system clock frequencies exceed 100 MHz, LVPECL clocking becomes an essential requirement. Virtex-E devices support high-performance LVPECL clock inputs for global and local clocking, with frequencies in excess of 300 MHz. In addition, through the use of its multiple DLLs coupled with SelectI/O+ technology, the Virtex-E devices enable zerodelay conversion of precise LVPECL clocks into any required I/O standard. Thus, Virtex-E FPGAs are an integral part of high-performance board-level clock distribution strategies.

In addition to LVPECL, the Virtex-E family has the industry's first programmable devices to support Low-Voltage Differential Signaling (LVDS). LVDS exists in two commonly available variants: LVDS and Bus LVDS. LVDS is optimized for high-speed point-to-point links, while Bus LVDS is optimized for backplane applications employing multi-drop (one transmitter, multiple receiver), and multi-point (multiple transmitters and receivers) configurations.

Virtex-E devices provide unparalleled support for both LVDS and Bus LVDS, with support on all devices and speed grades. You can use up to 688 pins (344 pairs) of LVDS and Bus LVDS capabilities on the largest device, providing differential I/O bandwidth in excess of 100 Gbps.

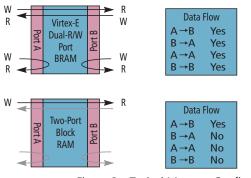

### True Dual-Port Embedded Block Memory

Whether used as FIFOs, caches, or ATM packet buffers, the system requirements for more memory grows much faster than logic requirements. Xilinx pioneered using embedded distributed memory (with its SelectRAM technology) in its XC4000 FPGAs, allowing the configurable logic block to support logic or memory. With the Virtex series, this technology was enhanced to include up to 128 Kbits of True Dual-Port block RAM. The Virtex-E family again provides a quantum leap in internal memory bandwidth by supporting up to 832 Kbits of True Dual-Port RAM (208 blocks of 4Kbits memory) capable of 250 MHz performance.

To emulate most of the functionality of a dual-port memory, two-port memory architectures require twice the number of memory bits and multiplexing of address and data as shown in Figure 3. This results in twoport memory at roughly half the bandwidth and half the efficiency of the Virtex-E True Dual-Port memory in any given configuration.

Figure 3 - Typical Memory Configurations

### Managing Bandwidth Using True Dual-Port Memory

Each Virtex-E True Dual-Port memory block supports 4 Kbits of memory, and each port can be configured separately to support a variety of depth/width combinations. Embedded memory can buffer high bandwidth data as well as reduce the internal processing speed by transparently converting from one data width to another.

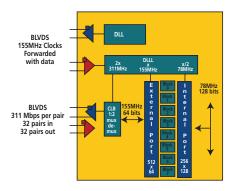

Figure 4 - An OC-192 Application Example

Figure 4 demonstrates an OC-192 application example. A data port with OC-192 bandwidth comes in on 32 BLVDS pairs running at 311 Mbps per pair. Eight blocks of embedded RAM are used to buffer the data internally. The port taking data from the I/O register to the memory is configured as 512 rows deep by 64 bits wide. The port leading to the internal processing of the data is configured as 256 by 128. Internal processing of the 128-bit data need only run at 78 MHz to keep up with the OC-192 bandwidth. An outgoing port would be configured similarly.

### Packaging

To support a 10-Gbps bandwidth, the device package must be capable of packing many high performance I/Os in limited board space. The package must also be able to dissipate several watts of power. Virtex-E devices continue the tradition of offering the industry's most reliable and flexible packaging, including

- PQFP Plastic quad flat pack.

- BGA 1.27 mm ball grid array.

- CSP Leading-edge 0.8 mm chip scale package.

• FG - 1.0 mm fine pitch BGA.

These packages are supported across the family.

For the fine pitch 1.0 mm BGA offering, the Virtex-E family introduces three new FG packages:

- FG900 31 mm X 31 mm.

- FG1156 35 mm X 35 mm.

- FG860 42.5 mm X 42.5 mm (thermally enhanced).

The Virtex-E family can now support up to 804 I/Os using board area as small as 35 mm by 35 mm. These packages set new standards in I/Os per square inch as well as maximum bandwidth per square inch.

### Summary

The new Virtex-E FPGA family helps you meet the bandwidth requirements of the next generation high performance systems by giving you significant performance and flexibility enhancements in the areas of clock management, SelectI/O+ technology, True Dual-Port block memory, and high performance differential signaling. **X**

For more detailed information on the Xilinx Virtex-E series, including data sheets and applications notes, visit the product section of the Xilinx website at www.xilinx.com.

# Virtex-E Package Compatibility Guide

*This package compatibility guide describes the Virtex-E pin-outs and establishes guidelines for package compatibility between Virtex and Virtex-E devices.*

*by Robert Le, Sr. Applications Engineer, Xilinx, robertle@xilinx.com*

he 1.8V Virtex-E FPGA family combines 0.18 mm technology with a synthesisfriendly silicon architecture to provide a new level of FPGA performance and density. Virtex-E FPGA availability in packages compatible with Virtex FPGAs allows systems to migrate from using Virtex family devices to Virtex-E family devices. Package pinout and pin functionality differences between Virtex-E and Virtex FPGAs are covered in this article.

### **Power Supplies**

As with the Virtex family, the Virtex-E positive supply is divided into two separate power supplies: VCCO and VCCINT. VCCO powers output pins and LVTTL, LVCMOS, and PCI output and input pins. VCCINT powers internal logic and all input pins except LVTTL, LVCMOS, and PCI inputs.

The Virtex-E VCCINT is 1.8V (while the Virtex VCCINT is 2.5V). This is a result of more advanced processing and 0.18 mm design rules, which also offer reduced die size, reduced power consumption, and increased speed. VCCO is adjustable, up to 3.3V, depending on the I/O standard used.

Voltage regulator modules with programmable output voltages can be used to power the VCCO and VCCINT inputs and accommodate the lower 1.8V VCCINT in the Virtex-E family.

### I/O Standards

Virtex-E devices can be used with 20 highperformance interface standards, including the LVDS and LVPECL differential signalling standards. A new LVCMOS I/O standard based on 1.8V VCCO is also supported. All I/O pins are 3V tolerant, and can be 5V tolerant with an appropriate external resistor. PCI 5V is not supported. Table 1 shows a complete listing of the supported I/O standards.

/IRTEX-E

### I/O Banking

There are eight I/O banks in the Virtex-E family, as in the Virtex family, and each bank has multiple VCCO pins. All of the VCCO pins in one bank must be connected to the same voltage level, as determined by the I/O standard in use.

In Virtex-E devices the banking rules are different because the input buffers with LVTTL, LVCMOS, and PCI standards are powered by VCCO instead of VCCINT. For these standards, only input and output buffers that have the same VCCO can be mixed together in the same bank.

### Low Voltage Differential Signals

The Virtex-E family incorporates differential signalling (LVDS and LVPECL). Two pins are utilized for these signals to be connected to a Virtex-E device. These are known as differential pin pairs. Each differential pin pair has a Positive

| I/O<br>Standard | Output<br>VCCO | Input<br>VCCO | Input<br>VREF | Board Termination<br>Voltage (VTT) |

|-----------------|----------------|---------------|---------------|------------------------------------|

| LVTTL           | 3.3            | 3.3           | N/A           | N/A                                |

| LVCMOS2         | 2.5            | 2.5           | N/A           | N/A                                |

| LVCMOS18        | 1.8            | 1.8           | N/A           | N/A                                |

| SSTL3   & II    | 3.3            | N/A           | 1.50          | 1.50                               |

| SSTL2   & II    | 2.5            | N/A           | 1.25          | 1.25                               |

| GTL             | N/A            | N/A           | 0.80          | 1.20                               |

| GTL+            | N/A            | N/A           | 1.0           | 1.50                               |

| HSTL I          | 1.5            | N/A           | 0.75          | 0.75                               |

| HSTL III & IV   | 1.5            | N/A           | 0.90          | 1.50                               |

| СТТ             | 3.3            | N/A           | 1.50          | 1.50                               |

| AGP-2X          | 3.3            | N/A           | 1.32          | N/A                                |

| PCI33_3         | 3.3            | 3.3           | N/A           | N/A                                |

| PCI66_3         | 3.3            | 3.3           | N/A           | N/A                                |

| BLVDS/LVDS      | 2.5            | N/A           | N/A           | N/A                                |

| LVPECL          | 3.3            | N/A           | N/A           | N/A                                |

Table 1 - Supported I/O Standards

(P) and a Negative (N) pin. These pairs are labeled in the following manner:

I/O\_L#[P/N]

where L= LVDS or LVPECL pin

- # = Pin Pair Number

- P = Positive

- N = Negative

I/O pins for differential signals can either be synchronous or asynchronous, input or output. The pin pairs can be used for synchronous input and output signals as well as asynchronous input signals. However, only some of the differential pairs can be used for asynchronous output signals.

Differential signals require the

pins of a pair to switch almost simultaneously. If the signals driving the pins are from IOB flipflops, they are synchronous. If the signals driving the pins are from internal logic, they are

| Pin Name                  | Description                                                                                                                                                                                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_L#[P/N]                | Represents a general I/O or a synchronous                                                                                                                                                                                               |

| Example: IO_L22N          | input/output differential signal. When used<br>as a differential signal, N means Negative I/O<br>and P means Positive I/O.                                                                                                              |

| IO_L#[P/N]_Y              | Represents a general I/O or a synchronous input/output differential signal, or a part-                                                                                                                                                  |

| Example: IO_L22N_Y        | dependent asynchronous output<br>differential signal.                                                                                                                                                                                   |

| IO_L#[P/N]_YY             | Represents a general I/O or a synchronous input/output differential signal, or an                                                                                                                                                       |

| Example: O_L22N_YY        | asynchronous output differen-tial signal (for<br>all devices within the same package.)                                                                                                                                                  |

| IO_LVDS_DLL_L#[P/N]       | Represents a general I/O or a synchronous<br>input/output differential signal, or a<br>differential clock input signal or a DLL input.<br>When used as a differential clock input, this<br>pin is paired with the adjacent GCK pin. The |

| Example: IO_LVDS_DLL_L16N | GCK pin is always the positive input in the differential clock input configuration.                                                                                                                                                     |

Table 2 - Differential Pin Pairs

asynchronous. Table 2 defines the names and function of the different types of differential pin pairs in the Virtex-E family.

| Part       | Package     | Pins                                  | Virtex     | Virtex-E    |

|------------|-------------|---------------------------------------|------------|-------------|

| XCV200     | FG456       | E11, U11                              | I/O        | No Connect  |

|            |             | B11, AA11                             | No Connect | IO_LVDS_DLL |

| XCV300     | BG432       | B26, C7, F1, F30, AE29, AF1, AH8, and | No Connect | VCCINT      |

|            |             | AH24                                  |            |             |

| XCV400     | FG676       | D13, Y13                              | I/O        | No Connect  |

|            |             | B13, AF13                             | No Connect | IO_LVDS_DLL |

| XCV400/600 | PQ240/HQ240 | P215, P87                             | IO_VREF    | IO_LVDS_DLL |

|            |             | P216, P86                             | I/O        | IO_VREF     |

| All        | PQ240/HQ240 | P232, P207, P176, P146, P116, P85,    | I/O        | Vcco        |

|            |             | P55, and P25                          | I/O        | IO_VREF     |

|            |             | P231                                  |            |             |

Table 3 - Virtex Family Compared to Virtex-E Pin-out Differences

### **Differential Clock Pins**

In addition to the four GCLKs in the Virtex family, the Virtex-E family has four IO\_LVDS\_DLL pins that can be paired with GCLKs to support up to four differential clocks. A differential clock input pair always includes one GCLK and the adjacent IO\_LVDS\_DLL pin. The GCLK pin is always the positive input in differential clock input configurations.

When differential clocks are not in use, these IO\_LVDS\_DLL pins can be used as single-ended I/Os or as DLL input pins.

### **DLL Input Pins**

Four additional DLL input pins (IO\_LVDS\_DLL) can be used as inputs to the DLLs, for a total of eight usable inputs for DLLs in the VIrtex-E family. This is very useful in clock mirroring applications.

### **Pinout Differences**

The Virtex-E and Virtex families are pincompatible with some minor exceptions as shown in Table 3. Some of the exceptions are described below:

- XCV200E Device, FG456 Package The Virtex-E XCV200E has two I/O pins swapped with the Virtex XCV200 to accommodate differential clock pairing.

- XCV300E Device, BG432 Package The Virtex-E XCV300E has eight pins (B26, C7, F1,

F30, AE29, AF1, AH8, and AH24) connected to VCCINT that are no-connect in the Virtex XCV300.

- XCV400E Device, FG676 Package The Virtex-E XCV400E has two I/O pins swapped with the Virtex XCV400 to accommodate differential clock pairing.

- All Devices, PQ240 and HQ240 Packages -The Virtex devices in PQ240 and HQ240 packages do not have VCCO banking, but Virtex-E devices do. To achieve this, eight Virtex I/O pins (P232, P207, P176, P146, P116, P85, P55, and P25) are now VCCO pins in the Virtex-E family. This change also requires one Virtex IO\_V<sub>REF</sub> pin to be swapped with a standard I/O pin.

Additionally, accommodating differential clock input pairs in Virtex-E caused some  $IO_V_{REF}$  differences in the XCV400E and XCV600E devices only. Virtex  $IO_V_{REF}$  pins P215 and P87 are Virtex-E  $IO_V_{REF}$  pins P216 and P86, respectively. Virtex-E pins P215 and P87 are now  $IO\_LVDS\_DLL$ .

### Conclusion

Though the new Virtex-E family has many enhancements, it can easily be interchanged with the Virtex family, with only minor considerations.  $\Sigma$

This information is subject to change. For the latest information, see the Xilinx web site at http://www.xilinx.com.

# Xilinx Receives Cisco's Highest Honor for a Supplier

*Xilinx has been named one of the top suppliers for 1999 by the worldwide leader in networking for the Internet.*

*by Ann Duft, Public Relations Manager, Xilinx, annd@xilinx.com*

uring the recent eighth annual supplier appreciation ceremonies, Cisco CEO John Chambers presented the Xilinx team with the President's Customer Satisfaction Award, Cisco's highest honor for a supplier. Chambers said that programmable logic technology

Cisco CEO, John Chambers, presented this award to Xilinx.

developed by Xilinx has helped Cisco reduce the time necessary to bring innovative new networking products to market.

"We are tremendously pleased to receive this award from Cisco and their recognition of the value of Xilinx programmable logic solutions," said senior vice president Dennis Segers, who accepted the award on behalf of Xilinx. "What pleases me most is it recognizes the results of the outstanding teamwork on the part of many, many Xilinx employees, as well as our suppliers, sales and distribution partners who are contributing to Cisco's success." customers," said Michael J. Campi, vice president of global supply management for Cisco Systems. "Xilinx has helped Cisco exceed our customers' expectations."

In addition to being nominated for the President's Customer Satisfaction Award, Xilinx was also nominated as best semiconductor supplier. Cisco presented awards to winners in 11 categories in all. Suppliers in each of the categories were selected by a panel of representatives from Cisco's Corporate Supply Management and Global Supply Management organizations.  $\boldsymbol{\Sigma}$

This was the first time Xilinx was nominated for the President's award.

"This award is given to the supplier who makes significant contributions that directly impact the customer satisfaction level of Cisco

# Stackable Virtex FPGA Board For General Use

A new basic board to help you quickly test and implement your Virtex-based design.

*by Dr. Stefan Schafroth, Hardware and Software Development Engineer, ErSt Electronic GmbH, stefan.schafroth@erst.ch*

he EVALXCV-HQ240 board has been designed to provide all the necessary basic components needed in most Virtexbased designs. All I/Os are routed to header connectors where you connect your special purpose interfaces. By stacking several boards you can easily cope with the complexity of a design which exceeds the scope of a single FPGA.

To overcome the annoying task of supplying the board with several supply and reference voltages, we have also created a power module which does this for you. It can be attached directly to the FPGA board such that the two boards form a single unit.

### **Key Features**

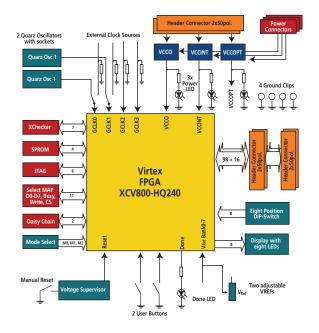

The heart of the board is a Virtex FPGA in an HQ-240 package (XCV800/600/400) . Vital components for a basic system are placed around the FPGA. These include two crystal oscillators, three push buttons, DIP switches, and nine status LEDs. All configuration modes of the FPGA are supported. You can provide configuration data either by serial configuration PROMs (SCPs) sitting in onboard sockets or by connecting a Xilinx MultiLINX, XChecker<sup>™</sup>, or JTAG cable. A functional diagram detailing the

Figure 1- Functional Diagram of the FPGA Board Module

building blocks of the Virtex FPGA board is shown in figure 1.

The board is very well suited to:

- Evaluate the larger members of the Virtex FPGA family.

- Implement custom designs utilizing the full power of Virtex FPGAs.

- Quickly and easily expand the complexity of the system by stacking several boards.

Figure 2 - Top View of the FPGA Board

Figure 2 shows a top view of the board. On the right side you see the connectors used to supply configuration data, sockets for SCPs, crystal oscillators, and LEDs. The push buttons and DIP switches are placed on the left side. Header connectors for I/O signals run along the top and bottom side of the board.

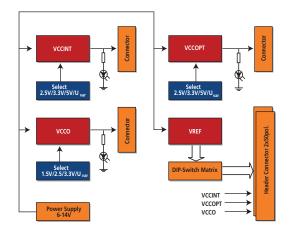

### **Power Module**

Although you can use the Virtex board standalone, we recommend that you use our PWR3 power module which has been designed to eliminate the burden of manually applying several low level supply voltages. It generates

Figure 3 - Functional Diagram of the Power Module

Figure 4 - View of the Power Module with Attached FPGA Board

three regulated output voltages and eight reference voltages from a single unregulated power supply. Its output power is sufficient to satisfy the needs of several FPGA boards stacked together. A functional diagram is shown in figure 3. In figure 4 you see the power module attached to the bottom side of the Virtex board.

### Conclusion

The EVALXCV-HQ240 gives you an ideal platform for evaluating, implementing, testing and extending Virtex FPGA based custom designs. You can also easily integrate the board into a larger system. The power module eliminates the need for several supply voltages and forms a compact unit with the FPGA board.

For additional information on EVALXCV-HQ240 and PWR3 see: www.erst.ch, or contact us at info@erst.ch.

## **O-Pro - for the**

With densities up to one million system gates, Virtex QPRO<sup>™</sup> devices provide an off-the-shelf system-level ASIC solution, without the non-recurring engineering costs, long prototype cycles, and minimum volumes required of custom ASICs.

*by Howard Bogrow, Marketing Manager, Aerospace and Defense Products, Xilinx, Inc., howard@xilinx.com*

he Aerospace and Defense market has been undergoing significant changes in recent years, and continues to challenge both system designers and component suppliers. Designers no longer have to specify mil-spec parts for every application, and as a result numerous mil-spec suppliers have exited the market. Thus, it has become increasingly difficult for aerospace and defense customers to obtain many needed devices. Additionally the use of custom or semi-custom ASICs may no longer be a viable option.

Even with all the changes that are taking place, the aerospace and defense market still has some unique product and supply chain requirements:

Design Evolution Using FPGAs

• **Operating temperature range** - This is typically a harsh operating environment, and while many new designs are able to use industrial temperature components, there are still numerous applications that require guaranteed performance over a wider temperature range. QPRO Virtex FPGAs provide this guarantee.

se market

- **Packaging** Many new applications are able to take advantage of the more cost-effective plastic packages. The QPRO Virtex family offers a wide range of solutions for these applications in both flat pack and ball grid technology. However, ceramic packaging is still available for those applications that require hermeticity, such as shipboard and space. The latest addition to our hermetic package offering is the CG560, a ceramic surface mount column grid array, which is available for the XQV1000 device.

- **COTS and DMS** There is a very strong trend towards the use of COTS (commercial off-the-shelf) components, and away from custom or specially processed parts. Also, a big concern is DMS (diminished material supply) or product obsolescence. The QPRO Virtex family are COTS products in every sense of the definition. They are commercially available standard products that require no special processing or specifications. And,

because the QPRO Virtex family is now available with up to 1,000,000 system gates, the functions of many obsolete components such as discrete logic, semi-custom ASICs, processors, memories, and interface chips can now be incorporated into a single QPRO Virtex FPGA.

• **IP Cores** - Many aerospace and defense systems use a PowerPC architecture, and military versions of the peripherals for this processor have become very difficult to obtain. To address this problem Eureka Technologies of Los Altos, California, has developed an IP core solution that can be incorporated into QPRO Virtex devices. This core includes a PowerPC bus master and slave, PCI host bridge, bus arbiter, SDRAM controller, DMA controller, and UART.

| Device  | System Gates | Packages                      |

|---------|--------------|-------------------------------|

| XQV100  | 100,000      | PQ240, BG256, CB228           |

| XQV300  | 300,000      | PQ240, BG352, BG432,<br>CB228 |

| XQV600  | 600,000      | HQ240, BG432, CB228           |

| XQV1000 | 1,000,000    | BG560, CG560                  |

Table 1 - QPRO Virtex Product Offering

### Summary

QPRO Virtex devices provide unsurpassed flexibility as a replacement for ASICs for the aerospace and defense market. These products offer system-level integration and performance, and because they are reconfigurable, field upgrades are possible. QPRO Virtex FPGAs bring state-of-the-art technology to this market, while solving the critical supply management issues. **X**

### **SEU Mitigation Techniques for Virtex FPGAs in Space Applications**

SRAM-based logic devices such as FPGAs have some susceptibility to Single Event Upsets (SEU) and functional interruption. This paper describes several reliable mitigation techniques for the Virtex series FPGA architecture, which will retain functional integrity while static upsets are detected and corrected.

Additionally, this paper demonstrates how an SEU in an FPGA can be corrected in 3us without disrupting operation of the device, how to build hardened voting circuits, and that a single event has only 1 chance out of 3.25 million of causing a functional interrupt.

Re-configurable computing and adaptive hardware is an emerging technology for space applications. The basis for this technology is the capability for device- and system-level functional changes to be implemented in-system and transmitted remotely. FPGAs provide an array of logic resources, which may be interconnected, and configured for specific functions. All logic definitions and block connections are controlled by static RAM cells. Thus, this technology is sometimes referred to as "SRAM Logic," which allows for on-the-fly reconfiguration of the circuits' functional definition.

The Xilinx XQVR product line is a radiation-tolerant version of the of the commercially popular Virtex series FPGA. Virtex has become a common ASIC replacement in commercial markets due to its density, performance, and wide range of capabilities. The XQVR utilizes an epitaxial process that renders it latch-up immune to an LET of 125MeV-cm2/mg.

This is an excerpt of a paper presented by Carl Carmichael, Xilinx Applications Engineer, at the 1999 MAPLD Conference, held at Johns Hopkins University. For the complete paper, go to http://www.xilinx.com/products/hirel\_qml.htm

# Gamma-ray Large Area Space Telescope (GLAST) Tower CPU

Sapphire Computers Inc. recently designed the prototype Tower CPU for the GLAST space telescope program, using XC4000XL FPGAs.

*by Dan Rudolf, President, Sapphire Computers, Inc. drudolf@fpgaConfigurator.com, Phone: (937) 767-1062*

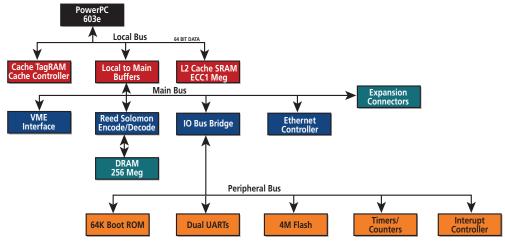

LAST will provide astronomers and physicists a direct view of galactic gamma-ray sources in the 10MeV to 300GeV range (such as black holes, neutron stars, blazars, and pulsars). The 16 Tower CPU (TCPU) cards planned for the telescope will provide high-speed parallel processing of the vast amount of data captured by each of 16 sensor arrays.

The GLAST TCPU provides a very high level of computing power for a space processor board design, to handle the bandwidth of the data stream from the sensor arrays. It incorporates a 100MHZ PowerPC 603e with 64-bit data paths to the level 2 (L2) cache and main DRAM memory. A split-level bus architecture ensures fast accesses to the L2 cache while allowing simultaneous DMA access to the main memory array. This level of processing power does not come without an increase in power consumption, so the TCPU design includes power saving sleep modes and allows programmable reduction of the bus clock rates. To provide solid operation in a space

environment, the L2 cache, the flash program store, and the DRAM memory are all error correction coded.

### **Specifications**

The prototype TCPU is a VME card running the VxWorks operating system, with one megabyte of L2 cache, 256 megabytes of 64-bit-wide Reed-Solomon corrected DRAM, Flash memory, serial I/O, and Ethernet capability. The prototype board's goal is to give the GLAST software developers a development platform that is a functional equivalent to the final space-qualified board without the expense of using radiation hardened components.

Finding space-qualified device equivalents turned out to be one of the more challenging aspects of this design. There are few radhard component vendors and very few high integration

devices available in radiation hardened versions. As a result, a number of system functions that are normally available in ASICs had to be custom designed in FPGAs. One of these is the PowerPC's companion L2 and cache memory controller, the MPC106. While the 603e processor is relatively radhard, the MPC106 is not.

All the memory and cache control functions had to be implemented in programmable logic. Additionally the interrupt controller, the system timers, the DRAM error corrector, and the DMA arbiter all had

### **About Sapphire Computers**

Sapphire Computers Inc. specializes in high performance digital microprocessor and FPGA design. Xilinx FPGAs are used to reduce system cost, to shorten the time to market, and to allow flexibility for updates and modifications. We are a Xilinx XPERT partner delivering solutions that range from optimizing a module in an FPGA design to a complete turnkey system. We also offer Xilinx-certified training in FPGA and advanced FPGA design.

to be custom designed in FPGAs. Xilinx XC4000XL FPGAs were chosen because of their flexibility and ease of debugging. Corrector) function for the 96bit-wide DRAM array. The EDAC is capable of correcting up to two four-bit errors in each 96-bit word.

### Conclusion

The typical development flow for a space design is to prototype the system using commercial grade parts and RAM-based FPGAs to allow low development cost, easy

debugging, and easy upgrading. The next step traditionally was to migrate to space grade parts and away from RAM-based FPGAs. The recent

TCPV Block Diagram

The functions were divided into three FPGAs on the board. An XC4036XL is used to implement the L2 cache and memory controller which also does sleep and clock speed control. Another XC4036XL is used to implement the peripheral bus controller incorporating system timers, interrupt controller, and DMA arbiter. The third FPGA is an XC4062XL which does the Reed-Solomon EDAC (Error Detector And availability of Xilinx QPRO<sup>™</sup> devices means that GLAST may be able to stay with RAM-based FPGAs for flight as well. This would allow unprecedented flexibility, allowing duringmission hardware updates and system failure workarounds. **£**

For more information on GLAST please see the Stanford GLAST website: http://glast.stanford.edu.

# Xilinx introduces-Nev High-Speed Download Cable

MultiLinx reduces download times by 10X over the older XChecker solution.

*by Frank Toth, Marketing Manager, Configuration Solutions, Xilinx, Frank.Toth@Xilinx.com*

ur new download cable, called MultiLINX<sup>™</sup>, features a high-speed USB input (or RS232 if you prefer) and a full set of interfaces for the SelectMAP (Virtex), Slave Serial, and IEEE JTAG Download Modes Using a USB cable (with an 8-Mbit per second throughput) the cable can download an XCV1000 in less than a second compared to more than 14 minutes using the older XChecker Cable.

MultiLINX supports all Xilinx FPGAs and CPLDs (Virtex, XC4000XL/XLA/XV, XC5000,

Spartan/XL, XC9500). It automatically switches to a wide range of interface voltages including TTL (5 volts), LVTTL (3.3 volts), LVCMOS (3 volts), JESD8-7 (2.5 volts normal and 2.5 volt wide), without the need for a separate external adapter. It's also compatible with 1.8-volt devices (with VCCIO set to 2.5 volts), and it accepts any voltage from 3.0 to 5.0 volts as a power supply input (from either a target application or external power supply).

> Download speeds are increased by 50% even when using the standard 25pin RS232 cable with the MultiLINX on-board bitstream compression.

MultjLI<u>NX</u>

MultiLINX offers both flexibility and highperformance to make downloading and

MultiLinx Download Cable

-dep

programmable logic easier and faster than ever.  ${f \Sigma}$

programming Xilinx

For more information see: http://www.xilinx.com/support /programr/cables.htm#Multilinx

# A New Family of In-System Programmable FLASH Serial/Parallel PROMs

Programming, storing, updating, and delivering bit streams for programmable logic has just become a lot easier.

*Eric Thacker, Marketing Manager, Xilinx, eric.thacker@xilinx.com*

> ilinx recently introduced a whole new family of JTAG in-system programmable, serial/parallel PROMs. The new XC1800 family uses the IEEE 1149.1 Boundary-Scan interface (commonly know as JTAG) and enables you to easily and cost-effectively configure an FPGA. The XC1800 family can easily interface to any Xilinx FPGA, including the Virtex and Spartan families, using a simple interface requiring only one user data pin. For the ultimate in download speed, these PROMs accommodate the 8-bit wide Select Map and Express modes that enable bit stream rates as fast as 500 Mbits per second.

| <b>Configuration Bits</b> |

|---------------------------|

| 4,194,304                 |

| 2,097,152                 |

| 1,048,576                 |

| 524,288                   |

| 262,144                   |

| 131,072                   |

|                           |

Table 1 - Product listing

### Flexible Bit Stream Reconfiguration

The XC1800 series makes it very easy to do power-on downloading and field updating of bit stream files. The power-on loading of the FPGA is enabled automatically, and if the configuration of the FPGA needs to be changed during operation (to remotely download hardware enhancements, debug configurations, or fix bugs, for example), the XC1800 series can be reprogrammed remotely using the JTAG port and then the bit stream is downloaded to the FPGA, without first powering down the FPGA. The FPGA can also be reconfigured directly from the JTAG port, without affecting the bit stream stored in the PROM.

### **Features:**

- Densities ranging from 128 Kbits to 4 Mbits.

- Endurance of 10,000 program/erase cycles.

- Fast programming and configuration speeds.

- Dual configuration modes.

- Serial Slow/Fast configuration (6 to 15 mHz).

- Parallel

- PROM controlled initiation of configuration without powering down FPGA.

- IEEE Std 1149.1 Boundary-Scan support.

- JTAG command initiation of standard FPGA configuration.

- Cascadable for storing longer or multiple bitstreams.

- I/O pins accept 5 V, 3.3 V, and 2.5 V.

- 3.3 V or 2.5 V output capability.

- Available in PC20, SO20, PC44, and VQ44 packages.

For more information see: http://www.xilinx.com/products/ configsolu.htm

# Simultaneous 4-channel, 12-bit A/D Conversion

Using Virtex FPGAs you can now process 600 Mbytes/s of data, a previously impossible task even with today's state-of-the-art DSP Processors.

*by Neil Harold, Design Engineer, Nallatech Ltd, n.harold@nallatech.com*

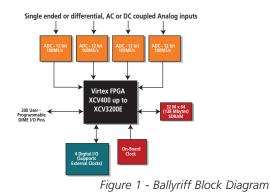

allatech Ltd. has created a very high performance analog-to-digital module that provides unrivalled data conversion abilities. The "Ballyriff" module, built using the company's DIME standard (DSP and Image processing Modules for Enhanced FPGAs), can incorporate a wide range of Virtex FPGAs from the XCV400 to XCV3200E parts, giving it maximum flexibility that is further enhanced by a wide variety of input options, as illustrated in Figure 1.

This A/D module has been meticulously planned to optimize the space available on the board, and so, Nallatech Ltd. has produced another DIME module with groundbreaking performance characteristics packed onto a few square inches.

The high-speed data conversion ability of the Ballyriff module comes from four of the very latest 12-bit, 100 Msps analog to digital converters. However, the benefits are not limited to data conversion, and include:

- Four digital input lines-for direct digital access to the Virtex FPGA, for external control and trigger functions.

- 128 Mbytes of SDRAM memory-more than any other DIME module.

- A variety of analog input options.

- A variety of clock sources-including external, on-board, and fed from DIME Motherboard

By using Nallatech's "Ballynuey" PCI Carrier Card, this module can be set up in minutes, and FPGA designs can be downloaded dynamically via the PCI bus directly, eliminating the need for PROMs or download cables.

### Conclusion

The Ballyriff DIME module gives you high levels of innovation with unsurpassed performance. Other DIME modules provide video capture and display, high-speed communications, and data capture functions. For more information on Ballyriff, or other DIME modules, contact Nallatech at: www.nallatech.com. **£**

# Spartan FPGAs Help Create Movie-quality Video on the PC

The Dazzle Digital Video Creator is designed around a low cost Spartan FPGA, and provides everything the PC user needs to record, edit, manage, and publish video.

by Kurt Wong, Product Manager, Xilinx, kwong@xilinx.com

azzle Multimedia designs, manufactures, and markets innovative and affordable MPEG digital video products for business and personal computer users. They turned to the Xilinx Spartan FPGA family for their latest groundbreaking product. "We looked very carefully at several different options, and Xilinx simply made the most sense in terms of gates, memory, reliability and price," said Sajid Sohail, Founder, and CEO for Dazzle Multimedia. "The Spartan FPGA was the optimum device for our design and made the process very easy for us. The design required several memory blocks that we implemented as a FIFO. The embedded distributed RAM blocks within the Xilinx device were much more efficient than any other product on the market."

Derived from the industry standard Xilinx XC4000 architecture, the 5-volt Spartan FPGA family combines unparalleled performance with low prices to provide the highest price performance ratio available in the industry. Fabricated on a leading edge silicon process, the Spartan family provides a full feature set including on-chip dual-port RAM, aggressive power management, densities ranging from 5,000 to 40,000 system gates, and small form factor packaging. The Spartan family is the first FPGA family that meets all the key requirements of ASIC designs for high volume production, and delivers unmatched benefits over competing PLDs.

"This product has been so well accepted by consumers, we can't seem to build them fast enough," said Sohail. "It is the first product of its kind at an affordable price." The Digital Video Creator is currently shipping at a high volume rate and retails for \$249. Dazzle chose to continue to utilize the Spartan FPGA throughout production. "There is certainly the advantage of quick time to market combined with the flexibility to modify our design. We found a bug in our software within the first six months of shipment - instead of a crisis, this was an easy fix. We simply fixed the problem and sent out our new software to everyone. This was a great win for us and for the FPGA."

Dazzle used Verilog, Exemplar, and the Xilinx Foundation Series software to create their design. "The Foundation Series software provided a ready-to-use solution combined with a powerful interface," said Sohail. This fully integrated design environment allows the user to access a complete set of design entry tools, and automates the creation of schematic and HDL symbols for inclusion within a design, making it easy to design complex circuits in minutes.

Dazzle Multimedia expects to continue its strong presence in the retail channel by introducing an array of new SpartanXL-based products later this year.  $\Sigma$

## **Success Story - Spartan**

# Infrared Digital Voice Module

Nextel, France, has created a better way for motorcyclists to communicate, by using digital infrared transceivers controlled by Xilinx Spartan FPGAs.

*by Christian Petiot, Technical Director Nextel France, nextel.france@wanadoo.fr*

alking to someone located just a few inches away from you may seem easy, but on a motorcycle it can be quite difficult and hazardous. Infrared IrDa devices are widely used in computers and mobile telephones, which makes them inexpensive. Digitizing voice is also a simple task, because there are many codecs available on the market. The problem is to design the interface between the half-duplex IrDa transceiver and the codec to make a fullduplex infrared voice transceiver. The logic design is quite complex.

Once the prototype breadboard had been set up, we had to find a way to reduce the size of the board so that it could be integrated into a helmet, we had to greatly reduce the power consumption using low voltage (3.3V) devices, and we obviously had to keep the price as low

as possible to address the consumer market. We found all our answers at Xilinx, thanks to the new Spartan FPGAs.

We selected the<br/>XCS05XL 5000-gate FPGA.<br/>With a sample from our local<br/>distributor, Compress, we made<br/>distributor, Compress, we made<br/>a new breadboard, but this time<br/>with very few components. For a fewFrench francs we got very powerful yet easy to<br/>use software from Xilinx (Foundation Series) to<br/>develop the FPGA, and after just two weeks the<br/>design was complete. Development time was

The Infrared Module

Once the prototype breadboard had been set up, we had to find a way to reduce the size of the board so that it could be integrated into a helmet, we had to greatly reduce the power consumption using low voltage (3.3V) devices, and we obviously had to keep the price as low as possible to address the consumer market. We found all our answers at Xilinx, thanks to the new Spartan FPGAs.

greatly reduced thanks to everyday support from the Compress application engineers.

The FPGA was used to generate the clocks for the codec, transform the NRZ signal from the codec to RZ signal for the infrared transceiver (and vice versa), and synchronize the incoming data. There were also enough gates left over to add features such as low battery audio alert and communication quality control.

### The Finished Product

The module is mounted in a hermetic box with an infrared transparent front. It is connected to the microphone and the speaker inside the helmet by a 4-wire cable. The box is tied to the helmet with an elastic strap. The box may be removed from the helmet in just a few seconds by removing the strap and disconnecting a small connector hidden in the helmet as shown in the pictures.

### Conclusion

Xilinx Spartan FPGAs are used in many unique applications. This Digital Infrared Voice Module is the smartest way to communicate on a motorbike; there is no interference at all, it is totally confidential, and it is inexpensive.  $\Sigma$

For more information e-mail Nextel at: nextel.france@wanadoo.fr

## **New Products - Software**

# Programming a Xilinx FPGA in "C"

Hardware designers are realizing they will need to use higher levels of abstraction to increase their productivity.

*by Doug Johnson, Business Development Manager, Frontier Design, doug\_johnson@frontierd.com; Marc Defossez, Field Applications Engineer, Xilinx, Inc. - BeNeLux, Belgium, marc.defossez@xilinx.com*

oday, many complex communications and digital signal processing (DSP) systems are described using ANSI C or C++ with floating-point mathematics. ANSI C or C++ is the language most commonly used by system engineers because it is powerful and popular, and a variety of environments are available for code development, compilation, and debugging. In addition, the simulation speed using C or C++ can be substantially faster than an equivalent design environment in Verilog or VHDL.

Typically, DSP functions modeled in C are algorithms that perform filtering, modulation, demodulation, compression, coding, and other operations on digital signals. However, most hardware designers are using a design methodology based on VHDL or Verilog HDL. System designers typically deliver a C language specification which has been simulated extensively with internal system-level simulators or commercial products like SPW (Cadence), COSSAP (Synopsys), or HP-ADS (HP EESOF). The hardware designer must then rewrite the specification at least once by hand in VHDL or Verilog and re-simulate the behavior. This manual re-write is difficult, time-consuming, and error prone. In addition, the floating-point C specification must be transformed into a fixedpoint implementation in hardware—a daunting task requiring extensive collaboration between the system and hardware engineers.

### Frontier Design's C to HDL Solution

The EDA software tools from Frontier Design bridge the gap between the system engineers, working on a design at a high level of abstraction, and the hardware engineer, tasked with the implementation of the design in hardware such as an FPGA or an ASIC. Frontier Design has embodied its 15 years of experience (in transforming DSP algorithms into working silicon) into a methodology that is called "Algorithm to Register Transfer," or A|RT.

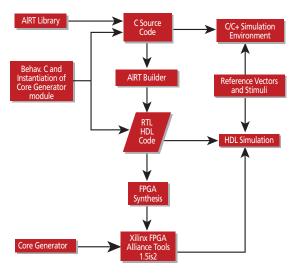

Two Frontier products incorporate the A|RT methodology: A|RT Library and A|RT Builder. A|RT Library extends ANSI C and C++ with fixedpoint data-types that allow bit-accurate modeling of arithmetic operations as well as modeling the overflow and quantization effects associated with finite precision operations. A|RT Builder supports automatic conversion from ANSI C to VHDL or Verilog. The tools thus enable architectural design in C. As a practical test of the tools, Xilinx - BeNeLux employed the A|RT methodology on three different test cases, one of which is covered here.

### Design Methodology Using A|RT

Xilinx - BeNeLux tested a "Coordinate Rotation on a Digital Computer," or CORDIC(1,2) algorithm supplied by Frontier Design using both A|RT Library and A|RT Builder. The algorithm is an iterative computing technique that is capable of evaluating mathematical functions like multiplication, square roots, and logarithms. The CORDIC algorithm is used extensively because its implementation in hardware utilizes shifts and adds only. A very important aspect of the test was to evaluate the tools to determine their applicability in implementing an algorithm based on C in a Xilinx FPGA, using HDL generated by the A|RT Builder product.

The design flow used for the evaluation is shown in Figure 1. A|RT Builder is the only C-to-HDL

Figure 1 - AIRT Design Flow

conversion tool that fully supports fixed-point algorithms. The tool employs a "What You Write Is What You Get" (WYWIWYG) paradigm. What WYWIWYG really means is that if you code in behavioral C, the output VHDL or Verilog will be behavioral. If you code in RTL C, you get RTL VHDL or Verilog. It is a supported subset of C that is utilized by A|RT Builder to generate the HDL code. Because some C constructs have no meaningful realization in hardware, there are ANSI C constructs that A|RT Builder does not support and for some constructs there are restrictions on the way they are supported. A|RT Builder automatically generates both C and HDL test benches so that the HDL and C simulations can be compared.

The A|RT software is available for both Unix and PC environments; Windows NT for the PC, HP-UX for Hewlett-Packard, and Solaris 2.6 for Sun platforms. The user interface is simple to use, and to ease the code development process, a cross-highlighting capability has been added to A|RT Builder. This feature allows you to highlight the generated HDL code by selecting the associated C code fragment.

Figure 2 shows the cross-highlighting built into the A|RT Builder user interface.

| AIRT Builder<br>roject Source | Edit Segrch                        | Options . | Beports Help           | A Build Options |                                                                                                                          |

|-------------------------------|------------------------------------|-----------|------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| oject: C:\WIND C              | WS\TEMP\co                         | rdic      |                        | - Build Options |                                                                                                                          |

| 🙆 🔂<br>Neн Dpen               | Inport                             | Save      | Editor Compile         | Language:       | VHDL -                                                                                                                   |

| els                           | ( xp = P_<br>e<br>( xp = P_        |           |                        | Work library:   | work Antimetic ib: Numeric_std                                                                                           |

| ste                           | r = 0;<br>te=LOOP;                 |           |                        | Entity.         | Configuration None -                                                                                                     |

| )                             | se = "dor                          | tcare"    | 1                      | Architecture:   | 🔽 Keep N-din arays                                                                                                       |

| case I                        | ak:<br>00P:                        | // exe    | cute one loop          |                 | Design: C:\WINDOWS\TEMP\cordic\aitb_hd\\design.vhd                                                                       |

| ×i_<br>×q_                    | inc = (xo<br>inc = (xi<br>ter:     |           |                        | - Clock -       | <pre>iter := iter + unsigned'("0001");     n6 := b2u(xi &lt; signed'("00000000000000");</pre>                            |

|                               |                                    | up_ang    | le_coeff[iter]         | , Nane:         | n5 := signed(cast(n6,31,0));<br>n3 := n5 xor n4;<br>different sim := n3 /= signed'("000000000000000000000000000000000000 |

|                               |                                    |           | P_FIX(0);<br>P_FIX(0); | € B             | <pre>different_sign := n3 /= signed'("000000000000000000000000000000000000</pre>                                         |

|                               | -                                  |           | i_sign_bit ^ x         | q C F.          | <pre>if (n1) then   state := unsigned'("10");</pre>                                                                      |

|                               | <pre>(differer<br/>x1 += x1_</pre> |           | ) {                    | Π 2             | <pre>end if;<br/>angle := lookup angle coeff(to integer( iter ));</pre>                                                  |

|                               | xq -= xq<br>xp += anç              |           |                        | 0 1             | if (different sign) then<br>xq := xq - xq inc;                                                                           |

|                               | lse {<br>×1 -= ×1_                 |           |                        | #Frames:        | xi := xi + xi_inc;<br>xp := xp + angle;                                                                                  |

|                               | xq += xq_<br>xp -= ang             |           |                        |                 | else<br>xq := xq + xq_inc;                                                                                               |

|                               | (iter>=P_                          |           | IONS) (                |                 | <pre>xi := xi - xi_inc;<br/>xp := xp - angle;<br/>end if;</pre>                                                          |

|                               |                                    |           |                        |                 | end II)<br>when "10" =><br>Phase nl := xp;                                                                               |

|                               |                                    |           |                        |                 | <pre>state := unsigned'("00"); when others =&gt;</pre>                                                                   |

|                               |                                    |           |                        | -               | Dimits                                                                                                                   |

|                               |                                    |           |                        | _               | URINES                                                                                                                   |

|                               |                                    | _         |                        |                 | Fto                                                                                                                      |

Figure 2 - AIRT Builder User Interface with Cross-highlighting

### The Evaluation

First, the CORDIC algorithm was designed and simulated in a C-based environment such as Visual C++ or GNU. Floating-point variables in the CORDIC algorithm were easily specified in fixed-point form by using the A|RT Library data type "Fix<w,p>", where "w" is the fixed word width and "p" is the fixed number of precision bits. For example, a variable with an 8-bit word length and 5 bits of precision is specified as follows: "Fix<8,5>".

Fixed-point values can also be specified as unsigned fixed-point, Ufix<w,p>, or as signed or unsigned integers, Int<w> and Uint<w>. In addition, several overflow and quantization characteristics can be applied to C variables to model the potentially adverse effects of finite precision arithmetic.

Once the desired response was achieved in C simulation, A|RT Builder was used to automatically convert the fixed-point CORDIC algorithm to Verilog or VHDL. For the evaluation, a number of different C coding "styles" were employed to optimize the data path length, to introduce pipelining, and to share resources and hierarchy in the generated VHDL and Verilog files.

Int<32> MultA; Int<32> MultB; MultA = InpA \* InpB; MultB = InpC \* InpD; OutP = MultA + MultB;

Figure 3 - No Resource Sharing In C Code

COMPUTE\_PROC: process( ..... begin InpA\_n1 := signed(InpA); InpB\_n1 := signed(InpB); InpC\_n1 := signed(InpC); InpD\_n1 := signed(InpD); OutP\_n2 := signed(OutP); MultA := InpA\_n1 \* InpB\_n1; MultB := InpC\_n1 \* InpD\_n1; OutP\_n2 := MultA + MultB; OutP\_n1 <= std\_logic\_vector(OutP\_n2); end process;

The examples in figures 3 and 4 illustrate two C coding styles: Figure 3 shows a nonresource shared operation coded in C and Figure 4 shows the corresponding VHDL code fragment generated by A|RT Builder to get a two multiplier, one clock-cycle, non resource shared implementation in VHDL.

```

static Uint<1> cycle = 0u;

static Int<32> MultA;

Int<32> MultB;

switch (cycle) {

case 0:

MultA = InpA * InpB;

break;

case 1:

Int<32> MultB = InpC * InpD;

OutP = MultA + MultB;

break;

}

++ cycle;

```

Figure 5 - Resource Sharing In C Code

begin

OutP\_n2 := "---- — copy state to local variables MultA := signed(MultA\_r); - compute new state and outputs InpA\_n1 := signed(InpA); InpB\_n1 := signed(InpB);  $InpC_n1 := signed(InpC);$ InpD\_n1 := signed(InpD);  $OutP_n2 := signed(OutP);$ cycle := unsigned'("0"); case cycle is when "0" => MultA := InpA\_n1 \* InpB\_n1; when "1" => MultB := InpC\_n1 \* InpD\_n1;  $OutP_n2 := MultA + MultB;$ when others => assert false report "Invalid (possibly unknown or dontcare) value for cycle" severity warning; end case; OutP\_n1 <= std\_logic\_vector(OutP\_n2);</pre> - copy local variables to next value for state MultA\_nxt <= std\_logic\_vector(MultA); end process; . . . . .

Figure 4 - No Resource Sharing in VHDL Code

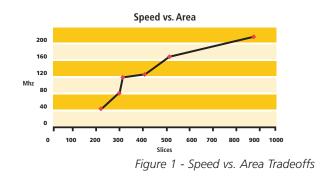

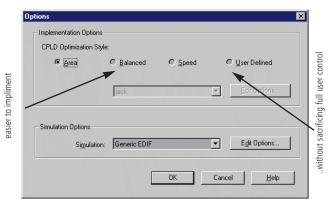

Figure 6 - Resource Sharing in VHDL Code