# Foundation Series 2.1i In-Depth Tutorials

Schematic-Based Designs

**HDL-Based Designs**

**Functional Simulation**

**Design Implementation**

**Timing Simulation**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

Xilinx Development System

# Preface

### About the In-Depth Tutorials

These tutorials give a description of the features and additions to Xilinx's newest product—Foundation 2.1i. The primary focus of this guide is to show the relationship between the design entry tools and the design implementation tools.

This guide should be used as the initial learning tool for designers who are unfamiliar with the features of the Foundation software.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                          |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/index.htm              |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                           |  |

| Resource       | Description/URL                                                                                                                                                                                                                                                           |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Book      | Pages from <i>The Programmable Logic Data Book</i> , which describe device-<br>specific information on Xilinx device characteristics, including<br>readback, boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                       |

| Tech Tips      | Latest news, design tips, and patch information on the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                       |

### **Quick Start Guide Contents**

This guide covers the following topics.

- **Chapter 1**, "Schematic-Based Design," explains many different facets of a schematic-based Foundation design flow using a design of a runner's stopwatch called "Watch". This chapter also shows how to use Foundation accessories such as the State Editor, Project Manager, LogiBLOX, and the HDL Editor.

- **Chapter 2**, "HDL-Based Design," guides you through a typical HDL-based design procedure using a design of a runner's stopwatch called "Watch".

- **Chapter 3**, "Functional Simulation," explains how to use the Logic Simulator to simulate a design before design implementation to verify that the logic that you have created is correct.

- **Chapter 4**, "Design Implementation," describes how to Translate, Map, Place, Route, (Fit for CPLDs) and generate a Bit file for designs.

- **Chapter 5**, "Timing Simulation," explains how to perform a timing simulation using the block and routing delay information from the routed design to give an accurate assessment of the behavior of the circuit under worst-case conditions.

# Conventions

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

### Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: -100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

Courier bold also indicates commands that you select from a menu.

$\texttt{File} \rightarrow \texttt{Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

edif2ngd [option\_name] design\_name

• Braces "{}" enclose a list of items from which you must choose one or more.

lowpwr ={on | off}

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on | off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2 ... locn;

### **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# Contents

#### Preface

| About the In-Depth Tutorials | i  |

|------------------------------|----|

| Additional Resources         | i  |

| Quick Start Guide Contents   | ii |

#### Conventions

| Typographical   | iii |

|-----------------|-----|

| Online Document | iv  |

#### Chapter 1 Schematic-Based Design

| Getting Started                        | 1-2  |

|----------------------------------------|------|

| Nomenclature                           | 1-2  |

| Required Software                      | 1-2  |

| Installing the Tutorial                | 1-2  |

| Tutorial Project Directories and Files |      |

| Starting the Project Manager           |      |

| Copying the Tutorial Files (Optional)  |      |

| Design Description                     |      |

| The Project Manager                    | 1-8  |

| Hierarchy Browser                      |      |

| Project Manager Functional Tabs        | 1-10 |

| Message Console Window                 |      |

| Design Entry                           | 1-10 |

| Starting the Schematic Editor          | 1-11 |

| Executing Commands                     |      |

| Hotkeys                                | 1-12 |

| Toolbar Buttons                        |      |

| Manipulating the Screen                | 1-13 |

| Creating a Schematic-Based Macro       | 1-14 |

|                                        |      |

| Creating the CNT60 Schematic                   |   |     |

|------------------------------------------------|---|-----|

| Opening the Schematic                          | 1 | -17 |

| Connectivity—Hierarchy Connectors              |   |     |

| Project Libraries                              |   |     |

| Adding Components to CNT60                     | 1 | -19 |

| Correcting Mistakes                            |   |     |

| Placing the Remaining Components               |   |     |

| Moving Hierarchy Terminals                     | 1 | -22 |

| Drawing Nets                                   | 1 | -22 |

| Adding Buses                                   | 1 | -23 |

| Adding Bus Taps                                | 1 | -25 |

| Saving the Schematic                           | 1 | -26 |

| Placing the CNT60 Macro                        | 1 | -26 |

| Creating a LogiBLOX Module                     | 1 | -28 |

| Creating a State Machine Module                | 1 | -30 |

| Opening the State Editor                       | 1 | -31 |

| Adding New States                              | 1 | -33 |

| Adding a Transition                            | 1 | -33 |

| Adding a State Action                          |   |     |

| Adding a State Machine Reset Condition         | 1 | -35 |

| Adding a Transition Condition                  | 1 | -36 |

| Creating the State Machine Macro               | 1 | -37 |

| Placing the STMACH symbol                      | 1 | -37 |

| Creating an HDL-Based Module                   |   |     |

| Using the HDL Design Wizard and HDL Editor     | 1 | -39 |

| Using the Language Assistant                   | 1 | -41 |

| Synthesizing the HDL Code and Creating a Macro | 1 | -43 |

| Adding the HEX2LED Component to the Schematic  | 1 | -43 |

| Specifying Device Inputs/Outputs               |   |     |

| Hierarchy Push/Pop                             |   |     |

| Adding Input Pins                              | 1 | -46 |

| Labeling Nets                                  |   |     |

| Assigning Pin Locations                        | 1 | -48 |

| Using Global Buffers                           | 1 | -50 |

| Completing the Schematic                       | 1 | -51 |

|                                                |   |     |

### Chapter 2 HDL-Based Design

| Getting Started                        |     |

|----------------------------------------|-----|

| Nomenclature                           |     |

| Required Software                      | 2-2 |

| Installing the Tutorial                | 2-2 |

| Tutorial Project Directories and Files | 2-3 |

| VHDL or Verilog?                                                |      |

|-----------------------------------------------------------------|------|

| Starting the Project Manager                                    | 2-4  |

| Copying the Tutorial Files (Optional)                           |      |

| Design Description                                              | 2-6  |

| The Project Manager                                             |      |

| Hierarchy Browser                                               |      |

| Project Manager Functional Tabs                                 | 2-9  |

| Message Console Window                                          | 2-10 |

| Design Entry                                                    |      |

| Adding Source Files                                             |      |

| Correcting HDL errors                                           |      |

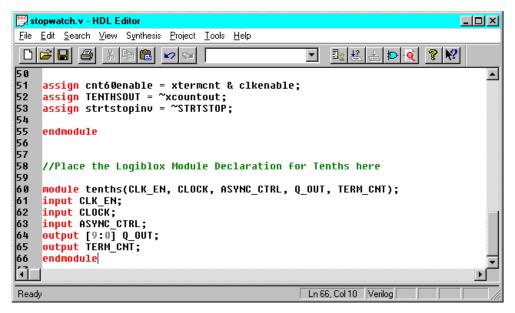

| Starting the HDL Editor                                         | 2-12 |

| Creating an HDL-Based Module                                    | 2-12 |

| Using the HDL Design Wizard and HDL Editor                      | 2-12 |

| Using the Language Assistant                                    | 2-15 |

| Creating a LogiBLOX Module                                      |      |

| Running the LogiBLOX Module Selector                            | 2-17 |

| Instantiating the LogiBLOX Module in the HDL Code               | 2-21 |

| Synthesizing the Design                                         |      |

| The Express Constraints Editor (Foundation Express Only)        | 2-27 |

| Using the Express Constraints Editor (Foundation Express Only). | 2-28 |

| Viewing Synthesis Results (Foundation Express Only)             | 2-32 |

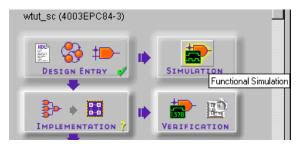

#### Chapter 3 Functional Simulation

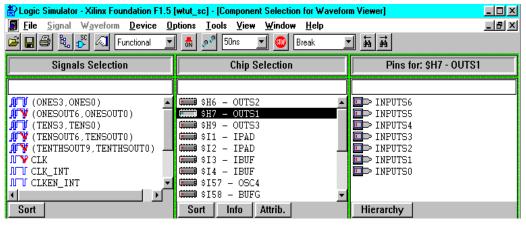

| Starting the Logic Simulator 3                        | 3-2  |

|-------------------------------------------------------|------|

| Performing Simulation                                 | 3-2  |

| Adding Signals 3                                      | 3-2  |

| Adding Signals Using Probes 3                         | 3-3  |

| Adding Signals Using the Component Selection Window 3 | 3-5  |

| Deleting a Signal                                     | 3-7  |

| Adding Stimulus                                       | 3-8  |

| Stimulating with the Internal Binary Counter          | 3-9  |

| Stimulating with Keyboard Stimulators                 | 3-10 |

| Stimulating with Custom Formulae                      | 3-10 |

| Other Sections of the Stimulator Selector             | 3-12 |

| Running the Simulation                                | 3-12 |

| Saving the Simulation                                 | 3-16 |

### Chapter 4 Design Implementation

| Project Management                       | 4-1  |

|------------------------------------------|------|

| Starting Implementation                  | 4-2  |

| Implementing the Schematic Design        | 4-2  |

| Implementing the HDL Design              | 4-3  |

| Implementation Options                   | 4-5  |

| Implementation Template                  | 4-6  |

| Control Files                            | 4-7  |

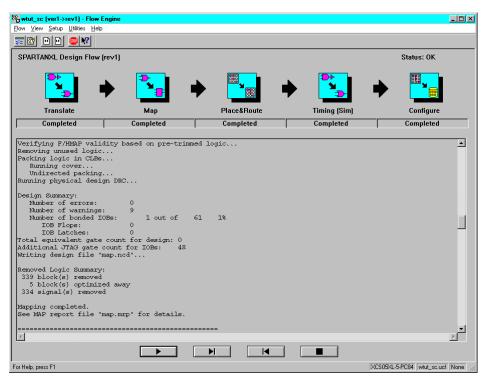

| Running Implementation — The Flow Engine | 4-8  |

| Viewing Implementation Results           | 4-9  |

| Other Implementation Tools               | 4-11 |

### Chapter 5 Timing Simulation

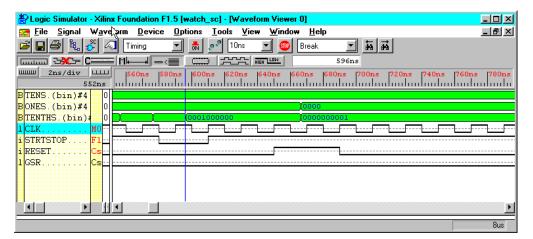

| Invoking Timing Simulation                              | 5-1  |

|---------------------------------------------------------|------|

| Simulating with Script Files                            | 5-2  |

| Creating Script Files — Script Wizard and Script Editor | 5-2  |

| Viewing the Script File with the Script Editor          | 5-10 |

| Running the Simulation from the Script Editor           | 5-11 |

| Viewing the Printed Output File                         | 5-13 |

| Closing the Simulator                                   | 5-13 |

# **Chapter 1**

# Schematic-Based Design

This chapter guides you through a typical FPGA schematic-based design procedure using a design of a runner's stopwatch called "Watch". The design example used in this tutorial demonstrates many device features, software features, and design flow practices that you can apply to your own design. The Watch design targets a SpartanXL device; however, all of the principles and flows taught are applicable to any Xilinx device family, unless otherwise noted.

For an example of how to design with CPLDs, see the online help by selecting  $\texttt{Help} \rightarrow \texttt{Foundation Help Contents}$  from the Project Manager. Under Tutorials, select CPLD Design Flows.

In the first part of the tutorial, you will use the Foundation design entry tools to complete the design. The design is composed of schematic elements, a state machine, a LogiBLOX component, and an HDL macro. After the design is successfully entered in the Schematic Editor, it is ready for functional simulation with the Foundation Logic Simulator, implementation with the Xilinx Implementation Tools, timing simulation.

**Note:** If you use Verilog or VHDL to create an HDL macro, then you must have Base Express or Foundation Express and a valid license.

This chapter includes the following sections.

- "Getting Started"

- "Design Description"

- "The Project Manager"

- "Design Entry"

# **Getting Started**

The following subsections describe the basic requirements for running the tutorial.

### Nomenclature

In this tutorial, the following terms are used:

- "Spartan family" includes the Spartan and SpartanXL devices.

- "Right-click" means click the right mouse button. Unless specified, all other mouse operations are performed with the left mouse button.

Throughout this tutorial, file names, project names, and directory names (paths) are specified in lower case, and the design is referred to as "Watch".

### **Required Software**

The Xilinx Foundation Series package, Version 2.1i, is required to perform this tutorial. The design requires that you install the SpartanXL libraries and device files, as well as the XABEL interface. These options are selected by default in the install program.

### Installing the Tutorial

This tutorial assumes that the software is installed in the default location c:fndtn active. If you have installed the software in a different location, substitute your installation path for c:fndtn active.

The tutorial projects are optionally installed (as sample projects) in the c:\fndtn\active\projects directory when you install the Foundation Series software. If you have installed the software, but are not sure whether the tutorial projects were installed, check for directories named c:\fndtn\active\projects\wtut\*. These directories contain the various tutorial files.

**Note:** For detailed instructions, refer to the *Foundation Series 2.1i Installation Guide and Release Notes.*

### **Tutorial Project Directories and Files**

During the software installation, the following schematic project directories are installed.

- c:\fndtn\active\projects\wtut\_sc (incomplete schematic tutorial)

- c:\fndtn\active\projects\watch\_sc (complete schematic tutorial)

The schematic tutorial files are copied into these directories.

The wtut\_sc project contains an incomplete copy of the tutorial design. You will create the remaining files when you perform the tutorial. As described in a later step, you can copy this project to another area and perform the tutorial in this new area if desired.

The watch\_sc solution project contains the design files for the completed tutorial, including schematics and the bitstream file. To conserve disk space, some intermediate files are not provided. Do not overwrite any files in the solutions directories.

### **Starting the Project Manager**

1. Double click the Foundation Series Project Manager icon on your desktop or select  $\texttt{Start} \rightarrow \texttt{Programs} \rightarrow \texttt{Xilinx}$  Foundation Series 2.1i $\rightarrow$  Project Manager from the Start menu.

2. A Getting Started dialog box displays, allowing you to select a project to open. If you have not opened this tutorial project before now, click the More Projects... button.

| Getting Started                               | ×             |

|-----------------------------------------------|---------------|

| © Open an Existing Project                    |               |

| wtut_sc  vtimer4e wtut_sc flash gate watch_sc | More projects |

| d:\fndtn15\active\projects\wtu                | it_sc         |

| C Create a <u>N</u> ew Project                |               |

| ☐ <u>A</u> lways open last project            |               |

| <u>Q</u> K <u>C</u> ancel                     | <u>H</u> elp  |

Figure 1-1 Getting Started Dialog Box

Browse to the c:\fndtn\active\projects directory in the Directories list (it should open to this location by default) and select the wtut\_sc project in the Projects list of the Open Project dialog box. Select Open to open the wtut\_sc project.

### **Copying the Tutorial Files (Optional)**

You can either work within the wtut\_sc directory as it has originally been installed, or you can make a copy to work on. Perform the following steps to make a working copy of the tutorial files. Whenever copying projects in Foundation, it is important to use the "Copy Project" feature in the Project Manager to ensure that the project's directory structure is kept intact.

- $1. \quad Select \, \texttt{File} \to \texttt{Copy Project}.$

- 2. Under the Destination section, type Mywatch (or a unique name of your choice) in the Name field.

- 3. Click OK.

- 4. Select File  $\rightarrow$  Open Project.

- 5. Scroll down in the project list and select Mywatch. Click Open.

- The Mywatch project may contain two UCF files. If this is the case, select the wtut\_sc.ucf file. Select Document → Remove or press Del to remove the file from the project. Click Yes to confirm the removal of the file.

This does not delete the file from disk. It only removes it from the project so that it is not used during compilation. The file still exists in the project directory on the disk. If you mistakenly remove a file from a project, select **Document**  $\rightarrow$  **Add** to add it back.

# **Design Description**

Throughout this tutorial, the design is referred to as Watch.

The design used in this tutorial is a hierarchical, schematic-based design, meaning that the top-level design file is a schematic sheet which refers to several other lower-level macros. The lower-level macros are a variety of different types of modules including schematic-based modules, LogiBLOX modules, state machine modules, and HDL modules.

The design begins as an unfinished design. Throughout the tutorial, you will complete the design by creating some of the modules, and by completing some others from existing files. After the design is complete, you will simulate it to verify the functionality.

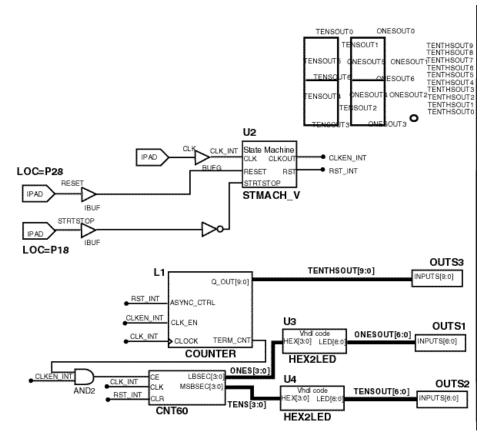

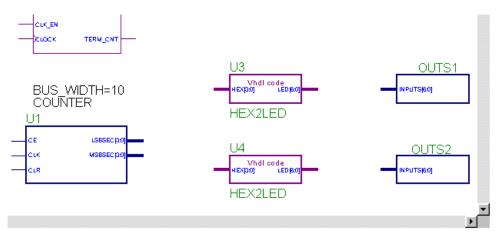

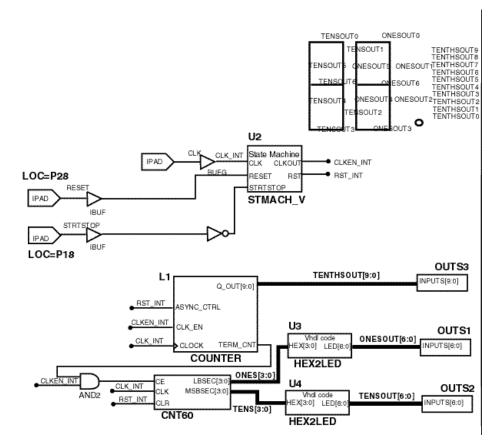

Watch is a simple runner's stopwatch. The completed schematic is shown in the following figure.

Figure 1-2 Completed Watch Schematic

There are three external inputs and three external outputs in the completed design. The following list summarizes the inputs and outputs and their functions.

#### Inputs:

- CLK—System clock for the Watch design.

- STRTSTOP—Starts and stops the stopwatch. This is an active-low signal which acts like the start/stop button on a runner's stopwatch.

- RESET—Resets the stopwatch to 00.0 after it has been stopped.

#### **Outputs**:

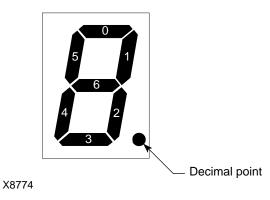

- TENSOUT[6:0]—7-bit bus which represents the Tens digit of the stopwatch value. This bus is in 7-segment display format to be viewable on the 7-segment LED display on the Xilinx demonstration board.

- ONESOUT[6:0]—similar to TENSOUT bus above, but represents the Ones digit of the stopwatch value.

- TENTHSOUT[9:0]—10-bit bus which represents the Tenths digit of the stopwatch value. This bus is one-hot encoded.

The completed design consists of the following functional blocks. Most of these blocks do not appear yet on the schematic sheet in the tutorial project since they will be created during this tutorial.

#### **Functional Blocks**

• STMACH\_A or STMACH\_V

State Machine macro. This module uses the Foundation State Editor to enter and implement the state machine. One is an ABEL version; the other is a VHDL version.

• CNT60

Schematic-based module which counts from 0 to 59, decimal. This macro has two 4-bit outputs, which represent the 'ones' and 'tens' digits of the decimal values, respectively.

• TENTHS

LogiBLOX 10-bit, one-hot encoded counter. This macro outputs the 'tenths' digit of the watch value as a 10-bit one-hot encoded value.

HEX2LED

HDL-based macro. This macro decodes the ones and tens digit values from hexadecimal to 7-segment display format to view on the FPGA Demonstration Board.

• OUTS1, OUTS2, OUTS3

Schematic-based macros which define the external output pin assignments for TENSOUT, ONESOUT, and TENTHSOUT output buses.

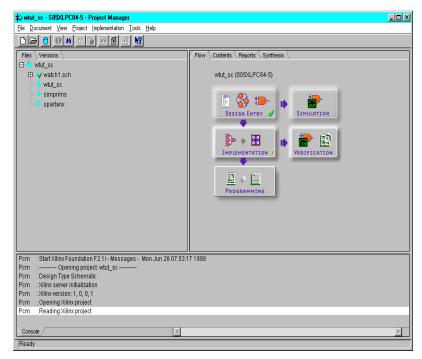

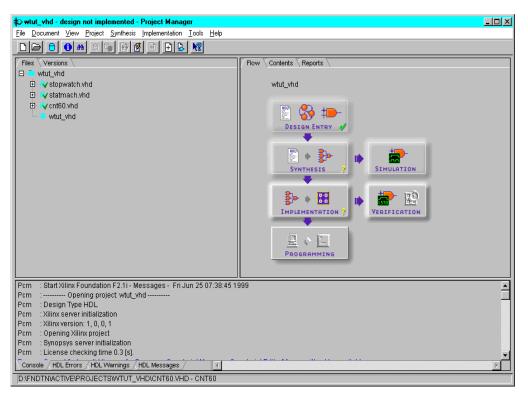

### The Project Manager

The Project Manager controls all aspects of the design flow. You can access all of the various design entry and design implementation tools as well as the files and documents associated with your project. The Project Manager also maintains revision control over multiple design iterations.

The Project Manager is divided into three main subwindows. To the left is the Design Hierarchy Browser which displays the project elements. To the right is a set of tabs, each one opens a separate functional window. The third window at the bottom of the Project Manager is the Message Console and shows status messages, errors, and warnings, and is updated during all project actions. These windows are discussed in more detail in the following sections.

Figure 1-3 Project Manager

### **Hierarchy Browser**

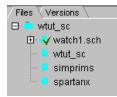

The Hierarchy Browser displays the project source files in a hierarchical tree. Within this display, you can quickly navigate to any point in your design.

In the Files tab of the Hierarchy Browser, the design source files and libraries are displayed. Next to each filename, an icon tells you the file type (schematic, HDL file, state machine, library, text file). If a file contains lower levels of hierarchy, the icon has a "+" in the lower right corner. You can expand the tree by clicking this icon. You can open a file to edit by simply double-clicking the filename in the browser.

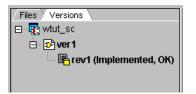

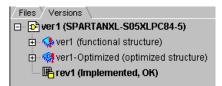

A Versions tab is also available behind the Files tab. This tab displays a design's implementation revisions. Because this is a new design which has not yet been implemented, the Versions tab does not yet contain any revision information. Versions are discussed in more detail later in the tutorial during design implementation.

### **Project Manager Functional Tabs**

As mentioned previously, the right-hand side of the Project Manager contains a series of functional tabs. Briefly, the functions of these tabs follow.

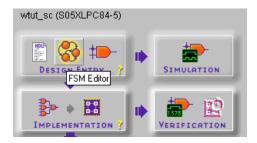

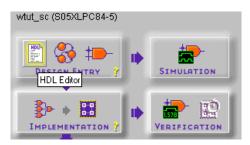

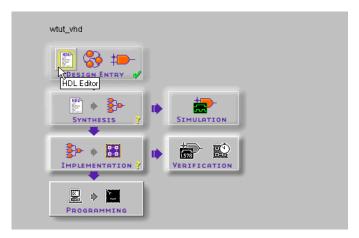

- Flow—Provides access to tools you use to complete your entire design, arranged in a flow-chart style to guide you through the design flow. Status indicators in the lower right corner of each phase button indicate whether the step has been completed successfully.

- Contents—Lists contents and date the file selected in the Hierarchy Browser was last modified.

- Reports—Displays design flow reports.

- Synthesis—Displays all of the HDL macros contained in the project, and, from this tab, you can update these macros.

You have the option to browse through these tabs to see how the tabs are updated during the design flow process.

### Message Console Window

Errors, warnings, and informational messages are displayed in the Message Window. Errors are displayed in red, warnings in blue, and informational messages in black.

# **Design Entry**

In this hierarchical design, you will create various types of macros, including schematic-based macros, HDL-based macros, state machine macros, and LogiBLOX macros. You will learn the process for creating each of these types of macros, and then you will connect them all together to create the completed Watch design. This tutorial gives you experience with creating and using each type of design macro so that you can apply this knowledge to your own design.

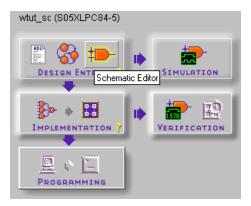

### **Starting the Schematic Editor**

There are two different ways to open the Schematic Capture tool.

• From the Flow tab, click the Schematic Capture icon in the Design Entry phase button. This instructs the Schematic Editor to open the project's top level schematic sheet.

• Double click the file name WATCH.SCH in the Files tab.

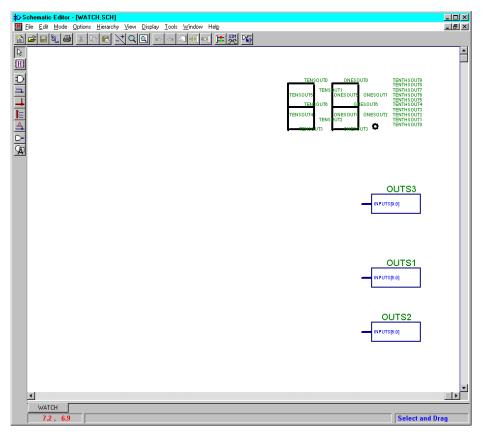

The Schematic Editor opens with the Watch schematic sheet loaded. The Watch schematic is incomplete at this point. Throughout the tutorial, you create the components to complete the design. The unfinished design is shown in the figure below.

#### Figure 1-4 Incomplete Watch Schematic

If you need to stop the tutorial at any time, save your work by selecting  $\texttt{File} \rightarrow \texttt{Save}$  from the pulldown menus.

### **Executing Commands**

There are three ways to execute commands within the Foundation tools: pulldown menus, hotkeys, and toolbar buttons. In most cases, this tutorial instructs you to use the pulldown menus.

#### Hotkeys

You can use the keyboard to execute various commands. These "hotkeys" are listed next to the commands within the pulldown menus. Some of the hotkeys are the function keys, some are single letters, and some require the Ctrl or Alt keys. You cannot customize them.

#### **Toolbar Buttons**

There are also toolbars that are located beneath the pulldown menus and to the left of the main Schematic Editor window. Hold your mouse over the buttons to see their function.

Figure 1-5 Schematic Editor

### **Manipulating the Screen**

Under the Display pulldown menu is a series of commands that modify the viewing area of the Schematic Editor window. Zoom in the schematic to comfortably view it.

#### **Creating a Schematic-Based Macro**

A schematic-based macro consists of a symbol and an underlying schematic. You can create either the underlying schematic or the symbol first, and the tools can automatically generate the corresponding symbol or schematic file, respectively. In the following steps, you create a schematic-based macro by first creating the symbol using the Symbol Wizard. A template schematic file is then created by the tools, and you complete the schematic with the appropriate logic. The created macro is then automatically added to the project's library.

The macro you will create is called CNT60. CNT60 is a binary counter with two 4-bit outputs, which represent the Ones and Tens values of the stopwatch. The counter counts from 0 to 59, decimal.

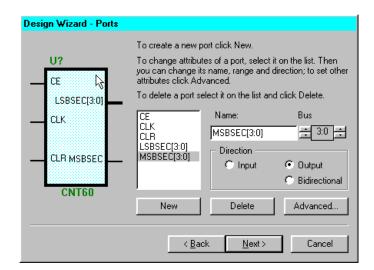

1. Select  $\texttt{Tools} \rightarrow \texttt{Symbol Wizard}$ . The Design Wizard opens.

The Design Wizard guides you through the process of creating a macro symbol. It also creates a "skeleton" file based on the pins you define and the type of macro (schematic, ABEL, VHDL, or state machine). The State Editor and the HDL Editor (described later in this tutorial) also use the Design Wizard.

- 2. Click Next.

- 3. In the Symbol Name field, type **CNT60**. In the Contents section, select **Schematic**. This tells the tool that the underlying file for the symbol is a schematic.

| Design Wizard - Conte                                                                                                | Shoose the name of the symbol you crea                                                                                                                | ite. Then select                              |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| -                                                                                                                    | how symbol's contents will be described.<br>In case of State Diagram and HDL Code<br>choose the language used for description<br>Symbol Name<br>CNT60 |                                               |

| pogen 18.1.5 (rock))<br>11 francisch - mar - Middatata<br>11 francisch - Middatata<br>min - Brygg - Midda<br>Ryggese | Contents<br>CEmpty CState Diagram<br>CSchematic CHDL Code                                                                                             | HDL Language<br>C VHDL<br>C ABEL<br>C Verilog |

|                                                                                                                      | < <u>B</u> ack <u>N</u> ext >                                                                                                                         | Cancel                                        |

Figure 1-6 Symbol Wizard - Contents Page

- 4. Click Next.

- 5. Click **New** to create a new pin. In the **Name** field, type **CE**. Check that the direction of the pin is set to **Input**.

- 6. Repeat Step 5 for input pins CLK and CLR.

- 7. Repeat Step 5 for output bus pins LSBSEC[3:0] and MSBSEC[3:0]. To create a bus pin, type the name of the bus in the Name field (that is, LSBSEC), and then use the up/down arrows in the Bus field to set the bounds of the bus (that is, 3:0). Check that the Direction of the pin is set to Output.

Figure 1-7 Symbol Wizard - Ports Page

8. Click Next.

**Note:** In the Comments section, you can type text that appears on the symbol when it is placed. You can also define a longer comment that only appears in the SC Symbols window when you place components.

9. Click Next and then click Finish.

The symbol is created and placed in the project library and can be accessed from the SC Symbols toolbox. The Symbol Wizard automatically creates and opens a schematic sheet with I/O terminals corresponding to the defined symbol pins.

**Note:** If the schematic is not automatically created, the most likely cause is that Empty was selected in step 4. Repeat steps 1-9, and click **Yes** or **OK** when prompted to overwrite the existing symbol.

### **Creating the CNT60 Schematic**

You have now created the symbol for CNT60 with the help of the Symbol Wizard. The next step is to create the underlying corresponding schematic for this macro. You can then reference this macro symbol by placing it on a schematic sheet.

#### **Opening the Schematic**

- 1. If the CNT60 schematic is not open, select  $\texttt{File} \rightarrow \texttt{Open}$ . The Open Sheet dialog box opens. Click **Browse**, select cnt60.sch from the files list, then click OK.

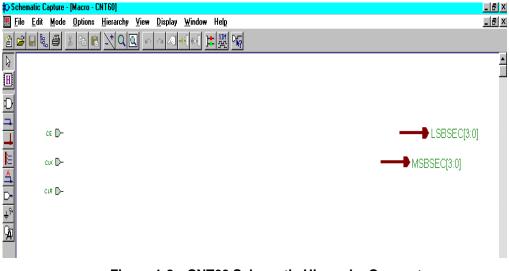

- 2. Zoom in or out until all of the Hierarchy Connectors are clearly visible. The hierarchy connectors represent connections between this schematic sheet and the pins of the corresponding symbol.

Figure 1-8 CNT60 Schematic Hierarchy Connectors

#### **Connectivity—Hierarchy Connectors**

Hierarchy Connectors logically connect the CNT60 symbol and its underlying schematic. The name of each pin on the symbol must have a corresponding connector in the underlying schematic. The Symbol Wizard automatically places hierarchy connectors on the schematic. If you need to add hierarchy connectors manually, you can use the Hierarchy Connector icon in the vertical toolbar.

When you save a macro, the Schematic Editor checks the hierarchy connectors against the corresponding symbol. If there is a discrepancy, you can let the software update the symbol automatically, or you can modify the symbol manually. Hierarchy connectors should *only* be used to connect signals between levels of hierarchy. Never use hierarchy connectors on top-level schematic sheets.

#### **Project Libraries**

When you create a new project in Foundation, three libraries are automatically added to the project: the appropriate device family library based on the target family you have chosen (for example, SpartanXL), the project library (with the same name as the project), and the SIMPRIMS library (for simulation). All libraries which are part of the project are listed in the Files tab of the Project Manager. You can double click on any of these libraries to see the contents of the library.

Figure 1-9 Project Libraries

The device family library (SpartanXL for this project) contains all of the Xilinx Unified Library components for the given family. A complete description of all of these components can be found in the Xilinx *Libraries Guide*.

The project library (WTUT\_SC for this project) is a writable library containing user-created macros. Any macro you create in this project is automatically placed in this library.

Additionally, you can copy macros from other libraries into this project library and vice versa using the Schematic Symbols Library Manager which you can open with the **Tools**  $\rightarrow$  **Utilities** menu in the Project Manager.

To facilitate simulation with the Foundation Logic Simulator, the SIMPRIMS is added to the project. This library contains the simulation models for the Xilinx devices.

You can add more libraries to the project by choosing File  $\rightarrow$  **Project Libraries** from the Project Manager. After you add a library to the project, you can use any component from that library in the current project.

#### Adding Components to CNT60

Components from all of the libraries (except SIMPRIMS) for the given project are available from the SC Symbols toolbox to place on the schematic. The available components listed in this toolbox are arranged alphabetically within each library.

From the menu bar, select Mode → Symbols or click the Symbols Toolbox button in the vertical toolbar on the left side of the Schematic Editor.

This opens the SC Symbols window and displays the libraries and their corresponding components.

| SC Symbols   | ĺ |

|--------------|---|

| D- 📲 👯 🛤 🔁   | l |

| (-) SPARTANX | l |

| ACC16        | l |

| ACC4         | l |

| ACC8         | l |

| ADD16        | l |

| ADD4         | l |

| ADD8         | l |

| ADSU16       | l |

| ADSU4        | l |

| ADSU8        | l |

| AND2         | l |

| AND2B1       | l |

| AND2B2       | l |

| AND3         | l |

| AND3B1       | l |

| AND3B2       | l |

| AND3B3       | l |

| AND4         | l |

| AND4B1       | l |

|              |   |

|              |   |

|              |   |

|              |   |

|              |   |

#### Figure 1-10 SC Symbols Toolbox

2. The first component you will place is an AND2, a 2-input AND gate. You can select this component by either scrolling down the list and selecting it or by typing **AND2** in the bottom of the SC Symbols Window. Then move the mouse back into the schematic window.

In the SC Symbols window, when the AND2 component is selected, a description of the component appears in the bottom of the window.

3. Move the symbol outline to the location shown in the following figure and click the left mouse button to place the object.

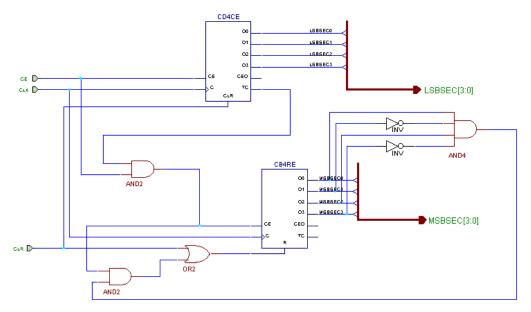

#### Figure 1-11 Completed CNT60 Schematic

**Note:** The preceding schematic illustrates the completed CNT schematic. Use this figure as a reference for drawing nets and buses in the following subsections.

#### **Correcting Mistakes**

If you make a mistake when placing a component, you can easily move or delete the component.

- 1. Press the Esc key on the keyboard to exit the Symbols Mode.

- 2. Select the component you want to move or delete. Make sure that no other components are selected (clicking on a blank area of the schematic deselects everything).

- 3. Click and drag to correctly place the component, or press the **Del** key on the keyboard or the Cut icon in the toolbar to delete the component.

#### **Placing the Remaining Components**

Follow the steps listed previously in the "Adding Components to CNT60" section to place the CD4CE, OR2, CB4RE, INV, and AND4 components on the schematic sheet as shown in the "Completed CNT60 Schematic" figure. For a detailed description of the functionality of each of these components, refer to the Xilinx *Libraries Guide*.

#### **Moving Hierarchy Terminals**

To make the schematic easier to draw and clearer to read, move some of the hierarchy connectors which were automatically created by the Symbol Wizard. Follow these steps to relocate the hierarchy connectors as shown in the "Completed CNT60 Schematic" figure.

- With the mouse cursor in point/select mode, select the CLR hierarchy connector, and drag it to the lower left area of the schematic sheet. If the mouse cursor is not in point/select mode, Press the Esc key on the keyboard to get into this mode.

- 2. To move the bus hierarchy terminal MSBSEC[3:0], select and drag an area surrounding the entire bus hierarchy terminal and label it, so that both the bus and the label are highlighted in red. With the bus and label highlighted, click on the terminal again, and drag the entire unit down to the lower right area of the schematic sheet. Release the mouse to place the terminal, and then click anywhere else on the schematic sheet to deselect the bus and label.

#### **Drawing Nets**

You use the Draw Wires icon in the vertical toolbar to draw wires (also called nets) between the various components on the schematic. Use Nets to physically connect single bits together.

Signals can also logically be connected by naming multiple segments identically. In this case, the nets do not need to be physically connected on the schematic to make the logical connection. In the CNT60 schematic, you will draw nets to connect the components together. Do not yet worry about drawing the nets for the LSBSEC and MSBSEC buses. These nets will be drawn in the next section.

Follow these steps to draw a net between the AND2 and the CB4RE components on the CNT60 schematic.

1. Click the Draw Wires icon in the vertical toolbar.

2. Click the source symbol pin (output pin of the AND2), then click on the destination pin (CE pin on the CB4RE). The net will automatically be drawn between the two pins.

**Note:** You can specify the shape of the net by moving the mouse in the direction you want to draw the net and then single-clicking to create a 90-degree bend in the wire.

Draw the nets to connect the remaining components as shown in the "Completed CNT60 Schematic" figure. To draw a net between an already existing net and a pin, click once on the component pin and once on the existing net. A junction point will be drawn on the existing net.

You should now have all the nets drawn except those connected to the LSBSEC and MSBSEC buses. You will draw these in the next section.

#### **Adding Buses**

Sometimes it is convenient to draw a set of signals as a bus rather than as several separate wires. You have the option to group signals in the form of a bus and "tap" this bus off to use each signal individually. In this CNT60 schematic, you will create two buses, each comprised of the 4 output bits of each counter. These buses will be named LSBSEC[3:0] and MSBSEC[3:0], and they will also be connected to hierarchy connectors to connect them to the CNT60 symbol.

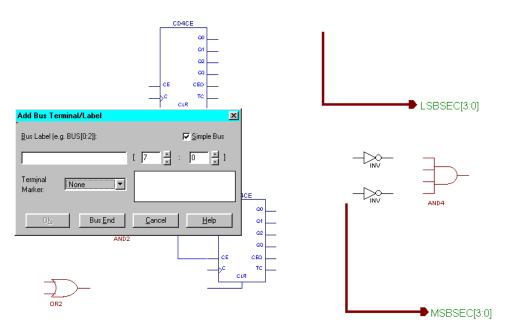

Add buses to the schematic as follows.

1. Select  $Mode \rightarrow Draw Buses$  or click the Draw Buses button in the vertical toolbar to get into the Draw Buses mode.

2. The CNT60 schematic has some bus "stubs" connected to Hierarchy Connectors which represent the symbol pins on the CNT60 macro symbol as defined with the Symbol Wizard. Click the end of the LSBSEC[3:0] stub, then move the mouse to a new position. Click to make a corner in the bus.

- 3. Terminate the bus by either double clicking with the left mouse button, or single-clicking with the right mouse button. This opens the Add Bus Terminal/Label dialog box where you can define the bus name, width, and the type of terminal you want to use.

- 4. In the Add Bus Terminal/Label dialog box, change the Terminal Marker type to None by choosing this selection from the pulldown menu. This sets the type of terminal for the point where you are terminating the bus. Do not change any of the other settings. Click Bus End (the bus name and width were defined with the Symbol Wizard, so it is unnecessary to redo this here).

#### Figure 1-12 Creating Bus Ends

- 5. Repeat Steps 2 through 4 for the MSBSEC[3:0] bus.

- 6. If you make a mistake, press the **Esc** key on the keyboard to exit the Draw Buses mode. Then click the bus you want to delete so that it is highlighted. Press **Del** to remove the bus.

7. After adding the two buses, press **Esc** or right-click to exit the Draw Buses mode.

#### **Adding Bus Taps**

Next, you add nets to attach the appropriate pins from the CB4RE and CD4CE counters to the buses. Use Bus Taps to tap off a single bit of a bus and connect it to another component. The Schematic Capture tool can automatically name the bus taps incrementally as they are drawn.

You have the option to enlarge the view of the schematic to make it easier to draw the nets.

1. Select Mode → Draw Bus Taps or click the Draw Bus Taps button in the vertical toolbar. The cursor changes, indicating that you are now in Draw Bus Taps mode.

2. Click the LSBSEC[3:0] bus label.

The status bar at the bottom of the window displays the message Expand Bus Tap: LSBSEC3. This tells you that the next bus tap drawn will be labeled LSBSEC3.

**Note:** The default is to start at 3 and decrement as bus taps are drawn. You can use the up and down arrow keys to change which bus bit will be tapped first.

- 3. Click the Q3 output pin of the CD4CE component to draw the bus tap. The net is automatically drawn and labeled. The status bar now reads Expand Bus Tap: LSBSEC2.

- 4. Click next on each of the other output pins of the CD4CE component. The bus taps will be drawn and labeled incrementally.

**Note:** If the bits are not automatically being labeled incrementally, check that you clicked the bus name (label) before clicking the counter output pins.

**Note:** If the nets appear disconnected, try selecting  $\mathtt{Display} \to \mathtt{Redraw}$  to refresh the screen.

If there is an error with the labeling of the bus taps, double click the bus tap net to edit the label.

- 5. Repeat Steps 1 through 4 for the MSBSEC[3:0] bus.

- 6. Press Esc twice or right-click to exit the Draw Bus Taps mode.

- 7. Complete the schematic by drawing the nets to connect the MSBSEC bus taps to the INV and AND4 components. If necessary, refer to the "Drawing Nets" section for guidance.

- 8. Compare your CNT60 schematic again with the "Completed CNT60 Schematic" figure to ensure that all connections are properly made.

#### Saving the Schematic

The CNT60 schematic is now complete.

Save the schematic by selecting  $\texttt{File} \rightarrow \texttt{Save}$  or clicking the Save icon in the horizontal toolbar.

All errors, warnings, and informational messages are displayed in the Message Window in the Project Manager. If any errors are issued, resolve them and save the schematic again.

#### Placing the CNT60 Macro

So far, you have created the CNT60 macro. The next step is to place this macro on the top-level Watch schematic sheet, where it may then be connected to other components in the design.

- 1. Open the Watch schematic sheet. If the Watch schematic is already open, you will see a tab at the bottom of the Schematic Capture tool where you can select that sheet.

- 2. If the Watch schematic is not open, select File  $\rightarrow$  Open, select the Watch sheet, and click OK.

- 3. Open the SC Symbols Toolbox to display a list of all the available design components. As mentioned before, you can select the Symbols Toolbox icon to open the SC Symbols Toolbox.

- 4. Near the bottom of the SC Symbols Toolbox, there is a header with the name of the project representing the current project library. Beneath this, find the newly created CNT60 macro in this list. Select this component.

- 5. Place the CNT60 macro as shown below.

Figure 1-13 Placing the CNT60 Macro

6. Press **Esc** to exit the Symbols mode. The cursor now returns to the standard "point and select" mode.

Notice that the SC Symbols window remains open. With this window open, you can quickly place additional symbols without having to click on the Symbols Toolbox icon again. If you want to close the SC Symbols window, click the '-' button in the upper left corner of the window.

7. Do not yet worry about connecting nets to the pins of the CNT60 symbol. You will do this later in the tutorial after you add the other components to the Watch schematic.

# Creating a LogiBLOX Module

LogiBLOX is a graphical interactive design tool that you use to create high-level modules such as counters, shift registers, RAM, and multiplexers. You can customize and pre-optimize the modules to take advantage of the inherent architectural features of the Xilinx FPGA architectures, such as Fast Carry Logic for arithmetic functions and on-chip RAM for dual-port and synchronous RAM.

In this design, you create a LogiBLOX module called Tenths. Tenths is a 10-bit one-hot encoded counter. It counts the tenths digit of the stopwatch's time value. To better see the digit when it is downloaded on the FPGA Demonstration Board, the encoding is set to one-hot. The series of LED lights displays the Tenths digit, where one light is on for each count of the tenths digit.

You use the LogiBLOX Module Selector GUI to select the type of module you want to create, as well as the specific features of the module. You may invoke this GUI from either the Project Manager, the Schematic Editor, or the HDL Editor. The operation of the tool is the same regardless of where you invoke it.

- 1. From within the Schematic Editor, select **Tools**  $\rightarrow$  **LogiBLOX**.

- 2. Fill in the Logiblox Module Selector with the following settings:

- Module Name: Tenths

Defines the name of the module.

• Module Type: Counters

Defines the type of module.

• Bus Width: 10

Defines the width of the data bus. You either choose from the pulldown menu, or type in a value.

• Operation: Up

Defines how the counter will operate. This field is dependent on the type of module selected.

• Style: Maximum Speed

Defines the type of optimization strategy for the module. This dictates how the layout of the module is defined. • Encoding: One Hot

Defines the register encoding for the module.

• Async Val: 000000001

Defines the value of the module on power-up and reset.

3. "Check" or "uncheck" the appropriate boxes on the module diagram so that *only* the following pins are used.

Q\_OUT, Clock Enable, Async Control, Terminal Count

| 🙀 LogiBLOX Module Sele                                           | ctor                     |                            | <u> </u>           |

|------------------------------------------------------------------|--------------------------|----------------------------|--------------------|

| Selection<br>Module <u>N</u> ame:<br>TENTHS                      | Module Type:<br>Counters | Bus <u>₩</u> idth:<br>10 ▼ | OK<br>Cancel       |

| Details                                                          |                          |                            | Set <u>u</u> p     |

| D_IN<br>Async. Control<br>Sync. Control<br>Clock Enable<br>Clock |                          | unt                        | User Prefs<br>Help |

| <u>Operation</u> =                                               | Up 💌                     |                            |                    |

| <u>S</u> tyle =                                                  | Maximum Speed 💌          |                            |                    |

| <u>E</u> ncoding =                                               | One Hot 💌                |                            |                    |

| Count Limit =                                                    |                          |                            |                    |

| <u>A</u> sync. Val =                                             | 0000000001               |                            |                    |

| Sync. ⊻al =                                                      |                          |                            |                    |

| Async. Count =                                                   |                          |                            |                    |

| Sync. <u>C</u> ount =                                            |                          |                            |                    |

Figure 1-14 LogiBLOX Module Selector

4. Click **OK**. The module is created and automatically added to the project library. Additionally, it will be automatically attached to the cursor to immediately place on the schematic.

**Note:** If you do not want to place the symbol at this time, you can press the **Esc** key on the keyboard to get out of the Place Symbol mode. You can then select it at any time from the SC Symbols Toolbox to place on the schematic.

5. Place the newly created Tenths component on the Watch schematic sheet, as shown below. You will connect this symbol to the rest of the schematic later in the tutorial. The symbol is labeled "L1" on the schematic sheet.

#### Figure 1-15 Placing the Logiblox TENTHS component

6. Save the schematic by selecting  $File \rightarrow Save$ . Close the Schematic Editor.

# **Creating a State Machine Module**

With the Foundation State Editor, you graphically create finite state machines. You draw states, inputs/outputs, and state transition conditions on the diagram using a simple windows GUI. Transition conditions and state actions are typed into the diagram in appropriate VHDL, Verilog, or ABEL syntax. The State Editor then synthesizes the diagram into either VHDL, Verilog or ABEL code. The resulting HDL file is finally synthesized to create a netlist and/or macro for you to place on a schematic sheet.

For this tutorial, a partially complete state machine diagram is provided. In the next section, you complete the diagram and synthesize the module into a macro to place on the Watch schematic. Both a VHDL and an ABEL version of the State Machine diagram have been provided for you.

If you have a Foundation Express package, you can use either the VHDL or ABEL version. If you have a Foundation Standard or a Foundation Base package, then you must use the ABEL version of the diagram.

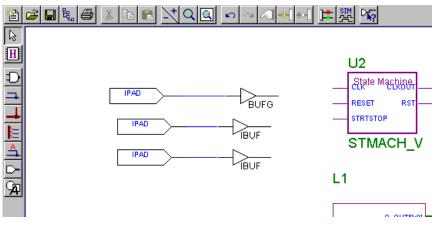

## **Opening the State Editor**

To invoke the State Editor, click the State Editor button in the Flow tab of the Project Manager.

A dialog box prompts you to select a document. Click Existing Document, click OK, and then select STMACH\_V.ASF (VHDL) or STMACH\_A.ASF (ABEL) to open the partially completed stopwatch state machine.

The unfinished State Machine diagram is shown below.

Figure 1-16 Incomplete State Machine Diagram

- The circles represent the various states.

- The purple underlined expressions are the transition conditions, defining how you move between states.

- The boxes containing expressions attached to each state are output actions for each state, defining how the outputs behave in each state.

In the State Machine diagrams, the transition conditions and the state actions are written in proper HDL syntax, either VHDL or ABEL.

In the following section, you add the remaining states, transitions, actions, and also a reset condition to complete the state machine.

#### **Adding New States**

Complete the state machine by adding a new state called CLEAR.

1. Click the State icon in the vertical toolbar.

The state bubble is now attached to the cursor.

- 2. Place the new state on the left-hand side of the diagram as shown below. Click the mouse to place the state bubble.

- 3. The state is given a default name, in this case S1. Double click the S1 in the state bubble, and change the name of the state by typing **CLEAR**. The name of the state is for your use only; it does not affect the synthesis, and so you can name it whatever you want.

Figure 1-17 Adding the CLEAR State

You can change the shape of the state bubble by clicking the bubble and dragging in the direction to "stretch" the bubble.

## **Adding a Transition**

A transition defines the movement between states of the state machine. Transitions are represented by arrows in the State Editor. You will be adding a transition from the CLEAR state to the ZERO state in the following steps. Because this transition is unconditional, there is no Transition Condition associated with it.

1. Click the Transition icon in the vertical toolbar.

2. Click first on the CLEAR state, then on the ZERO state to draw the transition arrow. The arrow's shape can be manipulated by clicking it and then dragging the mouse.

Figure 1-18 Adding State Transition

## **Adding a State Action**

A State Action dictates how the outputs should behave in a given state. There are three types of state actions: Entry Action, State Action, and Exit Action. These determine if the outputs should act upon entry to, existence in, or exit from a given state, respectively.

You will add two state actions to the CLEAR state, one to drive the CLKOUT output to 0, and one to drive the RST output to 1.

1. Click the State Action icon in the vertical toolbar.

- 2. Move the mouse over the diagram so that the small round ball at the end of the pointer is over the CLEAR state. After you are in this position, click the mouse to place the State Action box.

- 3. When a cursor appears, type the following state action:

- For ABEL:

```

clkout = 0;

rst = 1;

```

• For VHDL:

clkout <= `0';

rst <= `1';</pre>

4. Click in an empty space in the diagram to exit out of state action entry mode. The State Action should now appear in a black box next to the CLEAR state.

You have the option to click and drag the State Action to move it.

Figure 1-19 Adding State Actions

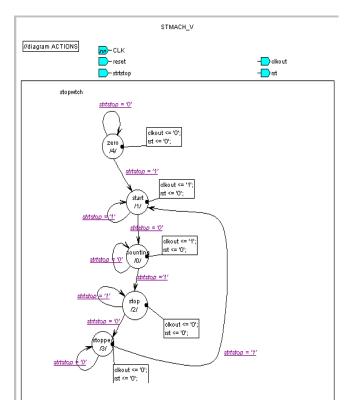

#### Adding a State Machine Reset Condition

Using the State Machine Reset, you specify a reset condition for the State Machine. The state machine initializes to this specified state and enters the specified state whenever the reset condition is met. In this design, you add a Reset condition which sends the state machine to the CLEAR state whenever the RESET signal is asserted.

1. Click the Reset icon in the vertical toolbar.

- 2. Place the Reset triangle onto the diagram near the CLEAR state, as shown in the diagram below.

- 3. The cursor is automatically attached to the transition arrow for this Reset. Move the cursor to the CLEAR state, and click the state bubble.

Figure 1-20 Adding Reset

#### Adding a Transition Condition

Add the Transition Condition to the Reset. Transition Conditions are applied to all transitions, not only Reset transitions, in the same way. Transition Conditions are attached to the transition arrows, and describe the required condition for the movement between states.

Add a transition condition which tells the state machine to reset to the CLEAR state whenever the signal RESET is high.

1. Click the Condition icon in the vertical toolbar.

- 2. Click the transition arrow which was drawn between the Reset triangle and the CLEAR state.

- 3. When the cursor appears, type in the following condition:

- For ABEL:

reset

• For VHDL:

reset = `1'

4. Click in an empty space in the diagram to exit the Draw Condition mode. The condition should now appear underlined and in purple text.

5. Save your changes by selecting File  $\rightarrow$  Save.

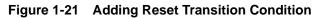

#### **Creating the State Machine Macro**

You will now synthesize the state machine and a macro will be created that you can place on the Watch schematic. The macro symbol will automatically be added to the project library. The synthesis process encompasses the creation of the HDL code from the state machine diagram and the synthesis of the HDL code by either the Foundation Express (VHDL) or XABEL (ABEL) compiler. Additionally, you have the option to use the State Editor to create a symbol for the state machine which you can place on the schematic.

- 1. Select  $Project \rightarrow Create Macro$ . This synthesizes the design as well as creates the macro symbol and adds the symbol to the SC Symbols toolbox.

- 2. To view the HDL code which the State Editor produced, select **Tools**  $\rightarrow$  HDL Editor.

- 3. Close the State Editor by clicking the X in the upper right corner of the window.

#### Placing the STMACH symbol

You can now place the STMACH state machine macro on the Watch schematic. If it is not already opened, open the Schematic Editor. Open the SC Symbols Toolbox to view the list of available library components. You should now be able to locate the STMACH\_A or STMACH\_V macro in this list. (If the SC Symbols Toolbox was already open, and you do not see the STMACH macro, select File  $\rightarrow$  Update Libraries.) Select the appropriate symbol, and add it to the Watch schematic as shown below. Do not worry about drawing the wires to connect this symbol. You will connect the entire schematic later in the tutorial.

Save the schematic.

## **Creating an HDL-Based Module**

With Foundation you can create modules from HDL code. The HDL code is synthesized by either the Express compiler (for VHDL or Verilog), or the XABEL compiler (for ABEL), and a symbol is generated which you can place on the schematic.

**Note:** If you use Verilog or VHDL to create an HDL macro, then you must have Base Express or Foundation Express and a valid license.

You will create an HDL module from scratch. This macro serves to convert the two 4-bit outputs of the CNT60 module into 7-segment LED display format.

#### Using the HDL Design Wizard and HDL Editor

The HDL Wizard is very similar to the Symbol Wizard that you used to create the CNT60 macro earlier. You enter the name and ports of the component and the HDL Wizard creates a "skeleton" HDL file which you can complete with the remainder of your code.

1. From the Flow tab in the Project Manager, click the HDL Editor button.

- 2. A dialog box opens, asking if you want to create an empty HDL file, select an existing HDL file, or use the HDL Wizard to create a new file. Click the radio button next to Use HDL Design Wizard and click OK.

- 3. Follow the instructions from the Wizard. When you are prompted for a preferred HDL language, choose one.

**Note:** You *must* have a Base Express or Foundation Express package in order to use VHDL or Verilog.

- 4. When you are prompted for a file name, type HEX2LED and click Next.

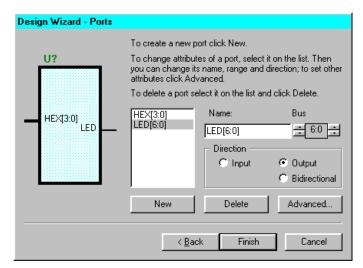

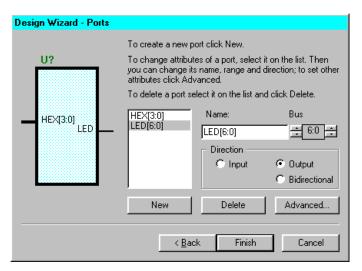

- 5. The HEX2LED component will have a 4-bit input port named HEX, and a 7-bit output port named LED. To enter these ports, click the New button in the Ports dialog box. Select Input as the direction and type HEX in the Name field. Then, click the arrow next to the Bus field to select 3:0, which is the width of the bus. In the Name field, you should now see HEX[3:0], and a corresponding pin should appear on the symbol diagram on the left.

#### Figure 1-23 HDL Wizard

6. Repeat the previous step for the LED[6:0] output bus. Be sure to set the direction to Output.

If you use ABEL, set the outputs to combinatorial instead of the default (registered). To set the outputs, make sure the LED[6:0] pin is highlighted and click the Advanced ... button. In the Advanced Port Settings dialog box, click the radio button next to Combinatorial.

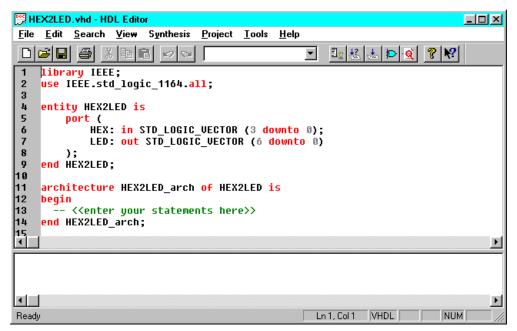

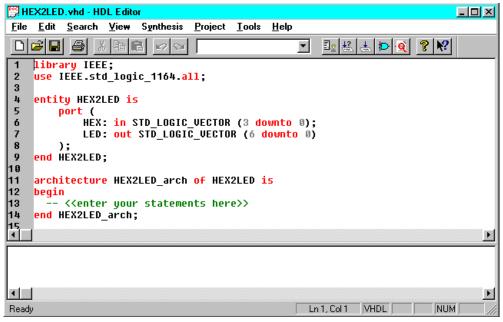

7. Click **Finish** to complete the Wizard session. A "skeleton" HDL file now appears in the HDL Editor.

Figure 1-24 Skeleton HDL File

In the HDL Editor, the ports are already declared in the HDL file, and some of the basic file structure is already in place. Keywords are printed in red, comments in green, and values are gray. This colorcoding enhances readability and recognition of typographical errors.

## Using the Language Assistant

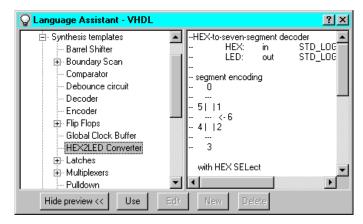

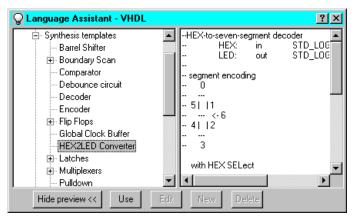

Use the templates from the Language Assistant for commonly used HDL constructs, as well as synthesis templates for commonly used logic components such as counters, D flip-flops, multiplexers, and global buffers. You can add your own templates to the Language Assistant for components or constructs you use often.

1. To invoke the Language Assistant, select  $\texttt{Tools} \rightarrow \texttt{Language}$ Assistant from the HDL Editor pulldown menu.

- 2. The Language Assistant is divided into three sections: Language Templates, Synthesis Templates and User Templates. To expand the view of any of these sections, click the '+' next to the topic. Click any of the listed templates to view the template in the right hand pane.

- 3. Use the template called HEX2LED Converter located under the Synthesis Templates heading. Locate this template, preview it in the right hand pane by clicking the template. This template provides source code to convert a 4-bit value to 7-segment LED display format.

Figure 1-25 HDL Language Assistant

- 4. Before adding this template to your HDL file, be sure that the cursor in the HDL Editor is positioned below the line with the comments "<<enter your statements here>>" for VHDL. For Verilog, enter code after the "// Add your code here" line. For ABEL, add the template below the line "<<add your equations here>>". When you use the template, the code is placed wherever the cursor is currently positioned in the HDL Editor.

- 5. To add the HEX2LED Converter template code, click the **Use** button in the Language Assistant while the HEX2LED Converter template is selected. The code is automatically placed in the HDL file.

- 6. Close the Language Assistant by clicking the X in the upper right corner of the window.

(Verilog only) After the "//add your declarations here" statement and before the HEX2LED converter that you just added, add the following line of code to the HDL file to allow an assignment.

reg LED;

- 8. You now have complete and functional HDL code and can check the syntax using Synthesis  $\rightarrow$  Check Syntax.

- 9. After you successfully complete the syntax check, save the file by selecting File  $\rightarrow$  Save from the HDL Editor.

#### Synthesizing the HDL Code and Creating a Macro

Synthesize the code and create a macro symbol which may be placed on the schematic.

1. From within the HDL Editor, select  $Project \rightarrow Create Macro$ .

The code is synthesized, and a symbol is created and placed in the project library.

2. Close the HDL Editor by clicking the X in the upper right corner of the window.

#### Adding the HEX2LED Component to the Schematic

You are now ready to place the HEX2LED macro on the Watch schematic. Open the Schematic Editor if it is not already open. Open the SC Symbols Toolbox (refer to the "Adding Components to CNT60" section) to view the list of available library components. You should now be able to locate the HEX2LED macro in this list. Select it, and add it to the Watch schematic as shown in the next figure.

This component will be placed on the Watch schematic sheet in two separate instances. To duplicate the component in the schematic, click the left mouse button while the pointer is on the placed symbol, and then click again to place the duplicate symbol.

**Note:** The Symbols Toolbox icon must still be depressed on the vertical toolbar to enable this feature to automatically duplicate a symbol.

Again, do not worry about drawing the wires and buses to connect this macro. You will connect the entire schematic later in the tutorial.

Figure 1-26 Placing the HEX2LED Component

# **Specifying Device Inputs/Outputs**

When specifying device I/O on a schematic sheet, use components from the Xilinx Unified Library to represent the input/output pads and buffers in the device. The SpartanXL library, which is attached to this Foundation project, contains primitive components for these, such as IPAD, OPAD, IBUF, OBUF, and IOPAD. You can place I/O components on any level of hierarchy in a Foundation schematic. However, it is recommended that the pad and the buffer (that is, IPAD/IBUF) reside on the same level of hierarchy. In other words, do not split up the pad and the buffer between levels of hierarchy.

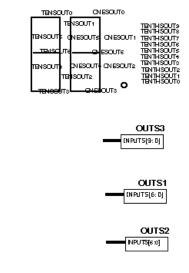

## **Hierarchy Push/Pop**

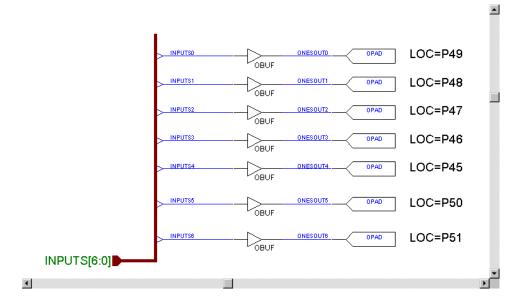

Descend into a lower-level of hierarchy to view the underlying file. You will be pushing down into the OUTS1 macro, which is a schematic-based user-created macro.

To push down into OUTS1, click the Hierarchy Push/Pop button. The mouse cursor changes to the letter "H". Double click the OUTS1 symbol.

In the OUTS1 schematic, you see a series of output buffers (OBUF) and output pads (OPAD). These represent output pins on the SpartanXL device. Each of these pads has a LOC=P\_\_\_\_ attribute attached to them. This attribute assigns each of the pins to a particular pin on the target device. You will add more pins with LOC attributes in the next section.

Figure 1-27 OUTS1 Schematic Macro

The OUTS2 and OUTS3 macros are similar to OUTS1, except that the pins have been locked to different device I/O.

2. "Pop" back out of the OUTS1 component. You can do this in one of two ways. Either click the Hierarchy Push/Pop icon, then double click in an empty space in the OUTS1 schematic, or click the Watch tab at the bottom of the Schematic Capture tool to return to the top-level Watch schematic sheet.

#### **Adding Input Pins**

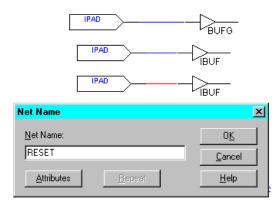

Add three more input pins to the Watch schematic, called CLK, RESET and STRTSTOP.

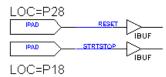

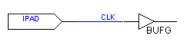

- 1. Add an IPAD and an IBUF for each of the two input pins, RESET and STRTSTOP. Add an IPAD and a BUFG for the input clock signal, CLK. To add these components, click the SC Symbols icon in the vertical toolbar to open the SC Symbols Toolbox. Browse to locate the IPAD, IBUF, and BUFG components in the SpartanXL library. Drop these on the schematic as shown below.

- 2. Draw a net between each IPAD/IBUF pair and the IPAD/BUFG input. If necessary, refer to the section on drawing nets (see the "Drawing Nets" section) for instruction.

Figure 1-28 Placing CLK, RESET and STRTSTOP I/O Components

# **Labeling Nets**

It is important to label nets and buses for several reasons. It aids in debugging and simulation, as you will more easily trace nets back to your original design. Any nets which remain unnamed in the design will be given machine-generated names which will mean nothing to you later in the implementation process. Naming nets also enhances readability and aids in documenting your design.

Label the three input nets you just drew. When naming input and output pins, it is advisable to label the net between the pad and the buffer. This name is carried through the entire design flow including place and route. If you label only the output of the buffer (in the case of an input pin) or input of the buffer (in the case of an output pin), you will not be able to easily trace your I/O pins in implementation tools and reports.

- 1. Double click the RESET net.

- 2. In the Net Name field, type **RESET** as shown below.

#### Figure 1-29 Labeling Nets

- 3. Click OK.

- 4. Repeat Steps 1 through 3 for the **STRTSTOP** and **CLK** pins. You have the option to click and drag the new attributes to better place them on the schematic.

Figure 1-30 Labeled Nets

# **Assigning Pin Locations**

Xilinx recommends that you let the automatic placement and routing program, PAR, define the pinout of your design. Pre-assigning locations to the pins can sometimes degrade the performance of the place and route tools. However, it is usually necessary, at some point, to lock the pinout of a design so that it can be integrated into a PCB (Printed Circuit Board).

Define the initial pinout by running the place-and-route tools without pin assignments, then locking down the pin placement so that it reflects the locations chosen by the tools. In this design, you assign locations to the pins in the Watch design so that the design can function in a Xilinx demonstration board. Because the design is simple and timing is not critical, these pin assignments will not adversely affect the ability of PAR to place and route the design.

Specify pin locations by attaching a LOC parameter to a pad component. Assign a LOC parameter to the pad associated with the RESET signal on the Watch schematic as follows.

- 1. Double click the IPAD connected to the net labeled RESET. The Symbol Properties dialog box opens.

- 2. In the Parameters section, add a new parameter with these values:

Name: LOC

Description: P28

This step assigns the RESET signal to pin P28 of the target device.

| Symbol Prope                 | erties                    |      |                    | ×                     |

|------------------------------|---------------------------|------|--------------------|-----------------------|