WD83C584 Bus Interface Controller Device

WESTERN DIGITAL

# TABLE OF CONTENTS

| Section | Title Pag                              | зe  |

|---------|----------------------------------------|-----|

| 1.0     | INTRODUCTION                           | 3-1 |

| 1.1     | Description                            | 3-1 |

| 1.2     | Features                               | 3-1 |

| 2.0     | PINOUTS                                | 3-2 |

| 2.1     | Pin Descriptions                       | 3-2 |

|         | 2.2.1 PC Bus Signals                   | 3-2 |

|         | 2.2.2 LAN Signal                       | 3-4 |

|         | 2.2.3 EEROM Signals                    | 3-5 |

|         | 2.2.4 RAM Signals                      | 3-6 |

|         | 2.2.5 General I/Os                     | 3-6 |

|         | 2.2.6 ROM Signals                      | 3-6 |

|         | 2.2.7 Voltages                         | 3-7 |

| 3.0     |                                        | 3-8 |

| 3.1     | Initialization                         | 3-8 |

| 3.2     | Arbitration                            | 3-8 |

| 3.3     | RAM Buffer                             | 3-8 |

| 3.4     | External EEROM                         | 3-8 |

| 4.0     | INTERNAL REGISTERS                     | 3-9 |

| 4.1     | I/O Map                                | 3-9 |

| 4.2     | Memory Select Register (MSR            | 10  |

| 4.3     | Interface Configuration Register (ICR) | ·11 |

| 4.4     | I/O Address Register (IAR)             | 13  |

| 4.5     | BIOS ROM Address Register (BIO)        | 14  |

| 4.6     | EEROM Address Register (EAR)           | 15  |

| 4.7     | Interrupt Request Register (IRR        | 16  |

| 4.8     | LA Address Register (LAAR)             | 17  |

| 4.9     | Initialize Jumper Register             | 18  |

| 4.10    | General Purpose Register 2 (GP2)       | 19  |

| 4.11    | LAN Address Registers (LAR)            | ·20 |

| 5.0     | TIMING                                 | ·22 |

# LIST OF ILLUSTRATIONS

| Figure | Title                       | Page  |

|--------|-----------------------------|-------|

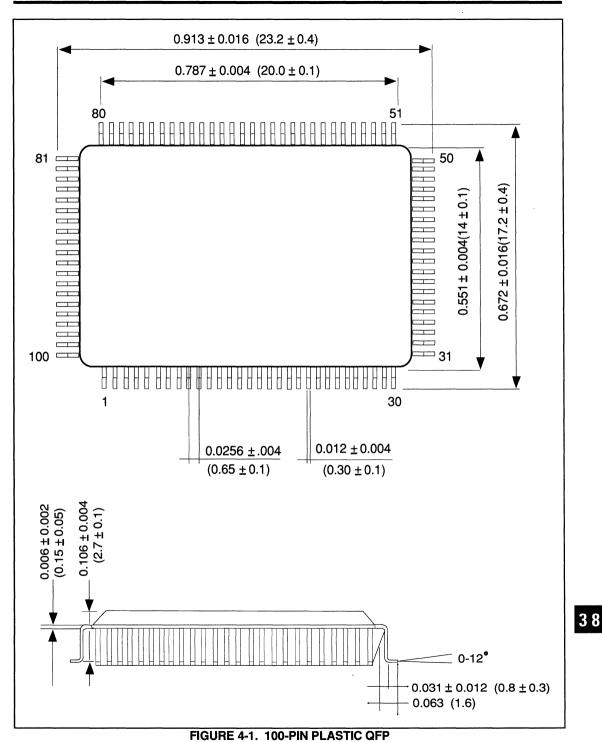

| 4-1    | 100-pin Plastic QFP         | 38-21 |

| 5-1    | I/O Read                    | 38-22 |

| 5-2    | I/O Write                   | 38-23 |

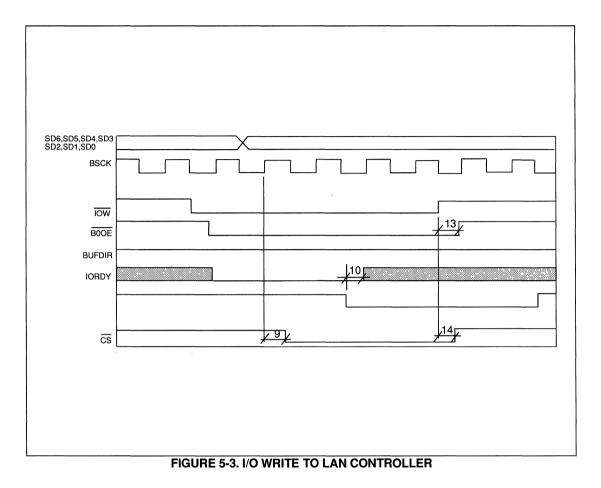

| 5-3    | I/O Write to LAN Controller | 38-24 |

| 5-4    | ROM Read                    | 38-25 |

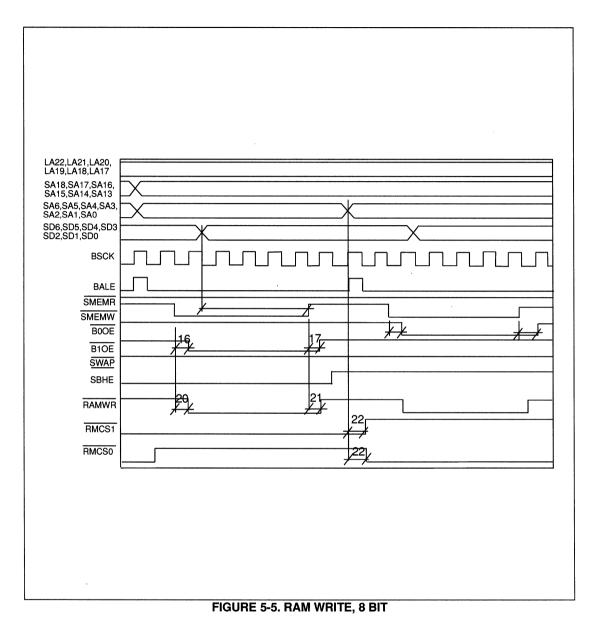

| 5-5    | RAM Write, 8 Bit            | 38-26 |

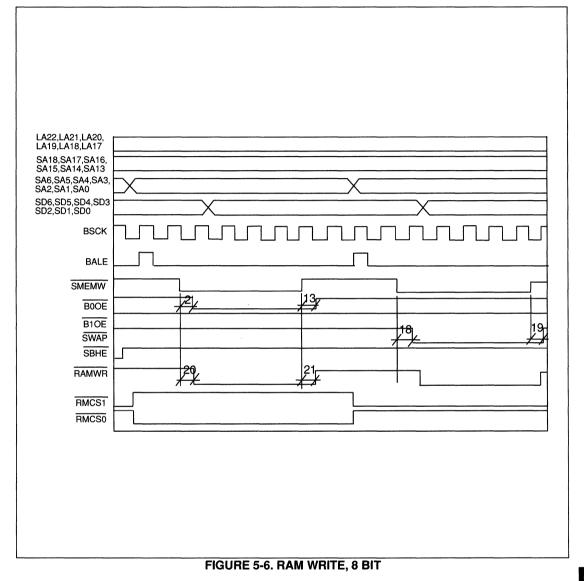

| 5-6    | RAM Write, 8 Bit            | 38-27 |

| 5-7    | RAM Read, 16 Bit            | 38-28 |

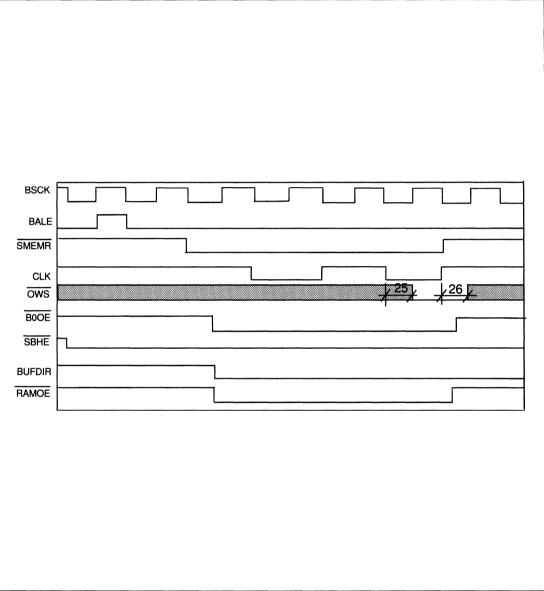

| 5-8    | OWS, 8 Bit                  | 38-29 |

| 5-9    | OWS, 16 Bit                 |       |

| 5-10   | M16CS                       | 38-31 |

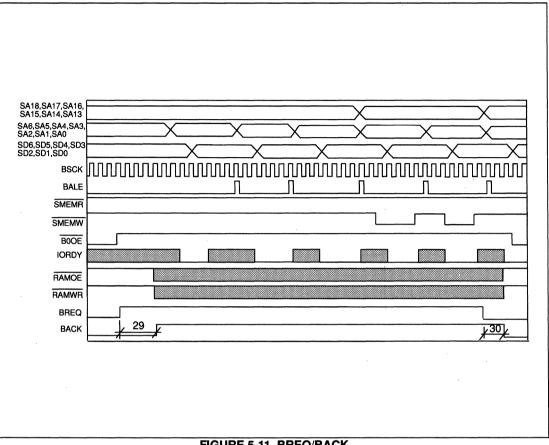

| 5-11   | BREQ/BACK                   | 38-32 |

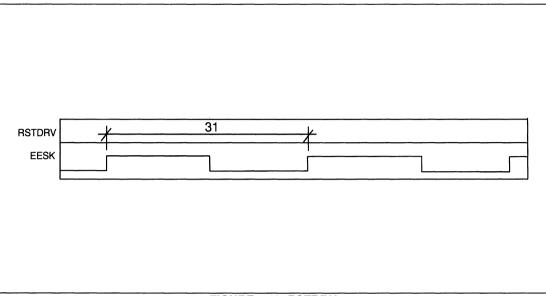

| 5-12   | RSTDRV                      | 38-33 |

## LIST OF TABLES

| Table | Title                          | Page    |

|-------|--------------------------------|---------|

| 2-1   | PC Bus Signals                 | 38-2    |

| 2-2   | LAN Signals                    | 38-4    |

| 2-3   | EEROM Signals                  | 38-5    |

| 2-4   | RAM Signals                    |         |

| 2-5   | General I/Os                   | 38-6    |

| 2-6   | ROM Signals                    |         |

| 2-7   | Voltages                       | 38-7    |

| 5-1   | WD83C584 Timing                | . 38-34 |

| B-1   | DC Parameter Characteristics   | . 38-36 |

| B-2   | Non-Operational Specifications | . 38-37 |

| B-3   | Operational Specifications     | . 38-37 |

# **APPENDICES**

| Α | Software Compatibility               | -35 |

|---|--------------------------------------|-----|

| B | Electrical Operating Characteristics | -36 |

### 1.0 INTRODUCTION

#### 1.1 DESCRIPTION

The WD83C584 is a single device bus interface controller that enables a LAN controller device to function with the standard PC XT, AT or compatible bus with minimum external logic. This device interfaces with BIOS ROM, shared memory, external EEPROM and the LAN controller. It's internal registers are automatically loaded with configuration data from the external EEPROM.

#### 1.2 FEATURES

- Host: IBM PC/XT/AT, PS/2s, and compatibles

- Interfaces to:

- WD83C690, 8390

- BIOS ROM: 16, 32 or 64 Kbyte windows

- in memory space

- Shared Memory

- 16-bit or 8-bit Memory Data

- 8-bit I/O Data

- Bus Speed: Supports 8.33 MHz EISA

- SRAM Memory:

- 8-bit: 8 or 32 Kbyte

- 16-bit: 16 or 64 Kbyte

- Shared Memory Mapped

- allowing 16-bit 1 wait state or 8-bit 4 wait state transfers

- Zero Wait State on AT busses allowing 16-bit 0 wait state or 8-bit 2 wait state memory transfers

- Interfaces to external EEROM which stores:

- I/O Address

- Memory Address

- Memory Size

- BIOS ROM Address

- Configuration

- LAN Address

- Controls 128 Byte External EEROM

# 2.0 PIN OUTS

### 2.1 PIN DESCRIPTIONS

## 2.2.1 PC Bus Signals

| PIN                                                                                | NAME                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 97<br>96<br>95<br>94<br>93<br>92<br>91                                             | LA23 (I)<br>LA22<br>LA21<br>LA20<br>LA19<br>LA18<br>LA17                                                                       | PC LA ADDRESS BUS<br>These input signals (unlatched) are used to address memory. They give the<br>system up to 16 Mbyte of addressability. They are valid when BALE is high.<br>Their purpose is to generate memory address decodes during 0 and 1 wait<br>state memory Read/Write cycles. |

| 19   18   17   16   15   14   13   12   11   10   09   08   07   06   05   04   03 | SA19 (I)<br>SA18<br>SA17<br>SA16<br>SA15<br>SA14<br>SA13<br>SA9<br>SA8<br>SA7<br>SA6<br>SA5<br>SA4<br>SA3<br>SA2<br>SA1<br>SA0 | PC ADDRESS BUS<br>Address lines SA 19-13 & SA 9-0 are used to decode and address memory.<br>SA 15-13 and SA 9-0 are used for I/O addressing.                                                                                                                                               |

| 99                                                                                 | BALE (I)                                                                                                                       | PC ADDRESS LATCH ENABLE<br>Used to enable address lines LA23-17 from the LA bus.                                                                                                                                                                                                           |

| 98                                                                                 | SBHE (I)                                                                                                                       | PC BUS HIGH ENABLE<br>Indicates a transfer of data on the upper byte of the data bus, SD8 - SD15.                                                                                                                                                                                          |

| 100                                                                                | M16CS (0)                                                                                                                      | PC MEMORY 16-BIT CHIP SELECT<br>Signals the system board that the present transfer is a 16-bit memory cycle.<br>It is derived from a decode of LA23 - LA17. It is driven by a tri-state driver.                                                                                            |

| 77                                                                                 | BIT8 (I)                                                                                                                       | PC 8-BIT BUS / 16-BIT BUS A 0 or low signal on this input indicates that the data bus is an 16-bit bus. A 1 or high signal indicates that the data bus is 8 bits.                                                                                                                          |

| 47<br>46<br>45<br>44<br>43<br>42<br>41<br>40                                       | SD7 (I/O)<br>SD6<br>SD5<br>SD4<br>SD3<br>SD2<br>SD1<br>SD0                                                                     | PC DATA BUS<br>These signals provide the low order data bus bits. They are the PC's access to<br>the internal registers.                                                                                                                                                                   |

#### TABLE 2-1. PC BUS SIGNALS

| PIN                                          | NAME                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21                                           | CLK (I)                                                                                           | PC CLOCK<br>PC system clock used to synchronize the zero wait state line when used in the<br>8-bit interface mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33                                           | RSTDRV (I)                                                                                        | PC RESET<br>Used to reset or initialize logic at power up time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 58                                           | ior (I)                                                                                           | PC I/O READ<br>When low, this input transfers the contents of the selected I/O register onto<br>the PC data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 59                                           | IOW (I)                                                                                           | PC I/O WRITE<br>When low, this input transfers the contents of the PC data bus onto the selected<br>I/O register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 82<br>22                                     | Memr (I)<br>Smemr (I)                                                                             | PC MEMORY READ<br>These inputs connect to the memory read signals on the PC bus. When this<br>signal is active, it enables data from the buffer memory onto the PC data bus.<br>SMEMW is active only when the memory address is within the first 1 Mbyte<br>of memory space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 81<br>23                                     | MEMW (I)<br>SMEMW (I)                                                                             | PC MEMORY WRITE<br>This input connects to the memory write signal on the PC bus. When this signal<br>is active, it enables data on the PC bus to be stored on the buffer memory.<br>SMEMW is active only when the memory address is within the first 1 Mbyte of<br>memory space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20                                           |                                                                                                   | PC ADDRESS ENABLE<br>This input connects to the address enable signal on the PC bus. If Address<br>Enable is active, the WD83C584 will not respond to any command.<br>PC READY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24                                           | IORDY (O)                                                                                         | I/O Channel Ready is pulled low (not ready) by a memory or I/O device to<br>lenthen I/O or memory cycles. Any slow device using this line should drive it low<br>immediately upon detecting its valid address and a Read or Write command.<br>This signal is driven by a tri-state buffer capable of sinking 24 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32                                           | 0WS (O)                                                                                           | PC ZERO WAIT STATE<br>Zero wait state signal tells the host processor that it can complete the present<br>bus cycle without inserting any additional wait cycles. In order to run a memory<br>cycle to a 16-bit device without wait cycles, $\overline{OWS}$ is derived from an address<br>decode gated with a MEMR or MEMW command. In order to run a memory<br>cycle to an 8-bit device with a minimum of two wait states, $\overline{OWS}$ should be<br>driven active one system clock after the SMEMR or SMEMW command is gated<br>with the address decode for the device. Memory Read and Write commands to<br>an 8-bit device are active on the falling edge of the system clock. $\overline{OWS}$ is a tri-<br>state output capable of sinking 24 mA. |

| 90<br>86<br>87<br>88<br>89<br>85<br>84<br>83 | IRQ2/9 (O)<br>IRQ3 (O)<br>IRQ4 (O)<br>IRQ5 (O)<br>IRQ7 (O)<br>IRQ10 (O)<br>IRQ11 (O)<br>IRQ15 (O) | PC INTERRUPT REQUESTS<br>An interrupt request is generated when INT is raised from low to high. The line<br>must be held high until the microprocessor acknowledges the interrupt request.<br>Only one line is active at a time; all others are tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# TABLE 2-1. PC BUS SIGNALS (Continued)

# 2.2.2 LAN Signals

| PIN            | NAME                             | DESCRIPTION                                                                                                                                                                                                          |  |

|----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 37<br>38<br>39 | BOOE (O)<br>B1OE (O)<br>SWAP (O) | PC BUFFER OUTPUT ENABLE<br>Controls the least significant, most significant and swap byte buffers respectively.                                                                                                      |  |

| 36             | BUFDIR (O)                       | PC BUFFER DIRECTION<br>Provides direction control for an external data buffer. BUFDIR is "1" for writes<br>and "0" for reads.                                                                                        |  |

| 78             | BSCK (I)                         | LAN CLOCK<br>20 MHz clock.                                                                                                                                                                                           |  |

| 55             | BREQ (I)                         | LAN BUS REQUEST<br>Bus Request is used to request the local bus for DMA transfers. this signal is<br>generated when the LAN controller FIFO needs servicing.                                                         |  |

| 56             | BACK (O)                         | LAN BUS ACKNOWLEDGE<br>Bus Acknowledge indicates that the LAN controller has been granted the bus.                                                                                                                   |  |

| 60             | <u>CS</u> (O)                    | LAN CHIP SELECT<br>Places the LAN in slave mode for access to LAN internal registers.                                                                                                                                |  |

| 57             | ACK (I)                          | LAN SLAVE I/O ACKNOWLEDGE<br>Active low when LAN controller grants access to WD83C584. Used to insert<br>wait states to WD83C584 until the LAN controller is synchronized for a register<br>read or write operation. |  |

|                | INT (I)                          | LAN INTERRUPT<br>Indicates that the LAN controller requires CPU attention after reception trans-<br>mission or completion of DMA transfers.                                                                          |  |

| 53             | RESET (O)                        | LAN RESET<br>Hardware reset to the LAN controller IC.                                                                                                                                                                |  |

|                |                                  |                                                                                                                                                                                                                      |  |

## TABLE 2-2. LAN SIGNALS

.

# 2.2.3 EEROM Signals

| PIN            | NAME                                | DESCRIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TION                          |                                          |                                                                                                                                                                                      |

|----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50<br>49<br>48 | INIT2 (I)<br>INIT1 (I)<br>INITO (I) | EEROM INITIALIZE<br>There are three EEPROM initialization pins. Depending on the state of these<br>pins, the WD83C584 registers will power up from different EEROM bytes. The<br>following table shows the bytes from which it will power up. Refer to each<br>register to determine the value of each byte loaded at power up. One case is<br>special, it causes the WD83C584 to its INITIAL state which overrides EEROM.<br>(Refer to each register for their INITIAL values.) Note that the LAN ADDRESS<br>is read from locations 40-47. |                               |                                          |                                                                                                                                                                                      |

|                |                                     | INIT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INIT1                         | <b>INITO</b>                             | EE ADDRESS                                                                                                                                                                           |

|                |                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                             | 1                                        | 00-07                                                                                                                                                                                |

|                |                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                             | 0                                        | 08-0F                                                                                                                                                                                |

|                |                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                             | 1                                        | 10-17                                                                                                                                                                                |

|                |                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                             | 0                                        | 18-1F                                                                                                                                                                                |

|                |                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                             | 1                                        | 20-27                                                                                                                                                                                |

|                |                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                             | 0                                        | 28-2F                                                                                                                                                                                |

|                |                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                             | 1                                        | 30-37, INITIAL CONDITION                                                                                                                                                             |

|                |                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                             | 0                                        | 38-3F                                                                                                                                                                                |

| 35             | TEST                                | TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               | · · · · · · · · · · · · · · · · · · ·    |                                                                                                                                                                                      |

|                |                                     | Used for fa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | actory testi                  | ing. Must b                              | e pulled up to +5V with 10 Kohm, 5% resistor.                                                                                                                                        |

| 64             | EECS (O)                            | EEROM C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HIP SELE                      | CT                                       |                                                                                                                                                                                      |

| 63             | EESK (O)                            | EEROM C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LOCK                          |                                          |                                                                                                                                                                                      |

| 62             | EEDI (O)                            | EEROM D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ATA INPU                      | Т                                        |                                                                                                                                                                                      |

| 61             | EEDO (I)                            | An externa<br>The above<br>at power u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e signals in<br>Ip time. It t | rial EEROM<br>Iterface to the akes about | I is used to store up to 1024 bits of EEROM data.<br>his chip. The EEROM is used to initialize registers<br>2 ms to read all 16 registers after the end of the<br>ns to store EEROM. |

# TABLE 2-3. EEROM SIGNALS

# 2.2.4 RAM Signals

| PIN            | NAME                                | DESCRIPTION                                                                                                                                                                    |

|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71             | RAMOE (O)                           | RAM OUTPUT ENABLE<br>This output connects to the output enable pins on the buffer RAM.                                                                                         |

| 70             | RAMWR (O)                           | RAM WRITE ENABLE<br>This output connects to the write enable pins on the buffer RAM.                                                                                           |

| 68<br>69<br>67 | RMCS0 (O)<br>RMCS1 (O)<br>RAM12 (O) | RAM0 CHIP SELECT<br>RAM1 CHIP SELECT<br>These outputs provide the chip select signals needed by the buffer RAMs.                                                               |

| 66<br>65       | MA13 (I)<br>MA0 (I)                 | These inputs are connected to memory address bus. They are used for memory address decode.                                                                                     |

| 73             | MEM16 (O)                           | MEMORY 16 ENABLE<br>Indicates the host PC to RAM access will be 16 bits wide. This output will not go<br>active if the WD83C584 is used and programmed for 8-bit applications. |

| 72             | LAN16 (O)                           | LAN 16 ENABLE<br>Indicates the LAN controller to RAM access will be 16 bits wide.                                                                                              |

## TABLE 2-4. RAM SIGNALS

### 2.2.5 General I/Os

| PIN            | NAME                            | DESCRIPTION                                                                       |

|----------------|---------------------------------|-----------------------------------------------------------------------------------|

| 52<br>26<br>27 | OUT3 (O)<br>OUT2 (O)<br>OUT1(O) | OUTPUTS<br>These three output pins follow bits D1, D2 and D3 in the IRR register. |

| 30<br>31       | INPUT2 (I)<br>INPUT1 (I)        | INPUTS<br>These two input pins are readable via software from IRR bits D1 and D2. |

# TABLE 2-5. GENERAL I/Os

# 2.2.6 ROM Signals

| PIN      | NAME                   | DESCRIPTION                                                                                                                                                                                               |

|----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76       | ROMOE (O)              | BIOS ROM OUTPUT ENABLE<br>Chip Select for BIOS ROM. This signal gates ROM data onto the SD7-0 bus.                                                                                                        |

| 75<br>74 | ROM15 (O)<br>ROM14 (O) | ROM ADDRESS LINES<br>These attach to the ROM address bits 15 and 14. Depending on the state of the<br>RAM and FLSH bits, these lines do the proper addressing and write strobes for<br>RAM and FLASH ROM. |

# TABLE 2-6. ROM SIGNALS

# 2.2.7 Voltages

| PIN          | NAME      | DESCRIPTION                                                                                                                                         |

|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 34           | POWER (I) | POWER SENSING INPUT<br>This signal is used to sense that the input power has risen to a useable level.<br>This signal has a Schmidtt trigger input. |

| 02,28,<br>79 | VCC (I)   | +5V (3 pins)                                                                                                                                        |

|              | GND (I)   | GROUND (4 pins)                                                                                                                                     |

## TABLE 2-7. VOLTAGES

# 3.0 THEORY OF OPERATION

#### 3.1 INITIALIZATION

Upon power-up, the WD83C584 accesses an external EEROM to set up its initial configuration. This takes about 2 milliseconds to read the data from the EEPROM into the WD83C584. After this time the BIOS ROM and I/O Ports will be enabled. The Shared Memory is always disabled upon power up, and must be enabled by software.

#### 3.2 ARBITRATION

Arbitration for the bus is mainly between the PC and the LAN controller. The LAN controller asserts BREQ and if the bus is free, a BACK is returned. When the LAN controller has the bus, it is in complete control and must provide all RAM and interface signals. Also, access to the ROM and the internal registers on the WD83C584 must also arbitrate for the bus.

#### 3.3 RAM BUFFER

The RAM buffer uses either 8K or 32K SRAMs. It may be either 8 bits or 16 bits wide (giving 64K maximum).

#### 3.4 EXTERNAL EEROM

The WD83C584 accesses an external EEROM. The contents of the EEROM are loaded into the internal registers of the WD83C584 upon power up.

The use of EEROM has several advantages over a separate PROM for the LAN address. It can also reduce the number of jumpers needed on the board. It allows for reconfiguration without removing the board from the system.

Upon power up, the EEROM data is read into the WD83C584 registers. Of course, the first time the EEROM is powered up, it will have random data. The INIT inputs allow the EEROM to be set to a known initial state.

All 128 bytes of EEROM can be accessed and modified from the WD83C584. They are read into the LAN Address registers 8 bytes at a time. Once there, they can be changed and stored back into the EEPROM.

# 4.0 INTERNAL REGISTERS

In the following descriptions, several values of each register are given as follows:

|                     | ۰<br>^                                                                                                                                                                          |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET               | The value during RSTDRV time.                                                                                                                                                   |

| INITIAL             | If the INIT2, 1, 0 pins (50,49,48)<br>are connected such that 001 is<br>present on these inputs, this<br>value is loaded into the register<br>immediately after RSTDRV<br>time. |

| POWER-<br>UP        | If not in the INITIAL setting, this<br>value is loaded into the register<br>immediately after RSTDRV time.                                                                      |

| RECALL              | This value is loaded each time a recall is performed.                                                                                                                           |

| REGISTER<br>VALUES: | ? = value unknown<br>EE = value loaded from EEROM<br>1 = logical 1<br>0 = logical 0<br>n/a = not used                                                                           |

4.1 I/O MAP

| 0x00      | MEMORY SELECT REGISTER<br>(MSR)           |

|-----------|-------------------------------------------|

| 0x01      | INTERFACE CONFIGURATION<br>REGISTER (ICR) |

| 0x02      | I/O ADDRESS REGISTER (IA)                 |

| 0x03      | BIOS ROM ADDRESS<br>REGISTER (BIO)        |

| 0x04      | INTERRUPT REQUEST<br>REGISTER (IRR)       |

| 0x05      | LA ADDRESS REGISTER<br>(LAAR)             |

| 0x06      | INITIALIZATION JUMPERS                    |

| 0x07      | GENERAL PURPOSE DATA<br>REGISTER (GP2)    |

| 0x08-0x0F | LAN ADDRESS REGISTERS<br>(LAR)            |

| 0x10-0x1F | LAN CONTROLLER<br>REGISTERS (LAN)         |

# 4.2 MEMORY SELECT REGISTER (MSR)

## Offset 0x00

Upon power-up, MENB is 0. Thus the memory is disabled at power up, and will not be enabled until the MSR has been programmed with the MENB bit a "1". It is possible to program the memory select bits and the memory enable bit simultaneously.

|          | D7<br>RST | D6<br>MENB | D5<br>RA18 | D4<br>RA17 | D3<br>RA16 | D2<br>RA15 | D1<br>RA14 | D0<br>RA13 |

|----------|-----------|------------|------------|------------|------------|------------|------------|------------|

| RESET    | 0         | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| INITIAL  | 0         | 0          | EE         | EE         | EE         | EE         | EE .       | EE         |

| POWER-UP | 0         | 0          | EE         | EE         | EE         | EE         | EE         | EE         |

| RECALL   | EE        | EE         | EE         | EE         | EE         | EE         | EE         | EE         |

| NAME | DESCRIPTION                                                                                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RST  | SOFTWARE RESET                                                                                                                                  |

| MENB | Set to 1 and then back to 0 to force a hardware reset to the LAN Controller.<br>MEMORY ENABLE<br>Set to 1 to enable PC access to shared memory. |

| RA18 | MEMORY ADDRESS BITS                                                                                                                             |

| RA17 | Must be set to the address at which the shared memory is to be placed. These                                                                    |

| RA15 | bits correspond to system memory address bits SA18 through SA13.<br>SA19 is assumed to be a "1". For example, address C4000 could be selected   |

| RA14 | by writing 0x62 to this register. In 16-bit mode, A19 is set by the LAAR register.                                                              |

| RA13 |                                                                                                                                                 |

|      |                                                                                                                                                 |

|      | RST<br>MENB<br>RA18<br>RA17<br>RA16<br>RA15                                                                                                     |

#### 4.3 INTERFACE CONFIGURATION REGISTER

(ICR) Offset 0x01, (Read/Write)

|          | D7<br>STO | D6<br>RIO | D5<br>RX7 | D4<br>RLA | D3<br>MSZ | D2<br>IR2 | D1<br>n/a | D0<br>BT16 |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------------|

| RESET    | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0          |

| INITIAL  | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0          |

| POWER-UP | 0         | 0         | 0         | 0         | EE        | EE        | EE        | NA         |

| RECALL   | EE        | NA         |

The ICR determines the configuration of the WD83C584.

.

| BIT | NAME                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-----|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D7  | STO                         | NON-VOLATILE EEROM STORE<br>Set to 1 to store registers into EEROM. The bit will be automatically reset. It<br>takes a maximum of 200 ms for a store to take place. It will be reset when the<br>store is complete. This bit may be polled to determine when the store operation<br>is complete. The EEROM has a limited number of stores that can take place.<br>The store operation should only take place at initial board configuration or at<br>initial installation. |  |  |  |  |  |

| D6  | RIO                         | RECALL I/O ADDRESS FROM EEROM<br>Set to 1 to recall the I/O address from EEROM into the I/O Address Register.<br>It will be reset when the recall is complete. This bit may be polled to determine<br>when the recall is complete.                                                                                                                                                                                                                                         |  |  |  |  |  |

| D5  | RX7                         | RECALL ALL BUT I/O and LAN ADDRESS<br>Set to 1 to recall registers with offsets 0x00 and 0x02 through 0x07. It will be<br>reset when the recall is complete. This bit may be polled to determine when the<br>recall is complete.                                                                                                                                                                                                                                           |  |  |  |  |  |

| D4  | RLA                         | RECALL LAN ADDRESS<br>Set to 1 to recall the LAN address only from EEROM (Registers 0x08 through<br>0x0F). It will be reset when the recall is complete. This bit may be polled to<br>determine when the recall is complete.                                                                                                                                                                                                                                               |  |  |  |  |  |

| D3  | MSZ                         | SRAM SIZEThis is the physical size of the SRAM chips on the board. $0 = 8K$ , $1 = 32K$ In order to determine the RAM window in host memory, this bit must be com-bined with LAN16 as follows: <b>MSZ LAN16 SIZE</b> 008 Kbytes0116 Kbytes1032 Kbytes1164 Kbytes                                                                                                                                                                                                           |  |  |  |  |  |

| D2  | IR2                         | Used to select the second set of IRQ lines. See IRR register.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| D1  | OTHER<br>REGISTER<br>ACCESS | This bit idetermines whether the BIOS ROM Address Register (BIO) or the EEROM Address Register (EAR) is enabled. At power up, BIO is enabled. $0 = BIO$ ; $1 = EAR$ .                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| D0  | BIT16                       | 16-BIT BUS<br>When the WD83C584 is used in an 8-bit interface, this bit is read/writable. When<br>used in a 16-bit interface, it will always read a 1.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

## 4.4 I/O ADDRESS REGISTER (IAR) Offset 0x02, (Read/Write)

The IAR sets the I/O address of the board. If the INIT2, INIT1, INIT0 pins are "001" at power-up, the I/O address will be hard initialized at 280.

|          | D7<br>IA15 | D6<br>IA14 | D5<br>IA13 | D4<br>IA9 | D3<br>IA8 | D2<br>IA7 | D1<br>IA6 | D0<br>IA5 |

|----------|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|

| RESET    | 0          | 0          | 0          | 0         | 0         | 0         | 0         | 0         |

| INITIAL  | 0          | 0          | 0          | 1         | 0         | 1         | 0         | 0         |

| POWER-UP | EE         | EE         | EE         | EE        | EE        | EE        | EE        | EE        |

| RECALL   | EE         | EE         | EE         | EE        | EE        | EE        | EE        | EE        |

| BIT | NAME          | DESCRIPTION                                                                           |

|-----|---------------|---------------------------------------------------------------------------------------|

| D7  | IA15          | I/O ADDRESS BITS                                                                      |

| D6  | IA14          | Must be set to the I/O address at which you want the board to be placed. These        |

| D5  | IA13          | bits correspond to system address bits SA15 thru SA13 and SA9 thru SA5.               |

| D4  | IA9           | For example, address 0x280 could be selected by writing to 0x14 to this register.     |

| D3  | IA8           |                                                                                       |

| D2  | IA7           |                                                                                       |

| D1  | IA6           |                                                                                       |

| D0  | IA5           |                                                                                       |

|     |               |                                                                                       |

|     |               | SA15 through SA13 can be used to select multiple boards while still taking up what is |

|     | normally cons | idered only 32 bytes of I/O space.                                                    |

|     |               |                                                                                       |

#### 4.5 BIOS ROM ADDRESS REGISTER (BIO) EEROM Address Register (EAR) Offset 0x03, (Read/Write)

There are two registers at this offset. Depending on what was **last written** to ICR-D1 (OTHER) one register or the other will be accessed.

ICR-D1 = 0:BIO will be accessed ICR-D1 = 1:EAR will be accessed.

The BIO sets the memory address of the BIOS ROM.

The ROM socket may be populated with a 64K ROM, a 32K RAM, or a 32K FLASH ROM.

|          | D7<br>RS1 | D6<br>RS0 | D5<br>BA18 | D4<br>BA17 | D3<br>BA16 | D2<br>BA15 | D1<br>BA14 | D0<br>INT |

|----------|-----------|-----------|------------|------------|------------|------------|------------|-----------|

| RESET    | 0         | 0         | 0          | 0          | Ó          | 0          | 0          | 0         |

| INITIAL  | 0         | 0         | 0          | 1          | 0          | 1          | 0          | 0         |

| POWER-UP | EE        | EE        | EE         | EE         | EE         | EE         | EE         | EE        |

| RECALL   | EE        | EE        | EE         | EE         | EE         | EE         | EE         | EE        |

| BIT | NAME | DESCRIPTION                                                                   |

|-----|------|-------------------------------------------------------------------------------|

| D7  | RS1  | BIOS ROM SIZE                                                                 |

| D6  | RS0  | RS1 RS0                                                                       |

|     |      | 0 0 ROM cannot be accessed                                                    |

|     |      | 0 1 16 Kbyte ROM                                                              |

|     |      | 1 0 32 Kbyte ROM                                                              |

|     |      | 1 1 64 Kbyte ROM                                                              |

| D5  | BA18 | BIOS ROM MEMORY ADDRESS BITS                                                  |

| D4  | BA17 | Must be set to the memory address at which you want the BIOS ROM is to be     |

| D3  | BA16 | placed. These bits correspond to system memory address bits SA18 through      |

| D2  | BA15 | SA13. SA19 is assumed to be a "1". For example, a 16 Kbyte ROM at             |

| D1  | BA14 | D8000 could be selected by writing 0x6C to this register.                     |

| DO  | INT  | Setting this bit raises one of the IRQ lines to the PC. This may be used as a |

|     |      | software interrupt. It must be reset to remove the IRQ.                       |

|     |      | ·                                                                             |

#### 4.6 EEROM ADDRESS REGISTER (EAR)

The EAR allows additional EEROM to be accessed. In order to access this register a "1" should be written to ICR-D1 (OTHER).

Operation of EEROM is as follows:

During power up or recall, 8 bytes of EEROM are loaded into the WD83C584 first 8 registers. Which 8 bytes are read depends on the position of the INIT input jumper pins. In the case that the INIT pins are all unjumpered (all 1s), bytes from 0X00 to 0X0F will be read. In all cases, these bytes will be from EEROM locations between 0X00 and 0X3F. During a store operation, the first 8 bytes are always written to the first 8 EEROM locations (0X00 through 0X07). At power up, the EAR was set with EA6, EA5, EA4, EA3 = 1000. The next 8 bytes are read into the LAN address registers using the EAR register addresses. Thus the LAN address should be stored at 0X40.

When the ICR-D1 bit is set. This EAR register may be programmed to point at other EEROM addresses. A STO or RLA would then transfer between the LAN address registers and this other EEROM address.

During a recall, ICR-D1 bit is not changed. Also the BIOS ROM ADDRESS (BIO) is recalled to offset 3 and not this EAR. There is no EEROM backup for the EAR. During a STO, the BIO is stored.

When the ICR-D1 bit is set, the EAR is readable from the host, not the BIO.

|          | D7<br>EA6 | D6<br>EA5 | D5<br>EA4 | D4<br>EA3 | D3<br>RAM | D2<br>RPE | D1<br>RP1 | D0<br>RP |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|

| RESET    | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0        |

| INITIAL  | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0        |

| POWER-UP | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0        |

| RECALL   | EE        | EE       |

| BIT | NAME | DESCRIPTION                                                                                                                                                            |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | EA6  | EEROM ADDRESS                                                                                                                                                          |

| D6  | EA5  | This determines which 8 bytes will be accessed with a recall or STO store.                                                                                             |

| D5  | EA4  | The default 0x80 says that bytesD4 EA3 0x40-0x47 will be read into the                                                                                                 |

| D4  | EA3  | LAN registers. A 0x10 would cause bytes 0x08-0x0F to be stored or read to or from the LAN ADDRESS registers. When ICR-D1 = 0, the EEROM Address will be reset to 0x40. |

| D4  | RAM  | RAM<br>Indicates that a 32K RAM is installed in the ROM socket.                                                                                                        |

| D2  | RPE  | ROM PAGE                                                                                                                                                               |

| D1  | RP1  | RPE enables ROM paging. The RP1 and RP0 bits determine what page of                                                                                                    |

| D0  | RP0  | ROM will be accessed. A page is equal to 16 Kbytes. Four 16-Kbyte pages are accessible.                                                                                |

# 4.7 INTERRUPT REQUEST REGISTER (IRR) Offset 0x04, (Read/Write)

|          | D7<br>IEN | D6<br>IR1 | D5<br>IR0 | D4<br>FLSH | D3<br>OUT3 | D2<br>OUT2 | D1<br>OUT1 | DÖ<br>OWS8 |

|----------|-----------|-----------|-----------|------------|------------|------------|------------|------------|

| RESET    | 0         | 0         | 0         | 0          | 0          | 0          | 0          | 0          |

| INITIAL  | 0         | 0         | 0         | 1          | 0          | 1          | 0          | 0          |

| POWER-UP | EE        | EE        | EE        | EE         | EE         | EE         | EE         | EE         |

| RECALL   | EE        | EE        | EE        | EE         | EE         | EE         | EE         | EE         |

The IRR controls which Interrupt Request will be used.

|   | BIT   | NAME  | DESCRIPTION                                                                       |  |  |  |  |

|---|-------|-------|-----------------------------------------------------------------------------------|--|--|--|--|

|   | D7    | IEN   | INTERRUPT ENABLE                                                                  |  |  |  |  |

|   |       |       | Enables the appropriate IRQ line onto the bus. The IRQ lines are tri-stated       |  |  |  |  |

|   |       |       |                                                                                   |  |  |  |  |

|   | ICR-D |       | INTERRUPT REQUEST                                                                 |  |  |  |  |

|   | D6    | IR1   | These bits determine which Interrupt Request Line will be enabled. IR2            |  |  |  |  |

|   | D5    | IR0   | is found as ICR-D2.                                                               |  |  |  |  |

|   |       |       | IR2 IR1 IR0                                                                       |  |  |  |  |

|   |       |       | 0 0 0 IRQ2/9                                                                      |  |  |  |  |

|   |       |       | 0 0 1 IRQ3                                                                        |  |  |  |  |

|   |       |       | 0 1 0 IRQ5                                                                        |  |  |  |  |

|   |       |       | 0 1 1 IRQ7                                                                        |  |  |  |  |

|   |       |       | 1 0 0 IRQ10                                                                       |  |  |  |  |

|   |       |       | 1 0 1 IRQ11<br>1 1 0 IRQ15                                                        |  |  |  |  |

|   |       |       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                             |  |  |  |  |

|   | D4    | FLSH  | FLASH MEMORY                                                                      |  |  |  |  |

|   | 04    | FLOH  |                                                                                   |  |  |  |  |

|   | D3    | OUT3  | This says that a 32K flash memory is in the ROM socket. It may be written to.     |  |  |  |  |

|   | D2    | OUT2  | The three output pins follow the data stored on these bits.                       |  |  |  |  |

|   | D1    | OUT1  | The three output pins follow the data stored on these bits.                       |  |  |  |  |

|   | DI    | 0011  |                                                                                   |  |  |  |  |

|   | D0    | 0WS8  | 8-BIT ZERO WAIT STATE ENABLE                                                      |  |  |  |  |

|   | 20    | 01100 | If set to 0: Zero Wait State disabled . Every memory byte access will include 4   |  |  |  |  |

|   |       |       | states. If set to 1: Zero Wait State enabled, 2 wait states will be included with |  |  |  |  |

|   |       |       | every memory byte access.                                                         |  |  |  |  |

|   |       |       |                                                                                   |  |  |  |  |

| L |       |       |                                                                                   |  |  |  |  |

# 4.8 LA ADDRESS REGISTER (LAAR) Offset 0x05 (Read/Write)

The LA address bits are used to decode the high order memory address when operating in 16-bit memory access mode. This register contains the LA bits which the memory will be compared against. This register has LA address bits LA23-19. Bits A18 and A17 are selected in the Memory Address register.

|          | D7<br>M16EN | . D6<br>L16EN | D5<br>OWS16 | D4<br>LA23 | D3<br>LA22 | D2<br>LA21 | D1<br>LA20 | D0<br>LA19 |

|----------|-------------|---------------|-------------|------------|------------|------------|------------|------------|

| RESET    | 0           | 0             | 0           | 0          | 0          | 0          | 0          | 1          |

| INITIAL  | 0           | 0             | 0           | 0          | 0          | 0          | 0          | 1          |

| POWER-UP | 0           | EE            | EE          | EE         | EE         | EE         | EE         | EE         |

| RECALL   | 0           | EE            | EE          | EE         | EE         | EE         | EE         | EE .       |

| BIT  | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7   | M16EN   | ENABLE 16 BIT MEMORY ACCESS<br>Set to 1 to enable 16-bit memory access. This bit should only be set when all<br>other interrupts have been disabled.                                                                                                                                                                                                                                                    |

| D6   | L16EN   | ENABLE 16 BIT LAN OPERATION<br>Set to 1 to allow 16-bit operation between the LAN controller and the on-board<br>RAM memory. This bit has another function, when operating in 8 bit mode only<br>8K byte RAM will be used. In 16-bit mode, the entire RAM (either 16K byte or<br>64K byte) will be available.                                                                                           |

| D5   | 0WS16   | OWS 16 ÉNABLE                                                                                                                                                                                                                                                                                                                                                                                           |

| D4-0 | LA23-19 | Enable zero wait state operation when running 16 bit memory accesses.<br>LA MEMORY DECODE BITS<br>Must be set to select the address at which the shared memory is to be accessed.<br>These bits correspond to system memory address bits LA23 through LA19. For<br>example, to select and enable base address register D0000, write a 0x01 to this<br>register and 0x68 to the memory address register. |

# 4.9 INITIALIZE JUMPER REGISTER Offset 0x06 (Read)

| PIN                                      | NAME                                  | DESCRIPTION                                                                                                                                                                                                             |

|------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7<br>D6<br>D5<br>D4,3<br>D2<br>D1<br>D0 | IN2<br>IN1<br>INIT2<br>INIT1<br>INIT0 | Undefined, will read a "0".<br>INPUT PINS<br>These bits read the state of the 2 input pins.<br>Undefined, will read a "0".<br>INITIALIZE PINS<br>These read the contents of the 3 initialize pins. They are active low. |

## 4.10 GENERAL PURPOSE REGISTER 2 (GP2) Offset 0x07 (Read/Write)

The GP2 is a byte register which is completely undefined and may be used as needed by software.

|          | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------|----|----|----|----|----|----|----|----|

| RESET    | ?  | ?  | ?  | ?  | ?  | ?  | ?  | ?  |

| INITIAL  | EE |

| POWER-UP | EE |

| RECALL   | EE |

## 4.11 LAN ADDRESS REGISTERS (LAR) Offset 0x08-0x0F

The LAN Address Registers contains the unique LAN address that has been assigned to a board. It should be read and written to the LAN controller. Bytes of the LAN address may be read at the offsets given below.

|          | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|----------|----|----|----|----|----|----|----|----|--|

| RESET    | ?  | ?  | ?  | ?  | ?  | ?  | ?  | ?  |  |

| INITIAL  | EE |  |

| POWER-UP | EE |  |

| RECALL   | EE |  |

| OFFSET | DESCRIPTION                                                                              |

|--------|------------------------------------------------------------------------------------------|

| 0x08   | Globally Assigned Address Block (LSB)                                                    |

| 0x09   | Globally Assigned Address Block                                                          |

| Dx0A   | Globally Assigned Address Block (MSB)                                                    |

| Dx0B   | Unique Board Address (LSB)                                                               |

| Dx0C   | Unique Board Address                                                                     |

| Dx0D   | Unique Board Address                                                                     |

| Dx0E   | WD Board ID Byte                                                                         |

| 0x0F   | Checksum, causes the twos complement sum of all 8 LAN Address Register bytes to be 0xFF. |

|        | Checksum, causes the twos complement sum of all 8 LAN Address Regist                     |

## 5.0 TIMING DIAGRAMS

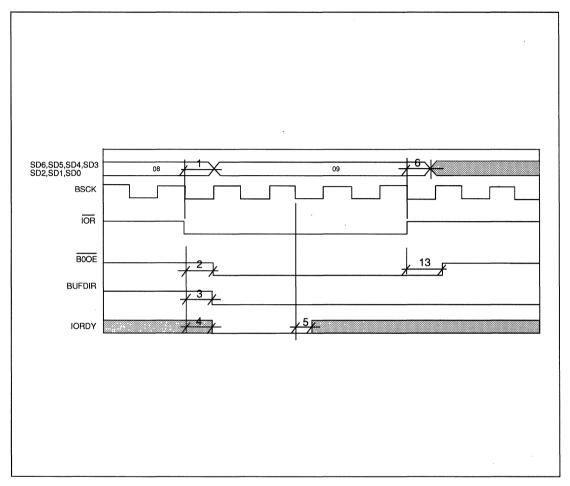

FIGURE 5-1. I/O READ

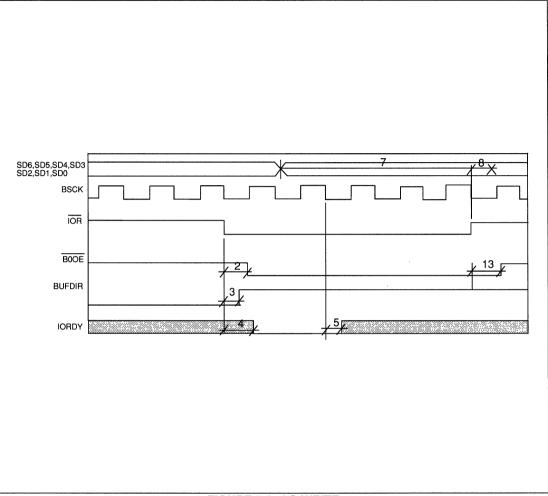

FIGURE 5-2. I/O WRITE

|                                                                      | ,                    |

|----------------------------------------------------------------------|----------------------|

| SA18,SA17,SA16,<br>SA15,SA14,SA13<br>SA6,SA5,SA4,SA3,<br>SA2,SA1,SA0 |                      |

| ROM15<br>ROM14<br>BSCK                                               | 15p                  |

| AEN<br>SMEMR<br>ROMOE<br>BOOE<br>BUFDIR                              |                      |

| IORDY                                                                |                      |

|                                                                      | FIGURE 5-4. ROM READ |

<u>38</u>

1/

| SA6,SA5,SA4,SA3,<br>SA2,SA1,SA0 | X        |        |

|---------------------------------|----------|--------|

| BSCK                            |          |        |

| BALE                            |          |        |

| SMEMR                           | <br>     |        |

| BOOE                            | <u> </u> | 13     |

| B1OE<br>SWAP                    |          | 17     |

| SBHE                            |          |        |

| BUFDIR                          | <u> </u> |        |

| RAMOE                           | <u> </u> | / 24 / |

| RAMWR                           |          |        |

| RMCS1<br>RMCS0                  |          |        |

| 10000                           |          |        |

|                                 |          |        |

|                                 |          |        |

|                                 |          |        |

|                                 |          |        |

|                                 |          |        |

|                                 |          |        |

|                                 |          |        |

FIGURE 5-7. RAM READ, 16 BIT

# FIGURE 5-8. OWS, 8 BIT

|                |              |            |      |                                                                                                                 | -   |

|----------------|--------------|------------|------|-----------------------------------------------------------------------------------------------------------------|-----|

|                |              |            |      |                                                                                                                 |     |

|                |              |            |      |                                                                                                                 |     |