June, 1984 Communication Products Handbook

STATISTICS CAL

king the leading

Kille

William A. B. R. William

Postility of the second

ma

A REAL PROPERTY AND A REAL

THE SUL RANK

2d

ork.

10

3/85

June, 1984 Communications Products Handbook

#### COPYRIGHT© 1984 WESTERN DIGITAL CORP. ALL RIGHTS RESERVED

This document is protected by copyright, and contains information proprietary to Western Digital Corp. Any copying, adaptation, distribution, public performance, or public display of this document without the express written consent of Western Digital Corp. is strictly prohibited. The receipt or possession of this document does not convey any rights to reproduce or distribute its contents, or to manufacture, use, or sell anything that it may describe, in whole or in part, without the specific written consent of Western Digital Corp.

### Making The Leading Edge Work For You.

This handbook is designed for you, the engineer. It's intended to be a useful tool, enabling you to make a preliminary evaluation of our products and later, with samples in hand, design our products into your own systems.

The data in these pages have been reviewed by our Marketing, Engineering, Manufacturing, and Quality groups. Now we would like you to review the information we've provided and tell us how we can improve it. Please feel free to suggest any changes, additions, or clarifications that occur to you. And don't hesitate to call to our attention any sins of omission or commission we may have made.

We're eager to help upgrade the quality of information our industry provides to its customers. So, please, help us. Direct your comments to:

Corporate Communications Director WESTERN DIGITAL CORPORATION 2445 McCabe Way Irvine, CA 92714 (714) 863-0102

## WESTERN DIGITAL

### **Regional and District Sales Offices**

### Northeastern United States/Eastern Canada

70 Atlantic Avenue Marblehead, MA 01945 Phone: (617) 631-6466 TWX: 710-347-1060

72 Sumit Avenue Montvale, NJ 07645 Phone: (201) 930-0700 TWX: 710-991-8360

### North Central United States

3600 West 80th Street Suite 620 Bloomington, MN 55431 Phone: (612) 835-1003 TWX: 910-576-2417

1301 West 22nd Street Suite 217 Oakbrook, IL 60521 Phone: (312) 655-8781 TWX: 910-651-3193

### Southern United States

1015 Semoran Blvd. Summit Plaza II, Suite D Casselberry, FL 32707 Phone: (305) 331-4434 TWX: 810-853-0297

4950 Westgrove Dr., Suite 115 Dallas, TX 75248 Phone: (214) 248-6785 TWX: 910-997-0509

2300 W. Meadowview Road Suite 209 Greensboro, NC 27407 Phone: (919) 299-6733 TWX: 510-922-7309

### Europe

28/30 Upper High Street Epsom, Surrey KT174QJ United Kingdom Phone: 44-3727-42178 Telex: 851-925796

Deutschland GMBH Prinzregentenstrasse 120/III D-8000 Muenchen 80 Federal Republic of Germany Phone: 011-49-89-470-7021 TWX: 841-521-4568

### Western United States/Western Canad

1151 Dove Street Suite 170 Newport Beach, CA 92660 Phone: (714) 851-1221 TWX: 910-595-2430

5677 Oberlin Drive, Suite 202 San Diego, CA 92121 Phone: (619) 457-1777 TWX: 910-337-1257

201 San Antonio Circle Building E, Suite 172 Mountain View, CA 94040 Phone: (415) 941-0216 TWX: 910-379-5038

5743 Corsa Ave. Suite 201 Westlake Village, CA 91361 Phone: 818-991-2556

### WESTERN DIGITAL

2445 McCABE WAY IRVINE, CALIFORNIA 92714

(714) 863-0102, TWX 910-595-1139

### **Table of Contents**

| Functional Index                                   | vii |

|----------------------------------------------------|-----|

| Numerical Index                                    | ix  |

| System Product Quality/Reliability                 | 1   |

| Quality/Reliability to Leading Edge Technology     | 5   |

| Announcing Burn-In Program Availability/Warranties | 11  |

|                                                    | 13  |

|                                                    | 15  |

| Local Area Network Products                        | 17  |

|                                                    | 87  |

| Asynchronous/Bisynchronous Products 1              | 77  |

| Data Security Products                             | 67  |

| Video Products                                     |     |

| Support Products                                   | 27  |

| Ordering Information                               |     |

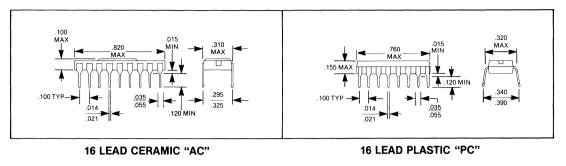

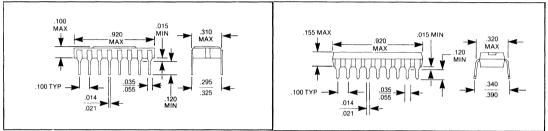

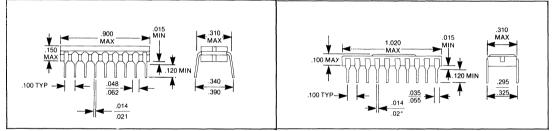

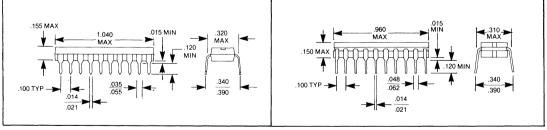

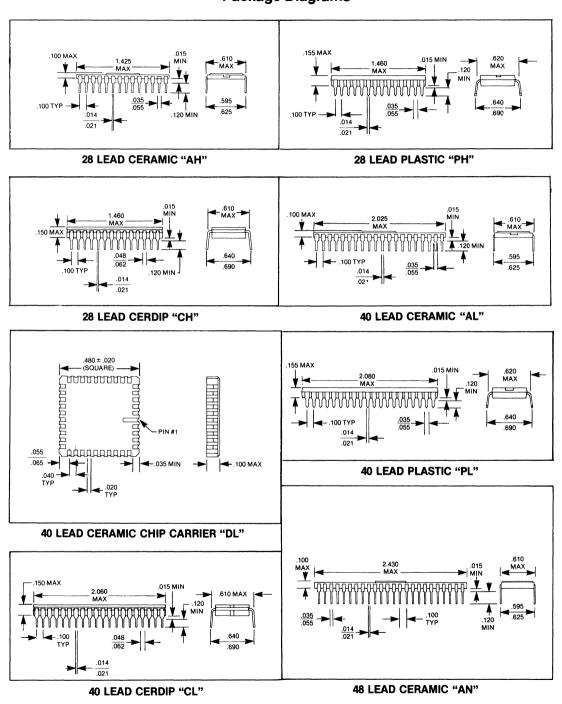

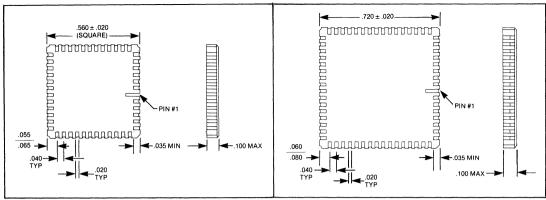

| Package Diagrams                                   | 84  |

| Pin Functional Compatibility Guide                 | 86  |

| Storage Management Product Overview                | 87  |

| Terms and Conditions                               | 89  |

Bulletin: New products soon to be announced.

Advance Information: This product has not been produced in volume and is subject to functional and timing revisions. Please contact Western Digital Corporation for current information.

**Preliminary:** This product is limited production and may be subject to change after device characterization has been completed. Please contact Western Digital Corporation for current information.

**Final:** This product is in full production and intended for normal commercial applications. For military, extended temperature, burn-in, or hi-rel applications, contact Western Digital Corporation for information regarding further processing.

Application Note: This is specific application information related to the designated product(s).

vi

### **COMMUNICATION PRODUCTS**

### **Functional Index**

### Part Number

### LOCAL AREA NETWORK PRODUCTS

| WD2840 Local Network Token Access Controller                                                                                                                                                                                                                                                                                                                                             | 53<br>65<br>69           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| SDLC/HDLC/X.25 PRODUCTS                                                                                                                                                                                                                                                                                                                                                                  |                          |

| WD2511 X.25 Packet Network Interface (LAPB)<br>WD2511 Application Note<br>WD1935 Synchronous Data Link Controller (SDLC)<br>WD1935 Application Note                                                                                                                                                                                                                                      | 117<br>137               |

| ASYNCHRONOUS/BISYNCHRONOUS PRODUCTS                                                                                                                                                                                                                                                                                                                                                      |                          |

| WD2123 Dual Enhanced Universal Communications Element (DEUCE)         WD8250 Asynchronous Communications Element         TR1863/1865 Universal Asynchronous Receiver/Transmitter (UART)         TR1863/1865 Application Note         UC1671 Asynchronous/Synchronous Transmitter/Receiver (ASTRO)         WD1993 Arinc 429 Receiver/Transmitter and Multi-Character Receiver/Transmitter | 195<br>213<br>223<br>235 |

| DATA SECURITY PRODUCTS                                                                                                                                                                                                                                                                                                                                                                   |                          |

| WD2001/WD2002 Data Encryption Device                                                                                                                                                                                                                                                                                                                                                     |                          |

| VIDEO PRODUCTS                                                                                                                                                                                                                                                                                                                                                                           |                          |

| WD8275 Programmable CRT Controller                                                                                                                                                                                                                                                                                                                                                       |                          |

| SUPPORT PRODUCTS                                                                                                                                                                                                                                                                                                                                                                         |                          |

| WD1943 Dual Baud Rate Clock                                                                                                                                                                                                                                                                                                                                                              | 335                      |

viii

### **Numerical Index**

| rrt Number   | Page |

|--------------|------|

| D1510        | 335  |

| 21671        | 235  |

| R1863/1865   | 213  |

| D1935        |      |

| D1943        | 327  |

| D1993        | 251  |

| D2001/WD2002 | 267  |

| D2123        | 177  |

| D2511        |      |

| D2840        | 17   |

| D4028        | 83   |

| D8250        | 195  |

| D8275        | 287  |

| D8276        | 309  |

| D9914        | 339  |

ix

х

## WESTERN DIGITAL

### System Product Quality/Reliability

### QUALITY PROGRAM DESCRIPTION

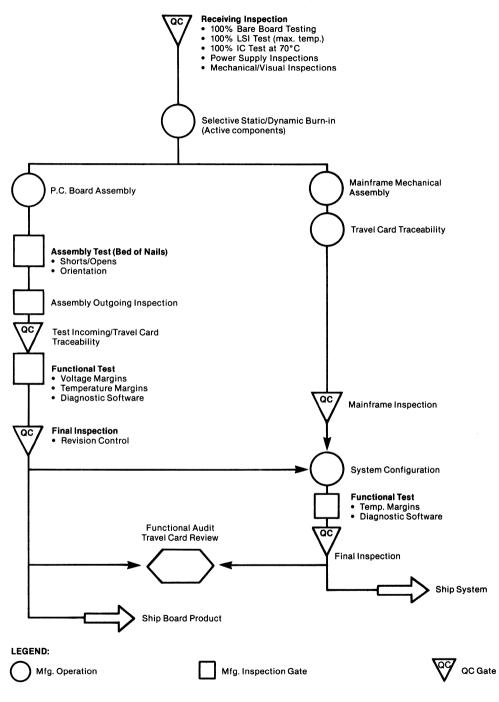

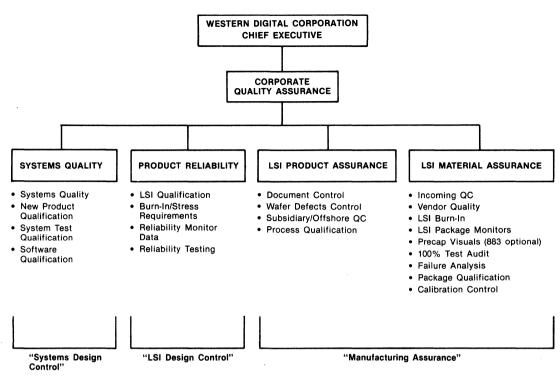

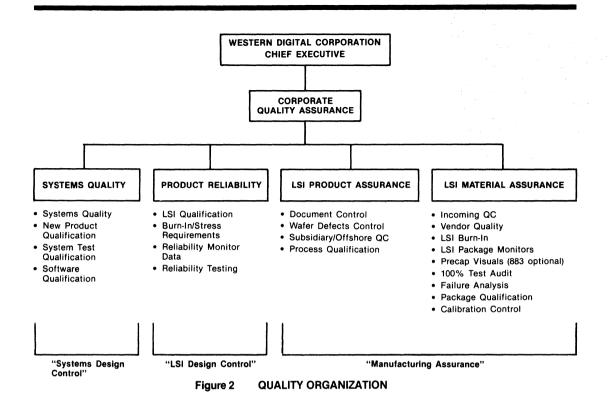

The Quality Organization shown on the attached organization chart (Figure 2) reports directly to the President of Western Digital. It assures compliance to design control, quality and reliability specifications pursuant to corporate policy. Quality assurance provisions are derived in part from MIL-Q-9858, as applied to high grade commercial products.

### CORPORATE QUALITY POLICY

It is the policy of Western Digital Corporation that every employee be committed to quality excellence in producing products/processes which conform to acceptable requirements. The total quality program is managed and monitored by the quality assurance organization. Quality assurance is chartered to review marketing product requirements, qualify hardware and software designs, certify manufacturing operations and monitor performance/control conformance to product specifications.

Primary responsibility for execution of the quality program rests with functional organizations to design, produce, and market high quality and high reliability products specified to our customers.

### DESIGNING FOR RELIABILITY

The premise upon which board and system manufacturing operations are based is that quality is planned and designed-in, not screened-in or selected. A welltested, high-quality design is far more reliable than a marginal design with any amount of burn-in or fixes. To assure top quality design, Western Digital maintains one of the most experienced board/system design staffs in the industry. A tightly controlled design review team comprising members from Quality Assurance, Marketing, Manufacturing and several experienced design engineers, provides review of each new design several times during its development to ensure widest possible performance margins. The production release procedure assures a checklist for:

- Test Method/Program Qualifications

- Characterization Report

- Field Test (Beta Test) Report

- Product Qualification Audit

- Documentation Package Release for Document Control

- Software/Diagnostics Qualification

### MAINTAINING QUALITY/RELIABILITY IN PRODUCTION

The Quality Control Testing Flow Chart shown on Figure 1 defines the exact stages contained in the production process. Internally manufactured LSI components undergo 100% testing at maximum specified operating temperatures as well as strict quality controls defined to assure high quality and reliability. Components not designed and manufactured by Western Digital are also 100% screened as shown in photos during incoming inspection at 70°C. The tests performed include selective active component burn-in performed at 125°C for 160 hours to insure guaranteed levels of reliability. This 125°C accelerated testing eliminates defects that cannot effectively be accelerated by burning-in boards and systems which have temperature limitations. Key quality control procedures include:

- Incoming Inspection Procedure

- In-Process Travel Card Traceability

- Workmanship Standards

- Quality Corrective Action Notice/MRB Procedure

- Quality Audit Procedure

### **PRODUCT FINAL TEST/CORRECTIVE ACTION**

All boards are 100% in-circuit tested and 100% functional tested for acceptable performance according to applicable test specifications on testers qualified by QA. Products are tested at maximum specified temperature and voltage margins using diagnostic software to ensure greater performance margins. Failures are logged on a travel card specifically designed to insure traceability to manufacturing steps and to maintain failure records for QA corrective action.

If the board is designed to perform in a host system, further diagnostics are performed in an environment configured to actual customer requirements.

#### **PRODUCT ACCEPTANCE**

Upon completing the final test, the board/system undergoes QC final workmanship standards inspection and selective samples are audited to the functional product specification to guarantee quality at specified operating margins to the customer.

Bare board test

Incoming IC 100% screening

In-circuit test

Complete documentation available for you at our facility.

3

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change specifications at anytime without notice.

## WESTERN DIGITAL

ORPORATION

### Quality/Reliability To Leading Edge Technology

### QUALITY PROGRAM DESCRIPTION

The Quality Organization shown in Figure 2 assures compliance to design control, quality and reliability specifications, pursuant to corporate policy.

### CORPORATE QUALITY POLICY

It is the policy of Western Digital Corporation that every employee be committed to quality excellence in producing products/processes which conform to acceptable requirements. The total quality program is managed and monitored by the quality assurance organization. Quality assurance is chartered to review marketing product requirements, qualify hardware and software designs, certify manufacturing operations and monitor performance/control conformance to product specifications.

Primary responsibility for execution for the quality program rests with functional organizations to design, produce and market high quality and high reliability products specified to our customers.

### LSI QUALITY ASSURANCE PROGRAM HIGHLIGHTS

- LSI manufacturing assurance provisions are derived in part from MIL-M-38510 and MIL-STD-883B as applied to high grade commercial components.

- All process raw materials used in the Mask/Wafer fabrication and assembly operations are monitored by Material Assurance.

- Material Assurance maintains a thorough control of incoming material and has developed unique "use/stress tests" (look ahead sample build acceptance) which critical material must pass before acceptance.

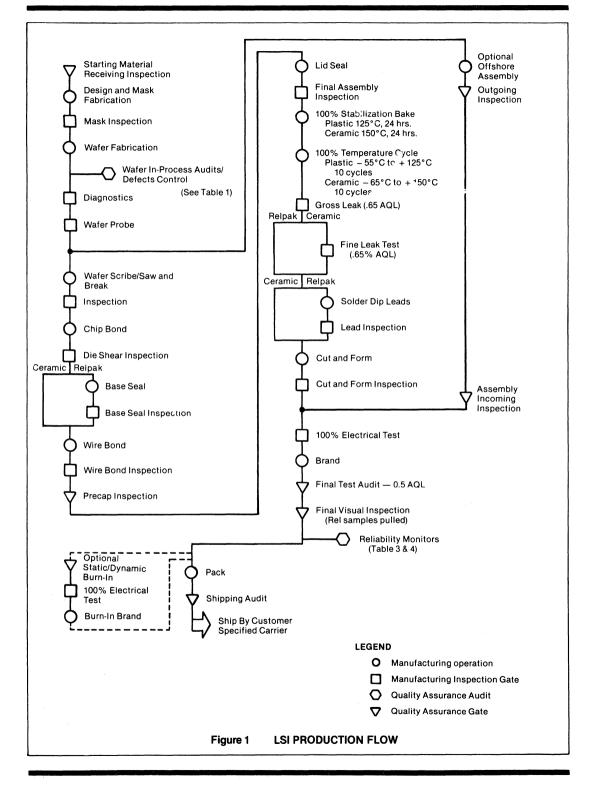

- The Product Assurance Department continuously monitors the internal and external manufacturing flow (shown in Figure 1) and issues process control reports displaying detailed data and trends for the associated areas.

- Document control is an integral part of Product Assurance. All specifications are issued and controlled by this activity.

- The Western Digital Malaysian assembly operation uses specifications and quality control provisions controlled by Document Control. Indicators of Malaysia quality are reviewed weekly.

- Purchased FAB and assembly operations are individually qualified and are certified against standard specifications during vendor qualification and monitored against reliability criteria.

- Defect control within the process assures the highest levels of built-in reliability.

- Quality audits and gates are located throughout the manufacturing process in order to assure a stable process and thus, a quality product to our customers. Figure 1 illustrates the manufacturing/ screening/inspection flow diagram and identifies the steps as they relate to the production of LSI devices.

- Testing assures quality margins through 100% testing by manufacturing and, in addition, all products must pass a specified AQL sample test performed by QA at maximum operating temperature as follows:

| SUBGROUPS INSPECTIO                                                       | N LEVEL  |

|---------------------------------------------------------------------------|----------|

| Subgroup 1 — Final 100% Electrical<br>Audit @ Max °C                      | 0.5 AQL* |

| Subgroup 2 — Visual (Marking, Lead<br>Integrity, Package, Verify customer |          |

| shipper)                                                                  | 1.0 AQL  |

| Subgroup 3 — Shipping Visual Audit                                        | 1.0 AQL  |

\*The double sampling techniques used allow considerably better AQL's in most all cases.

LSI devices are 100% tested on industry standard test systems like that shown below. Quality outgoing testing (auditing) is done on the Fairchild Sentry Series 20 where possible to allow better correlation with customers.

### **Reliability Means Lasting Value**

### • DESIGNING FOR RELIABILITY

The production release procedure for an LSI device is designed to assure maximum reliability with a Quality checklist for:

- Test program qualifications

- Characterization report

- Field test (Beta Test) report

- Reliability Lifetest Qualifications

- Infrared Thermal Analysis

- Static Protection

All new devices and major process changes must pass reliability qualification before incorporation into production using the criteria defined in Tables 2-4. The infrared microscope shown on the right assures optimum burn-in temperatures and margins of safety. The dynamic burn-in system shown on the right is one of two custom designed systems which assure protective device isolation during burn-in.

### • MAINTAINING RELIABILITY IN PRODUCTION

Process defects control are defined to continually measure built-in reliability, as measured by the following criteria:

| PROCESS RELIABILITY CONTROL            | METHOD                                               | CONDITION                                             | SAMPLE*                                             |

|----------------------------------------|------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|

| Subgroup 1 — Defects Control           |                                                      |                                                       |                                                     |

| a. Oxide Integrity                     | Non-destructive<br>bubble test                       | Pinhole defect density                                | 5 wafers                                            |

| b. Polysilicon Integrity               | SEM Analysis                                         | Visual                                                | 5 wafers                                            |

| Subgroup 2 — Electro-Migration Control |                                                      |                                                       |                                                     |

| Metal Step Coverage                    | MIL-STD-883<br>Method 2018                           | SEM Analysis                                          | 5 wafers                                            |

| Subgroup 3 — Defect Density            | Critical layers<br>Field<br>Gate<br>Contact<br>Metal | Visual of Photo defects<br>(Defects/in <sup>2</sup> ) | 8 wafers<br>each layer                              |

| Subgroup 4 — Passivation/Insulation    |                                                      |                                                       |                                                     |

| Integrity                              | MIL-STD-883 Method<br>2021                           | Visual of Pinhole<br>defect density                   | Final Silox<br>5 wafers<br>Intermediate<br>5 wafers |

TABLE 1

\*Inspection intervals are defined by the in-line process control data reviewed on a lot-by-lot basis.

### • PROGRAMS TO ASSURE OPTIMUM RELIABILITY

Improved levels of reliability are available under custom reliability programs using static and dynamic burn-in to further improve reliability. These programs focus on MOS failure mechanisms as follows:

| FAILURE<br>MECHANISM | EFFECT ON<br>DEVICE | ESTIMATED<br>ACTIVATION ENERGY | SCREENING<br>METHOD                 |

|----------------------|---------------------|--------------------------------|-------------------------------------|

| Slow Trapping        | Wearout             | 1.0 eV                         | Static Burn-In                      |

| Contamination        | Wearout/<br>Infant  | 1.4 eV                         | Static Burn-In                      |

| Surface Charge       | Wearout             | 0.5-1.0 eV                     | Static Burn-In                      |

| Polarization         | Wearout             | 1.0 eV                         | Static Burn-In                      |

| Electromigration     | Wearout             | 1.0 eV                         | Dynamic Burn-In                     |

| Microcracks          | Random              |                                | 100% Temp. Cycling                  |

| Contacts             | Wearout/<br>Infant  | _                              | Dynamic Burn-In                     |

| Oxide Defects        | Infant/<br>Random   | 0.3 eV                         | Dynamic Burn-In<br>at max. voltage  |

| Electron Injection   | Wearout             | _                              | Low Temp. Voltage<br>Operating Life |

#### FAILURE MECHANISMS IN MOS

#### **Temperature Acceleration of Failure**

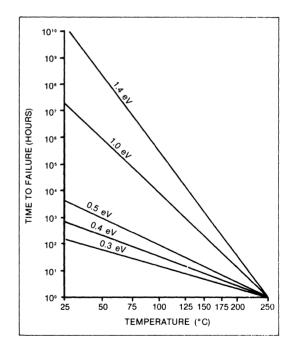

The Arrhenius Plot defines a failure rate proportional to exp(-Ea/kt) where Ea is the activation energy for the failure mechanism. The figure on the right indicates that lower activation energy failures are **not** effectively accelerated by temperature alone; hense, maximum voltage operation is selectively applied to optimize the burn-in process.

#### Static Burn-In (125°C — 48 hours or 160 hours)

Provided on a sample basis for process monitor/control of 0.5 eV - 1.0 eV failure mechanisms. 100% static burn-in may be specified at an additional cost. However, static burn-in is considered only partially effective for internal LSI gates at logic "O" levels.

### Dynamic Burn-In (Pattern test/125°C — 8 hours to 160 hours)

Accelerated functional dynamic operating life effectively controls internal MOS gate defects buried from external pin access. The input pattern is optionally pseudo-random or fixed pattern programmable to simulate 1000-3000 hours of field operation at maximum operating voltage(s).

### High-Rel "K" Testing Program

General conformance to MIL-STD-883B method 5004.4, Class B with static Burn-In (Dynamic Burn-In may be specified as an option).

### LSI RELIABILITY STANDARDS

### TABLE 2 STANDARD RELIABILITY LEVELS

| TEST                              | METHOD               | CONDITION         | FAILURE                                     |

|-----------------------------------|----------------------|-------------------|---------------------------------------------|

| Infant<br>Mortality<br>(see note) | Static<br>Burn-In    | 125°C — 160 hrs.  | <0.5%                                       |

| Long Term<br>Failure Rate         | Dynamic<br>Life Test | 125°C — 1000 hrs. | <.05%/1000 hrs.<br>@ 55°C<br>60% Confidence |

\*NOTE: Devices failing the infant mortality target remain on burn-in until acceptable failure rates are obtained.

TABLE 3 GROUP A DEVICE RELIABILITY MONITORS

| TEST                               | METHOD | CONDITIONS                                                      | LTPD |

|------------------------------------|--------|-----------------------------------------------------------------|------|

| Subgroup 1                         |        |                                                                 |      |

| a. Internal Visual                 |        |                                                                 | 15   |

| b. Thermal Shock                   | 1011   | Test Failure Used (cond. B or C)                                |      |

| c. Bond Strength                   | 2011   | Test Failures (cond. B)                                         |      |

| d. Die Shear Strength              | 2019   | Test Failures                                                   |      |

| Subgroup 2                         |        |                                                                 |      |

| a. Seal — Gross Leak               |        | Fluorocarbon detection 10 - 3<br>atm/cc/sec                     | 15   |

| b. Seal — Fine Leak                | 1014   | Test Condition A                                                |      |

| Subgroup 3                         |        |                                                                 |      |

| a. Rotating Steady State Life Test | 1005   | Static 160 hr. Burn-In 125°C<br>plus 125°C Lifetest — 1000 hrs. | 5    |

| b. Electrical Parameters           | _      | Final electrical @ 25°C (with data @ 70°C)                      |      |

#### TABLE 4 GROUP B PACKAGE RELIABILITY MONITORS

| TEST                                           | METHOD | CONDITIONS                                | LTPD |

|------------------------------------------------|--------|-------------------------------------------|------|

| Subgroup 1                                     |        |                                           |      |

| a. Thermal Shock                               | 1011   | Test Condition B or C                     | 15   |

| b. Temperature Cycling                         | 1010   | Test Condition B or C                     |      |

| c. Seal — Gross Leak                           | -      | Fluorocarbon detection 10-3<br>atm/cc/sec |      |

| d. Seal — Fine Leak (ceramic)                  | 1014   | Test Condition A                          |      |

| e. Electrical Parameters                       | _      | Electrical at max -C                      |      |

| f. 85/85 Moisture Resistance<br>(plastic only) | _      | 85% RH/85°C for 1000 hours<br>PDA = 10%   |      |

| g. Electrical Parameters                       | _      | Final electrical @ 25°C                   |      |

| Subgroup 2                                     |        |                                           |      |

| a. High Temp. Storage                          | 1008   | Test Condition B or C                     |      |

| b. Mechanical Shock                            | 2002   | Test Condition B                          | 15   |

| c. Seal — Gross Leak                           | -      | Fluorocarbon detection 10-3<br>atm/cc/sec |      |

| d. Seal — Fine Leak<br>(ceramic)               | 1014   | Test Condition A                          |      |

| e. Electrical Parameters                       | _      | Final electrical @ 25°C/max. C            |      |

| Subgroup 3                                     |        |                                           |      |

| a. Lead Integrity                              | 2004   | Test Condition B2<br>(Lead Fatigue)       | 15   |

| b. Seal — Gross Leak                           | _      | Fluorocarbon detection 10-3<br>atm/cc/sec |      |

| c. Seal — Fine Leak<br>(ceramic)               | 1014   | Test Condition A                          |      |

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change specifications at anytime without notice.

# WESTERN DIGITAL

### Announcing Burn-In Program Availability/Warranties

Western Digital now supports customer burn-in requirements for both static and dynamic burn-in under the strict control of the QA-Reliability organization.

This burn-in provides high performance 125°C static and dynamic burn-in for 8-160 hours to eliminate infant mortality and improve reliability. This process is executed using custom modified 32Bit AEHR test commercial burn-in equipment which provide monitored fixed pattern or pseudorandom burn-in with power supply and resistor device pin isolation.

LSI dynamic burn-in is verified in all cases by the design engineer for proper functioning. LSI Chip sets are also individually burned-in with dynamic equivalency to assure high performance bundled reliability.

The warranty on the program will optionally provide certificate of compliance to standard or custom designed burn-in programs and guarantee <.05%/Khrs failure rate.

#### CAUTION

Using outside burn-in methods not certified as acceptable by Western Digital may result in voided warranty, due to mishandling, junction temperature stress, or electrical damage. Further, since most burn-in houses do not support testing, catastrophic system condition can result in substantial damage before a problem is identified.

One consistent problem experienced with outside LSI burn-in houses can cause reliability problems; namely, parallelling totem pole MOS outputs, where the output states are not predictable, can cause a single (or a few) device(s) to sink all the current from the other devices on the burn-in tray — electromigration or current zaps are both possible.

Western Digital burn-in diagrams, dated after 1/1/82, must be used exactly as shown and will be provided upon request.

SEE YOUR LOCAL REPRESENTATIVE FOR COSTS AND ORDERING INFORMATION ON THIS NEW PROGRAM.

12

1.

## WESTERN DIGITAL

Hi-Rel "K" Testing Program

### FEATURES

INCLUDES:

PRECAP VISUALS SEAL INTEGRITY POWER CONDITIONING ENHANCEMENT OPTIONS

GENERAL CONFORMANCE TO MIL-STD-883B, METHOD 5004.4, CLASS B (SEE COMPARISON ON FOLLOWING PAGES)

#### **GENERAL DESCRIPTION**

Western Digital's Hi-Rel "K" program is designed to provide high reliability devices for extended temperature environments. Individual enhancements may be specified to meet a customer's requirements.

INITIATE LOT PACKAGE PROBED WAFERS TRAVELER ac AUDIT FINE LEAK RECEIVING SCRIBE/SAW QC INSPECTION GROSS LEAK (QC) AUDIT BREAK/SORT CLEAN CUT/FORM LEADS INSPECT BACKSIDE ID PRE BURN-IN ac AUDIT ELECTRICALS CHIPBOND 'QC AUDIT **BURN-IN** 160 HRS @ 125°C INSPECT FINAL TEST WIRE BOND LID FINAL TEST 'ac' AUDIT άc INSPECT 0.5% AQL CLEAN/BAKE/SEAL BRAND CERTIFICATE OF CONFORMANCE TEMP CYCLE MOVE TO 10 CYCLES FINISHED -65°/+150°C AUDIT ac GOODS STABAKE 24 HRS 150°C PACK SHIP VIA CUSTOMER SPECIFIED CARRIER HI-REL "K" PROGRAM FLOW DIAGRAM

### COMPARISON OF MIL-STD-883 AND HI-REL "K" TEST PROGRAM

| MIL-STD-883B, METHOD 5004.4, CLASS B                                                                                                                                           | HI-REL "K" TEST                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3.1.1 Internal Visual</b><br>Method 2010.3<br>Test condition B                                                                                                              | All Hi-Rel "K" devices receive 100% inspections<br>prior to lid seal. These inspections together com-<br>prise criteria comparable to Mil-Std-883, method<br>2010.3, test condition B. |

| 3.1.2 Stabilization Bake<br>Method 1008.1<br>Test condition C<br>24 hours at 150°C                                                                                             | Same                                                                                                                                                                                   |

| <b>3.1.3 Temperature Cycling</b><br>Method 1010.2, Test condition C<br>- 65°C to 150°C for 10 cycles, with 10 minutes<br>dwell and 5 minutes maximum transfer time             | Same                                                                                                                                                                                   |

| 3.1.4 Constant Acceleration<br>Method 2001.2, Test condition E. 30,000 G stress<br>level                                                                                       | Not Done Unless Specified                                                                                                                                                              |

| 3.1.5 Visual Inspection<br>Visual inspection for catastrophic failures after<br>screens                                                                                        | Same                                                                                                                                                                                   |

| <ul> <li>3.1.6 Seal Method 1014.2</li> <li>(a) Helium fine leak — Test condition A<sub>1</sub>. Bomb condition 2 hours at 60 psig. Reject limit 5 x 10<sup>-8</sup></li> </ul> | Same                                                                                                                                                                                   |

| torr<br>(b) Flourocarbon gross leak — Test condition C                                                                                                                         | Same                                                                                                                                                                                   |

| 3.1.9 Interim (pre-burn-in) Electricals<br>Per applicable device specification                                                                                                 | Preburn-in test at 25°C. Must meet requirements of device data sheets.                                                                                                                 |

| <b>3.1.10 Burn-in Test</b><br>Method 1015.2 160 hours @ 125°C                                                                                                                  | Same                                                                                                                                                                                   |

| <b>3.1.13 Interim (Post burn-in) electricals</b><br>Per applicable device specification                                                                                        | Burn-in equipment isolate failures automatically to assure no harmful interaction.                                                                                                     |

| <ul> <li>3.1.15 Final Electrical Test</li> <li>(a) Static Tests <ul> <li>(1) 25°C</li> <li>(2) Minimum and Maximum Operating Temperatures</li> </ul> </li> </ul>               | Same                                                                                                                                                                                   |

| <ul><li>(b) Dynamic and Switching Tests at 25°C</li><li>(c) Functional Tests at 25°C</li></ul>                                                                                 |                                                                                                                                                                                        |

| 3.1.17 Qualification or Quality Conformance<br>Inspection and Test Sample Selection                                                                                            | Not done unless defined using method 5005 as a quide.                                                                                                                                  |

| 3.1.18 External Visual<br>Method 2009.2                                                                                                                                        | Same                                                                                                                                                                                   |

| WESTERN DIGITAL RELIABILITY ENHANCEMENT                                                                                                                                        |                                                                                                                                                                                        |

| 100% Temperature Testing                                                                                                                                                       | Extended High Temperature Storage                                                                                                                                                      |

| Level                                                                                                                                                                          | + 150°C for 24 hours standard, other time/tempera                                                                                                                                      |

|                                                                                                                                                                                | ture storage requirements available as required.                                                                                                                                       |

| Thermal, Shock (Liquid to Liquid)           Level.         0° to + 100°C, 15 cycles                                                                                            | <b>Dynamic Burn-In</b><br>Per note previously supplied.                                                                                                                                |

### **COMMUNICATION FAMILIES**

- UART Universal Asynchronous Receiver-Transmitter

- PSAT Programmable Synchronous/Asynchronous Transmitter

- PSAR Programmable Synchronous/Asynchronous Receiver

- USART Universal Synchronous/Asynchronous Receiver-Transmitter

- BOART Bus Oriented Asynchronous Receiver-Transmitter

- DLC Data Link Controller

15

### WESTERN DIGITAL

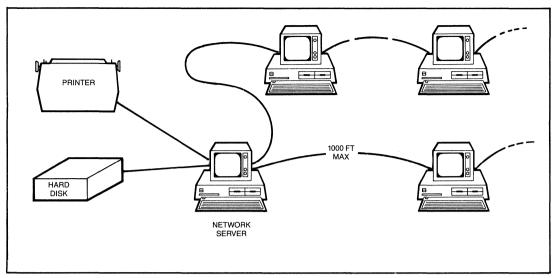

### WD2840 Local Network Token Access Controller

#### FEATURES

Broadcast Medium Independent (Coax, RF, CATV, IR, etc.)

Ω

- Up to 254 nodes

- Dual DMA/Highly efficient Memory Block Chaining

- Token based protocol

- · Acknowledge option on each datagram

- Adjustable fairness, stations may be prioritized

- · Frame format similar to industry standard HDLC

- Supports Global Addressing

- Diagnostic Support: Self-Tests, System and Network

- TTL Compatible

П

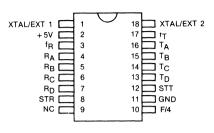

#### **PIN DESIGNATION**

### DESCRIPTION

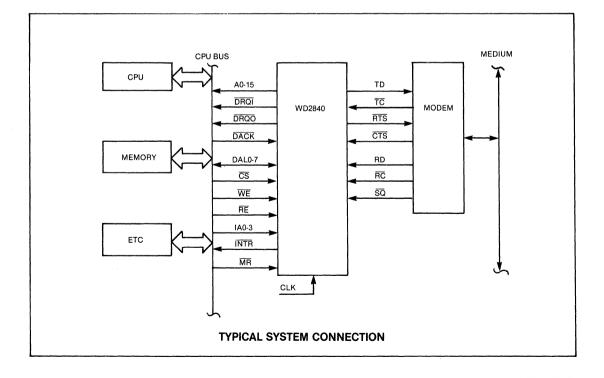

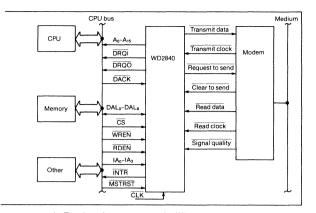

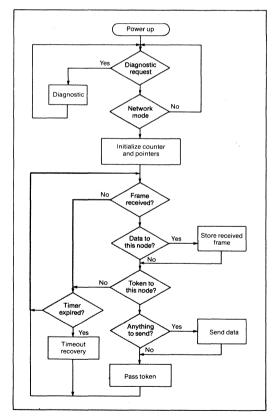

The WD2840 is a MOS/LSI device intended for local network applications, where reliable data communications over a shared medium is required. The device uses a buffer chaining scheme to allow efficient memory utilization. This scheme minimizes the host CPU time requirements for handling packets of data. The WD2840 frees the host CPU from extensive overhead by performing network initialization, addressing, coordination, data transmission, acknowledgements and diagnostics.

#### **APPLICATIONS**

The WD2840 is a general purpose Local Network Token Controller applicable to virtually all types of multi-point communications applications. The token protocol allows the sharing of one bus by up to 254 nodes. WD2840's will be designed into process control equipment, micro-computers, mini-computers, personal computers, proprietary micro-processor based applications, intelligent terminals, front-end processors, and similar equipment.

The great advantage for the design engineer is the ease with which he can implement a local network function. The WD2840 handles autonomously all major communications tasks as they relate to the local network function.

17

WD2840

A ARTHAN A A A

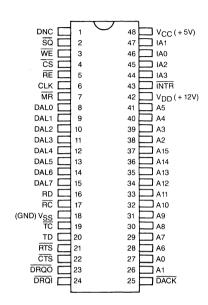

### 1.1 PIN DEFINITIONS

WD2840

| PIN NUMBER | SYMBOL   |                   | FUNCTION                                                                                                                                                                                                                                                            |  |

|------------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | DNC      | DO NOT CONNECT    | Leave pin open.                                                                                                                                                                                                                                                     |  |

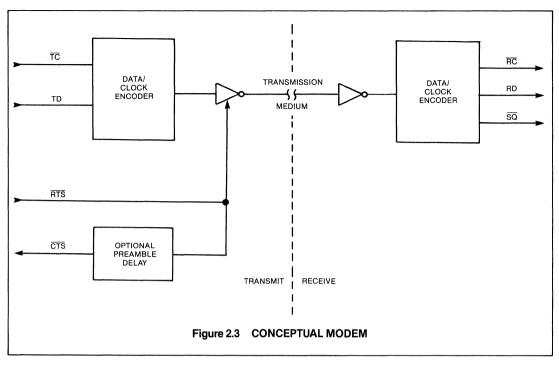

| 2          | SQ       | SIGNAL QUALITY    | An active low input which signals the WD2840<br>that a frame may be received. The modem may<br>negate this signal if its receive signal quality is<br>below a reliability threshold, ensuring that the<br>WD2840 will not accept the frame.                         |  |

| 3          | WE       | WRITE ENABLE      | The data on the DAL_are written into the<br>selected register when CS and WE are low. RE<br>and WE must not be low at the same time.                                                                                                                                |  |

| 4          | CS       | CHIP SELECT       | Active low chip select for CPU control of I/O registers.                                                                                                                                                                                                            |  |

| 5          | RE       | READ ENABLE       | The content of the selected register is placed on DAL when CS and RE are low.                                                                                                                                                                                       |  |

| 6          | CLK      | CLOCK             | Clock input used for internal timing.                                                                                                                                                                                                                               |  |

| 7          | MR       | MASTER RESET      | Initialize on active low. All registers reset to zero,<br>except control bit ISOL is set to 1. DACK must be<br>stable high before MR goes high. Status Register<br>0 is not defined at power-up (this register will be<br>set-up upon entry into the Network mode). |  |

| 8-15       | DAL0-7   | DATA ACCESS LINES | An 8-bit bi-directional three-state bus for CPU and DMA controlled data transfers.                                                                                                                                                                                  |  |

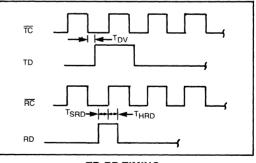

| 16         | RD       | RECEIVE DATA      | Receive serial data input.                                                                                                                                                                                                                                          |  |

| 17         | RC       | RECEIVE CLOCK     | This is a 1X clock input, and RD is sampled on the rising edge of RC.                                                                                                                                                                                               |  |

| 18         | VSS      | GROUND            | Ground.                                                                                                                                                                                                                                                             |  |

| 19         | TC       | TRANSMIT CLOCK    | A 1X clock input. TD changes on the falling edge of TC.                                                                                                                                                                                                             |  |

| 20         | TD       | TRANSMIT DATA     | Transmitted serial data output.                                                                                                                                                                                                                                     |  |

| 21         | RTS      | REQUEST-TO-SEND   | An open collector output which goes low when<br>the WD2840 is ready to transmit either data or<br>flags.                                                                                                                                                            |  |

| 22         | CTS      | CLEAR-TO-SEND     | An active low input which signals the WD2840 that transmission may begin.                                                                                                                                                                                           |  |

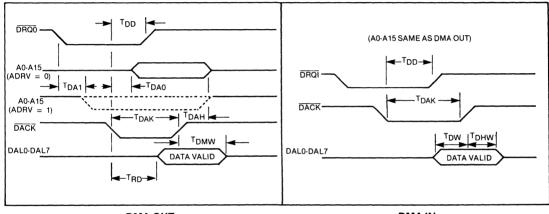

| 23         | DRQO     | DMA REQUEST OUT   | An active low output signal to initiate CPU bus request so that the WD2840 can output onto the bus.                                                                                                                                                                 |  |

| 24         | DRQI     | DMA REQUEST IN    | An active low output signal to initiate CPU bus requests so that data may be input to the WD2840.                                                                                                                                                                   |  |

| 25         | DACK     | DMA ACKNOWLEDGE   | An active low input from the CPU in response to DRQO or DRQI. DACK must not be low if CS and RE are low or if CS and WE are low.                                                                                                                                    |  |

| 26-41      | A0-A15*  | ADDRESS LINES OUT | Sixteen address outputs from the WD2840 for DMA operation.                                                                                                                                                                                                          |  |

| 42         | VDD      | POWER SUPPLY      | + 12VDC power supply input.                                                                                                                                                                                                                                         |  |

| 43         | INTR     | INTERRUPT REQUEST | An active low interrupt service request output.<br>Returns high when Interrupt Register is read.                                                                                                                                                                    |  |

| 44-47      | IA0-IA3* | ADDRESS LINES IN  | Four address inputs to the WD2840 for CPU controlled read/write operations with registers in the WD2840. If $ADRV = 0$ , these may be tied to A0-A3.                                                                                                                |  |

| 48         | Vcc      | POWER SUPPLY      | + 5VDC power supply input.                                                                                                                                                                                                                                          |  |

|            |          |                   |                                                                                                                                                                                                                                                                     |  |

#### WD2840 LOCAL NETWORK TOKEN ACCESS CONTROLLER

### INTRODUCTION

The WD2840 is a single LSI device which gives systems designers the ability to include networking capabilities into their unique products simply and economically.

A general and fundamental advantage to the use of complex LSI in a given system is the partitioning of required technical expertise. A successful user of the WD2840 need not be a data-communications expert, and further, he need not be at all concerned with low level network details (though these details are documented and available to him if he is interested). The potential user of the WD2840 must simply evaluate the communications facilities provided by the device to determine its suitability for the intended use.

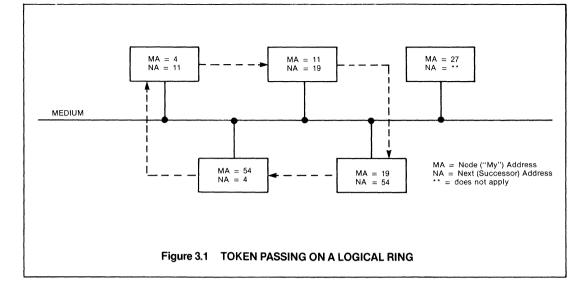

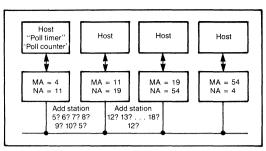

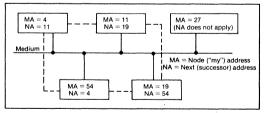

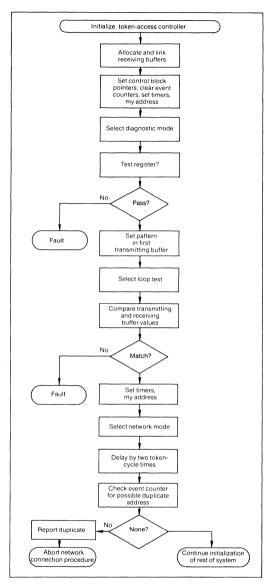

The WD2840 is designed to logically interconnect 2 to 254 user devices over a shared communications medium. Examples of typical mediums include coax cable, twisted pair bus, RF, and CATV. All network control functions, such as data framing and error checking, destination filtering, fair and adjustable transmission scheduling, and network initialization and fault recovery (caused by noise for example) are handled completely by the WD2840.

WD2840

The protocol implemented allows guaranteed station access intervals allowing applications in factory automation and other critical communications environments where "statistical delays" are not acceptable. The WD2840 token protocol also allows the addition and/or removal of stations to a network at anytime, including while operating.

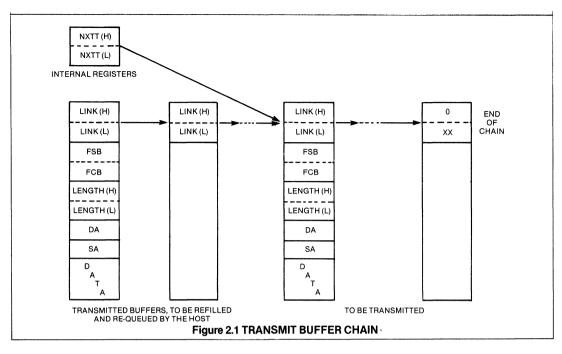

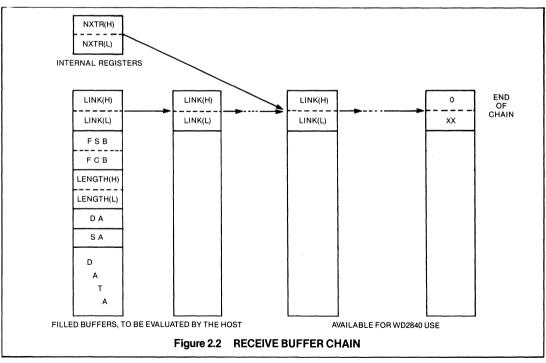

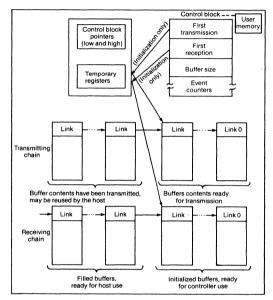

Serious attention has also been given to the user's interface to the device. The interface is a combination of conventional I/O registers and an elaborate DMA buffer chaining interface. This chaining feature allows the user much more efficient use of his system memory, particularly in situations where the maximum message sent over the network is much longer than the average size. This feature also allows the automatic queueing of messages independently of the user's consumption rate, in effect, speed decoupling the user's CPU and processing requirements from the network.

The WD2840 has several parameters (registers) that allow tailoring to the user's requirements. In this way, network priority and access ordering, to name two, can be manually set if desired.

Using an integrated version of these network algorithms saves not only the development costs already mentioned, but further, the total processing power required for the user's application is not increased. In other words, a CPU upgrade can likely be avoided by "distributing" the network processing task into LSI devices such as the WD2840.

#### SCOPE

This document differs from traditional LSI data sheets in that it details not only the LSI implementation of a function, but also defines the overall function in detail. Specifically, this document includes details of the communications protocol implemented by the WD2840 Token Access Controller.

The document is organized into three main sections:

SECTION ONE is much like a traditional data sheet including register descriptions, pin definitions, and hardware architecture.

SECTION TWO describes the interfaces to the WD2840. The network side is conventional, the host side consists of an elaborate DMA interface with control blocks and WD2840/host handshaking.

SECTION THREE details the network protocol implemented by the device. Normal operation, initialization, and the handling of error conditions are described.

### **1.2 DEVICE ARCHITECTURE**

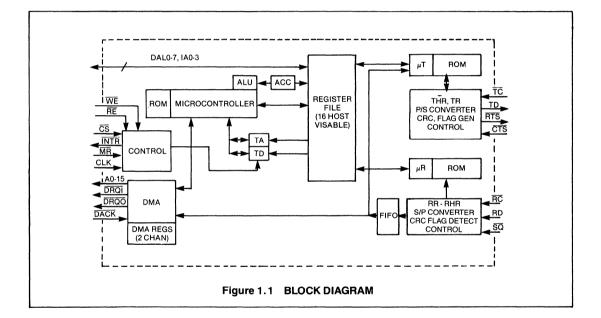

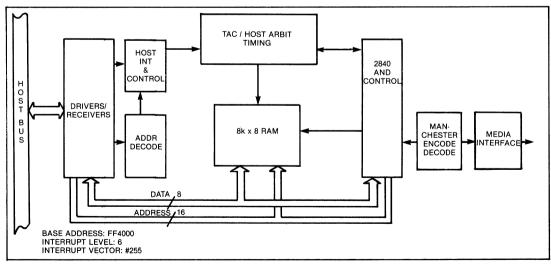

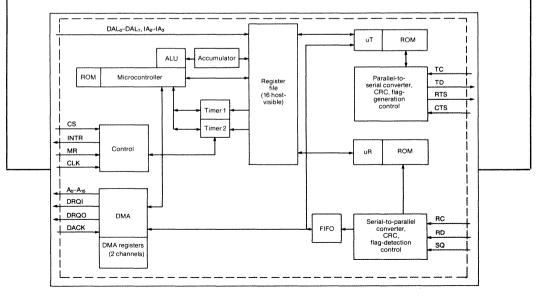

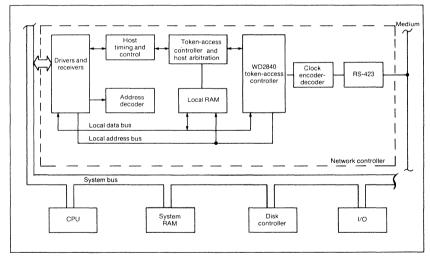

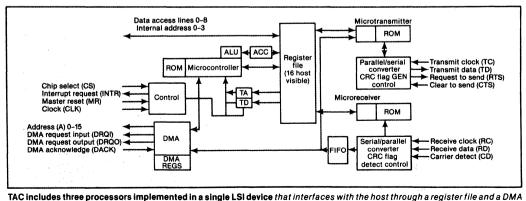

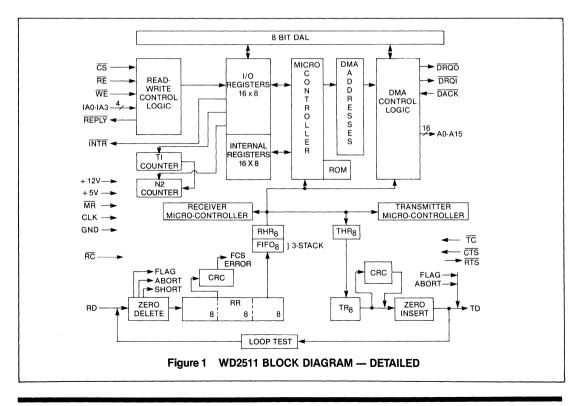

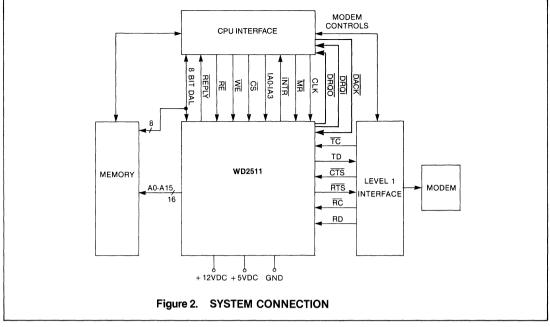

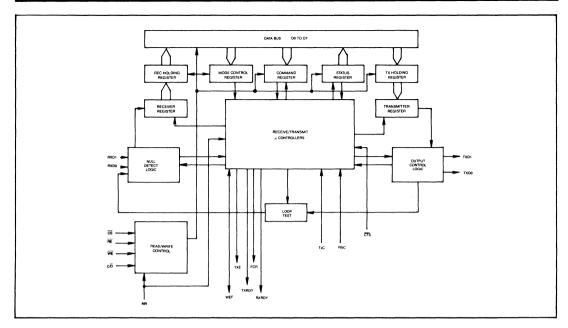

A detailed block diagram of the WD2840 is shown in Figure 1.1.

Mode control and monitor of status by the user's CPU is performed through the Read/Write Control circuit, which reads from or writes into registers addressed by IA0-IA3.

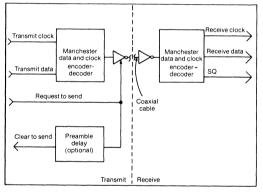

Transmit and receive data are accessed through DMA control. Serial data is generated and received by the bit-oriented controllers.

Internal control of the WD2840 is by means of three internal micro-controllers; one for transmit, one for receive, and one for overall control.

Parallel transmit data is entered into the Transmitter Holding Register (THR), and then presented to the Transmitter Register (TR) which converts the data to a serial bit stream. The Frame Check Sequence (FCS) is computed in the sixteen bit CRC register, and the results become the transmitted FCS.

Parallel receive data enters the Receiver Holding Register (RHR) from the 24 bit serial Receive Register (RR). The 24-bit length of RR prevents received FCS data from entering the RHR. The receiver CRC register is used to test the validity of the received FCS. A three level FIFO is included in the receiver.

The WD2840 sends all information, network control and user data, in blocks called frames. Each frame starts and ends with a single flag (binary pattern 0111110). In between flags, data transparency is provided by the insertion of a zero bit after all sequences of five contiguous one bits. The receiver will strip the inserted zero bits. (See section on frame format for location of address, control, and FCS fields.)

#### **1.3 REGISTER DEFINITION**

The WD2840 is controlled and monitored by sixteen 8 bit registers. This set of registers consists of two Control Registers, three Status Registers, an In-

terrupt Event Register, a Counter Register and a variety of Parameter Registers. In general the host is responsible for defining these registers (except certain host read-only registers: SR0-2, IR0, CTR0 and NA) to contain proper and meaningful values prior to entering Network Mode from Isolate State. Furthermore, while the WD2840 is in Network Mode, the CBP (H,L) and MA registers must not be changed by the host. Register NAR may be changed arbitrarily but will only be considered by the WD2840 in response to the NEWNA (CR10) control bit being set. The two Control Registers and the TA, TD, AHOLT, TXLT registers may change dynamically to control the behavior of the WD2840.

WD2840

| REG  |       |                             |

|------|-------|-----------------------------|

| [1]  | NAME  | DESCRIPTION                 |

| 0    | CR0   | Control Register 0          |

| 1    | CR1   | Control Register 1          |

| 2[2] | SR0   | Status Register 0           |

| 3[2] | IR0   | Interrupt Event Register    |

| 4[2] | SR1   | Status Register 1           |

| 5[2] | SR2   | Status Register 2           |

| 6[2] | CTR0  | Counter Register 0          |

| 7[2] | NA    | Next Address                |

| 8    | TA    | ACK Timer                   |

| 9    | TD    | Net Dead Timer              |

| Α    | CBPH  | Control Block Pointer       |

|      |       | (MSB)                       |

| В    | CBPL  | Control Block Pointer (LSB) |

| С    | NAR   | Next Address, Request       |

| D    | AHOLT | Access Hold-off Limit       |

| E    | TXLT  | Transmit Limit              |

| F    | MA    | My Address                  |

[1] = Hexadecimal representation of IA0-IA3.

[2] = CPU read only, write not possible.

Control, status, and interrupt bits will be referred to as CR, SR, or IR, respectively, along with two digits. For example, SR21 refers to status register #2 and bit 1, which is "STATE."

### SUMMARY - CONTROL, STATUS, INTERRUPT REGISTERS

WD2840

|                  |                |           |            | BIT #        |                |             |              |                 |

|------------------|----------------|-----------|------------|--------------|----------------|-------------|--------------|-----------------|

| REGISTER         | 7              | 6         | 5          | 4            | 3              | 2           | 1            | 0               |

| CR0              | TXDEN          | TXEN      | RXEN       | ITOKON       | ILOOP          | COPY        | NOINT        | ISOL[1]         |

| CR1[2]<br>CR1[4] | DIAGC<br>DIAGC | PIGT<br>0 | INIT<br>0  | ADRV<br>ADRV | GIRING<br>DMAT | 0<br>LOOPT  | TOFF<br>RAMT | NEWNA<br>NUDIAG |

| SR0              | LASTF          | SENDACK   | L2         | 0            | BSZ3 .         | . BSZ2 .    | . BSZ1 .     | . BSZ0          |

| IR0 [3]          | ITERR          | IROR      | INS        | ITRAN        | IREC           | ΙΤΟΚ        | ITA          | ITD/M           |

| SR1              | TAOUT          | IRTS      | RECIDL     | 1            | 1              | 1           | 1            | 1               |

| SR2              | NXTT0          | NXTR0     | TR         | ACKRQ        | RETRY          | TSENT       | STATE        | INRING          |

| NOTE: ZER        | O BITS (0) SI  | HOWN ABOV | E ARE RESI | ERVED AND    | SHOULD NO      | OT BE USED. |              |                 |

### NOTES:

[1] = Set to 1 on power-up or master reset.

[2] = Non diagnostic mode only (CR17-DIAGC cleared).

[3] = Any bit set causes host interrupt (INTR goes true) when Master Interrupt Suppress (CR01) is clear. All bits are cleared when register is read by the host.

[4] = Diagnostic State only (CR17-DIAGC set). See diagnostic section for register usage in diagnostic mode.

### **CR0** — CONTROL REGISTER 0 DEFINITION

| REGISTER | CR07  | CR06 | CR05 | CR04   | CR03  | CR02 | CR01  | CR00 |

|----------|-------|------|------|--------|-------|------|-------|------|

| CR0      | TXDEN | TXEN | RXEN | ITOKON | ILOOP | COPY | NOINT | ISOL |

| BIT  | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

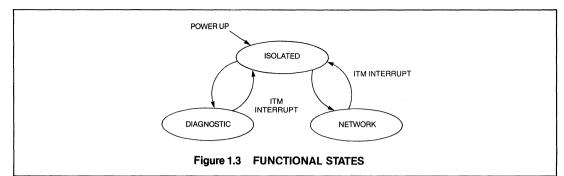

| CR00 | ISOL   | Isolate. Set true on power up or master reset. Host clears this bit after the host memory based WD2840 control block and other WD2840 registers have been set up. May be set by the host at any time (will be ignored if WD2840 is in diagnostic state). There is some delay for the WD2840 to respond to any state change request. A state change to network mode is acknowledged by the state confirmation status bit (SR21-STATE) being cleared. Setting ISOL while the WD2840 is in Network State will cause a state change to Isolate State, confirmed by an interrupt event (IR00-ITM) and the STATE status bit (SR21) being set. This transaction will be delayed until the node does not possess the token. Any in-progress frame transmission will be completed normally (at the current frame, regardless of queue length), followed by a normal token pass sequence. |

| CR01 | NOINT  | Master Interrupt Suppress. When clear, the WD2840 will generate host interrupt requests (INTR low) if any bit in the WD2840 interrupt request register (IR0) is set. When set, only the interrupt request is suppressed, not the setting of bits in IR0. Note that any interrupt request will be dropped by the WD2840 when IR0 is read since this will clear IR0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CR02 | COPY   | Enables COPY mode. When set causes all received data frames to be accepted<br>and DMA'ed into memory regardless of destination address. (See description in<br>Diagnostics Section.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

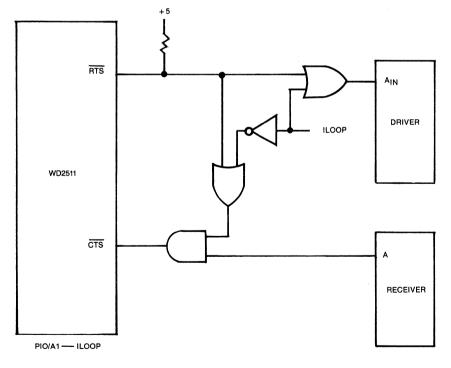

| CR03 | ILOOP  | Instructs the WD2840 to loop data internally from transmitter to receiver. Used with the LOOP diagnostic. Must NOT be set while in network mode (CR00-ISOL clear).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CR04 | ITOKON | Enable Token received interrupts. When clear no Token received interrupts are gener-<br>ated. When set the WD2840 generates an Itok interrupt when a token is received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BIT  | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR05 | RXEN  | Receive Data Enable. When clear, the WD2840 still makes normal responses to supervisory frames (scan, token pass), but will not DMA any data frames into memory and ignores the receiver buffer chain. However any data frame which is addressed to this node and for which an ACK is requested, will be NAK'ed with a "receiver not enable" Nak code. When RXEN is set, it allows the receiver to DMA appropriate data frames into memory. RXEN may be arbitrarily set and reset while in Network State but changes will not affect any frames in progress. |

|      |       | NOTE: Even when RXEN is clear, the WD2840 is "following" the receiver buffer chain with an internal register pointing either to the next available buffer (NXTR0 set) or, if the chain is exhausted, to a link field of zero (NXTR0 clear). The constraints on host manipulation of the receiver buffer chain are the same regardless of the state of RXEN. See the subsequent section on Receiver Memory Interface for more details.                                                                                                                        |

| CR06 | TXEN  | Master Transmit Enable. When clear no transmissions will occur and the transmit buffer chain will be ignored. When set, transmission activity is further dependent upon TXDEN (CR07).                                                                                                                                                                                                                                                                                                                                                                        |

|      |       | NOTE: Even when TXEN is clear, the WD2840 is "following" the transmitter buffer chain with an internal register pointing either to the next frame to transmit (NXTT0 set) or, if the chain is exhausted, to a link field of zero (NXTT0 clear). The constraints on host manipulation of the transmitter buffer chain are the same regardless of the state of TXEN. See the subsequent section on Transmitter Memory Interface for more details.                                                                                                              |

| CR07 | TXDEN | Data Transmit Enable. Has no meaning unless TXEN is set. When set in con-<br>junction with TXEN, normal WD2840 transmission of data and supervisory frames<br>will occur. When clear and with TXEN set, only data frame transmission will be<br>suppressed. That is, token pass and Ack/Nak supervisory frames will still be<br>transmitted when appropriate.                                                                                                                                                                                                |

|      |       | NOTE: The note above for TXEN applies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### **CR1** — CONTROL REGISTER 1 DEFINITION

| REGISTER | CR17  | CR16 | CR15 | CR14 | CR13   | CR12  | CR11 | CR10   |

|----------|-------|------|------|------|--------|-------|------|--------|

| CR1      | DIAGC | PIGT | INIT | ADRV | GIRING | 0     | TOFF | NEWNA  |

| CR1      | DIAGC | 0    | 0    | ADRV | DMAT   | LOOPT | RAMT | NUDIAG |

| BIT  | NAME   | DESCRIPTION (CR17 = 0, Network mode)                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

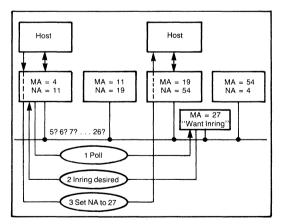

| CR10 | NEWNA  | Update NA register. When set causes WD2840 to copy the contents of register NAR into register NA. The WD2840 clears this bit after the function is complete. This mechanism allows the host to define the WD2840's successor in the logical ring. The node's next token pass will be to the new NA node.                                                                                                                                                 |

|      |        | NOTE: The normal token pass recovery applies. If the token pass to the new NA is<br>not successful, a normal scan sequence will occur where the WD2840 attempts a<br>single token pass to each node address in numerical sequence until a successful<br>pass occurs or the node's address itself is reached.                                                                                                                                             |

| CR11 | TOFF   | When set causes WD2840 to ignore timers. (This is NOT intended to be used in an operational network, but is provided to support network diagnosis.) CAUTION: This control bit disables all automatic network error recovery.                                                                                                                                                                                                                             |

| CR12 | _      | (Not used, Reserved.)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CR13 | GIRING | Get in logical ring. Instructs the WD2840 to gain entry into the logical ring at the next opportunity (i.e. respond to a token pass). The INRING status bit (SR20) is confirmation; when INRING is set, it indicates that the WD2840 is participating in a logical ring of at least two nodes. If the host clears GIRING while INRING is set, the WD2840 will not accept the next token pass to it at which time INRING will be cleared as confirmation. |

WD2840

| BIT  | NAME  | DESCRIPTION (CR17 = 0, Network mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR14 | ADRV  | Address Driver Enable. Enables the sixteen output address (A0-A15). If ADRV = 0, the outputs are tri-state and are in HI-Z, except when DACK goes low. If ADRV = 1, the outputs are always TTL levels.                                                                                                                                                                                                                                                                                                                                                                                                        |

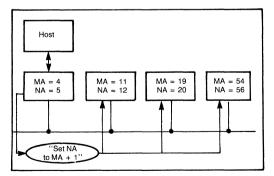

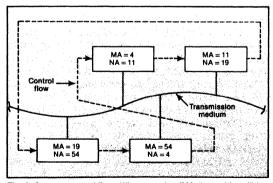

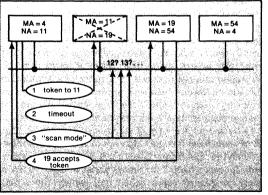

| CR15 | INIT  | Network Initialization Enable. When clear, the WD2840 will not attempt to (re)initialize the network if the net dead timer (TD) expires. When set, TD timer expiration causes the WD2840 to enter Scan Mode. In this mode it transmits a token pass frame to each node numerically higher in address, one after another, until either network activity occurs (another node responds) or until the node's own address is reached. When Scan Mode begins, the first node address used is the then current NA (Next Address) node address. This value is derived from and is affected by the following actions: |

|      |       | 1. At transition into Network State it defaults to MA + 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |