**Programmable Peripherals Design and Applications** Handbook

PSD3XX

OLLER

BOARD

GHER

SINGLE

PERIPHERAL

SIZE, REDU

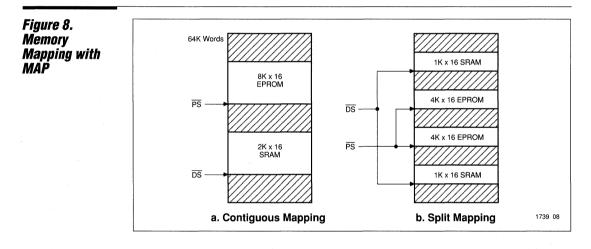

PROFITABL

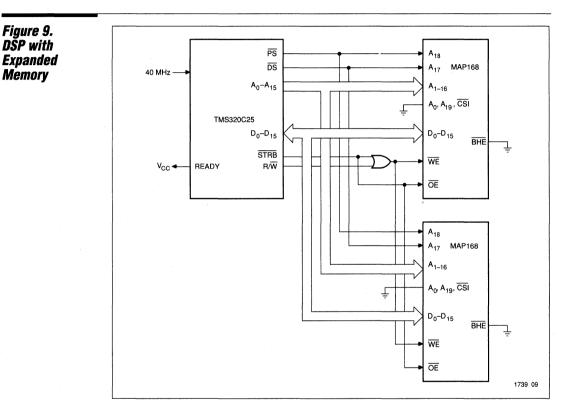

# Programmable Peripherals Design and Applications Handbook

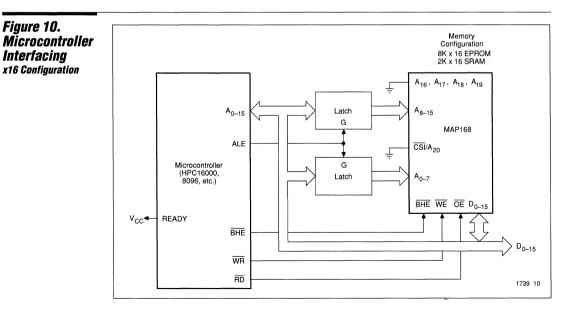

# *1992*

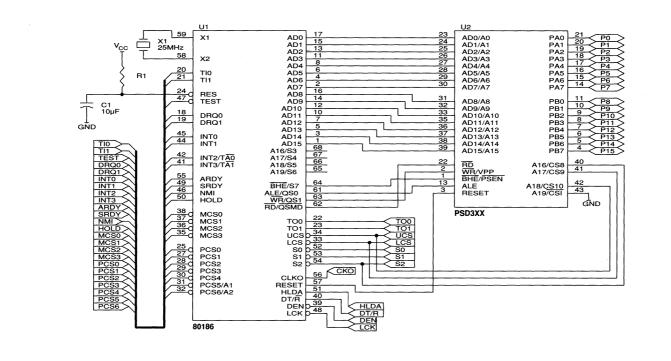

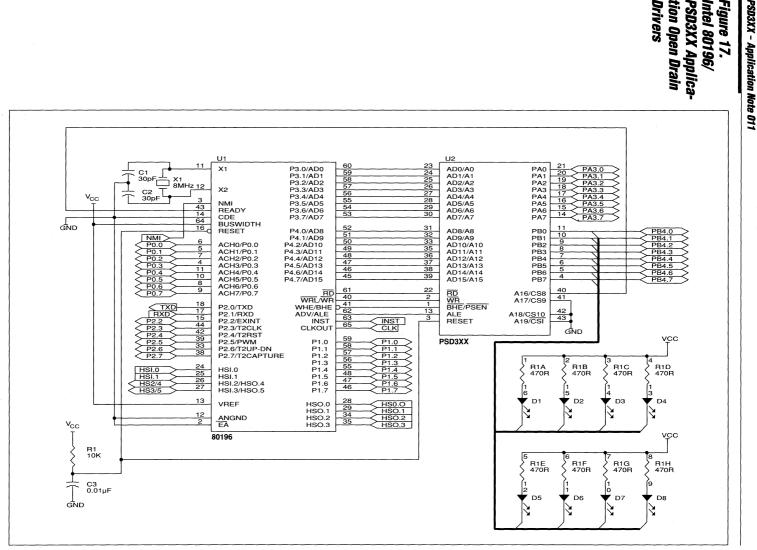

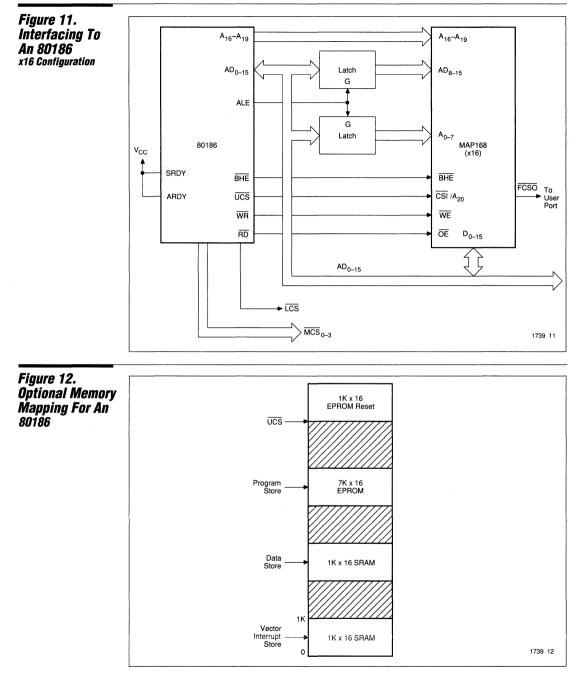

Copyright © 1992 WaferScale Integration, Inc. (All rights reserved.)

47280 Kato Road, Fremont, California 94538 Tel: 510-656-5400 Facsimile: 510-657-5916 Telex: 289255

Printed in U.S.A.

| General Information                       | 1 |

|-------------------------------------------|---|

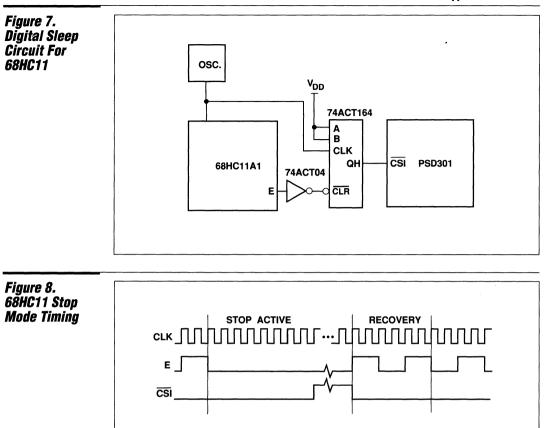

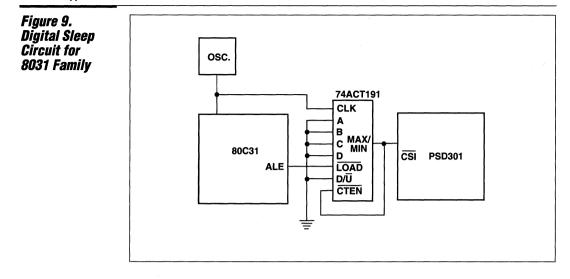

| PSD3XX Family                             | 2 |

| MAP168                                    | 3 |

| Development Systems                       | 4 |

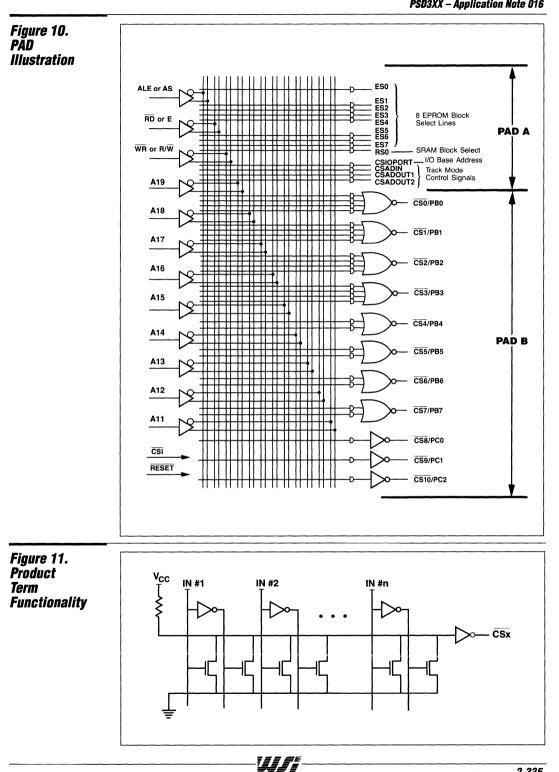

| Package Information                       | 5 |

| Sales Representatives<br>and Distributors | 6 |

# Section Index

| General     | Table of Contents      | 1_1  |

|-------------|------------------------|------|

| Information | Company Profile        |      |

|             | Article Reprint        | 1-7  |

|             | Product Selector Guide | 1-11 |

|             | Ordering Information   | 1-15 |

For additional information, call 800-TEAM-WSI (800-832-6974). In California, Call 800-562-6363.

Table of Contents

| General<br>Information | Table of Contents      |                                                                                      |

|------------------------|------------------------|--------------------------------------------------------------------------------------|

| mormation              | Company Profile        |                                                                                      |

|                        | Article Reprint        |                                                                                      |

|                        | Product Selector Guid  | le1-11                                                                               |

|                        | Ordering Information . | 1-15                                                                                 |

| PSD3XX<br>Family       | PSD301                 | Programmable Microcontroller<br>Peripheral with Memory2-1                            |

|                        | PSD311                 | Programmable Microcontroller<br>Peripheral with Memory2-45                           |

|                        | PSD302                 | Programmable Microcontroller<br>Peripheral with Memory2-83                           |

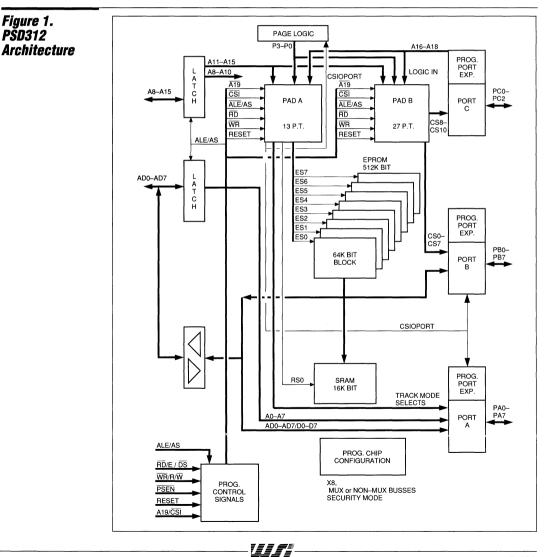

|                        | PSD312                 | Programmable Microcontroller<br>Peripheral with Memory2-127                          |

|                        | PSD303                 | Programmable Microcontroller<br>Peripheral with Memory2-165                          |

|                        | PSD313                 | Programmable Microcontroller<br>Peripheral with Memory2-209                          |

|                        | Application Note 011   | The PSD3XX Device Description2-247                                                   |

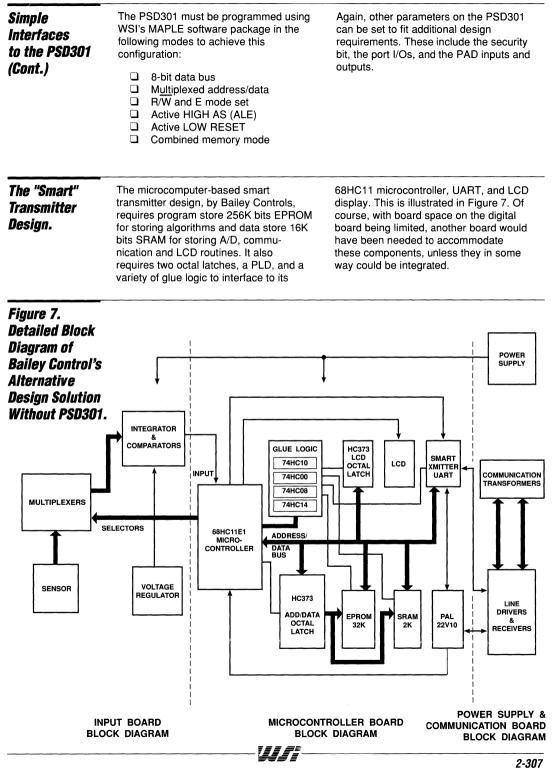

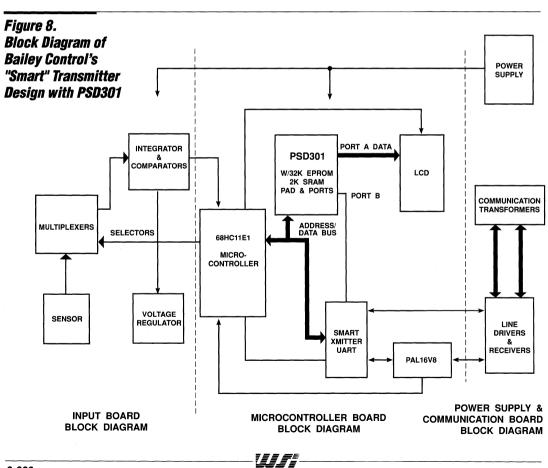

|                        | Application Note 013   | The PSD301 Streamlines a<br>Microcontroller-based<br>Smart Transmitter Design2-301   |

|                        | Application Note 014   | Using the PSD3XX PAD for System<br>Logic Replacement2-313                            |

|                        | Application Note 016   | Power Considerations In The PSD3XX2-327                                              |

|                        | Application Note 018   | Security of Design in the PSD3XX2-341                                                |

|                        | Application Note 019   | The PSD311 Simplifies an Eight Wire Cable<br>Tester Design and Increases Flexibility |

| Table of Contents                            |                                                         |                                                                              |

|----------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------|

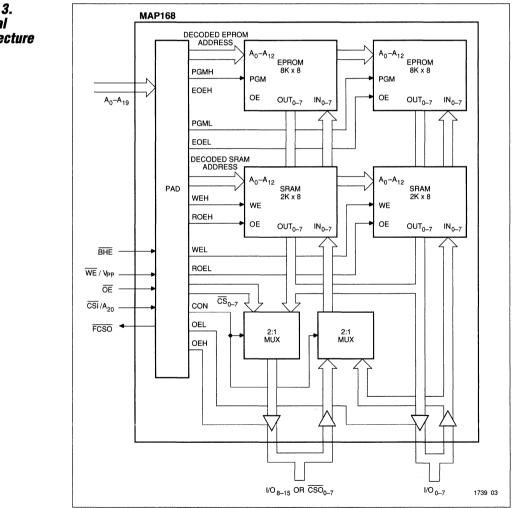

| MAP168                                       | MAP168 Introduction                                     | User-Configurable Peripheral with Memory                                     |

|                                              | MAP168                                                  | DSP Peripheral with Memory3-                                                 |

|                                              | Application Note 002                                    | Introduction to the MAP168<br>User-Configurable<br>Peripheral with Memory3-2 |

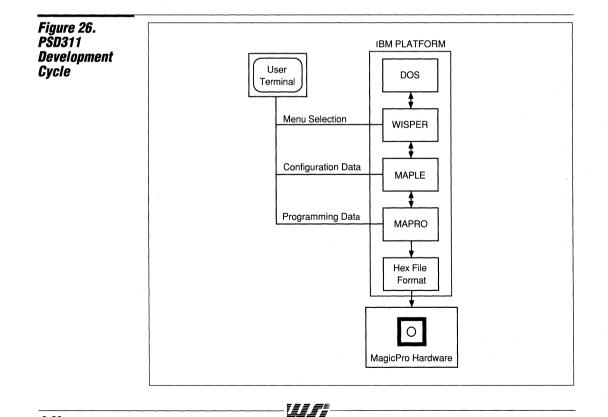

| Development                                  | Electronic Bulletin Boa                                 | rd4-                                                                         |

| Systems                                      | PSD-Gold/Silver Deve                                    | lopment System4-6                                                            |

|                                              | WS6000 MagicPro <sup>TM</sup> I<br>Programmable Periphe | Memory and<br>eral Programmer4-7                                             |

| Package<br>Information                       | -                                                       |                                                                              |

| Sales<br>Representatives<br>and Distributors |                                                         |                                                                              |

1-2

W/i-

# **Company Profile**

# Company Description

WSI is a market leading producer of highperformance programmable peripheral integrated circuits. The company was founded in 1983 to serve the needs of system designers who need to achieve higher system performance, reduce the size and power consumption of their systems, and shorten their product development cycles in order to achieve faster market entry.

WSI produces an innovative portfolio of Programmable Peripherals as well as a broad line of high-performance non-volatile programmable PROM and EPROM memory products, both based on its patented self-aligned split-gate CMOS EPROM technology. The new Programmable Peripherals enable rapid system design of high-performance application specific controllers and related products. These devices are the first to integrate high-performance EPROM, SRAM and user-configurable logic and deliver a performance and integration breakthrough to the programmable peripherals market.

WSI's Programmable Peripherals and nonvolatile memory products enable electronic designers to reduce their system size, shorten product development cycles and bring new system products to market in less time. As a result, WSI has established itself as a leading supplier of highperformance programmable solutions to a broad customer base that includes some of the world's largest and most technologically advanced electronics companies.

# Technology

WSI's patented self-aligned, split-gate EPROM technology enables higher performance and greater memory densities per chip area than the traditional stackedgate method. By developing significantly higher read current, the WSI EPROM cell has enabled the development of several memory devices that are the fastest of their type on the market. This core NVM technology is further leveraged by WSI's architecture and design innovations such as staggered virtual ground and contactless memory arrays resulting in dramatic die area savings. This high density memory capability enables WSI to provide cost-effective market leading products such as the smallest 4-Mbit EPROM on the market. WSI's proprietary NVM technology (licensed to Sharp Corporation and National Semiconductor Corporation) has enabled WSI to be first in the industry with numerous product breakthroughs in speed, high density, process innovations and packaging.

# Markets and Applications

WSI's Programmable Peripheral and highperformance non-volatile memory products are used by the world's leading suppliers of advanced electronic systems in telecommunications, data processing, military, automotive and industrial markets.

Applications for the Programmable Peripherals include cellular telephones, disk drive controllers, modems, bus controllers, engine management computers, telecom switchers, motor controllers and others. High performance memory applications include digital signal processing, engineering workstations, high-speed modems, video graphics controllers, radar and others. By virtue of their high speed and programming capability, WSI products are ideally suited for these applications where designers are pushing the limits of system performance in highly competitive markets. **Product Groups**

#### Programmable Peripherals

WSI's family of Programmable Peripherals represents a new class of programmable products. They enable system designers to reduce the size of their products, achieve lower operating power, optimize system performance and shorten product development cycles. They are the first devices to integrate high-speed EPROM, SRAM and programmable logic on a single chip. The Programmable Peripherals include the PSD3XX family, the MAP168 and the PAC1000.

# **PSD3XX Family: Microcontroller Peripherals with Memory**

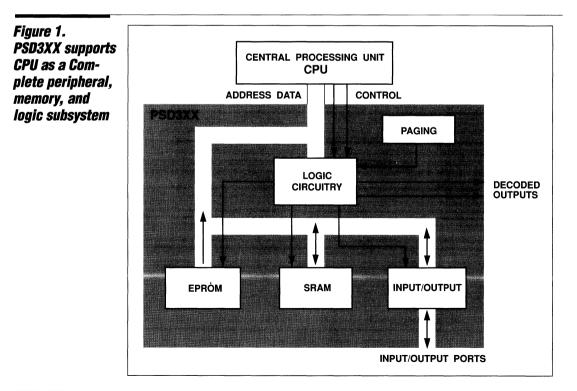

Each member of the PSD3XX family is a single-chip, field-programmable circuit that integrates all the required peripheral memory and logic elements for an embedded-control design. Programmable logic, page logic, programmable I/O ports, busses, address mapping, port address/data tracking, 256K to 1 Mb EPROM, and 16K SRAM are all on board. Advanced features such as memory paging, microcontroller port reconstruction, track mode, configuration security bit, and cascading further enhance the utility and value of the PSD3XX family. PSD3XX family devices are ideal for applications requiring high-performance, low power and very small form factors such as fixed disk control, cellular telephones, modems, computer peripherals, and automotive and military applications.

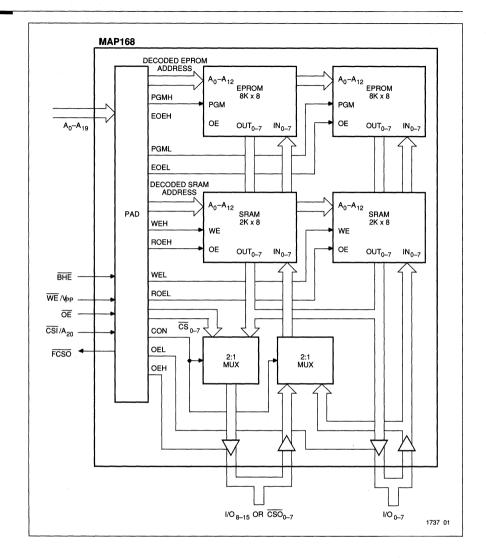

# MAP168 User-Configurable Peripheral with Memory

Similar to the PSD3XX family, the high speed MAP168 integrates highperformance EPROM, SRAM, a PAD and user-configurable logic. Ideal for highspeed applications requiring expanded memory, system integration and increased data security, the 45 ns MAP168 is used with high speed digital signal processors, microprocessors and microcontrollers.

us:

### PAC1000 Peripheral Controller

The high speed PAC1000 sets a new standard for Programmable Peripheral performance, integration and functionality. The PAC1000 replaces up to 50 complex devices in high-end embedded controllers and microprocessor-based systems. Combining a CPU, 1K x 64 EPROM and extensive user-configurable logic, the PAC1000 assists its host processor with high rates of data manipulation and control, freeing the processor for other system functions. The 16 MHz PAC1000 has been designed into numerous high-performance applications such as work-station direct memory access controllers, video imaging digital signal processors, and VME bus LAN controllers.

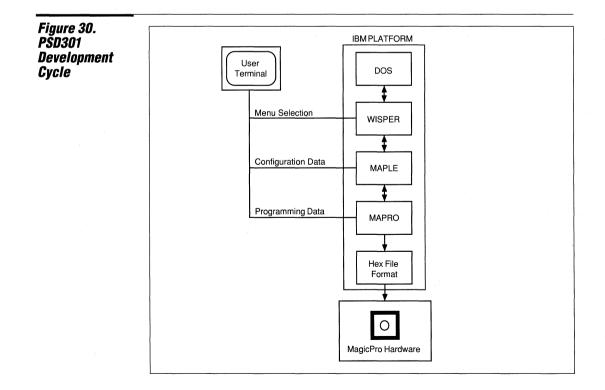

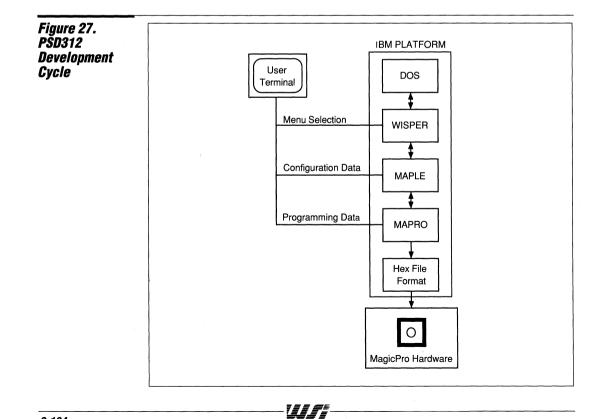

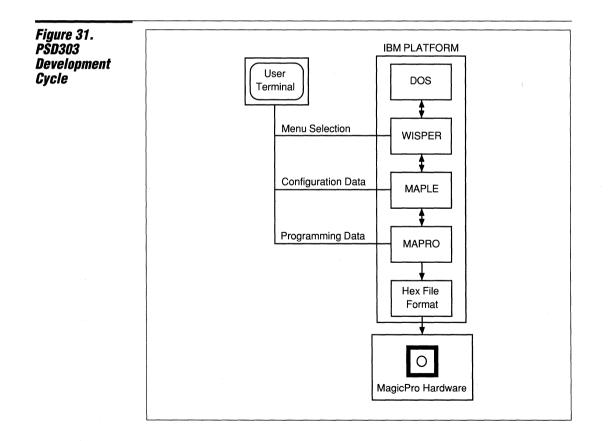

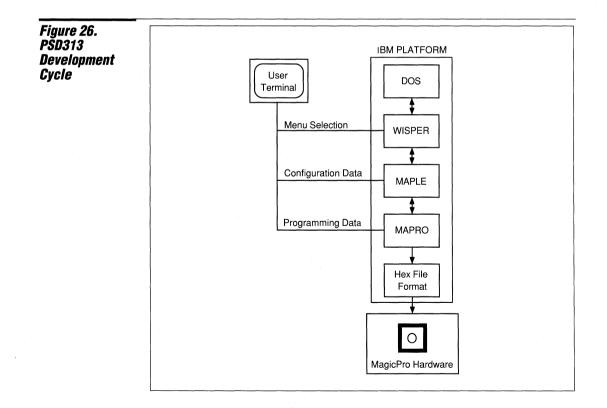

### Programmable Peripheral Development Tools

WSI's Programmable Peripheral products are supported with complete easy-to-use system development tools from both Data I/O and WSI. The Data I/O Unisite programmer can be used for production programming. The WSI tools include program development, simulation, and programming software, the IBM-PC hosted MagicPro<sup>™</sup> Memory and Peripheral Programmer, a dial-in applications bulletin board and WSI's team of factory service and field application engineers. The menudriven software tools run on popular customer owned computers and enable designers to rapidly configure and program the WSI part and try it in a prototype system. Additional design iterations are quickly accomodated. The system development tools increase the efficiency of the design process resulting in faster market entry for WSI's customers' products.

High-Performance Memory Products WSI offers a broad product line of highperformance CMOS PROMs and EPROMs featuring architectures ranging from 2K x 8 to 512K x 8, plus several x16 products, with speeds ranging from 25 to 150 ns. Commercial, industrial and military products including MIL-STD-883C/SMD are available. A wide variety of package selections include plastic and hermetic, through-hole and surface mount types.

#### **CMOS PROMs**

As WSI's fastest family of products, Re-Programmable Read Only Memories (RPROMs) provide high-speed bipolar PROM pinout with matching speed and low power operation. The product family includes architectures ranging from 2K x 8 to 32K x 8 with speeds ranging from 25 to 90 ns. Commercial, industrial and military MIL-STD-883C/SMD configurations are available in a variety of hermetic and plastic package types.

#### "F" Family EPROMs

The high-speed "F" series EPROM family offers speeds ranging from 35 to 70 ns and architectures from 8K x 8 to 32K x 8, plus several x16 products. "F" family EPROMs are ideal for use in high-end engineering and scientific workstations, data communications and similar highperformance applications.

### "L" Family Military EPROMs

WSI's "L" family military EPROM memory products feature high-density and high speed in popular JEDEC pinouts. With speeds ranging from 120 to 300 ns and architectures from 64K x 8 to 512K x 8 including several x16 products, the "L" family offers significant speed and high density benefits for developers of military avionics, communications, and control systems. The "L" family delivers world class densities from WSI's conservative 1.2 micron lithography CMOS process technology.

### Manufacturing

WSI's manufacturing strategy includes utilizing multiple world-class manufacturing partners for each facet of the production process.

WSI has licensed its CMOS EPROM and logic process technology to Sharp Corporation in Japan and National Semiconductor Corporation in the USA. The Sharp facility in Fukuyama, Japan employs the most advanced sub-micron VLSI integrated circuit manufacturing equipment available including ion implantation, reactive ion etch, and wafer stepper lithographic systems. The worldclass high volume National Semiconductor operation delivers low cost production of 1.2 micron CMOS technology product on 6" wafers. This low defect density manufacturing resource is capable of producing sub-micron technology product in the near future.

High-volume, low cost integrated circuit packaging and testing is performed for WSI by ANAM Electronics in Seoul, Korea, Fine Products in Hsinchu Taiwan, National Semiconductor in Santa Clara. CA and at WSI in Fremont, CA. ANAM is the largest independent manufacturer of I.C. packaging and produces excellent product quality. Test capability ranges from simple logic devices to complex VLSI product. ANAM routinely processes a wide variety of high volume packages and enables WSI to leverage its materiel needs through ANAM's combined high-volume, low cost procurement activity. Commercial, industrial, and military grade product processing is available from ANAM.

Additional quality assurance and reliability testing are performed at WSI in Fremont, CA.

WSI's manufacturing strategy ensures the supply of double-sourced high quality, highvolume product with low variable cost and fast delivery.

# Sales Network

WSI's international sales network includes several regional sales managers who direct the resources of the company to major market opportunities. Experienced technical field application engineers located in each field office assist WSI's customers during their advanced product development and match customer needs with WSI's product solutions. Over sixty manufacturer's representatives and leading national and regional component distributors in the United States, Europe and Asia round out the WSI sales network.

### **United States**

Direct sales and field application engineering offices in Boston, Chicago, Huntsville, Philadelphia, Dallas, Los Angeles and Fremont, CA; More than 25 manufacturer's representatives for major national accounts; national distributors include Arrow/Schweber, Time Electronics and Wyle Laboratories; and regional distributors.

### International

Direct WSI Sales management offices in Paris, Munich and Hong Kong; sales representatives and distributors in Germany, England, France, Italy, Sweden, Finland, Denmark, Norway, Spain, Belgium, Luxembourg, the Netherlands, and Israel. Sales representatives and distributors for the Asia/Pacific Rim region in Japan, Korea, Taiwan, Hong Kong, Singapore and Australia.

# Management and Previous Affiliations:

#### Michael Callahan

President, CEO and Chairman of the Board (Advanced Micro Devices, Monolithic Memories, Motorola)

#### Robert J. Barker

V. P. Finance, CFO and Secretary (Monolithic Memories, Lockheed)

### John Ekiss

V. P. Marketing (Intel, Motorola)

### Thomas Branch

V. P. Worldwide Sales (Monolithic Memories, Fairchild)

### George Kern

V. P. Operations (Advanced Micro Devices, Monolithic Memories)

#### Boaz Eitan

V. P. New Product and Technology Development (Intel)

#### **Bob Buschini**

Director of Human Resources (General Electric, Raychem)

# Financing

WSI is a privately held California corporation founded in August, 1983. The company has been financed by corporate investors, institutional investors, venture capital groups and private investors. Corporate investors are Sharp Corporation, National Semiconductor Corporation, Intergraph Corporation, and Kyocera Corporation. Venture capital investors include Accel Partners, Adler and Company, Bessemer Venture Partners, Genevest Consulting Group S. A., J. H. Whitney, Oak Investment Partners, Robertson Stephens and Co., Smith Barney Venture Corporation, and Warburg Pincus. The company has been audited annually since its inception by Ernst & Young (Arthur Young prior to 1989) and regularly reports financial information to Dunn & Bradstreet (Dunns number is 10-209-8167).

MagicPro<sup>TM</sup> is a trademark of WaferScale Integration, Inc.

IBM and IBM-PC are registered trademarks of International Business Machines Corporation.

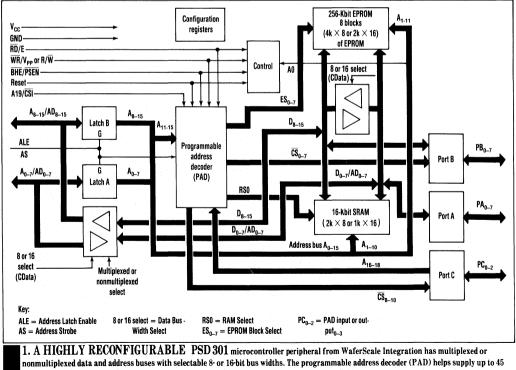

# PRODUCT INNOVATION PROGRAMMABLE SYSTEM<sup>\*\*</sup> DEVICE FITS MULTIPLE MICROCONTROLLERS

IC HAS EPROM, RAM, AND LOGIC FOR 45 CONFIGURATIONS; INTERFACES 8- AND 16-BIT MICROCONTROLLERS.

# MILT LEONARD

he embedded-controller market embraces a myriad of 8- and 16bit microcontroller architectures that can satisfy just about any conceivable application requirement. However, each different controller requires its own unique combination of discrete devices to link the part to other system elements. Furthermore, changing application requirements usually call for restructuring I/O ports. Consequently, the application may eventually outgrow system memory and shared resources may demand multiple chip solutions. This means that in addition to comparing controllers on the merits of price and performance, prospective users must also consider the external circuitry that the controller needs to interface to the rest of the system.

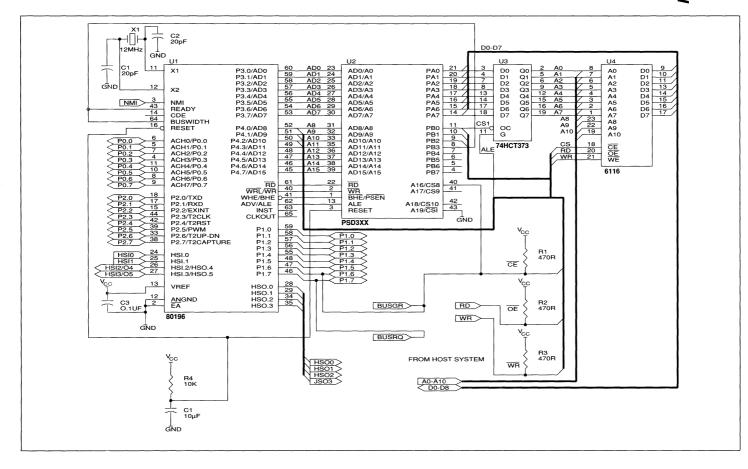

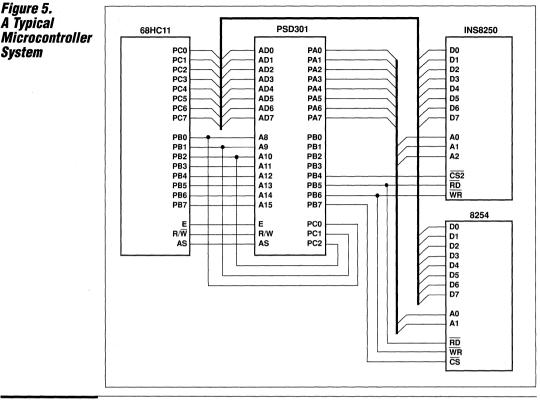

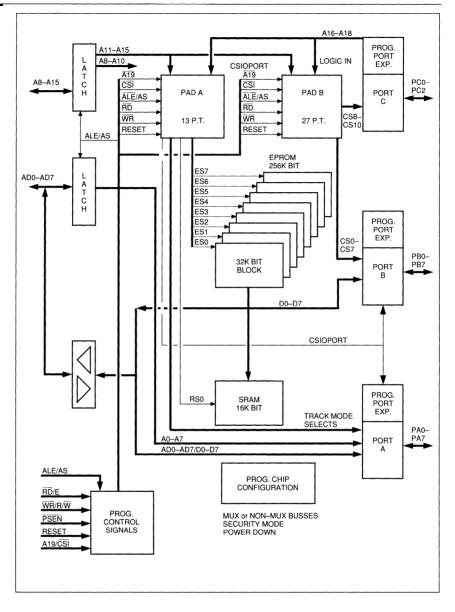

A new chip from WaferScale Integration Inc., Fremont, Calif., simplifies system integration by combining RAM, EPROM, programmable decoding, and configurable I/O ports that expand 8- or 16-bit microcontrollers when they run out of on-chip resources. WaferScale's PSD301 is the first single-chip solution to offer a microcontroller with port expansion, latched address lines, a programmable address decoder (PAD), an expansion interface to shared resources, a 256-kbit EPROM, and a 16-kbit static RAM. In addition, the chip links directly to popular 8- and 16-bit microcontrollers without using glue logic.

The PSD301 architecture is a major enhancement of WaferScale's MAP168 mappable memory chip introduced last year (see ELECTRONIC DESIGN, July 28, 1988, p. 91). In addition to the memory, decoding, and multiplexer functions of the 168, the 301 includes three software-configurable 8-bit I/O ports (A, B, and C), configuration registers, latched inputs, more chip-select lines, and more control on the strobe lines (Fig. 1). Like the 168, a programmable security bit is given to protect against reverse engineering.

Most controllers can't be reprogrammed once they're configured. Moreover, their controller's I/O ports are designed to perform one of two mutually exclu-

us:

Reprinted with permission from ELECTRONIC DESIGN

# USER-CONFIGURABLE MICROCONTROLLER INTERFACE

sive functions: convey control signals to peripheral devices or address and data signals to shared resources. Supplying both of these functions requires a multiple chip solution.

Microcontrollers also differ in boot-up locations and address mapping in memory. The 8051 and 8096 microcontrollers, for example, locate boot-up sequences in the lower half of their memory maps, while the 80186/88 and 68HCXXX use a high memory boot-up address. Another factor is the differences in controlsignal polarities.

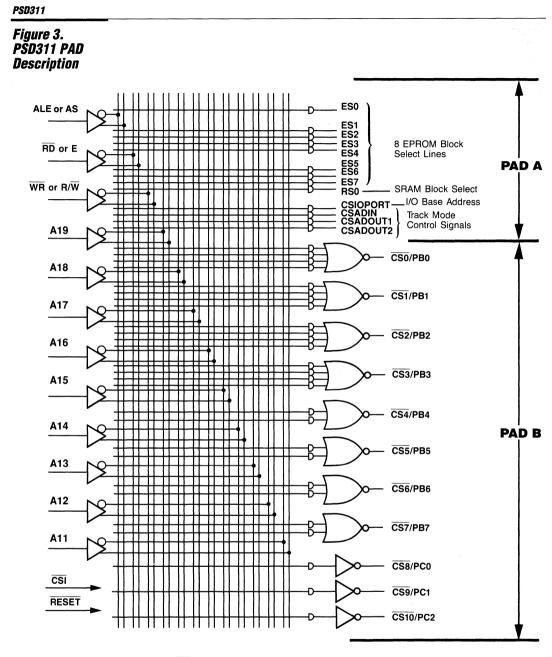

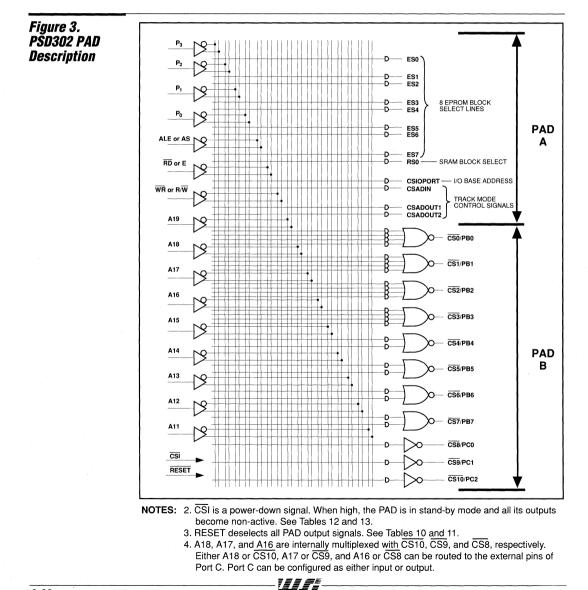

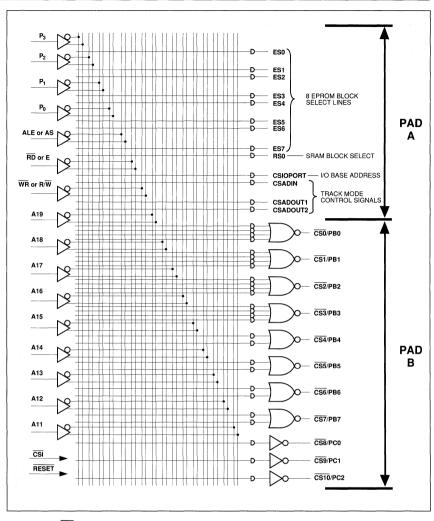

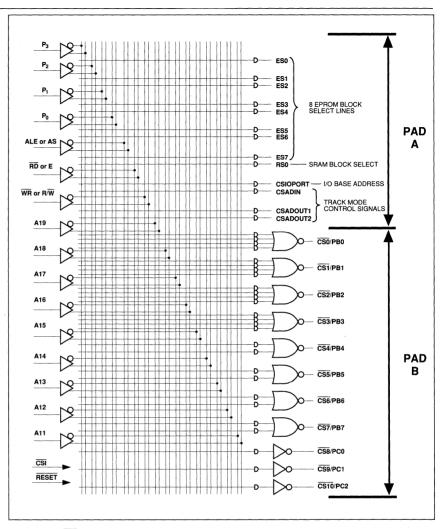

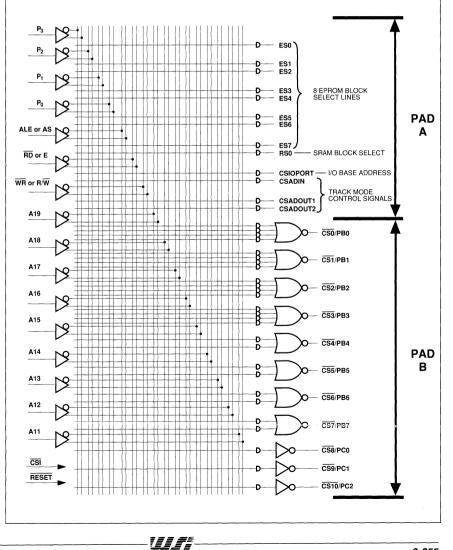

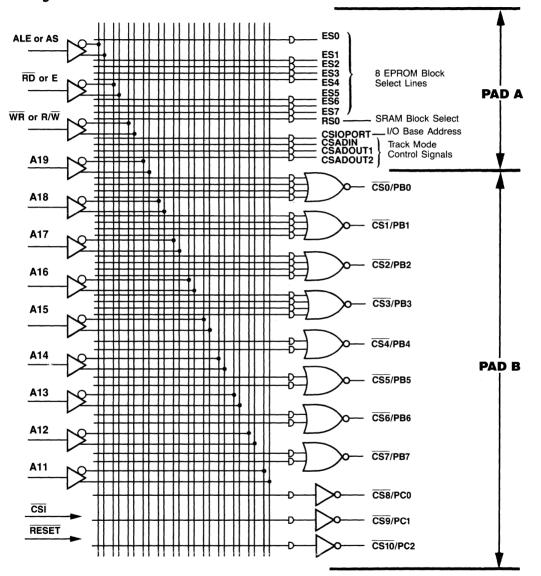

The **PSD301** is designed to adapt the characteristics of different microcontrollers to an embedded-control design. The PAD plays a major role in this function. It performs similarly to a small programmable array logic (PAL) device. The PAD has up to 13 inputs and 11 outputs in a NORgate array, and it can implement up to four sum-of-product expressions based on address inputs, control signals, and chip-select inputs. The PAD selects all of the chip's internal parts. and generates external chip selects with a 35-ns delay.

Address inputs from the host microcontroller are first fed to the 301's input latches, which stabilize the inputs when the device accesses memory in the multiplexed mode. The latches are made transparent in the nonmultiplexed mode. Five low-order address inputs and five programmable control lines are fixed functions; the Address-Latch-Enable and Reset lines have programmable polarity. The high-order address lines can be either address or general-purpose inputs for logic functions.

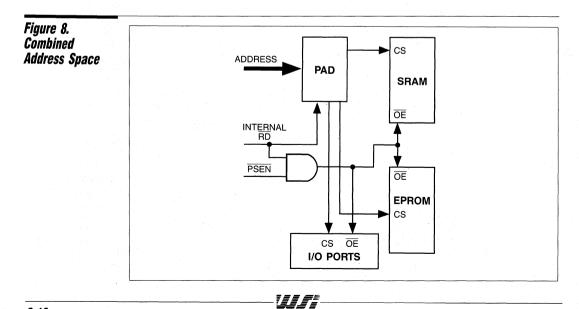

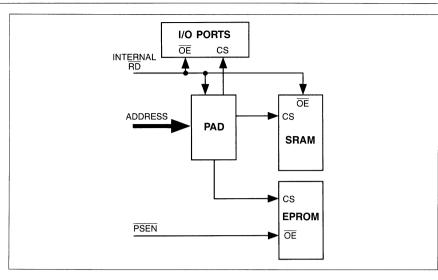

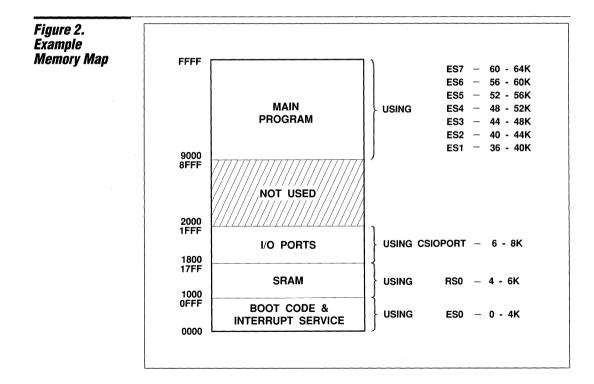

For more efficient use of memory space, internal and external PAD-Select signals can override EPROM memory with overlapping addresses. Therefore, if all of the EPROM isn't used for program storage, the unused space can be allocated to I/O ports, static RAM, or other PAD-select signals.

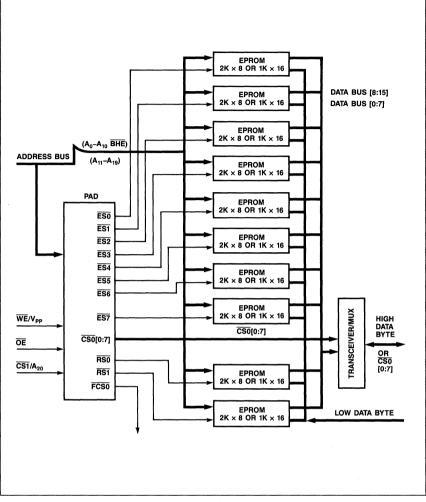

The EPROM is configurable as 32 kwords by 8 bits, or 16 kwords by 16 bits, and it's partitioned into eight equal mappable blocks with a resolution of 4 kbytes or 2 kwords. Access time, including PAD decoding time, is 120 ns. The configuration registers also consist of EPROM cells. The registers store the programmed configuration bits that make it possible for users to set the device. I/O, and control functions according to the required operating mode. The 16-kbit 120-ns static RAM is configurable as 2 kwords by 8 bits, or 1 kword by 16 bits. The memory blocks can be noncontiguously mapped over the addressable range of 1 Mbyte or 0.5 Mwords. Consequently, programmers can scramble the code to prevent direct copying.

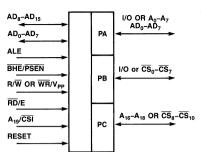

I/O ports A and B in the 8- and 16-

us:

configuration options for supporting a range of 8- and 16-bit microcontrollers.

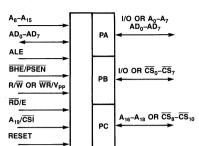

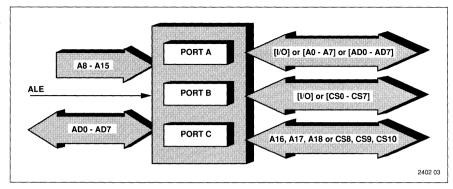

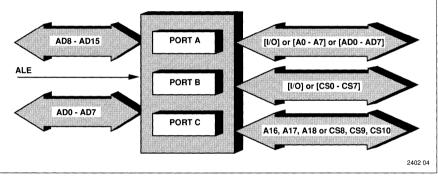

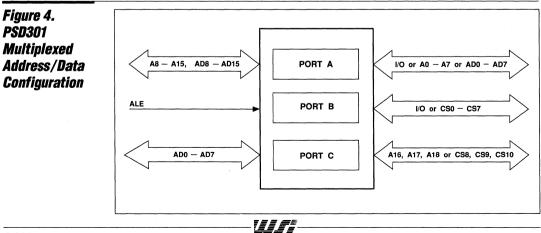

#### **USER-CONFIGURABLE MICROCONTROLLER INTERFACE** AD<sub>8-15</sub> -ALE = Address Latch Enable ► I/O or A<sub>0-7</sub> AD<sub>0-7</sub> Port A BHE/PSEN = Byte High Enable or Program Store Enable AD<sub>0-7</sub> ALE R/W or WR/V<sub>PP</sub> = Read/Write or Write/Programming Voltage BHE/PSEN Port B 1/0 or Chip Selector RD/E = Read/Enable R/W or WR/Vpp RD/E A19/CSI = High Address Bit or Chip Select Input (power down) A19/CSI I/O or $A_{0-7} AD_{0-7} = I/O$ , non-multiplexed low-order address A16-18 or Chip Selecte\_1 Port C Reset input byte, or multiplexed low-order address/data byte.

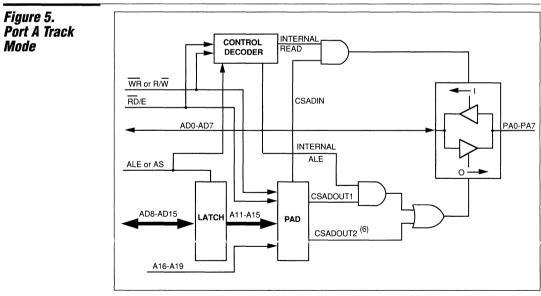

2. I/O PORT CONFIGURATION FOR THE PSD 301 IS PROGRAMMED by signals from the PAD, which are derived partly from programmed bits in the configuration registers. The three ports configured for multiplexed address and data with a 16-bit wide data bus are shown.

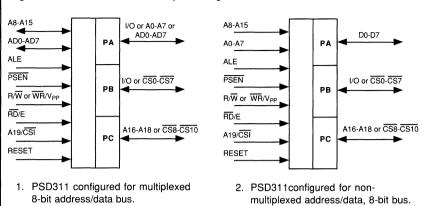

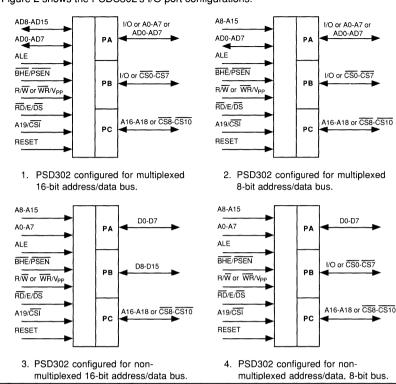

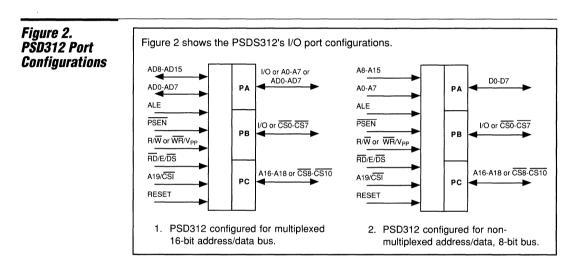

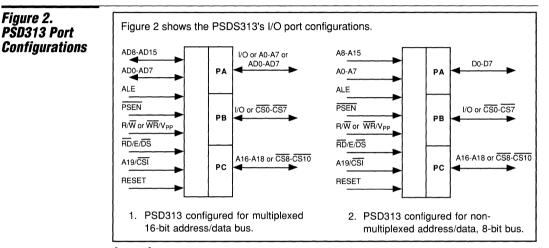

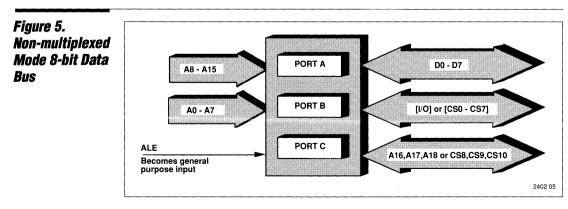

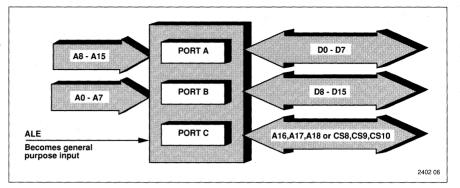

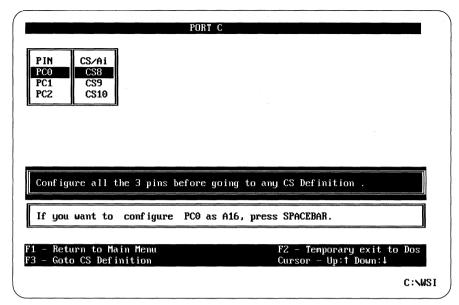

bit configurations are data ports in the nonmultiplexed mode, and both ports can be configured as either data or address ports in the multiplexed mode (*Fig. 2*). Port C is independent of any configuration—it can supply multiple chip-select outputs or serve as address inputs.

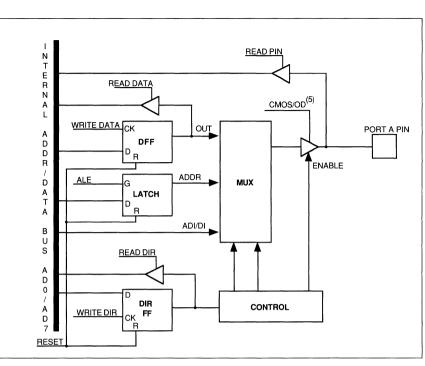

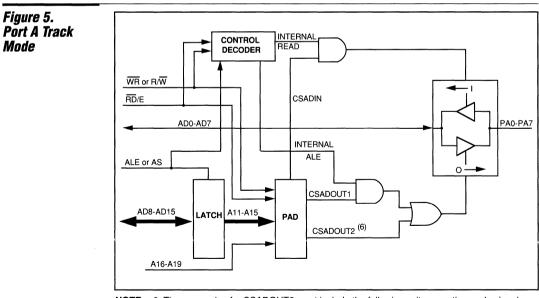

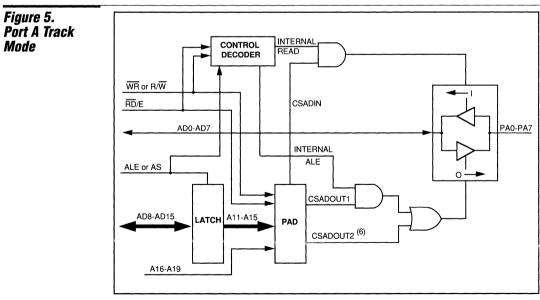

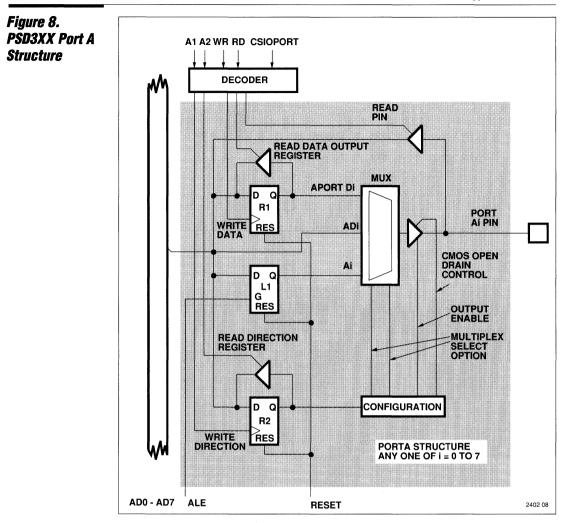

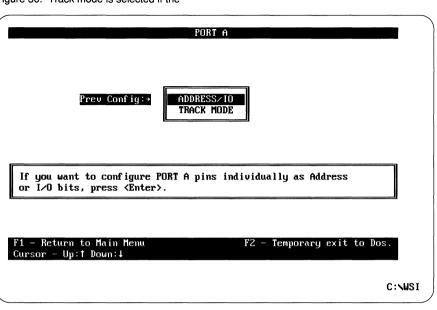

The default configuration of port A in the nonmultiplexed address/ data mode sets the port to deliver I/ O lines. In this mode, each pin can be set as an input or output and can have a CMOS or open-drain output. Alternatively, each bit of port A can be configured as a low-order latchedaddress-bus bit to access external peripherals or memory that requires several low-order lines. Another option in this mode sets the entire port to track the low-order address/data multiplexed bus. This feature links the host microcontroller to shared resources without the use of external buffers and decoders.

In the nonmultiplexed mode, port

**PRICE AND AVAILABILITY**

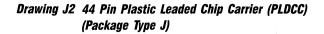

The commercial version of the **PSD301**, packaged in a 44-pin plastic leaded chip carrier, is priced at \$15 each in quantities of 1000. Military parts are also available. Other package options are ceramic leaded chip carriers and pin grid array packages with windows. The **PSD301** is being sampled now, with production quantities available in January, 1990.

WaferScale Integration Inc., 47280 Kato Rd., Fremont, CA 94538; (415) 656-5400. A becomes the chip's low-order databus byte. When a read operation is executed from an internal 301 location, data is directed out on port A pins. When a write cycle is executed into an internal 301 location, data is driven into port A.

The operation of port B in the multiplexed address/data and 8-bit nonmultiplexed modes is the same as port A. However, as an alternative. each bit can be configured to supply a Chip-Select Output signal from the PAD. In the 16-bit nonmultiplexed mode, port B is the high-order databus byte of the chip. When a read operation is executed from an internal high-order data-bus byte location, the data appears on port B pins. When a write operation is executed into an internal high-order data-bus byte location, data and write operation signals are present at port B.

Each pin of port C in all modes can be configured as an input or output from the PAD. Although designated as high-order address bus pins, they can be used for any logic inputs to the PAD or for external chip-select outputs from the PAD.

With this degree of operational flexibility, the 301 can team up with all popular 8- and 16-bit microcontrollers from such companies as Advanced Micro Devices, Intel, Motorola, National Semiconductor, Texas Instruments, and Zilog. For example, the polarity of the 301's control signals can be programmed for direct connection of the read-write and output enable pins of the 68HCXX microcontroller family. The 16-bit configuration can boost the performance of 16-bit controllers, such as the 80186, 8096, 80196, 16000, and others, without adding external devices. And the 8051 microcontroller family can extend its memory space by using the separate address and program memory space of the 301. The 301 is cascadable for increased width or depth for multiplexed byteor word-wide embedded-control designs.

In the standby mode, commercial versions of the 301 draw 150  $\mu$ A and 1.5 mA for CMOS and TTL interfaces, respectively. Active current for CMOS interfaces with or without selected memory blocks, or with the EPROM blocks selected, is 55 mA. That level increases to 80 mA for TTL interfaces. Selecting the static RAM block increases active current to 105 mA and 130 mA for CMOS and TTL, respectively.

WaferScale Integration houses the device in a 44-pin surface-mounted package to meet the form-factor requirements of such products as 5.25, 3.5, and 2.5-in. disk drives, cellular phones, and modems. System development tools include an IBM-PC plug-in programmer board and remote socket adaptor. They also contain a software development package that runs on an IBM PC/ XT/AT or compatible computer with a MS-DOS version 3.1 or higher, 640 kbytes of RAM, and a hard disk.□

configuration can boost the perfor- WAFERSCALE INTEGRATION, INC.

# PRODUCT SELECTOR GUIDE JANUARY 1992

# **PROGRAMMABLE PERIPHERALS**

| PSD301<br>PSD311<br>PSD302<br>PSD312<br>PSD303 |                                                                                                  | Spee    | d (ns)   | Availab | oility | Pack | age | Selec | tion |

|------------------------------------------------|--------------------------------------------------------------------------------------------------|---------|----------|---------|--------|------|-----|-------|------|

| Part No.                                       | Description                                                                                      | Comm'l  | Military | Samples | Prodn  | J    | L   | Q     | X    |

| PSD301                                         | Programmable Microcontroller                                                                     | 120     |          | NOW     | Q4 '91 | •    | •   | •     |      |

|                                                | Peripherals with Memory;                                                                         | 150-200 |          | NOW     | NOW    | •    | •   | •     | •    |

|                                                | x8/x16; 256Kb – 1Mb EPROM;                                                                       |         | 200      |         | NOW    |      | •   |       | •    |

| PSD311                                         | 16K SRAM; PAD; System                                                                            | 120     |          | NOW     | Q4 '91 | •    | •   | •     |      |

|                                                | Features.                                                                                        | 150-200 |          | NOW     | Q4 '91 | •    | •   | •     | •    |

|                                                |                                                                                                  |         | 200      |         | Q4 '91 |      | •   |       | •    |

| PSD302                                         |                                                                                                  | 120     |          | NOW     | Q1 '92 | •    | •   |       |      |

|                                                |                                                                                                  | 150-200 |          | NOW     | Q1 '92 | •    | •   |       |      |

| PSD312                                         |                                                                                                  | 120     |          | NOW     | Q1 '92 | •    | ٠   |       |      |

|                                                |                                                                                                  | 150-200 |          | NOW     | Q1 '92 | •    | •   |       |      |

| PSD303                                         |                                                                                                  | 120     |          | Q4 '91  | Q1 '92 |      |     |       |      |

|                                                |                                                                                                  | 150-200 |          | Q4 '91  | Q1 '92 |      |     |       |      |

| PSD313                                         |                                                                                                  | 120     |          | Q4 '91  | Q1 '92 |      |     |       |      |

|                                                |                                                                                                  | 150-200 |          | Q4 '91  | Q1 '92 |      |     |       |      |

| MAP168                                         | DSP Peripheral with Memory. Features:                                                            | 45-55   |          | NOW     | NOW    | •    | •   | •     | •    |

|                                                | 128K Bits EPROM, 32K Bits SRAM<br>Programmable Address Decoder (PAD)<br>Configurable: x8 or x16. |         | 55       |         | NOW    | •    |     | •     |      |

# HIGH-PERFORMANCE CMOS USER-CONFIGURABLE EMBEDDED CONTROLLER – COMMERCIAL & MILITARY

| Part No. |                                                                                                                                             | Speed (ns) |          | Availability |       | Package Selection |   |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------------|-------|-------------------|---|--|

|          | Description                                                                                                                                 | Comm'l     | Military | Samples      | Prodn | Q                 | Х |  |

| PAC1000  | Programmable Peripheral Controller                                                                                                          | 12MHz      |          | NOW          | NOW   | •                 | • |  |

|          | optimized for High-Performance Control                                                                                                      |            | 12MHz    | NOW          | NOW   |                   | • |  |

|          | Systems. Key Features Include:<br>16-Bit CPU, 16-Bit Address Port, 16-Bit<br>Output Control, 8-Bit I/O Port and<br>Configuration Registers. | 16MHz      |          | NOW          | NOW   | •                 | • |  |

# HIGH-PERFORMANCE CMOS USER-CONFIGURABLE MICROSEQUENCER/STATE MACHINE – COMMERCIAL & MILITARY

|          |                                       | Speed    | l (ns)   | Availat | oility | Packa | age S | elect | tion |

|----------|---------------------------------------|----------|----------|---------|--------|-------|-------|-------|------|

| Part No. | Description                           | Comm'l   | Military | Samples | Prodn  | J     | Ĺ     | S     | Т    |

| SAM448   | User-Programmable Microsequencer      | 20-25MHz |          | NOW     | NOW    | *     | •     | *     | •    |

|          | for Implementing High-Performance     |          | 20MHz    | NOW     | NOW    |       | • -   |       | •    |

|          | State Machines. Includes EPROM        |          |          |         |        |       |       |       |      |

|          | integrated with Branch Control Logic, |          |          |         |        |       |       |       |      |

|          | Pipeline Register, Stack and Loop     |          |          |         |        |       |       |       |      |

|          | Counter and 768 Product Terms.        |          |          |         |        |       |       |       |      |

# SOFTWARE DEVELOPMENT TOOLS t

| Part No.                      | Includes                                                                                                                                            | Availability |                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------|

| PSD - GOLD                    | Contains PSD301/MAP168 Software, Users Manual,<br>WS6000 MagicPro (PC Based Programmer), WS6014(J/L)<br>or WS6015( X ) Adapter and 2 Sample Devices | NOW          |                                       |

| PSD - SILVER                  | Contains PSD301/MAP168 Software and Users Manual                                                                                                    | NOW          | · · · · · · · · · · · · · · · · · · · |

| PAC1000 - GOLD                | Contains PAC1000 Software, Users Manual,<br>WS6000 MagicPro (PC Based Programmer), WS6010 (X)<br>Adapter and 2 Sample Devices                       | NOW          | ·.                                    |

| PAC1000 - SILVER              | Contains PAC1000 Software and Users Manual                                                                                                          | NOW          |                                       |

| SAM448 - GOLD                 | Contains SAM448 Software, Users Manual,<br>WS6000 MagicPro (PC Based Programmer), WS6008(T)<br>or 6009(C,J,L) Adapter and 2 Sample Devices          | NOW          |                                       |

| SAM448 - SILVER               | Contains SAM448 Software and Users Manual                                                                                                           | NOW          |                                       |

| MEMORY - SILVER <sup>††</sup> | Contains WSI EPROM/RPROM Programming Software<br>and Users Manual                                                                                   | NOW          |                                       |

1) All Development Systems include: 12 Month Software Update Service, access to WSI's 24 Hour Electronic Bulletin Board.

2) Package adaptor must be specified when ordering any "Gold" system.

tt 1) Memory-Silver is included in all development systems.

# NON-VOLATILE MEMORY CMOS PROMS – COMMERCIAL

|           |               |                    |            |   | Pa | ckage | Sele  | ction |                                        |  |

|-----------|---------------|--------------------|------------|---|----|-------|-------|-------|----------------------------------------|--|

| Part No.  | Architecture  | Description        | Speed (ns) | D | J  | Ē     | P     | S     | т                                      |  |

| WS57C191B | 2K x 8        | 16K CMOS PROM      | 35-55      | • | •  |       | • : . |       |                                        |  |

| WS57C291B | 2K x 8        | 16K CMOS PROM      | 35-55      |   |    |       |       | •     | •                                      |  |

| WS57C45   | 2K x 8        | 16K CMOS Reg. PROM | 25-35      |   |    |       |       | •     | •                                      |  |

| WS57C43B  | 4K x 8        | 32K CMOS PROM      | 35-70      | ٠ | •  |       |       | •     | •                                      |  |

| WS57C49B  | 8K x 8        | 64K CMOS PROM      | 35-70      | • | •  |       |       | •     | • ,                                    |  |

| WS57C49C  | 8K x 8        | 64K CMOS PROM      | 35-70      | ٠ | ٠  |       |       | ٠     | •                                      |  |

| WS57C51C  | 16K x 8       | 128K CMOS PROM     | 35-70      | • | ٠  | ٠     |       |       | •                                      |  |

| WS57C71C  | 32K x 8       | 256K CMOS PROM     | 45-70      | • | •  | •     |       |       | •                                      |  |

| CMOS PR   | OMs – MILITAR | Y                  |            |   |    |       |       | 12    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |

| :         |              |                    |            | DESC |   | Pa | ackag | ge Se | lection | on    |     |

|-----------|--------------|--------------------|------------|------|---|----|-------|-------|---------|-------|-----|

| Part No.  | Architecture | Description        | Speed (ns) | SMD  | С | D  | F     | Н     | Κ       | T     | Z   |

| WS57C191B | 2K x 8       | 16K CMOS PROM      | 45-55      | •    | • | •  | •     |       |         |       | •   |

| WS57C291B | 2K x 8       | 16K CMOS PROM      | 45-55      | •    |   |    |       |       | · · · • | •     |     |

| WS57C45   | 2K x 8       | 16K CMOS Reg. PROM | 35-45      | •    | • |    | •     | •     | •       | •     | · . |

| WS57C43B  | 4K x 8       | 32K CMOS PROM      | 45-70      |      | • |    |       |       |         | ٠     |     |

| WS57C49B  | 8K x 8       | 64K CMOS PROM      | 45-70      | •    | • | •  | •     |       |         | ٠     |     |

| WS57C49C  | 8K x 8       | 64K CMOS PROM      | 45-70      | •    | • | •  | •     |       |         | •     | 1.1 |

| WS57C51C  | 16K x 8      | 128K CMOS PROM     | 45-70      |      | • | •  |       |       |         | •     |     |

| WS57C71C  | 32K x 8      | 256K CMOS PROM     | 55-70      |      | • | •  |       |       | in pro- | ·*• * |     |

|           |              |                    |            |      |   |    |       |       |         |       |     |

# NON-VOLATILE MEMORY (Cont.)

HIGH-SPEED CMOS EPROMs - COMMERCIAL

|            |              |                            |            | Package Selection |   |   |   |  |  |

|------------|--------------|----------------------------|------------|-------------------|---|---|---|--|--|

| Part No.   | Architecture | Description                | Speed (ns) | D                 | J | L | т |  |  |

| WS57C64F   | 8K x 8       | High-Speed 64K CMOS EPROM  | 55-70      | •                 | • |   |   |  |  |

| WS57C128F  | 16K x 8      | High-Speed 128K CMOS EPROM | 55-70      | •                 |   |   |   |  |  |

| WS57C128FB | 16K x 8      | High-Speed 128K CMOS EPROM | 35-45      | •                 | • | • |   |  |  |

| WS57C256F  | 32K x 8      | High-Speed 256K CMOS EPROM | 45-70      | •                 | • | • | • |  |  |

### HIGH-SPEED CMOS EPROMs – MILITARY

|            |              |                            |            | DESC | Package Selection |   |   |   |  |

|------------|--------------|----------------------------|------------|------|-------------------|---|---|---|--|

| Part No.   | Architecture | Description                | Speed (ns) | SMD  | С                 | D | т | L |  |

| WS57C64F   | 8K x 8       | High-Speed 64K CMOS EPROM  | 70         | •    | •                 | • |   |   |  |

| WS27C64F   | 8K x 8       | Low-Power 64K CMOS EPROM   | 90         | •    | ٠                 | • |   |   |  |

| WS57C128F  | 16K x 8      | High-Speed 128K CMOS EPROM | 70         | •    | •                 | • |   |   |  |

| WS57C128FB | 16K x 8      | High-Speed 128K CMOS EPROM | 45-55      |      | •                 | • |   |   |  |

| WS27C128F  | 16K x 8      | Low-Power 128K CMOS EPROM  | 90         | •    | •                 | • |   |   |  |

| WS57C256F  | 32K x 8      | High-Speed 256K CMOS EPROM | 55-70      | •    | •                 | • | • |   |  |

| WS27C256F  | 32K x 8      | Low-Power 256K CMOS EPROM  | 90         | •    | •                 | • |   | • |  |

### **CMOS EPROMs – COMMERCIAL**

|           |              |                            |            | Packag | je Se | election |

|-----------|--------------|----------------------------|------------|--------|-------|----------|

| Part No.  | Architecture | Description                | Speed (ns) | D      | J     | L        |

| WS27C010L | 128K x 8     | Low-Power 1 Meg CMOS EPROM | 120-150    | •      | •     | •        |

| WS27C210L | 64K x 16     | Low-Power 1 Meg CMOS EPROM | 100-200    | •      | •     | •        |

#### CMOS EPROMs - MILITARY

|           |              |                            |            | DESC Package Sele |   |   |   | ction |

|-----------|--------------|----------------------------|------------|-------------------|---|---|---|-------|

| Part No.  | Architecture | Description                | Speed (ns) | SMD               | С | D | L | т     |

| WS27C256L | 32K x 8      | Low-Power 256K CMOS EPROM  | 120-250    | •                 | • | • |   | •     |

| WS27C512L | 64K x 8      | Low-Power 512K CMOS EPROM  | 120-200    | •                 | • | • |   | •     |

| WS27C010L | 128K x 8     | Low-Power 1 Meg CMOS EPROM | 150-200    | •                 | • | • | • |       |

| WS27C210L | 64K x 16     | Low-Power 1 Meg CMOS EPROM | 150-200    |                   | • | • | • |       |

ULF-

# CMOS BIT SLICE AND LOGIC

|          |                                 | Sp          | eed         |   | Package Selection |   |   |   |   |   |   |

|----------|---------------------------------|-------------|-------------|---|-------------------|---|---|---|---|---|---|

| Part No. | Description                     | Comm'l      | Military    | в | G                 | J | κ | L | Ρ | S | Y |

| WS5901   | 4-Bit CMOS Bit Slice Processor  | 32,43 MHz   | 32,43MHz    |   |                   |   |   |   | • |   | • |

| WS59016  | 16-Bit CMOS Bit Slice Processor | 15 MHz      | 12.5MHz     | • |                   | • |   | • |   |   |   |

| WS59032  | 32-Bit CMOS Bit Slice Processor | 26.4,33 MHz | 23.6,29 MHz |   | •                 |   |   |   |   |   |   |

| WS5910   | CMOS Microprogram Controller    | 20,30 MHz   | 20,30 MHz   |   |                   |   |   |   | • |   | • |

| WS59510  | 16K x 16 CMOS Multiplier-Accum. | 30-50 ns    |             |   | •                 | ٠ |   |   | • |   |   |

| WS59520  | CMOS Pipeline Register          | Tpd = 22ns  | Tpd = 24ns  |   |                   |   | • |   |   | • |   |

| WS59521  | CMOS Pipeline Register          | Tpd = 22ns  | Tpd = 24ns  |   |                   |   | • |   |   | • |   |

| WS59820  | CMOS Bi-Directional Register    | Tpd = 23ns  | Tpd = 25ns  |   | •                 | • |   |   |   |   |   |

# WSI PACKAGE DESCRIPTIONS

| Package Code | Description                           | Window | Surface Mount | Plastic/OTP |

|--------------|---------------------------------------|--------|---------------|-------------|

| B/R          | Ceramic Sidebrazed Dip                | N/Y    | N             | _           |

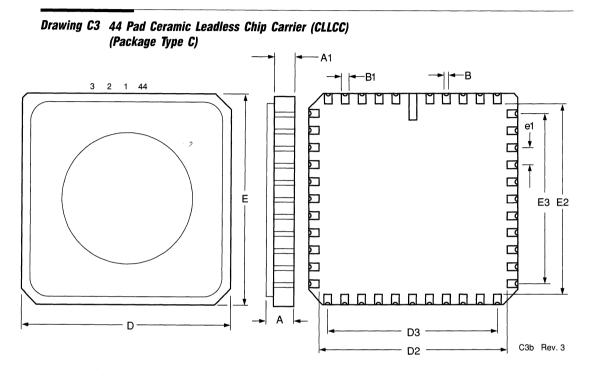

| С            | Ceramic Leadess Chip Carrier (CLLCC)  | Y      | Y             | -           |

| C/Z          | Ceramic Leadless Chip Carrier (CLLCC) | Y/N    | Y             | · - · · ·   |

| D/Y          | 0.600" Ceramic Dip                    | Y/N    | Ν             | -           |

| F/H          | Ceramic Flatpack                      | Y/N    | Y             | _           |

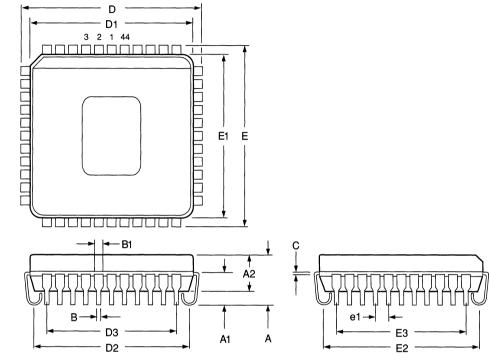

| J            | Plastic Leaded Chip Carrier (PLDCC)   | N      | Y             | Y           |

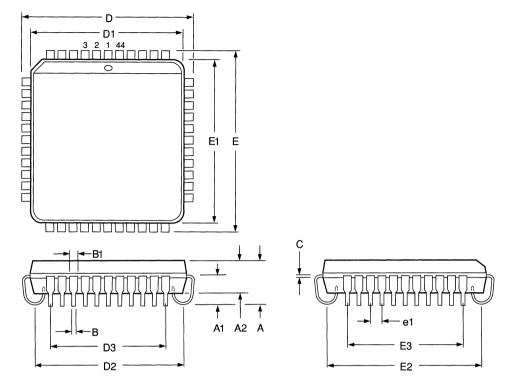

| L/N          | Ceramic Leaded Chip Carrier (CLDCC)   | Y/N    | Y             | _ '         |

| Р            | Plastic Dip                           | N      | Ν             | Y Y         |

| Q            | Plastic Quad Flat Pack (PQFP)         | Ν      | Y             | Y           |

| S            | 0.300" Plastic Dip                    | Ν      | N             | Y           |

| T/K          | 0.300" Ceramic Dip                    | Y/N    | Ν             | · _         |

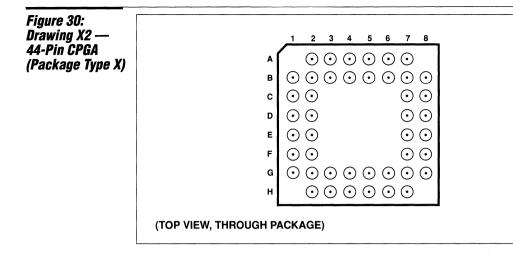

| X/G          | Ceramic Pin Grid Array (CPGA)         | Y/N    | Ν             | _           |

47280 Kato Road Fremont, California 94538-7333 Tel: 510-656-5400 Fax: 510-657-5916 800-TEAM-WSI (800-832-6974) In California 800-562-6363

# WSI REGIONAL HOTLINES

| USA Northwest:    | Tel: 510-656-5400        | Fax: 510-657-5916        |

|-------------------|--------------------------|--------------------------|

| USA Southwest:    | Tel: 714-753-1180        | Fax: 714-753-1179        |

| USA Midwest:      | Tel: 708-882-1893        | Fax: 708-882-1881        |

| USA Southeast:    | Tel: 214-680-0077        | Fax: 214-680-0280        |

| USA Mid-Atlantic: | Tel: 215-638-9617        | Fax: 215-638-7326        |

| USA Northeast:    | Tel: 508-685-6101        | Fax: 508-685-6105        |

| Europe (France):  | Tel: 33 (1) 69-32-01-20  | Fax: 33 (1) 69-32-02-19  |

| Europe (Germany)  | Tel: (49) 89.23.11.38.49 | Fax: (49) 89.23.11.38.11 |

| Asia (Hong Kong)  | Tel: 852-575-0112        | Fax: 852-893-0678        |

Printed in U. S. A. 1/92 • Revision 8.4

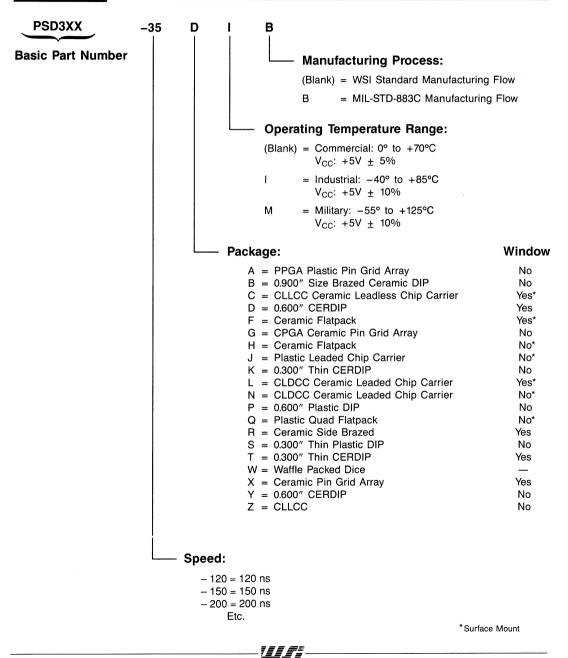

# **Ordering Information** High-Performance CMOS Products

1-15

**General Information**

PSD3XX Family

MAP168

**Development Systems**

**Package Information**

Sales Representatives and Distributors

2

# Section Index

| PSD3XX | PSD301               | Programmable Microcontroller<br>Peripheral with Memory2-1 |

|--------|----------------------|-----------------------------------------------------------|

| Family |                      | renpheral with Memory2-1                                  |

|        | PSD311               | Programmable Microcontroller                              |

|        |                      | Peripheral with Memory2-45                                |

|        | PSD302               | Programmable Microcontroller                              |

|        | 1 00000              | Peripheral with Memory2-83                                |

|        | PSD312               | Programmable Microcontroller                              |

|        | 100012               | Peripheral with Memory2-127                               |

|        | PSD303               | Programmable Microcontroller                              |

|        | 100000               | Peripheral with Memory2-165                               |

|        | PSD313               | Programmable Microcontroller                              |

|        |                      | Peripheral with Memory2-209                               |

|        | Application Note 011 | The PSD3XX Device Description2-247                        |

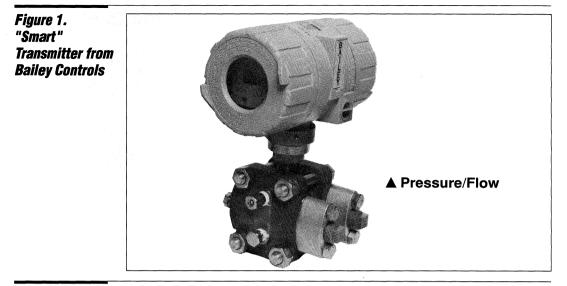

|        | Application Note 013 | The PSD301 Streamlines a                                  |

|        |                      | Microcontroller-based                                     |

|        |                      | Smart Transmitter Design2-301                             |

|        | Application Note 014 | Using the PSD3XX PAD for System                           |

|        | •••                  | Logic Replacement2-313                                    |

|        | Application Note 016 | Power Considerations in the PSD3XX2-327                   |

|        | Application Note 018 | Security of Design in the PSD3XX2-341                     |

|        | Application Note 019 | The PSD311 Simplifies an Eight Wire Cable                 |

|        |                      | Tester Design and Increases Flexibility2-345              |

For additional information, call 800-TEAM-WSI (800-832-6974). In California, Call 800-562-6363.

# **Programmable Peripheral PSD301** Programmable Microcontroller Peripheral with Memory

# Key Features

- Single Chip Programmable Peripheral for Microcontroller-based Applications

- 19 Individually Configurable I/O pins that can be used as

- Microcontroller I/O port expansion

- Programmable Address Decoder (PAD) I/O

- Latched address output

- Open drain or CMOS

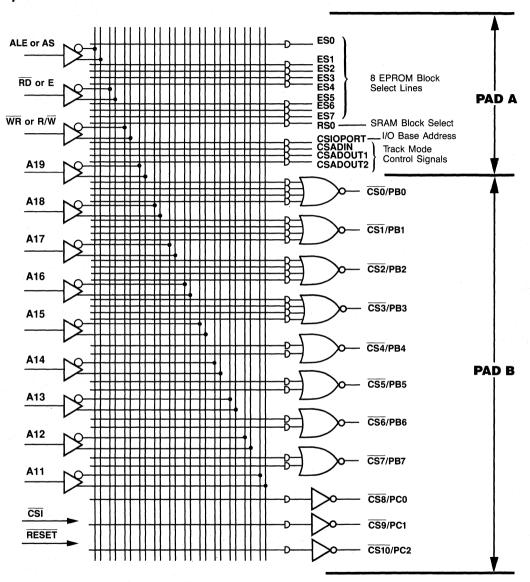

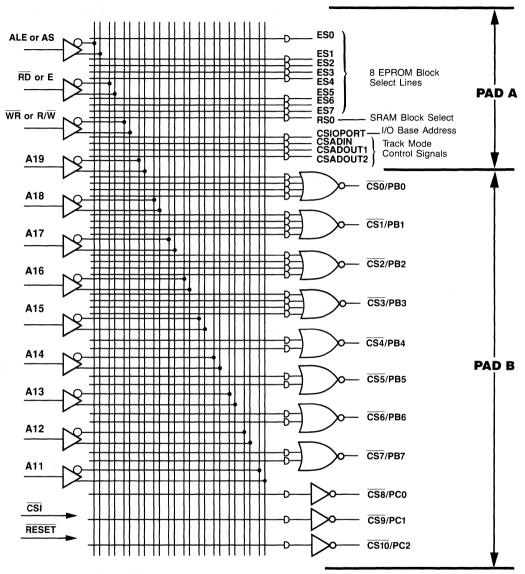

- Two Programmable Arrays (PAD A and PAD B)

- Total of 40 Product Terms and up to 16 Inputs and 24 Outputs

- Address Decoding up to 1 MB

- Logic replacement

- "No Glue" Microcontroller Chip-Set

- Built-in address latches for multiplexed address/data bus

- Non-multiplexed address/data bus mode

- Selectable 8 or 16 bit data bus width

- ALE and Reset polarity programmable

- Selectable modes for read and write control bus as RD/WR or R/W/E

- BHE/pin for byte select in 16-bit mode

- PSEN/pin for 8051 users

- 256 Kbits of UV EPROM

- Configurable as 32K x 8 or as 16K x 16

- Divides into 8 equal mappable blocks for optimized mapping

# Partial Listing of Microcontrollers Supported

Motorola family: M6805, M68HC11, M68HC16, M68000/10/20, M60008, M683XX

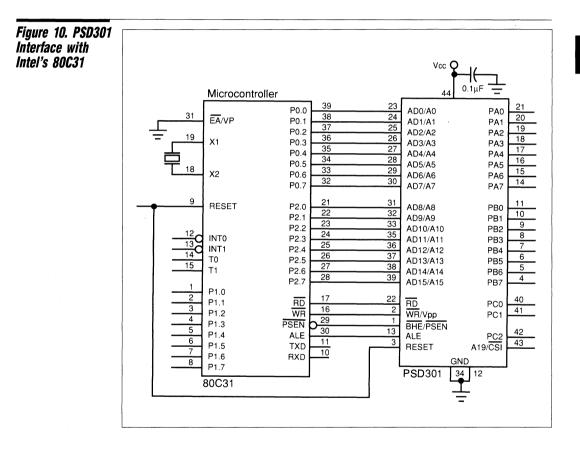

□ Intel family: 8031/8051, 8096/8098, 80186/88, 80196/98

- Block resolution is 4K x 8 or 2K x 16

- 120 ns EPROM access time, including input latches and PAD address decoding.

- 16 Kbit Static RAM

- Configurable as 2K x 8 or as 1K x 16

- 120 ns SRAM access time, including input latches and PAD address decoding

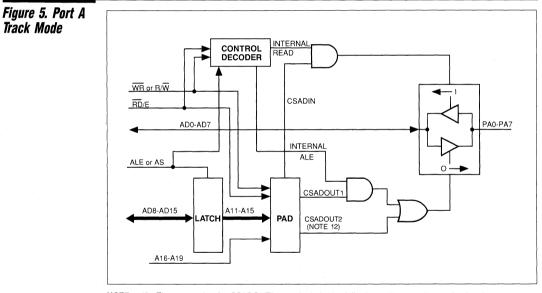

- Address/Data Track Mode

- Enables easy Interface to Shared Resources (Mail Box SRAM) with other Microcontrollers or a Host Processor

- Built-In Security

- Locks the PSD301 Configuration and PAD Decoding

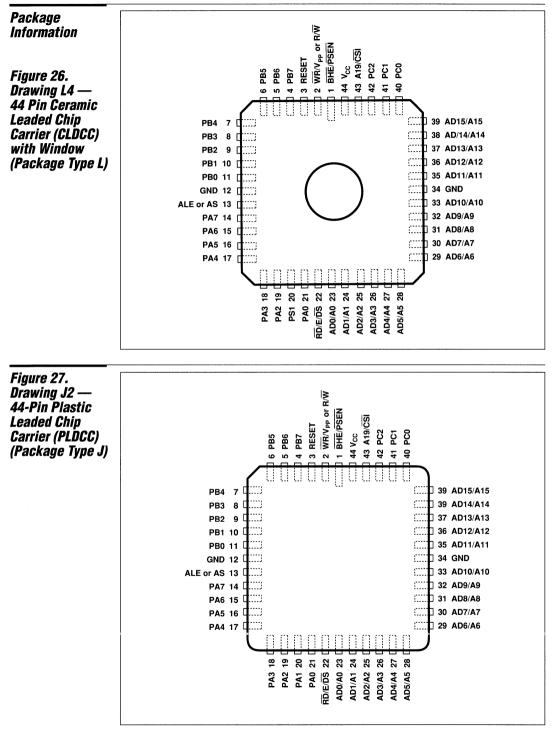

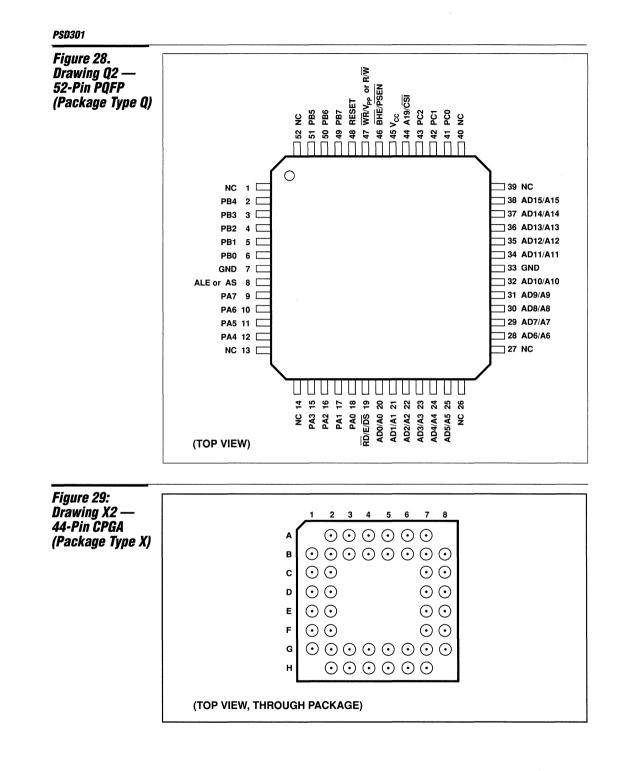

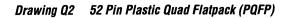

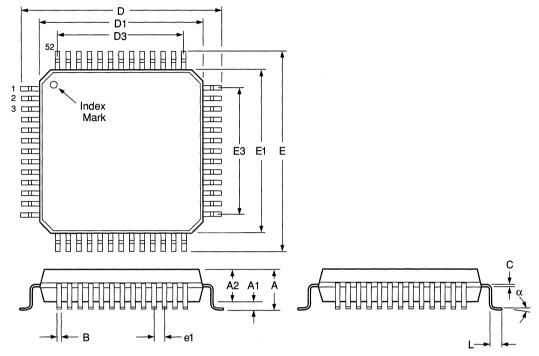

- □ Available in a Variety of Packaging

- 44 Pin PLDCC and CLDCC

- 52 Pin PQFP

- 44 Pin CPGA

- Simple Menu-Driven Software: Configure the PSD301 on an IBM PC

- Pin Compatible with the PSD3XX Family

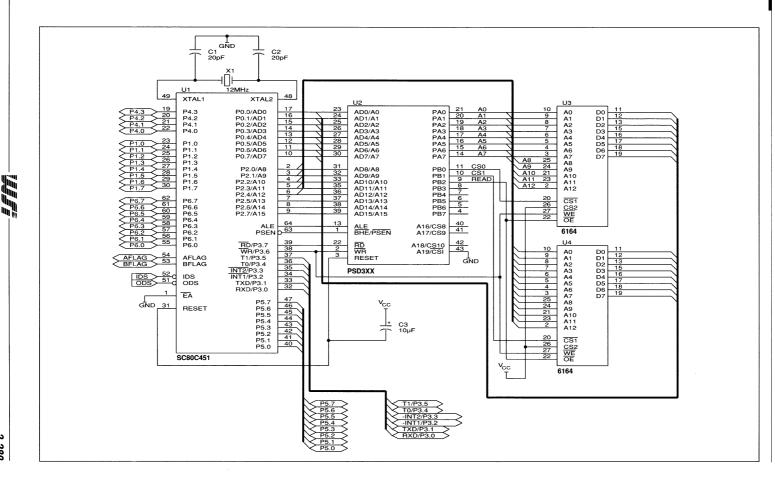

TI: TMS320C14

Signetics: SC80C451, SC80552

Zilog: Z8, Z80, Z180

National: HPC16000, HPC63400

| Applications           | <ul> <li>Computers (Workstations and PCs)</li> <li>Fixed Disk Control, Modem, Imaging,<br/>Laser Printer Control</li> </ul>                                                                                                                                                                              | <ul> <li>Industrial</li> <li>Robotics, Power Line Access,<br/>Power Line Motor</li> </ul>                                                                                                                                                                                                   |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | <ul> <li>Telecommunications</li> <li>Modem, Cellular Phone, Digital PBX,<br/>Digital Speech, FAX,</li> <li>Digital Signal Processing</li> </ul>                                                                                                                                                          | <ul> <li>Medical Instrumentation</li> <li>Hearing Aids, Monitoring Equipment,<br/>Diagnostic Tools</li> </ul>                                                                                                                                                                               |

|                        |                                                                                                                                                                                                                                                                                                          | <ul> <li>Military</li> <li>Missile Guidance, Radar, Sonar,<br/>Secure Communications, RF Modems</li> </ul>                                                                                                                                                                                  |

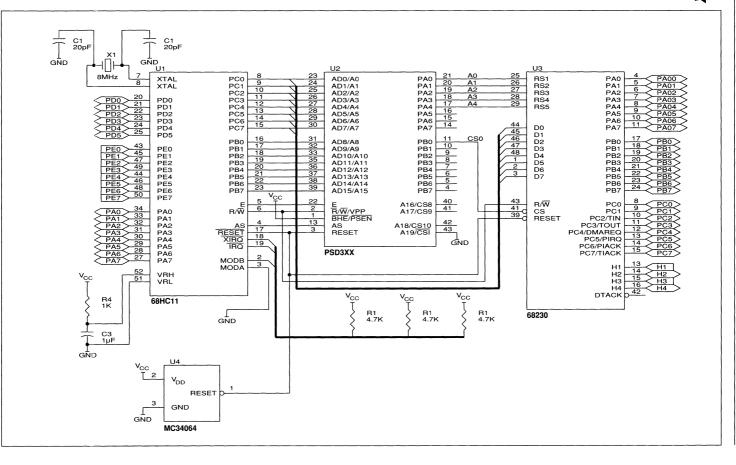

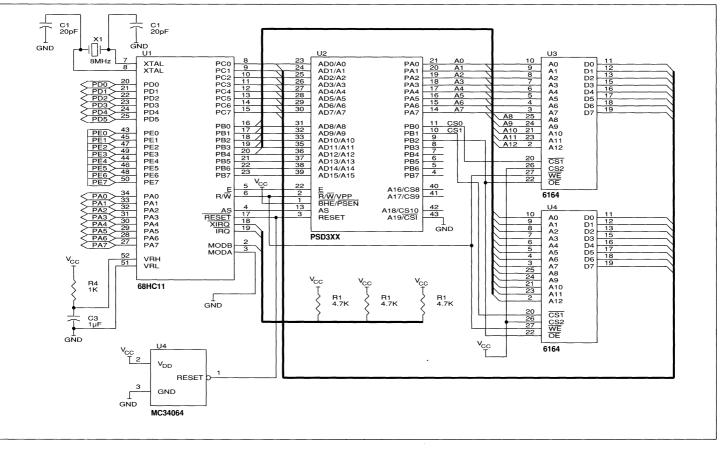

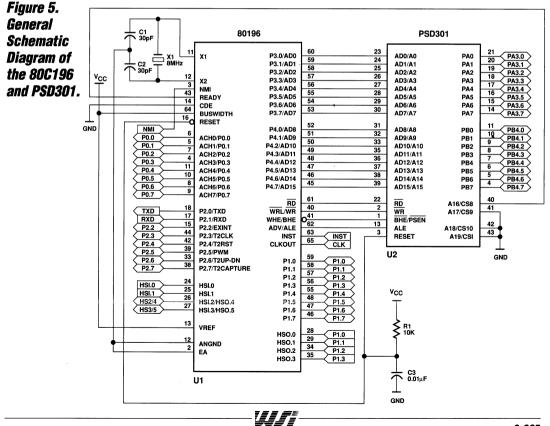

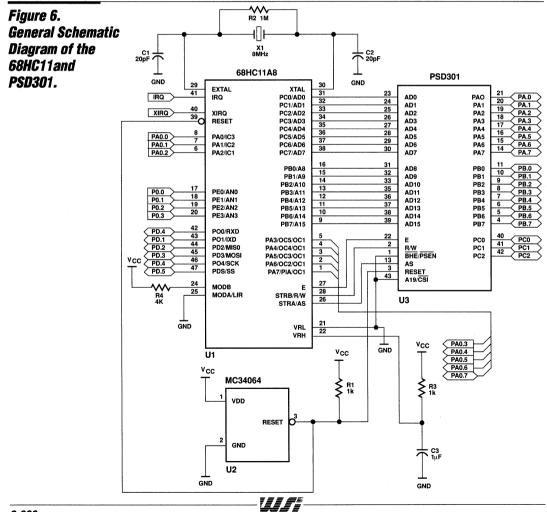

| Introduction           | The PSD301 is a member of the rapidly<br>growing family of PSD devices. The<br>PSD301 is ideal for microcontroller-based<br>applications, where fast time-to-market,<br>small form factor, and low power con-                                                                                            | required control and peripheral elements of<br>a microcontroller-based system peripheral<br>with no external discrete "glue" logic<br>required.                                                                                                                                             |

|                        | sinan form factor, and fow power con-<br>sumptions are essential. When combined<br>in an 8- or 16-bit system, virtually any<br>microcontroller (68HC11, 8051, 8096,<br>16000, etc.) and the PSD301 work together<br>to create a very powerful chip-set solution.<br>This implementation provides all the | The solution comes complete with simple<br>system software development tools for inte-<br>grating the PSD301 with the microcon-<br>troller. Hosted on the IBM PC platforms or<br>compatibles, the easy to use software<br>enables the designer complete freedom in<br>designing the system. |

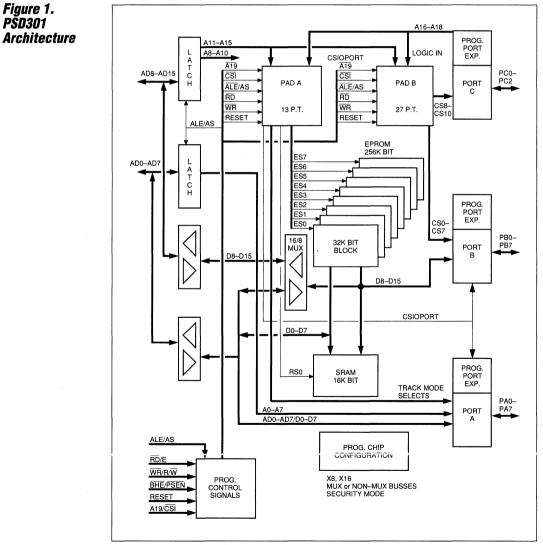

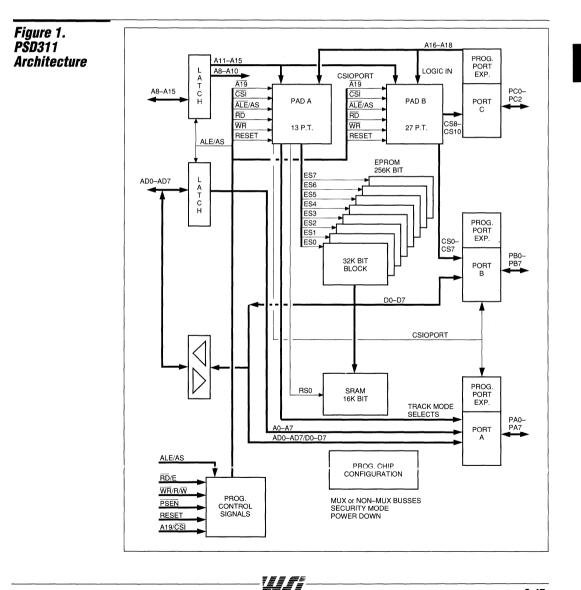

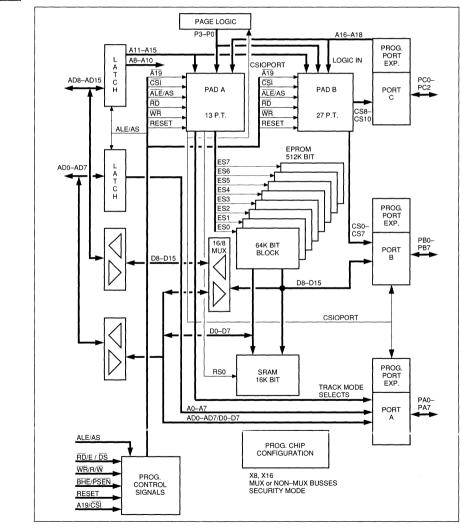

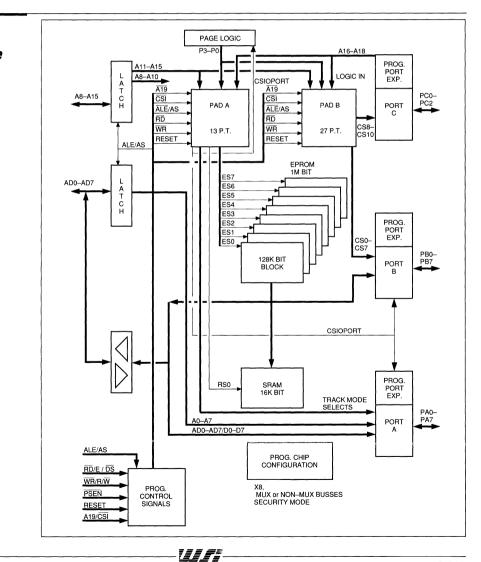

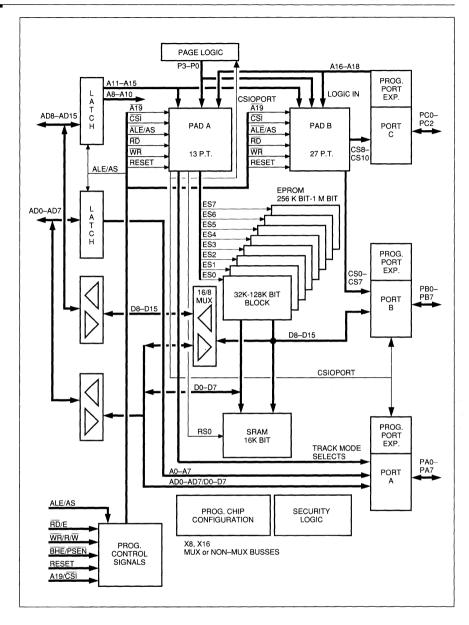

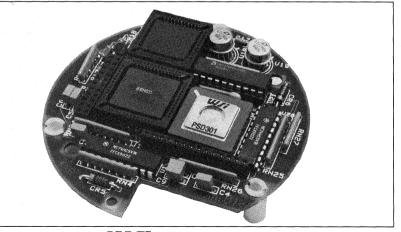

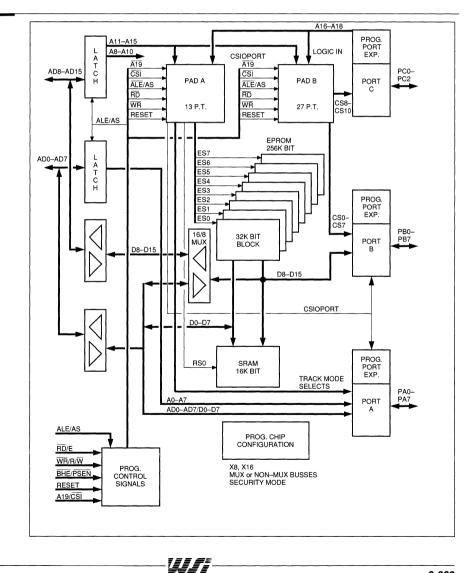

| Product<br>Description | The PSD301 integrates high performance<br>user-configurable blocks of EPROM,<br>SRAM, and programmable logic technology                                                                                                                                                                                  | An interface to shared external resources.                                                                                                                                                                                                                                                  |

|                        | to provide a single chip microcontroller<br>interface. The major functional blocks<br>include two programmable logic arrays,<br>PAD A and PAD B, 256K bits of high speed<br>EPROM, 16K bits of high speed SRAM,                                                                                          | WSI's PSD301 (shown in Figure 1) can effi-<br>ciently interface with, and enhance, any 8-<br>or 16-bit microcontroller system. This is the<br>first solution that provides microcontrollers<br>with port expansion, latched addresses,                                                      |

|                        | input latches, and output ports. The<br>PSD301 is ideal for applications requiring<br>high performance, low power, and very<br>small form factors. These include fixed disk<br>control, modem, cellular telephone, instru-<br>mentation, computer peripherals, military                                  | two programmable logic arrays PAD A and<br>PAD B, an interface to shared resources,<br>256K bit EPROM, and 16K bit SRAM on a<br>single chip. The PSD301 does not require<br>any glue logic for interfacing to any 8- or<br>16-bit microcontroller.                                          |

|                        | and similar applications.<br>The PSD301 offers a unique single-chip<br>solution for microcontrollers that need:                                                                                                                                                                                          | The 8051 microcontroller family can take<br>full advantage of the PSD301's separate<br>program and data address spaces. Users<br>of the 68HCXX family of microcontrollers                                                                                                                   |

|                        | I/O reconstruction (microcontrollers<br>lose at least two I/O ports when<br>accessing external resources).                                                                                                                                                                                               | can change the functionality of the control<br>signals and directly connect the $R/\overline{W}$ and<br>E, or the $R/\overline{W}$ and $\overline{DS}$ signals. Users of 16-<br>bit microcontrollers (including the 80186,                                                                  |

|                        | More EPROM and SRAM than the microcontroller's internal memory.                                                                                                                                                                                                                                          | 8096, 80196, 16XXX) can use the PSD301 in a 16-bit configuration. Address and data                                                                                                                                                                                                          |

|                        | Chip-select, control, or latched address lines that are otherwise implemented                                                                                                                                                                                                                            | buses can be configured to be separate or<br>multiplexed, whichever is required by the<br>host processor.                                                                                                                                                                                   |

W

2-2

# Product Discription (Cont.)

The flexibility of the PSD301 I/O ports permits interfacing to shared resources. The arbitration can be controlled internally by PAD A outputs. The user can assign the following functions to these ports: standard I/O pins, chip-select outputs from the PAD A and PAD B, or latched address or multiplexed low-order address/data byte. This enables users to design add-on systems such as disk drives, modems, etc., that easily interface to the host bus (e.g., IBM PC. SCSI).

The PSD301 on-chip programmable address decoder (PAD A) enables the user to map the I/O ports, eight segments of EPROM (as 4K x 8 or as 2K x 16) and SRAM (as 2K x 8 or as 1K x 16) anywhere in the address space of the microcontroller. PAD B can implement up to 4 sum-ofproduct expressions based on address inputs and control signals.

us:

# PŠD301 Architecture

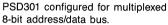

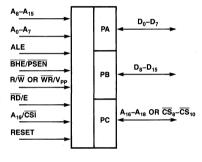

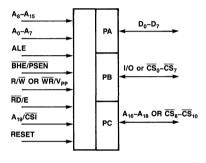

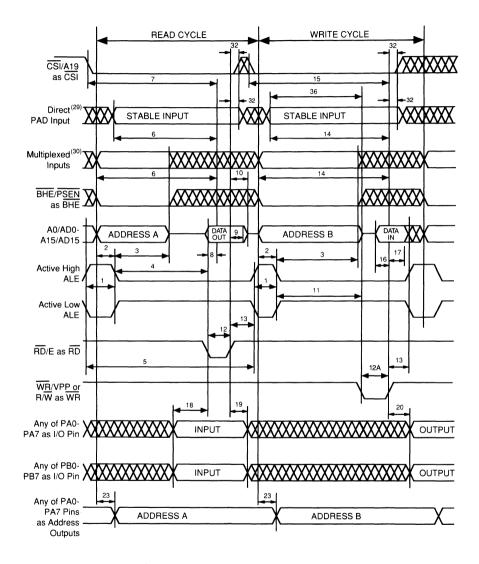

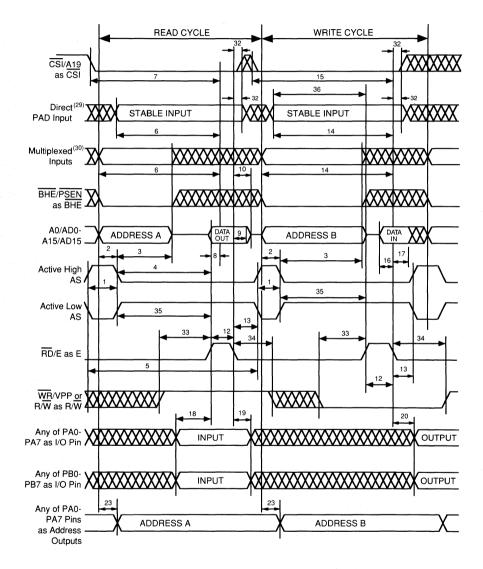

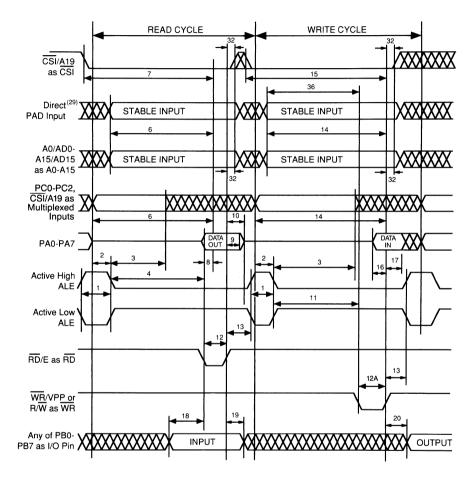

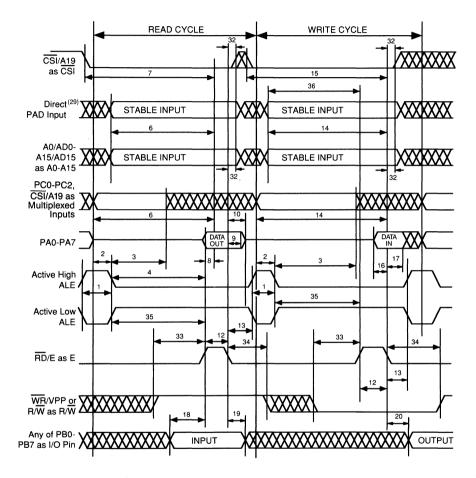

# *Figure 2. PSD301 Port Configurations*

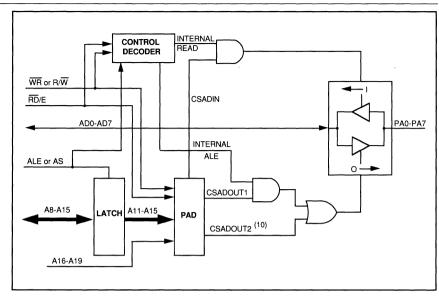

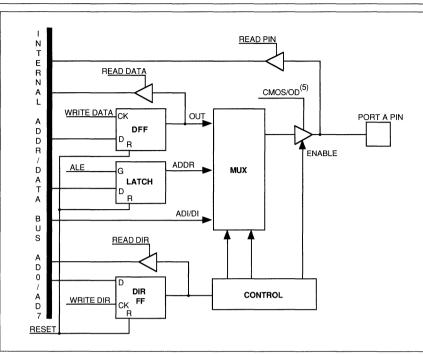

Figure 2 shows the PSD301's I/O port configurations.

PSD301 configured for multiplexed 16-bit address/data bus

PSD301 configured for nonmultiplexed 16-bit address/data bus. 3-bit address/data bus.

PSD301 configured for nonmultiplexed 8-bit address/data bus.

# Legend:

$AD_0-AD_7$  = addresses  $A_0-A_7$  multiplexed with data lines  $D_0-D_7$ .  $AD_8-AD_{15}$  = addresses  $A_8-A_{15}$  multiplexed with data lines  $D_8-D_{15}$ .

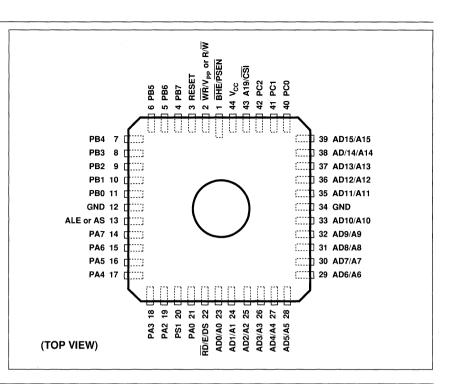

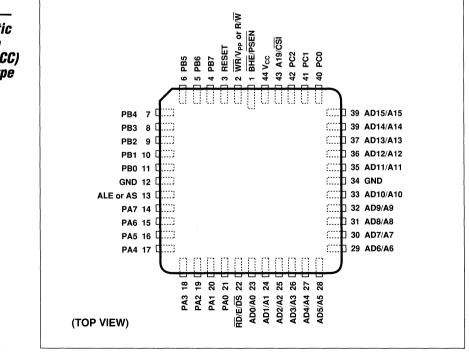

Table 1. PSD301Pin Descriptions

| Name                                         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BHE/PSEN                                     | I    | When the data bus width is 8 bits (CDATA = 0), this pin is $\overrightarrow{PSEN}$ . In this mode, $\overrightarrow{PSEN}$ is the active low EPROM read pulse. The SRAM and I/O ports read signal is generated when $\overrightarrow{RD}$ is low (CRRWR = 0), or when E and $\overrightarrow{RW}$ are high (CRRWR = 1). If the host processor is a member of the 8031 family, $\overrightarrow{PSEN}$ must be connected to the corresponding host pin. In other 8-bit host processors that do not have a special EPROM-only read strobe, $\overrightarrow{PSEN}$ should be tied to V <sub>CC</sub> . In this case, $\overrightarrow{RD}$ or E and $\overrightarrow{R/W}$ provide the read strobe for the SRAM, I/O ports, and EPROM. When the data bus width is configured as 16 (CDATA = 1), this pin is $\overrightarrow{BHE}$ . When $\overrightarrow{BHE}$ is low, a high-order byte is read from, or written into the PSD301, depending on the operation being read or write, respectively. In programming mode, this pin is pulsed between V <sub>PP</sub> and 0. |

| WR/V <sub>PP</sub> or<br>R/W/V <sub>PP</sub> | I    | In the operating mode, this pin's function is $\overline{WR}$<br>(CRRWR = 0) or R/ $\overline{W}$ (CRRWR = 1). When configured as<br>$\overline{WR}$ , a write operation is executed during an active low<br>pulse. When configured as R/ $\overline{W}$ , with R/ $\overline{W}$ = 1 and E = 1,<br>a read operation is executed; if R/ $\overline{W}$ = 0 and E = 1, a<br>write operation is executed. In programming mode, this pin<br>must be tied to V <sub>PP</sub> voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RD/E                                         | I    | When configured as $\overline{RD}$ (CRRWR = 0), this pin provides<br>an active low $\overline{RD}$ strobe. When configured as E (CRRWR<br>= 1), this pin becomes an active high pulse, which,<br>together with $\overline{R/W}$ defines the cycle type. Then, if $\overline{R/W}$ = 1<br>and E = 1, a read operation is executed. If $\overline{R/W}$ = 0 and<br>E = 1, a write operation is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

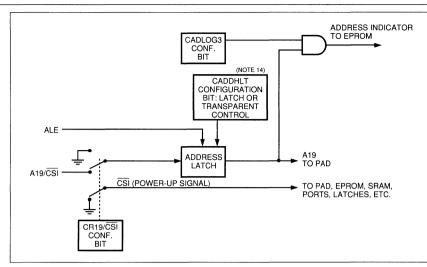

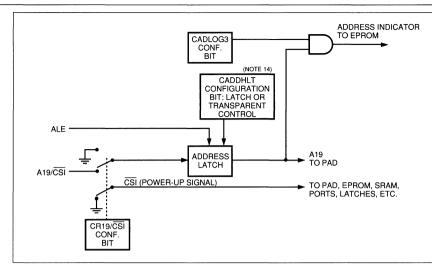

| CSI/A19                                      | I    | This pin has two configurations. When it is $\overline{CSI}$ (CA19/ $\overline{CSI}$ = 0) and the pin is asserted high, the device is deselected and powered down. (See Tables 12 and 13 for the chip state during power-down mode.) If the pin is asserted low, the chip is in normal operational mode. When it is A19, (CA19/ $\overline{CSI}$ = 1), this pin can be used as an additional input to the PAD. In this mode, there is no power-down capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET                                        | Ι    | This user-programmable pin can be configured to reset on<br>high level (CRESET = 1) or on low level (CRESET = 0).<br>It should remain active for at least 100 ns. See Tables 10<br>and 11 for the chip state after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALE or<br>AS                                 | I    | In the multiplexed modes, the ALE pin functions as an Address Latch Enable or as an Address strobe and can be configured as an active high or active low signal. The ALE or AS trailing edge latches lines AD15/A15-AD0/A0, A16-A19, and BHE, depending on the PSD301 configuration. See Table 8. In the non-multiplexed modes, it can be used as a general-purpose PAD input signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Legend: The I/O column abbreviations are: I = input; I/O = input/output; P = power.

NOTE: 3. All the configuration bits mentioned in Table 1 appear in parentheses and are explained in the Configuration Register section.

UJ:

Table 1. PSD301 Pin Descriptions (Cont.)

| Name                                                                                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

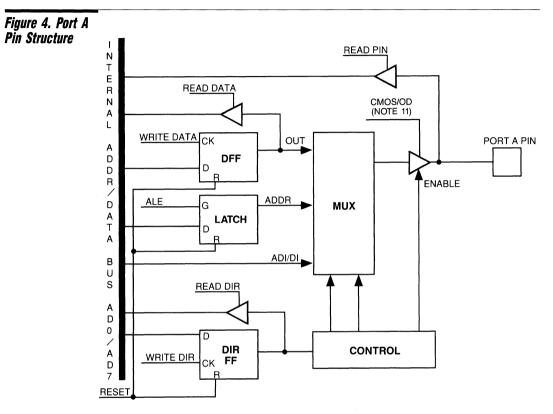

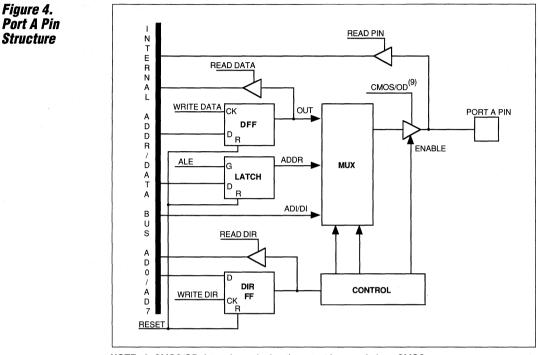

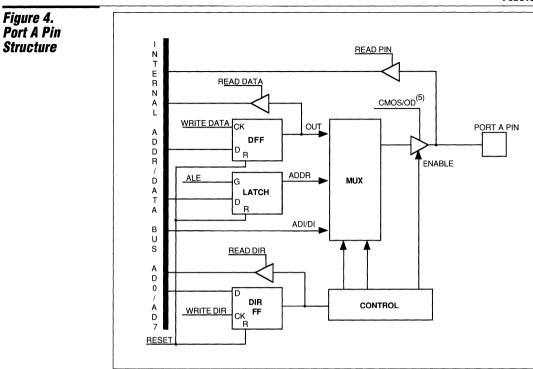

| PA7<br>PA6<br>PA5<br>PA4<br>PA3<br>PA2<br>PA1<br>PA0                                     | I/O  | PA7-PA0 is an 8-bit port that can be configured to track<br>AD7/A7-AD0/A0 from the input (CPAF2 = 1). Otherwise<br>(CPAF2 = 0), each bit can be configured separately as an<br>I/O or lower-order latched address line. When configured<br>as an I/O (CPAF1 = 0), the direction of the pin is defined<br>by its direction bit, which resides in the direction register. If<br>a pin is an I/O output, its data bit (which resides in the<br>data register) comes out. When it is configured as a low-<br>order address line (CPAF1 = 1), A7-A0 can be made the<br>corresponding output through this port (e.g., PA6 can be<br>configured to be the A6 address line). Each port bit can be<br>a CMOS output (CPACOD = 0) or an open drain output<br>(CPACOD = 1). When the chip is in non-multiplexed mode<br>(CADDRDAT = 0), the port becomes the data bus lines<br>(D0-D7). See Figure 4.  |

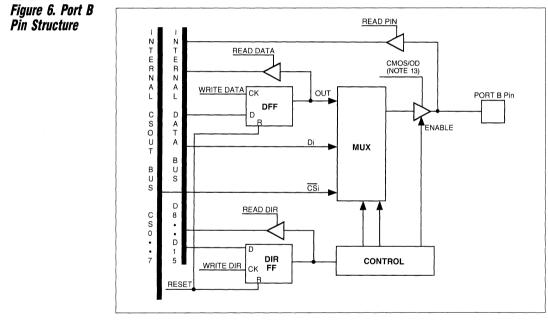

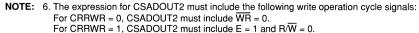

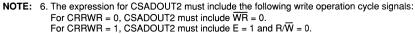

| PB7<br>PB6<br>PB5<br>PB4<br>PB3<br>PB2<br>PB1<br>PB0                                     | 1/0  | PB7-PB0 is an 8-bit port for which each bit can be<br>configured as an I/O (CPBF = 1) or chip-select output<br>(CPBF = 0). Each port bit can be a CMOS output<br>(CPBCOD = 0) or an open drain output (CPBCOD = 1).<br>When configured as an I/O, the direction of the pin is<br>defined by its direction bit, which resides in the direction<br>register. If a pin is an I/O output, its data (which resides in<br>the data register) comes out. When configured as a chip-<br>select output, $\overline{CSO}-\overline{CS3}$ are a function of up to four<br>product terms of the inputs to the PAD; $\overline{CS4}-\overline{CS7}$ then are<br>each a function of up to two product terms. When the chip<br>is in non-multiplexed mode (CADDRAT = 0) and the data<br>bus width is 16 (CDATA = 1), the port becomes the most<br>significant byte of the data bus (D8-D15). See Figure 6. |

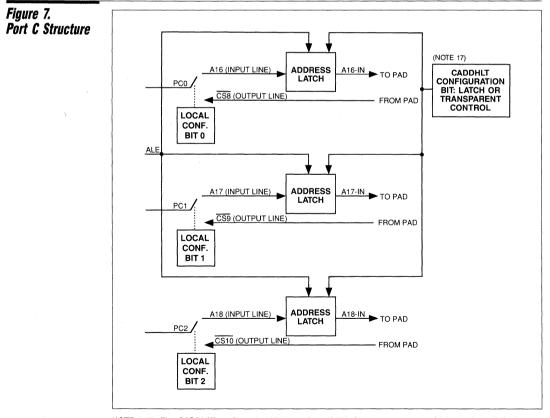

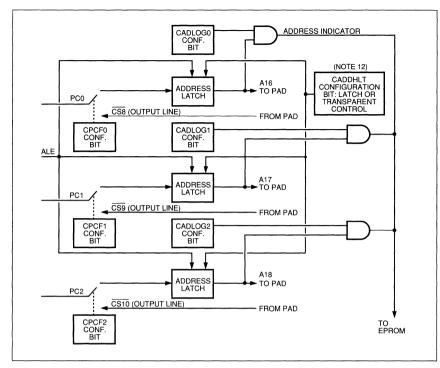

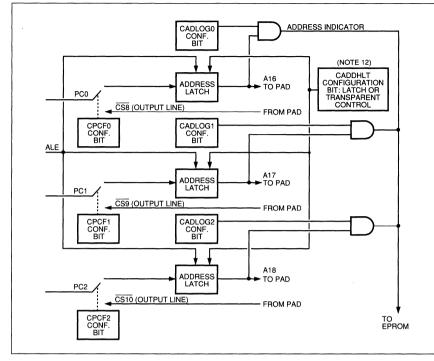

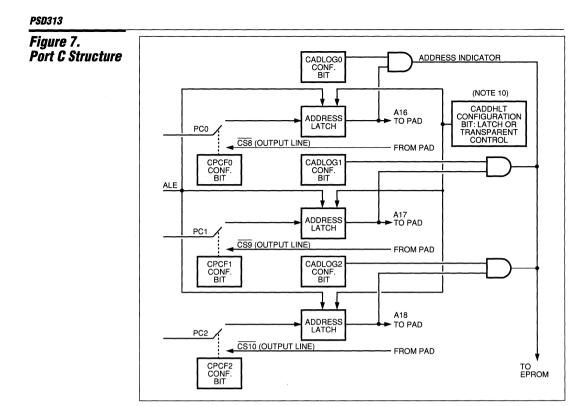

| PC0<br>PC1<br>PC2                                                                        | I/O  | This is a 3-bit port for which each bit is configurable as a PAD input or output. When configured as an input (CPCF = 0), the bits can be latched with ALE (CADDHLT = 1) or be transparent inputs to the PAD (CADDHLT = 0). When a pin is configured as an output (CPCF = 1), it is a function of one product term of all PAD inputs. See Figure 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AD0/A0<br>AD1/A1<br>AD2/A2<br>AD3/A3<br>AD4/A4<br>AD5/A5<br>AD6/A6<br>AD7/A7             | I/O  | In multiplexed mode, these pins are the multiplexed low-<br>order address/data byte. After ALE latches the addresses,<br>these pins input or output data, depending on the settings<br>of the $\overline{\text{RD}}/\text{E}$ , $\overline{\text{WR}}/\text{V}_{\text{PP}}$ or $\overline{R}/\overline{\text{W}}$ , and $\overline{\text{BHE}}/\overline{\text{PSEN}}$ pins. In<br>non-multiplexed mode, these pins are the low-order<br>address input byte.                                                                                                                                                                                                                                                                                                                                                                                                                                |

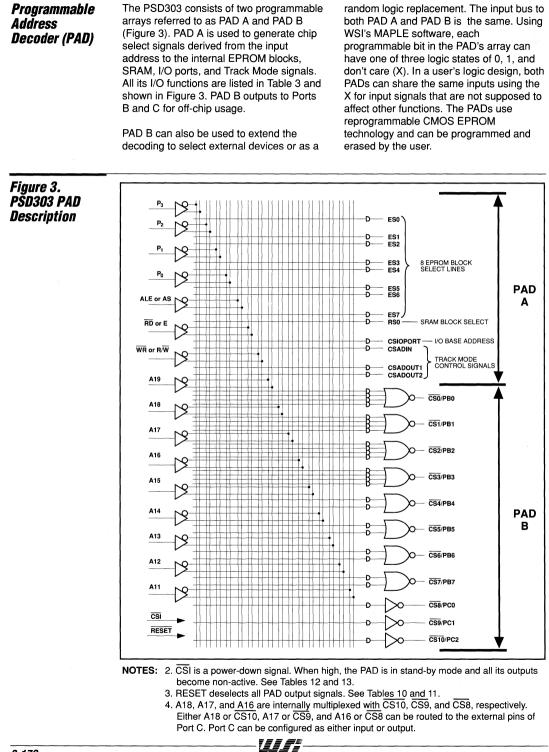

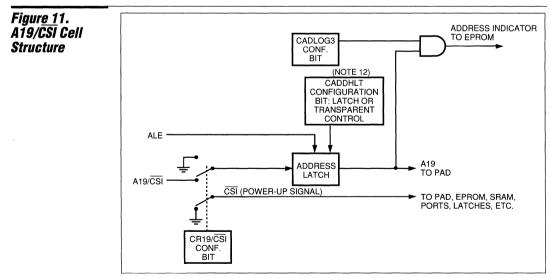

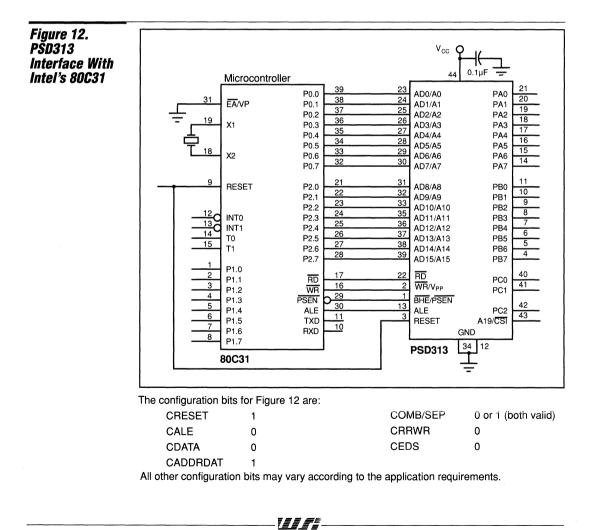

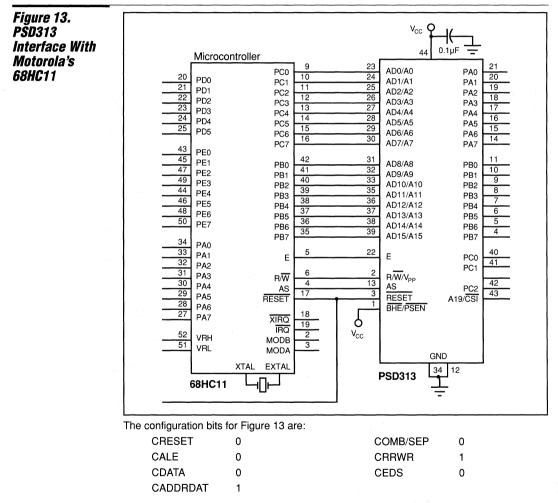

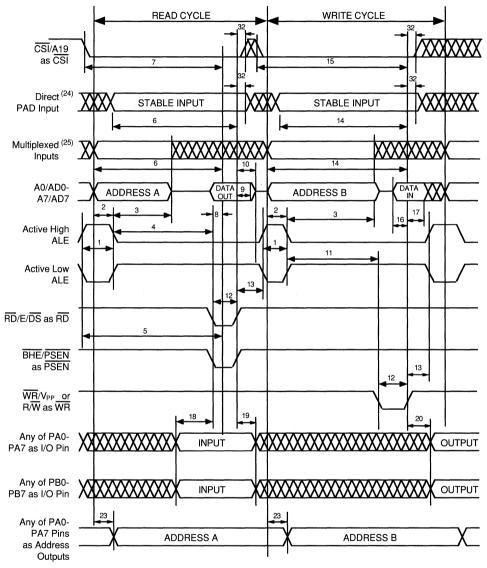

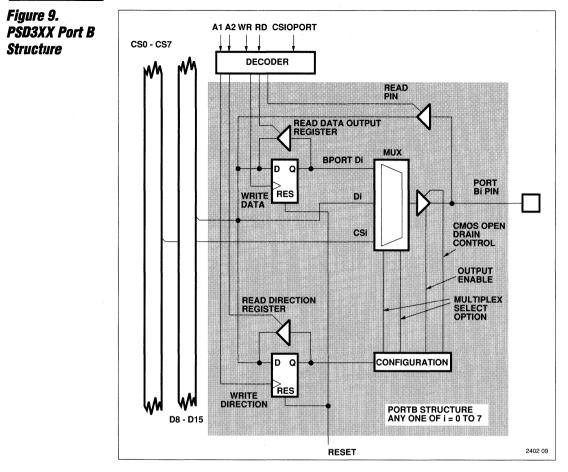

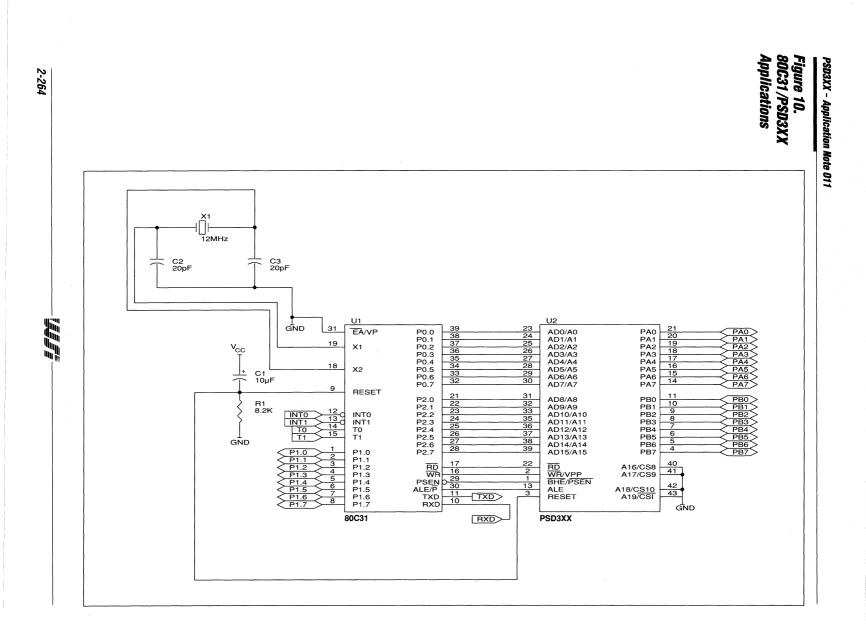

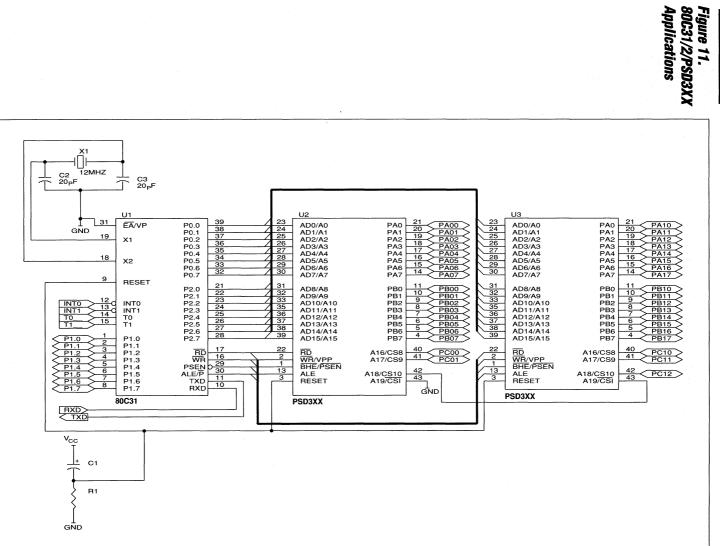

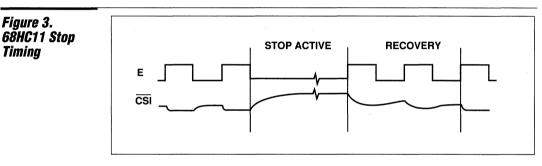

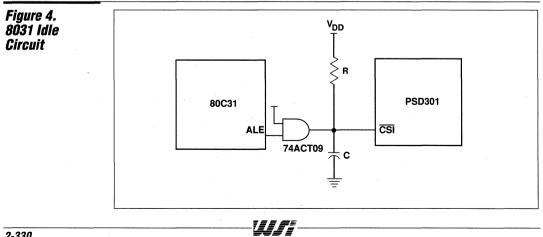

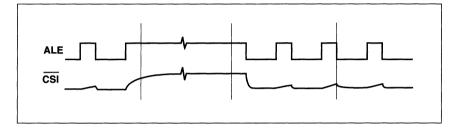

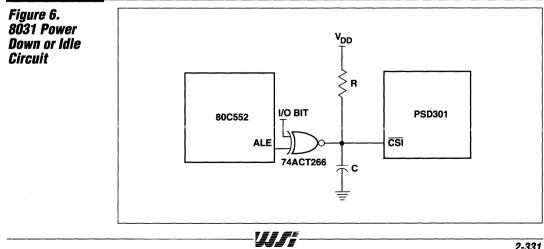

| AD8/A8<br>AD9/A9<br>AD10/A10<br>AD11/A11<br>AD12/A12<br>AD13/A13<br>AD14/A14<br>AD15/A15 | I/O  | In 16-bit multiplexed mode, these pins are the multiplexed<br>high-order address/data byte. After ALE latches the<br>addresses, these pins input or output data, depending on<br>the settings of the RD/E, WR/V <sub>PP</sub> or R/W, and BHE/PSEN<br>pins. In all other modes, these pins are the high-order<br>address input byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |