Programmable System<sup>™</sup> Devices

PSD

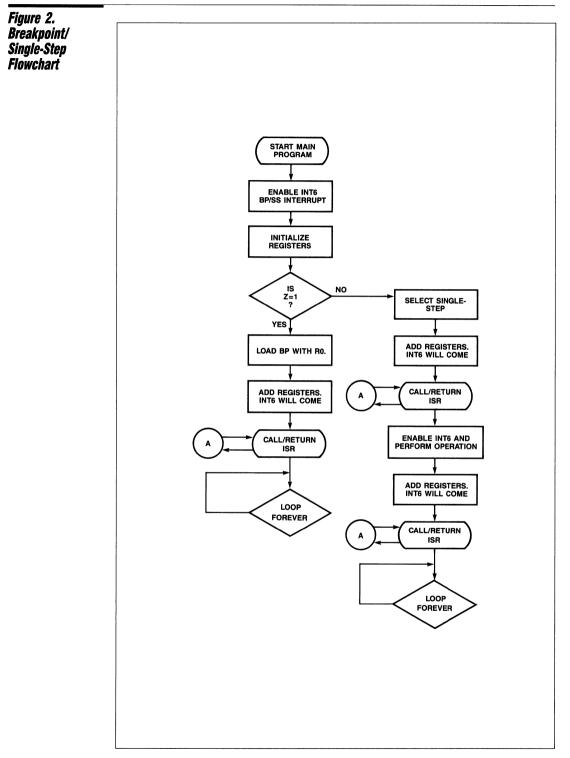

*Design and Applications Handbook* 1990

3350 Scott Blvd. Bldg. #44 • Santa Clara, CA 95054-3120

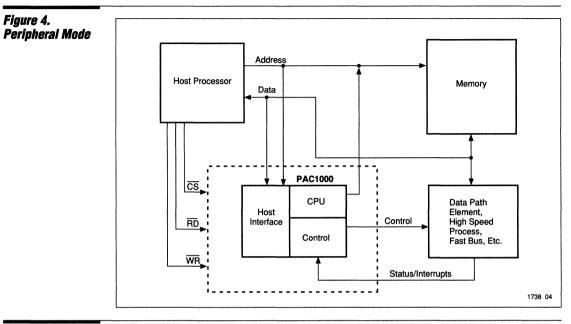

## **Programmable System<sup>™</sup> Devices** (PSD) Design and Applications Handbook

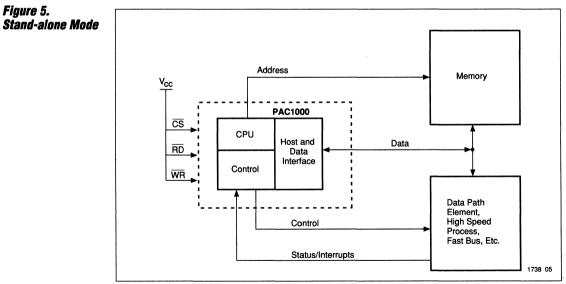

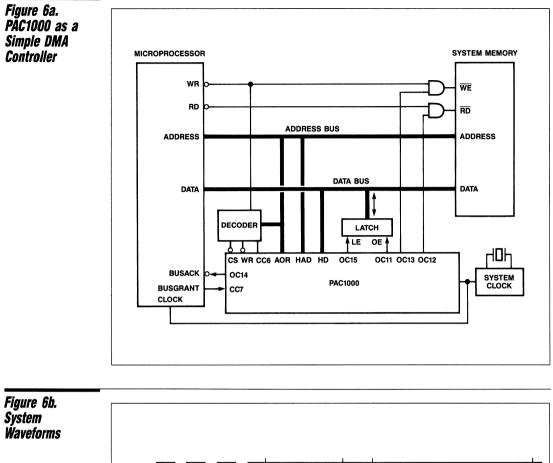

*1990*

Copyright © 1990 WaferScale Integration, Inc. (All rights reserved.)

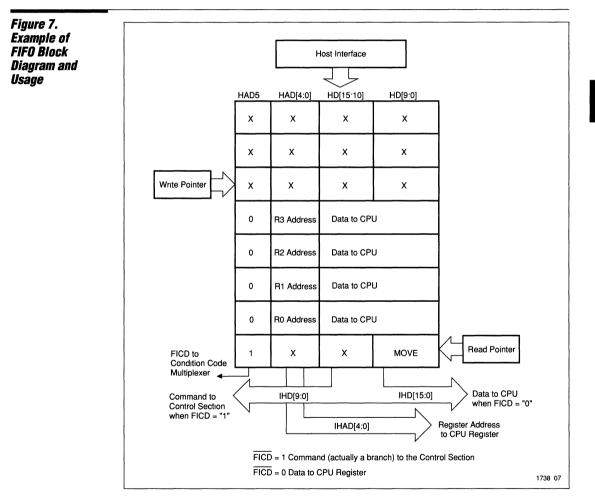

47280 Kato Road, Fremont, California 94538 415-656-5400 Facsimile: 415-657-5916 Telex: 289255

Printed in U.S.A.

. .

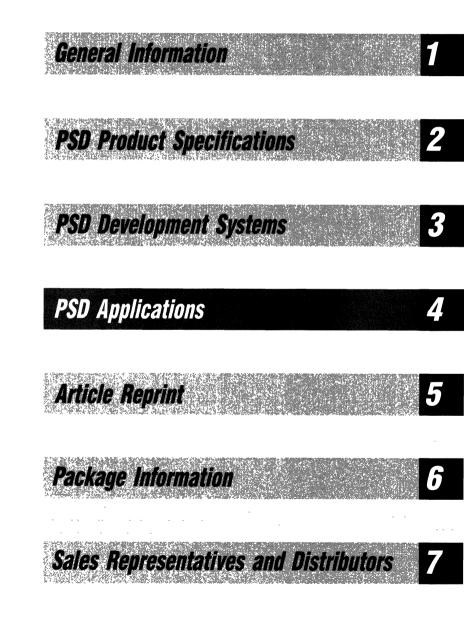

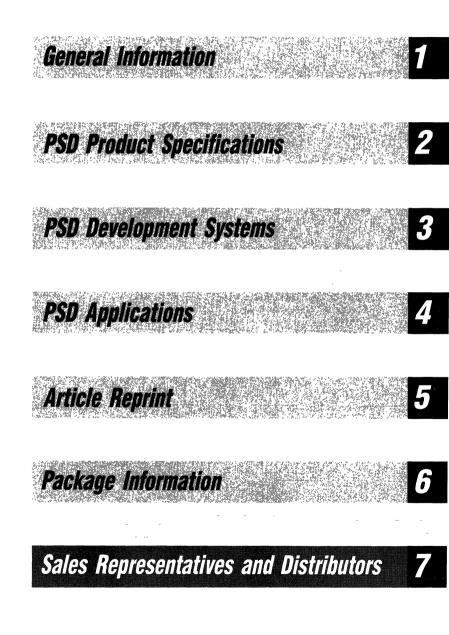

# **General Information PSD Product Specifications PSD Development Systems** 5 **PSD** Applications Article Reprint Package Information 6 Sales Representatives and Distributors

## Section Index

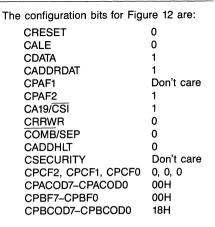

| General     | Table of Contents      | 1-1 |

|-------------|------------------------|-----|

| Information | Introduction to PSDs 1 | 1-3 |

|             | Company Profile        | 1-5 |

|             | Ordering Information   | 1-9 |

For additional information, call 800-TEAM-WSI (800-832-6974). In California, call 800-562-6363.

WAFERSCALE INTEGRATION, INC.

Table of Contents

## General Information Table of Contents 1-1 Introduction to PSDs 1-3 Company Profile 1-5 Ordering Information 1-9

| <b>PSD Product</b><br>Specifications | MAP168/PSD301<br>Introduction | User-Configurable Peripheral with Memory2-1 |

|--------------------------------------|-------------------------------|---------------------------------------------|

|                                      | MAP168                        | User-Configurable Peripheral with Memory2-5 |

|                                      | PSD301                        | User-Configurable Peripheral with Memory    |

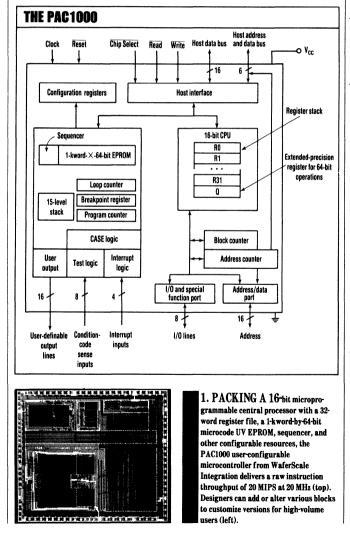

|                                      | PAC1000 Introduction          | User-Configurable Microcontroller           |

|                                      | PAC1000                       | User-Configurable Microcontroller           |

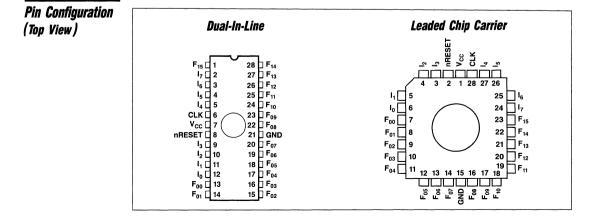

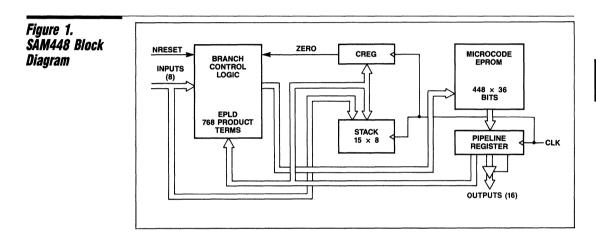

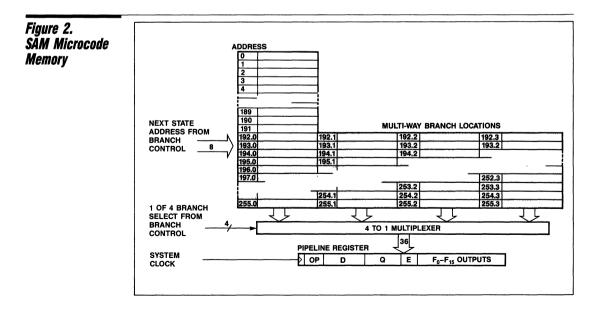

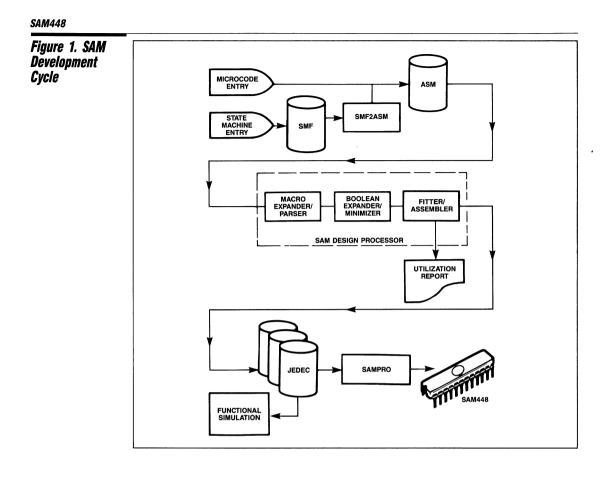

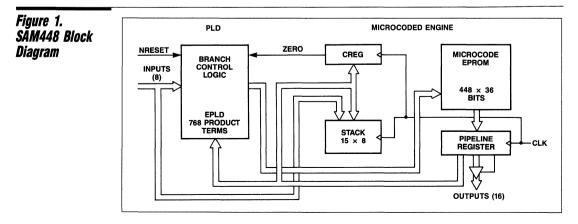

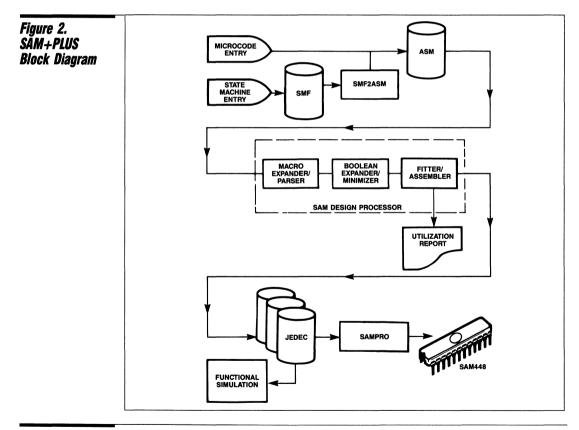

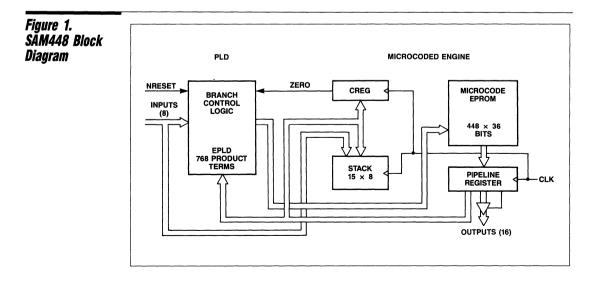

|                                      | SAM448 Introduction           | User-Configurable Microsequencer            |

|                                      | SAM448                        | User-Configurable Microsequencer            |

|         | MAP168 — PSD Development Systems                             | 3-1 |

|---------|--------------------------------------------------------------|-----|

| Systems | SAM448 — PSD Development Systems3                            | -5  |

|         | PAC1000 — PSD Development Systems                            | -9  |

|         | WS6000 MagicPro <sup>™</sup> Programmer and Package Adaptors | 13  |

| <b>PSD</b> Applications | Application Note 002 | Introduction to the MAP168 User-Configurable Mappable Memory Subsystem4-1 |

|-------------------------|----------------------|---------------------------------------------------------------------------|

|                         | Application Note 010 | PAC1000 Introduction4-13                                                  |

|                         | Application Note 005 | PAC1000 as a High-Speed Four-Channel DMA Controller4-39                   |

| Table of Contents                            |                       |                                                                                    |

|----------------------------------------------|-----------------------|------------------------------------------------------------------------------------|

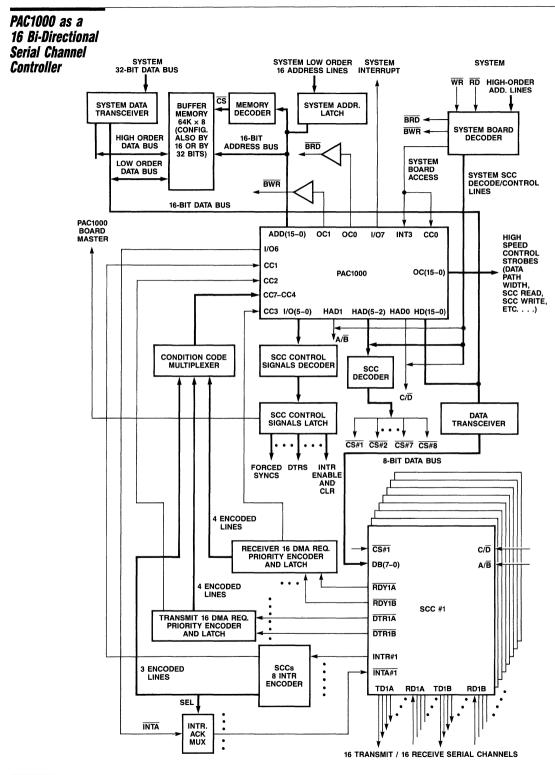

| PSD Applications<br>(Cont.)                  | Application Brief 006 | PAC1000 as a 16 Bi-Directional Serial<br>Channel Controller                        |

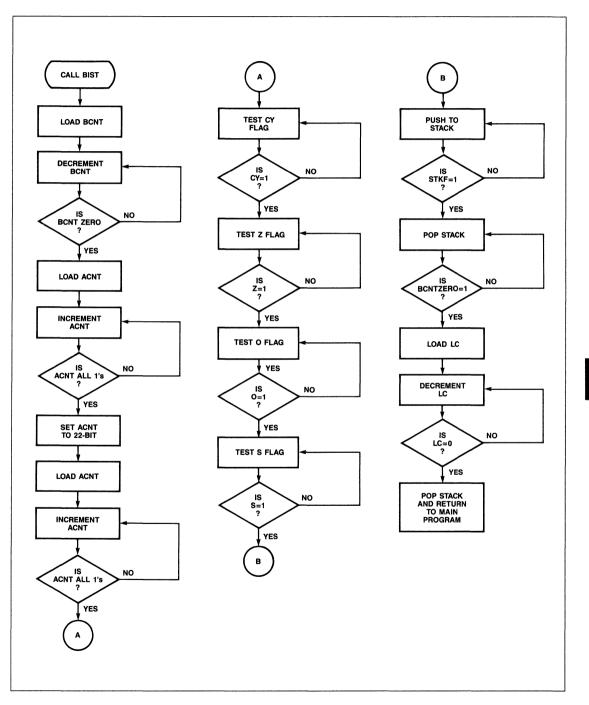

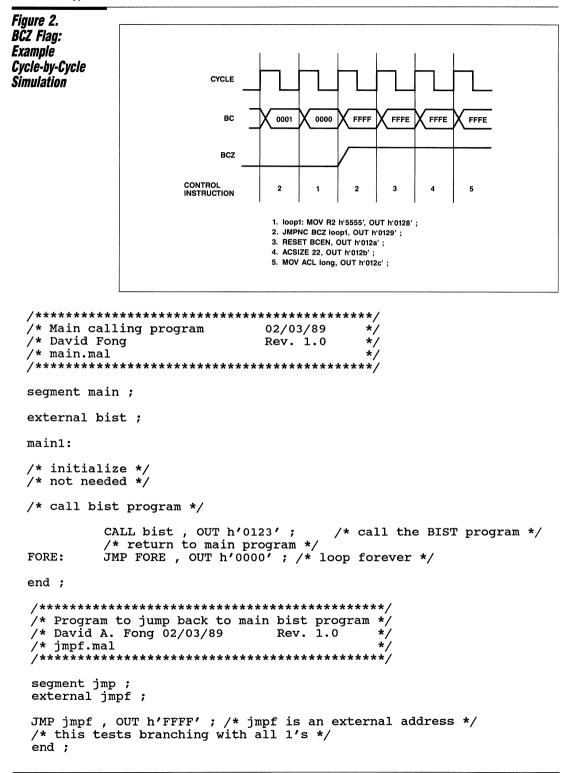

|                                              | Application Note 008  | PAC1000 User-Configurable Microcontroller with a Built-In-Self-Test Capability4-75 |

|                                              | Application Note 009  | In-Circuit Debugging for the PAC1000 User-Configurable Microcontroller4-83         |

|                                              | Application Brief 007 | Hardware Interfacing`the PAC1000 as a<br>Micro Channel Bus Controller4-99          |

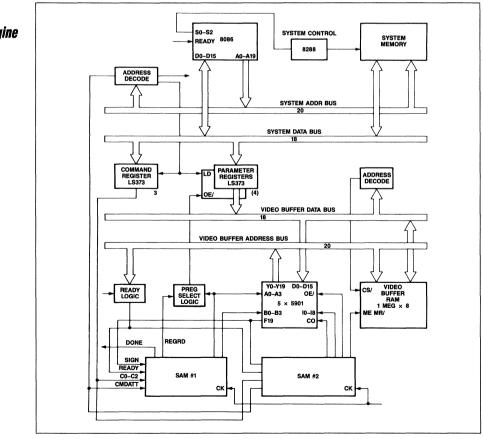

|                                              | Application Note 003  | High-End SAM Applications Using Microassembler Design Entry4-105                   |

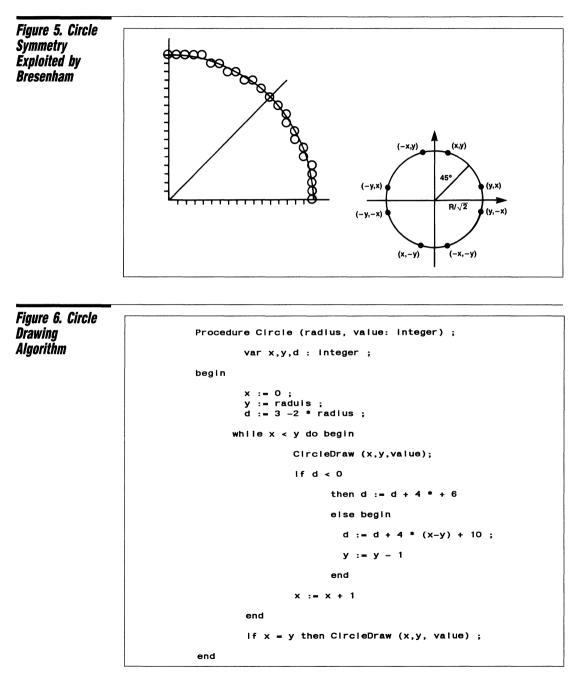

|                                              | Application Note 004  | SAM Applications Using State Machine Design Entry4-127                             |

| Article Reprint                              | Microprogram an Embe  | edded Controller — PAC10005-1                                                      |

| Package<br>Information                       |                       |                                                                                    |

| Sales<br>Representatives<br>and Distributors |                       |                                                                                    |

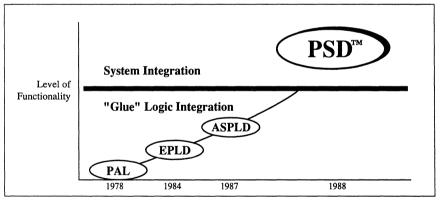

### Introduction to Programmable System<sup>™</sup> Devices (PSD)

Programmable System Devices, or PSDs, are user-configurable system level building blocks on-a-chip enabling quick implementation of application specific controllers and peripherals.

WSI PSDs are ideal for designers who require fast time-to-market, low risk, greater system integration and lower power consumption. PSDs enable designers to configure their microcontroller/peripheral to meet exact design requirements. WSI's PSDs are unique in that they are the only VLSI devices available today that provides a user-configurable off-the-shelf solution at the system level.

The user-configurability of PSDs enables them to be used in many different applications, including:

- Computers (Workstations and PCs) Fixed Disk Control, Modem, Imaging, Laser Printer Control

- Telecommunications Modem, Cellular Phone, Digital PBX, Digital Speech, FAX, Digital Signal Processing

- Industrial Robotics, Power Line Access, Power Line Monitor

- Medical Instrumentation Hearing Aids, Monitoring Equipment, Diagnostic Tools

- Military Missile Guidance, Radar, Sonar, Secure Communications, RF Modems

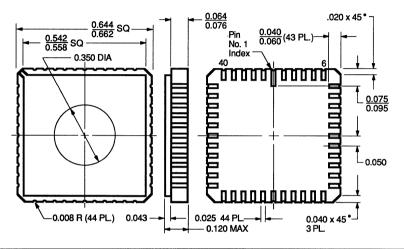

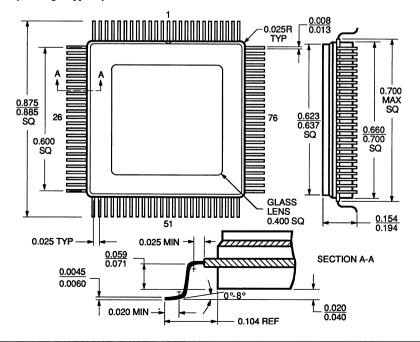

PSDs are available in a variety of space saving surface mount and through-hole package configurations for commercial, industrial, and military applications. WSI offers windowed package options for prototyping and low cost OTP (one-time programmable) packages for high volume applications. PSDs utilize WSI's proprietary split-gate CMOS EPROM technology for low power consumption.

There are currently four PSD family devices in production. These include the PAC1000, MAP168, PSD301, and SAM448.

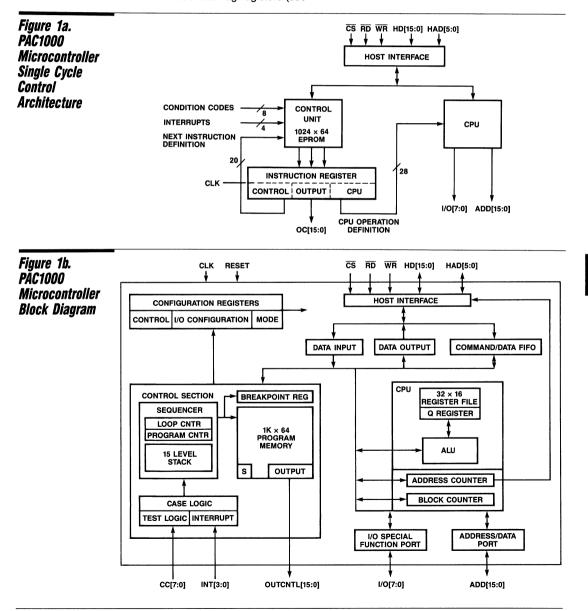

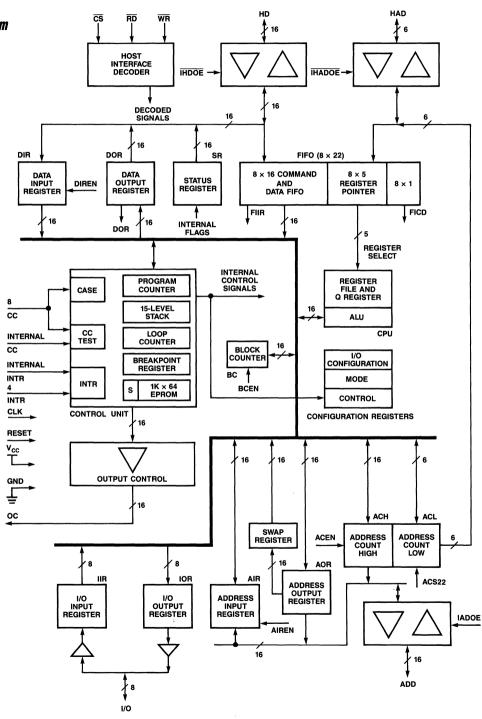

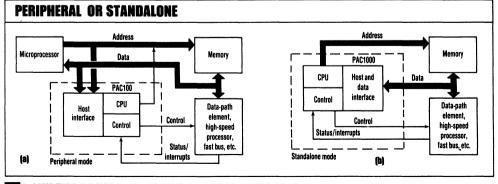

- The PAC1000 is a user-configurable microcontroller. It may be used as a stand-alone microcontroller or as a peripheral to microprocessors. It is ideal for embedded control applications, including graphics, local area network, and disk drive control in both military and commercial applications.

- The MAP168 is a user-configurable peripheral. It is used in DSP applications including modems, motor control and medical instrumentation. The MAP168 is ideal for DSP based applications where fast time-to-market, small form factor and low power consumption are essential. When combined together in an 8- or 16-bit system, virtually any DSP chip (TMS320 series, etc.) and the MAP168 work together to create a very powerful 2-piece chip-set. This combination provides essentially all of the required control and peripheral element of a DSP system.

- □ The PSD301 is a user-configurable peripheral for microcontroller applications including disk drives, low cost modems, and mobile phones. The PSD301 is ideal for microcontroller based applications where fast time-to-market, small form factor and low power consumption are essential. When combined together in an 8- or 16-bit system, virtually any microcontroller (8051, 8096, 16000, etc.) and the PSD301 work together to create a very powerful 2-piece chip-set. This implementation provides the required control and peripheral element of a microcontroller based system peripheral with no external "glue" logic required.

- The SAM448 is a user-configurable sequencer for state machine and bus interface applications. Its flexible I/O and architecture make it ideal for use in interfacing to both existing bus architectures (AT, VME, MCA-bus), and evolving bus standards (EISA, NuBUS).

Application specific features can be easily programmed into the PSD EPROM array for quick design implementation. Unlike the current generation of programmable gate arrays, which require the use of unpredictable, and often time unavailable routing resources, all PSD logic is fully connected internally. This means that all timing is predictable ahead of design implementation, and routing is assured. This greatly simplifies and reduces the design implementation and simulation process, and provides designers with a significantly more reliable. lower risk path to market, WSI PSDs also eliminate the NRE, turn-around-time, and risks associated with gate arrays and other ASIC solutions.

As product life cycles continue to shrink, designers can win the race from idea to marketable product with WSI PSDs. PSDs are quickly configured and programmed by the designer by using low cost, easy-touse WSI PC-based development tools. The user-friendly menu-driven software includes high level design entry, simulation and programming packages for rapid system development.

WSI supports its PSD product family with an applications hotline and bulletin board, as well as highly trained, technical Field Applications Engineers. As standard products, WSI PSDs are available from WSI's franchised world-wide distribution network.

## **Company Profile**

#### Introduction

WaferScale Integration, Inc. (WSI) designs and produces the world's broadest and fastest families of CMOS PROMs, RPROMs, EPROMs, and Programmable System<sup>™</sup> Devices (PSD). These product families target the needs of system designers who must reduce system development time and deliver market competitive products in continuously shorter periods of time. WSI's programmable VLSI products additionally enable higher system performance from smaller, more compact end products due to higher levels of system integration at the chip level.

WSI's mission is clear — to build a great company by serving its customers with a portfolio of high-performance programmable VLSI products that enable designers to achieve faster time to market with new, advanced electronic systems.

The company's patented self-aligned, splitgate EPROM technology forms the core of WSI's programmable products and delivers higher performance and greater density than competing "stacked gate" EPROM technologies. This core technology has enabled WSI to be first in the industry with numerous breakthroughs in speed, density, process and packaging. WSI has leveraged this technology into the broadest family of CMOS PROMs, RPROMs, and EPROMs available. WSI's new "off the shelf" user-configurable PSDs provide system level building blocks on a single chip that enable quick implementation of application specific controllers and peripherals. They are the first to integrate high-performance EPROM, SRAM and logic and deliver a performance and integration breakthrough to the programmable products market. PSDs are user-configurable on a PC or compatible and can be tailored for use in a variety of system applications. As a result, WSI has established itself as a leading supplier of high-performance programmable VLSI solutions to a broad customer base that includes some of the world's largest and most technologically advanced electronics companies.

Founded in 1983, WSI is headquartered in a 66,000 square foot facility in Fremont, California and has more than 125 employees. Through a long-term equity, manufacturing and technology license agreement with Sharp Corporation of Japan, WSI produces its products in a world-class products in facility that guarantees the highest quality at competitive costs.

#### Markets and Applications

WSI's high-performance non-volatile memory and PSD products are used by the world's leading suppliers of highperformance electronic systems in communications, data processing, military and industrial markets. Customer end products cover a broad spectrum and typically include cellular telephones, workstations, DSP computers, navigation controllers, T1 multiplexers, modems, image processors, missiles, LAN controllers, high density disk drives and the like. Customer applications include image processing, digital signal processing, bus control, LAN data and file control, real time process control, graphics processing, hard disk control, flight simulators, DMA control, and others. WSI products are ideally suited for these applications where designers are faced with increasingly shorter product life cycles and must develop new, competitive high-performance products in short periods of time.

1-5

#### **Products**

#### Memory Products

#### **EPROM**s

WSI offers the broadest line of CMOS EPROM products available featuring architectures ranging from  $8K \times 8$  to  $128K \times 8$ , plus several  $\times 16$  products, with speeds ranging from 40 to 200 ns. Commercial, industrial and MIL-STD-883C/ SMD products are available. A wide variety of package selections are available including plastic and hermetic, throughhole and surface mount types.

#### "L' Family

WSI's "L" family memory products are the industry's fastest, low power JEDEC pinout EPROMs and meet the requirements of many mainstream system applications. With speeds ranging from 90 to 200 ns and architectures from 8K × 8 to 128K × 8 including several ×16 products, "L" family EPROMs are ideal for high-performance personal computers and workstations. Taking advantage of its split-gate EPROM technology, WSI uses a conservative 1.2 micron lithography to achieve world-class memory densities that traditionally require lower yielding sub-micron technologies.

#### "F" Family

The "F" family is WSI's fastest line of EPROMs, featuring speeds ranging from 40 to 110 ns and architectures from  $8K \times 8$  to  $32K \times 8$ , plus several  $\times 16$  products. The high speed and word width options of the "F" family EPROMs make them attractive for use in high-end engineering and scientific workstations, data communications and other high-performance applications.

#### **RPROM**s

RPROMs provide bipolar PROM pin-out with matching speed and CMOS low power operation. The RPROM (Re-Programmable Read Only Memory) product series includes architectures ranging from  $2K \times 8$  to  $32K \times 8$  with speeds ranging from 25 to 70 ns.

Commercial, industrial and MIL-STD-883C/ SMD configurations are available in a variety of hermetic and plastic package styles.

#### Programmable System<sup>™</sup> Devices (PSDs)

WSI's family of Programmable System Devices (PSDs) represent a new class of programmable VLSI products, achieving unparalleled levels of performance, configurability and integration. Offering a significantly higher level of integration over programmable logic, PSDs are the first programmable VLSI products to integrate high-speed EPROM. SRAM and logic on a single chip thereby providing complete system solutions to the design engineer. PSDs are off-the-shelf system building elements that can be quickly configured and programmed for a variety of system applications thus enabling system designers to shorten system development time.

The PSD is a new solution for system designers who build high-end systems around embedded controllers and advanced microprocessors. These new systems require faster, more highly integrated and lower cost VLSI solutions as well as rapid design cycles. WSI's new PSD family meets this demanding set of needs.

The initial members of WSI's PSD family includes:

- The PAC1000 User-Configurable Microcontroller

- The MAP168 User-Configurable Peripheral with Memory

- The PSD301 User-Configurable Peripheral with Memory

- The SAM448 User-Configurable Microsequencer

| Products                   | –<br>Design Tools and Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Custom Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

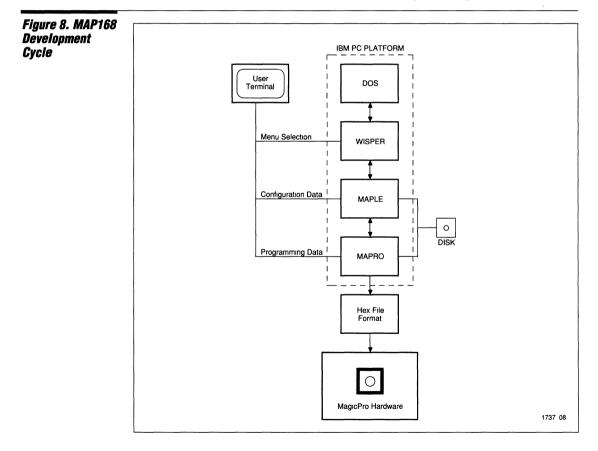

| (Cont.)                    | WSI's development tools minimize the time<br>required for designers to program PSDs<br>for use in a variety of system applications.<br>PSDs are supported with complete easy-<br>to-use program development, simulation<br>and programming software, the PC hosted<br>MagicPro <sup>™</sup> Memory and PSD Programmer,<br>a dial-in applications bulletin board and<br>WSI's team of factory and field<br>applications engineers. As a result, WSI<br>customers achieve their goal of shorter<br>system development time and reach new<br>markets sooner.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | To serve the needs of its customers with<br>unique requirements, WSI offers its custom<br>circuit capability using its cell based library<br>of EPROM, static RAM and logic functions.<br>Standard products described in this catalog<br>can usually be modified on a custom basis<br>to serve particular requirements. New<br>customer defined custom products that<br>incorporate high-performance non-volatile<br>memory, SRAM and logic can be<br>produced that deliver significant speed or<br>system integration advantages. Contact<br>your local WSI sales office for additional<br>information.                                                                                                                                                                                                                                                       |

| Manufacturing              | A key ingredient for success in leading-<br>edge semiconductors is a world-class<br>fabrication facility that ensures high<br>volume capacity and prompt delivery of<br>highly reliable and high yielding VLSI<br>circuits. To this end, WSI has licensed its<br>proprietary CMOS EPROM and logic<br>process technology to Sharp Corporation<br>of Osaka, Japan. This long term alliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ensures high quality, high-volume<br>production, competitive costs and fast<br>delivery. The Sharp facility in Fukuyama,<br>Japan employs the most advanced sub-<br>micron VLSI integrated circuit manufacturing<br>equipment available including ion<br>implantation, reactive ion etch, and wafer<br>stepper lithographic systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Quality and<br>Reliability | WSI is deeply committed to product<br>excellence. This begins with proper<br>management attitude and direction and<br>with this focus, the Quality and Reliability<br>Program is able to operate efficiently. As a<br>result, product quality becomes part of<br>each employee's responsibility.<br>Quality and Reliability begin with the<br>proper product and process designs and is<br>supported by material and process controls.<br>Examples are products manufactured on<br>an epitaxial silicon layer to reduce latch-up<br>sensitivity, all pins are designed to<br>withstand >2,000 volts ESDS, numerous<br>ground taps are used which increases<br>product noise immunity, metal traces are<br>designed to carry a current density of<br>>2.0 × 10 <sup>5</sup> amps/cm <sup>2</sup> , top passivation<br>extends over into the scribe lane to seal<br>the die edges, data retention is performed<br>100% on re-programmable products (T <sub>A</sub> =<br>+225°C, T = 72 hours), automated die<br>attach and bonding is used extensively,<br>wafers are fabricated in a Class 10 clean | are inspected before use, and statistical controls are used to keep the process on course.<br>Product and process introductions or changes are routinely evaluated for worthiness. Life tests are conducted at higher than typical stress levels ( $T_A = +150^{\circ}$ C, $V_{CC} = +6.5V$ ) and even at these stress levels, WSI products have demonstrated low failure rates (see the Quality and Reliability section in the WSI 1990 databook).<br>WSI is active in Military programs and its Quality and Reliability System supports Compliant Non-Jan products. WSI also supports DESC's (Defense Electronics Supply Center) Standardized Military Drawings (SMD) program. As of October, 1989, WSI has eighteen products on SMDs with additional products not on SMDs are available per MIL-STD-883C. See Section 7 (Military Products) in the WSI 1990 |

room, raw materials, chemicals and gases

Sales Network

WSI's international sales network includes regional sales managers, field applications engineers, manufacturers representatives and many of the leading component distributors in the United States, Europe and Asia. See Section 7.

#### **United States**

Direct sales and field applications engineering offices in Boston, Chicago, Huntsville, Philadelphia, Los Angeles areas and Fremont, CA; more than 25 manufacturers' representatives for major national accounts; national distributors including Schweber Electronics, Time Electronics and Wyle Laboratories; and regional distributors.

#### International

Distributors in West Germany, England, France, Italy, Sweden, Finland, Denmark, Norway, Spain, Belgium, Luxembourg, the Netherlands, and Israel. Distributors for the Asia/Pacific Rim region in Japan, Korea, Taiwan, Hong Kong and Australia.

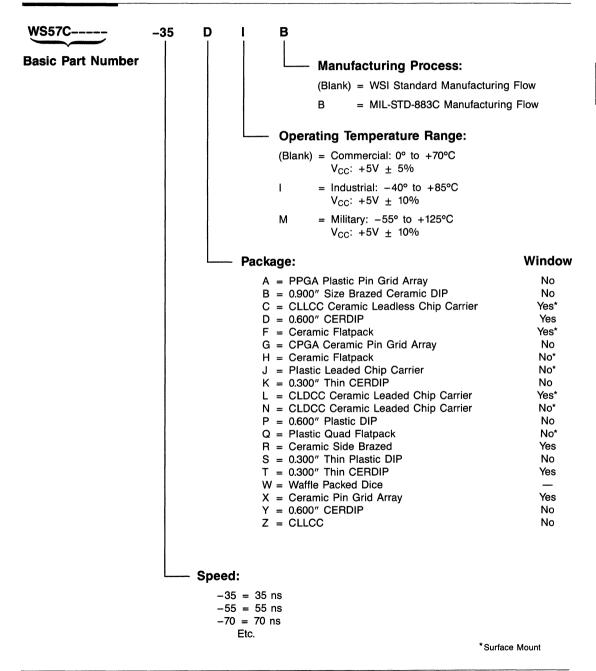

## **Ordering Information**

## High-Performance CMOS Products

## Section Index

| PSD Product<br>Specifications | MAP168/PSD301<br>Introduction | User-Configurable Peripheral with Memory2-1   |

|-------------------------------|-------------------------------|-----------------------------------------------|

|                               | MAP168                        | User-Configurable Peripheral with Memory      |

|                               | PSD301                        | User-Configurable Peripheral with Memory 2-23 |

|                               | PAC1000 Introduction          | User-Configurable Microcontroller             |

|                               | PAC1000                       | User-Configurable Microcontroller             |

|                               | SAM448 Introduction           | User-Configurable Microsequencer              |

|                               | SAM448                        | User-Configurable Microsequencer              |

For additional information, call 800-TEAM-WSI (800-832-6974). In California, call 800-562-6363.

WAFERSCALE INTEGRATION, INC.

## Programmable System™Device

MAP168/PSD301 Introduction

#### User-Configurable Peripheral with Memory

Overview

In 1988 WSI introduced a new concept in programmable VLSI: the Programmable System<sup>™</sup> Device (PSD). The PSD is defined as a family of *User-configurable* system level building blocks on-a-chip enabling quick implementation of application specific controllers and peripherals. The first generation PSD series includes the MAP168, a User-Configurable Peripheral with Memory; the SAM448, a User-Configurable Microsequencer; and the PAC1000, a User-Configurable Microcontroller.

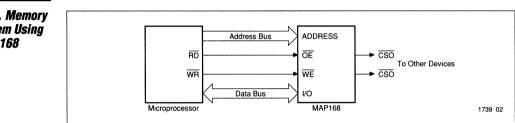

The MAP168 is a high-performance, userconfigurable peripheral with memory. It is used in DSP applications including modems, motor control and medical instrumentation. The MAP168 is ideal for DSP based applications where fast time-tomarket, small form factor and low power consumption are essential. When combined together in an 8- or 16-bit system, virtually any DSP chip (TMS320 series, etc.) and the MAP168 work together to create a very powerful 2-piece chip-set. This implementation provides the core of the required control and peripheral elements of a DSP system. The MAP168 contains three elements normally associated with discrete solutions to system memory requirements. It incorporates EPROM and SRAM plus a Programmable Address Decoder (PAD), all on the same die. The MAP168 is ideal for the systems designer who wishes to reduce the board space of his final design. By using the MAP168 in a system, five or six EPROM, SRAM and decode logic chips may be reduced into a single 44 pin PLDCC, CLDCC or PGA package.

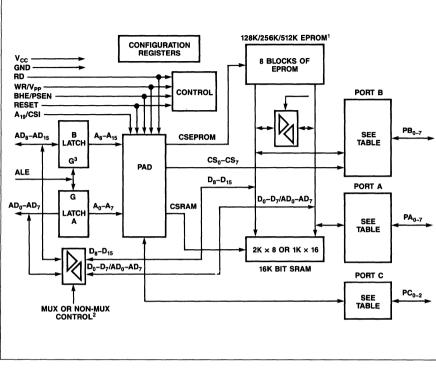

The second generation PSD301 is a userconfigurable peripheral for microcontroller applications including disk drives, low cost modems, and mobile phones. The PSD301 is ideal for microcontroller based applications where fast time-to-market, small form factor and low power consumption are essential. When combined together in an 8- or 16-bit system, virtually any microcontroller (8051, 8096, 16000, etc.) and the PSD301 work together to create a very powerful 2-piece chip-set. Together, this implementation provides all the required control and peripheral elements of a microcontroller based system peripheral with no external "glue" logic required.

#### Architecture

The MAP168 and PSD301 products incorporate the flexibility of using discrete memory addressing and decoding. With the support of WSI's user friendly PSD software called MAPLE, designers may configure their MAP168/PSD301 subsystems for 8 or 16 bit data paths. If the host system uses an 8051 microcontroller, the MAP168/PSD301 can be programmed with an eight bit data path. A sixteen bit data path can be programmed for microcontrollers like Intel's 80196. The depth of the memory organization will be modified accordingly to accept the different data path widths. The low cost MAPLE software package will handle the data path width adjustment automatically. The user can select either 16K bytes of EPROM and 4K bytes of SRAM or 8K words of EPROM

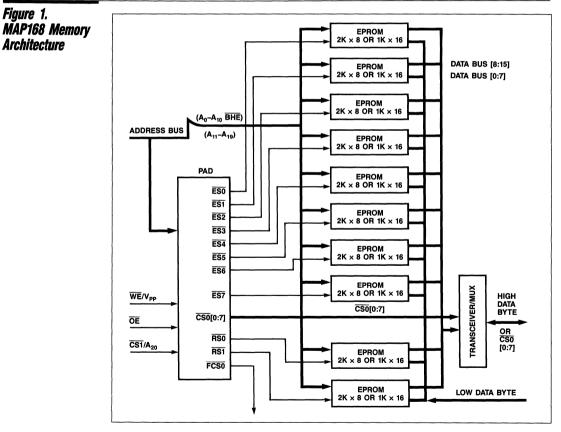

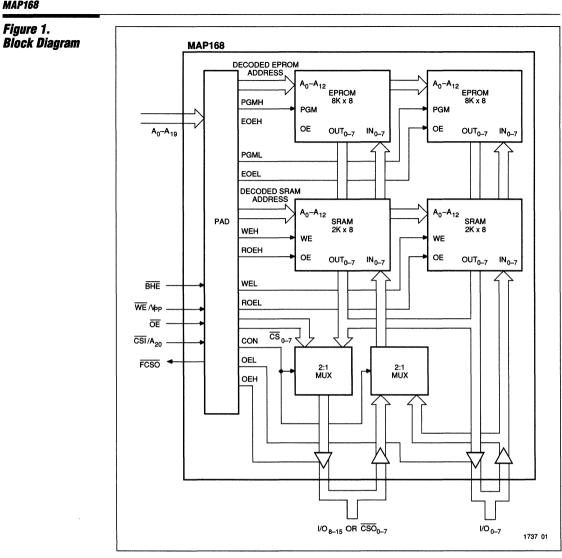

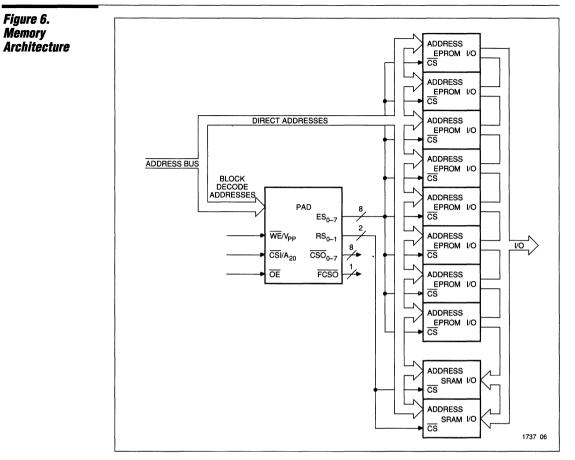

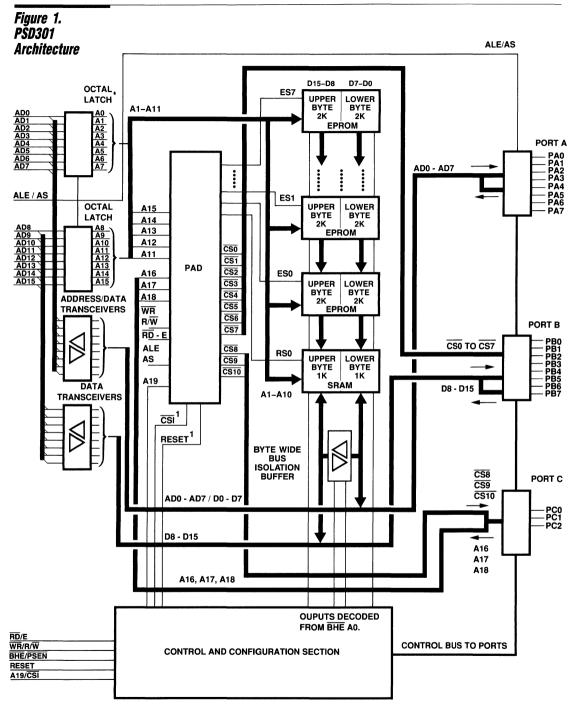

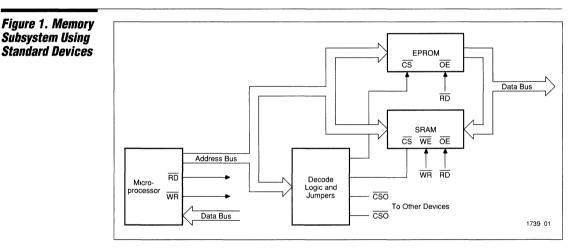

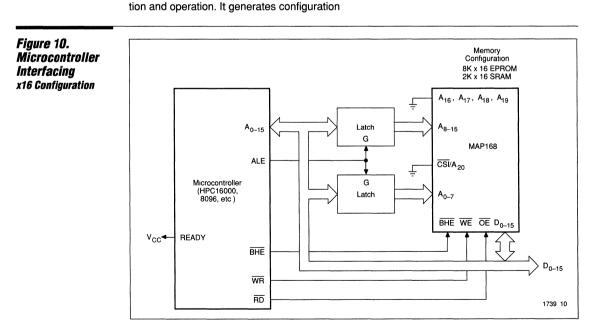

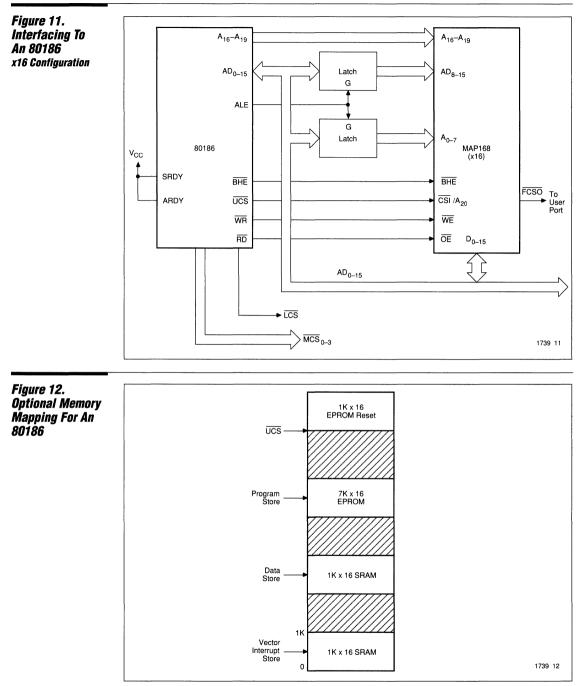

and 2K words of SRAM. The flexibility of the MAP168/PSD301 products enables two devices to be cascaded in width. It is possible to double the memory size of a sixteen bit system by using two MAP168 products in parallel but programmed in a byte-wide configuration. For example, with two MAP168 devices, 16K words of EPROM and 4K words of SRAM may be organized as upper and lower data bytes of a 16 bit word. Alternately, two MAP168 chips may expand the system memory vertically as two word organized memory devices. A block diagram of the MAP168 is shown in Figure 1.

An important feature of the MAP168/PSD301 products is their ability to incorporate the memory address decoding on-chip. One

Architecture (Cont.)

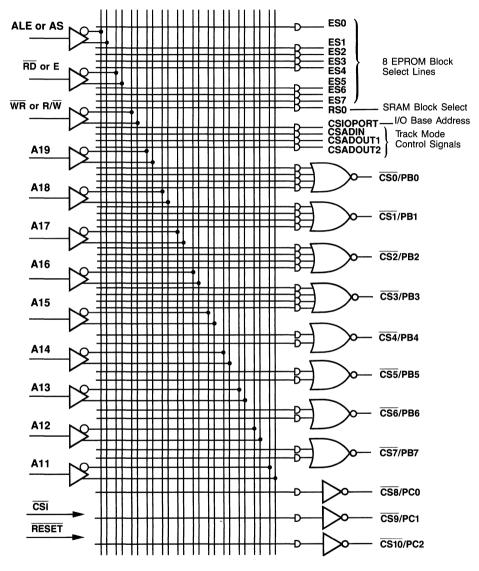

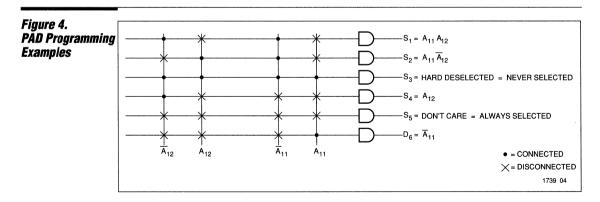

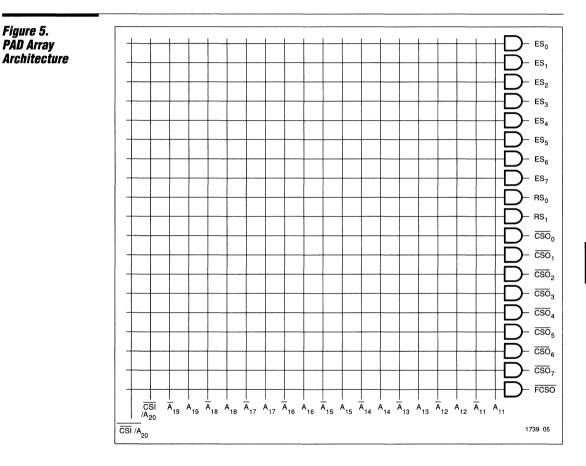

MAP168 memory peripheral can reside with other MAP168 devices in the same memory addressing scheme, with the onchip decoder allocating the memory blocks to different non-conflicting segments of the entire memory area. The decoding function is achieved by an on-chip feature called a Programmable Address Decoder (PAD), which is similar to a single fuse array programmable logic device supporting one product term (AND gate) per output in the MAP168 and four product terms per output in the PSD301.

In the MAP168, eighteen standard chip select outputs from the PAD are available with one fast chip select output generally used to select other external high speed memory devices. The chip select lines may be subdivided into ES0–ES7, active low internal EPROM chip selects, and two internal RAM chip selects RS0 and RS1. In byte-wide applications, eight chip select outputs drive external pins CS0–CS7. These can be used as external chip selects for other MAP168 devices or system memory. These outputs are not available for word-wide MAP168 configurations because the CS0–CS7 output pins carry the higher order data byte. Only FCS0 is available for external chip selection.

Figure 1 shows the organization of the EPROM and SRAM in relation to the PAD, for the MAP168 device.

#### Important Features:

- 40 ns EPROM/SRAM Access Time.

- Byte or Word Operation, Mappable into 1M Word or 2M Byte Address Space

- 22 ns Chip-Select 8 Outputs, 17 ns Fast Chip Select Output.

- 128K EPROM Bits, 32K SRAM Bits, On-Chip Programmable Decoder, Security Bit.

#### Figure 2. PSD301 Family Architecture

|                                   | By 8 Co                                                                                                             | nfiguration                                                                       | By 16 Con                                                                                                           | figuration                                                           |                                                                                    |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                   | Port A                                                                                                              | Port B                                                                            | Port A                                                                                                              | Port B                                                               | Port C                                                                             |

| Non-MUX Address Data <sup>5</sup> | D <sub>0</sub> –D <sub>7</sub>                                                                                      | CS <sub>0</sub> –CS <sub>7</sub> or<br>PB <sub>0</sub> –PB <sub>7</sub>           | D <sub>0</sub> -D <sub>7</sub> <sup>4</sup>                                                                         | D <sub>8</sub> –D <sub>15</sub>                                      | CSCS6                                                                              |

| MUX Address Data                  | A <sub>0</sub> -A <sub>7</sub> <sup>4</sup><br>PA <sub>0</sub> -PA <sub>7</sub><br>AD <sub>0</sub> -AD <sub>7</sub> | CS <sub>0</sub> -CS <sub>7</sub> <sup>4</sup><br>PB <sub>0</sub> -PB <sub>7</sub> | A <sub>0</sub> -A <sub>7</sub> <sup>4</sup><br>PA <sub>0</sub> -PA <sub>7</sub><br>AD <sub>0</sub> -AD <sub>7</sub> | CS <sub>0</sub> –CS <sub>7</sub><br>PB <sub>0</sub> –PB <sub>7</sub> | CS <sub>8</sub> –CS <sub>10</sub> <sup>6</sup><br>A <sub>16</sub> –A <sub>18</sub> |

#### NOTES:

1. Three MAP300 EPROM densities.

2. Internal signal can be set during programming.

3. Latch B can be set to be transparent (not dependent on ALE).

4. Each I/O pin can be individually set to perform one of the two functions.

5. The non-MUX configuration is compatible to MAP168 pinout.

6. Port C is independent of any configuration and can be chip select out or address in.

#### Software Support

The object code generated for the support microprocessor/microcontroller is generated by an assembler. This code, when generated as an Intel MCS file, may be easily programmed into the EPROM section of the MAP168/PSD301 device because the MAPLE software has been designed to accept this standard format.

The programmable address decoder is used to define the mapping of the various

EPROM and SRAM memory blocks. This mapping is achieved by the designer in the MAPLE environment. The software provides a safeguard that prevents the designer from inadvertently overlapping the address selection. After selecting the memory block assignments, the MAP168/PSD301 device may be programmed by the WSI MagicPro<sup>™</sup> memory and PSD programmer.

WAFERSCALE INTEGRATION, INC.

## Programmable System<sup>™</sup> Device

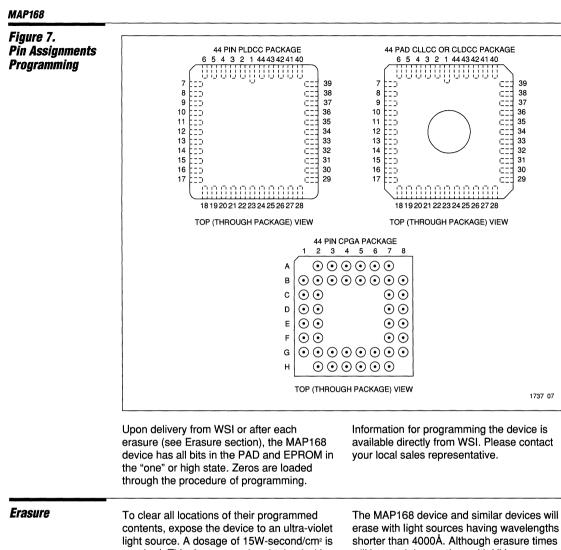

### MAP168 User-Configurable Peripheral with Memory

| Features                             | <ul> <li>First-generation Programmable System<br/>Device (PSD)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Programmable Security</li> <li>Protects memory map</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

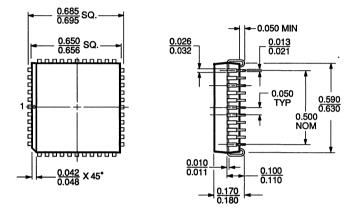

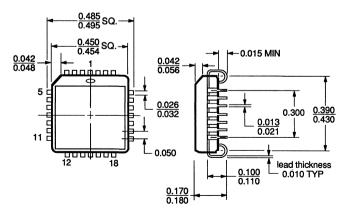

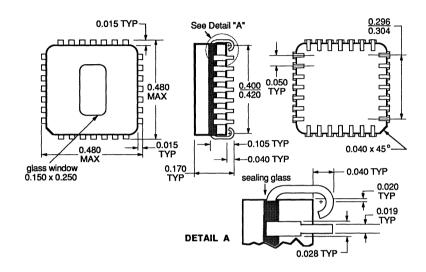

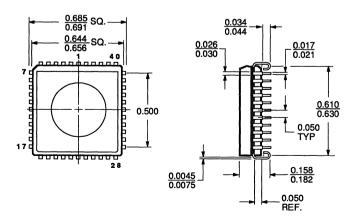

|                                      | User-Configurable Peripheral with<br>Memory<br>16Kx8 EPROM<br>4Kx8 SRAM<br>Programmable address decoder<br>Byte or Word Memory Configurations<br>16Kx8 or 8Kx16 EPROM<br>4Kx8 or 2Kx16 SRAM<br>2Mbyte or 1 Mword address range<br>High-Speed Operation<br>40-nsec memory access<br>17-nsec fast chip select output<br>External Chip Select Outputs<br>8 external chip selects<br>1 fast chip-select output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Protects program code</li> <li>Programming Support Tools</li> <li>PSD integrated software environment</li> <li>PC-XT/AT/PS2 platform support</li> <li>MAPLE location entry Software</li> <li>MAPPRO device programming Software</li> <li>MagicPro device programmer (PC-XT, AT)</li> <li>Military and Commercial Specifications</li> <li>44-pin Ceramic Leaded Chip Carrier</li> <li>package</li> <li>44-pad Ceramic Leadless Chip Carrier</li> <li>package</li> <li>44-pin Ceramic Leadless Chip Carrier</li> <li>package</li> <li>Plastic Leadless Chip Carrier</li> <li>package</li> <li>Plastic Leadless Chip Carrier</li> <li>package</li> <li>Plastic Leadless Chip Carrier</li> <li>Plastic Leadless Chip Carrier</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

| <i>General</i><br><i>Description</i> | In 1988 WSI introduced a new concept in<br>programmable VLSI, Programmable System<br>Devices (PSD). The PSD family consists of<br>user-configurable system-level building<br>blocks on-a-chip, enabling quick implementa-<br>tion of application-specific controllers and<br>peripherals. The first generation PSD series<br>includes the MAP168 User-Configurable<br>Peripheral with Memory; the SAM448, a<br>User-Configurable Microsequencer; and the<br>PAC1000, a User-Configurable Microcon-<br>troller.<br>The MAP168 is the first of WSI's Program-<br>mable System Devices (PSD) product line.<br>The device integrates high performance,<br>user-configurable blocks of EPROM, SRAM,<br>and logic in a single circuit. The major<br>functional blocks include a Programmable<br>Address Decoder (PAD), 16K bytes of high<br>speed EPROM, and 4K bytes of high speed<br>SRAM. A block diagram is given in Figure 1.<br>The MAP168 device is a complete memory<br>subsystem that can be mapped anywhere in<br>a 2M-byte address space of a microproces-<br>sor or microcontroller system. The EPROM<br>and SRAM memory blocks can be user-<br>configured in either byte-wide or word-wide | cantly reduces the board space and power<br>necessary to implement memory subsys-<br>tems, increases system performance, and<br>provides for secure data or program storage.<br>The device's high level of integration and<br>flexibility make it ideal for high-speed micro-<br>processors, microcontrollers, and Digital<br>Signal Processors like the TMS320XX family<br>The EPROM can be configured either as<br>16Kx8 or 8Kx16. The SRAM can be config-<br>ured either as 4Kx8 or 2Kx16. Individual<br>memory blocks of 2Kx8 or 1Kx16 can be<br>selectively mapped anywhere in the address<br>space. Since the Chip Select Input (CSI) car<br>be programmed as A20, the highest-order<br>address bit, the device's address range can<br>extend from 1M byte with CSI to 2M byte<br>without CSI.<br>For 16-bit microprocessors capable of byte<br>operations, the MAP168 device provides a<br>Byte High Enable input for accessing bytes<br>on any address boundary.<br>Pinout is compatible with the JEDEC<br>WS27C257 256K high-speed EPROM. This<br>pinout provides for memory expansion with<br>future WSI EPROM and PSD products. |

WAFERSCALE INTEGRATION, INC. 2-5

#### 2-6 WAFERSCALE INTEGRATION, INC.

2

| General<br>Description<br>(Con't) | programmed usi<br>programmer use<br>devices. Two so<br>Location Entry a<br>gramming Softw<br>menu-driven WIS<br>on an IBM® PC ><br>platform.                                                                                                                | d to program of<br>ftware package<br>nd MAPPRO D<br>are are availabl<br>SPER software | her WSI<br>s, MAPLE<br>evice Pro-<br>e in the<br>environment | For additional information on the MAP168<br>device, refer to <i>Application Note No. 002,</i><br><i>Introduction to the MAP168 User-Configur-<br/>able Peripheral with Memory.</i> For additional<br>information on development and program-<br>ming software for the MAP168 device, refer<br>to the <i>MAP168 User-Configurable Peripheral</i><br><i>with Memory Software User's Manual.</i> |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functional<br>Description         | The user-configurable architecture of the<br>MAP168 consists of an EPROM memory<br>block, an SRAM memory block, and a fast<br>Programmable Address Decoder (PAD) that<br>can be configured to select 2K-byte memory<br>blocks anywhere in a 2M-byte address |                                                                                       | l memory<br>and a fast<br>er (PAD) that<br>cyte memory       | range. The device can be programmed to<br>operate with memory configured either in a<br>byte or word organization (bytes can be<br>addressed in word mode). A programmable<br>security bit prevents access to the PAD<br>address-decode configuration table.                                                                                                                                  |

| Table 1.<br>Pin Description       | Signal                                                                                                                                                                                                                                                      | 1/0                                                                                   | Description                                                  | ·                                                                                                                                                                                                                                                                                                                                                                                             |

| Signal                                  | I/O | Description                                                                                                                                                                                                                                                 |

|-----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0-19</sub>                       | I   | Address Lines. For access to EPROM or SRAM.                                                                                                                                                                                                                 |

| FCSO                                    | 0   | Fast Chip-Select Output (active low). Used by the Pro-<br>grammable Address Decoder (PAD).                                                                                                                                                                  |

| BHE                                     | I   | Byte High Enable (active low). Selects the high-order byte when writing to SRAM.                                                                                                                                                                            |

| WE/V <sub>pp</sub>                      | I   | <i>Write Enable (active low) or Programming Voltage.</i> In normal mode, this pin causes data on the I/O pins to be written into SRAM. In programming mode, the pin supplies the programming voltage, V <sub>pp</sub> .                                     |

| ŌĒ                                      | I   | Output Enable (active low). Enable the I/O pins to drive the external bus.                                                                                                                                                                                  |

| CSI/A <sub>20</sub>                     | I   | Chip Select Input (active low) or High-Order Address.<br>This pin can be programmed as the bus-access chip<br>select or as an additional high-order address bit $(A_{20})$ .                                                                                |

| I/O <sub>0-7</sub>                      | I/O | Low-Order Byte of EPROM or SRAM.                                                                                                                                                                                                                            |

| I/O <sub>8-15,</sub> CSO <sub>0-7</sub> | I/O | High-Order Byte or Chip-Select Outputs. In word mode, these pins serve as the high-order byte $(I/O_{8-15})$ of EPROM or SRAM. In byte mode, the bits serve as Chip-Select Out signals $(\overline{CSO}_{0-7})$ for the Programmable Address Decoder (PAD). |

#### Programmable Address Decoder

The MAP168 device has a minimum of 20 address inputs  $A_0-A_{19}$  allowing the EPROM and SRAM memory blocks to reside anywhere in a 1M-byte address space. If the  $\overline{CSI}/A_{20}$  input is user-configured as an address line, the maximum addressable space increases to 2M bytes, as shown in the Configurations table.

The 16K bytes of EPROM and 4K bytes of SRAM, can be configured into eight independent 2K-byte blocks and two 2K-byte blocks respectively, as shown in the Memory Architecture figure. The PAD is a userconfigurable address decoder that compares input addresses to the 2K-byte address range selected for each of the eight EPROM blocks and two SRAM blocks. When the input address A<sub>0</sub>-A<sub>20</sub> is detected to be within one of the EPROM or SRAM address ranges, the PAD enables an internal chip select (ES<sub>0</sub>-ES<sub>7</sub> or RS<sub>0</sub>-RS<sub>1</sub>) to the selected block. If no block is selected, both the EPROM and SRAM memories remain in a power-down mode and the outputs are disabled allowing other devices to drive the

data bus. The SRAM retains its data in the power-down mode. The 2K-byte address ranges for any of the eight EPROM or two SRAM blocks may not overlap.

The PAD can also be user-configured to generate up to eight external chip selects,  $\overline{CS}_0-\overline{CS}_7$ . These outputs can be used to decode the input address lines  $A_0-A_{20}$  and to select other devices in the system. The outputs  $\overline{CS}_0-\overline{CS}_7$  are available on the eight higher-order  $I/O_{0.5}$  lines but only when the MAP168 device is configured in the byte mode; the lines are not available as chipselect outputs when the device is configured in the word mode.

The  $\overline{\text{CSI}}/\text{A}_{20}$  input is user-configurable as the most-significant address line or as an active-low chip enable. Its function is programmed as part of the PAD programming cycle.

The PAD also provides  $\overline{FSCO}$ , a single, fast chip-select output configurable by the user for any address. It can overlap with any of the internal EPROM, SRAM or external  $\overline{CSO}$  addresses.

#### Memory Subsystem EPROM Memory

The memory configuration of the MAP168 device includes 128K bits of WSI's patented high-speed, split-gate, UV-erasable EPROM. The EPROM is configured in byte mode as 16Kx8 and in word mode as 8Kx16. The memory is organized as eight 2Kx8 or 1Kx16 blocks, as shown in the Block Diagram figure. Each block has a separate and independent address range that cannot overlap. Each block is individually selected by one of the ES\_-ES, internal chip selects generated by the PAD when an input address is detected within its designated address range, as shown in the Memory Architecture figure. If not selected, each block of EPROM remains in a power-down mode.

For programming, the EPROM memory requires the  $\overline{WE}/V_{_{PP}}$  input to maintain the programming voltage  $V_{_{PP}}$ .

#### SRAM Memory

The device also includes 32K bits of highspeed SRAM. The SRAM is configured in byte mode as 4Kx8 and in word mode as 2Kx16. The memory is organized as two 2Kx8 or one 2Kx16 block(s), each with a separate and independent address range that cannot overlap. Each SRAM block is individually selected by one of the RS<sub>0</sub>–RS<sub>1</sub>, shown in the Memory Architecture figure, when an input address is detected by the PAD within its designated address range. When not selected, each of the SRAM memory blocks remains in a power down mode but does retain all data stored.

Data can be written into the SRAM only when the  $\overline{WE}/V_{_{PP}}$  input is active low.

| Memory<br>Subsystem<br>EPROM Memory | Byte/Word Mode<br>The PAD can be programm<br>the MAP168 device for eithe                                                                                                                                                                    |                                                                                          | output lines I                                                                   | e on the eight high-o<br>/O <sub>8</sub> –I/O <sub>15</sub> and enable<br>hen the OE input is I                                                                                       | d onto the                                                       |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| (Con't)                             | memory architecture. This a<br>to be used conveniently with<br>16-bit microcontrollers, micr<br>digital signal processor (DS<br>the Configurations table.                                                                                   | h either 8-bit or<br>oprocessors or                                                      | 8Kx16 and th<br>of both are tid                                                  | e, the EPROM is org<br>le SRAM as 2Kx16.<br>ed to the 16 input/ou<br>d enabled onto the b                                                                                             | The output<br>tput lines                                         |

|                                     | In byte mode, the EPROM i<br>16Kx8 and the SRAM as 4<br>of both are tied to the eight<br>output lines I/O <sub>0</sub> –I/O <sub>7</sub> and e<br>output bus when the OE inp<br>Only when configured in by<br>eight external chip selects p | X8. The outputs<br>low-order input/<br>nabled onto the<br>out is low.<br>te mode are the | address inpu<br>16-bit word o<br>be selected a<br>Selection tab<br>16-bit proces | e, the BHE input alor<br>t A0 allows the eight<br>n an even or odd bo<br>is shown in the High<br>le. This is a useful fe<br>sors that are not res<br>iting memory only on<br>ndaries. | bits of any<br>undary to<br>-Low Byte<br>ature for<br>tricted to |

| Mode Selection                      | The device's operational mode is controlled are ten separate modes of operation, all of by three inputs, $\overline{CSI}$ , $\overline{OE}$ , and $\overline{WE}/V_{PP}$ . There which are shown the Mode Selection table                   |                                                                                          |                                                                                  |                                                                                                                                                                                       |                                                                  |

| Table 2.<br>Configurations          | F                                                                                                                                                                                                                                           |                                                                                          |                                                                                  |                                                                                                                                                                                       |                                                                  |

| Configurations                      |                                                                                                                                                                                                                                             | v& Configura                                                                             | tion                                                                             | v16 Configura                                                                                                                                                                         | tion                                                             |

| oomiyurations                       |                                                                                                                                                                                                                                             | x8 Configura<br>CSI                                                                      | tion<br>A <sub>20</sub>                                                          | x16 Configurat<br>CSi                                                                                                                                                                 | tion<br>A <sub>20</sub>                                          |

| oomyurations                        | Address Space<br>words                                                                                                                                                                                                                      |                                                                                          | -                                                                                |                                                                                                                                                                                       | -                                                                |

| oomiyurations                       |                                                                                                                                                                                                                                             | CSI                                                                                      | A_20                                                                             | CSI                                                                                                                                                                                   | <b>A</b> <sub>20</sub>                                           |

| oonnyurations                       | words<br>Block Size                                                                                                                                                                                                                         | <b>CSI</b><br>1M bytes                                                                   | A <sub>20</sub><br>2M bytes                                                      | <b>CSI</b><br>512K words                                                                                                                                                              | <b>Α</b> <sub>20</sub><br>1Μ                                     |

| oonnyurations                       | words<br>Block Size<br>words                                                                                                                                                                                                                | <b>CSI</b><br>1M bytes<br>2K bytes                                                       | A <sub>20</sub><br>2M bytes<br>2K bytes                                          | <b>CSI</b><br>512K words<br>1K words                                                                                                                                                  | <b>А</b> <sub>20</sub><br>1М<br>1К                               |

| oomiyu atons                        | words<br>Block Size<br>words<br>Addressable Blocks                                                                                                                                                                                          | <b>CS</b> I<br>1M bytes<br>2K bytes<br>512                                               | A <sub>zo</sub><br>2M bytes<br>2K bytes<br>1024                                  | <b>CSI</b><br>512K words<br>1K words<br>512                                                                                                                                           | <b>Α</b> <sub>20</sub><br>1Μ<br>1Κ<br>1024                       |

16Kx8

4Kx8

8

yes

yes

yes

16Kx8

4Kx8

8

no

yes

yes

EPROM Configuration

SRAM Configuration

Low-power Standby

Protected Mode

Byte Operations

I/O Pins

8Kx16

2Kx16

16

yes

yes

yes

8Kx16

2Kx16

16

no

yes

yes

2

| Table 3.<br>Mode Selection | Mode/Pin                | CSI             | ŌĒ              | WE/V <sub>pp</sub> | Address                    | x16 (I/O <sub>0-15</sub> )<br>x8 (I/O <sub>0-7</sub> ) | x16 (FCSO)<br>x8 FCSO, CSO <sub>0-7</sub> |

|----------------------------|-------------------------|-----------------|-----------------|--------------------|----------------------------|--------------------------------------------------------|-------------------------------------------|

|                            | Read EPROM/SRAM         | ۷ <sub>L</sub>  | V <sub>iL</sub> | V <sub>IH</sub>    | EPROM/SRAM<br>Selected     | D <sub>OUT</sub>                                       | CS <sub>OUT</sub>                         |

|                            | Read External           | V <sub>IL</sub> | V <sub>⊫</sub>  | V <sub>IH</sub>    | EPROM/SRAM<br>Not Selected | High Z                                                 | CS <sub>OUT</sub>                         |

|                            | Output Disable          | х               | V <sub>IH</sub> | х                  | х                          | High Z                                                 | CS <sub>out</sub>                         |

|                            | Stand-By                |                 | X               | Х                  | х                          | High Z                                                 | CS <sub>OUT</sub>                         |

|                            | Write SRAM              | V <sub>IL</sub> | Х               | V <sub>IL</sub>    | SRAM Selected              | D <sub>IN</sub>                                        | CS <sub>OUT</sub>                         |

|                            | Write External          | V <sub>IL</sub> | х               | V <sub>IL</sub>    | No SRAM<br>Selected        | Х                                                      | CS <sub>OUT</sub>                         |

|                            | Program EPROM           | V <sub>IL</sub> | V <sub>IH</sub> | $V_{PP}$           | EPROM<br>Program Address   | D <sub>IN</sub>                                        | D <sub>IN</sub>                           |

|                            | Program Verify<br>EPROM | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub>    | EPROM<br>Program Address   | D <sub>OUT</sub>                                       | CS <sub>OUT</sub>                         |

|                            | Program PAD             | V <sub>IL</sub> | $V_{\rm IH}$    | $V_{PP}$           | PAD Program<br>Address     | D <sub>IN</sub>                                        | D <sub>IN</sub>                           |

|                            | Program Verify PAD      | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub>    | PAD Program<br>Address     | D <sub>OUT</sub>                                       | CS <sub>OUT</sub>                         |

| Table 4.<br>High/Low Byte | x16 Configuration Only     |              |                                   |                                            |  |  |  |

|---------------------------|----------------------------|--------------|-----------------------------------|--------------------------------------------|--|--|--|

| Selection                 | BHE (Pin 1) A <sub>a</sub> |              | Write Operation                   | <b>Read Operation</b>                      |  |  |  |

|                           | 0                          | 0            | Whole word                        | Whole word                                 |  |  |  |

|                           | 0                          | 1            | Upper byte from/to<br>odd address | Upper byte = Data Out<br>Lower byte = 'FF' |  |  |  |

|                           | 1                          | 0            | Lower byte from/to even address   | Whole word                                 |  |  |  |

|                           | 1                          | 1            | None                              | Upper byte = Data Out<br>Lower byte = 'FF' |  |  |  |

|                           | WR and BHE a               | are used for | SRAM functions                    |                                            |  |  |  |

| <i>Table 5. Product Selection Guide</i> | Parameter                          | MAP168-40 | MAP168-45 | MAP168-55 | Units |

|-----------------------------------------|------------------------------------|-----------|-----------|-----------|-------|

|                                         | Address Access Time (max)          | 40        | 45        | 55        | ns    |

|                                         | Chip-Select Access Time (max)      | 40        | 45        | 55        | ns    |

|                                         | Output Enable Time (max)           | 18        | 21        | 23        | ns    |

|                                         | Chip-Select Output Time            | 22        | 25        | 27        | ns    |

|                                         | Fast Chip-Select Output Time (max) | 17        | 20        | 22        | ns    |

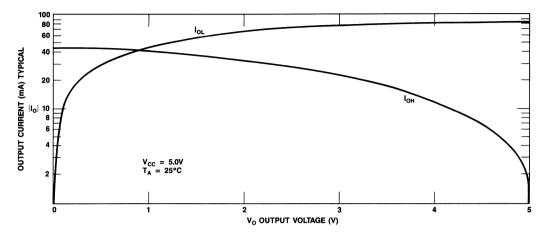

#### Table 6. DC Characteristics

| Parameter                                                                                                                                                 | Symbol                                | Test Conditions                  | Min | Max      | Units    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------|-----|----------|----------|

| Output Low Voltage                                                                                                                                        | V <sub>ol</sub>                       | l <sub>oL</sub> =8 mA            |     | 0.5      | V        |

| Output High Voltage                                                                                                                                       | V <sub>OH</sub>                       | l <sub>он</sub> =–2 mA           | 2.4 |          | V        |

| CMOS Standby<br>Current<br>—Commercial<br>—Military                                                                                                       | I <sub>SB1</sub>                      | notes 1, 3                       |     | 20<br>30 | mA<br>mA |

| TTL Standby<br>Current<br>—Commercial<br>—Military                                                                                                        | I <sub>SB2</sub>                      | notes 2, 3                       |     | 30<br>40 | mA<br>mA |

| CMOS Active Current<br>No Blocks Selected<br>—Commercial<br>—Military                                                                                     | I <sub>cc</sub> 1A                    | notes 1, 4                       |     | 20<br>30 | mA<br>mA |

| CMOS Active Current<br>EPROM Block Selected<br>—Commercial<br>—Military                                                                                   | I <sub>cc</sub> 1B                    | notes 1, 4                       |     | 35<br>45 | mA<br>mA |

| CMOS Active Current<br>SRAM Block Selected<br>—Commercial<br>—Military                                                                                    | I <sub>cc</sub> 1C                    | notes 1, 4                       |     | 55<br>65 | mA<br>mA |

| TTL Active Current<br>No Blocks Selected<br>—Commercial<br>—Military                                                                                      | I <sub>cc</sub> 2A                    | notes 2, 4                       |     | 30<br>40 | mA<br>mA |

| TTL Active Current<br>EPROM Block Selected<br>—Commercial<br>—Military                                                                                    | I <sub>cc</sub> 2B                    | notes 2, 4                       |     | 40<br>50 | mA<br>mA |

| TTL Active Current<br>SRAM Block Selected<br>—Commercial<br>—Military                                                                                     | I <sub>cc</sub> 2C                    | notes 2, 4                       |     | 65<br>75 | mA<br>mA |

| Input Load Current                                                                                                                                        | l <sub>u</sub>                        | V <sub>IN</sub> =5.5V<br>or GND  | -10 | 10       | μA       |

| Output Leakage Current                                                                                                                                    | I <sub>LO</sub>                       | V <sub>out</sub> =5.5V<br>or GND | -10 | 10       | μΑ       |

| Notes:<br>1. CMOS inputs: GND $\pm$ 0<br>2. TTL inputs: V <sub>IL</sub> $\leq$ 0.8V, <sup>1</sup><br>3. Add 1.5 mA/MHz for AC<br>4. Add 3.5 mA/MHz for AC | V <sub>H</sub> ≥ 2.0V.<br>C power com | ± 0.3V.<br>ponent.               |     |          |          |

2

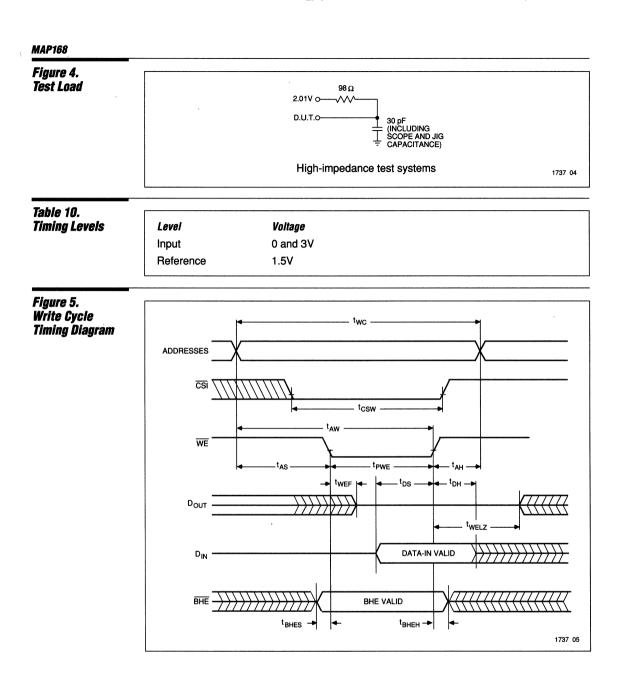

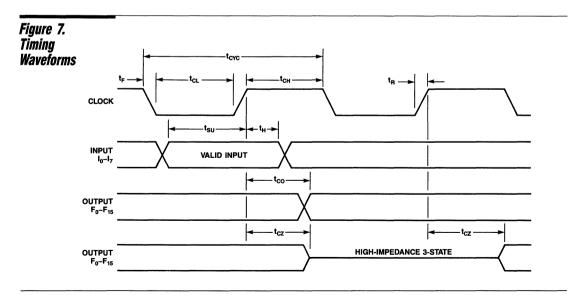

#### Table 7. AC Characteristic

| Parameter                          | Symbol            | MAP1<br>Min | 168-40<br>Max | MAP:<br>Min | 68-45<br>Max | MAP1<br>Min | 68-55<br>Max | Units |

|------------------------------------|-------------------|-------------|---------------|-------------|--------------|-------------|--------------|-------|

| Read Cycle Time                    | t <sub>RC</sub>   | 40          |               | 45          |              | 55          |              | ns    |

| Address to Output Delay            | t <sub>ACC</sub>  |             | 40            |             | 45           |             | 55           | ns    |

| CSI to Output Delay                | t <sub>ce</sub>   |             | 40            |             | 45           |             | 55           | ns    |

| OE to Output Delay                 | t <sub>oe</sub>   |             | 18            |             | 21           |             | 23           | ns    |

| Output Disable to Output Float     | t <sub>oef</sub>  |             | 15            |             | 18           |             | 20           | ns    |

| Chip Disable to Output Float       | t <sub>csF</sub>  |             | 15            |             | 18           |             | 20           | ns    |

| Address to Output Hold             | t <sub>он</sub>   | 10          |               | 10          |              | 10          |              | ns    |

| Address to CSO <sub>0-7</sub> True | t <sub>cso</sub>  |             | 22            |             | 25           |             | 27           | ns    |

| Address to FCSO True               | t <sub>FCSO</sub> |             | 17            |             | 20           |             | 22           | ns    |

| SRAM Write Cycle Time              | t <sub>wc</sub>   | 40          |               | 45          |              | 55          |              | ns    |

| Chip Enable to Write End           | t <sub>csw</sub>  | 40          |               | 45          |              | 55          |              | ns    |

| Address Setup Time                 | t <sub>as</sub>   | 0           |               | 0           |              | 0           |              | ns    |

| Address Hold Time                  | t <sub>an</sub>   | 0           |               | 0           |              | 0           |              | ns    |

| Address Valid to Write End         | t <sub>aw</sub>   | 40          |               | 45          |              | 55          |              | ns    |

| SRAM Write Enable Pulse Width      | t <sub>ewe</sub>  | 25          |               | 30          |              | 35          |              | ns    |

| Data Setup Time                    | t <sub>os</sub>   | 20          |               | 20          |              | 30          |              | ns    |

| Data Hold Time                     | t <sub>DH</sub>   | 0           |               | 0           |              | 0           |              | ns    |

| Write Enable to Data Float         | t <sub>weF</sub>  |             | 18            |             | 21           |             | 23           | ns    |

| Write Disable to Data Low Z        | t <sub>welz</sub> | 3           |               | 3           |              | 3           |              | ns    |

| BHE Setup Time                     | t <sub>BHES</sub> | 0           |               | 0           |              | 0           |              | ns    |

| BHE Hold Time                      | t <sub>BHEH</sub> | 10          |               | 10          |              | 10          |              | ns    |

*Table 8. Data Retention Characteristics*

| Parameter                           | Symbol            | Test Conditions                                   | Min             | Max | Units |

|-------------------------------------|-------------------|---------------------------------------------------|-----------------|-----|-------|