# HIGH PERFORMANCE CMOS PRODUCTS

**DATA BOOK** 1988

WAFERSCALE INTEGRATION, INC.

## WaferScale Integration, Inc.

### High Performance CMOS Products Databook

1988

Copyright © 1988 WaferScale Integration, Inc. (All rights reserved.)

47280 Kato Road, Fremont, California 94538 415-656-5400 Facsimile: 415-657-8495 Telex: 289255

Printed in U.S.A.

١

### SHATTERING BARRIERS THAT LIMIT GROWTH

In its short history, WaferScale Integration, Inc. (WSI) has made commonplace the breaking of traditional barriers that limit high-performance system evolution. Company "breakthroughs":

- First company to patent a self-aligned split-gate single transistor EPROM cell and place it in high volume production.

- First company to produce a 55 ns 8K  $\times$  8 CMOS EPROM.

- · First company to produce a 43 MHz 4-bit CMOS bit slice processor.

- First company to produce monolithic 16-bit and 32-bit CMOS bit slice processors, both as stand-alone products and as cell library macros.

- First company to produce a 128K CMOS re-programmable non-volatile memory with bipolar PROM pinouts.

- First company to produce a 30 ns 16 × 16 CMOS Multiplier Accumulator.

- First company to produce a 55 ns  $\times$  16 (wordwide) CMOS EPROM.

- First company to produce 55 ns 32K × 8 CMOS EPROMs.

- First company to combine high-performance EPROM, SRAM and logic all on the same circuit.

- First company to have 33 re-programmable CMOS EPROM products compliant to MIL-STD-883C.

- First company to produce user-configurable high-performance CMOS re-programmable board-replacement system controllers.

- First company to produce a family of 16K to 64K CMOS RPROMs<sup>™</sup> with sub-35 ns access time.

- First company to produce address mappable memory circuits that combine EPROM, SRAM and logic.

As WSI moves into faster sub-micron CMOS technologies in 1988 and continues to develop new programmable solutions for higher performance system markets, additional barriers will continue to be broken in our drive for leadership in high-performance next-generation programmable semiconductor products that integrate both memory and logic. WSI thus enables its customers to achieve faster market entry, higher performance systems and more easily producible end products.

WAFERSCALE INTEGRATION, INC.

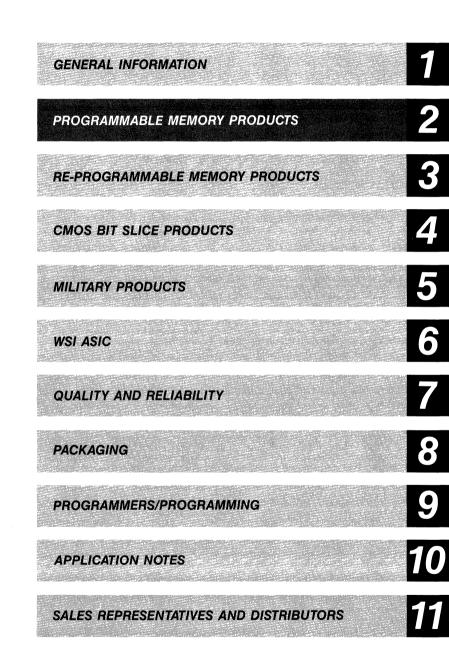

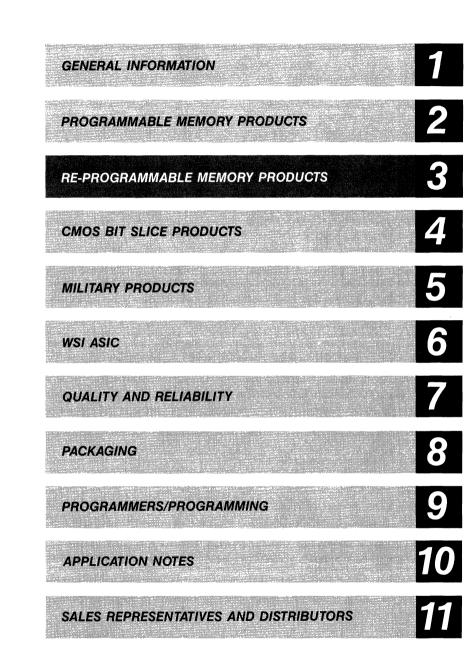

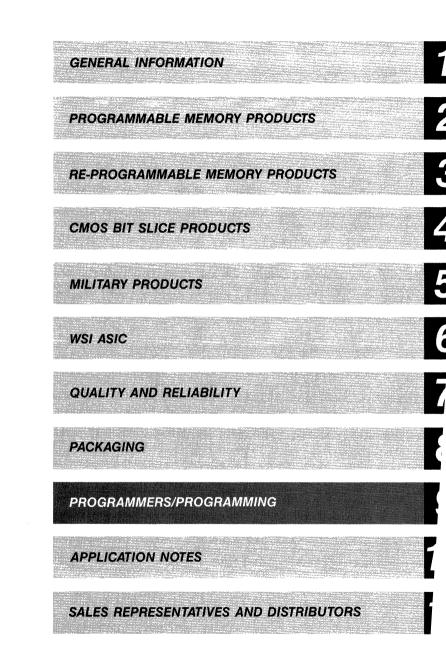

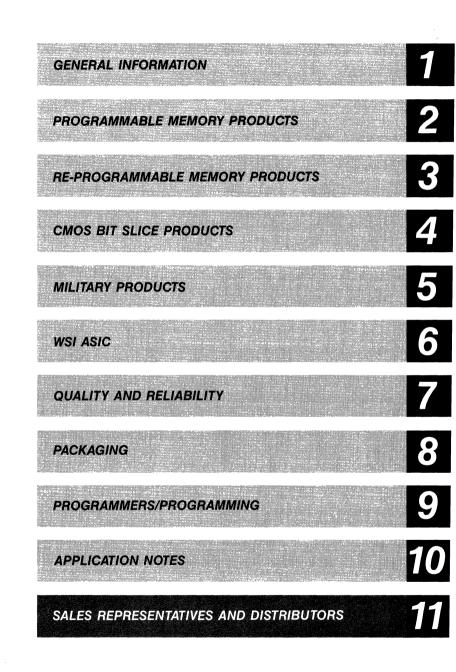

### **SECTION INDEX**

#### **GENERAL INFORMATION**

| Table of Contents                    | . 1-1  |

|--------------------------------------|--------|

| Company Profile                      | . 1-3  |

| NSI Technology & Electronics Article | . 1-7  |

| Product Summary                      | . 1-11 |

| Numerical Product Listing            | . 1-15 |

| Product Cross Reference              | . 1-19 |

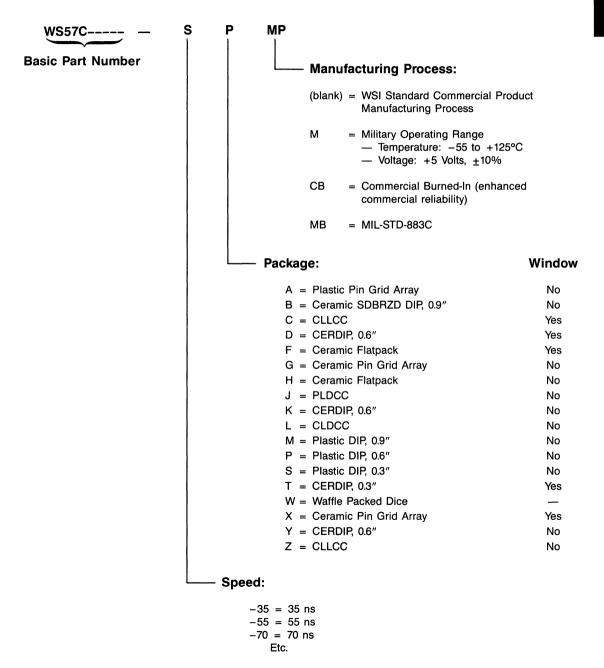

| Drdering Information                 | 1-21   |

For additional information, call 800-TEAM-WSI (800-832-6974). In California, call 415-656-5400.

### TABLE OF CONTENTS

### WAFERSCALE INTEGRATION, INC.

#### **General Information**

| Table of Contents                    |

|--------------------------------------|

| Company Profile                      |

| WSI Technology & Electronics Article |

| Product Summary                      |

| Numerical Product Listing            |

| Product Cross Reference              |

| Ordering Information                 |

#### **Programmable Memory Products**

| <b>PROM Memory:</b> |                                 |

|---------------------|---------------------------------|

| WS57C191/291        | 2K × 8 CMOS PROM                |

| WS57C191B/291B      | 2K × 8 CMOS PROM                |

| WS57C45             | 2K × 8 Registered CMOS PROM 2-9 |

| WS57C43B            | 4K × 8 CMOS PROM2-13            |

| WS57C49             | 8K × 8 CMOS PROM2-17            |

| WS57C49B            | 8K × 8 CMOS PROM                |

### **Re-Programmable Memory Products**

| RPROM Memory:     |                              |             |

|-------------------|------------------------------|-------------|

| WS57C191/291      | 2K × 8 CMOS RPROM            | 3-1         |

| WS57C191B/291B    | 2K × 8 CMOS RPROM            | 3-5         |

| WS57C45           | 2K × 8 Registered CMOS RPROM | 3-9         |

| WS57C43           | 4K × 8 CMOS RPROM            | 3-13        |

| WS57C43B          | 4K × 8 CMOS RPROM            | 3-17        |

| WS57C49           | 8K × 8 CMOS RPROM            | <b>3-21</b> |

| WS57C49B          | 8K × 8 CMOS RPROM            | <b>3-25</b> |

| WS57C51           | 16K × 8 CMOS RPROM           | 3-29        |

| WS57C51B          | 16K × 8 CMOS RPROM           | 3-33        |

| EPROM Memory (×8) | :                            |             |

| WS27C64F          | 8K × 8 CMOS EPROM (Mil)      | 3-37        |

| WS57C64F          | 8K × 8 CMOS EPROM            | 3-41        |

| WS27C128F         | 16K × 8 CMOS EPROM (Mil)     | 3-45        |

| WS57C128F         | 16K × 8 CMOS EPROM           | 3-49        |

| WS27C256F         | 32K × 8 CMOS EPROM (Mil)     | 3-53        |

| WS57C256F (-55)   | 32K × 8 CMOS EPROM           | 3-57        |

| WS57C256F (-35)   | 32K × 8 CMOS EPROM           | 3-61        |

| WS27C256L         | 32K × 8 CMOS EPROM           | 3-65        |

| WS27C256F         | 32K × 8 CMOS EPROM           | 3-69        |

| WS27C512F         | 64K × 8 CMOS EPROM           | 3-73        |

| WS27C010L         | 128K × 8 CMOS EPROM          | 3-77        |

| WS57C010F         | 128K × 8 CMOS EPROM          | 3-83        |

| EPROM Memory (×1                            | 6):                                            |

|---------------------------------------------|------------------------------------------------|

| WS57C65                                     | 4K × 16 CMOS EPROM                             |

| WS57C66                                     | 4K × 16 Muxed CMOS EPROM                       |

| WS57C257                                    | 16K × 16 CMOS EPROM                            |

| WS57C210F                                   | 64K × 16 CMOS EPROM                            |

|                                             | Products:<br>I61 MAP™ Memory                   |

| CMOS Bit Slice Product                      | e                                              |

| WS5901                                      | 4-Bit CMOS Bit Slice Processor4-1              |

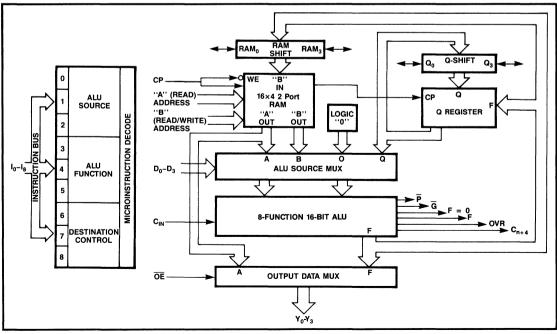

| WS59016                                     | 16-Bit CMOS Bit Slice Processor                |

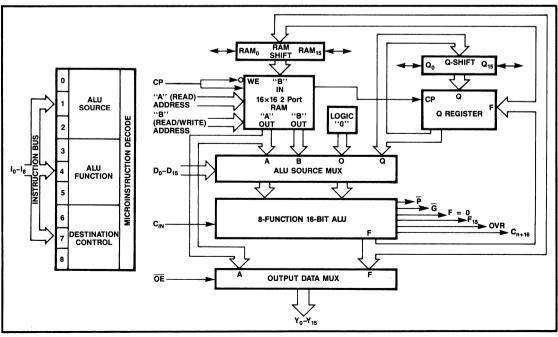

| WS59032                                     | 32-Bit CMOS Bit Slice Processor                |

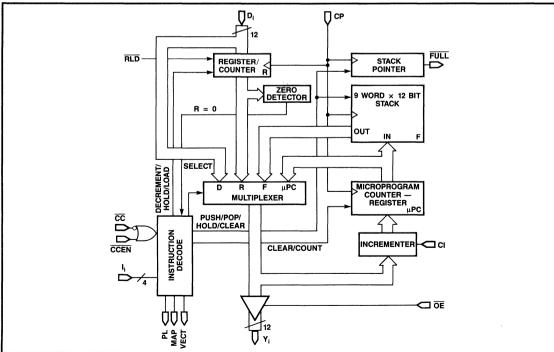

| WS5910A/B                                   | CMOS Microprogram Controller                   |

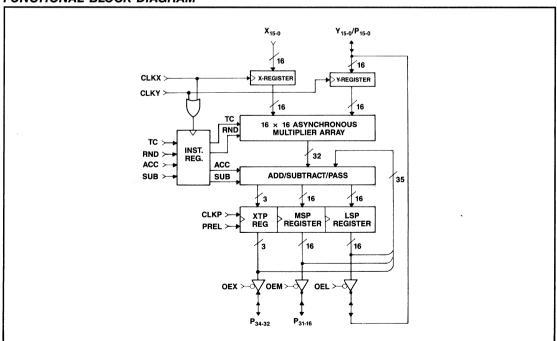

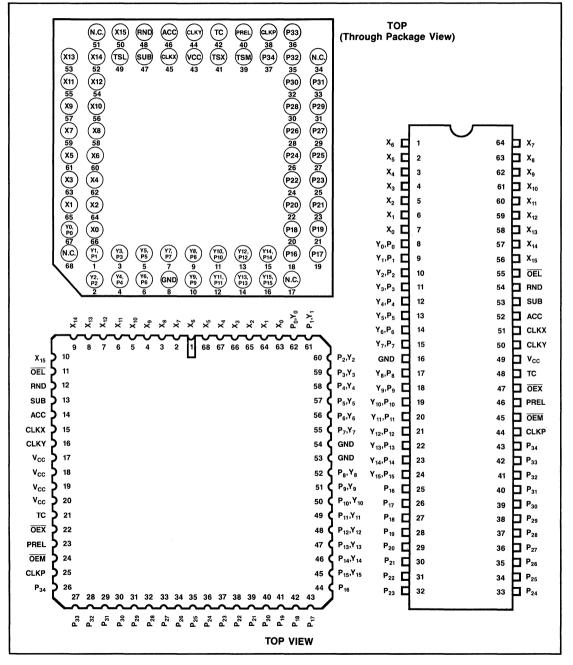

| WS59510                                     | 16 × 16 CMOS Multiplier Accumulator            |

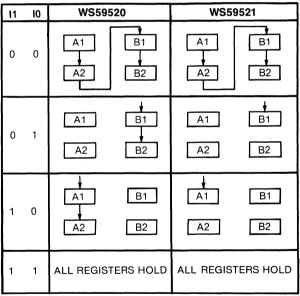

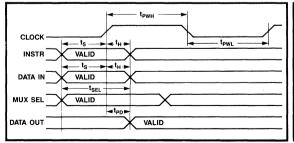

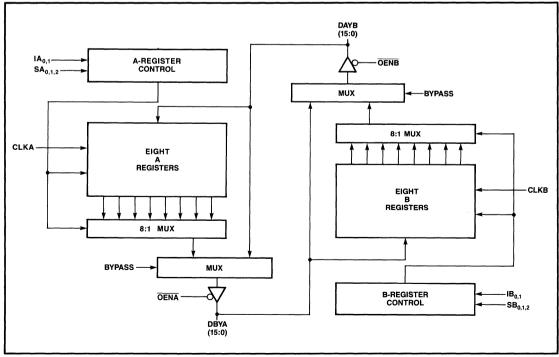

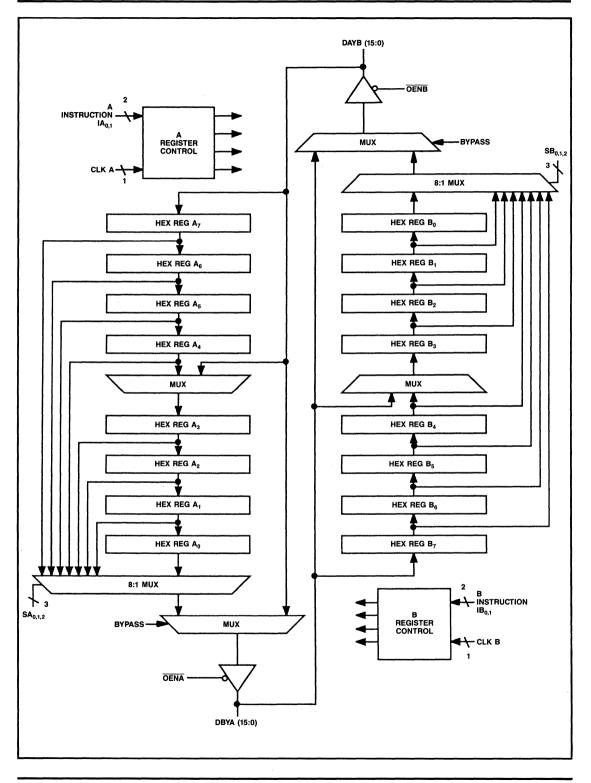

| WS59520/521                                 | Multilevel CMOS Pipeline Register              |

|                                             |                                                |

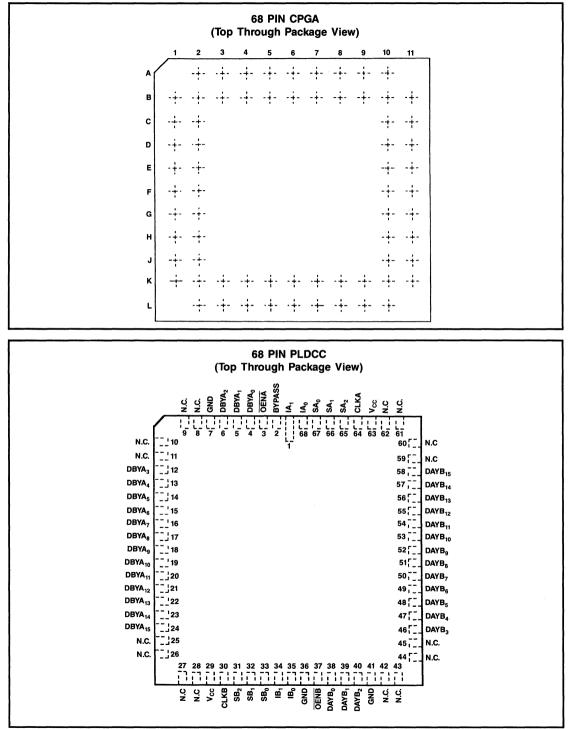

| WS59820                                     | Bi-Directional CMOS Bus Interface Register4-55 |

| Military Products                           |                                                |

| The Shortest Path From                      | System Concept to Market: WSI ASIC             |

| Microprogrammable (<br>Stand-Alone Microsed | oducts                                         |

| Quality and Reliability .                   |                                                |

| Packaging                                   |                                                |

| Programmers/Programm                        | ning                                           |

| WSI MagicPro <sup>™</sup> Eng               | Igorithms                                      |

| Application Notes                           |                                                |

|                                             | lodern Times                                   |

|                                             | the WSI Family of Mappable Memory Products     |

| Sales Representatives a                     | nd Distributors                                |

### WAFERSCALE INTEGRATION, INC.

### INTRODUCTION

WaferScale Integration, Inc. (WSI) has achieved marked increases in sales of its programmable CMOS memory, logic and semicustom products. These increased sales have resulted in a solid financial position including profitability. WSI is leveraging its proprietary CMOS technology and circuit architectures with strategic alliances involved in technology, manufacturing and distribution. This partnership structure has resulted in WSI's rapid emergence as the leader in high-performance next-generation user-programmable semiconductor products integrating both memory and logic.

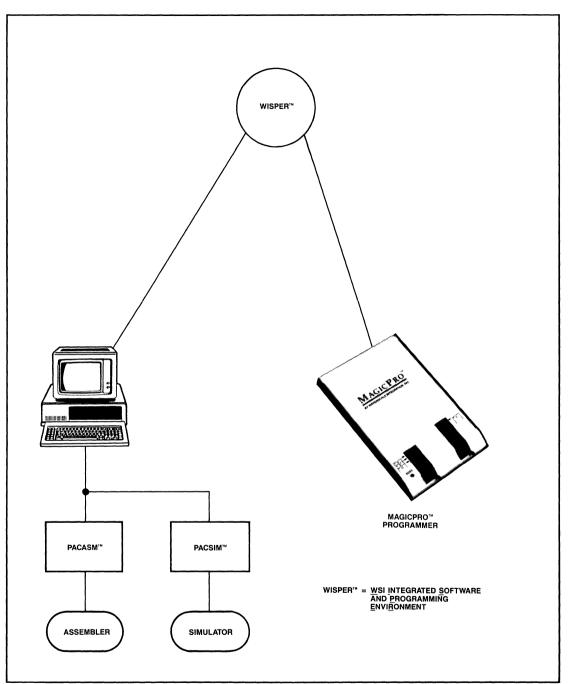

WSI serves its customers with the industry's fastest family of non-volatile CMOS EPROM and RPROM<sup>™</sup> memory circuits, high-speed CMOS bit-slice processors and peripherals and programmable board-replacement cell-based custom circuits. WSI continues to build on its unique technology by bringing to market fast new user-programmable controllers and specialized memory products that combine high-performance EPROM, SRAM and logic on one circuit. WSI supports these new products with a complete system development environment including software assemblers, simulators and utilities as well as the MagicPro<sup>™</sup> programmer. These development tools are used by customer design engineers during system development. Derived customer benefits from using the new user-programmable products include faster time to market, higher levels of integration resulting in smaller, more efficient products and higher system performance.

### THE COMPANY

WSI was founded in August, 1983, to develop integrated circuit technologies and products tailored specifically to meet the needs of high-performance systems developers. The company is headquartered in a 66,000 square foot facility in Fremont, California and employs 100 people.

The company's leveraging of its partnerships with Sharp Corporation, GE Solid State, Altera Corporation, Intergraph Corporation, and Kyocera Corporation enables WSI to invest its capital into advancing its technology, serving its customers, and realigning products to match market shifts.

Sharp Corporation and GE Solid State have invested in WSI through equity positions, and both companies hold WSI technology licenses. Altera Corporation and Intergraph Corporation are two additional strategic alliances involving either equity and/or technology. The Kyocera alliance involves equity and distribution of WSI product in Japan.

In its first round of financing in February, 1984, the company secured \$16.1 million in equity, equipment loans, leaselines, and facilities leasehold improvements. Investments were received from private sources, venture capital groups, and corporate investment funds.

After achieving significant milestones in its first year of operation, the company secured its second round of equity financing in October, 1984, for \$8.5 million. WSI completed its third round financing in January, 1986 raising an additional \$13 million in equity and licensing of its CMOS and EPROM technology. All of WSI's previous institutional investors participated in the third round.

A fourth round of financing with Kyocera Corporation as an added investor has been completed, exceeding \$8 million. This round brings the company's total financing to over \$30 million. Corporate investors cornerstoned and contributed over 60% of the fourth round.

### MARKETING STRATEGY

Today's rapidly expanding systems markets demand semiconductor products that provide exceptionally high speed, high reliability, high levels of integration, low power, a high electrostatic discharge protection, low to moderate cost, and in the case of semicustom circuits, the ability to tailor or program the product to achieve unique customer defined functions.

WSI focuses on high-performance markets that include telecommunications, minicomputers, local area networking, digital signal processing, array processing, high resolution color graphics, and military avionics and communications. The company's products are used where system designers are pushing the limits of system performance. These high-speed requirements often involve real time data manipulation and control.

Major market involvement of WSI's products presently include 55% office automation, 25% telecommunication, 15% military, and 5% other. Marketing direction has been established to balance office automation, telecommunication, and military to roughly 30% each by 1990.

To fulfill the needs of these markets, WSI has focused its attention on customer service. The company's productdevelopment teams rely heavily on first-hand input from its customer base regarding new products. WSI provides extensive technical information to customers in the form of printed product data, application notes, and personal design assistance. WSI is supplying an engineering programmer (dubbed "MagicPro" for <u>Memory And loGIC PROgrammer</u>) which will enable customer engineers to incorporate new WSI products into their designs without having to wait until the algorithms are commercially published for production use.

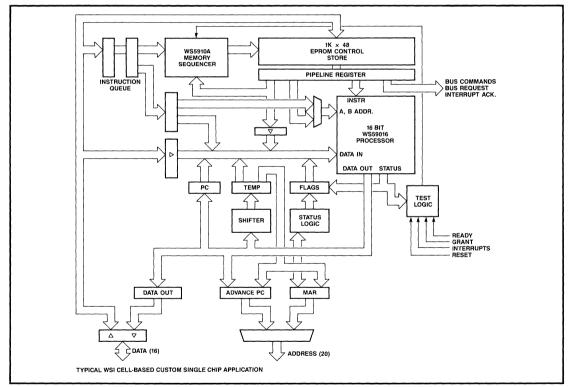

WSI has a CBIC (Cell-Based-Integrated-Circuit) program through which customers can combine a variety of proven macro-cell functions and produce a unique high-performance programmable integrated circuit tailored to exact customer specifications.

### SALES NETWORK

WSI's products are sold worldwide through a sales network that includes a combination of regional and direct sales managers, manufacturers' representative companies, and component distributors.

WSI has direct sales offices in Boston, MA; Huntsville, AL; Philadelphia, PA; Los Angeles and Fremont, CA; and Chicago, IL. Over 25 manufacturers' representative companies sell WSI products to major accounts on a nationwide basis. WSI's U.S. distributors include Time Electronics, Wyle Laboratories, Pioneer Technologies, and Pioneer Standard.

WSI has expanded its sales coverage in Europe and Japan. The company's European sales representatives include Tekelec Airtronic GmbH (Germany), Micro Call Ltd (England), REA (France), Silverstar (Italy), Traco AB (Sweden), Bacher GmbH (Austria, Switzerland), OY Comdax AB (Finland), OTE A/S (Norway), Distributoren Interelko, A/S (Denmark), Unitronics, S.A. (Spain), Inelco (Belgium and Luxembourg), Components & Systems Electronics B.V. (Holland), and Vectronics (Israel). In the Orient, Kyocera Corporation recently has been named as a WSI sales representative for Japan along with Nippon Imex Corporation (Japan), Components Agent Ltd (Hong Kong), Sertec International, Inc. (Taiwan), and Eastern Electronics, Inc. (Korea).

### MANUFACTURING STRATEGY

A key ingredient for success in leading-edge semiconductors is a world-class fabrication facility that ensures high volume capacity and prompt delivery of highly reliable and high yielding VLSI circuits. To this end, WSI has licensed its proprietary CMOS logic and EPROM process to Sharp Corporation of Osaka, Japan and GE Solid State in Somerville, NJ.

WSI's semicustom and standard products are manufactured at Sharp's highly automated manufacturing facility where it produces 5-inch wafers with 1.2 micron CMOS VLSI circuits in a Class 1 clean room environment. The Sharp facility employs the most advanced manufacturing equipment available including ion implantation, reactive ion etch, and wafer stepper lithographic systems.

The WSI-GE Solid State alliance provides WSI with a state-side second source. The GE Solid State Class 10 facility in Findley, Ohio provides 1.0 micron CMOS circuits on 5-inch wafers, and includes wafer stepper lithography and dry etch capability. As a self-contained unit, wafer fabrication, assembly, and test can all be performed at this facility.

The benefits derived from this WSI multi-fab strategy include product manufactured with very high quality, high wafer yields which enable low customer prices, and on-time delivery to meet demanding customer schedules . . . all at low fixed cost to WSI.

### PRODUCTS

WSI is the innovative leader in the high-speed EPROM arena. WSI began shipping the world's first CMOS 8K × 8 RPROM<sup>™</sup> in the first quarter of 1986. RPROMs (UV erasable re-programmable PROMs) provide bipolar PROM pinout and matching speed as well as CMOS low-power operation.

In mid-1987, WSI introduced the world's fastest pair of 256K CMOS EPROMs using its newly patented, self-aligned split gate EPROM technology. These EPROMs feature access times of just 55 ns and provide one- and two-chip program-store solutions for 16- and 32-bit MPU and DSP applications.

In addition to producing the world's fastest family of CMOS EPROMs, WSI supplies very high-speed CMOS bit-slice processors and peripheral circuits that operate faster than bipolar products while using only a small fraction of the power.

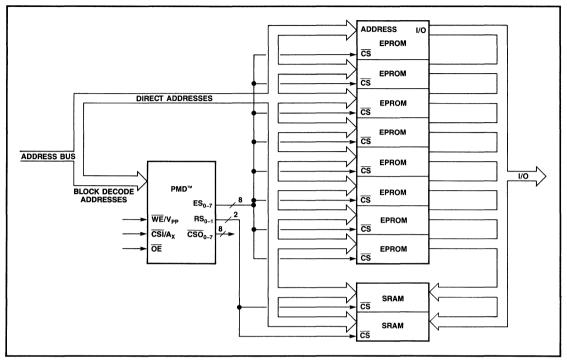

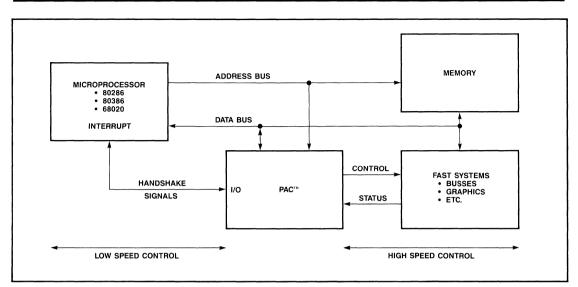

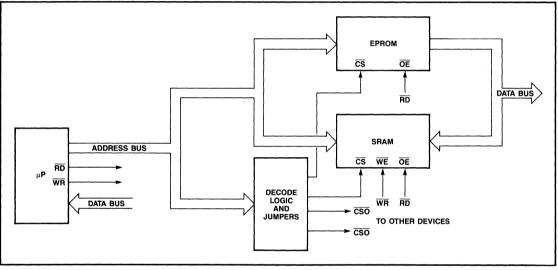

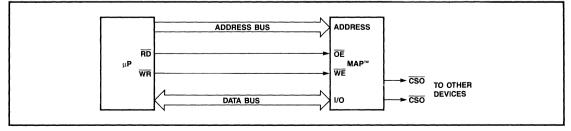

WSI's ability to combine EPROM, SRAM, and complex system logic functions on a single high-performance integrated circuit is unique among semiconductor companies. Examples of this capability are seen in the Microprogrammable Controller (PAC<sup>™</sup>) family, the MAP<sup>™</sup> family of mappable memory products and the Stand-Alone Microsequencer (SAM<sup>™</sup>) series. This same capability is used to develop powerful cell-based semicustom circuits that are unique to customer requirements. A re-programmable semicustom circuit provides flexibility in software, system configuration, and commonality of use among many customer projects.

The WSI CMOS macro-block cell library provides VLSI EPROM and SRAM memory and logic cells. When coupled with WSI's advanced CAD system, it enables WSI to build specially designed integrated circuits for its customers. The use of pre-characterized and pre-proven macro cells greatly insures the early success of each project. By using these powerful LSI functions, in addition to common logic elements, the cell library enables programmable subsystems or even complete system designs to be integrated on a single piece of silicon.

The macro-block CMOS cell library contains a family of high-performance bit-slice processor cells (from 4-bit to 32-bit) with better than bipolar LSI performance. Also included are bit-slice processor peripheral cells including microprogram controllers, variable pipelines, FIFOs, multipliers, bus registers, and register files. The library also contains high-density, very fast CMOS EPROM memory cell arrays, high-performance cell compilers for fast static RAM arrays, ROM arrays, and PLA cell arrays. High-speed random logic cells, which are functionally compatible with the popular 7400/4000 series, are also included in the library.

Many of the macro-cells developed for the cell library are excellent as stand-alone standard products. By providing these high-performance standard products, WSI can assist its customers in achieving enhanced system performance either in discrete design configurations or as design aids in advance of a full semicustom solution.

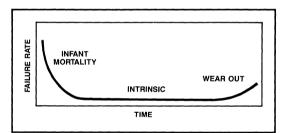

### QUALITY AND RELIABILITY

WSI has designed, developed and implemented a Quality and Reliability System whose mission is to continually produce Commercial and Military products that meet, and most often exceed, the customers' requirements.

WSI is deeply committed to product excellence. This begins with proper management attitude and direction and through this focus the Quality and Reliability Program is able to operate efficiently. As a result, product quality becomes part of each employee's responsibilities.

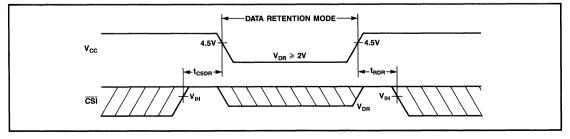

Quality and Reliability begin with the proper product and process designs and is supported by material and process controls. Examples are products manufactured on an epitaxial silicon layer to reduce latch-up sensitivity, all pins are designed to withstand >2,000 volts ESDS, numerous ground taps are used which increases product noise immunity, metal traces are designed to carry a current density of >2.0 ×  $10^5$  amps/cm<sup>2</sup>, top passivation extends over into the scribe lane to seal the die edges, data retention is performed 100% on re-programmable products (T<sub>A</sub> = +200°C, T = 48 hours), automated die attach and bonding is used extensively, wafers are fabricated in a  $\leq$  Class 10 clean room, raw materials, chemicals and gases are inspected before use, and statistical controls are used to keep the process on course.

Product and process introductions or changes are routinely evaluated for worthiness. Life Tests are conducted at higher than typical stress levels ( $T_A = +150^{\circ}$ C,  $V_{CC} = +6.5V$ ) and even at these stress levels, WSI products have demonstrated low failure rates (see the Quality and Reliability section in this databook).

WSI is active in Military programs and its Quality and Reliability System supports Compliant Non-Jan products. WSI also supports DESC's (Defense Electronics Supply Center) Standardized Military Drawings (SMD) program. As of February, 1988, WSI is on three SMDs, two are pending and more are in process. See the Military section in this databook.

For additional information, call 800-TEAM-WSI (800-832-6974). In California, call 415-656-5400.

#### LIFE SUPPORT POLICY:

WaferScale Integration, Inc. (WSI) products are not authorized for use as critical components in life support systems or devices without the express written approval of the President of WSI. As used herein:

A) Life support devices or systems are devices or systems which 1) are intended for surgical implant into the body, or 2) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury or death to the user,

B) A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

Information furnished herein by WaferScale Integration, Inc. (WSI) is believed to be accurate and reliable. However, no responsibility is assumed for its use. WSI makes no representation that the use of its products or the interconnection of its circuits, as described herein, will not infringe on existing patent rights. No patent liability shall be incurred by WSI for use of the circuits or devices described herein. WSI does not assume any responsibility for use of any circuitry described, no circuit patent rights or licenses are granted or implied, and WSI reserves the right without commitment, at any time without notice, to change said circuitry or specifications. The performance characteristics listed in this book result from specific tests, correlated testing, guard banding, design and other practices common to the industry. Information contained herein supersedes previously published specifications. Contact your WSI sales representative for specific testing details or latest information.

Products in this book may be covered by one or more of the following patents. Additional patents are pending.

USA: 4,328,565; 4,361,847; 4,409,723; 4,639,893; 4,649,520 West Germany: 3,103,160 Japan: 1,279,100 England: 2,073,484; 2,073,487

The following are trademarks of WaferScale Integration, Inc.: MagicPro<sup>™</sup>, RPROM<sup>™</sup>, PMD<sup>™</sup>, MAP<sup>™</sup>, PACASM<sup>™</sup>, PACSIM<sup>™</sup>, WSI<sup>™</sup>, PAC<sup>™</sup>, WISPER<sup>™</sup>

PAL is a registered trademark of Monolithic Memories, Inc. IBM is a trademark of International Business Machines Corporation. SAM and SAM+PLUS are trademarks of Altera Corporation.

### WSI CMOS TECHNOLOGY

Each generation of systems involved with data processing, digital communications, and real-time data analysis and control historically require faster and more efficient system elements to accomplish greater productivity. Issues of performance, reliability, integration, power and cost must be successfully addressed to insure the successful development of highly competitive end products. WSI's CMOS technology forms the foundation on which successful, high-performance next-generation systems may be realized.

The basic WSI CMOS process is a 1.2 micron N-well epi technology with double poly and single metal. This process enables the combining of non-volatile memory, static random access memory and logic functions all on the same low power circuit.

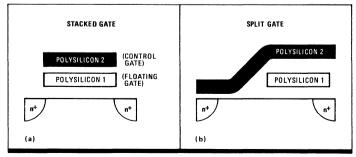

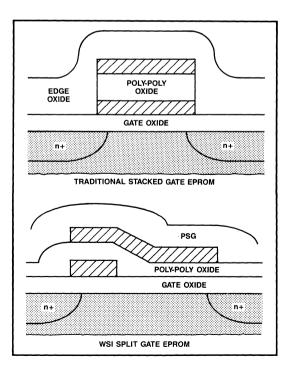

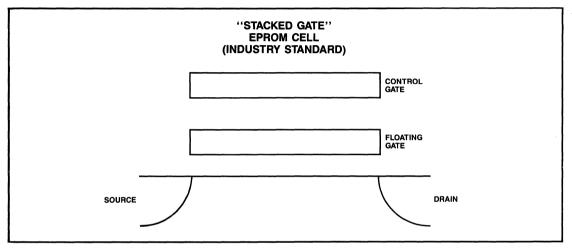

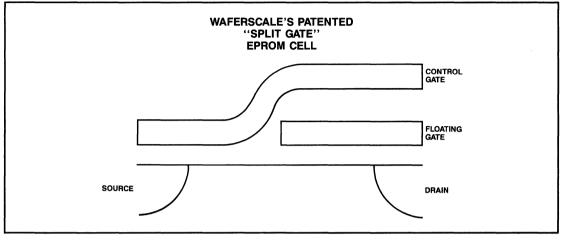

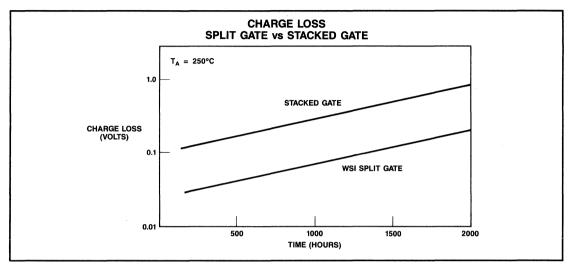

WSI's core EPROM technology begins with its patented self-aligned single transistor split-gate EPROM cell (Patent Number #4,639,893). This advancement beyond the traditional "stacked gate" EPROM cell provides much higher read current at comparable cell size. Proprietary EPROM array design enhancements such as clocked differential sensing, address-transition detection and the use of low resistance tungsten silicide in the second poly layer result in very high-speed memory products. Manufacturability is also improved as fewer EPROM cells are needed to complete a fast memory array, thus more conservative photolithography may be used.

WSI's use of epi wafers and design innovations result in products that exhibit immunity to latch-up and provide ESD protection far in excess of that specified by MIL-STD-883C.

The WSI EPROM technology has proliferated into families of high-performance EPROMs, bipolar PROM replacement products, user-configurable system products and cell-based custom capabilities described in this databook. When the high-speed split-gate EPROM technology is combined with high-performance cell-based logic functions, new user-configurable CMOS circuits such as the 20 MHz Microprogrammable Controller (PAC<sup>TM</sup>) series are realized. An additional family of 40 ns mappable (MAP<sup>TM</sup>) memory products combine EPROM, SRAM and logic on a single chip. WSI's fast CMOS logic has yielded a market leading 30 ns 16  $\times$  16 CMOS Multiplier Accumulator and a 33 MHz 32-bit CMOS bit slice processor . . . both the fastest in their class.

WSI's ability to rapidly combine any of these completed or modified macro memory or logic functions into a custom high-performance cell-based board-replacement circuit for special customer applications makes WSI unique among semiconductor companies.

#### TECHNOLOGY TO WATCH

Speed or density? Density or speed? Thanks to WaferScale Integration Inc., systems designers no longer must compromise. The Fremont, Calif., company has just unleashed a pair of high-speed, 256-Kbit ultraviolet-erasable CMOS programmable read-

only memories. With 50- to 55-ns access times, they are the fastest nonvolatile memories on the market at 256 Kbits and beyond—at least two to three times quicker than comparably sized PROMs, and coming within range, at twice the density, of the largest commercial bipolar PROM [*Electronics*, Feb. 10, 1986, p. 35]. And active power dissipation is a comfortable 325 milliwatts, just half that of its closest bipolar rival, sinking to 75 mW on standby.

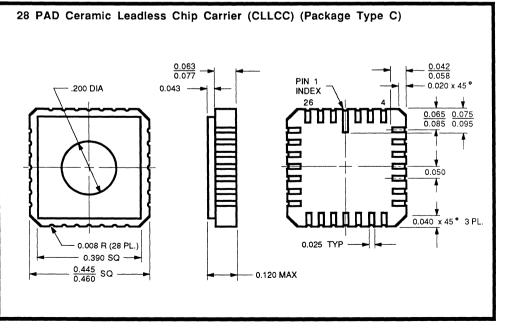

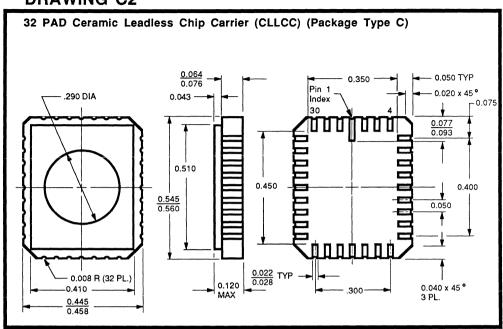

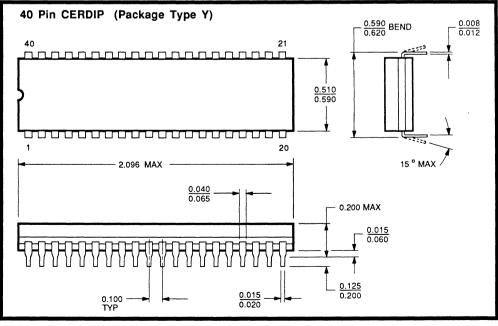

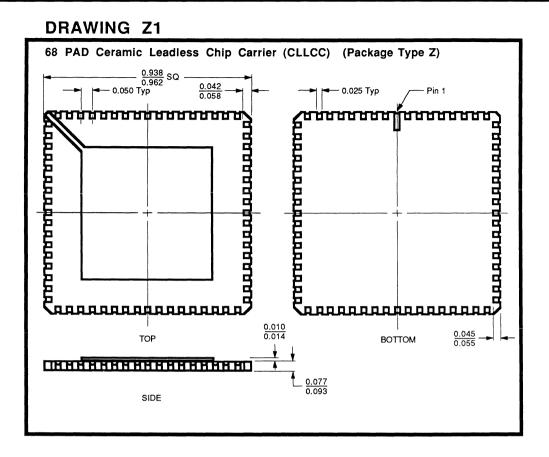

With their combination of speed and density, the word-wide 16-K-by-16-bit WS57C257 and bytewide 32-K-by-8-bit WS57C256F are tailored to one- and two-chip program storage for 16- and 32-bit microprocessors and digital signal processing. Conventionally, anywhere from 4 to 16 nonvolatile memories are needed. Current plans call for the byte-wide memory to hit the streets in July in standard 28-pin ceramic dual in-line packages and 32-pin ceramic leadless chip carriers. The word-wide part will follow sometime in the third quarter, in 40-pin Cerdips and 44-lead ceramic leadless chip carriers. Both are priced at \$94 per unit in 100-unit sample quantities.

To achieve this unprecedented combination of speed and density, engineers at WaferScale Integration refined the company's process technology and fine-tuned the circuit design. On the process side, a slimmed-down, second-generation 1.2-µm CMOS process, a scaled version of the company's patented split-gate EPROM cell, and tungsten silicide word lines were the keys to success. On the circuit-design side, clocked differential sensing and a novel precharge technique, a special two-step ac signal scheme, and

address-transition detection were the key developments. "These two devices disprove the traditional belief that you could have speed or size, but not both, in your microcontrol store," says Jerry Banks, marketing manager for standard products. "These large-architecture CMOS EPROMs are ideally suited for modems, real-time control, guidance systems, digital signal processing, and other real-time or complex processing applications."

WaferScale Integration first boiled down its CMOS process—from 1.5 to 1.2  $\mu$ m—and then used the

### WAFERSCALE'S 256-K EPROM RUNS SUPERFAST

refined technology to whip up a scaled version of its proprietary split-gate EPROM cell. Just  $6.5 \ \mu m$ on a side, the latest split-gate incarnation is roughly half the size of its predecessor. There's more to the new cell than just size, but the company won't go any further than saying that it adopted tungsten silicide.

The main problem with the traditonal stackedgate cell, notes Boaz Eitan, manager of the PROM program, is that it forces a tradeoff between the necessarily high read current and efficient programmability. "In traditional implementations, chip designers have had to make a choice," he says. "If they wanted speed, they had to implement a PROM cell with three to four transistors, separating the read, write, and select functions. If they wanted density, all three functions could be incorporated into a single-stacked PROM cell, but only at considerable sacrifice in speed."

The heart of the trouble lies in rapidly sensing the word- and bit-line voltages after address decoding. "The bit-line capacitance plays a big part in the equation," explains Syed Ali, manager of memory design. "If the capacitance remains fixed, a higher read current is needed to achieve greater speed. However, if the capacitance can be lowered, the speed can be boosted without increasing the read current."

The split-gate structure weds the best of the multiple-transistor and single-stacked cell approaches, requiring none of the compromises inherent in either. It consists of a MOS transistor linked in series with a floating-gate transistor that has been merged into a composite device (see fig. 1). In this design, says Eitan, the second polysilicon layer acts as the control gate and directly covers part of the channel area. "This eliminates drain turn-on and source-drain punchthrough, which adversely affects the stan-

1. SPLITS. Unlike the stacked-gate transistor (a), the split-gate transistor (b) has a second poly control gate that partly covers the channel, preventing drain turn-on and source-drain punch through.

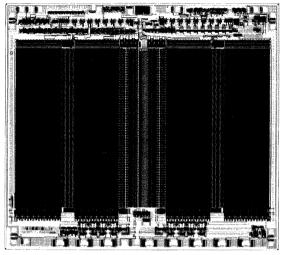

2. DELAY KILLER. Tungsten-silicide deposition helps Wafer-Scale's 256-Kbit EPROM achieve its 45-ns access time.

dard stacked-gate EPROM cell." As a result, bitline read currents in excess of 150  $\mu$ A can be achieved, compared with the 50  $\mu$ A typical of conventional stacked-gate cells, giving the speed of the multiple-transistor EPROM cell without its attendant die size.

The memory array (see fig. 2) is divided into two planes, each consisting of two blocks separated by a mid-word-line repeater. Tungsten silicide is deposited over the second polysilicon layer to reduce word-line RC delays, further improving access time. With a resistance of only 3  $\Omega$ per square  $\mu$ m, tungsten silicide helps reduce the delay to 60% of that incurred with traditional aluminum metallization. The 512 columns of the array are divided into blocks of eight columns, each block with its own dedicated source lines.

The higher bit-line voltage and read current established by the split-gate structure allow the company to employ a differential-sensing scheme that does not require a separate bit line, thus eliminating bit-line capacitance. In this scheme, the sense amplifier is designed to work in conjunction with a trip inverter. During precharge, the outputs of the differential amplifier and the inverter are precharged to the inverter trip point, enabling the inverter to move rapidly in either direction after a signal has been detected. The relative difference in the rate of discharge between the bit line and a column of reference cells provides just enough differential voltage for high-speed sensing.

To ensure that signal levels are high enough for sensing—a key consideration in all memories, as density increases and interconnects get longer—a two-step ac signal-development scheme has been incorporated into the circuits. In the first step of the proprietary approach, a small ac signal is generated by using a capacitor-imbalancing technique. This 100-mv signal is rapidly read out by a differential sense amplifier. In the second step, the on-chip circuitry converts this signal to a 300-mv dc signal that is used to increase programmed cell margins by as much as 25%.

As a result, says Eitan, the design senses bitline voltages more than five times faster than previous devices. The scheme also makes for fast programming. Typically, it takes only 0.1 ms to program a byte, compared with 1 ms for older technologies.

Address-transition detection also contributes to the improved access times. Normally associated with static random-access memories, it helps precharge the bit lines and to equalize the gain of the critical sense amplifiers. When an address transition is detected, an enable pulse is generated that precharges the bit-lines and critical sense-amplifier nodes. This eliminates the setup time normally encountered in PROMS. To further reduce the precharge time, the bit-line voltage swing is kept within narrow limits. More time is saved by performing the address decoding in parallel with the bit-line precharge, then ending them simultaneously.

To keep power dissipation down, only 25% of the cells in the array have access to the supply voltage during a read. This dramatically decreases the supply current to no more than 40 mA at 20 MHz, about half that of other designs.

WaferScale Integration is also using its highspeed process for a 64-Kbit PROM, the 8-K-by-8-bit WS57C49B, a direct pin-for-pin replacement for a bipolar PROM (called a reprogrammable ROM, or RPROM). At 35 ns it matches most high-speed CMOS SRAMS in access time. Another device for which it is using the high-speed process is a pinfor-pin CMOS relacement for the Am27C51, a 128-Kbit bipolar PROM from Advanced Micro Devices Inc., Sunnyvale, Calif. The WS57C51 is a 16-K-by-8-bit RPROM with an access time of only 55 ns and a chip area of only 32,000 mils<sup>2</sup>, 60% smaller than the AMD device.

The company is now working on its next-generation CMOS PROM process, which at 1.0  $\mu$ m will enable it to build 64-Kbit memories that access in only 25 ns and 128-Kbit and 256-Kbit devices that access in 35 ns. The same process will also allow WaferScale Integration to extend its speed challenge up into the megabit range. "There is nothing in our process that I can see that will prevent us from building 1-Mbit EPROMs with access times as low as 55 ns," Ali says. *Bernard C. Cole*

TECHNOLOGY TO WATCH is a regular feature of Electronics that provides readers with exclusive, in-depth reports on important technical innovations from companies around the world. It covers significant technology, processes, and developments incorporated in major new products.

Reprinted from ELECTRONICS, July 9, 1987, copyright 1987 by McGraw-Hill, Inc. with all rights reserved.

1-10

### HIGH-PERFORMANCE CMOS PRODUCT SUMMARY

### WAFERSCALE INTEGRATION, INC.

| PART NUMBER                      | DESCRIPTION                                   | SPEED          | PACKAGE                  |  |  |

|----------------------------------|-----------------------------------------------|----------------|--------------------------|--|--|

|                                  | One-Time Programmable (OTP) CMOS PROMs        |                |                          |  |  |

| WS57C191                         | 2K × 8 CMOS PROM                              | 45/55 ns       | 24 PDIP                  |  |  |

| WS57C191B                        | 2K × 8 CMOS PROM                              | 35/45 ns       | 24 PDIP                  |  |  |

| WS57C291                         | 2K × 8 CMOS PROM                              | 45/55 ns       | 24 PDIP                  |  |  |

| WS57C291B                        | 2K × 8 CMOS PROM                              | 35/45 ns       | 24 PDIP                  |  |  |

| WS57C45                          | 2K × 8 Registered CMOS PROM                   | 20/25/35 ns    | 24 PDIP<br>24 CERDIP     |  |  |

| WS57C43B                         | 4K × 8 CMOS PROM                              | 35/45 ns       | 24 PDIP                  |  |  |

| WS57C49                          | 8K × 8 CMOS PROM                              | 55/70 ns       | 24 PDIP                  |  |  |

| WS57C49B                         | 8K × 8 CMOS PROM                              | 35/45 ns       | 24 PDIP                  |  |  |

|                                  | Re-Programmable CMOS PROMs                    | (RPROMs)       |                          |  |  |

| WS57C191                         | 2K × 8 CMOS RPROM <sup>™(1)</sup>             | 45/55 ns       | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C191B                        | 2K × 8 CMOS RPROM <sup>™(1)</sup>             | 35/45 ns       | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C291                         | 2K × 8 CMOS RPROM <sup>™(1)</sup>             | 45/55 ns       | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C291B                        | 2K × 8 CMOS RPROM <sup>™(1)</sup>             | 35/45 ns       | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C45                          | 2K × 8 CMOS Registered RPROM <sup>TM(1)</sup> | 20/25/35 ns    | 24 Flatpack<br>24 CERDIP |  |  |

| WS57C43                          | 4K × 8 CMOS RPROM <sup>™(1)</sup>             | 55/70 ns       | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C43B                         | 4K × 8 CMOS RPROM <sup>™(1)</sup>             | 35/45/55 ns    | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C49                          | 8K × 8 CMOS RPROM <sup>™(1)</sup>             | 55/70 ns       | 24 CERDIP<br>28 CLLCC    |  |  |

| WS57C49B                         | 8K × 8 CMOS RPROM <sup>™(1)</sup>             | 35/45/55 ns    | 24 CERDIP<br>28 CLLCC    |  |  |

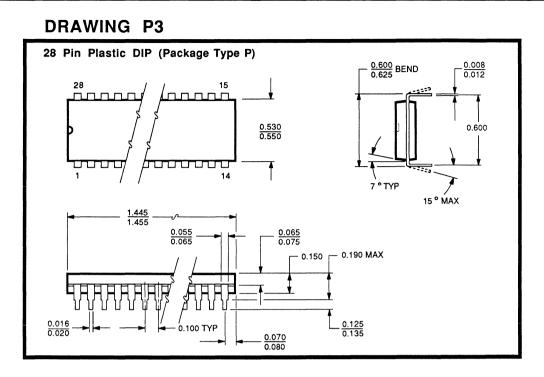

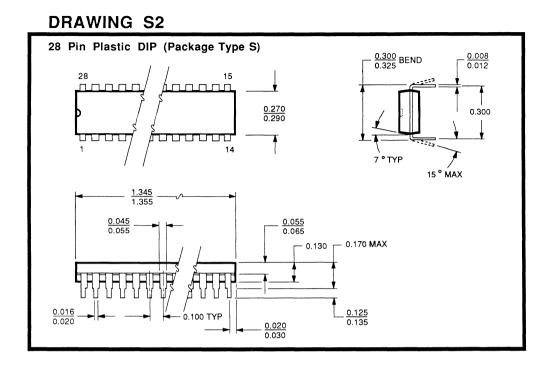

| WS57C51                          | 16K × 8 CMOS RPROM <sup>™(1)</sup>            | 70 ns          | 28 CERDIP                |  |  |

| WS57C51B                         | 16K × 8 CMOS RPROM <sup>™(1)</sup>            | 40/45/55/70 ns | 28 CERDIP<br>32 CLLCC    |  |  |

| High-Speed Byte-Wide CMOS EPROMs |                                               |                |                          |  |  |

| WS57C64F                         | 8K × 8 CMOS High Speed EPROM                  | 55/70 ns       | 28 CERDIP<br>32 CLLCC    |  |  |

| WS57C128F                        | 16K × 8 CMOS High Speed EPROM                 | 55/70 ns       | 28 CERDIP<br>32 CLLCC    |  |  |

| WS57C256F                        | 32K × 8 CMOS High Speed EPROM                 | 55/70 ns       | 28 CERDIP<br>32 CLLCC    |  |  |

1

### **PRODUCT SUMMARY (Continued)**

| PART NUMBER                               | DESCRIPTION                                      | SPEED         | PACKAGE                              |  |  |

|-------------------------------------------|--------------------------------------------------|---------------|--------------------------------------|--|--|

|                                           | High-Speed Byte-Wide CMOS EPROMs (Continued)     |               |                                      |  |  |

| WS57C256F                                 | 32K × 8 CMOS High Speed EPROM                    | 35/45 ns      | 28 CERDIP<br>32 CLLCC                |  |  |

| WS27C256L                                 | 32K × 8 CMOS High Speed LP EPROM                 | 90/120 ns     | 28 CERDIP<br>28 PDIP<br>32 CLLCC     |  |  |

| WS27C256F                                 | 32K × 8 CMOS High Speed LP EPROM                 | 90/120 ns     | 28 CERDIP<br>32 CLLCC                |  |  |

| WS27C512F                                 | 64K × 8 CMOS High Speed LP EPROM                 | 70/90 ns      | 28 CERDIP<br>32 CLLCC                |  |  |

| WS27C010L                                 | 128K × 8 CMOS High Speed LP EPROM                | 90/120/150 ns | 32 CERDIP                            |  |  |

| WS57C010F                                 | 128K × 8 CMOS High Speed EPROM                   | 55/70 ns      | 32 CERDIP                            |  |  |

|                                           | Military Low Power CMOS EPR                      | OMs           |                                      |  |  |

| WS27C64F                                  | 8K × 8 Military CMOS LP EPROM                    | 90/120/150 ns | 28 CERDIP<br>32 CLLCC                |  |  |

| WS27C128F                                 | 16K × 8 Military CMOS LP EPROM                   | 90/120/150 ns | 28 CERDIP<br>32 CLLCC                |  |  |

| WS27C256F                                 | 32K × 8 Military CMOS LP EPROM                   | 90/120/150 ns | 28 CERDIP<br>32 CLLCC                |  |  |

|                                           | High-Speed Word-Wide CMOS EF                     | PROMs         |                                      |  |  |

| WS57C65                                   | 4K × 16 CMOS EPROM                               | 55/70 ns      | 40 CERDIP<br>44 CLLCC                |  |  |

| WS57C66                                   | 4K × 16 CMOS EPROM<br>(Multiplexed Address/Data) | 55/70 ns      | 40 CERDIP<br>44 CLLCC                |  |  |

| WS57C257                                  | 16K × 16 CMOS EPROM                              | 55/70 ns      | 40 CERDIP<br>44 CLLCC                |  |  |

| WS57C210F                                 | 64K × 16 CMOS EPROM                              | 55/70 ns      | 40 CERDIP                            |  |  |

|                                           | Mapped-Address Programmable P                    | roducts       |                                      |  |  |

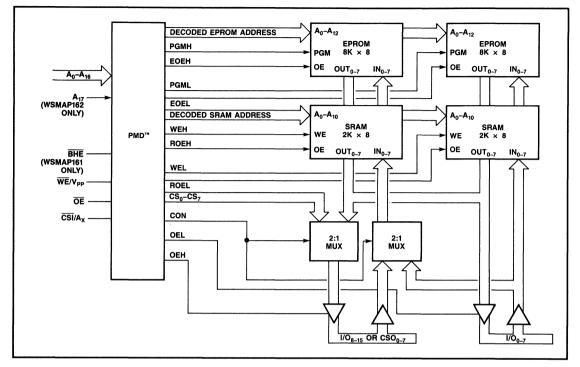

| WSMAP162                                  | 128K EPROM/32K SRAM MAP <sup>™</sup> Memory      | 40 ns         | 40 CERDIP                            |  |  |

| WSMAP161                                  | 128K EPROM/32K SRAM MAP <sup>™</sup> Memory      | 40 ns         | 40 CERDIP                            |  |  |

| WSMAP168                                  | 128K EPROM/32K SRAM MAP™ Memory                  | 40 ns         | 44 CPGA<br>44 CLLCC<br>44 PLDCC      |  |  |

| CMOS Bit-Slice Processors and Peripherals |                                                  |               |                                      |  |  |

| WS5901                                    | 4-Bit CMOS Bit-Slice Processor                   | C, D          | 40 PDIP                              |  |  |

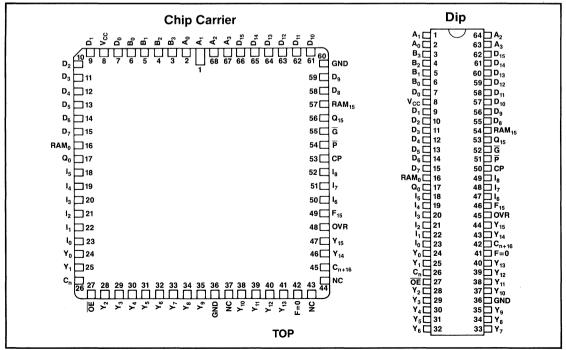

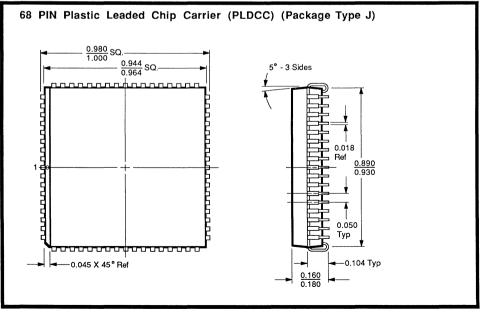

| WS59016                                   | 16-Bit CMOS Bit-Slice Processor                  | C, D          | 64 SDBRZ DIP<br>68 PLDCC<br>68 CLDCC |  |  |

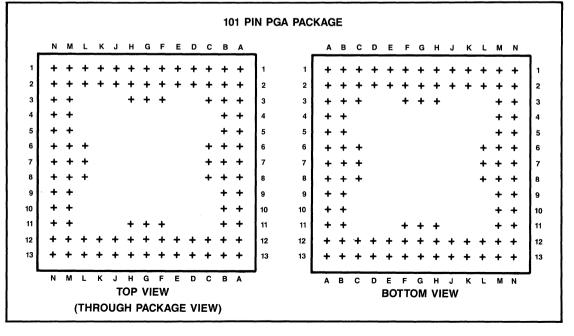

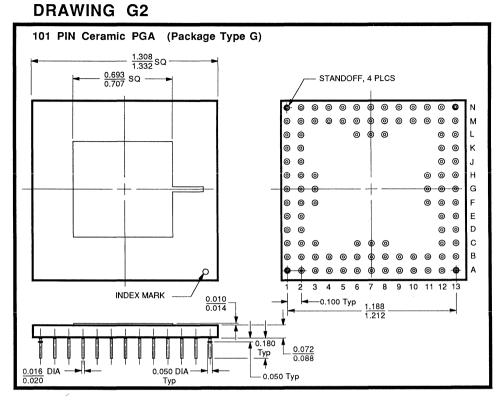

| WS59032                                   | 32-Bit CMOS Bit-Slice Processor                  | D, E          | 101 CPGA                             |  |  |

| WS5910A                                   | 12-Bit CMOS Variable Sequencer                   | А             | 40 CERDIP<br>40 PDIP                 |  |  |

### **PRODUCT SUMMARY (Continued)**

| PART NUMBER                                                                                | DESCRIPTION                                           | SPEED           | PACKAGE                        |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|--------------------------------|

|                                                                                            | CMOS Bit-Slice Processors and Periphera               | als (Continued) |                                |

| WS5910B                                                                                    | 12-Bit CMOS Variable Sequencer                        | В               | 40 CERDIP<br>40 PDIP           |

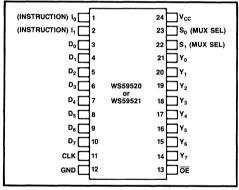

| WS59520                                                                                    | CMOS Variable Pipeline Register                       | —               | 24 CERDIP<br>24 PDIP           |

| WS59521                                                                                    | CMOS Variable Pipeline Register                       | _               | 24 CERDIP<br>24 PDIP           |

| WS59510                                                                                    | CMOS 16-Bit Multiplier Accumulator                    | 30/40/50 ns     | 68 PLDCC<br>68 CPGA<br>64 PDIP |

| WS59820                                                                                    | CMOS Bi-Directional Bus Register                      | 23 ns           | 68 PLDCC<br>68 CPGA            |

|                                                                                            | Programmable Logic Produc                             | ts              |                                |

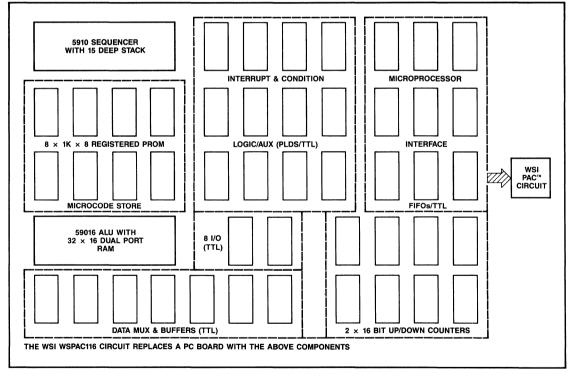

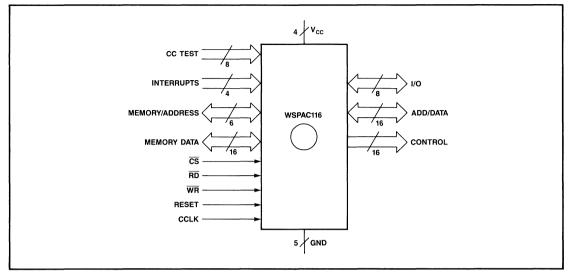

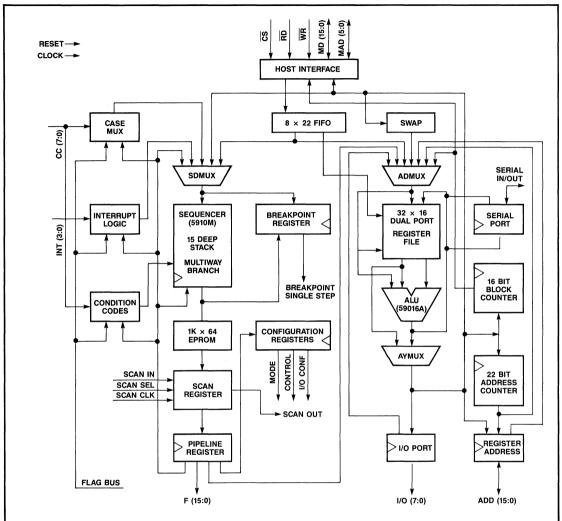

| WSPAC116                                                                                   | CMOS Programmable Stand-Alone<br>Controller           | 20 MHz          | 88 CPGA                        |

| WS444                                                                                      | CMOS Programmable Stand-Alone<br>Microsequencer (SAM) | 32 MHz          | 24 CERDIP                      |

| WS448                                                                                      | CMOS Programmable Stand-Alone<br>Microsequencer (SAM) | 32 MHz          | 24 CERDIP                      |

| NOTES: 1) RPROM <sup>™</sup> : Re-Programmable PROM<br>CMOS Replacement for Bipolar PROM's |                                                       |                 |                                |

| 2) LP EPROM: Low Power EPROM                                                               |                                                       |                 |                                |

### WAFERSCALE INTEGRATION, INC.

| PART NUMBER | DESCRIPTION                                           | SPEED          | PACKAGE                          |

|-------------|-------------------------------------------------------|----------------|----------------------------------|

| WS444       | CMOS Programmable Stand-Alone<br>Microsequencer (SAM) | 32 MHz         | 24 CERDIP                        |

| WS448       | CMOS Programmable Stand-Alone<br>Microsequencer (SAM) | 32 MHz         | 24 CERDIP                        |

| WS27C64F    | 8K × 8 Military CMOS LP EPROM                         | 90/120/150 ns  | 28 CERDIP<br>32 CLLCC            |

| WS27C010L   | 128K × 8 CMOS High Speed LP EPROM                     | 90/120/150 ns  | 32 CERDIP                        |

| WS27C128F   | 16K × 8 Military CMOS LP EPROM                        | 90/120/150 ns  | 28 CERDIP<br>32 CLLCC            |

| WS27C256F   | 32K × 8 Military CMOS LP EPROM                        | 90/120/150 ns  | 28 CERDIP<br>32 CLLCC            |

| WS27C256F   | 32K × 8 CMOS High Speed LP EPROM                      | 90/120 ns      | 28 CERDIP<br>32 CLLCC            |

| WS27C256L   | 32K × 8 CMOS High Speed LP EPROM                      | 90/120 ns      | 28 CERDIP<br>28 PDIP<br>32 CLLCC |

| WS27C512F   | 64K × 8 CMOS High Speed LP EPROM                      | 70/90 ns       | 28 CERDIP<br>32 CLLCC            |

| WS57C43     | 4K × 8 CMOS RPROM <sup>TM(1)</sup>                    | 55/70 ns       | 24 CERDIP<br>28 CLLCC            |

| WS57C43B    | 4K × 8 CMOS PROM                                      | 35/45 ns       | 24 PDIP                          |

| WS57C43B    | 4K × 8 CMOS RPROM <sup>™(1)</sup>                     | 35/45/55 ns    | 24 CERDIP<br>28 CLLCC            |

| WS57C45     | 2K × 8 CMOS Registered RPROM <sup>™(1)</sup>          | 20/25/35 ns    | 24 Flatpack<br>24 CERDIP         |

| WS57C45     | 2K × 8 CMOS Registered PROM                           | 20/25/35 ns    | 24 PDIP<br>24 CERDIP             |

| WS57C49     | 8K × 8 CMOS PROM                                      | 55/70 ns       | 24 PDIP                          |

| WS57C49     | 8K × 8 CMOS RPROM <sup>™(1)</sup>                     | 55/70 ns       | 24 CERDIP<br>28 CLLCC            |

| WS57C49B    | 8K × 8 CMOS PROM                                      | 35/45 ns       | 24 PDIP                          |

| WS57C49B    | 8K × 8 CMOS RPROM <sup>™(1)</sup>                     | 35/45/55 ns    | 24 CERDIP<br>28 CLLCC            |

| WS57C51     | 16K × 8 CMOS RPROM <sup>™(1)</sup>                    | 70 ns          | 28 CERDIP                        |

| WS57C51B    | 16K × 8 CMOS RPROM <sup>™(1)</sup>                    | 40/45/55/70 ns | 28 CERDIP<br>32 CLLCC            |

| WS57C64F    | 8K × 8 CMOS High Speed EPROM                          | 55/70 ns       | 28 CERDIP<br>32 CLLCC            |

| WS57C65     | 4K × 16 CMOS EPROM                                    | 55/70 ns       | 40 CERDIP<br>44 CLLCC            |

1

### NUMERICAL LISTING (Continued)

| PART NUMBER | DESCRIPTION                                      | SPEED       | PACKAGE                              |

|-------------|--------------------------------------------------|-------------|--------------------------------------|

| WS57C66     | 4K × 16 CMOS EPROM<br>(Multiplexed Address/Data) | 55/70 ns    | 40 CERDIP<br>44 CLLCC                |

| WS57C010F   | 128K × 8 CMOS High Speed EPROM                   | 55/70 ns    | 32 CERDIP                            |

| WS57C128F   | 16K × 8 CMOS High Speed EPROM                    | 55/70 ns    | 28 CERDIP<br>32 CLLCC                |

| WS57C191    | 2K × 8 CMOS PROM                                 | 45/55 ns    | 24 PDIP                              |

| WS57C191    | 2K × 8 CMOS RPROM <sup>™(1)</sup>                | 45/55 ns    | 24 CERDIP<br>28 CLLCC                |

| WS57C191B   | 2K × 8 CMOS PROM                                 | 35/45 ns    | 24 PDIP                              |

| WS57C191B   | 2K × 8 CMOS RPROM <sup>™(1)</sup>                | 35/45 ns    | 24 CERDIP<br>28 CLLCC                |

| WS57C210F   | 64K × 16 CMOS EPROM                              | 55/70 ns    | 40 CERDIP                            |

| WS57C256F   | 32K × 8 CMOS High Speed EPROM                    | 55/70 ns    | 28 CERDIP<br>32 CLLCC                |

| WS57C256F   | 32K × 8 CMOS High Speed EPROM                    | 35/45 ns    | 28 CERDIP<br>32 CLLCC                |

| WS57C257    | 16K × 16 CMOS EPROM                              | 55/70 ns    | 40 CERDIP<br>44 CLLCC                |

| WS57C291    | 2K × 8 CMOS PROM                                 | 45/55 ns    | 24 PDIP                              |

| WS57C291    | 2K × 8 CMOS RPROM <sup>™(1)</sup>                | 45/55 ns    | 24 CERDIP<br>28 CLLCC                |

| WS57C291B   | 2K × 8 CMOS PROM                                 | 35/45 ns    | 24 PDIP                              |

| WS57C291B   | 2K × 8 CMOS RPROM <sup>™(1)</sup>                | 35/45 ns    | 24 CERDIP<br>28 CLLCC                |

| WS5901      | 4-Bit CMOS Bit-Slice Processor                   | C, D        | 40 PDIP                              |

| WS5910A     | 12-Bit CMOS Variable Sequencer                   | A           | 40 CERDIP<br>40 PDIP                 |

| WS5910B     | 12-Bit CMOS Variable Sequencer                   | В           | 40 CERDIP<br>40 PDIP                 |

| WS59016     | 16-Bit CMOS Bit-Slice Processor                  | C, D        | 64 SDBRZ DIP<br>68 PLDCC<br>68 CLDCC |

| WS59032     | 32-Bit CMOS Bit-Slice Processor                  | D, E        | 101 CPGA                             |

| WS59510     | CMOS 16-Bit Multiplier Accumulator               | 30/40/50 ns | 68 PLDCC<br>68 CPGA<br>64 PDIP       |

| WS59520     | CMOS Variable Pipeline Register                  | _           | 24 CERDIP<br>24 PDIP                 |

| WS59521     | CMOS Variable Pipeline Register                  | _           | 24 CERDIP<br>24 PDIP                 |

| WS59820     | CMOS Bi-Directional Bus Register                 | 23 ns       | 68 PLDCC<br>68 CPGA                  |

### NUMERICAL LISTING (Continued)

| PART NUMBER | DESCRIPTION                                 | SPEED  | PACKAGE             |

|-------------|---------------------------------------------|--------|---------------------|

| WSMAP162    | 128K EPROM/32K SRAM MAP <sup>™</sup> Memory | 40 ns  | 40 CERDIP           |

| WSMAP161    | 128K EPROM/32K SRAM MAP <sup>™</sup> Memory | 40 ns  | 40 CERDIP           |

| WSMAP168    | 128K EPROM/32K SRAM MAP™ Memory             | 40 ns  | 44 CPGA<br>44 CLLCC |

| WSPAC116    | CMOS Programmable Stand-Alone<br>Controller | 20 MHz | 88 CPGA             |

### NOTES: 1) RPROM<sup>™</sup>: Re-Programmable PROM CMOS Replacement for Bipolar PROMs

2) LP EPROM: Low Power EPROM

1-18

1

### WAFERSCALE INTEGRATION, INC.

| AMD                | — WSI               | FUJITSU          | — WSI                 |

|--------------------|---------------------|------------------|-----------------------|

| AM27S191           | WS57C191            | MB7138           | WS57C191              |

| AM27PS191          | WS57C191            | MB7138-SK        | WS57C291              |

| AM27S291           | WS57C291            | MB7142           | WS57C43               |

| AM27PS191          | WS57C291            | MB7144           | WS57C49               |

| AM27S43            | WS57C43             |                  |                       |

| AM27PS43           | WS57C43             |                  | WO                    |

| AM27S49            | WS57C49             | HARRIS           | = WSI                 |

| AM27S49A           | WS57C49B            | HM-76161         | WS57C191              |

| AM27S51            | WS57C51 or WS57C51B | HM-76321         | WS57C43               |

| AM2901             | WS5901              | HM-76641         | WS57C49 or WS57C49B   |

| AM2910A            | WS5910A             |                  |                       |

| AM2970A<br>AM29520 | WS59520             | IDT              | = WSI                 |

|                    | WS59520<br>WS59521  | IDT39C01         | WS5901                |

| AM29521            |                     | IDT39C10         | WS5910A               |

| AM29C101           | WS59016*            | IDT49C401        | WS59016*              |

| AM29510            | WS59510             | IDT7210          | WS59510               |

| ATMEL              | WSI                 |                  |                       |

| 27HC64             | WS57C64F            | LDI              | = WSI                 |

| 27HC641            | WS57C49 or WS57C49B | L29C520          | WS59520               |

|                    |                     | L29C521          | WS59521               |

| CYPRESS            | — WSI               | MMI              | = WSI                 |

| CY7C291            | WS57C191            | 63S1681          | WS57C191              |

| CY7C292            | WS57C291            | 63\$3281         | WS57C43 or WS57C43B** |

| CY7C264            | WS57C49             | 0333201          | W357C45 01 W357C43B   |

| CY7C901            | WS5901              |                  |                       |

| CY7C910            | WS5910A             | NATIONAL         |                       |

| CY7C9101           | WS59016*            | DM87S191         | WS57C191              |

| CY7C510            | WS59510             | DM87S291         | WS57C291              |

| CY7C263            | WS57C49B            | DM87S321         | WS57C43 or WS57C43B** |

| CY7C264            | WS57C49B            |                  |                       |

| CY7C254            | WS57C51             | SIGNETICS        | = WSI                 |

|                    |                     | N82S191          | WS57C191              |

| FAIRCHILD          | WSI                 | N82S1913         | WS57C291              |

| 93Z511             | WS57C191            | N82S321          | WS57C43               |

| 93Z565             | WS57C49 or WS57C49B | N82HS321         | WS57C43 or WS57C43B** |

|                    | WS5901              | N82HS641         | WS57C49               |

| 29F01              |                     | N27HC641         | WS57C49 or WS57C49B   |

| 29F10              | WS5910A             | N2/HC641         | WS57C49 OF WS57C49B   |

|                    |                     | T.I              | — WSI                 |

|                    |                     | TBP38S166W       | WS57C191              |

|                    |                     | TBP38L166W       | WS57C191              |

|                    |                     | TBP38SA166W      | WS57C191              |

|                    |                     | TBP38S166T       | WS57C291              |

|                    |                     | TBP38L166T       | WS57C291              |

|                    |                     | TBP38SA166T      | WS57C291              |

| MILITARY ON        |                     |                  |                       |

| AMD                | WSI                 | INTEL            | = WSI                 |

| AM2764             | WS27C64F            | M2764            | WS27C64F              |

| AM27128            | WS27C128F           | M27128           | WS27C128F             |

| AM27256            | WS27C256F           | M27256           | WS27C256F             |

| ,                  | 102/0200            | M27250<br>M27C64 | WS27C2301<br>WS27C64F |

|                    |                     | M27C128          | WS27C128F             |

|                    |                     |                  |                       |

|                    |                     | M27C256          | WS27C256F             |

\* Functional Equivalent \*\*Available Q1 '88

1-19

WAFERSCALE INTEGRATION, INC.

### HIGH-PERFORMANCE CMOS PRODUCTS

### **SECTION INDEX**

#### **PROGRAMMABLE MEMORY PRODUCTS**

#### **PROM Memory:**

| WS57C191/291   | 2K × 8 CMOS PROM            | 2-1    |

|----------------|-----------------------------|--------|

| WS57C191B/291B | 2K × 8 CMOS PROM            | 2-5    |

| WS57C45        | 2K × 8 Registered CMOS PROM | 2-9    |

| WS57C43B       | 4K × 8 CMOS PROM            | 2-13   |

| WS57C49        | 8K × 8 CMOS PROM            | 2-17   |

| WS57C49B       | 8K × 8 CMOS PROM            | . 2-21 |

For additional information, call 800-TEAM-WSI (800-832-6974). In California, call 415-656-5400.

### 2K × 8 CMOS PROM

**KEY FEATURES**

- Fast Access Time - 45 ns

- Low Power Consumption — 225 mW Active Power

- Fast Programming

- Pin Compatible with AM27S191/291 and N82S191 Bipolar PROMs

- Immune to Latch-Up

Up to 200 mA

- ESD Protection Exceeds 2000V

### **GENERAL DESCRIPTION**

The WS57C191/291 is now available as a PROM. It utilizes the same design as the previously released RPROM<sup>™</sup> from WSI. The difference is the PROM version is available in plastic packages and is not re-programmable. The plastic packaging is ideal for high volume applications which require automatic insertion. The plastic packaging also provides an economic benefit when compared to a windowed cerdip package. For applications requiring reprogrammability, contact your WSI sales representative for information on the WSI family of RPROMs.

The WS57C191/291 is a High Performance 16K-bit CMOS PROM. It is manufactured in an advanced CMOS EPROM process which enables it to operate at bipolar speeds while consuming only 25% of the power of bipolar.

The WS57C191/291's patented CMOS EPROM technology enables the entire memory array to be fully programmed and erased prior to assembly. This capability ensures nearly 100% programming yield. Devices manufactured with other types of technologies utilize various types of fuses which cannot be tested without permanently programming the fuse. This results in a relatively high programming fallout at the packaged level.

Other testability features were designed into the 57C191/291 which enable it to be tested for speed after assembly without programming the memory array. This feature insures that the device will meet all A.C. as well as D.C. data sheet parameters.

Another feature of the WS57C191/291 is its uniquely designed output structure. When compared with other high speed devices, the output structure of the WS57C191/291 virtually eliminates the introduction of switch related noise into the system environment.

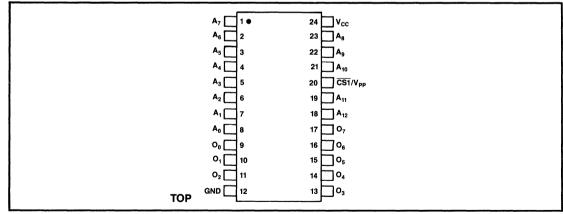

The WS75C191/291 is configured in the standard Bipolar PROM pinout. The WS57C191 is offered in a 600 mil wide Dip and the WS57C291 is offered in a 300 mil wide Dip.

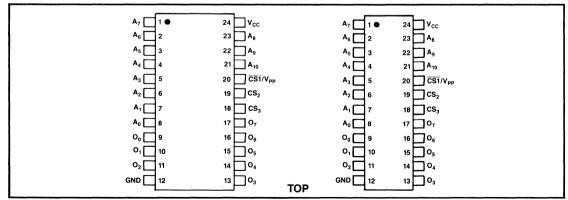

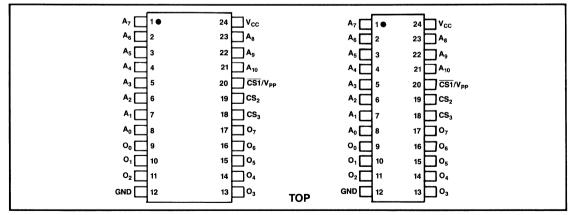

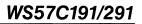

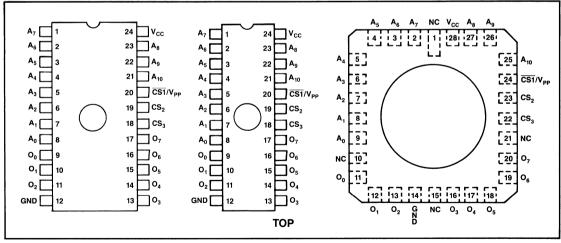

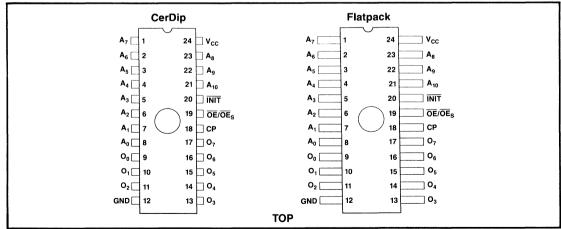

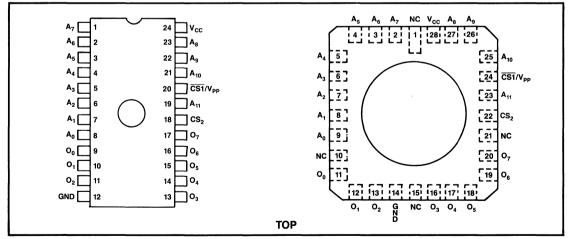

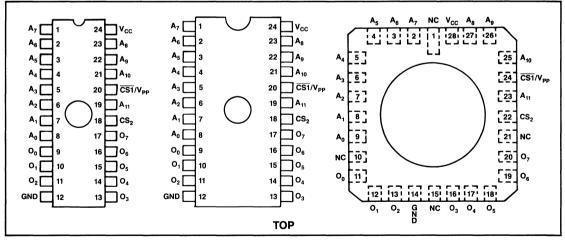

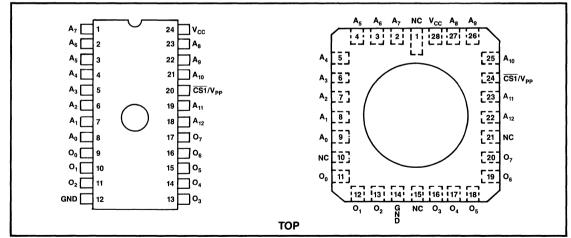

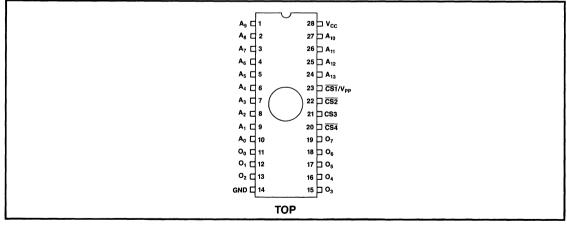

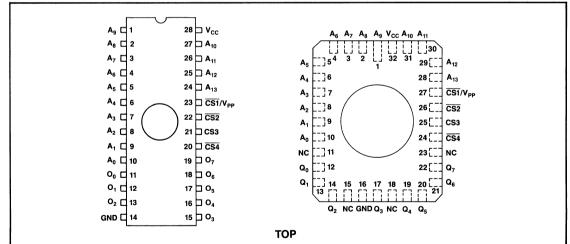

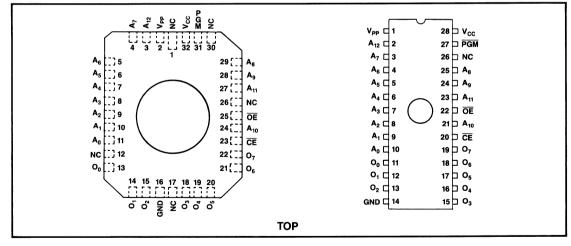

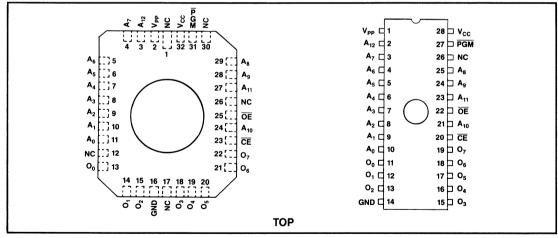

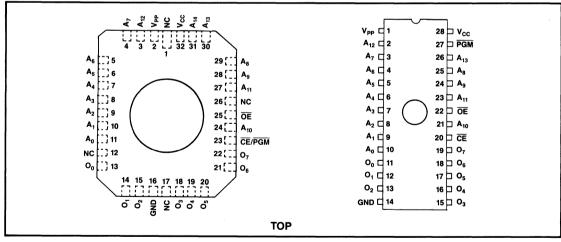

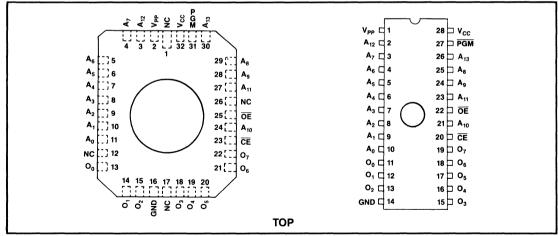

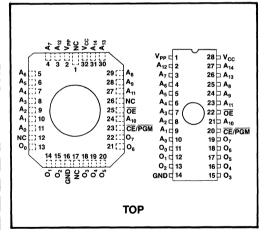

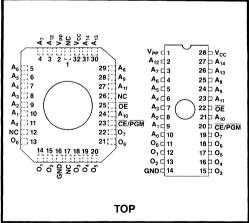

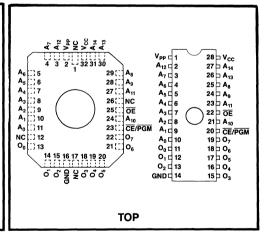

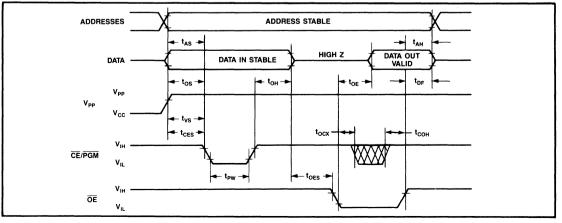

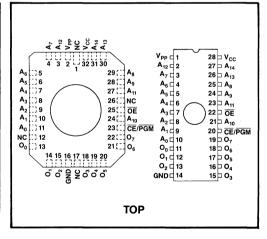

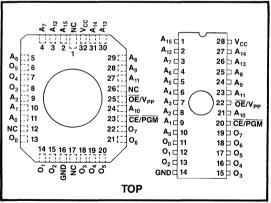

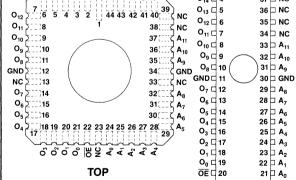

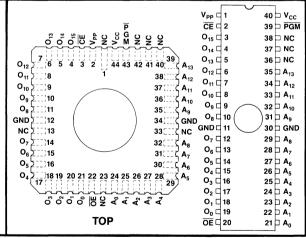

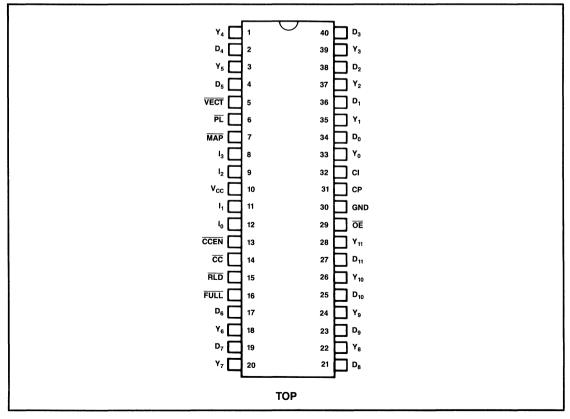

### PIN CONFIGURATION

### **PRODUCT SELECTION GUIDE**

| PARAMETER                 | WS57C191/291-45 | WS57C191/291-55 |

|---------------------------|-----------------|-----------------|

| Address Access Time (Max) | 45 ns           | 55 ns           |

| Output Enable Time (Max)  | 20 ns           | 30 ns           |

### **ABSOLUTE MAXIMUM RATINGS\***

| Storage Temperature     | 65° C to +150° C |

|-------------------------|------------------|

| Voltage on any pin with |                  |

| respect to GND          | 0.6V to +7V      |

| VPP with respect to GND | 0.6V to +14.0V   |

| ESD Protection          | >2000V           |

\*Notice: Stresses above those listed here may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

### **OPERATING RANGE**

| RANGE   | TEMPERATURE | V <sub>cc</sub> |

|---------|-------------|-----------------|

| Comm'l. | 0° to +70°C | +5V ± 5%        |

### DC READ CHARACTERISTICS Over Operating Range. (See Above)

| SYMBOL           | PARAMETER                             | TEST CONDITIONS                 |        | MIN | MAX | UNITS |

|------------------|---------------------------------------|---------------------------------|--------|-----|-----|-------|

| V <sub>OL</sub>  | Output Low Voltage                    | I <sub>OL</sub> = 16 mA         |        |     | 0.4 | v     |

| V <sub>OH</sub>  | Output High Voltage                   | $I_{OH} = -4 \text{ mA}$        |        | 2.4 |     | v     |

| I <sub>CC1</sub> | V <sub>CC</sub> Active Current (CMOS) | Notes 1 and 3                   | Commʻl |     | 20  | mA    |

| I <sub>CC2</sub> | V <sub>CC</sub> Active Current (TTL)  | Notes 2 and 3                   | Comm'l |     | 25  | 107   |

| I <sub>LI</sub>  | Input Load Current                    | $V_{IN} = 5.5V$ or Gnd          |        | -10 | 10  | μA    |

| I <sub>LO</sub>  | Output Leakage Current                | $V_{OUT} = 5.5V \text{ or Gnd}$ |        | 110 | 10  | μΛ    |

**NOTES:** 1) CMOS inputs: GND  $\pm$  0.3V or V<sub>CC</sub>  $\pm$  0.3V. 2) TTL inputs: V<sub>IL</sub>  $\leq$  0.8V, V<sub>IH</sub>  $\geq$  2.0V.

3) A.C. Power component adds 3 mA/MHz.

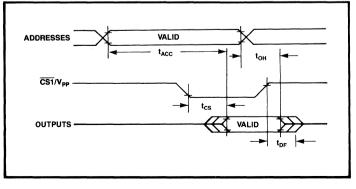

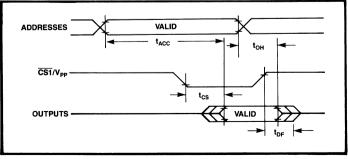

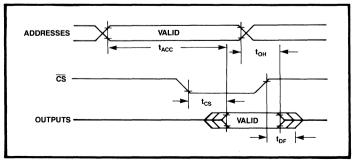

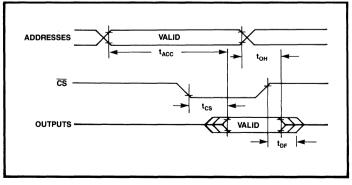

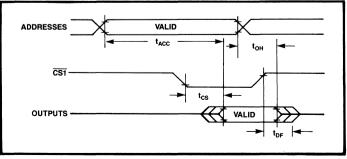

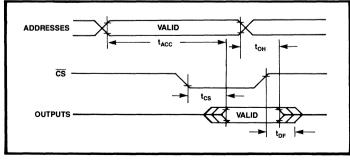

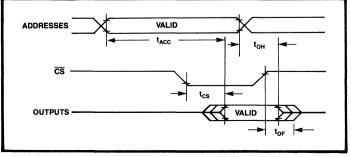

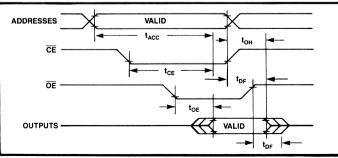

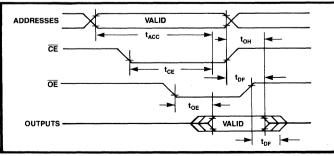

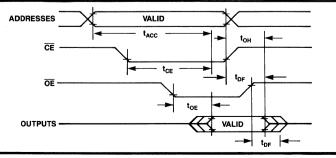

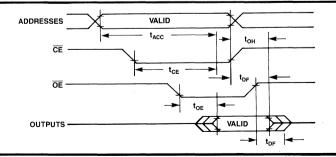

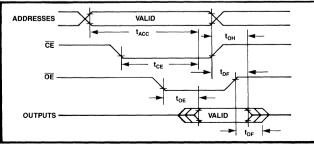

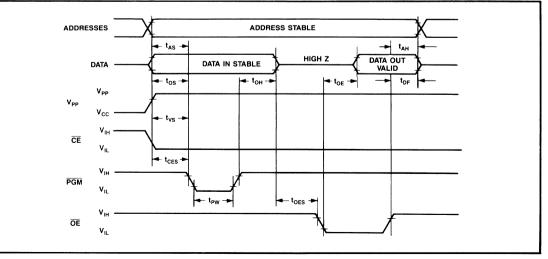

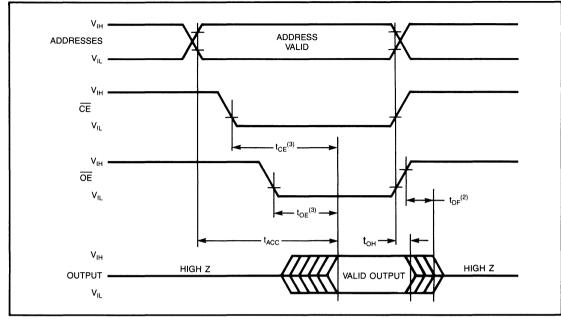

### AC READ CHARACTERISTICS Over Operating Range. (See Above)

| DADAMETED                      | SYMPOL           | WS57C1 | 91/291-45 | WS57C1 | 91/291-55 |       |

|--------------------------------|------------------|--------|-----------|--------|-----------|-------|

| PARAMETER                      | SYMBOL           | MIN    | MAX       | MIN    | MAX       | UNITS |

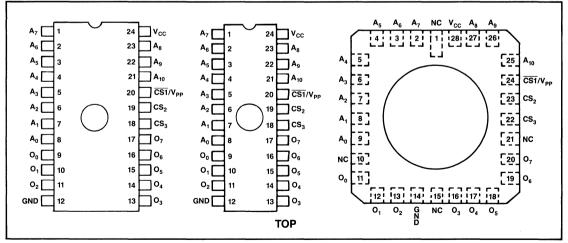

| Address to Output Delay        | t <sub>ACC</sub> |        | 45        |        | 55        |       |

| CS to Output Delay             | t <sub>CS</sub>  |        | 20        |        | 30        | ns    |

| Output Disable to Output Float | t <sub>DF</sub>  |        | 20        |        | 30        | 113   |

| Address to Output Hold         | t <sub>он</sub>  | 0      |           | 0      |           |       |

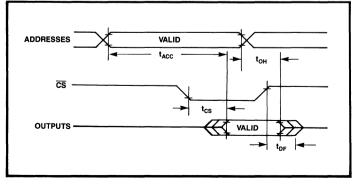

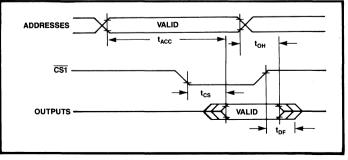

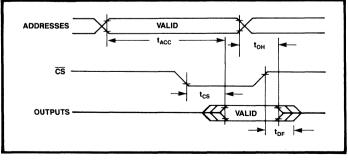

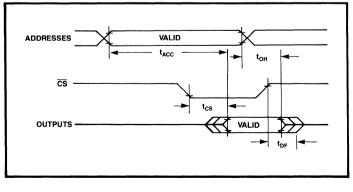

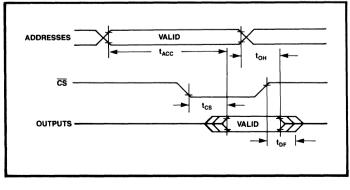

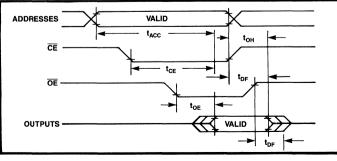

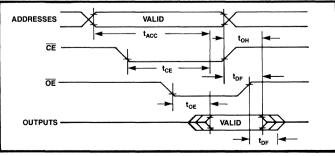

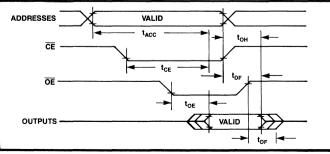

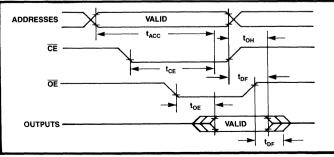

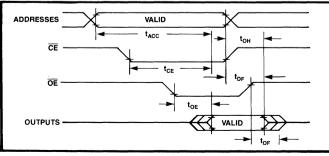

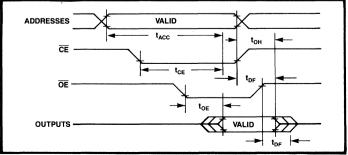

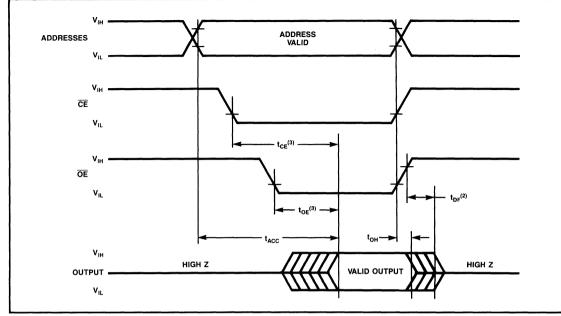

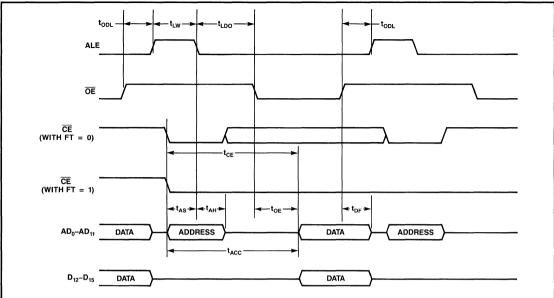

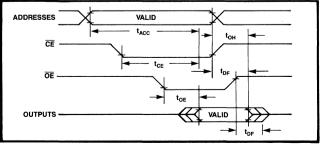

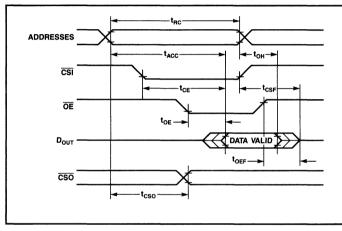

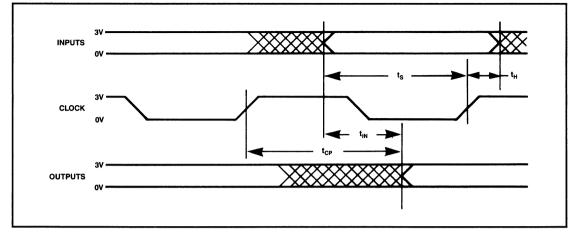

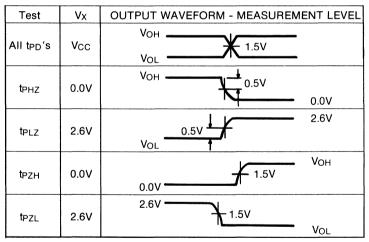

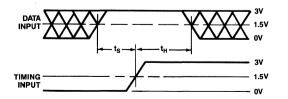

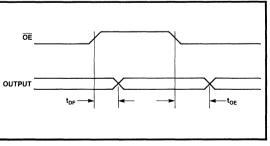

### AC READ TIMING DIAGRAM

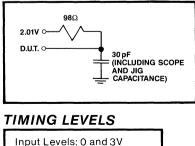

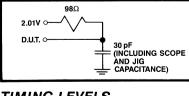

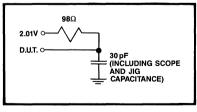

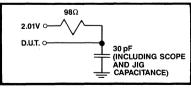

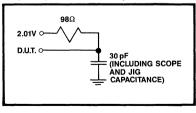

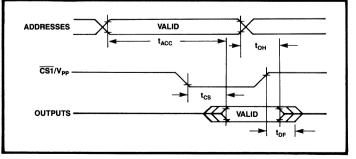

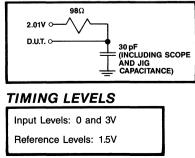

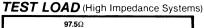

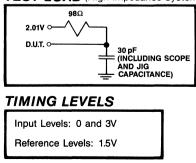

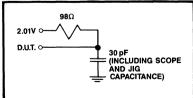

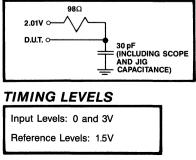

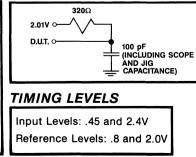

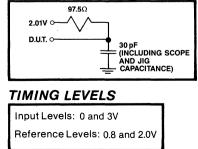

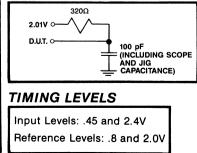

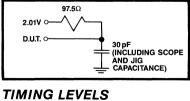

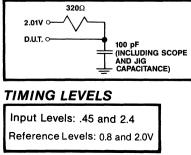

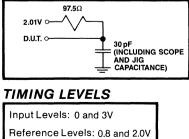

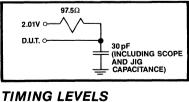

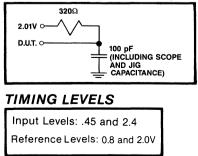

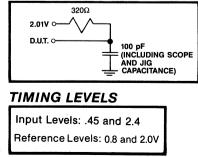

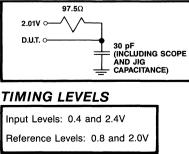

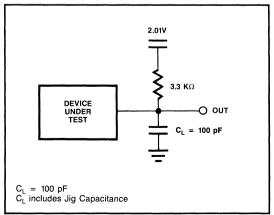

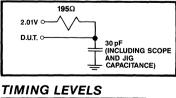

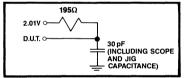

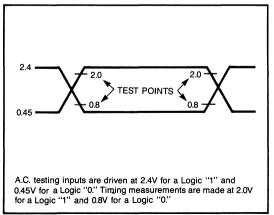

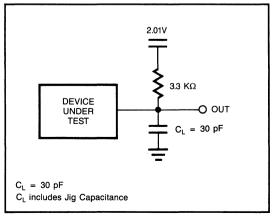

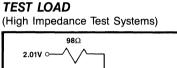

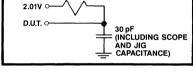

#### **TEST LOAD** (High Impedance Test Systems)

Reference Levels: 1.5V

### **PROGRAMMING INFORMATION**

### **DC CHARACTERISTICS** $(T_A = 25 \pm 5^{\circ}C, V_{CC} = 5.50V \pm 5^{\circ}V, V_{PP} = 13.5 \pm 0.5V)$

| PARAMETER                                                         | SYMBOLS         | MIN  | MAX                   | UNIT |

|-------------------------------------------------------------------|-----------------|------|-----------------------|------|

| Input Leakage Current<br>V <sub>IN</sub> = V <sub>cc</sub> or Gnd | I <sub>L1</sub> | -10  | 10                    | μΑ   |

| V <sub>PP</sub> Supply Current During<br>Programming Pulse        | I <sub>PP</sub> |      | 60                    | mA   |

| V <sub>CC</sub> Supply Current (Note 3)                           | I <sub>CC</sub> |      | 25                    | mA   |

| Input Low Level                                                   | V <sub>IL</sub> | -0.1 | 0.8                   | V    |

| Input High Level                                                  | ViH             | 2.0  | V <sub>CC</sub> + 0.3 | V    |

| Output Low Voltage During Verify $(I_{OL} = 16 \text{mA})$        | V <sub>OL</sub> |      | 0.45                  | V    |

| Output High Voltage During Verify $(I_{OH} = -4mA)$               | V <sub>OH</sub> | 2.4  |                       | V    |

NOTE: 5) V<sub>PP</sub> must not be greater than 14 volts including overshoot.

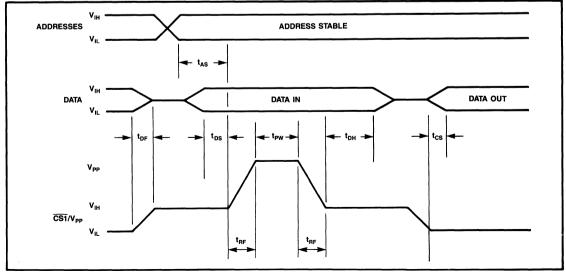

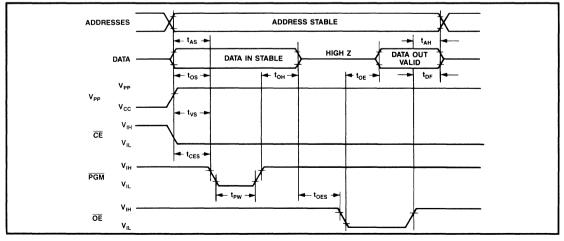

### **AC CHARACTERISTICS** ( $T_A = 25 \pm 5^{\circ}C$ , $V_{CC} = 5.50V \pm 5^{\circ}$ , $V_{PP} = 13.5 \pm 0.5V$ )

| PARAMETER                          | SYMBOLS         | MIN | ТҮР | MAX | UNIT |

|------------------------------------|-----------------|-----|-----|-----|------|

| Address Setup Time                 | t <sub>AS</sub> | 2   |     |     | μS   |

| Chip Disable Setup Time            | t <sub>DF</sub> | 2   |     | 30  | ns   |

| Data Set Up                        | t <sub>DS</sub> | 2   |     |     | μS   |

| Program Pulse Width (Note 6)       | t <sub>PW</sub> | 1   | 3   | 10  | ms   |

| Data Hold Time                     | t <sub>DH</sub> | 2   |     |     | μS   |

| Chip Select Delay                  | t <sub>cs</sub> |     |     | 30  | ns   |

| V <sub>PP</sub> Rise and Fall Time | t <sub>RF</sub> | 1   |     |     | μS   |

NOTE: 6) For programmers utilizing a one shot programming pulse, a 10 ms pulse width should be used.

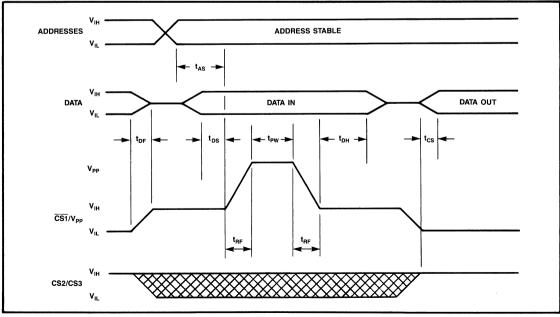

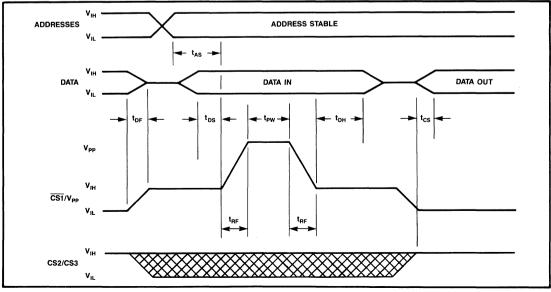

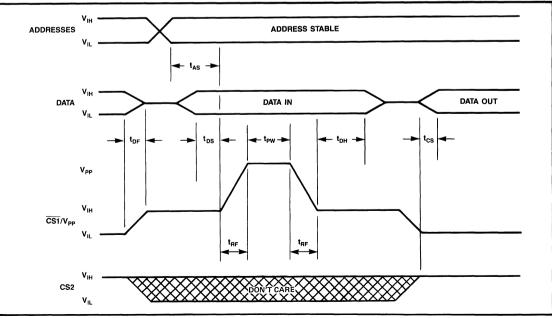

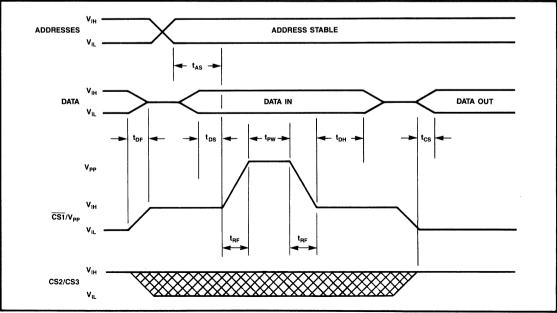

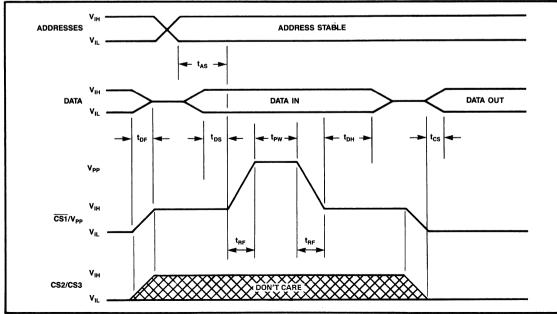

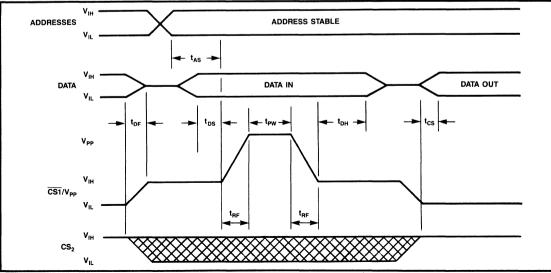

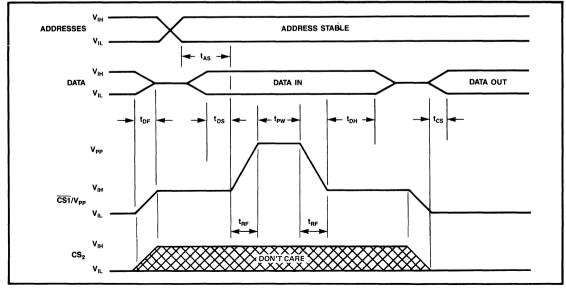

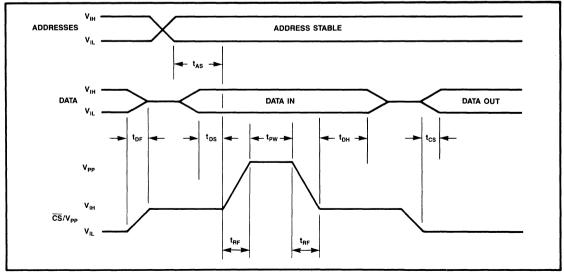

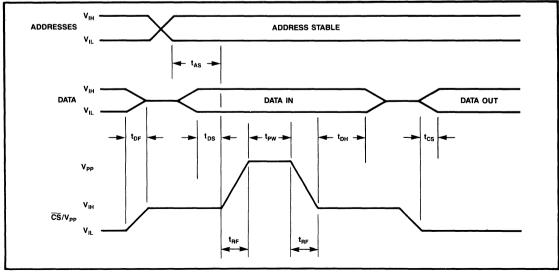

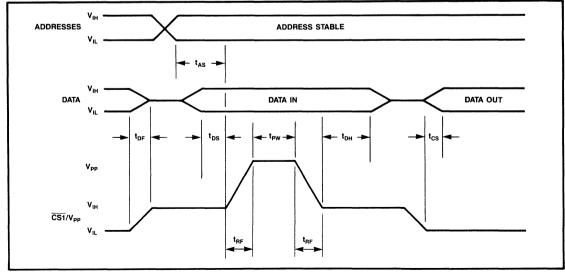

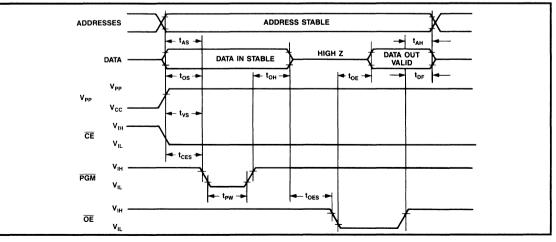

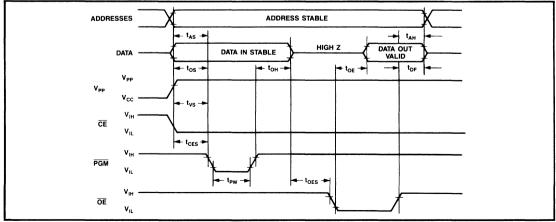

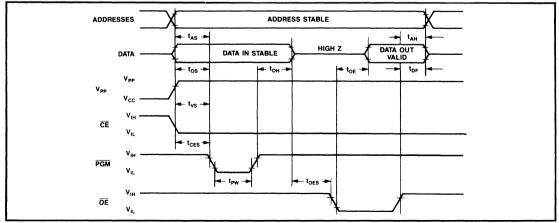

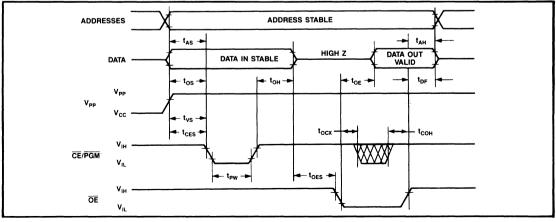

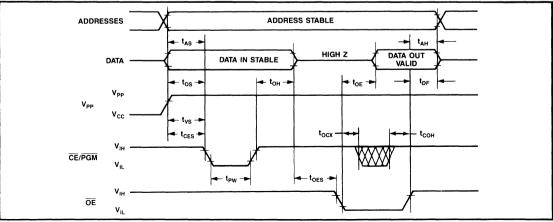

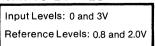

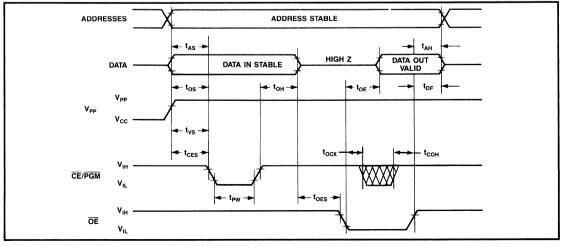

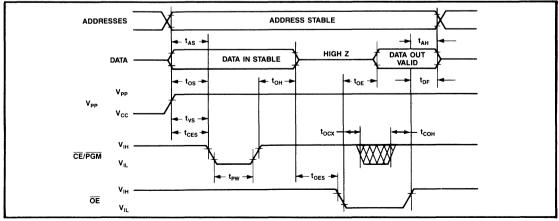

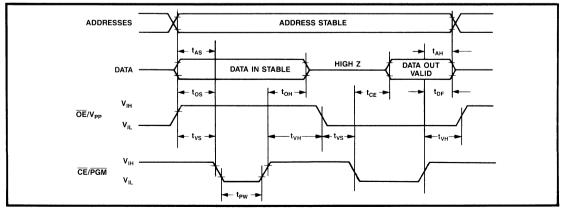

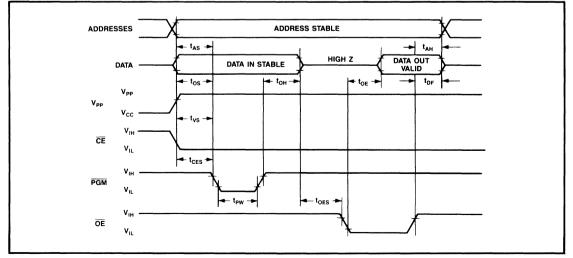

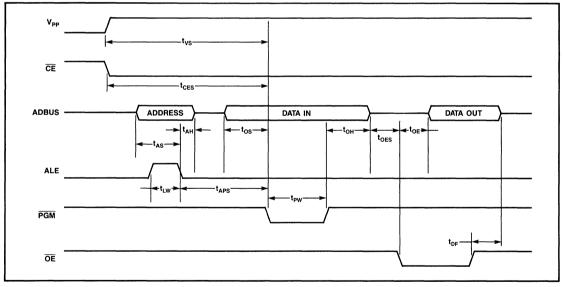

### **PROGRAMMING WAVEFORM**

#### PROGRAMMING

Upon delivery from WaferScale Integration, Inc., the WS57C191/291 has all 2048×8 bits in the "1," or high state. "0's" are loaded into the WS57C191/291 through the procedure of programming.

Programming is performed by raising V<sub>CC</sub> to 5.75V, disabling the outputs, addressing the byte to be programmed, presenting the data to be programmed onto the data pins, and applying a 13.5V pulse to the  $\overline{CS1}/V_{PP}$  pin for 5 ms. The byte is then verified by temoving the input data and reading the programmed byte as in the read operation. A 0.1  $\mu F$  capacitor between V\_PP and GND is needed to prevent excessive voltage transients which could damage the device.

#### PROGRAMMERS

Data I/O Unipak 2 or 2B, family/pinout code 7B/21; WSI's MagicPro<sup>™</sup> IBM PC Compatible Engineering Programmer.

### **ORDERING INFORMATION**

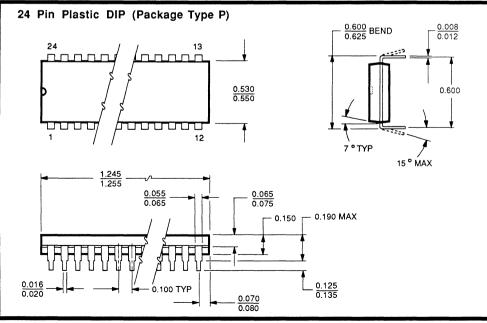

| PART NUMBER  | SPEED<br>(ns) | PACKAGE<br>TYPE   | PACKAGE<br>DRAWING | OPERATING<br>TEMPERATURE<br>RANGE | WSI<br>MANUFACTURING<br>PROCEDURE |

|--------------|---------------|-------------------|--------------------|-----------------------------------|-----------------------------------|

| WS57C191-45P | 45            | 24 Pin PDIP, 0.6" | P2                 | Comm'l                            | Standard                          |

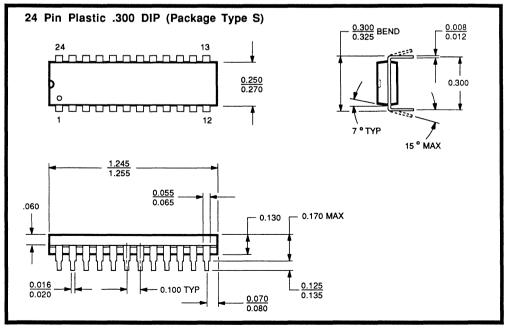

| WS57C291-45S | 45            | 24 Pin PDIP, 0.3" | S1                 | Comm'l                            | Standard                          |

| WS57C191-55P | 55            | 24 Pin PDIP, 0.6" | P2                 | Comm'l                            | Standard                          |

| WS57C291-55S | 55            | 24 Pin PDIP, 0.3" | S1                 | Comm'l                            | Standard                          |

### **ADVANCE INFORMATION**

### 2K × 8 CMOS PROM

### **KEY FEATURES**

Ultra-Fast Access Time

- 35 ns

WAFERSCALE INTEGRATION. INC.

- Low Power Consumption

\_ 225 mW Active Power

- Fast Programming

- Pin Compatible with AM27S191/291 and N82S191 Bipolar PROMs

- Immune to Latch-Up

- Up to 200 mA

- ESD Protection Exceeds 2000V

- Plastic Dip Package

### **GENERAL DESCRIPTION**

The WS57C191B/291B is an extremely HIGH PERFORMANCE 16K Electrically Programmable Read Only Memory. It is specifically designed to replace bipolar PROMs in existing applications.

The WS57C191B/291B is manufactured using WSI's patented CMOS EPROM technology. As a result, the entire memory array can be fully programmed and erased prior to assembly. This capability ensures nearly 100% programming yield. Devices manufactured with other types of technologies utilize various types of fuses which cannot be tested without permanently programming the fuse. This results in relatively high programming fallout when compared to a WSI PROM.

Other testability features were designed into the WS57C191B/291B which enable it to be tested for speed after assembly without programming the memory array. This capability insures that the product will meet all A.C. as well as D.C. data sheet parameters.

Another feature of the WS57C191B/291B is its uniquely designed output structure. When compared with other high speed devices, the output structure of the WS57C191B/291B virtually eliminates the introduction of switch related noise into the system environment.

The WS57C191B/291B is configured in the standard Bipolar PROM pinout. The WS57C191B is offered in a 600 mil wide Dip and the WS57C291B is offered in a 300 mil wide Dip.

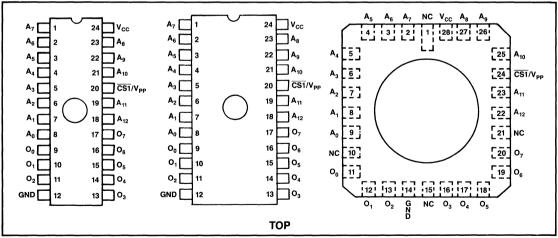

### PIN CONFIGURATION

### **PRODUCT SELECTION GUIDE**

| PARAMETER                 | WS57C191B/291B-35 | WS57C191B/291B-45 |

|---------------------------|-------------------|-------------------|

| Address Access Time (Max) | 45 ns             | 55 ns             |

| Output Enable Time (Max)  | 20 ns             | 30 ns             |

| Storage Temperature65° to +150°C                |

|-------------------------------------------------|

| Voltage on any pin with                         |

| respect to GND0.6V to +7V                       |

| V <sub>PP</sub> with respect to GND0.6V to +14V |

| ESD Protection>2000V                            |

\*Notice: Stresses above those listed here may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

#### **OPERATING RANGE**

| RANGE  | RANGE TEMPERATURE |          |

|--------|-------------------|----------|

| Comm'l | 0° to +70°C       | +5V ± 5% |

#### DC READ CHARACTERISTICS Over Operating Range. (See Above)

| SYMBOL           | PARAMETER                             | TEST CONDITIONS                 |        | MIN | MAX | UNITS |

|------------------|---------------------------------------|---------------------------------|--------|-----|-----|-------|

| V <sub>OL</sub>  | Output Low Voltage                    | $I_{OL} = 16 \text{ mA}$        |        |     | 0.4 | v     |

| V <sub>OH</sub>  | Output High Voltage                   | $I_{OH} = -4 \text{ mA}$        |        | 2.4 |     | v     |

| I <sub>CC1</sub> | V <sub>CC</sub> Active Current (CMOS) | Notes 1 and 3                   | Comm'l |     | 30  | mA    |

| I <sub>CC2</sub> | V <sub>CC</sub> Active Current (TTL)  | Notes 2 and 3                   | Comm'l |     | 40  |       |

| ۱ <sub>LI</sub>  | Input Load Current                    | $V_{IN} = 5.5V \text{ or Gnd}$  |        | -10 | 10  | μA    |

| I <sub>LO</sub>  | Output Leakage Current                | $V_{OUT} = 5.5V \text{ or Gnd}$ |        | -10 | 10  | μΛ    |

NOTES: 1) CMOS inputs: GND  $\pm$  0.3V or V<sub>CC</sub>  $\pm$  0.3V. 3) A.C. Power component adds 3 mA/MHz. 2) TTL inputs: V<sub>IL</sub>  $\leq$  0.8V, V<sub>IH</sub>  $\geq$  2.0V.

# AC READ CHARACTERISTICS Over Operating Range. (See Above)

|                                | CYMDOL           | WS57C19 | 1 <b>B/291B-3</b> 5 | WS57C191 | B/291B-45 | UNITS |

|--------------------------------|------------------|---------|---------------------|----------|-----------|-------|

| PARAMETER                      | SYMBOL           | MIN     | MAX                 | MIN      | MAX       | UNITS |

| Address to Output Delay        | t <sub>ACC</sub> |         | 35                  |          | 45        |       |

| CS to Output Delay             | t <sub>CS</sub>  |         | 20                  |          | 20        | ns    |

| Output Disable to Output Float | t <sub>DF</sub>  |         | 20                  |          | 20        | 113   |

| Address to Output Hold         | t <sub>он</sub>  | 0       |                     | 0        |           |       |

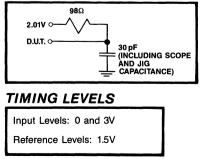

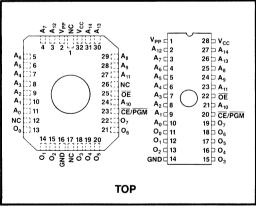

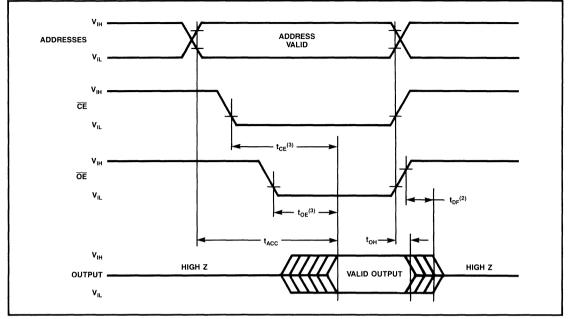

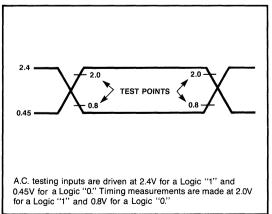

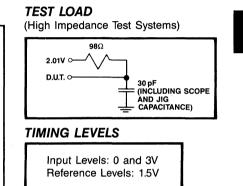

## AC READ TIMING DIAGRAM

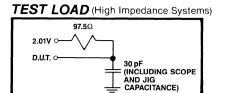

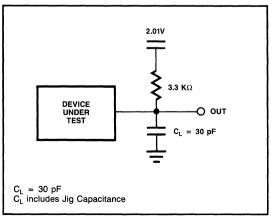

## TEST LOAD

(High Impedance Test Systems)

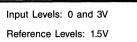

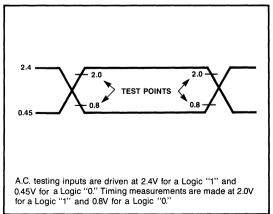

## TIMING LEVELS

| Input Levels: 0 and 3V |  |

|------------------------|--|

| Reference Levels: 1.5V |  |

DC CHARACTERISTICS (T<sub>A</sub> = 25  $\pm$  5°C, V<sub>CC</sub> = 5.50V  $\pm$  5%, V<sub>PP</sub> = 13.5  $\pm$  0.5V)

| PARAMETER                                                         | SYMBOLS         | MIN  | MAX                  | UNIT |

|-------------------------------------------------------------------|-----------------|------|----------------------|------|

| Input Leakage Current<br>V <sub>IN</sub> = V <sub>CC</sub> or Gnd | I <sub>LI</sub> | -10  | 10                   | μΑ   |

| V <sub>PP</sub> Supply Current During<br>Programming Pulse        | I <sub>PP</sub> |      | 60                   | mA   |

| V <sub>CC</sub> Supply Current (Note 3)                           | Icc             |      | 25                   | mA   |

| Input Low Level                                                   | V <sub>IL</sub> | -0.1 | 0.8                  | V    |

| Input High Level                                                  | V <sub>IH</sub> | 2.0  | V <sub>CC</sub> +0.3 | V    |

| Output Low Voltage During Verify<br>(I <sub>OL</sub> = 16 mA)     | V <sub>OL</sub> |      | 0.45                 | v    |

| Output High Voltage During Verify $(I_{OH} = -4 \text{ mA})$      | V <sub>OH</sub> | 2.4  |                      | v    |

NOTE: 4) V<sub>PP</sub> must not be greater than 14 volts including overshoot.

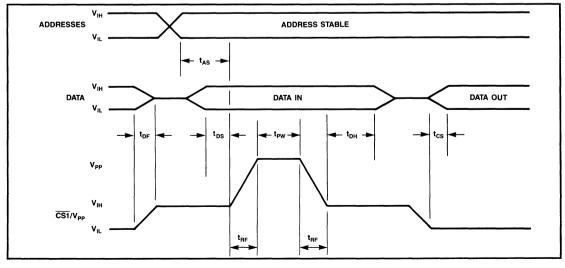

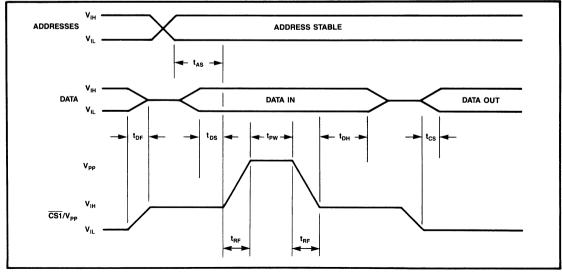

## AC CHARACTERISTICS (T<sub>A</sub> = 25 $\pm$ 5°C, V<sub>CC</sub> = 5.50V $\pm$ 5%, V<sub>PP</sub> = 13.5 $\pm$ 0.5V)

| PARAMETER                          | SYMBOLS         | MIN | ТҮР | МАХ | UNIT |

|------------------------------------|-----------------|-----|-----|-----|------|

| Address Setup Time                 | t <sub>AS</sub> | 2   |     |     | μs   |

| Chip Disable Setup Time            | t <sub>DF</sub> | 2   |     | 30  | ns   |

| Data Set Up                        | t <sub>DS</sub> |     |     |     | μs   |

| Program Pulse Width (Note 5)       | t <sub>PW</sub> | 1   | 3   | 10  | ms   |

| Data Hold Time                     | t <sub>DH</sub> | 2   |     |     | μs   |

| Chip Select Delay                  | t <sub>CS</sub> |     |     | 30  | ns   |

| V <sub>PP</sub> Rise and Fall Time | t <sub>RF</sub> | 1   |     |     | μs   |

NOTE: 5) For programmers utilizing a one shot programming pulse, a 10 ms pulse width should be used.

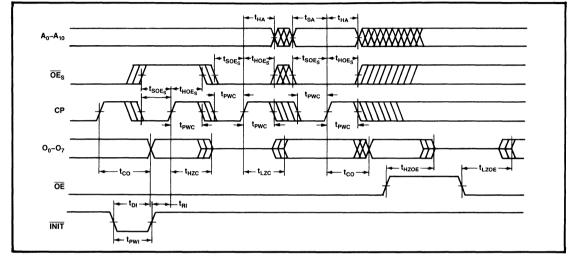

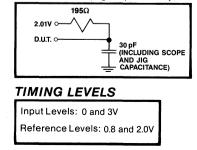

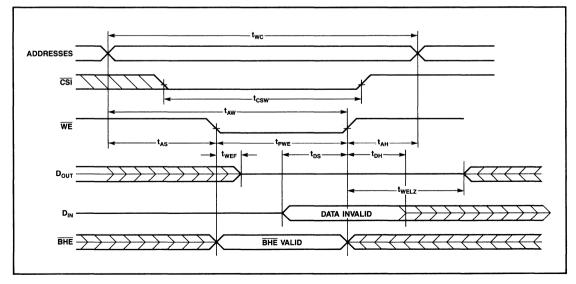

#### PROGRAMMING WAVEFORM

#### PROGRAMMING

Upon delivery from WaferScale Integration, Inc., the WS57C191B/291B has all  $2048 \times 8$  bits in the "1," or high state. "0's" are loaded into the WS57C191B/291B through the procedure of programming.

Programming is performed by raising V<sub>CC</sub> to 5.75V, disabling the outputs, addressing the byte to be programmed, presenting the data to be programmed onto the data pins, and applying a 13.5V pulse to the  $\overline{CS1}/V_{PP}$  pin for 5 ms. The byte is then verified by removing the input data and reading the programmed byte as in the read operation. A 0.1  $\mu F$  capacitor between V\_PP and GND is needed to prevent excessive voltage transients which could damage the device.

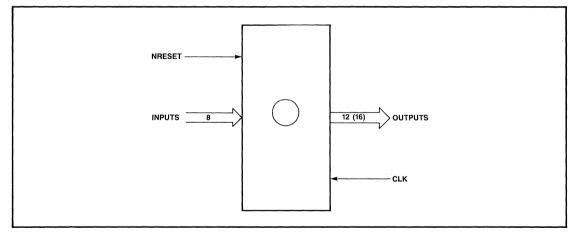

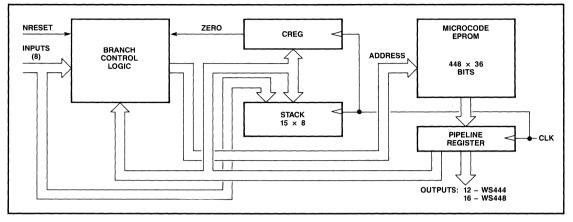

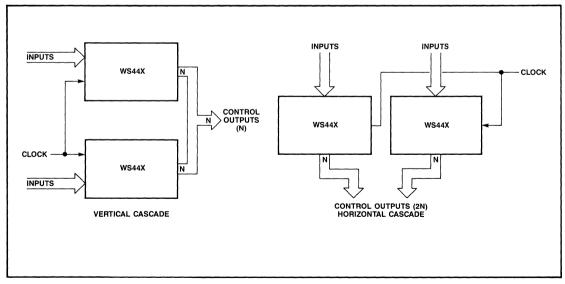

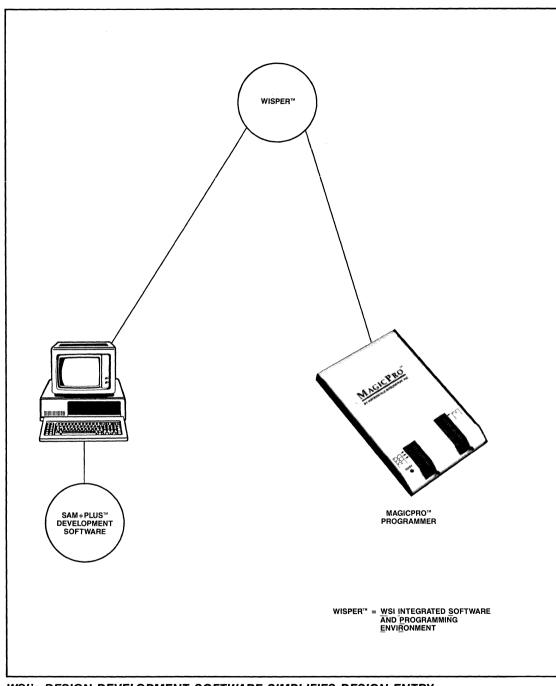

#### PROGRAMMERS