| ASIC<br>SOFTWARE<br>TOOLS<br>DATA BOOK |

|----------------------------------------|

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

| ASIC Division                          |

|   |   |                                       | ASIC<br>SOFTWARE<br>TOOLS<br>DATA BOOK |

|---|---|---------------------------------------|----------------------------------------|

| · |   |                                       |                                        |

|   |   |                                       |                                        |

|   |   |                                       |                                        |

|   | · | · · · · · · · · · · · · · · · · · · · | <br>                                   |

**ASIC** Division

©1988 VLSI Technology, Inc. All rights reserved. This document and the software that it describes are the proprietary and confidential property of VLSI Technology, Inc. ("VLSI") and Xidak Inc., for distribution and use only under license from VLSI and may not be copied without VLSI's written consent.

VLSI Technology reserves the right to make changes in the contents of this document without notice. VLSI Technology assumes no responsibility for any errors that appear in this document.

Mainsail is a trademark of Xidak, Inc. Bitpad is a trademark of Summagraphics, Inc. VAX and Vax/VMS are trademarks of Digital Equipment Corporation. Unix is a trademark of AT&T Bell Laboratories. EMBOS is a trademark of Elxsi, Inc. ROS is a trademark of Ridge Computers. Aegis is a trademark of Apollo Computer, Inc.

#### **RESTRICTED RIGHTS LEGEND**

Use, duplication or disclosure by the U.S. Government is subject to restrictions as set forth in subdivision (b) (3) (ii) of the Rights In Technical Data and Computer Software clause at 52.227-7013 (48 CFR 252).

### CONTENTS

i

| ſ     | Introduction                        | 1  |

|-------|-------------------------------------|----|

|       | Overall VLSI Tools System           | 3  |

| Π     | System Support Tools                | 9  |

|       | VLSI Cell Manager                   | 11 |

|       | VLSI Text Editor                    | 19 |

|       | VLSI Cell Library Window            | 23 |

| III a | Logic Design and Analysis Tools     | 29 |

|       | VLSI Design Assistant               | 31 |

|       | VLSI Schematic Editor               | 37 |

|       | VLSI Icon Editor                    | 43 |

|       | VLSI State Machine Compiler         | 47 |

|       | VLSI Screener                       | 55 |

| IV    | Logic and Timing Verification Tools | 61 |

|       | VLSI Timing Verifier                | 63 |

|       |                                     |    |

| VLSI Simulator        | 69  |

|-----------------------|-----|

| VLSI Switch           | 77  |

| VTImodel              | 81  |

| VLSI Test Package     | 87  |

| VLSI Vector Processor | 95  |

| VLSI Spice            | 103 |

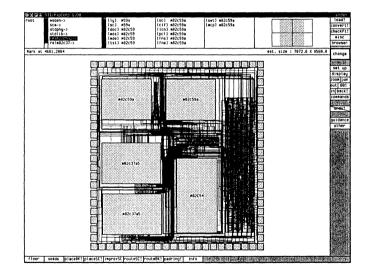

### Physical Design Tools 109

| VLSI Chip Compiler      | 111 |

|-------------------------|-----|

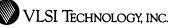

| VLSI Composition Editor | 121 |

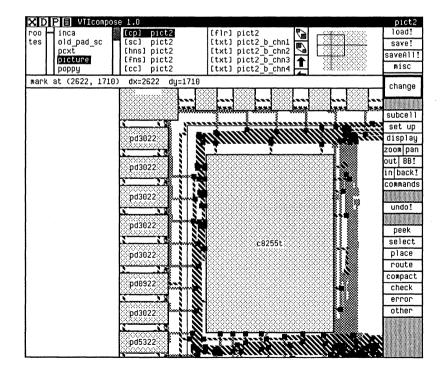

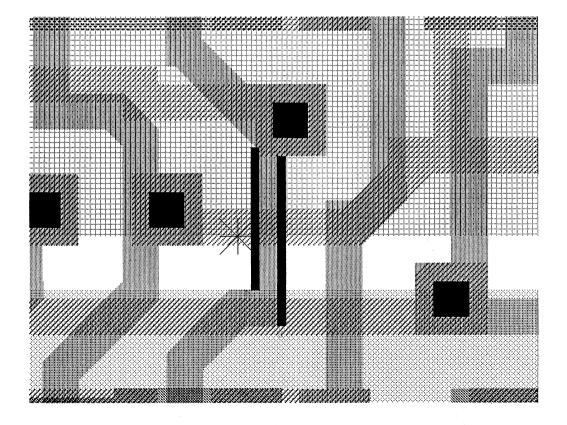

| VLSI Layout Editor      | 131 |

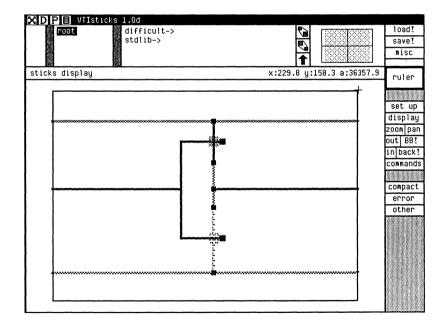

| VLSI Sticks Editor      | 137 |

| VLSI CalCif and CifCal  | 141 |

### Physical Verification Tools 145

| VLSI DRC          | 147 |

|-------------------|-----|

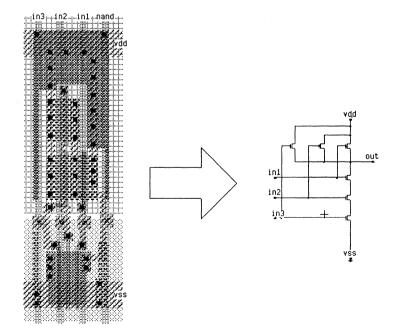

| VLSI Extractor    | 151 |

| VLSI Netcompare   | 157 |

| VLSI ERC          | 163 |

| VLSI Plot Package | 167 |

ii

# Introduction

# Overall VLSI Tools System

General Description

4

#### Overview

The Express<sup>tm</sup> ASIC Design System from VLSI Technology is an advanced set of CAE tools covering every phase of ASIC design, from conception and logic design through physical verification. Along with VLSI's extensive libraries, VLSI's Tools can be used for both gate array and cell-based designs, including any combination of standard cells, compiled blocks, Megacells, and full custom blocks.

The VLSI Tools greatly enhance design productivity, significantly decreasing the overall design time for complex and high integration ASIC's. The Tools are highly automated and simple to use, while also being highly flexible. They are therefore suitable for both advanced and novice users. The Tools' speed and efficiency allow them to handle designs ranging up to very high complexities -- over 100,000 gates, while resulting in extremely dense layouts.

The VLSI Tools are available in packages ranging in power from a logic-only design system to a full-scale ASIC CAD system. The Tools are available on a number of hardware platforms, including workstations and compute engines from Apollo, Sun, DEC, Hewlett Packard and Ridge.

The VLSI Tools also contain programs which support the automatic transfer of whole or partial designs in either direction between the VLSI Tools and a growing list of other design tools and environments. The list includes third-party CAE workstations, simulators, and hardware accelerators.

The VLSI Tools support a number of input devices, including mouses and tablets, besides keyboards.

The VLSI Tools are highly integrated, with a consistent, friendly user interface. The Tools have many general features in common, as described on the next page.

| $\mathbf{F}$ | eatures |  |

|--------------|---------|--|

| F            | eatures |  |

Convenient User Interface The VLSI Tools are highly integrated and have a consistent window-oriented, menu-driven user interface, making them easy to learn and use. All tools have similar commands with similar names, syntax and semantics. All windows and pop-up menus have similar graphic and command structures and have been designed to minimize the number of discrete button clicks and keystrokes.

Integrated Database

A common database with a simple abstract structure underlies all of the Tools. All pieces and types of design information are stored uniformly in objects called *cells*. Each tool can accept data in many forms, automatically converting between cell types if necessary.

Communication Between Windows An arbitrary number of windows can be open at once, on the same or different parts of your design. A change made to a cell in one window is automatically reflected in other windows containing that cell. Changes in lower level cells are automatically reflected at the top level.

Flexible Window Manipulation

6

A number of convenient features exist for manipulating graphical windows. Individual windows, with work in progress, can be parked off to the side to avoid cluttering the screen, and then conveniently reopened. Windows can also be reframed or moved conveniently. Similarly, even pop-up menus can be easily moved, to avoid obscuring something you might wish to see while making selections.

#### Powerful Zoom

The graphical windows have a variety of powerful and convenient zoom and pan mechanisms to change your current viewing scale and location. Each window has a graphical zoom pane which shows an outline representing your current view relative to the design's total extent. You can zoom in or out by framing an area in the zoom pane, or by framing an area in the actual view. There are also commands to zoom to the bounding box, the last zoomed view, a named previous view, or an explicit absolute scale. You can pan using the zoom pane, or by specifying source and destination points in the actual view. Similarly, all text windows have common convenient scrolling mechanisms.

Flexible Command Language Non-graphic tools have a flexible yet concise command language. Command abbreviations are recognized; you need only type enough characters to disambiguate the command. Often, you may also define macro-like aliases for commands and their parameter combinations, and any command that takes a list of node names as a parameter also takes wild card and exclude patterns. You can get help at any point by typing '?'.

1

| Aborting   | Most operations in VLSI Tools are quick, even when used         |

|------------|-----------------------------------------------------------------|

| Long       | interactively. However, operations that are a bit longer by     |

| Operations | their very nature, such as the complete compaction of a full    |

|            | complex chip, can often be interrupted in progress without      |

|            | leaving the editing session, by typing a simple abort sequence. |

Interactive or Batch Mode

The VLSI Tools can be run graphically or in a textual shell environment, allowing them to be run interactively or with command files. Most graphic tools also have a non-graphic command interface that allows them to be accessed from the shell environment. Conversely, the VLSI shell can be accessed from the graphics environment, through VLSI's terminal emulator window.

# System Support Tools

### VLSI Cell Manager

### Hierarchical Database Manager for IC Design Projects

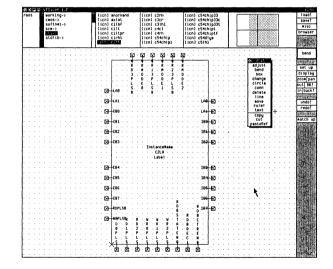

| VID         VITmanager         V           root         (sc)         ao01d1           VLSI         [sc]         ao02d1           GATE         (sc)         ao04d1           AND-         (sc)         ao05d1 | .0d<br>[icn] a002d1<br>[mde] a002d1<br>[scp] a002d1<br>[pmd] a002d1<br>[ipd] a002d1 | copy-mid<br>commands<br>set                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| [sc] a002d1<br>[sc] a003d1<br>[sc] a004d1<br>[sc] jkbnnb<br>[sc] mfbnst<br>[sc] mfcnsb<br>[sc] mfcnsn<br>[sc] tfcnnn<br>[sc] tfptnb                                                                          |                                                                                     | cut-top<br>commands<br>category<br>check<br>clear!<br>delete<br>library<br>notice!<br>port |

| POOL AND GATES<br>VISI AND-OR GATES<br>GATE CLOCK BUFFERS<br>INVERTERS<br>INVERTING 3-ST<br>NAND GATES<br>NON-INVERTING                                                                                      | [sc] a001d1<br>[sc] a002d1<br>[sc] a003d1<br>[sc] a004d1<br>[sc] a005d1             | saveI<br>session<br>info<br>commands                                                       |

12

#### **Overview**

VTImanager, VLSI's Cell and Project Manager, is an integral part of VLSI's tools that is responsible for all aspects of managing the design database. It consists of three parts which interact closely.

The first part is the data manager that underlies all of VLSI's tools. You need never interact directly with the data manager; rather, every VLSI tool interacts with it automatically on your behalf. The data manager is responsible for storing your design files in the file systems of the computers that you use, for finding these files there when they are needed, and for controlling simultaneous access to these files by other designers.

The second part is the browser, a pane attached to the top of every window which displays the various parts of your design for selection and use.

The third component is the manager window, a dedicated window that you use to control the operation of the cell manager and for major restructuring of the way that the browser presents your designs to you. Some of the commands in this window are also available directly in the browser pane in each window.

VTImanager provides extensive support for multi-person designs and individual experimentation. You can gain exclusive access to parts of a design in order to alter them, while other designers continue to use the old unchanged versions. When the alterations are completed to your satisfaction, you can release them to the other designers on the project. You do not need to get exclusive access to large parts of a design in order to alter just a small portion of it.

Component libraries can easily be shared among several designs. You select the libraries you wish to access by setting your search path. Public component libraries, which are frozen to maintain their integrity, can be stored in a particularly efficient way which uses less disk space and can be accessed in a faster manner.

Several versions of most design files are preserved. The oldest versions are deleted automatically.

VTImanager provides a simple mechanism for moving parts of, or even whole, designs to different computers, other designers or archive media. Little interaction is involved to restore the design at the destination or from archive.

#### Features

Structured Database

14

VTImanager provides a consistent, operating-system independent, abstract view of the design database. All pieces and types of design data are stored uniformly in objects called *cells*, and cells are grouped together into *libraries*, which can be shared among several designers and projects.

Search Path A search path mechanism allows individual designers and projects to make use of multiple libraries, and to selectively override cells that have multiple variations.

Graphical Interface Available cells on the search path are displayed graphically, in a browser pane at the top of each VLSI Tools window. The browser provides the means for cell selection in the various windows, so you don't have to type cell names. It also conveniently provides in each window a subset of the commands of the general manager window. VLSI TECHNOLOGY, INC.

| Hierar-<br>chical<br>Database | The cells can be structured into hierarchical browser categories<br>independently of the libraries or directories in which they are<br>located, and independent of any design hierarchy.                                                                                                                                                                                               |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integrated<br>Database        | The browser pane and underlying data manager are common<br>to all VLSI tools. VTImanager provides a unified data base<br>and user interface for all these tools.                                                                                                                                                                                                                       |

| Manager<br>Window             | There is a dedicated VTImanager window with more extensive<br>capabilities than available in the individual browsers. This<br>window provides the main interface for all the housekeeping<br>operations associated with the maintenance of libraries and<br>setting up projects. The VTImanager window also provides a<br>sophisticated way to reorganize browser category structures. |

| Cell<br>Manage-<br>ment       | The underlying data manager keeps track of various cell<br>attributes and manages the cells accordingly. These attributes<br>include both static attributes, such as creation date,<br>technology and cell type, and dynamic attributes, such as<br>whether the cell has been modified in the current session.                                                                         |

Project Management VTImanager provides a number high-level project management facilities which support multi-person designs. For example, the checkout mechanism allows you to get exclusive access to a cell to alter it, while other designers on the project continue to use the old unchanged version. Conversely, VTImanager lets you notice whether any cells have been altered by the other designers while you are in the midst of your session, so it is not necessary to lock all cells between the cell being altered and the root of the cell hierarchy.

Read-Only Libraries Libraries which are unchanging can be stored in a particularly efficient way which uses less disk space and is accessible faster than normal. This also protects such libraries from inadvertent permanent modifications, while still allowing temporary override using the search path mechanism.

Import/ Export The export and import mechanism allows any number of cells to be conveniently moved to another library or computer in a single file transfer. All administrative information is automatically transferred along with the cells, minimizing the amount of interaction needed to restore the design and make use of the cells at the destination.

| Backups                         | Backup versions of critical cells are kept. The number of<br>versions kept is under user control. Versions older than that<br>are automatically deleted as newer ones are created. |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interactive<br>or Batch<br>Mode | Many of the VTImanager window functions are also available<br>in the terminal environment, in which VTImanager can be<br>used interactively or with command files.                 |

|                                 |                                                                                                                                                                                    |

|                                 |                                                                                                                                                                                    |

|                                 |                                                                                                                                                                                    |

|                                 |                                                                                                                                                                                    |

|                                 |                                                                                                                                                                                    |

|                                 |                                                                                                                                                                                    |

|                                 |                                                                                                                                                                                    |

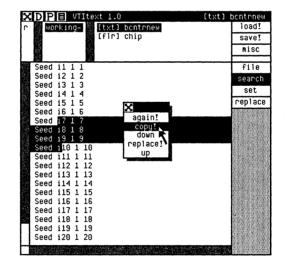

### VLSI Text Editor

### Editor for Manipulating Text Files

#### Overview

VTItext, VLSI's graphical Text Editor, is a screen-based text editor integrated into the VLSI Tools environment. As with all other VLSI editors, you give commands to the editor with the mouse and menus. This makes text manipulation very rapid and easy.

VLSI TECHNOLOGY, INC.

| Features                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The mouse is used for relocating the cursor, invoking<br>commands and moving blocks of text within the editor. The<br>mouse can be used to manually scroll to any point in the text<br>with just one or two clicks, instead of many repeated<br>keystrokes. This makes the text editor much easier to use and<br>faster than conventional keyboard-based text editors. |

| VTItext is fully integrated into the VLSI Tools environment.<br>This allows you to access the common VLSI Tools browser<br>database and quickly and easily edit any text files produced or<br>used by other tools without leaving the Tools environment.                                                                                                               |

| You can read either cells from VTItext's browser or standard<br>text files from outside, and write them back as either cells or<br>files, in any combination. This feature can be used to move<br>files into a VTImanager library, or to move cells from a library<br>to an outside directory.                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                        |

#### Flexible 2D Scrolling

Unlike most text editors, VTItext offers convenient horizontal scrolling and arbitrary line widths, in addition to vertical scrolling and unlimited length. Besides manual scrolling, automatic horizontal and vertical scrolling occurs to keep the cursor visible.

Auto Wraparound You can set VTItext to automatically begin a new line at the closest preceding word break when the line you are typing gets too long.

# VLSI Cell Library Window

Cell Library Compiler Interface and Parameter Editor

| XDP8 | VTIcellLib 1   | .0d            |        |             |       |        |        |         |

|------|----------------|----------------|--------|-------------|-------|--------|--------|---------|

| root | <u>v7-&gt;</u> |                | ibraru | ALU'        | S     |        |        | load!   |

|      | VLSI 20 CMC    | IS Compiler L: |        |             | PATHS |        |        | save!   |

|      | VLSI 2u CMC    | IS Compiler Si |        | FOUN<br>I/O |       |        |        | misc    |

|      | 8              |                |        | PLA'        |       |        |        | browser |

|      |                |                |        | RAM'        |       |        |        | make    |

|      |                |                |        | ROM'        | S     |        | ·      |         |

|      |                |                | edit   |             | help  | output | remake | set up  |

24

#### **Overview**

VTIcellLib, VLSI's Cell Library Window, is the compilation interface to VLSI's libraries, which include VLSI's high-level Datapath and State Machine Compilers, as well as VLSI's Module Compiler Library. VTIcellLib is used to specify parameter values and generate various forms of compiled data for these libraries. Compiled data includes physical layout, gate-level netlists, or schematic symbols with behavioral models. In some cases, the parameters include a reference to a higher-level specification.

VTIcellLib can also be used to specify parameters and generate schematic symbols for user-written behavioral models.

|                                 | Features                                                                                                                                                                                             |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Saved<br>Values                 | VTIcellLib enables you to save and recall sets of parameter<br>values for later use or further editing.                                                                                              |

| Menu<br>Interface               | You select a parameter graphically from a menu. If the<br>parameter has a discrete set of possible values, then those<br>values are also graphically selected. Otherwise, values may be<br>typed in. |

| Default<br>Values               | Parameters have default values, to quicken value specification.                                                                                                                                      |

| Range<br>Checking               | Parameters with a range of values are immediately range-checked upon value entry, prior to compilation.                                                                                              |

| Hierar-<br>chical<br>Parameters | Certain parameters are displayed for value specification only<br>when they are relevant, depending on the value of other<br>parameters.                                                              |

|                                 |                                                                                                                                                                                                      |

#### Compiled Output

Once parameter values have been specified, several forms of compiled output data can be generated. These include:

- Layout and Phantom. Optimized high-density layout in the form of CIF (CalTech Intermediate Format) can be generated. A phantom cell, which lacks the internal geometry, is also generated. The phantom cell enables quicker verification of the higher-level design by VTIextract, VTInetCompare and VTIdrc, because the internal, compiled geometry is already known to be correct.

- **Portable Netlist.** A netlist of primitive cells from VLSI's Portable Library can be generated in the case of many compilers, for implementation in a gate array or standard cells in a variety of process technologies.

- Simulation Netlist. A gate-level simulation netlist for modeling the compiled layout can be generated in the case of very complex compilers.

- Model Schematic. A schematic symbol can be quickly generated for either a compiler or a user-written behavioral model. In either case, the symbol represents the combination of a behavioral model with the specified parameter values.

| Quick<br>Check                  | The input descriptions for VLSI's high-level compilers, which<br>include the Datapath Compiler and State Machine Compiler,<br>can be checked for proper format or syntax without invoking a<br>full compilation. |  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Area<br>Estimate                | A quick estimate of compiled layout area, along with other<br>information, can be produced for complex compilers, without<br>invoking a full compilation.                                                        |  |  |  |  |

| Interactive<br>or Batch<br>Mode | You may use VTIcellLib interactively or with command files,<br>in either the graphics or terminal environments. VTIcellLib<br>can generate layout immediately or produce a command file to<br>do so later.       |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

|                                 |                                                                                                                                                                                                                  |  |  |  |  |

# Logic Design and Analysis Tools

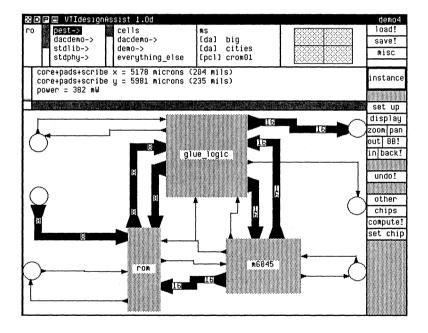

## VLSI Design Assistant

### System Partitioning and Design Evaluation Tool

#### Overview

VTIdesignAssist, VLSI's graphical Design Assistant, is an expert tool for system partitioning and design evaluation. It may be used for high-level "what-if" considerations at the very early stage of a design. It analyzes high-level trade-offs involved in partitioning a design and choosing an implementation technology, to ensure the optimal design approach and minimize system cost.

For example, the Design Assistant can help answer such questions as:

- Should I use a Megacell or a standard part?

- If the ROM is 1K larger, will the chip still fit in an inexpensive plastic package?

- Will multiplexing the data bus make a difference or is the design already core-limited?

- How much power will the chip dissipate?

- Will the design fit in a 10K gate-array?

VTIdesignAssist evaluates ASIC alternatives from a rough block diagram of the design. The diagram contains blocks representing whatever level of implementation detail is known, such as simple gate count, a list of TTL parts or other cells, a captured netlist, compiler specifications or actual data, VTIdesignAssist lavout. From this enumerates various the implementation alternatives for each chip and estimates several characteristics of the final chip for each alternative, including die size and power consumption. It also recommends the optimum package in each specified package family.

VTIdesignAssist's area analysis takes into account the known or estimated size of leaf cells, compiled blocks, gate array macros, gate array bases and so forth. In addition, it takes into account estimated routing, including standard-cell routing, inter-block routing and routing from the core to the pads. It also automatically distinguishes between core-limited and pad-limited designs, and takes the appropriate pad set into account.

The power consumption estimate takes into account operating frequency of both the pad and the core, and other factors. Besides number of pins, the package choice takes into account other factors such as die size and power dissipation.

VTIdesignAssist aids in the partitioning process at both the block and chip levels. Each block can be assigned to any of the chips in the chip set or, like a standard part, none at all. VTIdesignAssist automatically adjusts its estimates, including die size, to take into account pad requirements for inter-chip versus on-chip signals.

The analysis performed by VTIdesignAssist is driven from a user-extendable set of rules that describes the available technologies, cell libraries, routing approximation algorithms, decision criteria, and so on.

#### Features

System Partitioning VTIdesignAssist aids in the system partitioning process at both the block and chip levels. For multi-chip designs, VTIdesignAssist automatically tracks pin requirements for inter-chip signals as components and signals are moved during the analysis. This includes an estimate of the number of power and ground pins needed.

Complex Analysis VTIdesignAssist's analysis considers standard cells, compilers, megacells, gate array macro's and bases, standard cell and interblock routing, pad routing, gate array occupancy, choice of pad set, operating frequency, and available packages. VTIdesignAssist lists the possible implementation alternatives for each chip, along with close estimates of die size, power consumption, and optimum packages for each alternative.

Interactive Block Diagrams VTIdesignAssist works from generalized block diagrams and so allows the analysis of very high-level trade-offs. The diagram is entered in a very interactive way that is consistent with VTIschematic and makes changes very easy, so that different design configurations can be analyzed.

| Graphical           | Blocks are displayed dynamically in their relative estimated                                                                                                                                                                                                                                                                                                                  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feedback            | size on the chip. This gives immediate floorplanning feedback.                                                                                                                                                                                                                                                                                                                |

| Variety of<br>Input | Design feasibility can be explored using whatever level of<br>implementation detail is available. Input could be as simple as<br>gate count, a list of TTL parts or other cells, or a captured<br>netlist with instances and incomplete wiring. For yet greater<br>accuracy, input could be as detailed as a complete netlist,<br>compiler specification, or physical layout. |

| Technology          | All the technology-dependent information is contained within                                                                                                                                                                                                                                                                                                                  |

| Indepen-            | a machine-independent collection of rules containing                                                                                                                                                                                                                                                                                                                          |

| dence               | algorithmic information as well as list-oriented data.                                                                                                                                                                                                                                                                                                                        |

| Extend-             | The rule file can be tailored to your own needs or augmented                                                                                                                                                                                                                                                                                                                  |

| ibility             | for other available technologies.                                                                                                                                                                                                                                                                                                                                             |

| Schematic<br>Output | VTIdesignAssist writes out top-level schematics for each chip,<br>including all the pads and any necessary drivers or<br>level-shifters. It also writes a schematic template for each<br>block, including the connectors to the block, thus facilitating<br>top-down design.                                                                                                  |

|                     |                                                                                                                                                                                                                                                                                                                                                                               |

Documentation The block diagram can be plotted, and the results of the analysis are available in hardcopy, plain or as a quote form, as well as on-screen.

Undo

Most commands in VTIdesignAssist can be undone.

## VLSI Schematic Editor

## High Level Design Entry Program

#### **Overview**

VTIschematic, VLSI's graphical Schematic Editor, is a tool for front-end logic capture that provides you with the ability to create, view, edit and plot schematic diagrams. VTIschematic is a hierarchical tool, enabling you to create schematics that range from a complete chip description to the the gate or transistor level. Within VTIschematic, you can place and connect cells from any of VLSI's libraries, as well as behavioral models created using VTImodel. You can also place and connect standard logic gates or new schematics which you've built from a combination of any of these components.

VTIschematic diagrams provide input to many other VLSI tools, including those used for simulation, timing verification, chip compilation and netcompare.

|            | Features                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hierarchy  | With VTIschematic, you can place schematic cell instances in<br>schematic cells, building a hierarchy to describe the final<br>schematic. In this way, VTIschematic, along with the<br>companion tool VTIicon, supports both top-down and<br>bottom-up design styles along with a combination of either.                                                                                   |

| Parameters | Electrical parameters can be defined for any schematic, at any<br>level. For example, many cells in VLSI's libraries have<br>parameters handled in this way. Some behavioral model<br>parameters also show up as schematic parameters. Parameter<br>values for each instance of a schematic can then be set with<br>fixed values or they may be inherited from higher level<br>schematics. |

| Push/Pop   | You can easily push down into a schematic subcell and return,<br>to conveniently traverse the schematic hierarchy for editing.<br>Changes to lower level schematic cells are automatically<br>reflected at the top level.                                                                                                                                                                  |

#### Powerful Commands

VTIschematic provides a variety of powerful editing commands. These include an intelligent move command which retains existing connections, as well as commands to cut and paste whole regions.

Buses

VTIschematic supports buses, along with bus breakouts and bus connections.

Arrays

VTIschematic lets you conveniently and flexibly place arrays of instances or regions.

Dynamic Feedback VTIschematic's user interface gives instantaneous graphical feedback, such as rubber-banding, for pending operations.

Immediate Checking VTIschematic performs edit-time checks to prevent accidental shorting of incompatible or conflicting signals or buses. VLSI TECHNOLOGY, INC.

| Simulation<br>Feedback          | VTIschematic is tightly coupled with VTIsim, for convenient<br>circuit debugging. Nodes or instances selected in VTIsim can<br>automatically be found and highlighted in VTIschematic. |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Text<br>Annotation              | Comments and general text annotation may be added to any<br>part of a schematic to clarify the design.                                                                                 |

| Undo                            | The last several commands can be undone or redone.                                                                                                                                     |

| Plots                           | VTIschematic generates plot files for Versatec raster plotters<br>and Hewlett-Packard pen plotters.                                                                                    |

| Automatic<br>Icon<br>Generation | VTIschematic automatically generates icons to represent<br>schematic instances in higher level schematics. These icons<br>may be customized with VTIicon.                              |

| Interactive<br>or Batch<br>Mode | You may use VTIschematic interactively or with command files, in either the graphics or terminal environments.                                                                         |

|                                 |                                                                                                                                                                                        |

|                                 |                                                                                                                                                                                        |

## VLSI Icon Editor

### A Tool for Editing Schematic Symbols

#### Overview

VTIicon, VLSI's graphical Icon Editor, provides you with the ability to create, view, edit and plot schematic symbols, termed *icons*, for VTIschematic. You can create icons from scratch, or customize icons that the VLSI Tools automatically create, so that your schematics use familiar symbols and notations. VTIicon can also be used as a general-purpose graphic drawing tool.

|                                      | Features                                                                                                                                                                                                                |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Powerful<br>Commands                 | VTIicon provides a variety of powerful editing commands.<br>Arcs, circles, lines, rectangles and other objects are easily<br>created and manipulated. Whole areas can be cut and pasted.                                |

| Text<br>Annotation                   | Comments and general text annotation may be added to any<br>part of an icon to clarify the design. Several specialized text<br>fields are also available which can be changed in<br>VTIschematic.                       |

| Undo                                 | The last several commands can be undone or redone.                                                                                                                                                                      |

| Plotting                             | VTIicon generates plot files for Versatec raster plotters and<br>Hewlett-Packard pen plotters.                                                                                                                          |

| Automatic<br>Schematic<br>Generation | VTIicon can generate an empty schematic from a finished<br>icon. This allows the designer to draw a schematic using this<br>icon before any of the sub-blocks have been implemented,<br>facilitating a top-down design. |

|                                      |                                                                                                                                                                                                                         |

-

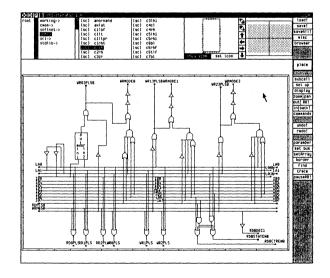

# VLSI State Machine Compiler

## ASIC Logic Synthesizer and Optimizer

| X   | DPE VTItext 1.0                                                                                                                                       | [sm] ad |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| n   | oot statemachn-> [sm] ad                                                                                                                              | load!   |

|     | [sm] idec                                                                                                                                             | save!   |

|     | [sc] riscdp_bare                                                                                                                                      | misc    |

|     |                                                                                                                                                       | browser |

|     |                                                                                                                                                       |         |

|     |                                                                                                                                                       |         |

| 28  | sm idec; # state machine for RISC instruction sequencing and decode                                                                                   | file    |

| 4   |                                                                                                                                                       | search  |

| 19  | # define bus types & symbolic values for instruction decode & control sign<br>define riscOP jump='d0 call='d1 load='d2 store='d3 loadr='d4 storer='d5 | set     |

| 8   | move='d6 add='d7 sub='d8 and='d3 or='d10 xor='d1                                                                                                      | replace |

| 8   |                                                                                                                                                       |         |

| 125 | define dpalu alu_add='b00000 alu_sub='b01000 alu_xor='b00100                                                                                          |         |

| 80  | •                                                                                                                                                     |         |

| 8   | <pre># declare inputs and outputs some are control signals from/to datapath</pre>                                                                     |         |

| 22  | latched \ inputs op[3:0] op2[3:0] cowait cc shiftmsb bit[15];                                                                                         |         |

| 8   | load .35 outputs memWr=0; # memory write enable                                                                                                       |         |

| S.  | RS=1 outputs<br>signextend # right shift msb input                                                                                                    |         |

| 62  | signextend                                                                                                                                            |         |

| 25  | alu:dpalu # alu op (a bus of tupe dpalu)                                                                                                              |         |

| 26  | selrgf:dpmux4=mux0                                                                                                                                    |         |

| S.  |                                                                                                                                                       |         |

|     | <pre># specify desired performance</pre>                                                                                                              |         |

|     | clock cp 10; # 10 MHz                                                                                                                                 |         |

|     | maxdelay 10 cp> memWr memRd memPC wenable; # 10 ns critical paths                                                                                     |         |

|     | reset r> FETCH; # specify reset signal and state                                                                                                      |         |

|     | reset i > reten, # specing reset signar and state                                                                                                     |         |

|     | let rgf_w1[0] = (r0[3:0]='d1 & !reg0) & wenable;                                                                                                      |         |

|     | state FETCH> EXECUTE seladda=muxnone wenable=0;                                                                                                       |         |

|     | # i.e. go to EXECUTE state and set these signals                                                                                                      |         |

|     | ,                                                                                                                                                     |         |

| M   | state EXECUTE                                                                                                                                         |         |

|     | op=add> alu=alu_add load_cc, # set these signals<br>op=sub> alu=alu_sub load_cc,                                                                      |         |

|     | op=addLit> alu=alu add selalub=mux1,                                                                                                                  |         |

| Н   |                                                                                                                                                       |         |

|     |                                                                                                                                                       |         |

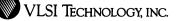

#### Overview

VLSI's State Machine Compiler, a logic synthesizer for ASIC's, is used to design, implement and optimize state machines and random logic. A state machine is a block of logic whose outputs (and next state) at any one time depend not only on the inputs at that time, but also on its current internal stored state.

State machines can be used for sequencers, controllers, or just pure combinational logic, such as decoders, with no stored state at all. They can also be used as on-chip PLD (Programmable Logic Device) replacements, for high integration.

The State Machine Compiler takes a flexible yet simple high-level language description of the desired logic and performs logic synthesis and optimization within user-specified performance constraints. It efficiently translates the high-level description to a netlist of primitives from VLSI's Portable Library, for implementation in a gate array or standard cells. It can also generate a PLA (Progammable Logic Array) code file for input to VLSI's PLA compiler. The State Machine Compiler aggressively optimizes the logic taking into account the available library and target implementation, using advanced optimization techniques.

The state machine description language is very readable, convenient and easy to use. For each relevant combination of inputs in each state, the language description specifies the desired outputs and next state, using high-level equations, buses and symbolic constants. The language and resulting state machines that can be produced are very flexible, with many useful options.

You access the State Machine Compiler through VTIcellLib or a special interface to the Compiler's PLA Optimizer. You then simulate the Compiler's output in VTIsim, using the behavioral or gate-level models

supplied with VLSI's Portable Library or PLA Compiler. The Compiler also includes a high-level behavioral model, so you can simulate your state machine directly from its description, without actually making the final netlist or code file, in order to quickly check out that description.

#### Features

Wide Applicability The State Machine Compiler can be used for a wide variety of applications, including any type of control or glue logic, with or without internal state. It can implement the most general forms of state machines and can even implement circuits beyond those normally thought of as state machines, such as pure combinational logic. It can also be used for PLD replacement.

Datapath

The State Machine Compiler smoothly complements VLSI's Datapath Compiler when used to generate datapath control and decode logic, making use of special provisions for that purpose. (See VLSI's separate Datapath Compiler Datasheet for more information on the Datapath Compiler.)

High-Level Language Input The State Machine Compiler accepts input in the form of a high-level language description. The language is very flexible, with many features:

- High-Level Equations. You describe combinational outputs and transitions between states using high-level equations.

- Buses and Symbolic Names. The inputs and outputs can be buses. You can use symbolic constants for bus values, and various operations such as comparison or assignment are allowed on such buses and constants.

VLSI TECHNOLOGY, INC.

Similarly, states are represented by symbolic names rather than actual bit codes. Such high-level symbolic names contribute to readability, ease of description, consistency and correctness.

- Flexible Performance Constraints. In the state description, you may specify performance requirements in the form of a maximum operating frequency or individual delays for one or more critical paths. You can specify maximum delays from inputs to outputs, from inputs to the state register (the setup times for the machine), from the state register to outputs, or from state register to state register (the operating frequency). To ensure meeting the performance requirements in the information actual system, about externalcircuit characteristics, such as how strongly the inputs are driven and how heavily loaded the outputs are, may also be specified.

- Flexible Clocking. You can have the machine change state on the rising or falling edge of the clock. You can also put latches on inputs and outputs, again clocked on either edge, to further control the timing of the machine's signals.

- Flexible Reset. You can specify which state to go to on reset, the initial values of the input and output latches on reset, and whether reset is active high or low.

- Simple Description. There are several options which can be used to further simplify the state machine description by minimizing the number of outputs whose values must explicitly be specified for each transition. For example, default values can be declared for outputs, whose values then need only be specified when they differ

from default. Outputs can also have RS flip-flops, with the effect that their values need only be specified when they change.

- Don't Cares. To enhance the quality of the optimization, don't care conditions can be explicitly specified.

- Intermediate Equations. To simplify the description, you can give intermediate logic equations for signals that are only used inside the machine, such as those that are fanned out to many places.

The State Machine Compiler can be used for either gate array or cell-based design, in a variety of technologies. From a single high-level description, output is available as a netlist of Portable primitives for implementation in a gate array or as standard cells, or as a custom-density layout block in the form of а. PLA. The high-level description is therefore technology-independent. It is easily migrated between implementation styles and process technologies.

Netlist Compilation and Advanced Optimization

Portability

Technology Indepen-

and

dence

When compiling a netlist, the State Machine Compiler Aggressively optimizes the logic for the target Portable library using several advanced techniques. Among them are

- PLA-like optimization,

- factorization into a multi-level network, and

|                                           | <ul> <li>application of library-dependent transformation rules,<br/>which ensures use of the most efficient gates available in<br/>the target library.</li> <li>The Compiler optimizes first with regard to speed, to meet<br/>your specifications, and then area. The resulting<br/>implementation is comparable to and often better than<br/>aggressively hand-optimized circuits, and is done in a fraction<br/>of the time, without error.</li> </ul>                                                                                                                                  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLA<br>Output<br>and<br>Optimi-<br>zation | The Compiler has a PLA Optimizer which can take a state<br>machine description and produce an optimized PLA code file<br>to implement the combinational logic for the state machine.<br>VLSI's PLA Optimizer can also take as input an<br>independently-generated bare PLA code file.                                                                                                                                                                                                                                                                                                      |

| Automatic<br>State<br>Assignment          | The State Machine Compiler performs automatic state<br>assignment (the assignment of bit codes to represent each state<br>in the state register), using a heuristic for further optimization.<br>The states can also be manually assigned if desired.                                                                                                                                                                                                                                                                                                                                      |

| High-Level<br>Model                       | The State Machine Compiler includes a high-level behavioral<br>model which serves as an interpretive facility for state machine<br>emulation and efficient simulation. You can directly simulate<br>your state machine in VTIsim from its description, without<br>actually synthesizing and optimizing the logic. This is useful<br>up-front during the design process for quickly checking out the<br>description. Special debug features are available, such as<br>feedback using the symbolic names. For example, the model<br>tells the name of the state it is in at any one instant. |

## VLSI Screener

Netlist Screener and Design Review Tool

#### **Overview**

VTIscreen, VLSI's Netlist Screener, analyzes your logic design and identifies gate or block-level electrical rule violations, for both gate array and standard cell designs. It also provides several design summary reports, including a utilization report for gate array designs.

VTIscreen can be run any time after the schematic netlist is created. You run it at least once before submitting a gate array design for placement and routing. You also run VTIscreen routinely earlier during the design process in order to keep track of your array utilization and to catch any errors as soon as possible. VTIscreen identifies connectivity errors and other potential problems.

VTIscreen also analyzes wire lengths and generates a back annotation file with either pre-route predictive capacitances or post-route actual capacitances. This file can then be used for back annotation in simulation or timing verification. A report comparing the actual to predicted capacitances is also produced.

Finally, VTIscreen interfaces to VTIvector, its companion vector screener and translator, by producing a file containing logical I/O signal information needed by that tool.

|                    | Features                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary<br>Reports | VTIscreen provides several summary reports. These include<br>design statistic and complexity reports, containing information<br>on number of interconnects, cell instances, gate equivalents,<br>and so forth, as well as a gate array utilization report on pad<br>and internal cell utilization, VTIscreen saves the reports in a<br>disk file as well as printing them on-screen. |

| Checking           | VTIscreen checks for certain connectivity errors and other<br>potential problems in your design, such as oddly or<br>dangerously connected or otherwise misused inputs, outputs,<br>parallel cells, clock buffers, pad drivers and level shifters.                                                                                                                                   |

| Back<br>Annotation | VTIscreen has a companion program that analyzes wire<br>lengths and generates a back annotation file in a variety of<br>formats, with either pre-route predictive capacitances or<br>post-route actual capacitances. The program also produces a<br>report comparing the actual to predicted capacitances.                                                                           |

|                    |                                                                                                                                                                                                                                                                                                                                                                                      |

Interactive or Batch Mode

58

You may use VTIscreen interactively or with command files, in either the graphics or terminal environments, from VLSI's text shell or terminal emulator window.

# Logic and Timing Verification Tools

# VLSI Timing Verifier

## Static Timing Analyzer

| 8 | DP                                                                                                                       | 🖬 VIIte                                                                                                                                                                                                                                                                                                                                                 | rminal 1.0                                                                                                                                                                                                                     | Dd                                                                                                                              |                              |                                                  |                                                 | shell    |

|---|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------|-------------------------------------------------|----------|

| r | 00                                                                                                                       | COUNTER                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                | [sc]                                                                                                                            | labnnb                       | [sc]                                             | labnst                                          | Compile! |

|   | LS 🚺                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                | [sc]                                                                                                                            | labnnn                       |                                                  | lacfnb                                          | DRCI     |

| F | F'                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                         | WITH I                                                                                                                                                                                                                         | [sc]                                                                                                                            | labnnt                       |                                                  | lacfnt                                          | extract! |

|   |                                                                                                                          | JK FF'                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                |                                                                                                                                 | labnsb                       |                                                  | lacfsb                                          | options  |

| L |                                                                                                                          | LATCHES                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                                                                                                                                                              | [sc]                                                                                                                            | labnsn                       | [sc]                                             | lacnnb                                          | <u> </u> |

|   | UI:<br>VTI:<br>VTI:<br>VTI:<br>VTI:<br>VTI:<br>VTI:<br>Tr:<br>Tr:<br>Tr:<br>Tr:<br>Tr:<br>Tr:<br>Tr:<br>Tr:<br>Tr:<br>Tr | cchnolog<br>ambda is<br>by ty [sc<br>ty 1.0d<br>aadNetLi<br>atwork 1<br>ty> set<br>ty> set<br>ty> show<br>acing 20<br>acing 20<br>acing 60<br>acing 60<br>acing 60<br>acing 60<br>acing 60<br>acing 60<br>acing 60<br>acing 80<br>acing 20<br>HRU u<br>13.3ns<br>THRU u<br>11.9ns<br>THRU u<br>df21.D<br>10.4ns<br>THRU u<br>10.2ns<br>THRU u<br>10.2ns | t cpu: 14<br>oaded, 23<br>clock clk:<br>clock clk:<br>critical<br>%<br>%<br>clock clk:<br>critical<br>%<br>%<br>%<br>cal cpu: 1<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>%<br>% | 3.0644<br>phantu<br>1 (10)<br>2 0(20)<br>START<br>(3.9)<br>df21.<br>START<br>(3.9)<br>START<br>(3.3)<br>START<br>(4.5)<br>START | DMS, 41 nodes, 90<br>) 0(30) | 21.0<br>df22.<br>df22.7<br>22.0<br>u22.7<br>32.0 | 5.<br>.D 8.4[5.4]<br>.D 8.4[5.4]<br>2N 7.0[4.6] | shell!   |

| Ľ | /TItv:                                                                                                                   | >                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                |                                                                                                                                 |                              |                                                  |                                                 | search   |

|   |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                |                                                                                                                                 |                              |                                                  |                                                 |          |

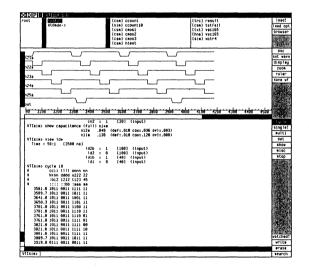

#### **Overview**

VTItv, VLSI's Timing Verifier, is a gate or block-level static timing analyzer for synchronous circuits. It is useful for a system designer who is designing a performance-critical circuit which is complex enough that verifying all timing purely using simulation would be difficult. No knowledge of transistor-level design is required. VTItv analyzes either the entire design at once, for global system checking, or certain paths as defined by the user, for more specific analysis.

VTItv does a static timing analysis. No input or case vectors are needed and no assertions need be added to the circuit for the analysis.

VTItv works with synchronous systems, systems that are composed of alternating stages of storage elements and combinational logic. For simplicity, system clocks are explicitly declared rather than derived.

VTItv is typically used to find and rectify potential timing problems after the overall functionality of the design has been verified with logic simulation. Identified critical nodes and paths can then be examined more closely during timing simulation, using actual data. These paths can also be weighted during physical design, to minimize wiring capacitances. VTItv assists you in filtering your design, so you can focus your attention on the most critical parts of the circuit.

VTItv can also be used to quickly re-verify designs which are ready for fabrication or which have been changed to a new technology. This is particularly useful when switching among gate arrays and cell-based technologies using VLSI's Portable Library.

#### Features

Flexible Analysis VTItv performs a flexible, extensive variety of analyses, on either the entire design at once or paths that you specify. These analyses include:

- Critical Paths. VTItv identifies the n most critical paths in your circuit, and reports the slack in non-critical paths.

- Cycle Time. VTItv identifies the minimum possible period for any clock, or the maximum operating frequency for your overall circuit, accurate to within a tolerance you specify.

- Delay. VTItv reports the delay along any particular path you specify. Delays waiting for clock transitions are taken into account.

- Longest Path. VTItv identifies the n "worst" paths from input to output of the entire circuit -- the paths with the greatest delay, that may limit the speed of the circuit and contribute to a critical path, or the paths with the least delay, which are used to check for hold time violations. Delays waiting for clock transitions are taken into account.

some control.