# RISC

# ACORN RISC MACHINE FAMILY DATA MANUAL

The

32-Bit RISC

Microprocessor

System

|   |  |  | , |

|---|--|--|---|

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

| i |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

| : |  |  |   |

|   |  |  |   |

|   |  |  |   |

| ACORN RISC MACHINE (ARM) FAMILY |

|---------------------------------|

| DATA MANUAL                     |

| _<br>_                          |

| _                               |

|                                 |

| <del></del>                     |

| _                               |

| <br>_                           |

| <del></del>                     |

| <del></del>                     |

Application Specific Logic Products Division

The information contained in this document has been carefully checked and is believed to be reliable. However, VLSI Technology, Inc., (VLSI) makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, it. VLSI does not guarantee that the use of any information contained herein will not infringe upon the patent or other rights of third parties, and no patent or other license is implied hereby.

This document does not in any way extend VLSI's warranty on any product beyond that set forth in its standard terms and conditions of sale. VLSI Technology, Inc., reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without notice.

#### LIFE SUPPORT APPLICATIONS

VLSI Technology, Inc., products are not intended for use as critical components in life support appliances, devices, or systems in which the failure of a VLSI Technology product to perform could reasonably be expected to result in personal injury.

Copyright © 1990 by VLSI Technology, Inc.

Published by Prentice-Hall, Inc.

A Division of Simon & Schuster

Englewood Cliffs, New Jersey 07632

This book can be made available to businesses and organizations at a special discount when ordered in large quantities. For more information, contact:

Prentice-Hall, Inc.

Special Sales and College Marketing

College Technical and Reference Division

Englewood Cliffs, N.J. 07632

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

PRENTICE-HALL INTERNATIONAL (UK) LIMITED, London

PRENTICE-HALL OF AUSTRALIA PTY. LIMITED, Sydney

PRENTICE-HALL CANADA INC., Toronto

PRENTICE-HALL HISPANOAMERICANA, S.A., Mexico

PRENTICE-HALL OF INDIA PRIVATE LIMITED, New Delhi

PRENTICE-HALL OF JAPAN, INC., Tokyo

SIMON & SCHUSTER ASIA PTE. LTD., Singapore

EDITORA PRENTICE-HALL DO BRASIL, LTDA., Rio de Janeiro

# **CONTENTS**

| ACORN RISC | MACHINE (ARM) DATA MANUAL                                  | PAGE<br>NUMBE |

|------------|------------------------------------------------------------|---------------|

| SECTION 1  | INTRODUCTION: THE RISC SYSTEM SOLUTION FOR SMALL COMPUTERS | 1-3           |

| SECTION 2  | VL86C010 - 32-BIT RISC MICROPROCESSOR                      | 2-3           |

|            | Description                                                |               |

|            | Signal Description                                         |               |

|            | Functional Description                                     |               |

|            | Examples of the Instruction Set                            |               |

|            | Instruction Cycle Operations                               |               |

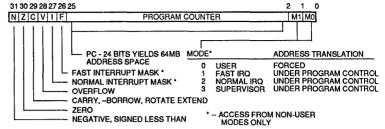

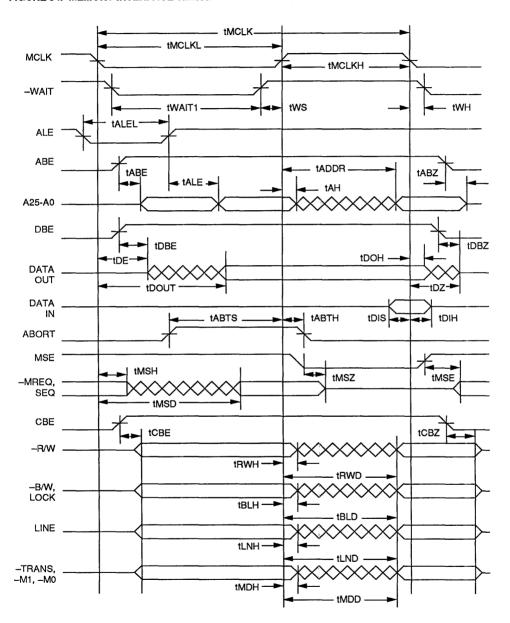

|            | Timing and AC Characteristics                              |               |

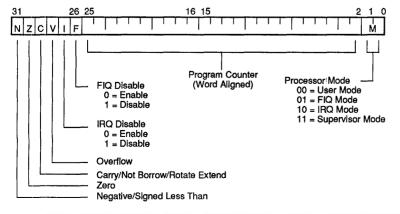

|            | RISC PROGRAMMER'S MODEL                                    | 2-25          |

|            | Byte Significance                                          |               |

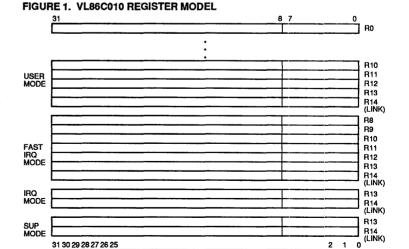

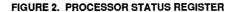

|            | Registers                                                  | 2-25          |

|            | Exceptions                                                 |               |

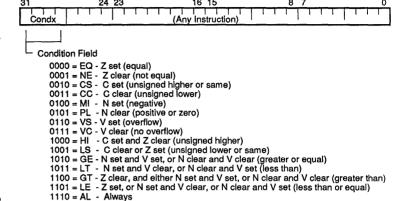

|            | Instruction Set                                            |               |

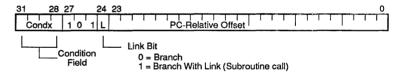

|            | Branch, Branch-and-Link (B, BL)                            |               |

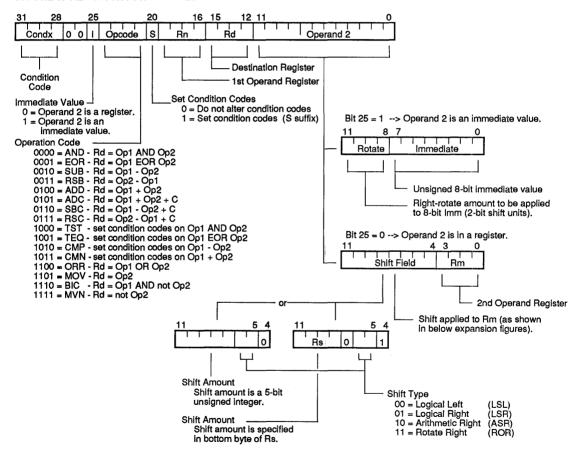

|            | ALU Instructions (AND, EOR, SUB, RSB, ADD, ADC, SBC,       |               |

|            | RSC, TST, TEQ, CMP, CMN, ORR, MOV, BIC, MVN)               | 2-31          |

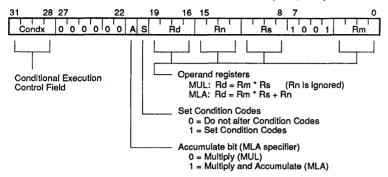

|            | Multiply, Multiply-Accumulate (MUL, MLA)                   |               |

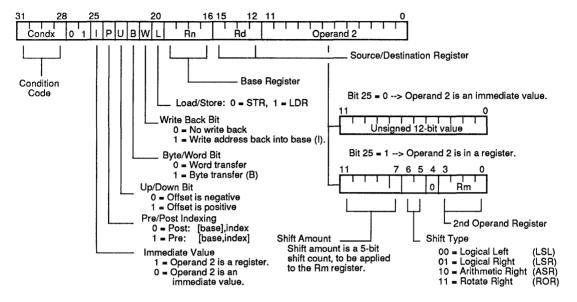

|            | Load/Store Value from Memory (LDR, STR)                    | 2-37          |

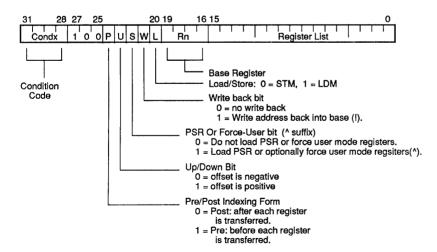

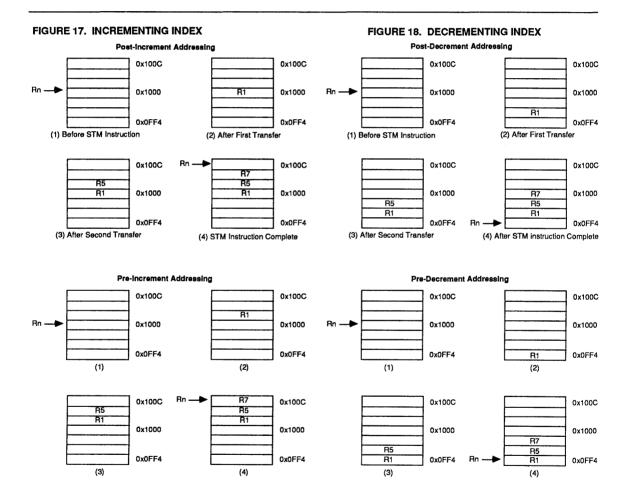

|            | Load/Store Register List (LDM, STM)                        |               |

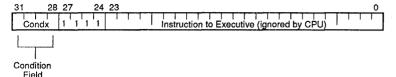

|            | Software Interrupt (SWI)                                   |               |

|            | Coprocessor Data Operations (CPD)                          |               |

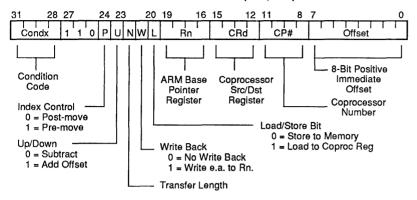

|            | Coprocessor Load/Store Data (LDC, STC)                     | 2-45          |

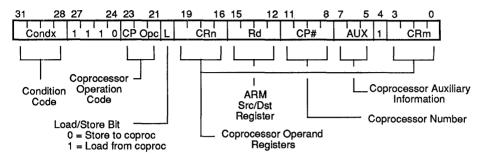

|            | Coprocessor Register Transfer (MCR, MRC                    |               |

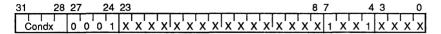

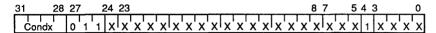

|            | Undefined (Reserved) Instructions                          |               |

|            | Instruction Set Summary (and Examples)                     |               |

|            | Appendix A                                                 |               |

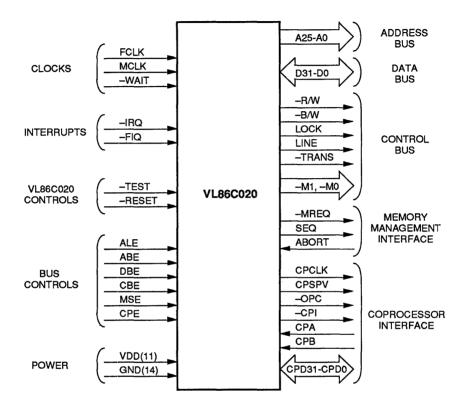

| SECTION 3  | VL86C020 - 32-BIT MICROPROCESSOR WITH CACHE MEMORY         |               |

|            | Description                                                |               |

|            | Signal Description                                         |               |

|            | RISC PROGRAMMER'S MODEL                                    |               |

|            | Byte Significance                                          |               |

|            | Registers                                                  |               |

|            | Exceptions                                                 |               |

|            | Instruction Set                                            |               |

|            | Branch, Branch-and-Link (B, BL)                            | 3-16          |

|            | ALU Instructions (AND, EOR, SUB, RSB, ADD, ADC, SBC,       |               |

|            | RSC, TST, TEQ, CMP, CMN, ORR, MOV, BIC, MVN)               |               |

|            | Multiply, Multiply-Accumulate (MUL, MLA)                   |               |

|            | Load/Store Value from Memory (LDR, STR)                    | 3-25          |

|            | Load/Store Register List from Memory (LDM, STM)            |               |

|            | Single Data Swap (SWP)                                     |               |

|            | Software Interrupt (SWI)                                   |               |

|            | Coprocessor Data Operations (CDO)                          |               |

|            | Coprocessor Data Transfers (LDC, STC)                      | 3-36          |

|            | Coprocessor Register Transfers (MCR, MRC)                  |               |

|            | Undefined (Reserved) Instructions                          |               |

|            | Instruction Set Summary (and Examples)                     |               |

|            | CACHE OPERATION                                            |               |

|            | Read/Write Operations                                      | 3-44          |

|            | Cache Validity                                             | 3-44          |

|            | Non-cachable Areas of Memory                               | 3-44          |

|            | Doubly Mapped Space                                        |               |

|            | Control Registers                                          |               |

|            | VL86C020 Memory Timing                                     |               |

## **CONTENTS**

| ACORN RISC | MACHINE (ARM) DATA MANUAL                              | NUMBER |

|------------|--------------------------------------------------------|--------|

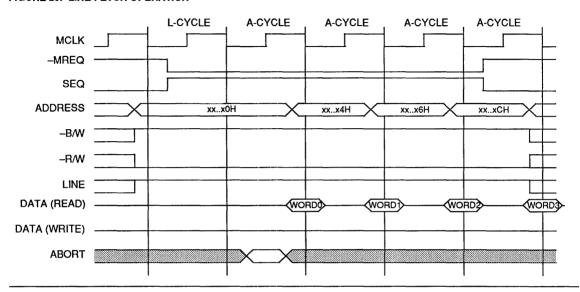

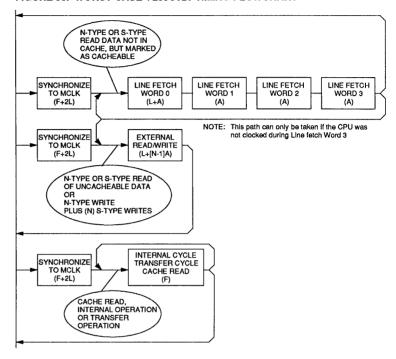

|            | Cycle Types                                            | 3-48   |

|            | Data Transfer                                          |        |

|            | Byte Addressing                                        |        |

|            | Locked Operations                                      |        |

|            | Line Fetch Operations                                  |        |

|            | Address Timing                                         |        |

|            | Virtual Memory Systems                                 |        |

|            | Stretching Access Times                                |        |

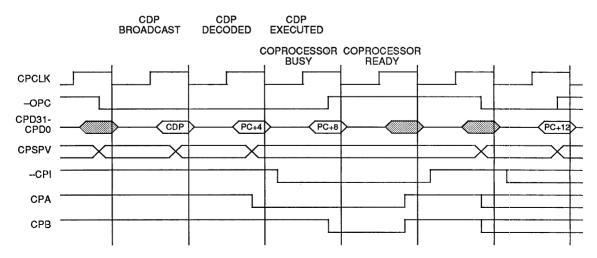

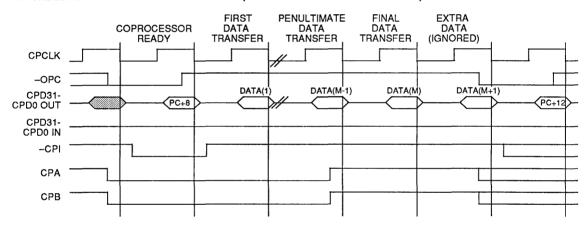

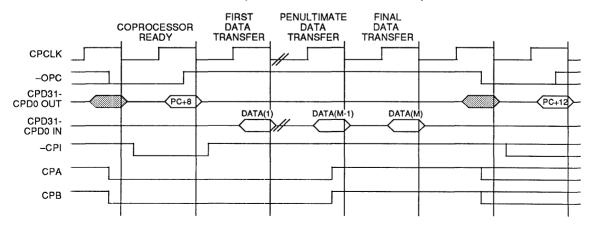

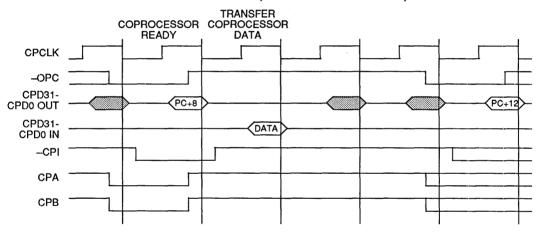

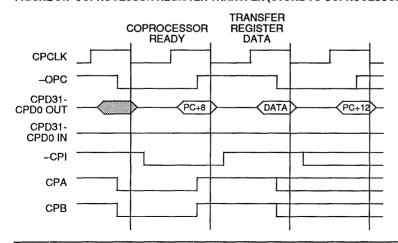

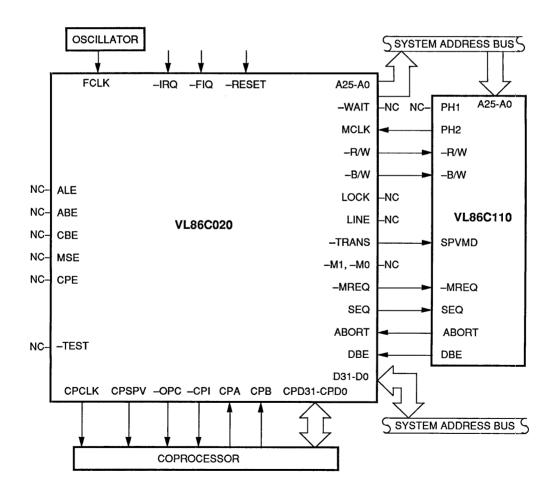

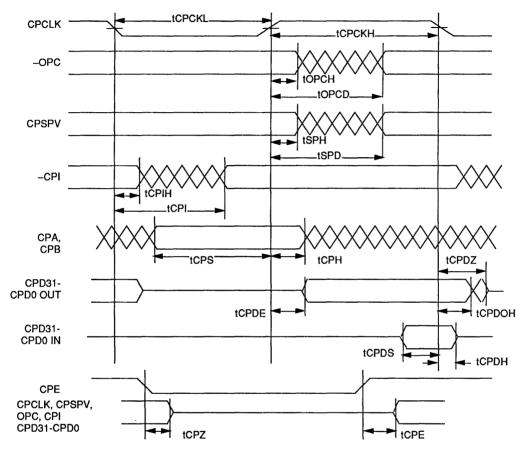

|            | Coprocessor Interface                                  |        |

|            | Data Transfer Cycles                                   |        |

|            | Register Transfer Cycle                                |        |

|            | Privileged Instructions                                |        |

|            | Repeatability                                          |        |

|            | Undefined Instruction                                  |        |

|            | VL86C020 Instruction Cycles                            |        |

|            | Instruction Tables                                     |        |

|            | Software Interrupt and Exception Entry                 |        |

|            | Coprocessor Data Operation                             | 3-60   |

|            | Coprocessor Data Transfer                              |        |

|            | Coprocessor Data Transfer (From Coprocessor to Memory) |        |

|            | Coprocessor Data Transfer (Load from Coprocessor)      |        |

|            | Coprocessor Data Transfer (Store to Coprocessor)       |        |

|            | Undefined Instruction and Coprocessor Absent           |        |

|            | Instruction Speeds                                     |        |

|            | Cache Off                                              |        |

|            | Cache On                                               |        |

|            | Compatibility with Existing Arm Systems                |        |

|            | Test Conditions                                        |        |

|            | AC Characteristics                                     |        |

|            | Absolute Maximum Ratings                               |        |

|            | DC Characteristics                                     | 3-73   |

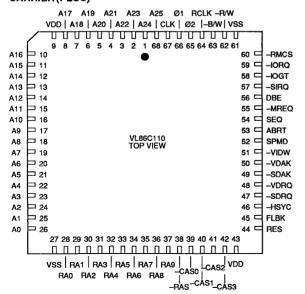

| SECTION 4  | VL86C110 - RISC MEMORY CONTROLLER                      | 4-3    |

|            | Description                                            | 4-3    |

|            | Signal Description                                     | 4-5    |

|            | Functional Description                                 | 4-8    |

|            | Memory Pages                                           | 4-8    |

|            | Master/Slave Configuration                             | 4-8    |

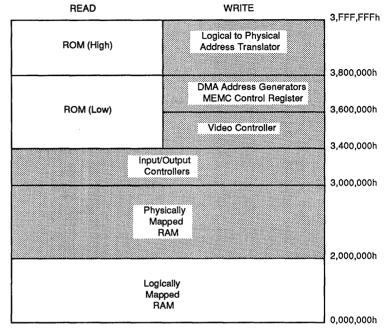

|            | Memory Map                                             | 4-8    |

|            | Logically Mapped RAM                                   | 4-8    |

|            | Physically Mapped RAM                                  | 4-9    |

|            | I/O Controllers                                        |        |

|            | ROM                                                    | 4-9    |

|            | DMA Address Generators                                 | 4-9    |

|            | Logical-Physical Translator                            | 4-9    |

|            | Effect of Reset                                        | 4-9    |

|            | Access Times                                           |        |

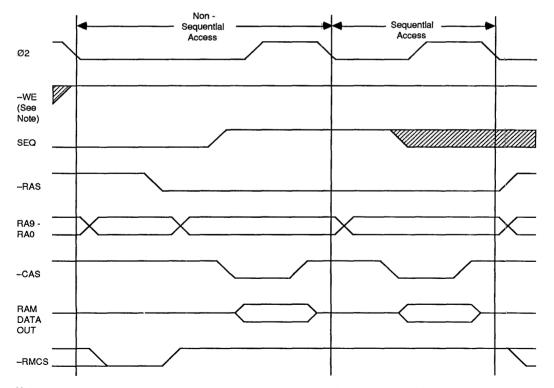

|            | N-Cycles and S-Cycles                                  | 4-10   |

|            | Processor Interface                                    |        |

|            | DMA Address Generators                                 | 4-16   |

|            | DMA and Memory Arbitration                             |        |

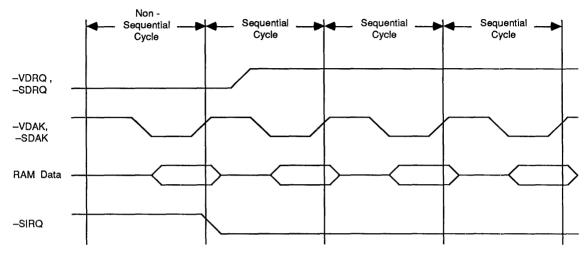

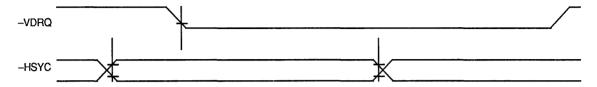

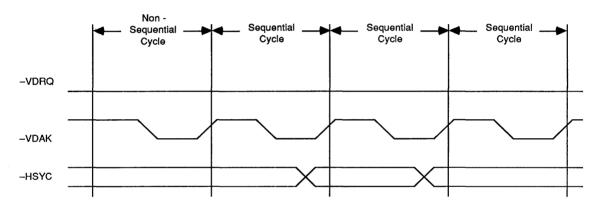

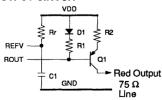

|            | Video Controller (VIDC) Interface                      | 4-20   |

|            | I/O Controller Interface                               |        |

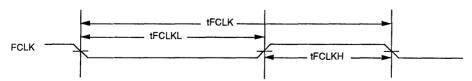

|            | Timing and AC Characteristics                          |        |

|            | -                                                      |        |

# CONTENTS

| ACORN RISC | MACHINE (ARM) DATA MANUAL                       | PAGE<br>NUMBER |

|------------|-------------------------------------------------|----------------|

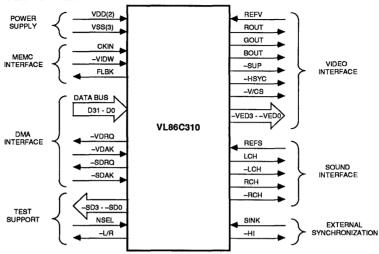

| SECTION 5  | VL86C310 - RISC VIDEO CONTROLLER                | 5-3            |

|            | Description                                     | 5-3            |

|            | Signal Description                              |                |

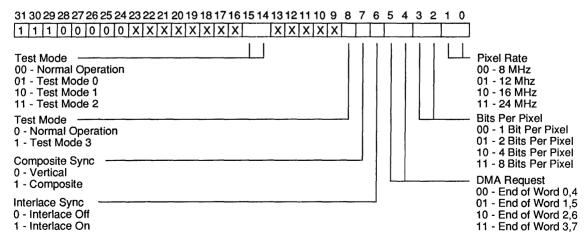

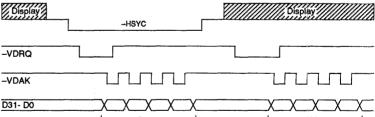

|            | Functional Description                          | 5-7            |

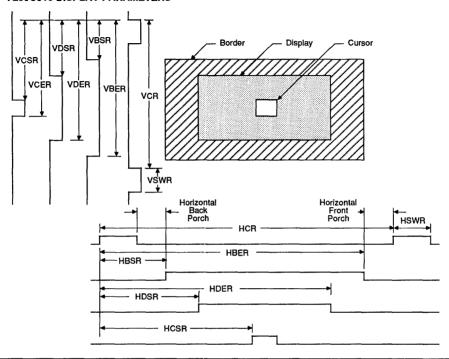

|            | Using the VIDC                                  | 5-13           |

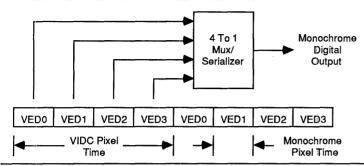

|            | Display Formats                                 | 5-15           |

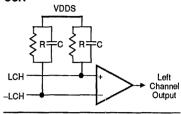

|            | Sound System                                    | 5-17           |

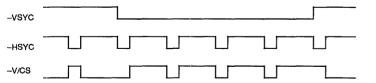

|            | Timing and AC Characteristics                   | 5-19           |

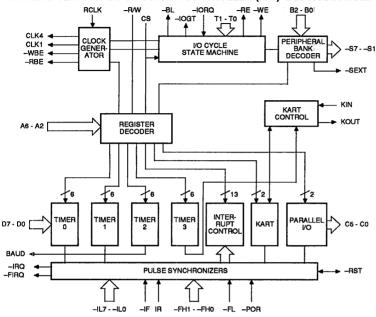

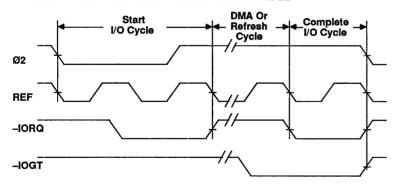

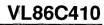

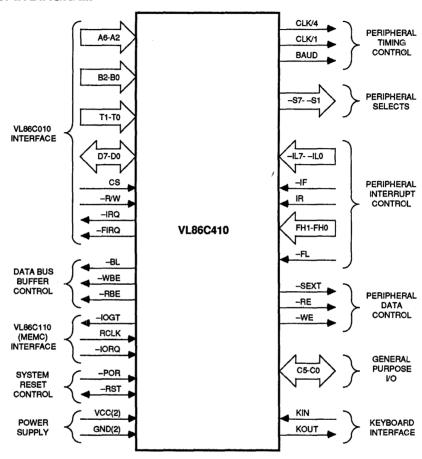

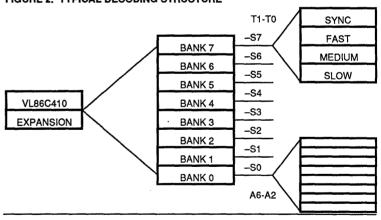

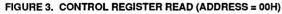

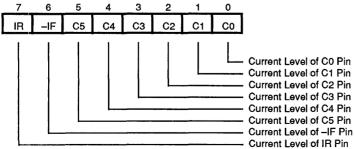

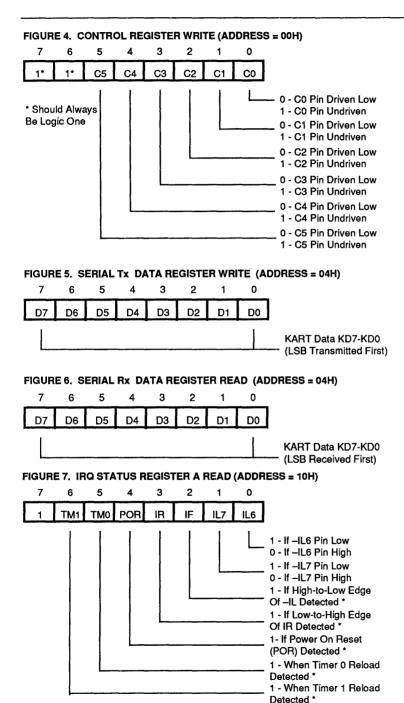

| SECTION 6  | VL86C410 -RISC I/O CONTROLLER                   | 6-3            |

|            | Description                                     |                |

|            | Signal Description                              | 6-5            |

|            | Functional Description                          | 6-8            |

|            | Internal Registers                              | 6-8            |

|            | External Peripherals                            | 6-12           |

|            | Timing and AC Characteristics                   | 6-15           |

| SECTION 7  | RISC DEVELOPMENT TOOLS OVERVIEW                 | 7-3            |

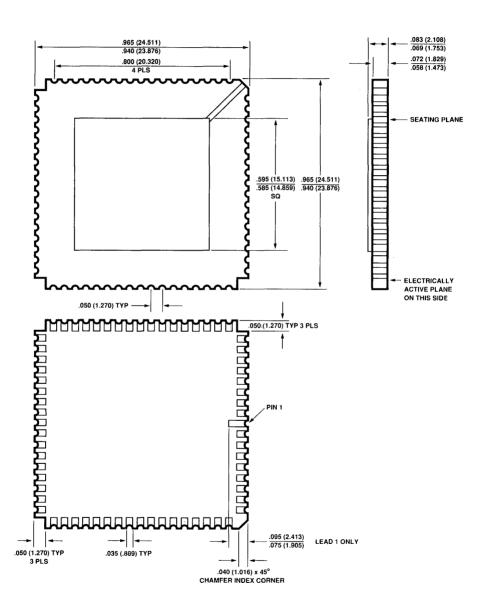

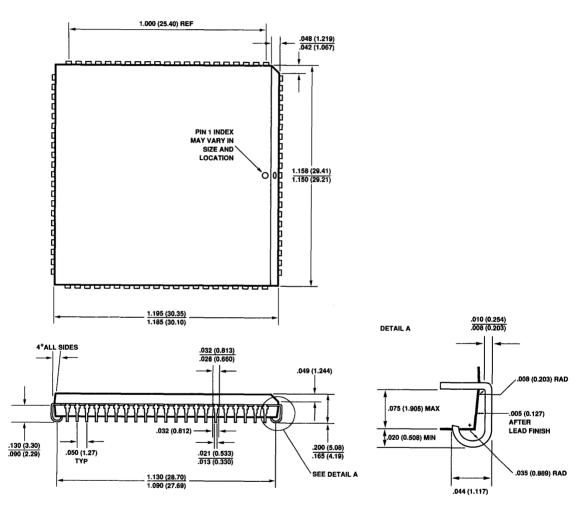

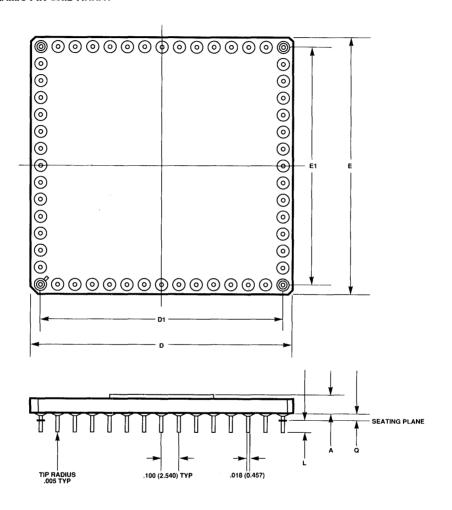

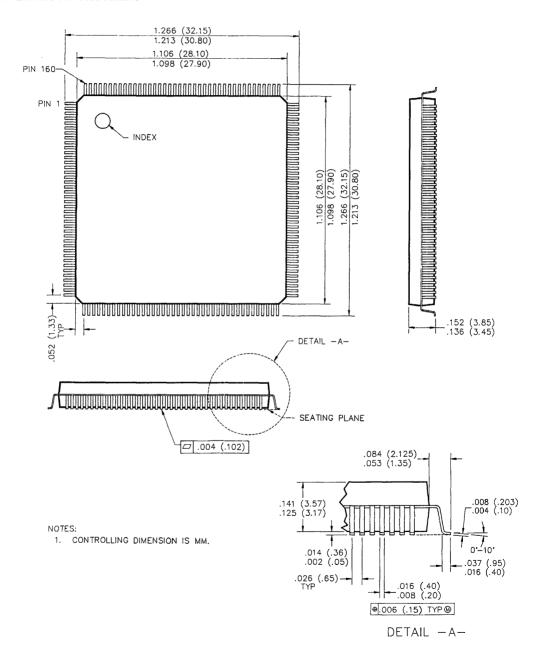

| SECTION 8  | PACKAGING INFORMATION                           | 8-3            |

|            | 68-Pin Plastic Leaded Chip Carrier (PLCC)       |                |

|            | 84-Pin Plastic Leaded Chip Carrier (PLCC)       |                |

|            | 144-Pin Ceramic Pin Grid Array                  | 8-5            |

|            | 160-Pin Ceramic Pin Grid Array                  |                |

| SECTION 9  | SALES OFFICES, DESIGN CENTERS, AND DISTRIBUTORS | 9-3            |

| CONTENTS                                                |

|---------------------------------------------------------|

| INTRODUCTION – ACORN RISC MACHINE                       |

| VL86C010 – 32-BIT RISC MICROPROCESSOR                   |

| VL86C020 – 32-BIT RISC MICROPROCESSOR WITH CACHE MEMORY |

| VL86C110 – RISC MEMORY CONTROLLER                       |

| VL86C310 – RISC VIDEO CONTROLLER                        |

| VL86C410 - RISC I/O CONTROLLER                          |

| RISC DEVELOPMENT TOOLS OVERVIEW                         |

| PACKAGINGINFORMATION                                    |

|                                                         |

SALES OFFICES, DESIGN CENTERS, AND DISTRIBUTORS

This book provides the reader with an in-depth and concise reference on the VLSI Technology, Inc. VL86C010 RISC system product. The RISC microprocessor and three RISC peripherals described in this text are both world-class and international. They were designed in the United Kingdom by Acorn Computer Ltd., using VLSI Technology, Inc. design tools, and are presently manufactured in the United States by VLSI. In addition, under recently signed alternate sourcing agreement, Sanyo, Ltd., will both manufacture the VL86C010 RISC family in Japan and develop derivative product.

In addition to a detailed hardware description of each device, this text extensively examines the software aspect of RISC Architecture. The instruction set is thoroughly explained, with numerous examples shown of programming techniques. Most readers who have some programming experience, whether familiar with existing "standard" microprocessors or not, should quickly understand programming in VLSI RISC system environment.

Except for the cover and VLSI logo, this book was entirely produced using desktop publishing. To maximize the desktop publishing program's usefulness, this text was produced using a preceding minus (–) sign rather than an overbar or asterisk to indicate a complemented signal.

| SECTION 1 INTRODUCTION - ACORN RISC MACHINE |

|---------------------------------------------|

|                                             |

|                                             |

Application Specific Logic Products Division

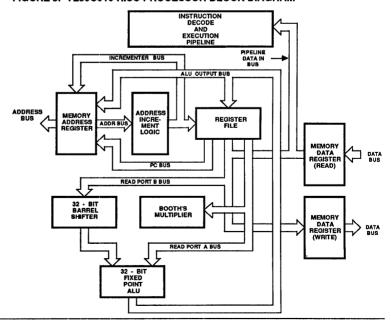

## 32-BIT RISC MICROPROCESSOR FAMILY

## THE RISC SYSTEM SOLUTION FOR SMALL COMPUTERS

## INTRODUCTION

Perhaps the most important topic in the computer industry the past few years has been the emergence of the Reduced Instruction Set Computer (RISC) touted as the next generation of performance oriented architectures. Several different suppliers - both component and system - have announced new computers based on the RISC design methodology. All claim that RISC offers much higher performance than more traditional Complex Instruction Set Computers (CISC). The common denominator among these suppliers has been a systems approach to the CPU design problem, in other words, the CPU is considered as a single unit. When multi-chip solutions are involved (as most are), interfaces are defined around performance and bandwidth requirements more than functional blocks, the partitioning found in most commercial microprocessors today. Component suppliers often partition their systems around functions, like scalar processor, memory management unit, and floating point processor. This allows each circuit to be used without the others, meaning that not all components have to be available before sales start. By partitioning around functions, the component suppliers usually sacrifice performance or require other system elements, such as memory, be faster than necessary at a given performance level.

As RISC technology moves from the laboratory into the commercial environment it is important for system designers to understand these new considerations. When new applications arise that cannot be addressed cost-effectively by CISC architectures, this new technology may provide the only solution. By examining the following system, the designer will become familiar with this new, emerging computer technology and learn how systems can be partitioned around parameters other than functional blocks.

## Brief Evolution of CISC and RISC Architectures

Most commercially available computers today should be classified as CISC. Many of these machines have existed for more than a decade, and have their foundation in technology that was radically different from today. When most existing machines began, logic and memory were expensive. In addition, software development was limited by the programming ability of assembler language and lack of efficient high-level language compilers. Early system designers were forced to heavily encode their limited instruction sets to minimize memory requirements of the system. Many processors began. with what was then considered as large, address spaces of 64K words/bytes of memory. Of course 64K words of assembler language code did represent a very large programming effort at the time.

Higher integration in semiconductor technology brought down the high cost of logic and memory. Soon, computer architects found they could build an equivalent system cheaper, with lower power requirements, and having more reliability. Also, integration allowed them to add enhancements to the instruction set to improve performance of key customer applications for less cost than before. Assembler language programmers wanted more enriched addressing modes that moved some of the computing functions from software to hardware. In addition, it improved programmer productivity by reducing the number of lines of assembler language necessary to code programs. Less lines per function meant more functions could be coded in the same time - i.e. higher productivity. Highlevel languages were available but generally were too inefficient to use except in the most complex applications level.

Hardware designers began adding new instructions and addressing modes to meet the programmer requests while remaining compatible with previous generations of software. Soon, system architects realized that they could provide more performance if they could sacrifice backwards compatibility and redefine their instruction sets to exploit new technologies. Instruction complexity had increased to the point where decoding multi-word, multi-format instructions was the limiting factor in

processor speed. Unfortunately, customers had huge investments in software and were reluctant to change to hardware that could not execute their installed base. New architectures were limited to new customers and applications.

High-level language efficiency and hardware performance improved dramatically and became useful for most applications. This helped two areas of concern in computer systems. programmer productivity and program transportability. High-level languages helped programmers write code that was hardware independent, at least in theory, as compilers stood between the programmer and the execution environment (physical hardware and operating system). Compiler differences and ambiguous language specifications caused some portability problems, but in general it was practical to port programs between machines.

With more high-level language programs being written, hardware suppliers felt pressured to add even more complication to their instruction sets to support compiled code. Many architectures added hardware implementations of high-level constructs like FOR, WHILE, and PROC (procedure calls) directly into the instruction set. The problem arose as to which language to support because each is different, e.g. whether the conditional execution expression is evaluated at the beginning of the loop or the end. As a result, most architectures may support only one language well or are so general that the compiler cannot exploit them efficiently (Wulf, 1981).

In the mid-seventies computer scientists began to investigate new methods to support all high-level languages more efficiently. It was becoming apparent that most problems were too complex to be written in assembler language and no one high-level language was sufficient to support all applications. From these development efforts came the RISC methodology for CPU design. What constitutes a RISC computer is yet another area of debate, but most emerging machines do have some characteristics in common.

First, most RISC machines are based on single-cycle instruction execution. Unlike their Complex Instruction Set Computers (CISC) counterparts that may take up to 100 minor (clock) cycles to complete complex instructions, the RISC machines instruction set is limited to primitive functions that can execute in a single or extremely few machine cycles. Compiler writers have suggested that it is more efficient to provide primitives to build solutions rather than solutions in the instruction set. When instructions have too much semantic content, a clash occurs between the language and the instruction set (Wulf. 1981) introducing inefficiency and increasing compiler complexity. In addition, single clock execution helps lower interrupt latency, thus making the system more responsive to the asynchronous environment of today's timeshared and/or networked systems.

Another common trait of RISC machines is a load/store architecture providing larger CPU register files. In a load/store architecture, the data processing instructions (logical and numeric functions) can only operate on the CPU registers. A separate set of instructions are used for memory reference that usually support a limited set of addressing modes. Streamlining the addressing modes helps simplify instruction decode, eliminate specialpurpose address ALUs, and speed pipeline processing that can be slowed by multi-word address operand fetches. Recent improvements in the global register allocation problem faced by compilers have made efficient use of large numbers of registers possible. In response to compiler improvements. most RISC systems have added larger register files to improve performance. Two factors bring about significant performance increases from added registers: (1) register operations execute much faster, and (2) memory references are reduced because registers can hold temporary results.

In general, RISC machines are tightly coupled to their memory. The simple instruction set translates into a higher effective instruction execution rate, meaning the processors demand a high bandwidth from their memory systems to provide peak performance. In order to provide this bandwidth most, but not

all, systems have implemented very sophisticated caching techniques which increase system cost and complexity dramatically.

## The VLSI Technology RISC Computer System

VLSI Technology has a full system solution to the design of a costeffective, small computer. This system was designed by Acorn Computers Ltd. of Cambridge, United Kingdom, using the VLSI Technology, Inc. CAD system. What makes this system different is its unique method of partitioning the four circuits. Instead of designing the circuits around self-contained functions. this system is partitioned around basic computer fundamentals such as memory bandwidth, die size of all four components, and low-cost packaging available today. Careful attention to these fundamentals has yielded a small computer system that can bring excellent performance to the user at significantly lower cost than ever before. An examination of the system and its alternate form of partitioning will highlight the advantages of a top down design approach to the entire problem, not just CPU optimization.

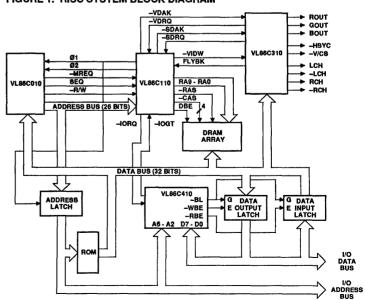

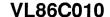

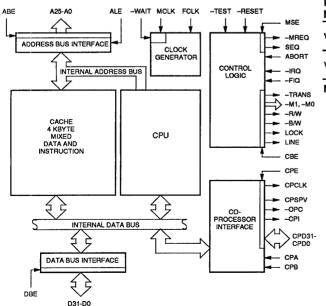

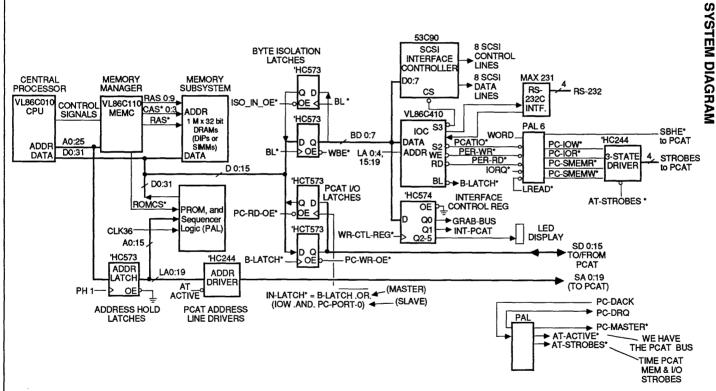

The computer shown in Figure 1 is partitioned into four circuits: the

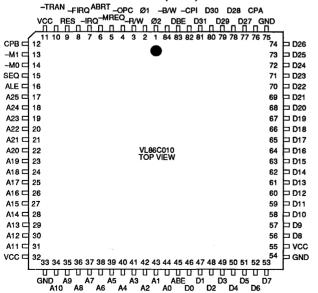

VL86C010 Acorn RISC Machine (ARM) processor, VL86C110 Memory Controller (MEMC), VL86C310 Video Controller (VIDC), and VL86C410 I/O Controller (IOC). These four circuits together form a full 32-bit microcomputer system with performance in the 5 to 6 millioninstructions-per-second (MIPS) range. Somewhat surprising is the fact that the four parts are available in one 84-pin (processor) and three 68-pin packages (JEDEC Type-B or Plastic-Leaded-Chip-Carriers, PLCC) while implementing full 32-bit functions. A more surprising fact is that no part in the system has a die size larger than 230 mils square in VLSI Technology's 2 µm double-layer metal CMOS process which means highly manufacturable circuits are available.

### **Partitioning The System**

Traditionally, component designers viewed a computer system as "centered" around the CPU. The processor was designed in a vacuum, without concern for other elements in the system. The CPU was optimized to be high-performance and then the system designers found that in order to exploit the performance, they had to resort to expensive memory systems or cache sub-systems, increasing the cost

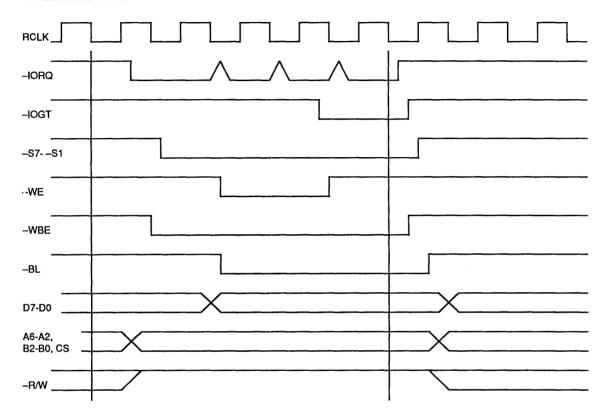

#### FIGURE 1. RISC SYSTEM BLOCK DIAGRAM

dramatically. The CPU made such high demands on the memory that I/O transactions were not sufficiently served. This forced the systems designer to implement ever more complex I/O sub-systems, yet another

addition to cost, complexity, and decreased reliability. Even today's most popular personal computers use plug in cards with on-board memory sub-systems for video and data communications.

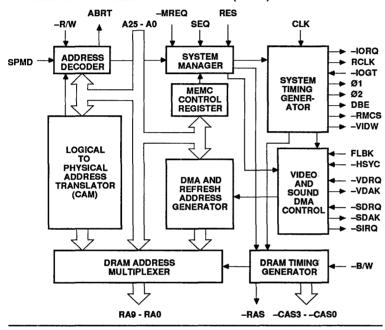

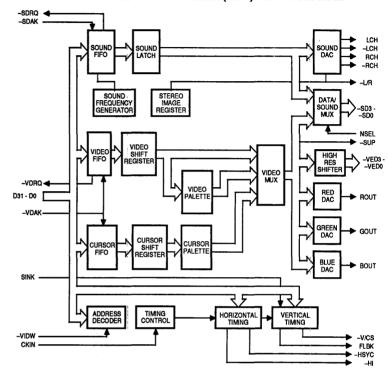

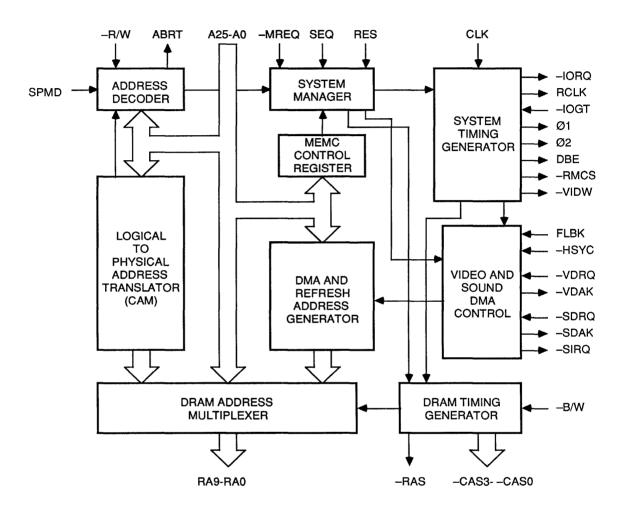

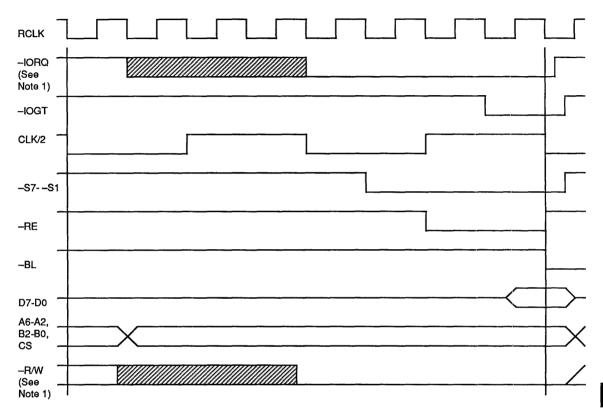

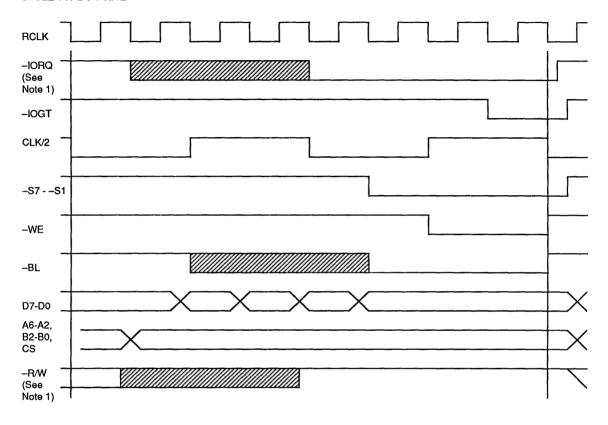

#### FIGURE 2. VL86C110 MEMORY CONTROLLER (MEMC) BLOCK DIAGRAM

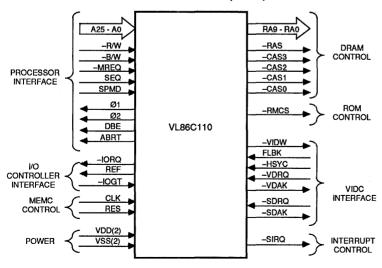

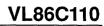

FIGURE 3. VL86C110 MEMORY CONTROLLER (MEMC) PIN DIAGRAM

The requirements for a small computer today, are very much different than even a few years ago. Now users expect a small computer to have capabilities that were only available in minicomputers. Full color displays at resolutions up to 640 by 480, real memory of 1 Mbyte, and networking support are common features demanded by end-users.

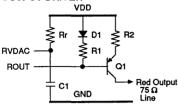

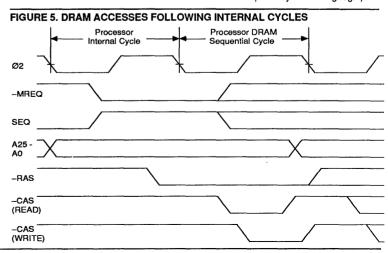

The VLSI Technology, Inc. system is "centered" around the memory, with each element designed to use the bandwidth efficiently without making large demands that require premium memory components. The video display is integrated into the design to utilize the main memory for display area, eliminating the need for expensive add-on video cards. The system operates with a 24 MHz clock that yields a basic processor cycle of 8 MHz (125 ns). Even at this speed, the memory system uses inexpensive 120 ns access time page-mode DRAMs.

# Memory Controller Functions Since the system is designed around the memory, it is logical that the VL86C110 Memory Controller (MEMC) should be discussed first. Understanding how this part functions provides insight into the other elements and how they are coordinated together.

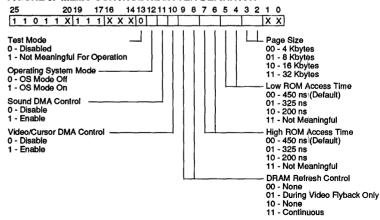

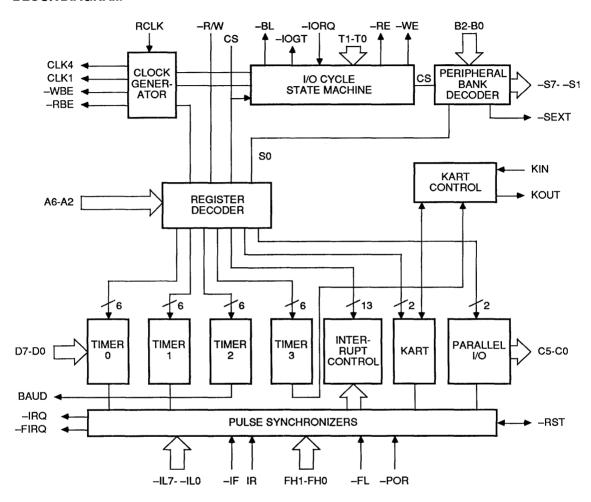

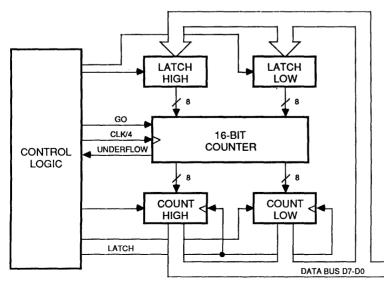

As the name would indicate, the MEMC generates the timing and control signals required by DRAM. In addition, MEMC acts as the main interface between the other three components by providing the critical timing signals for all elements from a single clock input. Figure 2 shows a block diagram and Figure 3 the functional pin out of the memory controller. It should be noted that MEMC does not have a data bus connection allowing it to be placed in a 68-pin package. To program the internal registers of MEMC, the data is encoded on the address bus during a processor write to the part. While at first this may seem a large overhead, using the simple/fast addressing modes and barrel shifter in the processor, the programmer will find that the address encoding causes very little impact.

The part generates all the timing signals required for interfacing the elements with the memory. High speed timing is generated from a single clock, usually 24 MHz for an 8 MHz processor. All

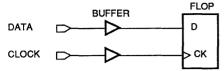

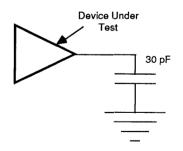

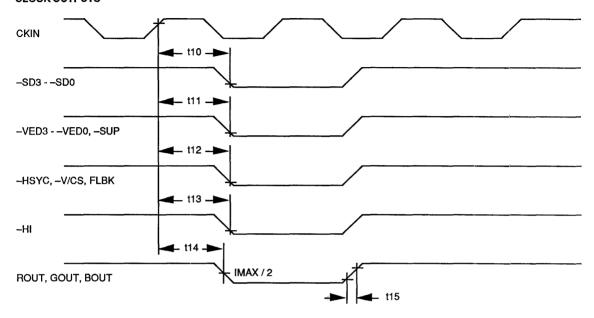

#### FIGURE 4. CLOCK SKEW TIMING EXAMPLE

Minimim Setup Time = Flop Setup Time + Data Buffer Maximum - Clock Buffer Minimum

Minimum Hold Time = Floo Hold Time + Clock Buffer Maximum - Data Buffer Minimum

system timing is generated on the MEMC with minimal buffering on the other devices. This scheme minimizes clock skew in the system allowing slower access time memory devices to be used. Figure 4 shows an example of how clock skew occurs in timing paths. Having all buffers on a single chip allows delays to track more closely than the total process variation. As shown by the example, fewer buffers in the path lower the amount of time that data must be valid on the bus, minimizing setup and hold times. Removing the clock buffer will eliminate the difference between the clock buffer delay minimum and maximum times.

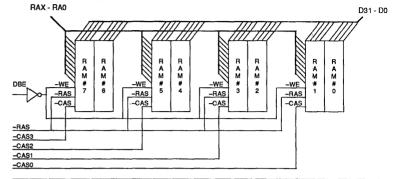

The clock is divided by three and used to generate the processor and main system bus reference clocks. The MEMC drives up to 32 memory parts directly in several different configurations. Various configurations provide for up to 4 Mbytes of real memory in the system. The bandwidth of the low-cost DRAM memory is increased through extensive use of page-mode transfers because many memory references in computer systems are sequential in nature. MEMC also provides memory map decoding for I/O and ROM in the system. In order to optimize bandwidth, MEMC will take the ROM chip select active at the beginning of every nonsequential access and remove it if the cycle is not a ROM access making slower ROM accesses more efficient and once again allowing lower-cost ROMs to used.

MEMC supports several key functions in the system that usually have a tendency to impact performance or require faster components, so that this is not the case in this system. If a small computer is to support networking it must provide for multi-tasking and

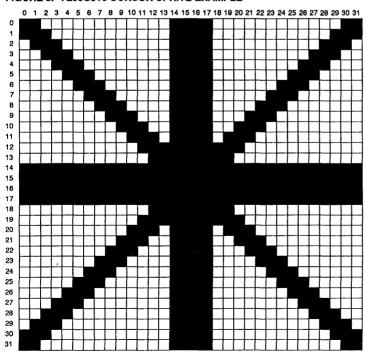

process isolation. MEMC provides full virtual memory support with a Logicalto-Physical Address Translator implemented as a 128 entry content addressable memory (CAM). Logical pages can be 4K, 8K, 16K, or 32K bytes each. RAM memory is always treated as 128 physical pages, meaning that MEMC contains a CAM entry (descriptor) for each physical page in memory. Having a CAM location for every physical page of memory eliminates descriptor thrashing, thus improving system performance. Thrashing occurs when the MMU system has fewer descriptors than physical pages of memory which introduces another source of address translation misses - the data is resident in memory but a descriptor to translate to that page is not available. A descriptor must be taken from another page to point to the requested page.

Many current memory management units contain only a small sub-set of the page tables and must retranslate the logical address whenever a new logical page is referenced (descriptor miss). Translation can take up to several microseconds depending on how many memory cycles must be performed. In this system the address translation is not in the critical path and does not require faster memory than a system that uses physical addresses. No translation takes place on the row address values which are required early in the memory cycle. The mapped address bits are placed into the column address field and are therefore not needed until much later in the cycle. This approach can be taken because the memory is usually configured as a single bank meaning all memories are active when the RAS becomes active regardless. Systems that have more than one bank of DRAM and use this

approach would be required to select (bring RAS active) all memory devices on every cycle. Multi-bank memory systems designed in this manner would have much higher power consumption and lose much of the advantage of DRAM technology.

The simple CAM contained in MEMC can support demand paging with some software assistance and it provides a full virtual memory implementation with three levels of access protection efficiently. The goal of virtual memory support in this system was to let programs be written independent of real memory size rather than for multi-user support. Today's most popular PC has suffered recently due to the artificial real memory limitation placed on it by the machine designers.

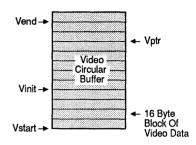

MEMC contains all the address generators to support DMA activity related to video, cursor, and sound generation. These were placed on this circuit for two reasons. First, it eliminates the need to have the full address bus placed on the video interface circuit. This allows the VIDC to have the full 32-bit data bus and still be packaged in a 68-pin package. Second, this arrangement uses the memory bandwidth more efficiently by reducing synchronization and buffer delays on the memory bus while improving DMA latency. In most systems a DMA operation proceeds as follows: (1) the DMA device requests a transfer, (2) the memory controller synchronizes to the system clock and recognizes the request, (3) processor is signaled to relinquish the bus. (4) processor synchronizes and recognizes the request, (5) processor issues grant to memory controller, (6) memory controller synchronizes and recognizes grant, (7) memory controller issues DMA grant, (8) DMA synchronizes and recognizes grant, (9) DMA device enables address bus drivers, (10) memory controller receives address and multiplexes address to memory devices, (11) memory controller issues data acknowledge, (12) DMA device synchronizes and recognizes acknowledge, and (13) DMA device removes request to end cycle.

MEMC provides the memory arbitration and all address sources in a single

device within the system. This eliminates several levels of pulse synchronizers and buffering delays. When the VIDC signals a DMA request, MEMC only has to recognize the request, disable the processor when appropriate, and enable the address from the internal source. The DMA device has a simple interface to latch the data when the acknowledge signal goes inactive. This interface provides a very efficient DMA capability for read-only devices like video and sound generators. In order to optimize bandwidth usage, MEMC performs four memory cycles

per DMA request, one full access taking 250 ns and three sequential page-mode accesses of 125 ns each. Four cycle bursts were chosen for all devices to increase bandwidth but keep bus latency to a reasonable value. Long latency introduces other costly problems that are usually solved with expensive FiFO buffers or other interface hardware that is duplicated in every device that connects to the bus.

RISC Processor Functions

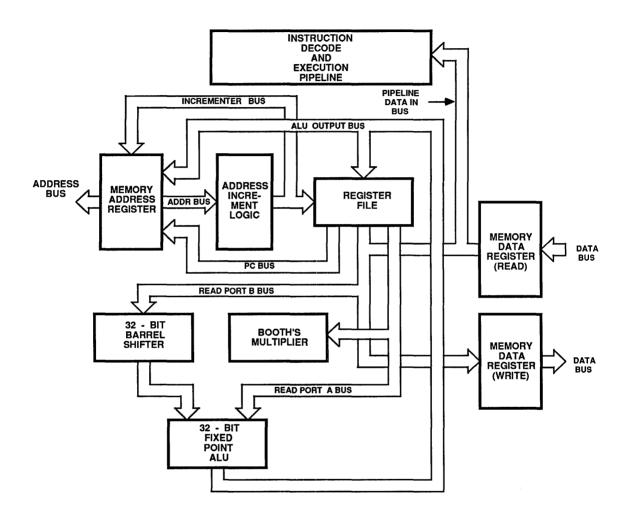

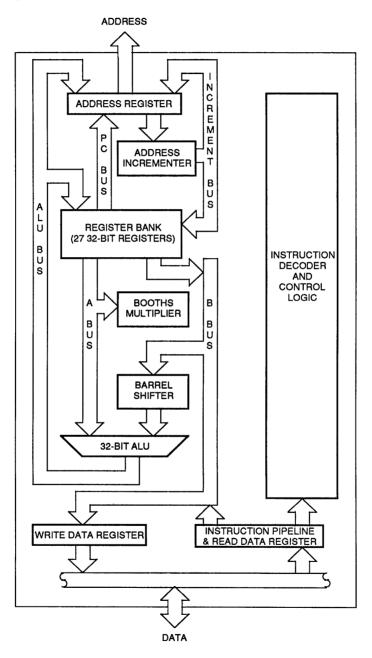

The VL86C010 RISC processor

provides the computational element in

the system. The processor has a

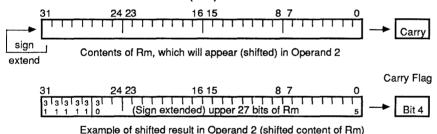

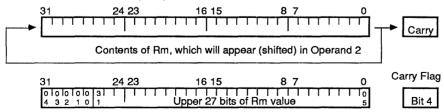

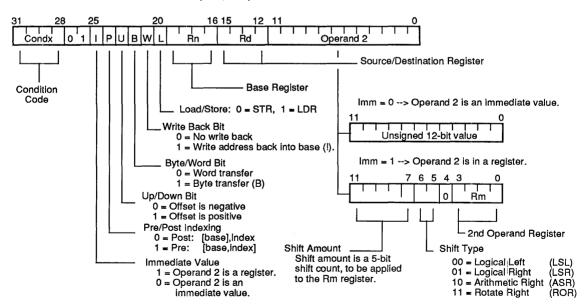

radically reduced instruction set containing a total of only 46 different operations. Unlike most others, all instructions occupy one 32-bit word of memory. In keeping with the tradition of RISC methodology, the processor is implemented as with a single-cycle execution unit and a load/store architecture. The basic addressing mode supported is indexed from a base register, with several different methods of index specification. The index can be a 12-bit immediate value contained within the instruction, or another register (optionally shifted in some

## **TABLE 1. VL86C010 INSTRUCTIONS**

| PROCESSOR CYCLES   PROCESSOR CYCLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IADEL I. VEGOGGIGI          |                 |                            |                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|----------------------------|------------------|

| Add with Carry         ADC         Rd:=Rn + Shift(Rm) + C         1S           Add         ADD         Rd:=Rn + Shift(Rm)         1S           And         AND         Rd:=Rn + Shift(Rm)         1S           Bit Clear         BIC         Rd:=Rn + Not Shift(Rm)         1S           Compare Negative         CMN         Shift(Rm) + Rn         1S           Compare         CMP         Rn - Shift(Rm)         1S           Exclusive - OR         EOR         Rd:=Rn XOR Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Sh + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs         16S max           Move Mogative         MVN         Rd:=Rn * Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn * Shift(Rm)         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Reverse Subtract with Carry         SBC         Rd:=Rn * Shift(Rm)         1S                                                                                                 | <u>FUNCTION</u>             | <b>MNENOMIC</b> | <u>OPERATION</u>           | PROCESSOR CYCLES |

| Add         ADD         Rd:=Rn + Shift(Rm)         1S           And         AND         Rd:=Rn • Shift(Rm)         1S           Bit Clear         BIC         Rd:=Rn • Not Shift(Rm)         1S           Compare Negative         CMN         Shift(Rm) + Rn         1S           Compare         CMP         Rn - Shift(Rm)         1S           Exclusive - OR         EOR         Rd:=Rn XOR Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn NOR Shift(Rm)         1S           Test Masked         TST         Rn • Shift(Rm)         1S                                                                                                                                 | Data Processing             |                 |                            |                  |

| And         AND         Rd:=Rn · Shift(Rm)         1S           Bit Clear         BIC         Rd:=Rn · Not Shift(Rm)         1S           Compare Negative         CMN         Shift(Rm) + Rn         1S           Compare         CMP         Rn - Shift(Rm)         1S           Exclusive - OR         EOR         Rd:=Rn XOR Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test M                                                                                                                      | Add with Carry              | ADC             | Rd:=Rn + Shift(Rm) + C     | 18               |

| Bit Clear         BIC         Rd:=Rn · Not Śhift(Rm)         1S           Compare Negative         CMN         Shift(Rm) + Rn         1S           Compare         CMP         Rn - Shift(Rm)         1S           Exclusive - OR         EOR         Rd:=Rn XOR Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn         1 S           Subtract with Carry         SBC         Rd:=Shift(Rm) - 1 + C         1S           Subtract Carry         SBC         Rd:=Rn - Shift(Rm)         1 S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn **o*shift(Rm)         1S                                                                                                             | Add                         | ADD             | Rd:=Rn + Shift(Rm)         | 18               |

| Compare Negative         CMN         Shift(Rm) + Rn         1S           Compare         CMP         Rn – Shift(Rm)         1S           Exclusive - OR         EOR         Rd:=Rn XOR Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=Rn OR Shift(Rm)         1S           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm)         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm)         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Data Transfer         LOR         Rd:=Effective address:= Rd         2                                                                                            | And                         | AND             | Rd:=Rn • Shift(Rm)         | 18               |

| Compare         CMP         Rn - Shift(Rm)         1S           Exclusive - OR         EOR         Rd:=Rn XOR Shift(Rm)         1S           Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn         1 S           Subtract with Carry         SBC         Rd:=Shift(Rm) - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm)         1 S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1 S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S                                                                                                 | Bit Clear                   | BIC             | Rd:=Rn • Not Shift(Rm)     | 18               |

| Exclusive - OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Compare Negative            | CMN             | Shift(Rm) + Rn             | 18               |

| Multiply with Accumulate         MLA         Rn:=Rm * Rs + Rd         16S max           Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm) - 1 + C         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn * Shift(Rm)         1S           Data Transfer         Load Flegister         LDR         Rd:=Effective address:= Rd         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer         Load Multiple         LDM         Rist:=Effective Address:=Rlist         (n**+1)S + 1N <t< td=""><td>Compare</td><td>CMP</td><td>Rn - Shift(Rm)</td><td>18</td></t<> | Compare                     | CMP             | Rn - Shift(Rm)             | 18               |

| Move         MOV         Rn:=Shift(Rm)         1S           Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=NOT Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Rn OR Shift(Rm)         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm)         1 S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1 S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn * Shift(Rm)         1S           Data Transfer         Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer         Load Multiple         LDM         Rlist:=Effective Address:=Rlist         (n**+1)S + 1N           Load Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump         Branch         B         PC:=PC+Offset         2S + 1N <td>Exclusive - OR</td> <td>EOR</td> <td>Rd:=Rn XOR Shift(Rm)</td> <td>15</td> | Exclusive - OR              | EOR             | Rd:=Rn XOR Shift(Rm)       | 15               |

| Multiply         MUL         Rn:=Rm * Rs         16S max           Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm) - 1 + C         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn * Shift(Rm)         1S           Data Transfer           Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer           Load Multiple         LDM         Rlist:=Effective Address:=Rlist         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (2S + 1N           Jump         Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link                                                                                                           | Multiply with Accumulate    | MLA             | Rn:=Rm * Rs + Rd           | 16S max          |

| Move Negative         MVN         Rd:=NOT Shift(Rm)         1S           Inclusive - OR         ORR         Rd:=Rn OR Shift(Rm)         1S           Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm) - 1 + C         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn * Shift(Rm)         1S           Data Transfer           Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer           Load Multiple         LDM         Rlist:=Effective Address         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump           Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                   | Move                        | MOV             | Rn:=Shift(Rm)              | 18               |

| Inclusive - OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Multiply                    | MUL             | Rn:=Rm * Rs                | 16S max          |

| Reverse Subtract         RSB         Rd:=Shift(Rm) - Rn         1S           Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm) - 1 + C         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn * Shift(Rm)         1S           Data Transfer           Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer           Load Multiple         LDM         Rlist:=Effective Address         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump           Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                        | Move Negative               | MVN             | Rd:=NOT Shift(Rm)          | 18               |

| Reverse Subtract with Carry         RSC         Rd:=Shift(Rm) - Rn - 1 + C         1S           Subtract with Carry         SBC         Rd:=Rn - Shift(Rm) - 1 + C         1S           Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn * Shift(Rm)         1S           Data Transfer           Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer           Load Multiple         LDM         Rlist:=Effective Address         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump           Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                     | Inclusive - OR              | ORR             | Rd:=Rn OR Shift(Rm)        | 1S               |

| Subtract with Carry SBC Rd:=Rn - Shift(Rm) - 1 + C 1S Subtract SUB Rd:=Rn - Shift(Rm) 1S Test for Equality TEQ Rn XOR Shift(Rm) 1S Test Masked TST Rn • Shift(Rm) 1S  Data Transfer Load Register LDR Rd:=Effective address 2S + 1N Store Register STR Effective address:= Rd 2N  Multiple Data Transfer Load Multiple Data Transfer Load Multiple STM Rlist:=Effective Address (n*+1)S + 1N Store Multiple STM Effective Address:=Rlist (n*+1)S + 2N  Jump Branch B PC:=PC+Offset 2S + 1N Branch and Link BL R14:=PC, PC:= PC+Offset 2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reverse Subtract            | RSB             | Rd:=Shift(Rm) - Rn         | 1S               |

| Subtract         SUB         Rd:=Rn - Shift(Rm)         1S           Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn • Shift(Rm)         1S           Data Transfer           Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer           Load Multiple         LDM         Rlist:=Effective Address         (n*+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n*+1)S + 2N           Jump           Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reverse Subtract with Carry | RSC             |                            | 1S               |

| Test for Equality         TEQ         Rn XOR Shift(Rm)         1S           Test Masked         TST         Rn • Shift(Rm)         1S           Data Transfer         Load Register         LDR         Rd:=Effective address         2S + 1N           Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer         Load Multiple Data Transfer           Load Multiple         LDM         Rlist:=Effective Address         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump         Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Subtract with Carry         | SBC             | Rd:=Rn - Shift(Rm) - 1 + C | 1S               |

| Test Masked  TST  Rn • Shift(Rm)  1S  Data Transfer  Load Register  Store Register  STR  Effective address:= Rd  2N  Multiple Data Transfer  Load Multiple  LDM  Rlist:=Effective Address  (n**+1)S + 1N  Store Multiple  STM  Effective Address:=Rlist  (n**+1)S + 2N  Jump  Branch  B  PC:=PC+Offset  BL  R14:=PC, PC:= PC+Offset  2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Subtract                    | SUB             | Rd:=Rn - Shift(Rm)         | 1S               |

| Data Transfer Load Register LDR Rd:=Effective address 2S + 1N Store Register STR Effective address:= Rd 2N  Multiple Data Transfer Load Multiple LDM Rlist:=Effective Address (n*+1)S + 1N Store Multiple STM Effective Address:=Rlist (n*+1)S + 2N  Jump Branch B PC:=PC+Offset 2S + 1N Branch and Link BL R14:=PC, PC:= PC+Offset 2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Test for Equality           | TEQ             | Rn XOR Shift(Rm)           | 1S               |

| Load Register  Store Register  STR  Effective address:= Rd  2N  Multiple Data Transfer  Load Multiple  LDM  Rlist:=Effective Address  (n**+1)S + 1N  Store Multiple  STM  Effective Address:=Rlist  (n**+1)S + 2N  Jump  Branch  B  PC:=PC+Offset  BL  R14:=PC, PC:= PC+Offset  2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Test Masked                 | TST             | Rn • Shift(Rm)             | 1S               |

| Load Register  Store Register  STR  Effective address:= Rd  2N  Multiple Data Transfer  Load Multiple  LDM  Rlist:=Effective Address  (n**+1)S + 1N  Store Multiple  STM  Effective Address:=Rlist  (n**+1)S + 2N  Jump  Branch  B  PC:=PC+Offset  BL  R14:=PC, PC:= PC+Offset  2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data Transfer               |                 |                            |                  |

| Store Register         STR         Effective address:= Rd         2N           Multiple Data Transfer         Load Multiple         LDM         Rlist:=Effective Address         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump         Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | IDB             | Rd:-Effective address      | 29 ± 1N          |

| Multiple Data Transfer  Load Multiple LDM Rlist:=Effective Address (n**+1)S + 1N Store Multiple STM Effective Address:=Rlist (n**+1)S + 2N  Jump  Branch B PC:=PC+Offset 2S + 1N Branch and Link BL R14:=PC, PC:= PC+Offset 2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |                 |                            |                  |

| Load Multiple         LDM         Rlist:=Effective Address         (n**+1)S + 1N           Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump         Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clore Hegister              | 0111            | E11001170 add1633.2 1 td   | 214              |

| Store Multiple         STM         Effective Address:=Rlist         (n**+1)S + 2N           Jump         Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Multiple Data Transfer      |                 |                            |                  |

| Jump         Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Load Multiple               | LDM             | Rlist:=Effective Address   | (n**+1)S + 1N    |

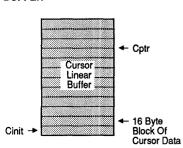

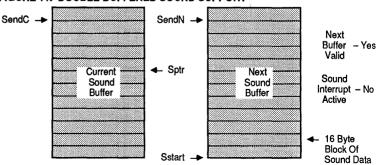

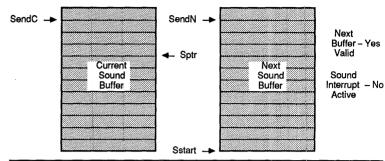

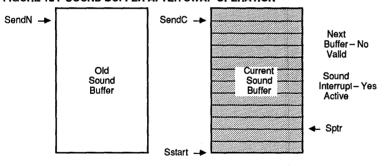

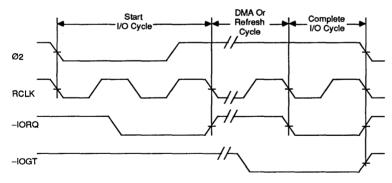

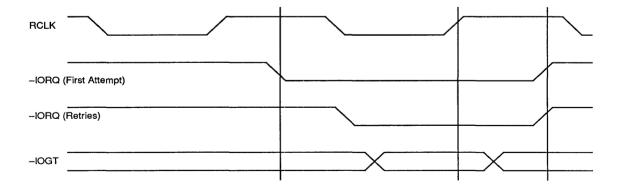

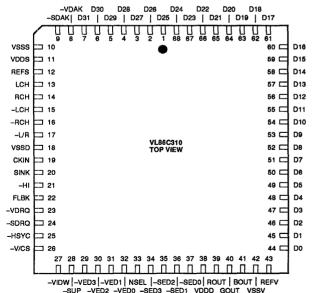

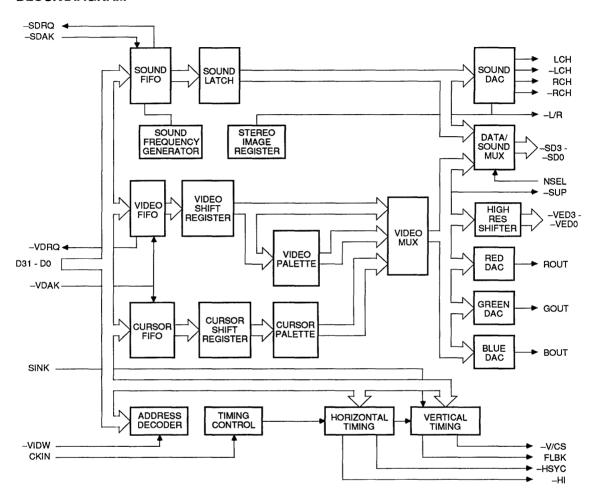

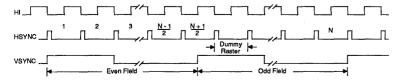

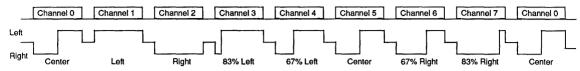

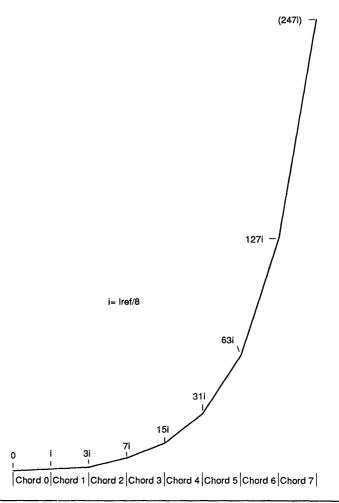

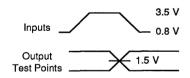

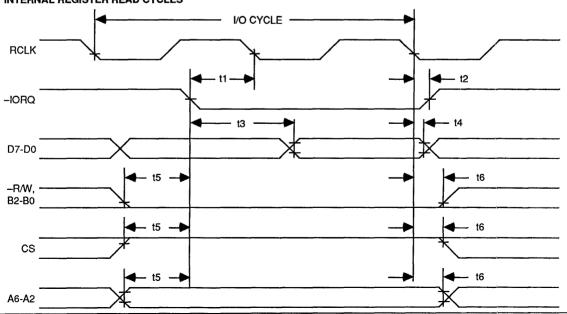

| Branch         B         PC:=PC+Offset         2S + 1N           Branch and Link         BL         R14:=PC, PC:= PC+Offset         2S + 1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Store Multiple              | STM             | Effective Address:=Rlist   | (n**+1)S + 2N    |